Forschungsberichte aus dem Institut für Nachrichtentechnik der Universität Karlsruhe (TH)

Arnd-Ragnar Rhiemeier

# ■ Modulares Software Defined Radio

Band 9

Copyright: Institut für Nachrichtentechnik

Universität Karlsruhe (TH), 2004

Druck: Druckerei Ernst Grässer, Humboldtstr. 1

76131 Karlsruhe, Tel. 0721/615050

ISSN: 1433-3821

# Forschungsberichte aus dem Institut für Nachrichtentechnik der Universität Karlsruhe (TH)

Herausgeber: Prof. Dr. rer. nat. Friedrich Jondral

Band 1 Marcel Kohl

Simulationsmodelle für die Bewertung von Satellitenübertragungsstrecken im 20/30 GHz Bereich

Band 2 Christoph Delfs

Zeit-Frequenz-Signalanalyse: Lineare und quadratische Verfahren sowie vergleichende Untersuchungen zur Klassifikation von Klaviertönen

Band 3 Gunnar Wetzker

Maximum-Likelihood Akquisition von Direct Sequence Spread-Spectrum Signalen

Band 4 Anne Wiesler

Parametergesteuertes Software Radio für Mobilfunksysteme

Band 5 Karl Lütjen

Systeme und Verfahren für strukturelle Musteranalysen mit Produktionsnetzen

Band 6 Ralf Machauer

**Multicode-Detektion im UMTS**

Band 7 Gunther M. A. Sessler

Schnell konvergierender Polynomial Expansion Multiuser Detektor mit niedriger Komplexität

Band 8 Henrik Schober

Breitbandige OFDM Funkübertragung bei hohen Teilnehmergeschwindigkeiten

# Forschungsberichte aus dem Institut für Nachrichtentechnik der Universität Karlsruhe (TH)

Herausgeber: Prof. Dr. rer. nat. Friedrich Jondral

Band 9 Arnd-Ragnar Rhiemeier

Modulares Software Defined Radio

## Vorwort des Herausgebers

Seit Joseph Mitola den Begriff Software Radio (SR) in die Diskussion gebracht hat, sind fast 15 Jahre vergangen. Es wurde schnell deutlich, dass die Realisierung idealer SRs (breitbandige Abtastung des Antennenausgangs) problematisch ist und für die absehbare Zukunft auch bleibt. Als praktische Alternative bietet sich das Software Defined Radio (SDR) an, das die Digitalisierung des Empfangssignals erst nach einer Zwischenfrequenzfilterung oder direkt im komplexen Basisband vornimmt.

Zur Konstruktion von SDRs wurden bisher verschiedene Wege eingeschlagen. Einer dieser Wege ist das Parameter Controlled (PaC-) SDR, in dem die gesamte Verarbeitung des Transceivers über einen Parametersatz, der im Wesentlichen einen Standard darstellt, gesteuert wird<sup>1</sup>. Voraussetzung für diesen Ansatz ist die Kenntnis der zu unterstützenden Standards. Der Austausch von Signalverarbeitungseinheiten (z.B. von En- und Decodern) ist daher in einem PaC-SDR schwierig.

Um die Diskussion über SDRs auf einer höheren Ebene führen zu können, muss insbesondere von den Signalverarbeitungsalgorithmen der physikalischen Schicht abstrahiert werden. Dazu wird die gesamte Signalverarbeitung eines Senders bzw. eines Empfängers als gerichteter Graph dargestellt, in dessen Knoten Software Module ablaufen. Diese Module sind in einem SDR nicht fest vorgegeben sondern in einem gewissen Rahmen austauschbar. Aus dieser Vorstellung stammt der Begriff Modulares Software Defined Radio (Mod-SDR).

Charakteristische Größen für die Module sind ihre Laufzeit und ihr Speicherbedarf. Im Weiteren wird nun davon ausgegangen, dass die Realisierung von Mod-SDRs eine Mehrprozessorhardware voraussetzt. So ergibt sich natürlich die Frage nach der Bewertung verschiedener modularer Realisierungen desselben Übertragungsverfahrens auf einer Mehrprozessorplattform. Die vorliegende Arbeit misst die Qualität der beschriebenen Entwicklungen nicht wie üblich an der Darstellung der mittleren Bitfehlerrate über dem Signal-Rausch-Verhältnis sondern schlägt andere Maße wie den (relativen) Speedup bei Mehrprozessorsystemen, die durch die Signalverarbeitung verursachte Laufzeitverzögerung oder den Speicherbedarf als Gütemaße vor.

<sup>&</sup>lt;sup>1</sup>Anne Wiesler: Parametergesteuertes Software Radio für Mobilfunksysteme. Dissertation, Forschungsberichte aus dem Institut für Nachrichtentechnik der Universität Karlsruhe (TH), Band 4, 2001, ISSN 1433-3821

Mit seiner Dissertation Modulares Software Defined Radio betritt Herr Rhiemeier Neuland bei der Beschreibung und Entwicklung von Funkgeräten. Dabei bestätigt er einen Trend, der unterschwellig seit der Verabschiedung der Software Communications Architecture (SCA) durch das SDR Forum im Jahr 1999 zu spüren ist: Der Entwickler für die digitale Signalverarbeitung in Funkgeräten muss in Zukunft neben der Algorithmik sender- und empfängerspezifischer Aufgaben (Kanalschätzung, Entzerrung, Modulation/Demodulation, Encodierung/Decodierung etc.) die objektorientierte Programmierung im Auge haben, um höchste Flexibilität in seine Geräte implementieren zu können.

Karlsruhe im Dezember 2004 Friedrich Jondral

## Modulares Software Defined Radio

Zur Erlangung des akademischen Grades eines

#### **DOKTOR-INGENIEURS**

von der Fakultät für

Elektrotechnik und Informationstechnik

der Universität Fridericiana Karlsruhe

genehmigte

#### **DISSERTATION**

von

Dipl.-Ing. Arnd-Ragnar Rhiemeier

aus

Bochum

Tag der mündlichen Prüfung:

Hauptreferent:

Prof. Dr. rer. nat. Friedrich Jondral

Korreferent:

Prof. Dr. rer. nat. Hartmut Schmeck

## **Danksagung**

Die vorliegende Dissertation entstand im Rahmen meiner Tätigkeit als wissenschaftlicher Mitarbeiter am Institut für Nachrichtentechnik der Universität Karlsruhe (TH). Mein besonderer Dank gilt Herrn Prof. Dr. rer. nat. Friedrich Jondral, dem Leiter dieses Instituts, für sein Vertrauen auf meine Fähigkeiten in Forschung und Lehre ebenso wie für die sehr gute Zusammenarbeit und seine Unterstützung bei der Durchführung meiner Arbeit. Dazu gehört jede einzelne Diskussion, die wir im Laufe der Zeit geführt haben. Für seine Bereitschaft, das Hauptreferat zu übernehmen, danke ich ebenfalls.

Herrn Prof. Dr. rer. nat. Hartmut Schmeck, Leiter des Instituts für Angewandte Informatik und Formale Beschreibungsverfahren, Fakultät für Wirtschaftswissenschaften der Universität Karlsruhe (TH), danke ich für sein Interesse an meiner Arbeit und für die Übernahme des Korreferats.

Allen Kollegen, mit denen ich im Laufe meiner Tätigkeit am Institut für Nachrichtentechnik zusammengearbeitet habe, möchte ich meinen Dank aussprechen. Besonders angenehm war die Zusammenarbeit mit meinem Kollegen Timo Weiß, dessen unkomplizierte und zuverlässige Art ich sehr schätze. Des Weiteren behalte ich Herrn Dr.-Ing. Ralf Machauer stets in guter Erinnerung. Er hat in wichtigen Momenten das Wenige und Richtige gesagt, das ihn als einen hervorragenden Kollegen auszeichnet.

Mein Dank gilt auch Herrn Dipl.-Ing. (FH) Reiner Linnenkohl für sein tägliches Engagement beim Betrieb aller Rechner- und Netzsysteme. Weiterhin möchte ich unsere Sekretärinnen, besonders Frau Gabriele Kuntermann, und unsere Grafikerin, Frau Angelika Olbrich, in meinen Dank einbeziehen. Sie alle tragen auf ihre Weise zu der sehr guten Arbeitsatmosphäre am Institut für Nachrichtentechnik bei.

Schließlich danke ich ganz besonders meinen Eltern, deren Vertrauen und Rat mir stets eine wertvolle Unterstützung waren, und meiner zukünftigen Frau Verena für ihr Verständnis.

## Zusammenfassung

Seit dem Bekanntwerden des Begriffs Software Radio vor rund 10 Jahren sind zahlreiche Beiträge auf diesem Gebiet veröffentlicht worden, sowohl zum Konzept des idealen Software Radio als auch zu realisierbaren Kompromisslösungen, die unter dem Begriff Software Defined Radio (SDR) zusammengefasst werden. Bei nahezu allen Arbeiten steht lediglich ein Teilaspekt der gesamten Signalverarbeitung im Vordergrund, und eine bestimmte Entwurfsaufgabe wird isoliert von anderen Vorgängen in einem SDR-Endgerät betrachtet. Insbesondere die Beiträge zur Signalverarbeitung im komplexen Basisband eines SDR konzentrieren sich stark auf die Algorithmen der Nachrichtentechnik. Das Zusammenspiel vieler verschiedener Algorithmen in einem größeren Verbund logischer Abhängigkeiten und die Abbildung derartiger Strukturen auf ein flexibles Hardware-System sind in der SDR-Literatur bisher unbeachtet geblieben.

Unter dem Begriff des Modularen Software Defined Radio (Mod-SDR) werden in dieser Arbeit alle Arten von SDRs verstanden, bei denen sowohl die Hardware als auch die Software modular aufgebaut ist. Eine wesentliche Grundannahme besteht darin, dass das SDR-Konzept am ehesten auf einer einfach erweiterbaren Multiprozessor-Hardware in die Realität umzusetzen sein wird. Unter Software werden alle Formen von ausführbarem Maschinencode verstanden, der Aufgaben der digitalen Signalverarbeitung auf der physikalischen Schicht eines mobilen Funkgerätes bewältigt. Allgemein gültige Richtlinien für den Entwurf und Betrieb solcher Mod-SDRs herzuleiten ist das Ziel der vorliegenden Arbeit.

Das SDR-Konzept verspricht eine große Flexibilität bei der drahtlosen Anbindung mobiler Endgeräte an das Festnetz. Die vielfältigen neuen Anwendungsmöglichkeiten, die mit dieser Flexibilität einhergehen, werden in der Literatur nur all zu oft als die großen Vorteile von SDR angeführt. Die Nachteile von SDR sind zwar durchaus bekannt, aber es wird üblicherweise angenommen, dass sich ihr Gewicht im Zuge des Fortschritts in der Mikro- und Nanotechnologie stetig verringern wird. Insgesamt existiert eine Vielzahl unterschiedlichster Sichtweisen zum Thema SDR, und daher gilt es, zunächst alle wesentlichen technischen und wirtschaftlichen Aspekte für den Einsatz flexibler, modularer SDR-Systeme zu verstehen, um dann entsprechende Schlussfolgerungen für die Signalverarbeitung auf der physikalischen Schicht zu ziehen: Mod-SDR wird im Rahmen dieser Arbeit als der Prototyp eines eingebetteten Echtzeitsystems in der Nachrichtentechnik interpretiert.

Diese Sichtweise erfordert zuerst eine neuartige und abstrakte Modellbildung, vor allem für die Signalverarbeitungssoftware. Das in dieser Arbeit eingeführte Modell bedient sich gerichteter azyklischer Graphen und weist den entscheidenden Vorteil auf, sowohl vom Stand der Technik als auch von konkreten Realisierungen heutiger Mobilfunkstandards unabhängig zu sein. In einem zweiten Schritt wird die Entwurfsaufgabe auf der physikalischen Schicht eines Mod-SDR mathematisch präzise erfasst und dabei formal in das Gebiet der linearen ganzzahligen Optimierung eingeordnet. Es stellt sich schnell heraus, dass das Auffinden der optimalen Lösung NP-schwer und damit für den praktischen Einsatz in einem Mod-SDR nicht geeignet ist.

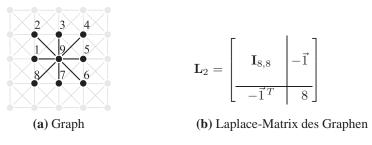

Um in der Praxis schnell eine hinreichend gute Lösung für die Mod-SDR-Entwurfsaufgabe hervorzubringen, bedarf es verschiedener Methoden der Partitionierung und der Ablaufplanung. In dieser Arbeit werden dazu folgende Ansätze verwendet: Erstens der Algorithmus von Hu, der unter speziellen Randbedingungen die parallelen Strukturen eines Graphen optimal ausnutzt. Zweitens ein heuristisches Verfahren nach Kernighan und Lin, das eine lokale Suchstrategie im Raum der Lösungen verfolgt. Drittens die spektrale Partitionierung, die einen Graphen als Ganzes bewertet und eine Anwendung der algebraischen Graphentheorie darstellt.

Eine radikal andere Betriebsart wird von den Verfahren Graph Duplication Pipelining (GDP) und Half-Frame Pipelining (HFP) angestrebt. Die entsprechende Vorgehensweise in der Partitionierung und Ablaufplanung ist überaus einfach und dennoch sehr erfolgreich. Aus den Untersuchungen zur Leistungsfähigkeit der verschiedenen Ansätze geht das Pipelining-Prinzip als die zentrale Richtlinie für den Entwurf und Betrieb von Mod-SDR-Systemen hervor.

# Inhaltsverzeichnis

| 1 | Einl | eitung                             |                                            | 1  |  |

|---|------|------------------------------------|--------------------------------------------|----|--|

|   | 1.1  | Randbedingungen                    |                                            |    |  |

|   | 1.2  | 2 Modulares Software Defined Radio |                                            |    |  |

|   | 1.3  | Bisher                             | rige Arbeiten im Bereich Software Radio    | 8  |  |

|   | 1.4  | Ziel ui                            | nd Aufbau der vorliegenden Arbeit          | 11 |  |

| 2 | Mod  | dellbild                           | ung                                        | 13 |  |

|   | 2.1  | Hardw                              | vare-Modell                                | 14 |  |

|   |      | 2.1.1                              | Symmetrischer Multiprozessor               | 15 |  |

|   |      | 2.1.2                              | Einsatz eines Coprozessors                 | 18 |  |

|   | 2.2  | Softwa                             | are-Modelle                                | 19 |  |

|   |      | 2.2.1                              | Echtzeitanforderungen im Mobilfunk         | 23 |  |

|   |      | 2.2.2                              | Gerichtete Graphen und diskrete Laufzeiten | 25 |  |

|   |      | 2.2.3                              | Stochastisches Laufzeit-Modell             | 27 |  |

|   |      | 2.2.4                              | Erweitertes Ressourcen-Laufzeit-Modell     | 30 |  |

|   |      | 2.2.5                              | Familien von UMTS-Graphen                  | 33 |  |

|   |      | 2.2.6                              | Zufallsgraphen                             | 37 |  |

|   | 2.3  | Zusam                              | nmenfassung                                | 38 |  |

| 3 | Die  | Entwur                             | rfsaufgabe                                 | 41 |  |

|   | 3.1  | Formu                              | llierung als Optimierungsaufgabe           | 41 |  |

|   | 3.2  | Subop                              | timale Ablaufplanung und Speedup           | 47 |  |

|   | 3.3  | Ergebi                             | nisse mit einfachen Graphen                | 49 |  |

|   | 3 4  | 7usam                              | nmenfassung                                | 68 |  |

| 4 | Part | rtitionierung und Ablaufplanung |                                                         |     |  |

|---|------|---------------------------------|---------------------------------------------------------|-----|--|

|   | 4.1  | Grund                           | ndsätzliches Vorgehen                                   |     |  |

|   | 4.2  | Ansätz                          | nsätze zur Partitionierung                              |     |  |

|   |      | 4.2.1                           | Implizite Partitionierung mit dem Hu-Algorithmus        | 74  |  |

|   |      | 4.2.2                           | Kernighan-Lin-Algorithmus                               | 75  |  |

|   |      | 4.2.3                           | Spektrale Partitionierung                               | 80  |  |

|   |      | 4.2.4                           | Graphenverdoppelung                                     | 85  |  |

|   | 4.3  | Ansätz                          | ze zur Ablaufplanung                                    | 86  |  |

|   |      | 4.3.1                           | Hu-Scheduling ohne und mit Pipelining                   | 86  |  |

|   |      | 4.3.2                           | Graph Duplication Pipelining                            | 91  |  |

|   |      | 4.3.3                           | Half-Frame Pipelining                                   | 96  |  |

|   | 4.4  | Zusam                           | nmenfassung                                             | 100 |  |

| 5 | Leis | tungsfä                         | higkeit von Mod-SDR                                     | 101 |  |

|   | 5.1  | Leitun                          | gsvermittelte Dienste                                   | 102 |  |

|   |      | 5.1.1                           | Grundlegende Mod-SDR-Systemparameter                    | 102 |  |

|   |      | 5.1.2                           | Vergleich der Partitionierungsansätze ohne Pipelining   | 112 |  |

|   |      | 5.1.3                           | Vergleich der Partitionierungsansätze mit zwei Bussen   | 114 |  |

|   |      | 5.1.4                           | Vergleich der Partitionierungsansätze mit Pipelining    | 116 |  |

|   |      | 5.1.5                           | Ergebnisse mit Graphenverdoppelung                      | 118 |  |

|   |      | 5.1.6                           | Leistungseffizienter Betrieb eines Coprozessors         | 121 |  |

|   |      | 5.1.7                           | Familien von UMTS-Graphen                               | 131 |  |

|   |      | 5.1.8                           | Verschiedenartig strukturierte Graphen                  | 134 |  |

|   | 5.2  | Paketo                          | orientierte Dienste                                     | 143 |  |

|   |      | 5.2.1                           | Ergebnisse mit Half-Frame Pipelining                    | 143 |  |

|   |      | 5.2.2                           | Ergebnisse mit Graph Duplication Pipelining             | 145 |  |

|   |      | 5.2.3                           | Relevanz der Ergebnisse für etablierte WLAN-Standards . | 148 |  |

|   |      |                                 |                                                         |     |  |

| A Laplace-Operatoren in der digitalen Bildverarbeitung | 155 |

|--------------------------------------------------------|-----|

| Abkürzungen, Terminologie und Formelzeichen            | 157 |

| Literaturverzeichnis                                   | 165 |

| Studien- und Diplomarbeiten                            | 174 |

| Index                                                  | 175 |

| Lebenslauf                                             | 177 |

## 1 Einleitung

Der Begriff Software Radio ist 1995 zum ersten Mal in das Bewusstsein einer breiten Öffentlichkeit gerückt [61]. Der Begriff wurde wesentlich von Mitola geprägt, der sich bereits zuvor [59, 60] mit der Flexibilisierung und der Interoperabilität von Mobilfunkgeräten beschäftigt hatte. Die Grundidee besteht darin, die gesamte verfügbare Information innerhalb eines breiten Frequenzbandes zunächst vollständig zu digitalisieren und dann abhängig von den Bedürfnissen des Nutzers und seiner aktuellen Kommunikationssituation beliebige Unterbänder zu demodulieren und deren Information weiter zu verarbeiten. Dabei können in den Unterbändern verschiedenste Mobilfunkstandards angetroffen werden.

Um verschiedenste Standards bedienen zu können, muss die Signalverarbeitungskette sehr flexibel gehalten werden. Insbesondere ist es unmöglich, zur Zeit des Systementwurfs alle Nutzersituationen vorherzusehen und Spezialhardware für alle möglichen Mobilfunkstandards bereitzuhalten. Auch ist es beim Entwurf von Spezialhardware sehr oft nicht möglich, denjenigen Änderungen zu folgen, die sich aus einem laufenden Standardisierungsprozess ergeben. Zuletzt ist es unmöglich, die Entwicklung völlig neuartiger Mobilfunkstandards vorherzusehen und Hardware dafür zu entwickeln, weil die Signalverarbeitungskette zum Zeitpunkt der Hardware-Entwicklung schlichtweg unbekannt ist.

Die Lösung für dieses Problem besteht darin, die Signalverarbeitung nicht mehr durch Spezialhardware zu bewältigen, sondern mit Hilfe von Software. Diese Software soll auf einer allgemein gültigen Hardware ablaufen. Weil die Funktionalität des Gerätes wesentlich durch Software definiert wird, spricht man von einem idealen Software Radio.

Die Vorteile liegen in der großen Flexibilität von Software und in der Wiederverwendung von Hardware-Komponenten für verschiedenste Mobilfunkstandards. Software kann eingesetzt werden, um alle möglichen Signalverarbeitungsaufgaben auf allen Schichten des OSI-Modells [41] zu lösen. Von besonderem Interesse für die Nachrichtentechnik sind jedoch die Aufgaben der beiden untersten Schichten, also der physikalischen Schicht und der Datensicherungsschicht. Gerade die Realisierung dieser Schichten in Software erlaubt erst die äußerst flexible drahtlose Anbindung eines Nutzers an das Festnetz.

Die Betreiber von Mobilfunknetzen könnten durchaus ein Interesse an der Verbreitung von Software Radios haben [33], weil die Nutzer solcher Geräte entsprechend ihrer momentanen Mobilität verschiedene Arten des drahtlosen Zugangs zum Netz ein und desselben Betreibers wählen können und erwartet wird, dass sich auf diese Weise die Verbindungszeiten im Durchschnitt erhöhen. Zusätzlich nennen Netzbetreiber die Möglichkeiten für ein differenziertes Diensteangebot sowie einfache Fehlerbehebung, Wartung und Aufrüstung von Geräten (vorrangig in Basisstationen) als Vorteile von Software Radio [32].

Für mobile Endgeräte liegen die Nachteile eines idealen Software Radios eindeutig in der erhöhten Leistungsaufnahme und in den hohen Stückkosten flexibler Hardware-Komponenten (DSP, FPGA) im Vergleich zu Spezialhardware (ASIC, ASSP). Eine umfassende Sammlung von Beiträgen zu Hardware-Komponenten und zur Abwägung von Vor- und Nachteilen von idealen Software Radios findet sich in [45]. Im Folgenden sollen lediglich zwei Argumentationslinien herausgegriffen werden, die letztlich auf die Modelle und Lösungsansätze der vorliegenden Arbeit geführt haben.

Aus technischer Sicht ist es nicht sinnvoll, ein sehr breites Frequenzband zu digitalisieren und dann die Auswahl eines relativ schmalen Nutzbandes mit Hilfe von Digitalfiltern vorzunehmen. Dazu wäre nicht nur ein A/D-Umsetzer mit extrem hoher Abtastrate notwendig, sondern gleichzeitig eine große Wortbreite der gewandelten Werte, um die hohe Dynamik der Empfangssignale im gesamten breiten Frequenzband zu beherrschen. Es ist bekannt [108], dass zwischen Abtastrate und Wortbreite eines A/D-Umsetzers eine Beziehung herrscht, die dem Zeit-Bandbreite-Produkt in der Nachrichtentechnik ähnelt: Man kann A/D-Umsetzer herstellen, die entweder eine hohe Abtastrate bei kleiner Wortbreite erzielen oder umgekehrt, aber nicht gleichzeitig beides in unbeschränktem Maße. Bei konstanter Abtastrate verschiebt sich die Technologiegrenze alle 8 Jahre etwa um 1,5 bit [108]. Demnach ist nicht zu erwarten, dass sich das Wandlerproblem durch schlichtes Abwarten in den kommenden Jahren lösen wird. Zudem ist die Herstellung solcher Wandler zunächst sehr teuer und die elektrische Leistungsaufnahme enorm. Der technologische Aufwand ist ebenso wenig zu rechtfertigen wie die erhöhte Leistungsaufnahme, wenn man bedenkt, dass unmittelbar nach der Wandlung durch die Reduktion der Bandbreite auf ein relativ schmales Nutzband der Großteil aller digitalisierten Informationen bereits wieder verworfen wird. Das ideale Software Radio ist damit per se teuer und bezüglich der elektrischen Leistungsaufnahme ineffizient.

Aus betriebswirtschaftlicher Sicht ist es für die Hersteller von Endgeräten äußerst

zweifelhaft, ob sich mit einem idealen Software Radio ein tragfähiges Geschäftsmodell aufbauen lässt. Angenommen, ein solches Gerät kann hergestellt und vom Endkunden zu einem akzeptablen Preis gekauft werden. Dann könnte es auch möglich werden, ein und dasselbe Gerät allein durch den Austausch von Software zu künftigen Mobilfunkstandards kompatibel zu machen. Signalverarbeitungssoftware für Software Radio würde zu einem neuen Markt werden, der auch für Dritte offen ist, so z.B. für unabhängige Software-Anbieter. Sicherlich besteht die Möglichkeit, dass der Hersteller eines Software Radios nicht nur als Hardware- sondern auch als Software-Anbieter am Markt auftritt. Jedoch würde sich der ursprüngliche Hersteller von Endgeräten dadurch selbst unter Druck setzen: Er müsste seine eigenen Kompetenzen erweitern und sich gleichzeitig der Konkurrenz durch Dritte stellen. Beides birgt unternehmerische Risiken.

Die geschilderte Art der Aufrüstbarkeit durch Software (*engl.* future upgradability) wurde lange Zeit als einer der Vorzüge von Software Radios angeführt. Nach der vorangegangenen Überlegung ist in der Tat jedoch das Gegenteil der Fall. Dennoch zeigen namhafte Hersteller von mobilen Endgeräten Interesse an dem Thema Software Radio [91, 116, 117]. Dabei wird vor allem auf die Flexibilität hingewiesen, die ein Software Radio mit sich bringt (*engl.* "Flexibility sells, future upgradability does not." [16]). Dass es sich hierbei im Wesentlichen um die Flexibilität der Unternehmen handelt und nicht um die des Endkunden, wird im folgenden Abschnitt erläutert.

### 1.1 Randbedingungen

Traditionell wurden Funkgeräte entworfen und gebaut, um die Anforderungen einer bestimmten Nutzergruppe (z.B. Militär, BOS, Luftfahrt, Privatpersonen, Nachrichtenagenturen) zu befriedigen, die unter festgelegten Randbedingungen und über eine bestimmte Klasse von Kanälen kommunizieren. Sprachkommunikation stand dabei zunächst im Vordergrund. Folglich waren viele Aspekte in Bezug auf die analogen Hochfrequenzbaugruppen und die digitale Signalverarbeitung im Basisband wohldefiniert. Produkte wurden selbstverständlich mit Spezialhardware realisiert, insbesondere für einen Massenmarkt wie den zivilen Mobilfunk der zweiten Generation. Mittlerweile sind die Nutzeranforderungen jedoch alles andere als wohldefiniert, und dafür gibt es mehrere Gründe: Der wachsende Anteil von Daten- und Multimediadiensten (die den Anwendern aus leitungsgebundenen Netzen bekannt

sind), die Vielfalt der Mobilfunkstandards und nicht zuletzt die Verunsicherung der Endkunden über das Preis-/Leistungsverhältnis der dritten Mobilfunkgeneration.

Der Anteil von Daten- und Multimediainhalten am gesamten Kommunikationsaufkommen ist in den letzten Jahren deutlich gestiegen. Insbesondere die Anbindung privater Haushalte an das Internet über ISDN und ADSL hat dazu beigetragen, den Anteil paketorientierter Dienste, die auf dem Internetprotokoll aufbauen, zu vergrößern. Eine große Anzahl von Anwendern kennt die Vorteile von HTTP-, FTP- und SMTP-basierten Diensten und das (häufig kostenlose) Herunterladen von Anwendungssoftware. Es ist anzunehmen, dass diese Dienste in den kommenden Jahren mehr und mehr auf mobile Geräte übertragen werden und dass diese von den Nutzern auch nachgefragt werden. Dazu ist es unabdingbar, die passenden Übertragungstechniken zu beherrschen, und zwar gerade auch im Endgerät, abhängig von der aktuellen, vorher nicht festgelegten Kommunikationssituation des Nutzers. Entwurfstechniken aus dem Bereich Software Radio können dabei von Vorteil sein.

In leitungsgebundenen Netzen ist derzeit ein Trend zu beobachten, der langfristig darauf abzielt, die Leitungsvermittlung abzuschaffen und jegliche Kommunikation paketorientiert abzuwickeln. VoIP ist ein extremes Beispiel dafür. Mit diesem Trend geht die Konvergenz verschiedener Netze zu einem einheitlichen Netz (*engl.* all-IP network), das mit dem IPv6 arbeitet, einher.

Ganz im Gegenteil dazu beobachtet man im Bereich der drahtlosen Zugangsnetze eine wachsende Vielfalt von Mobilfunkstandards: Weltweit sind verschiedenste Standards der zweiten Generation im Einsatz (GSM, TETRA, TETRAPOL, PHS, IS-54, IS-136, IS-95A/B). Diejenigen Varianten, die zur Generation 2,5 gezählt werden, umfassen technische Änderungen (z.B. 8-PSK in EDGE anstelle von GMSK bei GSM Phase 1) oder die Bündelung von physikalischen Kanälen (HSCSD) zur Erhöhung der Nutzdatenrate oder die Umstellung der Luftschnittstelle auf paketorientierte Übertragung (GPRS). Die Einführung eines umfassenden Standards zur mobilen Telekommunikation (engl. Universal Mobile Telecommunications System, UMTS) als einziger Standard der dritten Generation war ursprünglich gedacht, um dieser Vielfalt ein Ende zu setzen. Allerdings kann der Versuch als gescheitert angesehen werden, weil die ITU unter dem Kürzel IMT-2000 nicht ein einziges, sondern fünf verschiedene Luftschnittstellenkonzepte zusammenfasst [42], darunter auch die zu IS-136 rückwärtskompatible Variante TDMA Single Carrier sowie DECT, einen Standard der zweiten Generation für Schurlostelefonie. In Europa versteht man unter dem Kürzel UMTS hauptsächlich UTRA-FDD und UTRA-TDD mit DS-CDMA als Vielfachzugriffsverfahren, während die Firma

Qualcomm die Variante MC-CDMA (cdma2000 1X/3X) favorisiert, die ebenfalls rückwärtskompatibel ist, und zwar zum nordamerikanischen IS-95B (cdmaOne). Nicht nur technische Überlegungen, sondern vor allem wirtschaftliche Interessen werden für die Entscheidung der ITU zu Gunsten einer solchen Kompromisslösung verantwortlich gemacht. Damit wird letztlich der Erfolg am Telekommunikationsmarkt über die genaue technische Ausprägung der dritten Generation entscheiden, nicht ein Standardisierungsgremium.

Neben dem flächendeckenden zellularen Mobilfunk der dritten Generation rücken auch WLANs ins Interesse von Nutzern und Geräteherstellern. Hier sind insbesondere die Standards HIPERLAN/2 und IEEE802.11a/b zu nennen. Mittlerweile sehen die Hersteller in UMTS und WLAN eine Kombination von komplementären Lösungen für unterschiedliche Nutzersituationen: Auf der einen Seite UMTS für hohe Mobilität und niedrige Datenraten in flächendeckenden Netzen, auf der anderen Seite WLAN für nomadische Anwendungen und höhere Datenraten in der unmittelbaren Umgebung von isolierten Zugangspunkten (*engl.* hot spots). Bereits bei der technischen Beherrschung dieser Kombination kommen Techniken aus dem Bereich Software Radio zum Einsatz [11, 66, 117].

Die oben genannten Vertreter der zweiten und dritten Generation sind nur ein unvollständiger Ausschnitt aus der zunehmenden Vielfalt von Mobilfunkstandards. Der Grund dafür liegt im weitesten Sinne in der Vielfalt der Situationen und Anforderungen mobiler Nutzer. Je besser man einen Standard an die augenblickliche Lage des Nutzers anpasst, desto besser die Ergebnisse bezüglich der Übertragungsqualität. Bei dieser Anpassung sind die physikalische Schicht und die Datensicherungsschicht von besonderer Bedeutung, da höhere Schichten letztlich nur auf die Fähigkeiten der untersten Schichten aufbauen können. Daher beschäftigt sich die vorliegende Arbeit mit Software, welche in einem Software Radio die Signalverarbeitungsaufgaben auf diesen untersten Schichten des OSI-Modells erfüllt.

Ein weiterer Grund dafür, den traditionellen Entwurf von Funkgeräten grundsätzlich zu überdenken, besteht in betriebswirtschaftlichen Überlegungen. Beispielsweise zeigt die Einführung von UMTS in Europa ganz deutlich: Wenn die Nachfrage nach einem Mobilfunkstandard hinter den Erwartungen eines bestimmten Geschäftsmodells zurückbleibt, oder wenn zufolge einer Trendwende plötzlich andere Dienste (und damit auch andere zugrunde liegende Übertragungstechniken) nachgefragt werden, dann wäre es für Hersteller ebenso wie für die Netzbetreiber sehr vorteilhaft, auf diese Situation schnell und angemessen reagieren zu können. Das schließt die Wiederverwendung (oder modulare Erweiterung) eines bereits fertig

entwickelten Hardware-Konzeptes ein, so dass nur Software ausgetauscht werden müsste. Software Radio zeigt genau für diese Situation das benötigte Lösungspotential.

Man kann aus den geschilderten Randbedingungen den Schluss ziehen, dass die Flexibilität von Software Radio also nicht in vollem Umfang an den Endkunden weitergegeben, sondern weitgehend von Geräteherstellern kontrolliert werden wird. Der genaue Hardware-Aufbau und alle Aspekte, welche die interne Organisation der Software und das Betriebssystem betreffen, werden nach wie vor firmenspezifisches Know-how bleiben. Diese Prognose spricht nicht gegen die Einführung offener Schnittstellen [89], sondern lediglich für spezifische Implementierungen von Software Radios. So können sich Hersteller weiterhin voneinander differenzieren und trotz kurzer Produktzyklen Entwicklungskosten über mehrere Geräteversionen und verschiedene Produktlinien amortisieren. Software Radio ist also als **der** Prototyp des eingebetteten Systems (*engl.* embedded system) in der Telekommunikation aufzufassen.

#### 1.2 Modulares Software Defined Radio

In der Begriffswelt wird zuweilen zwischen Software Radio und Software Defined Radio unterschieden [114], wobei der erste Begriff das ideale Software Radio meint, das in der Einleitung bereits diskutiert worden ist. Um klarzustellen, dass die vorliegende Arbeit von realistischen Randbedingungen ausgeht, wird im Folgenden nur noch der Begriff des Software Defined Radio (SDR) gebraucht. Unter diesem Sammelbegriff werden alle Techniken verstanden, die das Ideal an einer oder an mehreren Stellen kompromittieren, jedoch dafür sorgen, dass die Grundideen und Vorteile von Software Radio auf verfügbarer Hardware technisch anwendbar und wirtschaftlich sinnvoll nutzbar werden.

Die Flexibilität eines Software Defined Radios kann um so besser für verschiedene Mobilfunkgeräte genutzt werden, je allgemeiner und skalierbarer der Entwurfsansatz ist. Gerade bei der Einführung einer neuen Gerätegeneration ist schnell einsichtig, dass eine bestimmte Hardware, egal wie leistungsfähig sie im Moment erscheinen mag, beim Übergang auf wesentlich kompliziertere Verfahren zur drahtlosen Datenübertragung irgendwann an ihre Grenzen stößt. Es wäre in solchen Fällen günstig, wenn diese Grenzüberschreitung zwar die aktuelle Hardware-Realisierung, nicht aber das gesamte Hardware-Konzept beträfe. Die Entwicklungsteams

eines Unternehmens würden dann mit dem gleichen vertrauten Konzept weiterarbeiten können und müssten lediglich für eine Steigerung der Rechenleistung sorgen, so dass der neue Mobilfunkstandard beherrschbar wird. Das Hardware-Konzept für ein Software Defined Radio sollte also modular sein in dem Sinne, dass Leistungssteigerungen allein durch Hinzufügen von einzelnen Zusatzkomponenten (z.B. weitere DSPs oder eines speziellen Coprozessors für die Beschleunigung bestimmter Signalverarbeitungsaufgaben) möglich sind. Damit ist offensichtlich, dass es sich bei der Hardware eines sinnvoll aufgebauten Software Defined Radios im Allgemeinen um ein Multiprozessorsystem handeln wird.

Unter diesen Bedingungen muss auch die Software zur Signalverarbeitung zunächst auf das Gesamtsystem verteilt (*engl.* partitioning) und ein Ablaufplan für alle Module erstellt (*engl.* scheduling) werden. Folglich braucht ein SDR ein Betriebssystem, das sich um diese Aufgaben kümmert. Dieses Betriebssystem wird sicherlich herstellerspezifisch sein und zu derjenigen Software gehören, die zusammen mit der Hardware an den Endkunden ausgeliefert wird (*engl.* firmware), aber weder vom Nutzer noch vom Netzbetreiber geändert werden kann. Um nicht für jede modulare Hardware-Konfiguration ein neues Betriebssystem entwickeln zu müssen, gilt es, allgemeine Richtlinien für den Entwurf und den Betrieb von Software Defined Radios zu finden, die mit allen möglichen Hardware-Konfigurationen zurechtkommen. Das Betriebssystem ist also das klassische Bindeglied zwischen Hardware und Software eines SDRs.

Auch Software in einem Software Defined Radio ist modular. Abhängig davon, welcher Mobilfunkstandard bedient werden soll, sind verschiedenste nachrichtentechnische Funktionen notwendig, so z.B. Quellencodierung, Kanalcodierung, Symbolerzeugung, Rahmenaufbau, Entzerrung und lineare Signaltransformation durch Filter oder FFT. Diese klassischen Funktionen können entweder vom Hersteller selbst entwickelt werden und aus kleineren Funktionsblöcken zusammengesetzt sein, oder sie werden von spezialisierten Anbietern in Form von monolithischen Funktionskernen (*engl.* IP cores) eingekauft und in die Softwaresammlung integriert. Die kleinsten zusammenhängenden Einheiten von ausführbaren Maschinenbefehlen werden im Folgenden Module genannt. Klassische nachrichtentechnische Funktionen sind in einem SDR hierarchisch aufgebaut und können wiederum aus Funktionen, Softwaremodulen oder Kombinationen aus beidem bestehen, je nachdem welche Hierarchieebene man betrachtet. Aus Sicht eines Prozessors gibt es sicherlich nur die unterste Ebene, in der ausschließlich Module vorhanden sind. Im Hinblick auf ein möglichst einfaches Betriebssystem wird angenommen, dass

die Ausführung von Modulen nicht unterbrochen werden kann: Ein Modul kann gestartet werden, wenn alle Eingangsdaten verfügbar sind. Das Modul belegt Datenspeicher, während es Eingangsdaten verarbeitet und Ausgangsdaten produziert. Die Ausführung des Moduls wird erst mit dem letzten Maschinenbefehl beendet. Zwischen Start und Ende der Ausführung eines Moduls m vergeht die Laufzeit p m (engl. processing runtime).

Es ist im Rahmen der vorliegenden Arbeit von besonderer Wichtigkeit, dass die Laufzeit als die wesentliche charakteristische Größe zur Beschreibung eines Moduls erkannt wird, da sie unabhängig ist von der konkreten Hardware, auf der das Modul abläuft. Diese laufzeitorientierte Sichtweise wird den Kern der Software-Modelle für Modulares Software Defined Radio bilden.

Mit dem Umfang, in dem die komplexen Funktionen eines beliebigen Mobilfunkstandards aus kleineren Funktionsblöcken und Modulen zusammengesetzt werden, erhöht sich die Wahrscheinlichkeit, dass der Hersteller bei der Umstellung seines SDRs auf einen anderen Standard Funktionsfragmente und Module wiederverwenden kann (engl. code reuse). Das birgt den Vorteil geringerer Entwicklungszeiten für ein neues Produkt und ebenso den Vorteil der weitgehenden Fehlerfreiheit bereits getesteter Funktionen und Softwaremodule. Im Weiteren sollen unter dem Begriff Modulares Software Defined Radio (Mod-SDR) alle Arten von Software Defined Radios verstanden werden, bei denen die Hardware aus einem einfach zu erweiternden Multiprozessorsystem besteht und Software für die Signalverarbeitungsaufgaben der physikalischen Schicht aus Modulen zusammengesetzt ist. Allgemein gültige Richtlinien für den Entwurf und Betrieb solcher Modularer Software Defined Radios sind Gegenstand der Untersuchungen in der vorliegenden Arbeit.

## 1.3 Bisherige Arbeiten im Bereich Software Radio

In der Literatur finden sich zahlreiche Beiträge zum grundlegenden Konzept des idealen Software Radios [13,61,63,64] und zu Kompromisslösungen, also Software Defined Radios [102]. Die Ursprünge, Entstehungsgeschichte und verschiedene Sichtweisen zu SDR sind in [103] umfassend beschrieben. Mittlerweile werden auch alle Aufgaben der Netzwerk- und Nutzerverwaltung in die Überlegungen zur Realisierung flexibler Mobilfunkanwendungen einbezogen [19]. Dies schließt adaptive Protokollschichten, Organisation des Diensteangebots, Sicherheitsaspekte, "intelligente" Endgeräte (engl. "Cognitive Radios" [64,65]), flexible Frequenzver-

gabe ("Spectrum Pooling" [52, 68, 111]) und Modulationsartenerkennung [67] ein. Die zuletzt genannten, sehr umfangreichen Aufgaben gehen weit über den Rahmen der vorliegenden Arbeit hinaus und werden im Folgenden nicht weiter behandelt.

Frühe Beiträge zu flexiblen Endgeräten erläutern meist Bauteile, Komponenten und technologische Randbedingungen [4, 17, 48, 88], ziehen jedoch kaum konkrete Schlussfolgerungen bezüglich des Entwurfs und Betriebs von SDRs. Die fortgeschrittenen Artikel befassen sich fast ausschließlich mit einem bestimmten Teil der Signalverarbeitungskette, so z.B. mit MEMS [84,85] für den Antennen- und Filterentwurf [7, 73], der Wahl der Zwischenfrequenzen im analogen Hochfrequenzteil des Empfängers [7, 21, 58, 90, 114], A/D- und D/A-Umsetzung [46, 96], der Abtastratenumsetzung [2, 3, 37] oder der Kanalcodierung [4, 100, 105]. Manche Ergebnisse beziehen sich auch gar nicht zwingend auf das Konzept des SDRs, sondern auf die klassische Nachrichtentechnik [118]. In diesen Artikeln gibt es oft einen Bruch zwischen einer Einführung, die viel von SDR verspricht, und einem Teil mit konkreten Ergebnissen in der Form BER = f (SNR), die mit Hilfe von Spezialhardware ebenso hätten erzielt werden können wie mit einer Softwarerealisierung [35, 44]. Systematische Aspekte von SDR werden häufig vermischt mit den Aufgaben der Signalverarbeitung aus anderen Bereichen der Nachrichtentechnik: Intelligente Antennensysteme (engl. smart antenna systems) [39, 71, 72] und MUD [94]. Diese Analyse soll die erzielten Ergebnisse in keiner Weise schmälern, jedoch muss man sich klarmachen, dass sie nicht unmittelbar eine Methodik zum Entwurf und Betrieb eines Software Defined Radios betreffen, sondern lediglich spezielle Funktionen der Signalverarbeitung, die hinsichtlich der Integration in ein Mod-SDR methodisch genau so zu behandeln sind wie alle klassischen nachrichtentechnischen Funktionen.

Eine Arbeit [62], die sich dem Thema Software Defined Radio von theoretischer Seite nähert, zeigt deutliche Schwächen im Hinblick auf die Begriffsbildung (*engl.* "topology") und auf die statistischen Eigenschaften der in einem SDR benötigten Rechenleistung (*engl.* "statistical demand for processing power"). Die Ergebnisse der genannten Arbeit gehen letztlich nicht über die bekannten Aussagen der theoretischen Informatik hinaus (Church-Turing-These [113]).

Ein wichtiger Schritt auf dem Weg zu konkreten Entwurfsrichtlinien für Software Defined Radio besteht in dem Ansatz PaC-SDR [43,114], der die Signalverarbeitung im digitalen Basisband betrifft. Dabei wird eine zum Entwurfszeitpunkt festgelegte Menge an Mobilfunkstandards auf ihre Gemeinsamkeiten und Unterschiede hin untersucht. Eine grundlegende Hypothese von PaC-SDR besteht darin,

dass die Gemeinsamkeiten bisher weit überwogen haben und sich das auch in Zukunft nicht ändern wird, ungeachtet der Möglichkeit, ganz andersartige Standards zu entwerfen. Der Grund liegt im Wesentlichen darin, dass die klassische Nachrichtentechnik Antworten auf die Eigenschaften des Mobilfunkkanals entwickelt hat und sich letztere auch in Zukunft nicht ändern werden. Das Entwurfsziel von PaC-SDR besteht nun darin, die Algorithmen der Signalverarbeitung so allgemein zu halten, dass sie sich lediglich durch die Angabe eines Parametersatzes von einem auf den anderen Standard umschalten lassen. Die Idee kann der Realisierung von schnellem vertikalen Handover dienen, aber auch der Interoperabilität zwischen Nutzergruppen (BOS und Militär, multinationale Einsätze). Das Konzept des Betriebs allgemein gültiger, parametrisierter Softwaremodule zieht sich durch alle hierarchischen Funktionen der untersten OSI-Schichten. Zum ersten Mal geht es bei PaC-SDR also nicht um eine Einzellösung, sondern um ein Konzept, das einzig und allein SDR zu Eigen sein kann.

Der Hauptvorteil von PaC-SDR liegt im geringen Datenvolumen der Parametersätze im Vergleich zur gesamten Software. Gerade dadurch, dass man eben nicht die Gesamtheit der nachrichtentechnischen Funktionen beim Wechsel auf einen neuen Mobilfunkstandard laden muss, sondern lediglich einen neuen Parametersatz, kann man schnelles vertikales Handover realisieren. Weiterhin ist die Wiederverwendbarkeit von Modulen und Funktionen selbst in komplizierten Anwendungen (z.B. zyklische Faltungscodes [74] oder Bandspreizen [76]) gezeigt worden.

Allerdings stößt man bei den Aufgaben der Kanalcodierung auch schnell an die Grenzen von PaC-SDR [74]: Zum einen kann es mitunter einfacher sein, Spezialaufgaben wie einen einfachen Viterbi-Decoder und einen Turbo-Decoder getrennt zu entwerfen und nicht eine allgemeine Funktion, die abhängig von Parametern entweder auf die eine oder andere Weise decodiert. Zum anderen besteht immer die Gefahr, dass ein allgemein gültiges Softwaremodul bezüglich seiner Laufzeit weit weniger effizient ist als getrennte Spezialmodule für beide Decodieraufgaben. Ein weiterer Schwachpunkt besteht darin, dass man bei der Erweiterung auf ein neues Codierverfahren gegebenenfalls gezwungen wird, das Modul von Grund auf neu zu entwickeln, und zwar ohne Wiederverwendung existierender Softwaremodule. Beispielsweise ist es nicht möglich, ein auf Binärcodes ausgelegtes Modul zur Erzeugung von Symbolcodes (Reed-Solomon-Codes) zu nutzen. Das umgekehrte Vorgehen ist ohne Weiteres vorstellbar, aber es erfordert den völlig neuen Entwurf eines Reed-Solomon-Encoders, der parameterabhängig auch Binärcodes beherrscht. Zudem ist die Wahrscheinlichkeit hoch, dass dieser neue Encoder für

die einfacheren Binärcodes ineffizient arbeitet. Der Kompromiss aus Flexibilität und Effizienz, der schon mit Blick auf die Hardware von Software Radios diskutiert wurde, setzt sich bei PaC-SDR also in die Welt der Software fort. Und schließlich betreffen die quantitativen Ergebnisse [114] wieder die klassische Nachrichtentechnik in Form von BER = f (SNR).

### 1.4 Ziel und Aufbau der vorliegenden Arbeit

Mod-SDR steht keinesfalls im Widerspruch zu den Ansätzen von PaC-SDR, sondern kann als Verallgemeinerung und systemtheoretisches Komplement betrachtet werden. Die Tatsache, dass die Modullaufzeiten im Vordergrund stehen, schließt weder aus, dass diese Module parametergesteuert sind, noch dass es sich um Spezialmodule handelt oder sogar um Spezialhardware. Wo PaC-SDR aber an seine Grenzen stößt (Komplexität und Laufzeitineffizienz allgemein gültiger Softwaremodule), sind stets Speziallösungen für nachrichtentechnische Aufgaben zu finden und in ein offenes, modulares System zu integrieren. Jedes allgemeine wie spezielle Softwaremodul hat eine Laufzeit, ja sogar jede Form von Spezialhardware (also Funktionen in ASICs, Coprozessoren oder auf spezialisierte Beschleuniger-Hardware ausgelagerte Funktionen), so dass Mod-SDR heterogene Systeme oder eine Mischung aus Hardware- und Softwarelösungen nicht von vornherein ausschließt.

Im Gegensatz zu PaC-SDR ist Mod-SDR eher strukturorientiert. Von den Algorithmen der Nachrichtentechnik wird so weit abstrahiert, dass lediglich die Laufzeit von Softwaremodulen, ihre Beziehungen untereinander und die Speicheranforderungen für Ein- und Ausgangsdaten erhalten bleiben. Wenn es in dieser Arbeit um Algorithmen geht, so sind nicht die Algorithmen der Signalverarbeitung gemeint, sondern diejenigen Algorithmen, die der Organisation des Softwareablaufs in einem Multiprozessorsystem dienen. Modulares Software Defined Radio verlässt damit naturgemäß die klassische Nachrichtentechnik und liegt eher an der Schnittstelle zwischen Informatik, Nachrichtentechnik und den Techniken des automatischen Entwurfs elektronischer Schaltungen. Daher sind an keiner Stelle dieser Arbeit Ergebnisse in der Form BER = f (SNR) zu finden. Nichts desto trotz werden sowohl die Modellvorstellungen als auch die Interpretation der Ergebnisse für die Anwendung in der Nachrichtentechnik entwickelt.

Das Ziel der vorliegenden Arbeit besteht darin, grundlegende und allgemein gültige

Richtlinien herzuleiten, die zum optimalen Betrieb von SDR-Systemen (parametrisiert oder nicht, homogen oder heterogen) nötig sind. Diese Richtlinien sollen so weit wie möglich von konkreten Hardware-Systemen und von bekannten Mobilfunkstandards unabhängig sein.

Wegen der Neuartigkeit der Sichtweise beschäftigt sich Kapitel 2 zunächst mit der Modellbildung für Hardware und Software unter den geschilderten Randbedingungen. Kapitel 3 führt dann eine präzise mathematische Formulierung der SDR-Entwurfsaufgabe ein. Diese Betrachtung zeigt jedoch recht eindeutig, dass diese Formulierung die Aufgabe zwar klassischen Lösungsverfahren zugänglich macht, die Anwendung der Verfahren im Betriebssystem eines Mod-SDRs aber nicht praktikabel ist. Alternative Lösungsverfahren werden sodann in Kapitel 4 beschrieben. Dort geht es um die Partitionierung von Signalverarbeitungssoftware und um das Erstellen von Ablaufplänen. Das Kapitel 5 zeigt die Ergebnisse, die mit den beschriebenen Verfahren zu erzielen sind und vergleicht ihre Eigenschaften. Diese Ergebnisse werden im Sinne der Nachrichtentechnik interpretiert und führen letztlich auf die grundlegenden Entwurfsrichtlinien für Modulares Software Defined Radio.

## 2 Modellbildung

Um die Ziele dieser Arbeit verfolgen zu können, müssen zunächst geeignete Modelle für Hardware und Software in einem Modularen Software Defined Radio entwickelt werden. Eine besondere Schwierigkeit besteht darin, die Flexibilität von Software Defined Radio in die Modellbildung zu übernehmen. Die Eigenschaften von Hardware und Software sind einerseits möglichst allgemein zu beschreiben, andererseits sollen mit Hilfe der Modelle aber auch Simulationen betrieben und konkrete Ergebnisse abgeleitet werden.

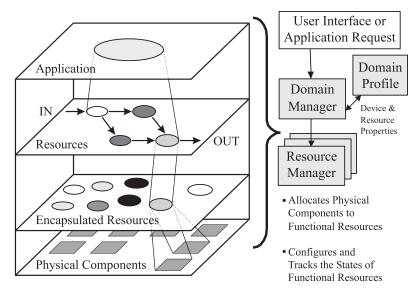

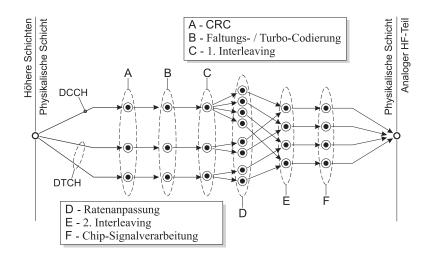

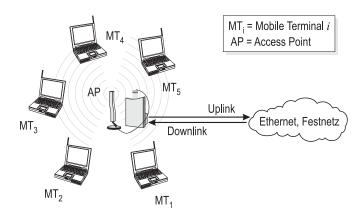

Bild 2.1 Frühe Modellvorstellung eines SDRs, Quelle: SDRF [92]

Das Bild 2.1 zeigt die Darstellung eines SDRs wie sie bereits Ende 1999 vom SDRF favorisiert wurde [92]. Es ist deutlich zu erkennen, dass eine Anwendungssoftware (engl. application) in einem SDR nicht als ein einziges großes Maschinenprogramm zu sehen ist, sondern sich naturgemäß aus verschiedenen nachrichtentechnischen Funktionen (engl. "functional resources" [92]) zusammensetzt, die alle zusammen Eingangsdaten verarbeiten und Ausgangsdaten produzieren. Zwischen den Funktionen bestehen logische Abhängigkeiten, und diese Funktionen sind in

irgendeiner Weise (engl. "encapsulated resources" [92]) auch auf einer niedrigeren Hierarchieebene wiederzufinden. Desweiteren wird eine Abbildung von Software auf Hardware durchgeführt, und zwar so, dass "encapsulated resources" unter Umständen auf mehr als einer physikalischen Komponente ablaufen. Bei der Hardware handelt es sich offensichtlich um ein System aus mehreren Prozessoren. Der Verbund aus Signalverarbeitungssoftware und Hardware wird von einem Betriebssystem verwaltet, das sich nach Bild 2.1 aus einem "Domain Manager" und mehreren "Resource Managern" zusammensetzt und das unabhängig vom betrachteten Mobilfunkstandard als Firmware in dem Software Defined Radio existiert. Bemerkenswert ist weiterhin, dass das Betriebssystem Anfragen des Nutzers oder einer laufenden Anwendung entgegennimmt.

Was sich genau hinter den verschiedenen Begriffen verbirgt und welche Verfahren für die Abbildung von Software auf Hardware zu wählen sind, bleibt in [92] offen. Versteht man jedoch unter "functional resources" die nachrichtentechnischen Funktionen im Sinne von Kapitel 1, die hierarchisch aus anderen Funktionen und einfachen Softwaremodulen aufgebaut sind, so trifft das Bild bereits den Kern des in dieser Arbeit beschriebenen realistischen Modells für modulare, aus Hardware und Software bestehende Systeme: Es besteht die Notwendigkeit, Hardware und Software vermittels eines Betriebssystems zu kontrollieren, den Ablauf von Modulen auf einem Multiprozessorsystem so gut wie möglich zu koordinieren und auf Nutzeranfragen zu reagieren.

Allein aus Bild 2.1 wird in keiner Weise klar, wie Hardware und Software zu beschreiben sind (*engl.* "domain profile" [92]) und wie die Hardware-Komponenten miteinander in Verbindung stehen. Eine entsprechende Verfeinerung dieser Aspekte zur Anwendung auf Modulares Software Defined Radio ist Gegenstand dieses Kapitels.

#### 2.1 Hardware-Modell

Die allgemeine Vorstellung von einem idealen Software Radio ist im Zusammenhang mit Mod-SDR nicht hilfreich, denn dieses Ideal schließt den Begriff des Multiprozessors gar nicht ein, sondern basiert auf einem einzelnen Zentralprozessor (engl. CPU), der alle Signalverarbeitungsaufgaben auf allen Schichten des OSI-Modells erledigt. Sollte es jemals möglich sein, eine solche Ideallösung kostenund leistungsgünstig herzustellen, besteht die in dieser Arbeit geschilderte Ent-

wurfsaufgabe nicht mehr. Allerdings ist aus der Diskussion der technischen und wirtschaftlichen Randbedingungen in Kapitel 1 zu schließen, dass dieser Fall mit sehr hoher Wahrscheinlichkeit auf absehbare Zeit nicht eintreten wird. Es gibt derzeit sogar eine ganze Reihe von Hinweisen [18, 31, 98, 101, 104, 106], dass sich die Signalverarbeitung in der mobilen Telekommunikation eher auf Strukturen mit verteilten Prozessorelementen stützen wird. Folglich braucht auch Modulares Software Defined Radio ein entsprechendes Hardware-Modell.

#### 2.1.1 Symmetrischer Multiprozessor

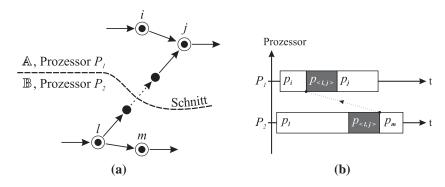

Als Prototyp des Mehrprozessorsystems wird in dieser Arbeit ein symmetrischer Multiprozessor mit L identischen Prozessoren und B unabhängigen Bussen zur Inter-Prozessor-Kommunikation betrachtet.

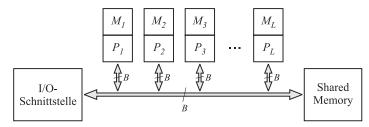

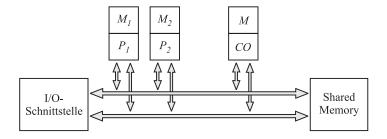

Bild 2.2 Symmetrischer Multiprozessor

Bild 2.2 zeigt das System mit einer Schnittstelle zur Ein- und Ausgabe von Daten  $(engl.\ I/O\ interface)$  und einem gemeinsamen Speicherbereich  $(engl.\ shared\ memory)$ , auf den alle Prozessoren beliebig lesend und schreibend zugreifen können. Jedem Prozessor  $P_k,\ 1\leq k\leq L$  ist ein eigener Datenspeicherbereich  $M_k$  zugeteilt  $(engl.\ distributed\ memory)$ , auf den von  $P_k$  aus jederzeit uneingeschränkt zugegriffen werden kann. Es soll angenommen werden, dass Prozessoren aktiv an allen Buszugriffen beteiligt sind, d.h. ein Prozessor kann parallel zur Buskommunikation keine anderen Softwaremodule ausführen. Sollen Zwischenergebnisse zwischen zwei Prozessoren ausgetauscht werden, so schreibt der Quellprozessor die Daten über einen Bus in das Shared Memory, und der Zielprozessor holt die Daten dort später mit einem weiteren Zugriff auf den Bus ab. Der Vorteil eines solchen asynchronen Datenaustausches über das Shared Memory liegt darin, dass nicht beide Prozessoren gleichzeitig verfügbar sein müssen. Der Zielprozessor kann nach wie vor Rechnungen im Rahmen der Signalverarbeitung ausführen, während der Quell-

prozessor bereits Daten schreibt, und der Quellprozessor muss später die Ausführung von Modulen nicht mehr unterbrechen, wenn der Zielprozessor die für ihn bestimmten Daten aus dem Shared Memory liest.

Sicherlich bieten moderne Prozessoren Kommunikationsschnittstellen an, die unabhängig von der Aktivität des Prozessorkerns Daten versenden oder empfangen können, vorausgesetzt ein Softwaremodul wird ausdrücklich dahingehend programmiert. Zum Entwurfszeitpunkt eines Moduls ist im Allgemeinen aber unbekannt, ob parallel zur Signalverarbeitung ein Austausch von Zwischenergebnissen stattfinden soll. Das wird erst vom Betriebssystem zum Einsatzzeitpunkt geplant. Gerade das konkrete Zusammenspiel eines Moduls mit anderen Modulen entscheidet ja darüber, ob Inter-Prozessor-Kommunikation nötig ist oder nicht. Ferner kann ein nicht-präemptives Betriebssystem auch keine speziellen Maschinenbefehle in ein Modul einfügen, weil Module nach Voraussetzung in ihrer Ausführung nicht unterbrochen werden können. Demnach ist die Wahrscheinlichkeit gering, dass spezielle Kommunikationsschnittstellen immer genau so genutzt werden wie vom Prozessorhersteller angegeben. In dieser Hinsicht kann man also volle Prozessoraktivität bei Buskommunikation als pessimistische, aber nicht unwahrscheinliche Annahme werten.

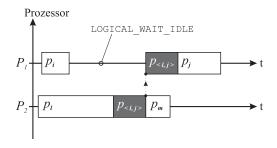

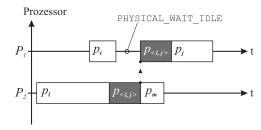

Buszugriffe sollen exklusiv sein, d.h. während der Zugriff durch einen Prozessor stattfindet, kann ein zweiter Prozessor nicht gleichzeitig auf den gleichen Bus zugreifen. Sollte dieser Fall auftreten, spricht man von einem Buskonflikt. Im Rahmen des beschriebenen, möglichst einfachen Betriebssystems soll ein solcher Buskonflikt aufgelöst werden, indem der zweite Prozessor solange angehalten wird ("PHYSICAL\_WAIT\_IDLE condition" [80]), bis der Bus vom ersten Prozessor wieder freigegeben ist. Auf diese Weise können Leerlaufzeiten (engl. idle times) entstehen, in denen weder sinnvolle Rechnungen durchgeführt noch Zwischenergebnisse an andere Prozessoren verschickt werden. Es ist unmittelbar einsichtig, dass diese Leerlaufzeiten vermieden werden sollten, um die vorhandenen Prozessoren möglichst gut auszunutzen.

Ein symmetrischer Multiprozessor ist leicht erweiterbar, indem weitere Prozessoren gleicher Bauart an das Bussystem angeschlossen werden. Ein Bus kann beliebige Prozessoren miteinander verbinden, unterliegt also im Prinzip keinen Einschränkungen bezüglich der logischen Hardware-Struktur. Da physikalisch aber nur eine einzige Verbindung vorhanden ist, erlaubt ein einzelnes Bussystem die Vollvermaschung lediglich im zeitlichen Multiplex. Die Anzahl B der nötigen unabhängigen Busse ist eine kritische Größe beim Hardware-Entwurf, weil die Komplexität und

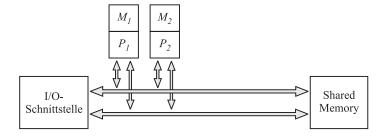

**Bild 2.3** Symmetrischer Multiprozessor, L=2 Prozessoren, B=2 Busse

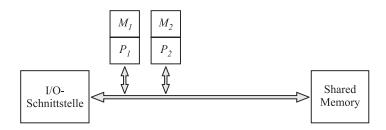

**Bild 2.4** Zwei-Prozessor-System, B = 1 Bus

damit die Kosten sicherlich mit wachsendem B steigen. Bereits an dieser Stelle wird klar, dass der symmetrische Multiprozessor zwar einige Anforderungen erfüllt, die man von einem allgemeinen Hardware-Strukturmodell für Software Defined Radio erwartet, aber auch grundlegende Eigenschaften besitzt, die die Allgemeinheit einschränken.

Wenn sich der allgemeine Fall mit L Prozessoren als zu komplex erweist, erscheint es zunächst plausibel, die Entwurfsprinzipien für L=2 Prozessoren zu untersuchen. Mehr als B=2 Busse sind dann nicht sinnvoll, denn mehr als zwei gleichzeitige Zugriffe auf das Shared Memory oder die I/O-Schnittstelle kann es bei L=2 Prozessoren nicht geben. Bild 2.3 zeigt diesen Sonderfall.

Bei dieser besonderen Prozessorkonfiguration besteht die Frage, ob sich das Software Defined Radio nicht auch genau so gut mit einem einzigen Bus betreiben lässt (siehe Bild 2.4). Die in Kapitel 4 diskutierten Algorithmen und die meisten Simulationsergebnisse in Kapitel 5 beziehen sich auf diese beiden Hardware-Konfigurationen.

2.1.2 Einsatz eines Coprozessors

Selbst wenn der Betrieb von 2 Bussen das Auftreten von Buskonflikten unterbindet, kann es sein, dass L=2 Prozessoren nicht ausreichen, um die für einen bestimmten Mobilfunkstandard nötige Rechenleistung aufzubringen. In diesem Fall sind die Grenzen der Realisierbarkeit einfach überschritten, und es muss entschieden werden, dass dieser Standard mit dem gegebenen Software Defined Radio nicht betrieben werden kann.

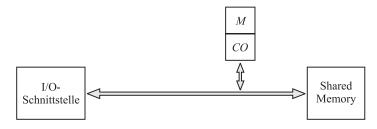

Ein Lösungsansatz, der immer wieder im Zusammenhang mit SDR-Hardware auftaucht, ist der Einsatz eines Coprozessors als Beschleuniger für bestimmte Signalverarbeitungsaufgaben. Bild 2.5 zeigt diese Konfiguration.

Ausgehend von einem Zwei-Prozessor-System wird also ein dritter Prozessor an die Busse angeschlossen. Zunächst sollen keine Annahmen über die Spezialisierung des Coprozessors gemacht werden, weil man in der Phase des Systementwurfs ja noch entscheiden kann, welche Module auf den Beschleuniger ausgelagert werden. Dennoch ist zu prüfen, ob selbst unter idealen Bedingungen die Realisierungsgrenzen überschritten werden oder ob der Betrieb des Standards durch Einsatz des Coprozessors nun möglich ist. Unter idealen Bedingungen soll dabei ein unendlich schneller Coprozessor verstanden werden.

Im Rahmen der Untersuchungen zum effizienten Betrieb eines Coprozessors wird das Zwei-Prozessor-System mit B=2 Bussen aus Bild 2.3 als hypothetisches Coprozessorsystem aufgefasst, das aus Bild 2.5 hervorgeht, wenn ideale Bedingungen für eine Beschleunigung der Rechnungen angenommen werden. Die Laufzeiten der ausgelagerten Module werden damit zu Null, die Ein- und Ausgangsdaten der betreffenden Module werden jedoch nach wie vor über das Bussystem mit den beiden anderen Prozessoren ausgetauscht. Eine Alternative zu diesem hypothetischen System besteht darin, das System aus Bild 2.5 gedanklich in zwei Subsysteme zu zerlegen: Ein tatsächlich realisierbares Coprozessor-Subsystem mit einem Bus (siehe Bild 2.6) und ein Restsystem nach Bild 2.4, das die beiden ursprünglichen Prozessoren und ebenfalls einen Bus enthält. Diese beiden Subsysteme können vom Betriebssystem des Mod-SDR koordiniert betrieben werden und zeigen den Vorteil, zur gleichen Zeit unterschiedliche Daten verarbeiten zu können.

Am Beispiel des Coprozessorseinsatzes wird deutlich, dass selbst der Sonderfall mit L=2 Prozessoren und B=2 Bussen bereits verschiedene Möglichkeiten zum Betrieb eines Software Defined Radios eröffnet und dass die Koordination zwischen Signalverarbeitungssoftware und Hardware durch das Betriebssystem von

**Bild 2.5** Zwei-Prozessor-System mit Coprozessor (CO), B = 2 Busse

Bild 2.6 Coprozessor-Subsystem mit einem Bus

entscheidender Bedeutung sein wird. Bevor allgemeine Richtlinien für die Art und Weise dieser Koordination gefunden werden können, müssen noch Modelle für modulare Software eingeführt werden.

## 2.2 Software-Modelle

Der Begriff der Software wird in der Literatur häufig für alle möglichen Arten von ausführbaren Maschinenbefehlen benutzt. Auch verstehen Netzbetreiber unter Software zuweilen etwas anderes als die Hersteller von Endgeräten, und es muss bei Diskussionen viel Zeit darauf verwendet werden, sich auf eine gemeinsame Vorstellung von den Begriffen zu einigen. Leider bleibt der Softwarebegriff häufig voll und ganz unerklärt, oder er dient als intuitiver Sammelbegriff für alle möglichen Arten von Software auf allen Schichten des OSI-Modells. Der Grund liegt möglicherweise darin, dass das Konzept von Software Radio ja gerade dazu gedacht ist, sich konkreten Entwurfsentscheidungen so lange wie möglich zu enthalten und – übertrieben gesprochen – "alles möglich" zu machen. Das ist natürlich für quan-

titative Untersuchungen nicht haltbar, denn die grundlegenden Vorstellungen von Softwareeigenschaften sollen klar nachvollziehbar und Randbedingungen reproduzierbar sein. Daher werden in diesem Abschnitt Modelle für Mod-SDR entwickelt, die sowohl die Flexibilität von Software Radio widerspiegeln, als auch mathematisch präzise sind, so dass sie später als Grundlage für Rechnersimulationen dienen können.

Die einzige verfügbare Spezifikation, welche eine allgemein gültige Beschreibung der Organisation und sinnvoller Schnittstellen für Software Defined Radios anstrebt, ist die Software Communications Architecture (SCA) [89]. Das Dokument befindet sich derzeit noch im Standardisierungsprozess und wird laufend erweitert. Die SCA entspringt einer Initiative des amerikanischen Verteidigungsministeriums, das mit Hilfe von SDR-Techniken bestehende Systeme interoperabel machen und langfristig die Vielfalt der Gerätschaften zur Funkkommunikation in den amerikanischen Streitkräften reduzieren soll. Die Arbeit an der SCA wird mit einem großen finanziellen und personellen Aufwand vorangetrieben, und da es keine alternativen Vorschläge aus Europa oder Asien gibt, stellt die SCA derzeit faktisch den Standard für Software Defined Radio dar, an dem sich Gerätehersteller weltweit orientieren.

Die vorliegende Arbeit soll keinesfalls auf militärisches SDR beschränkt sein, sondern allgemeine Entwurfsrichtlinien herleiten. Dennoch ist es sinnvoll, ein Software-Modell zu wählen, das mit der SCA kompatibel ist. Desweiteren sind die technischen Anforderungen an zivil genutzte Endgeräte oft eine Untermenge der Anforderungen aus dem militärischen Bereich. Die militärischen Randbedingungen (nicht-kooperatives Umfeld, fehlende Infrastruktur, verschiedenste Reichweiten, Notwendigkeit zur Verschlüsselung) werden lediglich durch andere ersetzt (Absatz auf einem Massenmarkt, niedrige Produktionskosten, Notwendigkeit zur Produktdifferenzierung). Daher muss es möglich sein, die Arbeit in den Rahmen der SCA einzuordnen.

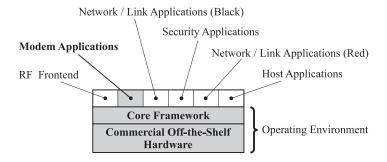

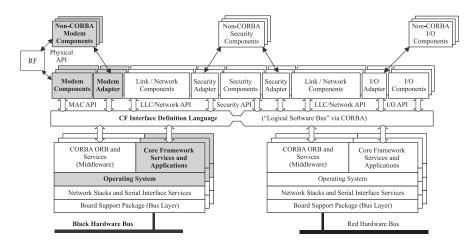

Bild 2.7 zeigt einen Überblick über die prinzipielle Organisation eines Software Defined Radios nach der SCA. Die gesamte Software aus allen Schichten des OSI-Modells wird von einem Betriebssystem (engl. "core framework" [89]) verwaltet und soll letztlich aus Kostengründen auf einem System ablaufen, das aus handels-üblichen Hardware-Bausteinen (engl. "COTS hardware" [89]) besteht. Hardware und Betriebssystem bilden zusammen die Betriebsumgebung (engl. "operating environment" [89]), in der die gesamte Software eines SDRs ihren Dienst tun soll.

Die vorliegende Arbeit beschränkt sich auf die physikalische Schicht (engl. "mo-

Bild 2.7 Signalverarbeitungssoftware und Betriebssystem, Quelle: JTRS JPO [89]

dem applications" [89]), wobei die beiden Schichten 1 und 2 des OSI-Modells im Folgenden unter diesem Begriff zusammengefasst werden. Das Bild 2.8 zeigt etwas detaillierter, wie Signalverarbeitungssoftware mit dem Betriebssystem interagiert und wo die Software der physikalischen Schicht einzuordnen ist.

Bild 2.8 Software Communications Architecture, Quelle: JTRS JPO [89]

Im Mobilfunk wird für die physikalische Schicht auch oft der Begriff der Luftschnittstelle (*engl.* air interface) gebraucht. Darunter versteht man die Gesamtheit aller Signalverarbeitungsschritte, die notwendig sind, um Binärinformationen (Bits) auf die Funkübertragung über einen physikalischen Kanal vorzubereiten.

Darunter fällt auch die Sicherung der Binärinformationen durch eine auf die Ei-

Darunter fällt auch die Sicherung der Binärinformationen durch eine auf die Eigenschaften des Funkkanals angepasste Kanalcodierung.

Es wird angenommen, dass die Signalverarbeitung für die Luftschnittstelle eines Mobilfunkstandards vollständig in Form von Softwaremodulen realisiert ist. Diese Software verarbeitet Signale zwischen dem Dienstzugangspunkt (engl. "SAP" [41], "interface" [40]) des analogen Hochfrequenzteils (engl. "RF frontend" [89]) für die physikalische Schicht einerseits und dem Dienstzugangspunkt der physikalischen Schicht für die nächsthöhere Protokollschicht (engl. "network/link applications" [89], "network layer" [41], "internet module" [40]) andererseits. Bei der Betrachtung der physikalischen Schicht geht es nicht um den gleichzeitigen Betrieb von mehreren Mobilfunkstandards, sondern allein um die optimale Abbildung der in Software realisierten Luftschnittstelle eines beliebigen Standards auf die zur Verfügung stehende Hardware. Der Nutzer wählt also aus vielen Alternativen genau eine drahtlose Zugangsmöglichkeit zum Festnetz.

Im Hinblick auf ein Inter-System-Handover [114] wird hier davon ausgegangen, dass alle Softwaremodule für die beiden am Handover beteiligten Luftschnittstellen bereits im Programmspeicher des Mobilgerätes stehen und dass ein hartes Umschalten zwischen den Standards möglich ist. Noch schneller als das Umladen von Parametersätzen in PaC-SDR ist sicherlich das Ändern der Befehlszeiger (engl. instruction pointer) von Prozessoren auf einen neuen Wert, so dass die Module des neuen Standards anstelle der Module des alten Standards abgearbeitet werden. Demnach entsteht dem Ansatz Mod-SDR auch in dieser Hinsicht kein Nachteil gegenüber PaC-SDR. Die Anzahl der Softwaremodule in einem Mod-SDR ist wahrscheinlich gröSSer als bei PaC-SDR, dafür können spezialisierte Module aber auch kompakter mit Maschinenbefehlen dargestellt werden. Generell soll in dieser Arbeit angenommen werden, dass der Programmspeicher keine kritische Ressource des Endgerätes darstellt, sondern nur der Datenspeicher. Desweiteren ist der Programmspeicherbedarf abhängig von vielen, im Allgemeinen unbekannten Details im Laufe des Entwurfsprozesses (engl. design flow), wohingegen der Datenspeicherbedarf eng an die Vorgaben eines Mobilfunkstandards gebunden ist. Auch aus diesem Grunde wird im Folgenden neben den Laufzeiten hauptsächlich der Datenspeicher berücksichtigt.

## 2.2.1 Echtzeitanforderungen im Mobilfunk

Das erklärte Entwurfsziel ist also die physikalische Schicht eines Modularen Software Defined Radios. Selbst unter dieser Einschränkung wird zuweilen davon gesprochen, dass eine unvorhersehbare Mischung aus unterschiedlichsten Diensten vorliegt und deshalb der Bedarf an Rechenleistung zufällig ist [62]. Der Grund liegt möglicherweise in der Auffassung, dass die besagte Mischung an Diensten zum Entwurfszeitpunkt unbekannt ist und ein stochastisches Verhalten in der Software nach sich zieht, das mit demjenigen von Zugriffen vieler Nutzer auf ein gemeinsames Medium vergleichbar ist. In diesem Abschnitt wird gezeigt, warum diese Sichtweise nicht haltbar ist, und zwar für keine wohldefinierte physikalische Schicht eines mobilen Kommunikationsgerätes.

Aus der Theorie der Kommunikation [34, 99] ist bekannt, dass sich zwei Kommunikationspartner zunächst auf einen gemeinsamen Protokollstapel einigen müssen, bevor erfolgreich Nutzdaten ausgetauscht werden können. Für den Mobilfunk bedeutet das: Zur drahtlosen Anbindung an ein Festnetz müssen sich Basisstation und Mobilgerät zunächst auf eine gemeinsame Luftschnittstelle einigen. Zwar können beim Verbindungsaufbau durchaus Parameter, die die Verbindungsqualität betreffen, zwischen den Kommunikationspartnern verhandelt werden, danach aber liegt die Signalverarbeitung auf beiden Seiten der Funkstrecke eindeutig fest, und zwar insbesondere deshalb, weil bei der Funkübertragung harte Echtzeitbedingungen einzuhalten sind. Nicht die ablaufende Software, sondern die in der Luftschnittstelle festgelegten Zeitbezüge der Funksignale (Rahmendauern, Wiederholraten usw.) bestimmen die notwendige Rechenleistung im Endgerät. In einem Software Defined Radio mag die Signalverarbeitung zwar beliebig sein, aber fest für jede Einzelverbindung. In dieser Hinsicht unterscheidet sich ein Mod-SDR nicht von anderen Mobilfunkgeräten.

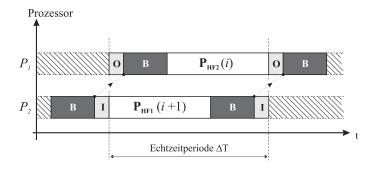

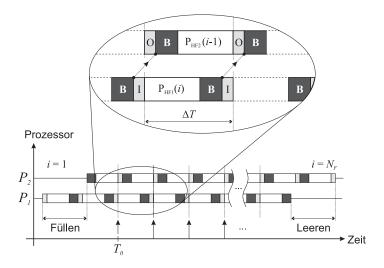

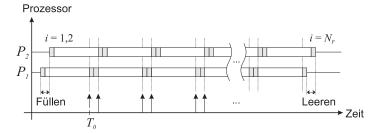

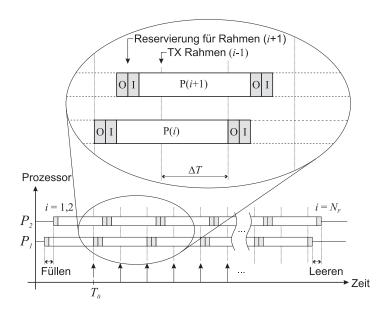

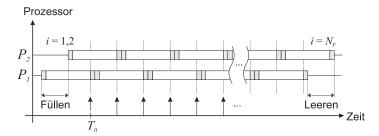

#### Leitungsvermittelte Dienste

Im Gegensatz zu Endgeräten in leitungsgebundenen Netzen haben mobile Geräte nicht beliebig viel Datenspeicher zur Verfügung. Weiterhin sind viele Mobilfunkstandards nach wie vor auf leitungsvermittelte Übertragung ausgelegt, hauptsächlich aus Gründen der Kompatibilität zu Sprachdiensten, so z.B. auch die DCHs von UMTS [24].

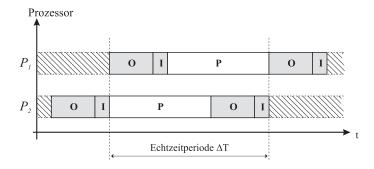

Ein leitungsvermittelter Dienst stellt klare Qualitätsanforderungen in Form von harten Echtzeitbedingungen über alle Schichten des OSI-Modells hinweg. Wenn

man lediglich die physikalische Schicht betrachtet, so sind Qualitätsanforderungen  $(engl.~{\rm QoS})$  in diesem Kontext wohldefiniert. Im Sender müssen die Binärdaten von höheren Schichten  $(engl.~{\rm PDU})$  in regelmäßigen Abständen übernommen und nach der Signalverarbeitung innerhalb einer festen Zeitdauer  $\Delta T$  an den analogen Hochfrequenzteil zur Übertragung weitergegeben werden. Auf ähnliche Weise agiert der Empfänger: Dort werden Abtastwerte vom analogen Hochfrequenzteil in regelmäßigen Abständen übernommen und müssen innerhalb der Zeitdauer  $\Delta T$  in PDUs für höhere Schichten umgewandelt sein.

Sollte die physikalische Schicht unfähig sein, die betreffenden Daten innerhalb von  $\Delta T$  zu verarbeiten, würde das Endgerät im günstigsten Falle spektrale Ressourcen verschwenden: Bei Vielfachzugriff nach dem TDMA-Prinzip würden Zeitschlitze ungenutzt bleiben, im Falle des FDMA-Prinzips wäre auf dem zugewiesenen Band keine kontinuierliche Übertragung möglich, und im Falle von CDMA reserviert das Endgerät einen Spreizcode, ohne ihn kontinuierlich zu nutzen. In allen diesen Fehlerfällen würde das mobile Endgerät zum Engpass im Mobilfunksystem werden, und nicht wie üblich der Mobilfunkkanal.

#### **Paketvermittelte Dienste**

Da paketvermittelte Dienste für die Betreiber von Mobilfunknetzen immer wichtiger werden, dürfen paketorientierte Signalverarbeitung und Zugriff auf ein gemeinsam genutztes Medium in der Argumentationskette nicht ausgelassen werden.

In diesem Falle denke man sich die Forderung nach Übertragungsqualität derart gelockert, dass lediglich im Mittel ein konstanter Nutzdatenfluß durch die physikalische Schicht des Endgerätes aufrechterhalten werden muss. Wenn dieser mittlere Durchsatz in der gleichen Größenordnung liegen soll wie der einer leitungsvermittelten Übertragung, gelangt man schnell zu derselben Schlußfolgerung wie vorher: Ein gemeinsam genutztes Medium erlaubt zwar Paketverzögerungen, ohne notwendigerweise Frequenzressourcen zu verschwenden, aber der Datenspeicher in einem Mobilgerät ist nach wie vor begrenzt, und allein diese Tatsache begrenzt das Zeitfenster zur Mittelung des Datendurchsatzes. Wenn höhere Protokollschichten die physikalische Schicht übermäßig mit Anfragen zur Paketübertragung belasten, beginnt der Speicher mit unverarbeiteten Daten solange vollzulaufen, bis die Signalverarbeitung komplett zusammenbricht. Wiederum würde das mobile Endgerät anstelle des Mobilfunkkanals zum Engpass im Mobilfunksystem werden.

Aus diesen Überlegungen folgt, dass die Signalverarbeitung für alle Dienstklassen

mehr oder weniger harten Echtzeitbedingungen unterworfen ist, und zwar unabhängig davon, ob die physikalische Schicht in Software realisiert ist oder nicht. Die Schritte zur Verarbeitung von Datenrahmen können von Standard zu Standard völlig verschieden sein, sie sind aber innerhalb eines Standards von Rahmen zu Rahmen identisch. Benachbarte Rahmen sind alle gleich aufgebaut und enthalten lediglich andere Binärinformationen. Das Senden und Empfangen von Rahmen über eine Luftschnittstelle (und damit auch die Rahmenverarbeitung) erfolgt in regelmässigen Zeitabständen  $\Delta T$ , entweder strikt (leitungsvermittelt) oder im Mittel (paketvermittelt).

## 2.2.2 Gerichtete Graphen und diskrete Laufzeiten

In einer Umgebung, in der ein Software Defined Radio zum Einsatz kommt, sind also viele verschiedene Luftschnittstellen vorstellbar, die aus unterschiedlichsten nachrichtentechnischen Funktionen bestehen. Unabhängig von dieser Vielfalt sind alle diese Funktionen letztlich aus Softwaremodulen aufgebaut. Allen Modulen ist gemeinsam, dass sie irgendwann vom Betriebssystem zur Abarbeitung auf einem Prozessor  $P_k$  vorgesehen sind.

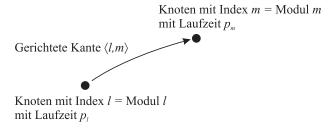

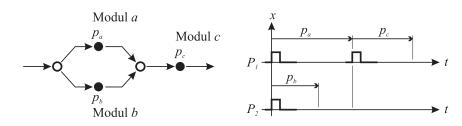

Bild 2.9 Grundlegende Bestandteile gerichteter azyklischer Graphen

Sobald alle von einem Modul m benötigten Eingangsdaten im lokalen Speicher  $M_k$  des Prozessors  $P_k$  verfügbar sind, kann die Ausführung beginnen. Eingangsdaten werden verarbeitet, die Laufzeit  $p_m$  vergeht, und Ausgangsdaten werden erzeugt. Diese Ausgangsdaten sind im Allgemeinen Zwischenergebnisse, die von einem oder mehreren anderen, nachfolgenden Modulen wieder als Eingangsdaten benötigt werden, und das gilt für alle Module zwischen den beiden Dienstzugangspunkten an den Grenzen der physikalischen Schicht. Derartige Datenflüsse können auf abstrakte Art und Weise mit gerichteten azyklischen Graphen (engl. DAG) dargestellt werden. Das Bild 2.9 zeigt die grundlegenden Bestandteile solcher Graphen.

PDU Codierter DTCH

\*\* Codierter DTCH

DPDCH

Abtastwerte

DPCCH

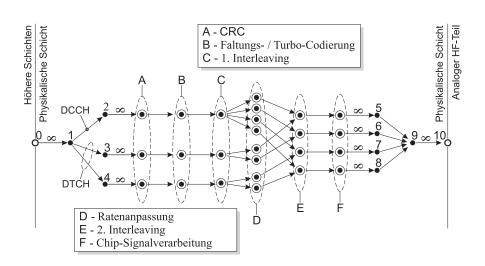

Bild 2.10 Graph mit verschiedenen Knotentypen, Beispiel, Sender eines MMRs

Gefüllte Kreise stehen für eindeutig nummerierte Module. Die Laufzeit  $p_m \in \mathbb{N}$  sei zunächst ein ganzzahliges Vielfaches einer bestimmten Zeitauflösung  $\Delta t$ . Zwischenergebnisse fließen zwischen Modulen entlang durchgezogener, gerichteter Kanten  $\langle l,m \rangle$ . Im Allgemeinen definieren gerichtete Kanten logische Vorgänger-Nachfolger-Beziehungen zwischen Modulen. Kanten, die nicht unmittelbar mit einem Datenfluss verknüpft sind, sollen gestrichelt gezeichnet werden. Die Gesamtheit aller Kanten bildet die Kantenmenge  $\mathbb{K}$ .

Der Graph in Bild 2.10 entstammt der Darstellung eines Multi Mode Radios [114] auf der obersten Hierarchieebene. Knoten einer hierarchischen Graphendarstellung können nicht nur Module sein, sondern auch Funktionen, die als Doppelkreise dargestellt werden. Knoten mit sehr einfachen Funktionen, also z.B. Multiplexer, Demultiplexer oder SAPs, werden als nicht gefüllte, einfache Kreise dargestellt. Solchen Knoten ist die Laufzeit Null zugeordnet. Der Signalfluss in den hier betrachteten gerichteten Graphen verläuft stets von links nach rechts. Alle Rechnungen gehen von einem einzelnen Knoten, dem Startknoten (dem äußersten Knoten links in Bild 2.10), aus und laufen in einem einzelnen Knoten, dem Zielknoten (dem äußersten Knoten rechts in Bild 2.10), zusammen. Start- und Zielknoten können als Dienstzugangspunkte der Schichten interpretiert werden.

Der Graph in Bild 2.10 ist azyklisch, weil er keine Zyklen enthält. Insbesondere sind in solchen Graphendarstellungen also weder Programmschleifen noch Rekursionen erlaubt. Diese Aussage mag zunächst als eine starke Einschränkung erscheinen, weil viele bekannte nachrichtentechnische Funktionen wie z.B. entscheidungsrückgekoppelte Entzerrer, Träger- und Abtastratenregelung sowie Turbo-Decodierung traditionell Schleifenstrukturen enthalten. Bei genauer Betrachtung stellt sich jedoch heraus, dass die Schleifen lediglich zur kompakten Darstellung von Datenabhängigkeiten zwischen Iterationen dienen, während die Abfolge von Maschinenbefehlen innerhalb einer jeden Iteration eindeutig feststeht. Das muss auch so sein,

denn aus Sicht des Prozessors ist zu jedem Zeitpunkt genau klar, welcher Befehl als nächster ausgeführt und mit welchen Daten gearbeitet wird. In der praktischen Realisierung von Schleifen entkoppeln dabei für gewöhnlich Datenspeicher die zyklischen Abhängigkeiten zwischen den Iterationen, und es ist prinzipiell immer möglich, eine Schleife zu entrollen und rein sequentiell darzustellen. Da die gerichteten Kanten in Graphen dafür vorgesehen sind, logische Abfolgen von Modulen darzustellen, können Schleifen im Rahmen des gewählten Software-Modells sogar nur in nicht-iterativer, rein sequentieller Form auftreten. Im Hinblick auf Schleifen und Rekursionen wird in [62] gezeigt, dass beide aus Stabilitätsgründen eine endliche Laufzeit haben müssen. Demnach können in einem Modularen Software Defined Radio alle sinnvollen Rekursionen genau so wie alle sinnvollen Schleifen in rein sequentieller Form dargestellt werden. Folglich stellt die Wahl gerichteter azyklischer Graphen keine prinzipielle Einschränkung dar für das Ziel, ein SDR-Kommunikationsgerät zu entwerfen.

#### 2.2.3 Stochastisches Laufzeit-Modell

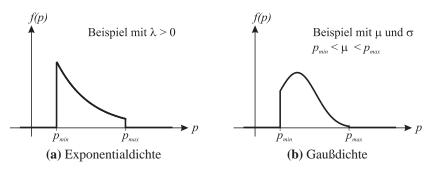

Die Modellierung diskreter Laufzeiten im vorangegangenen Abschnitt entspringt im Wesentlichen der Vorstellung von der Taktung digitaler Rechensysteme. Die Zeitauflösung kann daher im Prinzip so hoch sein, dass  $\Delta t$  genau einem Prozessortakt entspricht. Bestehen aber selbst die kleinsten Softwaremodule aus relativ vielen Maschinenbefehlen, so wird die Quantisierung der Zeitachse dadurch sehr fein, und die Laufzeiten können als quasi-kontinuierlich angesehen werden. Für die Simulation im Rechner wird man daher für die Diskretisierung von Laufzeiten eine weit geringere Auflösung als den Prozessortakt wählen oder gleich mit reellwertigen Laufzeiten arbeiten.

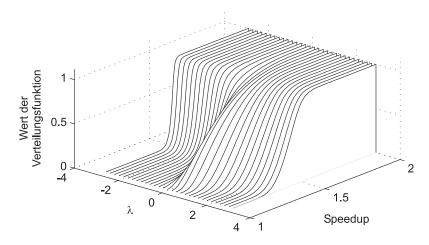

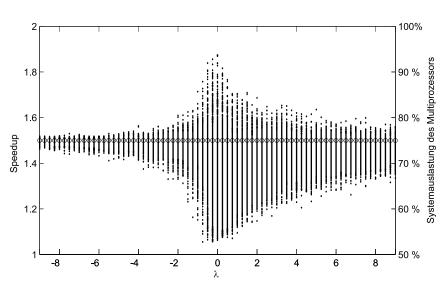

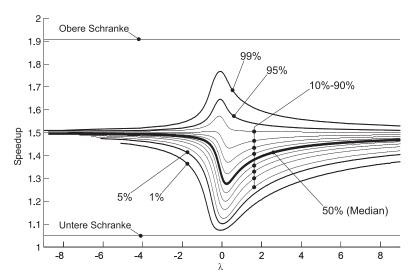

Bereits mehrfach wurde darauf hingewiesen, dass Laufzeiten in einer SDR-Umgebung beliebig aber fest sind, und das nicht nur wegen der wachsenden Zahl an verfügbaren Mobilfunkstandards: Die Kombination der technischen Fähigkeiten von Netzbetreibern, Programmierteams, Geräteherstellern und Softwareanbietern, die Existenz vielfältiger Produktvarianten und verschiedenster Prozessoren, viele verschiedene Anwendungssituationen und letztlich das Verhalten einer großen Menge unabhängiger Nutzer trägt nur dazu bei, dass das Betriebssystem der physikalischen Schicht eines Modularen Software Defined Radios potentiell mit einer ungeheuren Vielfalt von Softwaremodulen und Laufzeiten konfrontiert wird. Ein entscheidender Beitrag der vorliegenden Arbeit ist es, diese potentielle Vielfalt als Zufallspro-

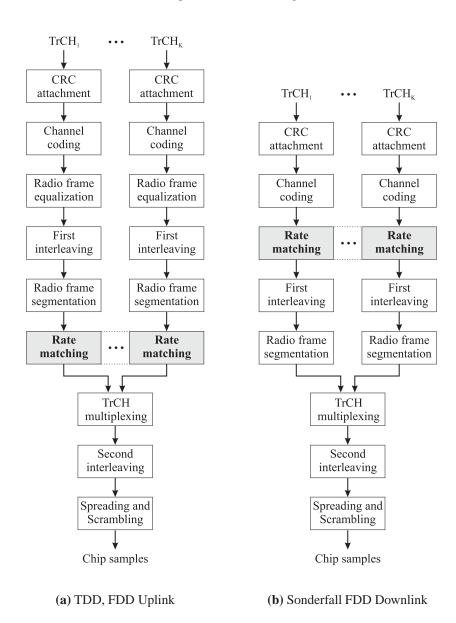

zess zu verstehen. Laufzeiten werden zu Zufallsvariablen, und konkrete Realisierungen von Mobilfunkstandards beinhalten nichts weiter als Realisierungen dieser Zufallsvariablen, die über Graphen in logischen Beziehungen zueinander stehen.