### Andreas Vörg

# Automatisierte Qualifizierung und Auslieferung wiederverwendbarer Komponenten

#### Andreas Vörg

## Automatisierte Qualifizierung und Auslieferung wiederverwendbarer Komponenten

## Automatisierte Qualifizierung und Auslieferung wiederverwendbarer Komponenten

von Andreas Vörg

Dissertation, Eberhard-Karls-Universität Tübingen,

Fakultät für Informations- und Kognitionswissenschaften, 2005

Dekan: Prof. Dr. Michael Diehl

1. Berichterstatter: Prof. Dr. Wolfgang Rosenstiel

2. Berichterstatter: Prof. Dr. Dietmar Müller (Technische Universität Chemnitz)

#### **Impressum**

Universitätsverlag Karlsruhe c/o Universitätsbibliothek Straße am Forum 2 D-76131 Karlsruhe www.uvka.de

Dieses Werk ist unter folgender Creative Commons-Lizenz lizenziert: http://creativecommons.org/licenses/by-nc-nd/2.0/de/

Universitätsverlag Karlsruhe 2005 Print on Demand

ISBN 3-937300-84-8

#### **Danksagung**

Diese Arbeit entstand während meiner Tätigkeiten als wissenschaftlicher Mitarbeiter im Forschungsbereich "Systementwurf in der Mikroelektronik" am FZI Forschungszentrum Informatik an der Universität Karlsruhe.

An dieser Stelle möchte ich Allen danken, die sich in dieser Zeit auf vielfältige Weise an der Entstehung dieser Arbeit beteiligt haben.

Mein besonderer Dank gilt Herrn Prof. Dr. Wolfgang Rosenstiel für die Betreuung und Unterstützung während meiner Arbeit, für seine wertvollen Hinweise und die Übernahme des Gutachtens. Ebenso danke ich Herrn Prof. Dr. Dietmar Müller für die Erstellung des Gutachtens.

Danken möchte ich auch allen meinen Kollegen für die Diskussionen, Hinweise, Vorschläge und Korrekturen. Dies alles hat zum Gelingen dieser Arbeit beigetragen.

Ohne die finanzielle Unterstützung des Projekts "Intellectual Property Qualifizierung" (IPQ - 01M3048) und des europäischen MEDEA+ Projekts "Tools and Methods for Intellectual Property" (ToolIP - A511) durch das Bundesministerium für Bildung und Forschung (BMBF) wäre meine Arbeit nicht möglich gewesen. Ich bedanke mich recht herzlich dafür.

Ein ganz besonderer Dank gilt meiner Frau für ihr Verständnis und ihre besondere Unterstützung in diesem Lebensabschnitt. Schließlich danke ich meinen Eltern, die mich stets bestärkt und unterstützt und mir so meinen Weg ermöglicht haben.

Hannover im Juni 2005 Andreas Vörg

#### Inhaltsverzeichnis

| Danksagung                                          | i   |

|-----------------------------------------------------|-----|

| Inhaltsverzeichnis                                  | iii |

| Kurzfassung                                         | vii |

| 1 Einleitung                                        | 1   |

| 1.1 Ausgangssituation                               | 1   |

| 1.2 Ziel der Arbeit                                 | 4   |

| 1.3 Aufbau der Arbeit                               | 5   |

| 2 Grundlagen                                        |     |

| 2.1 Konventionen                                    | 7   |

| 2.2 Entwurf elektronischer Schaltungen              | 8   |

| 2.2.1 Integrationsdichte                            |     |

| 2.2.2 System-auf-einem-Chip                         |     |

| 2.3 Entwurfsmethoden                                |     |

| 2.3.1 IP-basierter Entwurf                          | 9   |

| 2.3.2 Plattformbasierter Entwurf                    | 11  |

| 2.4 Abstraktionsebenen                              | 12  |

| 2.4.1 Systemebene                                   | 13  |

| 2.4.2 Algorithmische Ebene                          | 14  |

| 2.4.3 Register-Transfer-Ebene                       |     |

| 2.4.4 Logikebene                                    | 14  |

| 2.4.5 Physikalische Ebene                           | 14  |

| 2.5 Qualität                                        | 15  |

| 2.5.1 Qualitätskriterien                            | 16  |

| 2.5.2 IP-Qualitätsmessung                           | 17  |

| 2.5.3 IP-Qualitätsbewertung                         | 18  |

| 3 Stand der Technik                                 | 23  |

| 3.1 Qualitätskriterien und -bewertung für IP-Module | 23  |

| 3.2 Standardisierung der Qualitätskriterien         | 24  |

| 3.3 Automatisierung der Qualitätsmessungen          | 26  |

| 3.4 Qualifizierungswerkzeuge                        | 26  |

| 3.5 Wiederverwendungsdatenbanken                    | 27  |

| 3.6 Anpassung von IP-Modulen                        | 27  |

| 3.7 IP-Auslieferung                                 | 28  |

| 3.8 IP-Formate                                      | 29  |

| 3.8.1 OpenAccess-Format                             | 29  |

| 3.8.2 Platform Express Format                       |     |

| 3.8.3 SPIRIT-Format                                 | 30  |

| 3.8.4 Advanced Library Format                       | 30  |

|                                                     |     |

|   | 3.9 Zusammenfassung der offenen Probleme                | . 31 |

|---|---------------------------------------------------------|------|

| 4 | IP-Qualifizierung                                       | . 33 |

|   | 4.1 Automatisierbare Kriterienprüfungen                 | . 33 |

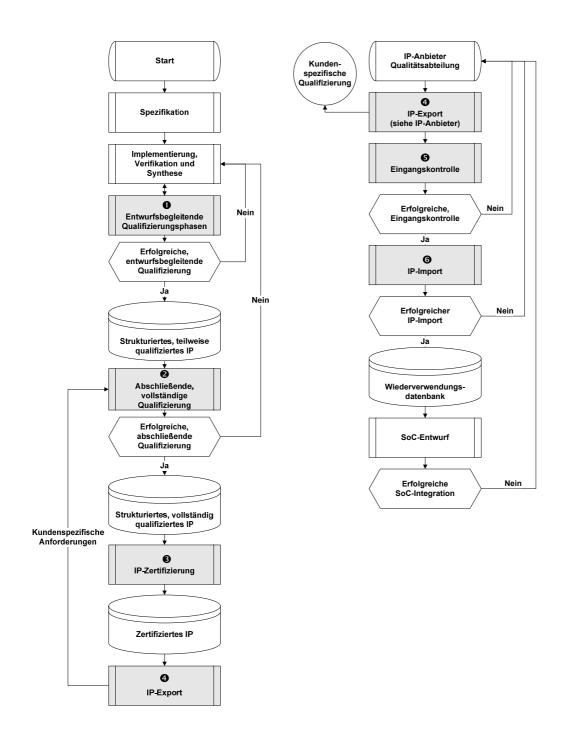

|   | 4.2 Entwurfsablauf und Wiederverwendungsprozess         | . 34 |

|   | 4.2.1 Entwurfsbegleitende Qualifizierungsphase          | . 37 |

|   | 4.2.2 Abschließende Qualifizierungsphase                | . 38 |

|   | 4.2.3 IP-Zertifizierungsphase                           | .40  |

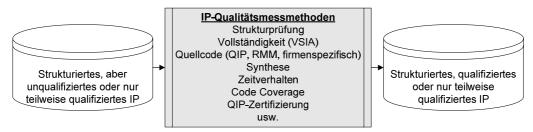

|   | 4.3 Qualitätsmessmethoden                               | .41  |

|   | 4.3.1 Quellcodequalität                                 | . 42 |

|   | 4.3.2 Validierung                                       | . 43 |

|   | 4.3.3 Entwurfsqualität                                  | .44  |

|   | 4.3.4 Integritätsprüfung                                | . 44 |

|   | 4.3.5 Konsistenzprüfung                                 | . 45 |

| 5 | IP-Austausch und -Auslieferung                          | . 47 |

|   | 5.1 IP-Austausch – ein Überblick                        | . 47 |

|   | 5.2 IP-Format Anforderungen                             | . 49 |

|   | 5.2.1 IP-Struktur                                       | . 49 |

|   | 5.2.2 Unabhängigkeit der IP-Struktur                    | . 50 |

|   | 5.2.3 Semantik der IP-Struktur                          | . 50 |

|   | 5.2.4 Vermeidung einer Werkzeug-API                     | . 51 |

|   | 5.2.5 Dokumentation des Entwurfablaufs                  | .51  |

|   | 5.2.6 Nachvollziehbarkeit der Qualifizierungsergebnisse | . 51 |

|   | 5.2.7 Qualitätsmessungen und -dokumentation             | . 51 |

|   | 5.2.8 Vollständigkeits- und Integritätsmessungen        | . 52 |

|   | 5.2.9 Modellierung von Abhängigkeiten                   | . 52 |

|   | 5.2.10 Dauer des IP-Imports                             | . 52 |

|   | 5.2.11 Zusammenfassung der Anforderungen                | . 53 |

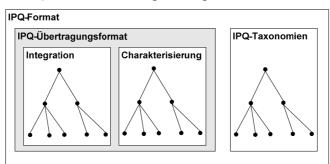

|   | 5.3 IPQ-Format                                          | . 53 |

|   | 5.4 IPQ-Integrationsdatenformat                         | . 54 |

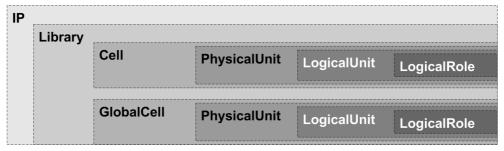

|   | 5.4.1 Bibliotheken                                      | . 55 |

|   | 5.4.2 Zellen                                            | . 56 |

|   | 5.4.3 Physikalische Einheiten                           | . 56 |

|   | 5.4.4 Logische Einheiten                                | . 56 |

|   | 5.4.5 Logische Rollen                                   | . 56 |

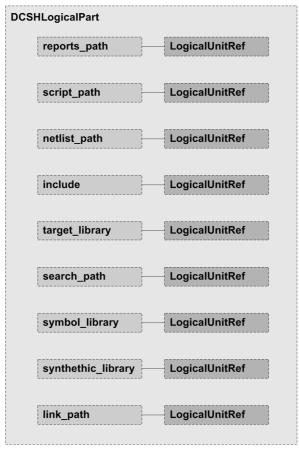

|   | 5.4.6 Logische Teile                                    | . 57 |

|   | 5.4.7 Erweiterbarkeit                                   | . 57 |

|   | 5.4.8 Formatpflege                                      | . 57 |

|   | 5.5 IP-Qualifizierungsphasen                            | . 58 |

|   | 5.5.1 IP-Export                                         | . 58 |

|   | 5.5.2 Virtueller IP-Export                              | . 61 |

|   |                                                         |      |

| 5.5.3 IP-Übermittlung und Eingangskontr | olle61 |

|-----------------------------------------|--------|

| 5.5.4 IP-Import                         | 62     |

| 6 Implementierung                       | 71     |

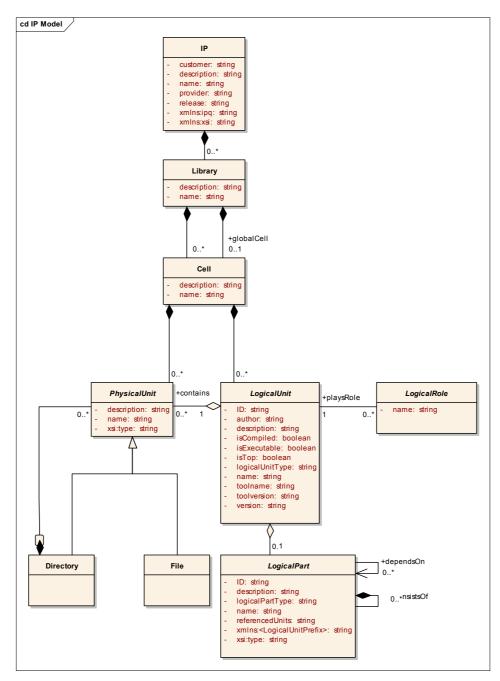

| 6.1 IPQ-Integrationsdatenformat         | 71     |

| 6.1.1 IP-Modul                          | 72     |

| 6.1.2 Bibliotheken                      | 72     |

| 6.1.3 Zellen                            | 72     |

| 6.1.4 Physikalische Einheiten           | 73     |

| 6.1.5 Logische Einheiten                | 73     |

| 6.1.6 Logische Rollen                   | 74     |

| 6.1.7 Logische Teile                    | 74     |

| 6.2 IP-Wiederverwendungsdatenbank       | 79     |

| 6.3 IP-Qualifizierungsframework         | 80     |

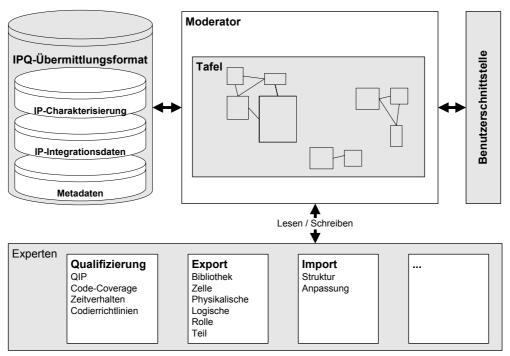

| 6.3.1 Tafelarchitektur                  | 80     |

| 6.3.2 Erweiterung um neue Datentypen    | 82     |

| 6.3.3 Nutzung des Objektmodells         | 85     |

| 6.3.4 Qualifizierungsexperten           | 86     |

| 7 Ergebnisse                            | 109    |

| 7.1 Standardisierung                    | 109    |

| 7.2 IP-Qualifizierung                   | 109    |

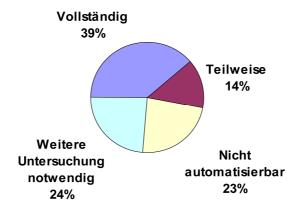

| 7.2.1 IP-Qualifizierungsphasen          | 110    |

| 7.2.2 Fallstudie                        | 110    |

| 7.3 IP-Auslieferungsphasen              | 114    |

| 8 Zusammenfassung und Ausblick          | 115    |

| 8.1 Erreichte Ziele                     | 115    |

| 8.2 Ausblick                            | 116    |

| Literaturverzeichnis                    | 117    |

| Anhang A                                | 121    |

| A.1 Implementierung                     | 121    |

| Anhang B Verzeichnisse                  | 125    |

| B.1 Akronyme und Abkürzungen            | 125    |

| B.2 Abbildungsverzeichnis               | 126    |

| B.3 Tabellenverzeichnis                 | 127    |

| B.4 Quellcode-Verzeichnis               | 128    |

#### Kurzfassung

Aktuelle und zukünftige Chipentwürfe werden aus wiederverwendbaren Basisbausteinen, so genannten IP-Modulen, aufgebaut. Diese IP-Module müssen definierte Qualitätskriterien erfüllen, um den Chipentwurf zu beschleunigen, das Integrationsrisiko aufseiten des IP-Nutzers und den Aufwand für Nacharbeit aufseiten des IP-Anbieters zu reduzieren. Die Übereinstimmung des IP-Modulentwurfs mit diesen Kriterien muss automatisch geprüft werden, da durch das exponentielle Komplexitätswachstum manuelle Prüfungen nicht mehr durchführbar sind. Qualitätsmängel und die Bindung von Ressourcen, die durch einen konventionellen Austauschprozess nach der Qualifizierung durch den IP-Anbieter entstehen, können durch einen automatisierten, qualitätserhaltenden IP-Austauschprozess verhindert beziehungsweise wesentlich reduziert werden.

Die vorliegende Arbeit stellt eine automatisierte Qualifizierungs- und Auslieferungsmethode anhand applikationsunspezifischer Standardqualitätskriterien für digitale Soft-IP-Module vor. Die Automatisierung basiert auf einem einheitlichen Qualifizierungs- und Austauschformat. Durch die vorgestellten Methoden wird der gesamte Wiederverwendungsprozess vorhersehbarer und robuster. Einerseits bleiben qualifizierte Merkmale erhalten und andererseits dürfen mehr als 80 % Zeit- und Ressourceneinsparungen erwartet werden.

**Schlüsselwörter:** Intellectual Property; IP; Virtual Component; VC; VSIA; QIP; Quality IP; Auslieferung; Export; Import; Qualität; Qualifizierung; Automatisierung; Austauschformat; Qualitätsbewertung

#### 1 Einleitung

Die Mikroelektronik steht an der Schwelle zur Nanoelektronik. Erste Produkte in 90-nm-Technologie, wie beispielsweise AMDs Opteron-Prozessor, der seit dem Frühjahr 2004 in Dresden gefertigt wird, dokumentieren den Übergang zur Nanoelektronik. SEMATECH prognostiziert in der "International Technology Roadmap for Semiconductors" (ITRS) im Jahr 2007 den 65-nm-Technologieknoten zu erreichen und 2010 den 45nm-Knoten [54]. Aktuellere Quellen kündigen erste Produkte in 65-nm-Technologie sogar schon für 2006 an. So soll beispielsweise die 65-Nanometer-Fertigung von AMD64-Prozessoren 2006 in Dresden beginnen [78]. Dadurch wird einmal mehr der ungebrochen anhaltende Trend in der Halbleiterfertigung deutlich gemacht. Mit geringen Schwankungen stehen alle 18 Monate neue Fertigungstechnologien bereit, die elektronische Schaltungen mit sinkender Strukturgröße auf wachsender Chipfläche und Waferfläche ermöglichen. Bereits 1965 hat Gordon Moore diesen Trend vorausgesagt, der auch als "Mooresches Gesetz" bekannt ist. Seitdem folgt die Halbleiterforschung und -industrie diesem Gesetz ([26], [27]). Das Mooresche Gesetz zählt zu den wenigen Dingen, die sich in diesem von Veränderungen geprägten Umfeld nicht verändert hat. Es hat immer noch seine Gültigkeit.

In der Vergangenheit haben technologische Möglichkeiten Halbleiterprodukte in ihrer Realisierbarkeit begrenzt. Inzwischen ist die Entwurfsproduktivität das begrenzende Glied in der Herstellungskette. Laut einer SEMATECH-Studie wächst die Entwurfsleistung mit lediglich 21 %. Ihr steht eine Zunahme der technologisch realisierbaren Komplexität von ca. 58 % gegenüber [28]. Die Komplexität ist durch die eingangs beschriebenen Fortschritte in der Fertigungstechnologie bedingt. Die Lücke zwischen Entwurfs- und Komplexitätswachstum wird Produktivitätslücke (engl. productivity gap) genannt. Sie zu schließen ist die Herausforderung an die Forschung in der elektronischen Entwurfsautomatisierung (engl. Electronic Design Automation, EDA).

Die exponentiell wachsende Zahl an integrierbaren Transistoren (Integrationsdichte) ermöglicht den Entwurf kompletter elektronischer Systeme auf einem einzigen Chip. Solche Systeme werden auch System-auf-einem-Chip (engl. System-on-a-Chip, SoC) genannt. Aufgrund der geschilderten Wachstumsverhältnisse ist es gegenwärtig eine Herausforderung, die geplante Produkteinführungszeit (engl. Time-to-Market) bei immer kürzer werdenden Entwicklungszyklen einzuhalten. In der Zukunft wird es sogar unmöglich sein, einen Entwurf erfolgreich abzuschließen, wenn nicht neue Entwurfsmethoden angewendet werden [29].

#### 1.1 Ausgangssituation

Aus diesem Grund wurde in den 90er Jahren die Methode der Wiederverwendung zur Steigerung der Entwurfsproduktivität eingeführt. In [57] wird sogar eine Halbierung der Entwurfskosten durch Wiederverwendung

prognostiziert. Das Neue an dieser Art der Wiederverwendung ist die Abstraktionsebene, auf der Funktionalität gekapselt und wieder verwendet wird. Seit jeher war Abstraktion ein erfolgreiches Mittel zur Beherrschung der wachsenden Komplexität. Transistoren wurden durch logische Gatter abstrahiert und logische Gatter durch arithmetische Funktionen (Addierer, Multiplizierer, Multiplexer usw.). Mit jedem Abstraktionsschritt konnte die Erzeugung der darunter liegenden (weniger abstrakten) Ansichten zunehmend EDA-Werkzeugen überlassen werden. Dadurch konnte jeweils eine Steigerung der Entwurfsproduktivität erreicht werden.

Die in der vorgelegten Arbeit behandelte Wiederverwendungsmethode schlägt die Erzeugung elektronischer Modulentwürfe (Prozessoren, Mikrokontroller, Standardschnittstellen (PCI, USB, ...) usw.) vor, um diese als Grundbausteine in mehreren unterschiedlichen SoC-Entwürfen wieder zu verwenden [44]. Wiederverwendbare Module werden auch Intellectual Property (IP) genannt. Durch die Vermeidung des Neuentwurfs und einer kontinuierlichen Verbesserung evtl. enthaltener Entwurfsfehler reduziert diese Methode die Komplexität und damit das Entwurfsrisiko. Darüber hinaus unterstützt sie die Einhaltung der geplanten Produkteinführungszeit. Ein SoC kann sehr viel schneller aus bereits verifizierten IP-Modulen aufgebaut werden, als es in einer kompletten Neuentwicklung möglich ist. Im Vergleich zu einem einmaligen Auftragsprojekt für ein Funktionsmodul erhöhen wiederverwendbare IP-Module darüber hinaus den Kapitalertrag (engl. Return on Investment, ROT). Der Grund dafür liegt in der Wiederverwendbarkeit des IP-Entwurfs in verschiedenen Projekten innerhalb der eigenen Firma aber auch durch einen externen IP-Nutzer.

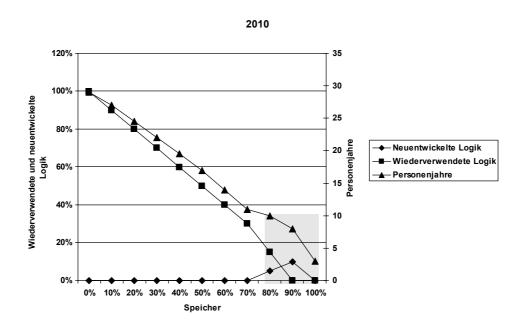

Abbildung 1 zeigt, dass, neben den Vorteilen des IP getriebenen SoC-Entwurfs, Wiederverwendung sogar absolut notwendig ist, um ein SoC-Projekt erfolgreich zu beenden [29]. In Abbildung 1 geht die ITRS von einer 42 prozentigen Verbesserung der Entwurfsproduktivität aus. Die ITRS bezeichnet dieses Wachstum selbst als unzureichend. Ihre Prognose geht davon aus, dass ein erfolgreicher SoC-Entwurf innerhalb eines Zeitrahmens von zehn Personenjahren fertig gestellt sein muss, dass so viel wie möglich neue Logik im SoC-Entwurf integriert werden soll und dass wiederverwendbare Logik doppelt so schnell integriert werden kann wie neue Logik. Die Ressourcen für Speichergenerierung werden wegen der Verwendung von Speichergeneratoren vernachlässigt. Unter diesen Umständen ist ein erfolgreicher SoC-Entwurf im Jahr 2010 nur möglich, wenn über 80 % der verfügbaren Chipfläche von Speicher belegt sind (grau hinterlegter Bereich in Abbildung 1 auf Seite 3).

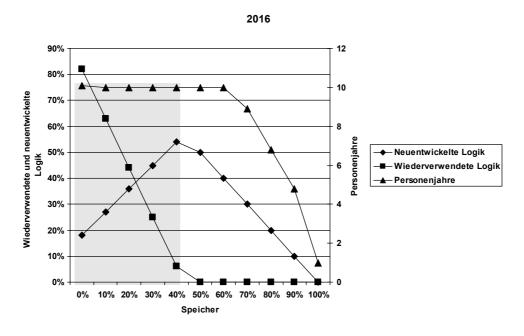

Die Entwurfsproduktivität muss um 100 % verbessert werden, um auch in Zukunft erfolgreiche SoC-Projekte durchführen zu können. Die Voraussetzung für eine solche Verbesserung der Entwurfsproduktivität ist der Einsatz eines hohen Anteils (zwischen sechs und 82 %) wiederverwendbarer Logik. Dieser Anteil ist notwendig, wenn neue Logik maximiert werden und weniger als die Hälfte des SoC von Speicher belegt sein soll. Abbildung 2 auf Seite 3 zeigt, dass dadurch erfolgreiche SoC-Projekte bis ins Jahr 2016 ermöglicht werden.

Abbildung 1: Ungenügende 42 prozentige Verbesserung der Entwurfsproduktivität für SoC im Jahre 2010 nach ITRS 2001

Abbildung 2: Ausreichende 100 prozentige Verbesserung der Entwurfsproduktivität für SoC im Jahre 2016 nach ITRS 2001

IP-Module werden von IP-Anbietern unabhängig vom Anwendungskontext entwickelt, um ihren Wiederverwendungsgrad zu erhöhen. Sie werden dann in einer möglichst großen Zahl von applikationsspezifischen Projekten wieder verwendet. In Deutschland und Europa haben sich Kernkompetenzen für Automotive-, Telekommunikation- und zunehmend auch Multimediaapplikationen etabliert. Seit der Einführung des IP-basierten

Entwurfs hat sich ein wachsender Markt für IP-Module entwickelt. Es werden beispielsweise Prozessoren, Mikrokontroller, digitale Signalprozessoren, Peripheriekomponenten, Komprimierungs- und Dekomprimierungskomponenten, kryptografische und multimediale Verschlüsselungsund Entschlüsselungskomponenten angeboten und wieder verwendet. Die Wiederverwendbarkeit muss sowohl durch eine sorgfältige Marktanalyse vor der Entwicklung eines IP-Moduls als auch durch die Übereinstimmung des Entwurfs mit Wiederverwendbarkeitskriterien während und bei Abschluss der Entwicklung eines IP-Moduls sichergestellt werden.

Häufig werden IP-Module nicht nur intern (in der eigenen Firma zwischen Abteilungen), sondern auch mit externen (über Firmengrenzen hinweg) IP-Nutzern ausgetauscht. Dabei hat sich gezeigt, dass insbesondere die externe Wiederverwendung nicht die gewünschte Beschleunigung beim Entwurf komplexer Systeme gebracht hat. Die Analyse der Wiederverwendungsprozesse in Forschung und Industrie hat gezeigt, dass die Schnittstelle zwischen IP-Anbieter und IP-Nutzer nur unzureichend definiert ist. Unter Schnittstelle ist die Qualität des IP-Moduls zu verstehen. Eine ausreichend definierte, aber proprietäre Schnittstellenvereinbarung kann den Nutzen bei weitem übersteigen [32] und der Aufwand zur Einhaltung der geforderten Qualität kann mit enormen Kosten verbunden sein [77]. Insbesondere muss die Extraktion aus der Entwicklungsumgebung des IP-Anbieters beziehungsweise die Integration in die Entwicklungsumgebungen des IP-Nutzers unterstützt werden. Dabei spielt die Gewährleistung der Qualität eine enorme Rolle.

#### 1.2 Ziel der Arbeit

Das Ziel der vorliegenden Arbeit ist es, die Schnittstelle zwischen IP-Anbieter und IP-Nutzer überprüfbar zu gestalten und dadurch die Erhaltung standardisierter Qualitätsmerkmale aus dem Entwurfsablauf des IP-Anbieters in den SoC-Integrationsprozess des IP-Nutzers zu garantieren. Anhand quantitativer Ergebnisse wird belegt werden, dass die Nutzung der vorgeschlagenen Methoden eine Verbesserung der Wiederverwendbarkeit und eine Verringerung des Integrationsrisikos zur Folge hat. Dieses Ziel wird mit automatisierten Qualifizierungs- und Auslieferungsmethoden anhand von Standardqualitätskriterien für digitale Soft-IP-Module erreicht. Die Automatisierung basiert auf einem einheitlichen Qualifizierungs- und Austauschformat. Durch die vorgestellten Methoden wird der gesamte Wiederverwendungsprozess vorhersehbarer und robuster. Einerseits bleiben qualifizierte Merkmale erhalten und andererseits dürfen mehr als 80 % Zeit- und Ressourceneinsparungen erwartet werden.

Es wird gezeigt, dass die Einhaltung von Qualitätsmerkmalen das Integrationsrisiko verringert und den Wiederverwendungsprozess beschleunigt. Das kann aber nur erreicht werden, wenn die Einhaltung dieser Merkmale mit vertretbarem Aufwand sowohl vom IP-Anbieter als auch vom IP-Nutzer überprüft werden kann. Des Weiteren muss die Einhaltung der Merkmale auch nach der IP-Übermittlung vom IP-Anbieter an den IP-Nutzer sichergestellt sein. Dazu wird eine Austauschmethode erforscht, durch die

die Erhaltung dieser Merkmale bis in den SoC-Entwurf gewährleistet wird. Nur so wird es möglich sein, die von der ITRS prognostizierte Zahl an IP-Modulen bereitzustellen und diese in kalkulierbarer Zeit mit vorhersehbarem Risiko zu integrieren.

#### 1.3 Aufbau der Arbeit

Im folgenden Kapitel 2 werden die Grundlagen für die vorliegende Arbeit gelegt. Benötigte Begriffe werden definiert und die relevanten Entwurfsmethoden vorgestellt.

Themenverwandte Arbeiten, Werkzeuge und Organisationen, die an der IP-Qualifizierung und Standardisierung beteiligt sind, werden in Kapitel 3 vorgestellt, um den aktuellen Stand der Technik aufzuzeigen.

Der Hauptteil dieser Arbeit wird in den Kapiteln 4 und 5 dargelegt. Es wird die IP-Qualifizierungsmethode zur automatischen Überprüfung von Standardqualitätskriterien beschrieben und wie derartig qualifizierte IP-Module ohne Qualitätsverlust automatisiert an einen IP-Anbieter übertragen und in den Chipentwurfsablauf integriert werden können.

Das einheitliche Qualifizierungs- und Austauschformat sowie die Implementierung der vorgestellten Methoden wird in Kapitel 6 beschrieben.

In Kapitel 7 werden die ermittelten Ergebnisse diskutiert, um die Tauglichkeit der vorgestellten Methoden zu verdeutlichen. Mit einer Zusammenfassung und einem kurzen Ausblick auf mögliche Anknüpfungspunkte und Anwendungsmöglichkeiten schließt Kapitel 8.

#### 2 Grundlagen

In den nachfolgenden Kapiteln wird ausführlich auf die Qualifizierung und den Austausch von IP-Modulen eingegangen. Doch zuvor werden in diesem Kapitel die zum Verständnis benötigten Grundlagen und Definitionen dargestellt. Verwendete Begriffe werden erläutert und es wird darauf eingegangen, in welchem Umfeld IP-Module verwendet werden und auf welche IP-Module die vorliegende Arbeit angewendet werden kann.

Die in der vorliegenden Arbeit verwendeten Konventionen werden in Abschnitt 2.1 erläutert.

Ausgehend von den Bedingungen unter denen elektronische Schaltungen entworfen werden, wird in Abschnitt 2.2 auf die Möglichkeit des SoC-Entwurfs eingegangen.

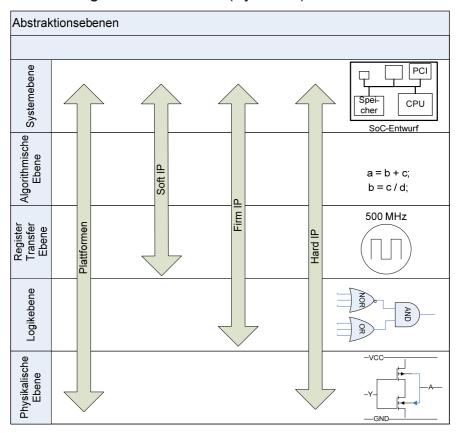

Die Zusammenhänge zwischen IP-basierter und plattformbasierter Entwurfsmethodik werden in Abschnitt 2.3 dargelegt. Anschließend werden die aus der Literatur bekannten IP-Härtegrade in die gewohnten Abstraktionsebenen in Abschnitt 2.4 eingeordnet.

Schließlich definiert Abschnitt 2.5 die verwendeten Qualitätsbegriffe.

#### 2.1 Konventionen

Im Verlauf dieser Arbeit werden die folgenden Konventionen verwendet.

| Konvention                                           | Steht für                                                                                                                                                                                                                                                                                                                                                        |

|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <variablenname> oder \$Variablenname</variablenname> | Variablennamen sind in spitzen Klammern eingeschlossen oder es ist ein \$-Zeichen vorangestellt. Des Weiteren gelten die Konventionen zur Darstellung von Variablen des jeweils dargestellten Datenformats. Beispielsweise werden in XML Tags in spitzen Klammern codiert. In diesem Fall hat die spitze Klammer also nicht die hier erläuterte Sonderbedeutung. |

| Quellcode                                            | Quellcode ist in der Schriftart Courier New gesetzt.                                                                                                                                                                                                                                                                                                             |

| Dateinamen                                           | Verzeichnis- und Dateinamen sind in der<br>Schriftart Courier New und kursiv gesetzt.                                                                                                                                                                                                                                                                            |

| Wichtige Begriffe                                    | Wichtige Begriffe werden bei ihrer ersten<br>Verwendung und Erklärung durch Fettdruck<br>hervorgehoben.                                                                                                                                                                                                                                                          |

**Tabelle 1: Verwendete Konventionen**

Verwendete Akronyme und Abkürzungen werden im Anhang auf Seite 125 erläutert.

#### 2.2 Entwurf elektronischer Schaltungen

Die Entwicklung der Entwurfsmethoden für elektronische Schaltungen wird im Wesentlichen durch die exponentiell wachsende Integrationsdichte getrieben.

#### 2.2.1 Integrationsdichte

Die Integrationsdichte bezeichnet die Anzahl Transistoren eines Mikrochips pro Flächeneinheit. Gemäß dem Mooreschen Gesetz verdoppelt sich die Integrationsdichte etwa alle 18 Monate, was seit über 35 Jahren mit kleinen Schwankungen zutrifft.

So enthielt 1999 Intels erster Pentium-III mit 500 MHz Taktfrequenz noch einen externen L2-Cache und bestand aus etwa 9,5 Millionen Transistoren. Nur etwa 1½ Jahre später arbeitete der Pentium 4 bereits mit 1,4 GHz Taktfrequenz, einer 20-stufige Pipeline, wurde in 130-nm-Technologie gefertigt und bestand aus etwa 42 Millionen Transistoren.

Das Wachstum der Integrationsdichte ist durch die Verkleinerung der physikalischen Strukturen auf dem Chip bedingt. Derzeit überschreitet die Mikroelektronik die Schwelle zur Nanoelektronik mit ersten Produkten in 90-nm-Technologie. Als Beispiel sei AMDs Opteron-Prozessor genannt, der seit dem Frühjahr 2004 in Dresden gefertigt wird. Die International Technology Roadmap for Semiconductors (ITRS) rechnet 2007 damit den 65-nm-Technologieknoten zu erreichen und 2010 den 45-nm-Knoten [54].

Diese Beispiele zeigen, dass in absehbarerer Zeit nicht mit einer Abflachung oder gar Konvergenz des exponentiellen Integrationsdichtewachstums zu rechnen ist. Die fortschreitende Verkleinerung der physikalischen Strukturen (Leiterbahnen, Transistoren usw.) ermöglicht die Fertigung eines kompletten Systems-auf-einem-Chip (engl. System-on-a-Chip, SoC).

#### 2.2.2 System-auf-einem-Chip

In der Vergangenheit musste die Funktionalität eines Systems auf mehrere Chips verteilt werden. Diese Chips wurden anschließend auf Leiterplatten zu einem System integriert. Aber schon heute ist aufgrund der wachsenden Integrationsdichte die Funktionalität eines gesamten Systems auf einem einzigen Chip integrierbar. Mit Erreichen des 45-nm-Knotens werden fast eine Milliarde Transistoren auf einem einzigen Chip zur Verfügung stehen. Die hieraus resultierenden Parameter, welche die Systemfunktion beeinflussen, können beim Entwurf unmöglich einzeln berücksichtigt werden. Andererseits soll das Potenzial eines Chips ausgeschöpft werden. Das bedeutet, die Entwurfskomplexität muss beherrscht werden. Systementwickler könnten andernfalls ungenutzte Chipfläche nur durch automatische Generierung homogener Strukturen, wie z. B. mit Speichermatrizen, füllen. Aus diesem Grund sind verschiedene Entwurfsmethoden mit fortschreitender Zunahme der Entwurfskomplexität erforscht und eingesetzt worden.

#### 2.3 Entwurfsmethoden

Um beim Entwurf nicht alle Parameter berücksichtigen zu müssen, wurden Entwurfsmethoden entwickelt, die mit fortschreitender Integrationsdichte zunehmend von den physikalischen Transistorparametern abstrahieren. Dies ist die einzige Möglichkeit, um die fortschreitende Komplexität zu beherrschen. Wurden früher Transistoren durch logische Gatter (AND, NAND, OR, NOR, ...) und später Gatter durch arithmetische Funktionen (Addierer, Multiplizierer, Multiplexer, ...) abstrahiert, so abstrahieren heute Funktionsblöcke (IP-Module) komplette Prozessoren (CPU, DSP), Mikrokontroller (MCU) usw. Diese IP-Module werden beim IP-basierten Entwurf als Basisbausteine für den Systemaufbau verwendet.

#### 2.3.1 IP-basierter Entwurf

Hardware, die häufig benötigte Aufgaben erfüllt, wird von spezialisierten Anbietern (IP-Anbieter) als wiederverwendbarer Funktionsblock (IP-Modul) entwickelt. So werden beispielsweise im Multimediabereich Audio und Video Codecs, für Ver- und Entschlüsselungsaufgaben, Kryptografieblöcke oder Standardschnittstellen (z. B. PCI, OCP-IP [60]) für die Verbindung der Blöcke über On-Chip Busse (z. B. AMBA) angeboten. Solche IP-Module werden beim IP-basierten Entwurf als Basisbausteine für die SoC-Entwicklung von einem IP-Nutzer verwendet.

Ein SoC besteht aus mindestens einem Prozessor, häufig aber aus einer Kombination von CPU, DSP und MCU, Speicher und Peripheriehardware. Spezielle Hard- und Software zur Erfüllung der Systemfunktionalität wird zusätzlich in Form von IP-Modulen in den Chipentwurf integriert.

IP-Module (engl. Intellectual Property Module) oder kurz IPs werden häufig auch als virtuelle Komponenten (engl. Virtual Components, VC) bezeichnet. Der Begriff "Virtual Component™" ist eine geschützte Bezeichnung der Virtual Socket Interface Alliance für Komponenten. welche die Virtual Socket Interface™ Spezifikation erfüllen [56]. Diese Spezifikation muss noch als visionär bezeichnet werden. Sie beschreibt eine Standardschnittstelle für virtuelle Komponenten und Sockel, die unabhängig von der gekapselten Funktion ist. Vorlagen für Systementwürfe (Plattformen) stellen die virtuellen Sockel bereit, in die dann unabhängig von dieser Vorlage entworfene, beliebige virtuelle Komponenten eingesetzt werden können. Dadurch soll eine einfache Austauschbarkeit und Wiederverwendbarkeit sichergestellt werden. In der Praxis werden die beiden Begriffe IP und VC jedoch gleichwertig benutzt. Im Laufe dieser Arbeit wird in der Regel von IP-Modulen gesprochen, da es der geläufigere Begriff ist. Soll die Einhaltung bestimmter Qualitätskriterien betont werden, wird der Begriff qualifiziertes IP verwendet. Diese Begriffe werden in Abschnitt 2.5 definiert.

Ein gebräuchliches Charakterisierungsmerkmal für IP-Module ist ihre "Härte" beziehungsweise der Grad, mit dem sie auf einen bestimmten Fertigungsprozess abgestimmt sind. Dabei spiegelt der Härtegrad die Abstraktionsebene wieder, auf der die Integrationsdaten des IP-Moduls beschrieben sind. Die üblichen Abstraktionsebenen werden in Abschnitt

2.4 erklärt. Anerkannt sind die Härtegarde der VSIA in [56]. Sie werden im Folgenden erläutert.

#### 2.3.1.1 Soft-IP

Soft-IP wird als synthetisierbare HDL-Beschreibung ausgeliefert und hat dadurch den Vorteil am flexibelsten zu sein und den Nachteil, dass seine zeitliche Leistungsfähigkeit, der Flächenbedarf und die elektrische Leistungsaufnahme nur bedingt vorhersehbar sind. Die Notwendigkeit, den RTL-Quellcode an den IP-Nutzer ausliefern zu müssen, erhöht das Missbrauchrisiko des geistigen Eigentums für Soft-IP-Module.

#### 2.3.1.2 Firm-IP

Firm-IP ist strukturell und topologisch hinsichtlich Leistungsfähigkeit und Flächenbedarf durch Platzierung und Verwendung einer allgemeinen Technologiebibliothek optimiert. Der Detaillierungsgrad reicht von der Platzierung der RTL-Blöcke über relativ platzierte Datenpfade und parametrisierte Generatoren, bis zu einer vollständig platzierten Netzliste. Häufig wird eine Kombination dieser Ansätze angewandt, um das Entwurfsziel zu erreichen. Firm-IP stellt einen Kompromiss zwischen Softund Hard-IP dar. Es ist flexibler und portierbarer als Hard-IP, aber vorhersehbarer in der Leistungsfähigkeit und dem Flächenbedarf als Soft-IP. Der Auslieferungsumfang eines Firm-IP-Moduls enthält eine Kombination aus synthetisierbarem RTL-Quellcode, Referenztechnologiebibliothek. detailliertem Platzierungsplan und eine vollständige oder in Teilen vorhandene Netzliste. Wird eine vollständige Netzliste ausgeliefert, so wird erwartet, dass Testlogik eingefügt wurde und Testlisten zum Lieferumfang gehören. Firm-IP ist nicht verdrahtet. Das Missbrauchsrisiko entspricht dem von Soft-IP, wenn RTL-Quellcode zum Lieferumfang gehört.

#### 2.3.1.3 Hard-IP

Hard-IP ist hinsichtlich Leistungsaufnahme, Flächenbedarf und/oder zeitlicher Leistungsfähigkeit optimiert und bereits auf eine bestimmte Technologie abgebildet. Beispiele enthalten vollständig platzierte und verdrahtete Netzlisten, die für eine bestimmte Technologiebibliothek optimiert sind, ein kundenspezifisches, physikalisches Layout oder eine Kombination dieser Optionen. Hard-IP ist spezifisch auf den Technologieprozess abgestimmt und wird im Allgemeinen im GDSII-Format ausgeliefert.

Die Performanz von Hard-IP ist am besten vorhersehbar, aber durch seine Prozessabhängigkeit ist es die am wenigsten flexible IP-Härte. Hard-IP benötigen zumindest ein Verhaltensmodell auf hoher Abstraktionsebene, eine Testliste, vollständige physikalische Modelle und Zeitverhaltensmodelle zusammen mit den GDSII-Daten. Die Möglichkeiten Hard-IP rechtlich zu schützen sind sehr viel klarer durch den Copyrightschutz geregelt und es muss kein RTL-Quellcode ausgeliefert werden. Bedingt durch die enormen Fortschritte bei der Chipherstellung, bedeutet Wiederverwen-

dung von Hard-IP in der Regel, seine GDSII-Darstellung auf eine neue Prozesstechnologie abzubilden.

Die Form des Hard-IP eignet sich am besten zur Auslieferung und Integration analoger und performanzoptimierter Entwürfe. In diesen Fällen ist die EDA-Unterstützung noch unzureichend. Ein optimales Integrationsergebnis kann nur durch die Einbeziehung der unteren Abstraktionsebenen bis hin zur physikalischen Ebene bei der Entwicklung des IP-Moduls erzielt werden. Die Auslieferung von Hard-IP wird daher mittel- bis langfristig als Zwischenlösung angesehen, bis ausreichende EDA-Unterstützung auch für diese Entwürfe verfügbar ist. Die Notwendigkeit, die Entwurfsleistung zu erhöhen, erfordert IP-Module auf hoher Abstraktionsebene zu entwerfen und wieder zu verwenden (Soft-IP). Um mit Soft-IP in die Hard-IP vorbehaltenen Domänen vorzudringen, muss jedoch die Vorhersehbarkeit von Soft-IP gesteigert werden und damit das Integrationsrisiko für den IP-Nutzer verringert werden. Für Soft-IP muss folglich der größte Aufwand getrieben werden, um seine endgültige Ausprägung im SoC vorhersehbar zu machen und so das Integrationsrisiko zu verringern. Die vorliegende Arbeit konzentriert sich daher auf digitales Soft-IP. Abbildung 3 zeigt eine Einordnung der IP-Härtegrade in die Abstraktionsebenen.

Eine Erweiterung des IP-basierten Entwurfs ist der plattformbasierte Entwurf. Beide Entwurfsmethoden sind eng miteinander verbunden.

#### 2.3.2 Plattformbasierter Entwurf

Der plattformbasierte Entwurf berücksichtigt die Tatsache, dass ein neuer Chip in einer Produktfamilie oder einem Applikationsbereich nur wenig neue Funktionalität bereitstellt, sodass die meisten Eigenschaften des Vorgängers beziehungsweise des Applikationsbereichs übernommen werden. Als Beispiel sei die Entwicklung von Digitalkameras und Mobiltelefonen genannt. Bei einem Mobiltelefon etwa bleibt die Funktionalität des Vorgängermodells jeweils erhalten und wird um Zusatzfunktionen wie MP3-Player, UKW-Radio, Digitalkamera erweitert.

Eine Entwurfsplattform besteht aus den grundlegenden Komponenten (Prozessor, Speicher, On-Chip Bus, ...), die zur Erfüllung der Systemfunktionalität notwendig sind [55]. Zur Erweiterung oder Differenzierung der Funktionalität innerhalb der Produktfamilien oder zu Produkten der Mitbewerber können zusätzliche IP-Module eingebaut werden beziehungsweise Plattformkomponenten ausgetauscht werden [71]. Bei der Entwicklung einer Plattform wird nach einem Kompromiss gesucht, um einerseits eine Vorlage für möglichst viele Entwürfe bereitzustellen und andererseits die Freiheitsgrade beim Entwurf der auf der Plattform basierenden Produkte zugunsten einer Entwicklungsbeschleunigung einzuschränken.

Je nach adressierter Entwurfsunterstützung unterscheidet man verschiedene Plattformtypen ([58], [59]). Tabelle 2 gibt einen Überblick über die gängigsten Typen und nennt Beispiele.

| Plattform                  | Anbieter               | Plattformtyp |

|----------------------------|------------------------|--------------|

| AMBA bus architecture [62] | ARM                    | KZP          |

| Excalibur [61]             | Altera                 | PP           |

| Nexperia [65]              | Philips Semiconductors | AP           |

| PrimeXsys [63]             | ARM                    | AP           |

| StarCore [64]              | freescale              | PZP          |

Tabelle 2: Übersicht verfügbarer Plattformen

Kommunikationszentrische Plattformen (KZP) geben lediglich die Kommunikationsinfrastruktur mit Peripherie vor und schränken auf diese Weise den Entwurfsaufwand ein. Ein Vertreter dieser Kategorie ist ARMs AMBA Bus.

Programmierbare Plattformen (PP) eignen sich besonders zur Entwicklung von Anwendungen, in denen Rekonfigurierbarkeit verlangt wird. Das Beispiel einer Altera Excalibur Plattform zeigt, dass solche Plattformen in der Regel aus einem rekonfigurierbaren Prozessor und programmierbarer Logik bestehen.

Applikationsplattformen (AP) wie Philips Nexperia oder ARMs PrimeXsys unterstützen komplette Applikationsbereiche. So unterstützt beispielsweise ARMs PrimeXsys in erster Linie Networking- und Automotive-Anwendungen und Nexperia Multimedia- beziehungsweise Kommunikationsanwendungen. Bedingt durch den großen Einsatzbereich ist der Entwurfsaufwand basierend auf Applikationsplattformen sehr hoch.

Prozessorzentrische Plattformen (PZP) geben den Prozessor plus Peripherie, sowie Softwaretreiber und grundlegende Anwendungsroutinen vor und schränken damit den Entwurfsaufwand ein. Ein Beispiel für diesen Plattformtyp ist Freescales StarCore Plattform.

Aufgrund der zu Beginn erwähnten Produktdifferenzierung werden in die Plattformen weitere Hardware-/Software-IP-Module (HW/SW-IP-Module) integriert. Dabei muss die Kompatibilität der IP-Module mit der Plattform und den bereits integrierten IP-Modulen gewährleistet werden. Zu diesem Zweck bieten die Plattformanbieter ein begleitendes Kompatibilitätsprogramm. Durch umfangreiche Kontrollen seitens des Plattformanbieters wird angestrebt, Inkompatibilitäten auszuschließen. Hierbei müssen IP-Module unterschiedlicher Art (HW/SW), unterschiedlicher Härtegrade und unterschiedlicher Qualitätsstandards größtenteils manuell überprüft werden.

#### 2.4 Abstraktionsebenen

Die Beschreibung komplexer Systeme wird durch die Darstellung auf unterschiedlichen Abstraktionsebenen erleichtert. Dadurch kann der Betrachter einer solchen Beschreibung sich auf die für die jeweilige Ebene interessanten Details konzentrieren. Überflüssige Details werden ignoriert. Die Einordnung in Abstraktionsebenen erfolgt im Hardware-Bereich nach dem Y-Diagramm [66]. In der folgenden Abbildung 3 wurden die Abstraktionsebenen aus dem Y-Diagramm übernommen und die vorgestellten Begriffe Plattform und IP-Härtegrade eingeordnet. Je tiefer liegend eine

Ebene ist, desto mehr Details sind in der Beschreibung enthalten, und umso komplexer ist die Beschreibung zu verstehen. Höher liegende Ebenen abstrahieren von diesen Details und helfen somit die Komplexität zu beherrschen. Ermöglicht wird diese Betrachtungsweise durch verfügbare EDA-Werkzeuge die automatisch tiefer liegende Beschreibungen aus den abstrakteren generieren können (Synthese).

Abbildung 3: Abstraktionsebenen

#### 2.4.1 Systemebene

Auf Systemebene, der abstraktesten Ebene, ist es ausreichend die Funktionalität des Systems zu beschreiben. Es ist nicht erforderlich festzulegen, welche Teile in Hardware gefertigt oder als Software programmiert werden sollen, dies ist Teil der Hardware/Software-Partitionierung. Diese Ebene eignet sich zur Architekturexploration mit abstrakten IP-Modulbeschreibungen. So können geeignet spezifizierte, abstrakte Modelle zur Performanzanalyse verwendet werden, um sich für ein bestimmtes IP-Modul zu entscheiden. Dafür erforderlich ist eine abstrakte Beschreibung des IP-Moduls mit geeigneten Charakterisierungseigenschaften. Die Überprüfung, ob ein solches Modell zum Lieferumfang eines IP-Moduls gehört, ist Teil der automatischen IP-Qualifizierung, die in Kapitel 4 beschrieben wird. Eine Exploration auf dieser Ebene ist die Grundlage, um festzulegen welche Teile auf bereits vorhandene IP-Module abgebildet werden können und welche Teile neu entwickelt werden müssen. Plattformen werden ausgehend von der Systemebene bis zur physikalischen Ebene beschrieben. Dabei ist es nicht erforderlich, dass auf jeder Ebene eine explizite Beschreibung der Plattform vorliegt. Es müssen nur die Ebenen beschrieben sein, auf denen das System validiert werden soll beziehungsweise Funktionalität integriert werden soll. Teilweise ist es ausreichend, wenn Konzepte zur Einbindung von IP-Modulen einer anderen Abstraktionsebene genutzt werden können.

#### 2.4.2 Algorithmische Ebene

Die algorithmische Ebene erlaubt eine zeitfreie Beschreibung der Funktionalität. Komplexe algorithmische Ausdrücke, Prozeduren, Prozesse und Variablen beschreiben das Verhalten des Entwurfs. Die Struktursicht auf die algorithmische Ebene zeigt Hardware-Module, die nebenläufig interagieren.

#### 2.4.3 Register-Transfer-Ebene

Auf Register-Transfer-Ebene (RT-Ebene) wird das Zeitverhalten einer Schaltung in Taktzyklen betrachtet. Innerhalb eines Taktzyklus muss ein Signal (Datentransfer) ausgehend von einem Register das Zielregister erreicht haben. Daher wird diese Ebene RT-Ebene genannt. Es wird zwischen sequenziellen und kombinatorischen Verhalten unterschieden. Zwischen Registern verhält sich die Schaltung kombinatorisch, d. h. es sind keine speichernden Elemente (Register) zwischen Start- und Zielregister im Signalpfad enthalten. Demgegenüber enthält ein sequenzieller Signalpfad speichernde Elemente.

Soft-IP-Module sind auf RT-Ebene beschrieben. Mit zusätzlichen Zeitinformationen wie Taktdauer und Zeitverhalten der Beschreibungselemente lassen sich auf RT-Ebene bereits qualitative Aussagen über das Zeitverhalten (z. B. synchron, asynchron, multicycle path) machen. Auf Qualitätsprüfungen auf RT-Ebene geht Kapitel 4 detailliert ein.

#### 2.4.4 Logikebene

Auf Logikebene wird ein Schaltungsentwurf sehr implementierungsnah, aber noch unabhängig von der Zieltechnologie, durch Boolsche Gleichungen und Automaten beschrieben. Mit Firm-IP-Modulen macht man sich die bessere Vorhersehbarkeit der implementierungsnahen Darstellung zunutze, ohne die Flexibilität in Bezug auf die Zieltechnologie aufzugeben.

#### 2.4.5 Physikalische Ebene

Diese Ebene beschreibt Schaltungsentwürfe anhand ihres elektrischen Potenzial- und Stromverlaufs mit Differenzialgleichungen. Schaltungskomponenten wie Transistoren, Dioden, Widerstände und Kapazitäten sind durch die Zieltechnologie vorgegeben. Die physikalische Ebene ist die typische Beschreibungsform für Hard-IP-Module. Sie ist aufgrund der zieltechnologienahen Beschreibung die vorhersehbarste Abstraktionsebene in Bezug auf das Verhalten der realen, gefertigten Schaltung. Das bevorzugte Austauschformat auf dieser Ebene ist das GDSII-Format.

Es wurde bereits beschrieben, dass sich die vorliegende Arbeit auf digitale Soft-IP-Module konzentriert. Der IP-Anbieter stellt in diesem Fall Integrationsdaten auf RT-Ebene bereit, die in Bezug auf die Zieltechnologie noch zu abstrakt formuliert sind, um performanzrelevante Aspekte vorherzusehen. Dies erschwert einem IP-Nutzer die Entscheidung für ein IP-Modul, da das mit dem IP-Modul verbundene Integrationsrisiko nur unzureichend abgeschätzt werden kann. Die Aufgabe der IP-Qualifizierung ist es unter anderem, diese Vorhersehbarkeit zu erhöhen. Doch bevor auf die Durchführung der IP-Qualifizierung eingegangen werden kann, muss geklärt werden, was unter Soft-IP-Qualität zu verstehen ist.

#### 2.5 Qualität

Qualität ist nach ISO-9000 definiert als: "Vermögen einer Gesamtheit inhärenter Merkmale eines Produkts, eines Systems oder eines Prozesses zur Erfüllung von Kundenforderungen und anderen interessierten Parteien" [3].

Diese abstrakte Definition muss zunächst für die Anwendung auf IP-Module interpretiert werden. Dabei ergeben sich drei wesentliche Anforderungen:

- Es müssen Qualitätskriterien definiert werden, welche die Qualität und in diesem Sinne die Wiederverwendbarkeit und Vorhersehbarkeit eines IP-Moduls ausdrücken können.

- 2. Qualität muss messbar sein. Eine Qualitätsmessung bedeutet, den Grad der Übereinstimmung mit den definierten Qualitätskriterien zu bestimmen.

- 3. Der Übereinstimmungsgrad muss bewertet werden, um entscheiden zu können, ob ein IP-Modul von guter oder schlechter Qualität ist.

Zusätzlich muss definiert sein, was qualifiziert werden muss. Bei der Entwicklung eines IP-Moduls beim IP-Anbieter werden die so genannten Entwurfsdaten generiert.

**Entwurfsdaten:** Daten (HDL-Beschreibungen, Synthese- und Simulationsumgebung, Dokumentation, Qualifizierungsberichte usw.) eines IP-Moduls, die beim IP-Anbieter entstehen. Dazu zählen alle Daten, die für den Entwurf benötigt werden beziehungsweise beim Entwurf und während der Verarbeitung der Entwurfsdaten entstehende Daten (z. B. Protokolldateien der Synthese und Simulation).

Da nicht alle Entwurfsdaten zur Integration benötigt werden, sind die Entwurfsdaten von den Integrationsdaten zu unterscheiden.

**Integrationsdaten:** Die Integrationsdaten eines IP-Moduls sind in der Regel eine echte Untermenge der Entwurfsdaten. Der Umfang der Integrationsdaten entspricht den Daten, die vom IP-Anbieter an den IP-Nutzer ausgeliefert werden. Sie sind entweder durch Defacto-Standards ([15], [22]) festgelegt oder werden individuell bei Vertragsabschluss zwischen IP-Anbieter und IP-Nutzer vereinbart.

Wichtige Begriffe im Zusammenhang mit der Qualität eines IP-Moduls sind die Vollständigkeit, die Integrität und die Konsistenz eines IP-Moduls.

Vollständig ist ein IP-Modul, wenn alle durch einen Standard definierten oder vertraglich vereinbarten Dateien zum Umfang der Integrationsdaten gehören. Zu beachten ist, dass der Umfang der Integrationsdaten nicht statisch ist, sondern sich aus den jeweiligen Vertragsvereinbarungen und Standards ergibt. Die Integrität eines IP-Moduls ist gewährleistet, wenn alle internen Dateiabhängigkeiten eines vollständigen IP-Moduls aufgelöst werden können. Abhängigkeiten zu externen Dateien dürfen nur bestehen, wenn diese ausnahmslos in jeder relevanten Entwicklungsumgebung als verfügbar vorausgesetzt werden können (z.B. VHDL ieee und std Bibliotheken). Sind dateiformatübergreifend alle Verweise der Dateiinhalte eindeutig, vollständig, und ohne unnötige Verweise erfüllt, ist die Konsistenz eines IP-Moduls gewährleistet. Beispielsweise verweisen Objektnamen in Syntheseskripten beispielsweise auf Entity-, Port-, Signalnamen usw. des HDL-Quellcodes. Werden während der Entwicklung eines IP-Moduls beispielsweise Portnamen nur im Quellcode geändert, wird das IP-Modul inkonsistent, da das Syntheseskript noch einen Verweis auf den alten Portnamen enthält. Eine automatische Qualitätsmessung kann in diesem Fall nur die Inkonsistenz feststellen, nicht aber entscheiden, ob eine Inkonsistenz aufgrund eines unnötigen Verweises (Quellcode-Redundanz) oder aufgrund einer Objektnamensänderung (Quellcode-Änderung) vorliegt.

Teilweise ist es erforderlich zusätzliche Daten für den IP-Nutzer zu generieren, um beispielsweise einen automatischen Import in den Entwurfsablauf des Nutzers zu ermöglichen. Diese Thematik wird in Kapitel 5 ausführlich diskutiert.

Mit diesen Voraussetzungen kann der Begriff der IP-Qualifizierung definiert werden.

**IP-Qualifizierung:** Die Messung und Bewertung des Übereinstimmungsgrads eines IP-Moduls mit definierten Qualitätskriterien basierend auf den Entwurfs- beziehungsweise Integrationsdaten.

#### 2.5.1 Qualitätskriterien

Viele Bücher und wissenschaftliche Konferenzbeiträge beschäftigen sich mit Qualitätskriterien, um elektronische Entwürfe oder den Entwurfsprozess zu verbessern. Die adressierten Teilbereiche des Entwurfs lassen sich zu den folgenden Themen zusammenfassen: Verbesserung der Codierung (engl. Coding Style) [68], unter anderem in Bezug auf Synthetisierbarkeit oder Simulierbarkeit mit unterschiedlichen Werkzeugen, Entwurf für die Fertigung (engl. Design for Manufacturability, DFM) [67] und Entwurf für Testbarkeit (engl. Design for Test, DFT) ([69], [70]).

IP-Module müssen diese Anforderungen ebenfalls erfüllen und zusätzlich portierbar und wiederverwendbar sein. Aus diesem Grund können aus den genannten Themenkomplexen Qualitätskriterien für IP-Module abgeleitet werden. Viele Firmen haben daraus firmeninterne Richtlinien entwickelt (z. B. STMicroelectronics "Blue Book"). Die Einhaltung der firmeninternen Qualitätsanforderungen führt zwar zu verbesserter Qualität und damit zu besserer Wiederverwendbarkeit, aber die Anforderungen unterscheiden sich von Firma zu Firma. Da die firmeninternen Qualitätskriterien meist unveröffentlicht bleiben, sind dem IP-Nutzer die erfüllten Qualitätskriterien nicht bekannt. Die firmeninternen Qualitätskriterien eignen sich daher nicht zum Qualitätsvergleich von IP-Modulen unterschiedlicher Hersteller. Werden beispielsweise unterschiedliche Codierrichtlinien der Hardware-Beschreibungssprache (engl. Hardware Description Language, kurz HDL) eingehalten und der IP-Anbieter hält die durchgängige Verwendung der downto-Anweisung und der IP-Nutzer die durchgängige Verwendung der to-Anweisung für qualitativ hochwertig, ist es offensichtlich, dass dadurch eine Quelle für Fehlverbindungen zwischen Bussen solcher unterschiedlich qualifizierter IP-Module gegeben ist.

Um solche Missverständnisse zu vermeiden, ist das Vorhandensein von standardisierten oder zumindest veröffentlichten Kriteriensammlungen, die die Gesamtqualität eines IP-Moduls berücksichtigen, unerlässlich. Mit zu den bekanntesten, veröffentlichten Sammlungen solcher Qualitätskriterien gehören das Reuse Methodology Manual (RMM) [4] und die Kriteriensammlung im Quality IP (QIP) Programm der Virtual Socket Interface Alliance (VSIA) [7].

Auf der Grundlage definierter Qualitätskriterien kann die Qualität eines IP-Moduls gemessen werden. Eine darüber hinausgehende Standardisierung der Kriterien trägt zur Transparenz des Qualitätsbegriffs bei und fördert die Entwicklung automatischer Qualitätsmessmethoden.

#### 2.5.2 IP-Qualitätsmessung

Bei der Qualitätsmessung wird der Übereinstimmungsgrad eines IP-Moduls mit definierten Qualitätskriterien gemessen. Bei einer an die Qualitätsbewertung angepassten Messung hängt das Messergebnis von der Formulierung des Kriteriums und der vorgesehenen Quantifizierung ab. Quantifizierung bezeichnet den Detaillierungsgrad eines Qualitätsmessergebnisses bezüglich eines Qualitätskriteriums. Häufig wird darauf geachtet, dass innerhalb einer Qualitätsbewertung eine möglichst einheitliche und einfache Quantifizierung gewählt wird. So waren in OpenMORE lediglich "ja" und "nein" Antworten möglich. In QIP gibt es zusätzlich die Möglichkeit Fragen mit "immer", "häufig" oder "nie" zu beantworten. Welchen Detaillierungsgrad eine Antwort haben kann, ist in der Regel durch die Qualitätsbewertung vorgegeben.

Für Qualitätsmessungen können kommerzielle Werkzeuge eingesetzt werden. Synthesewerkzeuge, Simulatoren, Linter und Code-Coverage-Werkzeuge gehören zu den bekanntesten Vertretern. Ein **Linter** (engl. Lint = dt. Fussel) oder **Rule-Checker** ist ein Programmierwerkzeug, das

lexikalische und semantische Quellcodeanalysen durchführt und dadurch Codierrichtlinien überprüfen kann. Eine typische Aufgabe für die Lint-Analysen ist es, Variablen zu finden, die vor ihrer Nutzung nicht gesetzt wurden oder die in einem anderen Zusammenhang verwendet werden als ihr Datentyp es zulässt usw. Daher sind Linter auf ein bestimmtes Datenformat (z. B. C, C++) festgelegt. Heute sind viele typische Lint-Analysen Teil eines optimierenden Compilers. Lint-Analysen prüfen aber auch Fälle, die von einem Compiler nicht geprüft werden, wie z.B. die Konsistenz zwischen Modulen und die Compiler-Portabilität. Die ersten Linter waren für C-Code verfügbar. Heute gibt es auch Linter für weitere Programmiersprachen und HDLs. Für eine umfassende Qualifizierung reichen diese Werkzeuge jedoch nicht aus, da nur einzelne Qualitätsbereiche unabhängig davon wie sie zur Gesamtqualität des IP-Moduls beitragen, adressiert werden. Mit den genannten Werkzeugen können applikationsunspezifische Standardkriterien automatisch geprüft werden. Applikationsspezifische Übereinstimmung, beispielsweise der Implementierung eines Busprotokolls mit der Spezifikation, kann von diesen Werkzeugen nicht geleistet werden. Häufig werden daher Qualitätsmessungen noch manuell, beispielsweise während Code-Überprüfungen, durchgeführt.

Qualitätsmessungen sind in der Regel an die durchzuführende Qualitätsbewertung angepasst.

#### 2.5.3 IP-Qualitätsbewertung

Je mehr Qualitätskriterien von einem IP-Modul erfüllt werden, desto höherwertig ist seine Qualität. Aufgrund der Tatsache, dass die Qualitätskriterien mit Bezug auf die Wiederverwendbarkeit formuliert sind, ist mit zunehmender Qualität eine Verringerung des Integrationsrisikos verbunden. Messbare Qualitätskriterien sind daher unabdingbar für die Abschätzung des Integrationsrisikos.

Eine Qualitätsbewertung komprimiert die Vielzahl an Qualitätskriterien in eine überschaubare Anzahl an Qualitätsindikatoren und ermöglicht daher einen effektiven Qualitätsvergleich. IP-Entwicklern zeigt eine Qualitätsbewertung die Abweichung vom intern oder standardisiert festgelegten Qualifizierungsziels an. Dieses Abweichungsergebnis ermöglicht eine Abschätzung des Aufwands, der bis zur Erreichung des Qualifizierungsziels notwendig ist. Es werden die Kriterien hervorgehoben auf deren Einhaltung die Entwickler sich konzentrieren müssen, um das IP-Modul wiederverwendbarer zu machen. Viele IP-Anbieter haben dafür interne Qualitätsrichtlinien entwickelt [43]. Darüber hinaus ist eine Standardisierung einer Qualitätsbewertung für die Ausweitung des IP-Geschäfts erforderlich, da sie IP-Anbietern hilft den Kundenanforderungen zu entsprechen und für IP-Nutzer der Qualitätsbegriff dadurch transparent wird.

Die Virtual Component (VC) Quality Development Working Group (DWG) der VSIA hat einen solchen Standard entwickelt. Folgt man der Definition, dass IP-Qualität als "messbare Übereinstimmung mit festgelegten Quali-

tätskriterien" definiert ist, muss eine Qualitätsmetrik aus den folgenden Elementen bestehen:

- eine Menge Qualitätskriterien C<sub>i</sub>,

- eine Bewertung (Wertemenge) Q<sub>i</sub> für jedes Kriterium und

- ein Bewertungsschema, um einen Gesamtqualitätswert des IP-Moduls zu berechnen.

Die Beurteilung eines IP-Moduls umfasst das Folgende:

- für jedes Qualitätskriterium muss ein Qualitätswert  $q_i \in Q_i$  bestimmt und zugewiesen werden und

- ullet Berechnung der Gesamtqualität q entsprechend dem Bewertungsschema.

Eine frühe und bekannte Qualitätsbewertung war OpenMORE [5]. OpenMORE basiert auf dem Reuse Methodology Manual (RMM) [4] und weist jedem Kriterium  $C_i$  ein Gewicht  $w_i$  zu:

- $w_i$  = 2, falls  $C_i$  eine RMM-Richtlinie ist und

- $w_i = 10$ , falls  $C_i$  eine RMM-Regel ist.

#### Die Bewertung ist:

- 0, falls das Kriterium nie erfüllt ist,

- ½, falls das Kriterium manchmal erfüllt ist und

- 1, falls das Kriterium immer erfüllt ist.

Die Gesamtqualität wird als gewichtete Summe berechnet:  $q = \sum_{i} w_i \cdot q_i$

Als Ergebnis wird ein durchschnittlicher Qualitätswert berechnet; qualitätsschwache Kriterien können durch hohe Qualität in anderen Bereichen kompensiert werden.

Im Gegensatz dazu folgten der VSIA Virtual Component Transfer (VCT) Ansatz (Anhang D in [15]) und der nie veröffentlichte Quality Spreadsheet (QSS) Ansatz der Philosophie, dass immer das schwächste Glied (Qualitätskriterium) die Kette (IP-Modul) zum Reißen bringt. Daher berechneten diese Ansätze notwendigerweise das Minimum der einzelnen  $q_i$ . Eine solche Bewertung ist sehr streng, trägt aber weder zur Unterscheidung zwischen IP-Modulen ähnlicher Qualität bei, noch erlaubt sie dem IP-Entwickler sukzessive Qualitätsverbesserungen anzuzeigen.

Für die QIP-Bewertung wurde ein kombinierter Ansatz gewählt ([7], [8]). Die primäre Bewertung wird als gewichtete Summe mit Standardgewichten durchgeführt. Dies führt zu einem einheitlichen, vergleichbaren Bewertungsschema zwischen funktional gleichwertigen IP-Modulen. Durch eine anwendungs- beziehungsweise nutzerspezifische Auswahl der definierten Gewichte für jedes Kriterium kann eine individuelle Bewertung durchgeführt werden. Die primäre QIP-Bewertung wird durch eine "schwächste-Glied"-Bewertung ergänzt. Dieses sekundäre Bewertungsschema signalisiert zusätzlich, ob problematische Kriterien (Pflichtkriterien

(engl. imperatives) beziehungsweise Regeln (engl. rules)) verletzt sind. Neben den problematisch eingestuften Kriterien existieren Richtlinien (engl. guidelines), deren Einhaltung ein Indiz für gute Entwurfspraktiken ist. Die Einhaltung von optional gewichteten Kriterien erhöht die Qualität. Optionale Kriterien können die Gesamtqualität nicht verschlechtern, ihre Bewertung verhält sich im Verletzungsfall neutral. Falls heilbare Kriterien erfüllt sind, verschlechtern sie die Gesamtqualität. Ein heilbares Kriterium wird in QIP immer von einer untergeordneten, neutralisierenden Gegenmaßnahme begleitet. Ist die Gegenmaßnahme im IP-Modul umgesetzt, neutralisiert sie die Qualitätsverschlechterung. Eine Gegenmaßnahme kann nur bewertet werden, falls das übergeordnete heilbare Kriterium zutrifft. Eine Übersicht über die QIP-Gewichtungen ist in Tabelle 3 zusammengestellt.

| Pflicht (engl. imperative)      | Verletzungen in dieser Kategorie führen zwangsläufig zu unzuverlässigem Verhalten des IP-Moduls.                                                                                                                                                                                                  |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Regel<br>(engl. rule)           | Regelverletzungen können zu erheblichen und unvorhersehbaren Kosten während der Integration des IP-Moduls führen.                                                                                                                                                                                 |

| Richtlinie<br>(engl. guideline) | Die Einhaltung von Richtlinien führt zur generellen Verbesserung der Integrationsfähigkeit und der Wartbarkeit des IP-Moduls. Die Erfüllung von Richtlinien wird als Indiz angesehen, dass allgemein als gut bewertete Entwurfspraktiken bei der Entwicklung des IP-Moduls beachtet wurden.       |

| Optional                        | Die Einhaltung optional gewichteter Kriterien führt zu einer Verbesserung der Qualität, ansonsten verhält sich ihre Bewertung neutral in Bezug auf die Gesamtqualität.                                                                                                                            |

| Heilbar<br>(engl. mitigable)    | Erfüllt ein IP-Modul ein heilbar gewichtetes Kriterium, führt das zu einer Verschlechterung der Gesamtqualität. Die Auswirkung auf das Qualitätsergebnis kann durch die Einhaltung geeigneter Gegenmaßnahmen neutralisiert werden. QIP definiert zu jedem heilbaren Kriterium eine Gegenmaßnahme. |

Tabelle 3: QIP-Gewichtungen

Die Gesamtbewertung eignet sich, um verschiedene IP-Module qualitativ zu klassifizieren. Vor einer Kaufentscheidung sollte der IP-Nutzer die einzelnen Bewertungen der Qualitätskriterien betrachten, um einen detaillierten Einblick in die IP-Qualität und das potentielle Risiko zu erhalten. Evtl. sollte der IP-Nutzer eine Veränderung der Standardgewichtung in Betracht ziehen, um spezifische Bedürfnisse in die Bewertung einfließen zu lassen.

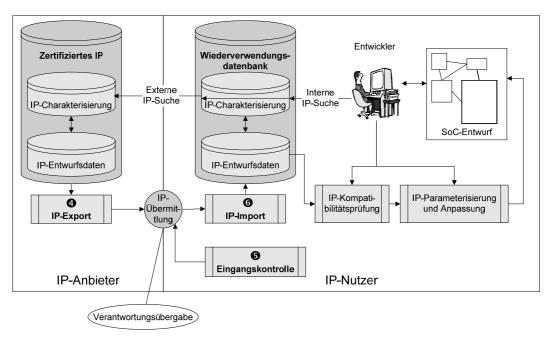

Hinsichtlich ihrer Qualität bewertete IP-Module werden als qualifizierte IP-Module bezeichnet. Wurde das IP-Modul nur anhand einer Teilmenge der Kriterien bewertet, spricht man von einem teilqualifizierten IP-Modul. Die Daten fertig gestellter IP-Module, die zur Wiederverwendung freigegeben wurden, werden in einer Wiederverwendungsdatenbank (engl. IP repository) gespeichert. Eine solche Datenbank pflegen sowohl IP-Anbieter, als auch IP-Nutzer. IP-Anbieter exportieren IP-Module aus der Datenbank, falls ein IP-Nutzer ein IP-Modul einkauft. IP-Nutzer verwenden eine solche Datenbank, um extern eingekaufte IP-Module für die interne Wiederverwendung freizugeben und um bereits intern vorhandene IP-Module in einem Chipentwurf wieder zu verwenden. Beim IP-Anbieter

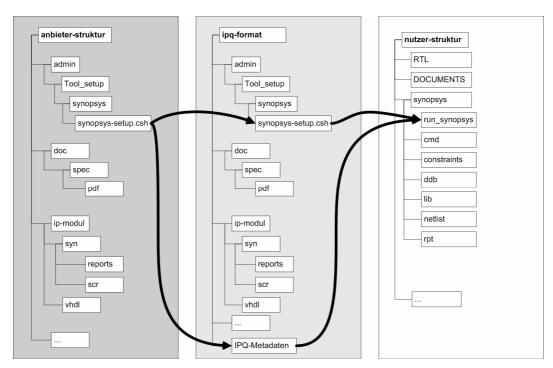

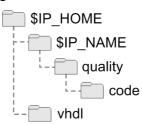

spricht man vom IP-Export, wenn ein IP-Modul zur Auslieferung an den IP-Nutzer aufbereitet wird. Dazu wird auf die Entwurfsdaten in der Wiederverwendungsdatenbank des IP-Anbieters zugegriffen. Nach der Übernahme der Integrationsdaten des exportierten IP-Moduls durch den IP-Nutzer spricht man vom IP-Import, wenn das IP-Modul für den Entwurfsablauf des IP-Nutzers aufbereitet wird und in der Wiederverwendungsdatenbank des IP-Nutzers gespeichert wird. Zum Auffinden geeigneter IP-Module bei der **IP-Suche** (engl. IP retrieval) in einer Wiederverwendungsdatenbank, müssen die IP-Module charakterisiert werden. Die Charakterisierungsdaten werden zusammen mit den strukturierten Integrationsdaten in der Wiederverwendungsdatenbank gespeichert. Eine IP-Struktur definierte, hierarchische Verzeichnisstruktur, in der die Entwurfs- beziehungsweise Integrationsdaten eines IP-Moduls unter festgelegten Dateinamen eingeordnet sind. Innerhalb einer Firma ist meist eine einheitliche IP-Struktur festgelegt. Über Firmengrenzen hinweg unterscheiden sich IP-Strukturen in der Regel. Die IP-Struktur ist an den Entwurfsablauf angepasst.

Wird ein IP-Modul in einen Entwurfsablauf mit anderer IP-Struktur importiert, muss es umstrukturiert werden. Eine **Umstrukturierung** ist eine Veränderung der IP-Struktur aufgrund von Dateinamensänderungen und Änderungen der hierarchischen Verzeichnisstruktur.

Unter **Anpassung** wird der Prozess der Anpassung der Dateiinhalte nach einer Umstrukturierung verstanden. Das Ziel der Anpassung ist die Ausführbarkeit (z. B. der Skripte) und die Integrität der Daten des IP-Moduls wiederherzustellen.

Ein **IP-Format** entspricht einer IP-Struktur, die um zusätzliche, semantische Informationen ergänzt wird. Es bedarf zusätzlicher Werkzeuge, diese Semantik zu interpretieren. Darüber hinaus werden weitere Informationen in einem IP-Format gespeichert, die beispielsweise die Funktion (charakterisierende Daten), die Qualität des IP-Moduls beziehungsweise den Entwurfsablauf dokumentieren.

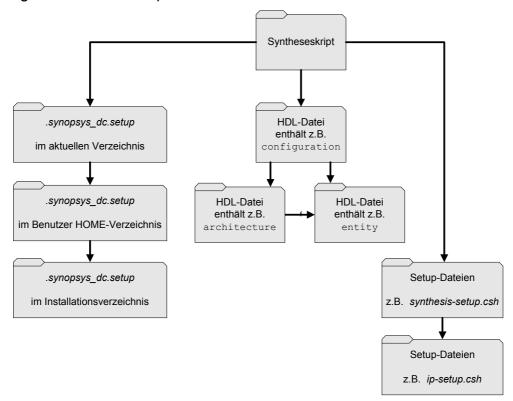

Der **Entwurfsablauf** definiert das Vorgehen ausgehend von der Spezifikation einer elektronischen Schaltung über die Implementierung und Verfeinerung bis zur Hardwarerealisierung in einer bestimmten Zieltechnologie. Teilaufgaben im Entwurfsablauf werden von Werkzeugen unterstützt. Diese Werkzeuge sind in den Entwurfsablauf integriert und auf die IP-Struktur abgestimmt. Das bedeutet, dass die Werkzeuge die Eingabedaten an festgelegten Stellen der IP-Struktur erwarten und ihre Ausgabedaten an ebenso festgelegten Stellen unter bestimmten Dateinamen ablegen.

Die üblichen **Zieltechnologien** des integrierten Schaltungsentwurfs sind ASICs (engl. Application Specific Integrated Circuit) oder FPGAs (engl. Field Programmable Gate Arrays). Während ASICs speziell für eine Anwendung hergestellt werden, handelt es sich bei FPGAs um universal vorgefertigte Bausteine, die vom Kunden im Anwendungsfeld, also vor Ort, programmiert werden können. FPGAs werden häufig verwendet, um IP-Module kostengünstig auf Hardware abzubilden und in einer

Umgebung testen zu können. Eine funktionierende Hardwareabbildung eines IP-Moduls, beispielsweise auf einem FPGA, ist ein wichtiges qualitätssteigerndes Kriterium, auch dann, wenn das IP-Modul bei weiteren Wiederverwendungen auf ASICs abgebildet werden soll.

Um die Daten eines IP-Moduls im Entwurfsablauf verarbeiten zu können, werden Konfigurationsdateien für die integrierten Werkzeuge benötigt. Eine **Konfigurationsdatei** enthält spezifische Einstellungen eines Werkzeugs, die zum Erreichen der gewünschten Ausgabe (z. B. Qualifizierungsergebnis, synthetisierte Netzliste usw.) unbedingt notwendig sind. Solche Einstellungen müssen vom IP-Anbieter an den IP-Nutzer ausgeliefert werden, falls die Ausgabe beim IP-Nutzer erzeugt werden muss (z. B. Synthese) oder nachvollziehbar sein soll (z. B. Qualifizierung). Konfigurationsdateien unterscheiden sich von den Installationsdateien.

Eine Installationsdatei ist in der Regel eine ausführbare Skriptdatei, die die Umgebung für ein bestimmtes Werkzeug erzeugt. Diese Umgebung ist unbedingt erforderlich, um das Werkzeug ausführen zu können. Bestandteile einer solchen Umgebung sind beispielsweise eine Umgebungsvariable, die auf das Installationsverzeichnis des Werkzeugs verweist, ein Verweis auf den Lizenzserver, das Setzen der Pfadvariable usw. Installationsdateien sind eng mit dem Entwurfsablauf verbunden und gehören daher nicht zum Auslieferungsumfang.

Eine Übersicht über den Wiederverwendungsablauf ist in Abbildung 8 auf Seite 49 grafisch aufbereitet.

Nachdem die grundlegenden Begriffe zum Verständnis der weiteren Arbeit gelegt wurden und geklärt wurde, dass sich die im Folgenden zu erläuternden Methoden auf digitale Soft-IP-Module beziehen, wird im nächsten Kapitel der Stand der Technik für die Qualifizierung und den Austausch von IP-Modulen aufgezeigt.

## 3 Stand der Technik

Dieses Kapitel gibt einen Überblick über aktuelle Ansätze, Werkzeuge und Organisationen, die mit den Teilgebieten dieser Arbeit, der IP-Qualifizierung und dem IP-Austausch, in Beziehung stehen.

Ausgehend von existierenden Qualitätskriterien für IP-Module und deren Bewertung in Abschnitt 3.1 werden aktuelle Standardisierungsbemühungen für IP-Qualitätskriterien in Abschnitt 3.2 untersucht. Daran schließt sich in Abschnitt 3.3 eine Diskussion über die Notwendigkeit der Automatisierung von Qualitätsmessungen zur Überprüfung von Qualitätskriterien an. In Abschnitt 3.4 werden schließlich verfügbare Qualifizierungswerkzeuge besprochen, die für automatische Qualitätsmessungen verwendet werden können.

Im Anschluss an eine erfolgreiche Qualifizierung werden IP-Module in Wiederverwendungsdatenbanken gespeichert. Aus diesen Datenbanken werden IP-Module für die Wiederverwendung ausgeliefert. Die Eignung dieser Datenbankansätze zur Qualitätserhaltung beziehungsweise Anpassung an neue Entwicklungsumgebungen werden in Abschnitt 3.5 diskutiert. Ansätze der objektorientierten und parametrischen Anpassung von IP-Modulen werden in Abschnitt 3.6 besprochen und in Abschnitt 3.7 die Arbeiten zur Unterstützung der IP-Auslieferung. Hinsichtlich ihrer Tauglichkeit zur Übermittlung der Integrationsdaten wurden Formate zur Verarbeitung elektronischer Systementwürfe in Abschnitt 3.8 untersucht. Mit einer Zusammenfassung der offenen Probleme in Abschnitt 3.9 schließt dieses Kapitel.

# 3.1 Qualitätskriterien und -bewertung für IP-Module

Das Reuse Methodology Manual (RMM) [4] ist eine umfangreiche Qualitätskriteriensammlung für IP-Module. Die Veröffentlichung des RMM und das Befolgen der vorgeschlagenen Regeln beziehungsweise Richtlinien sind für die IP-Geschäftswelt von Vorteil. Für den IP-Anbieter gibt das RMM Qualitätsziele vor, die zur Verbesserung der Wiederverwendbarkeit beitragen. IP-Nutzer profitieren von einem transparenten, durch das RMM definierten Qualitätsbegriff.

OpenMORE [5] ist eine auf dem RMM basierende Qualitätsbewertung. Aufgrund der Bewertung kann ein qualitativ hochwertiges IP-Modul von einem minderwertigen IP-Modul unterschieden werden. Die Akzeptanz und Umsetzung von RMM und OpenMORE in einigen Firmen hat zu einer Verbesserung des IP-Qualitätsniveaus geführt. Allerdings verhindert der manuelle Aufwand angesichts unzureichender, automatischer Qualitätsmessmethoden, zusammen mit der Tatsache, dass RMM und OpenMORE keine Industriestandards sind, eine weitere Akzeptanz.

Trotz des hohen Bekanntheitsgrads des Reuse Methodology Manual (RMM) [4] und OpenMORE [5] wird für die Akzeptanz einer Kriteriensammlung und Qualitätsbewertung durch alle IP-Anbieter und IP-Nutzer ein Industriestandard benötigt, um mit IP-Modulen das gewünschte Pro-

duktivitätswachstum zu erreichen. Die Standardisierung einer einheitlichen Qualitätsmetrik und einheitlicher Qualitätskriterien sind wesentliche Voraussetzungen dafür, dass der Begriff IP-Qualität eine sinnvolle Bedeutung erhält.

## 3.2 Standardisierung der Qualitätskriterien

Die Virtual Socket Interface Alliance (VSIA) hat einen solchen Standard erarbeitet [6]. Die Aufgabe der VSIA ist es, "die Produktivität der SoC-Entwicklung durch die Festlegung offener Standards und Spezifikationen, die die Software- und Hardware-VC-Integration aus mehreren Quellen unterstützen, grundlegend zu verbessern". An der Verbesserung der IP-Qualität arbeitet die Quality Development Working Group (QDWG) [9] beziehungsweise der neu geschaffene Quality Pillar.

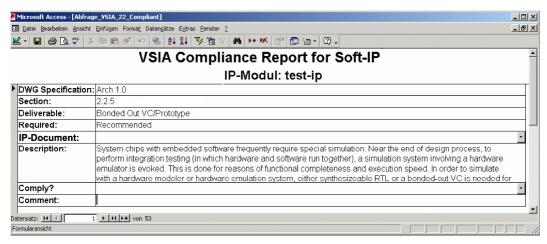

Im Juni 2004 ist die erste offizielle Version 1.11 der VSIA-Qualitätsbewertung (Quality IP, kurz QIP) kostenfrei für VSIA-Mitglieder freigegeben worden [7]. Mitglieder können sich von der VSIA-Webseite im Mitgliederbereich [42] das QIP-Arbeitsblatt im Microsoft®-Excel-Format mit dem dazugehörenden Benutzerhandbuch herunterladen. Im Herbst 2004 wurde der Beitritt zur VSIA und damit die Nutzung der QIP-Metrik vereinfacht. VSIA-Mitglieder dürfen die QIP-Bewertungsergebnisse ihrer IP-Module auch Nicht-Mitgliedern kostenfrei zur Verfügung stellen.

Der Standard umfasst derzeit Qualitätskriterien für digitales Soft-IP, digitales Verifikations-IP und eine Bewertung der IP-Reife sowie des IP-Anbieters. QIP ersetzt damit die bekannte OpenMORE Qualitätsbewertung. OpenMORE wurde der VSIA gestiftet [23]. Der Veröffentlichung von QIP ist ein Beta-Test mit großer Industriebeteiligung vorausgegangen. Daneben wurden weitere Firmenbeiträge interner Qualifizierungskriterien untersucht und in QIP integriert.

Der Autor hat innerhalb der VSIA-QDWG bis zum aktuellen Stand aktiv an der Standardisierung mitgearbeitet. QIP ist eine Sammlung von Qualitätskriterien für digitale IP-Module und einer darauf basierenden Metrik. QIP ermöglicht die Bewertung der IP-Qualität und wird derzeit durch die Kategorien digitales Hard-IP, Analog-IP und Mixed-Signal-IP, durch eine Kombination der Kriterien von digitalem Soft- und Analog-IP, ergänzt.

Innerhalb der Kategorien deckt QIP jeweils zwei Sichtweisen ab, die Sicht des Nutzers und die Sicht des Anbieters auf ein IP-Modul. Ein Nutzer hat die Möglichkeit, das IP-Modul vor einer Kaufentscheidung zu bewerten. In diesem Fall ist nur eine eingeschränkte Bewertung möglich, da er zu diesem Zeitpunkt noch keine vollständige Einsicht in das IP-Modul hat. Die Bewertung wird im Wesentlichen auf den Charakterisierungsdaten basieren, die ihm vom IP-Anbieter zur Verfügung gestellt werden. Eine weitere Anwendung von QIP für den IP-Nutzer ist, dem IP-Anbieter eine Rückmeldung bezüglich seiner Erfahrungen bei der IP-Integration zu geben.

Da in den QIP-Kriterien die Nutzeranforderungen an IP-Module manifestiert sind, kann ein IP-Anbieter die Einhaltung der Qualitätsanforderungen

überprüfen. Es liegt also im eigenen Interesse des IP-Anbieters, ein IP-Modul vor der Auslieferung an den IP-Nutzer mit QIP zu bewerten.

In der Kategorie IP-Reife- und IP-Anbieterbewertung müssen vom IP-Anbieter Fragen wie beispielsweise: "Wurde das IP-Modul bereits von einem Referenzkunden in Silizium gefertigt oder in einen FPGA abgebildet?" beantwortet werden. Die Anbieterbewertung bewertet die Fähigkeiten und Möglichkeiten des IP-Anbieters, qualitativ hochwertige IP-Module zu entwickeln und Support bereitzustellen. Dies wird beispielsweise anhand der Frage: "Ist der technische Support während normaler Geschäftszeiten erreichbar?", ermittelt.

IP-Nutzer- und Anbietersicht sind in QIP folgendermaßen gegliedert:

- Nutzersicht

- Dokumentationsqualität:

Unter diesem Gliederungspunkt werden die Qualität des Integrationshandbuchs, des digitalen Hardware-Referenzhandbuchs und der Versionsanmerkungen ermittelt.

- Integrationsunterstützung

Hierunter wird die Qualität der Konfigurierbarkeit und Parametrisierung, Build-Umgebung, Portierbarkeit, Erweiterbarkeit, Systemebenenmodellierung, API-Schnittstelle, Hardware-Schnittstelle, Syntheseunterstützung, Produktionstest (JTAG, ATPG usw.), Blockebenen-Selbsttest, Verifikationsumgebung und SoC-Verifikationsunterstützung bewertet.

Die Anbietersicht gliedert sich wie folgt:

- Entwurfs- und Verifikationsqualität

- Entwurfsqualität interne Entwurfsdokumentation:

Die Qualität der internen Entwurfsdokumentation wird anhand von

Produktbrief, Projektplan und der Dokumente über die Systemanfor derungen, Entwurfsspezifikation, Verifikationsspezifikation und Qua litätsabschlussprüfung sowie der Prüfliste für den IP-Modul Speicher

bewertet.

- Entwurfsqualität Entwurfsdetails:

In diesem Abschnitt muss der IP-Entwickler über die Systemtechnik,

Entwurf für die Synthese, eingebettete Speicher, Taktdomänen,

Rücksetzrichtlinien, Code-Kommentierung, Codierrichtlinien und Skripte Auskunft geben.

- Entwurf für den Test, Fertigungstest und Fertigung sind weitere wichtige Details, die durch die Unterabschnitte Verifikationsqualität, Code-Coverage, Datentransfer, Terminierung, Konfiguration, Datengenerierung, Protokollprüfung, Behandlung der Verifikationsrücksetzung, Verifikationskomponenten und -umgebung und Prozessprüfliste ergänzt werden.

QIP ist eine veröffentlichte, verfügbare Kriteriensammlung und ermöglicht dadurch eine für IP-Anbieter und IP-Nutzer transparente Qualitätsbewer-

tung. Die Akzeptanz eines Qualitätsstandards hängt aber stark davon ab, wie aufwendig die Durchführung einer Qualitätsmessung ist.

## 3.3 Automatisierung der Qualitätsmessungen

Ein Nachteil, der dem IP-basierten Entwurf anhaftet, ist ein zwei- bis dreimal höherer Entwicklungsaufwand, der darin besteht, den Entwurf des IP-Moduls wiederverwendbar zu machen [11]. Zum erhöhten Entwicklungsaufwand zählt auch das Aufzeigen der Übereinstimmung des IP-Entwurfs mit Qualitätskriterien. Dieser erhöhte Aufwand kann durch automatische Qualitätsmessungen reduziert werden.

Bisher ist die Qualitätsmessung sowohl für IP-Anbieter als auch IP-Nutzer nur unzureichend gelöst. Häufig bedeutet eine IP-Qualifizierung aufseiten des IP-Anbieters, Papiersammlungen von Qualitätskriterien einzuhalten. Gehören Qualitätsmessungen zum festen Bestandteil der Firmenpolitik, müssen sie dennoch oft manuell durchgeführt werden. Zeitintensive und fehleranfällige Code-Überprüfungen sind die Folge. Eine Qualifizierungsmethode, die die Entwicklung des IP-Moduls begleitet, ist meist nicht installiert. Auch für den IP-Nutzer gibt es nur unzureichende Unterstützung bei der Auswahl des "richtigen" IP-Moduls. Sehr häufig kann eine Qualitätsmessung aus Zeit- und Komplexitätsgründen und in Ermangelung automatisierter Prozesse nicht durchgeführt werden.

Daher ist die Qualität des IP-Moduls nur so gut wie das Vertrauen, das in die Fähigkeiten des IP-Anbieters gesetzt wird. Die Folge von nicht effizient durchführbaren Qualitätsmessungen können Integrationsprobleme sein, die im Vorfeld hätten vermieden werden können. Solche Integrationsprobleme führen zumindest zu Verzögerungen im Projektplan und schlimmstenfalls zum Scheitern des Projekts, falls aufwendige Nacharbeiten durch den IP-Anbieter während des Integrationsprozesses notwendig werden. Das führt zwangsläufig zu einer nachhaltigen Schädigung der Geschäftsbeziehungen, da keine objektiven und effizienten Qualitätsmessmethoden verfügbar sind, die eine erneute Kaufentscheidung rechtfertigen könnten.

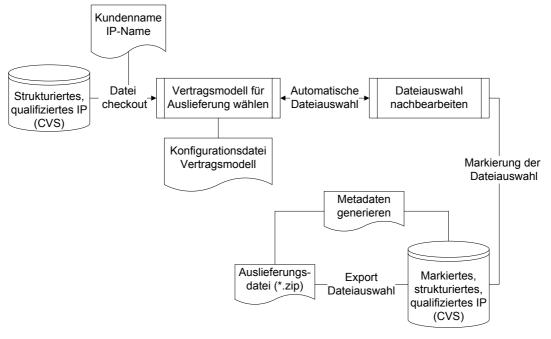

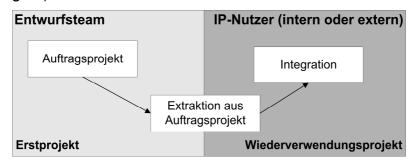

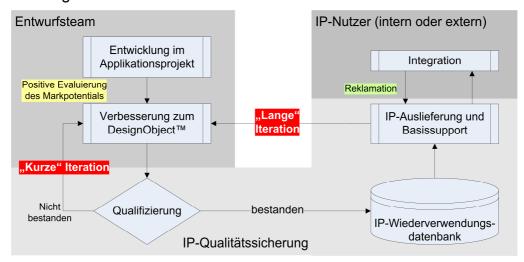

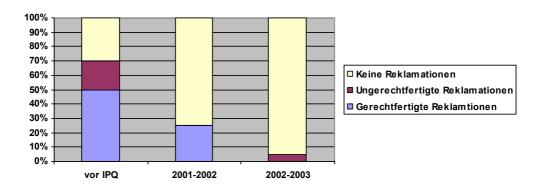

# 3.4 Qualifizierungswerkzeuge