## Konzept einer bibliotheksbasiert konfigurierbaren Hardware-Testeinrichtung für eingebettete elektronische Systeme

Zur Erlangung des akademischen Grades eines

#### **DOKTOR-INGENIEURS**

von der Fakultät Elektrotechnik und Informationstechnik der Universität Fridericiana Karlsruhe genehmigte

#### DISSERTATION

von Dipl.-Ing. Carsten Bieser aus Alzey

Tag der mündlichen Prüfung : 05. Juli 2007

Hauptreferent : Prof. Dr.-Ing. Klaus D. Müller-Glaser

Korreferent : Prof. Dr.-Ing. Sorin A. Huss

ISBN 978-3-937295-78-7

E&B Engelhardt und Bauer – Druck und Verlags GmbH Käppelestraße 10 ■ 76131 Karlsruhe ■ Germany

Telefon: 0721 / 9 62 26-100 • Fax: 0721 / 9 62 26-101 Internet: www.ebdruck.de • eMail: center@ebdruck.de

## Kurzfassung

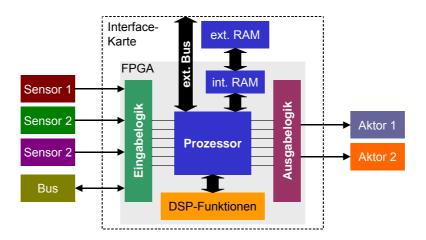

Die vorliegende Dissertation befasst sich mit dem schnellen Erzeugen von Prototypen (Rapid Prototyping, RP) und dem Test fertiger Steuergeräte (Hardware-in-the-Loop, HiL) unter Verwendung programmierbarer Logikbausteine (FPGAs). Letztere erlauben eine flexible und zeitsparende Implementierung von Funktionen in Hardware – auch zur Laufzeit des Systems. Außerdem wird somit ein hoher Wiederverwendungsgrad, sowohl der Hardware-Komponenten, als auch der darin integrierbaren Funktionen (Intellectual Property, IP) erreicht.

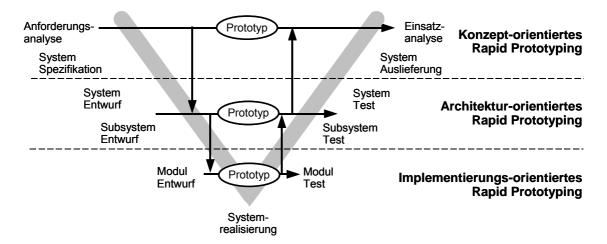

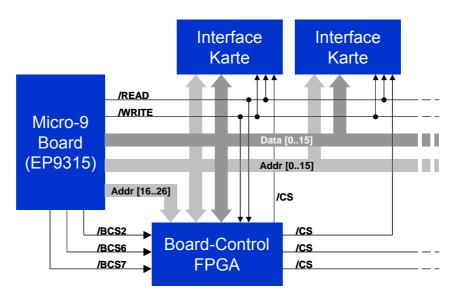

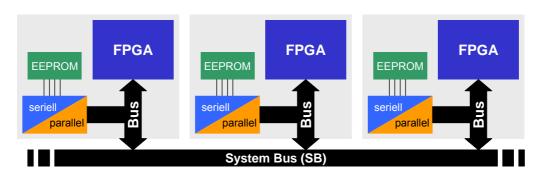

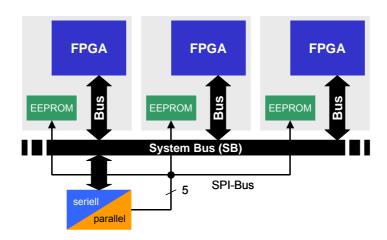

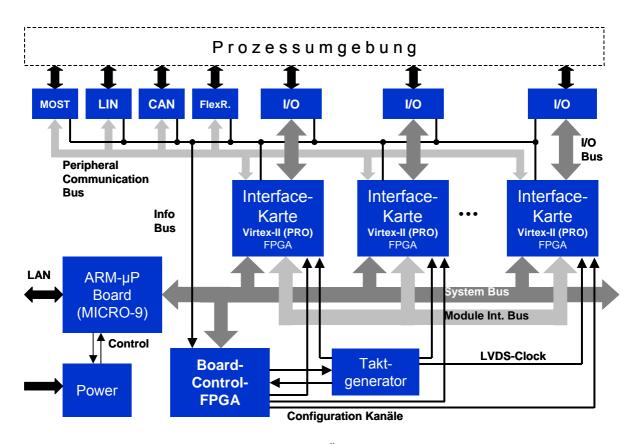

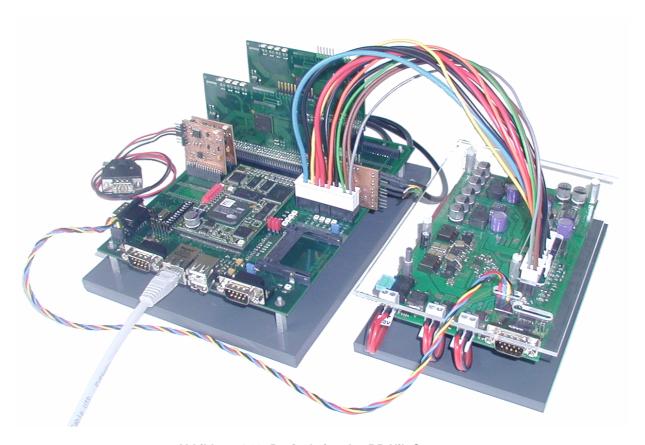

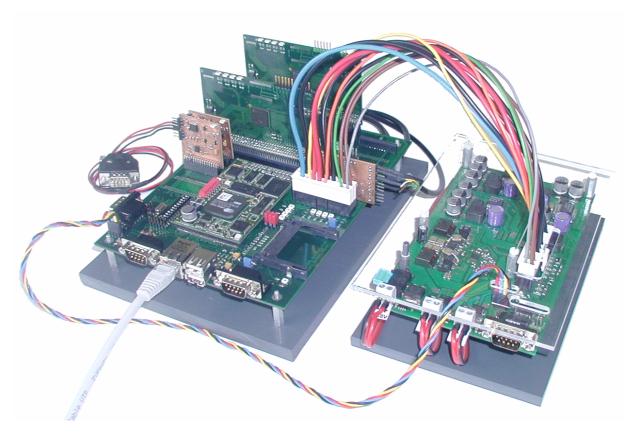

Wesentlicher Bestandteil der Arbeit ist die Entwicklung einer mobilen Hardware-Plattform, die sowohl für Rapid-Prototyping als auch für Hardware-in-the-Loop eingesetzt werden kann. Im Gegensatz zu Standardprodukten werden hier anstelle von dedizierten I/O-Schnittstellen ausschließlich programmierbare Interface-Karten auf Basis von FPGAs verwendet, die eine nahezu uneingeschränkte Programmierbarkeit aufweisen und damit helfen, die Kartenvielfalt stark einzuschränken. Weiterhin wird die konservative "Ein-Bus-Architektur" aufgeweicht und hinsichtlich mehrerer Bussysteme für verschiedene Aufgaben und Zwecke erweitert. Durch dieses Konzept werden neben der Unterstützung von konzept-, architektur- und realisierungs-orientiertem RP auch Berechnungen von mehreren HiL-Testmodellen parallel auf einer Plattform durch Verteilung auf mehrere Interface-Karten möglich. Dies macht die Plattform für den Einsatz im ganzen Entwicklungsprozess innerhalb des V-Modells interessant.

Der zweite, wichtige Aspekt der Arbeit betrifft die Erstellung der Konfiguration für die auf den Interface-Karten implementierten FPGAs. Dazu wird eine neue slot-basierte Methodik vorgestellt, die es erlaubt, eine Belegung mit verschiedenen Schnittstellenmodulen für einen FPGA mit Hilfe einer grafischen Benutzerschnittstelle (Graphical User Interface, GUI) zu arrangieren, ohne dafür jegliche Kenntnisse einer Hardware-Beschreibungssprache (VHDL oder Verilog) oder spezifisches Wissen hinsichtlich der FPGA-Interna zu besitzen. Diese Methodik gewährleistet zum einen die Performanz der einzelnen, getesteten und in einer Bibliothek abgelegten Module – auch in der Gesamtkonfiguration. Zum anderen stellt sie die Verträglichkeit der Module untereinander sowie die Korrektheit des Gesamtarrangements (Bitstream) sicher.

Das gesamte System ist von einem umfassenden Sicherheitskonzept umgeben, das den Benutzer vor Fehlkonfigurationen und damit auch die Plattform vor Zerstörungen bewahrt. Das Konzept ist dazu auf verschiedene Ebenen von Hard- und Software umgesetzt, um eine optimale Abdeckung möglicher Fehlerquellen zu erreichen.

Durch diverse Experimente anhand relevanter und dem industriellen Umfeld angepasster Beispielimplementierungen aus dem Automobilbereich wird die Einsetzbarkeit und Effektivität des RP-HiL-Systems sowie der FPGA-Design-Methodik nachgewiesen.

## **Danksagung**

Die vorliegende Arbeit ist während meiner Tätigkeit als wissenschaftlicher Mitarbeiter am Institut für Technik der Informationsverarbeitung (ITIV) der Universität Karlsruhe (TH) entstanden. An dieser Stelle möchte ich mich bei all denjenigen bedanken, die zum Gelingen derselben beigetragen haben.

Besonders bedanke ich mich bei den Leitern des Instituts, Herrn Prof. Dr.-Ing. K.-D. Müller-Glaser und Herrn Prof. Dr.-Ing. Jürgen Becker für die Möglichkeit, an ihrem Institut zu arbeiten und währenddessen meine wissenschaftliche Arbeit vorantreiben zu können. Herrn Prof. Dr.-Ing. Klaus D. Müller-Glaser gilt mein besonderer Dank für die – nicht selbstverständliche – Zuteilung des nötigen Freiraums zur Verfolgung meines eigenen wissenschaftlichen Forschungsthemas. Herrn Prof. Dr.-Ing. Sorin A. Huss von der TU Darmstadt danke ich für die freundliche Übernahme des Zweitgutachtens.

Weiterhin richtet sich mein Dank an die Mitarbeiter des ITIV für deren bereitwillige und kollegiale Unterstützung meiner Aktivitäten in allen wissenschaftlichen, technischen und organisatorischen Belangen. Namentlich zu erwähnen sind hierbei insbesondere in alphabetischer Reihenfolge Herr Dipl.-Ing. J. Becker, Herr Dipl.-Ing. R. König, Herr Dipl.-Ing. T. Köster und Herr Dipl.-Ing. A. Thomas, die stets eine fundierte Plattform für fachliche wie private Diskussionen boten und mit denen ich auch über die universitären Grenzen hinweg ein überaus freundschaftliches Verhältnis pflegte.

Mein Dank gilt ebenfalls den weit mehr als 35 Studenten, die im Laufe meiner Tätigkeit im Rahmen von Diplom-, Studien- und Seminararbeiten mit mir zusammengearbeitet haben, mich durch ihre Begeisterungsfähigkeit und ihr unermüdliches Engagement unterstützt, sowie durch ihre Ergebnisse wesentlich zum Gelingen dieser Arbeit beigetragen haben. Hierbei sind Herr Dipl.-Ing. M. Bahlinger, Herr Dipl.-Ing. M. Heinz, Herr Dipl.-Ing. M. Schwarz und Herr Dipl.-Ing. C. Stops besonders hervorzuheben.

Nicht zuletzt möchte ich meiner Frau Sandra für ihre stete Unterstützung und ihre Nachsicht und Toleranz während der Entstehungszeit dieser Arbeit und insbesondere meinen Eltern, Renate und Wilhelm, die es mir letztlich ermöglicht haben, nach meiner Berufsausbildung ein Hochschulstudium zu absolvieren und so meinen Berufswunsch vollends umzusetzen, meinen herzlichen Dank aussprechen. Einschließen darf ich an dieser Stelle auch meine Schwiegereltern Waltraud und Richard Daniel für ihren Beitrag zu meinem Fortkommen.

Abschließend danke ich meinen Studienkollegen Dipl.-Ing. H.-P. Weyand und Dipl.-Ing. M. Zöller, die mich während des Studiums begleitet haben und mit denen mich nach wie vor eine überaus gute Freundschaft verbindet, sowie meinem Berufschullehrer Herrn Dipl.-Ing. Gramberg, der mich in meinem Bestreben, die universitäre Ingenieurslaufbahn einzuschlagen, stets bestärkt hat und letztlich auch mit den Ausschlag für die Wahl des Studienortes gab.

Karlsruhe, Juli 2007

Carsten Bieser

# Inhaltsverzeichnis

| 1 | Ein  | leitun  | ng                                                 | 1  |

|---|------|---------|----------------------------------------------------|----|

|   | 1.1  | Motiva  | ation – Entwicklung und Test von Steuergeräten     | 2  |

|   | 1.2  | Ziele d | der Arbeit – Der eigene Beitrag                    | 4  |

|   | 1.3  | Gliede  | erung der Arbeit                                   | 5  |

| 2 | Elel | ktroni  | ik im Kraftfahrzeug                                | 7  |

|   | 2.1  | Bussy   | steme im Automobil                                 | 8  |

|   |      | 2.1.1   | Unterscheidung von Bustypen                        | 8  |

|   |      | 2.1.2   | Controller Area Network (CAN-Bus)                  |    |

|   |      | 2.1.3   | Local Interconnect Network (LIN)-Bus               |    |

|   |      | 2.1.4   | Media Oriented System Transport (MOST)-Bus         |    |

|   |      | 2.1.5   | FlexRay-Bus                                        | 15 |

|   |      | 2.1.6   | Time Triggered Protocol (TTP/C)                    |    |

|   | 2.2  | •       | bettete Systemebettete Systeme                     |    |

|   |      | 2.2.1   | Einsatzgebiete                                     |    |

|   |      |         | Vernetzung                                         |    |

|   | 2.3  |         | derungen an Eingebettete Systeme im Kfz            |    |

|   |      | 2.3.1   | Umgebungseinflüsse                                 |    |

|   |      | 2.3.2   | Zeitbedingungen                                    |    |

|   | 2.4  | Aktue   | lle und zukünftige Trends im Automobil             |    |

|   |      | 2.4.1   | Reduktion von Steuergeräten – Verteilte Funktionen |    |

|   |      | 2.4.2   | Fahrerassistenzsysteme                             | 19 |

| 3 | Sta  | nd de   | er Technik                                         | 21 |

|   | 3.1  | Progra  | ammierbare Bausteine                               | 21 |

|   |      | 3.1.1   | Field Programmable Gate Arrays (FPGAs)             |    |

|   |      | 3.1.2   | Virtex-II-FPGAs von Xilinx                         | 23 |

|   |      | 3.1.3   | Bitstream und Konfigurationslogik                  |    |

|   |      | 3.1.4   | Konfiguration von Xilinx-FPGAs                     |    |

|   |      | 3.1.5   | FPAA (Free Programmable Analog Array)              |    |

|   | 3.2  | Senso   | ren und Aktoren                                    | 35 |

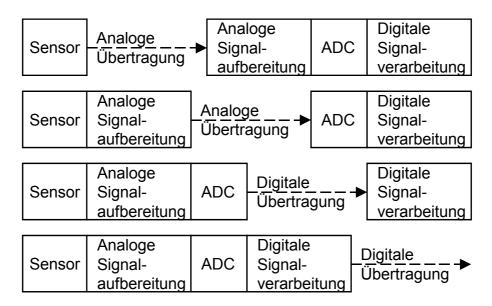

|      |                | Klassifizierung von Sensorschnittstellen                                                   |       |

|------|----------------|--------------------------------------------------------------------------------------------|-------|

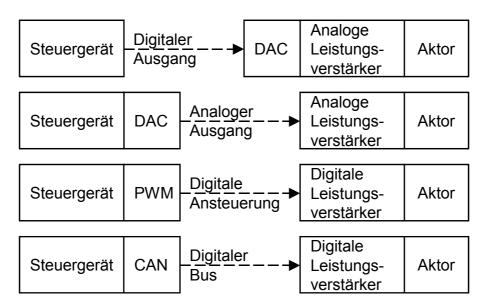

|      |                | Klassifizierung von Aktorschnittstellen                                                    |       |

| 3.3  | •              | e Schnittstellen                                                                           |       |

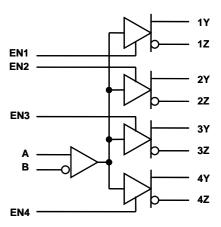

|      |                | Parallele I/O-Ports von Mikrocontrollern und FPGAs                                         |       |

|      | 3.3.2          |                                                                                            |       |

| 3.4  |                | konditionierung                                                                            |       |

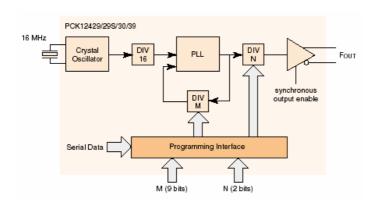

| 3.5  |                | zeugung und Verteilung                                                                     |       |

|      |                | Takterzeugung                                                                              |       |

|      |                | Taktverteilung                                                                             |       |

| 3.6  |                | onsprinzipien von Spannungswandlern                                                        |       |

| 3.0  | 3.6.1          | Linearregler                                                                               |       |

|      | 3.6.2          | -                                                                                          |       |

| 3.7  |                | adrantenverstärker                                                                         |       |

| 3.8  | -              | Erzeugung für programmierbare Schaltungen                                                  |       |

|      | 3.8.1          |                                                                                            |       |

|      | 3.8.2          | IP-Cores                                                                                   |       |

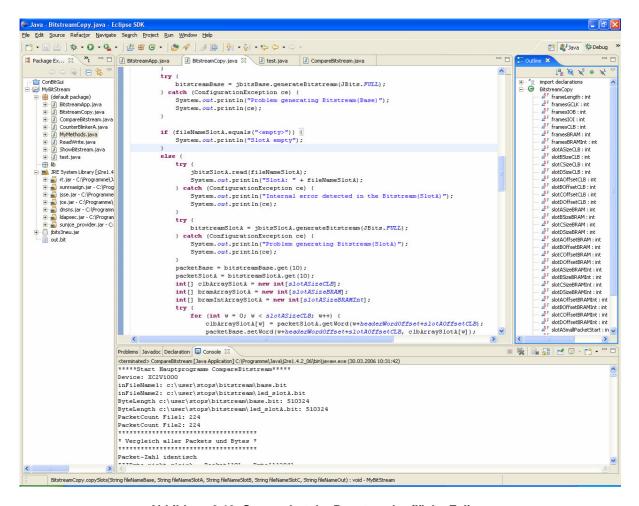

|      | 3.8.3          | Programmiersprache Java und der Editor Eclipse                                             |       |

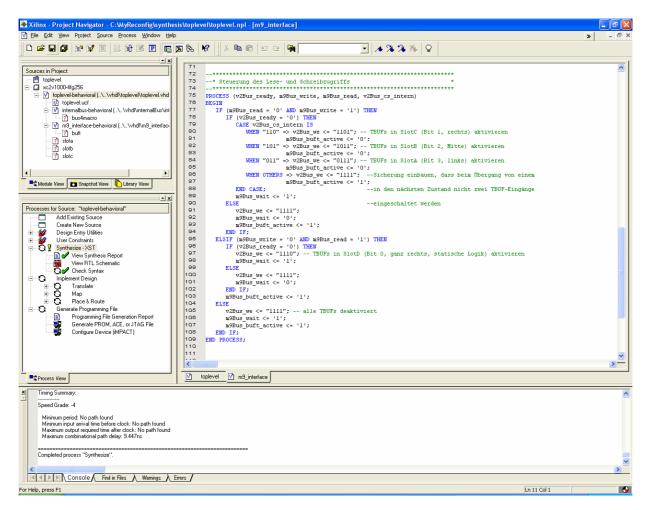

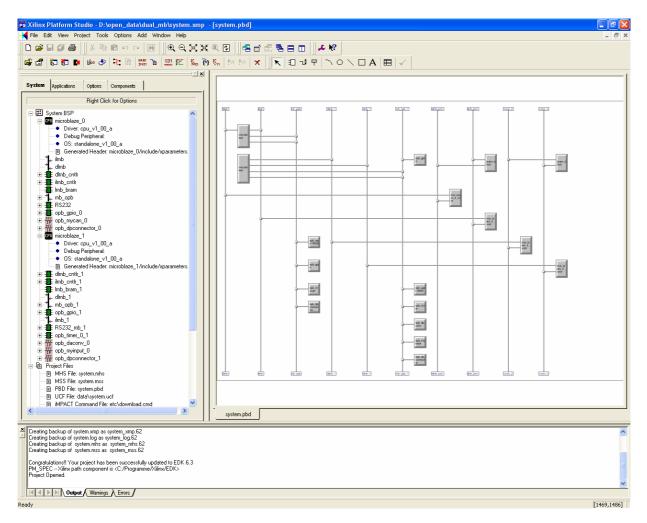

|      | 3.8.4<br>3.8.5 | Kombinationswerkzeuge (Xilinx ISE/EDK/PlanAhead)                                           |       |

| 2.0  |                |                                                                                            |       |

| 3.9  | _              | nensmodelle und Werkzeugeinsatz                                                            |       |

|      |                | Lebenszyklusmodelle zur Systementwicklung Graphische Modellierung mit Case-Tools           |       |

| 3.10 |                | Prototyping                                                                                |       |

| 00   | -              | Arten des Rapid Prototyping                                                                |       |

|      |                | Phasen des Rapid Prototyping                                                               |       |

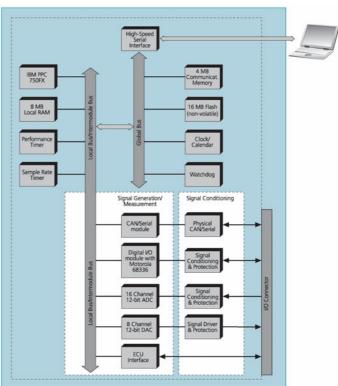

|      | 3.10.3         | Schnittstellen für Rapid Prototyping                                                       | . 59  |

|      |                | Stand der Technik und der Forschung                                                        |       |

|      |                | Bewertung Rapid-Prototyping-Systeme                                                        |       |

| 3.11 |                | are-in-the-Loop                                                                            |       |

|      |                | Schnittstellen für Hardware-in-the-Loop                                                    |       |

|      |                | Stand der Technik und der Forschung                                                        |       |

| 2 12 |                | ich von Rapid Prototyping und Hardware-in-the-Loop                                         |       |

| 3.12 | •              | Bewertung                                                                                  |       |

| 3 13 |                | erungen                                                                                    |       |

| 0.10 | 71111010       | or <b>u</b> nger                                                                           | , , , |

| Die  | RP-H           | iL-Plattform                                                                               | 75    |

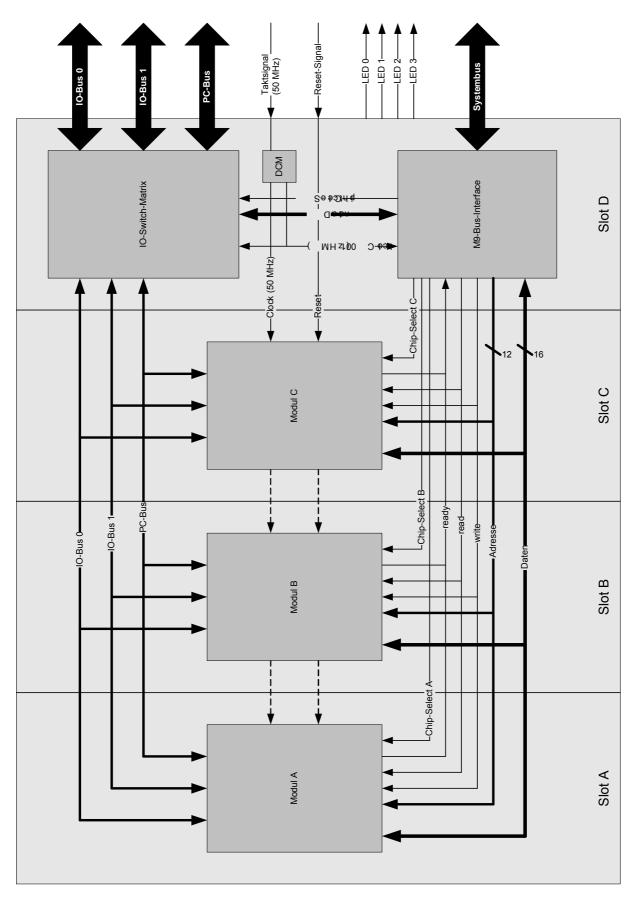

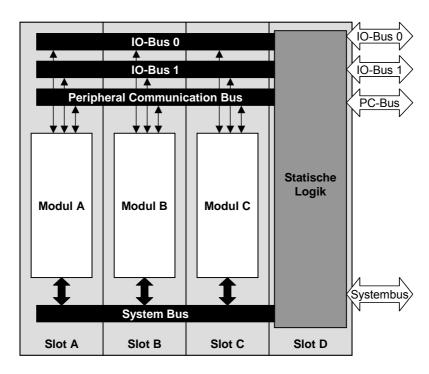

| 4.1  | System         | nkonzept des Basissystems                                                                  | . 75  |

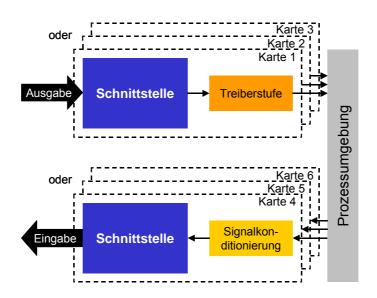

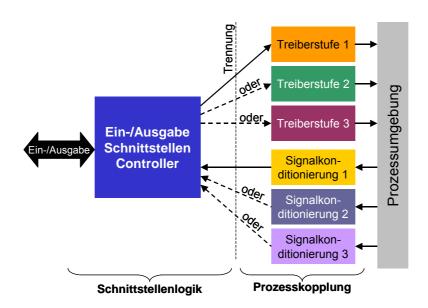

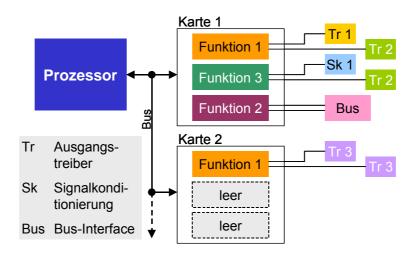

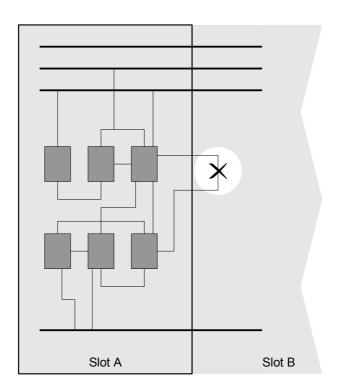

|      | 4.1.1          | Trennung von Logik und Prozesskopplung bei I/O-Schnittstellen                              |       |

|      | 4.1.2          | Bedarfsgerechte Konfiguration des Systems                                                  |       |

|      | 4.1.3          | Einsatz von FPGAs                                                                          |       |

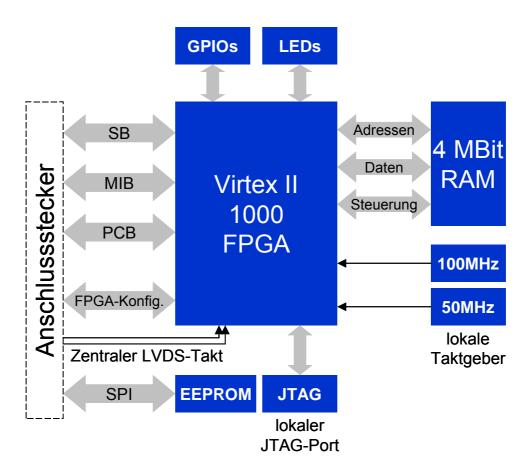

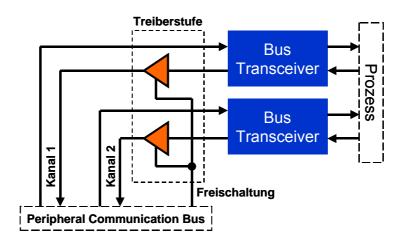

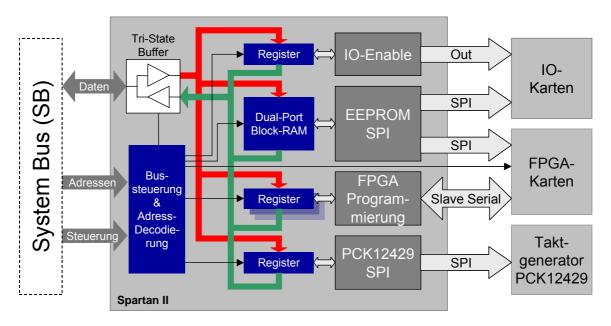

|      | 4.1.4<br>4.1.5 | Ressourcenbelegung auf dem FPGA Modularer Aufbau und Aufteilung der Systemfunktionalitäten |       |

|      | 4.1.5          | modularer Auroau und Aurtending der Systemidiktionalitäten                                 | . 04  |

4

|   |     |                | Identifikation der Steckkarten                                                                 |     |

|---|-----|----------------|------------------------------------------------------------------------------------------------|-----|

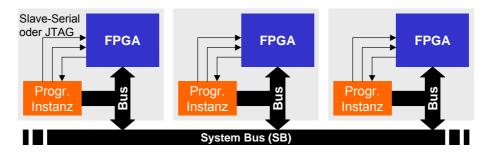

|   |     |                | Konfiguration der FPGAs                                                                        |     |

|   |     |                | Zentrale Takterzeugung und -verteilung                                                         |     |

|   |     |                | Bussystemarchitektur                                                                           |     |

|   |     |                | Speicherung von Konfigurations- oder Messdaten                                                 |     |

|   |     |                | Temperaturbereich                                                                              |     |

|   |     |                | Energieversorgung des Systems                                                                  |     |

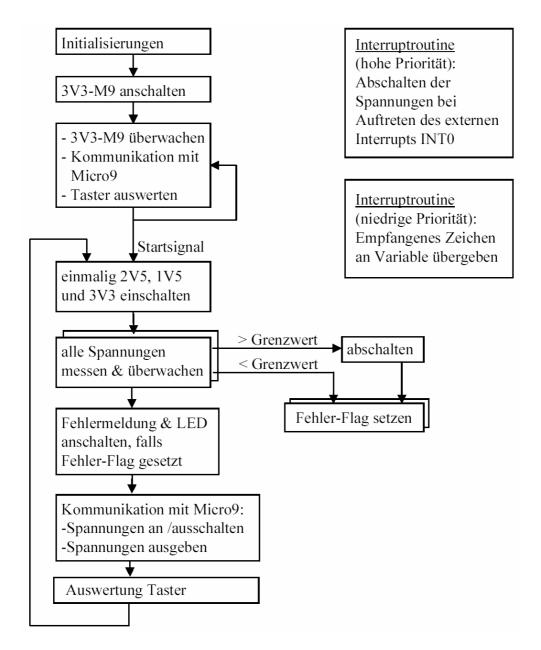

|   |     |                | Sicherheitskonzept                                                                             |     |

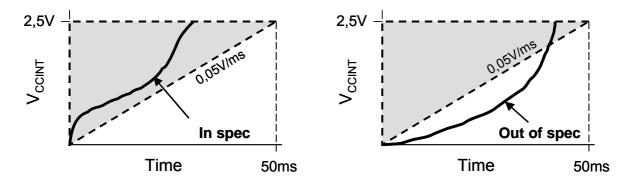

|   | 4.2 | Konzep         | t der Stromversorgung (Power Management Unit)                                                  | 100 |

|   |     |                | Abschätzung der Leistungsaufnahme der Plattform                                                |     |

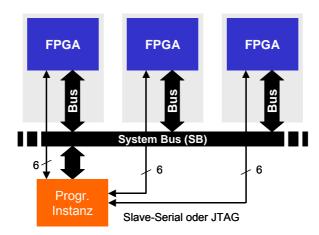

|   |     |                | Anforderungen zur Versorgung der FPGAs                                                         |     |

|   |     |                | Anforderungen an das Einschalten der FPGA-Spannungen Blockschaltbild der PMU                   |     |

|   |     |                | Spannungs-Monitoring, An- und Abschaltezyklen                                                  |     |

|   | 4.3 |                | is des Konzepts                                                                                |     |

|   | 4.4 |                | erung der Plattform                                                                            |     |

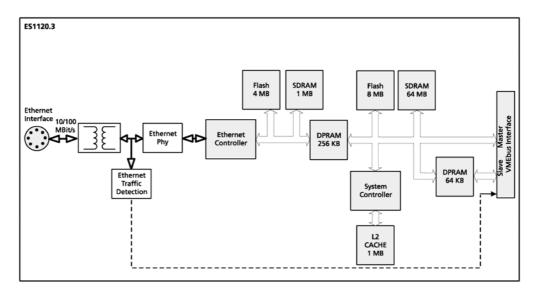

|   | 7.7 |                | Überblick über die Basisplatine und die Stromversorgung                                        |     |

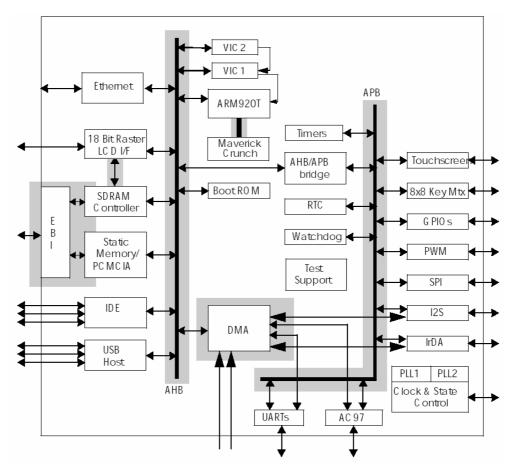

|   |     |                | Hauptprozessoreinheit                                                                          |     |

|   |     |                | CAN-Bus                                                                                        |     |

|   |     |                | Ethernet-Anschluss                                                                             |     |

|   |     |                | Serielle Schnittstellen                                                                        |     |

|   |     | 4.4.6          | USB-Schnittstelle                                                                              |     |

|   |     | 4.4.7<br>4.4.8 | Interface-Karte                                                                                |     |

|   |     |                | Automotive-Karte                                                                               |     |

|   | 4.5 |                | erung der PMU                                                                                  |     |

|   | 1.0 |                | Überblick über die Stromversorgung (PMU)                                                       |     |

|   |     |                | Ausgangsleistung und Wirkungsgrad der PMU-Schaltregler                                         |     |

| _ | Cla | . boois        | arta FDCA Kanfiguration                                                                        | 117 |

| 5 |     |                | erte FPGA-Konfiguration                                                                        |     |

|   | 5.1 |                | von FPGAs in RP- oder HiL-Geräten                                                              |     |

|   |     |                | Problematik bei inkrementeller Änderung                                                        |     |

|   |     |                | Anforderungen                                                                                  |     |

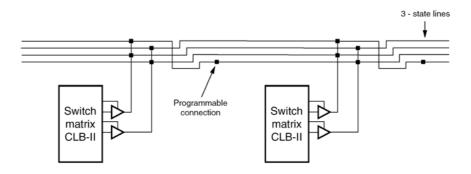

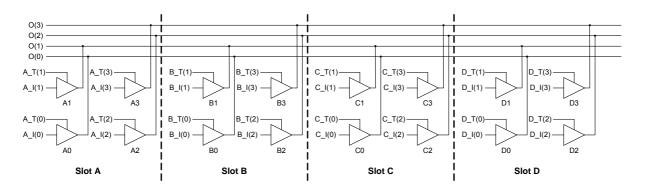

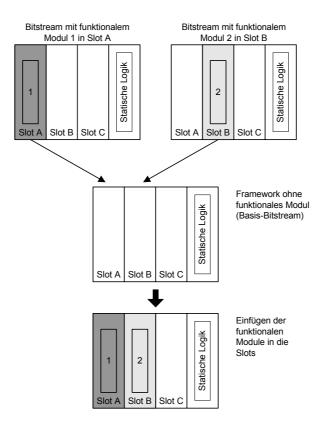

|   | 5.2 |                | dee                                                                                            |     |

|   |     |                | Aufteilung der FPGA-Logik in Bereiche                                                          |     |

|   | 5.3 | Konzep         | t des "Bitstream-Merging"                                                                      | 123 |

|   | 5.4 | Hardwa         | are-Framework                                                                                  | 124 |

|   |     | 5.4.1          | Integration verschiedener Module                                                               |     |

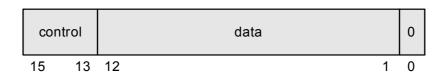

|   |     |                | Kommunikation der Module mit der Umgebung                                                      |     |

|   |     |                | Systembus                                                                                      |     |

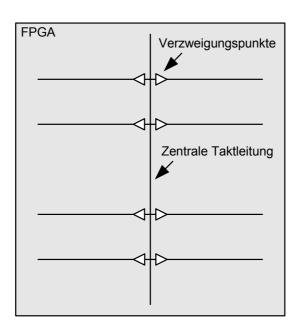

|   |     |                | I/O-Schnittstellen und Peripheral Communication Bus<br>Verteilung des Taktsignals auf dem FPGA |     |

|   | 5.5 |                | erstellung                                                                                     |     |

|   | 5.5 |                | Design-Ablauf                                                                                  |     |

|   |     | J.J. I         | Design-Abiaul                                                                                  | ISC |

|   |     | 5.5.2  | Netzliste des Toplevel-Designs                               |     |

|---|-----|--------|--------------------------------------------------------------|-----|

|   |     | 5.5.3  | Netzlisten der funktionalen Module                           |     |

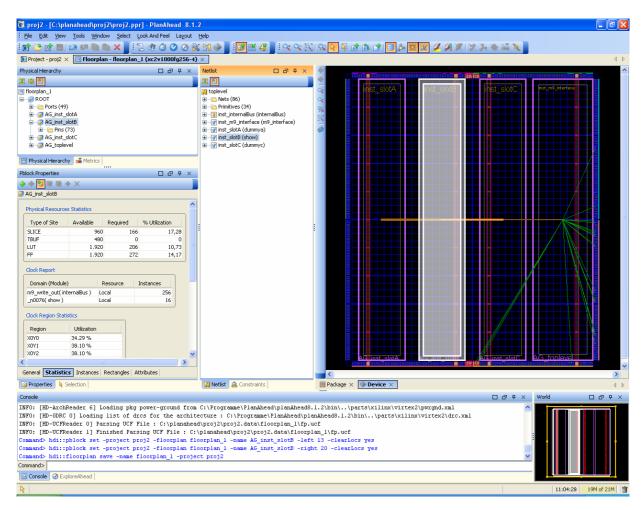

|   |     | 5.5.4  | Implementierung mit PlanAhead                                |     |

|   |     | 5.5.5  | Anlegen eines Projekts                                       |     |

|   |     | 5.5.6  | Exportieren des Floorplans                                   |     |

|   |     | 5.5.7  | ISE Place-&-Route und Bitgen                                 |     |

|   |     | 5.5.8  | Erstellen aller Bitstreams                                   |     |

|   |     | 5.5.9  | Abweichungen vom Standard-Design-Ablauf                      |     |

|   |     |        | Vergleich der Bitstreams                                     |     |

|   |     |        | Aktivierung des Taktsignals auf dem FPGA                     |     |

|   | г,  |        | XML-Konfigurationsdateien der funktionalen Module            |     |

|   | 5.6 |        | bibliothek                                                   |     |

|   |     | 5.6.1  | Ansteuerung D/A-Wandler (Modul dac)                          |     |

|   |     |        | CAN-Controller (Modul can)                                   |     |

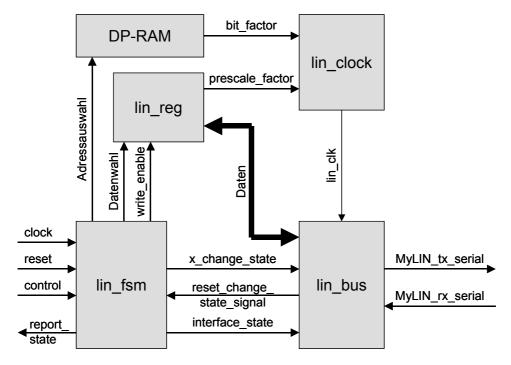

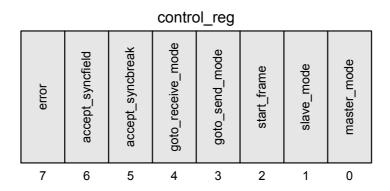

|   |     |        | LIN-Controller (Modul lin)                                   |     |

|   | 5.7 | Abschl | ließende Bewertung der Designmethode                         | 143 |

|   | 5.8 | Sicher | heitskonzept                                                 | 144 |

| 6 | Sof | tware  | -Umgebung                                                    | 147 |

| J | 6.1 |        | are für RP-HiL-Plattform                                     |     |

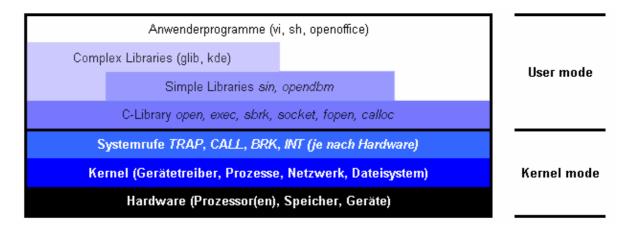

|   | 0   | 6.1.1  | Betriebssystem Embedded Linux                                |     |

|   |     | 6.1.2  | Plattform-Konfigurations-Tool                                |     |

|   |     | 6.1.3  | Linux-Gerätetreiber                                          |     |

|   |     | 6.1.4  | CompassLink-Applikation                                      |     |

|   |     | 6.1.5  | Starten und Herunterfahren des Netzwerkservers               |     |

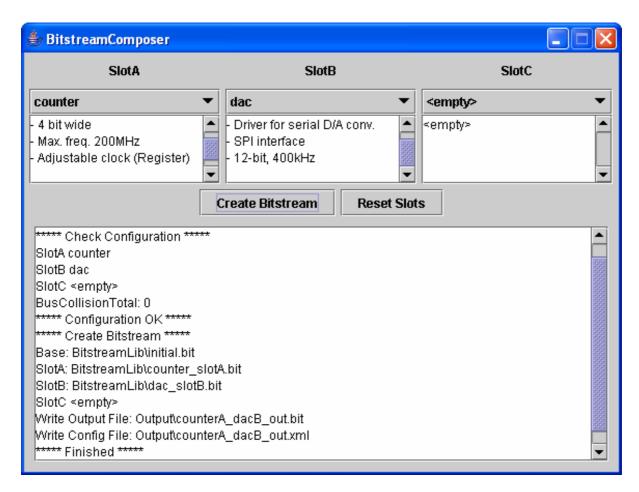

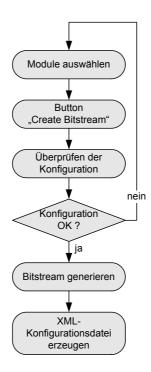

|   | 6.2 |        | amComposer - Modulaustausch per "Drop-Down-Menü"             |     |

|   |     | 6.2.1  | Funktion des Programms                                       |     |

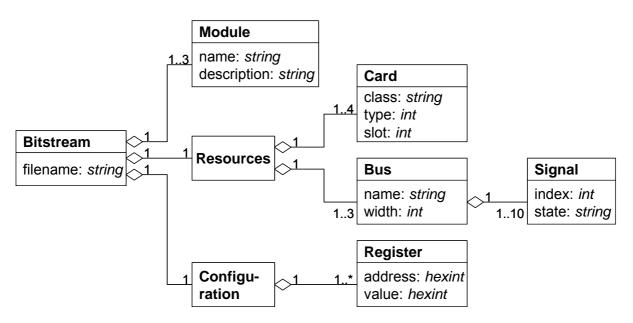

|   |     | 6.2.2  | XML-Konfigurationsdatei des Gesamtsystems                    |     |

|   |     | 6.2.3  | Verzeichnisstruktur der Applikation                          |     |

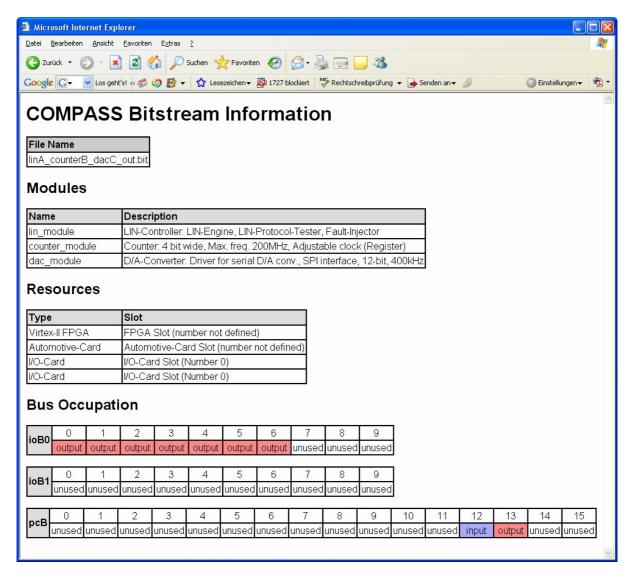

|   |     | 6.2.4  | Ergebnisse der Methodik anhand einer Beispielimplementierung | 162 |

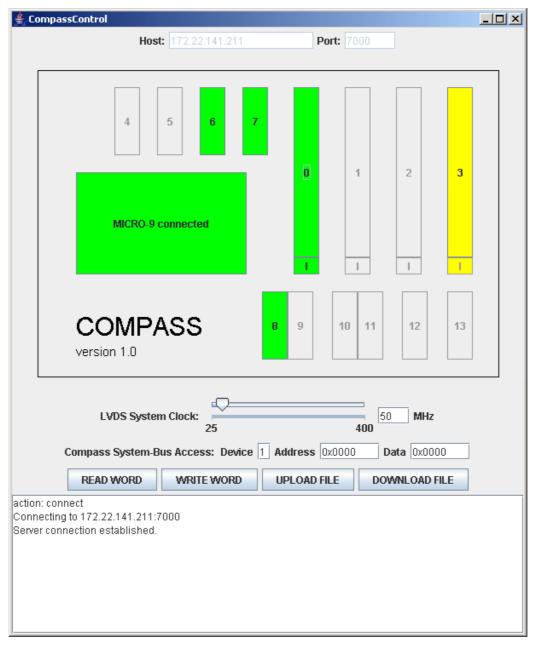

|   | 6.3 | Compa  | assControl - Bedienung und Steuerung des Systems             | 163 |

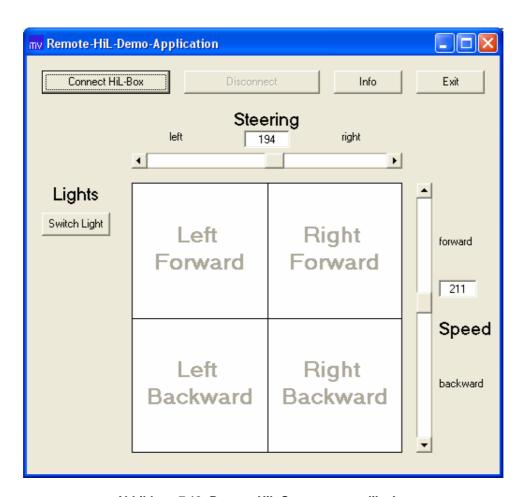

|   |     | 6.3.1  | Grafische Benutzeroberfläche (GUI)                           | 163 |

|   |     | 6.3.2  | Bedienung des Programms                                      |     |

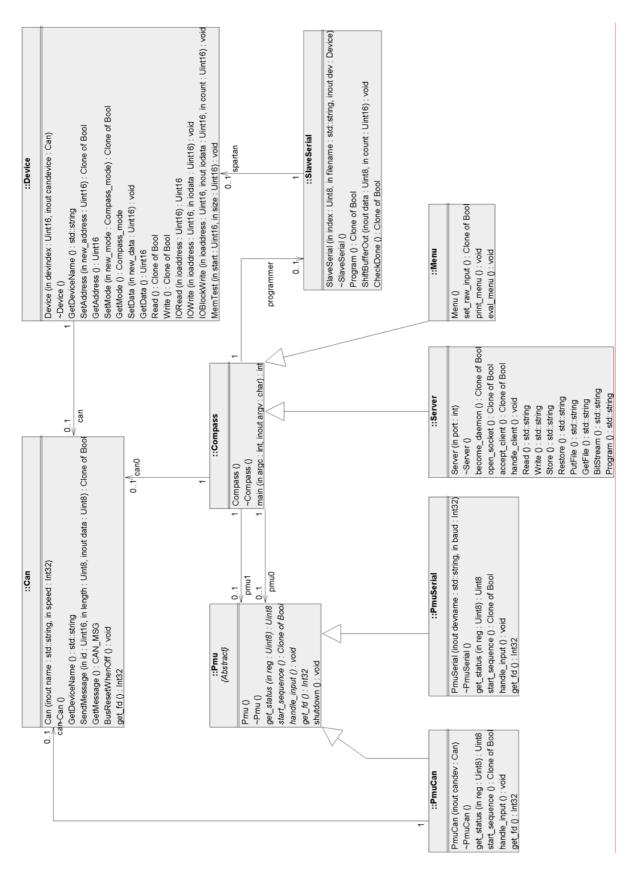

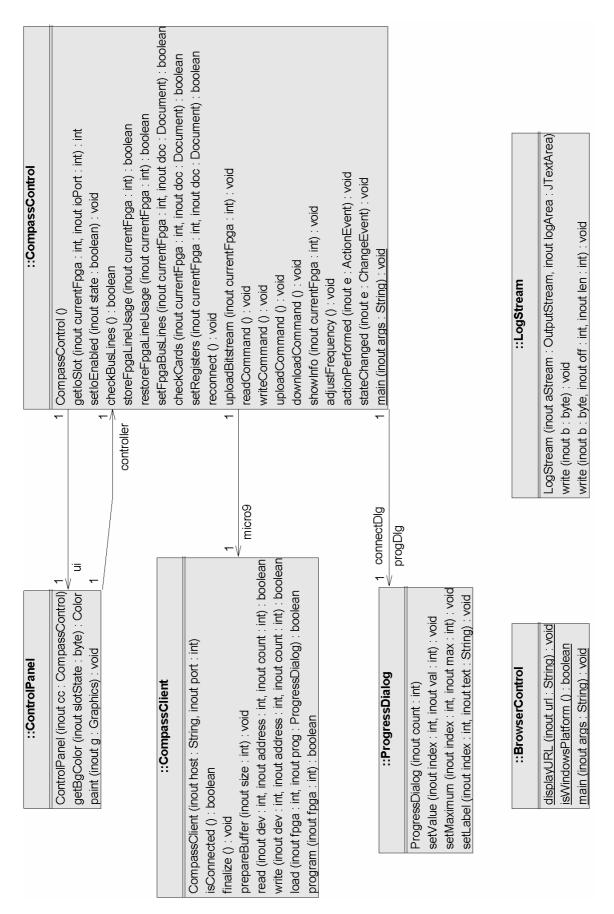

|   |     | 6.3.3  | Klassendiagramm CompassControl                               | 165 |

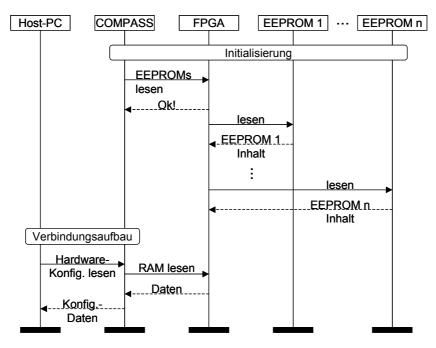

|   |     | 6.3.4  | Kommunikation zwischen GUI und Plattform                     | 167 |

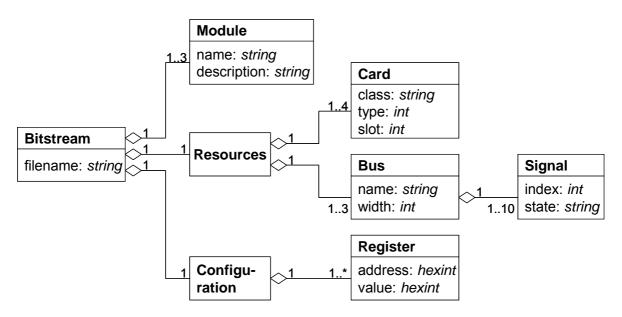

|   |     | 6.3.5  | Bitstream-Beschreibung im XML-Format                         | 168 |

|   |     | 6.3.6  | Kompatibilitätsprüfung zwischen Bitstream und Plattform      |     |

|   |     | 6.3.7  | Dokumentation der Schnittstellenkonfiguration                |     |

|   |     | 6.3.8  | Remote-RP und Remote-HiL                                     | 173 |

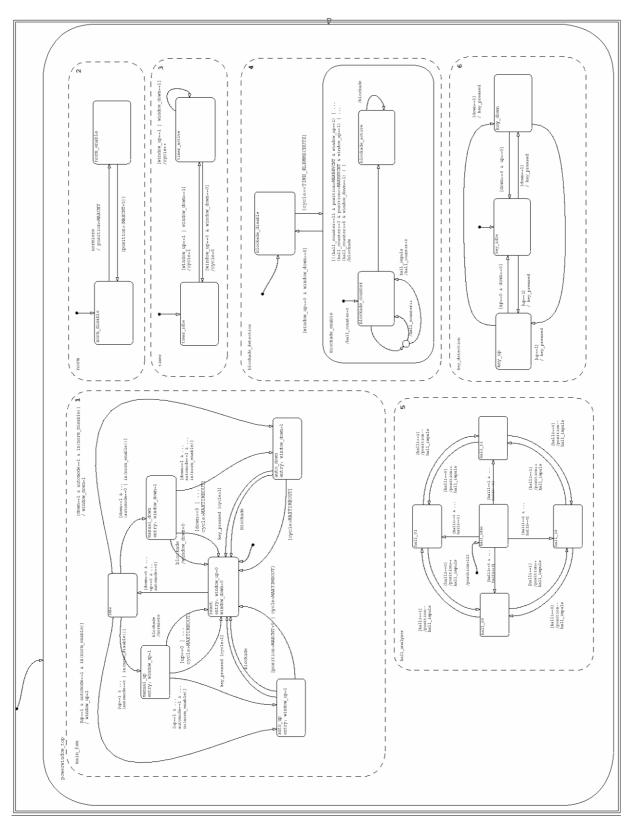

|   | 6.4 |        | basierte Applikationserstellung                              |     |

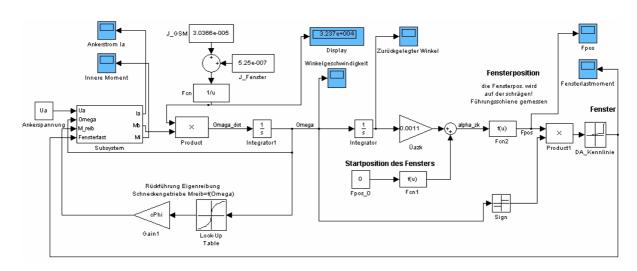

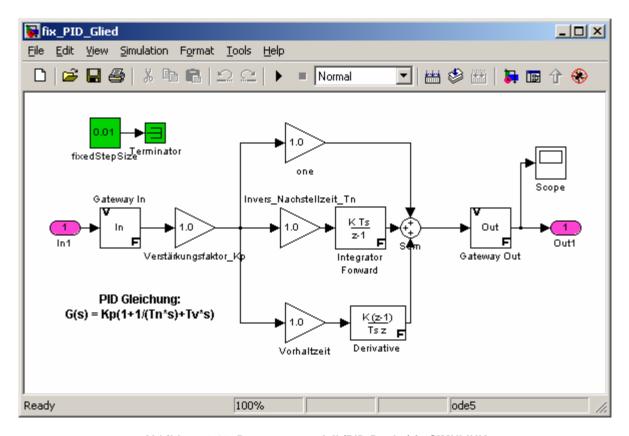

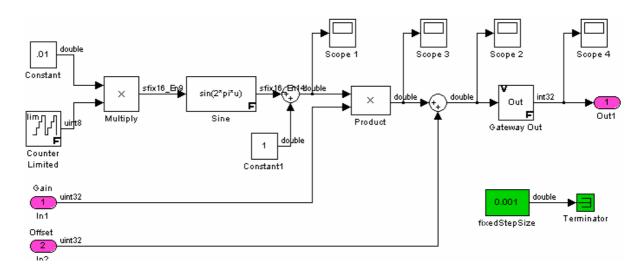

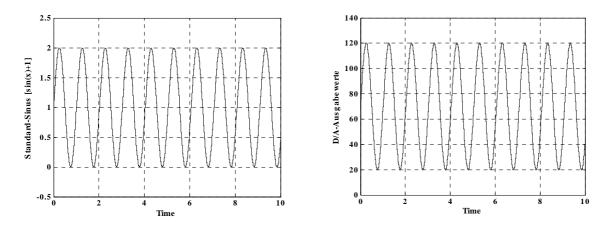

|   |     | 6.4.1  | Modellierung kontinuierlicher Systeme                        |     |

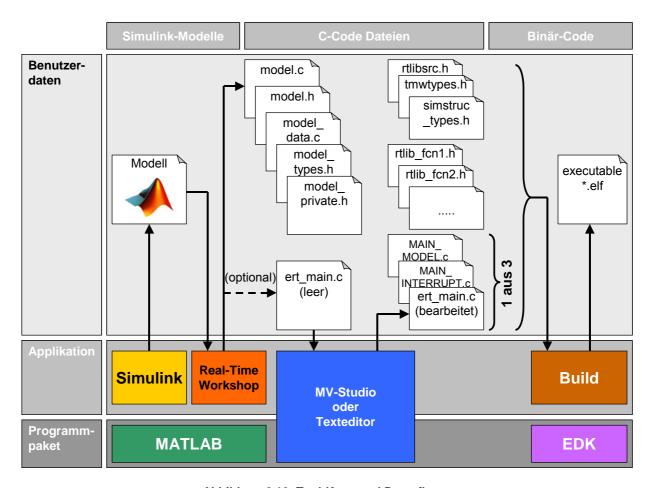

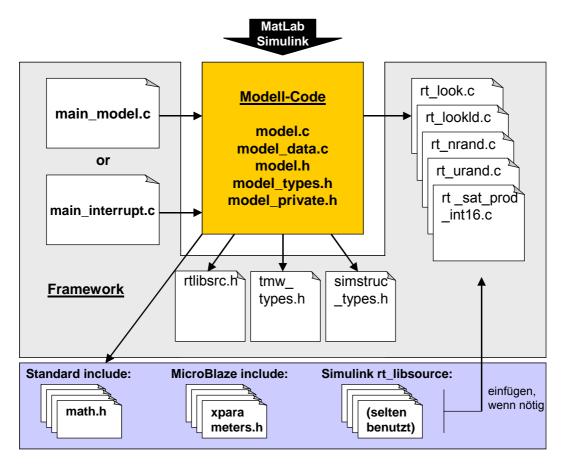

|   |     | 6.4.2  | Modellausführung auf einem MicroBlaze                        |     |

|   |     | 6.4.3  | Integration als reine Hardware-Lösung                        |     |

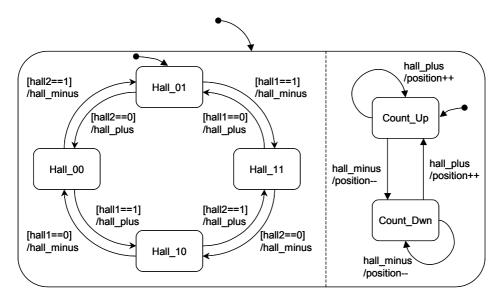

|   |     | 6.4.4  | Modellierung zeitdiskreter Systeme                           |     |

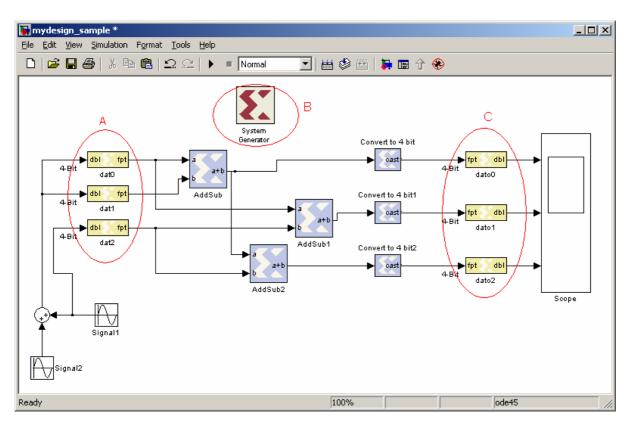

|   |     | 6.4.5  | Modellimplementierung in Hardware                            | 190 |

| 7 | Anv | 191                                              |     |

|---|-----|--------------------------------------------------|-----|

|   | 7.1 | RP-Anwendungen                                   | 191 |

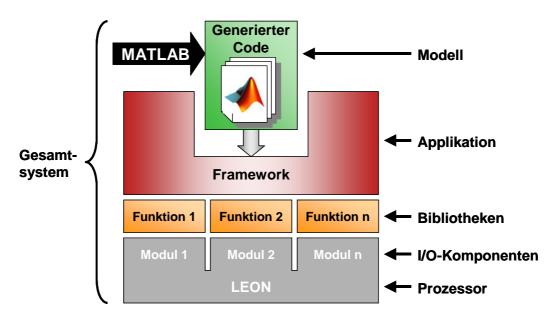

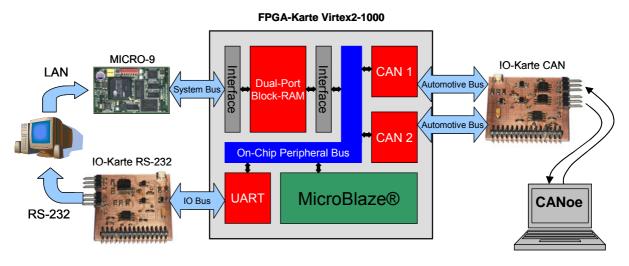

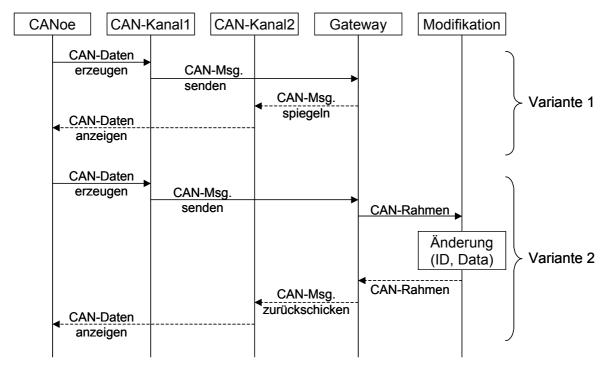

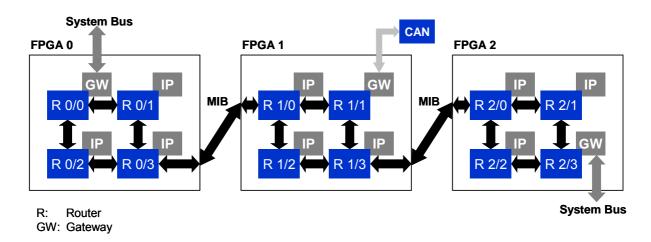

|   |     | 7.1.1 CAN2CAN-Gateway                            | 191 |

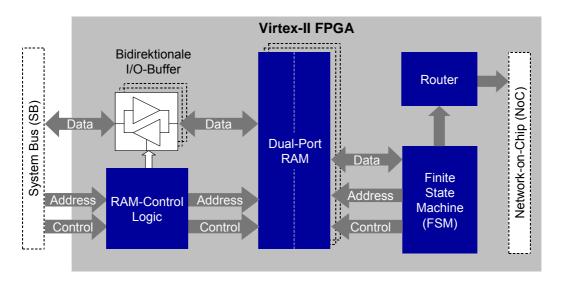

|   |     | 7.1.2 NoC-Testszenario                           |     |

|   | 7.2 | HiL-Anwendungen                                  | 196 |

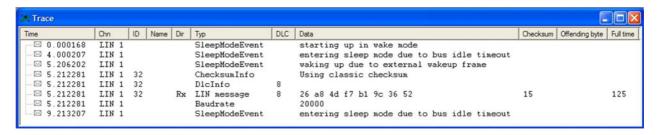

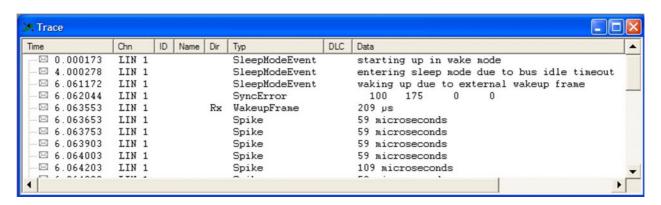

|   |     | 7.2.1 LIN-Bus-Tester                             |     |

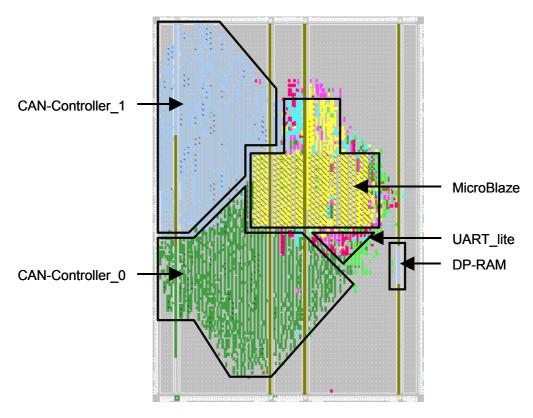

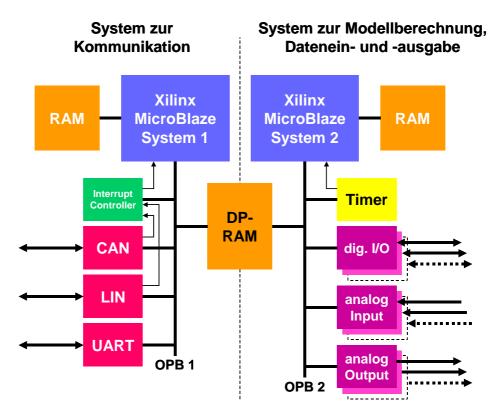

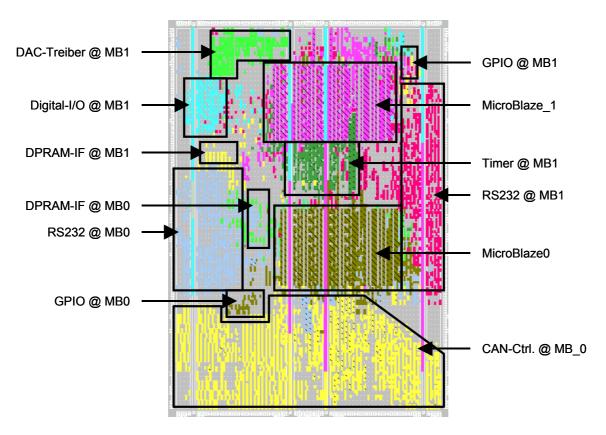

|   |     | 7.2.2 Doppel-MicroBlaze-Subsystem                | 202 |

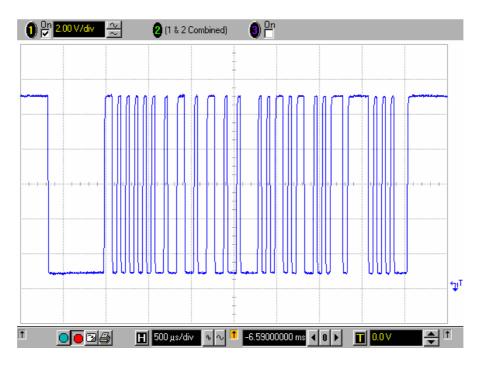

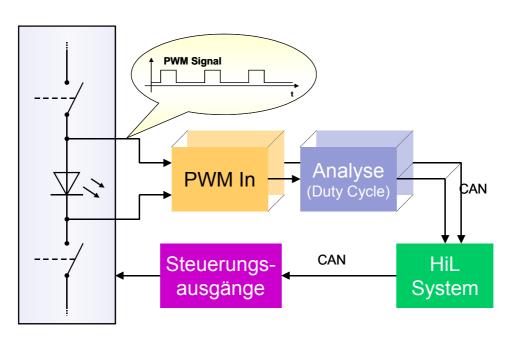

|   |     | 7.2.3 PWM-Analysator für Automotive-Steuergeräte |     |

|   |     | 7.2.4 Remote-HiL-Demonstrationsszenario          | 209 |

| 8 | Zus | sammenfassung, Ergebnisse und Ausblick           | 213 |

|   | 8.1 | Zusammenfassung und Ergebnisse                   | 213 |

|   | 8.2 | Ausblick                                         | 215 |

| 9 | Ver | zeichnisse                                       | 219 |

|   | 9.1 | Abbildungsverzeichnis                            | 219 |

|   | 9.2 | Tabellenverzeichnis                              | 223 |

|   | 9.3 | Formelverzeichnis                                | 224 |

|   | 9.4 | Abkürzungsverzeichnis                            | 225 |

|   |     | 9.4.1 Allgemeine Abkürzungen                     |     |

|   |     | 9.4.2 Eigene Abkürzungen                         |     |

|   | 9.5 | Formelzeichen                                    | 228 |

|   | 9.6 | Literaturverzeichnis                             | 229 |

|   | 9.7 | Betreute Diplom-, Studien- und Seminararbeiten   |     |

|   |     | 9.7.1 Diplomarbeiten                             |     |

|   |     | 9.7.2 Studienarbeiten                            |     |

|   |     | 9.7.3 Seminararbeiten                            | 251 |

|   | 9.8 | Eigene Veröffentlichungen                        | 252 |

## 1 Einleitung

Eingebettete Systeme haben mittlerweile in alle Lebensbereiche Einzug gehalten. Bekannte Felder aus dem täglichen Umgang sind dabei die Unterhaltungselektronik im Allgemeinen, die Medizintechnik, die Automobilbranche, aber auch die Luft- und Raumfahrt-, sowie die Automatisierungstechnik im industriellen Umfeld (Abbildung 1.1). In allen aufgeführten Bereichen ist die Komplexität der Systeme in den letzten Jahre enorm gestiegen, so dass die Entwicklungs- und Testverfahren, sowie die entsprechenden Entwicklungs- und Testsysteme angepasst bzw. verbessert werden müssen. Durch die wachsende Interaktion der bisher autonom agierenden eingebetteten Systeme ergibt sich eine weitere Dimension der Systemüberprüfung.

Abbildung 1.1: Einsatzbereiche von Eingebetteten Systemen

Wie nachhaltig sich die Verhältnisse teilweise darstellen können, lässt sich am anschaulichsten am Beispiel der Steuergeräteentwicklung im Automobilsektor demonstrieren. Dort ist

neben dem großen Bekanntheitsgrad auch die Innovationsdichte am höchsten. Daher bietet sich eine genaue Betrachtung des Automotive-Umfeldes an, das im Folgenden die Basis dieser Arbeit bildet.

## 1.1 Motivation - Entwicklung und Test von Steuergeräten

Im Bereich der Kraftfahrzeuge ist in den letzten eine enorme Komplexitätssteigerung der elektrischen und elektronischen Systeme zu verzeichnen. Dies gilt zum einen für die Steuergeräte selbst, als auch für deren Vernetzung untereinander. Damit diese komplexen Systeme über mehrere Jahre zuverlässig funktionieren können, sind neben einer guten Planung umfangreiche Tests notwendig. Dabei muss nicht nur die Korrektheit der Funktion überprüft werden, sondern insbesondere auch die Reaktion einer Baugruppe auf Fehlfunktionen der angeschlossenen Komponenten.

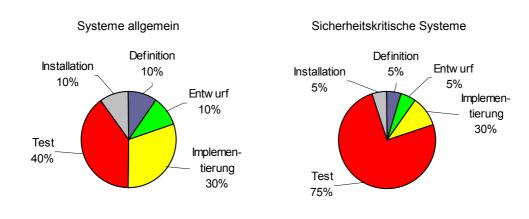

Abbildung 1.2: Aufwände (Kosten) bei der Systementwicklung [Fraun03]

In Abbildung 1.2 wird deutlich, wie groß der Testaufwand bei der Entwicklung von elektronischen Systemen ist. Handelt es sich dabei um sicherheitskritische Systeme, erhöht sich dieser Anteil im Entwicklungsprozess auf fast das Doppelte. Dieser Aufwand kann nur durch den konsequenten Einsatz von Entwicklung- und Testmethoden, sowie den entsprechenden Werkzeugen bewältigt werden.

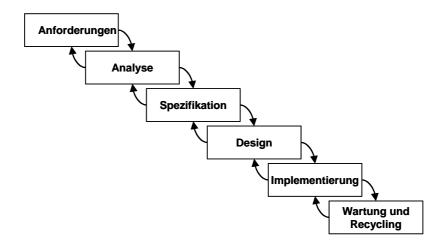

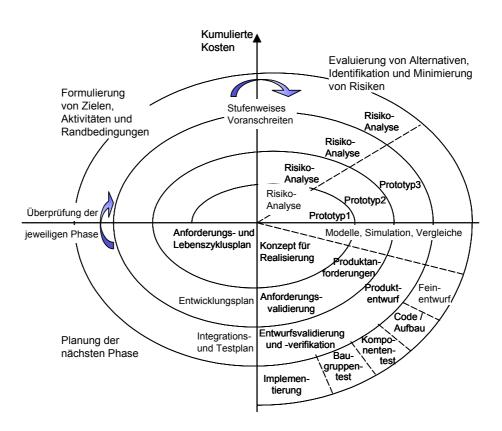

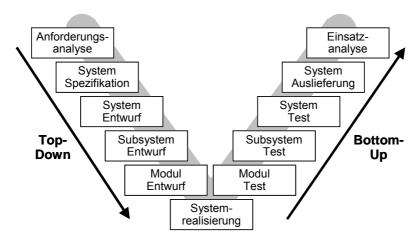

Daher werden heute Entwicklung und Test von elektronischen Systemen im Allgemeinen nach dem V-Modell durchgeführt ([IABG06], bzw. Kapitel 3.9.1.3). Zu Beginn erfolgt zunächst eine Systemanalyse, in welcher der Auftraggeber alleine oder in Zusammenarbeit mit einem Entwicklungsteam des Auftragnehmers die Anforderungen in einem iterativen Prozess ermittelt. Im Idealfall geschieht dies bereits mit Hilfe einer formalisierten Beschreibung, damit die Konsistenz dieser Phase zu den folgenden gewährleistet bleibt. In der anschließenden Spezifikationsphase werden Lasten- und Pflichtenhefte formuliert, die das Verhalten, den Aufbau sowie weitere technische aber auch finanzielle Randbedingungen festlegen. Die vom Auftraggeber geforderten Basismerkmale hinsichtlich Funktion und Ausführung, die das Endprodukt erfüllen muss, werden im Lastenheft zusammengefasst. Nach Abschluss dieser ersten Schritte wird mit dem Systementwurf begonnen, der sich weiter in den Subsystemund den Modulentwurf gliedert. An den Übergängen der einzelnen Phasen werden Verifikationsschritte zwischengeschaltet, um die Entwicklung auf Konsistenz zu prüfen. Der Abschluss des Entwurfs mündet dann in der Systemrealisierung, in der bereits ein Vorläufer des Produkts verfügbar ist. Bis zur Systemauslieferung und der Einsatzanalyse, werden nun alle entwickelten Systemteile (Module, Subsysteme), sowie das Gesamtprodukt getestet.

Zur Unterstützung der im V-Modell festgelegten Vorgänge kommen Methoden und Testverfahren zum Einsatz, die durch das Erreichen einer frühen Konzeptsicherheit die Fehlerquote senken helfen, zum anderen die entstandenen Teilprodukte gegen die vorher festgelegte Spezifikation testen. Die im Folgenden aufgeführten Methoden sind daher auf beiden Ästen des V-Modells (siehe Kapitel 3.9.1.3) angesiedelt.

|        |             | Umwe                  | elt               |

|--------|-------------|-----------------------|-------------------|

|        |             | Simuliert             | Real              |

| S      | Modell      | Model in the loop     | Rapid Prototyping |

| y<br>s | Code        | Software in the loop  |                   |

| t<br>e | Testboard   | Processor in the loop |                   |

| m      | Steuergerät | Hardware in the loop  |                   |

Abbildung 1.3: Testverfahren zur Unterstützung der Produktentwicklung

Mit Rapid Prototyping (RP) (Kapitel 3.10) können durch eine Validierung der Kundenvorgaben bereits frühzeitig konzeptionelle Fehler eliminiert werden. Es wird daher verstärkt zwischen der Anforderungs- und Spezifikationsphase und zwischen der Spezifikationsphase und dem Systementwurf eingesetzt.

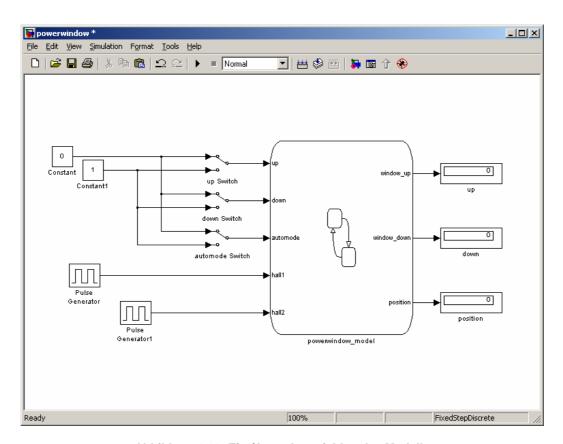

Model-in-the-Loop (MiL) ist der erste Vertreter der X-in-the-Loop-Tests. Hierbei werden die durch CASE-Tools (MatLab/Simulink oder Stateflow [Math04][Math13], ...) in Modellen beschriebenen Zusammenhänge in einer virtuellen Umgebung auf einem Rechner simuliert. Für dieses Verfahren – sowie für alle folgenden X-in-the-Loop Verfahren – wird ein Modell der Umgebung des zu Entwickelnden Steuergeräts benötigt. Das Umgebungsmodell besitzt allerdings einen recht hohen Abstraktionsgrad. Gleiches gilt für Software-in-the-Loop (SiL) Tests, bei denen anstelle eines Modells, bereits der aus dem Modell erzeugte Programm-Code (meist in C) in einer Simulationsumgebung verifiziert wird. Eine zu diesem Zeitpunkt unter Umständen noch nicht verfügbare Zielhardware wird bis zu diesem Zeitpunkt nicht benötigt. Im Gegensatz dazu hat das Processor-in-the-Loop (PiL) Verfahren das Ziel, den in der Simulationsumgebung überprüften Code auf dem tatsächlich eingesetzten Prozessor ablaufen zu lassen. Dieser wird jedoch isoliert betrachtet, d.h. er ist noch nicht im letztlichen Produkt (Steuergerät) eingebaut.

Den Abschluss der X-in-the-Loop-Testverfahren bildet der Hardware-in-the-Loop (HiL) Test (Kapitel 3.11), der ein fertiges Produkt hinsichtlich Hardware und Software verlangt. Seine Aufgabe ist es, den letzten Implementierungsschritt zu verifizieren und darüber hinaus die Überprüfung der Korrektheit des Produkts an der gegebenen Spezifikation vorzunehmen.

Diese Techniken, insbesondere für Rapid Prototyping und Hardware-in-the-Loop, sind in vielen Jahren gewachsen und finden bei der Systementwicklung im Automobilbereich Anwendung. Die dazu existierenden Testplattformen haben einen Stand erreicht, der sehr auf die Erfordernisse der bisherigen Technologien ausgerichtet (Kapitel 3.10.4 bzw. 3.11.2) und getrennte Hardware-Plattformen für RP und HiL vorsieht. Um dem schnellen technologischen Fortschritt standhalten zu können, müssen zum einen die Tests und Testmethoden intensiv weiterentwickelt, zum anderen aber auch die dazu nötigen Hardware-Plattformen an die geänderten Bedingungen angepasst werden. Dazu gehören eine höhere Flexibilität hinsichtlich der Adaptierbarkeit der Schnittstellen und der Systemarchitektur unter Beibehaltung eines modularen Aufbaus. Besonders der steigende Einsatz von schnellen Kommunikationssystemen im Fahrzeug und der damit verbundene Test verlangt nach höheren Abtastraten zur Erreichung einer höheren zeitlichen Auflösung der Signale. Aber auch rechenintensive

Prozesse benötigen entsprechende Hardware-Voraussetzungen, z.B. durch die Möglichkeit einer parallelen Ausführung. Feld programmierbare Bausteine (FPGAs, Field Programmable Gate Arrays – Kapitel 3.1.1) bieten dazu eine sehr gute Alternative zu den bisherigen Konzepten, da mit ihnen eine flexible Implementierung von Hardware, eine schnelle Anpassung an sich ändernde Umgebungen und ein hoher Wiederverwendungsgrad möglich ist.

## 1.2 Ziele der Arbeit - Der eigene Beitrag

Die Grundidee der Arbeit war es, ein flexibles und leistungsfähiges, aber dennoch kleines und mobiles System auf Basis feld-programmierbarer Logik (FPGA) zu entwickeln, das gleichermaßen für Rapid-Prototyping und Hardware-in-the-Loop eingesetzt werden kann und damit eine Kombinationslösung für beide Zwecke darstellt. Das Hauptaugenmerk lag dabei auf einer möglichst gut parametrierbaren Lösung, die außerdem einfach zu handhaben und zu bedienen ist.

Die Basis der Plattform bildet ein modularer Aufbau, bei dem frei programmierbaren Interface-Karten, Kommunikationsmodule für Bussysteme und Ein-/Ausgabe-Schnittstellen nach Bedarf eingesteckt werden können. Gegenüber den derzeitigen kommerziellen Geräten ergibt sich durch den Einsatz von FPGAs anstelle dedizierter I/O-Komponenten eine Erhöhung der Flexibilität hinsichtlich der Funktionsimplementierung. Die I/O-Funktionen in Form von Schnittstellen-Controller werden als Logikblöcke zur Systemlaufzeit in FPGAs geladen, wobei eine Karte mehrere verschiedene Funktionen (verschiedene I/O-Controller, z.B. digitale I/O, PWM [in, out], Nachbildung serieller Protokolle, ...) enthalten kann. Dadurch lässt sich die Anzahl verschiedenartiger Karten erheblich reduzieren. Die Trennung der logischen Ansteuerung und der I/O-Treiber (Signalkonditionierung) unterstützt außerdem eine flexible Anpassung an sich ändernde Prozessumgebungen.

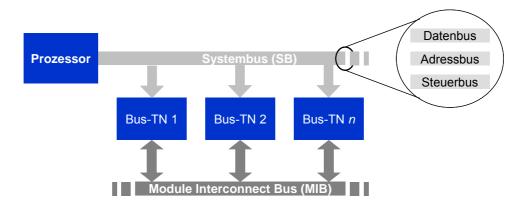

Die Plattform-interne Bussystemkonfiguration besteht aus verschiedenen Kommunikationswegen bzw. -kanälen, die so angelegt sind, dass auch hier eine möglichst große Flexibilität hinsichtlich des Einsatzes der Plattform und der darauf implementierten Systeme erreicht wird. Der Prozessor ist dazu mit allen Interface-Karten verbunden, wobei letztere auch untereinander, unabhängig vom Prozessor, kommunizieren können (Sub-System-Unterstützung, Modul-Synchronisierung, etc.). Die Auswahl eines externen Kommunikationsbussystems (z.B. CAN, LIN) ist nicht an eine Interface-Karte gebunden, sondern kann von allen Steckplätzen aus erreicht und auch zur Laufzeit adaptiert werden.

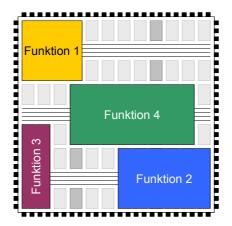

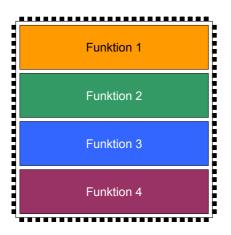

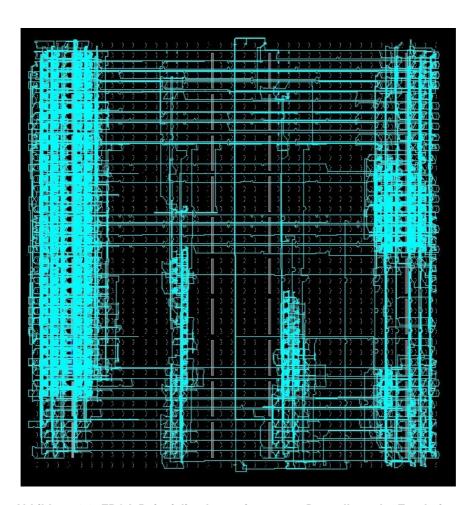

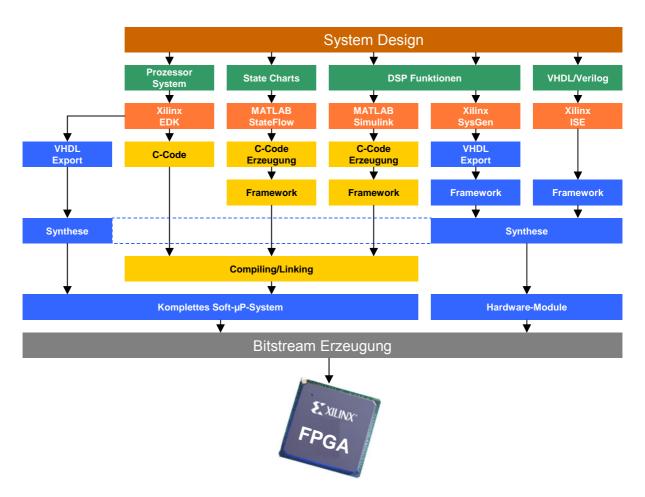

Zur Konfigurierung der FPGAs auf der Plattform wurde eine Methodik entwickelt, die durch Einführung einer weiteren Abstraktionsebene den kompletten Vorgang der Funktionsimplementierung verbirgt. Dadurch werden keinerlei Kenntnisse an Hardware-Beschreibungsprachen (wie VHDL, Verilog, SystemC, o.ä.), von Synthese-Tools oder FPGA-Interna benötigt, wodurch auch im Umgang oder der Programmierung von FPGAs unerfahrene Benutzer effizient mit der Plattform arbeiten können. Die gewünschten Funktionsmodule werden in einer grafischen Benutzeroberfläche (BitstreamComposer, Kapitel 6.2) aus einer Liste ausgewählt und einzelnen Bereichen innerhalb des FPGA zugewiesen. Eine Bibliothek bietet dazu vorgefertigte, funktions- und performanzgetestete Module. Die Abbildung auf die Strukturen des FPGA wird per Klick automatisch ausgeführt, wobei die ausgewählten Module in ein Framework eingebettet werden, das eine Basisfunktionalität (externe Busankopplung an den Prozessor und interne Bussysteme) bereitstellt. Das Ergebnis ist eine komplette Instrumentierungsdatei für den FPGA. Durch diesen Ansatz kann eine FPGA-Konfiguration binnen weniger Minuten zusammengestellt werden. Zeitraubende Iterationen durch Timingoder Ressourcenprobleme wie bei herkömmlichen CASE-Tool-Ansätzen fallen nicht an.

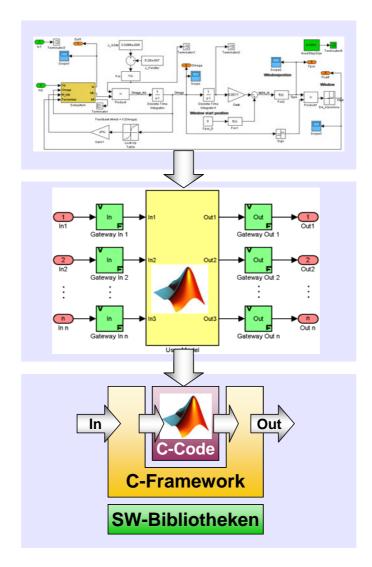

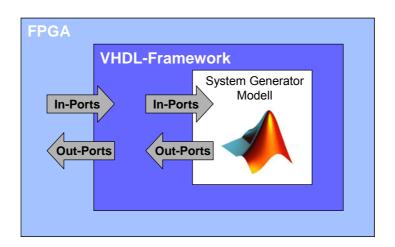

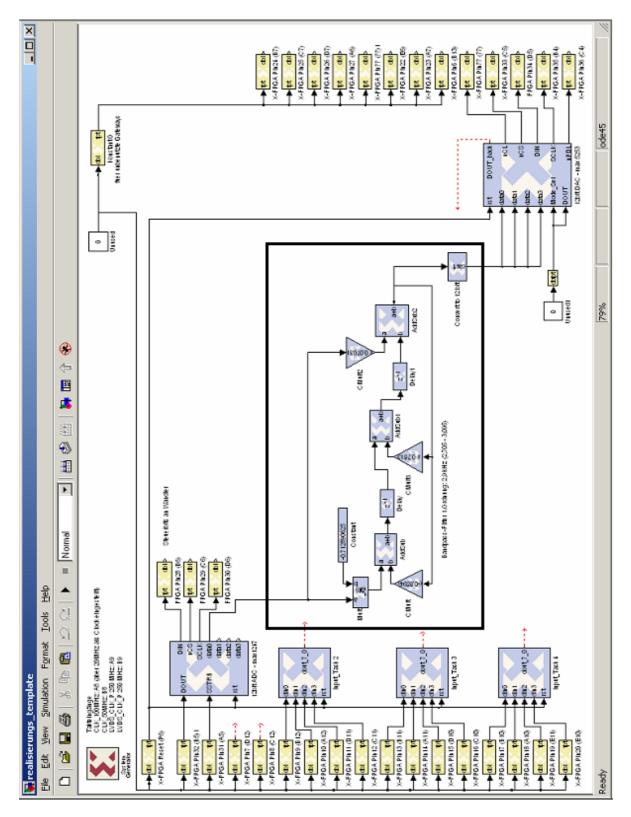

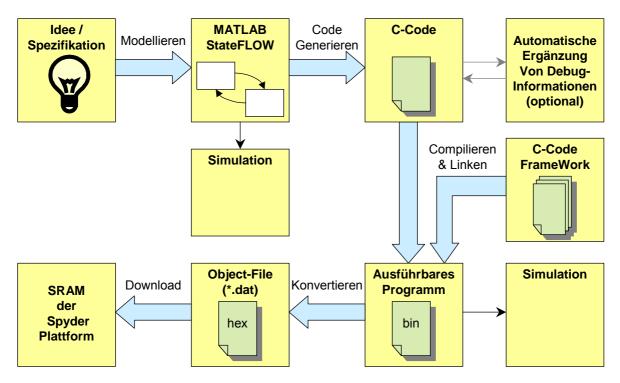

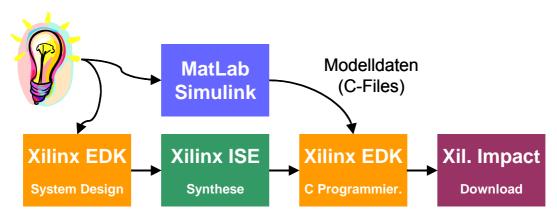

Als Alternative zu der obigen Methodik wurde ein durchgängiger Design-Flow für Funktionsimplementierungen auf den FPGAs der Interface-Karten mit Hilfe grafischer Modellbildung durch die Case-Tools MATLAB Simulink/StateFlow und Xilinx SystemGenerator realisiert. Hierbei wird aus der grafischen Repräsentierung ein Modell-Code (VHDL oder C-Code) erzeugt, der eingebettet in Hardware-/Software-Frameworks und auf IP-Prozessoren (z.B.

PPC, MicroBlaze [XMB03] und LEON [LEON01], [Gais02]) lauffähig ist. Die jeweiligen Frameworks adaptieren die verfügbaren Prozessschnittstellen und vereinfachen so die Integration auf dem FPGA erheblich.

## 1.3 Gliederung der Arbeit

Die hier vorliegende Arbeit ist in folgende Abschnitte gegliedert:

In diesem ersten Kapitel werden das Umfeld der Arbeit, sowie die daraus entstandene Motivation zur Aufgabenstellung dargestellt. Es werden außerdem die abgeleiteten Ziele und der daraus resultierende eigene Beitrag erläutert.

Kapitel 2 gibt einen Überblick über die im heutigen Kraftfahrzeug verwendete Bussysteme und Elektronikkomponenten. Außerdem wird auf den Begriff der "Eingebetteten Systeme" näher eingegangen. Aktuelle und zukünftige Trends im Bereich der Fahrerassistenzsysteme werden kurz anhand von Beispielen aufgeführt.

Kapitel 3 widmet sich dem Stand der Technik. Hier werden die für das Verständnis der Arbeit wichtigsten elektronischen Bauteile, insbesondere die programmierbaren Logikbausteine (FPGAs), sowie die verwendeten Programmiersprachen vorgestellt. Einen weiteren Schwerpunkt bilden die für die Entwicklung und den Test von Steuergeräten in der Automobilindustrie angewandten Methoden. Hier geht es im Speziellen um die Vorgehensmodelle bei der Entwicklung solcher Systeme und die Verflechtung von Rapid Prototyping (RP) und Hardware-in-the-Loop (HiL) mit den verschiedenen Lebenszyklusmodellen in diesem Zusammenhang. Die Begriffe werden dabei ausgiebig erläutert und die Einsatzgebiete und Wirkungsweisen der Methoden dargestellt.

Kapitel 4 präsentiert das aus den Anforderungen abgeleitete Konzept und dessen Umsetzung in eine kombinierte Rapid Prototyping- und Hardware-in-the-Loop-Plattform als funktionsfähige Hardware. Dabei werden sowohl das Konzept ausführlich erläutert, als auch die Realisierungsalternativen dargelegt und diskutiert. Die daraus entstandenen einzelnen Komponenten, die zum Betrieb der Plattform nötig sind, werden anschließend vorgestellt und deren Aufbau und Funktion detailliert erklärt. Außerdem wird ein für die Plattform entworfenes Sicherheitskonzept zur Fehlervermeidung thematisiert.

Die Designmethodik, mit Hilfe derer auf einfachstem Wege komplette Konfigurationsdatenströme für FPGAs durch Auswählen aus einem Menü erstellt werden können, ist Thema in Kapitel 5. Hier wird ausgehend von der eigentlichen Problematik bei der Konfiguration von FPGAs der Ansatz der Slot-basierten Konfiguration dargelegt und mit der Umsetzung der Methodik in eine funktionierende Umgebung bestehend aus VHDL-Code und einer Java-Applikation namens BitstreamComposer komplettiert.

In Kapitel 6 wird die Software-Umgebung dieser Arbeit beschrieben. Diese gliedert sich in die Steuerungs-Software zur Bedienung des Systems, die Applikationen zur Erstellung der FPGA-Konfigurationsdaten und letztlich das Betriebssystem und dessen Erweiterungen auf der Plattform selbst.

Die Anwendung und Erprobung der in dieser Arbeit entstandenen Hard- und Software-Teile wird in Kapitel 7 dargestellt. Getrennt nach Rapid Prototyping und Hardware-in-the-Loop sind verschiedene Applikationen aufgeführt, die zur Lösung dedizierter Szenarien erstellt und eingesetzt wurden.

Kapitel 8 fasst die Ergebnisse der Arbeit zusammen, zeigt die erzielten Fortschritte, aber auch die Grenzen der Arbeit auf und gibt einen Überblick über die in diesem Zusammenhang entstandenen Hardware- und Softwareteile, sowie deren Funktionen im Gesamtsystem. In einem Ausblick werden die noch nicht umgesetzten Punkte besprochen und bestehende Probleme diskutiert.

Abschließend finden sich in Kapitel 9 noch die Verzeichnisse für Abbildungen, Tabellen, Formeln, verwendete Abkürzungen und eine umfassende Literaturangabe. Die Listen mit be-

treuten Diplom-, Studien und Seminararbeiten, sowie eigenen Veröffentlichungen runden die Aufzählung ab.

## 2 Elektronik im Kraftfahrzeug

Neben der klassischen Elektrik zur Versorgung der Zünd- oder Lichtanlage mit Energie, sind im Kraftfahrzeug im Laufe der Zeit eine große Anzahl ehemals mechanischer Funktionen elektrifiziert worden. Diese Funktionen müssen umgesetzt, sowie deren einwandfreie Funktion während des Betriebs überprüft werden, um die Sicherheit der Insassen und anderen Personen zu gewährleisten. Dazu werden im Auto verschiedenste elektronische Komponenten in Form von eingebetteten Systemen eingesetzt, die diese Aufgaben übernehmen. Solche Komponenten lassen sich mit dem Oberbegriff der Kfz-Steuergeräte zusammenfassen.

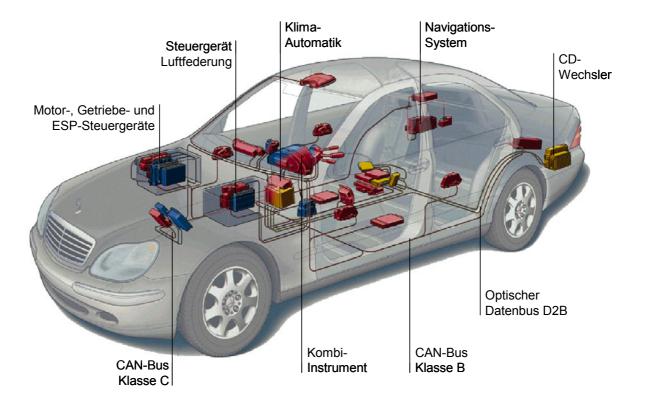

Abbildung 2.1: Steuergeräte und Busse im W220 (S-Klasse) von DaimlerChrysler

Abbildung 2.1 zeigt eine Auswahl an elektronischen Komponenten und Datenkommunikationssystemen, wie sie in heutigen Fahrzeugen zu finden sind. Der Integrationsgrad an Informationselektronik hängt dabei in erster Linie von der Fahrzeugklasse, vom Hersteller und von der vom Kunden gewählten (Sonder-) Ausstattung ab. Während in der Unterklasse Autos noch gänzlich ohne einen CAN-Bus auskommen, sind in der Oberklasse mindestens zwei verbaut und werden zusätzlich noch durch andere Kommunikationssysteme ergänzt. Auch die Verfügbarkeit von Sicherheits- und Komfortkomponenten ist in der gehobenen Kategorie eher gegeben.

## 2.1 Bussysteme im Automobil

In den heutigen Fahrzeugen werden zur Vernetzung von Steuergeräten so genannte Bussysteme eingesetzt, um Daten zu transportieren. Der noch immer zunehmende Anteil an Elektrik und Elektronik im Kraftfahrzeug und die damit einhergehende Notwendigkeit des Austausches von Informationen macht den Einsatz von hoch-performanten Kommunikationssystemen nötig. Allerdings gibt es dahingegen auch Entwicklungen zur Kostenreduktion in Bereichen, in denen Performanz eine untergeordnete Rolle spielt und es nur auf die Vernetzung ankommt (Body-Elektronik im Komfortbereich). Die einzelnen elektronischen Kontroll-/Steuersysteme (Steuergeräte) sind im gesamten Fahrzeug verteilt (siehe auch Abbildung 2.1). Die einzelnen Steuergeräte müssen in der Lage sein, Daten untereinander austauschen (z.B. benötigt die Getriebesteuerung vom Motorsteuergerät die aktuelle Motordrehzahl).

#### 2.1.1 Unterscheidung von Bustypen

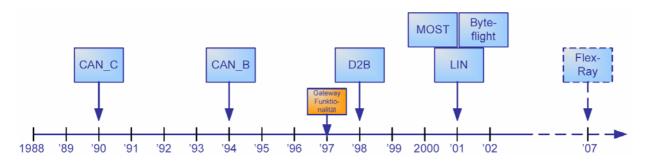

Bei der Kommunikation in modernen Fahrzeugen beschränkt man sich nicht auf ein Medium, sondern verwendet eine Vielzahl verschiedener Busse. Die Vielfalt der verschiedenen Systeme ist allerdings erst mit der Zeit entstanden, wie man in Abbildung 2.2 gut erkennen kann. Einige sind dabei mittlerweile schon an die Grenze ihrer Leistungsfähigkeit gestoßen, so dass die Erforschung und die Entwicklung neuer Technologien zum Datentransport intensiv vorangetrieben wird.

Abbildung 2.2: Etablierung von Kommunikationssystemen im Automobil

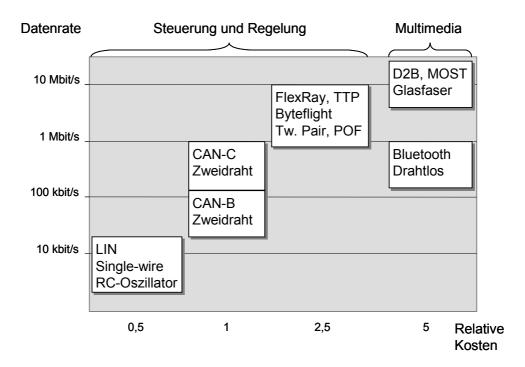

Die Bussysteme bedienen entsprechend ihrer Leistungen und Merkmale unterschiedliche Einsatzgebiete und variieren dadurch aber auch stark in Komplexität, Aufbau und Protokoll. Je nach Anforderung und Leistungsbedarf der jeweiligen Applikation (meist gemessen in der Übertragungsgeschwindigkeit) und den Kosten zur Realisierung einer Funktion werden die derzeit gängigsten Typen unterschieden. Ein weiteres Merkmal stellt auch das Übertragungsmedium dar, d.h. ob die Signalisierung über Draht, einen optischen Leiter – wie z.B. POF (Plastic Optical Fiber) – oder durch einen Funkkanal erfolgt.

Abbildung 2.3 zeigt eine Übersicht und einen Vergleich der aktuellen Bussysteme und - protokolle im Kraftfahrzeug. Es wird dabei zwischen Übertragungsgeschwindigkeit und Kosten je Netzknoten unterschieden.

Abbildung 2.3: Aktuell im Automobil eingesetzte Bussysteme

Der nun folgende Abschnitt soll einen Überblick über die gängigen, heute im Kraftfahrzeug verwendeten Bussysteme geben und deren wichtigste Grundlagen zusammenfassen, die für das Verständnis der folgenden Kapitel notwendig sind. Für weitere Details sei an dieser Stelle auf sekundäre Literatur verwiesen, zum Beispiel [Schü97].

#### 2.1.1.1 Topologien

Unter dem Term Topologie wird die Verbindungsstruktur eines Netzwerks verstanden. Es beschreibt die räumliche Anordnung des Verbindungsnetzwerks zum Transport von Nachrichten und Daten zwischen den einzelnen Teilnehmern.

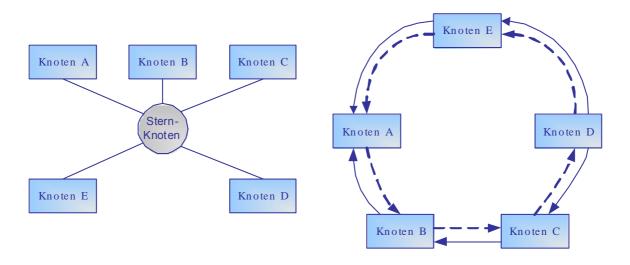

Bei der Stern-Topologie sind alle Knoten eines Clusters über einen so genannten Stern-knoten miteinander verbunden (Abbildung 2.4). Zwischen Sternknoten und den einzelnen Busknoten besteht eine Punkt-zu-Punkt-Verbindung. Die Stern-Topologie ist einfach zu verwalten und problemlos erweiterbar. Der einzige Nachteil dieser Realisierung besteht darin, dass beim Ausfall des Sternknotens das gesamte Netz lahm gelegt ist.

Für Netze, die als Ringe ausgeführt sind, gibt es zwei Arten der Realisierung, den Einfachring und den Doppelring (Abbildung 2.5). Beim Einfachring läuft die Kommunikation über einen Zyklus von Punkt-zu-Punkt-Verbindungen. Der Anschluss erfolgt über einen Ringkoppler (nicht im Bild zu sehen). Bei Doppelringen hat jeder Knoten die Möglichkeit in beide Richtungen über jeweils separate Leitungen im Ring zu senden. Die dadurch entstehende Redundanz ermöglicht den Busbetrieb bei Ausfall einer Ringleitung.

Bei Netzen, die als Bustopologie realisiert sind, werden die Knoten über eine gemeinsame Leitung miteinander verbunden (Abbildung 2.6). Der Anschluss jedes Teilnehmers erfolgt über eine Stichleitung. Die Kommunikation über nur eine Leitung impliziert eine aufwendige Kollisionsverwaltung, um einen reibungslosen Datenaustausch zu realisieren.

Abbildung 2.4: Stern-Topologie

Abbildung 2.5: Ring-Topologie

Abbildung 2.6: Bus-Topologie

#### 2.1.1.2 Übertragungsverfahren

Bei der Datenübertragung auf einem Kanal kann hinsichtlich Datenrichtung und Grad der Parallelität unterschieden werden. Bei der Übertragungsrichtung gibt es das Simplex-Verfahren (in eine Richtung) und Halb-/Duplex-Verfahren (in beide Richtungen).

Beim Raummultiplex-Verfahren werden die zu übertragenden Signale auf mehrere Leitungen verteilt. Daraus resultiert die direkte Abhängigkeit der Datenübertragungsrate von der Anzahl der Leitungen – d.h. je mehr parallele Leitungen zur Verfügung stehen, desto mehr Daten können gleichzeitig übertragen werden.

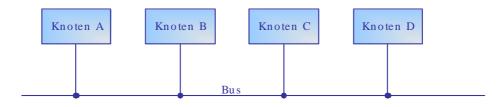

Abbildung 2.7: TDMA-Verfahren

Abbildung 2.8: FDMA-Verfahren

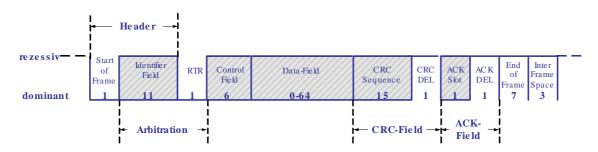

Das Zeitmultiplex-Verfahren (Time Division Multiple Access = TDMA) teilt jedem Sendeteilnehmer (Knoten) einen genau definierten Zeitabschnitt eines Sendezyklus zu (Abbildung 2.7). Innerhalb dieses Slots darf der entsprechende Knoten Daten auf dem Bus übertragen.

Beim Frequenzmultiplex-Verfahren (Frequency Division Multiple Access = FDMA) wird das Frequenzband in Bereiche aufgeteilt, die von den Busteilnehmern zur Datenübertragung genutzt werden können (Abbildung 2.8). Zwischen den einzelnen Bändern ist ein Abstand einzuhalten, um Interferenzen zwischen den Bändern zu vermeiden.

Die zu übertragenden Signale breiten sich innerhalb der Leiter wellenförmig aus. Es existiert immer eine hinlaufende Welle und ggf. auch eine rücklaufende (reflektierte) Welle. Um die Reflektion am Leitungsende möglichst gering zu halten, ist ein Abschlusswiderstand  $Z_0$  (Terminierung) anzubringen.

#### 2.1.1.3 Cyclic Redundancy Check

Der Cyclic Redundancy Check CRC dient zur Fehlererkennung der nach einer Übertragung empfangenen Daten. Dieses Verfahren ist wesentlich effektiver als das Hinzufügen eines Paritätsbits an das Ende einer Sendesequenz. Das CRC-Verfahren basiert auf der Modulo-Zwei-Arithmetik. Dabei werden aber keine Überträge verwendet. Es entspricht also einer XOR-Operation.

$0100010 + 1010111 \equiv 0001010$

Formel 2.1: Beispiel einer CRC-Code-Berechnung (XOR)

Je nach Busprotokoll werden entweder nur das Nachrichtenfeld oder Teilbereiche einer Botschaft von einem oder mehreren CRC-Feldern abgesichert. Die Darstellung der Bitstrings erfolgt durch Polynome. Jede Stelle eines Bitstrings, welche eine Eins enthält wird durch das entsprechende ni repräsentiert (i steht für eine Stelle innerhalb des Bitstrings).

$$01101101 \rightarrow p(n) = n^6 + n^5 + n^3 + n^2 + 1$$

Formel 2.2: Beispiel für ein Polynom zur CRC-Berechnung

Durch ein so genanntes Generatorpolynom G(n) wird beim Sender eine Prüfsumme erzeugt und mit übertragen. Der Empfänger überprüft anhand der Prüfsumme und des gleichen Generatorpolynoms G(n), ob die Daten korrekt übertragen wurden. Folgende Fehler können mit der Hilfe des CRC-Verfahrens erkannt werden:

- Einzelbitfehler

- Zwei Einzelbitfehler, wenn (n<sup>k</sup>+1) nicht durch das Generatorpolynom teilbar ist (k ≤ Rahmenlänge)

- Ungerade Anzahl von Bitfehlern, wenn G(n) den Faktor (n+1) enthält

- Alle Fehler-Bursts = Grand des Generatorpolynoms G(n)

#### 2.1.2 Controller Area Network (CAN-Bus)

Das Controller Area Network (CAN) wurde 1981 von den Firmen BOSCH und Intel entwickelt und in der ISO 11898 als ein asynchrones serielles Bus-System mit einer logischen Busleitung definiert [Bosc]. Als Kommunikationsnetzwerk zum Datenaustausch einfacher Prozesse wurde es ursprünglich im Komfortbereich und im Motormanagement bei Kraftfahr-

zeugen eingesetzt, findet heute aber auch Anwendung in der Gebäude- und Produktionsautomatisierung.

Abhängig vom Datenaufkommen und zeitlichen Anforderungen unterscheidet man drei Arten von CAN-Systemen, wie sie in der folgenden Tabelle 2.1 zusammengefasst sind:

| Klasse | Bezeichnung         | Baudrate          |

|--------|---------------------|-------------------|

| CAN-C  | High-Speed CAN      | bis zu 1 MBit/s   |

| CAN-B  | Low-Speed CAN       | bis zu 125 kbit/s |

| CAN-A  | Super Low-Speed CAN | bis zu 10 kbit/s  |

Tabelle 2.1: Klassifizierung von CAN-Bussen

#### 2.1.2.1 Eigenschaften

Der CAN-Bus basiert auf einer Bustopologie und einer Multimaster-Architektur mit bitserieller Datenübertragung. Die Busarbitrierung erfolgt durch das CSMA/CD-Verfahren (Carrier Sense Multiple Access/Collision Detect). Über den Identifier wird die Nachrichtenpriorisierung vorgenommen – dabei hat der niedrigste Wert die höchste Priorität. Die Daten werden NRZ-codiert inklusive Bitstuffing. Die Datenkonsistenz wird über ein 15Bit großes CRC-Feld und einer Hamming-Distanz von 6 sichergestellt.

Als Übertragungsmedium dient eine abgeschirmte, verdrillte Zweidrahtleitung. Die Ansteuerung erfolgt über einen differentiellen Spannungspegel, der mit Hilfe eines Transceiver-Bausteins (Buskoppler) erzeugt wird. Die Transceiver basieren auf dem Prinzip der symmetrische RS-485-Schnittstellen, von denen je einer an jedem einzelnen Busteilnehmer benötigt wird.

Beim CAN-Bus (Class C) kann nominell eine Datenübertragungsrate von bis zu 1Mbit/s erzielt werden. Durch den Protokoll-Overhead sind reell jedoch nur bis maximal 500kbit/s möglich. Eine weitere Einschränkung, d.h. Reduktion der Übertragungsrate, ergibt sich bei steigender Leitungslänge und einer Erhöhung der Buslast.

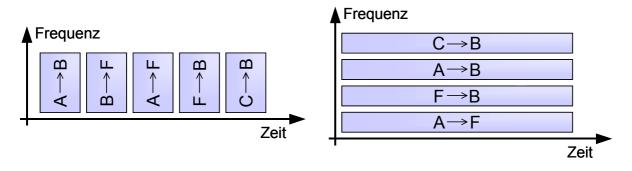

Unterstützt werden verschiedene Nachrichtentypen: Daten-, Remote-, Error- und Overload-Nachrichten. Jede Nachricht enthält mindestens ein SOF-Bit (Start-of-Frame) und einen Identifier. Das Maximum der in einem Rahmen (Frame) zu übertragenden Daten sind 8 Byte. In Abbildung 2.9 ist der Aufbau einer CAN-Botschaft dargestellt.

Abbildung 2.9: Aufbau einer CAN-Botschaft

Für genauere Informationen zum CAN-Bus sei an dieser Stelle auf die CAN-Spezifikation 2.0 der Firma Bosch verwiesen [Bosc91]. Diese kann kostenlos von deren Internet-Seite heruntergeladen werden. Außerdem finden sich weitere Details zum CAN-Bus und dessen Einsatz in [Law97], [Enge00], [Etsc01], [Lawr02], [Etsc02], sowie auf der Webseite der Organisation CAN-in-Automation [CiA06]. Letztere bietet auch Dienstleistungen und Literatur zu

auf CAN basierenden Systemen und Protokollen. Die Steckerbelegung nach Tabelle 2.2 wurde ebenfalls von der CiA standardisiert.

| Pin | Signal | Beschreibung                           |  |

|-----|--------|----------------------------------------|--|

| 1   | -      | reserviert                             |  |

| 2   | CAN-L  | CAN-L                                  |  |

| 3   | GND    | Masse                                  |  |

| 4   | -      | reserviert                             |  |

| 5   | -      | reserviert                             |  |

| 6   | (GND)  | Masse (optional)                       |  |

| 7   | CAN-H  | CAN-H                                  |  |

| 8   | -      | reserviert (error line)                |  |

| 9   | (V +)  | externe Versorgung 7V - 13V (optional) |  |

Tabelle 2.2: CAN-Steckerbelegung nach DIN 41652 (CiA/DS 102-1)

#### 2.1.3 Local Interconnect Network (LIN)-Bus

Das Local Interconnect Network (LIN) wurde 1989 als einfaches Bussystem von den Automobilherstellern Audi, BMW, DaimlerChrysler sowie dem Chiphersteller Motorola und dem schwedischen Softwarehersteller Volcano spezifiziert. Mittlerweile gehören dem Konsortium noch weitere Firmen an. Nach der Einführung [LINS13] erfolgte eine kontinuierliche Weiterentwicklung und Verbesserung bis zum heutigen Stand. Mit der Revision 2.0 [LINS20] steht ein ausgereiftes und voll funktionsfähiges Busprotokoll zur Verfügung.

#### 2.1.3.1 Eigenschaften

Das Bussystem LIN basiert ebenfalls auf der Bustopologie mit bitserieller Übertragung der Daten. Ein LIN-Bussystem besteht aus einem Masterknoten und einem bis 16 Slave-Knoten. Die gesamte Kommunikation wird vom Master-Knoten aus gesteuert, so dass die Slave-Knoten sehr einfach zu realisieren sind. Die Übertragungssequenz wird in so genannten Schedule Tables organisiert. Darin erfolgt die Festlegung, in welcher Reihenfolge der Master Nachrichten an die Slaves sendet oder entsprechende Sendeanforderungen schickt. Ein Slave-Knoten darf nicht von sich aus Nachrichten auf den Bus zu legen. Dieser kann erst eine Nachricht an den Master und/oder an ein oder mehrere Slaves senden, wenn dieser die entsprechende Anforderung vom Master-Knoten empfangen hat.

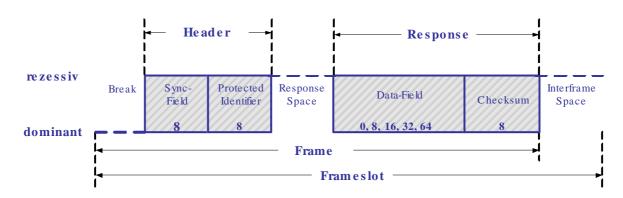

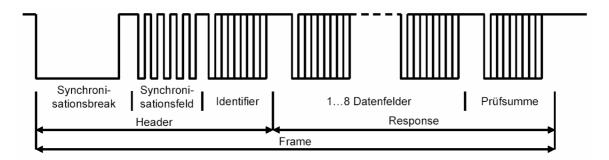

Abbildung 2.10: Aufbau einer LIN-Botschaft

Die Übertragung der Daten erfolgt zur Einsparung von Kosten NRZ-codiert über eine Eindrahtleitung (Bezugspunkt ist Masse). Zur Wahrung der Datenkonsistenz kommen verschiedene Sicherheitsmechanismen zum Einsatz. Das Identifier-Feld enthält ein zwei Bit großes Parity-Feld im Anschluss an den 6Bit langen Identifier. Im Anschluss an das Datenfeld wird eine 8Bit große Checksumme angehängt. Die einzelnen Busknoten werden über eine erweiterte UART/SCI-Schnittstelle an den Bus angekoppelt. Zur Übertragung steht eine maximale Geschwindigkeit von 20kbit/s zur Verfügung. Empfohlen werden die Geschwindigkeiten 2400, 9600 und 19200kbit/s.

Insgesamt kommen fünf verschiedene Nachrichtentypen zum Einsatz: Sporadische, ereignisgesteuerte, zyklische, diagnose- und benutzerdefinierte Nachrichten. Eine Nachricht setzt sich, wie in Abbildung 2.10 dargestellt, zusammen.

Für genauere Informationen zum LIN-Bus sei an dieser Stelle auf die LIN-Spezifikation 2.0 verwiesen, die kostenlos von der Internet-Seite des LIN-Konsortiums heruntergeladen werden kann (URL: www.lin-subbus.org). Außerdem finden sich weitere Details in [Atme05], [Grze03a] - [Grze04c], [LINS13] und [LINS20].

#### 2.1.4 Media Oriented System Transport (MOST)-Bus

Das Kommunikationssystem MOST (Media Oriented System Transport) wurde ursprünglich von BMW entwickelt. Parallel dazu führte DaimlerChrysler das Multimedia-Bussystem D2B ein. Im Jahr 1998 gründeten die beiden Automobilhersteller gemeinsam mit den Zulieferern Harmann/Becker und OASIS Systems das MOST-Konsortium, um einen gemeinsamen Standard für Multimedia-Anwendungen im Automobil zu schaffen.

#### 2.1.4.1 Eigenschaften

Für MOST-Netzwerke stehen verschiedene Realisierungsvarianten zur Verfügung – Punkt-zu-Punkt-Verbindung, Stern- und Ring-Topologie. Die Datenübertragung auf der physikalischen Schicht erfolgt auf einem optischen Medium, z.B. Glasfaser oder POF (Plastic Optical Fiber). Das Einkoppeln der Daten geschieht über einen Electrical Optical Converter (EOC) mit einer Lichtquelle der Wellenlänge von 650nm. Dies hat zur Folge, dass die Übertragungsstrecke bei einer maximalen Datenrate von bis zu 24Mbit/s auf 250m begrenzt ist. MOST unterstützt sowohl synchrone (bis zu 24Mbit/s) als auch asynchrone (bis zu 14Mbit/s) Datenübertragungen.

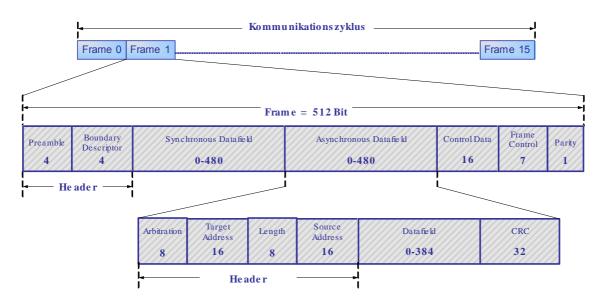

Abbildung 2.11: Aufbau eines MOST-Frames

Eine MOST-Botschaft wird als Frame bezeichnet. Jeder Frame enthält einen Header, ein synchrones sowie ein asynchrones Datenfeld und ein Kontrollfeld. Die Absicherung der Daten wird über ein CRC-Feld, sowie ein Paritätsfeld erledigt. In Abbildung 2.11 ist der Aufbau einer MOST-Botschaft dargestellt.

Für weitere Informationen sei an dieser Stelle auf den Internetauftritt des Konsortiums verwiesen (www.mostconsortium.com).

#### 2.1.5 FlexRay-Bus

Im Jahre 1999 haben die BMW AG und die DaimlerChrysler AG zusammen mit den Halbleiterherstellern Motorola und Philips das FlexRay-Konsortium zur Entwicklung einer neuartigen Kommunikationstechnologie gegründet. Als weitere Mitglieder traten Bosch, General Motors, Volkswagen und Siemens VDO dem Konsortium bei. Das Ziel war und ist die Entwicklung eines echtzeitfähigen, deterministischen und fehlertoleranten Kommunikationssystems. Wie in Abbildung 2.2 dargestellt, soll(te) die Einführung von FlexRay im Jahre 2007 erfolgen und das System danach verstärkt eingesetzt werden. Neueste Entwicklungen zeigen, dass die Etablierung von FlexRay noch einige Jahre benötigen wird und erst nach einer intensiven Evaluierungsphase der Hersteller erfolgt.

#### 2.1.5.1 Eigenschaften

Der eigentliche Grund zur Entwicklung von FlexRay war der geplante Einsatz im Bereich der X-by-Wire-Systeme. Hier werden schnelle und vor allem aber zeitlich deterministische Datenübertragungen verlangt. Doch inzwischen sind viele weitere Anwendungsbereiche hinzugekommen. FlexRay kann in Teilbereichen CAN ablösen und als Grundlage für eine zukünftige Backbone Vernetzungstopologie im Automobil eingesetzt werden. FlexRay bietet eine Reihe von Eigenschaften, die von den bisher im Automobil eingesetzten Kommunikationssystemen nicht abgedeckt werden. Die wesentlichen Eigenschaften von FlexRay sind [DeEl05]:

- Datenrate (10MBit/s)

- Synchronisierte Zeitbasis

- Bekannte Nachrichtenlaufzeit mit garantierter Varianz

- Redundante und nicht redundante Kommunikation (Ein- oder Zweikanalübertragung)

- Flexibilität in Redundanz, Verfügbarkeit, Durchsatz und Vernetzungstopologien

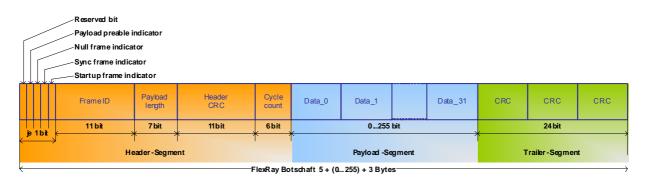

Eine FlexRay-Botschaft setzt sich aus drei Teilen zusammen: Einem Header-Segment, einem Payload-Segment und einem Trailer-Segment. Ein Netzknoten sendet eine Botschaft immer genau mit diesem Aufbau. In Abbildung 2.12 ist der Aufbau einer FlexRay-Botschaft detailliert aufgezeigt.

Abbildung 2.12: Datenformat einer FlexRay-Botschaft

Das Header-Segment besteht aus 5 Bytes und dient der Qualifizierung der Daten des Palyload-Segments, zur richtigen Erkennung und Behandlung der Botschaft im Empfänger. Das Payload-Segment enthält die eigentlichen Nutzdaten und kann Längen zwischen 0 und 254 Bytes besitzen. Die einzelnen Bytes des Datenfeldes werden immer von links nach rechts durchnummeriert, beginnend mit dem Data\_0 Byte bis zum Data\_n Byte. Das Trailer-Segment hat eine Länge von drei Bytes (24Bit) und enthält nur einen Datensatz, den CRC-Frame. Dieser dient zur Prüfung auf Korrektheit der Daten des vorangegangenen Payload-Segments. Die Prüfsumme wird über folgendes Polynom untersucht:

$$x^{24} + x^{22} + x^{20} + x^{19} + x^{18} + x^{16} + x^{14} + x^{13} + x^{11} + x^{10} + x^8 + x^7 + x^6 + x^3 + x + 1$$

=  $(x+1)^2 \cdot (x^{11} + x^9 + x^8 + x^7 + x^5 + x^3 + x^2 + x + 1) \cdot (x^{11} + x^9 + x^8 + x^7 + x^6 + x^3 + 1)$

Formel 2.3: Berechnung der CRC-Prüfsumme für das Payload-Segment

Für weitere Informationen sein an dieser Stelle auf die FlexRay Protocol Specification 2.1 verwiesen [Flex05].

#### 2.1.6 Time Triggered Protocol (TTP/C)

Das Time Triggered Protocol (TTP) wurde von der Firma TTTech 1998 auf den Markt gebracht. Es wurde für den Einsatz in sicherheitskritischen Bereichen entwickelt, hier hauptsächlich für die Automobilindustrie. Das Protokoll setzt auf der Time Triggered Architecture (TTA) auf und ist ein fehlertolerantes Echtzeitprotokoll.

#### 2.1.6.1 Eigenschaften

Bei TTA stehen verschiedene Netztopologien zur Verfügung. Es können Netzsegmente in Bustopologie oder als Sterne realisiert werden. Weiterhin sind auch Mischformen beider Topologien zulässig. Die Knoten werden immer über zwei replizierte Kommunikationskanäle verbunden. Die Übertragungsgeschwindigkeit hängt von den verwendeten Bustreibern und der Vernetzungstopologie ab. Im besten Fall kann diese bis zu 10MBit/s betragen.

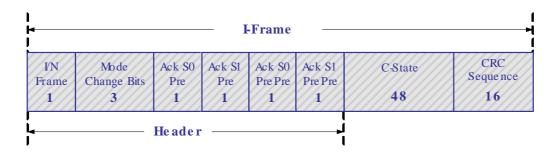

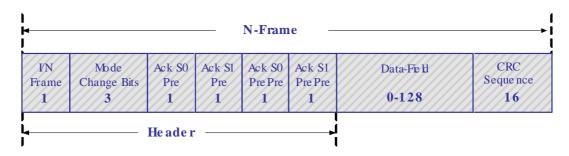

Bei TTP kommen zwei Botschaftsformate zum Einsatz: Der N-Frame (Abbildung 2.14) und der I-Frame. Der I-Frame dient zur Initialisierung. Innerhalb des C-State-Feldes wird der Zustand des Controllers übertragen. Der N-Frame (Abbildung 2.13) wird zur Datenübertragung verwendet. Die Datenkonsistenz einer Botschaft wird durch ein zwei Byte großes CRC-Feld gesichert.

Abbildung 2.13: Botschaftsformat eines I-Frames

Abbildung 2.14: Botschaftsformat eines N-Frames

Für genauere Informationen zu TTP/C und der TTP-Spezifikation finden sich auf der Internet-Seite der Firma TTTech (URL: www.tttech.com/technology/specification.htm).

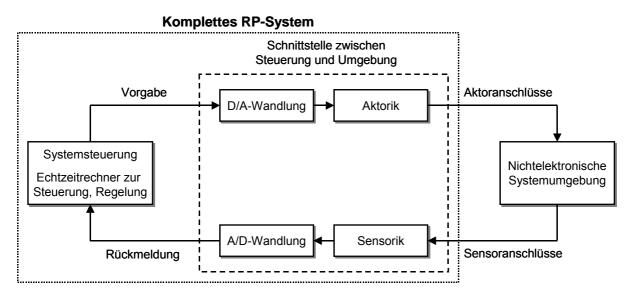

## 2.2 Eingebettete Systeme

Der Begriff Eingebettetes System (englisch: Embedded System) bezeichnet im Allgemeinen ein Rechnersystem, das in ein technisches Gerät zu Lösung komplexer Steuerungs-, Regelungs- oder Datenverarbeitungsaufgaben eingebaut (eingebettet) ist. Das System ist dabei meist nach außen nicht zu erkennen und wird daher vom Benutzer selten als solches wahrgenommen. Die Komponenten, meist Mikrocontroller oder Mikroprozessoren mit entsprechenden weiteren peripheren elektronischen Bauelementen eingesetzt, werden auf einer Platine integriert und mit Sensoren und Aktoren mit dem technischen Gerät, in das sie eingebaut sind, verbunden. Die zur Steuerung oder Regelung des Gerätes nötigen Informationen (Temperatur, Druck, Füllstand, (Winkel-) Geschwindigkeit, Drehzahl, usw.) werden zyklisch über Sensoren eingelesen und teilweise durch Eingaben des Benutzers ergänzt. Über eine in dem Prozessor oder Controller ablaufende Software werden die berechneten Daten über die Aktoren nach außen weitergegeben, d.h. wieder in physikalische Größen gewandelt.

#### 2.2.1 Einsatzgebiete

Da eingebettete Systeme in den meisten Fällen weitestgehend unsichtbar in Geräten, Maschinen und Apparaturen verbaut sind, pflegt der Benutzer einen selbstverständlichen Umgang mit diesen Systemen, ohne davon Kenntnis zu haben. Der Einsatzzweck kann dabei verschiedene Gründe haben: Vereinfachung der Handhabung, Erledigung stupider Routinearbeiten, Bearbeitung präziser und lange anhaltender Tätigkeiten oder die Verknüpfung komplexer Aufgaben in kurzer Zeit. Mindestens einer dieser Gründe trifft bei allen technischen Geräten des täglichen Gebrauchs zu, wie z. B. in Kaffeemaschinen, Wasch- und Spülmaschinen, Mobiltelefonen, Fernsehgeräten, MP3-Playern, elektronischem Kinderspielzeug, usw. – um nur eine kleine Auswahl zu nennen. Aber auch bei komplexen Gesamtsystemen, z.B. im industriellen Umfeld, werden eingebettete Systeme eingesetzt. Ein weiteres und wichtiges Einsatzgebiet eingebetteter Systeme stellt natürlich der Kraftfahrzeugbereich dar, wobei diese dort als Steuergeräte bezeichnet werden. Die Namensgebung ist etwas unglücklich gewählt, da die meisten Rechnersysteme im Kfz nicht nur steuern, sondern Prozesse regeln.

#### Definition einer Steuerung (DIN 19226):

Die Steuerung, ist der Vorgang in einem System, bei dem eine oder mehrere Größen als Eingangsgrößen andere Größen als Ausgangsgrößen aufgrund der dem System eigentümlichen Gesetzmäßigkeiten beeinflussen. Kennzeichen für das Steuern ist der offene Wirkungsweg oder ein geschlossener Wirkungsweg, bei dem die durch die Eingangsgrößen beeinflussten Ausgangsgrößen nicht fortlaufend und nicht wieder über die selben Eingangsgrößen auf sich selbst wirken.

#### Definition einer Regelung (DIN 19226):

Die Regelung ist ein Vorgang, bei dem fortlaufend eine Größe, die Regelgröße (die zu regelnde Größe) erfasst, mit einer anderen Größe, der Führungsgröße, verglichen und im Sinne einer Angleichung an die Führungsgröße beeinflusst wird. Kennzeichen für das Regeln ist der geschlossene Wirkungsablauf, bei dem die Regelgröße im Wirkungskreis des Regelkreises fortlaufend sich selbst beeinflusst.

#### 2.2.2 Vernetzung

Eingebettete Systeme können autonom arbeiten oder auch im Verbund mit anderen Systemen gleicher oder ähnlicher Bauart zur Lösung einer Gesamtaufgabe ([Bosc02], [CiA06]). Dazu müssen die einzelnen Systeme miteinander verbunden sein, um untereinander kommunizieren, also Daten austauschen zu können. Dies geschieht über definierte Schnittstellen und Protokolle unter Verwendung drahtgebundener Medien (zum Beispiel CAN-Bus oder TCP/IP über Ethernet) oder über Funk (WLan, Bluetooth oder ZigBee). Mitunter kommen auch Glasfaserverbindungen als Kommunikationsmedium zum Einsatz, wenn es sich um EMV-kritische Applikationen (Flugzeug, Auto) handelt oder hohe Übertragungsraten gefordert sind (MOST-Bus im Auto).

## 2.3 Anforderungen an Eingebettete Systeme im Kfz

Je nach Einsatzbereich werden unterschiedliche Anforderungen an das oder die eingebetteten Systeme gestellt. Das Automobil bietet dafür eine der anspruchsvollsten Umgebungen, die es zu beherrschen gilt. Es gehört zu der Gruppe der sicherheitskritischen Systeme, da Menschen darin befördert werden, hat nur eingeschränkte Energiereserven zur Verfügung und ist Umwelteinflüssen ausgesetzt. Die eingesetzten elektronischen Komponenten müssen daher auch unter ungünstigsten äußeren Bedingungen zuverlässig arbeiten.

#### 2.3.1 Umgebungseinflüsse

Elektronische Systeme im Auto sind teilweise Umwelteinflüssen ausgesetzt, die bei der Entwicklung mit eingeplant werden müssen. Eine der wichtigsten und einflussreichsten Größen ist die Temperatur. Je nach Einsatzort, Jahreszeit und Wetter können in extremen Situationen zwischen –40°C und +200°C auftreten [VDE06]. Tabelle 2.3 zeigt einige Beispiele von Extremtemperaturen, klassifiziert nach Einbauorten im Fahrzeug.

| Bauraum      |                    | Temperatur |       |

|--------------|--------------------|------------|-------|

|              |                    | Min.       | Max.  |

| Motorraum    | Drosselklappe      | -40°C      | 204°C |

|              | Ansaugrohr         | -40°C      | 121°C |

|              | Spritzwand         | -40°C      | 141°C |

| Fahrwerk     | Isolierte Bereiche | -40°C      | 84°C  |

|              | An Wärmequellen    | -40°C      | 121°C |

|              | Antriebsstrang     | -40°C      | 177°C |

| Außenbereich | Beliebig           | -40°C      | 113°C |

| Innenraum    | Armaturenbrett     | -40°C      | 84°C  |

|              | Dachhimmel         | -40°C      | 113°C |

| Kofferraum   | Beliebig           | -40°C      | 84°C  |

Tabelle 2.3: Extremtemperaturen nach Einbauräumen gemäß SAE-Standard J1211

Hinzu kommen weitere Faktoren wie chemische Substanzen (heißes, tropfendes Öl, aufgewirbeltes Salzwasser im Winter oder Treibstoffgase), die das Gehäuse nicht beschädigen und vor allem nicht in dasselbe eindringen dürfen, mechanische Einwirkungen durch starke Vibration und Beschleunigungen sowie Störungen des Spannungsversorgungsnetzes im Fahrzeug. Im Zuge der Fahrzeugvernetzung durch Funkverbindungen sind die Steuergeräte auch elektromagnetischen Störungen ausgesetzt.

#### 2.3.2 Zeitbedingungen

Eingebettete Systeme müssen insbesondere im Auto (z.B. beim Motormanagement) Echtzeitanforderungen genügen [Bosc01], [Sens01], [Bosc02], [Just04]. Dies bedeutet, dass innerhalb einer bestimmten Zeitspanne die Neuberechnung eines Ausgabewertes erfolgt sein muss. Das schließt z.B. das Einlesen eines Sensorwertes, die Berechnung und die Ausgabe ein. Bei solchen Anwendungen werden Betriebssysteme eingesetzt, mit deren Hilfe eine zeitgesteuerte Abarbeitung der Funktionen eingehalten und so die Echtzeitfähigkeit garantiert werden kann. In der Regel arbeitet man mit Echtzeitbetriebssystemen wie VxWorks, Nucleus, OSEK, OS-9 usw., die für den Einsatz in Rechnersystemen mit eingeschränkten Ressourcen optimiert sind. Allerdings finden auch spezielle eingebettete Versionen von Standardbetriebssystemen wie Linux (Embedded Linux), NetBSD oder Windows (CE, XP Embedded, Automotive oder Embedded for PoS) inzwischen weitere Verbreitung. Sind die Systeme sehr klein, kann im Zweifel auch auf ein Betriebssystem völlig verzichtet werden, da die Existenz eines solchen, unnötigen Speicherplatz belegen und Rechenzeit beanspruchen würde, ohne wesentliche Vorteile durch ein strukturiertes Task-Scheduling, d.h. das kontrollierte Abarbeiten von Programmteilen, zu erbringen.

## 2.4 Aktuelle und zukünftige Trends im Automobil

#### 2.4.1 Reduktion von Steuergeräten - Verteilte Funktionen

Mit dem verstärkten Einsatz von eingebetteten Systemen (Steuergeräten) in Automobilen tritt derzeit ein weiteres Problem zu Tage. Die Anzahl der Systeme ist inzwischen so hoch, dass neben den geringen Platzressourcen und des erhöhten Verdrahtungsaufwands, vor allem der Kommunikationsbedarf immens ansteigt. Daher geht man in neuen Steuerungen dazu über, mehrere Funktionen in einem Steuergerät zu vereinen. Dabei wird nicht wie bisher, lediglich eine dedizierte Funktion auf ein Steuergerät abgebildet, sondern versucht, diese auf mehrere innerhalb des Verbunds zu verteilen.

Dies hat zum einen den Vorteil, dass die Ressourcenanforderungen besser an den Bedarf angepasst werden können und zum anderen bei möglichen Ausfällen eines Steuergeräts, andere Systemteile diese Aufgabe wahrnehmen können. Eine Teilung in hochperformante Funktionen des Motormanagements und der Getriebesteuerung und weniger zeitkritischen Innenraumfunktionen wird dabei aber weiterhin erhalten bleiben. So wäre es beispielsweise denkbar, dass Teile der Lichtsteuerung und der Klimaregelung auf einem Steuergerät implementiert werden.

#### Definition: Funktionen im Auto

Eine Funktion im Auto ist eine von einer elektrischen oder elektronischen Komponente ausgeführte Aktion, die der Sicherheit, der Unterhaltung, der Information oder der Bequemlichkeit dient. Sie kann entweder vom Fahrer selbst ausgelöst werden (Blinker, Fensterheber, Sitzverstellung, Lüftung, ...) oder autonom, d.h. ohne Zutun eines Benutzers, selbständig agieren (Motorsteuerung, Getriebesteuerung, etc.).

#### 2.4.2 Fahrerassistenzsysteme

Fahrerassistenzsysteme wurden und werden entwickelt, um den Fahrer während der Fahrt zu unterstützen und dadurch zu entlasten. Hinsichtlich ihrer Wirkung unterscheidet

man zwei Kategorien. Passive Systeme, die nur zur Information dienen und aktive, die in das Fahrgeschehen eingreifen können.

Zu der Gruppe der passiven Systeme zählen z.B. das Human Machine Interface (Mensch-Maschine-Schnittstelle) und die Verkehrsschildererkennung (Traffic Sign Recognition). Beispiele für aktive Systeme sind die Abstandsregelung (Adaptive Cruise Control), der darauf aufbauende Stauassistent (Traffic Jam Assist) und der Einparkassistent (Park Assist). Letztere sind außerdem sicherheitskritische Systeme, da sie entscheidend für die Sicherheit des Gesamtsystems – hier des Fahrzeugs – und der Insassen Verantwortung tragen.

Definition: Sicherheitskritische Systeme

Sicherheitskritische oder auch sicherheitsrelevante Systeme bezeichnen Systeme, welche die Sicherheit einer Anlage garantieren bzw. sie unterstützen, d.h. die Unversehrtheit von Personen in deren Aktionsbereich gewährleisten. Im Auto sind das Systeme, die – wie oben bereits genannt – aktiv in das Fahrgeschehen eingreifen, wie X-by-Wire, ABS, ESP, ACC, etc. und bei Fehlfunktionen die Sicherheit der Insassen gefährden können.

## 3 Stand der Technik

Nach der Einführung in die Materie und der Vorstellung des Umfeldes, soll hier nun der Stand der Technik dargelegt werden. Ein besonderer Schwerpunkt liegt dabei auf den feldprogrammierbaren Logikbausteinen (Field Programmable Gate Array, FPGA) und deren Programmierung bzw. Konfigurierung. Alle weiteren Kapitel decken die Grundlagen, die zur Konzeptionierung, Entwicklung und dem Aufbau der Hardware-Plattformen und Software-Applikationen des RP-HiL-Testsystems benötigt wurden, ab. Außerdem wird auf die Methoden und Werkzeuge, sowie die kommerziellen Systeme, die bei der Entwicklung und dem Test eingebetteter elektronischer Systeme im Bereich der Automobilindustrie eingesetzt werden, eingegangen.

Einschränkend muss hier aber bereits erklärt werden, dass nicht alle Details, die während der Entwicklung einer solchen kombinierten Hardware- und Software-Lösung berücksichtigt werden müssen, behandelt werden können. Die erschöpfende Darstellung der Themen und Überlegungen würde durch Umfang und Komplexität den Rahmen der Arbeit sprengen. Der interessierte Leser findet die Grundlagen der Digitaltechnik in [Beck05], Grundlagen zum Entwurf von Schaltwerken in [Teic97] und das nötige Basiswissen zum VHDL-Design in [LeWS94] und [MüGl06]. Die Entwicklung von Systemen oder Teilsystemen analoger oder digitaler Art wird in [TiSC02] und [MüGl05] behandelt. Weiterhin existieren Informationsschriften und Tutorials zu den verwendeten Tools im Internet, die kostenlos heruntergeladen werden können und somit der Ergänzung des hier Dargelegten dienen.

## 3.1 Programmierbare Bausteine

Bei der Herstellung von ICs gilt es einen Kompromiss zwischen Preis, Stückzahl und Anwenderflexibilität einzugehen. Dies führt, wegen der unterschiedlichen Randbedingungen, zu diversen Lösungsangeboten der Hersteller.

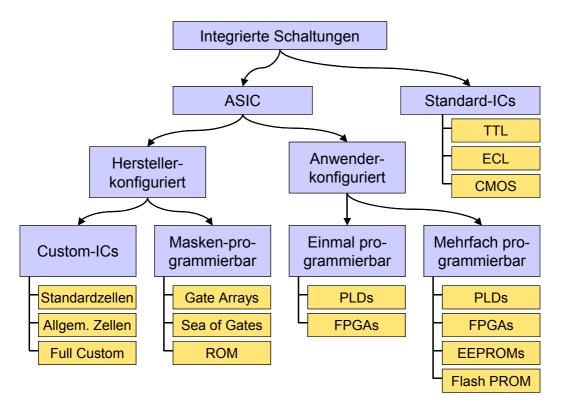

Integrierte Schaltungen lassen sich grob in "Anwenderspezifische Integrierte Schaltkreise (ASIC)" und "Standard-ICs" unterteilen. Für eine genauere Unterscheidung der ASICs ist kennzeichnend welche Seite, ob Hersteller oder Anwender, die Konfiguration vornimmt. So hat der Hersteller die Möglichkeit mit Custom-ICs, die auf "Standard-Zellen", "Allgemeinen Zellen" oder "Full Custom" beruhen, bereits konfigurierte ICs anzubieten, welche sehr kompakt und bei hohen Stückzahlen auch wirtschaftlich sind. Vollkundenspezifische ICs werden auf Transistorebene entwickelt. Da dedizierte Masken hergestellt werden müssen, resultiert eine lange Lieferzeit und ein hoher Preis. Bei den Zellentechniken kann auf die Verschaltung bewährter Zellstrukturen aus einer, vom Hersteller als Betriebsgeheimnis gehütete, Zellenbibliothek zurückgegriffen werden.

Abbildung 3.1: Integrierte Schaltungen

Um auch in Anwendungssektoren mit geringeren Stückzahlen herstellerkonfigurierte Logikbausteine kostengünstig bereitzuhalten, werden so genannte "Maskenkonfigurierbare A-SICs" angeboten. Wie der Name bereits andeutet, legt der Hersteller die Funktion dieser ICs durch die Erzeugung von Masken für das Abarbeiten der letzten Prozessschritte fest. Vertreter dieser Klasse sind "Gate Arrays", "Sea of Gates" und ROMs. Es sei hier kurz angemerkt, dass die Beherrschung der Mehrlagen-Metallisierung zu einer Weiterentwicklung der Gate-Arrays zu den Sea-of-Gates führte, da die Verdrahtungskanäle zwischen den regelmäßig angeordneten Zellen (bestehend aus aneinander gereihten Transistoren) sich nun über den Zellen befinden und der Aufbau damit kompakter ist.

Wichtige Vertreter des Gebiets der anwenderprogrammierbaren Schaltkreise sind "Programmable Logic Devices" (PLDs), "Field Programmable Gate Arrays" (FPGAs) und Anwender programmierbare Speicherbausteine.

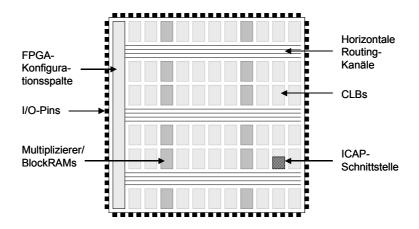

#### 3.1.1 Field Programmable Gate Arrays (FPGAs)

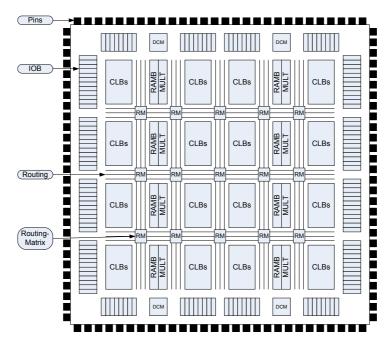

FPGAs sind auf eine möglichst hohe Nutzung der Logikressourcen ausgelegt. Eine Vielzahl kleiner Logikblöcke ermöglicht eine hohe Komplexität und Anpassungsfähigkeit. Diese Vorteile werden aber durch eine aufwändige Verdrahtung erkauft, weswegen es Schwierigkeiten mit knappen Zeitbedingungen geben kann. Der hohe Verdrahtungsaufwand bringt es auch mit sich, dass beispielsweise ein Virtex-II-1000-FPGA (z.B. XC2V1000BGA256) der Firma Xilinx theoretisch eine Million Gatter besitzt, diese jedoch praktisch nicht alle verdrahtbar sind.

Eine grobe Unterscheidung der verschiedenen FPGA-Typen einzelner Hersteller am Markt kann anhand der folgenden Liste geschehen:

- ROM-, Flash- oder RAM-basiert

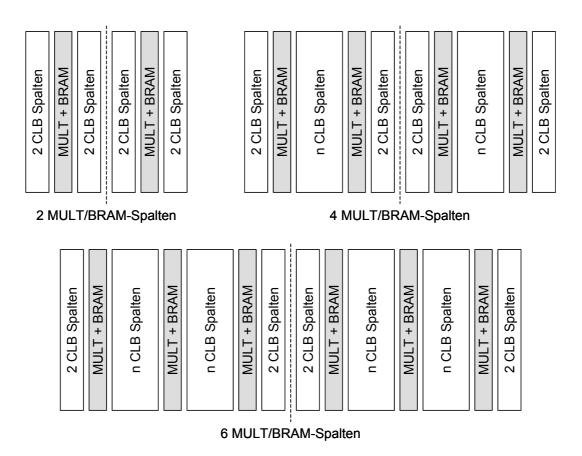

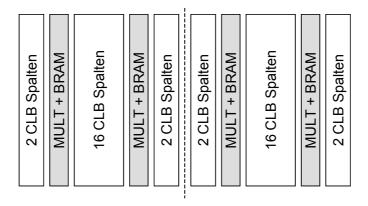

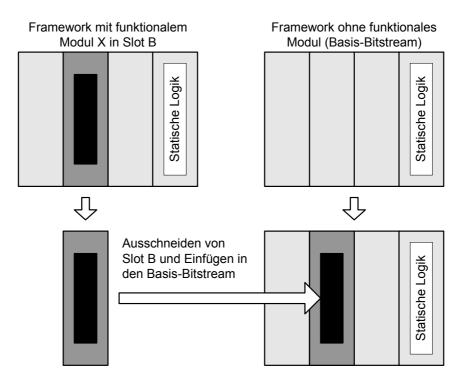

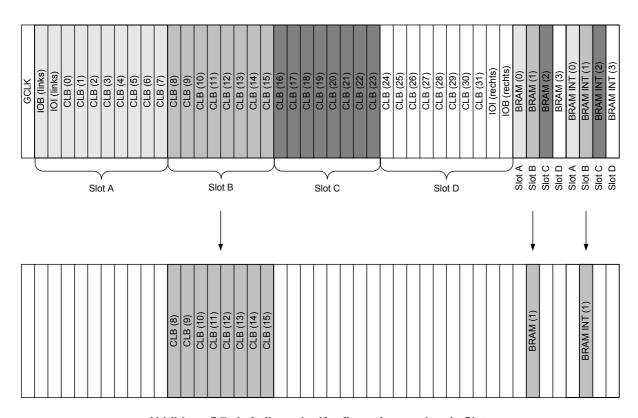

- dynamisch bzw. nicht dynamisch re-konfigurierbar