# Task Activity Vectors: A Novel Metric for Temperature-Aware and Energy-Efficient Scheduling

zur Erlangung des akademischen Grades eines

## Doktors der Ingenieurwissenschaften

von der Fakultät für Informatik des Karlsruher Institutes für Technologie (KIT)

#### genehmigte

#### Dissertation

von

#### **Andreas Merkel**

aus Karlsruhe

Tag der mündlichen Prüfung:4. Februar 2010Erster Gutachter:Prof. Dr. Frank BellosaZweiter Gutachter:Prof. Dr. Wolfgang Karl

#### Abstract

Over the past decades, microprocessors have seen an enormous increase in integration density and power consumption. Today, we have reached a point where on-chip temperature has become a severe problem, and energy efficiency is of paramount importance. In addition, increasing the frequency or the complexity of a processor core is no longer economical. This has lead to the introduction of explicit thread-level parallelism on processor chips (simultaneous multithreading, chip multiprocessing). Threads running in parallel on a chip compete for shared chip resources and are affected by chip-wide power management, which leads to interdependencies between those threads.

All three aspects—temperature, energy efficiency, and interdependency between threads of execution—are strongly connected to the characteristics of the applications (tasks) executed by the processor. Different tasks utilize chip-related resources such as integer or floating point units, caches, or the memory interface to different degrees. Since power dissipation is caused by activity on the chip, processor temperature is inherently coupled to the utilization of the resources on the chip and thus depends on the running task. Tasks that run in parallel and utilize the same shared chip resources to a high degree lead to contention, poor performance, and poor energy efficiency.

The operating system scheduler—managing the running tasks—can take great influence on temperature and resource contention by virtue of its scheduling decisions, i.e., by deciding which tasks to run at what time and in combination with which other tasks. Schedulers found in today's general purpose operating systems are unaware of the utilization of chip resources caused by the tasks they manage. Uninformed scheduling decisions lead to thermal problems, resource contention and, overall, inefficient use of the processor's resources.

In this thesis, we propose *task activity vectors* as a new metric to guide scheduling. An activity vector provides the scheduler with information about which processor resources a particular task uses. With this knowledge, the scheduler can make more informed scheduling decisions and use the chip's resources more efficiently.

Two use cases demonstrate the applicability of task activity vectors. Firstly, we show that the information provided by activity vectors can be used to attain a more balanced temperature distribution on the chip and to avoid pernicious hotspots by controlling the temporal order in which tasks are scheduled. Secondly, we show that activity vectors are suitable for co-scheduling tasks in a way that avoids resource contention and improves performance as well as energy efficiency.

We implemented our proposed policies for the Linux kernel. Our evaluations with multithreaded and multicore processors show that vector-based scheduling is a lowoverhead way to improve performance, attain better thermal behavior, and make more efficient use of energy.

# Contents

| 1 | Introduction                 |                                                          |    |  |  |  |  |  |

|---|------------------------------|----------------------------------------------------------|----|--|--|--|--|--|

|   | 1.1                          | 1 Modern Microprocessors—a Challenge for Task Scheduling |    |  |  |  |  |  |

|   | 1.2                          | The Role of Resource Utilization                         | 2  |  |  |  |  |  |

|   |                              | 1.2.1 Temperature-aware task scheduling                  | 2  |  |  |  |  |  |

|   |                              | 1.2.2 Co-scheduling for energy efficiency                | 3  |  |  |  |  |  |

|   | 1.3                          | Contributions                                            | 6  |  |  |  |  |  |

|   | 1.4                          | Structure                                                | 7  |  |  |  |  |  |

| 2 | Background 9                 |                                                          |    |  |  |  |  |  |

|   | 2.1                          | Tasks                                                    | 9  |  |  |  |  |  |

|   | 2.2                          | Symmetric Multiprocessing                                | 9  |  |  |  |  |  |

|   | 2.3                          | Chip Multiprocessing and Simultaneous Multithreading     | 10 |  |  |  |  |  |

|   | 2.4                          | Multiprocessor Scheduling                                | 10 |  |  |  |  |  |

|   | 2.5                          | Thermal Behavior of a Processor Chip                     | 11 |  |  |  |  |  |

|   | 2.6                          | Thermal Management                                       | 13 |  |  |  |  |  |

|   | 2.7                          | Power Management                                         | 14 |  |  |  |  |  |

|   | 2.8                          | Energy Efficiency Metrics                                | 15 |  |  |  |  |  |

|   | 2.9                          | Event Monitoring Counters                                | 15 |  |  |  |  |  |

| 3 | Task Activity Vectors1       |                                                          |    |  |  |  |  |  |

|   | 3.1                          | The Need for Task Characterization                       | 17 |  |  |  |  |  |

|   | 3.2                          | Definition of Task Activity Vectors                      | 18 |  |  |  |  |  |

|   | 3.3                          | Versatility and Portability                              | 19 |  |  |  |  |  |

|   | 3.4                          | Activity Vector Framework                                | 21 |  |  |  |  |  |

|   | 3.5                          | Determining Activity Vectors                             | 21 |  |  |  |  |  |

|   | 3.6                          | Implementation                                           | 26 |  |  |  |  |  |

|   | 3.7                          | Overhead                                                 | 27 |  |  |  |  |  |

|   | 3.8                          | Vector-Based Scheduling                                  | 28 |  |  |  |  |  |

|   | 3.9                          | Uniform vs. Non-uniform Policies                         | 29 |  |  |  |  |  |

| 4 | Temperature-Aware Scheduling |                                                          |    |  |  |  |  |  |

|   | 4.1                          | Introduction                                             | 31 |  |  |  |  |  |

|   | 4.2                          | Determining Chip Temperature                             | 33 |  |  |  |  |  |

|   | 4.3                          | Related Work                                             | 35 |  |  |  |  |  |

|   |                           | 4.3.1                                                                                                                                                        | Approaches guided by temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |                           | 4.3.2                                                                                                                                                        | Approaches guided by utilization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|   |                           | 4.3.3                                                                                                                                                        | Approaches at the hardware level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|   |                           | 4.3.4                                                                                                                                                        | Shortening timeslices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|   | 4.4                       | Vector                                                                                                                                                       | -Based, Temperature-Aware Scheduling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|   |                           | 4.4.1                                                                                                                                                        | Runqueue sorting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|   |                           | 4.4.2                                                                                                                                                        | Activity balancing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|   |                           | 4.4.3                                                                                                                                                        | Activity unbalancing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|   | 4.5                       | Impler                                                                                                                                                       | nentation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|   |                           | 4.5.1                                                                                                                                                        | Activity vectors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|   |                           | 4.5.2                                                                                                                                                        | Runqueue sorting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|   |                           | 4.5.3                                                                                                                                                        | Activity balancing/unbalancing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|   | 4.6                       | Evalua                                                                                                                                                       | tion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|   |                           | 4.6.1                                                                                                                                                        | Setup and methodology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|   |                           | 4.6.2                                                                                                                                                        | Overhead of activity vectors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|   |                           | 4.6.3                                                                                                                                                        | Runqueue sorting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|   |                           | 4.6.4                                                                                                                                                        | Activity balancing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|   |                           | 4.6.5                                                                                                                                                        | Activity unbalancing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|   |                           | 4.6.6                                                                                                                                                        | Shortening timeslices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|   |                           | 4.6.7                                                                                                                                                        | Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|   | 4.7                       | Summ                                                                                                                                                         | ary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|   |                           | 5 411111                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 5 |                           |                                                                                                                                                              | onscious Scheduling for Energy Efficiency 73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5 |                           | ource-co                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 5 | Reso                      | ource-co<br>Introdu                                                                                                                                          | onscious Scheduling for Energy Efficiency 73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5 | <b>Reso</b><br>5.1        | ource-co<br>Introdu                                                                                                                                          | onscious Scheduling for Energy Efficiency       73         action       73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5 | <b>Reso</b><br>5.1        | ource-co<br>Introdu<br>Relateo                                                                                                                               | onscious Scheduling for Energy Efficiency       73         action       73         d Work       75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 5 | <b>Reso</b><br>5.1        | Durce-co<br>Introdu<br>Relateo<br>5.2.1                                                                                                                      | onscious Scheduling for Energy Efficiency       73         action       73         d Work       75         Contention for SMT resources       76                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 5 | <b>Reso</b><br>5.1        | Introdu<br>Related<br>5.2.1<br>5.2.2                                                                                                                         | onscious Scheduling for Energy Efficiency       73         action       73         d Work       75         Contention for SMT resources       76         Cache contention       77                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 5 | <b>Reso</b><br>5.1        | Introdu<br>Related<br>5.2.1<br>5.2.2<br>5.2.3                                                                                                                | <b>Onscious Scheduling for Energy Efficiency 73</b> Inction       73         Id Work       75         Contention for SMT resources       76         Cache contention       77         Memory contention       78                                                                                                                                                                                                                                                                                                                                                                                          |

| 5 | <b>Reso</b><br>5.1        | Introdu<br>Related<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5                                                                                              | onscious Scheduling for Energy Efficiency       73         action       73         d Work       75         Contention for SMT resources       76         Cache contention       77         Memory contention       78         Profiting from shared resources       79         Frequency selection       80         sis of Resource Contention and Frequency Selection       82                                                                                                                                                                                                                           |

| 5 | <b>Reso</b><br>5.1<br>5.2 | Introdu<br>Related<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5                                                                                              | onscious Scheduling for Energy Efficiency       73         action       73         d Work       75         Contention for SMT resources       76         Cache contention       77         Memory contention       78         Profiting from shared resources       79         Frequency selection       80                                                                                                                                                                                                                                                                                               |

| 5 | <b>Reso</b><br>5.1<br>5.2 | Introdu<br>Related<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>Analys                                                                                    | onscious Scheduling for Energy Efficiency       73         action       73         d Work       75         Contention for SMT resources       76         Cache contention       77         Memory contention       78         Profiting from shared resources       79         Frequency selection       80         sis of Resource Contention and Frequency Selection       82                                                                                                                                                                                                                           |

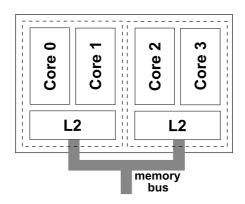

| 5 | <b>Reso</b><br>5.1<br>5.2 | Introdu<br>Related<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>Analys<br>5.3.1                                                                           | Onscious Scheduling for Energy Efficiency73action73d Work75d Work75Contention for SMT resources76Cache contention77Memory contention78Profiting from shared resources79Frequency selection80sis of Resource Contention and Frequency Selection82System description83                                                                                                                                                                                                                                                                                                                                      |

| 5 | <b>Reso</b><br>5.1<br>5.2 | Introdu<br>Related<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>Analys<br>5.3.1<br>5.3.2                                                                  | Onscious Scheduling for Energy Efficiency73action73action73d Work75Contention for SMT resources76Cache contention77Memory contention78Profiting from shared resources79Frequency selection79Sis of Resource Contention and Frequency Selection82System description83Metric84                                                                                                                                                                                                                                                                                                                              |

| 5 | <b>Reso</b><br>5.1<br>5.2 | Introdu<br>Related<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>Analys<br>5.3.1<br>5.3.2<br>5.3.3                                                         | Onscious Scheduling for Energy Efficiency73action73action73d Work75Contention for SMT resources76Cache contention77Memory contention78Profiting from shared resources79Frequency selection80Sis of Resource Contention and Frequency Selection82System description83Metric84Energy measurements86                                                                                                                                                                                                                                                                                                         |

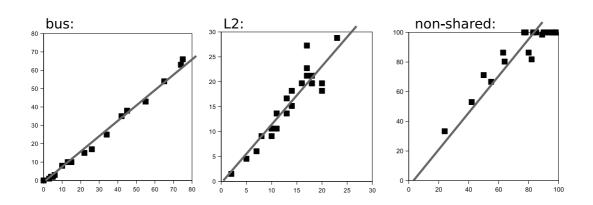

| 5 | <b>Reso</b><br>5.1<br>5.2 | Introdu<br>Related<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>Analys<br>5.3.1<br>5.3.2<br>5.3.3<br>5.3.4                                                | Onscious Scheduling for Energy Efficiency73action73d Work75Contention for SMT resources76Cache contention77Memory contention78Profiting from shared resources79Frequency selection80sis of Resource Contention and Frequency Selection82System description82Metric84Energy measurements86Resource contention86Resource contention86                                                                                                                                                                                                                                                                       |

| 5 | <b>Reso</b><br>5.1<br>5.2 | Introdu<br>Related<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>Analys<br>5.3.1<br>5.3.2<br>5.3.3<br>5.3.4<br>5.3.5<br>5.3.6<br>5.3.7                     | onscious Scheduling for Energy Efficiency       73         iction       73         iction       73         d Work       75         Contention for SMT resources       76         Cache contention       77         Memory contention       78         Profiting from shared resources       79         Frequency selection       80         sis of Resource Contention and Frequency Selection       82         System description       84         Energy measurements       86         Resource contention       91         Optimal co-scheduling       92         Results for the AMD Opteron       96 |

| 5 | <b>Reso</b><br>5.1<br>5.2 | Introdu<br>Related<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>Analys<br>5.3.1<br>5.3.2<br>5.3.3<br>5.3.4<br>5.3.5<br>5.3.6<br>5.3.7                     | Omscious Scheduling for Energy Efficiency73action73action73d Work75Contention for SMT resources76Cache contention77Memory contention78Profiting from shared resources79Frequency selection80sis of Resource Contention and Frequency Selection82System description82Metric84Energy measurements86Resource contention91Optimal co-scheduling92Results for the AMD Opteron96y Vectors for Multicore Scheduling97                                                                                                                                                                                            |

| 5 | <b>Reso</b><br>5.1<br>5.2 | Introdu<br>Related<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>Analys<br>5.3.1<br>5.3.2<br>5.3.3<br>5.3.4<br>5.3.5<br>5.3.6<br>5.3.7<br>Activit<br>5.4.1 | Omscious Scheduling for Energy Efficiency73action73action73d Work75Contention for SMT resources76Cache contention77Memory contention78Profiting from shared resources79Frequency selection80Sis of Resource Contention and Frequency Selection82System description83Metric84Energy measurements86Resource contention91Optimal co-scheduling92Results for the AMD Opteron96y Vectors for Multicore Scheduling97Frequency dependency of activity vectors98                                                                                                                                                  |

| 5 | <b>Reso</b><br>5.1<br>5.2 | Introdu<br>Related<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>Analys<br>5.3.1<br>5.3.2<br>5.3.3<br>5.3.4<br>5.3.5<br>5.3.6<br>5.3.7<br>Activit<br>5.4.1 | Omscious Scheduling for Energy Efficiency73action73action73d Work75Contention for SMT resources76Cache contention77Memory contention78Profiting from shared resources79Frequency selection80sis of Resource Contention and Frequency Selection82System description82Metric84Energy measurements86Resource contention91Optimal co-scheduling92Results for the AMD Opteron96y Vectors for Multicore Scheduling97                                                                                                                                                                                            |

|              |        | 5.5.2 Vector-based co-scheduling                                | 105 |

|--------------|--------|-----------------------------------------------------------------|-----|

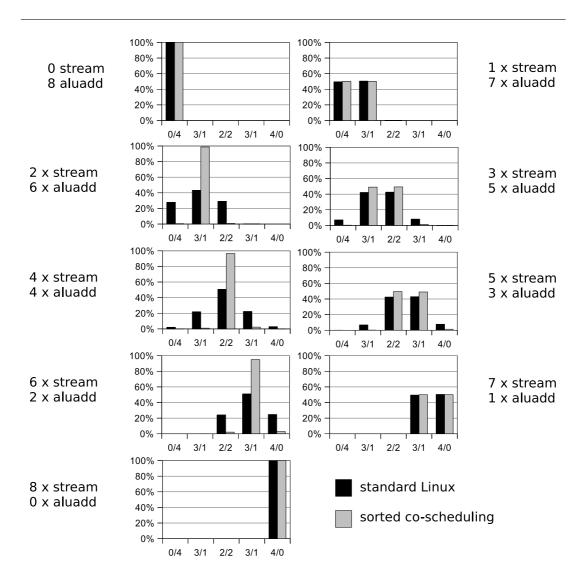

|              |        | 5.5.3 Sorted co-scheduling                                      | 106 |

|              |        | 5.5.4 Greedy co-scheduling                                      | 108 |

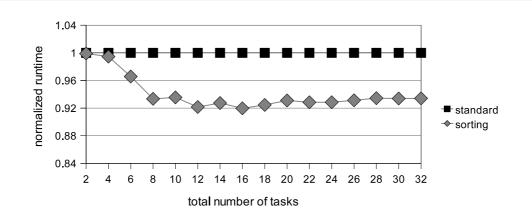

|              |        | 5.5.5 Scalability                                               | 112 |

|              | 5.6    | Frequency Heuristic                                             |     |

|              | 5.7    | Implementation                                                  |     |

|              |        | 5.7.1 Activity vectors                                          |     |

|              |        | 5.7.2 Vector balancing and co-scheduling                        |     |

|              |        | 5.7.3 Frequency selection                                       | 118 |

|              | 5.8    | Evaluation                                                      |     |

|              |        | 5.8.1 Methodology                                               |     |

|              |        | 5.8.2 Overhead                                                  |     |

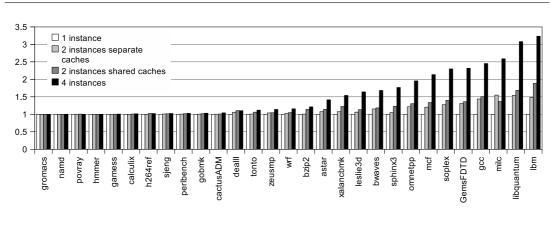

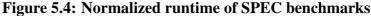

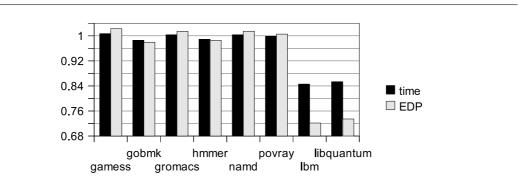

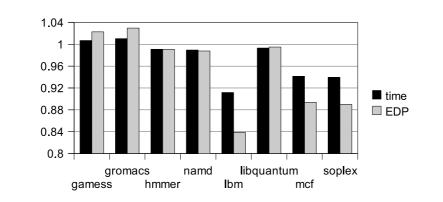

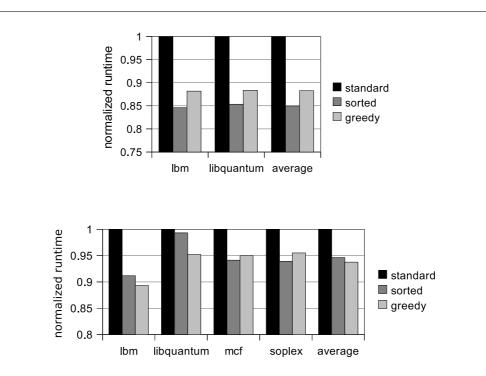

|              |        | 5.8.3 Workload dependence                                       |     |

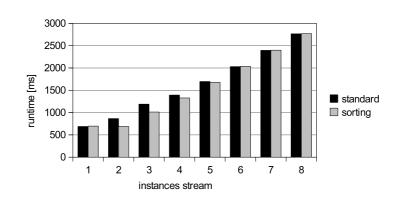

|              |        | 5.8.4 Sorted co-scheduling                                      |     |

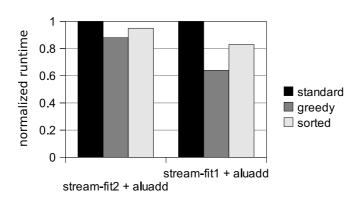

|              |        | 5.8.5 Greedy co-scheduling                                      |     |

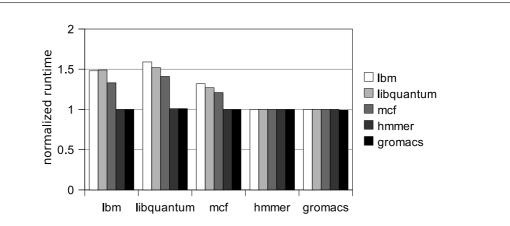

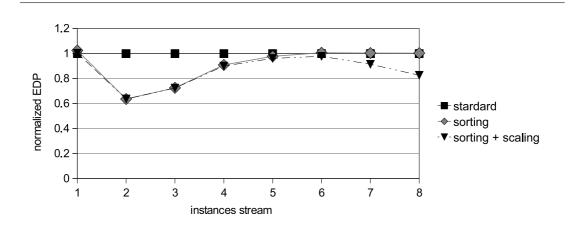

|              |        | 5.8.6 Frequency heuristic                                       | 130 |

|              |        | 5.8.7 Application of co-scheduling to the NetBurst architecture |     |

|              | 5.9    | Summary                                                         | 133 |

| 6            | Con    | clusion                                                         | 135 |

|              | 6.1    | Recapitulation                                                  | 135 |

|              | 6.2    | Comparison of the Proposed Scheduling Policies                  | 136 |

|              | 6.3    | Achievements                                                    | 137 |

|              | 6.4    | Limitations and Future Work                                     | 138 |

| List         | t of I | Tigures                                                         | 141 |

| List         | t of ] | Tables                                                          | 142 |

| Bibliography |        |                                                                 |     |

| A            | The    | SPEC CPU 2006 Benchmarks                                        | 159 |

| B            | Deu    | tschsprachige Kurzfassung                                       | 161 |

# **1** Introduction

# 1.1 Modern Microprocessors—a Challenge for Task Scheduling

In the past decades, microprocessors have seen a steady increase in integration density and power consumption. This has lead to the following situation:

- Heat has become a severe problem. Today's processor chips dissipate power in the order of 100W in an area as small as 1cm<sup>2</sup>, which is ten times the power density of a hot-plate. This necessitates considerable cooling efforts, as well as thermal management features provided by the hardware to counteract thermal emergencies. Thermal management has implications on the computational performance of the chip, because preventing thermal emergencies usually means slowing down the processor. Since chip temperature depends on the instructions executed by the chip and thus on the software, achieving optimal performance under thermal constraints necessitates software that is aware of thermal problems and supports thermal management.

- Energy efficiency is becoming an ever more important issue. Better energy efficiency mitigates thermal problems and reduces the need for cooling. In addition, rising energy costs increase the demand for energy efficient computer systems in the area of compute centers as well as for workstations. For mobile computers, energy efficiency enables longer battery times. This has led to the inclusion of power management features in today's microprocessors. Similar to thermal management, the power management mechanisms offered by the hardware affect performance, and the efficiency of the mechanisms at conserving energy depends on the instructions executed by the chip and thus on the software.

- Increasing the operating frequency or the complexity of a processor core in order to increase performance is no longer economical. Instead, thread-level parallelism has been introduced in today's processors in the form of simultaneous multithreading (SMT) or chip multiprocessing (CMP). In contrast to traditional symmetric multiprocessing with physically distinct chips, SMT or CMP threads share resources of one chip and are thus likely to influence each other. In particular, if the software running on the individual hardware threads utilizes the same shared resources excessively, contention can lead to poor performance and bad

#### 1 Introduction

energy efficiency. In addition, power management features such as frequency scaling often affect all threads running on a chip, which creates further interdependencies.

In this thesis, we address the problems of temperature, energy efficiency, and interdependency between execution contexts (that is, SMT threads or CMP cores) by adapting *operating system task scheduling*, i.e., the assignment of running applications to processors performed by the operating system.

The operating system is the central component that is suitable to address the mentioned problems from the software side. In its role as a resource manager, the operating system has knowledge about and exercises control over both hardware as well as applications. Task scheduling is a central functionality of an operating system and has great implications on temperature and energy efficiency, since the task selected for running on a processor determines the processor's power consumption and temperature [BWWK03, IM03]. In SMT and CMP systems, contention for shared resources makes co-scheduling, i.e., selecting what tasks run in parallel on the hardware contexts, decisive for performance and energy efficiency, since the combination of tasks determines the degree of resource contention [ST00, BP04, MM07].

We argue that in order to address the problems of today's processors, a scheduler needs to be aware of task specific characteristics like the utilization of processorrelated resources. Only with this knowledge, a suitable scheduling policy can consider the implications that scheduling decisions have on temperature, energy efficiency, and on the interdependencies between tasks running in parallel.

To limit the complexity of our research, the focus of this thesis is on single-threaded applications. In the remainder of the thesis, when we use the term "task" we will therefore imply that a task is single-threaded unless mentioned otherwise.

### **1.2 The Role of Resource Utilization**

#### **1.2.1** Temperature-aware task scheduling

Heat is a localized phenomenon caused by switching activity in different parts of the chip. Processor chips encompass various components such as functional units (arithmetic logic units (ALUs), floating point units (FPUs), branch predictors, reorder buffers), storage units (register files and caches), or interface units (cache and memory interface). Different tasks utilize these resources to varying degrees. Therefore, the switching activity in the chip units and the temperature distribution on the chip depend on the task being executed. High utilization of a particular resource can lead to an increased temperature in the respective part of the chip, resulting in a *hotspot*. To avoid damage to the chip, thermal management reduces the chip's power consumption by *throttling*, implemented with mechanisms that reduce switching activity but also performance.

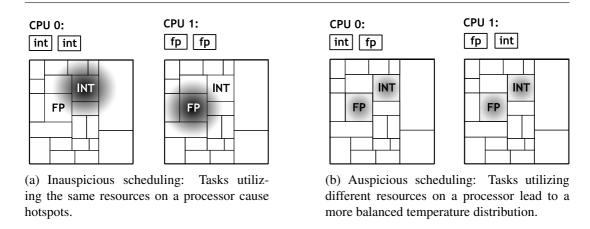

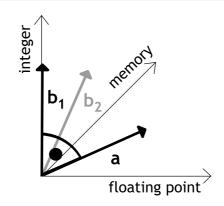

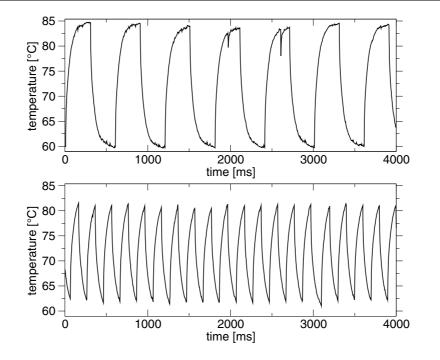

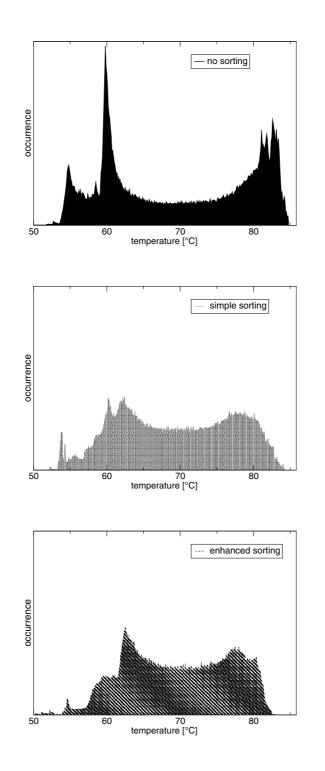

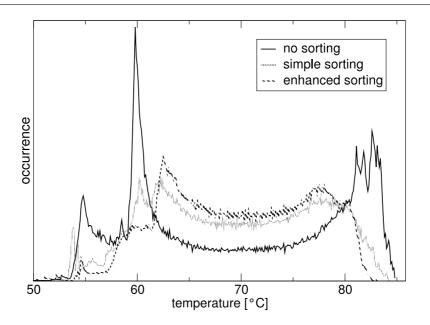

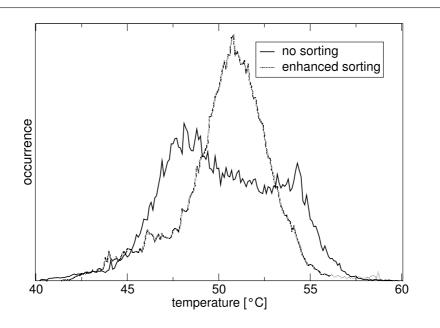

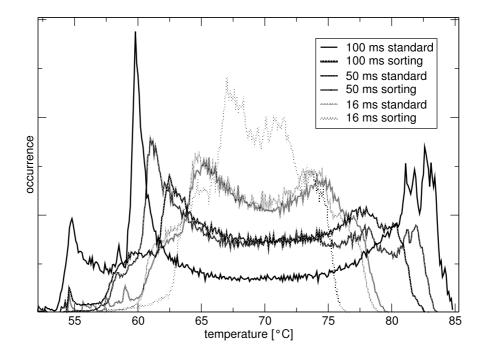

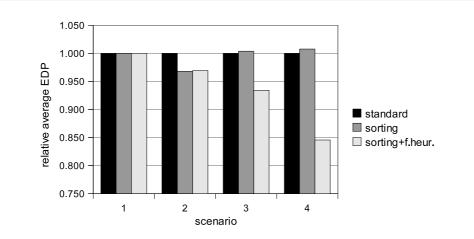

Figure 1.1: Impact of scheduling on temperature distribution

The decisions that a scheduler makes have a direct impact on temperature distribution and thus indirectly affect throttling and performance. Depending on the current temperature distribution on the chip and the resource utilization of the selected task, a scheduling decision can either aggravate thermal problems, if a task is selected that utilizes resources that already have an increased temperature, or mitigate thermal problems if a task is selected that utilized resources having only a moderate temperature.

Figure 1.1 shows an example of a dual-processor system with two floating point tasks and two integer tasks. A scheduler that is unaware of task characteristics could possibly schedule both integer tasks on CPU 0 and both floating point tasks on CPU 1, causing continuous activity in the respective units of the CPUs (left part of the figure). Thus, the integer unit would become a hotspot on CPU 0, while the floating point unit would become a hotspot on CPU 1. Eventually, thermal management would have to intervene and reduce temperature by throttling at the cost of performance penalties.

A scheduler that is aware of the tasks' resource utilizations and their implication on temperature can schedule one integer task and one floating point task alternatingly on each CPU, allowing integer and floating point units to cool down during the periods of inactivity (right side of Figure 1.1), and rendering throttling unnecessary. *Knowledge about the resource utilization of tasks enables temperature-aware scheduling policies that lead to a balanced temperature distribution and avoid overheating parts of the chip.*

#### **1.2.2** Co-scheduling for energy efficiency

For SMT chips, almost all chip resources are shared by multiple logical processors. To a lesser extent, this is also the case for CMP chips, where memory access infrastructures and, in some cases, caches are shared by multiple cores residing on a chip.

#### 1 Introduction

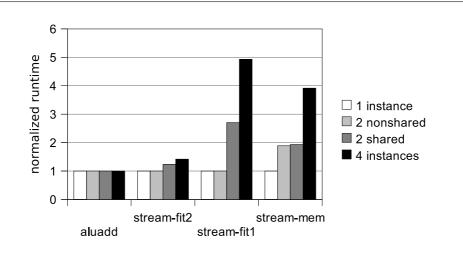

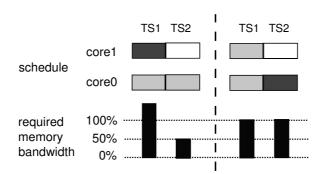

The resource utilization characteristics of tasks running in parallel on different logical processors or cores determine the degree of contention for shared resources and thus the performance. For example, the demands of several memory-bound tasks running in parallel on a multicore chip can easily exceed the memory bandwidth available to the chip. This leads to reduced performance because of stall cycles introduced on the cores while waiting for memory requests to be serviced.

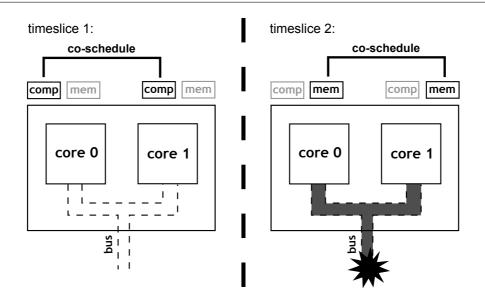

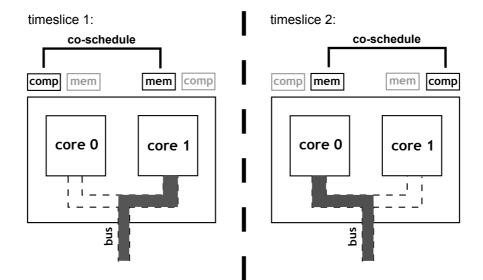

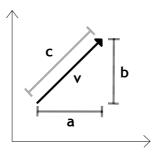

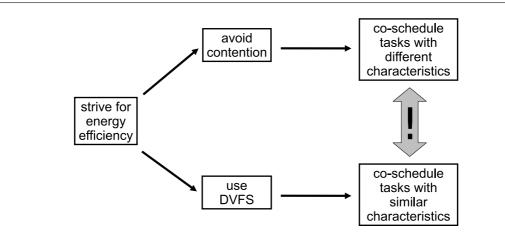

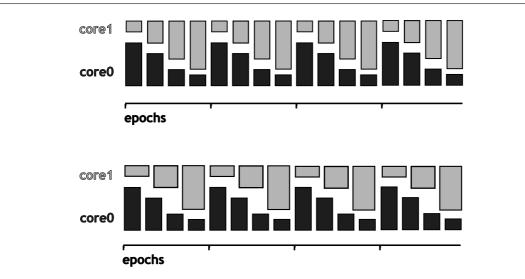

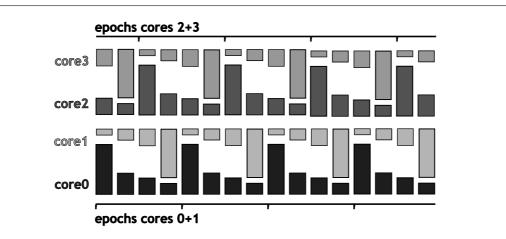

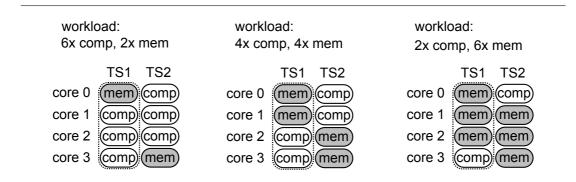

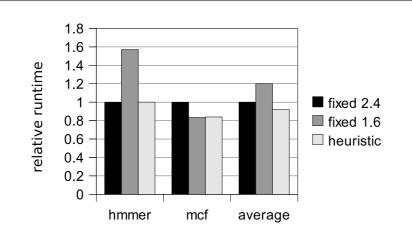

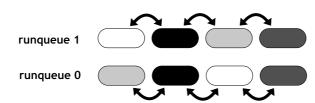

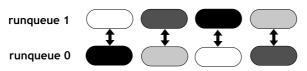

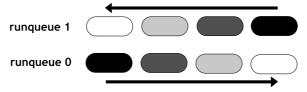

Figure 1.2 shows a dual-core system with two compute-bound tasks and two memory-bound tasks. Scheduling both compute-bound tasks during one timeslice and both memory-bound tasks during the next timeslice (top half of the figure) leads to unused capacity of the memory bus in the first timeslice and a bottleneck with corresponding performance degradation for the memory-bound tasks in the second timeslice. This performance degradation is avoided if memory-bound tasks are co-scheduled with compute-bound tasks each timeslice, making optimal use of the memory bus's capacity (bottom half of Figure 1.2).

A scheduler that is unaware of resource sharing will inadvertently schedule tasks in a way that causes resource contention and sub-optimal performance. Sub-optimal performance in this context also implies inefficiency in terms of energy: The power consumed by the processor is wasted if the processor has to stall while waiting for resources to become available. *Knowledge about the resource utilization of tasks enables co-scheduling policies that avoid contention and increase performance and energy efficiency.*

Power management features such as frequency and voltage scaling create further interdependencies between the cores of a CMP, which need be taken into account for optimal performance and energy efficiency. Many multicore chips offer frequency and voltage scaling only chip-wide, meaning that all cores need to run at the same frequency and voltage, since allowing multiple frequencies and voltages introduces additional hardware complexity.

The optimal frequency at which the processor can execute a task most efficiently in terms of runtime and energy depends on the task's characteristics [WB02, CSP04,  $KDG^+04$ ], in particular on the frequency of memory accesses. With chip-wide frequency scaling, it is only possible to run all tasks at their corresponding optimal frequency if tasks with similar characteristics are running on all cores of a chip. This however, can be in conflict with the goal of avoiding contention, since tasks with similar characteristics are likely to utilize the same resources.

As a consequence, when taking both, resource contention and frequency selection into account, the question arises whether it is more advantageous to run tasks with different characteristics or tasks with similar characteristics together, since the former avoids resource contention, while the latter allows to run the chip at a frequency that is optimal for all tasks.

(a) Inauspicious co-scheduling: tasks utilizing shared chip resources simultaneously cause contention.

(b) Auspicious co-scheduling: tasks utilizing shared resources at different times avoid contention.

## **1.3 Contributions**

A scheduler that is supposed to exercise control over temperature distribution or resource contention needs information about the tasks it manages. We show that information about the utilization of processor resources can be used as a basis for scheduling policies that attain an improved temperature distribution, reduced resource contention, and better energy efficiency. Such information is not available to schedulers in today's operating systems, so these schedulers make resource-unaware decisions leading to thermal problems, contention, and energy inefficiency.

Our thesis makes three main contributions: *task activity vectors* as an abstraction to represent resource utilization, *temperature-aware, vector-based scheduling* as a policy to mitigate thermal problems and *resource-conscious scheduling and frequency selection* as a policy to achieve energy efficiency.

**Task activity vectors** We introduce the concept of *task activity vectors* as an abstraction that represents a task's resource utilization. An activity vector is part of the task's runtime context and describes the degree of utilization the task causes for various chip-related resources when executed. This enables scheduling policies to consider resource utilization when selecting a task to be scheduled.

We show that the operating system can maintain task activity vectors with minimal overhead by using performance monitoring counters, which are present in almost all modern processors.

**Temperature-aware, vector-based scheduling** Based on activity vectors, we propose scheduling policies that strive at balancing the temperature within a chip and between chips to avoid hotspots and throttling. We achieve this (1) by scheduling tasks that use different resources successively on a chip, (2) by distributing tasks among the processors of a multiprocessor system so that each processor executes tasks that use different resources, and (3) by running tasks that use different resources simultaneously on multithreaded processors. Our evaluations show that vector-based scheduling succeeds at reducing hotspots considerably.

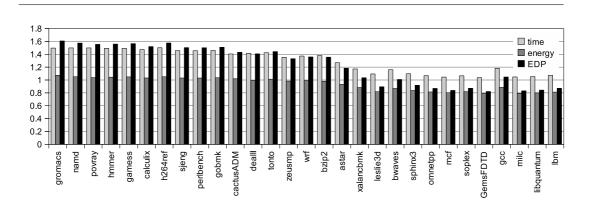

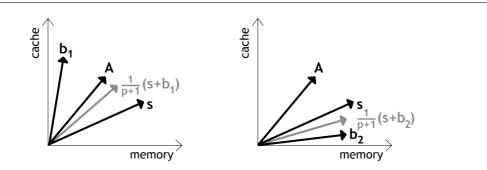

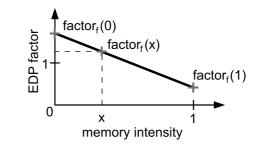

**Resource-conscious scheduling and frequency selection** We analyze what is the optimal way to co-schedule tasks considering the criteria of resource contention and frequency selection. We find that in order to optimize the product of runtime and expended energy (energy delay product, EDP) in today's architectures, the main goal must be to avoid contention by combining tasks that use different resources; it is not worthwhile to co-schedule tasks that share a common optimal frequency if this would lead to resource contention.

According to our analysis, we propose two scheduling policies that avoid resource contention by co-scheduling tasks with different resource demands, based on the information provided by activity vectors. We propose a specialized policy applicable if there is one resource mainly responsible for contention, and a generic policy that is applicable if different resources cause contention. For workloads that contain too many memory-bound tasks for our scheduling policies to avoid contention, we propose a heuristic that engages frequency scaling as a fallback to mitigate the waste of energy introduced by memory contention. Our evaluation with a Linux implementation of vector-based co-scheduling reveals that our policies manage to reduce EDP considerably.

## 1.4 Structure

The rest of this thesis is structured as follows: Chapter 2 discusses the background upon which our work depends. In Chapter 3, we introduce the abstraction of task activity vectors. We cover the application of activity vectors to scheduling in Chapters 4 and 5. Chapter 4 shows how vector-based scheduling can tackle the problem of thermal imbalances and hotspots, and leads to a better and more balanced temperature distribution. Chapter 5 shows how the information provided by activity vectors can be used to reduce resource contention and to make efficient use of a microprocessor in terms of time and energy. With Chapter 6, we conclude and discuss directions for future work.

1 Introduction

# 2 Background

In the following, we briefly introduce the terminology we will be using in the remainder of the thesis. We also cover common hardware and operating system principles that constitute the foundation of our thesis.

## 2.1 Tasks

We have already introduced the term *task* for a running application. More precisely, a *task* is an abstraction that encompasses flows of execution (*threads*), a view on memory protected from other tasks (*address space*) and other resources managed by the operating system such as open files or communication channels. As mentioned, we will use the term *task* in the meaning of "single-threaded task".

## 2.2 Symmetric Multiprocessing

In a multiprocessor system, multiple processors operate in parallel. The focus of our thesis lies on symmetric, cache coherent, shared memory multiprocessor systems. In a *shared memory* multiprocessor system, all processors have access to a shared memory for storing data and code. *Cache* is fast processor-local memory of limited size that buffers contents of main memory in order to hide memory latencies. A *cache coherent* multiprocessor system provides consistency of data written to or read from different processors' caches. In a *symmetric multiprocessor system*, all processors are equal, i.e., identical pieces of hardware. From the software side, symmetric multiprocessing means that the operating system as well as any application can run on any processor. Originally, symmetric multiprocessor (SMP) system were assembled of several physically different single-core, single threaded processor chips. We will refer to such systems as *traditional SMP* systems.

Processors of an SMP system communicate with memory via a shared memory interconnect. This way, limited memory bandwidth can become a bottleneck, especially in systems with many processors. To mitigate contention for the memory interconnect, *non uniform memory access* (NUMA) systems partition their processors into *nodes*. Each node possesses its own memory and memory interconnect. Access to memory of other nodes is possible, but has a higher latency than access to node-local memory.

# 2.3 Chip Multiprocessing and Simultaneous Multithreading

A *chip multiprocessor* (CMP) consists of several processors, also termed *cores*, laid out next to each other on one chip [ONH<sup>+</sup>96]. Like traditional SMP systems, the cores of a CMP share a common memory, potentially with cores from other chips if the system consists of multiple CMPs. Depending on the cache architecture, cores of a CMP can also share a common cache.

*Simultaneous multithreading* (SMT) means that a processor has multiple execution contexts called *logical processors*, which are able to simultaneously issue instructions from different flows of execution (e.g., different tasks) to the chip's functional units [TEL95]. To the software, the logical processors look like independent processors, each with its own registers and state. On the hardware side, the logical processors share the resources (e.g., ALUs, FPUs, caches) of one single processor. For distinction from the logical processors, we call this the *physical processor*. Logical processors of the same physical processor are termed *siblings*.

## 2.4 Multiprocessor Scheduling

In an SMP system, a task can run on any processor. If there are more runnable tasks than processors in the system, next to the question which task to execute on which processor, the additional question arises which tasks shall be executed on a processor at a certain point in time and which ones not. In its role as a resource manager, the operating system performs *scheduling*, the assignment of tasks to processors. The corresponding component of the operating system is called *scheduler*.

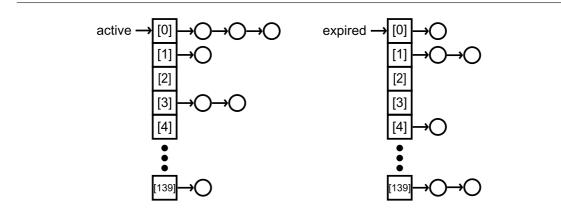

Schedulers found in general purpose operating systems like Linux or Windows perform *time-sharing multitasking*: They assign a processor to different tasks in a row for a defined period of time, a *timeslice*. This way, several tasks can make progress and the user has the impression that the tasks are running in parallel, even if there are more tasks than processors.

For SMP systems, most of today's general purpose operating systems do *affinity scheduling*, which means they associate each task to a particular processor and run the task—either preferably or exclusively—on this processor. This takes advantage of the fact that a task that has once run on a particular processor has built up some state; for example, the data the task is working on is in the processor's cache [SL93].

Many operating systems, like recent versions of Linux, partition the set of runnable tasks between the processors and assign a subset of tasks to each processor. The scheduler manages the set of runnable tasks assigned to a processor in a data structure, the *runqueue*, which keeps track of all tasks eligible for running on a specific processor. To provide optimal performance and fairness, schedulers perform *load balancing*; they

migrate tasks between runqueues for equalizing the number of tasks assigned to each processor.

If scheduling decisions on different processors happen in a coordinated fashion, and tasks are selected to run in parallel on different processors following a defined scheme, we speak of *co-scheduling*. In today's general purpose operating systems, co-scheduling is usually not performed.

Most general purpose operating systems schedule the tasks of a runqueue following the same basic principles. Firstly, all tasks are supposed to make progress. The simplest scheduling policy that ensures this property is *round robin*, i.e., executing each task in turn for a timeslice. Secondly, most operating systems allow a form of prioritization in the sense that higher priority tasks are allotted more CPU time. Thirdly, there is often a distinction between *interactive* and *CPU-bound* tasks. Interactive tasks tend to use the processor only for short periods of time and block frequently, waiting for input data from a user or a peripheral device like a hard disk. CPU-bound task occupy the processor continuously and have little interaction with the user or peripheral devices. Therefore, many schedulers favor interactive tasks over CPU-bound tasks to give the user the impression of a more responsive system and to utilize peripheral devices better.

## 2.5 Thermal Behavior of a Processor Chip

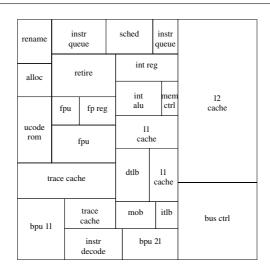

The units a microprocessor consists of (ALUs, FPUs, caches, register files, and so on) are usually laid out as blocks, i.e., (mostly) rectangular areas on the die. Figure 2.1 shows the floorplan of an Intel Pentium 4 Northwood, derived from a die photo, as an example.

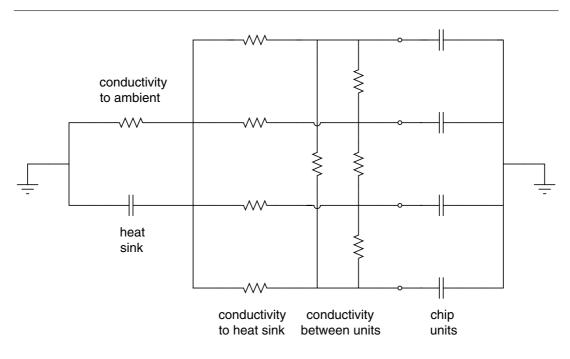

From a physical point of view, the units are located on a silicon die, which in today's processor generations is of rather small dimensions—typically in the order of one centimeter in width and length and of one millimeter in height. The die is covered by a heat spreader consisting of thermally well conducting material and by a heat sink, which is comparably large in relation to the die and consists of copper or aluminum. In relation to its size, the die dissipates large amounts of power, which can surpass 100W in recent processors. This results in a power density of 100W/cm<sup>2</sup> and more.

The temperature of an object, be it a chip unit, the die as a whole, or the heat sink, is determined by the amount of energy that the object contains (referred to as *internal* or *intrinsic energy*) and its *heat capacity*. The heat capacity is a material specific constant describing how many Joules it requires to heat the object by one Kelvin.

The heat capacity of the die is small compared to its power dissipation. Therefore the die (and thus the individual chip units) can heat up rather quickly. A small example shall demonstrate this: A silicon die of  $11 \text{mm} \times 12 \text{mm} \times 0.7 \text{mm}$  (which corresponds to the chip we use in our evaluation of temperature-aware scheduling in Chapter 4) has a heat capacity of 0.15J/K. If it dissipates 70W and no heat is removed from the die,

#### 2 Background

Figure 2.1: Floorplan of the Intel Pentium 4 Northwood processor

it takes only 2ms for the die to heat up by 1K. In contrast to that, the heat sink has a much larger heat capacity, since it is considerably more massy, and typically takes seconds to heat by 1K.

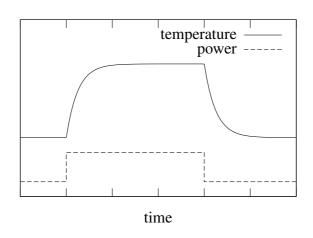

A rapid increase in chip temperature as described in the example happens primarily when there is a boost in chip power consumption, since the removal of heat via conduction requires a temperature gradient between the chip and the heat sink having built up in the first place. The bigger the gradient, the more heat is removed; therefore the increase in temperature slows down, until temperature settles at a certain level, depending on the power consumption (see Figure 2.2). The inverse happens when the chip's power consumption drops.

Since different chip units have different structures and are—depending on the software—utilized to varying degrees, they show mutually different power densities. In addition, owing to the small height of the chip, lateral heat conduction between neighboring chip areas is limited. As a result, the temperature varies from chip unit to chip unit, so there typically is a non-uniform temperature distribution on the chip.

The course of the intrinsic energy and the temperature of the units on the die and of the heat sink can be described by similar differential equations. The solution to those equations is an exponential function [BWWK03, MB06]. The function

$$\vartheta(t) = \frac{-\tilde{c}}{c_2} \cdot e^{-c_2 t} + \frac{c_1}{c_2} \cdot P + \vartheta_0 \tag{2.1}$$

describes the course of temperature for the heat sink or of a single chip unit (neglecting lateral heat conduction to other units) over time. The only difference between the heat

Figure 2.2: Dependence of temperature from power

sink and the chip units is the size of the constants in the equation. The constants  $c_1$  and  $c_2$  depend on the thermal resistance and the thermal capacitance of the chip units or the heat sink;  $\tilde{c}$  is an integration constant depending on the initial temperature at the time t = 0.  $\vartheta_0$  is the temperature of the component the heat is conducted to (i.e., ambient air or heat sink).

## 2.6 Thermal Management

With increasing power densities, designing cooling facilities for the theoretical maximum power that a processor can consume in the worst case results in over-provisioning and high costs. Thus, cooling is usually designed for a lower *thermal design power* (TDP). If the processor exceeds the TDP, overheating and damage to the chip can result. Preventing this requires *thermal management*, i.e., monitoring temperature and engaging countermeasures in case of critical temperatures.

For thermal management, processors support hardware mechanisms that decrease power consumption, for instance by scaling the voltage and/or frequency, by modulating the clock signal, or by introducing halt cycles [BM01, SSH<sup>+</sup>03]. We refer to these mechanisms as *throttling*. All throttling mechanism have in common that they not only reduce power consumption, but also performance.

Since thermal management must reliably prevent thermal emergencies, policies for thermal management are typically implemented in hardware or firmware. Examples are Intel's Catastrophic Shutdown Detectors (Thermal Monitor 1 and 2), which engage clock modulation or frequency scaling if a certain temperature threshold is reached [Int06].

#### 2.7 Power Management

Similar to thermal management, *power management* uses hardware mechanisms to reduce power consumption in exchange for reduced performance. However, the focus of power management is not limited to preventing thermal emergencies. The aim of most power management policies is to make efficient use of energy, for example, to perform a given task using as little energy as possible. This leads to longer battery times on mobile systems, or lower expenses for power and cooling in data centers.

For processor power management, frequency and voltage scaling is often the mechanism of choice, since it allows non-linear power reduction in relation to the runtime increase it causes. For most other throttling mechanisms, the increase in runtime is proportional to the reduction in power. In that case, consuming less power, but for a longer time, does not lead to energy savings.

Using a very simple model, the power dissipation of a processor can be described as proportional to the square of its operating voltage and as proportional to its operating frequency [BB95, Fle01, Mud01]:

$$P \propto V^2 \cdot f$$

The voltage required to drive the processor reliably, in turn, is (within a limited range) approximately proportional to the operating frequency:

$$V \propto f$$

Scaling down the voltage requires a low enough frequency, so voltage scaling is commonly applied in combination with frequency scaling (*dynamic voltage and frequency scaling*, DVFS). With frequency and voltage scaling in combination, the power is proportional to the cube of the frequency (combination of the above two equations):

$$P \propto f^3$$

Since performance is in the best case proportional to the frequency, DVFS allows net energy savings (it reduces power by a greater factor than it increases runtime). Although, in practice, these savings are diminished by static contributions to power consumption such as leakage, DVFS is beneficial in certain scenarios, for example, when not the speed of the processor, but the speed of other components such as memory is decisive for performance [WB02, CSP04].

The simplest option for implementing DVFS for multicore hardware is *per-chip DVFS*, i.e., running all cores at the same frequency and voltage. Adding multiple clock generators and latches for synchronizing the data flow between different clock domains allows running cores at different frequencies (*per-core DVFS*). However, without additional voltage regulators (which introduce additional complexity), all cores need to run at the voltage determined by the core running at the highest frequency,

which greatly diminishes the potential for energy savings. Recently, on-chip voltage regulators have been proposed for enabling per-core DVFS [KGWB08]. Though on-chip regulators facilitate running different cores at different voltages, introducing multiple voltage domains still causes overhead in terms of die area and energy efficiency.

## 2.8 Energy Efficiency Metrics

The mechanism of DVFS allows the processor to execute tasks while requiring less energy, at the expense of a prolonged runtime. For situations where both performance and energy consumption are important, the *energy delay product* (EDP) has been proposed as a metric [HIG94, GH96]. The EDP is obtained by multiplying the runtime of a task with the amount of energy required for the run. A similar metric that gives more weight to runtime is ED<sup>2</sup>, the product of energy and squared runtime.

## 2.9 Event Monitoring Counters

*Event monitoring counters* are model-specific registers that are able to count various processor-internal events. Event monitoring counters found in today's commercially available processors were introduced for performance analysis and profiling (*performance monitoring counters*) and are therefore tailored to performance-critical events like, for example, cache misses or mispredicted branches.

Despite their focus on performance, in the past, event monitoring counters of various architectures have also been used for inferring the activity of different parts of the processor chip [IM03] and for deducing power consumption and temperature [BWWK03].

# 2 Background

# **3** Task Activity Vectors

Information about what chip resources particular task is using constitutes valuable input for a scheduler. In order to make informed decisions concerning which tasks to run at what time and in which combination, a scheduler needs to know what effects running a particular task or a particular combination of tasks will have; it needs to be provided with a characterization of the tasks it manages.

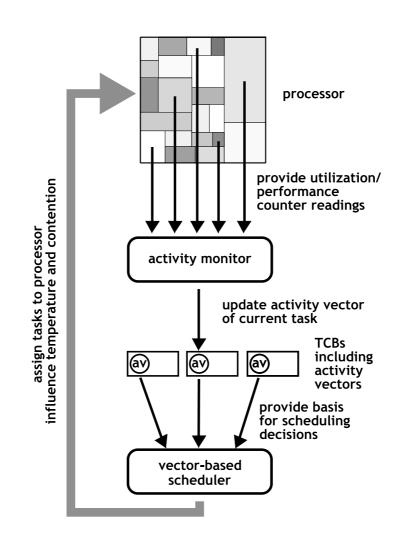

In this chapter, we introduce the abstraction of the *task activity vector* as a way to characterize a task by the resource utilization it causes [MB08b]. The notion of *vector-based scheduling* describes a scheduling policy that makes use of the task characterization provided by activity vectors to attain a specific goal.

### 3.1 The Need for Task Characterization

As outlined in Chapter 2, today's general purpose operating systems like Linux or Windows categorize tasks by applying user-specified priorities, and, in addition, distinguish between interactive and CPU-bound tasks. Still, CPU-bound tasks having the same priority are treated as equal. We argue that treating such tasks as equal for scheduling is no longer optimal on today's processors, and that a coarse categorization into interactive and CPU-bound tasks does not consider the importance of the utilization of CPU-related resources.

In order to make optimal decisions, a scheduler needs to know what consequences running a particular task will have, for instance, what will be the impact on chip temperature and temperature distribution, and how the task will interact with other tasks running on the same chip. Thus, we need to provide the scheduler with a way to judge the impact of running a task.

As mentioned in the introduction, phenomena like the dissipation of energy and the interaction between tasks running on a chip are closely coupled to the utilization of processor-related resources like the units on the chip (e.g., ALUs, FPUs, register files, or caches) and the memory interconnect. A task that causes a high utilization of a particular resource leads to an increased temperature in the corresponding part of the chip because of increased switching activity. If the resource in question is shared between several logical processors or cores, the task will interfere with tasks running on other logical processors or cores. If several tasks utilize a resource at the same time, this leads to a slowdown of the tasks involved, and, in turn, to inefficient use of energy.

#### 3 Task Activity Vectors

We propose the concept of task activity vectors to reflect the growing importance that the characteristics of tasks have on the temperature, the performance, and the energy efficiency of modern processors. The activity vector is an abstraction that models the resource utilization caused by a task. Task activity vectors make the resources the task uses part of the task's runtime context, so the operating system and especially the scheduler have detailed information about the characteristics of each task and can foresee and consider the implications that running this particular task will have.

### 3.2 Definition of Task Activity Vectors

We define a *task activity vector* as an *n*-dimensional vector that is part of a task's runtime context. The dimension of an activity vector corresponds to the number of resources we want to consider, and each component of the vector corresponds to the degree of utilization of one specific resource. The values of the vector's components range between 0 (the resource is not utilized at all) and 1 (the resource is fully utilized).

We define utilization as the number of accesses a task makes to the resource in a period of time, divided by the maximum number of accesses the resource supports in that period of time. The maximum can either be calculated theoretically by studying the microarchitecture (for instance, deducing that an integer unit containing three ALUs can execute up to three integer operations per cycle) or measured using specific microbenchmarks (for instance measuring memory bandwidth with the stream [McC95] benchmark).

For chips that support multiple operating frequencies, we define the activity vector of a task by the resource utilization the task causes at the chip's maximum frequency. We postpone a detailed discussion of activity vectors in connection with frequency scaling to Chapter 5.

In general, an activity vector can be used to model any resource that can be utilized by a task to varying degrees, including, for example, network or disk bandwidth. In this thesis, we focus on resources related to the processor chip, since we want to study the implications of scheduling on processor-related phenomena. Including the utilization of other resources such as peripheral devices is a topic for future research.

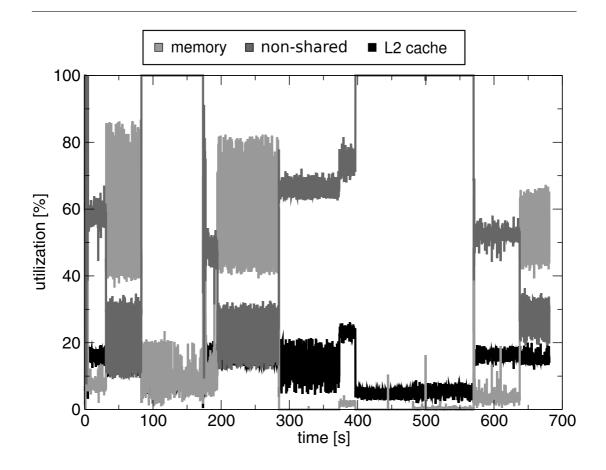

For most resources, the definition of utilization by access frequency is a suitable, and the only sensible way to define utilization. An exception are storage units such as cache or memory, for which utilization can also be defined in terms of space occupancy. For example, two memory-bound applications running in parallel on a CMP are competing for both memory bandwidth and for memory space, and performance is diminished both by insufficient bandwidth (stall cycles) and insufficient space (thrashing).

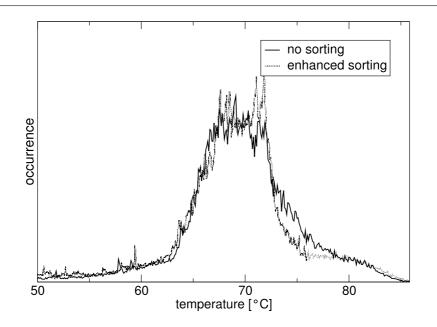

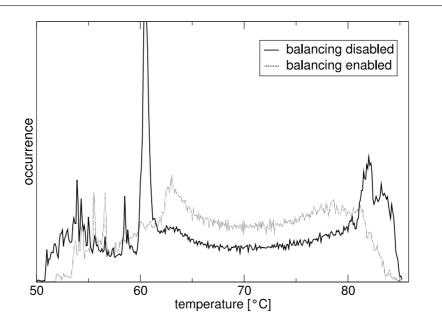

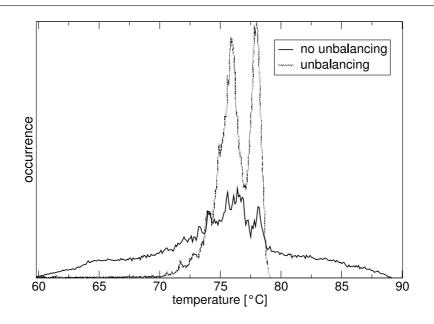

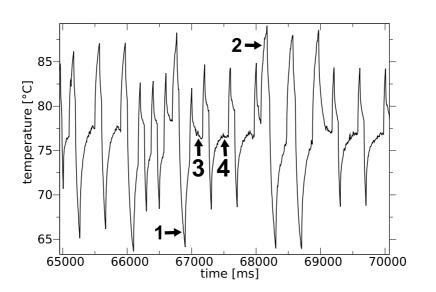

In our thesis, we assume that memory space is available in sufficient quantity and that bandwidth is the limiting factor. With the growing size of the main memory found in typical systems, this is a reasonable assumption. Contention for memory space is beyond of the scope of this thesis.