# Huffman-based Code Compression Techniques for Embedded Systems

zur Erlangung des akademischen Grades eines

### Doktors der Ingenieurwissenschaften

der Fakultät für Informatik der Universität Fridericiana zu Karlsruhe (TH)

genehmigte

Dissertation

von

Talal Bonny

aus Aleppo

Tag der mündlichen Prüfung: 18.06.2009

Erster Gutachter: Prof. Dr.-Ing. Jörg Henkel

Zweiter Gutachter: Prof. Dr.-Ing. Wael Adi

| alal Bonny<br>ugust-Bebel-Str.68<br>5187 Karlsruhe                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| iermit erkläre ich an Eides statt, dass ich die von mir vorgelegte Arbeit selbstständig verfasst abe, dass ich die verwendeten Quellen, Internet-Quellen und Hilfsmittel vollständig angegeben abe und dass ich die Stellen der Arbeit – einschließlich Tabellen, Karten und Abbildungen –, ie anderen Werken oder dem Internet im Wortlaut oder dem Sinn nach entnommen sind, auf den Fall unter Angabe der Quelle als Entlehnung kenntlich gemacht habe. |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| alal Bonny                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

# Acknowledgements

First and foremost, I would like gratefully and sincerely to thank my advisor Professor Jörg Henkel for enabling and supporting the research presented in this thesis and for offering an enjoyable work environment for his PhD students. This dissertation could not have been written without his support and guidance.

I am also very grateful to Professor Wael Adi for accepting to be my co-examiner and providing valuable feedback.

I thank members of our chair "Chair for Embedded Systems" at University of Karlsruhe for their feedback and interesting discussions, especially (in alphabetical order) Mohammad Al Faruque, Hussam Amrouch, Lars Bauer, Thomas Ebi, Fridtjof Feldbusch, Fazal Hameed, Nabeel Iqbal, Semeen Rehman, Muhammad Shafique and Sammer Srouji. And all others that influenced the research of this PhD thesis and were not explicitly mentioned here.

I thank the students I supervised during their Master/Diploma thesis for their contributions to the implementation and evaluation of the code compression techniques.

I am also deeply indebted to my family for believing in me and for giving me the inspiration to apply and complete a doctoral degree. Their love, guidance, and encouragement have been a constant source of strength for me.

And last but not least, my heartfelt thanks go out to my beloved better-half, Amani, who has been so patient and supportive since I started the master program. She has been my inspiration and provided encouragement when research progress was slow, and when research felt like spiraling out of control, she brought serenity. It should be no surprise that this dissertation would be impossible without her. I dedicate this thesis to her.

## List of Publications

### Conferences

[C.1] Talal Bonny and Jörg Henkel:

LICT: Left-uncompressed Instructions Compression Technique to Improve the Decoding Performance of VLIW Processors.

In 46th ACM/EDA/IEEE Design Automation Conference (DAC09),

Pages: 903-906, San Fransisco CA, USA, July, 2009 (accepted).

### [C.2] Talal Bonny and Jörg Henkel:

FBT: Filed Buffer Technique to Reduce Code Size for VLIW Processors.

In 26th IEEE/ACM International Conference on Computer-Aided Design (ICCAD'08),

Pages: 549-554, San Jose CA, USA, November, 2008.

#### [C.3] Talal Bonny and Jörg Henkel:

### Instruction Re-encoding Facilitating Dense Embedded Code.

In IEEE/ACM Proceedings of Design Automation and Test in Europe Conference (DATE'08),

Pages: 770-775, Munich, Germany, 2008.

#### [C.4] Talal Bonny and Jörg Henkel:

### Instruction Splitting for Efficient Code Compression.

In ACM/EDA/IEEE Design Automation Conference (DAC07),

Pages: 646-651, San Diego CA, USA, June 2007.

### [C.5] Talal Bonny and Jörg Henkel:

### Efficient Code Density Through Look-up Table Compression.

In IEEE/ACM Proceedings of Design Automation and Test in Europe Conference (DATE'07),

Pages: 809-814, Nice, France, April 2007.

[C.6] Talal Bonny and Jörg Henkel:

Using Lin-Kernighan Algorithm for Look-up Table Compression to Improve Code Density

In ACM/IEEE 16th, Great Lakes Symposium on VLSI (GLSVLSI'06), Pages: 259-265, Philadelphia, USA, April 2006.

### **Journals**

[J.1] Talal Bonny and Jörg Henkel:

Efficient Code Compression for Embedded processors.

In IEEE Transactions on Very Large Scale Integration Systems (TVLSI), Volume 16, Issue 12, Pages: 1696-1707, December 2008.

### **Book Chapter**

[B.1] S. Parameswaran, J. Henkel, A. Janapsatya, T. Bonny and A. Ignjatovic: Design and Run Time Code Compression for Embedded Systems. In Designing Embedded Processors.

pp. 97-128, Springer 2007.ISBN 978-1-4020-5868-4 (HB).ISBN 978-1-4020-5869-1 (e-book).

### Abstract

Increasing embedded systems functionality causes a steep increase in code size. For instance, more than 60MB of software is installed in current state-of-the-art cars [9].

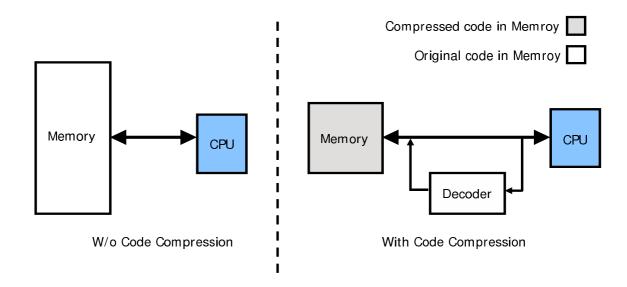

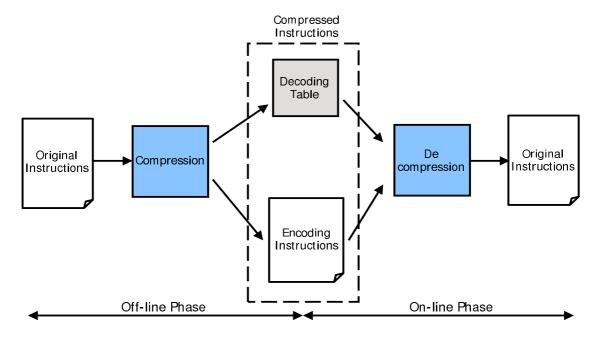

It is often challenging and cumbersome to host vast amount of software in an efficient way within a given hardware resource budget of an embedded system. This may be done by using code compression techniques, which compress the program code off-line (i.e. at design time) and decompress it on-line (i.e. at run time).

Among all statistical compression algorithms, Huffman Coding is one of the best compression techniques since it provably provides the shortest average codeword length [36]. When Huffman Coding is used as a compression technique, Look-up Table(s) are generated to store the original instructions. As the size of the tables becomes large, it may negatively affect the final compression ratio (defined as the ratio of compressed code to uncompressed code). Thus, the Look-up Tables diminish the advantages that could be obtained by compressing the code.

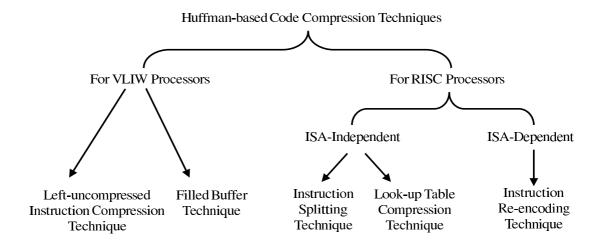

This thesis presents different Huffman-based hardware supported code compression techniques, which can efficiently solve this problem and improve the compression ratio. In addition to that, this the presents a new technique to improve the performance of the hardware decoder. The code compression techniques are targeted two processor architectures, namely RISC and VLIW.

In this thesis, the Look-up Table size is reduced by using the "Look-up Table Compression Technique" for RISC processors. This is done by sorting the entries of the table to decrease the number of bit toggles between each two successive entries.

To show the efficiency of the "Look-up Table Compression Technique", we apply it to two compression schemes, i.e. Dictionary-based Compression Scheme and Statistical Compression Scheme.

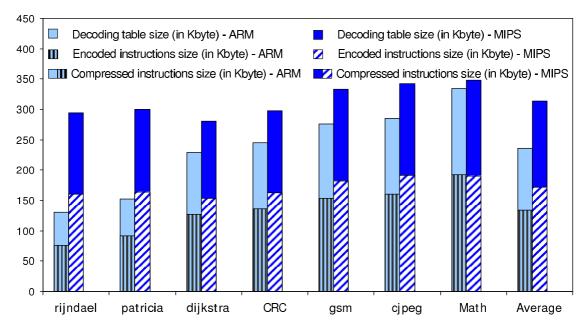

Using the "Look-up Table Compression Technique" reduces the table size by up to 45% and improves the compression ratio on average by more than 25%.

The evaluations are conducted using a representative set of applications from MiBench [20] and are built for three major embedded processor architectures, namely ARM, MIPS

Abstract ix

and PowerPC.

The Look-up Table size may further be reduced if its instructions are encoded efficiently before the "Look-up Table Compression Technique" is applied to it. For that, the second compression technique for RISC processors is introduced, which is called "Instruction Splitting Technique". This technique reduces not only the Look-up Table size but also the size of the encoded instructions generated by using Huffman Coding. It splits the instructions into patterns of varying size before Huffman Coding is applied. Using this technique improves the final compression ratio (including all overhead) by more than 20% compared to known schemes based on *Huffman Coding*. Average compression ratios of 47% and 49% are achieved for ARM and MIPS processors, respectively.

Both our compression techniques "Look-up Table Compression Technique" and "Instruction Splitting Technique" are ISA (Instruction Set Architecture)-Independent, i.e. they can be applied to any processor architecture.

When the ISA is specified, the code compression technique utilizes the information in the opcodes and the instruction format to build the hardware decoder. In this case, the compression ratio will be further improved. For that, ISA-Dependent code compression technique is introduced for RISC processors, which is called "Instruction re-encoding Technique". In this technique, the benefits of re-encoding the unused bits in the instruction format for a specific application are investigated to improve the compression ratio. Re-encoding those bits may reduce the size of decoding table by more than 37%. Compression ratio as low as 44% is achieved (including all overhead that incurs), targeting MIPS and ARM processors.

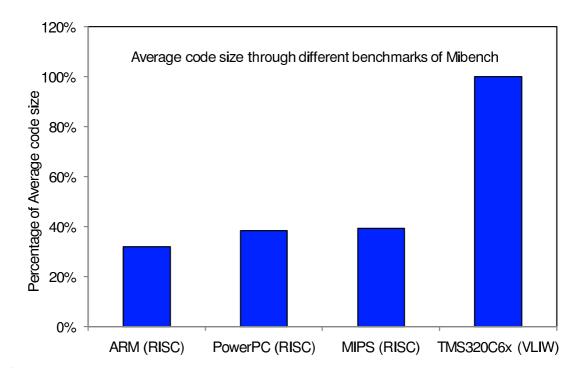

VLIW processors provide higher performance and better efficiency than RISC processors in specific domains like multimedia applications. The drawback of the VLIW processors is the bloating code size of their compiled applications in comparison to the size of the same applications compiled for RISC processors. Therefore, reducing the size of embedded applications is a key issue for VLIW processors.

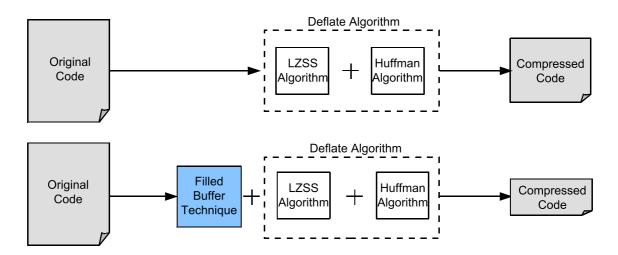

For that, the last code compression technique (Deflate Algorithm [107]) in this thesis is targeting the VLIW processors. It significantly reduces the code size compared to state-of-the-art approaches for VLIW processors.

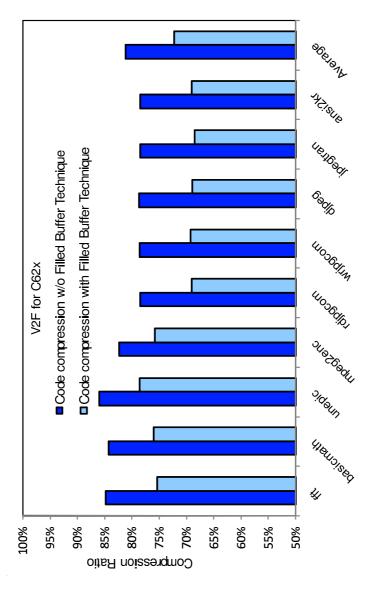

The Deflate Algorithm is enhanced by using a new technique called "Filled Buffer Technique", which can be applied to any Lempel-Ziv family algorithms to improve the compression ratio. This compression technique is independent of the Instruction Set Architecture and can be used by previous compression techniques [82] to further improve the obtained compression ratio. Using the "Filled Buffer Technique" in conjunction with the previous work "V2F" [77] improves the compression ratio by 10%. The evaluations are

Abstract x

conducted using a representative set of benchmarks (from MediaBench and MiBench) and targeting two VLIW processors, namely TMS320C62x and TMS320C64x. Average compression ratios of 61% and 56% are achieved for TMS320C62x and TMS320C64x VLIW processors, respectively.

The main disadvantage of any code compression technique is the system performance penalty because of the extra time required to decode the compressed instructions during run time.

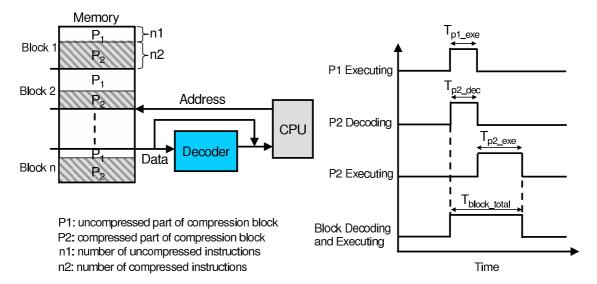

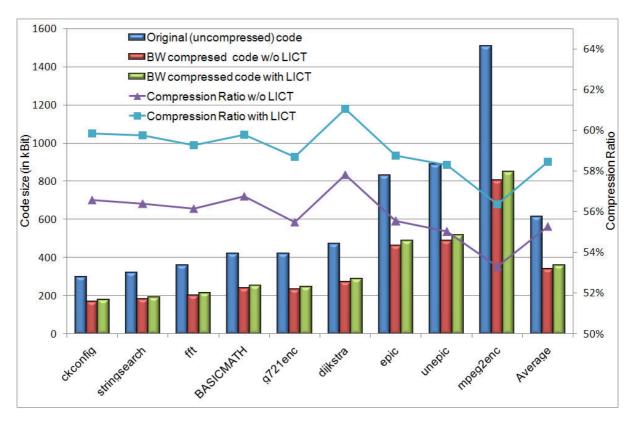

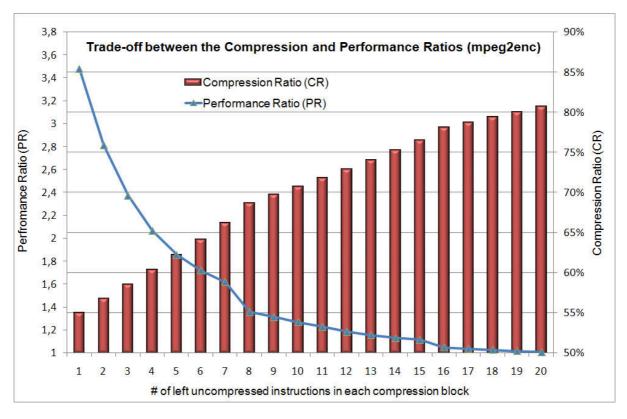

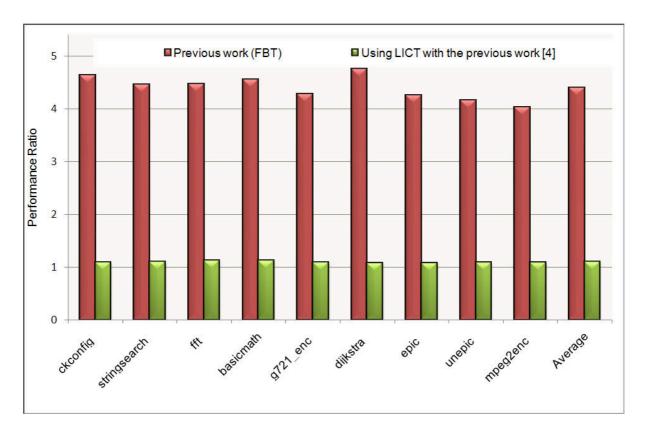

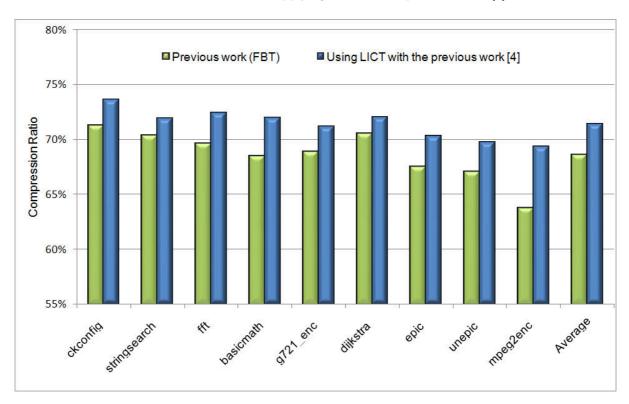

For that, we improve the performance of decoding compressed instructions by using our novel compression technique (LICT: Left-uncompressed Instruction Technique) which can be used in conjunction with any compression algorithm. Using our LICT in conjunction with the Burrows-Wheeler (BW) algorithm [107] improves the performance explicitly (2.5x) with a little impact on the compression ratio (only 3% compression ratio loss).

# Zusammenfassung

Erweiterungen der Funktionalität eingebetteter Systeme führen zu deutlich größeren Programmgrößen. Beispielsweise sind mehr als 60MB Software in einem aktuellen Auto installiert [9]. Es ist oft herausfordernd und mühsam in einem eingebetteten System mit beschränkten Hardwareressourcen eine große Menge an Software effizient bereitzustellen. Dies kann jedoch durch Codekomprimierungstechniken erreicht werden, die das Programm off-line (d.h. zur Entwurfszeit) komprimieren und es on-line (d.h. zur Laufzeit) dekomprimieren.

Unter allen statistischen Komprimierungsalgorithmen ist die Huffmankodierung eine der besten Komprimierungstechniken, da sie wohl die kürzeste durchschnittliche Codewortlänge liefert [36]. Zur Verwendung der Huffmankodierung als Komprimierungstechnik werden Nachschlagetabellen erzeugt, um die originalen Befehle zu speichern. Da diese Nachschlagetabellen groß werden, kann die endgültige Komprimierungsrate, die durch das Größenverhältnis von komprimiertem Code zu unkomprimiertem Code definiert ist, negativ beeinflusst werden. Daher verringern die Nachschlagetabellen die Vorteile, die durch Codekomprimierung erreicht werden könnten.

Diese Arbeite präsentiert Huffman-basierte hardwareunterstützte Codekomprimierungstechniken, die dieses Problem effizient lösen können und die Komprimierungsrate verbessern. Die Codekomprimierungstechniken sind auf zwei Prozessorarchitekturen ausgerichtet, nämlich RISC und VLIW.

Wir reduzieren die Größe der Nachschlagetabellen durch die "Look-up Table Compression Technique" für RISC Prozessoren. Dies wird durch eine Sortierung der Tabelleneinträge erreicht, mit der die Anzahl der Bitunterschiede zwischen zwei aufeinander folgenden Einträgen verringert werden.

Um die Effizienz der "Look-up Table Compression Technique" zu zeigen, wenden wir sie auf zwei Komprimierungsschemata an: Wörterbuch-basierte und statische Komprimierungsschemata.

Die Verwendung unserer "Look-up Table Compression Technique" reduziert die Tabellengröße um bis zu 45% und verbessert die Kompressionsrate im Durchschnitt um mehr

Zusammenfassung xiii

als 25%. Die Evaluierungen wurden unter Verwendung einer repräsentativen Menge an Applikationen aus MiBench [20] für drei bedeutende eingebettete Prozessorarchitekturen (ARM, MIPS und PowerPC) durchgeführt.

Die Größe der Nachschlagetabellen kann weiter reduziert werden, wenn die Instruktionen effizient enkodiert werden, bevor die "Look-up Table Compression Technique" angewendet wird. Dafür präsentieren wir unsere zweite Codekomprimierungstechnik für RISC Prozessoren, die "Instruction Splitting Technique" heißt. Diese Technik reduziert nicht nur die Größe der Nachschlagetabelle, sondern außerdem auch die Größe der enkodierten Instruktionen, die durch die Huffmankodierung erzeugt werden. Sie unterteilt die Instruktionen in Muster unterschiedlicher Größe, bevor die Huffmankodierung angewendet wird. Durch die Verwendung dieser Technik wird die endgültige Komprimierungsrate (inklusive aller Extraaufwendungen) im Vergleich zu bekannten, auf Huffmankodierung bestehenden Verfahren, um mehr als 20% verbessert. Wir erreichen eine durchschnittliche Komprimierungsrate von 47% und 49% für ARM, beziehungsweise MIPS Prozessoren.

Beide Komprimierungstechniken ("Look-up Table Compression Technique" und "Instruction Splitting Technique") sind ISA unabhängig, d.h. sie können für jede Prozessorarchitektur verwendet werden.

Wenn die ISA bekannt ist, verwendet die Codekomprimierungstechnik die Information in den Opcodes oder dem Instruktionsformat, um den Hardwaredekodierer zu erstellen. In diesem Fall wird die Komprimierungsrate weiter verbessert. Dafür präsentieren wir unsere ISA-abhängige Kodekomprimierungstechnik für RISC Prozessoren, die "Instruction re-encoding Technique" heißt. In dieser Technik untersuchen wir die Vorteile, die unbenutzten Bits im Instruktionsformat für eine bestimmte Applikation neu zu kodieren, um so die Komprimierungsrate zu verbessern. Diese Bits neu zu kodieren kann die Größe der Kodierungstabelle um mehr als 37% verringern. Wir erreichen Komprimierungsraten (inklusive aller Extraaufwendungen) bis runter zu 44% für MIPS und ARM Prozessoren.

VLIW Prozessoren erbringen in bestimmten Domänen wie Multimediaapplikationen höhere Performanz und bessere Effizienz als RISC Prozessoren. Der Nachteil der VLIW Prozessoren ist die deutlich vergrößerte Codemenge der kompilierten Applikationen im Vergleich zu der Größe derselben Applikation die für RISC Prozessoren übersetzt wurde. Daher ist die Verringerung der Codegröße ein Hauptanliegen für VLIW Prozessoren.

Dafür führen wir unsere letzte Codekomprimierungstechnik (Deflate Algorithmus [107]) in dieser Arbeit speziell für VLIW Prozessoren ein. Sie verringert die Codegrößen im Vergleich zu aktuellen Ansätzen für VLIW Prozessoren deutlich.

Wir erweitern den Deflate Algorithmus durch die neue "Filled Buffer Technique", die auf

Zusammenfassung xiv

jeden Algorithmus der Lempel-Ziv Familie angewandt werden kann, um die Komprimierungsrate im Durchschnitt um mehr als 13% - im Vergleich zur ausschließlichen Anwendung des Deflate Algorithmus - verbessern. Diese Komprimierungstechnik ist unabhängig von dem Befehlssatz (ISA) und kann von früheren Komprimierungstechniken [82] benutzt werden, um die erreichte Komprimierungsrate weiter zu verbessern. Die Verwendung unserer "Filled Buffer Technique" zusammen mit "V2F" [77] verbessert die Kompressionsrate um 10%. Wir haben Evaluierungen anhand einer repräsentativen Menge an Benchmarks (aus MediaBench und MiBench) durchgeführt und unser Schema auf zwei VLIW Prozessoren angewandt, nämlich TMS320C62x und TMS320C64x. Wir erreichten bei Verwendung des Deflate Algorithmus eine gesamtKompressionsrate bis runter zu 44% (im Durchschnitt 61% bzw. 56% für den TMS320C62x bzw. TMS320C64x).

# Contents

| A              | cknov                    | rledgements                                                                                                                                                                                                                                                                                                                                                               | iv                                                       |

|----------------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| Li             | st of                    | Publications                                                                                                                                                                                                                                                                                                                                                              | vi                                                       |

| $\mathbf{A}$ l | bstra                    | et                                                                                                                                                                                                                                                                                                                                                                        | viii                                                     |

| $\mathbf{Z}$ ι | ısam                     | nenfassung                                                                                                                                                                                                                                                                                                                                                                | xii                                                      |

| Co             | onter                    | $5\mathbf{S}$                                                                                                                                                                                                                                                                                                                                                             | xvi                                                      |

| Li             | st of                    | Figures                                                                                                                                                                                                                                                                                                                                                                   | xx                                                       |

| $\mathbf{Li}$  | st of                    | Γables x                                                                                                                                                                                                                                                                                                                                                                  | xiv                                                      |

| Li             | st of                    | Algorithms                                                                                                                                                                                                                                                                                                                                                                | xvi                                                      |

| 1              | 1.1<br>1.2<br>1.3<br>1.4 | Motivation  Motivation  Introduction and Background  1.2.1 Measurements and Terms  1.2.2 Types of Compression  Scope of Our Research Work in this Thesis  Outline of Thesis                                                                                                                                                                                               | 1<br>1<br>2<br>3<br>5<br>6<br>8                          |

| 2              | Bac 2.1 2.2 2.3          | Code Compression and Data Compression  Placement of Hardware Decoder  Basis Classification of Code Compression Techniques  2.3.1 Dictionary-based Compression Techniques  2.3.1.1 Instructions Sequence Dictionary-based Technique  2.3.1.2 Lempel and Ziv  2.3.1.3 LZSS Algorithm  2.3.2 Statistical Compression Techniques  2.3.2.1 Huffman Coding  Embedded Processors | 11<br>14<br>15<br>15<br>15<br>17<br>18<br>20<br>20<br>22 |

|                | ∠. <del>'1</del>         | 2.4.1.1 MIPS Processor                                                                                                                                                                                                                                                                                                                                                    | 22<br>23<br>25                                           |

*Contents* xvii

|   |     |        | 2.4.1.3 PowerPC Processor                                        | 26 |

|---|-----|--------|------------------------------------------------------------------|----|

|   |     | 2.4.2  |                                                                  | 27 |

|   |     |        |                                                                  | 28 |

|   |     |        |                                                                  | 30 |

|   |     |        |                                                                  | 34 |

|   |     | 2.4.3  |                                                                  | 35 |

|   |     |        |                                                                  |    |

| 3 |     | ated W |                                                                  | 39 |

|   | 3.1 |        | 1 1                                                              | 39 |

|   |     | 3.1.1  |                                                                  | 39 |

|   |     | 3.1.2  |                                                                  | 40 |

|   |     | 3.1.3  |                                                                  | 42 |

|   |     |        | 1                                                                | 43 |

|   |     |        | 1                                                                | 45 |

|   | 0.0 | G1     |                                                                  | 46 |

|   | 3.2 |        |                                                                  | 46 |

|   |     | 3.2.1  | v 1                                                              | 47 |

|   |     | 3.2.2  | Classification by ISA-Dependability                              | 60 |

| 4 | Cod | le Con | apression for RISC Processors                                    | 65 |

|   | 4.1 |        | -                                                                | 67 |

|   |     | 4.1.1  | Look-up Table Compression Technique for Dictionary-based Com-    |    |

|   |     |        | - · · · · · · · · · · · · · · · · · · ·                          | 68 |

|   |     |        | 4.1.1.1 Generating the Compressed Instructions (Encoded Instruc- |    |

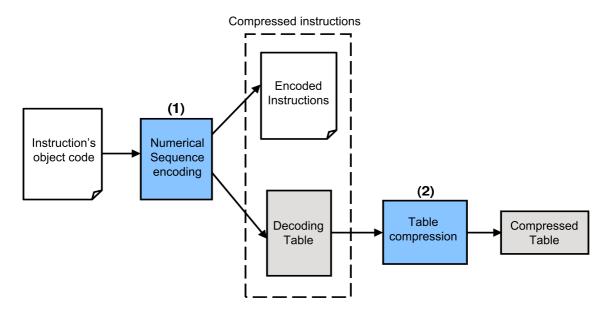

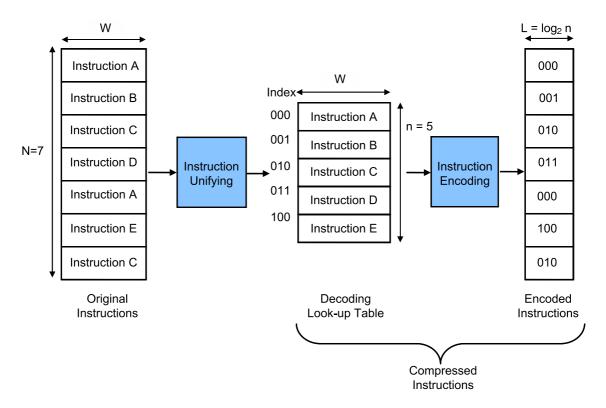

|   |     |        | tions and Decoding Table)                                        | 69 |

|   |     |        | 4.1.1.2 Compressing the Decoding Table                           | 70 |

|   |     |        | 4.1.1.3 Hardware Implementation                                  | 75 |

|   |     | 4.1.2  | Look-up Table Compression Technique for Statistical Compression  |    |

|   |     |        | Schemes                                                          | 76 |

|   |     |        | 9                                                                | 78 |

|   |     |        | 4.1.2.2 Canonical Huffman Coding                                 | 78 |

|   |     |        | 4.1.2.3 Minimizing the Cost of the Look-up Tables                | 80 |

|   |     |        | 4.1.2.4 Hardware Implementation                                  | 83 |

|   |     |        | 4.1.2.5 Experimental Results                                     | 84 |

|   |     | 4.1.3  | Instruction Splitting Technique                                  | 90 |

|   |     |        | 4.1.3.1 Splitting Algorithm                                      | 92 |

|   |     |        | 4.1.3.2 Applying Compression on Split Instructions               | 93 |

|   |     |        | 4.1.3.3 Decompression via Hardware                               | 96 |

|   |     |        | 4.1.3.4 Experiments and Results                                  | 97 |

|   |     | 4.1.4  | Discussion                                                       | 01 |

|   | 4.2 | ISA-D  | ependent Compression Technique                                   | 01 |

|   |     | 4.2.1  | Steps of Instruction Re-encoding Compression Technique 1         | 02 |

|   |     |        | 4.2.1.1 Analyzing the Instruction Format                         | 03 |

|   |     |        | 4.2.1.2 Huffman Coding Algorithm                                 | 08 |

|   |     |        | 4.2.1.3 Reducing the Size of Decoding Table                      | 08 |

|   |     | 4.2.2  | Hardware Decoder                                                 | 11 |

Contents xviii

|              |     | 4.2.3 Experimental Results                                           | 112 |

|--------------|-----|----------------------------------------------------------------------|-----|

|              | 4.3 | Discussion                                                           | 115 |

|              | 4.4 | Comparing to Previous Work                                           | 117 |

| 5            | Cod | e Compression for VLIW Processors                                    | 119 |

|              | 5.1 | Our Code Compression Technique                                       | 122 |

|              |     | 5.1.1 Deflate Compression Algorithm                                  | 122 |

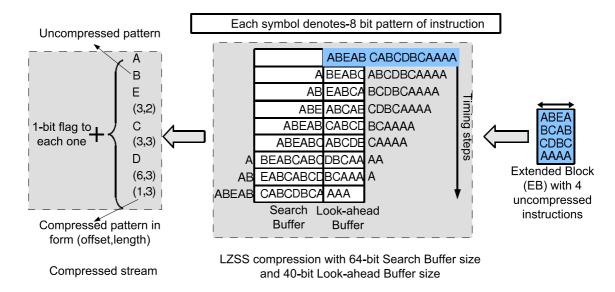

|              |     | 5.1.2 Our Filled Buffer Technique                                    | 125 |

|              | 5.2 | Decompression Architecture Design                                    | 128 |

|              |     | 5.2.1 Huffman Hardware Decoder                                       | 128 |

|              |     | 5.2.2 LZSS Hardware Decoder                                          | 129 |

|              | 5.3 | Experiments and Results                                              | 129 |

|              |     | 5.3.1 Statistics of the Benchmarks                                   | 130 |

|              |     | 5.3.2 Compression Ratios Using the Deflate Algorithm                 | 131 |

|              |     | 5.3.3 Compression Ratios Using the LZMA Algorithm                    | 132 |

|              |     | 5.3.4 Performance                                                    | 134 |

|              |     | 5.3.5 Improving the Results of Previous Work Using our Filled Buffer |     |

|              |     | Technique                                                            | 135 |

|              | 5.4 | Discussion                                                           | 136 |

|              | 5.5 | Comparing to Previous Work                                           | 138 |

| 6            | Cod | e Compression to Improve the Performance                             | 141 |

| U            | 6.1 | Basics of code/data compression                                      | 142 |

|              | 0.1 | 6.1.1 Traditional Code Compression Techniques                        | 143 |

|              | 6.2 | Left-uncompressed Instruction Compression Technique (LICT)           | 144 |

|              | 6.3 | Burrows-Wheeler Code Compression Algorithm                           | 147 |

|              | 0.5 | 6.3.1 The BW Encoding Steps                                          | 148 |

|              |     | 6.3.2 The BW Decoding Steps                                          | 149 |

|              | 6.4 | Applying $LICT$ to the FBT                                           | 150 |

|              | 6.5 |                                                                      | 150 |

|              | 0.5 | Experiments and Results                                              | 150 |

| 7            | Con | clusion                                                              | 157 |

|              | 7.1 | Thesis Summary                                                       | 157 |

|              | 7.2 | Future Work                                                          | 158 |

|              |     |                                                                      |     |

| $\mathbf{A}$ | MIF | PS Instruction Set                                                   | 161 |

|              | A.1 | Load and Store                                                       | 162 |

|              | A.2 | Computational Instructions                                           | 162 |

|              | A.3 | Jump and Branch                                                      | 164 |

|              | A.4 | Miscellaneous                                                        | 165 |

|              | A.5 | Coprocessor                                                          | 165 |

|              |     |                                                                      |     |

167

Bibliography

# List of Figures

| 1.1  | Overview of an embedded system                                            |

|------|---------------------------------------------------------------------------|

| 1.2  | Compression (off-line) and decompression (on-line) phases                 |

| 1.3  | Scope of our research work in this thesis                                 |

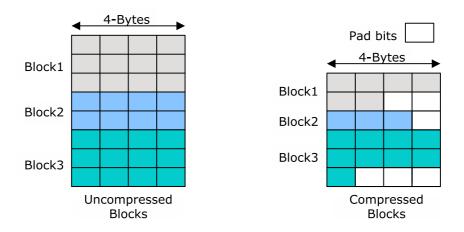

| 2.1  | Alignment of compressed blocks in memory boundary                         |

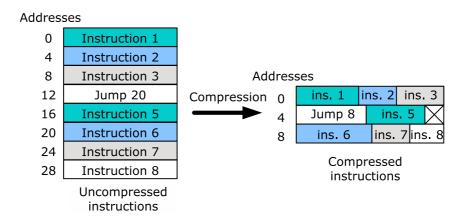

| 2.2  | Solving the branch target problem for variable encoded instructions 13    |

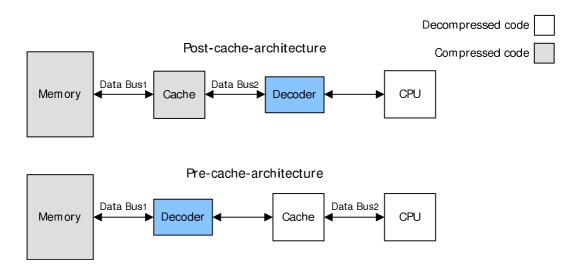

| 2.3  | Placement possibilities of the hardware decoder                           |

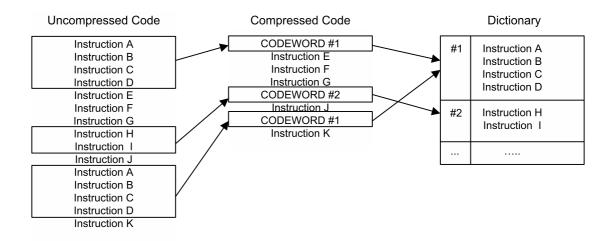

| 2.4  | Dictionary-based compression technique                                    |

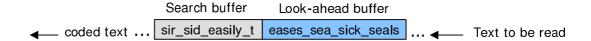

| 2.5  | LZ77 sliding window                                                       |

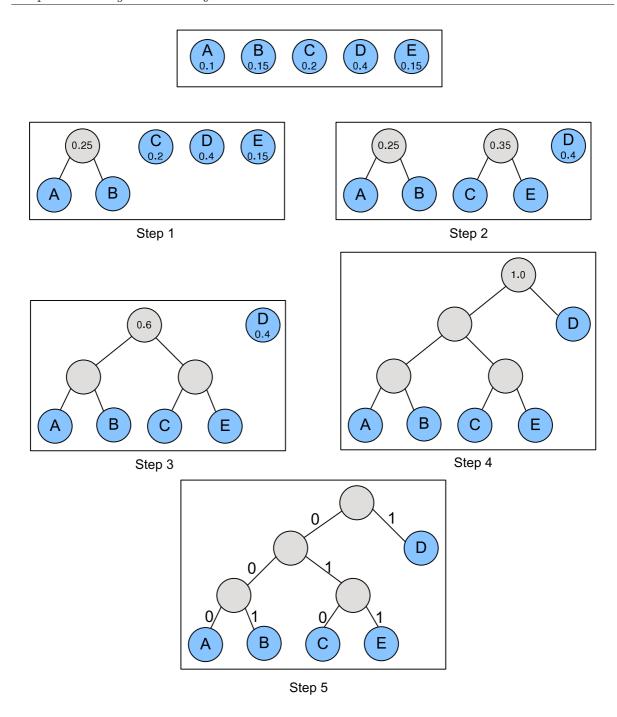

| 2.6  | Huffman Code Example                                                      |

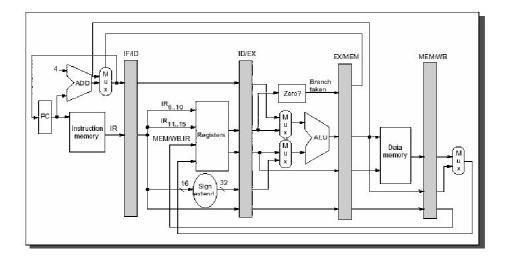

| 2.7  | General Pipeline stages of a RISC processor                               |

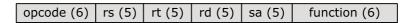

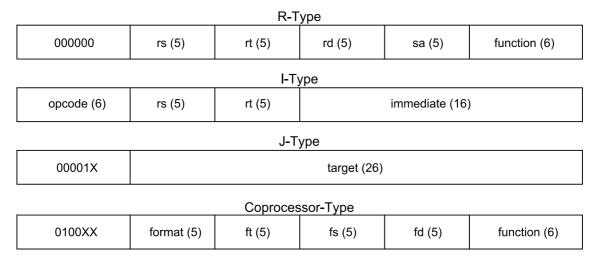

| 2.8  | MIPS instruction format of R-Type group                                   |

| 2.9  | MIPS instruction format of I-Type group                                   |

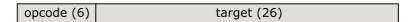

| 2.10 | MIPS instruction format of J-Type group                                   |

| 2.11 | MIPS instruction format of Coprocessor-Type group                         |

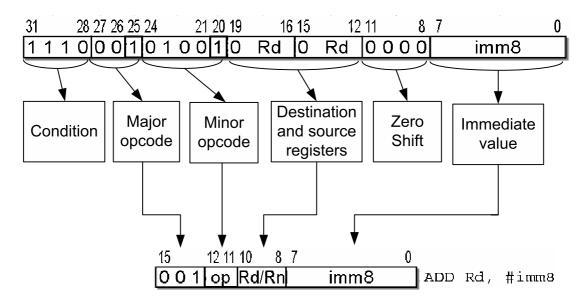

| 2.12 | Basic encoding format of ARM instructions                                 |

| 2.13 | ARM instruction set summary                                               |

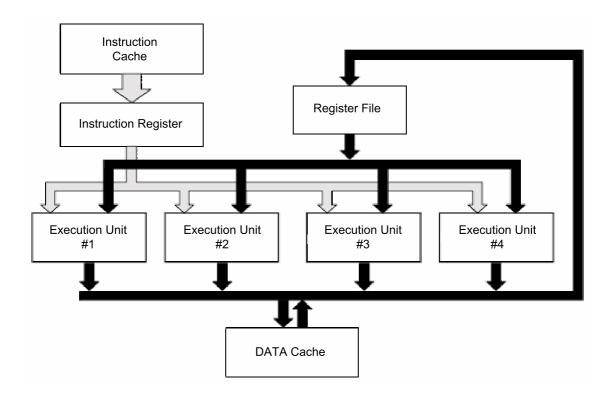

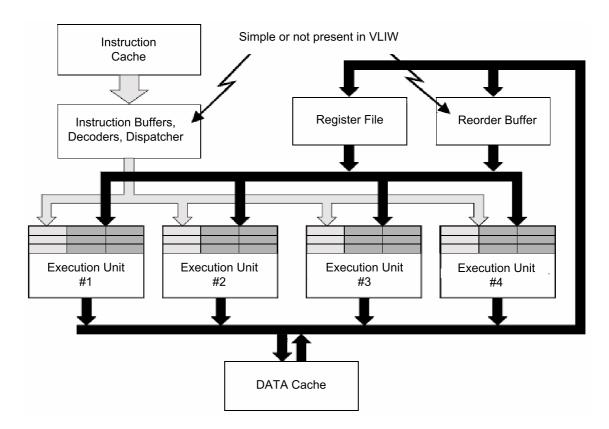

| 2.14 | Block diagram of a generic VLIW Processor                                 |

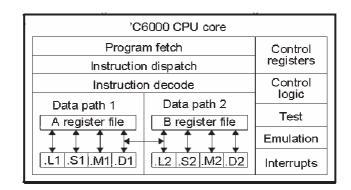

| 2.15 | Block diagram of the TMS320C62x CPU                                       |

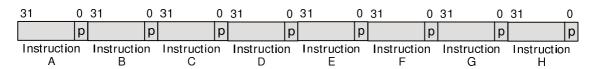

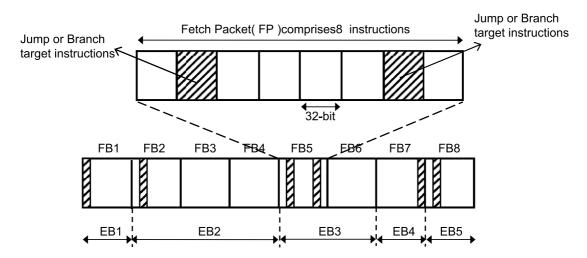

| 2.16 | Basic Format of Fetch Packet                                              |

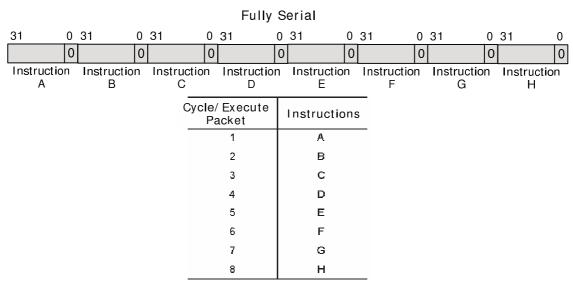

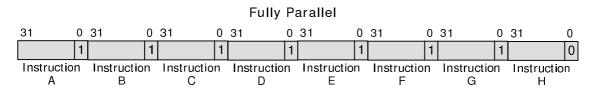

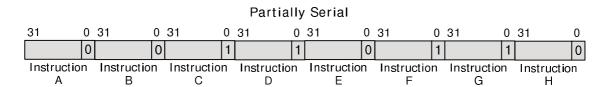

| 2.17 | Fully Serial p-Bit Pattern in a Fetch Packet                              |

| 2.18 | Fully Parallel p-Bit Pattern in a Fetch Packet                            |

| 2.19 | Partially Serial p-Bit Pattern in a Fetch Packet                          |

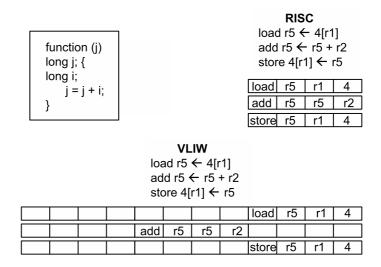

| 2.20 | Example for implementing a function in RISC and VLIW processors 30        |

| 2.21 | Block diagram of a superscalar RISC Processor                             |

| 3.1  | Mapping of ARM instruction format of ADD to Thumb                         |

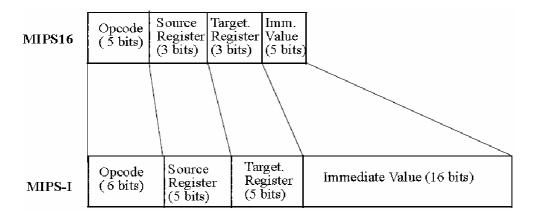

| 3.2  | Mapping of MIPS-I instruction format to the compressed form of MIPS16. 49 |

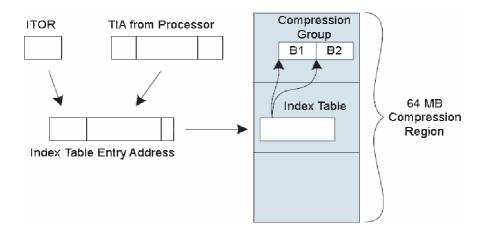

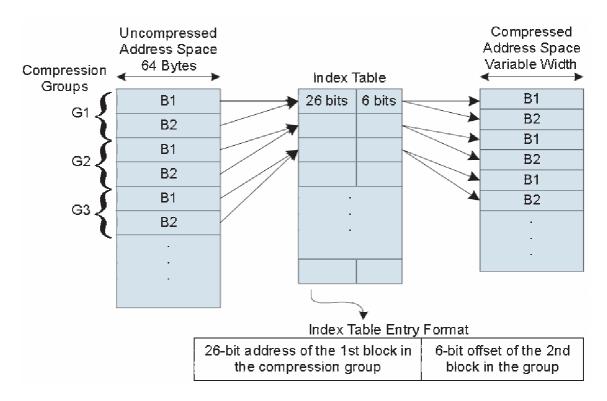

| 3.3  | Locating compression blocks in CodePack                                   |

| 3.4  | Index Table mapping of Target Instruction Address (TIA) to compressed     |

|      | memory                                                                    |

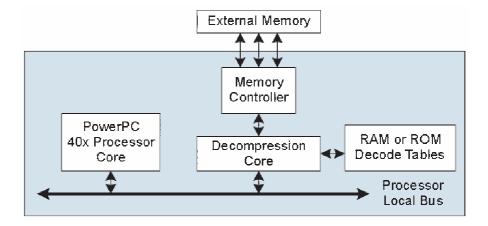

| 3.5  | An integrated design including the CodePack decompression core 48         |

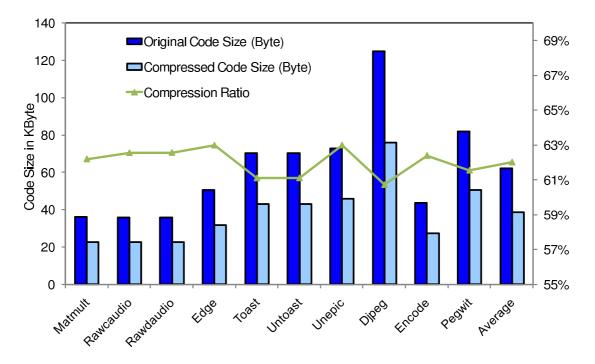

| 3.6  | CodePack Compression Ratio                                                |

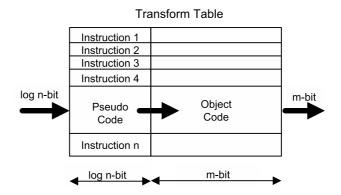

| 3.7  | Transform table of the compression technique in [27]                      |

| 3.8  | compressed Line Structure in [15]                                         |

| 3.9  | Instruction fetch path in [109] for VLIW processor-based systems 50       |

| 3.10 | Identifying common substrings in [61]                                     |

| 3.11 | Overview of compressed program processor in [28]                                                                                                                 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.12 | Proposed codeword format for the extended dictionary-based compression                                                                                           |

|      | scheme in [101]                                                                                                                                                  |

|      | Encoding process of SAMC [101]                                                                                                                                   |

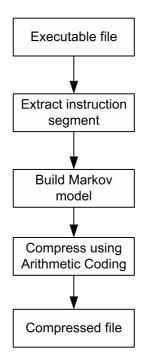

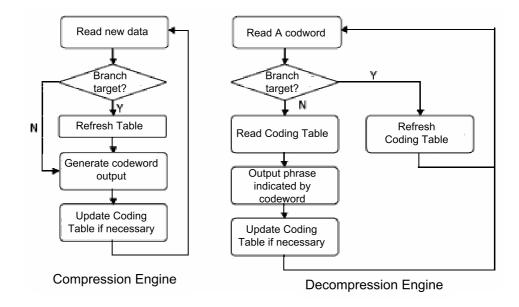

|      | Flowchart of compression and decompression methods [81]                                                                                                          |

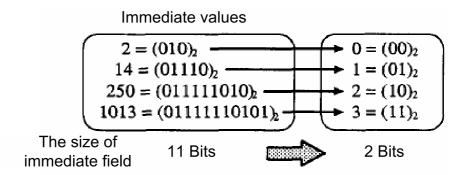

| 3.15 | Encoding of immediate values in [106]                                                                                                                            |

| 3.16 | Format of Compressed Program Code in [114]                                                                                                                       |

| 4.1  | Comparing the size of the Huffman decoding table to the size of the Huffman compressed instructions for different benchmark programs and processor architectures |

| 4.2  | Compression steps for the Dictionary-based Scheme                                                                                                                |

| 4.3  | Example for generating compressed instructions in the Dictionary-based Scheme                                                                                    |

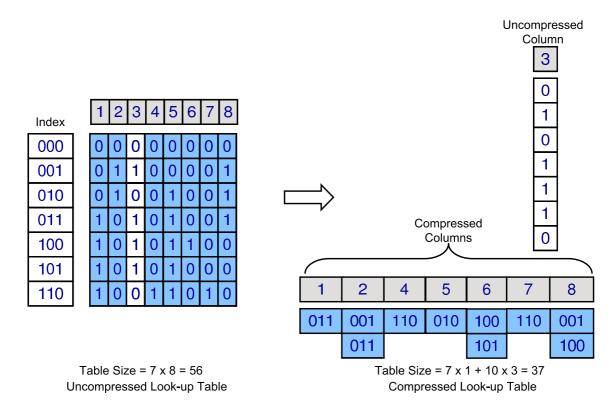

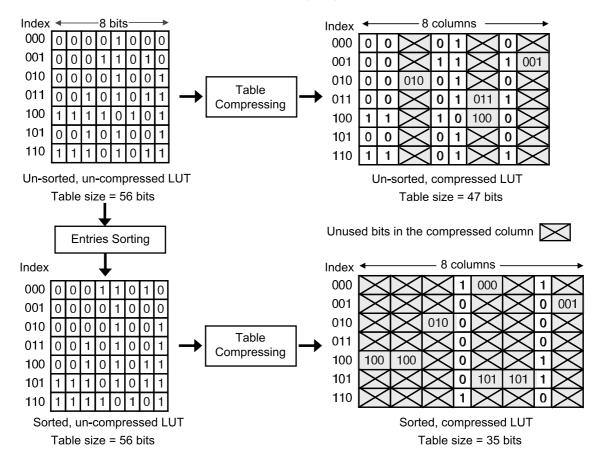

| 4.4  | Simple example for compressing table with 8 bits symbols                                                                                                         |

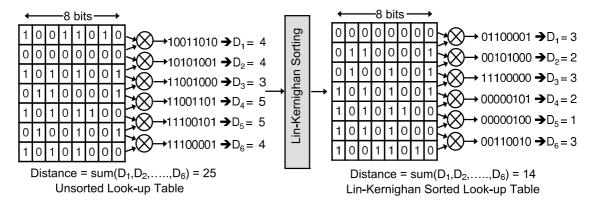

| 4.5  | Example for sorting table with 8-bits symbols using Table Entries Sorting algorithm (TES)                                                                        |

| 4.6  | Sorted and Un-sorted Look-up Table (LUT) compression                                                                                                             |

| 4.7  | Look-up Table decoder                                                                                                                                            |

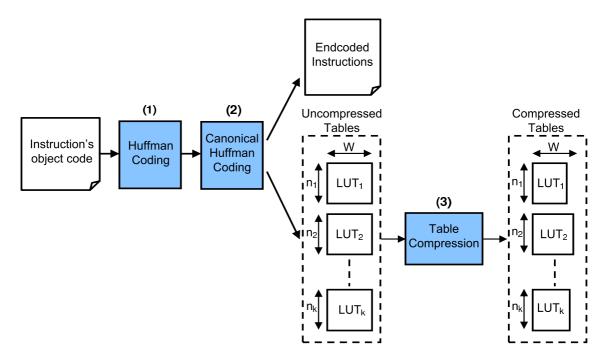

| 4.8  | Compression steps for the Statistical compression scheme                                                                                                         |

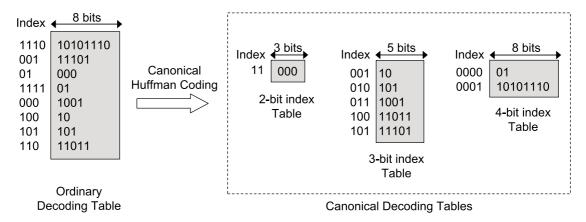

| 4.9  | Look-up Tables generated from Canonical Huffman Coding                                                                                                           |

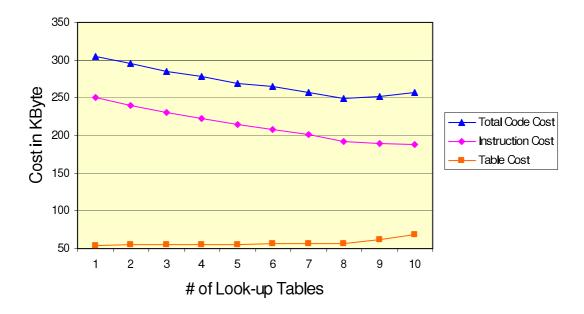

| 4.10 | Optimizing the number of Look-up Tables                                                                                                                          |

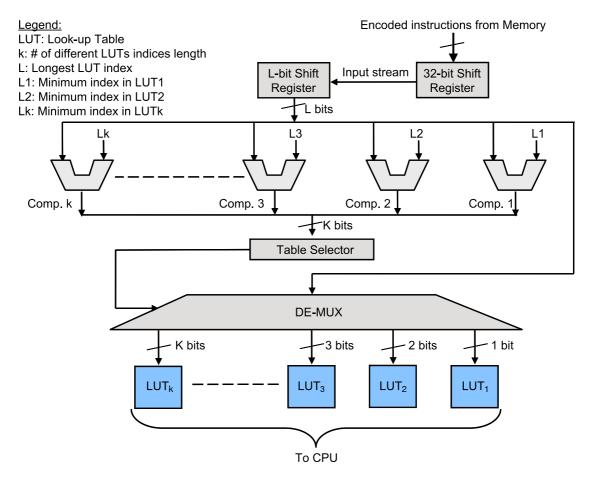

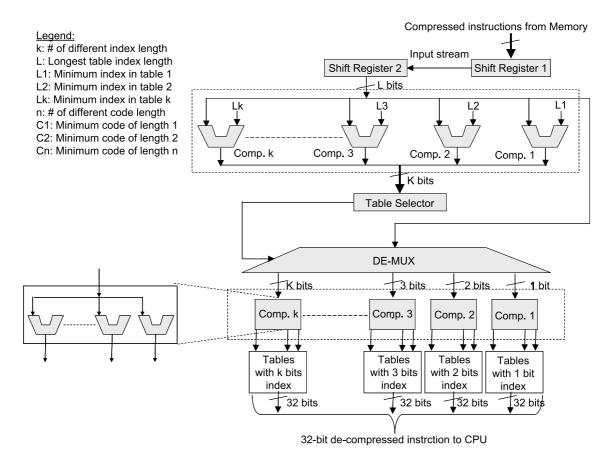

|      | Canonical Huffman Decoder                                                                                                                                        |

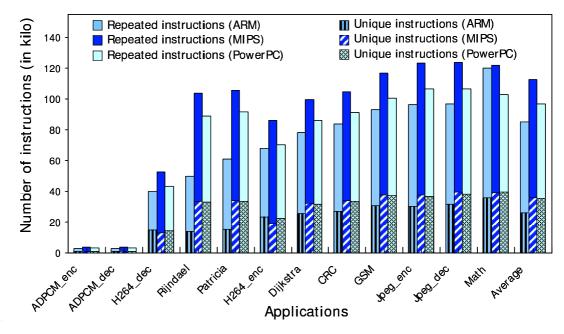

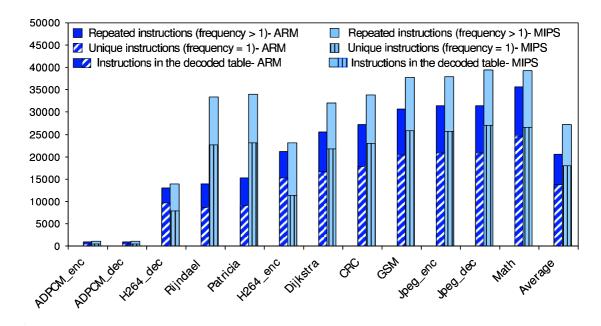

|      | Number of original (repeated and unique) instructions for ARM, MIPS and PowerPC                                                                                  |

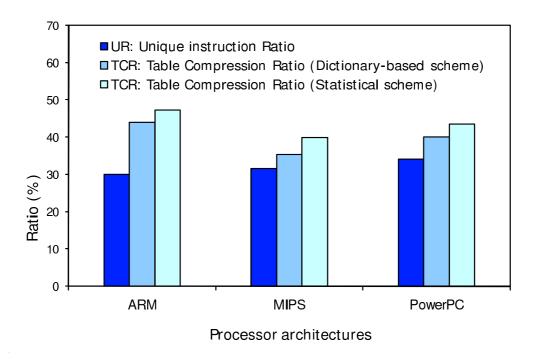

| 4.13 | The average unique instruction and Table Compression Ratios 85                                                                                                   |

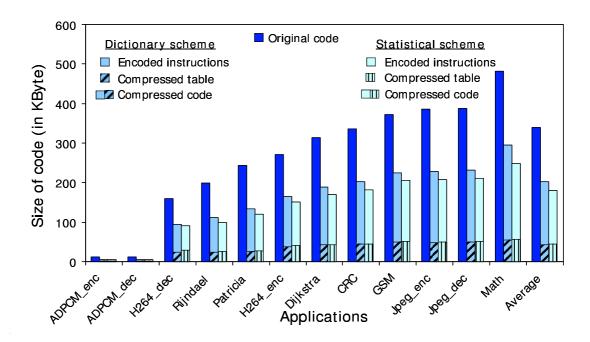

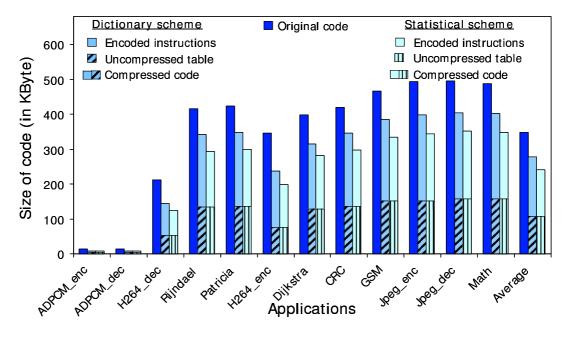

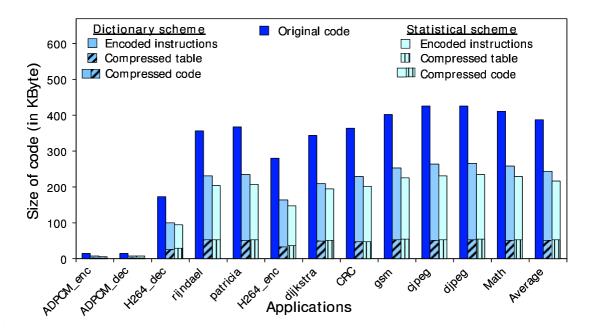

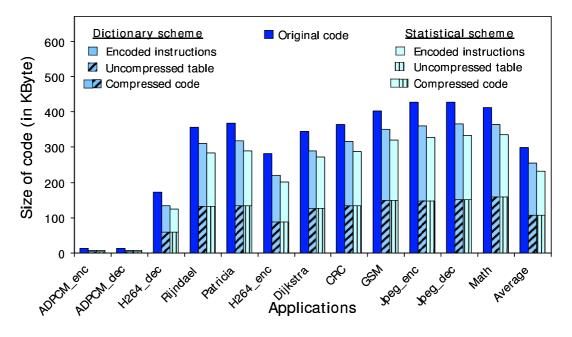

|      | Compression results for ARM (the decoding table is compressed) 87                                                                                                |

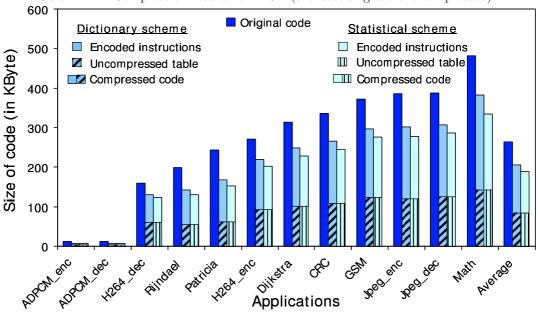

|      | Compression results for ARM (the decoding table is not compressed) 87                                                                                            |

|      | Compression results for MIPS (the decoding table is compressed) 88                                                                                               |

|      | Compression results for MIPS (the decoding table is not compressed) 88                                                                                           |

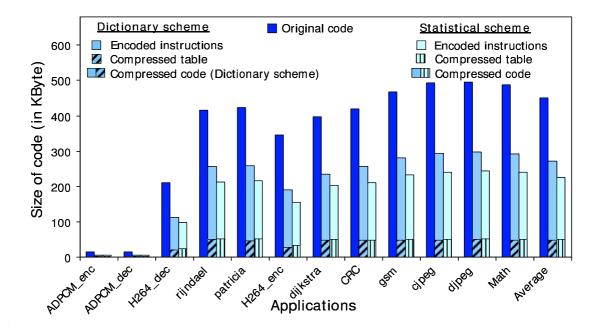

|      | Compression results for PowerPC (the decoding table is compressed) 89                                                                                            |

|      | Compression results for PowerPC (the decoding table is not compressed) 89                                                                                        |

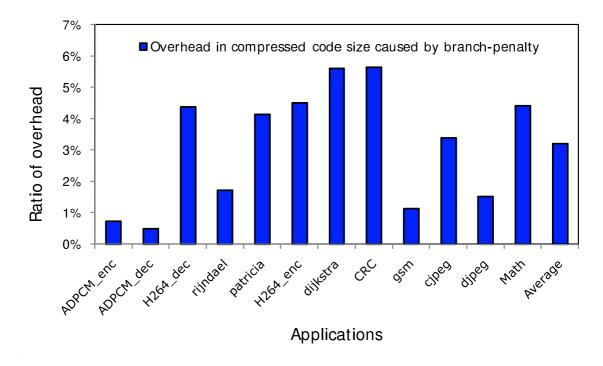

|      | Overhead in compressed code size caused by branch-penalty 90                                                                                                     |

|      | Number of "unique instructions" and "repeated instructions" within the decoding table                                                                            |

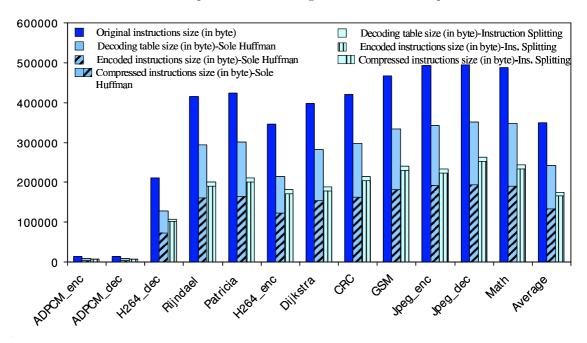

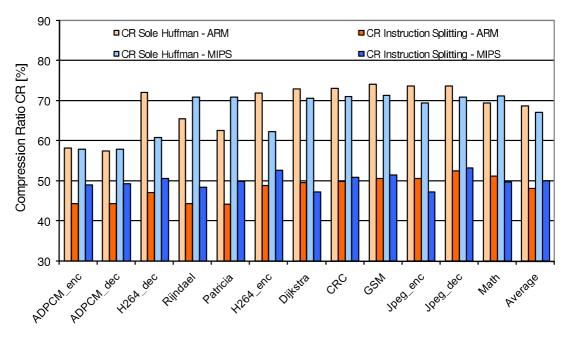

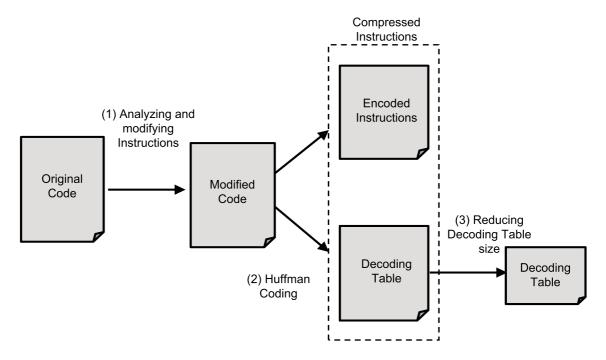

| 1 22 | Example: Code compression using Huffman Coding only (upper part) and                                                                                             |

|      | our "Instruction Splitting Technique" (lower part)                                                                                                               |

| 4.23 | Example: Applying Canonical Huffman Coding to improve sparseness of decoding table as opposed to traditional Huffman Coding                                      |

| 4.24 | Decoding i.e. decompression hardware                                                                                                                             |

|      | The compressed and the original instructions compiled for ARM 98                                                                                                 |

|      | The compressed and the original instructions compiled for MIPS 98                                                                                                |

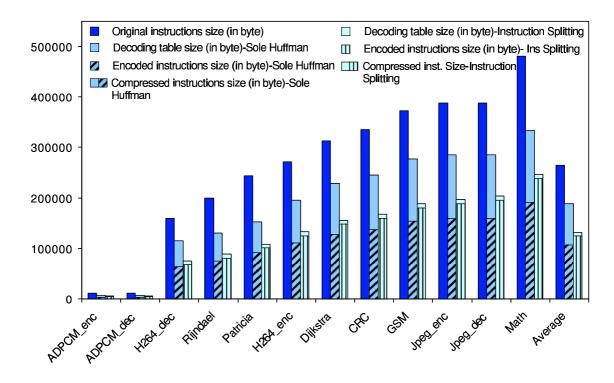

|      | Compression ratios using sole Huffman Coding and our scheme for ARM and MIPS                                                                                     |

| 4.28 | Performance of the "Instruction Splitting Technique"                                                                                                             |

|      | Steps of "Instruction Re-encoding Technique"                                                                                                                     |

|      | 2007-21                                                                                                                                                          |

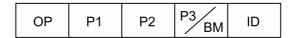

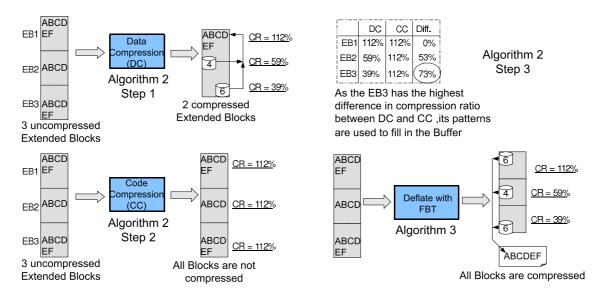

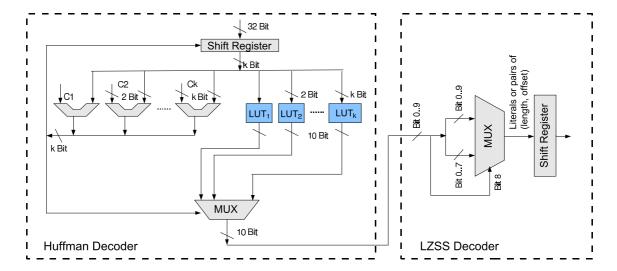

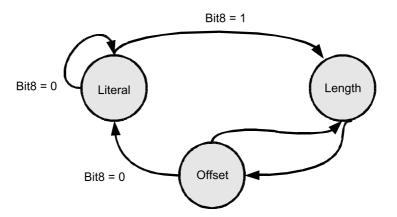

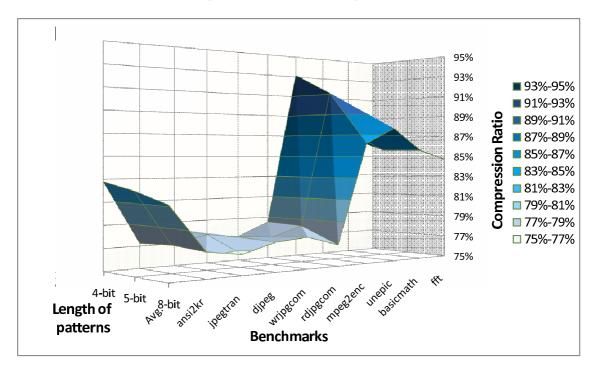

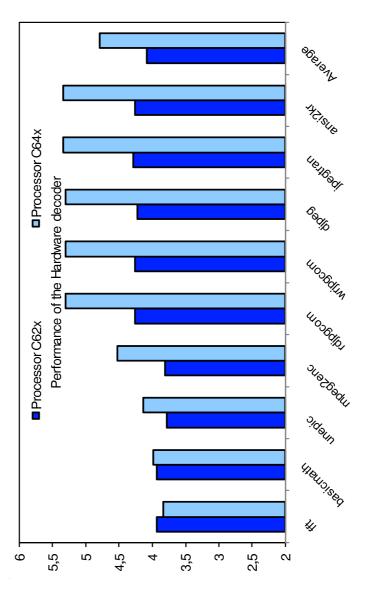

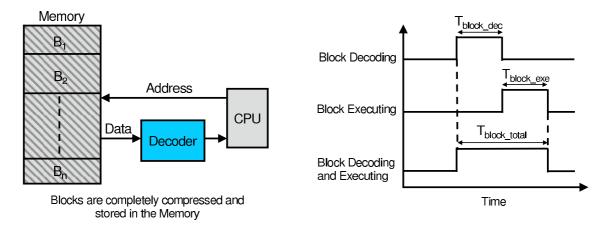

| <ul> <li>4.31 Example for re-encoding the opcode in the "R-Type" group.</li> <li>4.32 Example for ARM instruction groups</li> <li>4.33 Replacing unused fields in the "R-Type" group with don't care symbols X' for different instructions</li> <li>4.34 Steps for reducing the size of the decoding table</li> <li>4.35 Example for re-encoding the 'X' fields: make them identical to the preceding instruction.</li> <li>4.36 Hardware decoder of the "Instruction Re-encoding Technique"</li> <li>4.37 Ratio of re-encodable bits size compared to original code size for ARM and MIPS processors</li> <li>4.38 Size of decoding table for ARM and MIPS processors</li> <li>4.39 Compression ratios for ARM and MIPS processors</li> <li>4.40 Time taken by the original and the compressed code for ARM processor (in Million of cycles)</li> <li>5.1 Percentage of the average code size through different benchmarks of MiBencl on different processor architectures</li> <li>5.2 Example for exploring the Extended Blocks (EB) form "Fetch Packets" (FP) for compression</li> <li>5.3 Steps for our code compression technique</li> <li>5.4 Example for compressing an Extended Block using the LZSS Algorithm in conjunction to the Filled Buffer Technique</li> <li>5.5 State diagram of the LZSS decoder</li> <li>5.6 Number of original instructions, Basic and Extended Blocks for the benchmarks compiled for C62x and C64x processors</li> <li>5.9 Compression Ratios for different Benchmarks compressed using the LZSS Algorithm for C62x VLIW processor</li> <li>5.10 Compression ratios using three different models of the Deflate Algorithm for C62x VLIW processor</li> <li>5.11 Compression ratios using three different models of the Deflate Algorithm for C62x VLIW processor</li> <li>5.12 Compression ratios using three different models of the Deflate Algorithm for C64x VLIW processor</li> <li>5.13 Pipeline stages of the Deflate hardware decoder</li> <li>5.14 Performance of the Deflate hardware decoder</li> <li>5.15 Compression ratios using our Filled Buffer technique combined wi</li></ul> | 4.30 | MIPS instruction groups                                                     | 104 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----------------------------------------------------------------------------|-----|

| <ul> <li>4.32 Example for ARM instruction groups</li> <li>4.33 Replacing unused fields in the "R-Type" group with don't care symbols 'X' for different instructions</li> <li>4.34 Steps for reducing the size of the decoding table</li> <li>4.35 Example for re-encoding the 'X' fields: make them identical to the preceding instruction</li> <li>4.36 Hardware decoder of the "Instruction Re-encoding Technique"</li> <li>4.37 Ratio of re-encodable bits size compared to original code size for ARM and MIPS processors</li> <li>4.38 Size of decoding table for ARM and MIPS processors</li> <li>4.39 Compression ratios for ARM and MIPS processors</li> <li>4.40 Time taken by the original and the compressed code for ARM processor (in Million of cycles)</li> <li>5.1 Percentage of the average code size through different benchmarks of MiBenel on different processor architectures</li> <li>5.2 Example for exploring the Extended Blocks (EB) form "Fetch Packets" (FP) for compression</li> <li>5.3 Steps for our code compression technique</li> <li>5.4 Example for compressing an Extended Block using the LZSS Algorithm</li> <li>5.5 Example to compress 3 Extended Blocks using the Deflate Algorithm in conjunction to the Filled Buffer Technique</li> <li>5.6 Hardware Decoder</li> <li>5.7 State diagram of the LZSS decoder</li> <li>5.8 Number of original instructions, Basic and Extended Blocks for the benchmarks compiled for C62x and C64x processors</li> <li>5.9 Compression Ratios for different Benchmarks compressed using the LZSS Algorithm for 4-bit, 5-bit and 8-bit pattern length</li> <li>5.10 Compression ratios using three different models of the Deflate Algorithm for C62x VLIW processor</li> <li>5.11 Compression ratios using three different models of the Deflate Algorithm for C62x VLIW processor</li> <li>5.12 Compression ratios using three different models of the Deflate Algorithm for C64x VLIW processor</li> <li>5.13 Pipeline stages of the Deflate hardware decoder</li> <li>5.14 Performance of the Deflate hardware decoder</li> <li>5.15 Compressi</li></ul> |      |                                                                             | 104 |

| 'X' for different instructions 4.34 Steps for reducing the size of the decoding table 4.35 Example for re-encoding the 'X' fields: make them identical to the preceding instruction 4.36 Hardware decoder of the "Instruction Re-encoding Technique" 4.37 Ratio of re-encodable bits size compared to original code size for ARM and MIPS processors 4.38 Size of decoding table for ARM and MIPS processors 4.39 Compression ratios for ARM and MIPS processors 4.40 Time taken by the original and the compressed code for ARM processor (in Million of cycles) 5.1 Percentage of the average code size through different benchmarks of MiBenel on different processor architectures 5.2 Example for exploring the Extended Blocks (EB) form "Fetch Packets" (FP) for compression 5.3 Steps for our code compression technique 5.4 Example for compressing an Extended Block using the LZSS Algorithm 5.5 Example to compress 3 Extended Blocks using the Deflate Algorithm in conjunction to the Filled Buffer Technique 5.6 Hardware Decoder 5.7 State diagram of the LZSS decoder 5.8 Number of original instructions, Basic and Extended Blocks for the benchmarks compiled for C62x and C64x processors 5.9 Compression Ratios for different Benchmarks compressed using the LZSS Algorithm for 4-bit, 5-bit and 8-bit pattern length 5.10 Compression ratios using three different models of the Deflate Algorithm for C62x VLIW processor 5.11 Compression ratios using three different models of the Deflate Algorithm for C64x VLIW processor 5.12 Compression ratios using the LZMA Algorithm for C62x and C64x VLIW processor 5.13 Pipeline stages of the Deflate hardware decoder 5.14 Performance of the Deflate hardware decoder 5.15 Compression ratios using our Filled Buffer technique combined with the V2F [77] for C62x VLIW processor 6.1 Traditional decoding techniques. Each block is decoded first and then executed. 6.2 Our compression technique. During the execution of uncompressed instructions in each block, compressed instructions are decoded. 6.3 Trade-off between Compression Ratio           |      |                                                                             | 105 |

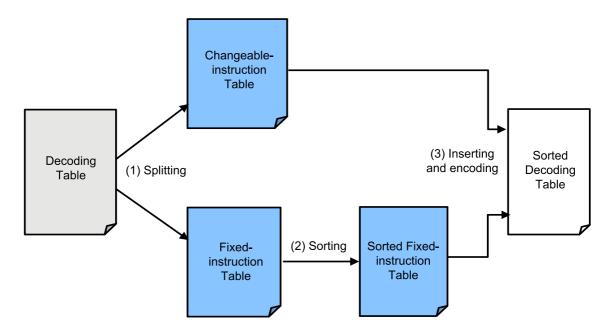

| <ul> <li>4.34 Steps for reducing the size of the decoding table</li> <li>4.35 Example for re-encoding the 'X' fields: make them identical to the preceding instruction</li> <li>4.36 Hardware decoder of the "Instruction Re-encoding Technique"</li> <li>4.37 Ratio of re-encodable bits size compared to original code size for ARM and MIPS processors</li> <li>4.38 Size of decoding table for ARM and MIPS processors</li> <li>4.39 Compression ratios for ARM and MIPS processors</li> <li>4.40 Time taken by the original and the compressed code for ARM processor (in Million of cycles)</li> <li>5.1 Percentage of the average code size through different benchmarks of MiBencl on different processor architectures</li> <li>5.2 Example for exploring the Extended Blocks (EB) form "Fetch Packets" (FP) for compression</li> <li>5.3 Steps for our code compression technique</li> <li>5.4 Example for compressing an Extended Block using the LZSS Algorithm</li> <li>5.5 Example to compress 3 Extended Blocks using the Deflate Algorithm in conjunction to the Filled Buffer Technique</li> <li>5.6 Hardware Decoder</li> <li>5.7 State diagram of the LZSS decoder</li> <li>5.8 Number of original instructions, Basic and Extended Blocks for the benchmarks compiled for C62x and C64x processors</li> <li>5.9 Compression Ratios for different Benchmarks compressed using the LZSS Algorithm for 4-bit, 5-bit and 8-bit pattern length</li> <li>5.10 Compression ratios using three different models of the Deflate Algorithm for C62x VLIW processor</li> <li>5.11 Compression ratios using three different models of the Deflate Algorithm for C64x VLIW processor</li> <li>5.12 Compression ratios using three different models of the Deflate Algorithm for C64x VLIW processor</li> <li>5.13 Pipeline stages of the Deflate hardware decoder</li> <li>5.14 Performance of the Deflate hardware decoder for C62x and C64x vLIW processor</li> <li>5.15 Compression ratios using our Filled Buffer technique combined with the V2F [77] for C62x VLIW processor</li> <li>6.1 Traditional decoding te</li></ul> | 4.33 | Replacing unused fields in the "R-Type" group with don't care symbols       |     |

| <ul> <li>4.35 Example for re-encoding the 'X' fields: make them identical to the preceding instruction.</li> <li>4.36 Hardware decoder of the "Instruction Re-encoding Technique".</li> <li>4.37 Ratio of re-encodable bits size compared to original code size for ARM and MIPS processors.</li> <li>4.38 Size of decoding table for ARM and MIPS processors.</li> <li>4.39 Compression ratios for ARM and MIPS processors.</li> <li>4.40 Time taken by the original and the compressed code for ARM processor (in Million of cycles)</li> <li>5.1 Percentage of the average code size through different benchmarks of MiBencl on different processor architectures.</li> <li>5.2 Example for exploring the Extended Blocks (EB) form "Fetch Packets" (FP) for compression.</li> <li>5.3 Steps for our code compression technique.</li> <li>5.4 Example for compressing an Extended Block using the LZSS Algorithm.</li> <li>5.5 Example to compress 3 Extended Blocks using the Deflate Algorithm in conjunction to the Filled Buffer Technique.</li> <li>5.6 Hardware Decoder.</li> <li>5.7 State diagram of the LZSS decoder.</li> <li>5.8 Number of original instructions, Basic and Extended Blocks for the benchmarks compiled for C62x and C64x processors.</li> <li>5.9 Compression Ratios for different Benchmarks compressed using the LZSS Algorithm for 4-bit, 5-bit and 8-bit pattern length.</li> <li>5.10 Compression ratios using three different models of the Deflate Algorithm for C62x VLIW processor.</li> <li>5.11 Compression ratios using three different models of the Deflate Algorithm for C64x VLIW processor actions using three different models of the Deflate Algorithm for C64x VLIW processor.</li> <li>5.12 Compression ratios using three different models of the Deflate Algorithm for C64x VLIW processor.</li> <li>5.13 Pipeline stages of the Deflate hardware decoder.</li> <li>5.14 Performance of the Deflate hardware decoder for C62x and C64x processor.</li> <li>5.15 Compression ratios using our Filled Buffer technique combined with the V2F [77] for C62x VLIW processor.</li></ul> |      | 'X' for different instructions                                              | 106 |

| ing instruction .  4.36 Hardware decoder of the "Instruction Re-encoding Technique" .  4.37 Ratio of re-encodable bits size compared to original code size for ARM and MIPS processors .  4.38 Size of decoding table for ARM and MIPS processors .  4.39 Compression ratios for ARM and MIPS processors .  4.40 Time taken by the original and the compressed code for ARM processor (in Million of cycles) .  5.1 Percentage of the average code size through different benchmarks of MiBencl on different processor architectures .  5.2 Example for exploring the Extended Blocks (EB) form "Fetch Packets" (FP) for compression .  5.3 Steps for our code compression technique .  5.4 Example for compressing an Extended Block using the LZSS Algorithm .  5.5 Example to compress 3 Extended Blocks using the Deflate Algorithm in conjunction to the Filled Buffer Technique .  5.6 Hardware Decoder .  5.7 State diagram of the LZSS decoder .  5.8 Number of original instructions, Basic and Extended Blocks for the benchmarks compiled for C62x and C64x processors .  5.9 Compression Ratios for different Benchmarks compressed using the LZSS Algorithm for 4-bit, 5-bit and 8-bit pattern length .  5.10 Compression ratios using three different models of the Deflate Algorithm for C62x VLIW processor .  5.11 Compression ratios using three different models of the Deflate Algorithm for C64x VLIW processor .  5.12 Compression ratios using the LZMA Algorithm for C62x and C64x VLIW processor .  5.13 Pipeline stages of the Deflate hardware decoder for C62x and C64x Processor .  5.14 Performance of the Deflate hardware decoder for C62x and C64x processor .  5.15 Compression ratios using our Filled Buffer technique combined with the V2F [77] for C62x VLIW processor .  6.1 Traditional decoding techniques. Each block is decoded first and then executed  6.2 Our compression technique. During the execution of uncompressed instructions in each block, compressed instructions are decoded .  6.3 Trade-off between Compression Ratio (CR) and Performance Ratio (PR)                      | 4.34 | Steps for reducing the size of the decoding table                           | 109 |

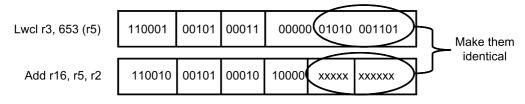

| <ul> <li>4.36 Hardware decoder of the "Instruction Re-encoding Technique"</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4.35 | Example for re-encoding the 'X' fields: make them identical to the preced-  |     |

| <ul> <li>4.37 Ratio of re-encodable bits size compared to original code size for ARM and MIPS processors</li> <li>4.38 Size of decoding table for ARM and MIPS processors</li> <li>4.39 Compression ratios for ARM and MIPS processors</li> <li>4.40 Time taken by the original and the compressed code for ARM processor (in Million of cycles)</li> <li>5.1 Percentage of the average code size through different benchmarks of MiBenel on different processor architectures</li> <li>5.2 Example for exploring the Extended Blocks (EB) form "Fetch Packets" (FP) for compression</li> <li>5.3 Steps for our code compression technique</li> <li>5.4 Example for compressing an Extended Block using the LZSS Algorithm</li> <li>5.5 Example to compress 3 Extended Blocks using the Deflate Algorithm in conjunction to the Filled Buffer Technique</li> <li>5.6 Hardware Decoder</li> <li>5.7 State diagram of the LZSS decoder</li> <li>5.8 Number of original instructions, Basic and Extended Blocks for the benchmarks compiled for C62x and C64x processors</li> <li>5.9 Compression Ratios for different Benchmarks compressed using the LZSS Algorithm for 4-bit, 5-bit and 8-bit pattern length</li> <li>5.10 Compression ratios using three different models of the Deflate Algorithm for C62x VLIW processor</li> <li>5.12 Compression ratios using three different models of the Deflate Algorithm for C64x VLIW processor</li> <li>5.12 Compression ratios using the LZMA Algorithm for C62x and C64x VLIW processors</li> <li>5.13 Pipeline stages of the Deflate hardware decoder</li> <li>5.14 Performance of the Deflate hardware decoder</li> <li>5.15 Compression ratios using our Filled Buffer technique combined with the V2F [77] for C62x VLIW processor</li> <li>6.1 Traditional decoding techniques. Each block is decoded first and then executed.</li> <li>6.2 Our compression technique. During the execution of uncompressed instructions in each block, compressed instructions are decoded.</li> <li>6.3 Trade-off between Compression Ratio (CR) and Performance Ratio (PR)</li> </ul>              |      | ing instruction                                                             | 110 |

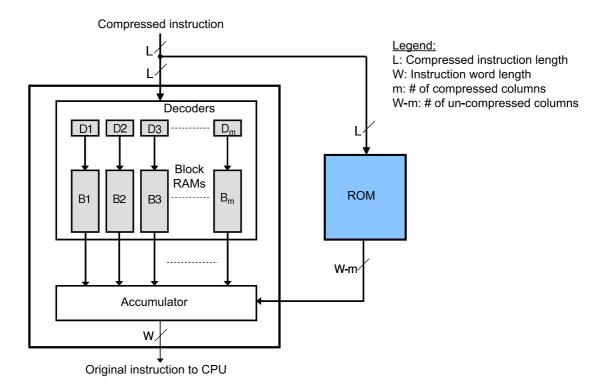

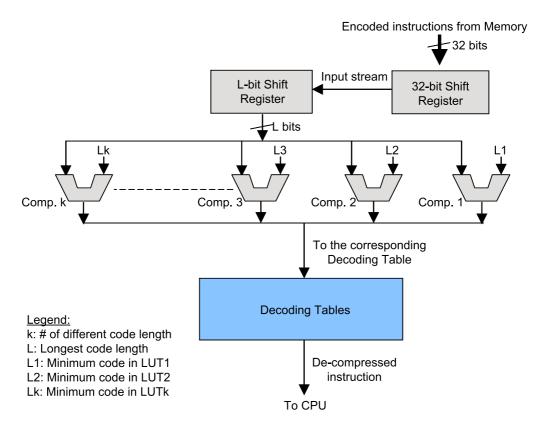

| MIPS processors 4.38 Size of decoding table for ARM and MIPS processors 4.39 Compression ratios for ARM and MIPS processors 4.40 Time taken by the original and the compressed code for ARM processor (in Million of cycles) 5.1 Percentage of the average code size through different benchmarks of MiBencl on different processor architectures 5.2 Example for exploring the Extended Blocks (EB) form "Fetch Packets" (FP) for compression 5.3 Steps for our code compression technique 5.4 Example for compressing an Extended Block using the LZSS Algorithm 5.5 Example to compress 3 Extended Blocks using the Deflate Algorithm in conjunction to the Filled Buffer Technique 5.6 Hardware Decoder 5.7 State diagram of the LZSS decoder 5.8 Number of original instructions, Basic and Extended Blocks for the benchmarks compiled for C62x and C64x processors 5.9 Compression Ratios for different Benchmarks compressed using the LZSS Algorithm for 4-bit, 5-bit and 8-bit pattern length 5.10 Compression ratios using three different models of the Deflate Algorithm for C62x VLIW processor 5.11 Compression ratios using three different models of the Deflate Algorithm for C64x VLIW processor 5.12 Compression ratios using the LZMA Algorithm for C62x and C64x VLIW processor 5.13 Pipeline stages of the Deflate hardware decoder 5.14 Performance of the Deflate hardware decoder for C62x and C64x VLIW processor 5.15 Compression ratios using our Filled Buffer technique combined with the V2F [77] for C62x VLIW processor 6.1 Traditional decoding techniques. Each block is decoded first and then executed. 6.2 Our compression technique. During the execution of uncompressed instructions in each block, compressed instructions are decoded. 6.2 Our compression technique. During the execution of uncompressed instructions in each block, compressed instructions are decoded. 6.3 Trade-off between Compression Ratio (CR) and Performance Ratio (PR)                                                                                                                                          | 4.36 | Hardware decoder of the "Instruction Re-encoding Technique"                 | 111 |

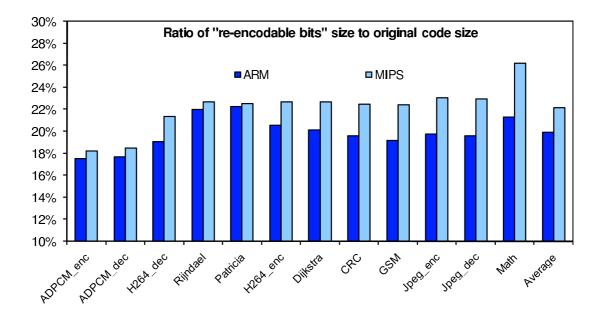

| <ul> <li>4.38 Size of decoding table for ARM and MIPS processors</li> <li>4.39 Compression ratios for ARM and MIPS processors</li> <li>4.40 Time taken by the original and the compressed code for ARM processor (in Million of cycles)</li> <li>5.1 Percentage of the average code size through different benchmarks of MiBench on different processor architectures</li> <li>5.2 Example for exploring the Extended Blocks (EB) form "Fetch Packets" (FP) for compression</li> <li>5.3 Steps for our code compression technique</li> <li>5.4 Example for compressing an Extended Block using the LZSS Algorithm</li> <li>5.5 Example to compress 3 Extended Blocks using the Deflate Algorithm in conjunction to the Filled Buffer Technique</li> <li>5.6 Hardware Decoder</li> <li>5.7 State diagram of the LZSS decoder</li> <li>5.8 Number of original instructions, Basic and Extended Blocks for the benchmarks compiled for C62x and C64x processors</li> <li>5.9 Compression Ratios for different Benchmarks compressed using the LZSS Algorithm for 4-bit, 5-bit and 8-bit pattern length</li> <li>5.10 Compression ratios using three different models of the Deflate Algorithm for C62x VLIW processor</li> <li>5.11 Compression ratios using three different models of the Deflate Algorithm for C64x VLIW processor</li> <li>5.12 Compression ratios using three different models of the Deflate Algorithm for C64x VLIW processor</li> <li>5.13 Pipeline stages of the Deflate hardware decoder</li> <li>5.14 Performance of the Deflate hardware decoder for C62x and C64x processor</li> <li>5.15 Compression ratios using our Filled Buffer technique combined with the V2F [77] for C62x VLIW processor</li> <li>6.1 Traditional decoding techniques. Each block is decoded first and then executed.</li> <li>6.2 Our compression technique. During the execution of uncompressed instructions in each block, compressed instructions are decoded.</li> <li>6.2 Our compression technique. During the execution of uncompressed instructions in each block, compression Ratio (CR) and Performance Ratio (P</li></ul> | 4.37 | Ratio of re-encodable bits size compared to original code size for ARM and  |     |

| <ul> <li>4.39 Compression ratios for ARM and MIPS processors</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |                                                                             | 112 |

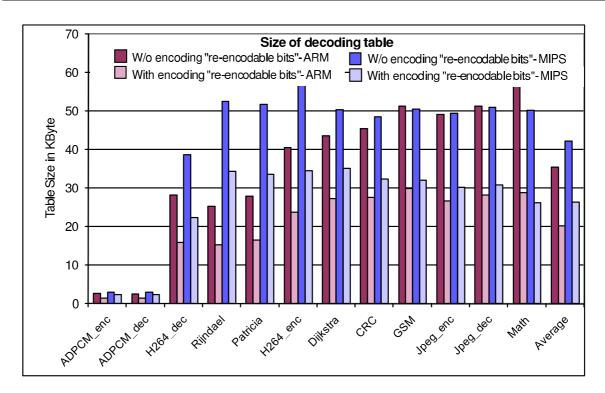

| <ul> <li>4.40 Time taken by the original and the compressed code for ARM processor (in Million of cycles)</li> <li>5.1 Percentage of the average code size through different benchmarks of MiBencl on different processor architectures</li> <li>5.2 Example for exploring the Extended Blocks (EB) form "Fetch Packets" (FP) for compression</li> <li>5.3 Steps for our code compression technique</li> <li>5.4 Example for compressing an Extended Block using the LZSS Algorithm</li> <li>5.5 Example to compress 3 Extended Blocks using the Deflate Algorithm in conjunction to the Filled Buffer Technique</li> <li>5.6 Hardware Decoder</li> <li>5.7 State diagram of the LZSS decoder</li> <li>5.8 Number of original instructions, Basic and Extended Blocks for the benchmarks compiled for C62x and C64x processors</li> <li>5.9 Compression Ratios for different Benchmarks compressed using the LZSS Algorithm for 4-bit, 5-bit and 8-bit pattern length</li> <li>5.10 Compression ratios using three different models of the Deflate Algorithm for C62x VLIW processor</li> <li>5.11 Compression ratios using three different models of the Deflate Algorithm for C64x VLIW processor</li> <li>5.12 Compression ratios using the LZMA Algorithm for C62x and C64x VLIW processors</li> <li>5.13 Pipeline stages of the Deflate hardware decoder</li> <li>5.14 Performance of the Deflate hardware decoder for C62x and C64x processor</li> <li>5.15 Compression ratios using our Filled Buffer technique combined with the V2F [77] for C62x VLIW processor</li> <li>6.1 Traditional decoding techniques. Each block is decoded first and then executed.</li> <li>6.2 Our compression technique. During the execution of uncompressed instructions in each block, compressed instructions are decoded</li> <li>6.3 Trade-off between Compression Ratio (CR) and Performance Ratio (PR)</li> </ul>                                                                                                                                                                                                                          | 4.38 | Size of decoding table for ARM and MIPS processors                          | 113 |

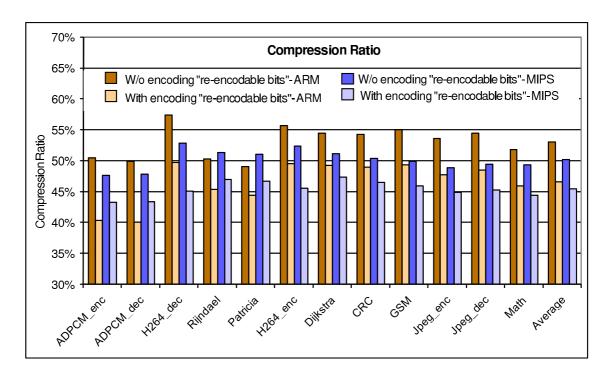

| (in Million of cycles)  5.1 Percentage of the average code size through different benchmarks of MiBench on different processor architectures  5.2 Example for exploring the Extended Blocks (EB) form "Fetch Packets" (FP) for compression  5.3 Steps for our code compression technique  5.4 Example for compressing an Extended Block using the LZSS Algorithm  5.5 Example to compress 3 Extended Blocks using the Deflate Algorithm in conjunction to the Filled Buffer Technique  5.6 Hardware Decoder  5.7 State diagram of the LZSS decoder  5.8 Number of original instructions, Basic and Extended Blocks for the benchmarks compiled for C62x and C64x processors  5.9 Compression Ratios for different Benchmarks compressed using the LZSS Algorithm for 4-bit, 5-bit and 8-bit pattern length  5.10 Compression ratios using three different models of the Deflate Algorithm for C62x VLIW processor  5.11 Compression ratios using three different models of the Deflate Algorithm for C64x VLIW processor  5.12 Compression ratios using the LZMA Algorithm for C62x and C64x VLIW processor  5.13 Pipeline stages of the Deflate hardware decoder  5.14 Performance of the Deflate hardware decoder for C62x and C64x processor  5.15 Compression ratios using our Filled Buffer technique combined with the V2F [77] for C62x VLIW processor  6.1 Traditional decoding techniques. Each block is decoded first and then executed.  6.2 Our compression technique. During the execution of uncompressed instructions in each block, compressed instructions are decoded.  6.2 Our compression technique. During the execution of uncompressed instructions in each block, compressed instructions are decoded.  6.3 Trade-off between Compression Ratio (CR) and Performance Ratio (PR)                                                                                                                                                                                                                                                                                                                                  | 4.39 |                                                                             | 114 |

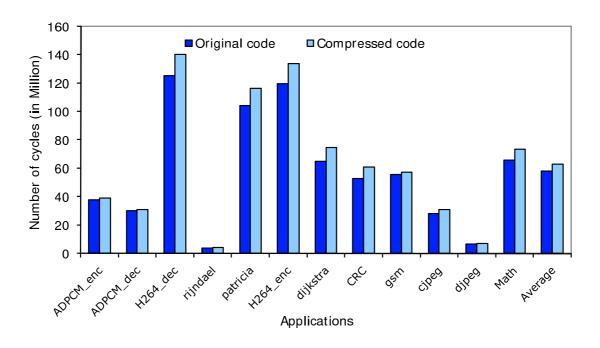

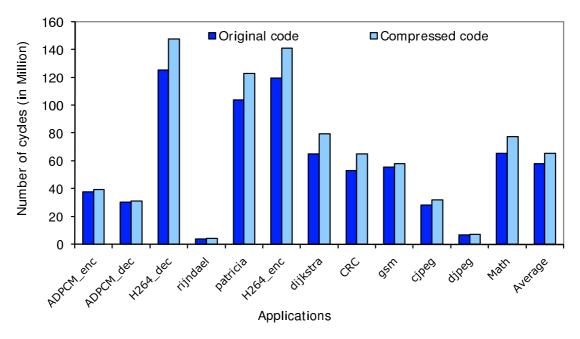

| 5.1 Percentage of the average code size through different benchmarks of MiBench on different processor architectures 5.2 Example for exploring the Extended Blocks (EB) form "Fetch Packets" (FP) for compression 5.3 Steps for our code compression technique 5.4 Example for compressing an Extended Block using the LZSS Algorithm 5.5 Example to compress 3 Extended Blocks using the Deflate Algorithm in conjunction to the Filled Buffer Technique 5.6 Hardware Decoder 5.7 State diagram of the LZSS decoder 5.8 Number of original instructions, Basic and Extended Blocks for the benchmarks compiled for C62x and C64x processors 5.9 Compression Ratios for different Benchmarks compressed using the LZSS Algorithm for 4-bit, 5-bit and 8-bit pattern length 5.10 Compression ratios using three different models of the Deflate Algorithm for C62x VLIW processor 5.11 Compression ratios using three different models of the Deflate Algorithm for C64x VLIW processor 5.12 Compression ratios using the LZMA Algorithm for C62x and C64x VLIW processor 5.13 Pipeline stages of the Deflate hardware decoder 5.14 Performance of the Deflate hardware decoder for C62x and C64x processor 5.15 Compression ratios using our Filled Buffer technique combined with the V2F [77] for C62x VLIW processor 6.1 Traditional decoding techniques. Each block is decoded first and then executed. 6.2 Our compression technique. During the execution of uncompressed instructions in each block, compressed instructions are decoded 6.3 Trade-off between Compression Ratio (CR) and Performance Ratio (PR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4.40 | v 9                                                                         |     |

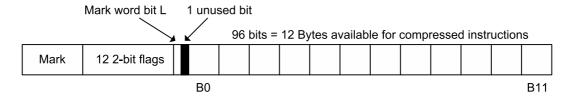

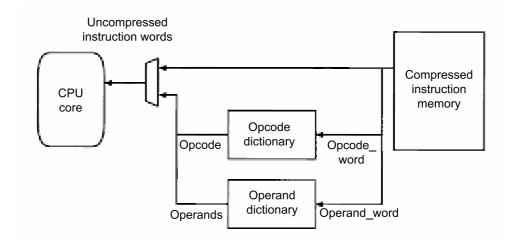

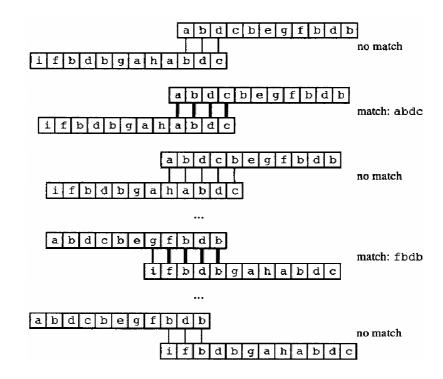

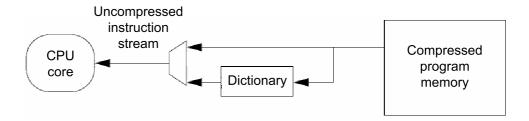

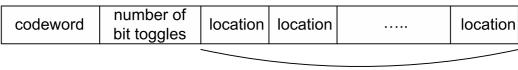

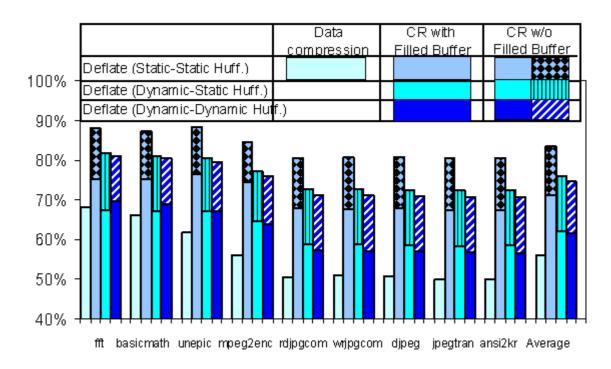

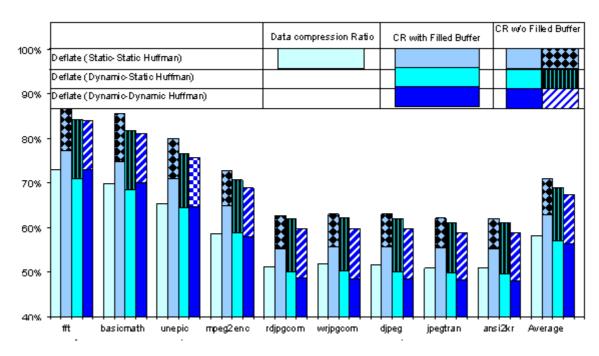

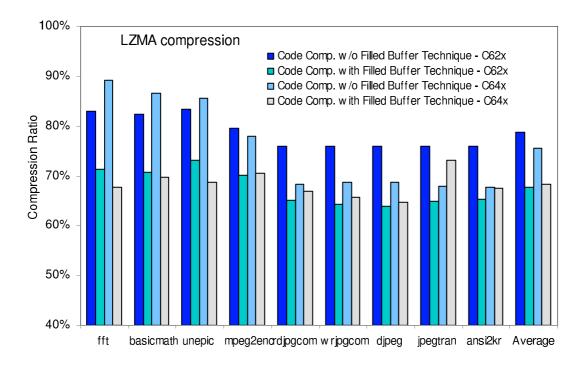

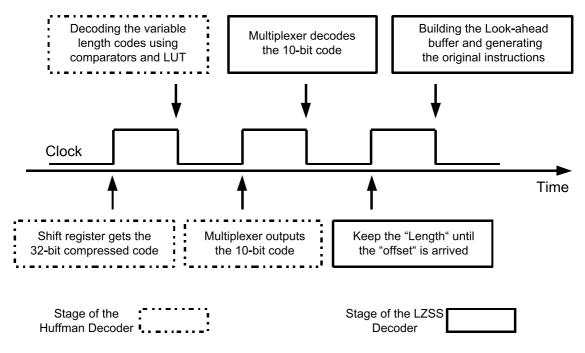

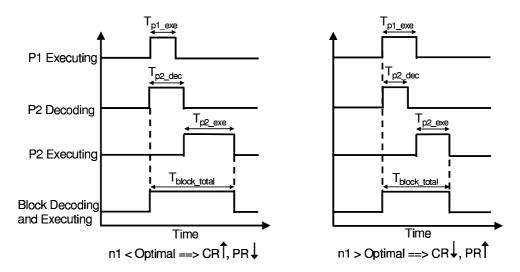

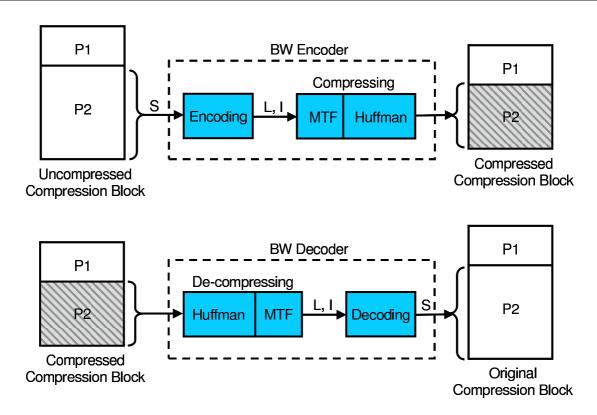

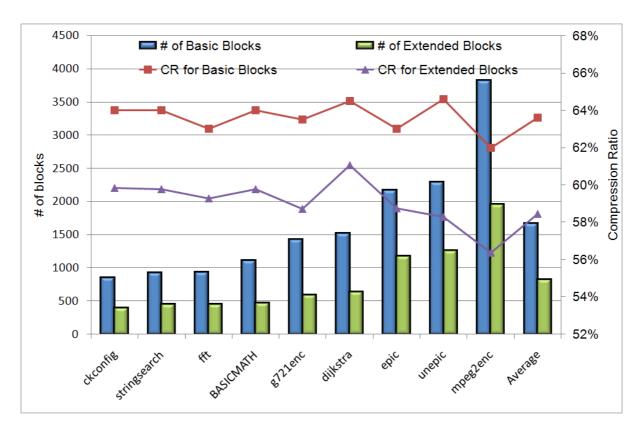

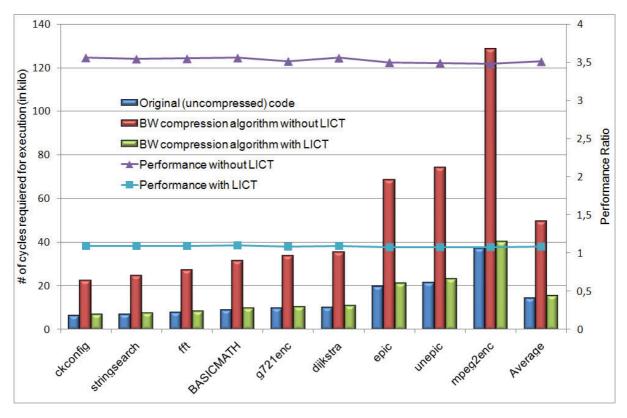

| on different processor architectures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      | (in Million of cycles)                                                      | 114 |