# High-performance and Hardware-aware Computing

Proceedings of the Second International Workshop on New Frontiers in High-performance and Hardware-aware Computing (HipHaC'11)

Rainer Buchty, Jan-Philipp Weiß (eds.)

#### **High-performance and Hardware-aware Computing**

Proceedings of the Second International Workshop on New Frontiers in High-performance and Hardware-aware Computing (HipHaC'11)

San Antonio, Texas, USA, February 2011 (In Conjunction with HPCA-17)

# **High-performance and Hardware-aware Computing**

Proceedings of the Second International Workshop on New Frontiers in High-performance and Hardware-aware Computing (HipHaC'11)

San Antonio, Texas, USA, February 2011 (In Conjunction with HPCA-17)

Rainer Buchty Jan-Philipp Weiß (eds.)

#### **Impressum**

Karlsruher Institut für Technologie (KIT) KIT Scientific Publishing Straße am Forum 2 D-76131 Karlsruhe www.ksp.kit.edu

KIT – Universität des Landes Baden-Württemberg und nationales Forschungszentrum in der Helmholtz-Gemeinschaft

Diese Veröffentlichung ist im Internet unter folgender Creative Commons-Lizenz publiziert: http://creativecommons.org/licenses/by-nc-nd/3.0/de/

KIT Scientific Publishing 2011 Print on Demand

ISBN 978-3-86644-626-7

#### Organization

**Workshop Organizers:**

Rainer Buchty Vincent Heuveline

Eberhard Karls University Tübingen, Germany, Karlsruhe Institute of Technology, Germany

**Steering Committee:**

& Karlsruhe Institute of Technology, Germany Wolfgang Karl

Jan-Philipp Weiß Karlsruhe Institute of Technology, Germany

Karlsruhe Institute of Technology, Germany

**Program Committee:**

David A. Bader Michael Hübner

Georgia Tech, Atlanta, USA Karlsruhe Institute of Technology, Germany

Michael Bader Ben Juurlink

Univ. Stuttgart, Germany TU Berlin, Germany

Mladen Berekovic Wolfgang Karl

Univ. Braunschweig, Germany Karlsruhe Institute of Technology, Germany

Alan Berenbaum Rainer Keller

SMSC, USA HLRS, Stuttgart, Germany

Martin Bogdan Hiroaki Kobayashi

Univ. Leipzig, Germany Tohoku University, Japan

Dominik Göddeke Harald Köstler

TU Dortmund, Germany Univ. Erlangen, Germany

Georg Hager Dieter an Mey

Univ. Erlangen, Germany RWTH Aachen, Germany

Vincent Heuveline Andy Nisbet

Karlsruhe Institute of Technology, Germany Manchester Metropolitan University, UK

Eric d'Hollander Christian Perez

Ghent University, Belgium INRIA, France

#### **Program Committee (continued):**

Franz-Josef Pfreundt Masha Sosonkina

ITWM Kaiserslautern, Germany Ames Lab, USA

Wolfgang Rosenstiel Thomas Steinke

Eberhard Karls University Tübingen, Germany Zuse-Institut Berlin, Germany

Olaf Schenk Josef Weidendorfer

Basel University, Switzerland TU Munich, Germany

Martin Schulz Felix Wolf

LLNL, USA GRS-SIM Aachen/Jülich, Germany

#### **Preface**

High-performance system architectures are increasingly exploiting heterogeneity: multi- and manycore-based systems are complemented by coprocessors, accelerators, and reconfigurable units providing huge computational power. However, applications of scientific interest (e.g. in high-performance computing and numerical simulation) are not yet ready to exploit the available high computing potential. Different programming models, non-adjusted interfaces, and bandwidth bottlenecks complicate holistic programming approaches for heterogeneous architectures. In modern microprocessors, hierarchical memory layouts and complex logics obscure predictability of memory transfers or performance estimations.

For efficient implementations and optimal results, underlying algorithms and mathematical solution methods have to be adapted carefully to architectural constraints like fine-grained parallelism and memory or bandwidth limitations that require additional communication and synchronization. Currently, a comprehensive knowledge of underlying hardware is therefore mandatory for application programmers. Hence, there is strong need for virtualization concepts that free programmers from hardware details, maintaining best performance and enable deployment in heterogeneous and reconfigurable environments.

The Second International Workshop on New Frontiers in High-performance and Hardware-aware Computing (HipHaC'11) – held in conjunction with the 17<sup>th</sup> IEEE International Symposium on High-Performance Computer Architecture (HPCA-17) – aims at combining new aspects of parallel, heterogeneous, and reconfigurable system architectures with concepts of high-performance computing and, particularly, numerical solution methods. It brings together international researchers of all affected fields to discuss issues of high-performance computing on emerging hardware architectures, ranging from architecture work to programming and tools.

The workshop organizers would therefore like to thank the HPCA-17 Workshop Chair for giving us the chance to host this workshop in conjunction with one of the world's finest conferences on high-performance architectures – and of course all the people who made this workshop finally happen. Thanks to the many contributors submitting exciting and novel work, HipHaC'11 will reflect a broad range of issues on architecture design, algorithm implementation, and application optimization.

Karlsruhe, January 2011

Rainer Buchty<sup>1,2</sup> & Jan-Philipp Weiß<sup>2</sup>

<sup>1</sup>Eberhard Karls University Tübingen

<sup>2</sup> Karlsruhe Institute of Technology (KIT)

## **Table of Content**

|          |    | • 4          | 4   |      |

|----------|----|--------------|-----|------|

| Λr       | ſП | 110          | CTI | IPAC |

| $\Delta$ | u  | $\mathbf{u}$ | LIL | ires |

| Convey HC-1 Hybrid Core Computer – The Potential of FPGAs in Numerical Simulation Werner Augustin, Jan-Philipp Weiss, and Vincent Heuveline | 1    |

|---------------------------------------------------------------------------------------------------------------------------------------------|------|

| Optimized Replacement in the Configuration Layers of the Grid Alu Processor                                                                 | 9    |

| Performance Measurement, Modeling, and Engineering                                                                                          |      |

| Performance Engineering of an Orthogonal Matching Pursuit Algorithm for Sparse Representation of Signals on Different Architectures         | . 17 |

| Impact of Data Sharing on CMP design: A study based on Analytical Modeling                                                                  | . 25 |

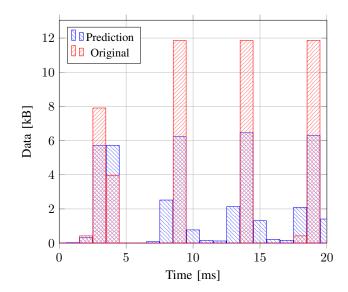

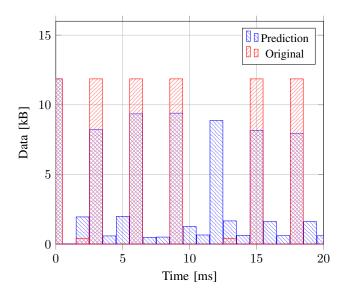

| Traffic Prediction for NoCs using Fuzzy Logic                                                                                               | . 33 |

| GPU Acceleration of the Assembly Process in Isogeometric Analysis                                                                           | .41  |

| GPU Accelerated Scientific Computing: Evaluation of the NVIDIA Fermi Architecture; Elementary Kernels and Linear Solvers                    | . 47 |

| List of Authors                                                                                                                             | . 55 |

# Convey HC-1 Hybrid Core Computer – The Potential of FPGAs in Numerical Simulation

Werner Augustin, Jan-Philipp Weiss

Engineering Mathematics and Computing Lab (EMCL)

SRG New Frontiers in High Performance Computing

Exploiting Multicore and Coprocessor Technology

Karlsruhe Institute of Technology, Germany

werner.augustin@kit.edu, jan-philipp.weiss@kit.edu

Vincent Heuveline

Engineering Mathematics and Computing Lab (EMCL)

Karlsruhe Institute of Technology, Germany

vincent.heuveline@kit.edu

Abstract—The Convey HC-1 Hybrid Core Computer brings FPGA technologies closer to numerical simulation. It combines two types of processor architectures in a single system. Highly capable FPGAs are closely connected to a host CPU and the accelerator-to-memory bandwidth has remarkable values. Reconfigurability by means of pre-defined application-specific instruction sets called personalities have the appeal of optimized hardware configuration with respect to application characteristics. Moreover, Convey's solution eases the programming effort considerably. In contrast to hardware-centric and time-consuming classical coding of FPGAs, a dual-target compiler interprets pragma-extended C/C++ or Fortran code and produces implementations running on both, host and accelerator. In addition, a global view of host and device memory is provided by means of a cache-coherent shared virtual memory space.

In this work we analyze Convey's programming paradigm and the associated programming effort, and we present practical results on the HC-1. We consider vectorization strategies for the single and double precision vector personalities and a suite of basic numerical routines. Furthermore, we assess the viability of the Convey HC-1 Hybrid Core Computer for numerical simulation.

*Keywords*-FPGA, Convey HC-1, reconfigurable architectures, high-performance heterogeneous computing, coherent memory system, performance analysis, BLAS

#### I. INTRODUCTION

Field Programmable Gate Arrays (FPGAs) have their main pillar and standing in the domain of embedded computing. Application-specific designs implemented by hardware description languages (HDL) like VHDL and Verilog [1], [2] make them a perfect fit for specific tasks. From a software-oriented programmer's point of view FPGA's capabilities are hidden behind an alien hardware design development cycle. Although there are some C-to-HDL tools like ROCCC, Impulse C or Handle-C [3] available, viability and translation efficiency for realistic code scenarios still have to be proven.

For several years, FPGAs have not been interesting for numerical simulations due to their limited capabilities and resource requirements for double precision floating point arithmetics. But following Moore's law and with increased FPGA sizes more and more area is becoming available for computing. Moreover, further rates of increase are expected to outpace those of common multicore CPUs. For a general deployment

and in particular for numerical simulation FPGAs are very attractive from further points of view: run-time configurability is an interesting topic for applications with several phases of communication and computation and might be considered for adaptive numerical methods. In addition, energy efficiency is a great concern in high performance computing and FPGA technology is a possible solution approach. The main idea of FPGAs is to build one's own parallel fixed-function units according to the special needs of the underlying application.

Currently, numerical simulation adopts all kinds of emerging technologies. In this context, a trend towards heterogeneous platforms has become apparent [4]. Systems accelerated by graphics processing units (GPUs) offer unrivaled computing power but often suffer from slow interconnection via PCIe links. The idea to connect FPGAs via socket replacements closer to CPUs is nothing new (cf. technologies from Nallatech, DRC, XtremeData) – but the software concept offered by Convey is revolutionary [5]. A related FPGA platform is Intel's Atom reconfigurable processor – an embedded single board computer based on the Intel Atom E600C processor paired with an Altera FPGA in a single package. Here, both entities communicate via PCIe-x1 links. Former hybrid CPU-FPGA machines were the Cray XD1 [6] and the SGI RC100.

In this work we outline the hardware and software architecture of the Convey HC-1 Hybrid Core Computer. We analyze Convey's programming concept and assess the functionalities and capabilities of Convey's single and double precision vector personalities. Furthermore, we evaluate the viability of the Convey HC-1 Hybrid Core Computer for numerical simulation by means of selected numerical kernels that are well-known building blocks for higher-level numerical schemes, solvers, and applications. Some performance results on the HC-1 can be found in [7]. Our work puts more emphasis on floating point kernels relevant for numerical simulation. Stencil applications on the HC-1 are also considered in [8].

#### II. HARDWARE CONFIGURATION OF THE CONVEY HC-1

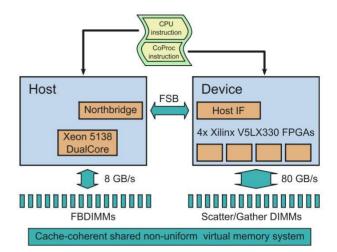

The Convey HC-1 Hybrid Core Computer is an example of a heterogeneous computing platform. By its hybrid setup, specific application needs can either be handled by an x86-64 dual-core CPU or by the application-adapted FPGAs. All

computational workloads are processed by a 2.13GHz Intel Xeon 5138 dual-core host CPU and by the application engines (AE), a set of four Xilinx Virtex 5 LX330 FPGAs. Two more V5LX110 FPGAs implement the host interface - the application engine hub (AEH) - for data transfers and control flow exchange between host and device, and eight V5LX155 FPGAs build the eight accelerator's memory controllers. Data transfers are communicated via the CPU's front-side bus (FSB), Intel's aging technology. Across the whole system a cache-coherent shared virtual memory system is provided that allows to access data in the CPU's memory and in the accelerator device memory. However, the system incorporates a ccNUMA system where proper data placement is performance-critical. In our system the host CPU is equipped with 16x667MHz FBDIMMs providing 16 GB of memory and a theoretical bandwidth of 8 GB/s. On the device 16 DDR2 memory channels feed Convey's special 16x667MHz Scatter-Gather-DIMMs with 8 GB device memory and a theoretical peak bandwidth of 80 GB/s. The fundamental advantage of this memory configuration is that non-unit strides have no drawback on the effective bandwidth. All data can be accessed with 8 byte granularity. Functional units on the FPGAs are implemented by logic synthesis by means of Convey's personalities [5]. The single precision vector personality provides a load-store vector architecture with 32 function pipes, each one containing a vector register file and four fused-multiply-add (FMA) vector units for exploiting data parallelism by means of vectorization. Furthermore, out-of-order execution provides a means for instruction-level parallelism. While the clock rate of the FPGAs is undisclosed, the peak GFlop/s rate is expected to be about 80 GFlop/s for single precision and 40 GFlop/s for double precision. The most accented difference of the FPGA accelerator memory subsystem is that there are no caches and no local memory available. All block-RAM on the FPGA is not accessible by the user (unless custom personalities and FPGA designs are created that support this feature). The whole system consumes about 650-850 Watt (depending on the actual workload). A sketch of the HC-1's hardware configuration is shown in Figure 1.

In comparison to other accelerators – like e.g. recent GPUS or the Cell BE – the HC-1 offers lower peak performance and lower bandwidth. But in contrast, fast device memory can be configured up to 128 GB in size and is not limited to a few GB as on GPUs. Furthermore, Convey's technology and its future development will possibly allow fast cluster-like connection between several FPGA-based entities. The latest Convey product, the HC-1ex was improved with newer Xilinx Virtex 6 FPGAs and an Intel 5408 Xeon quad-core processor.

#### III. CONVEY HC-1'S SOFTWARE ENVIRONMENT

Programming of FPGAs by means of HDL is a time-consuming and non-intuitive effort – and so FPGAs have been out of reach for many domain experts. With Convey's solution, FPGAs are now a viable alternative from a programming point of view. On the Convey HC-1, the CPU's capabilities are extended by application-specific

Fig. 1. Hardware Configuration of the Convey HC-1

instructions for the FPGAs [5]. However, the asymmetric computing platform is hidden by Convey's unified software interface. A single code base (C, C++ or Fortran) can be enhanced with pragmas to advise the compiler how to treat computations and data. In particular, code regions that should be executed on the FPGAs can be identified by inserting #pragma cny begin\_coproc / end\_coproc.

Another possibility is to compile whole subroutines for the accelerator, or even to use compiler's capability for automatic identification of parts, that shall be offloaded to the FPGAs. Typical code sections are those suitable for vectorization, especially long loops. The compiler then produces a dual target executable, i.e. the code can be executed on both the CPU host (e.g. if the coprocessor is not available) and on the FPGA accelerator. Hence, a portable solution is created that can run on any x86 system. There are some restrictions to coprocessor code: it is not possible to do I/O, to make system calls or to call non-coprocessor functions. A compiler report gives details on the vectorization procedure. Specific pragmas give further hints for compiler-based optimizations.

Both memories on the host CPU and on the FPGA accelerator are combined into a common address space and data types are common across both entities. In order to prevent NUMA effects, placement of data can be controlled by pragmas. Data allocated in the CPU memory can be transferred to the accelerator with #pragma cny migrate\_coproc. Dynamic and static memory on the FPGA device can be allocated directly via #pragma cny\_cp\_malloc and #pragma cny coproc\_mem respectively. In case of memory migration whole memory pages are transferred. In order to avoid multiple transfers, several data objects should be grouped into larger structs.

The actual configuration of the FPGAs is represented by means of application-specific instruction sets called personalities. These personalities augment the host's x86-64 instruction set. This features allows adaptation and optimization of the hardware with respect to the specific needs of the underlying

algorithms. The user only has to treat an integrated instruction set controlled by pragmas and compiler settings. Convey offers a set of pre-defined personalities for single and double precision floating point arithmetics that turn the FPGAs into a soft-core vector processor. Furthermore, personalities for financial analytics and for proteomics are available. Currently, a finite difference personality for stencil computations is under development. The choice for a requested personality is specified at compile time by setting compiler flags. With Convey's personality development kit custom personalities can be developed by following the typical FPGA hardware design tool chain (requiring considerable effort and additional knowledge). Convey's Software Performance Analysis Tool (SPAT) gives insight into the system's actual runtime behavior and feedback on possible optimizations. The Convey Math Library (CML) provides tuned basic mathematical kernels. For our experiments we used the Convey64 Compiler Suite, Version 2.0.0.

#### IV. THE POTENTIAL OF FPGAS

FPGAs have been considered to be non-optimal for floating point number crunching. But FPGAs show particular benefits for specific workloads like processing complex mathematical expressions (logs, exponentials, transcendentals), performing bit operations (shifts, manipulations), and performing sort operations (string comparison, pattern recognition). Further benefits can be achieved for variable bit length of data types with reduced or increased precision, or for treating non-standard number formats (e.g. decimal representation). The latter points are exploited within Convey's personalities for financial applications and proteomics. Recently, Convey reported a remarkable speedup of 172 for the Smith-Waterman algorithm [9].

Pure floating point-based algorithms in numerical simulation are often limited by bandwidth constraints and low arithmetic intensity (ratio of flop per byte). The theoretical peak bandwidth of 80 GB/s on the Convey FPGA device goes along with a specific appeal in this context. However, memory accesses on the device are not cached. Hence, particular benefits are expected for kernels with limited data reuse like vector updates (SAXPY/DAXPY), scalar products (SDOT/DDOT) and sparse matrix-vector multiplications (SpMV). Convey's special Scatter-Gather DIMMs are well adapted to applications with irregular data access patterns where CPUs and GPUs typically show tremendous performance breakdowns.

#### V. PERFORMANCE EVALUATION

In order to assess the performance potential of Convey's FPGA platform for floating point-based computations in numerical simulation we analyze some basic numerical kernels and their performance behavior. In particular, we consider library-based kernels provided by the CML and hand-written, optimized kernels. By comparing both results we draw some conclusion on the capability of Convey's compiler. In all cases, vectorization of the code and NUMA-aware placement of data is crucial for performance. Without vectorization there is a

dramatic performance loss since scalar code for the accelerator is executed on the slow *application engine hub* (AEH) that builds the interface between host and accelerator device. If data is not located in the accelerator memory but is accessed in the host memory over the FSB, bandwidth and hence performance also drop considerably.

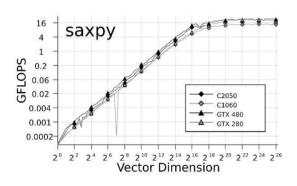

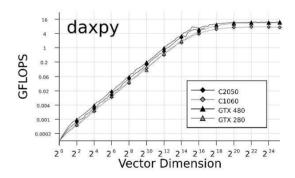

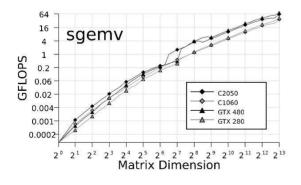

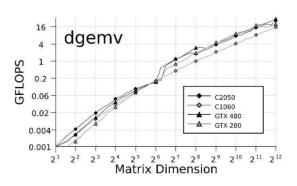

For our numerical experiments we consider some basic building blocks for high-level solvers, namely vector updates z = ax + y (SAXPY/DAXPY in single and double precision), vector product  $\alpha = x \cdot y$  (SDOT/DDOT), dense matrix-vector multiplication y = Ax (SGEMV/DGEMV), dense matrix-matrix multiplication C = AB (DGEMM/SGEMM), sparse matrix vector multiplication (SpMV), and stencil operations.

#### VI. VECTORIZATION AND OPTIMIZATION OF CODE

In order to exploit the full capabilities of the FPGA accelerator specific measures are necessary for code creation, for organizing data accesses, and to support the compiler for vectorizing code. Due to its nature as a low frequency, highly parallel vector architecture, performance on the Convey HC-1 heavily depends on the ability of the compiler to vectorize the code. One of the examples where this did not work out-of-the-box is dense matrix-vector multiplication SGEMV. The code snippet in Figure 2 shows a straightforward implementation. Here, the pragma cny no\_loop\_dep gives a hint to the compiler for vectorization that there are no data dependencies in the corresponding arrays.

Fig. 2. Straightforward implementation of dense matrix-vector multiplication (SGEMV)  $\,$

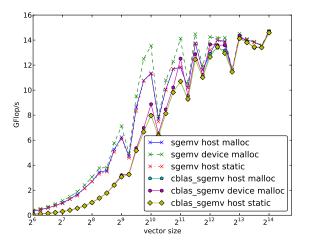

Although the compiler claims to vectorize the inner loop, performance is only approx. 2 GFlop/s and by a factor of 7 below the performance of the CML math library version. The coprocessor instruction set supports vector reduction operations, but these seem to have a pretty high startup latency. The outer loop is not unrolled. Attempts to do that manually improved the performance somewhat, but introduced new performance degradations for certain vector lengths.

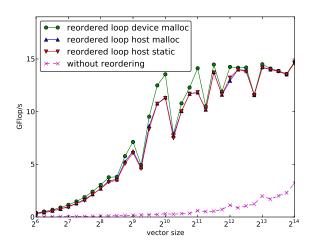

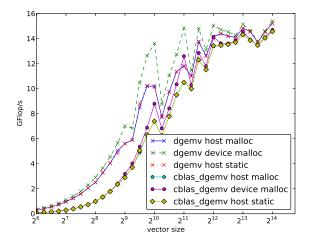

The solution lies in exploiting Convey's scatter-gather memory which allows for fast strided memory reads and therefore allows to change the loop ordering (see Figure 3). This gives considerably better results; performance improvements by loop reordering are detailed in Figure 4. For the reordered loops we consider three different memory allocation scenarios: dynamic memory allocated on the host and migrated with

Convey's pragma cny migrate\_coproc, dynamic memory allocated on the device, and static memory allocated on the host and migrated to the device with the pragma mentioned above. Performance increases with vector length but has some oscillations. These results even outperform the CML CBLAS library implementation from Convey (cf. Figure 13).

Fig. 3. Dense matrix-vector multiplication (SGEMV) optimized by loop reordering

Fig. 4. Performance results and optimization for single precision dense matrix-vector multiplication (SGEMV) with and without loop reordering and for different memory allocation schemes; cf. Fig. 2 and Fig. 3

#### VII. PERFORMANCE RESULTS AND ANALYSIS

#### A. Device Memory Bandwidth for Different Access Patterns

Performance of numerical kernels is often influenced by the corresponding memory bandwidth for loading and storing data. For our memory bandwidth measurements we use the following memory access patterns that are characteristic of diverse kernels:

```

\begin{array}{lll} \text{Sequential Read (SeRd):} & d[i] = s[i] \\ \text{Sequential Read Indexed (SeRdI):} & d[i] = s[seq[i]] \\ \text{Scattered Read Indexed (ScaRdI):} & d[i] = s[rnd[i]] \\ \text{Sequential Write (SeWr):} & d[i] = s[i] \\ \text{Scattered Write Indexed (SeWrI):} & d[rnd[i]] = s[i] \\ \end{array}

```

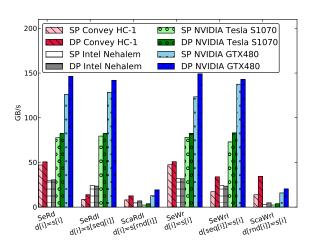

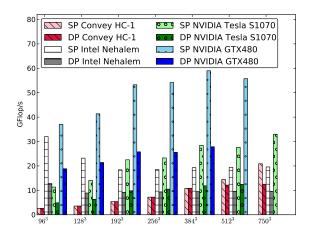

Here,  $seq[i]=i,\ i=1,\ldots,N$ , is a sequential but indirect addressing and rnd[i] is an indirect addressing by an arbitrary permutation of  $[1,\ldots,N]$ . Performance results for the described memory access patterns in single and double precision on the Convey HC-1, on a 2-way 2.53 GHz Intel Nehalem processor using 8 threads on 8 cores, on a single GPU of a NVIDIA Tesla S1070 system, and on a GTX 480 consumer GPU with the latest Fermi architecture are presented in Figure 5.

Fig. 5. Memory bandwidth for different memory access patterns on the Convey HC-1, on a 2-way 2.53 GHz Intel Nehalem system processor with 8 cores, on a single GPU of an NVIDIA Tesla S1070 system, and on an NVIDIA GTX480 consumer GPU

For the sequential indirect access, the CPU and GPU have built-in hardware mechanisms (caches for the CPU and memory coalescing for the GPU) to detect the access locality and therefore the performance does not decrease much while the HC-1 bandwidth already drops considerably. For the scattered read and write access, Convey's memory configuration gives better values than the Nehalem system and even outpaces the GTX 480 for scattered write in double precision. The Convey HC-1 not only has an about 60% percent higher peak memory bandwidth than the Nehalem system, but it really shows the potential of its scatter-gather capability when accessing random locations in memory. Here, traditional cache-based architectures typically perform poorly and at least the older generation of GPU systems has a breakdown by an order of magnitude. Newer GPU systems represented by the GTX 480 on the other hand have improved considerably.

#### B. Data-Transfers Between Host and Device

Because of the strong asymmetric NUMA-architecture of the HC-1 there are different methods to use main memory. Three of them are used in the following examples:

dynamically allocate (malloc) and initialize on the host; use migration pragmas

- dynamically allocate (cny\_cp\_malloc) and initialize on the device

- statically allocate and initialize on the host; use migration pragmas

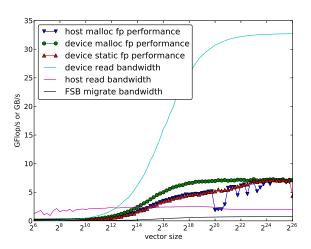

By initialization we mean the first touch of the data in memory. Because the Convey HC-1 is based on Intel's precedent technology of using the front-side bus (FSB) to connect memory to processors a major bottleneck is the data connection between host memory and device memory. Figure 6 shows a comparison between read bandwidth on the host and the device and the migration bandwidth over the HC-1's front side bus in GB/s. While read bandwidth on the device memory reaches almost 33 GB/s, the transfer over the FSB achieves only about 700 MB/s. This impedes fast switching between parts of an algorithm which perform well on the coprocessor and its vector units and other parts relying on the flexibility of high-clocked general purpose CPU. Compared to GPUs attached via PCIe, the FSB represents an even more narrow bottleneck.

Fig. 6. Read bandwidth on host and device and migration bandwidth in GB/s on the Convey HC-1; Performance results in GFlop/s for the SAXPY vector update for different memory allocation schemes

Furthermore, Figure 6 depicts performance of the SAXPY in terms of GFlop/s (the unit on the y-axis has to be chosen correspondingly). For data originally allocated on the host and migrated to the device we observe some oscillations in the performance.

#### C. Avoiding Bank Conflicts with 31-31 Interleave

The scatter-gather memory configuration of the Convey HC-1 can be used in two different mapping modes:

- Binary interleave: traditional approach, parts of the address bitmap are mapped round-robin to different memory banks

- 31-31 interleave: modulo 31 mapping of parts of the address bitmap

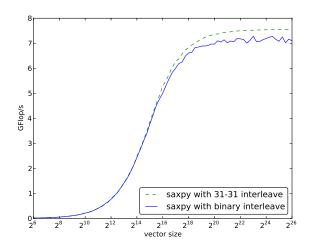

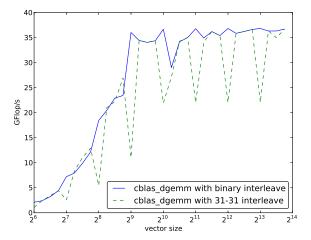

Because in the 31-31 interleave mode the memory is divided into 31 groups of 31 banks, memory strides of powers of two and many other strides hit different banks and therefore do not suffer from memory bandwidth degradation. But to integrate this prime number scheme into a power of two dominated world, one of 32 groups and every 32th bank are not used resulting in a loss of some addressable memory and approximately 6% of peak memory bandwidth. In Figure 7 performance results for the SAXPY vector update are shown for both interleave options. For the SAXPY, binary memory interleave is slightly worse. Performance results for the CML DGEMM routine in Figure 8 show larger variations with 31-31 interleave. The DGEMM routine achieves about 36 GFlop/s and the SGEMM routine yields about 72 GFlop/s on our machine. In both cases this is roughly 90% of the estimated machine peak performance.

Fig. 7. Performance of SAXPY vector updates with 31-31 and binary interleave

#### D. BLAS Operations

Basic Linear Algebra Subprograms (BLAS) [10] are a collection and interface for basic numerical linear algebra routines. We use these routines for assessment of the HC-1 FPGA platform. We compare our own, straightforward implementations of BLAS-routines with those provided by Convey's Math Library (CML). Loop reordering techniques are applied for performance improvements. In the following examples we use the three different memory usage schemes detailed in Section VII-B. In all three cases initialization and migration costs are not considered in our measurements.

Data allocation on the host followed by migration routines or pragmas is not really a controllable and reliable procedure. From time to time considerable drops in performance are observed. So far, we could not identify a reasonable pattern or a satisfactory explanation for these effects. Our measurements are made using separate program calls for a set of parameters. When trying to measure by looping over different vector

3.5

3.0

2.5

1.5

1.0

0.5

0.0

2.6

2.8

2.10

2.12

2.14

2.16

2.18

2.20

2.21

2.14

2.16

2.18

2.20

2.21

2.24

2.24

2.24

2.24

2.24

Fig. 10. DAXPY vector update using different implementations and different memory allocation strategies

lengths, allocating and freeing memory on the host and using migration calls in between, the results are even less reliable.

We observe that our own implementations are usually faster for short vector lengths – probably due to lower call over-

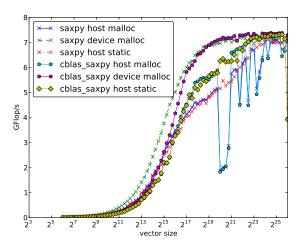

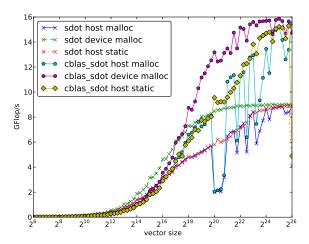

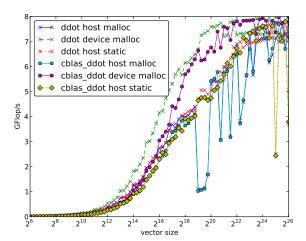

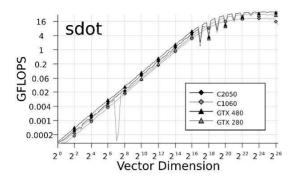

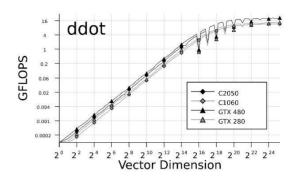

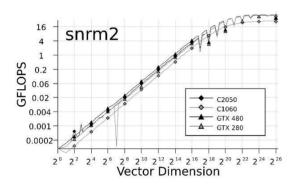

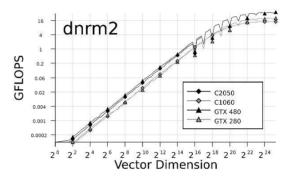

we observe that our own implementations are usually faster for short vector lengths – probably due to lower call overhead and less parameter checking. For longer vector lengths the CML library implementations usually give better results. Results for the SAXPY/DAXPY vector updates are depicted in Figure 9 and in Figure 10. Performance data for the SDOT/DDOT scalar products are shown in Figure 11 and in Figure 12, and for the SGEMV/DGEMV dense matrix-vector multiplication in Figure 13 and in Figure 14.

Fig. 9. SAXPY vector update using different implementations and different memory allocation strategies

Fig. 11. SDOT scalar product using different implementations and different memory allocation strategies

#### E. Sparse Matrix-Vector Multiplication

Many numerical discretization schemes for scientific problems result in sparse system matrices. Typically, iterative methods are used for solving these sparse systems. On top of scalar products and vector updates, the efficiency of sparse matrix-vector multiplications is very important for these scenarios. When using the algorithm for the compressed sparse row (CSR) storage format [11] presented in Figure 15, loops and reduction operations are vectorized by the compiler. However, the performance results are very disappointing – being in the range of a few MFlop/s. Although the memory bandwidth for indexed access as presented in Figure 5 is very good, the relatively short vector length and the overhead of the vector reduction in the inner loop seem to slow down computations

Fig. 12. DDOT scalar product using different implementations and different memory allocation strategies

Fig. 13. SGEMV matrix-vector multiplication using different implementations and different memory allocation strategies

(see also observations in Section VI on loop optimizations). Unfortunately, in this case loop reordering is not that easy because the length of the inner loop depends on the outer loop. A possible solution is to use other sparse matrix representations like the ELL format, as used on GPUs e.g. in [12].

#### F. Stencil Operations

Stencil kernels are one of the most important routines applied in the context of solving partial differential equations (PDEs) on structured grids. They originate from the discretization of differential expressions in PDEs by means of finite element, finite volume or finite difference methods. They are defined as a fixed subset of nearest neighbors where the corresponding node values are used for computing weighted

Fig. 14. DGEMV matrix-vector multiplication using different implementations and different memory allocation strategies

Fig. 15. Sparse matrix-vector multiplication (SpMV) routine for CSR data format

sums. The associated weights correspond to the coefficients of the PDEs where coefficients are assumed to be constant in our context. In our test we use a 3-dimensional 7-point stencil for solving the Laplace equation on grids of different sizes. The performance results on the HC-1, on an 8-core Nehalem CPU system, and on two different NVIDIA GPUs are shown in Figure 16. Our stencil code for the HC-1 is close to the example given in the Convey documentation material. The CPU implementation is the one used in [13], not using the presented in-place optimization but only conventional spaceblocking and streaming optimizations. The NVIDIA CUDA GPU implementation uses blocking of input values in shared memory for data reuse.

For the conventional CPU one can see a high peak for small grid sizes when the data can be kept in the cache. For larger grid sizes a pretty constant performance with slight

Fig. 16. Performance of a 3-dimensional 7-point Laplace stencil (one grid update is counted as 8 Flop) in single precision (SP) and double precision (DP) on the Convey HC-1, on a 2-way 2.53 GHz Intel Nehalem system using 8 cores, on a single GPU of an NVIDIA Tesla S1070 system, and on an NVIDIA GTX480 consumer GPU

increases due to less loop overhead is observed. The Convey HC-1 on the other hand shows no cache effects but lower performance on smaller grids. But unfortunately because of its lack of caching, neighboring values of the stencil have to be reloaded every time they are needed – wasting a large portion of the much higher total memory bandwidth. On the Convey HC-1 the difference between single and double precision stencil performance becomes apparent only for large grid size. Both NVIDIA GPUs show impressive performance, especially the newer generation. At the same time, they show the restrictive memory limitations – especially for the budget-priced consumer GPU with only 2 GB device memory. Here, the larger samples could not be computed.

#### VIII. CONCLUSION

Convey's HC-1 Hybrid Core Computer offers seamless integration of a highly capable FPGA platform with an easy coprocessor programming model, a coherent memory space shared by the host and the accelerator, and remarkable bandwidth values on the coprocessor. Moreover, Convey's scattergather memory configuration offers advantages for codes with irregular memory access patterns. With Convey's personalities the actual hardware configuration can be adapted to, and optimized for specific application needs. With its HC-1 platform, Convey brings FPGAs closer to high performance computing. However, we have failed to port more complex applications originating in numerical simulation due to the failure to obtain acceptable speed for sparse matrix-vector multiplication.

The HC-1 has the potential to be used for general purpose applications. Although the HC-1 falls behind the impressive performance numbers of GPU systems and the latest multicore CPUs, it provides an innovative approach to asymmetric processing, to compiler-based parallelization, and in particular

to portable programming solutions. Only a single code base is necessary for x86-64 and FPGA platforms which facilitates maintainability of complex codes. In contrast to GPUs, memory capacity is not limited by a few GB and FPGAs connected by direct networks come in reach. A great opportunity lies in the possibility to develop custom personalities – if time, knowledge and costs permit.

Convey's approach represents emerging technology with some deficiencies but also with a high level of maturity. Major drawbacks arise from limitations for floating point arithmetics on FPGAs, compiler capabilities for automatic vectorization, and the usage of Intel's obsolete FSB communication infrastructure. In our experience, typical code bases still show room for code and compiler improvements. While major benefits have been reported for specific workloads in bioinformatics, the HC-1 also provides a viable means for floating point-dominated and bandwidth-limited numerical applications. Despite its high acquisition costs, this breakthrough technology needs further attention.

#### ACKNOWLEDGEMENTS

The Shared Research Group 16-1 received financial support by the Concept for the Future of Karlsruhe Institute of Technology in the framework of the German Excellence Initiative and by the industrial collaboration partner Hewlett-Packard.

#### REFERENCES

- P. J. Ashenden, The VHDL Cookbook. Dept. Computer Science, Univ. Adelaide, S. Australia. [Online]. Available: http://tams-www.informatik.uni-hamburg.de/vhdl/doc/cookbook/VHDL-Cookbook.pdf

- [2] D. Thomas and P. Moorby, The Verilog Hardware Description Language, 2008.

- [3] J. M. P. Cardoso, P. C. Diniz, and M. Weinhardt, "Compiling for reconfigurable computing: A survey," ACM Comput. Surv., vol. 42, pp. 13:1–13:65, June 2010. [Online]. Available: http://doi.acm.org/10.1145/1749603.1749604

- [4] A. Shan, "Heterogeneous processing: A strategy for augmenting Moore's law," *Linux J.* [Online]. Available: http://www.linuxjournal.com/article8368

- [5] T. M. Brewer, "Instruction set innovations for the Convey HC-1 Computer," *IEEE Micro*, vol. 30, pp. 70–79, 2010.

- [6] O. Storaasli and D. Strenski, "Cray XD1 exceeding 100x speedup/FPGA: Timing analysis yields further gains," in *Proc.* 2009 Cray User Group, Atlanta GA, 2009.

- [7] J. Bakos, "High-performance heterogeneous computing with the Convey HC-1," *Computing in Science Engineering*, vol. 12, no. 6, pp. 80 –87, 2010.

- [8] J. M. Kunkel and P. Nerge, "System performance comparison of stencil operations with the Convey HC-1," Research Group Scientific Computing, University of Hamburg, Tech. Rep. 2010-11-16, 2010.

- [9] Convey Computer, http://www.conveycomputer.com/resources/ConveyBio informatics\_web.pdf.

- [10] Basic Linear Algebra Subprograms (BLAS), http://www.netlib.org/blas/.

- [11] S. Williams, R. Vuduc, L. Oliker, J. Shalf, K. Yelick, and J. Demmel, "Optimizing sparse matrix-vector multiply on emerging multicore platforms," *Parallel Computing (ParCo)*, vol. 35, no. 3, pp. 178–194, March 2009

- [12] N. Bell and M. Garland, "Efficient sparse matrix-vector multiplication on CUDA," NVIDIA Corporation, NVIDIA Technical Report NVR-2008-004, Dec. 2008.

- [13] W. Augustin, V. Heuveline, and J.-P. Weiss, "Optimized stencil computation using in-place calculation on modern multicore systems," pp. 772–784, 2009.

## Optimized Replacement in the Configuration Layers of the Grid ALU Processor

Ralf Jahr, Basher Shehan, Theo Ungerer University of Augsburg Institute of Computer Science 86135 Augsburg, Germany

Email: {jahr, shehan, ungerer}@informatik.uni-augsburg.de

Sascha Uhrig Technical University Dortmund Robotics Research Institute 44221 Dortmund, Germany

Email: sascha.uhrig@tu-dortmund.de

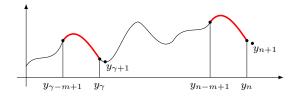

Abstract—The Grid ALU Processor comprises a reconfigurable two-dimensional array of ALUs. A conventional sequential instruction stream is mapped dynamically to this array by a special configuration unit within the front-end of the processor pipeline. One of the features of the Grid ALU Processor are its configuration layers, which work like a trace cache to store instruction sequences that have been already mapped to the ALU

Originally, the least recently used (LRU) strategy has been implemented to evict older configurations from the layers. As we show in this paper the working set is frequently larger than the available number of configuration layers in the processor resulting in thrashing. Hence, there is quite a large gap between the hit rate achieved by LRU and the hit rate achievable with an optimal algorithm. We propose an approach called qdLRU to enhance the performance of the configuration layers. Using qdLRU closes the gap between LRU and an optimal eviction strategy by 66% on average and achieves a maximum performance improvement of 390% and 5.06% on average with respect to the executed instructions per clock cycle (IPC).

Index Terms-Trace Cache, Replacement Strategy, Post-link Optimization, Feedback-directed Optimization, Coarse-Grained Reconfigurable Architecture

#### I. INTRODUCTION

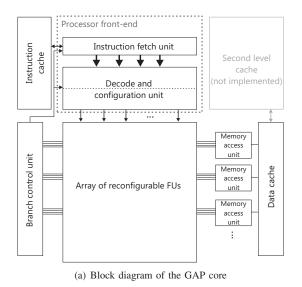

Within this paper, we present an optimization for the Grid ALU Processor (GAP), which has been introduced by Uhrig et al. [1]. It brings together a superscalar-like processor frontend and a coarse-grained reconfigurable architecture, i.e. a reconfigurable array of functional units (FUs). The front-end consisting of instruction fetch and decode unit is extended with a new configuration unit. This unit maps the instructions from the instruction stream dynamically and at run-time onto the array of FUs. Mapping of instructions and execution of instructions in the array run in parallel until there is a reason to flush the array and restart the mapping process. The mapping which has been built until this moment is called a configuration.

These configurations can be buffered in so-called configuration layers, which are formed by some memory cells very close to all the FUs. The configuration layers are very similar to trace caches. If a part of a program, i.e. a configuration, is already stored in the configuration layers it can be executed faster because it does not have to go through the front-end first, so instruction cache misses cannot occur. The timing inside the

array is optimized, too. Because of this, it is a worthwhile goal to increase the usage of the configuration layers. Analyzing the execution of benchmarks we came to the conclusion that for some of them our default replacement strategy LRU works unexpectedly bad, even worse than replacing a random configuration layer (we call this strategy RANDOM). So LRU is in some cases not clever at all and humbles the execution speed.

The main contributions of this paper are (1) the analysis and comparison of the behavior of well-known replacement algorithms when applied to the replacement in the configuration layers and (2) the introduction and analysis of qdLRU. QdLRU improves the hit rate of LRU by adding flags to the program code based on a feedback-directed approximation of the working sets.

After giving a short introduction of the target platform in Section II, we discuss some basics about replacement strategies in Section III. The extended version of LRU called qdLRU is introduced in Section IV and evaluated in Section V. Related work is presented in Section VI and Section VII concludes the paper.

#### II. TARGET PLATFORM: THE GRID ALU PROCESSOR

The Grid ALU Processor (GAP) has been developed to speed up the execution of conventional single-threaded instruction streams. To achieve this goal, it combines the advantages of superscalar processor architectures, those of coarse-grained reconfigurable systems, and asynchronous execution.

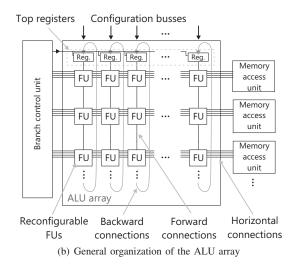

A superscalar-like processor front-end consisting of fetchand decode units is used together with a novel configuration unit (see Figure 1(a)) to load instructions and map them dynamically onto an array of functional units (FUs) accompanied by a branch control unit and several load/store units to handle memory accesses (see Figure 1(b)).

The array of FUs is organized in columns and rows. Each column is dynamically and per configuration assigned to one architectural registers. Instructions are assigned to the columns whose register match the instructions' output registers. The rows of the array are used to model dependencies between instructions. If an instruction B is dependent of an instruction A, it will be mapped to a row below the row of A. This way it is possible for the in-order configuration unit to also "issue"

Fig. 1. Architecture of the Grid ALU Processor

dependent instructions without the need of complex out-oforder logic. A bimodal branch predictor is used to effectively map control dependencies onto the array.

Execution starts in the first row of the array. The dataflow is performed asynchronously inside the array of FUs and it is synchronized with the clock of the branch control unit and the L/S units by so-called timing tokens [1].

Whenever either a branch is miss-predicted or execution reaches the last row of the array with configured FUs the array is cleared and the configuration unit maps new instructions starting from the first row of the array. In order to save configurations for repeated execution all elements of the array are equipped with some memory cells which form configuration layers. Typically, 2, 4, 8, 16, 32, or 64 configuration layers are available. The array is quasi three-dimensional and its size can be written as columns x rows x layers.

With this extension it has to be checked before mapping new instructions if the next instruction to execute is equal to the first instruction in any of the layers. If a match is found, the corresponding layer is set to active and execution continues there. If no match is found, the least recently used configuration layer is cleared and used to store the new configuration. In all cases, the new values of registers calculated in columns are copied into the registers at the top of the columns.

To evaluate the architecture a cycle- and signal-accurate simulator has been developed. It uses the Portable Instruction Set Architecture (PISA), hence the simulator can execute the identical program files as the SimpleScalar simulation tool set [2] (but it is not based on it). Detailed information about the processor are given by Uhrig et al. [1] and Shehan et al. [3].

#### III. TOWARDS AN IMPROVED POLICY

Several basic terms of replacement strategies with respect to the GAP architecture are discussed in this section.

#### A. Measuring the Performance of a Replacement Strategy

To analyze the performance of a replacement policy, we suggest two measures. The total hit rate  $h_{total}$  of the layer subsystem, which is the number of accesses of layers which can be found in the configuration layers  $a_{hit}$  divided by the total number of accesses  $a_{total}$ . The total hit rate  $h_{total}$  can also be understood as the sum of the hit rate by re-accessing the identical configuration subsequently  $h_{loop} = a_{loop}/a_{total}$ , which is independent from the number of layers available, and the hit rate contributed by the layer subsystem  $h_{layer} = a_{layer}/a_{total}$  for all other accesses:

$$h_{total} = \frac{a_{hit}}{a_{total}} = \frac{a_{loop}}{a_{total}} + \frac{a_{layer}}{a_{total}} = h_{loop} + h_{layer}$$

A replacement policy can influence only the hit rate of the layer subsystem  $h_{layer}$ . For a given benchmark,  $h_{loop}$  has the same value for all replacement strategies.

An optimal offline replacement algorithm (named OPT in the remainder) has been introduced by Belady [4] and it can be used as upper bound. In other words, no (online) replacement policy can achieve a better hit rate than this offline policy, which chooses the element for eviction that will be reused as the last one of all elements in the future.

Another offline algorithm has been mentioned by Temam [5] with the goal to maximize the number of instructions which can be accessed without cache misses. As upper bound for the performance of a replacement policy the algorithm OPT is a much more feasible measure because in the GAP, the penalty caused by activating the front-end of the processor when a new configuration must be build is much higher compared to the time, which is saved when some additional instructions can be found in a layer.

The second measure to evaluate a replacement policy is the performance of the whole system, which is e.g. described by the number of instructions executed per clock cycle (IPC).

#### B. Known algorithms and their performance

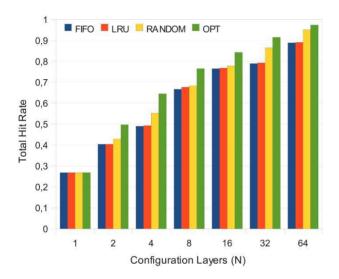

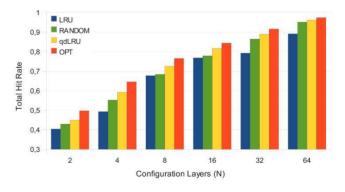

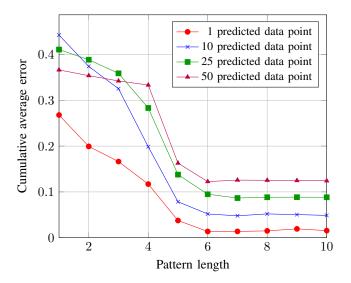

Figure 2 shows the simulated average total hit rate  $h_{total}$  of different well-known page replacement policies and the optimal offline policy OPT for 15 benchmarks of the MiBench Benchmark Suite [6] executed on the GAP with an array of width 12 and height 12 and a varying number of configuration layers. The hit rate achieved with one layer is equal to  $h_{loop}$  and replacement policies do not have any influence on it. The additional hit rate achieved with more than one layer is contributed by the layer subsystem, i.e.  $h_{layer}$ . As expected, LRU performs slightly better than FIFO. The out-performance of RANDOM over LRU is surprising as this replacement strategy behaves quite dumb by evicting random elements.

Fig. 2. Average total hit rate over 15 benchmarks for several numbers of configuration layers of GAP configured with an array of 12x12xN functional units

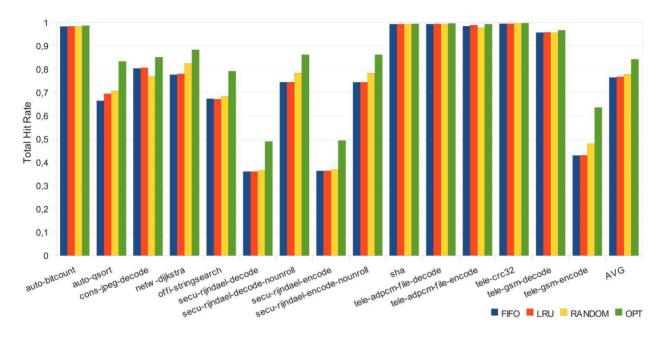

A more detailed view on the hit rate achieved with FIFO, LRU, RANDOM and OPT for the 15 benchmarks on GAP with a 12x12x16 array is presented in Figure 3. Six benchmarks reach a nearly optimal total hit rate close to 1.0 while benchmarks like auto-qsort, netw-dijkstra, offi-stringsearch, secu-rijndael-encode and others show a larger gap between the policies.

Table I shows the gap  $\Delta$  between the performance of LRU and OPT. The second column is the difference  $\Delta$  of the hit rates of LRU and OPT. In the third column, the achievable improvement with respect to the hit rate of LRU is shown. Closing this gap is the goal of our work.

#### C. Thrashing as major drawback of LRU

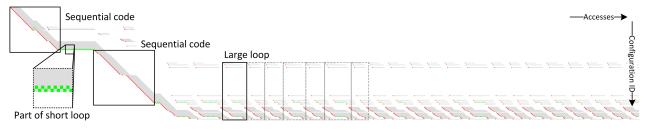

As first step towards an improved replacement policy we designed a graphical representation showing configuration layer accesses and the state of the layers. This type of graphics is referred to as *access plot* in the following. As example, the first 1000 accesses in the layer subsystem are shown in Figure 4(a) and 4(b). To render an access plot, the accesses to configurations are recorded in the GAP simulator. Next,

| Layers | $\Delta$ | $\Delta$ / LRU |

|--------|----------|----------------|

| 1      | 0        | 0%             |

| 2      | 0.09     | 23%            |

| 4      | 0.15     | 31%            |

| 8      | 0.09     | 13%            |

| 16     | 0.08     | 10%            |

| 32     | 0.12     | 16%            |

| 64     | 0.08     | 9%             |

| AVG    | 0.09     | 15%            |

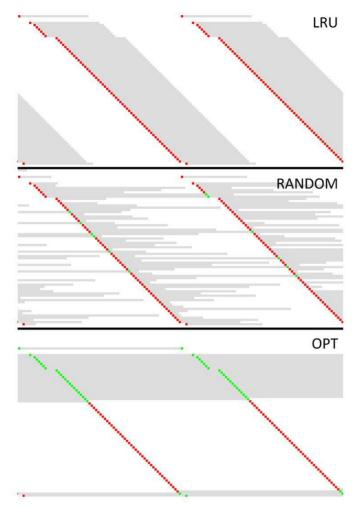

each configuration is given an incrementing number (ID). Each access to a configuration is numbered, too. To plot an access, its coordinates are determined by its access number (X-axis) and the number of the accessed configuration (ID, Y-axis). If an already available configuration is accessed, it is colored green (or dark grey, if printed black/white only). If the configuration is not available it is colored red (or black, if printed black/white only). If the target configuration is the same as the one requested by the last access, the current configuration will not be modified. The reuse of the current configuration is not shown in the image because it has no interference with the replacement policy. The content of the layers at the time an access is done is displayed by vertical light gray pixels.

Although only a short part of the total program execution time is visible in Figure III-C it is sufficient to show some important facts. First, there is only a small number of different array configurations compared to the number of actually executed configurations which can be recognized by the width/hight relationship of the plot. Second, several patterns appear very often. They differ mostly by the number of configurations which they contain and the locality [7] of the accesses of the configurations:

- Sequentially executed code, e.g. the starting sequence: The reuse distance is extremely high or unlimited.

- Small loops, i.e. a small number of repeatedly executed configurations: The reuse distance is comparable to the number of configurations of the loop; the number of configurations is smaller than the number of configuration layers.

- Large loops, i.e. a larger number of repeatedly executed configurations: The reuse distance is comparable to the number of configurations of the loop; the number of configurations is larger than the number of configuration layers.

- Program phases: They consist of multiple loops and phases of sequentially executed code. As they contain lots of configurations the locality is only medium. The reuse distance can vary.

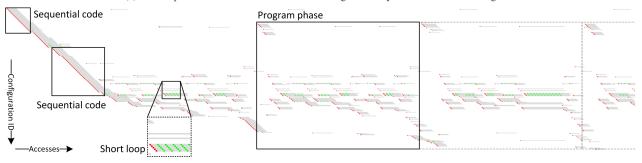

In a more detailed analysis we came to the conclusion that the well-known and already mentioned eviction polices show for these patterns always a very similar behavior. For sequential code, none of the strategies can achieve hits because configurations with infinite (or very long) time since a last usage are loaded. Small loops can be handled very well

Fig. 3. Total hit rate for the benchmarks run on GAP with a 12x12x16 array

by LRU and OPT. RANDOM does not perform competitive because it evicts random configurations that might be needed again very soon. Large loops are the sticking point. If LRU is used, thrashing (see. e. g. [8]) can occur because the algorithm has to evict configurations that are part of the beginning of the loop and will be reused soon. The hit rate drops to zero. RANDOM performs better because it keeps at least some of the configurations of the loop in the layers. The OPT algorithm does the following: In every iteration of the loop it does not throw away some of the configurations, but keeps them for the next iteration. In Figure 5 the access plots for LRU, RANDOM and OPT can be seen. LRU produces only misses while RANDOM provides some and OPT a reasonable number of hits.

In short, for the replacement of the configuration layers thrashing is the main issue on the way to close the gap between LRU and OPT. Increasing the number of configuration layers would solve this problem to some extend but the number of layers is restricted by their hardware complexity and more complex applications would tend to thrashing again. Therefore, we look for a better replacement strategy to prevent thrashing or at least limit its effects.

#### IV. QDLRU STRATEGY

The main idea of this new approach is to explicitly add flags to those configurations which would cause thrashing. Those marked configurations are then immediately replaced by another configuration. In other words, they are inserted at the least recently used position instead of the most recently used position. Because the marked configurations are dropped quickly we call the strategy *quick drop LRU* (qdLRU).

As example assume the configurations  $c_0$  to  $c_{47}$  are in a

working set  $W:=[c_0,...,c_{47}]$  and GAP has 32 configuration layers. Repeated executions of W would cause thrashing (when using LRU as replacement strategy) because the size of the working set |W|=48 is larger than 32 which is the number of layers available in the GAP. If W is executed for a longer time with LRU then  $h_{layer}$  drops to 0 because of thrashing. The optimal offline strategy would buffer 31 of the 48 configurations, hence:  $h_{layer}\approx 31/48=0.64583$ . With qdLRU you get the same and optimal hit rate for this thrashing-risky situation.

#### A. Adding flags to instructions

QdLRU is a feedback-directed optimization. The basis to be able to calculate which instructions shall be marked is a trace of addresses of the first instructions of the configurations executed during a program execution. To get this trace file we use the cycle-accurate simulator available for the GAP.

The next step is to find the so-called configuration lines. A configuration line C, e.g.  $C = \{c_0, ..., c_{47}\}$ , represents one of the diagonal lines in Figure 5 and is very similar to a working set. To generate the set of all configuration lines  $\mathbb{C} = \{C_0, ..., C_j\}$  and their usage counters the heuristics described in Listing 1 is used.

These configuration lines represent the working sets with the "smallest degree of reuse". To construct them, we assume that, whenever a configuration is already available in the working set and different from the last handled configuration, a branch back to the start of the current working set is performed.

Afterwards, several configurations within each configuration line are selected as candidates to be dropped quickly. For this, the configuration lines are split into two groups, one group  $\mathbb{C}_{short}$  contains all lines whose length is smaller than the

```

Listing 1. Algorithm to configuration lines

input: list < configuration > trace

#define line list < configuration >

set < line > all_lines

map<line, int > line_counters

line current_line = {}

configuration last_configuration

foreach (configuration item in trace)

if (item == last_configuration)

// Do nothing

else if (item ∉ current_line)

current_line += item

last_configuration = item

else

all_lines += current_line

line_counters[current_line]++

current_line = {}

last_configuration = item

```

number of layers in the processor and the other group  $\mathbb{C}_{long}$  contains all the other configuration lines, those configuration lines are too long to fit into the layers without evictions. With having prepared these groups the following algorithm is performed:

- 1) Select a configuration line item from  $\mathbb{C}_{long}$ .

- 2) Select from item the configuration with the least usage in  $\mathbb{C}_{short}$ , mark its first instruction.

- 3) Select all configuration lines from  $\mathbb{C}_{long}$  where the number of all configurations minus the number of all marked configurations in the line is smaller than the number of layers of the processor. Move them to  $\mathbb{C}_{short}$ .

- 4) If  $\mathbb{C}_{long}$  is not empty, restart the algorithm with step 1.

By this heuristic, we select configurations in a manner that they influence as little as possible the execution of configuration lines that fit into the layers. If a configuration line fits into the layers, but one of its configurations is marked, than this can humble the hit rate of this configuration line extremely.

In the last step, our post-link optimization tool GAPtimize (introduced in [9]) is used to mark the first instruction of the selected configurations with a special *drop quickly* flag. This flag directs the configuration layer subsystem of GAP to drop the configuration starting with the actual instruction quickly.

#### B. Executing the modified binary

When implementing qdLRU, changes are necessary both in hardware and in software. The changes in hardware are very simple. All which has to be done is to make sure that either a configuration beginning with a marked instruction is inserted in the least recently used position in the LRU access queue or that, when looking for a layer for eviction, it is first looked for a configuration layer starting with a marked instruction and then replacing this layer.

If a program is executed on the GAP which has not been optimized (and is hence without flags), then qdLRU behaves exactly like LRU, which still offers reasonable performance. This graceful degradation is one of the requirements of all techniques used for the GAP.

#### V. EVALUATION

For the practical evaluation we rely on the cycle-accurate simulator which has been developed for the GAP and was extended to support qdLRU. As the hardware complexity of GAP can vary very much because of different sizes of its ALU array, we set it to a fixed size of 12 columns and 12

(a) Access plot for the first 1000 accesses of configuration layers for benchmark stringsearch

(b) Access plot for the first 1000 accesses of configuration layers for benchmark qsort

Fig. 4. Access plots (see Section III-C) for GAP with 12x12x16 array and LRU as replacement policy; some patterns are marked and labeled.

Fig. 5. Access plots (see Section III-C) for LRU, RANDOM and OPT (from top to bottom) dealing with a large loop (rijndael on GAP with 12x12x32 array)

rows, which is a realistic size. The performance of the qdLRU policy was evaluated using a varying number of layers. The configuration of the GAP is in the following abbreviated as columns x rows x layers.

We use integer-focused benchmarks from the MiBench benchmark suite [6] which have been compiled with GCC for the PISA instruction set architecture (see [2]) with optimizations turned on, i.e. -03. These benchmarks are analyzed and modified with GAPtimize, our tool for feedback-directed post-link optimizations.

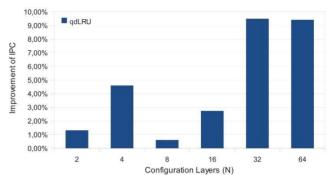

For 15 benchmarks, including benchmarks where we expected only little or no change, we achieve an improvement in performance measured by the IPC of 5.06% on average for qdLRU compared to LRU. The highest improvements are achieved for 32 and 64 layers, where we get improvements of 9.48% and 9.41% respectively (compare Figure 8). These values do not seem to be very brilliant which is mainly caused by the fact that for most of the benchmarks we cannot expect the improvement to be very high due to a very small gap

Fig. 6. Average IPC improvement for 15 benchmarks executed on GAP and configurations 12x12xN with qdLRU compared to LRU

between LRU and OPT. Details are shown in Figure 6.

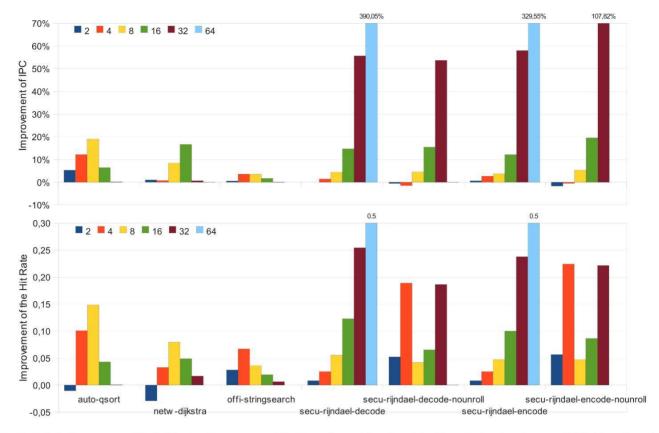

In the top part of Figure 7, more details on the IPC are displayed for some selected benchmarks where thrashing is an issue. The most impressive numbers can be seen for the benchmarks secu-rijndael-decode and secu-rijndael-encode with a maximum improvement of 390 % for the IPC achieved with qdLRU compared to LRU.

This improvement of the IPC is mainly based on the improved hit rate of the layer subsystem. The total average improvement of the hit rate over 15 benchmarks and all configurations is 0.06. This average hit-rate improvement seems to be small but it has to seen in relation to the maximal possible improvement (0.09) which can be achieved with the optimal algorithm OPT (see Section III-B).

For selected benchmarks which might cause thrashing with LRU the total hit rate can be seen in the bottom part of Figure 7. Here again, the benchmarks secu-rijndael-encode and secu-rijndael-decode show supreme results as thrashing is here a very critical problem when using LRU.

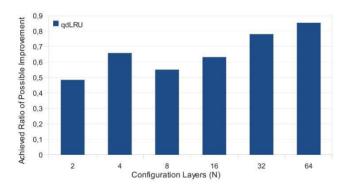

In Figure 8 we show the average performance of LRU and qdLRU compared to OPT and RANDOM. QdLRU shows better performance than LRU and RANDOM. The gap between LRU and OPT can be closed with qdLRU by 65.97 % on average, varying between 48,38 % for 2 layers and 78,05% for 32 layers (see Figure 9).

Fig. 8. Simulated total hit rate for LRU, RANDOM, qdLRU and OPT (average over 15 benchmarks, GAP with 12x12xN functional units)

Fig. 7. Relative improvement of the IPC (top) and improvement of the hit rate (bottom) for selected thrashing-risky benchmarks run on GAP with configurations 12x12xN for qdLRU compared to LRU

Fig. 9. Ratio of the gap between qdLRU an OPT which can be covered by qdLRU (average over 15 benchmarks, GAP with 12x12xN functional units)

If the memory latency (which has been set to 24 clock cycles) is increased, we expect the effect of an improved hit rate to have stronger implications on the system performance. On the other side, if the size of the also available instruction cache is increased, the effect of increasing the hit rate will decrease because the penalty to load instructions from the instruction cache will decrease due to less instruction cache misses.

#### VI. RELATED WORK

As mentioned before the configuration layers of the GAP are used to buffer configurations. They work like a cache and a replacement policy is implemented to find the element to evict if space is needed to load a new one. For the GAP, finding a suitable replacement strategy for the configuration layers has not yet been explored. Nevertheless, related work can be found mainly dealing with caches in general and trace caches.

The main difference of the replacement problem for configuration layers compared to general caches is the extremely small number of configurations layers compared to the large number of lines in caches. Because of this, thrashing-risky situations where the working set is larger than the number of available lines are much more frequent for configuration layers than for caches.

Our goal is to find a lightweight solution which can make use of the software infrastructure already available and used for other platform-specific code optimizations, e.g. static speculation [9]. Because of this, our attention is drawn to techniques using both hardware- and software techniques.

As hardware-only solutions, two classes of strategies are known. The first are well-known algorithms which can be implemented with small or reasonable effort in hardware. Some of those strategies are FIFO, RANDOM, WsClock [10] and LRU. From these strategies, LRU is deemed to be the superior

one. Together with OPT as upper bound the performance of LRU, FIFO and RANDOM have been compared for our situation in Section III-B.

The second class of algorithms are the Dynamic Insertion Policy (DIP) proposed by Qureshi et al. [11] and the Shepherd Cache proposed by Rajan etc al. [12]. Both share the property that they require additional hardware effort. In our experiments, we also got for our particular situation performance numbers at most comparable to LRU for the Shepherd Cache. The DIP is only applicable if it can select between LRU and BIP with extreme parameters to prevent thrashing. The suggested approach to divide the configuration layers into two sets does not seem to be applicable due to the small number of configuration layers. The small number of lines prevents using strategies like ARC [13] where the lines are split into two sections and handled in different ways.

Some other techniques have also been proposed (see e.g. [14]) but most of them either require large changes of the hardware and/or are not supposed to work well because the low number of layers available in the GAP normally restricts the eventual gain in performance caused by replacement strategies.

Trace caches as introduced by Rotenberg et al. [15] work for superscalar processors very similar to the configuration layers because they are used to buffer parts of a program flow, too. To our knowledge, nobody has yet been working on thrashing situations in this context.

#### VII. CONCLUSION AND FUTURE WORK

We introduced a software-supported replacement strategy for the configuration layers of the GAP processor, which are used like a trace cache to buffer instructions sequences ready for execution. So far, LRU is used as replacement strategy which offers an unsatisfying performance for several benchmarks. Strangely enough, LRU shows for some benchmarks even worse performance than RANDOM, a strategy evicting a random element. The main reason for this is thrashing, which can happen if the elements of a working set are processed repeatedly and sequentially, i.e. there is a huge degree of locality, and the set contains more configurations than the GAP provides configuration layers. In this case, the hit rate achieved with LRU collapses.

To overcome this issue, we proposed a replacement strategy called qdLRU and a heuristic to approximate the working sets in software. Based on working sets we select some configurations which are evicted immediately from the configuration layers. With this, we can draw the behavior of qdLRU nearer to the optimal strategy OPT. The performance measured by the IPC for qdLRU is on average 5.06% higher than the performance achieved by LRU. A peak improvement of 390% is gained for secu-rinjdael-decode caused by a peak improvement of the hit rate of 0.5.

This approach could be adapted for all situations in which a replacement strategy is needed for a small number of complex elements with many thrashing-risky situations. The introduced strategy requires only very little changes of the hardware when LRU has already been implemented. It also supports graceful degradation back to LRU.

As future work, we propose to work on the detection of working sets. The rule which has been introduced is simple and effective. Nevertheless, there are situations where this rule cannot find a sufficient solution. Hence, to find better solutions it should be thought about the scope of the working sets. From our point of view, it is important that the configurations in a working set should be executed repeatedly in the same order. If this restriction is weakened, the scope of working sets could be enlarged which must be handled carefully but might lead to further improved results. Concluding, it might be possible to find better solutions with biologically inspired algorithms, e.g. ant algorithms or genetic algorithms. Linear programming should also be taken into consideration.

#### REFERENCES

- S. Uhrig, B. Shehan, R. Jahr, and T. Ungerer, "The two-dimensional superscalar gap processor architecture," *International Journal on Advances in Systems and Measurements*, 2010.

D. Burger and T. Austin, "The simplescalar tool set, version 2.0," *ACM*

- [2] D. Burger and T. Austin, "The simplescalar tool set, version 2.0," ACM SIGARCH Computer Architecture News, vol. 25, no. 3, pp. 13–25, June 1997

- [3] B. Shehan, R. Jahr, S. Uhrig, and T. Ungerer, "Reconfigurable grid alu processor: Optimization and design space exploration," in *Proceedings of* the 13th Euromicro Conference on Digital System Design (DSD) 2010, Lille, France, 2010.

- [4] L. A. Belady, "A study of replacement algorithms for a virtual-storage computer," *IBM Systems*, vol. 5, no. 2, pp. 78–101, 1966.

- [5] O. Temam, "Investigating optimal local memory performance," SIGOPS Oper. Syst. Rev., vol. 32, no. 5, pp. 218–227, 1998.

- [6] M. Guthaus, J. Ringenberg, D. Ernst, T. Austin, T. Mudge, and T. Brown, "MiBench: A free, commercially representative embedded benchmark suite," 4th IEEE International Workshop on Workload Characteristics, pp. 3–14, December 2001.

- [7] P. J. Denning, "The locality principle," *Commun. ACM*, vol. 48, no. 7, pp. 19–24, 2005.

- [8] P. Denning, "Thrashing: its causes and prevention," in AFIPS '68 (Fall, part I): Proceedings of the December 9-11, 1968, fall joint computer conference, part I. New York, NY, USA: ACM, 1968, pp. 915–922.

- [9] R. Jahr, B. Shehan, S. Uhrig, and T. Ungerer, "Static speculation as post-link optimization for the grid alu processor," in *Proceedings of the* 4th Workshop on Highly Parallel Processing on a Chip (HPPC 2010), 2010.

- [10] R. W. Carr and J. L. Hennessy, "WSCLOCK a simple and effective algorithm for virtual memory management," in SOSP '81: Proceedings of the eighth ACM symposium on Operating systems principles. New York, NY, USA: ACM Press, 1981, pp. 87–95.

- [11] M. K. Qureshi, A. Jaleel, Y. N. Patt, S. C. Steely, and J. Emer, "Adaptive insertion policies for high performance caching," in ISCA '07: Proceedings of the 34th annual international symposium on Computer architecture. New York, NY, USA: ACM, 2007, pp. 381–391.

- [12] K. Rajan and G. Ramaswamy, "Emulating optimal replacement with a shepherd cache," in MICRO 40: Proceedings of the 40th Annual IEEE/ACM International Symposium on Microarchitecture. Washington, DC, USA: IEEE Computer Society, 2007, pp. 445–454.

- [13] N. Megiddo and D. S. Modha, "Outperforming Iru with an adaptive replacement cache algorithm," *Computer*, vol. 37, no. 4, pp. 58–65, 2004.

- [14] G. Keramidas, P. Petoumenos, and S. Kaxiras, "Where replacement algorithms fail: a thorough analysis," in CF '10: Proceedings of the 7th ACM international conference on Computing frontiers. New York, NY, USA: ACM, 2010, pp. 141–150.

- [15] E. Rotenberg, S. Bennett, and J. E. Smith, "Trace cache: a low latency approach to high bandwidth instruction fetching," in MICRO 29: Proceedings of the 29th annual ACM/IEEE international symposium on Microarchitecture. Washington, DC, USA: IEEE Computer Society, 1996, pp. 24–35.

# Performance Engineering of an Orthogonal Matching Pursuit Algorithm for Sparse Representation of Signals on Different Architectures

Markus Stürmer, Harald Köstler University of Erlangen-Nuremberg 91058 Erlangen Germany Florian Rathgeber Imperial College London London SW7 2AZ United Kingdom

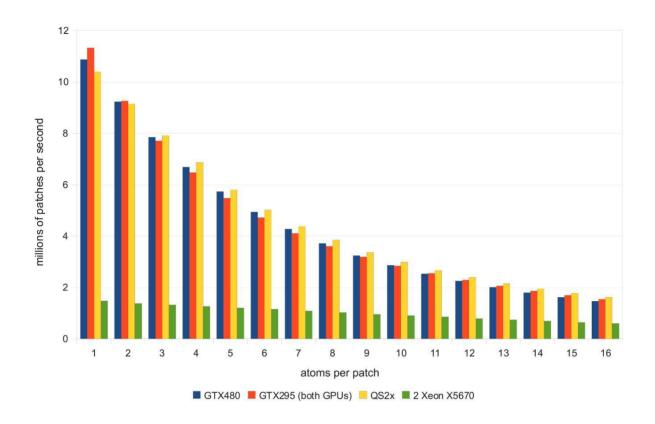

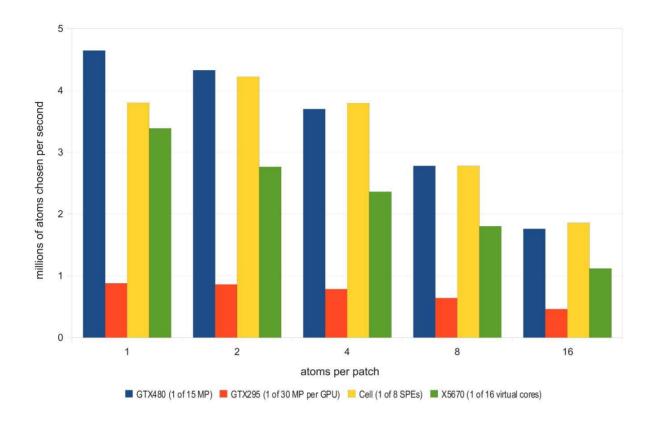

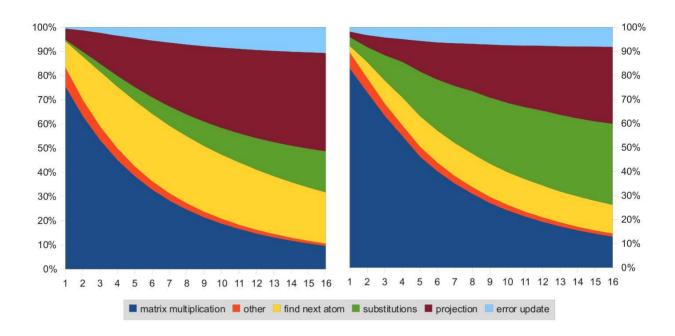

Abstract—Modern multicore architectures require adapted, parallel algorithms and implementation strategies for many applications. As a non-trivial example we chose in this paper a patch-based sparse coding algorithm called Orthogonal Matching Pursuit (OMP) and discuss parallelization and implementation strategies on current hardware. The OMP algorithm is used in imaging and involves heavy computations on many small blocks of pixels called patches. From a global view the patches within the image can be processed completely in parallel but within one patch the algorithm is hard to parallelize. We compare the performance on the Cell Broadband Engine Architecture (CBEA), different GPUs, and current multicore CPUs.

Index Terms—Batch-OMP algorithm, orthogonal matching pursuit, GPGPU, Cell Broadband Engine Architecture, performance engineering, multicore

#### I. Introduction

Since image acquisition systems produce more and more data and most imaging applications are time-critical, efficient implementations are needed that run on current hardware.

In this work we consider sparse coding, i.e. finding sparse representations of signals or images, based on a frame (overcomplete basis), the so-called dictionary. Sparse representations are widely used and currently state-of-the-art in imaging applications like image denoising, super-resolution, or image restoration [1], [2], [3]. Since sparse coding is in general an NP-hard problem, we reduce the complexity for the creation of the sparse representation of an image by decomposing it into many small blocks called patches. Then, sparse coding is done independently for each of them. While the

patches thus can be processed completely in parallel, within one patch the very time-consuming and hardly parallelizable task is to find the coefficients for the sparse representation in the given basis. We solve this approximately by a variant of an orthogonal matching pursuit (OMP) [4], the Batch-OMP algorithm [5].

In previous work we have shown that sparse representations are suitable for CT image denoising and compared the results to other denoising approaches [6], [7], [8], [9]. We also accelerated the Batch-OMP algorithm on the Cell Broadband Engine Architecture (CBEA) in order to achieve close to real-time performance [10]. In this paper we compare the performance of the Batch-OMP algorithm on different hardware architectures like standard CPUs, the CBEA, and GPUs.

Sparse coding is a prominent topic and thus several other contributions have been made by other groups. GPU, CPU, and CBEA implementations for the related compressive sensing are presented in [11], [12] and general image reconstruction algorithms on GPUs in [13]. In [14], a matching pursuit algorithm is implemented on the GPU, which is easier to parallelize and requires less computational effort than OMP. Closest to our work are Septimus and Steinberg [15], who port the Batch-OMP algorithm to a Xilinx Virtex 5 FPGA, and Braun [16], who shows a GPU implementation of the Batch-OMP algorithm. Since Braun states that GPUs are not significantly better or worse than CPUs for OMP, we decided to make a deeper analysis. We achieve better performance with our manually tuned code, but still observe interestingly similar results for CBEA, GPUs and standard CPUs. This is due to the versatile requirements of the different parts of OMP algorithm which cancel out the specifics of each platform.

In the following we give more details about sparse representations and the Batch-OMP algorithm in section II. After that we discuss our GPU implementation strategy in section III and in section IV we present a performance comparison on CPU, GPU, and CBEA. Future work is outlined in section V.

#### II. METHODS

#### A. Sparse representation

The goal of a sparse representation of a signal is to reduce the amount of data required to store it. This is achieved by first defining a frame — an overcomplete basis of the signal vector space—that is also called dictionary and then representing signals compactly by a linear combination of only few vectors out of the frame. The signals can also be represented only approximately to reduce data. Mathematically, the problem of finding the sparsest representation  $\mathbf{a} \in \mathbb{R}^K$  of a signal  $\mathbf{X} \in \mathbb{R}^n$ , up to a given error tolerance  $\epsilon > 0$ , can be formulated as:

$$\min_{\mathbf{a}} \|\mathbf{a}\|_0$$

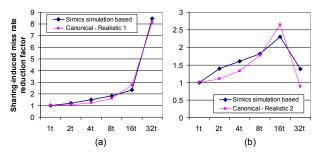

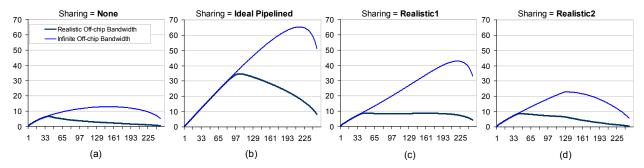

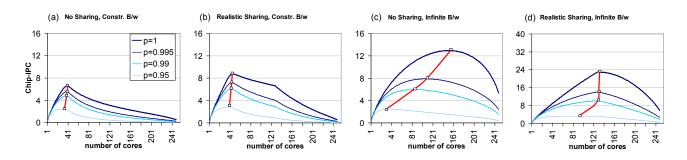

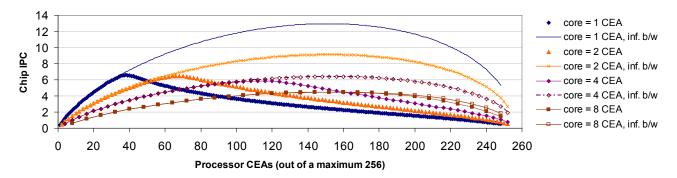

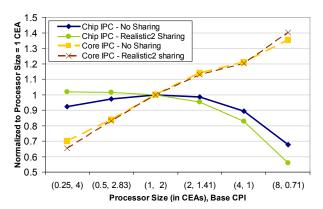

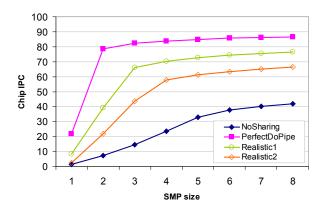

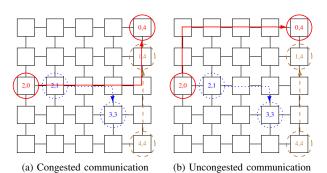

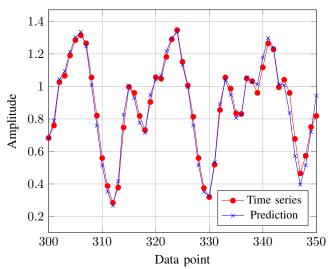

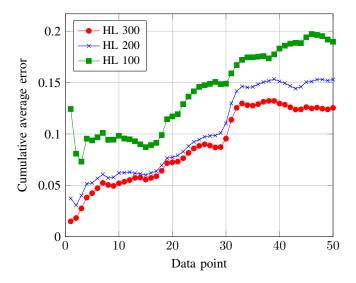

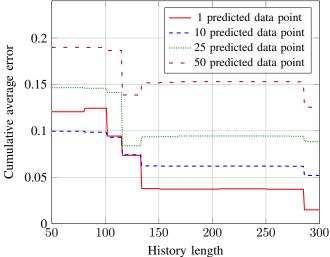

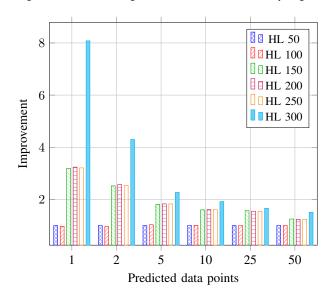

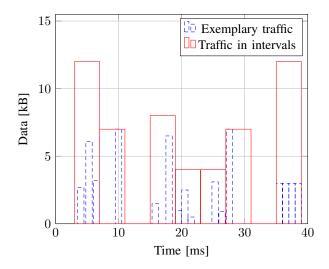

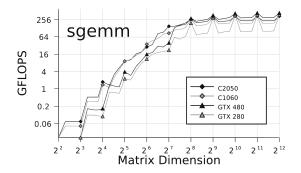

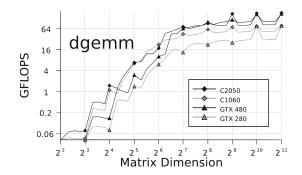

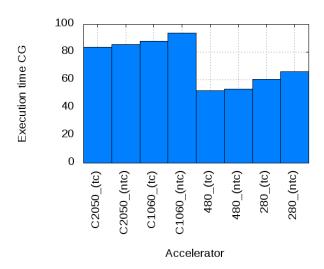

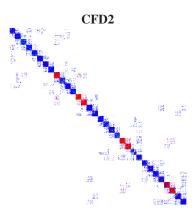

subject to  $\|\mathbf{D}\mathbf{a} - \mathbf{X}\|_2 \le \epsilon$ , (1)