Jan Wassenberg

# Efficient Algorithms for Large-Scale Image Analysis

Schriftenreihe Automatische Sichtprüfung und Bildverarbeitung | Band 4

Jan Wassenberg

### Efficient Algorithms for Large-Scale Image Analysis

#### Schriftenreihe Automatische Sichtprüfung und Bildverarbeitung Band 4

Herausgeber: Prof. Dr.-Ing. Jürgen Beyerer

Lehrstuhl für Interaktive Echtzeitsysteme am Karlsruher Institut für Technologie

Fraunhofer-Institut für Optronik, Systemtechnik und Bildauswertung IOSB

Eine Übersicht über alle bisher in dieser Schriftenreihe erschienenen Bände finden Sie am Ende des Buchs.

# Efficient Algorithms for Large-Scale Image Analysis

by Jan Wassenberg

Dissertation, Karlsruher Institut für Technologie Fakultät für Informatik Tag der mündlichen Prüfung: 24. Oktober 2011

#### Impressum

Karlsruher Institut für Technologie (KIT) KIT Scientific Publishing Straße am Forum 2 D-76131 Karlsruhe www.ksp.kit.edu

KIT – Universität des Landes Baden-Württemberg und nationales Forschungszentrum in der Helmholtz-Gemeinschaft

Diese Veröffentlichung ist im Internet unter folgender Creative Commons-Lizenz publiziert: http://creativecommons.org/licenses/by-nc-nd/3.0/de/

KIT Scientific Publishing 2012 Print on Demand

ISSN: 1866-5934 ISBN: 978-3-86644-786-8

## Efficient Algorithms for Large-Scale Image Analysis

zur Erlangung des akademischen Grades eines

Doktors der Ingenieurwissenschaften

der Fakultät für Informatik des Karlsruher Instituts für Technologie

#### genehmigte

### Dissertation

von

### Jan Wassenberg

aus Koblenz

Tag der mündlichen Prüfung:24. Oktober 2011Erster Gutachter:Prof. Dr. Peter SandersZweiter Gutachter:Prof. Dr.-Ing. Jürgen Beyerer

### Abstract

The past decade has seen major improvements in the capabilities and availability of imaging sensor systems. Commercial satellites routinely provide panchromatic images with sub-meter resolution. Airborne line scanner cameras yield multi-spectral data with a ground sample distance of 5 cm. The resulting overabundance of data brings with it the challenge of timely analysis. Fully automated processing still appears infeasible, but an intermediate step might involve a computer-assisted search for interesting objects. This would reduce the amount of data for an analyst to examine, but remains a challenge in terms of processing speed and working memory.

This work begins by discussing the trade-offs among the various hardware architectures that might be brought to bear upon the problem. FPGA and GPU-based solutions are less universal and entail longer development cycles, hence the choice of commodity multi-core CPU architectures. Distributed processing on a cluster is deemed too costly. We will demonstrate the feasibility of processing aerial images of  $100 \text{ km} \times 100 \text{ km}$  areas at 1 m resolution within 2 hours on a single workstation with two processors and a total of twelve cores. Because existing approaches cannot cope with such amounts of data, each stage of the image processing pipeline – from data access and signal processing to object extraction and feature computation – will have to be designed from the ground up for maximum performance. We introduce new efficient algorithms that provide useful results at faster speeds than previously possible.

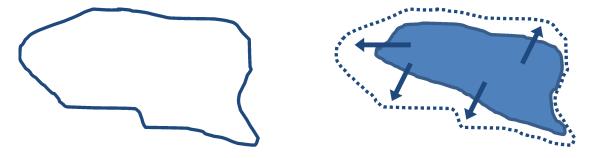

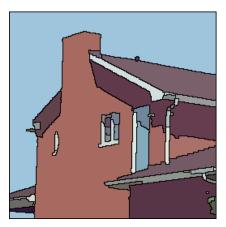

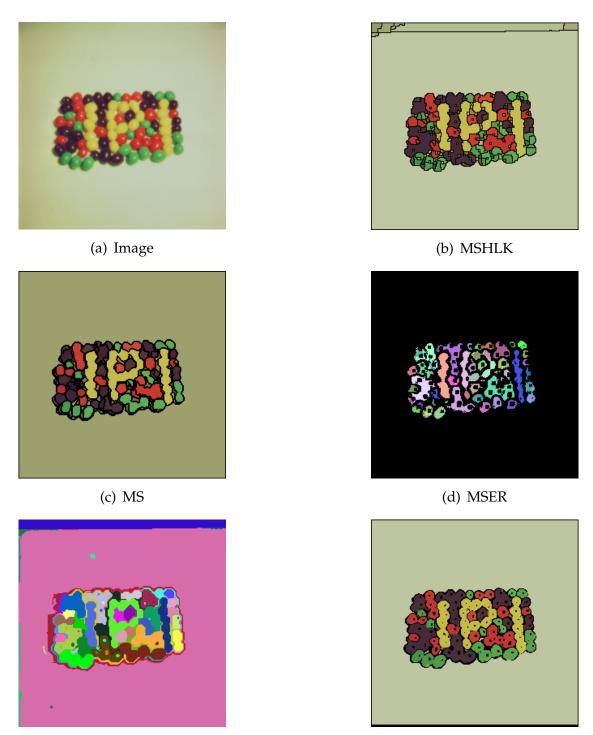

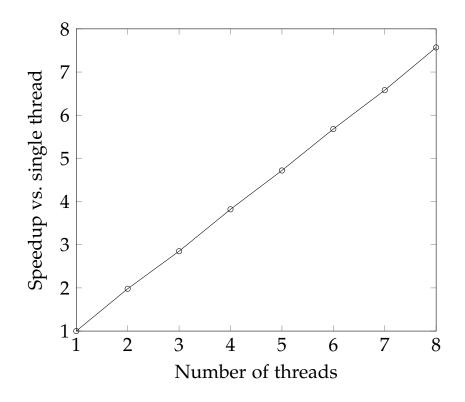

Let us begin with the most time-critical task – the extraction of 'object' candidates from an image, also known as segmentation. This step is necessary because individual pixels do not provide enough information for the screening task. A simple but reasonable model for the objects involves grouping similar pixels together. High-quality clustering algorithms based on mean shift, maximum network flow and anisotropic diffusion are far too time-consuming. We introduce a new graph-based algorithm with the important property of avoiding both under- and oversegmentation. Its distinguishing feature is the independent parallel processing of image tiles without splitting objects at the boundaries. Our efficient implementation takes advantage of SIMD instructions and outperforms mean shift by a factor of 50 while producing results of similar quality. Recognizing the outstanding performance of its microarchitecture-aware virtual-memory counting sort subroutine, we develop it into a general 32-bit integer sorter, yielding the fastest known algorithm for shared-memory machines.

Because segmentation groups together similar pixels, it is helpful to suppress sensor noise. The 'Bilateral Filter' is an adaptive smoothing kernel that preserves edges by excluding pixels that are distant in the spatial or radiometric sense. Several fast approximation algorithms are known, e.g. convolution in a downsampled higher-dimensional space. We accelerate this technique by a factor of 14 via parallelization, vectorization and a SIMD-friendly approximation of the 3D Gauss kernel. The software is 73 times as fast as an exact computation on an FPGA and outperforms a GPU-based approximation by a factor of 1.8.

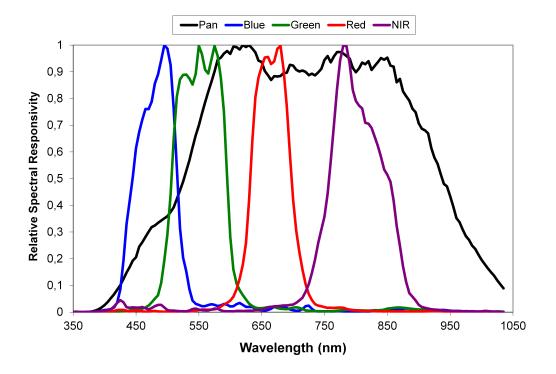

Physical limitations of satellite sensors constitute an additional hurdle. The narrow multispectral bands require larger detectors and usually have a lower resolution than the panchromatic band. Fusing both datasets is termed 'pan-sharpening' and improves the segmentation due to the additional color information. Previous techniques are vulnerable to color distortion because of mismatches between the bands' spectral response functions. To reduce this effect, we compute the optimal set of band weights for each input image. Our new algorithm outperforms existing approaches by a factor of 100, improves upon their color fidelity and also reduces noise in the panchromatic band.

Because these modules achieve throughputs on the order of several hundred MB/s, the next bottleneck to be addressed is I/O. The ubiquitous GDAL library is far slower than the theoretical disk throughput. We design an image representation that avoids unnecessary copying, and describe little-known techniques for efficient asynchronous I/O. The resulting software is up to 12 times as fast as GDAL. Further improvements are possible by compressing the data if decompression throughput is on par with the transfer speeds of a disk array. We develop a novel lossless asymmetric SIMD codec that achieves a compression ratio of 0.5 for 16-bit pixels and reaches decompression throughputs of 2700 MB/s on a single core. This is about 100 times as fast as lossless JPEG-2000 and only 20–60% larger on multispectral satellite datasets.

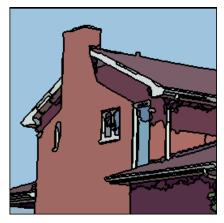

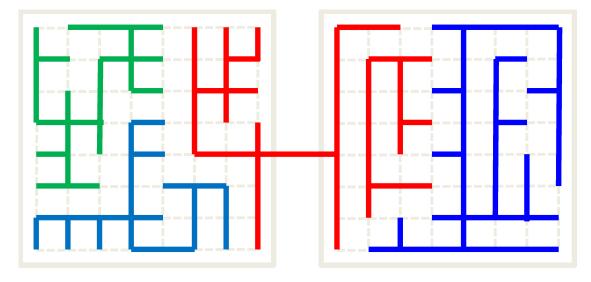

Let us now return to the extracted objects. Additional steps for detecting and simplifying their contours would provide useful information, e.g. for classifying them as man-made. To allow annotating large images with the resulting polygons, we devise a software rasterizer. High-quality antialiasing is achieved by deriving the optimal polynomial low-pass filter. Our implementation outperforms the Gupta-Sproull algorithm by a factor of 24 and exceeds the fillrate of a mid-range GPU.

The previously described processing chain is effective, but electro-optical sensors cannot penetrate cloud cover. Because much of the earth's surface is shrouded in clouds at any given time, we have added a workflow for (nearly) weather-independent synthetic aperture radar. Small, highly-reflective objects can be differentiated from uniformly bright regions by subtracting each pixel's background, estimated from the darkest ring surrounding it. We reduce the asymptotic complexity of this approach to its lower bound by means of a new algorithm inspired by Range Minimum Queries. A sophisticated pipelining scheme ensures the working set fits in cache, and the vectorized and parallelized software outperforms an FPGA implementation by a factor of 100.

These results challenge the conventional wisdom that FPGA and GPU solutions enable significant speedups over generalpurpose CPUs. Because all of the above algorithms have reached the lower bound of their complexity, their usefulness is decided

by constant factors. It is the thesis of this work that optimized software running on general-purpose CPUs can compare favorably in this regard. The key enabling factors are vectorization, parallelization, and consideration of basic microarchitectural realities such as the memory hierarchy. We have shown these techniques to be applicable towards a variety of image processing tasks. However, it is not sufficient to 'tune' software in the final phases of its development. Instead, each part of the algorithm engineering cycle design, analysis, implementation and experimentation – should account for the computer architecture. For example, no amount of subsequent tuning would redeem an approach to segmentation that relies on a global ranking of pixels, which is fundamentally less amenable to parallelization than a graph-based method. The algorithms introduced in this work speed up seven separate tasks by factors of 10 to 100, thus dispelling the notion that such efforts are not worthwhile. We are surprised to have improved upon long-studied topics such as lossless image compression and line rasterization. However, the techniques described herein may allow similar successes in other domains.

### Acknowledgements

I sincerely thank my advisor, Prof. Peter Sanders, for providing guidance – identifying promising avenues to explore, teaching algorithm engineering, and sharing the lore of clever optimizations. Thank you, Prof. Dr.-Ing. Jürgen Beyerer, for reviewing this thesis.

Looking back earlier, I thank my parents for their love and support, and for allowing me access to a TRS-80 microcomputer. The resulting interest in computing was kindled early on at Randolph School, especially by Dr. Robert Kirchner's physics assignment concerning a model rocket simulator. Thanks to my soccer coach, H. Killebrew Bailey, for instilling the spirit "practice hard, play hard; no regrets!"

I gratefully acknowledge the productive working environment at the FGAN-FOM research institute, now a part of Fraunhofer IOSB. Thanks to my office mates Dominik Perpeet and Sebastian Wuttke for interesting discussions over lunch and fruitful collaboration; Romy Pfeiffer and Anja Blancani for helping with administrative matters; my supervisor Dr. Wolfgang Middelmann and department head Dr. Karsten Schulz for providing guidance and the latitude to work on interesting problems.

This thesis builds upon machine-oriented groundwork laid for the 0 A.D. strategy game project starting in 2002. It has been a pleasure to work with this team of enthusiastic, self-motivated volunteers, especially Philip Taylor.

I am grateful to the authors of GDAL for developing a truly useful tool to read/write nearly any image file format. Thanks to Charles Bloom, Prof. Tanja Schultz and Dominik Perpeet for valuable feedback concerning parts of this work.

I appreciate the patience and understanding of friends, family, and most of all, my beloved Sufen. Her love and support mean so much to me. This work is dedicated to the scientists/engineers/craftsmen who bridge the gap between theory and practice of computing, devising solutions for previously insurmountable problems and teasing out maximum performance due to a detailed understanding of the underlying hardware. Keep the flame burning!

## Contents

| Co | onten | ts                              | xv |

|----|-------|---------------------------------|----|

| Ι  | Ap    | petizers                        | 1  |

| 1  | Intr  | oduction                        | 3  |

|    | 1.1   | Fundamentals                    | 3  |

|    | 1.2   | The Need for Speed              | 4  |

|    | 1.3   | Image Processing Chain          | 5  |

| 2  | Con   | nputer Architecture             | 7  |

|    | 2.1   | Brief Architecture Descriptions | 7  |

|    | 2.2   | Datasheet Comparison            | 9  |

|    | 2.3   | Our Choice                      | 11 |

|    | 2.4   | Consequences for the Algorithms | 13 |

|    |       | Memory Hierarchy                | 14 |

|    |       | SIMD                            | 17 |

|    |       | Parallelization                 | 18 |

|    | 2.5   | Discussion                      | 21 |

| II | Ma    | in Course                       | 23 |

| 3  | Inp   | ut/Output                       | 25 |

|    | 3.1   | Image Representation            | 25 |

|    | 3.2   | Efficient $I/O$                 | 26 |

|    |       | Synchronous vs. Asynchronous    | 27 |

|    |       |                                 |    |

|   |                  | Block Size                        | 28 |  |  |  |

|---|------------------|-----------------------------------|----|--|--|--|

|   |                  | Implementation Details            | 30 |  |  |  |

|   |                  | Throughput                        | 32 |  |  |  |

|   | 3.3              | File Format                       | 33 |  |  |  |

|   | 3.4              | Performance                       | 34 |  |  |  |

|   | 3.5              | Conclusion                        | 36 |  |  |  |

| 4 | Los              | sless Asymmetric SIMD Compression | 39 |  |  |  |

|   | 4.1              | Introduction and Related Work     | 40 |  |  |  |

|   |                  | Lossless Image Compression        | 40 |  |  |  |

|   |                  | Entropy Coding                    | 41 |  |  |  |

|   |                  | Asymmetric Compression            | 42 |  |  |  |

|   | 4.2              | Fast SIMD Integer Packing         | 43 |  |  |  |

|   | 4.3              | SIMD Sliding-Window Compression   | 45 |  |  |  |

|   | 4.4              | Measurements                      | 49 |  |  |  |

|   |                  | Hardware and Software             | 49 |  |  |  |

|   |                  | Datasets                          | 50 |  |  |  |

|   |                  | Throughput                        | 51 |  |  |  |

|   |                  | Compression Ratio                 | 54 |  |  |  |

|   |                  | Further Experiments               | 56 |  |  |  |

|   | 4.5              | Conclusion                        | 57 |  |  |  |

| 5 | Pan Sharpening 6 |                                   |    |  |  |  |

|   | 5.1              | Introduction and Related Work     | 62 |  |  |  |

|   | 5.2              | Algorithm                         | 64 |  |  |  |

|   | 5.3              | Noise Reduction                   | 65 |  |  |  |

|   | 5.4              | Results                           | 68 |  |  |  |

|   | 5.5              | Quality Metrics                   | 72 |  |  |  |

|   | 5.6              | Performance                       | 76 |  |  |  |

|   | 5.7              | Conclusion                        | 77 |  |  |  |

| 6 | Ima              | ge Segmentation                   | 79 |  |  |  |

|   | 6.1              | Introduction and Related Work     | 79 |  |  |  |

|   | 6.2              | Algorithm                         | 81 |  |  |  |

|   | 6.3              | Results                           | 85 |  |  |  |

|    | 6.4  | Parallel Algorithm            | 88  |

|----|------|-------------------------------|-----|

|    | 6.5  | Region Features               | 91  |

|    | 6.6  | Performance                   | 94  |

|    | 6.7  | Conclusion                    | 96  |

| 7  | Ant  | ialiased Line Rasterization   | 97  |

|    | 7.1  | Introduction and Related Work | 97  |

|    | 7.2  | Algorithm                     | 100 |

|    | 7.3  | Performance                   | 102 |

|    | 7.4  | 'Optimal' Antialiasing        | 104 |

|    | 7.5  | Results                       | 107 |

|    | 7.6  | Conclusion                    | 110 |

| 8  | Syn  | thetic Aperture Radar         | 111 |

|    | 8.1  | Hotspot Operator              | 112 |

|    | 8.2  | Algorithm                     | 113 |

|    | 8.3  | Results                       | 121 |

|    | 8.4  | Performance                   | 122 |

|    | 8.5  | Conclusion                    | 122 |

| 9  | Disc | cussion                       | 125 |

| II | Des  | sserts                        | 129 |

| Α  | Virt | ual-Memory Counting Sort      | 131 |

|    | A.1  | Introduction                  | 131 |

|    | A.2  | Software Write-Combining      | 132 |

|    | A.3  | Virtual-Memory Counting Sort  | 134 |

|    | A.4  | Radix Sort                    | 135 |

|    | A.5  | Performance                   | 138 |

|    | A.6  | Conclusion                    | 142 |

| B  | Imp  | lementation Details           | 145 |

|    | B.1  | Software Engineering          | 145 |

|              | Unaligned Memory Accesses |     |  |  |

|--------------|---------------------------|-----|--|--|

| Bibliography |                           |     |  |  |

| Index        |                           | 189 |  |  |

| Zusa         | ammenfassung              | 197 |  |  |

| Lebe         | enslauf                   | 203 |  |  |

# Part I

# Appetizers

### Chapter 1

### Introduction

This chapter sets the stage by briefly reviewing fundamentals of digital imaging, explaining the need for automation, and introducing our processing chain for image analysis.

### 1.1 Fundamentals

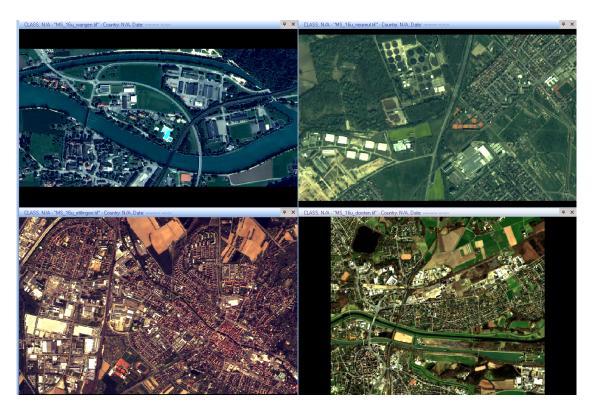

We begin with electro-optical imaging, in which an array of detector elements measure the intensity of certain frequencies of electromagnetic radiation (e.g. visible light) that fall upon their surface. Each detector yields a digital number, referred to as pixels (picture element) because they are typically combined to form a two-dimensional image. When the detectors are sensitive to all frequencies of visible light, the image is described as 'panchromatic'. Placing filters in front of some of the detectors allows them to ascertain the contribution of a certain [spectral] 'band' – a range of frequencies, e.g. what we perceive as blue. Images in which each pixel consists of multiple components (per-band intensity measurements) are termed 'multispectral'. This work is primarily concerned with such images because their color information is particularly useful for automated analysis. However, clouds or rain can obscure objects behind them because visible light is scattered by water molecules or other particles [1].

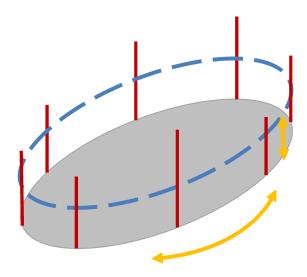

By contrast, synthetic aperture radar (SAR) is nearly unaffected by atmospheric conditions and weather. These systems illuminate scenes with an antenna and record the multiple echoes. Sophisticated post-processing combines these signals into what might have been measured by a large antenna, which allows the generation of an image with relatively high resolution compared to conventional radar. [2] Because electro-optical and radar images have different and perhaps complementary advantages, this thesis also gives attention to the analysis of SAR data.

### **1.2** The Need for Speed

The past decade has seen significant improvements in the capabilities of imaging sensor systems. For example, the recently launched WorldView-2 imaging satellite boasts a ground sample distance  $(GSD)^1$  of only 46 cm [3]. This corresponds to NIIRS (National Image Interpretability Rating Scale) level 6 of 9 [4], indicating the images are suitable for a wide range of interpretation tasks. Large format cameras on airborne platforms operating at much lower altitudes and movement speeds allow even finer resolutions, e.g. 17 mm for the DMC II 250 [5]. Such increases in technical capability are invariably accompanied by greater expectations. For example, an image analyst has expressed a desire to count the number of individual dwellings in an area spanning hundreds of square kilometers. Computer assistance is an absolute necessity for tasks of such magnitude [6]. Human analysts remain indispensable, but their workload could be reduced by screening images for relevant objects. Assuming the detection probability is sufficiently high, other regions need not be examined by the analyst. However, even basic screening approaches for wide-area data are challenging in terms of processing time and memory requirements. The author participated in a study of existing algorithms and modules for image interpretation, including co-registration, screening for objects

<sup>&</sup>lt;sup>1</sup>For convenience, we often refer to this as the '[spatial] resolution' of an image.

such as vehicles, storage tanks and airplanes, and terrain passability analysis. In 2009, we measured throughputs between 0.01 and 3 MPixel/s on a X5365 CPU for nine software modules delivered by various firms. Let us contrast this with the data rates of recent cameras. The DMC II captures a 252 MPixel image every 1.7 s, and a JAS-150s system scans nine 12 000 pixel lines 800 times per second [5]. Real-time processing entails speeding up the existing software by a factor of 100 to 10 000. To at least minimize the additional processing time and thereby enable swift responses in disaster relief [7] and other time-critical applications, this thesis develops new, highly efficient algorithms capable of throughputs in excess of 40 MPixel/s.

### **1.3 Image Processing Chain**

We have designed a general image processing chain suitable for various applications such as screening images for certain types of objects, classifying them, or reporting changes with respect to a previous image. It begins with receiving data from satellites or other sources, performs noise reduction, extracts objects and computes their features. Because the computational cost of existing algorithms is far too high, each link of the chain has been redesigned from the ground up for efficiency. Chapter 2 gives an overview of computer architectures and explains low-level techniques for maximizing performance. Our processing chain is engineered to take advantage of them, and reduces the pixels to a more compact object-based representation. Subsequent analysis applications no longer require expensive per-pixel operations and therefore need not be as concerned with performance.

The following chapters of this thesis are devoted to the individual links of the processing chain:

- **Chapter 3** describes our image representation and framework for transferring to and from block storage devices, with emphasis on avoiding copies and maximizing throughput via asynchronous input/output (I/O).

- **Chapter 4** introduces a novel algorithm for lossless asymmetric compression that accelerates I/O by reducing the amount of data to be transferred. Its decompression is faster than copying the original data in memory.

- **Chapter 5** presents an efficient approach for fusing high resolution panchromatic and lower resolution multispectral satellite images. A fast edge-preserving filter reduces noise. Objective quality metrics report improved color fidelity in comparison to current algorithms.

- **Chapter 6** develops a high-quality algorithm for extracting objects from images. Our graph-based approach enables parallelization without any tiling artifacts. It tends to avoid excessive subdivision and merging of objects despite making only local decisions.

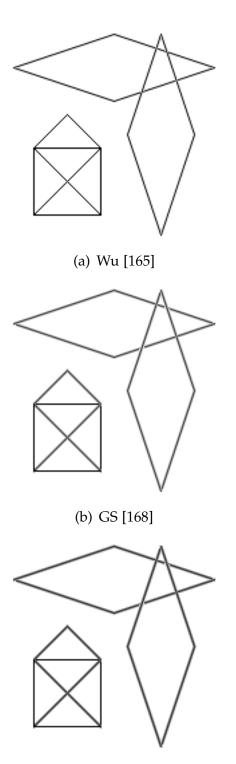

- **Chapter 7** introduces a software line rasterizer, e.g. for separately extracted segment contours, that outperforms the fillrate of a mid-range graphics processor. We derive the optimal cubic polynomial filter for antialiasing, which respondents in a subjective survey preferred over existing approaches.

- **Chapter 8** presents a highly efficient algorithm for finding pointlike objects in infrared and radar images.

- **Chapter 9** concludes this work by discussing the resulting performance gains and proposing avenues for future work.

## **Chapter 2**

## **Computer Architecture**

As always, high performance comes at a price, including paying careful attention to the computer architecture. This chapter sets forth several options, explains our choice and discusses the implications for our algorithms.

### 2.1 Brief Architecture Descriptions

We first introduce and briefly describe several possible computer architectures.

- **Digital Signal Processors** (DSP) are tailored towards low-latency signal processing applications. Their specialized architectures often include hardware acceleration for loops, multiply-add sequences and data copying. Single Instructions that apply the same operation to Multiple 'lanes' of Data (SIMD) increase the computational throughput. The deliberate omission of complicated hardware for out-of-order execution and virtual memory management significantly reduces power and cooling requirements, making DSPs suitable for embedded systems. [8]

- **Graphics Processing Units** (GPU) have evolved from graphics accelerator chips towards general-purpose processing. Their

design emphasizes aggregate throughput, utilizing hundreds of SIMD lanes and over a thousand independent threads of execution to hide memory latency [9]. Multiple interfaces to high-performance GDDR5 memory [10] provide increased bandwidth. The recent Fermi architecture includes several major advances, including full-fledged and fast floating point arithmetic, caches, and error-correction codes for memory. Its unified 64-bit address space and improved support for higher-level languages continues the trend of convergence towards general-purpose architectures. [11]

- **Field Programmable Gate Arrays** (FPGA) encompass blocks of programmable logic (typically lookup tables) and configurable interconnects. Their inherent parallelism enables major speedups in comparison to serial processing. Because 'instructions' are implicit in the programmed structure, they need not be fetched from memory nor decoded [12]. Although area and power requirements are an order of magnitude higher than application-specific integrated circuits, FPGAs shorten development time and offer the intriguing possibility of runtime adaptive reconfiguration [13].

- **Central Processing Units** (CPU) are understood to be generalpurpose microprocessors. Decades of effort have gone into improving their serial performance by means of caches, prediction and super-scalar pipelining with out-of-order execution [14][p. 1314]. These facilities enable a flexible and simple programming model. However, physical limitations motivated a paradigm shift towards parallelism in the form of multiple processors/cores and SIMD [15]. Recently, special hardware support has been added for applications such as video encoding, cryptography and checksums [16][p. 13], thus blurring the distinction between CPUs and accelerators.

### 2.2 Datasheet Comparison

To gain further insight into the strengths of each architecture, we compare several of their key characteristics. Table 2.1 lists the total cache and memory size available to each architecture. The CPU

Table 2.1: Total size of the architectures' caches (or block RAM in

the case of FPGAs) and external memory.

Arch.

Model

Cache [MiB]

Mem. [GiB]

| Arch. | Model              | Cache [MiB] | Mem. [GiB] |

|-------|--------------------|-------------|------------|

| DSP   | TI TMS320C6678     | 6.50        | 8          |

| GPU   | NVidia GF100 Fermi | 1.75        | 6          |

| FPGA  | Xilinx Virtex-7    | 10.63       | (?)        |

| CPU   | Intel Sandy Bridge | 9.25        | 192        |

|       |                    |             |            |

devotes a significant proportion of its transistors to the cache [17]. Although the DSP lacks a third level cache, its other levels match the CPU's capacity [18]. With the advent of 16 GiB DDR3 modules, commodity workstations can accommodate 192 GiB of memory [19]. The limit for a custom FPGA memory interface is unknown, but both other architectures are restricted to a few gigabytes [18, 20]. This is of particular concern for image segmentation, which requires large amounts of 'random-access' memory (c.f. Chapter 6).

Table 2.2 provides a rough estimate of attainable performance by listing the advertised<sup>1</sup> floating-point operations per second (FLOPS). The GPU and especially FPGA boast higher values than the other processors due to their massive parallelism [22, 23]. However, despite multiple memory interfaces, their memory bandwidth lags far behind the raw computational power [20, 23]. Amdahl suggested a rule of thumb for balanced computer designs: "1 byte of memory and 1 byte per second of I/O are required for each instruction per second" [11]. Interestingly, the CPU is much closer to meeting these guidelines than the other architectures [24, 25].

<sup>&</sup>lt;sup>1</sup>The CPU's entry is an actual measurement on an overclocked system [21].

Table 2.2: Key performance indicators for each architecture. '[SIMD] Lanes' are understood to be CUDA cores (DSP slices) in the case of GPUs (FPGAs).

| Arch. | Lanes | Mem. BW [GB/s] | GFLOPS |

|-------|-------|----------------|--------|

| DSP   | 128   | 12             | 160    |

| GPU   | 512   | 144            | 1 500  |

| FPGA  | 5280  | 233            | 6737   |

| CPU   | 64    | 29             | 130    |

That aside, FLOPS are an incomplete characterization of performance. We also wish to provide a measure that is less dependent on the clock rate. It is difficult to compare the irregular execution units of a DSP to the plentiful but severely restricted 'CUDA cores' on a GPU, or simple 'DSP slices' (a multiplier combined with an adder/subtracter and multiplexer) in FPGAs to complex, high performance CPU cores. However, we can consider 'lanes', the aggregate number of values that can be computed per clock. There is about a tenfold increase from CPU to GPU to FPGA [9, 23, 26]. This yields the important insight that GPUs and especially FPGAs require large amounts of parallelism to realize their full potential.

Despite our focus on performance, the suitability of an architecture depends heavily on other factors, some of which are listed in Table 2.3. For example, the estimated cost of a Virtex-7 FPGA [27]

| Arch. | Process [nm] | Power [W] | Transistors $\times 10^{6}$ | Price [€] |

|-------|--------------|-----------|-----------------------------|-----------|

| DSP   | 40           | 10        | (?)                         | 110       |

| GPU   | 40           | 225       | 3 000                       | 3 500     |

| FPGA  | 28           | 40        | (?)                         | 19000     |

| CPU   | 32           | 95        | 995                         | 220       |

Table 2.3: Non-performance-related characteristics that also affect an architecture's real-world suitability.

is about 100 times the price of a DSP or CPU [26]. A more costeffective means of matching the FPGA's FLOPS may involve an array of DSP boards or a CPU cluster. The high-end Quadro 6000 GPU is also comparatively expensive, presumably due in part to its relatively large GDDR5 memory capacity.

Power requirements are another important consideration. The DSP is quite efficient in this regard [28], making it suitable for embedded systems. Conversely, the GPU draws twice the CPU's power [20, 26] and uses three times as many transistors [9, 17]. A fair comparison between GPU and CPU should therefore involve at least a dual-CPU system. The FPGA has been optimized for low power and is extremely efficient in terms of FLOPS/Watt [29]. However, let us note that it is manufactured on a smaller process node [30]. This advantage may soon be reversed, because CPUs with 22 nm physical gate lengths are expected to be available by 2012 [31].

#### 2.3 Our Choice

Having seen the relative strengths and weaknesses of each architecture, we now present a perhaps controversial case for a CPU-based approach. Our envisioned large-scale image analysis pipeline requires the development of new algorithms and approaches for coping with the flood of data. As famously remarked by Werner Freiherr von Braun: "Basic research is what I am doing when I don't know what I am doing" [32]. This uncertainty calls for exploration, i.e. the development of prototypes. CPUs' flexibility and ease of programming greatly simplify this task. An initial software implementation that ignores performance can often be constructed and tested more rapidly than an FPGA, and probably developed at lesser cost than GPU or DSP software.

Aside from productivity concerns, recent studies have also dampened the enthusiasm for GPU acceleration. A survey of 14

data-parallel kernels found that a GPU is only about 2.5 times as tast when both implementations are optimized [33]. However, even this advantage is negated by the above argument that a fair comparison (in terms of price, transistors and power dissipation) requires at least two CPUs. The conventional wisdom that GPUs provide a large speedup seems to be a self-fulfilling prophecy, because it leads to an increased awareness of GPU optimization techniques. Indeed, a Google Scholar search in June 2011 for 'GPGPU' (general purpose GPU) returned 437 works from that year, whereas only 82 contained the words 'optimized, SSE, SIMD'. Heeding guidelines for CPUs may be dismissed as 'tuning' that only slightly decreases constant factors. However, the optimization techniques are fundamentally related in that they both call for explicit vectorization [34]. A study taking this into account found that GPUs are only as fast as one or two CPUs in traditional highperformance computing applications [35].

Why does the actual performance of GPUs lag so far behind their theoretical power? A recent simulation found that a representative set of non-graphics applications only used 45% of the GPU's computational resources on average, with a worst case of 5% for one bioinformatics algorithm. Three main causes were identified. The first is waiting for data from memory. GPUs attempt to hide this latency by performing other work in the meantime, but algorithms do not always provide enough parallelism. The second is similar: computations that depend on previous operations must wait for them to have been completed. The final pitfall concerns conditionally executed logic. If the threads in a GPU-defined group ('warp') differ in terms of the path taken, they are executed sequentially! [36] These observations confirm the well-known fact that peak FLOPS are an inadequate predictor of performance.

However, there is a more important conclusion to be drawn from these studies. Because similar performance was reported for equally optimized CPU and GPU implementations, the benefits and costs of optimizing an algorithm for a particular architecture should carefully be considered. We believe CPUs hold much untapped potential in this regard. Let us now return to the initial productivity argument. It is relatively easy to transform and optimize software implementations for CPUs. Verifying correctness with built-in logic checks and comparisons with the previous iteration improves reliability. Measuring the actual improvement at each step enables informed decisions when exploring the design space. This cycle of design, analysis, implementation and measurements is the defining characteristic of the emerging discipline of algorithm engineering [37]. It facilitates novel algorithmic transformations that might not arise during straightforward, hardware-oriented development efforts. The following chapters describe multiple cases in which the resulting software surpasses the stated performance of a GPU or FPGA implementation.

Although it is often possible to achieve additional speedups by means of distributed-memory algorithms designed for clusters (multiple independent computers connected by a network), we are somewhat constrained by power, cooling and space considerations. Some applications (e.g. in mobile ground control stations) only permit the use of a single computer. We therefore target commercially available off-the-shelf workstations with dual CPUs. Unless otherwise noted, the test platform is a Dell T5500 with two X5690 CPUs (3.6 GHz) and 48 GiB DDR3 memory running 64-bit Windows 7. With the stated exceptions, our software is compiled with ICC 12.0.1.096 /ox /ob2 /oi /ot /GA /GR- /GS- /Gy /EHsc /MD /Qipo /QxSSE4.1 /Qopenmp /Qstd=c++0x. The resulting executables also run on AMD processors that support the requisite SSE3 instruction set.

### 2.4 Consequences for the Algorithms

What implications does our choice of architecture bring about? Because we are not dealing with compute clusters, our algorithms can be designed for the simpler shared memory model instead of having to communicate by passing messages. The prevalent Intel architecture also provides a favorable, i.e. strict, memory consistency model in which processors see memory writes occur in a total global order [38]. Apart from these simplifications, there are three major peculiarities of CPUs to be taken under consideration: a memory hierarchy, SIMD extensions, and multiple cores/processors. These are discussed in the following subsections.

### **Memory Hierarchy**

Current semiconductor technology allows certain levels of integration and signal propagation times. This entails a trade-off between storage size and access latency. In an attempt to bridge the growing gap between computational power and memory bandwidth, CPUs provide a hierarchy of storage including cache and main memory. Caches are small and fast, whereas memory provides plentiful but slow storage. Let us examine their properties in turn.

#### Cache

Caches are storage areas managed by the CPU that enable faster access to frequently-used data. For concreteness, current microarchitectures provide 32 KiB L1D (first level data) caches with an aggregate thoughput of 650 GB/s and 256 KiB L2D capable of 435 GB/s [39]. A comparison with the 29 GB/s memory bandwidth [24] underscores the importance of making good use of the cache. We therefore strive to minimize 'misses', i.e. cases where the desired data is not stored within any 'line' (a fixed-size portion of the cache). To that effect, let us address each of the potential causes: compulsory, capacity, and conflict [40].

**Compulsory.** Even an infinite-sized cache would incur 'compulsory' misses when data is first accessed. Their latency can be hidden by 'prefetching', i.e. accessing memory before it is actually needed. However, this is not always feasible or worthwhile; a more practical workaround is to downsize the data. This may involve the use of smaller types (e.g. single precision instead of double) or compression. For example, small flags or indices can be embedded into the lower bits of pointers, because their values are generally a multiple of the processor's word size. A series of large, slowly varying values can be delta-encoded, storing the differences between individual values. The addition of occasional full-sized 'keyframes' enables efficient random access by accumulating deltas since the previous value. In the case of 64-bit values with 32 8bit deltas between keyframes, the data is reduced by a factor of six, and the average access is still faster than a cache miss. Even more spectacular savings are enabled by probabilistic counting, which approximates sums  $\leq n$  while using only  $\log \log n$  bits. It has been shown that incrementing the truncated logarithm  $|\log n|$ with probability inversely proportional to *n* yields an unbiased estimator for *n* [41].

**Capacity.** A finite cache size and imperfect replacement strategy give rise to so-called capacity misses when lines are evicted in favor of newer data. The previously mentioned compression improves the utilization of a particular cache. However, algorithms must also exhibit locality of reference to derive any benefit. Temporal locality (i.e. re-using the same memory locations within a short timespan) increases the likelihood of data still residing in the cache. Similarly, spatial locality (accessing nearby locations) decreases the number of cache lines to populate, thus reducing evictions of previous data. Caches are designed to exploit both of these properties. However, their behavior is suboptimal for sequential write-only access patterns. The memory to be written is first loaded into a cache line, which 'pollutes' the cache by replacing

its previous contents with data that will not be accessed again. Loading from memory is also unnecessary if the entire cache line will be overwritten. To avoid these problems, algorithms should implement write-only transfers via special instructions that bypass the cache and write directly to memory.

**Conflict.** Cache lines are associated with a memory location by means of 'tags' that indicate the address. Because it is difficult to examine each line's tag when checking whether data is present in the cache, CPUs typically provide a fixed mapping of addresses to 'sets' of lines. Their cardinality (the cache 'associativity', e.g. 8) therefore determines the number of memory locations that can map to the same set without evicting a line. Examples of access patterns that exceed this limit include iterating over power-of-two sized matrix rows and writing data to multiple destinations with the same alignment. These problems can be mitigated by offsetting the various addresses by random multiples of the cache line size.

#### Memory

To a lesser extent, memory also exhibits some of the same characteristics as the cache. It is faster to access nearby locations in the same row of memory cells that is currently 'open' [42][pp. 8–9]. Non-uniform memory access (NUMA) systems are also characterized by variable latency. For example, the integration of memory controllers into the CPU has resulted in faster accesses to 'local' memory managed by the current processor. Software implementations should be aware of this issue and explicitly allocate their memory from 'nearby resources', i.e. the current NUMA proximity domain. It is interesting to observe that the memory hierarchy encourages local data accesses despite the trend towards ever larger memory sizes. Reducing data sizes – even with non-trivial (de)compression overhead – generally also speeds up a program!

#### SIMD

'Superscalar' CPUs enable the concurrent execution of multiple instructions per clock cycle. However, this comes at the cost of complicated control circuitry and only allows a limited degree of parallelism. Many architectures have therefore added support for SIMD extensions such as 3DNow!, AltiVec, MAX, MDMX, MMX, MVI, SSE, VIS [43] and more recently, AVX, LRBni and NEON. The instructions concurrently apply operations to all elements (typically 4 or 8) of a short vector, thus significantly increasing peak FLOPS. Algorithms should therefore be designed to utilize these capabilities. However, automatic vectorization of existing software is a challenge [44] and compilers cannot always transform code into a form suitable for the often incomplete and irregular instruction sets. A library solution for Java only resulted in a 34% speedup due to significant overhead and additional memory traffic [45]. We therefore utilize 'intrinsics', special functions known to the major C++ compilers that typically result in the generation of single SIMD instructions. Although avoiding the inconvenience of assembly language and manual register allocation, the syntax is somewhat verbose, as exemplified by multiplication using Intel's Streaming SIMD Extensions (SSE) instruction set: \_\_m128 product = \_mm\_mul\_ps(input, multiplier). Where possible, we use compiler-provided short vector classes with overloaded functions, which affords more convenient notation: F32vec4 product = multiplier \* multiplicand. This also allows generating both vector and scalar (single-operand) variants of the same code by means of C++ templates, which is helpful for testing and benchmarking. Besides differing syntax, SIMD raises challenges concerning dependencies and alignment.

**Dependencies.** Algorithms must be structured so that operations can proceed in parallel. Although SIMD cannot significantly decrease the latency of tasks such as polynomial evaluation that

involve dependencies on previous or intermediate values, it does increase throughput by computing several results in parallel. Even seemingly sequential tasks such as updating a sum can be done in parallel using prefix sums.

**Alignment.** To simplify the hardware, instruction sets may require operands to be 'aligned', i.e. residing at addresses that are a multiple of the vector size. Later revisions of the SSE instruction set provide separate instructions for loading aligned and possibly unaligned operands. Their relative cost and possible workarounds are discussed in Section B.2. If possible, algorithms should be designed to load and store aligned vectors.

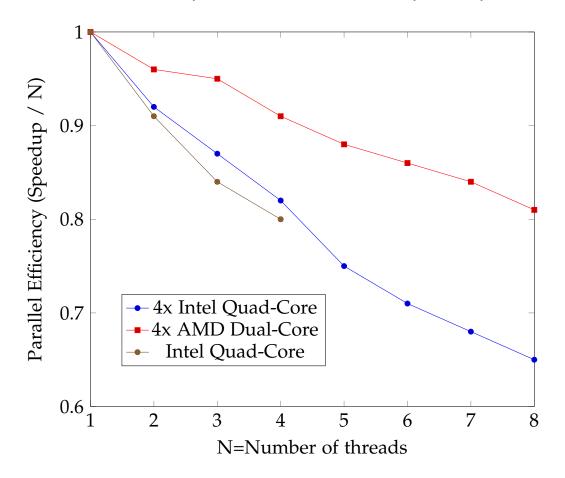

#### Parallelization

It is well-known that single-core improvements such as speculation, caches and superscalar pipelines have reached the point of diminishing returns. CPU architects therefore began allocating available transistors towards multiple cores and logical processors. [15] This has also been motivated by power and cooling, the importance of which was highlighted when the Pentium 4 processor exceeded a hot plate's thermal power density by a factor of ten [46]. Because dynamic power is proportional to frequency  $\times$  voltage<sup>2</sup>, a common argument proposes running several processors at a fraction of the frequency, thus also allowing lower voltages [47]. This has the potential for near-cubic reductions in 'power' and may even increase performance. However, both of these assumptions are flawed. First, dynamic power consumption excludes various kinds of leakage in semiconductors. Such 'static power' already accounted for 40% of the total dissipation in a 90 nm process and increases with smaller gate lengths [48]. Subthreshold leakage also grows exponentially with a decrease in threshold voltage [49]. Second, algorithms may require communication or synchronization between processors, thus eroding any performance gains. Amdahl's well-known argument also limits the parallel speedup to the reciprocal of the serial portion of an algorithm.

Looking beyond power, which affects cooling requirements, energy (i.e. power  $\times$  time) is also a critical factor. One study has found that lower frequencies *increase* the total energy consumption because other system components are used for a longer period of time [50]. These arguments notwithstanding, our algorithms should make full use of the available hardware, including multiple cores and logical processors. Unfortunately, parallelization also brings with it two challenges: correctness and infrastructure.

**Correctness.** It is difficult to guarantee the correctness of parallel programs running on multiple processors. Algorithms must first split up the data into (preferably entirely independent) subtasks and dispatch them to the processors. If the tasks depend on a certain order of execution, the software must take care of synchronization, typically via mutual exclusion or lock-free algorithms. However, the former is prone to deadlocks (multiple processes waiting on each other), whereas the latter requires awareness of the exact memory ordering guarantees made by the compiler and CPU. To avoid most of these difficulties, we strive to process portions of the inputs independently and later accumulate the individual results.

**Infrastructure.** Traditional software development tools often provide only limited support for parallelization. For example, the 2003 revision of the C++ standard (ISO/IEC 14882) makes no mention of multiple threads, memory consistency nor ordering guarantees. Efforts have been undertaken to develop library solutions, including parallel variants of C++ standard library functions [51] and 'Threading Building Blocks' suitable for common parallel idioms [52]. Although useful, these do not provide the full degree of control necessary to maximize performance. For example, a

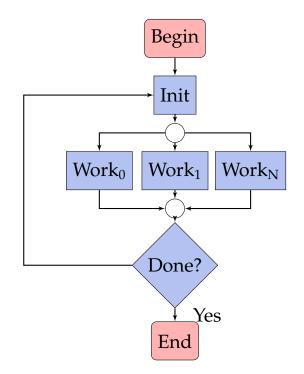

Figure 2.1: Fork-join parallelization model.

parallelization scheme should take into account the NUMA and cache topology, e.g. when mapping threads to processors. We provide infrastructure for this purpose that is shared between all parallel algorithms. It is based on the fork-join paradigm (Figure 2.1), which is characterized by one or more 'phases' consisting of initialization, parallel work and sequential reduction. This allows synchronization and safe handling of dependencies between parts of an algorithm while hiding implementation details. In fact, the algorithms can be expressed as if they ran serially, as shown by Figure 2.2. Each worker thread executes Assist, which receives an indication of the phase number and the thread's ID. When all are finished, Supervise is called on a single thread and decides whether to continue. Finally, a reduction is performed by successive calls to Accumulate; this example records the latest time reported by any thread. We use OpenMP parallel regions to launch ('fork') the worker threads, which has the advantage of avoiding platform-specific implementations. Threads can also be combined

```

void Assist(size_t phase, size_t id) {

if(phase == 2) LocalLSD(id);

else LocalMSD(id); }

static Status Supervise(size_t phase) {

if(phase == 2) return DONE;

else return ComputeGlobalRanks(); }

void Accumulate(const Group& rhs) {

endTime = std::max(endTime, rhs.endTime); }

```

Figure 2.2: Simplified example of parallel C++ code using the fork-join model.

into 'groups', which can work together on the same subset of data. This improves resource utilization when the group's processors share caches or NUMA memory.

## 2.5 Discussion

We have chosen to develop image processing algorithms for generalpurpose CPUs because they are more flexible and require less development effort than specialized architectures. Recent advances in CPU designs have also provided the potential for significant computational power. In contrast to the 'free lunch' previously offered by increasing clock rates [15], developers must take action and account for SIMD parallelization and the memory hierarchy. It may even be difficult to adapt existing designs towards these new requirements. Instead, they are best considered during the design phase.

At this point, three concerns might be raised. Would the additional effort exceed the design and validation cost incurred on other architectures such as FPGAs? We argue that successively refined

software has valuable side effects. Prototyping avoids wasting effort on optimizing algorithms that might turn out to be unsuitable, and allows verifying the correctness of each transformation along the way. We do not believe the rather complex Hotspot algorithm described in Chapter 8 would have been forthcoming – or even feasible – without such an approach. A second potential interjection is that these techniques can only improve performance by a constant factor. That is true, but no other improvements are possible for algorithms that are already at the lower bound of their complexity. The previous sections have also hinted at the magnitude of the potential speedups: 4 to 16 for vectorization, 4 to 12 for parallelization, and up to 22 from the cache. In our opinion, such factors are highly relevant. A final concern relates to obsolescence: will these considerations still apply to future microarchitectures? The past being our best predictor of the future, let us examine the evolution of CPUs over the last 10 years. Cache line sizes are an important parameter for cache-aware algorithms, and have remained constant at 64 bytes [53]. The SSE2 SIMD instruction set is still useful, and code written with intrinsics would even benefit from new capabilities in the AVX instruction set after a recompile. Efforts are also underway to develop auto-tuning mechanisms for adapting algorithms to the target hardware [54].

Maximizing performance currently requires an awareness of the system internals, which typically entails manual intervention by the developer. However, it is the thesis of this work that such efforts may be richly rewarded. In the subsequent chapters, note the multiple cases in which our algorithms – running on commodity CPUs – outperform specialized hardware.

# Part II Main Course

# Chapter 3

# Input/Output

The first and last links of the image processing chain involve loading the pixels into memory and storing them to disk. This chapter describes our representation of images and how to efficiently transfer them to and from block storage devices such as hard disk drives (HDD).

## 3.1 Image Representation

Images are typically two-dimensional arrays of pixels. In accordance with the C++ standard [55, 8.3.4], we mandate a 'row-major' layout in which the row indices vary faster than column indices. In other words, the pixels constituting a row are stored before those of the next row. An additional constraint arises from SIMD instruction sets. They often require or at least benefit from natural alignment, i.e. ensuring addresses are integral multiples of the operand size. Because we wish to allow parallel processing of images, with each processor responsible for an arbitrary interval of the image rows, the starting address of each row should be aligned to the vector size.

It is convenient and efficient to represent the image as a contiguous virtual address range together with a 'step', i.e. the offset to the next row. Row n is reached by adding  $n \times$  step to the starting address. This is expected to be at least as fast as a table lookup [56] and certainly more economical in terms of cache usage. The Intel Performance Primitives (IPP) library [57] also uses such a representation.

Because image processing algorithms often require access to neighboring pixels or each band at a certain pixel position, we choose a band-interleaved-by-pixel layout in which the first pixel's components are followed by those of the next pixel in the row (Figure 3.1). This representation corresponds to some simple file

(1,y)R |(1,y)G |(1,y)B  $|(\cdots)|(w,y)$ R |(w,y)G |(w,y)B

Figure 3.1: R/G/B component ordering for the *w* pixels (x, y) in row *y*.

formats such as PM (c.f. Section 3.3), which allows reading an entire image into memory and storing it to disk without any reshuffling. We are therefore only concerned with sequential, not random, I/O. However, the row-major layout has poor locality for some access patterns because vertically adjacent pixels are stored far apart. This is particularly relevant for compression, which benefits from spatial locality. A common workaround involves splitting the image into small square 'tiles', each of which is stored in row-major order. Locality is improved because most vertically adjacent pixels are now only spaced one *tile* row apart. GPU-based rendering of large images also requires splitting the image into tiles due to limits on the maximum texture size. We therefore use a tiled representation for the final result image that is to be compressed and displayed in a viewer (c.f. Section 3.3).

## 3.2 Efficient I/O

In our applications, storage devices are accessed through the file system. However, modern operating systems provide multiple I/O interfaces. The chief distinction is whether the application can proceed while a transfer is in progress (asynchronous), as opposed to waiting inside the operating system kernel until I/O is complete (synchronous). Which of these is better suited for our needs, and what techniques can further improve performance? These questions are addressed in the following sections.

#### Synchronous vs. Asynchronous

Let us measure the rate at which data can be written to disk ('throughput') with the synchronous and asynchronous I/O methods provided by the ATTO Disk Benchmark 2.46. The test platform consists of a W3550 CPU running Windows 7 with the pagefile disabled and a WD6400AAKS HDD. Due to various resource limits in the application, operating system, drivers and hardware, I/O requests will eventually be split into blocks. Table 3.1 shows increasing throughputs for larger application-requested block sizes due to amortization of overhead. There are further, nearly negligible improvements for even larger blocks. However, 1 MiB is

| size [KiB] | write MB/s | async MB/s |

|------------|------------|------------|

| 4          | 24.9       | 45.2       |

| 8          | 42.8       | 75.6       |

| 16         | 68.5       | 100.9      |

| 32         | 91.5       | 105.2      |

| 64         | 103.3      | 107.9      |

| 128        | 105.7      | 108.9      |

| 256        | 104.9      | 108.5      |

| 512        | 105.5      | 108.2      |

| 1024       | 106.1      | 107.4      |

Table 3.1: Conventional and asynchronous write throughput measured with the ATTO benchmark on a WD6400AAKS HDD for various block sizes.

a reasonable cutoff point (c.f. Section 3.2). As found in previous work [58], asynchronous writes are faster to converge to the disk's maximum throughput. This is because the disk controller can immediately begin the next transfer after the previous one completes without requiring the application to first transition into kernel mode. Asynchronous I/O generally involves higher CPU overhead [59][p. 381], especially on Windows, which only provides Fast I/O driver entry points for synchronous I/O [60]. However, it has the major advantage of allowing the application to perform work (e.g. compression) while waiting on previous transfers. We therefore prefer it to the more commonly used synchronous access method.

#### **Block Size**

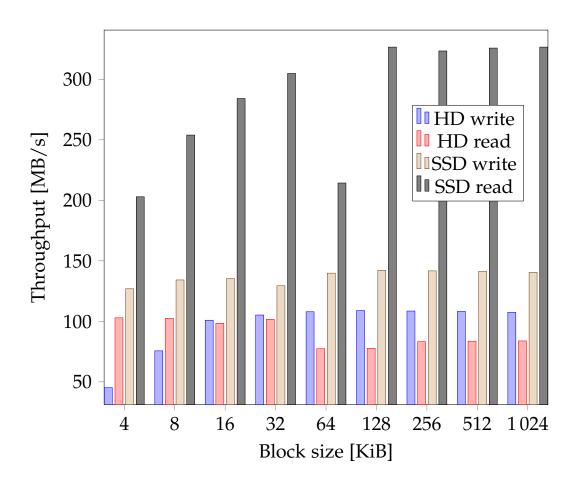

We wish to maximize disk throughput while overlapping computation with I/O. It is straightforward to interleave these two tasks by splitting transfers into blocks. Computations can be carried out for a completed block while waiting for subsequent I/Os. The block size is bounded by the following considerations: Transfers are carried out via Direct Memory Access hardware, which requires contiguous physical memory. Drivers must therefore represent the application-provided memory buffer as a list of physical pages (scatter-gather list). These are stored in nonpaged pool – a small memory area set aside by Windows – and are therefore restricted to 255 entries [61]. The resulting limit is 1 MiB given a 4 KiB page size. Although it is desirable to amortize system call overhead over large requests, those exceeding this limit incur additional overhead due to splitting. Conversely, there must be a minimum block size because the number of pending I/O requests may be finite. Windows also requires transfer sizes to be sector-aligned, and the Advanced Format industry initiative [62] has introduced drives with 4 KiB sectors, so we consider that to be the minimum. Table 3.2 shows the read and write throughputs measured by ATTO

on the previously mentioned HDD and a 128 GB Crucial C300 Solid-State Disk (SSD) over this range of block sizes. Although

Table 3.2: Asynchronous read and write throughput [MB/s] measured with ATTO on a WD6400AAKS HDD and C300 SSD for various block sizes.

| size [KiB] | HD write | HD read | SSD write | SSD read |

|------------|----------|---------|-----------|----------|

| 4          | 45.2     | 102.9   | 126.9     | 202.9    |

| 8          | 75.6     | 102.4   | 134.2     | 253.9    |

| 16         | 100.9    | 98.4    | 135.3     | 284.1    |

| 32         | 105.2    | 101.7   | 129.4     | 304.8    |

| 64         | 107.9    | 77.4    | 139.8     | 214.3    |

| 128        | 108.9    | 77.7    | 142.1     | 326.6    |

| 256        | 108.5    | 83.2    | 141.7     | 323.4    |

| 512        | 108.2    | 83.6    | 141.3     | 325.8    |

| 1024       | 107.4    | 83.8    | 140.5     | 326.6    |

SSD read throughput tends to increase with larger block sizes, the bar plot representation of these numbers in Figure 3.2 makes apparent a sharp drop at 64 KiB. The cause is unclear; perhaps transfers are being split up due to scatter-gather list limitations or other inefficiencies within the driver or controller. However, write throughputs remain nearly constant. Interestingly, HDD writes can outperform reads due to caching by the controller. We choose 128 KiB blocks as a reasonable compromise that provides good throughput without requiring large buffers that exceed the L2 cache size. Note that this discussion presumes sequential I/O, which is justified in Section 3.1. Random I/O may require larger block sizes to amortize the cost of HDD 'seeks'<sup>1</sup>.

<sup>&</sup>lt;sup>1</sup>Repositioning the read/write head in preparation for reading or writing from another location.

Figure 3.2: Bar-plot representation of HDD and SSD read/write throughputs.

#### **Implementation Details**

Let us now briefly examine details of our I/O implementation. To ensure source code portability, we adhere to the POSIX asynchronous I/O interface, which is codified in the 2004 edition of IEEE Standard 1003.1 [63]. These functions are not included with Windows, but the Intel Compiler's libicaio library [64] provides replacements. The implementation in version 12.0 (Parallel Studio 2011) appears to be based on synchronous I/O in helper threads<sup>2</sup>. This approach does not maximize disk throughput, al-

<sup>&</sup>lt;sup>2</sup>We observed thread suspend/resume operations and found that the functions fail when applied to files opened for Windows asynchronous I/O.

though it does avoid the restrictions mentioned below. We instead implement the POSIX functions in terms of Windows asynchronous I/O. This entails specifying FILE\_FLAG\_OVERLAPPED and FILE\_FLAG\_NO\_BUFFERING when opening the file. Windows then requires addresses, sizes and offsets to be a multiple of the volume sector size. Our low-level functions pass on these constraints to their callers, which can handle them without penalty. Several lesser-known tricks [65] have also been applied. Contiguous storage for OVERLAPPED structures, the Windows equivalent of POSIX aiocb (asynchronous I/O control blocks), allows pinning them in the kernel address space by means of the SetFileIoOverlappedRange API. This means I/O completion can be handled by any thread, which avoids an asynchronous procedure call and the associated context switch and locking in the kernel. SetFileCompletionNotificationModes is used to avoid unnecessary completion notifications. Finally, disk space is preallocated via SetEndOfFile and SetFileValidData. Without the latter, all writes that extend a file are forced to complete synchronously, which prevents overlapping I/O with computation (e.g. checksums) [66]. To avoid exposing previous disk contents, we deny read sharing when opening files.

Having gone to great lengths to ensure an efficient implementation of the POSIX aio interface, the application logic is comparatively simple. A ring buffer holds aiocb control blocks. Block I/Os are issued up to a default maximum queue depth of 32. We use aio\_suspend to wait until the next I/O is complete and then invoke a user-specified callback (specified as a C++ function object template to avoid call overhead). The loop terminates when all block I/Os have completed. The Windows alignment requirements (similar considerations apply when using the equivalent Linux/BSD O\_DIRECT functionality) are satisfied by the memory allocator, which also expands block buffers to a multiple of the sector size. After writing, we trim any excess padding at the end of the file by calling truncate.

#### Throughput

To determine the effectiveness of our implementation techniques, we compare the resulting throughput to the output of the ATTO and CrystalDisk 3.0.1 x64 benchmarks. Note that ATTO only allows a queue depth of 10, which may limit performance. CrystalDisk is run in sequential mode with 500 MB blocks, because it cannot match the 256 MB used by both other programs. Our 'waio' (POSIX aio for Windows) implementation and ATTO are configured for the 128 KiB block size established in Section 3.2. To ensure this value is not specific to a particular system configuration, we use different hardware for these tests: dual X5690 CPUs running Windows 7 x64 with a Hitachi HDS721010CLA HDD and Samsung PM810 SSD. Note that ATTO and waio write zero-valued data, whereas CrystalDisk defaults to random-valued data. Disk controllers based on SandForce chipsets improve read and write performance for repetitive data by means of compression [67]. However, to the best of our knowledge, the C300's 88SS9174-BJP2 and PM810's S3C29MAX controllers do not include such an optimization.

As seen in Table 3.3, our waio outperforms both benchmarks in all respects. Despite the straightforward nature of sequential I/O

| Table 3.3: Read and write throughputs [MB/s] reported by our |

|--------------------------------------------------------------|

| implementation and the ATTO and CrystalDisk benchmarks on a  |

| PM810 SSD and HDS721010CLA HDD.                              |

| Benchmark   | HD write | HD read | SSD write | SSD read |

|-------------|----------|---------|-----------|----------|

| CrystalDisk | 145.00   | 146.00  | 233.70    | 241.20   |

| ATTO        | 144.89   | 143.34  | 250.58    | 255.98   |

| waio        | 151.35   | 146.07  | 252.75    | 256.73   |

and previous efforts to maximize write throughput, we have improved it by 4%. Measurements of ATTO's memory usage indicate block buffers are being reused, whereas our implementation reads the entire file into memory, which is more expensive. However, waio's reads still turn out to be faster.

## 3.3 File Format

With the in-memory image representation and I/O method established, we may now decide upon the format of the files to read/write. A multitude of image file formats have been devised. However, our applications and large amounts of data impose exacting requirements, including minimal conversion overhead, support for relevant pixel formats, compression, tiling, 'image pyramids'<sup>3</sup> and flexible 'metadata'<sup>4</sup>. Let us briefly review a selection of existing formats and evaluate them in light of these requirements:

- **PM** is a simplistic format that only specifies one or more planes of band-interleaved pixels without any additional features [68]. Application-specific metadata could be stored in the freeform comment field, but we would prefer a standardized approach.

- **OpenEXR** is a newer format for High Dynamic Range (HDR) images that unfortunately lacks support for 8 or 16-bit integers [69].

- **HFA/IGE** are the feature-rich internal file formats of the ERDAS IMAGINE framework for geospatial image processing [70]. However, the HFA format is quite complex and somewhat inefficient (c.f. Section 3.4).

- **NITF** is a standardized interchange format that is even more complex than HFA, but limited to 10 GB and lacking support for embedded image pyramids. Note that NSIF (NATO Secondary Image Format) corresponds to NITF with a different version field in the header. [71]

<sup>&</sup>lt;sup>3</sup>A series of successively spatially subsampled versions of the image, also known as mipmaps. Subsequent to the 'base' (the original image), each 'level' typically halves the resolution. A viewer can reduce the overhead of 'minifying' many image pixels to few screen pixels by interpolating between the two levels whose resolutions are closest to the desired zoom scale.

<sup>&</sup>lt;sup>4</sup>Literally "data about data", here understood to be additional information about the image such as its geographic location.

**BigTIFF** expands the well-known TIFF format to 64-bit offsets [72], but inherits its major 'disadvantage' of allowing non-native byte orders and non-tiled pixel formats, which would require expensive conversion when loading.

Unfortunately, each of these formats is either prone to inefficiency, or lacks some of the required features. We have devised a flexible new format designed with knowledge of low-level details such as SIMD vector and disk sector alignment requirements. It provides support for tiled pyramids ordered according to a novel space-filling curve, the new lossless compression scheme described in Chapter 4, and user-defined metadata. Details are given in Appendix B.3. However, we recognize the value of interoperability and wish to support existing applications and viewers, particularly ERDAS IMAGINE. We therefore provide fast methods for writing NITF and IGE files. The key enabling factor of their high performance is assembling the file in memory and writing it to disk in large chunks. Avoiding unnecessary copying of the data and additional allocations (e.g. for headers) also saves time.

## 3.4 Performance

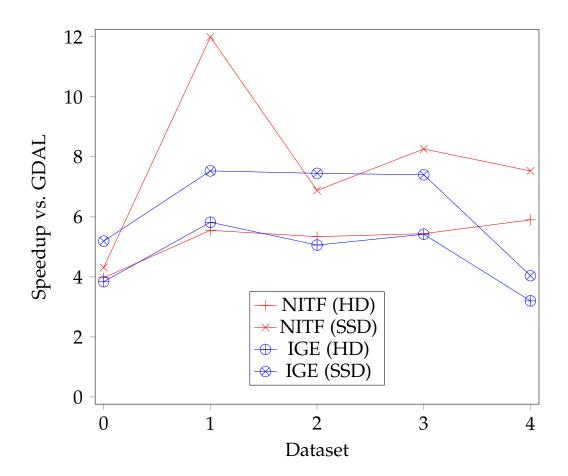

Let us now study the real-world performance attained by the methods described in this chapter. We compare the total time required to write NITF and IGE images with our software and the ubiquitous Geospatial Data Abstraction Library (GDAL), version 1.7.3.

To avoid favoring a particular tile size, we generate images with random dimensions in the interval  $[2^i, 2^{i+1})$  for  $10 \le i < 15$ . The resulting values are given in Table 3.4. Table 3.5 compares the relative costs of our NITF and IGE codecs vs. GDAL. The current balance of CPU performance and disk throughput means writing NITF images takes about 5–25% longer because pixels must be

| Dataset | Width   | Height |

|---------|---------|--------|

| 0       | 1 1 4 0 | 1917   |

| 1       | 3 0 3 9 | 3752   |

| 2       | 8 0 8 4 | 7 505  |

| 3       | 8921    | 10251  |

| 4       | 24 608  | 19359  |

Table 3.4: Randomly chosen image dimensions [pixels] for the write throughput test.

Table 3.5: Normalized cost of the formats – elapsed times for NITF and IGE are divided by the I/O time, GDAL measurements are relative to our implementation.

| Drive | Dataset | NITF | IGE  | GDAL NITF | GDAL HFA |

|-------|---------|------|------|-----------|----------|

| HD    | 0       | 1.62 | 2.61 | 3.97      | 3.84     |

| HD    | 1       | 1.12 | 1.36 | 5.55      | 5.82     |

| HD    | 2       | 1.05 | 1.47 | 5.34      | 5.06     |

| HD    | 3       | 1.07 | 1.41 | 5.44      | 5.42     |

| HD    | 4       | 1.12 | 1.49 | 5.90      | 3.20     |

| SSD   | 0       | 1.42 | 2.50 | 4.31      | 5.19     |

| SSD   | 1       | 1.15 | 1.38 | 11.99     | 7.53     |

| SSD   | 2       | 1.24 | 1.45 | 6.88      | 7.45     |

| SSD   | 3       | 1.22 | 1.55 | 8.26      | 7.40     |

| SSD   | 4       | 1.20 | 1.35 | 7.53      | 4.04     |

reshuffled into a tiled layout<sup>5</sup>. The relative cost of this computation is higher on the smallest dataset because less time is required for I/O (possibly due to caching in the disk controller). Our IGE writer performs much more work: computing and storing an image pyramid as well as statistics (standard deviation, minimum,

<sup>&</sup>lt;sup>5</sup>Our normative reference for NITF is NATO Standardization Agreement 4545, which requires NSIF images with a dimension exceeding 8 192 pixels to be split into tiles. We use a fixed tile dimension of 256.

maximum, mean, median, mode and histogram of each band's values). This only requires 35-50% more time than I/O due to our efficient vectorized and parallelized implementation. However, the overhead appears particularly large on the smallest image because the cost of writing the extra metadata file is not amortized. Our NITF implementation is roughly five times as fast as GDAL's when writing to the HDD, and up to 12 times as fast on the SSD (whose higher throughput increases the relative cost of GDAL's less efficient pixel copying). Our IGE writer is 'only' about 5 times as fast as GDAL on the HDD and 7 times as fast on the SSD because GDAL does not compute image statistics. For reasons unknown, GDAL's throughput increases on the largest (3.8 GB) image. The width is a multiple of 32, but a block size of 64 is used. Figure 3.3 shows the speedups vs. GDAL. Although mere constant factors, we believe a 3 to 12-fold improvement to be of major practical relevance.

## 3.5 Conclusion

This chapter has described a technique for asynchronous I/O that avoids various inefficiencies at the hardware/operating system level, thereby outperforming existing benchmarks by 4%. We build upon this foundation with efficient routines for writing common image file formats. The result is a 3 to 12-fold speedup vs. the well-established GDAL library. Finally, the aligned image layout discussed herein serves to avoid penalties when accessing individual rows via SIMD instructions, thus enabling the high performance of the subsequent modules.

Figure 3.3: Speedup of our writers vs. GDAL.

# Chapter 4

# Lossless Asymmetric SIMD Compression

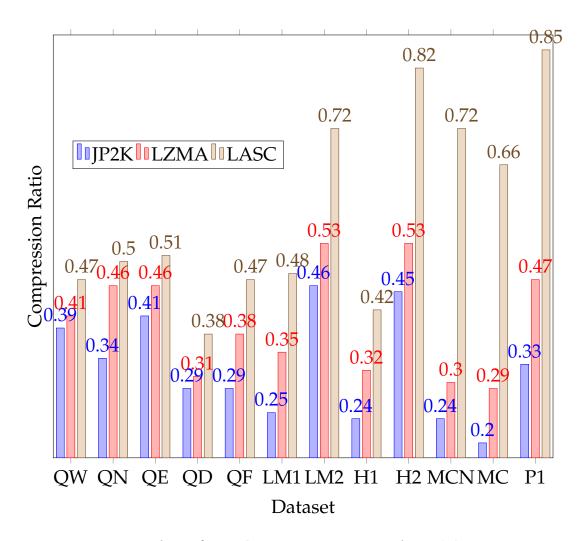

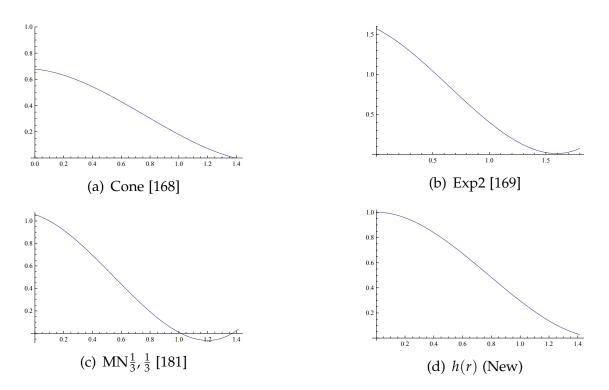

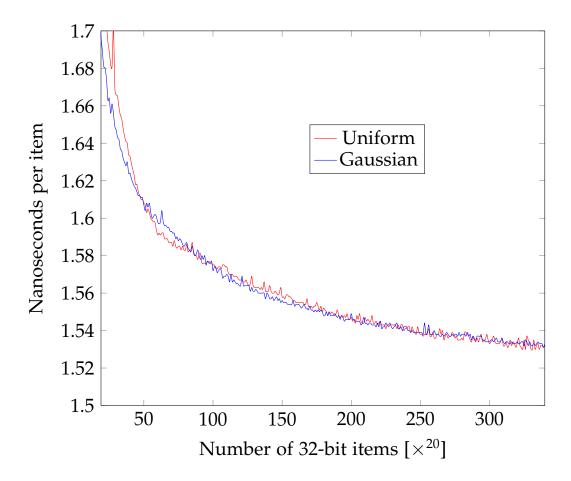

This chapter introduces a new lossless asymmetric SIMD codec (LASC) designed for extremely efficient decompression of large satellite images. A throughput in excess of 3 GB/s allows decompression to proceed in parallel with asynchronous transfers from fast block devices such as disk arrays. This is made possible by a simple and fast SIMD entropy coder that removes leading null bits. Our main contribution is a new approach for vectorized prediction and encoding. Unlike previous approaches that treat the entropy coder as a black box, we account for its properties in the design of the predictor. The resulting compressed stream is 1.2 to 1.5 times as large as JPEG-2000, but can be decompressed 100 times as quickly – even faster than copying uncompressed data in memory. Applications include streaming decompression for out of core visualization. To the best of our knowledge, this is the first entirely vectorized algorithm for lossless compression.

This chapter has been published in the "Software: Practice and Experience" journal [73] and is reproduced here with minor formatting and wording clarifications.

## 4.1 Introduction and Related Work

Displaying images that are too large to fit within main memory necessitates streaming, that is, loading sections of the data from a slower storage medium when they are needed. For interactive performance, it is important to minimize the latency of these requests. Asynchronous I/O allows computation to proceed while waiting on the storage medium. However, panning a  $2560 \times 1600$  pixel viewport such that 10% of the 16-bit, four component pixels are updated every 16 ms requires a sustained throughput of 196 MB/s, which exceeds the capability of current magnetic media [74]. Such data rates are enabled by drive arrays and top of the line solid-state disks, but these are not always available. Instead, a common remedy involves compression of the data. In contrast to the entertainment sector, some medical and automated image analysis applications cannot tolerate any loss of information.

#### **Lossless Image Compression**

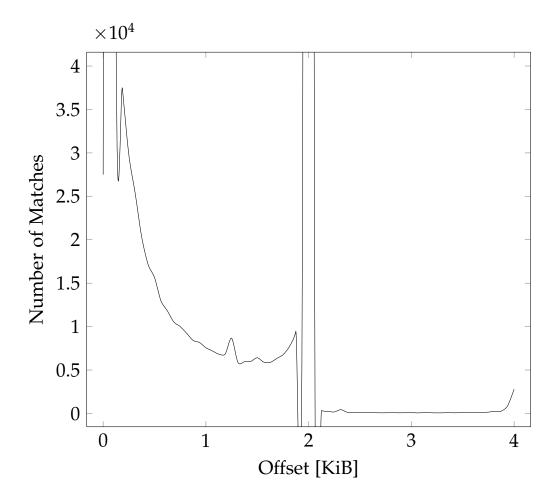

By 1993, a general framework for lossless image compression had been established that is still useful today. The intensity of the next pixel to encode is predicted using a context of previously seen pixels. The resulting residuals, that is, prediction errors, are relayed to a statistical coder that may act upon knowledge of their distribution [75]. These components are all interdependent; we briefly discuss them in increasing order of complexity. In most cases, the simple and intuitive raster scan order is used. Surprisingly, the order induced by a Hilbert space-filling curve can *increase* the residuals' entropy [76], and the 'rain scan order' only yields a 4% improvement [77]. The circular dependency between prediction and coding is often resolved by assuming that prediction errors follow a Laplacian distribution [78], for which a variant of Golomb coding is optimal [79]. With the entropy coder thus established, most efforts have been directed at prediction – using larger contexts [80], combining various predictors [77] or minimizing the squared or absolute prediction error [81]. However, this does not necessarily result in optimal compressed sizes [82], and conventional entropy coders are too slow for our application. A highly-optimized implementation of Rice's independently discovered subset of Golomb codes only decodes 200 MIntegers/s [83]. Prior work on reducing branches in a Huffman decoder reached 90.95 MPixel/s (including a fast DCT) [84]. However, this algorithm is not well-suited for acceleration via GPU, which only manages 570–750 MB/s [85]. Note that Huffman codes are equivalent to a restricted case of arithmetic coding [86], so the latter cannot be expected to be faster. Dictionary-based approaches are neither significantly better in terms of performance [87], nor are they ideally suited for this task because residuals are not drawn from a small alphabet.

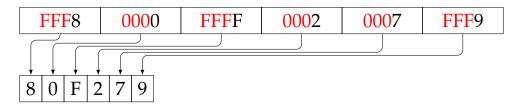

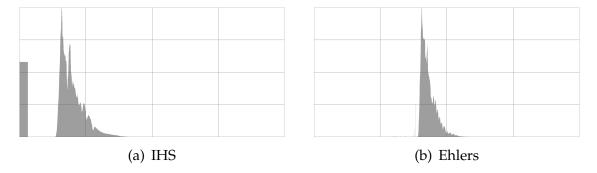

#### **Entropy Coding**

Having ruled out conventional entropy coders, we must consider alternatives. Variable-length codes are generally inefficient to decode because of their bit-level accesses, and even table-based approaches are not much faster [88]. We therefore turn to fixed-length codes. One interesting approach involves packets of compressed fields and a selector indicating their length [89]. Recently, a similar scheme using 64-bit words with support for values spanning multiple packets was also proposed [90]. These are faster than variable-length codes and improve upon the compression of byte-aligned codes, but suffer from several drawbacks. Extracting the fields still requires bit arithmetic. The varying number of output values per packet complicates single instruction multiple data (SIMD) writes. A single large residual increases the size of all fields in the packet. The latter issue can be addressed by storing 'exceptions', that is, a list of values to overwrite after decompression and their locations [91]. However, this is unlikely to be useful for 16-bit values