ROBERT VAUPEL

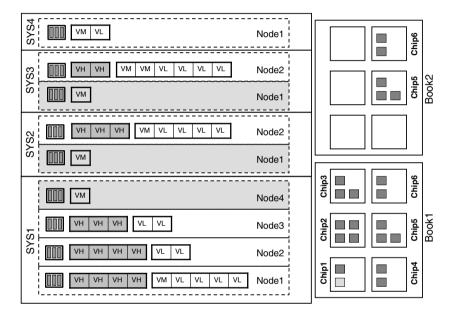

# HIGH AVAILABILITY AND SCALABILITY\_

OF MAINFRAME ENVIRONMENTS

Scientific Publishing

#### **Robert Vaupel**

High Availability and Scalability of Mainframe Environments using System z and z/OS as example

# High Availability and Scalability of Mainframe Environments using System z and z/OS as example

by Robert Vaupel

#### Impressum

Karlsruher Institut für Technologie (KIT) KIT Scientific Publishing Straße am Forum 2 D-76131 Karlsruhe www.ksp.kit.edu

KIT – Universität des Landes Baden-Württemberg und nationales Forschungszentrum in der Helmholtz-Gemeinschaft

Diese Veröffentlichung ist im Internet unter folgender Creative Commons-Lizenz publiziert: http://creativecommons.org/licenses/by-nc-nd/3.0/de/

KIT Scientific Publishing 2013 Print on Demand

ISBN 978-3-7315-0022-3

## **Contents**

| 1. | Intro | oductio  | n                                     | 1  |

|----|-------|----------|---------------------------------------|----|

|    | 1.1.  | Motiva   | tion                                  | 1  |

|    | 1.2.  | High A   | vailability                           | 3  |

|    | 1.3.  |          | lity                                  | 5  |

| 2. | z/Ar  | chitect  | ure                                   | 9  |

|    | 2.1.  | A Little | e History                             | 9  |

|    | 2.2.  |          |                                       | 12 |

|    | 2.3.  |          |                                       | 13 |

|    | 2.4.  | System   | zEC12 Components                      | 14 |

|    | 2.5.  |          |                                       | 16 |

|    |       | 2.5.1.   | Memory                                | 17 |

|    |       | 2.5.2.   |                                       | 18 |

|    |       | 2.5.3.   | Processor Characterization            | 18 |

|    | 2.6.  |          |                                       | 19 |

|    |       | 2.6.1.   |                                       | 20 |

|    |       | 2.6.2.   |                                       | 21 |

|    |       | 2.6.3.   |                                       | 22 |

|    | 2.7.  | System   | z Software and Firmware Layers        | 25 |

|    | 2.8.  |          | · · · · · · · · · · · · · · · · · · · | 27 |

|    |       | 2.8.1.   |                                       | 27 |

|    |       | 2.8.2.   |                                       | 30 |

|    |       | 2.8.3.   | =                                     | 31 |

|    |       | 2.8.4.   |                                       | 33 |

|    |       | 2.8.5.   | Decimal Arithmetic                    | 35 |

|    |       | 2.8.6.   | Floating Point Arithmetic             | 37 |

|    |       | 2.8.7.   |                                       | 40 |

|    |       | 2.8.8.   |                                       | 42 |

|    |       | 2.8.9.   |                                       | 43 |

|    |       | 2.8.10.  |                                       | 46 |

|    |       |          |                                       | 47 |

|    |       |          |                                       | 49 |

ii Contents

|    | 2 8 1       | 3. Out-Of-Order Execution                  | 49 |

|----|-------------|--------------------------------------------|----|

|    |             | 4. System z196 Microprocessor Core         | 51 |

|    |             | 5. System z196 Instruction Handling        | 54 |

|    |             | 6. System z196 Instruction Optimization    | 54 |

|    |             | 7. System z196 Microprocessor Summary      | 57 |

|    |             | rupts                                      | 57 |

|    | 2.9.1       | -                                          | 59 |

|    |             | ng Facilities                              | 60 |

|    |             | 1. Time-of-Day Clock                       | 60 |

|    | 2.10.       | 2. Clock Comparator                        | 62 |

|    | 2.10.2      | 3. CPU Timer                               | 62 |

|    |             | ge Addressing                              | 63 |

|    |             | 1. Address Types                           | 63 |

|    | 2.11.       | 2. Dynamic Address Translation             | 64 |

|    |             | 3. Large Page Support                      | 66 |

|    |             | 4. Storage Protection                      | 66 |

|    |             | 5. Prefixing                               | 67 |

|    |             | iprocessing                                | 68 |

|    | 2.12.       | 1. Atomic Instructions                     | 69 |

|    |             | and Output                                 | 70 |

|    |             | 1. z196 I/O Infrastructure                 | 71 |

|    |             | 2. I/O System Overview                     | 72 |

|    |             | 3. I/O Drawer                              | 74 |

|    |             | 4. I/O Operation                           | 74 |

|    |             | 5. Logical Channel Subsystem               | 76 |

|    |             | 6. I/O Configuration                       | 78 |

|    | 2.14. Logic | cal Partitioning                           | 78 |

|    | 2.14.       | 1. z/VM                                    | 80 |

|    |             | 2. Start Interpretive Execution            | 81 |

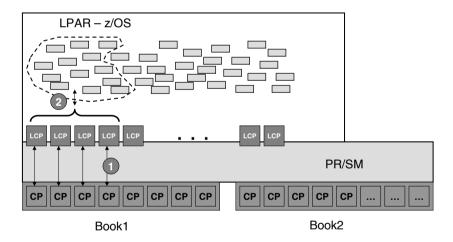

|    |             | 3. Logical Processor Management            | 82 |

|    |             | 4. Storage of a Logical Partition          | 84 |

|    |             | 5. Storage of a Virtual Machine under z/VM | 85 |

|    |             | mary                                       | 86 |

| 3. | z/OS        |                                            | 87 |

|    |             | Structure                                  | 87 |

|    |             | ess Spaces                                 | 89 |

|    | 3.2.1.      | _                                          | 91 |

|    | 3.2.2.      | · · · · · · · · · · · · · · · · · · ·      | 93 |

|    | 3.2.3.      | Storage Protection                         | 94 |

Contents iii

|    |       | 3.2.4.   | Address Space Creation           | 94  |

|----|-------|----------|----------------------------------|-----|

|    | 3.3.  | Progran  | m Execution                      | 96  |

|    |       | 3.3.1.   | Reentrant Programming            | 97  |

|    |       | 3.3.2.   | Program Recovery                 | 99  |

|    |       | 3.3.3.   | Recovery Processing              | 101 |

|    | 3.4.  | Program  | m Data Exchange                  | 102 |

|    |       | 3.4.1.   | Data Exchange via Common Storage | 103 |

|    |       | 3.4.2.   | Data Exchange via Cross Memory   | 104 |

|    |       | 3.4.3.   | Access Registers                 | 108 |

|    | 3.5.  | Storage  | Management                       | 108 |

|    |       | 3.5.1.   | z/OS Storage Managers            | 109 |

|    |       | 3.5.2.   | Managing Storage                 | 110 |

|    | 3.6.  | z/OS D   | ata Sets                         | 114 |

|    |       | 3.6.1.   | Sequential Data Sets             | 116 |

|    |       | 3.6.2.   | Partitioned Data Sets            | 117 |

|    |       | 3.6.3.   | Allocating a Data Set            | 118 |

|    |       | 3.6.4.   | Virtual Storage Access Method    | 118 |

|    |       | 3.6.5.   | Data Set Organization            | 119 |

|    | 3.7.  | Starting | g z/OS                           | 119 |

|    | 3.8.  |          | ry System                        | 123 |

|    | 3.9.  | Time S   | haring Option                    | 124 |

|    | 3.10. | Unix S   | ystem Services                   | 126 |

|    | 3.11. | Summa    | ıry                              | 127 |

| 4. | Disp  | atching  | a                                | 129 |

|    | 4.1.  |          | ching Requirements               | 129 |

|    | 4.2.  |          | ispatching                       | 132 |

|    |       | 4.2.1.   | CPU and Storage Management       | 133 |

|    |       | 4.2.2.   | Dispatcher Queue                 | 134 |

|    |       | 4.2.3.   | Dispatching Work                 | 135 |

|    |       | 4.2.4.   | Preemption and Time Slicing      | 137 |

|    |       | 4.2.5.   | Interrupt Processing             | 138 |

|    |       | 4.2.6.   | I/O Enablement                   | 139 |

|    |       | 4.2.7.   | CPU Report Example               | 141 |

|    | 4.3.  | PR/SM    | Dispatching                      | 143 |

|    |       | 4.3.1.   | Dispatching Logical Processors   | 144 |

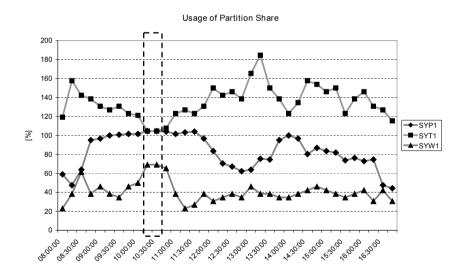

|    |       | 4.3.2.   | LPAR Report Example              | 147 |

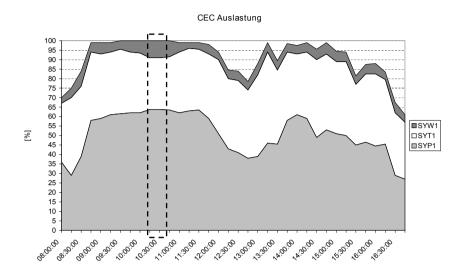

|    |       | 4.3.3.   | CEC Utilization Example          | 149 |

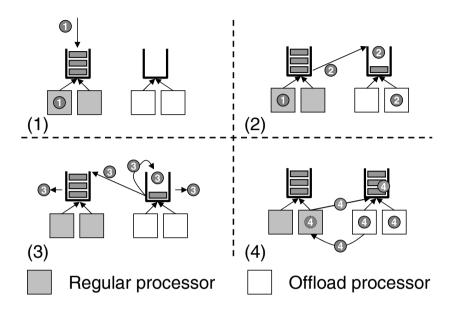

|    | 4.4.  | Offload  | Processors                       | 151 |

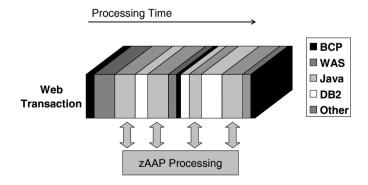

|    |       | 4.4.1.   | Using zIIPs and zAAPs            |     |

iv Contents

|    |      | 4.4.2.  | Processor Pools                                     | 154 |

|----|------|---------|-----------------------------------------------------|-----|

|    |      | 4.4.3.  | LPAR Report Example including Offload Processors .  | 155 |

|    | 4.5. | Examp   | le on how z/OS and PR/SM Dispatcher work together . | 156 |

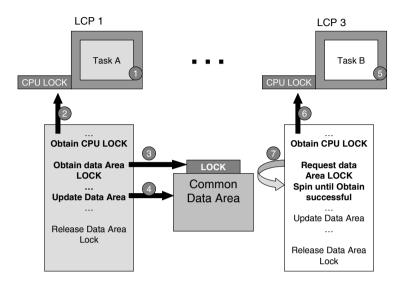

|    |      | 4.5.1.  | z/OS Serialization                                  | 156 |

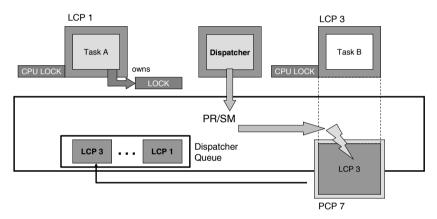

|    |      | 4.5.2.  | z/OS Spin Lock Processing                           | 158 |

|    | 4.6. | Limitat | tions of Dispatching                                | 160 |

|    |      | 4.6.1.  | Large System Effects                                | 161 |

|    | 4.7. | Hiperd  | ispatch                                             | 163 |

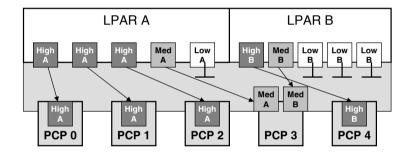

|    |      | 4.7.1.  | Vertical CPU Management                             | 164 |

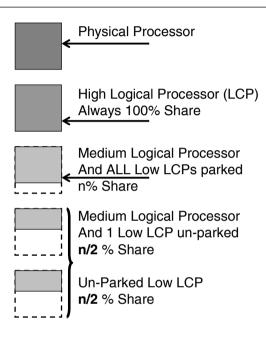

|    |      | 4.7.2.  | Processor Shares                                    | 165 |

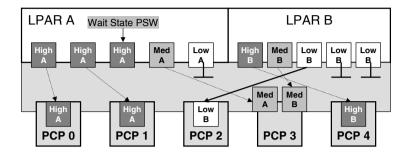

|    |      | 4.7.3.  | Example for Unparking Low Processors                | 167 |

|    |      | 4.7.4.  | Hiperdispatch in z/OS                               | 170 |

|    |      | 4.7.5.  | Affinity Nodes                                      | 171 |

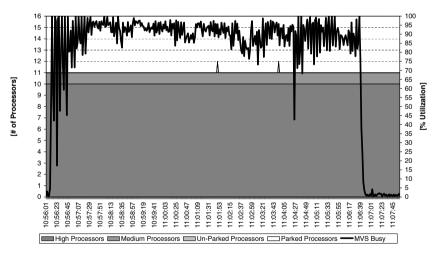

|    |      | 4.7.6.  | Assessment for Parking and Unparking Low Processors | 173 |

|    |      | 4.7.7.  | Balancing Work                                      | 174 |

|    |      | 4.7.8.  | Helper Processing                                   | 175 |

|    |      | 4.7.9.  | System Work                                         | 177 |

|    | 4.8. | Hiperd  | ispatch Analysis                                    | 178 |

|    |      | 4.8.1.  | Processor Utilization                               | 178 |

|    |      | 4.8.2.  | Cycles per Instruction                              | 179 |

|    |      | 4.8.3.  | Hiperdispatch on z196 and zEC12                     | 181 |

|    | 4.9. | Summa   | ary                                                 | 182 |

| 5. | Wor  | kload N | Management                                          | 185 |

|    | 5.1. | Worklo  | oad Management Concepts                             | 185 |

|    | 5.2. | Why W   | Vorkload Management                                 | 186 |

|    | 5.3. | Worklo  | oad Management on z/OS                              | 186 |

|    | 5.4. | z/OS W  | Vorkload Management Basics                          | 187 |

|    |      | 5.4.1.  | Work Classification                                 | 187 |

|    |      | 5.4.2.  | Service Class Goals                                 | 190 |

|    |      | 5.4.3.  | Response Time Goals                                 | 191 |

|    |      | 5.4.4.  | Execution Velocity Goals                            | 193 |

|    |      | 5.4.5.  | Managing Work in z/OS                               | 195 |

|    |      | 5.4.6.  | WLM Transaction Management                          | 196 |

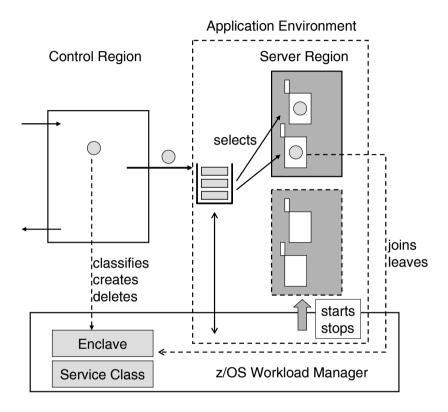

|    |      | 5.4.7.  | Enclaves                                            | 197 |

|    |      | 5.4.8.  | Managing CICS and IMS Transactions                  | 199 |

|    |      | 5.4.9.  | Service Definition                                  | 201 |

|    |      |         | Service Unit                                        | 202 |

|    |      | 5.4.11. | Goal Achievement                                    | 203 |

<u>Contents</u> v

|    | 5.5. | z/OS W   | Vorkload Manager Algorithms                        | 204 |

|----|------|----------|----------------------------------------------------|-----|

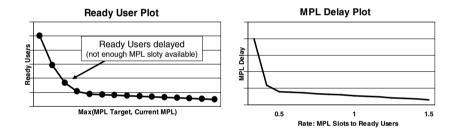

|    |      | 5.5.1.   | Data Sampling                                      | 205 |

|    |      | 5.5.2.   | Histories                                          | 207 |

|    |      | 5.5.3.   | Data Plots                                         | 209 |

|    |      | 5.5.4.   | Policy Adjustment                                  | 210 |

|    |      | 5.5.5.   | Policy Adjustment Example: Fix MPL Delay           |     |

|    |      | 5.5.6.   | Projecting a Change for Accessing a Resource       | 215 |

|    |      | 5.5.7.   | Receiver Value Assessment                          | 216 |

|    |      | 5.5.8.   | Net Value Assessment                               | 217 |

|    |      | 5.5.9.   | Policy Adjustment Example: Fix CPU Delay           | 218 |

|    |      | 5.5.10.  | Policy Adjustment Example: Time-line for Changes . | 221 |

|    |      | 5.5.11.  | Test Scenario versus Real Environment              | 224 |

|    |      | 5.5.12.  | Resource Adjustment                                | 226 |

|    |      | 5.5.13.  | Timed Algorithms                                   | 228 |

|    |      |          | Management Approach and Restrictions               |     |

|    |      | 5.5.15.  | Resource Groups                                    | 229 |

|    |      | 5.5.16.  | CPU Critical                                       | 231 |

|    |      | 5.5.17.  | Storage Critical                                   | 232 |

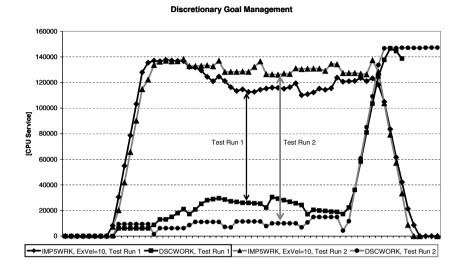

|    |      | 5.5.18.  | Discretionary Goal Management                      | 233 |

|    | 5.6. | z/OS W   | Vorkload Manager Advanced Functions                |     |

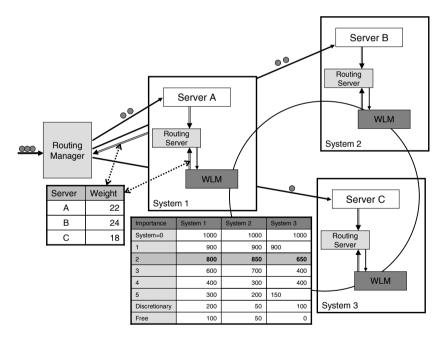

|    |      | 5.6.1.   | Routing Support                                    |     |

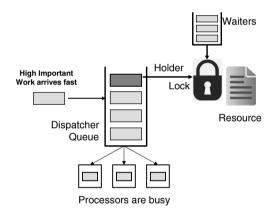

|    |      | 5.6.2.   | Contention Management                              |     |

|    |      | 5.6.3.   | Scalable Server Environments                       |     |

|    |      | 5.6.4.   | WLM Batch Management                               |     |

|    |      | 5.6.5.   | Workload Scheduling Support                        | 243 |

|    |      | 5.6.6.   | Adjusting Resources in a CEC                       | 244 |

|    |      | 5.6.7.   | Support for Software Licensing                     |     |

|    |      | 5.6.8.   | Subsystem Participation                            | 249 |

|    | 5.7. | Summa    | ary                                                | 250 |

| 6. | Para | ıllel Sy | splex                                              | 253 |

|    | 6.1. |          | vailability Aspects                                |     |

|    | 6.2. | Cluster  | Technologies                                       |     |

|    |      | 6.2.1.   | Shared-Nothing Cluster                             |     |

|    |      | 6.2.2.   | Shared-Disk Cluster                                |     |

|    |      | 6.2.3.   | Shared-Disk and Shared-Memory Cluster              |     |

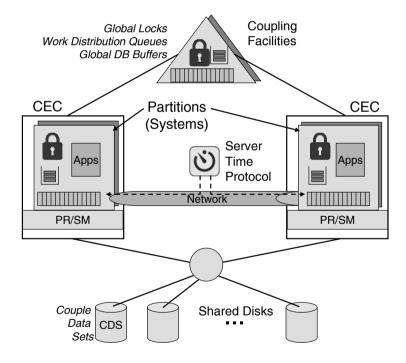

|    | 6.3. |          | l Sysplex Overview                                 |     |

|    | 6.4. |          | x Couple Data Sets                                 |     |

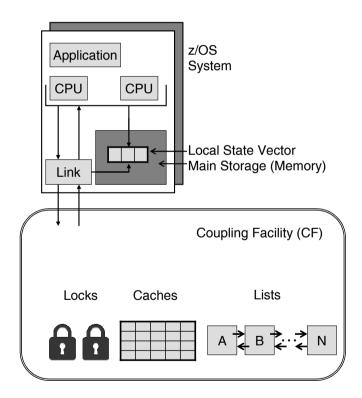

|    | 6.5. | Couplin  | ng Facility                                        | 261 |

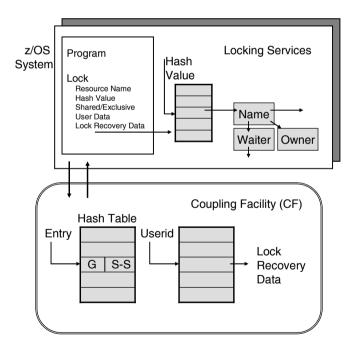

|    |      | 6.5.1.   | Lock Structure                                     | 261 |

vi Contents

| В. | Trad  | lemarks                                                     | 311        |

|----|-------|-------------------------------------------------------------|------------|

| A. | Glos  | ssary                                                       | 297        |

| 7. | Sum   | nmary                                                       | 295        |

|    |       | Summary of Business Resilience Concepts                     | 291<br>292 |

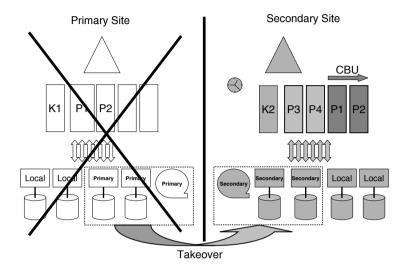

|    |       | 6.15.4. Multi Site Failure Scenario                         | 290        |

|    |       | 6.15.3. Multi Site Workload (Active/Active)                 | 288        |

|    |       | 6.15.2. Single Site Failure Scenario                        | 287        |

|    |       | 6.15.1. Single Site Workload (Active/Standby)               | 287        |

|    |       | Disaster Recovery Scenarios                                 | 287        |

|    |       | Peer-to-Peer Virtual tape Support                           | 286        |

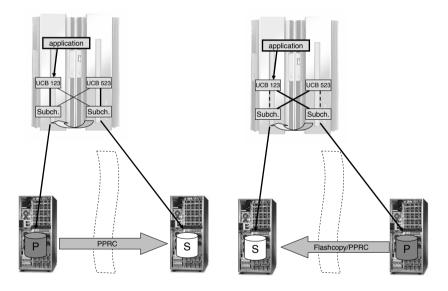

|    | 6.13. | Extended Remote Copy                                        | 285        |

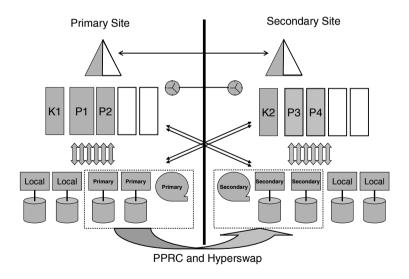

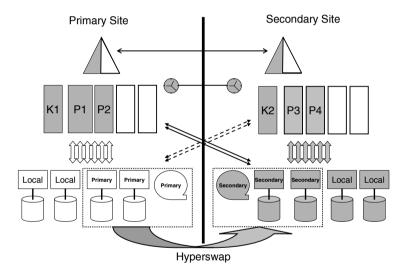

|    |       | 6.12.2. Hyperswap                                           | 283        |

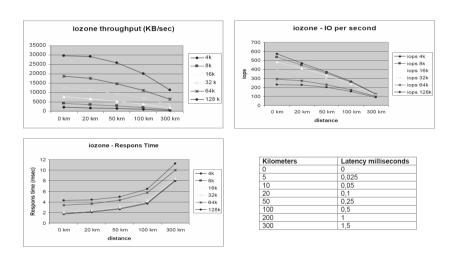

|    | 0.12. | 6.12.1. Latency of Synchronous Copy                         | 282        |

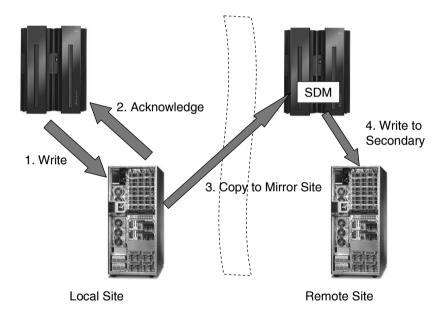

|    | 6.12  | 6.11.2. Data Mirror Techniques                              | 280<br>281 |

|    |       | 6.11.1. Capacity Backup                                     | 279        |

|    | 6.11. | Disaster Recovery Prevention                                | 279        |

|    |       | 6.10.1. Continuous Operations                               | 277        |

|    | 6.10. | Business resilience                                         | 276        |

|    | 6.9.  |                                                             | 275        |

|    | 6.8.  | Using IMS as an Example how a Parallel Sysplex is exploited | 271        |

|    | 6.7.  | Parallel Sysplex Configuration                              | 270        |

|    |       | 6.6.2. Coupling Facility Duplexing                          | 267        |

|    |       | 6.6.1. XCF Groups                                           | 267        |

|    | 6.6.  |                                                             | 266        |

|    |       | 6.5.3. Cache Structure                                      | 264        |

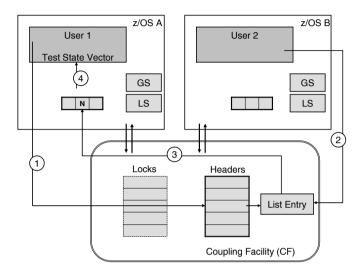

|    |       | 6.5.2. List Structure                                       | 263        |

## **List of Figures**

| 1.1.  | Definition of Availability                           |

|-------|------------------------------------------------------|

| 1.2.  | Capacity Range of a High-End System z196             |

| 2.1.  | History of System z Architecture and z/OS            |

| 2.2.  | System z: CMOS Mainframe Heritage                    |

| 2.3.  | System zEC12 Frames and Blade Extensions             |

| 2.4.  | Under the Hood of System zEC12                       |

| 2.5.  | System zEC12 Cache Level Structure                   |

| 2.6.  | Transparent CPU Sparing                              |

| 2.7.  | CPU Error Detection                                  |

| 2.8.  | z196 Memory within an MCM                            |

| 2.9.  | System z Software and Firmware Layers                |

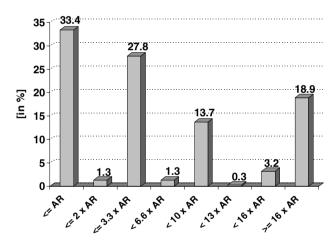

| 2.10. | Percent of Executed Transactions                     |

| 2.11. | Transaction Execution Time                           |

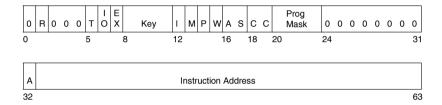

| 2.12. | Program Status Word in 31-bit Addressing Modes       |

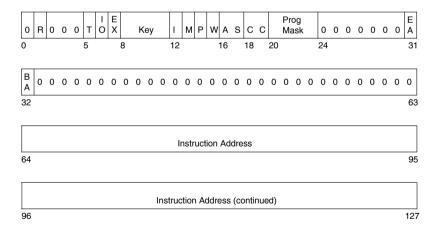

| 2.13. | Program Status Word in 64-bit Addressing Modes       |

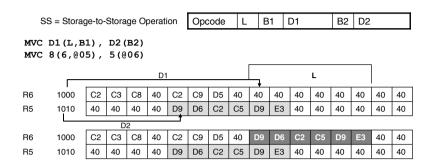

| 2.14. | ADD REGISTER Example 3:                              |

| 2.15. | MOVE CHARACTER Example                               |

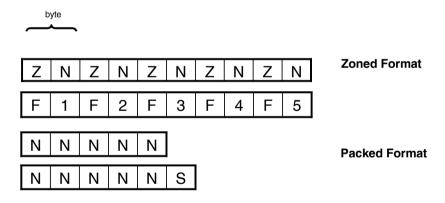

|       | Decimal Arithmetic Data Format                       |

| 2.17. | Representation of PI                                 |

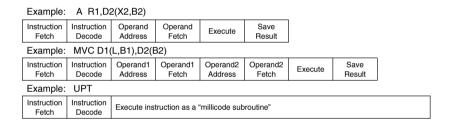

|       | Conceptual View of Instruction Execution             |

| 2.19. | Decomposition of Instructions (System z Examples) 40 |

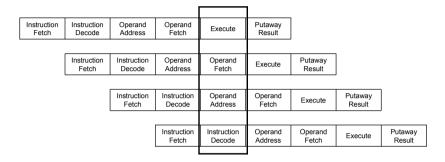

| 2.20. | Pipeline View of Instruction Execution 4             |

| 2.21. | Example of Super-Scalar Processing 42                |

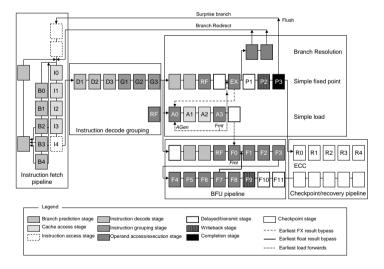

| 2.22. | System z10 Microprocessor Pipeline                   |

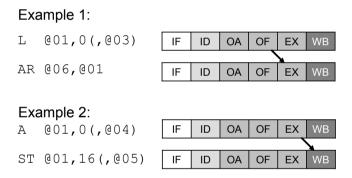

| 2.23. | Examples of Result Forwarding                        |

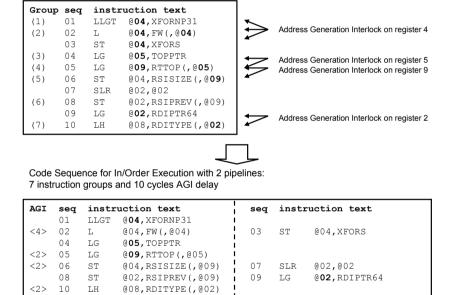

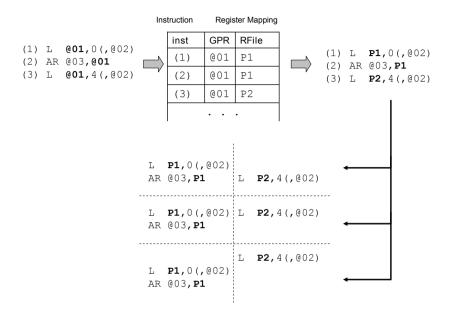

| 2.24. | Example of Instruction Re-Ordering 4                 |

| 2.25. | Example for Register Renaming                        |

| 2.26. | Example for Out-Of-Order Execution                   |

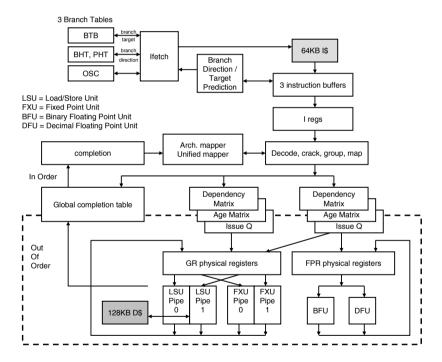

|       | System z196 Microprocessor Core                      |

|       | System z196 Microprocessor Execution Pipeline 52     |

|       | Result Forwarding 5                                  |

viii List of Figures

| 2.30. Instruction Execution on older System z generations 55     |

|------------------------------------------------------------------|

| 2.31. LOAD ON CONDITION (LOCR) Instruction                       |

| 2.32. Optimized instruction sequence by using LOCR 56            |

| 2.33. Time of Day Clock                                          |

| 2.34. Time of Day Clock Extended Format 60                       |

| 2.35. TOD Clock Steering                                         |

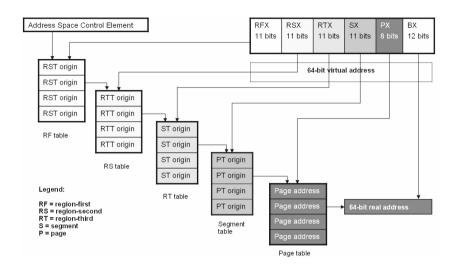

| 2.36. System z Dynamic Address Translation 65                    |

| 2.37. Dynamic Address Translation for Large Pages 66             |

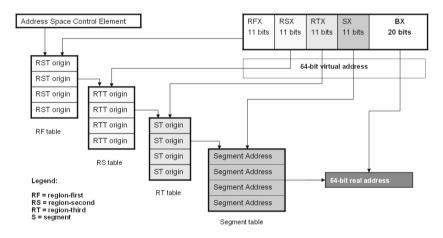

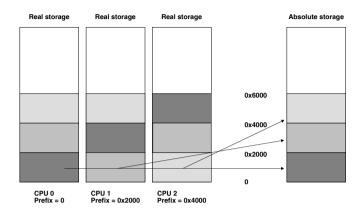

| 2.38. Storage Protection                                         |

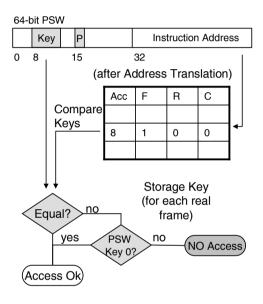

| 2.39. Prefixing                                                  |

| 2.40. Compare And Swap Example                                   |

| 2.41. Better Implementation for Compare And Swap 70              |

| 2.42. z196 I/O Infrastructure                                    |

| 2.43. System z I/O Flow                                          |

| 2.44. Multiple Sub-Channel Sets                                  |

| 2.45. Platform Virtualization on System z                        |

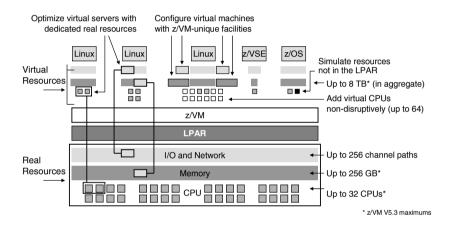

| 2.46. Virtualization with z/VM 5.3                               |

| 2.47. SIE Instruction Flow                                       |

| 2.48. Logical Processor Management 83                            |

| 2.49. Mapping of Absolute to Physical Storage 84                 |

| 2.1 (00.0)                                                       |

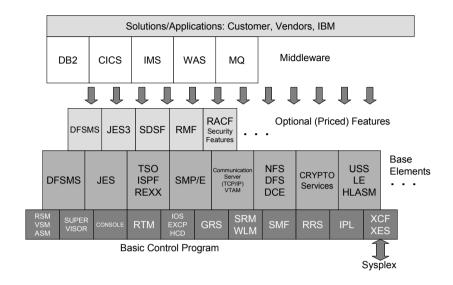

| 3.1. z/OS Structure and Stack                                    |

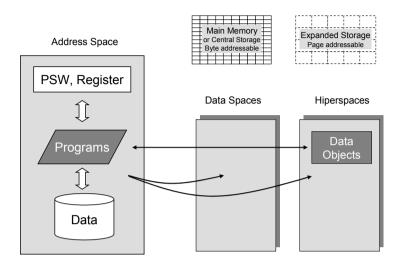

| 3.2. Address Space Structure Structure                           |

| 3.3. Address Space and Storage Types                             |

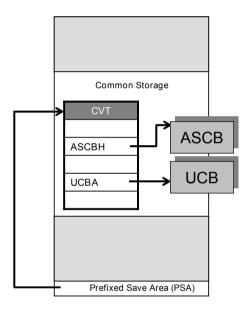

| 3.4. Prefixed Save Area and Common Storage                       |

| 3.5. Address Space Creation                                      |

| 3.6. Program Execution                                           |

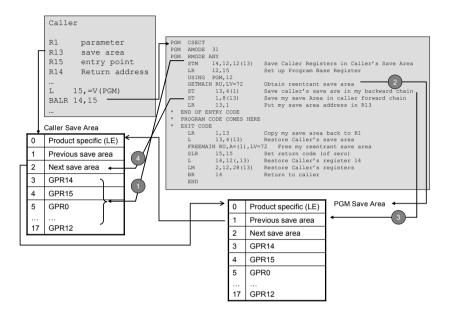

| 3.7. Reentrant programming for 31 bit Programs                   |

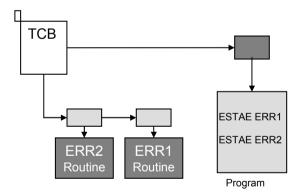

| 3.8. Problem Mode Error Recovery Routines                        |

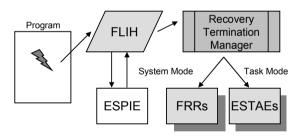

| 3.9. Error Recovery Components                                   |

| 3.10. Error Recovery Processing                                  |

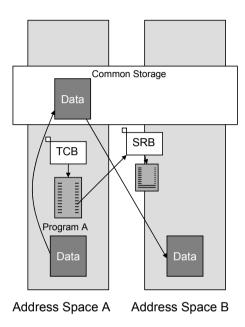

| 3.11. Data Exchange via Common Storage                           |

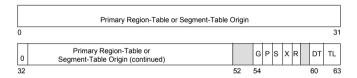

| 3.12. Address Space Control Element                              |

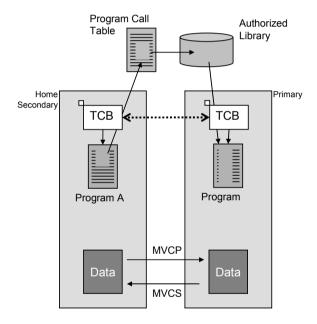

| 3.13. Data Exchange via Program Call                             |

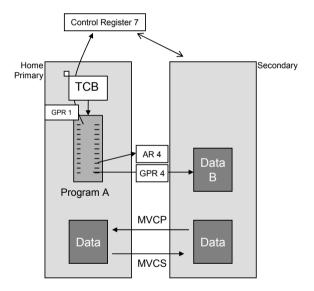

| 3.14. Data Exchange via Access Registers and Cross Memory 107    |

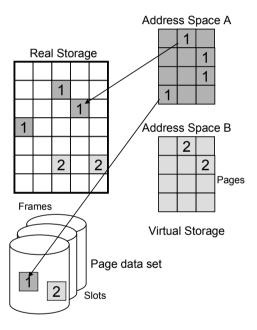

| 3.15. Real, Virtual and Auxiliary Storage                        |

| 3.16. Page Statistics                                            |

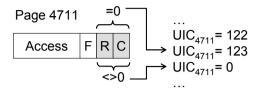

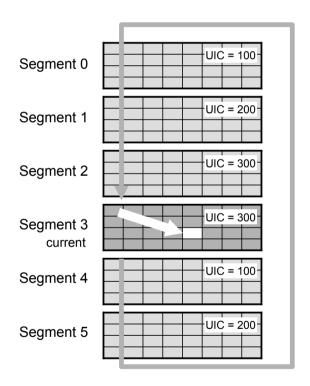

| 3.17. UIC Calculation on current z/OS Systems                    |

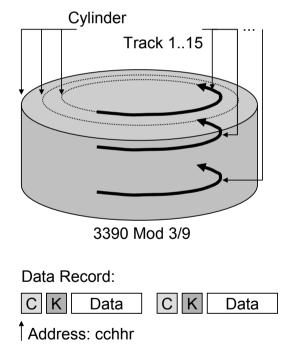

| 3.18. Structure of a Direct Access Device and Count Key Data 115 |

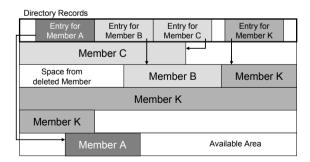

| 3.19. Structure of a Partitioned Data Set                        |

List of Figures ix

| 3.20. Allocating a z/OS Data Set via ISPF                               |

|-------------------------------------------------------------------------|

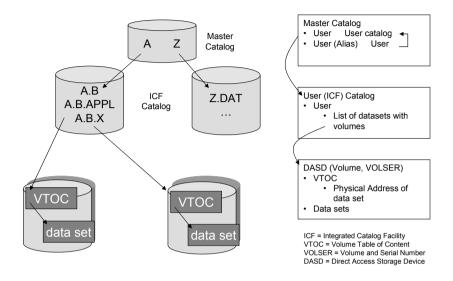

| 3.21. Data Set Index                                                    |

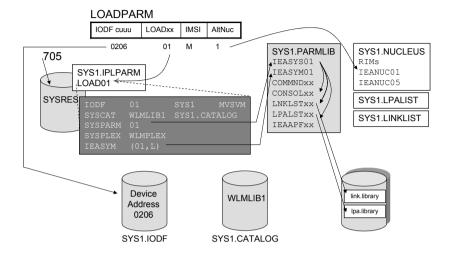

| 3.22. Information to IPL a z/OS System                                  |

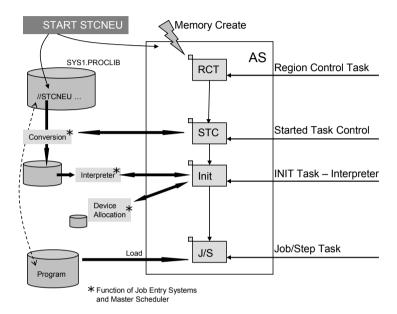

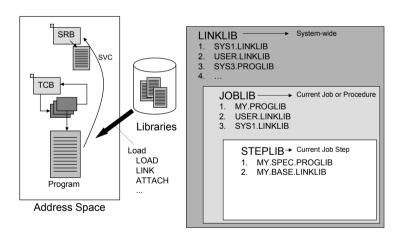

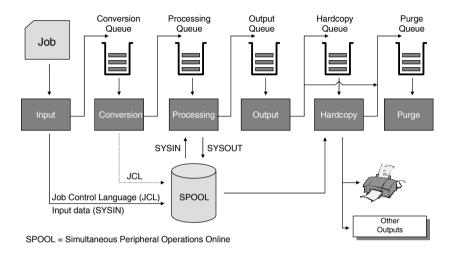

| 3.23. Steps of Job Execution                                            |

| 3.24. Initializing a TSO Address Space                                  |

| 3.25. Unix System Services                                              |

| 4.1. Logical Partitioning supported on System z 130                     |

| 4.2. Typical Partitioning of a System z CEC                             |

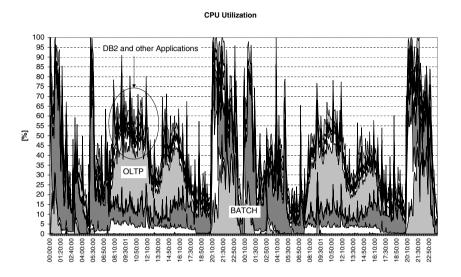

| 4.3. Typical Workload Utilization on z/OS                               |

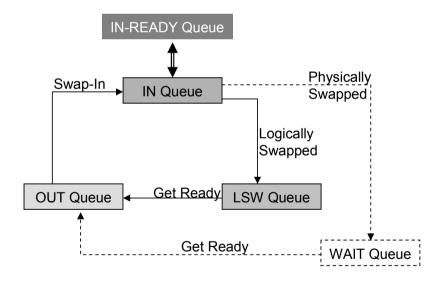

| 4.4. Address Space States                                               |

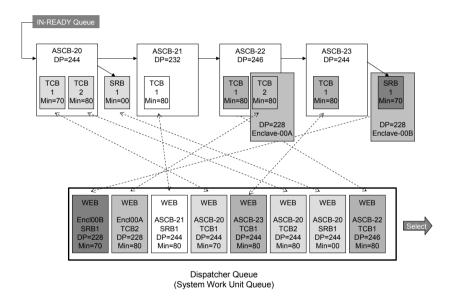

| 4.5. Dispatcher Queue                                                   |

| 4.6. Dispatching Work                                                   |

| 4.7. Time Slicing                                                       |

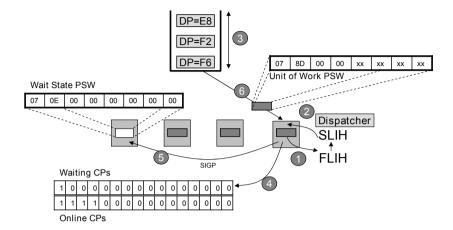

| 4.8. Interrupt Processing                                               |

| 4.9. CPU Enablement for I/O                                             |

| 4.10. CPU Report Example                                                |

| 4.11. History Time Interval per Logical Processor 146                   |

| 4.12. RMF Partition Data Report Example                                 |

| 4.13. Physical Utilization for a CEC with 3 Partitions 150              |

| 4.14. Used Share for the CEC with 3 Partitions                          |

| 4.15. Executing Work on 2 Processor Pools                               |

| 4.16. Websphere Transaction Phases                                      |

| 4.17. Processor Pools on System z                                       |

| 4.18. RMF Partition Data Report with Offload Processors 157             |

| 4.19. Two Logical Processors requesting the same spin lock 158          |

| 4.20. z/OS and PR/SM Spin Lock Synchronization 159                      |

| 4.21. Relative Access to Data in Cache Structures for System z196 . 160 |

| 4.22. Hiperdispatch Objectives                                          |

| 4.23. Vertical CPU Management with High Demand 164                      |

| 4.24. Unparking of Low Processors                                       |

| 4.25. Vertical CPU Management and Processor Shares 166                  |

| 4.26. RMF CPU Activity Report Example                                   |

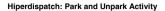

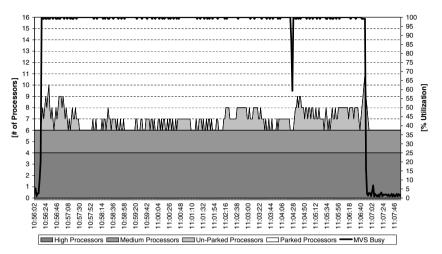

| 4.27. R71: Park and Unpark                                              |

| 4.28. R72: Park and Unpark                                              |

| 4.29. Hiperdispatch Processing in z/OS WLM 170                          |

| 4.30. Affinity Nodes on a z196 System                                   |

| 4.31. Assignement of Logical to Physical Processors 173                 |

| 4.32. Balancing Work                                                    |

| 4.33. Unpark Processing for System SYS1 176                             |

x List of Figures

| .34. Helper Processing for Node 1 of SYS1                          | 176 |

|--------------------------------------------------------------------|-----|

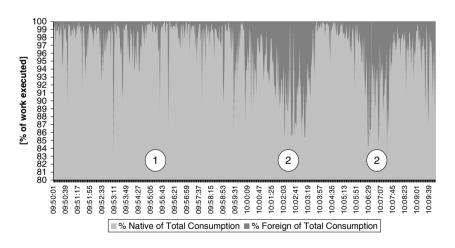

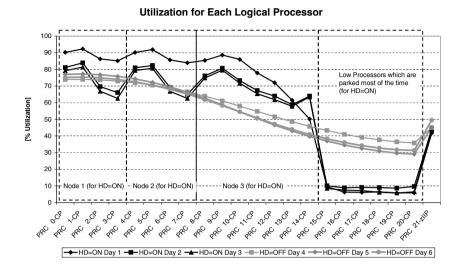

| .35. Hiperdispatch Analysis: Processor Utilization                 | 179 |

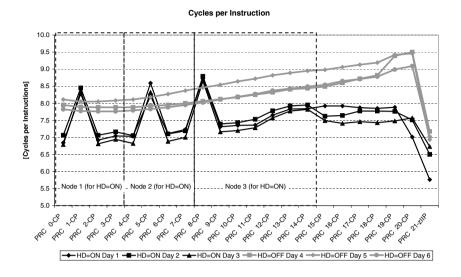

| .36. Hiperdispatch Analysis: Cycles per Instructions per Processor | 180 |

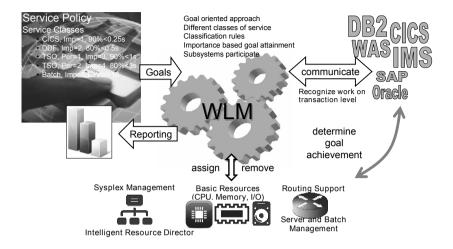

| .1. Conceptual View on z/OS Workload Management                    | 187 |

| .2. Work Classification Example for Batch Jobs                     | 188 |

| .3. Example for a Service Class Definition for Batch Work          | 190 |

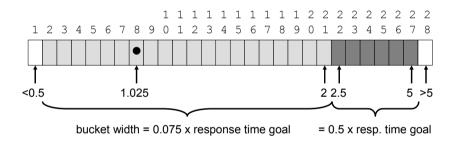

| .4. Response Time Distribution Buckets                             | 192 |

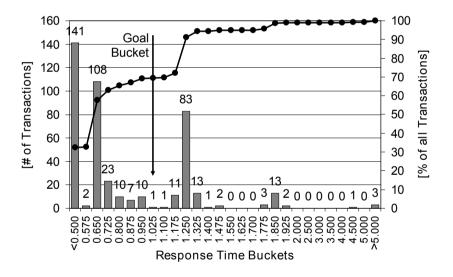

| .5. Response Time Distribution for a Service Class                 | 193 |

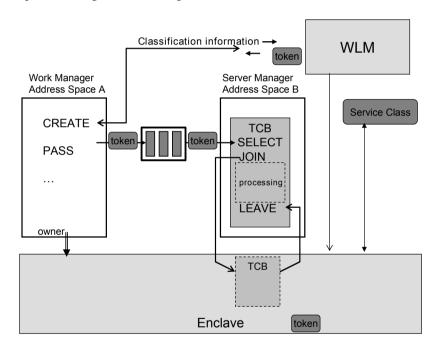

| .6. WLM Transaction Management                                     | 196 |

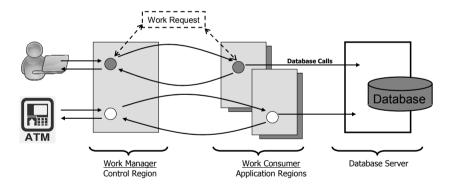

| .7. Enclave Processing Model for Websphere                         | 198 |

| .8. Processing Model for CICS Transactions                         | 200 |

| .9. WLM Service Definition                                         | 201 |

| .10. Actual Response Time for a Percentile Response Time Goal .    | 204 |

| .11. Data Plots                                                    | 209 |

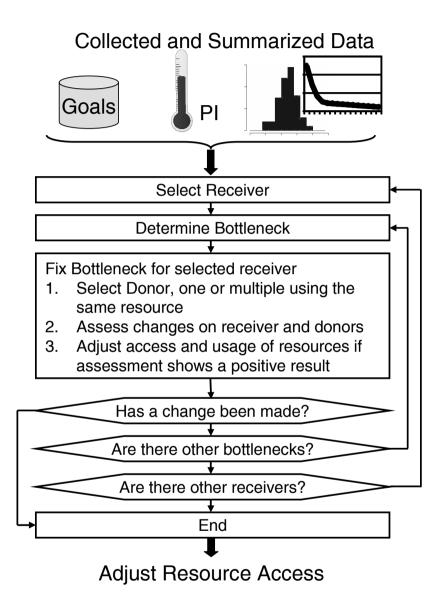

| .12. Policy Adjustment Process                                     | 211 |

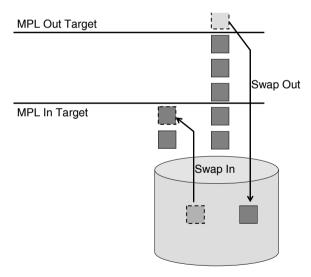

| .13. Swapping Related to MPL In and Out Targets                    | 213 |

| .14. Plots to Adjust MPL In and Out Targets                        | 214 |

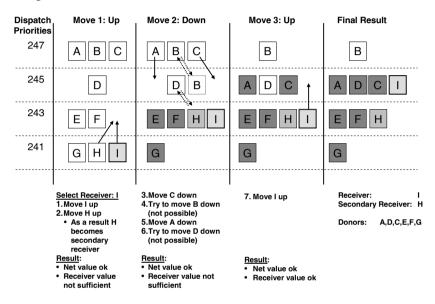

| .15. Example for Adjusting Dispatch Priorities                     | 220 |

| .16. Sample Work Execution                                         | 223 |

| .17. Sample Goal Achievement                                       | 224 |

| .18. CPU Service consumption in a real system                      | 225 |

| .19. Dispatch Priorities in a real system                          | 225 |

| .20. Resource Adjustment                                           | 227 |

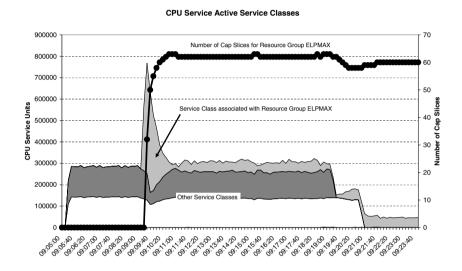

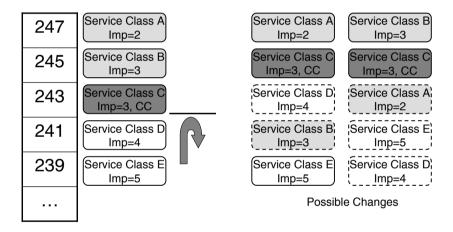

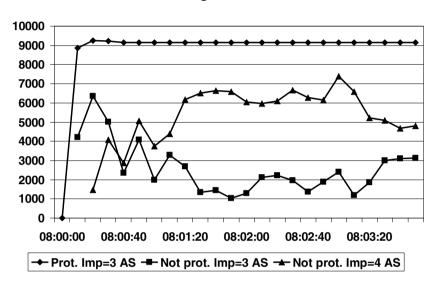

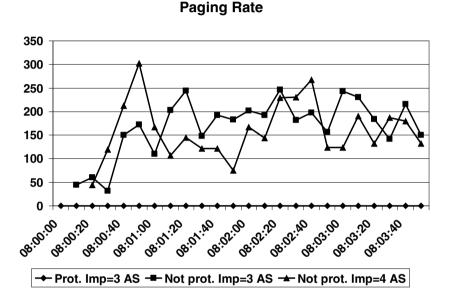

| .21. Example for a Resource Group with Maximum Limit               | 230 |

| .22. Example for a Service Class with CPU Critical Definition      | 231 |

| .23. Storage Frames of Service Classes                             | 232 |

| .24. Paging Rate of Service Classes                                | 233 |

| .25. Discretionary Goal Management                                 | 234 |

| .26. Routing Support                                               | 236 |

| .27. Contention Situation                                          | 238 |

| .28. WLM Queue Management                                          | 240 |

| .29. WLM Batch Management                                          | 242 |

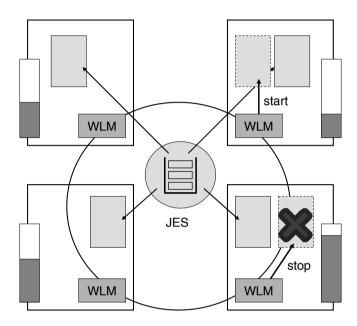

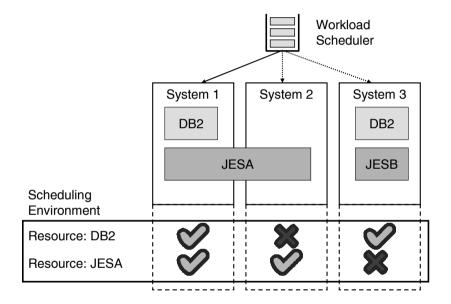

| 30. WLM Supported Workload Scheduling                              | 243 |

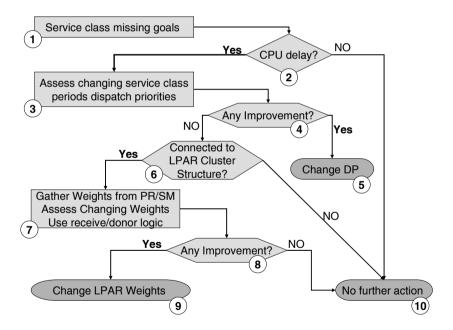

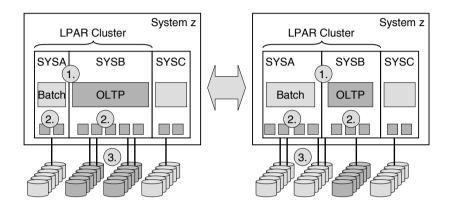

| 31. WLM Policy Adjustment for Weight Changes                       | 245 |

| .32. Intelligent Resource Director Functions                       | 246 |

| .33. Group Capping Example                                         | 248 |

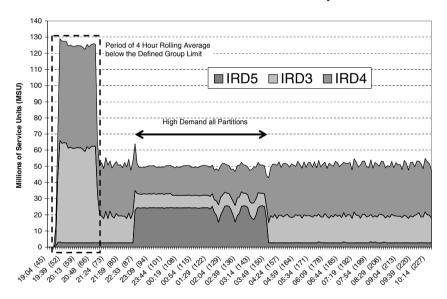

| .1. Total System Capacity of System z compared to IBM H5           |     |

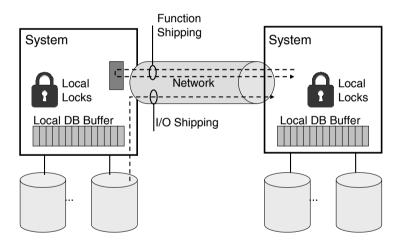

| .2. Shared-Nothing Cluster                                         | 255 |

List of Figures xi

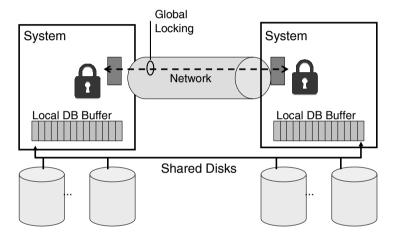

| 6.3. | Shared-Disk Cluster                              |

|------|--------------------------------------------------|

| 6.4. | Parallel Sysplex                                 |

| 6.5. | Coupling Facility Components                     |

| 6.6. | Sysplex Couple Data Sets                         |

| 6.7. | Lock Structure                                   |

| 6.8. | List Structure                                   |

| 6.9. | Cache Structure                                  |

|      | . Sysplex Setup                                  |

|      | . Coupling Facility Duplexing                    |

|      | . Original Parallel Sysplex Configuration        |

|      | . Modern Parallel Sysplex Configuration          |

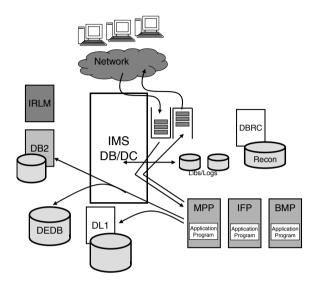

| 6.14 | . Information Management System Structure        |

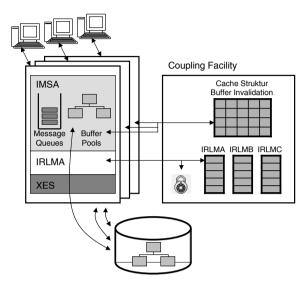

|      | . IMS Parallel Sysplex Exploitation Step 1       |

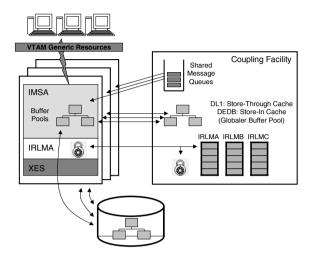

| 6.16 | . IMS Parallel Sysplex Exploitation Step 2       |

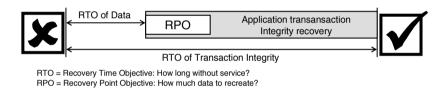

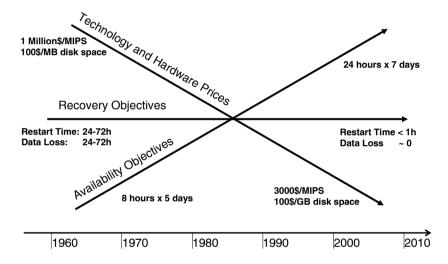

|      | . Recovery Objectives                            |

|      | . Requirements on Recovery Objectives            |

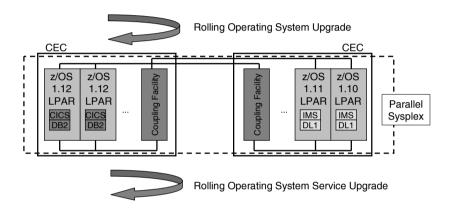

|      | . Rolling Upgrades and Service                   |

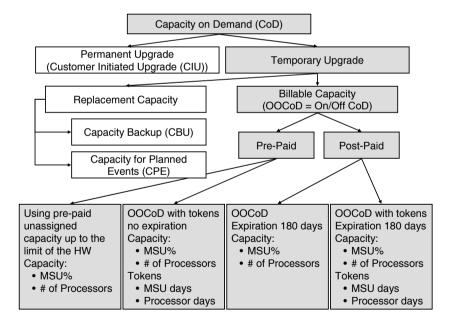

|      | . Capacity Upgrade Options                       |

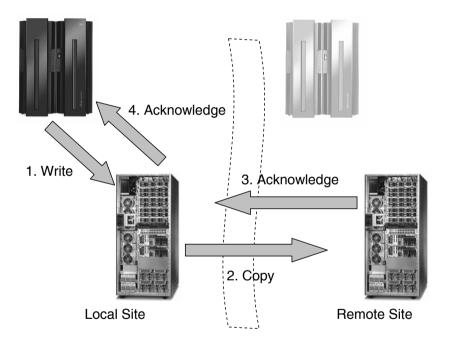

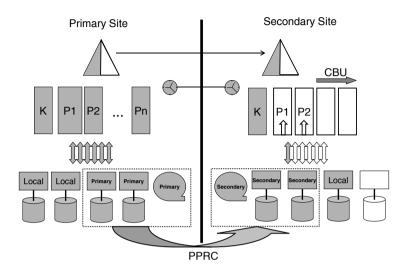

|      | . Peer-to-Peer Remote Copy                       |

|      | . I/O Benchmark for Synchronous Copy             |

|      | . Hyperswap                                      |

|      | Extended Remote Copy                             |

|      | . Single Site Workload (Active/Standby)          |

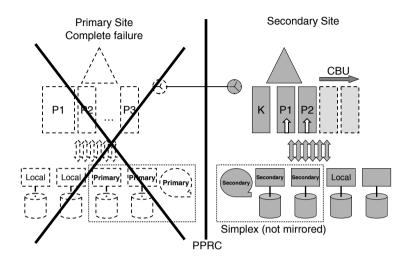

|      | . Single Site Failure Scenario                   |

|      | . Multi Site Workload (Active/Active)            |

|      | . Multi Site Workload: I/O Subsystem Failure 290 |

|      | . Multi Site Workload: Complete Site Failure 291 |

## **List of Tables**

| 1.1. | Cost of Downtime by Industry                             | 2   |

|------|----------------------------------------------------------|-----|

| 2.1. | Comparison of Cache Size for System z196 and zEC12       | 17  |

| 2.2. | Number of Processing Units per zEC12 Model               | 19  |

| 2.3. | RAS Capabilities for RAIM Memory                         | 24  |

| 2.4. | Halfword Codes for Decimal Format                        | 37  |

| 2.5. | Floating Point Formats on System z                       | 38  |

| 2.6. | Decomposing CISC Instructions                            | 48  |

| 2.7. | Interrupt Locations                                      | 59  |

| 2.8. | Handling of Virtual Addresses                            | 63  |

| 3.1. | Abnormal Termination Codes                               | 101 |

| 3.2. | Sizes of last physically build z/OS DASDs                | 115 |

| 4.1. | Example for Processor Shares of three Logical Partitions | 144 |

| 4.2. | PR/SM Dispatching Example                                | 147 |

| 4.3. | LPAR Configuration Example                               | 149 |

| 4.4. | Relative Capacity Indicators for System z196             | 162 |

| 4.5. | LPAR Definition Example                                  | 171 |

| 4.6. | Nodes of System SYS1                                     | 175 |

| 4.7. | Hiperdispatch Analysis: Cycles per Instructions          | 181 |

| 4.8. | Hiperdispatch Benefit for System z196                    | 182 |

| 5.1. | Possible Goals for Workload Types                        | 195 |

| 5.2. | WLM Data Sample Categories                               | 206 |

| 5.3. | Data Aging in WLM Histories                              | 207 |

| 5.4. | Service Class State Sample Matrix                        | 208 |

| 5.5. | Net Value Decision Matrix                                | 217 |

| 5.6. | Dispatch Priorities in z/OS                              | 219 |

| 5.7. | Sample Service Class Definition                          | 222 |

| 5.8. | Group Capping Definitions                                | 247 |

| 5.9. | Subsystem Participation with z/OS Workload Management    | 249 |

| xiv  | 1                             |  |  |  |  |  | List of |  |  |  | f Ta | <u> Fables</u> |  |

|------|-------------------------------|--|--|--|--|--|---------|--|--|--|------|----------------|--|

|      |                               |  |  |  |  |  |         |  |  |  |      |                |  |

| 6.1. | Parallel Sysplex Exploitation |  |  |  |  |  |         |  |  |  |      | 275            |  |

#### **Preface**

Asking people whether they ever used mainframe computers? The usual answer is No. People are often not aware what a mainframe computer is and what role it plays in the real world. Good examples are ATM, which book on mainframe computer. Everybody who uses its money card is accessing mainframe computer technology. Generally mainframe computing is everywhere where critical data processing is required. The dominating mainframe computing platform is IBM System z and its main operating system z/OS.

While mainframe computing is the backbone of industrial and commercial computing, the answer of many students about the acquaintance with mainframe computing would not be different to those of usual people. In order to emphasize the importance of mainframe computing, the KIT together with the FZI formed an alliance with IBM R&D Germany the Informatics Innovation Center (IIC). The IIC is a platform for cooperation between research, academic education and industry exchanging knowledge, experience and providing a higher degree of industry experience for bachelor and master students. Part of the IIC are lectures about mainframe computing with emphasis on System and z/OS underlining the strength and special capabilities of mainframe technology.

The present book analyzes why mainframe technology is highly scalable and how it provides high availability enabling the technology as base for critical business operations. It gives examples on how scalability must be build throughout the complete hardware and software stack providing elasticity of the business. High availability solutions ensure that the business can operate with any interruptions surviving any kind of possible disaster. The book is the result of the fruitful cooperation between academy and industry and helps to strengthen the knowledge of students and everybody involved with computers about mainframe technology.

I am very happy, that Robert Vaupel, Senior Technical Staff Member of IBM and Manager of the IIC, contributes to the goal of the IIC so well with this book. I hope the readers are like me amazed about the remarkable technical solutions of mainframe computers which are often far looking into the future,

xvi List of Tables

in strong contrast to the reputation of mainframe computing which is often called legacy technology.

Prof. Dr. Ralf Reussner Director of IIC

#### **Acknowledgments**

Many thanks to the following people for their contribution to the project:

- **Dieter Wellerdiek** IBM Systems & Technology Group, zOS WLM/SRM Development, IBM R & D Böblingen, Germany

- **Joachim von Buttlar** IBM Systems & Technology Group, System z Firmware Development and Simulation, IBM R & D Böblingen, Germany

- **Robert R. Rogers** IBM Systems & Technology Group, Power & z Systems, Distinguished Engineer z/OS Designer/Philosopher, Software Architect: System z Core Technologies, IBM Poughkeepsie, USA

#### 1. Introduction

A mainframe computer is what businesses use to host their commercial databases, transaction servers, and applications that require a greater degree of security and availability than is commonly found on smaller scale machines. Such computers typically execute hundreds of applications, they connect to thousands of I/O devices, and serve thousands of users simultaneously. Mainframes can be best defined by their characteristics:

- To ensure a reliable and predictable execution of transactions

- To store business critical data

#### 1.1. Motivation

The characterization and definition of mainframes also define their most important features: RAS. RAS is an abbreviation which stands for reliability, availability, and serviceability, or optionally scalability, or security. These features lead to the subject of this course which shows the requirements and efforts to provide and support computing environments which are highly available at best without any interruption of the operation and which are highly scalable to support the requirements of large customer installations. We will use System  $z^{(8)}$  and its main operating system  $z/OS^{(8)}$  as example to describe these features.

The requirements of highly resilient business environments become obvious if we take a look at cost of unexpected interruptions of business operations caused by computing failures (see table 1.1). Today's business operations are highly dependent on non interruptible operations and even short downtimes can't be afforded anymore. Over the last 40 years IBM® developed the System /360 architecture into a highly resilient and non interruptible computer environment. As a result 95% of the world's biggest companies use System z. The highest usage can be found in the financial industry. Around 97% of all retail banks, insurance companies and brokerage firms use System z as their main back-end server environment. 65 to 70% of all relevant data for companies is stored on

2 Introduction

databases on System z. High Availability is one of the most important aspects for business operations and it goes hand in hand with scalability which defines the ability of an environment to adapt to changing business needs. System z and its main operating system z/OS are a perfect example how high availability and scalability is implemented and which hurdles must be taken to get to an operational environment which meets the requirement of nearly no downtime and which is flexible enough to meet capacity requirements for world wide operating businesses.

| Industry Sector                                               | Loss per Hour |  |  |  |

|---------------------------------------------------------------|---------------|--|--|--|

| Financial                                                     | \$8,213,470   |  |  |  |

| Telecommunications                                            | \$4,611,604   |  |  |  |

| Information Technology                                        | \$3,316,058   |  |  |  |

| Insurance                                                     | \$2,582,382   |  |  |  |

| Pharmaceuticals                                               | \$2,058,710   |  |  |  |

| Energy                                                        | \$1,468,798   |  |  |  |

| Transportation                                                | \$1,463,128   |  |  |  |

| Banking                                                       | \$1,145,129   |  |  |  |

| Chemicals                                                     | \$1,071,404   |  |  |  |

| Consumer Products                                             | \$989,795     |  |  |  |

| Source: Robert Francis Group 2006: "Picking the Value of PKI: |               |  |  |  |

| Leveraging z/OS for Improving Manageability, Reliability, and |               |  |  |  |

| Total Cost of Ownership of PKI and Digital Certificates."     |               |  |  |  |

Table 1.1.: Cost of Downtime by Industry

System z and z/OS are also the best examples to show how High Availability and Scalability requirements are implemented from hardware, firmware layers, operating system, to the application layers. They need to be covered at all layers and also require interaction across the whole operating stack. This course consists of five segments:

- Introduces System z hardware and firmware and shows which efforts are undergone to support scalability for high frequency processors and how to support dozens of processors in parallel. High availability features are discussed which enable the System z environment to continue to operate even if processors, parts of the main memory or complete parts of the system fail.

- 2. This segment introduces z/OS which is the main operating system used to run large transaction environments of System z. The roots of z/OS go

- 40 years back into the past and it is a very good example how legacy computing technology meets the requirements of the modern business world.

- 3. At this point we will focus on the dispatching processes of the System z Hypervisor as well as the z/OS operating system. The main focus is on how the different dispatching processes meet the requirements of their environments, at which points they work together and at which points they become problematic for system scaling. The second part of this segment highlights a feature named Hiperdispatch which has been introduced to overcome the scalability limitations of large n-way systems such as System z.

- 4. One important aspect of system operation is the supervision and controlling of the work which flows through the system. A well tuned environment is crucial for running business applications efficiently and furthermore it is a guarantee to maintain high availability at the application level. z/OS includes a component named Workload Manager (WLM) which controls and manages the workload of the system. WLM is the main component for autonomic performance management and it also includes capabilities to maintain application availability.

- 5. The last segment goes beyond the single system. z/OS systems can form a cluster environment named a Parallel Sysplex®. The Parallel Sysplex was originally introduced to overcome limitations of computing speed. While this is no longer the biggest issue with today's technology the Parallel Sysplex is nowadays the base for a continuously operating environment on a global scale.

#### 1.2. High Availability

In this section we want to take a look at the terminology around High Availability. High Availability means a resilient IT infrastructure which allows to mask individual component failures and which also allows to recover from errors. High Availability is based on an infrastructure which is created of reliable components. Reliability is the probability of a single component or device to perform its intended function during a specified period of time under stated conditions. Mathematically reliability can be expressed as a probability density function:

4 Introduction

$$\begin{split} R(t) &= & Pr[no\ failure\ in(0,t]] \\ &= & Pr\{T>t\} \\ &= & \int_t^\infty f(x)\ \mathrm{d}x \\ &= & \begin{cases} e^{-\lambda t} & \text{for random failures,} \\ \frac{1}{\sigma\sqrt{2\pi}}\int e^{\frac{1}{2}(\frac{T-\mu}{\sigma})^2} & \text{for wear-out failures.} \end{cases} \end{split}$$

A failure is usually regarded a random phenomenon. For random failures the exponential function  $e^{-\lambda t}$  describes the probability of the failure occurrence. Another set of failures are wear out problems which typically occur towards the end of the life-cycle of a device. These failures typically follow a normal distribution. At the beginning of the life cycle failures may occur which are based on insufficient tests, design flaws or oversights. Such errors are named infant mortality failures and they should be avoided by following design, implementation and testing guidelines. In any case reliability is concerned with the fact that failures should be avoided and for cases where they can't be avoided that the system should be designed to survive them.

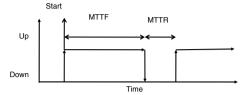

For our discussions we are also primarily interested in reliability during the "useful life period" of a device. The reliability measure is the Mean-Time-Between-Failures (MTBF):

$$MTBF = \Theta = \frac{1}{\lambda} = \frac{T}{r}$$

with  $\lambda$  = failure rate, T = total time, r = number of failures. This is sometimes also defined as Mean-Time-To-Failures (MTTF) in case the system is replaced after the failure. The time after the failure occurrence until the system is operational again is defined as Mean-Time-To-Repair (MTTR). Availability is now defined as the probability function of the total time the system is up and running divided by the time the system should be operational, (see also table 1.1):

$$PA(t) = \frac{MTTF}{MTTF + MTTR}$$

Our discussion of System z will start with the components of the system and techniques to support the claim of the system to provide extraordinary high reliability. System z is currently known to provide a reliability of 99.999 % which

1.3 Scalability 5

Figure 1.1.: Definition of Availability

means that the probability for the system to be non operational is less that 31.5 seconds per year. Nevertheless high reliable components are not sufficient to support the customer demand for a continuously operating environment. We will also discuss Disaster Recovery techniques and system and environment layouts which are necessary to achieve a maximum resilient business environment.

#### 1.3. Scalability

The second feature of a modern business environment which we will discuss in this course is scalability. Scalability in our context means how the environment is able to adjust to different business needs and we will also discuss techniques and functions which enable the system to provide a stated capacity and performance. We will encounter that increasing the processor frequency is not sufficient anymore to provide higher system capacity and we will discuss the difficulties which occur when an existing environment grows bigger. Scalability will also cover the ability of the system to incremental grow based on required demand. System and business growth on an application scale can be achieved in two ways:

- 1. Horizontally, that means if more application instances are needed more systems need to be deployed.

- Vertically, which means that an existing system can grow to support more instances of the same application as well as to support multiple different applications.

System z is the best example for an environment which support vertical growth if needed. We will see that System z and especially z/OS allow to host multiple

6 Introduction

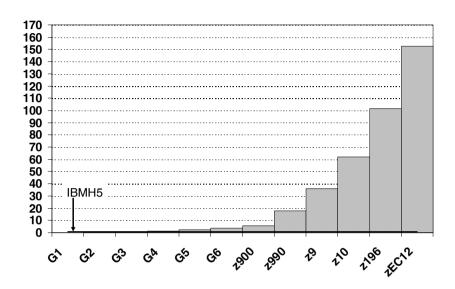

applications at the same time and we will discuss the functions which are required to ensure a meaningful operation under such conditions. System z can be upgraded in very small incremental steps. Figure 1.2 shows the capacity range of high-end z196 systems. The possible system configuration of the z196 7xx systems encompass a range from 150 to 6140 Million of Service Units (MSU) which is a measure of system capacity (see [21]). The important factor is that the high end z196 mainframe can cover a capacity range which allows to scale 40 times from the smallest to the largest system.

# 2196 High End: Million of Service Units 6140 MSU 5500 4500 4500 4500 2500 150 MSU 150 MSU 1500 1500 1500 1500

Figure 1.2.: Capacity Range of a High-End System z196

In addition low end z196 systems exist which provide further upgrade capability in the range from 30 to 1000 MSU. The low end systems are available in 3 configurations: 401 to 415, 501 to 515, and 601 to 615. The first letter determines the single engine speed and the two following letters the numbers of available physical processors. This allows installations with smaller capacity requirements to adjust their systems to their needs. If this is not sufficient another set of smaller systems named z114 are available which cover the capacity range from 3 to 388 MSU. These systems are available with 26 different single engine speeds and up to 5 physical engines. The newer zEC12 mainframe which became available in September 2012 provides the same choice of models like the earlier versions z10<sup>TM</sup> and z9<sup>®</sup> did.

1.3 Scalability 7

The possibility to grow the systems incrementally and to cover a very wide capacity range requires that the software from the virtualization layer up to the middleware which process the end user applications provide the elasticity to deal with such high differences. Also upgrades and downgrades can be applied instantaneously and the software layer must react accordingly to them. We will discuss these functions in detail and we will give examples for the different layers how it is possible to provide the elasticity so that the capacity can be used by the end users.

#### 2. z/Architecture

In the segment we will discuss the design of System z and which functions and techniques are used to support the claims of high availability and scalability.

#### 2.1. A Little History

Since when does System z exist and what where the design decisions to create such an environment? The roots of System z and z/Architecture are now nearly 50 years back in history to System /360 which has been introduced on April 7th, 1964. System /360 was the first computing architecture. The promise which was made at that time to the customer was that all following systems of the same architecture were compatible to the first systems, meaning that programs which were created on the first systems will still run on all future environments.

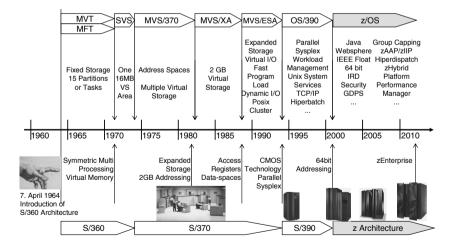

Figure 2.1.: History of System z Architecture and z/OS

10 z/Architecture

Why was this necessary? Prior to System /360 different system designs existed. More important, with every new system a new system design was introduced. That required the user to re-program nearly everything so that it could run on the new hardware. This was highly inefficient and therefore IBM introduced a system architecture with the promise of upward compatibility for all future environments.

Figure 2.1 shows the major development steps from System /360 to System z from 1964 to today. The graphic also covers the development of the main operating system of System, z/OS. The name System /360 was created from 360 degree of a circle meaning that this architecture covers all computing aspects from hardware to operating systems for all IBM computers. System /360 was also introduced for commercial and technical processing. Aside of compatibility the focus was also on easy extending the environment by adding additional processors and I/O units. Thus scalability was a major design point of the system architecture.

While System /360 was nearly unchanged during its first years the first major enhancement was the introduction of virtual storage and multi processing in the 1970s. The increasing capacity demand and the necessity of exploiting the enhanced architecture lead to the development of a common operating system: Multiple Virtual Storage (MVS<sup>™</sup>). MVS is still the base for z/OS today's operating system for System z and was introduced in 1974. With the introduction of MVS, virtual storage and symmetric multi processing an architectural change from System /360 to /370 was carried out. System/370 still maintained the compatibility to System /360 but marked a major milestone of advanced computer technology.

The following years and developments were marked by the hunger for more system memory. The initial System /360 architecture used 24 bit for addressing which just allowed to address 16 MB of virtual and physical memory. This became too small and in the early 1980s the addressing was increased to 2 GB or 31 bit addresses. The 32nd bit of the address was used to distinguish a 31 bit from a 24 bit address and we will also later see that both the architecture and the operating system underwent every effort to maintain compatibility to 24 bit addressing and programs written on older technology.

Storage was still the main concern during these days. On the one hand main memory was very expensive on the other hand storage was the limiting factor of computer technology while processor technology advanced much faster. Many attempts were made to overcome the limiting factor main memory and one of such developments were the introduction of expanded storage. Expanded storage.

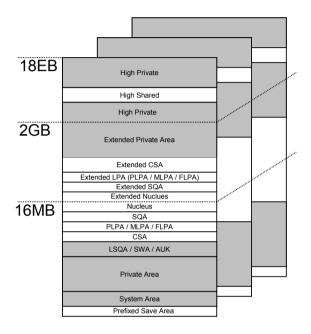

age was a 4KB addressable storage which extended the main memory. While it was not byte addressable it was not so easy to access the storage by programs. Thus it was first primarily used as a fast paging device and only later techniques, like data spaces and Hiperspaces allowed to use the storage more directly. Nevertheless in 2001 with the introduction of the System z architecture and the z/OS operating system the addressability was extended to 64 bits and the limitations of only 2 GB addressable storage were finally removed. At that time the cost for storage was relative small compared to other elements of the system and nowadays environments can afford hundredths of GB of main memory.

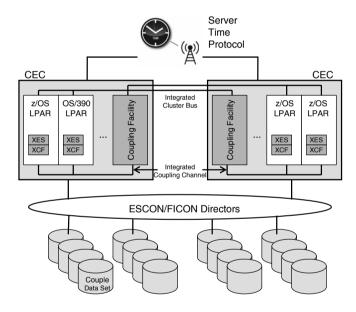

But before the change from 31 bit to 64 bit addressing was made another important development must be noticed. System /360 and its successor /370 was based on bipolar chip technology. Bipolar chip technology was in the 1980s the fastest existing chip technology but its manufacturing costs and further more the cooling problem of the thermal effects of the chip caused a high problem to future development of the architecture. As a matter of fact System /370 based on bipolar technology reached a scalability limitation at the end of the 1980s which could not be overcome within this technology. In 1994 IBM introduced a completely re-newed generation based on CMOS (complementary metal-oxide-semiconductor) chip technology. The new generation was named System/390<sup>®</sup> and the first notice to be made was that the single processor speed of the new system reached only 28% of the speed of the last bipolar system of System /370 while the available system capacity even was shrinking to only 16%. This was a significant scalability issue and in order to overcome this limitation a cluster technology the Parallel Sysplex was introduced which allows to couple multiple OS/390® and later on z/OS systems via a fast storage device the coupling facility.

The fourth generation of new System /390 hardware based on CMOS technology finally reached the capacity and performance of the previous bipolar System /370 hardware. Nowadays the CMOS technology advanced to performance and capacity ratings which are higher than ever before. System z196 with 5.2 GHz frequency is the fastest commercial processor in the industry. System z is also a wonderful example of a technology which scales since 50 years and which were able to overcome a technological limitation by changing the base of its chip technology. The first S/360 systems provided a capacity of roughly 0.005 Million Instructions per Second (MIPS) and a 2817-701 which is a one way z196 offers a capacity of 1200 MIPS. With the very high increased in system capacity the focus for scalability changes from providing the minimum capacity as it was in the early 90s to exploiting the available capacity.

12 z/Architecture

We will also see that the introduction of very high clock frequency does not alone provide a high system capacity and that advanced techniques are necessary to exploit the this technology. On the other hand the focus of the Parallel Sysplex technology is no longer scalability but high availability and continuous operations of the environment. The Parallel Sysplex technology has been enhanced to support a Geographically Dispersed Parallel Sysplex  $^{\text{TM}}$  (GDPS $^{\text{(R)}}$ ) environment and thus providing a resilient business environment on a global scale.

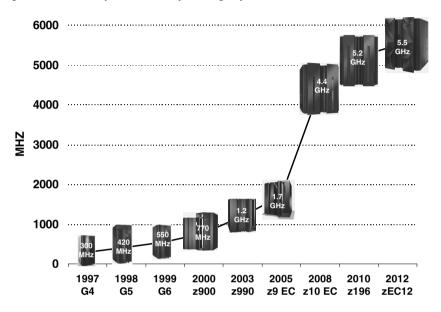

#### 2.2. System z CMOS Heritage

System z196 is the latest system of the CMOS mainframe heritage started in 1994 which replaced the bipolar technology of the 1980s. Figure 2.2 shows the development of the processor frequency starting with the fourth generation of CMOS mainframe processors. We remember that the fourth generation was the first processor which provided the same capacity and speed than the earlier bipolar technology. Generation 5 (G5) and 6 introduced IEEE standard binary floating point and copper technology. System z900 was the first system of the System z architecture and it introduced full 64 bit architecture.

System z990 also where a milestone in processor technology. It was the first multi book system and it introduced super-scalar processor pipeline. A significant advance was made with the change from System z9 to z10. System z10 increased the clock frequency by 2.5 times. This now required significant improvements of the System z microprocessor. Enhancements of the super-scalar pipeline became necessary as well as for the cache topology between the microprocessor and main memory. Another significant advance in this direction was made with the System z196 microprocessor which also introduced a new out-of-order pipeline on System z. It should be noted that this was by far not the introduction of out of order processing. The last generations of bipolar technology also already used out of order processing. But the high clock frequency and using the existing microprocessor technology efficiently now require again more sophisticated processor design. Until now the advantage of the newest generation was mostly given by incremental technology advances. In addition System z196 completes the cache topology which was introduced with System z10. System zEC12 has been released in September 2012 and it is the newest member of the System z family. The processor frequency increased to 5.5 GHz and the processor has been enhanced for its out-of-order processing. The following chapters will discuss the System z microprocessor technology with examples shown for System z10, z196 and zEC12. The discussion will focus on the necessary functionality to exploit high processor frequency and to provide scalability and elasticity on large systems.

Figure 2.2.: System z: CMOS Mainframe Heritage

At this point we also need to introduce a common terminology for a System z mainframe environment. Such a computing system is named a Central Electronic Complex (CEC) or Central Processing Complex (CPC).

# 2.3. System zEC12 Central Electronic Complex

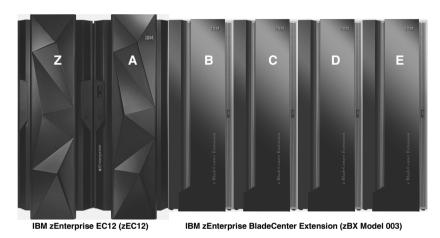

The term Central Electronic Complex becomes much more clear when we take a look at the possible expansions for a System zEC12 compared to a classical mainframe environment. Figure 2.3 shows how a zEC12 may look like. The classical mainframe consists of two frames, the A and Z frame which will be discussed later in more detail. In addition Blade Center Extensions named zBX and enumerated as B, C, D, or E frame can be added to the classical mainframe.

14 z/Architecture

In the first stage this provides a closer integration of application servers running on Linux and Windows environments to the transaction and database servers running on the classical mainframe environment. Using zBX extensions also integrates many manageability aspects on a single console which make complex environments more suitable for large installations. the zBX extensions were introduced with System z196. The z196 was the first System z which provided the structure of a classical mainframe and up to 5 zBX extensions.

Figure 2.3.: System zEC12 Frames and Blade Extensions

In our excursion on High Availability and Scalability we will concentrate on the classical mainframe environment which is the Z and A frame of the CEC.

#### 2.4. System zEC12 Components

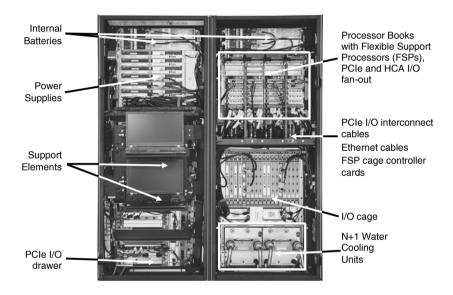

Figure 2.4 shows how the high end System zEC12 looks when the covers are removed. The depicted system is a water cooled model which is only available for the largest extension of the largest models H89 and HA1. Water cooling is optionally, the standard cooling method uses a refrigerator liquid in a closed circuit cycle. The water cooling models allow the installation to provide additional cooling which is especially advisable in warmer region.

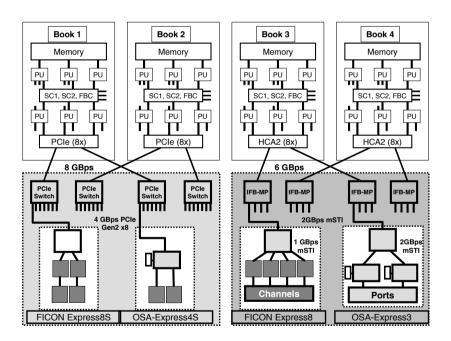

The A frame of the CEC contains the system processors, I/O cages, optional battery backup systems and the cooling environment. The HA1 model contains

120 processors of which 101 can be used for customer workloads. The processors are contained on 4 books. The HA1 as well as the H89 are always made of 4 books. Smaller models like the H66 consist of 3 books, the H43 of 2 and the H20 of 1 book. The number denotes the maximum number of processors which can be used for workloads. The additional processors are utilized for internal processing or as spares. One book can keep up to 30 processors. The books also contain the memory cards of the system.

Figure 2.4.: Under the Hood of System zEC12

The Z frame contains the Support Elements (SE) which are used for maintenance. Usually only a system technician has a need to use a support element for example when the replacement of a part becomes necessary. The management of the system is usually done from a Hardware Management Console (HMC) which is connected remotely to the CEC. The Z frame also contains power supplies and additional I/O drawers. It should be noted that the general structure of the z196 is the same just with a smaller number of total processors. The biggest z196 has 96 processors of which are 80 can be used for workloads.

# 2.5. System z Multi Chip Module

Figure 2.5.: System zEC12 Cache Level Structure

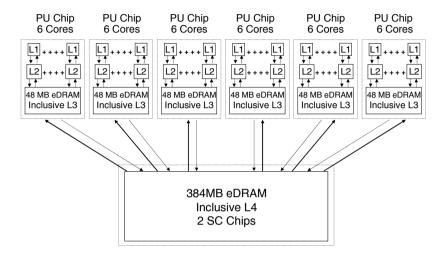

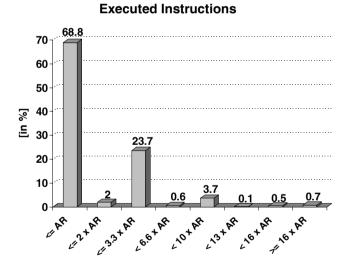

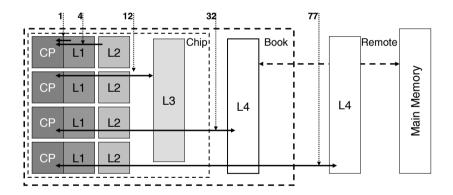

The heart of all System z systems is the Multi Chip Module (MCM). The MCM contains the processor and storage controller chips. The MCM for z196 and zEC12 always consist of 6 processor chips with up to 6 physical processor units for a zEC12 system and 3 or 4 active processor cores for z196. The processor cores are complemented with a Level 1 cache and an additional Level 2. The cores of the same processor chip then share a common Level 3 cache and all processor chips a common Level 4 cache on the same book. Figure 2.5 depicts the cache hierarchy on one book for the zEC12 system.

The structure for the z196 is the same but the cache sizes have changed. Table 2.1 shows the differences in cache sizes for z196 compared to zEC12. It can be observed that the L1 cache structure for zEC12 is smaller because of the higher clock frequency. On the other hand the shared cache structures on the processor chip and the book have doubled in size. When a processor changes a data item it is stored through Level 1 and 2 caches into the Level 3 cache. Data from the Level 3 cache is cast out to the Level 4 cache based on a Last Recently Used (LRU) algorithm.

The 4 level cache hierarchy becomes necessary to reduce the access of data from main memory. On System z10 a 3 level cache hierarchy was already implemented while earlier systems only contained a 2 level cache hierarchy. Introducing this hierarchy and making efficient use of it is a significant factor of system performance which we will discuss in much more detail when we take a look at work dispatching across the firmware and operating system layers of a System z.

| Cache  | z196                  | zEC12                |  |  |  |  |

|--------|-----------------------|----------------------|--|--|--|--|

| L1     | 64KB 128KB (1)        | 64KB (1)             |  |  |  |  |

|        | 128KB (2)             | 96 KB (2)            |  |  |  |  |

| L2     | 1.5 MB                | 1MB (1) and 1 MB (2) |  |  |  |  |

| L3     | 24 MB                 | 48 MB                |  |  |  |  |

| L4     | 192 MB                | 384 MB               |  |  |  |  |

| Notes: | (1) Instruction Cache |                      |  |  |  |  |

|        | (2) Data Cache        |                      |  |  |  |  |

Table 2.1.: Comparison of Cache Size for System z196 and zEC12

The processors on each chip are complemented by a Cryptographic Co-processor (CoP). The interface to the Storage Control (SC) chip supports a data transfer rate of 41.6 GB/sec for z196 and 44 GB/sec for zEC12 between memory and Level 4 cache. Finally the chip has an interface to the to the Host Channel Adapter (GX) and the memory controllers (MC). The chip area for z196 is  $512.3mm^2$ , consists of 13 layers of metal and 3.5 km of wire. The chip has 1.4 billion transistors and is made of 45nm of Silicon on Insulator (SOI) technology.

For a zEC12 the chip area is bigger and has a size of  $597mm^2$  and consists of 15 layers of metal and 7.68 km of wire. The zEC12 chip has 2.75 billion transistors and is made of 32nm of Silicon on Insulator (SOI) technology. A more detailed description of the processor structure, used processor technology and MCM layout can be found in [17].

# 2.5.1. Memory

Maximum physical memory size is directly related to the number of books in the system. Each book may contain up to 960 GB of physical memory, for a

total of 3840 GB (3.75 TB) of installed memory per system.

A System z CEC has more memory installed than ordered. Part of the physical installed memory is used to implement the redundant array of independent memory (RAIM) design, resulting on up to 768 GB of available memory per book and up to 3072 GB (3 TB) per system.

The minimum installed memory is 40 GB per book and the minimum amount of memory that can be ordered is 32 GB for small machines with up to 256 GB installed memory and up to 256 GB for large systems with 1776 to 3056 GB installed memory.

#### 2.5.2. Book

The MCM, DIMMs, together with power supplies, cooling interconnects and fanout cards are placed in a book. A z196 can have up to 4 books and up to 96 processors and the zEC12 4 books with 120 processors.

# 2.5.3. Processor Characterization

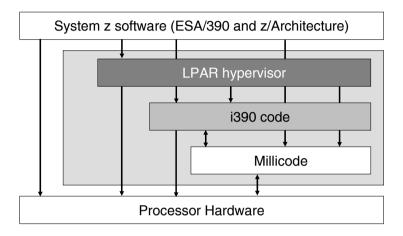

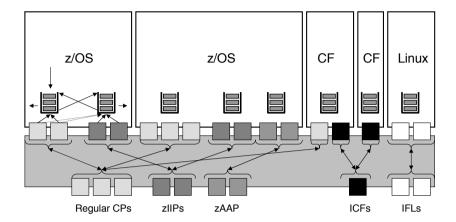

In each MCM, some PUs may be characterized for customer use. The characterized PUs may be used for general purpose to run supported operating systems (as z/OS, z/VM<sup>®</sup>, Linux on System z), or specialized to run specific workloads (as Java, XML services, IPSec, some DB2 workloads) or functions (as Coupling Facility Control Code).

The maximum number of characterized PUs depends on the System z model. Some PUs are characterized by the system as standard system assist processors (SAPs), to run the I/O processing. Also as standard, there are at least two spare PUs per system, which are used to assume the function of a failed PU. The remaining installed PUs can be characterized for customer use. The System z model nomenclature includes a number which represents this maximum number of PUs that can be characterized for customer use, as shown in table 2.2 for the zEC12.

System assist processors and spare PUs are required to run the system and to provide the redundancy against PUs errors. General purpose PUs as well as special processors are used to run customer workloads. The differentiation is made for licensing reasons and to provide an environment on System z which maintains the high investment in technology for legacy workloads as well as

| Model  | Books                                                                     | PUs | CPs      | IFLs     | zAAPs   | SAPs | Spares |  |  |  |  |

|--------|---------------------------------------------------------------------------|-----|----------|----------|---------|------|--------|--|--|--|--|

|        |                                                                           |     |          | ICFs     | zIIPs   |      |        |  |  |  |  |

| H20    | 1                                                                         | 27  | 0 to 20  | 0 to 20  | 0 to 10 | 4    | 2      |  |  |  |  |

| H43    | 2                                                                         | 54  | 0 to 43  | 0 to 43  | 0 to 21 | 8    | 2      |  |  |  |  |

| H66    | 3                                                                         | 81  | 0 to 66  | 0 to 66  | 0 to 33 | 12   | 2      |  |  |  |  |

| H89    | 4                                                                         | 108 | 0 to 89  | 0 to 89  | 0 to 44 | 16   | 2      |  |  |  |  |

| HA1    | 4                                                                         | 120 | 0 to 101 | 0 to 101 | 0 to 50 | 16   | 2      |  |  |  |  |

| Notes: | s: Number of processors for IFLs, ICFs, zIIPs, and zAAPs is for each type |     |          |          |         |      |        |  |  |  |  |

Table 2.2.: Number of Processing Units per zEC12 Model

to provide the possibility to run specialized functions on System z. Special purpose processors are:

- **IFL** Integrated Facility for Linux allows to run Linux operating system as well as z/VM on System z to a lower price point than on regular purpose processors.

- **ZAAP** System z Application Assist Processors can be exploited by the z/OS operating system to run Java code and XML services aside from general purpose processors.

- **zIIP** System z Integrated Information Processors are also exploited by z/OS to execute DB2 and IPsec services. In addition they also allow to execute the same workloads than zAAPs thus requiring installation to use only one type of assist processors if needed.

- **ICF** The Integrated Coupling Facility is an assist processor to run the coupling facility control code which is the operating system for common data connection in a Parallel Sysplex.

# 2.6. System z High Availability Design

The following section will discuss two methods for achieving high reliability and availability of System z hardware. The two components used as example are the System z processor and memory design.

# 2.6.1. Transparent CPU Sparing

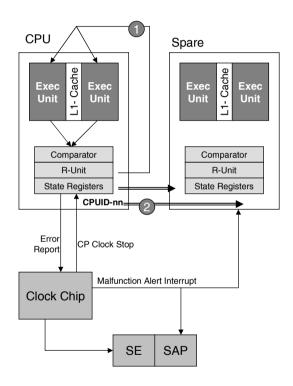

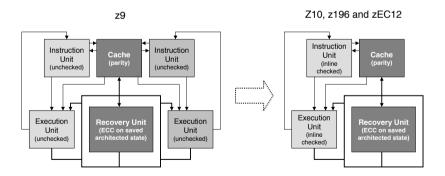

Transparent CPU Sparing is an error detection and correction mechanism which allows error detection during instruction execution and transparent error correction if spare processors have been configured to the system. The process is also called transient error recovery. It was introduced with 5th generation of CMOS processors and the original design uses two physical execution units on each core or physical PU (see figure 2.6)

Figure 2.6.: Transparent CPU Sparing on System z9

Every Physical Processing Unit (actual Core on a PU chip) contains two execution units. Each instruction is fetched concurrently from the L1 cache by both execution units and processed. The result is compared and if it is equal processing is resumed with the next instruction. If the result is not equal the instruction is executed again to find out whether a temporary error existed. If it is

still not the same an error mark is set. The R-Unit now signals the higher cache structures that the processing unit is running an error recovery process. The error recovery process resets all data store activities of the failing instruction. The CPU is now ready to get out of the configuration. The CPU is stopped and the CPU clock is stopped too. The error is signaled to the service assist processor and the service element. One possibility is now that the CPU is just configured out of the system. In this case the effect for the operating systems depend on their error recovery. A linux system for example may crash because a CPU fails. z/OS can mask the CPU and continue to process with the remaining CPUs in case more than 1 CPU is configured for the system. PR/SM can also mask the error by dispatching the logical CPs to fewer physical CPs.

Another possibility is to use a spare CPU. This requires that a spare CPU is configured to the system. The Service Assist Processor activates the spare processor and moves all register and cache contents to the new CPU. In addition the CPU id from the failing CPU is also moved to the spare CPU so that the new CPU looks identical to the failing CPU. The newly configured CPU can now immediately start to process the failing instruction again and can seamlessly and transparently replace the failing CPU.

# 2.6.2. CPU Error Detection for newer System z machines

Figure 2.7.: CPU Error Detection and Recovery on System z10, z196 and zEC12

For System z9 each CPU chip includes two cores. System z10, z196 and zEC12

the CPU chip does not contain the execution units two times. Instead an error-correcting code (ECC) protected processor state is used inside the recovery unit (RU) to employ the same reliability features than its predecessors. Thousands of error checkers (parity, residue, illegal state, hardware redundancy compares, and so on) are embedded within the microprocessors and system cache hierarchy. Every instruction that executes successfully, and without error, updates the check-pointed state. Any error associated with the execution of an instruction blocks completion, and its associated state is not check-pointed.

Upon detection of an error within the microprocessor, execution is stopped, and the core enters a sophisticated recovery sequence. All the core's non-architectural facilities are reset, and the hardened architectural facilities are corrected as needed. Next, the core retries execution, starting at the check-pointed state. In this way, the microprocessor can recover after any soft failure. However, if instruction execution continues to fail, a sparing event is initiated on a spare core, whereby millicode copies the architectural state from the failing to the spare core. Then, the failing core is removed from and the spare core is added to the system configuration, and task execution restarts on the spare core.

# 2.6.3. Redundant Array of Independent Memory

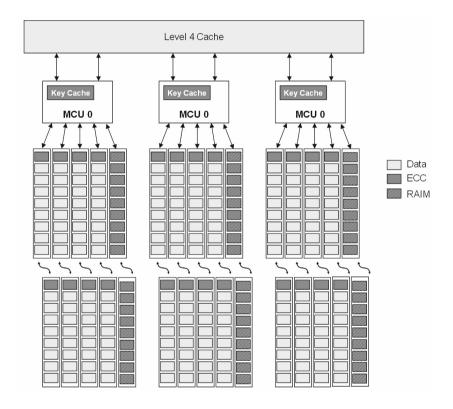

The z196 RAIM memory subsystem is a revolutionary, next-generation memory design that tolerates complete failure of any single DIMM. This design yields the highest level of memory availability of any System z generation<sup>2</sup>.

In order to implement RAIM, 'extra' memory is installed on each book. Each z196 book can contain up to 960 GB of physical memory, for a total of 3840 GB (3.75 TB) of installed memory per system (with four books). 20% of the physical installed memory is used to implement the RAIM design, resulting in up to 768 GB of available memory per book and up to 3072 GB (3 TB) per system. RAIM, and this additional memory, is provided as a standard feature of the z196 and zEC12.

Each book has from 10 to 30 DIMMs (depending on how much memory is installed). The DIMMs are connected through three memory control units (MCUs), each located on a processor unit on the book. Each MCU uses five channels, one of them for RAIM implementation, on a 4 +1 (parity) design. Each channel has one or two chained DIMMs, so a single MCU can have five

<sup>&</sup>lt;sup>1</sup>More detailed descriptions can be found in [18] and [20] for z196 and [19] for z10

<sup>&</sup>lt;sup>2</sup>The content of this section is based on [23]

or ten DIMMs. The parity of the four data DIMMs is stored and attached to the fifth memory channel. This data, along with CRC bus protection in each of the five channels allows for failures in a memory component to be detected and corrected dynamically.

Figure 2.8.: z196 Memory within an MCM

Figure 2.8 illustrates the memory layout of a fully-configured book. The RAIM design detects and recovers from DRAM, socket, memory channel, or DIMM failures. It is loosely similar to a RAID level 3 design. Five memory channels are involved in any read or write request. (A memory channel is either one DIMM, or two DIMMs chained together.) Cyclic Redundancy Check (CRC) data is used on each channel bus to detect and isolate channel errors. On top of that, RAIM ECC is used to cover the entire end-to-end path from original store to the DIMMs to the final fetch. During reads, this CRC data is verified again,

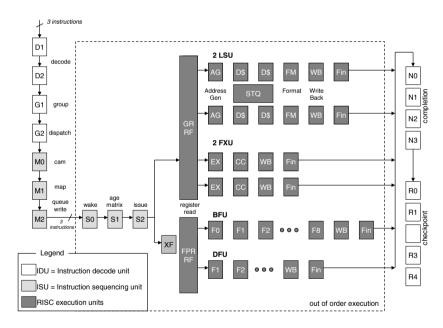

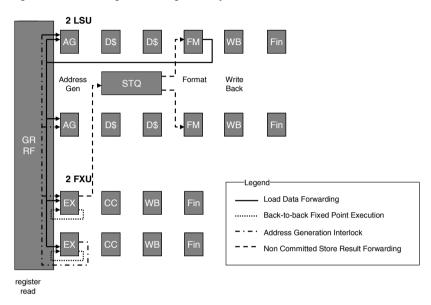

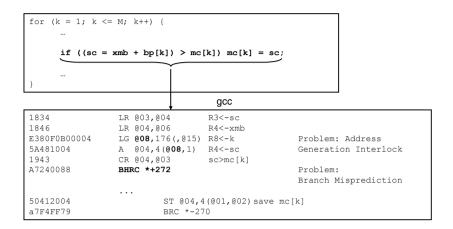

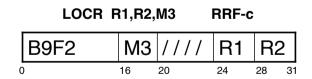

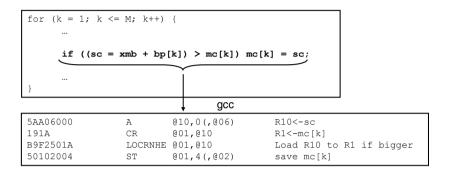

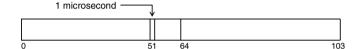

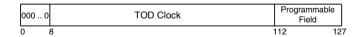

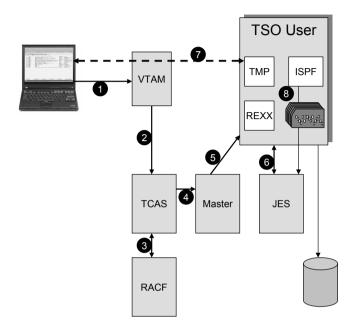

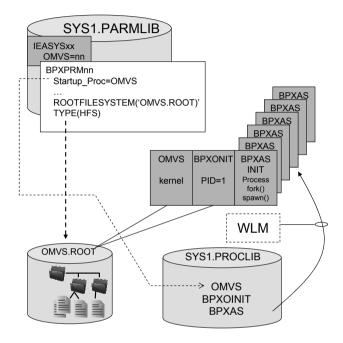

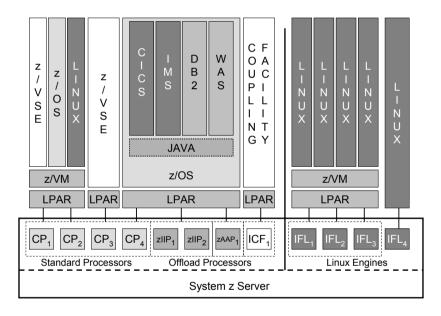

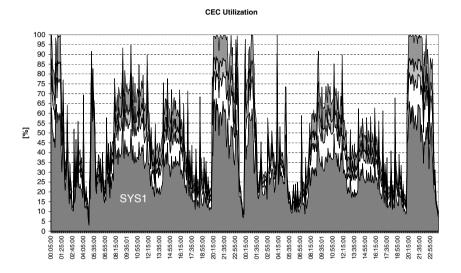

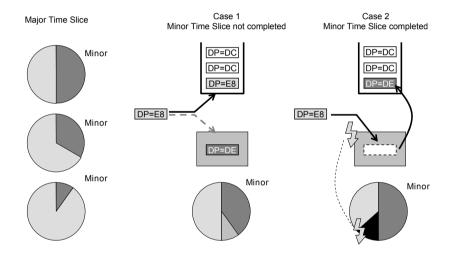

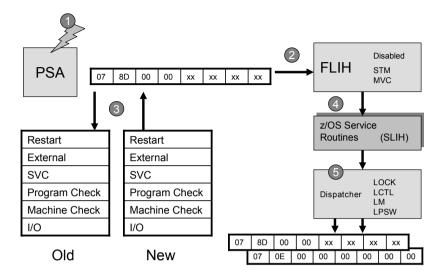

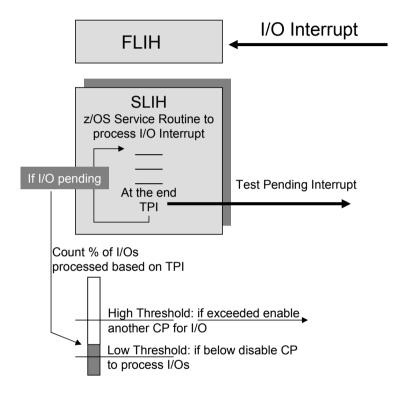

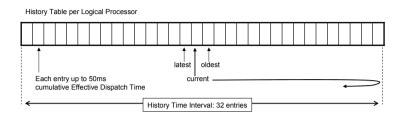

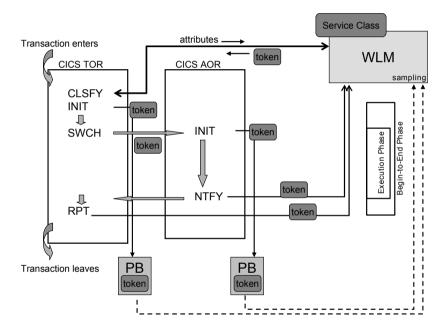

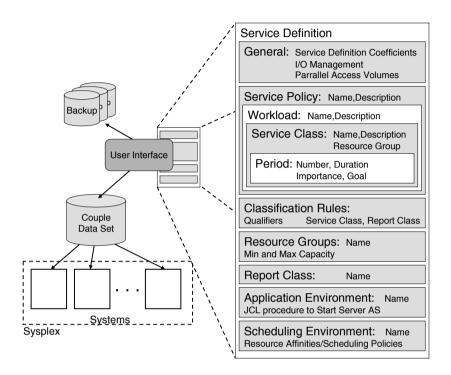

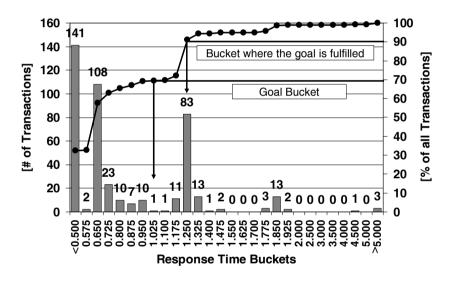

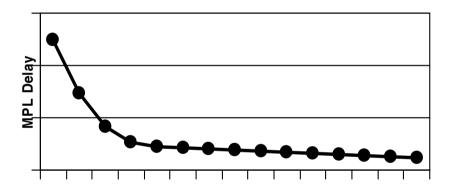

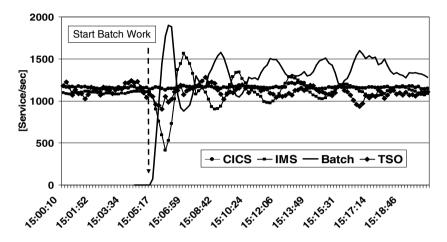

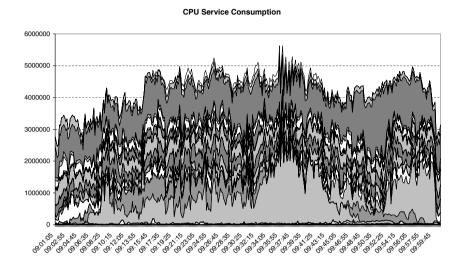

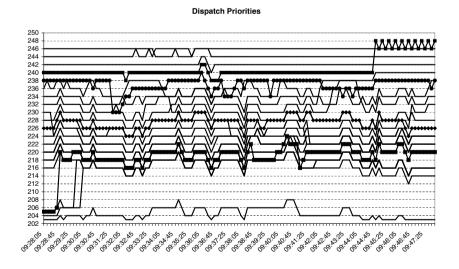

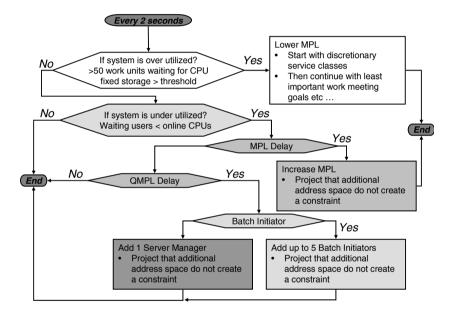

allowing for proactive error detection and correction. This allows the recovery from multiple chip failures that RAIM provides.