# Analyse und Simulation parasitärer Effekte in flüssig prozessierten organischen Transistoren

Zur Erlangung des akademischen Grades eines

### **DOKTOR-INGENIEURS**

an der Fakultät für

Elektrotechnik und Informationstechnik

des Karlsruher Instituts für Technologie (KIT)

genehmigte

# DISSERTATION

von

Stefan Hengen, M.Sc.

geb. in Darmstadt

Tag der mündlichen Prüfung: 23.02.2015

Hauptreferent: Prof. Dr. Uli Lemmer

1. Korreferent: Prof. Dr. Michael Siegel

2. Korreferent: Prof. Dr. Jürgen Giehl

### Vorwort

Diese Arbeit befasst sich mit der Analyse und Simulation unerwünschter Eigenschaften von organischen Transistoren. Solche Simulationen sind für eine Serienfertigung mit hoher Ausbeute unerlässlich, und daher von hohem Interesse auf dem Gebiet der organischen Elektronik. Die verwendeten Simulationsmodelle sind bewusst einfach gehalten, was eine Analyse der einzelnen parasitären Effekte vereinfacht. Die untersuchten Transistoren können mit den verwendeten Modellen unter Berücksichtigung der Serienstreuung sehr gut beschrieben werden. Darüber hinaus werden die weiteren parasitären Effekte als jeweils eigene Modellerweiterungen betrachtet, was das Verständnis erleichtert und die Verwendung im Schaltungssimulator vereinfacht. Die Schaltungssimulationen wurden mittels SPICE¹ durchgeführt, wobei LTspice IV als Software verwendet wurde.

Karlsruhe, im Januar 2015 Stefan Hengen Karlsruher Institut für Technologie (KIT)

i

<sup>&</sup>lt;sup>1</sup>Simulation Programm with Integrated Circuit Emphasis

#### **Publikationsliste**

#### Publikationen in referierten Zeitschriften

S. Hengen, M. Alt, G. Hernandez-Sosa, J. Giehl, U. Lemmer, N. Mechau "Modelling and simulation of gate leakage currents of solution-processed OTFT. "Organic Electronics, 2014, doi:10.1016/j.orgel.2013.12.022

#### Beiträge in Tagungsbänden

- S. Hengen, S. Pankalla, M. Glesner, J. Giehl, "Mass Characterisation of OTFT", LOPE-C, Frankfurt, 2011 ISBN: 978-3-00-034957-7

- S. Hengen, B. Vettermann, C. Haas, B. Scherwath, J. Giehl, "Modelling and Simulation of Organic Thin Film Transistor Circuits", LOPE-C, München, 2012, ISBN: 978-3-00-038122-5

- S. Hengen, B. Scherwath, C. Haas, B. Vettermann, J. Giehl, "Entwicklung von Schaltungen auf Basis organischer Elektronik", 49.

Workshop der Multi Projekt Chip Gruppe, Mannheim Februar 2013, Tagungsband 49, ISSN: 1868-9221

- S. Hengen, K. Heit, L. Lewandowski, B. Vettermann, J. Giehl, "Entwicklung eines SPICE Modells für organische Transistoren", 50.

Workshop der Multi Projekt Chip Gruppe, Konstanz Jul.2013, Tagungsband 50, ISSN: 1868-9221

#### Poster

- S. Hengen, S. Pankalla, M. Glesner, J. Giehl, "Mass Characterisation of OTFT", LOPE-C, Frankfurt 2011

- S. Hengen, B. Vettermann, C. Haas, B. Scherwath, J. Giehl, "Modelling and Simulation of Organic Thin Film Transistor Circuits", LOPE-C, München 2012

S. Hengen, B. Vettermann, J. Giehl, "Circuit Simulation for Solution Processed OTFT", Clusterkonferenz Forum Organic Electronic, Heidelberg 2013

#### Betreute Studentische Arbeiten

Diese Arbeiten wurden, im Rahmen meiner Tätigkeiten an der Hochschule Mannheim, von mir als Zweitgutachter betreut.

- R. Blanco, "Entwurf, Simulation und Messung einer analogen Schaltung mit Transistoren auf der Basis organischer Materialien.", Bachelorarbeit, Informationstechnik, 2011

- C. Haas, "Charakterisierung von Bauelementen auf der Basis organischer Materialien und Erstellung einer Auswerte- und Archivierungssoftware.", Diplomarbeit, Informationstechnik, 2011

- C. Kenmogne, "Charakterisierung des Temperaturverhaltens von Dioden auf der Basis organischer Materialien.", Bachelorarbeit, Informationstechnik, 2011

- F. Kühne, "Simulation und Modellierung von organischen Transistoren.". Bachelorarbeit. Informationstechnik, 2011

- S. Ngansso, "Aufbau eines Reihenmessplatzes zur Charakterisierung von Bauelementen auf der Basis organischer Materialien.", Bachelorarbeit, Informationstechnik, 2011

- B. Scherwath, "Entwicklung eines Messverfahrens zur Bestimmung von Kapazitäten an Feldeffekttransistoren auf Basis organischer Materialien.", Bachelorarbeit, Informationstechnik, 2011

- I. Abyanoglu, "Simulationen von gedruckten organischen Transistoren mit dem Variable Range Hopping (VRH) Modell unter LTspice IV", Diplomarbeit, Informationstechnik, 2012

- M. Bouarda, "Umsetzung eines SPICE -Modells für organische Transistoren.", Diplomarbeit, Informationstechnik, 2012

- D. S. Garcia, "Development of a Software Tool to evaluate Printed Organic Transistors.", Masterarbeit, Informationstechnik, 2012

- K. Heit, "Reihenmessungen an OTFTs.", Bachelorarbeit, 2012

- C. Kenmogne, "Leckströme in organischen Transistoren und deren Einfluss auf die Kennlinien.", Masterarbeit, Informationstechnik, 2012

- M. Mischler, "Charakterisierung von Bauelementen auf der Basis organischer Materialien und Erweiterung einer Auswerte- und Archivierungssoftware.", Bachelorarbeit, Informationstechnik, 2012

- G. Ndongmo, "Simulation von organischen Transistoren mit Hilfe der Monte-Carlo Methode in Mentor.", Bachelorarbeit, Informationstechnik, 2012

- B. Scherwath, "Charakterisierung und Modellierung des Temperaturverhaltens organischer Transistoren.", Masterarbeit, Informationstechnik, 2012

- M. Bader, "Entwicklung eines Messkopfes zur Reihenmessung von Transistoren auf der Basis gedruckter organischer Materialien (OFETs)", Bachelorarbeit, Informationstechnik, 2013

- C. Haas, "Charakterisierung des transienten Verhaltens von Transistoren auf der Basis organischer Materialien.", Masterarbeit, Informationstechnik, 2013

- L. Komguem, "Messungen und Implementierung des Sub-Threshold-Bereich-Verhaltens Organischer Transistoren (OFETs).", Bachelorarbeit, Informationstechnik, 2013

- L. Lewandowski, "Untersuchung zur Schichtdickenabhängigkeit von organischen Transistoren.", Bachelorarbeit, Informationstechnik, 2013

- L. Lewandowski, "Messung und Auswertung von Transistoren auf Basis gedruckter organischer Materialien", Masterarbeit, Informationstechnik, 2013

- K. Müller, "Untersuchung und Simulation von Inverterschaltungen aus Organischer Elektronik.", Bachelorarbeit, Informationstechnik, 2013

# Inhaltsverzeichnis

| V  | orwor  | t                                           | i  |

|----|--------|---------------------------------------------|----|

| Pι | ublika | tionsliste                                  | ii |

| 1  | Einle  | eitung                                      | 1  |

|    | 1.1    | Motivation                                  | 3  |

|    | 1.2    | Gliederung                                  | 3  |

| 2  | Grui   | ndlagen                                     | 5  |

|    | 2.1    | Feldeffekttransistor                        | 5  |

|    | 2.2    | Herleitung der Kennlinie                    | 6  |

|    | 2.3    | Modellierung                                | 7  |

|    | 2.4    | Shichman-Hodges MOS-Modell                  | 9  |

|    | 2.5    | Bändermodell                                | 11 |

|    | 2.6    | Ladungstransport in organischen Halbleitern | 12 |

|    | 2.7    | Organische Halbleiter                       | 14 |

|    | 2.8    | Metall-Halbleiter Übergang                  | 15 |

| 3  | Verv   | wendete Materialien und Herstellung         | 19 |

|    | 3.1    | Verwendete Transistoren                     | 19 |

|    | 3.2    | Herstellung                                 | 20 |

|    | 3.3    | Halbleiter                                  | 26 |

|    | 3.4    | Dielektrikum                                | 26 |

|    | 3.5    | Iniektionsschicht                           | 27 |

| 4 | Elek | trische Charakterisierung                    | 29         |

|---|------|----------------------------------------------|------------|

|   | 4.1  | TRIAX-Technik                                | 30         |

|   | 4.2  | Kontaktierung                                | 30         |

|   | 4.3  | Messungen                                    | 34         |

|   | 4.4  | Parameter Extraktion                         | ŀO         |

| 5 | Mod  | dellierung und Simulation 4                  | <b>!</b> 7 |

|   | 5.1  | SPICE                                        | <b>!</b> 7 |

|   | 5.2  | OTFT-Modellierung                            | 18         |

|   | 5.3  | Verwendetes Modell                           | ١9         |

|   | 5.4  | Modell-Erweiterungen                         | 52         |

| 6 | Gate | e-Leckströme                                 | 31         |

|   | 6.1  | Erläuterungen 6                              | 31         |

|   | 6.2  | Analyse der Gate-Leckströme 6                | 3          |

|   | 6.3  | Wirkung des Leckstromes auf die Kennlinien 6 | 35         |

|   | 6.4  | Modellierung von Gate-Leckströmen 6          | 35         |

|   | 6.5  | Extraktion der Simulationsparameter 6        | 39         |

|   | 6.6  | Wirkung auf die Kennlinien                   | 71         |

| 7 | Vari | ation der Schichtdicken                      | <b>'</b> 5 |

|   | 7.1  | Erläuterungen                                | 75         |

|   | 7.2  | Halbleiterdicke                              | 76         |

|   | 7.3  | Halbleiterdicke des Einzeltransistors        | 33         |

|   | 7.4  | Dielektrikumsdicke                           | 33         |

| 8 | Proz | zessvariation                                | 7          |

|   | 8.1  | Prozessstatistik Transistor                  | 97         |

|   | 8.2  | Prozessstatistik Inverter                    | 9          |

|   | 8.3  | Modellierung                                 | 0          |

|   | 8.4  | Schaltungssimulation                         | 0          |

|     | 8.5   | Fazit Prozessvariation               | 02  |

|-----|-------|--------------------------------------|-----|

| 9   | Tem   | peratureffekte                       | 103 |

|     | 9.1   | Erläuterungen                        | 03  |

|     | 9.2   | Ladungsträgerbeweglichkeit           | 04  |

|     | 9.3   | Schwellspannung                      | 09  |

|     | 9.4   | Simulation eines Einzeltransistors   | 12  |

|     | 9.5   | Simulation eines Ringoszillators     | 13  |

|     | 9.6   | Fazit Temperatursimulation           | 20  |

|     |       | C                                    | 121 |

| 11  | Aust  | blick                                | 123 |

| Α   | Anha  | ang                                  | 125 |

| В   | Forn  | nelzeichen und Abkürzungsverzeichnis | 133 |

| Lit | eratu | urverzeichnis                        | 135 |

| Αb  | bildu | ingsverzeichnis                      | 151 |

| Та  | belle | nverzeichnis                         | 161 |

| Da  | nksa  | gung                                 | 163 |

# 1. Einleitung

Organische Elektronik bezeichnet elektronische Bauelemente und Schaltungen, welche zum Teil oder komplett aus organischen<sup>1</sup> Materialien hergestellt werden. Im Gegensatz hierzu basieren herkömmliche elektronische Schaltungen auf anorganischen Materialien, meistens Silizium, seltener Germanium, Gallium-Arsenid und anderen Materialien [1]. Während anorganische Halbleiter seit vielen Jahrzehnten untersucht und verwendet werden, ist die Entwicklung der organischen Elektronik noch relativ jung. Halbleiter sind seit 1874 [2] bekannt, und werden seit Anfang des 20. Jahrhunderts kommerziell verwendet [3, 4]. Der erste organische Transistor wurde jedoch erst 1986 veröffentlicht [5, 6]. Steigendes Interesse erhielt dieses Forschungsgebiet mit dem Nobelpreis für Chemie im Jahr 2000 für Heeger, MacDiarmid und Shirakawa [7, 8, 9, 10]. Neben organischen Transistoren (OTFTs<sup>2</sup>) wird organische Elektronik unter anderem noch für Sensoren, organische Leuchtdioden (OLEDs) und organische Photovoltaik (OPV) verwendet. Generell haben organische Halbleiter eine geringere Leistungsfähigkeit als z. B. Silizium [11, 1]. Diesem Manko stehen jedoch große Vorteile gegenüber, so lassen sich viele organische Materialien in Lösemitteln lösen und flüssig verarbeiten, außerdem können elektrisch leitfähige Strukturen auf flexiblen Trägermaterialien aufgebracht werden, was mit herkömmlicher Technologie nicht ohne weiteres möglich ist [12, 13, 14]. So sind z. B. schon transparente OLEDs und flexible Displays präsentiert worden, welche beide völlig neuartige Anwendungen

<sup>&</sup>lt;sup>1</sup>organisch = aus Kohlenstoff-Verbindungen aufgebaut

<sup>&</sup>lt;sup>2</sup>OTFT = Organic Thin Film Transistor = Organischer Dünnschicht Transistor

eröffnen [15, 16]. Auch ein flexibler Mikroprozessor aus 4000 Transistoren wurde bereits 2011 von K. Myny et al. demonstriert [17].

Das Verarbeiten von gelösten und damit flüssigen Materialien führt zu einer drastischen Vereinfachung des Herstellungsprozesses. So lassen sich die einzelnen Schichten aus der jeweiligen Lösung heraus z. B. aufschleudern<sup>3</sup> oder drucken und müssen nicht zwingend in aufwendigen Vakuumprozessen verarbeitet werden [18]. Das Drucken als mögliche Herstellungstechnologie ist von besonders großem Interesse, weil neben der geringeren Kosten auch größere Flächen mit wesentlich höherer Geschwindigkeit prozessiert werden können, was insbesondere für OLEDs und OPV von großem Nutzen ist [19]. Aktuell gängige Silizium-Wafer haben einen Durchmesser von 300 mm und werden einzeln oder in kleinen Chargen prozessiert. Dem gegenüber stehen Druckmaschinen, welche auf einer Breite von über 2m kontinuierlich drucken können. Dem deutlich höheren Durchsatz der Drucktechnologie stehen jedoch wesentlich geringere Genauigkeiten gegenüber, während bei aktuellen integrierten Schaltkreisen Strukturgrößen im Nanometer-Bereich verwendet werden, so sind es bei Druckmaschinen µm bis mm. Ebenso sind die resultierenden Schichten in der klassischen Halbleiterherstellung wesentlich präziser, reiner und homogener als solche, die aus Lösungen heraus produziert werden. Daher sind die Bauelemente, welche aus flüssig prozessierten organischen Materialien hergestellt werden, in ihren Dimensionen und der Leistungsfähigkeit mit Siliziumchips nicht vergleichbar. Aktuell sind durch die wesentlich kleineren Strukturen auch die Herstellungskosten pro Transistor in der Silizium Technologie deutlich geringer als bei organischen Materialien; pro prozessierter Fläche jedoch, sind organische Materialien in der Verarbeitung günstiger. Die geschätzten Kosten betragen \$ 3 pro cm<sup>2</sup> bei klassischer Silizium Fertigung und \$ 0,1 pro  $m^2$  im Offset Druck [20]. Um eine Produktion im großen Maßstab zu ermöglichen, müssen zum einen die Fertigungsmethoden weiter verbessert werden. Es müssen jedoch auch Modelle zur Schaltungssi-

<sup>&</sup>lt;sup>3</sup>Aufschleudern = Spincoating / Rotationsbeschichten

mulation entwickelt werden, welche die Bauteileigenschaften der organischen Elektronik hinreichend genau beschreiben. Dies gilt sowohl für das einfache elektrische Verhalten, als auch für Serienstreuung, Alterung und die Auswirkung von Umwelteinflüssen wie z.B. Temperaturänderung.

#### 1.1. Motivation

Für die Simulation von OTFTs sind bereits verschiedene Modelle entwickelt worden, welche das elektrische Verhalten beschreiben [21, 22, 23, 24]. Diese Modelle beschränken sich jedoch auf die Simulation der idealen Materialeigenschaften; parasitäre Effekte werden üblicherweise nicht im Modell berücksichtigt. Für die Serienfertigung von integrierten Schaltungen auf Basis organischer Materialien müssen jedoch auch unerwünschte Effekte berücksichtigt werden. Hierzu müssen diese Effekte identifiziert und untersucht werden, anschließend sind Modelle zu entwickeln um die Effekte simulieren zu können.

### 1.2. Gliederung

Kapitel 1 gibt einen grundlegenden Überblick über das Themengebiet und die Grundlagen organischer Transistoren. Hier werden grundlegende Sachverhalte erläutert, Halbleiter und Transistorfunktion beschrieben. Kapitel 3 beschreibt den Aufbau, die verwendeten Materialien und die Herstellung der untersuchten organischen Transistoren. In Kapitel 4 werden die durchgeführten Messungen und die Methoden zur Extraktion der einzelnen Parameter erläutert. Im Kapitel 5 werden das verwendete OTFT-Modell, die verwendete Simulationsumgebung und erste Modellerweiterungen beschrieben. Im Kapitel 6 wird eine Modellerweiterung zur Simulation von parasitären Gate-Leckströmen vorgestellt. Das Kapitel 7 zeigt die Auswirkungen verschiedener Schichtdicken von Halbleiter und Dielektrikum auf die Parameter der produzierten OTFTs. Das Kapitel 8 beschäftigt sich mit

### 1. Einleitung

der Analyse und Simulation von Schwankungen der Prozessparameter. In Kapitel 9 wird der Einfluss von Temperaturänderungen auf das Verhalten von OTFTs untersucht und ein Modell entwickelt, mit dem das Temperaturverhalten simuliert werden kann.

# 2. Grundlagen

Dieses Kapitel gibt einen grundlegenden Überblick über die prinzipielle Funktionsweise von Feldeffekttransistoren. Es wird die Entstehung der Kennlinien und das MOS-Modell nach Shichman-Hodges erklärt. Zum besseren Verständnis des Ladungsträgertransportes in organischen Materialien wird das Bändermodell und der Metall-Halbleiter Übergang erläutert. In einem Überblick über organische Halbleiter werden die verschiedenen Gruppen und die aktuell erreichten Ladungsträgerbeweglichkeiten verglichen.

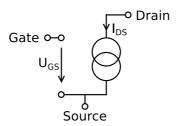

#### 2.1. Feldeffekttransistor

Die in dieser Arbeit untersuchten OTFTs sind Dünnschichttransistoren, welche von der Funktionsweise her wiederum Feldeffekttransistoren sind. In Feldeffekttransistoren (FET) wird der Stromfluss zwischen zwei Elektroden (Drain und Source) durch das elektrische Feld gesteuert, welches auf den dazwischen liegenden Halbleiter einwirkt. In der einfachen Modellvorstellung liegt das Feld orthogonal zur Richtung des späteren Stromflusses. Das äußere elektrische Feld übt eine Kraft auf die Ladungsträger im Halbleiter aus, hierdurch können Ladungsträger angesammelt oder verdrängt werden, wodurch im Halbleiter ein leitfähiger Bereich entsteht, welcher Kanal genannt wird [1, 25].

In kristallinen FETs ist der Halbleiter dotiert, so dass ein Ungleichgewicht an Ladungsträgern entsteht, die Mehrheit wird Majoritäts-, die Minderheit Minoritätsladungsträger genannt. Üblicherweise wird der Kanal hier durch Verdrängen der Majoritätsladungsträger und Inversion des

Kanalgebietes gebildet. So sind im Kanalgebiet, bei ausgebildetem Kanal, die Minoritätsladungsträger in der Überzahl, dieser Zustand wird als Inversion bezeichnet. OTFTs werden üblicherweise in Akkumulation betrieben, hierbei werden die Majoritätsladungsträger im Kanalgebiet vermehrt angesammelt und so die Leitfähigkeit gesteuert. Der Begriff Dünnschichttransistoren bezeichnet Transistoren, welche auf einem Trägermaterial aufgebaut werden – im Gegensatz hierzu werden konventionelle Transistoren in das Halbleitermaterial eingebracht. Dünnschicht kann ebenso auf die Schichtdicke von Halbleiter und Isolator bezogen werden, diese reichen von einigen nm zu wenigen  $\mu m$ .

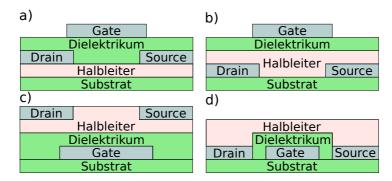

Der prinzipielle Aufbau des Dünnschichttransistors ist folgender: Auf dem isolierenden Trägermaterial befinden sich zwei leitende Elektroden, welche Drain und Source genannt werden. Zwischen den Elektroden liegt der Halbleiter, über dem gesamten Aufbau eine Isolationsschicht (Dielektrikum), auf dieser Schicht sitzt die Gateelektrode, welche idealerweise nur über dem Bereich zwischen Drain und Source positioniert wird. Es gibt prinzipiell vier verschiedene Varianten für Dünnschichttransistoren. Sowohl das Gate als auch Drain und Source können auf dem Substrat liegen (Bottom-Gate / -Contact) oder erst als letzte Schicht im Herstellungsprozess aufgebracht werden (Top-Gate /-Contact). Abbildung 2.1 zeigt die vier Transistortypen schematisch. Die in dieser Arbeit untersuchten Transistoren haben ausschließlich Bottom-Contact, Top-Gate Topologie.

# 2.2. Herleitung der Kennlinie

Wird zwischen Source und Gate eine Spannung angelegt, so ergibt sich ein elektrisches Feld zwischen diesen beiden Kontakten. Dieses Feld übt eine Kraft auf die Ladungsträger aus, welche sich im Halbleiter befinden. Ist die Gate-Spannung positiv, so sammeln sich Löcher auf der Gateelektrode. Dieser positiven Ladung steht eine negative Spiegelladung im Halbleiter gegenüber. Bei positiver Gatespannung sammeln sich im Halbleiter unter-

Bild 2.1.: Schematische Darstellung der verschiedenen Transistortypen: a) Top-Contact, Top-Gate. b) Bottom-Contact, Top-Gate. c) Top-Contact, Bottom-Gate. d) Bottom-Contact, Bottom-Gate.

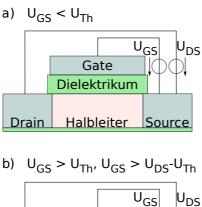

halb der Gateelektrode negative Elektronen. Abbildung 2.2 zeigt die Bildung des Kanals in verschiedenen Betriebsbereichen. Durch unterschiedliche Austrittsarbeiten oder ortsfeste Ladungsträger kann sich die Ausbildung des Kanals zu positiven oder negativen Schwellspannungen  $(U_{Th})$  verschieben. Ist bereits bei  $U_G=0V$  ein Kanal ausgebildet, so wird der Transistor als selbstleitend, anderenfalls als selbstsperrend bezeichnet.

Die Beweglichkeit der Ladungsträger wird durch den Parameter  $\mu$  (Ladungsträgerbeweglichkeit) beschrieben. Je größer dieser Wert, desto weniger wird der Transport der Ladungsträger gestört und desto mehr Strom kann fließen. Der Wert von  $\mu$  wird daher auch zum Vergleich verschiedener Halbleiter verwendet, je höher der Wert, desto leistungsfähiger ist das Material.

# 2.3. Modellierung

Modelle beschreiben, wie sich Ausgangsgrößen eines Systems in Abhängigkeit von Eingangsgrößen verhalten. Diese Modelle können rein numerischer Natur sein oder auf physikalischen Grundlagen basieren. Numeri-

Bild 2.2.: Ausbildung des leitfähigen Kanals in einem OTFT. a) Off-Bereich, kein Kanal gebildet. b) Linearer Bereich, der Kanal ist komplett gebildet. c) Sättigungsbereich, der Kanal ist ausgebildet, wird jedoch am drainseitigen Ende abgeschnürt, da  $U_{GS} < U_{DS} - U_{Th}$ .

sche Modelle haben nicht zwingend einen physikalischen Bezug zur Realität, können jedoch ein System durch Gleichungen oder Wertetabellen beschreiben, welche aus Messdaten extrahiert werden. Physikalische Modelle hingegen basieren auf einer Beschreibung des Systems nach physikalischen

Gesetzmäßigkeiten und Regeln. Das Simulationsergebnis wird durch physikalische Modelle nicht zwangsläufig genauer, hat jedoch einen direkten Bezug zum realen System. Somit können auch Änderungen am Aufbau des Systems simuliert werden, was mit rein mathematischen Modellen nicht unbedingt möglich ist. Neben der Simulation von Schaltungen aus OTFTs, werden parallel auch die Bauteile weiter erforscht und verbessert. Daher werden in dieser Arbeit Modelle verwendet, die das Verhalten von OTFTs nicht nur beschreiben, sondern auch einen physikalischen Hintergrund haben. Hierdurch wird das Verständnis für die Bauteile und den Einfluss von Prozessveränderungen auf einzelne Parameter verbessert.

### 2.4. Shichman-Hodges MOS-Modell

Das sogenannte einfache MOS-Modell nach Shichman-Hodges beschreibt den Strom in kristallinen Feldeffekttransistoren [26]. In Grundzügen lassen sich mit diesem relativ einfachen Modell auch Transistoren aus organischen Materialien beschreiben, weshalb es z. B. auch zur Parameterextraktion verwendet wird. Das Modell beschreibt den Stromfluss zwischen Drain und Source ( $I_D$ ), in Abhängigkeit der angelegten Spannungen  $U_{GS}$  und  $U_{DS}$ . Der Betrieb des Transistors wird grundsätzlich in drei Betriebsbereiche unterteilt, diese sind: Sperrbereich, Sättigungsbereich und Widerstandsbereich (vgl. Abb. 2.2).

## 2.4.1. Sperrbereich

Die Bedingung für den Sperrbereich lautet:  $U_{GS} < U_{Th}$ . In diesem Bereich hat sich noch kein Kanal ausgebildet. Im einfachen MOS-Modell wird der Strom mit 0A modelliert. In der Realität fließt jedoch ein geringer Strom, der mehrere Größenordnungen kleiner ist als der maximale Betriebsstrom. In einfachen Modellen kann der Off-Bereich durch einen Widerstand zwischen Drain und Source simuliert werden. Bessere Simulationsergebnisse liefert jedoch die Beschreibung durch einen exponentiellen Verlauf des

Stromes und die weitere Aufteilung des Sperrbereiches in Sub-threshold und Off-Bereich.

### 2.4.2. Sättigungsbereich

Die Bedingungen für den Sättigungsbereich lauten:  $U_{GS} > U_{Th}$  und  $U_{GS} - U_{Th} < U_{DS}$ . Der Drainstrom im Sättigungsbereich wird durch Gleichung (2.1) beschrieben. In diesem Bereich verhält sich der Kanalstrom quadratisch zur angelegten Gatespannung. Der Kanal wird am drainseitigen Ende abgeschnürt, was bedeutet, dass die Ladungsträger sich mit der maximal möglichen Geschwindigkeit bewegen. Eine weitere Erhöhung der Drainspannung bewirkt keinen höheren Strom im Kanal. Um einen Kanal auszubilden muss die effektive Spannung zwischen Gate ( $U_{Geff} = U_G - U_{Th}$ ) und Kanal mehr als 0V betragen. Die Spannung auf der Gate-Elektrode ist näherungsweise konstant, die Spannung im Kanal ist jedoch ortsabhängig.

Ist  $U_{Geff(x)}$ , nicht größer als die ortsabhängige Spannung im Kanal, kann sich kein vollwertiger Kanal ausbilden und es kommt zur Abschnürung. Erst bei  $U_{Geff} > U_{DS}$  wird auf der gesamten Länge der Kanal vollständig ausgebildet, dann befindet sich der Transistor jedoch nicht mehr im Sättigungs- sondern im linearen Bereich.

$$I_D = \frac{1}{2} \frac{W}{L} \mu C_{Ox} (U_{GS} - U_{Th})^2$$

(2.1)

#### 2.4.3. Linearer Bereich

Die Bedingungen für den linearen Bereich lauten:  $U_{GS} > U_{Th}$  und  $U_{GS} - U_{Th} > U_{DS}$ . Der Kanal ist zwischen Drain und Source voll ausgebildet, der Kanalstrom verhält sich in diesem Bereich linear zur Gatespannung. Der Drainstrom wird durch Gleichung (2.2) beschrieben.

$$I_{D} = \frac{W}{L} \mu C_{Ox} \left( U_{GS} - U_{Th} - \frac{U_{DS}}{2} \right) U_{DS}$$

(2.2)

#### 2.5. Bändermodell

Zum besseren Verständnis des Ladungstransports wird als Modell für die elektrische Leitfähigkeit das Bändermodell herangezogen. Ausschlaggebend für die elektrische Leitfähigkeit eines Materials ist eine genügend große Anzahl freier Elektronen. Freie Elektronen sind solche, die nicht in Bindungen mit anderen Atomen verwendet werden und sich daher frei bewegen können. Im Bändermodell besetzen die freien Elektronen das Leitungsband, die Valenzelektronen besetzen das Valenzband. Der energetische Abstand zwischen Leitungs- und Valenzband wird als Bandlücke bezeichnet. Dieser Wert besagt, welche Energie zugeführt werden muss um ein Elektron vom Valenzband in das Leitungsband zu befördern [27]. Die Höhe der Bandlücke wird üblicherweise in Elektronenvolt (eV) angegeben, wobei ein eV ca.  $1,602 \cdot 10^{-19} J$  entspricht.

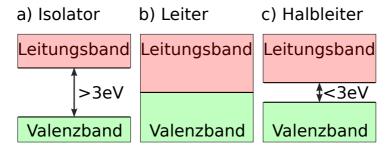

Abbildung 2.3 zeigt schematisch das Bändermodell für Isolator, Leiter und Halbleiter. Bei Isolatoren ist der Abstand zwischen Valenz- und Leitungsband so groß ( $\gtrsim 3 \, eV$ ), dass bei Raumtemperatur keine Ladungsträger durch thermische Anregung in das Leitungsband gelangen können. Bei Leitern liegen Valenz- und Leitungsband entweder direkt übereinander oder überlappen sich, so dass das Leitungsband bei Raumtemperatur stets besetzt ist. Halbleiter haben eine Bandlücke, diese ist jedoch kleiner als 3 eV [28]. Dieser Wert ergibt sich aus folgender Definition: Halbleiter sind Materialien, bei denen bei Raumtemperatur die Energie der thermischen Anregung ausreicht, um Elektronen in das Leitungsband zu befördern. So sind Halbleiter bei T = 0 K Isolatoren und leiten mit zunehmender Temperatur besser. Typische Werte für die Bandlücke bei Raumtemperatur sind: Kristallines Silizium (Si) - 1,12eV, Gallium-Arsenid (GaAs) - 1,42eV [1]. Bei Halbleitern lässt sich die Besetzung des Leitungsbandes und damit die Leitfähigkeit, durch äußere Einflüsse steuern. Diese Einflüsse können z. B. die Temperatur, die Beleuchtungsstärke oder ein äußeres elektrisches Feld sein [29]. Der letzte Fall wird in Feldeffekttransistoren ausgenutzt, hier steuert ein von außen angelegtes elektrisches Feld die Leitfähigkeit des Halbleiters.

Bild 2.3.: Darstellung von Valenzband und Leitungsband bei verschiedenen Materialien. a) Isolator, hier ist die Energiedifferenz größer als 3 eV, b) Leiter, die Bänder liegen direkt aneinander oder überlappen sich. c) Halbleiter, die Bänder berühren sich nicht, der Abstand beträgt jedoch weniger als 3 eV.

### 2.6. Ladungstransport in organischen Halbleitern

Der Ladungstransport, wie ihn das Bändermodell (vgl. Abschnitt 2.5) beschreibt, gilt nur für kristalline Halbleiter, welche ein weitläufig geordnetes Kristallgitter besitzen. Organische Halbleiter liegen jedoch meistens nicht als Einkristall, sondern als polykristalline<sup>1</sup> oder amorphe<sup>2</sup> Schicht vor. Während Einkristalle eine hohe Ordnung aufweisen, werden amorphe und polykristalline Strukturen als ungeordnet angesehen.

Die verwendeten Modelle werden zu großen Teilen zur Beschreibung von amorphem Silizium verwendet und für organische Elektronik ggf. modifiziert. Amorphes Silizium wird z.B. für Solarzellen und Transistoren zur Ansteuerung von LCDs<sup>3</sup>s verwendet. Es ist günstiger zu prozessieren und

<sup>&</sup>lt;sup>1</sup>Polykristallin = einzelne kristalline Gebiete unterschiedlicher Ausrichtung

<sup>&</sup>lt;sup>2</sup>Amorph = keine ausgedehnte kristalline Struktur vorhanden, die Moleküle haben nur eine Nahordnung

<sup>&</sup>lt;sup>3</sup>LCD = Liquid Crystal Display = Flüssigkristall Anzeige

kann bei niedrigeren Temperaturen abgeschieden werden als kristallines Silizium.

Gegenüber dem Bandtransport, welcher den Ladungsträgern hohe Beweglichkeiten ermöglicht, ist Ladungstransport in ungeordneten Systemen durch das Springen zwischen unterschiedlichen Energieniveaus dominiert und wird als Hopping<sup>4</sup>-Transport bezeichnet. Bei dieser Art des Ladungstransportes können sich die Ladungsträger nicht frei bewegen, sondern springen zwischen Gebieten hoher Aufenthaltswahrscheinlichkeit. Da diese Gebiete unterschiedliche Energieniveaus besitzen ist diese Art des Transports üblicherweise thermisch angeregt. Für niedrige Temperaturen ergeben sich nur geringe Sprungenergien, der Transport kann nur zu energetisch günstigeren bzw. räumlich naheliegenden Gebieten erfolgen. Bei höheren Temperaturen können die Sprünge auch über größere Energiedifferenzen erfolgen. Die Mechanismen werden je nach Temperaturbereich Nearest-Neighbour Hopping (NNH) oder Variable Range Hopping (VRH) genannt [30, 31]. Neben der thermischen Anregung ist üblicherweise auch eine Abhängigkeit des von außen angelegten elektrischen Feldes zu messen, diese äußert sich bei Transistoren in einer Abhängigkeit der Ladungsträgerbeweglichkeit von der Gatespannung.

Zur Unterscheidung zwischen Bänder- und Hoppingtransport werden folgende Kriterien untersucht: Eine Temperaturabhängigkeit der Ladungsträgerbeweglichkeit in der Form von  $\mu \propto T^{-\frac{3}{2}}$  und eine Richtungsabhängigkeit der Ladungsträgerbeweglichkeit von der Orientierung der Kristallstruktur. Beide Anzeichen können an organischen Einkristallen, nicht jedoch in ungeordneten Systemen nachgewiesen werden [30, 32].

Bei organischen Transistoren liegt die Beweglichkeit in der Größenordnung von  $0.01\,cm^2V^{-1}s^{-1}$  bis  $10\,cm^2V^{-1}s^{-1}$  [33]. Für Überschlagsrechnungen bei Silizium Transistoren werden üblicherweise  $300\,cm^2V^{-1}s^{-1}$  für n-Kanal Transistoren und ca.  $100\,cm^2V^{-1}s^{-1}$  für p-Kanal Transistoren verwendet. Die wahren Werte hängen jedoch sehr stark von der Do-

<sup>&</sup>lt;sup>4</sup>Hopping (engl.) = springen

tierungskonzentration und von der Feldstärke ab und liegen zwischen ca.  $200\,cm^2V^{-1}s^{-1}$  bis  $800\,cm^2V^{-1}s^{-1}$  für Elektronen und  $60\,cm^2V^{-1}s^{-1}$  bis  $200\,cm^2V^{-1}s^{-1}$  für Löcher [1]. Bei reinem Silizium betragen die Werte  $1350\,cm^2V^{-1}s^{-1}$  für Elektronen und  $500\,cm^2V^{-1}s^{-1}$  für Löcher [25]. Alle Werte gelten für Raumtemperatur bzw.  $300\,K$ .

### 2.7. Organische Halbleiter

Organische Halbleiter werden üblicherweise in zwei Untergruppen eingeteilt, Polymere und sogenannte kleine Moleküle (small molecules). Während Moleküle aus mehreren Atomen bestehen, sind Polymere wiederum aus mehreren Molekülen aufgebaut und daher deutlich größer. Von beiden Gruppen gibt es sowohl p- als auch n-Leiter, wobei p-leitende Materialien üblicherweise eine höhere Ladungsträgerbeweglichkeit aufweisen als n-leitende [34]. Die resultierenden Schichten sind bei den kleinen Molekülen üblicherweise polykristallin, während Polymere meistens amorphe Schichten bilden. Dem gegenüber steht die klassische Halbleitertechnik, welche große Einkristalle verwendet, weshalb hier auch der Begriff kristalline Materialien üblich ist. Es gibt jedoch auch Ansätze, OTFTs aus Einkristallen herzustellen [35]. Für die Flüssigprozessierung werden meistens Polymere verwendet, da diese besser aus einer Lösung heraus verarbeitet werden können. Kleine Moleküle erreichen jedoch höhere Beweglichkeiten und versprechen daher leistungsfähigere Bauteile [33].

Aktuell erreichte Werte der Ladungsträgerbeweglichkeiten in OTFTs sind z. B.  $10,7\,cm^2V^{-1}s^{-1}$  für Flüssig- und  $15\,cm^2V^{-1}s^{-1}$  für Vakuumprozesse [11, 38, 39].In kristallinen organischen Halbleitern werden Beweglichkeiten von bis zu  $40\,cm^2V^{-1}s^{-1}$  ermittelt [40]. Ein weit verbreiteter organischer Halbleiter aus der Gruppe der kleinen Moleküle ist Pentacen. Dieses Material hat Ladungsträgerbeweglichkeiten von über  $20\,cm^2V^{-1}s^{-1}$  und ist damit vergleichbar mit amorphem Silizium [41].Reines Pentacen ist sehr schlecht löslich und eignet sich somit nicht für die Flüssigprozes-

Bild 2.4.: Schematische Darstellung der Moleküle von a) Pentacen und b) TIPS-Pentacen. Bei TIPS-Pentacen werden zusätzliche Seitengruppen zur Erhöhung der Löslichkeit verwendet [36].

sierung, jedoch gibt es Derivate bei denen die Löslichkeit durch zusätzliche Seitengruppen verbessert wird. Der bekannteste Vertreter ist 6,13-bis(triisopropyl-silylethynyl)-Pentacen (TIPS-Pentacen), welches flüssig prozessiert ebenfalls Beweglichkeiten von über  $1\,cm^2V^{-1}s^{-1}$  erreicht [42, 43]. Aus der Gruppe der Polymere werden z. B. Poly[bis(4-phenyl)(2,4,6-trimethylphenyl)amine] (PTAA) und Poly(3-hexylthiophen-2,5-diyl) (P3HT) häufig verwendet, die einzelnen Moleküle sind in Abb. 2.5 dargestellt. PTAA erreichet Ladungsträgerbeweglichkeiten von ca.  $0,005\,cm^2V^{-1}s^{-1}$ , und P3HT ca.  $0,01\,cm^2V^{-1}s^{-1}$  [44, 45].

# 2.8. Metall-Halbleiter Übergang

Beim Kontakt zwischen Leiter und einem Halbleiter mit unterschiedlichen Austrittsarbeiten, wandern Elektronen von höheren zu niedrigeren Ener-

Bild 2.5.: Schematische Darstellung der Moleküle von a) Poly(3-hexylthiophen-2,5-diyl) (P3HT) und b) Poly[bis(4-phenyl)(2,4,6-trimethylphenyl)amine] (PTAA). [37].

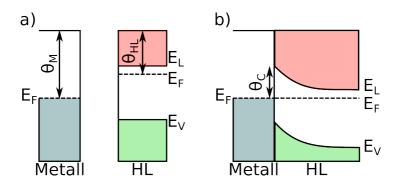

gieniveaus. Hierbei werden die Ferminiveaus von Leiter und Halbleiter angeglichen, woraus eine Bandverbiegung im Halbleiter resultiert. Abbildung 2.6a zeigt Metall und Halbleiter im Ausgangszustand, Das Ferminiveau des Halbleiters liegt oberhalb des Metalls. Nach Kontakt (Abb. 2.6b) hat ein Ladungstransport vom Halbleiter zum Metall stattgefunden, wodurch im n-Halbleiter Löcher zurückgeblieben sind, hierdurch werden die Bandkanten verbogen. Durch dieses Verbiegen entsteht eine Potentialbarriere ( $\Phi_C$ ), die beim Stromfluss vom Metall in den Halbleiter überwunden werden muss [46].

Der Übergang zwischen Drain- bzw. Sourceelektrode und Halbleiter ist bei Si-Transistoren üblicherweise ohmsch ausgeführt. Das bedeutet, dass das Ferminiveau der Elektrode oberhalb des Leitungsbandminimums des Halbleiters liegt [1]. Dieser Zustand kann jedoch in OTFTs nicht immer erreicht werden. Die resultierende Potentialbarriere zwischen der Elektrode und dem HOMO bzw. LUMO des Halbleiters verursacht einen Spannungsabfall welcher die wirksame Drain-Source Spannung verringert [47]. Dieser Effekt wird im allgemeinen als Kontaktwiderstand ( $R_C$ ) bezeichnet. Bei kurzen Kanallängen kann der Kontaktwiderstand das Verhalten des Transistors sogar dominieren [48, 49].

Bild 2.6.: Bändermodell für den Metall-Halbleiter Übergang. a) Zeigt Metall und Halbleiter ohne leitfähige Verbindung,  $\Phi_M$  bezeichnet die Austrittsarbeit des Metalls,  $\Phi_{HL}$  die des Halbleiters. b) Zeigt Metall und Halbleiter im direkten Kontakt, die Fermieniveaus  $(E_F)$  haben sich angeglichen, Valenz- $(E_V)$  und Leitungsband  $(E_L)$  werden am Kontakt verbogen. Die Barrierehöhe  $\Phi_C$  ist die Differenz der Austrittsarbeiten von Metall und Halbleiter [46].

Obwohl es sich um einen nicht-ohmschen Widerstand handelt, ist es üblich den Wert des Kontaktwiderstandes in Ohm ( $\Omega$ ) bzw. normiert auf die verwendete Weite in  $\Omega$ cm anzugeben. Insbesondere ist zu beachten, dass die angegebenen Werte stark von der Gatespannung abhängen können [50]. Daher muss für vergleichende Messungen der Kontaktwiderstand immer am gleichen Arbeitspunkt extrahiert werden. Es gibt verschiedene Ansätze den Kontaktwiderstand zu minimieren, so hat die Wahl der Elektrodenmaterialien durch die Austrittsarbeit direkten Einfluss auf den resultierenden Kontaktwiderstand [51]. Ebenso gibt es Ansätze die Elektroden z. B. durch eine Vorbehandlung mit einem Plasma anzupassen [52]. Durch Zwischenschichten kann die Injektion ebenfalls verändert werden, als Injektionsschichten werden oftmals Selbstorganisierende Monolagen (SAM<sup>5</sup>) verwendet, wodurch die Austrittsarbeit deutlich verändert werden kann [53].

<sup>&</sup>lt;sup>5</sup>SAM = Self Assembled Monolayer (engl.) = Selbstorganisierende Monoschicht

# 3. Verwendete Materialien und Herstellung

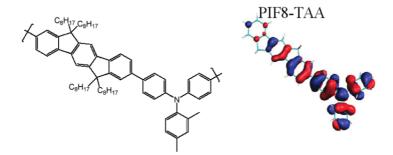

In diesem Kapitel werden die untersuchten Transistoren vorgestellt. Hierzu werden zunächst die verschiedenen Layouts erklärt und die verwendeten Materialien kurz beschrieben. Anschließend wird der Herstellungsprozess kurz erläutert. Als Halbleiter wird PIF8-TAA, für das Dielektrikum und das SAM werden jeweils kommerziell verfügbare Materialien von Merck KGaA verwendet.

#### 3.1. Verwendete Transistoren

Solange nicht explizit anders erwähnt, beziehen sich alle Messdaten, Angaben und Parameter auf Transistoren wie sie im BMBF<sup>1</sup> geförderten PO-LYTOS II Projekt verwendet wurden. Bei diesen Transistoren handelt es sich um Bottom-Contact, Top-Gate Transistoren (vgl. Kapitel 2.1). Diese sind auf flexiblen Substraten aus  $50\mu m$  dickem PET<sup>2</sup> hergestellt, als Elektrodenmaterial für Drain und Source wird Silber verwendet. Als Halbleiter wird PIF8-TAA verwendet. Als Dielektrikum wird lisicon® D320 verwendet, welches von Merck KGaA bezogen wird. Als Gatematerial wird aufgedampftes Gold verwendet. Halbleiter und Dielektrikum werden flüssig prozessiert. Nach elektrotechnischer Betrachtung handelt es sich um selbstsperrende p-Kanal Transistoren. Als Richtwerte für die Bauteilparameter können folgende Werte angenommen werden: Schwellspannung -5V bis -10V, Ladungsträgerbeweglichkeit  $0.02\,cm^2Vs^{-1}$  bis  $0.05\,cm^2Vs^{-1}$ .

<sup>&</sup>lt;sup>1</sup>BMBF = Bundesministerium für Bildung und Forschung

<sup>&</sup>lt;sup>2</sup>Polyethylenterephthalat

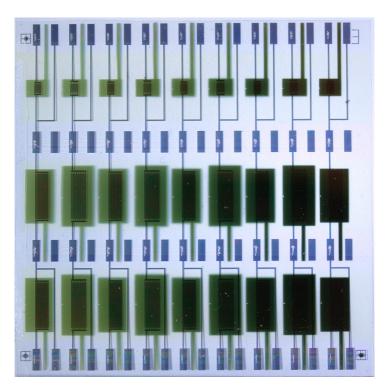

### 3.2. Herstellung

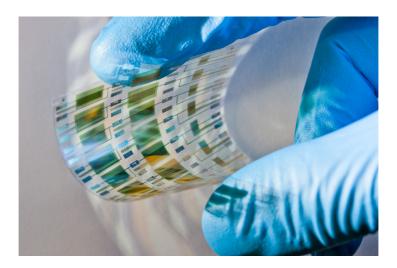

Die vorstrukturierten, 50 µm dicken PET Substrate lassen sich im Laborprozess nicht zufriedenstellend verarbeiten, daher werden diese auf Glas oder dickere Kunststofffolien aufgezogen und erst anschließend weiter verarbeitet. Die Substrate werden in Ultraschallbädern mit Aceton und Isopropanol gereinigt, anschließend mit gereinigtem Wasser abgespült und getrocknet. Zur Anpassung der Austrittsarbeit von Elektrodenmaterial und Halbleiter, wird eine SAM Lösung aufgebracht. Diese wirkt eine Minute ein, anschließend wird das Substrat auf einer Heizplatte bei 100°C für eine Minute getrocknet. Halbleiter und Dielektrikum werden nacheinander per Aufschleudern aufgebracht und jeweils anschließend für eine Minute bei 100°C getrocknet. Das Gate wird durch eine Schattenmaske aufgedampft. Abbildung 3.1 zeigt ein fertig prozessiertes Substrat.

Bild 3.1.: Prozessiertes Referenzsubstrat auf Trägerfolie.

#### 3.2.1. Transistorstrukturen

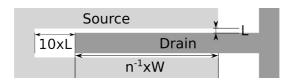

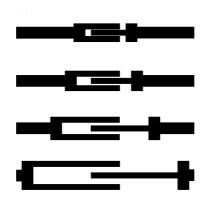

Die Transistorstrukturen werden mit einem Layout Generator erzeugt, welcher in einem Chipdesign-System (Mentor Graphics ICstudio©) implementiert ist. Dieses Werkzeug generiert aus vorgegebenen Parametern automatisch die Interdigitalstrukturen für Drain und Source. Die Breite der einzelnen Finger beträgt 100 μm, die Breite der Querbalken 200 μm. Der Abstand an der Stirnseite der Finger zum Ouerbalken der gegenüberliegenden Struktur ist festgelegt als 10x Kanallänge (siehe Abb. 3.2). Dieser vergrö-Berte Abstand wird gewählt um die Kanallänge möglichst gut zu definieren. Bei zu kleinen Kanallängen bzw. Abständen kann durch Randeffekte die wirksame Kanalweite vergrößert werden, was zu falsch extrahierten Parametern führt [54]. Abbildung 3.3 zeigt Transistoren mit gleicher Weite und den vier verwendeten Längen. Es ist zu sehen wie der Abstand zum Querbalken mit der Kanallänge skaliert. Abbildung 3.4 zeigt wie die Interdigitalstrukturen mit zunehmender Weite größer werden, Allgemein wird durch die großen Strukturen erreicht, dass die Substrate sowohl händisch, als auch mit einfachen Druckmaschinen verarbeitet werden können. Bei einfachen Druckprozessen auf Probedruckmaschinen beträgt die Positioniergenauigkeit ca.  $\pm 1 \, mm$ , diese Toleranzen addieren sich für jede zusätzliche Schicht, was bei der Layouterstellung berücksichtigt werden muss.

Bild 3.2.: Schematische Darstellung der Transistorstruktur. n = Anzahl der einzelnen Kanäle = 2x Anzahl der Drainfinger.

Bild 3.3.: Drain- und Sourcestruktur für Transistoren mit einer Kanalweite von 1mm. Die Kanallängen betragen von oben nach unten: 10,25,50 und  $100\,\mu m$ .

Bild 3.4.: Drain- und Sourcestruktur für Transistoren mit einer Kanallänge von  $100\,\mu m$ . Die Kanalweiten betragen von oben nach unten: 1,10 und  $100\,mm$ .

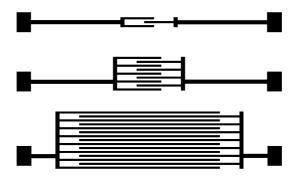

### 3.2.2. Referenzlayout

Die Substrate werden in vier verschiedenen Layouts prozessiert. Auf jedem einzelnen Substrat befinden sich 27 Transistoren in drei Reihen und neun Spalten. Abbildung 3.5 zeigt ein prozessiertes Referenzsubstrat. Innerhalb einer Reihe haben die Transistoren immer die gleiche Weite, die Länge wechselt zwischen geraden und ungeraden Spalten. Die Transistoren der Reihen zwei (Mitte) und drei (Unten) haben die zehnfache Weite der Transistoren der Reihe eins. So ergeben sich auf jedem Substrat vier verschiedene Transistorgeometrien aus zwei verschiedenen Weiten und zwei verschiedenen Längen. Als Kanalweiten werden 1, 10 und 100 mm und als Kanallängen 10, 25, 50 und 100 µm ausgewählt. Tabelle 3.1 zeigt die Weiten, Längen und die resultierenden W/L-Verhältnisse. Die Anordnung der Transistoren wird so gewählt, dass diese als einzelne Transistoren, Inverter oder NAND-Gatter gemessen werden können. Das Kontaktlayout ist bei allen Substraten gleich, so dass diese automatisch gemessen werden können. Die Drain- / Sourcestrukturen bestehen aus Silber und sind mittels Druckverfahren auf das PET-Substrat aufgebracht. Die strukturierten Substrate werden von PolyIC© GmbH & CO. KG bezogen.

| $L\ddot{a}nge  ightarrow$ | 10 μm | 25 μm | 50 μm | 100 μm |

|---------------------------|-------|-------|-------|--------|

| ↓ Weite                   |       |       |       |        |

| 1 <i>mm</i>               | 100   | 40    | 20    | 10     |

| 10 <i>mm</i>              | 1000  | 400   | 200   | 100    |

| 100 <i>mm</i>             | 10000 | 4000  | 2000  | 1000   |

Tabelle 3.1.: Kanal-Längen und -Weiten der untersuchten Transistoren.

| Substrat Nr. | Weite                        | Länge                   |

|--------------|------------------------------|-------------------------|

| 1            | 1 mm, 10 mm                  | $10\mu m, 25\mu m$      |

| 2            | 1 mm, 10 mm                  | $50  \mu m, 100  \mu m$ |

| 3            | 10 <i>mm</i> , 100 <i>mm</i> | $10\mu m, 25\mu m$      |

| 4            | 10 <i>mm</i> , 100 <i>mm</i> | $50\mu m, 100\mu m$     |

Tabelle 3.2.: Übersicht der vier verschiedenen Substrate.

Bild 3.5.: Prozessiertes und charakterisiertes Referenzsubstrat mit Layout Nr. 3. Sichtbar ist das aufgedampfte Gate, darunter die Interdigitalstruktuen von Drain und Source. Ebenfalls zu erkennen sind Kratzer, welche die Messnadeln bei der Kontaktierung verursacht haben.

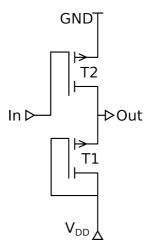

## 3.2.3. Inverter

Werden auf den Referenzsubstraten Inverter oder NAND NOR Gatter charakterisiert, so sind die Transistoren der Schaltung alle in einer Spalte und haben jeweils die gleiche Länge, jedoch unterschiedliche Weiten. Beide Schaltungen haben jeweils Schalt- und Lasttransistoren, wobei die Schalttransistoren die zehnfache Weite der Lasttransistoren haben. Die Lasttransistoren sind in der Reihe 1 auf dem Referenzsubstrat angeordnet, die Schalttransistoren des Inverters in Reihe 2, in Reihe 3 sind die zweiten Schalttransistoren, welche für das NAND Gatter verwendet werden. Abbildung 3.6 zeigt den Schaltplan der vorgesehenen Inverter. Der Lasttransistor ist bei dieser Konfiguration immer in Sättigung und verhält sich ähnlich wie eine Diode [25]. Für die automatisierte Messung der Inverter wird über den Messkopf eine Verbindung zwischen Drain und Gate des Lasttransistors hergestellt und mit der Versorgungsspannung verbunden.

Bild 3.6.: Inverter aus p-Kanal OTFTs, wie auf dem Referenzsubstrat vorgesehen. T1 ist der Transistor aus Reihe 1, T2 aus Reihe 2. Es gilt:  $W_{T2} = 10xW_{T1}$

## 3.3. Halbleiter

Als Halbleiter wird PIF8-TAA verwendet, welches in Mesitylen (Reinheit >98 %) gelöst wird, die Konzentration beträgt 2 %. Das Material ist eine Weiterentwicklung von PTAA³, gegenüber PTAA wird die Beweglichkeit um ca. eine Größenordnung erhöht, Literaturwerte sind  $0,004\,cm^2V\,s^{-1}$  für PTAA und  $0,04\,cm^2V\,s^{-1}$  für PIF8-TAA [55]. Das Material kann sowohl per Aufschleudern als auch durch Druckverfahren (z. B. Flexodruck oder Tiefdruck) verarbeitet werden. Die in dieser Arbeit gezeigten Transistoren sind jedoch ausschließlich per Aufschleudern hergestellt.

Bild 3.7.: Verwendeter Halbleiter, Molekülstruktur und Verteilung der höchsten besetzten Orbitale [55].

## 3.4. Dielektrikum

Als Dielektrikum wird lisicon® D320 verwendet, welches von Merck KGaA bezogen wird. Das Material wird flüssig geliefert und ohne weitere Behandlung verarbeitet. Das Auftragen kann prinzipiell per Aufschleudern oder im Tiefdruck erfolgen, die hier untersuchten Proben sind jedoch alle per Aufschleudern hergestellt. Der resultierende Film hat eine relative Permittivität von  $\varepsilon_r=2,3$  und wird standardmäßig in einer Schichtdicke von

<sup>&</sup>lt;sup>3</sup>PTAA = Poly(triarylamine)

928 nm aufgebracht. Dieser Wert wurde in der Vergangenheit gewählt um hohe Ausbeuten zu erreichen. Aus dieser relativ dicken Schicht resultiert ein Gatekapazitätsflächenbelag ( $C_{OX}$ ) von 21,94  $\mu F/m^2$ .

## 3.5. Injektionsschicht

Durch unterschiedliche Austrittsarbeiten von Metallelektroden (Silber, je nach Orientierung und Quelle 4, 26 bis 4, 72 eV) und Halbleiter (PIF8-TAA 5,5 eV) entsteht eine Potentialbarriere, welche die Injektion bzw. Extraktion von Ladungsträgern behindert [56, 50]. Durch geschickte Wahl des Elektrodenmaterials lässt sich die Potentialbarriere verringern, wobei nicht nur das Material sondern auch dessen Orientierung eine Rolle spielt [57, 581. Ein anderes gängiges Verfahren ist die Anpassung der Austrittsarbeiten durch SAM-Behandlung so anzupassen, dass die Potentialbarriere minimal und der Kontakt möglichst ohmsch wird. Hierzu haben SAM-Moleküle üblicherweise zwei unterschiedlich wirkende Enden, eines haftet auf dem Metall der Elektroden, das andere Ende ist elektrisch geladen und erzeugt hierdurch ein elektrostatisches Feld [59]. Die SAMs lagern sich mit dem haftenden Ende auf dem Metall der Elektroden an und bilden eine monomolekulare Lage, wobei die Einwirkzeit großen Einfluss auf die Wirkung der Injektionsschicht hat [60]. Durch die elektrische Ladung werden die Feldverhältnisse verändert, bei richtiger Wahl der SAMs wird die Potentialbarriere reduziert und die Injektion verbessert. Das verwendete SAM ist lisicon® M001, bezogen von Merck KGaA. Das Material wird durch Aufschleudern aufgetragen, wobei das Substrat vorher für eine Minute komplett benetzt ist.

# 4. Elektrische Charakterisierung

Dieses Kapitel beschreibt die durchgeführten Messungen und die Vorgehensweisen zur Bestimmung der einzelnen Parameter. Von den untersuchten OTFTs werden Transfer- und Ausgangskennlinien aufgenommen und aus diesen anschließend die Bauteilparameter extrahiert. Das Kapitel 4.3 beschreibt die durchgeführten Messungen und deren Rahmenbedingungen, der Abschnitt 4.4 die Bestimmung der einzelnen Bauteilparameter. Alle Messungen werden mit SMUs von Keithley, Modell 2636A durchgeführt. Diese Geräte verfügen über zwei Kanäle, welche an Drain und Gate angeschlossen werden, wobei Source als gemeinsames Bezugspotential dient.

Bild 4.1.: Manuell kontaktierte Probe auf dem Einzelmessplatz.

## 4.1. TRIAX-Technik

Da die erwarteten Ströme, insbesondere im Off-Bereich sehr klein sind, wird für die Leitungen TRIAX-Technik verwendet. TRIAX-Kabel sind ähnlich wie Koaxialkabel aufgebaut, haben jedoch zu einem Innenleiter zwei getrennte Abschirmungen. Der innere der beiden Schirme wird Guard genannt und im Messgerät auf das Potential des Innenleiters gebracht. Hierzu wird ein Verstärker mit sehr hochohmigem Eingang und einer Verstärkung von 1 verwendet. Durch diese Technik wird die Feldstärke zwischen Innenleiter und innerem Schirm auf  $0Vm^{-1}$  gehalten, dadurch werden Leckströme durch das Kabel vermindert und ebenso die wirksame Leitungskapazität verringert.

# 4.2. Kontaktierung

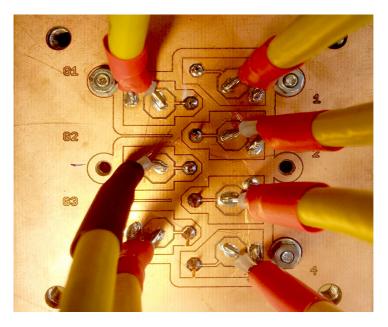

Die Analyse einzelner Transistoren erfolgt durch manuelles Kontaktieren mit Mikro-Manipulatoren auf einem herkömmlichen Spitzenmessplatz. Abbildung 4.1 zeigt einen manuell kontaktierten OFET auf dem Referenzsubstrat. Für Reihenmessungen an mehreren Transistoren wird eine modifizierte CNC-Fräsmaschine verwendet, welche über ein LabView Programm gesteuert wird. Abbildung 4.2 zeigt die Maschine mit montiertem Messkopf. Der Messkopf besteht aus zwei herkömmlichen FR4 Platinen, in die Federkontakte eingelötet werden. Über die Platine werden die Federkontakte mit den TRIAX-Kabeln verbunden, hierbei wird darauf geachtet die auftretenden Leckströme zu minimieren. Aus Einzelmessungen ist bekannt, dass die Off-Ströme der OTFTs zum Teil  $\leq 1~pA$  betragen, das verwendete Messgerät kann diese Ströme mit einem Fehler von  $\leq 20\,\%$  messen.

Um diese Genauigkeit nicht wesentlich zu verschlechtern wird festgelegt, dass durch den Messplatz auftretende Ströme möglichst kleiner sein sollen als  $0,2\,pA$ . Zur Überprüfung wird der Strom zwischen Innenleiter und äußerem Schirm bei 0V und 100V gemessen. Die Messung bei 100V

Bild 4.2.: Reihenmessplatz vor der Installation. Zu erkennen sind der Messkopf mit gelben TRIAX-Kabeln und die Vakuum-Spannplatte zur Fixierung der Substrate.

dient zur Ermittlung des Isolationswiderstandes, bei 0V werden Ströme gemessen, welche durch Verunreinigungen auf der Platine entstehen können. Als Messgerät wird ein Elektrometer vom Typ Keithley 6717B verwendet, dieses Gerät kann Ströme von 0,1 pA mit einem Fehler von  $\leq 4$ % messen.

In den Messungen zeigt sich, dass lithographisch hergestellte Platinen die geforderten Ströme nicht einhalten. Es werden sowohl bei 0V, als auch bei 100V Messspannung häufig zu hohe Werte gemessen. Daher werden Platinen mit gefrästen Leiterbahnen verwendet, welche bessere Werte lie-

Bild 4.3.: Oberseite des Messkopfes mit angelöteten TRIAX-Kabeln. Zu erkennen sind die gefrästen Leiterbahnen.

fern. Die Platinen werden nach der Herstellung mit Isopropanol gereinigt und ggf. die Isolationsflächen nochmals mit einem Messer nachgezogen. Abbildung 4.3 zeigt die Oberseite des Messkopfes mit angelöteten TRIAX-Kabeln. Messungen an fertigen Messkopfplatinen mit ca.  $20\,cm$  Anschlusskabel zeigen, dass Ströme von unter  $50\,fA$  erreicht werden können. Daraus wird geschlossen, dass die Isolation zwischen Innenleiter und Guard sehr hochohmig ( $\geq 2 \cdot 10^{15} \Omega$ ) ist und des weiteren keine Verunreinigungen vorliegen.

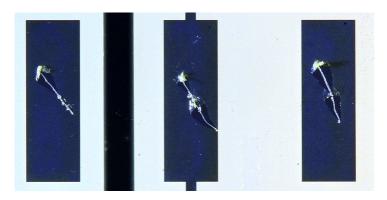

Bei den untersuchten OTFTs wird das Dielektrikum flächig auf dem Substrat aufgebracht und bildet hierbei eine robuste Schicht, die bei der Kontaktierung durchdrungen werden muss. Dies geschieht durch eine horizontale Bewegung der Kontaktnadel, wodurch das Dielektrikum angeritzt wird.

Bild 4.4.: Unterseite des Messkopfes mit drei eingesetzten Nadeln. Die Nadeln für Drain und Source sind spitz und stehen weiter heraus als die abgerundete für das Gate.

Abbildung 4.4 zeigt die Unterseite des Messkopfes mit den Nadeln. Um das Ritzen zu erleichtern, sind die Nadeln für Drain und Source spitz. Die Gate-Nadel ist abgerundet und ca.  $0,5\,mm$  höher montiert als die für Drain und Source, damit dass Gate beim Ritzen nicht beschädigt wird. Nach dem Ritzen werden die Nadeln angehoben und auf den nun blanken Metallkontakt gesetzt. In der Praxis werden Ritzlängen von  $100\,\mu m$  am Reihenmessplatz und bis zu  $1\,mm$  bei manueller Kontaktierung verwendet. Abbildung 4.5 zeigt drei Kontakpads nach manueller Kontaktierung. Zu erkennen sind das rhombisch abgehobene Dielektrikum und die Kratzer in den Metallflächen. Am Reihenmessplatz wird die Nadel zusätzlich noch um  $50\,\mu m$  seitlich versetzt, falls der Metallkontakt beim Ritzen durchstoßen wurde, wird er somit dennoch sicher kontaktiert.

Bild 4.5.: Kontakte nach manueller Kontaktierung, Kratzer in den Metallflächen und abgehobenes Dielektrikum sind zu sehen.

## 4.3. Messungen

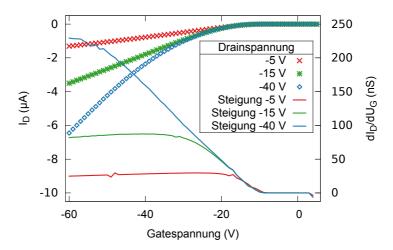

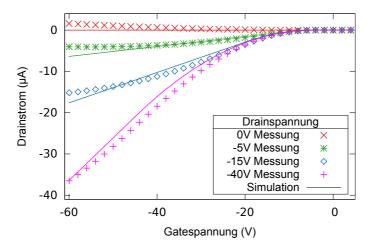

## 4.3.1. Transferkennlinie

In der Transferkennlinie wird die Wirkung der Gatespannung auf den Drainstrom untersucht. Ebenso werden aus der Transferkennlinie die Schwellspannung  $U_{Th}$  und die Ladungsträgerbeweglichkeit  $\mu$  ermittelt. Bei kleinen Drainspannungen kann unter Umständen auch der Leckstrom zwischen Gate und Drain beurteilt werden. Bei der Messung wird die Drainspannung konstant gehalten und die Gatespannung variiert. Zur Analyse von Hystereseeffekten werden die Messungen sowohl mit ansteigender als auch mit fallender Gatespannung durchgeführt. Üblicherweise wird die Kurve für mindestens zwei verschiedene Drainspannungen dargestellt, um verschiedene Betriebsbereiche des Transistors zu untersuchen. Die Darstellung kann linear oder logarithmisch erfolgen. In der linearen Darstellung kann hauptsächlich der Betriebsbereich analysiert werden. Die logarithmische Darstellung eignet sich besser um die Übergänge zwischen den Bereichen zu Untersuchen, außerdem lässt sich der Off-Strom und das On-

Bild 4.6.: Simulierte Transferkennlinie eines OTFT (ideale Simulation). Die Simulationsparameter sind im Anhang A.1 aufgelistet.

Off-Verhältnis leicht ablesen. Abbildung 4.6 zeigt eine simulierte, ideale Transferkennlinie eines organischen Transistors mit p-Halbleiter.

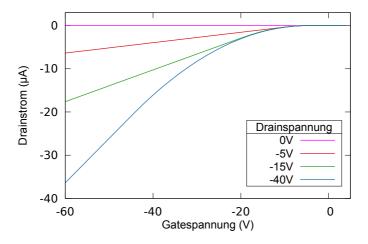

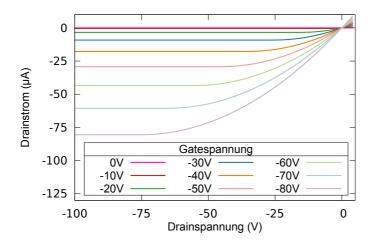

# 4.3.2. Ausgangskennlinie

In der Ausgangskennlinie wird die Wirkung der angelegten Drainspannung auf den Drainstrom dargestellt. Während der Messung wird die Gatespannung konstant gehalten und die Drainspannung variiert. Insbesondere der Stromanstieg im Sättigungsbereich kann hier beurteilt werden. Abbildung 4.7 zeigt simulierte Ausgangskennlinien eines organischen Transistors mit p-Kanal. Bei kleinen Drainspannungen können an den Ausgangskennlinien sowohl die Einflüsse der Gate-Leckströme als auch die der Kontaktwiderstände beurteilt werden. Aus der Steigung der Kennlinie im Sättigungsbereich werden der Ausgangswiderstand  $r_{ds}$  und die Early-Spannung  $V_E$  errechnet.

Bild 4.7.: Simulierte Ausgangskennlinie eines OTFT (ideale Simulation). Die Simulationsparameter sind im Anhang A.1 aufgelistet.

# 4.3.3. Relaxationsmessung

Während der Relaxationsmessungen (kurz: Relax-Messung) werden Drain, Gate und Source auf das gleiche Potential gelegt und die fließenden Ausgleichströme gemessen. So soll für alle Transistoren vor jeder Messung die gleiche Grundvoraussetzung geschaffen werden. Ursprünglich waren Messdauern von mehreren Minuten geplant, diese Zeitdauer ist jedoch bei den Reihenmessungen nicht zweckmäßig. Die Ergebnisse der Relax-Messung werden standardmäßig nicht ausgewertet, können jedoch bei fehlerhaften Bauteilen auf die Art des Defekts hinweisen.

#### 4.3.4. Messstandard

Zur Charakterisierung von organischen Bauelementen existiert der IEEE<sup>1</sup> Standard 1620. Dieser beschreibt welche Daten zu erfassen sind und wel-

<sup>&</sup>lt;sup>1</sup>IEEE = Institute of Electrical and Electronics Engineers

che Vorgehensweisen empfohlen werden [61]. Jedoch bleibt der eigentliche Messablauf hiervon unberührt, so dass für vergleichbare Messungen ein eigenes Schema entwickelt wird. Dieses beschreibt genau die anzulegenden Spannungen und zeitlichen Abläufe der durchgeführten Messungen. Durch Probemessungen wird der Einfluss der einzelnen Parameter auf die Messergebnisse ermittelt und anschließend unter Berücksichtigung der zu erwartenden Messdauer ein Optimum gewählt. Der Messablauf eines einzelnen OTFT ist wie folgt definiert:

- 1. 5 s Relaxationsmessung

- 2. Transferkennlinien bei Drainspannungen von 0V, -5V, -15V und -40V mit Gatespannungen von +5V bis -60V

- 3. 5 s Relaxationsmessung

- 4. Ausgangskennlinien bei Gatespannungen von 0V, -10V, -20V, -30V und -40V mit Drainspannungen von +5V bis -60V

Um Hystereseeffekte zu erkennen, werden die Transfer- und Ausgangskennlinien jeweils vor- und rückwärts durchlaufen. Zur Ermittlung der Bauteilparameter wird jeweils die erste Messung verwendet.

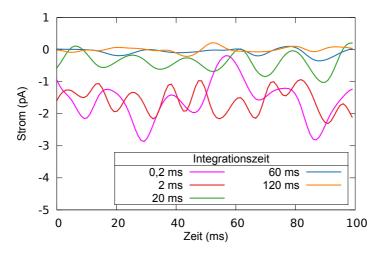

# 4.3.5. Integrationszeit

Präzise Messungen kleiner und niederfrequenter Ströme werden üblicherweise über einen Zeitraum von  $20\,ms$  integriert. Das entspricht einer kompletten Schwingung der  $50\,Hz$  Netzfrequenz. Durch die Netzspannung induzierte Wechselanteile werden hierdurch unterdrückt. Testmessungen weisen jedoch auch  $16,7\,Hz$  Wechselanteile auf, als Ursache wird das nahegelegene Bahnnetz vermutet. Abbildung 4.8 zeigt einen Vergleich der verschiedenen Integrationszeiten von  $0,2\,ms$  bis  $120\,ms$ . Die Integrationszeit wird für die Messungen auf  $60\,ms$  gesetzt, wodurch sowohl Störungen aus

dem Licht- als auch dem Bahnnetz unterdrückt werden. 120*ms* Integrationszeit zeigen gegenüber 60*ms* nur eine geringe Verbesserung, führen jedoch zu einer Verdoppelung der Messdauer.

Bild 4.8.: Vergleich verschiedener Integrationszeiten bei der Strommessung, gemessen wird ein Keramikkondensator mit  $100\,pF$  bei einer konstanten Spannung von -1V.

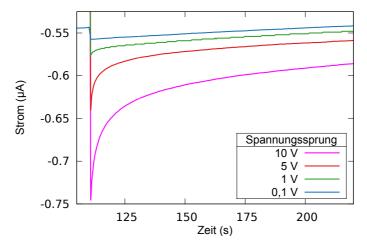

### 4.3.6. Schrittweite

Für das Aufnehmen der Kennlinien müssen die angelegten Spannungen variiert werden, dies wird in äquidistanten Schritten durchgeführt. Zur Ermittlung des Einflusses der Schrittgröße auf die Messwerte wird in Abb. 4.9 an einem OTFT die Gatespannung sprunghaft verändert. Der Endwert beträgt jeweils  $U_G = -10V$  der Ausgangswert wird so gewählt, dass die Endspannung nach dem Schritt immer -10V beträgt. Eine große Änderung deutet auf ein großes Überschwingen und langes Abklingen hin, wie es z. B. bei der  $\Delta U = 10V$  Kurve zu sehen ist. Zur quantitativen Beurteilung des Zeit-

Bild 4.9.: Auswirkung unterschiedlicher Spannungssprünge auf den gemessenen Stromverlauf. Die Kurven zeigen eine RC-Sprungantwort, jedoch ist der Endwert nicht konstant. Der Herstellungsprozess der untersuchten OTFTs ist noch nicht optimal eingestellt, daher sind die OTFTs unter Umständen nicht stabil und können ihre Parameter während der Messung ändern.

verhaltens werden die Ströme nach  $\Delta t = 0 s$ , 0,25 s und 110 s verglichen, und die relative Abweichung vom Messwert bei  $\Delta t = 0 s$  untersucht, die Ergebnisse sind in Tabelle 4.1 dargestellt. Für die weiteren Messungen wird eine Schrittweite von  $\Delta U = 1 V$  gewählt. Eine weitere Verkleinerung der Schrittweite bringt nur ein etwas geringeres Überschwingen, verzehnfacht jedoch der Messdauer. Für präzise Untersuchungen an einzelnen Transistoren ist dennoch eine Schrittweite von  $\Delta U = 0,1 V$  empfehlenswert, da dann für eine Auswertung der Kennlinie mehr Datenpunkte zur Verfügung stehen.

| Schrittweite | $\Delta t = 0,25  s$ | $\Delta t = 100 s$ |

|--------------|----------------------|--------------------|

| 10 <i>V</i>  | 1,01 %               | 18,77 %            |

| 5 V          | 0,69 %               | 10,21 %            |

| 1 V          | 0,14 %               | 4,27 %             |

| 0,1V         | 0,004 %              | 2,66 %             |

Tabelle 4.1.: Vergleich verschiedener Spannungssprünge, aufgeführt ist die Höhe der relativen Änderung zwischen Initialwert und 0,25 s bzw. 100 s nach dem Spannungssprung. Die relativen Änderungen geben eine quantitative Angabe über das Überschwingen (vgl. Abb. 4.9).

## 4.4. Parameter Extraktion

Die gewonnenen Messdaten werden mit eigens entwickelter Software ausgewertet. Aus den einzelnen Messpunkten werden die Transfer- und Ausgangskennlinien dargestellt und erste Simulationsparameter ermittelt. Für die Parameterextraktion und die spätere Simulation, werden im weiteren folgende Werte als bekannt vorausgesetzt:

- W und L Weite und Länge des Kanals werden im Layout definiert, die tatsächlich wirksamen Werte können jedoch durch Fertigungstoleranzen und Randeffekte abweichen, diese Abweichungen werden bei der Parameterextraktion zunächst vernachlässigt. Es ist jedoch zweckmäßig die Parameterextraktion bei großen L durchzuführen um Randeffekte und den Einfluss von RC zu minimieren.

- $C_{Ox}$  Der Gateoxidkapazitäts-Flächenbelag gibt die Gate-Kapazität pro Flächeneinheit an. Berechnet wird  $C_{Ox}$  aus dem Quotienten von  $\varepsilon_r \varepsilon_0^2$  und Dicke des Dielektrikums. Der Wert für  $\varepsilon_r$  ist als Materialparameter bekannt, die Schichtdicke des Dielektrikums wird während der Herstellung stichprobenartig gemessen.

$<sup>^{2}\</sup>varepsilon_{0}$  = Permittivität des Vakuums  $\approx 8,854 \cdot 10^{-12} AsV^{-1} m^{-1}$

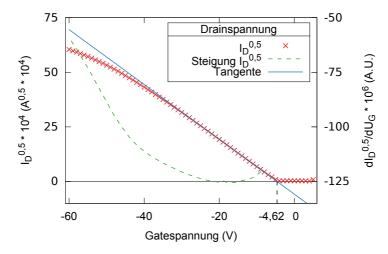

Bild 4.10.: Beispielhafte Bestimmung der Schwellspanung nach der ESR-Methode. Aus der Transferkennlinie wird im Sättigungsbereich die Wurzel des Stromes aufgetragen. Am Punkt maximaler (negativer) Steigung (hier -18V) wird eine Tangente angelegt und der Schnittpunkt mit  $0A^{0.5}$  bestimmt. Der ermittelte Wert ist die Schwellspannung, in diesem Beispiel -4.62V.

# 4.4.1. Schwellspannung

Die Schwellspannung  $U_{Th}$  ist bei selbstsperrenden Silizium-Transistoren, bei denen der Halbleiter im Kanalgebiet invertiert wird, genau definiert. Es ist die Spannung, bei der im Kanal die Minoritätsladungsträgerdichte genau doppelt so groß ist, wie die Majoritäsladungsträgerdichte ohne angelegte Gatespannung [1]. Bei den untersuchten OTFTs ist diese Definition jedoch nicht verwendbar, da das Kanalgebiet nicht invertiert, sondern die Majoritätsladungsträger akkumuliert werden. Da jedoch die resultierende Kurvenform für beide Funktionsweisen gleich ist und für die Simulation die gleichen Modelle verwendet werden wie für Siliziumtransistoren, werden die Methoden zur Parameterextraktion übernommen. Prinzipiell kann  $U_{Th}$  in Sättigung oder im linearen Bereich ermittelt werden, wobei in jedem

der beiden Bereiche wiederum mehrere verschiedene Verfahren verwendet werden können [59]. Einen breiten Überblick gibt Ortiz-Conde et al. [62]. Für die in dieser Arbeit ausgewerteten Daten, wird ein Verfahren gewählt welches gut automatisierbar ist und für die Simulation hinreichend gute Ergebnisse liefert.

Aus einer Transferkennlinie in Sättigung wird  $U_{Th}$  mittels der ESR<sup>3</sup>-Methode bestimmt. Hierzu wird zunächst die Wurzel von  $I_D$  über  $U_{GS}$  aufgetragen. Als Messdaten wird die Transferkennlinie bei  $U_D = -40V$  verwendet. Da es sich bei den untersuchten Transistoren um selbstsperrende p-Kanal Transistoren handelt befindet sich der Transistor zwischen 0V und -40V sicher in Sättigung, erst bei  $U_G \le -40V + U_{Th}$  wird der lineare Bereich erreicht. Aus der Wurzel des Stromes wird die Steigung über Differenzenbildung errechnet und der Punkt stärkster Steigung ermittelt. An diesem Punkt wird eine Tangente angelegt und der Schnittpunkt mit der X-Achse ermittelt. Abbildung 4.10 zeigt exemplarisch die  $U_{Th}$  Bestimmung nach der ESR-Methode. Bei parasitären Effekten, wie z. B. großen  $R_C$ , muss der Bereich, in dem die maximale Steigung ermittelt wird, eingeschränkt werden. Bei den in dieser Arbeit ermittelten Parametern wird der Bereich auf Werte zwischen -3V und -25V eingeschränkt.

# 4.4.2. Ladungsträgerbeweglichkeit

Aus der ermittelten Schwellspannung wird an einem Messpunkt im linearen Bereich die Ladungsträgerbeweglichkeit ermittelt. Hierzu werden ein gemessenes I-U-Wertepaar, die zuvor ermittelte  $U_{Th}$  und die bekannten Parameter W, L und  $C_{Ox}$  in die Formel des einfachen MOS-Modells (Gleichung (2.2)) eingesetzt, welche zuvor nach  $\mu$  umgestellt wird (Gleichung (4.1)).

$$\mu = \frac{I_D}{\frac{W}{L} C_{Ox} \left( U_{GS} - U_{Th} - \frac{U_{DS}}{2} \right) U_{DS}}$$

(4.1)

<sup>&</sup>lt;sup>3</sup>Extrapolation in Saturation Regime = Extrapolation im Sättigungsbereich

Die Einheit für die Ladungsträger-Beweglichkeit ist (m/s)/(V/m). Was sich zu  $m^2V^{-1}s^{-1}$  kürzt. Aus praktischen Gründen wird üblicherweise  $cm^2V^{-1}s^{-1}$  angegeben.

## 4.4.3. Ausgangswiderstand

Aus der Steigung der Ausgangskennlinie in Sättigung lässt sich der differentielle Ausgangswiderstand  $r_{DS}$  bestimmen. Im Sättigungsbereich wird der Transistor als eine Stromquelle angenähert, der Ausgangswiderstand ist in diesem Fall der Innenwiderstand der Stromquelle. Da der Ausgangswiderstand von der angelegten Drainspannung  $U_{DS}$  abhängig ist, wird als Modellparameter die Early-Spannung  $U_E$  verwendet [63]. Zur Ermittlung der Early-Spannung wird eine Tangente an die Ausgangskennlinie in Sättigung angelegt und zu  $I_D = 0A$  extrapoliert. Die Spannung an diesem Schnittpunkt ist die Early-Spannung ( $\lambda^{-1}$ ). Da die Ausgangswiderstände der untersuchten OTFTs sehr groß sind ergeben sich Early-Spannungen von mehreren hundert Volt.

#### 4.4.4. Kontaktwiderstand

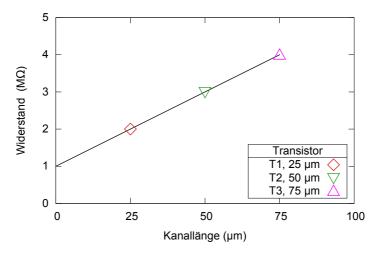

Der Kontaktwiderstand (vgl: Kapitel 2.8) wird aus den Messdaten mehrerer Transistoren mit gleichen Kanalweiten und unterschiedlichen Kanallängen extrahiert. Hierfür wird die Transfer-Line-Methode (TLM) verwendet. Bei diesem Verfahren wird der Kanalwiderstand der einzelnen Transistoren ermittelt und über der Kanalweite aufgetragen. Anschließend wird eine Gerade durch die Punkte gefittet, welche zur Länge  $L=0\,m$  extrapoliert wird. Der so ermittelte Widerstand ist der Kontaktwiderstand. Abbildung 4.11 zeigt ein Beispiel, die Kanallängen betragen hierbei 25,50 und 75  $\mu m$ , der ermittelte Kontaktwiderstand beträgt  $1\,M\Omega$ . Hintergrund dieser Methode ist die Annahme, dass der Kanalwiderstand linear mit der Länge skaliert wogegen der Kontaktwiderstand konstant bleibt [64].

Bild 4.11.: Bestimmung des Kontaktwiderstandes nach der Transfer Line Methode. In diesem simulierten Beispiel wird  $R_C$  aus drei verschiedenen Kanallängen zu  $1\,M\Omega$  bestimmt.

Durch die TLM wird  $R_C$  nur an einem diskreten Punkt bestimmt. Da jedoch der Wert von den angelegten Spannungen  $U_{GS}$  und  $U_{DS}$  abhängt, ist es wichtig für vergleichende Messungen immer den gleichen Arbeitspunkt zu wählen. In dieser Arbeit werden diskret angegebene Werte von  $R_C$  immer bei  $U_{DS} = -15V$  und  $U_{GS} = -59V$  ermittelt. An diesem Wert arbeiten die untersuchten Transistoren mit großer Sicherheit im linearen Bereich, zudem ist der Einfluss eventueller Leckströme deutlich kleiner als bei der  $U_{DS} = -5V$  Kennlinie.

# 4.4.5. Sub-Threshold Slope

Ein einfacher Widerstand beschreibt das Verhalten des Transistors im Sperrbereich nicht genau genug für komplexere Simulationen. Eine bessere Simulation ist die Annäherung über einen exponentiellen Verlauf. Der Modellparameter n wird Sub-Threshold Slope genannt. Die Berechnung des Stromes erfolgt nach Gleichung 4.2.

$$I_D = I_{D0} * \left( e^{\frac{U_{GS} - U_{Th}}{n \, k \, T}} \right) \tag{4.2}$$

$n = \text{Sub-Threshold Slope}, I_{D0} = \text{Drainstrom bei } U_{GS} = U_{Th}$

$k = \text{Boltzmann Konstante} \approx 8,617 \cdot 10^{-5} \text{eV} \text{K}^{-1}$

T =Absolute Temperatur

## 4.4.6. Gate-Leckstrom

Für Transistoren, welche vollständig gedruckt werden sollen, muss auch das Dielektrikum flüssig prozessiert werden. Wie auch beim Halbleiter sind die resultierenden Schichten nicht perfekt und können eine hohe Dichte von Defekten aufweisen. Daher muss bei der Charakterisierung auch das Dielektrikum untersucht werden. Hierzu wird während der Messung der Transfer- und Ausgangskennlinien auch der Gatestrom gemessen. Defekte zeigen sich in Gleichströmen, diese Ströme durch das Dielektrikum werden mit zwei neuen Parametern beschrieben. Diese werden  $K_{GS}$  und  $K_{GD}$  genannt und beschreiben den Stromfluss von Gate zu Source bzw. Drain. In Abschnitt 6 werden die Parameter und die Extraktion genau beschrieben.

# 4.4.7. Überlappkapazitäten

Die zu untersuchenden Transistoren werden im Laborprozess händisch hergestellt. Hierbei müssen relativ große Toleranzen vorgesehen werden um den Versatz der einzelnen Schichten untereinander zu kompensieren. Um das Kanalgebiet vollständig zu bedecken muss das Gate 1–2*mm* größer als die Transistorstrukturen sein. Hieraus resultiert im Transistor ein Plattenkondensator mit ungleichen Elektroden. Eine Elektrode bildet das aufgedampfte Gate, die anderen werden von den Drain- und Source-Strukturen gebildet. Diese Kapazitäten verschlechtern das AC-Verhalten der Bauteile,

die Effekte können jedoch unter Umständen, auch bei den durchgeführten elektrischen Messungen beobachtet werden.

Die wirksamen Kapazitäten werden üblicherweise durch Messung der Impedanz ermittelt. An einem Parameter-Messplatz (Agilent 4294A) wird exemplarisch an einigen Substraten die Überlapp-Kapazität gemessen und mit errechneten Werten verglichen. Hierbei zeigt sich, dass die Kapazitäten unter Vernachlässigung von Randeffekten nicht zufriedenstellend angenähert werden.

# 5. Modellierung und Simulation

Dieses Kapitel beschreibt die durchgeführten Simulationen. Hierzu wird zunächst das SPICE Simulationsprogramm und die verwendeten Modelle vorgestellt. Anschließend wird das Modell schrittweise um parasitäre Elemente erweitert und deren Einfluss auf die Simulationsergebnisse erläutert.

## 5.1. SPICE

Für die Simulation elektrischer Schaltungen hat sich das Programm SPICE¹ als Standard etabliert. SPICE wurde 1973 an der Universität Berkeley entwickelt und bildet die Basis für verschiedene Programme. Diese reichen von kostenlos verfügbaren Varianten wie z.B. ngspice (Open Source) oder LTspice (ⓒ Linear Technology), bis zu professionellen Werkzeugen welche für den Entwurf von integrierten Schaltkreisen verwendet werden, z.B. ELDO (ⓒ Mentor Graphics) oder PSpice (ⓒ Cadence). Das besondere an SPICE ist die Vorgehensweise mit der die Schaltungen berechnet werden. Alle Bauteile und deren Anschlüsse werden in einer Netzliste aufgelistet und in eine Matrix eingetragen, welche zur Berechnung vereinfacht wird. Diese Vorgehensweise ermöglicht es auch komplexe Schaltungen in relativ kurzer Zeit zu simulieren [65]. Je nach verwendeter SPICE-Software werden unterschiedliche Analysearten angeboten. Für diese Arbeit sind die drei grundlegenden Analysen von Interesse.

<sup>&</sup>lt;sup>1</sup>SPICE = Simulation Programm with Integrated Circuit Emphasis = Simulationsprogramm für Integrierte Schaltkreise

- 1. DC-Analyse eine oder mehrere Quellen werden quasistatisch verändert, hierbei wird kein Zeitverhalten untersucht.

- AC-Analyse an einem definierten Arbeitspunkt wird ein Wechselsignal erzeugt und die Auswirkung auf die Schaltung untersucht. Hierbei wird das Frequenzverhalten der Schaltung untersucht.

- 3. Transiente Analyse Untersuchung des Einschwingverhaltens.

# 5.2. OTFT-Modellierung

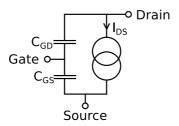

SPICE beinhaltet vordefinierte Modelle für gebräuchliche Bauelemente wie z. B. Widerstände, Dioden und Transistoren, kann jedoch auch um externe Modelle erweitert werden. Für die Umsetzung des in Kapitel 5.3 vorgestellten Modells wird eine programmierbare Stromquelle (BI-Quelle) verwendet. Abb. 5.1 zeigt ein einfaches Ersatzschaltbild (ESB) für einen Feldeffekttransistor. Der Gate Anschluss ist offen, zwischen Drain und Source liegt eine Stromquelle, der Strom  $I_{DS}$  wird nach dem verwendeten Modell in Abhängigkeit von  $U_{GS}$  und  $U_{DS}$  errechnet.

Bild 5.1.: Einfaches Ersatzschaltbild eines Feldeffekttransistors.

## 5.3. Verwendetes Modell

Das einfache MOS-Modell (vgl. Kapitel 2.4) kann OTFTs prinzipiell beschreiben, jedoch ist der physikalische Hintergrund nicht korrekt. Das MOS-Modell geht von Landungsträgertransport in Bändern (vgl. Kapitel 2.5) aus, welcher nur in hochgradig geordneten Halbleitern stattfinden kann. Flüssig prozessierte organische Halbleiter sind jedoch meist amorph und der Ladungsträgertransport wird von anderen Effekten beeinflusst. Daher werden für die Simulation von OTFTs meistens Modelle verwendet, die solche Systeme besser beschreiben können. Diese Modelle sind zum Teil sehr komplex und haben viele Parameter, um die Kurven einzelner OTFTs sehr präzise beschreiben zu können. Diese Präzision bringt jedoch den Nachteil, dass das Modell nur schwer zu verstehen ist und die Parameterextraktion sehr aufwendig wird.

Problematisch bei der Modellierung von OTFTs ist der Umstand, dass der Ladungstransport in organischen Halbleitern nicht komplett verstanden ist [66]. Es gibt Ansätze der Beschreibung, jedoch keine umfassende Theorie welche die Systeme komplett beschreibt. Eines der Probleme hierbei ist die Vielzahl der organischen Halbleiter und der Dielektrika.

Das hier verwendete Modell basiert auf dem VRH²-Modell [67]. Dieses beschreibt den Stromtransport in ungeordneten Halbleitern, wie z. B. organischen Halbleitern und amorphem Silizium. In seiner Form in [68] ähnelt es den Gleichungen des einfachen MOS-Modells (vgl. Kapitel 2.4), jedoch werden weitere Simulationsparameter eingeführt, die spezielle Eigenschaften der ungeordneten Halbleiter beschreiben. So wird z. B. die Ladungsträgerbeweglichkeit  $\mu$  nicht mehr als konstant angenommen, sondern der Wert ist abhängig von der angelegten Gatespannung [69, 70]. Das VRH-Modell in [68] wird stufenweise aufgebaut. Für die hier verwendeten Transistoren hat sich jedoch schon die erste Stufe,  $I_D^{acc,1}$  genannt, als hinreichend ge-

<sup>&</sup>lt;sup>2</sup>VRH = variable range hopping

nau herausgestellt. Gleichung (5.1) zeigt die verwendete Formel für den p-Kanal OTFT.

$$I'_{D} = -\frac{1}{(2+\gamma)} \frac{W}{L} \mu C_{Ox} ([[-U_{GS} + U_{Th}]]^{(2+\gamma)} - [[-U_{GS} + U_{Th} + U_{DS}]]^{(2+\gamma)})$$

Mit:  $[[x]] = 0, 5x + |0, 5x|$

(5.1)

Von dem VRH-Modell wird nur der Teil des Sättigungsbereiches implementiert, welcher jedoch auch den linearen Bereich annähern kann. Der Vorteil einer solchen Implementierung ist, dass keine Fallunterscheidung und kein Bereichswechsel in SPICE implementiert werden müssen. Fallunterscheidungen und das Umschalten zwischen verschiedenen Formeln führen bei Simulationen unter Umständen zu Problemen. So kann es vorkommen, dass die simulierten Kennlinien nicht stetig und daher auch nicht differenzierbar sind.

Der Parameter  $\gamma$ , beschreibt die Abhängigkeit der Ladungsträgerbeweglichkeit von der angelegten Gatespannung. Abbildung 5.2 zeigt exemplarisch eine Transferkennlinie und die Transkonduktanz ( $gm = \delta I_D/\delta U_D$ ), welche proportional zur Ladungsträgerbeweglichkeit ist. Nach Erreichen des linearen Bereiches bleibt der Wert annähernd konstant. Das zeigt, dass die Ladungsträgerbeweglichkeit nicht von der Gatespannung beeinflusst wird [71]. Diese Abhängigkeit ist bei allen untersuchten Transistoren sehr gering und wird daher vernachlässigt.

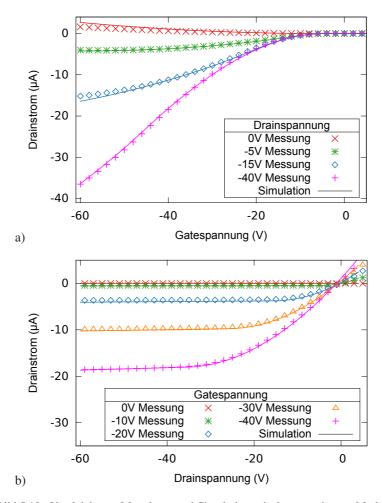

Abbildung 5.3 zeigt den Vergleich von Messwerten und Simulation mit dem vereinfachten VRH-Modell unter Vernachlässigung von  $\gamma$ . Die Simulation beschreibt die gemessenen Werte insgesamt relativ gut. Daher wird für die weitere Modellierung auf den Parameter  $\gamma$  verzichtet, was auch die Extraktion der Parameter vereinfacht. Das Modell vereinfacht sich hierdurch von Gleichung (5.1) zu (5.2).

Bild 5.2.: Exemplarisch gemessene Transferkennlinie eines OFET. Zusätzlich ist die Transkonduktanz abgebildet, dieser Wert ist proportional der Ladungsträgerbeweglichkeit  $\mu$ . Es ist zu erkennen, dass die Transkonduktanz zwischen  $U_G = -9,9V = U_{Th}$  und dem jeweiligen linearen Bereich bei  $U_G \leq U_{Th} + U_D$  ansteigt. Anschließend bleibt der Wert etwa konstant.

$$I'_{D} = -\frac{1}{2} \frac{W}{L} \mu C_{Ox} \left( \left[ \left[ -U_{GS} + U_{Th} \right] \right]^{2} - \left[ \left[ -U_{GS} + U_{Th} + U_{DS} \right] \right]^{2} \right)$$

(5.2)

Formel (5.2) wird um die Kanallängenmodulation nach Gleichung (5.3) erweitert. Dieser Zusatz beschreibt das Verhalten realer FET im Sättigungsbereich, wobei ein endlicher Ausgangswiderstand simuliert wird, was auch der Realität entspricht. Gleichung (5.3) errechnet aus einem idealisierten  $I_D'$  unter Berücksichtigung der Early-Spannung ( $\lambda^{-1}$ ) (vgl. Kapitel 4.4.3) den korrigierten Wert für  $I_D$ .

$$I_D = I_D'(1 + \lambda U_{DS}) \tag{5.3}$$

Bild 5.3.: Vergleich von Messwerten und Simulation der Transferkennlinie eines OTFT mit dem vereinfachten VRH-Modell. Die Simulationsparameter sind im Anhang A.1 aufgelistet.

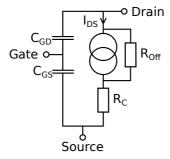

# 5.4. Modell-Erweiterungen

Da das VRH-Modell aus Abschnitt 5.3 nur das idealisierte Verhalten beschreibt, wird das SPICE-Modell um weitere Elemente erweitert. Diese Elemente dienen dazu, unerwünschte Effekte abzubilden, welche das Verhalten realer Bauteile beeinflussen. Hier sind insbesondere der Metall-Halbleiter Übergang (Kapitel 2.8) und die Gate-Leckströme (Kapitel 6) zu nennen. In den folgenden Abschnitten werden verschiedene Modellerweiterungen schrittweise vorgestellt und die Wirkung auf die Kennlinien einzeln gezeigt. Hierzu werden jeweils die gleichen Messdaten verwendet, um den Einfluss der Modellerweiterungen schrittweise zu verdeutlichen.

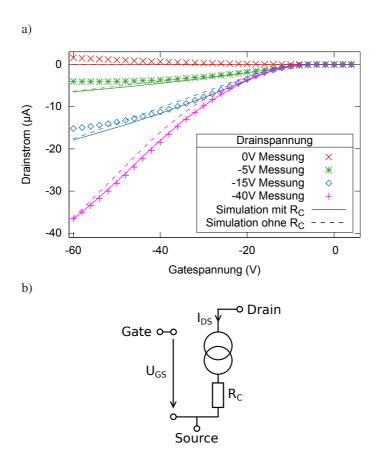

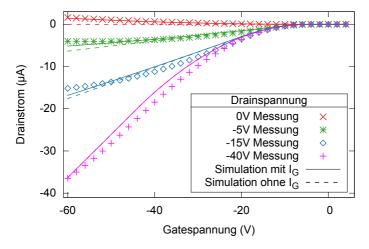

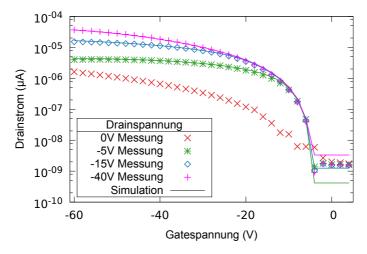

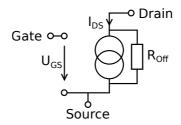

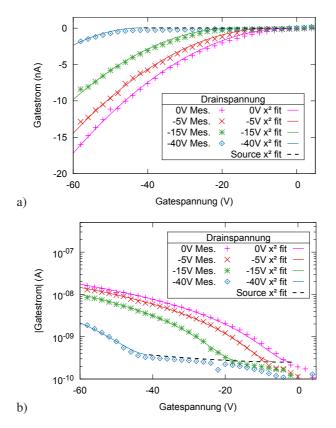

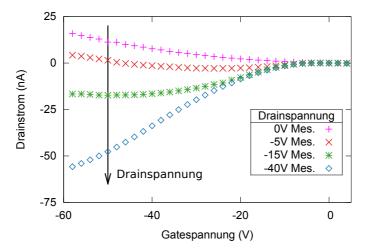

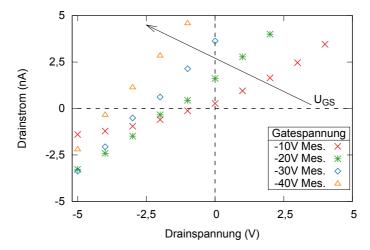

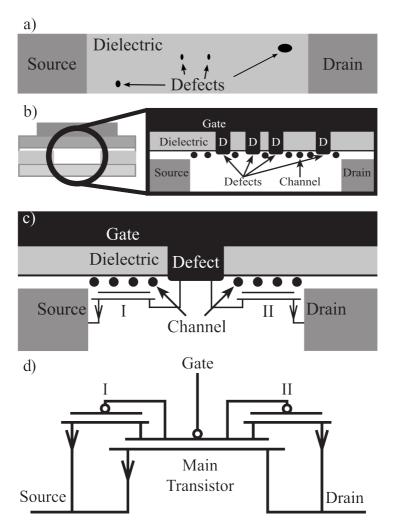

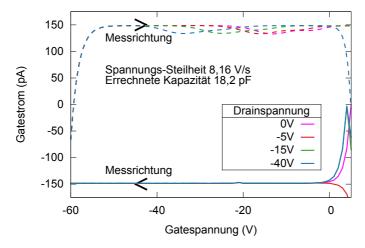

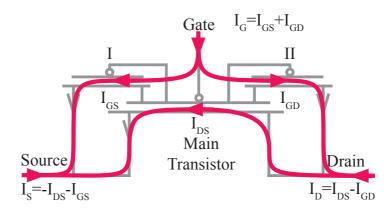

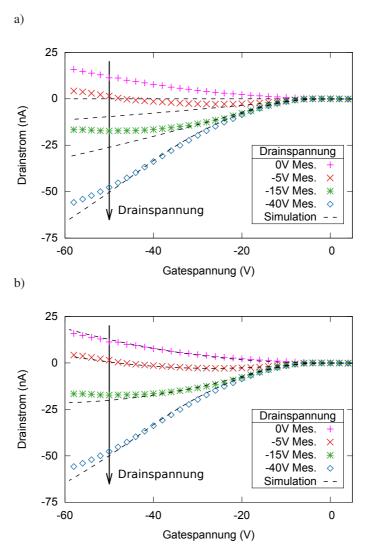

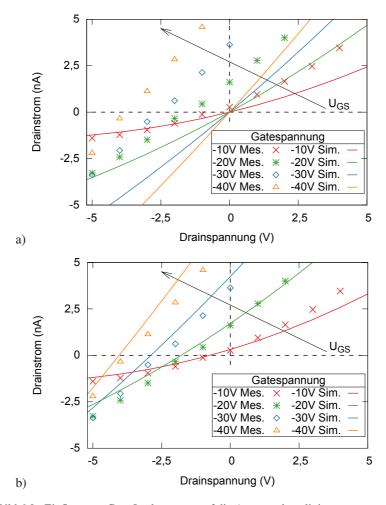

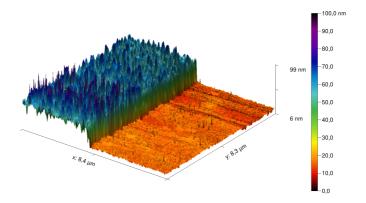

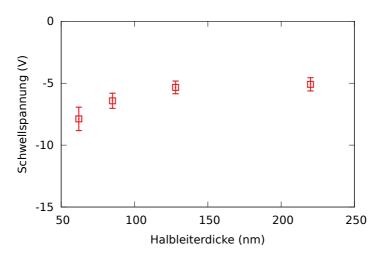

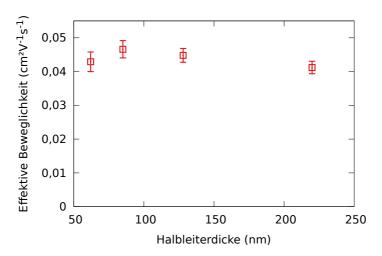

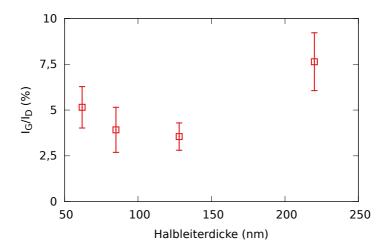

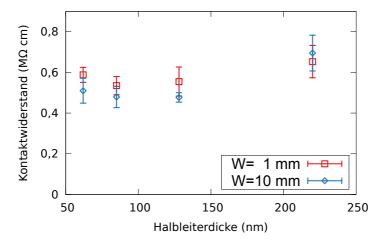

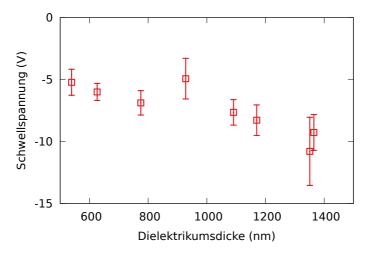

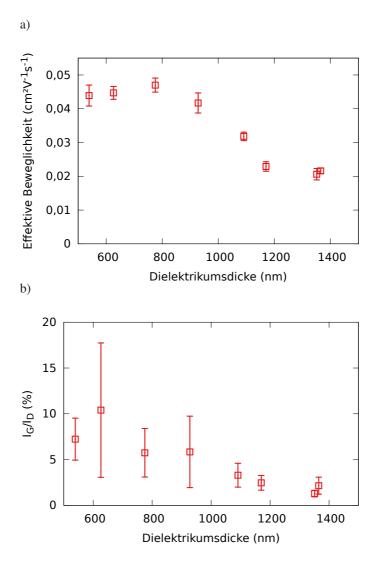

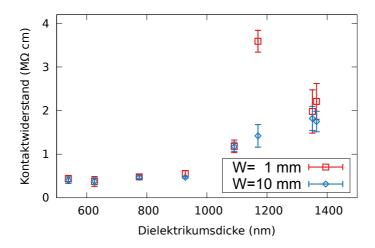

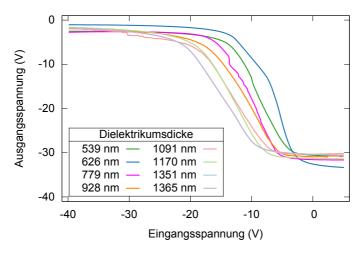

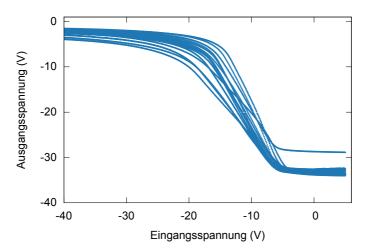

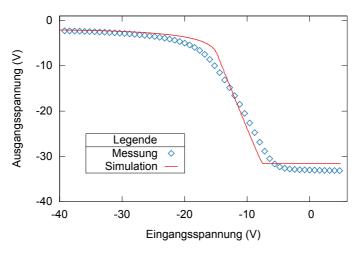

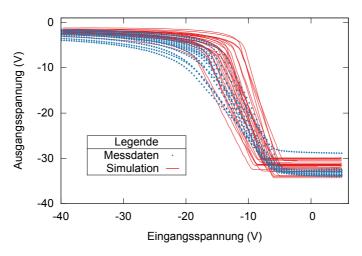

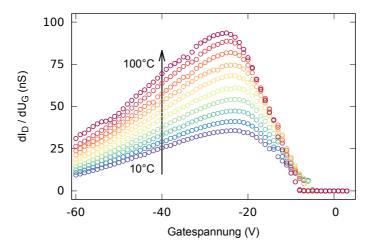

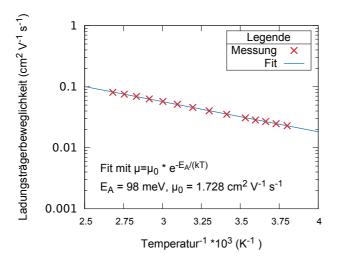

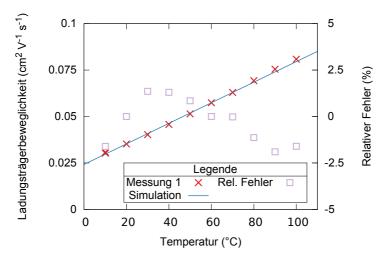

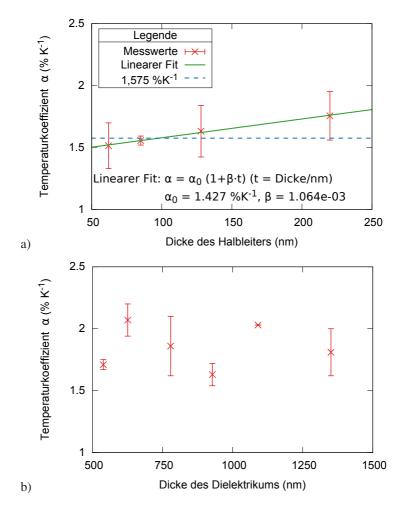

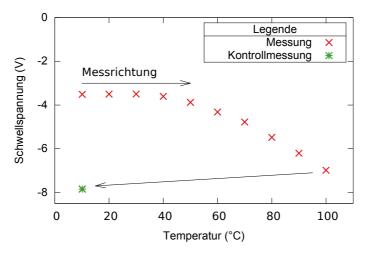

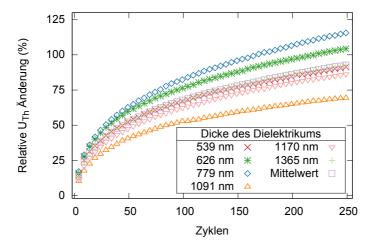

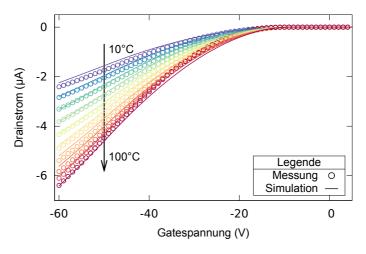

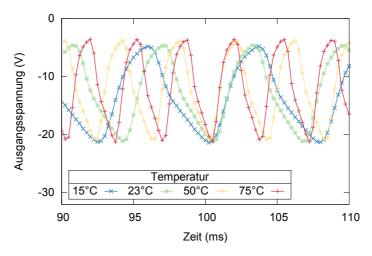

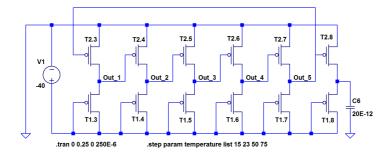

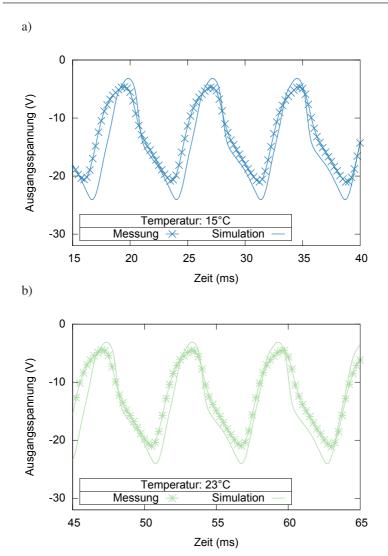

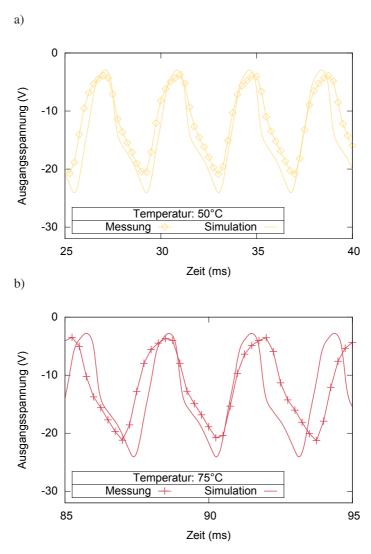

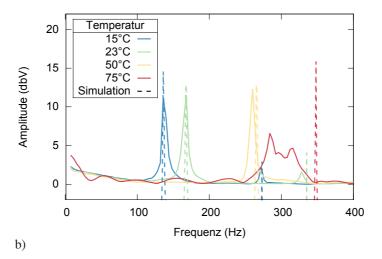

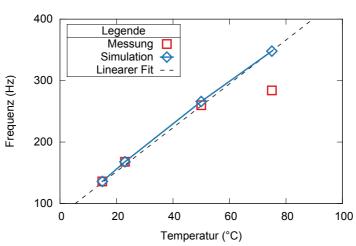

## 5.4.1. Kontaktwiderstand