# Thermal Management for Dependable On-Chip Systems

zur Erlangung des akademischen Grades eines

# Doktors der Ingenieurwissenschaften

der Fakultät für Informatik des Karlsruher Instituts für Technologie (KIT)

genehmigte

**Dissertation**

von

**Thomas Ebi**

aus Basel

| Tag der mündlichen Prüfung: | 8. Juli 2014        |

|-----------------------------|---------------------|

| Erster Gutachter:           | Prof. Jörg Henkel   |

| Zweiter Gutachter:          | Prof. David Atienza |

| Dritter Gutachter:          | Prof. Mehdi Tahoori |

for my father, the original Dr. Ebi

First and formost, I would like to thank my wife and my family for their continued support without which none of this would be possible. I would also like to thank Prof. Jörg Henkel for his advice and guidance that have led me here. Additional thanks go out to my many collegues that have accompanied me through the years. Thank you also to my co-supervisors David Atienza and Mehdi Tahoori for their valuable input.

# List of Own Publications Included in this Thesis

#### 1. Major contributions to thesis

- [43] Thomas Ebi, M Faruque, and Jörg Henkel. TAPE: Thermal-aware agent-based power econom multi/many-core architectures. In Computer-Aided Design-Digest of Technical Papers, 2009. ICCAD 2009. IEEE/ACM International Conference on, pages 302–309. IEEE, 2009.

- [45] Thomas Ebi, David Kramer, Wolfgang Karl, and Jörg Henkel. Economic learning for thermal-aware power budgeting in many-core architectures. In *Hardware/Software Codesign and System Synthesis (CODES+ ISSS)*, 2011 Proceedings of the 9th International Conference on, pages 189–196. IEEE, 2011.

- [44] Thomas Ebi, Hussam Amrouch, and Jörg Henkel. Cool: control-based optimization of load-balancing for thermal behavior. In *Proceedings of the eighth IEEE/ACM/IFIP international conference on Hardware/software codesign and system synthesis*, pages 255–264. ACM, 2012.

- [56] Jörg Henkel, Thomas Ebi, Hussam Amrouch, and Heba Khdr. Thermal management for dependable on-chip systems. In *ASP-DAC*, pages 113–118, 2013.

#### 2. Minor contributions to thesis

- [46] Thomas Ebi, Holm Rauchfuss, Andreas Herkersdorf, and Jörg Henkel. Agent-based thermal management using real-time i/o communication relocation for 3d many-cores. Integrated Circuit and System Design. Power and Timing Modeling, Optimization, and Simulation, pages 112–121, 2011.

- [15] Hussam Amrouch, Thomas Ebi, and Jörg Henkel. Stress balancing to mitigate nbti effects in register files. In *The 43rd Annual IEEE/IFIP International Conference on Dependable Systems and Networks (DSN'13)*, 2013.

[67] Muhammad Ismail, Osman Hasan, Thomas Ebi, Muhammad Shafique, and JÖrg Henkel. Formal verification of distributed dynamic thermal management. In *Proceedings of the International Conference on Computer-Aided Design (ICCAD)*, pages 248–255, 2013.

## The Big Picture

The Chair for Embedded Systems (CES) at the Karlsruhe Institute of Technology (KIT) provided me with a productive research environment within which to complete my thesis. Currently, the focus at the CES for architecture and design lie in multi-core systems, dependability, and low power. This includes, for instance, both adaptive and self-organizing on-chip systems as well as leveraging dark silicon to achieve thermal/dependability goals.

As with any work of this nature, this thesis builds upon the foundation laid by past explorations and has benefited from various collaborations. My initial work in the realm of distributed run-time adaptive management was done during my Diploma thesis [CES1], which developed AdNoC, an adaptive Network-on-Chip architecture. This work also manifested itself in two publications of the CES: In [CES2], the adaptive Network-on-Chip router architecture is presented, and in ROAdNoC [CES3] the corresponding distributed monitoring infrastructure. Al Faruque et al subsequently published their landmark paper ADAM [CES4] for the CES introducing agent-based resource management to multi-core systems, and thereby overcoming growing scalability concerns.

The developed concepts were then incorporated and expanded in the Digital On-demand Computing Organism (DodOrg) project. This collaboration between Computer- and Electrical-Engineering departments at the KIT (including the CES) along with the Embedded Systems department of the University of Frankfurt, aimed to create a computing architecture inspired by processes occurring in nature [CES5] [CES6]. Initially the contribution of the CES focused on power management. This was later extended to also include thermal management (TAPE [CES7]). This was realized through the application of economic principles to agent-based management. The DodOrg project itself was part of a wider initiative, the Priority Program (Schwerpunktprogramm, SPP) 1183, "Organic Computing", of the German Research Foundation (DFG).

The CES also played a pivotal role in the creation of a further Priority Program, the DFG SPP 1500 "Dependable Embedded Systems". This ongoing SPP deals with the growing dependability concerns in nano-scale CMOS [CES8] due to aging effects, high power densities, high process variation, etc. The SPP 1500 unifies various individual projects throughout Germany, working together to identify future trends and to model/quantify and improve dependability [CES9]. An example of the challenges it aims to address is managing the

viii 0. The Big Picture

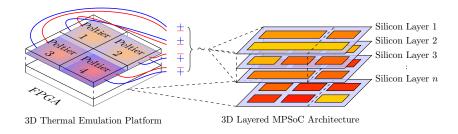

aforementioned dark silicon [CES10]. The projects cover a wide scope: spanning from the architecture level over the OS level to the compiler level. The SPP 1500 also cooperates with NSF Variability Expedition, a US initiative for the development of variability-aware software for nano-scale devices. One of the contributions of the CES is the VirTherm-3D project – in collaboration with TU Munich (TUM) [CES11]. In it, mulit-core adaptivity is employed in order to achieve dependability in a 3D layered architecture. The VirTherm-3D project is also responsible for the joint hardware platform available to all SPP 1500 members.

The CES is also involved in multiple sub-projects of the DFG Transregional Collaborative Research Center (TCRC) 89 "Invasive Computing". This ambitous undertaking of KIT, TUM, together with the Friedrich Alexander University in Erlangen (FAU) has set its goal to facilitate self-adaptive and resource-aware programming by unifying new programming concepts, languages, compilers, operating systems together with a customized multi-core architecture [CES12]. The key idea therein being that programs are given the possibility to spread compution of code fragments over a dynamic area in a multi-core system – in a sense "invading" additional resources. This results in a high degree of paralellism. One of the contributions of the CES is an agent-based approach that manages computational resources and facilitates coordination of invasion [CES13] in a distributed manner, thus maintaining scalability.

- [CES1] T. Ebi, "Design and analysis of adaptive networks on chip," Diploma Thesis, University of Karlsruhe, 2007.

- [CES2] A. Faruque, M. Abdullah, T. Ebi, and J. Henkel, "Run-time adaptive on-chip communication scheme," in Computer-Aided Design, 2007. ICCAD 2007. IEEE/ACM International Conference on. IEEE, 2007, pp. 26–31.

- [CES3] M. A. A. Faruque, T. Ebi, and J. Henkel, "ROAdNoC: Runtime observability for an adaptive network on chip architecture," *IEEE/ACM International Conference on Computer-Aided Design*, 2008. ICCAD 2008, pp. 543–548, Nov. 2008.

- [CES4] M. A. A. Faruque, R. Krist, and J. Henkel, "Adam: Run-time agent-based distributed application mapping for on-chip communication," *Design Automation Conference* (DAC), pp. 760–765, 2008.

- [CES5] J. Becker, K. Brändle, U. Brinkschulte, J. Henkel, W. Karl, T. Köster, M. Wenz, and H. Wörn, "Digital on-demand computing organism for real-time systems." in ARCS Workshops, vol. 81, 2006, pp. 230–245.

- [CES6] T. Ebi, D. Kramer, C. Schuck, A. von Renteln, J. Becker, U. Brinkschulte, J. Henkel, and W. Karl, "Dodorg - a self-adaptive organic many-core architecture," in *Organic Computing - A Paradigm Shift for Complex Systems*. Springer, 2011, pp. 353–368.

- [CES7] T. Ebi, M. A. A. Faruque, and J. Henkel, "TAPE: Thermal-aware agent-based power economy for multi/many-core architectures," in 27th IEEE/ACM International Conference on Computer-Aided Design (ICCAD '09), 2009, pp. 302–309.

- [CES8] J. Henkel, L. Bauer, J. Becker, O. Bringmann, U. Brinkschulte, S. Chakraborty, M. Engel, R. Ernst, H. Härtig, L. Hedrich et al., "Design and architectures for dependable embedded systems," in Hardware/Software Codesign and System Synthesis (CODES+ ISSS), 2011 Proceedings of the 9th International Conference on. IEEE, 2011, pp. 69–78.

- [CES9] J. Henkel, L. Bauer, N. Dutt, P. Gupta, S. Nassif, M. Shafique, M. Tahoori, and N. Wehn, "Reliable on-chip systems in the nano-era: lessons learnt and future trends," in *Proceedings of the 50th Annual Design Automation Conference*. ACM, 2013, p. 99.

- [CES10] M. Shafique, S. Garg, D. Marculescu, and J. Henkel, "The eda challenges in the dark silicon era: Temperature, reliability, and variability perspectives," pp. 185:1–185:6, 2014.

- [CES11] T. Ebi, H. Rauchfuss, A. Herkersdorf, and J. Henkel, "Agent-based thermal management using real-time i/o communication relocation for 3D many-cores," in *Integrated Circuit and System Design. Power and Timing Modeling, Optimization, and Simulation workshop (PATMOS)*, 2011, pp. 112–121.

- [CES12] J. Henkel, A. Herkersdorf, L. Bauer, T. Wild, M. Hübner, R. K. Pujari, A. Grudnitsky, J. Heisswolf, A. Zaib, B. Vogel, V. Lari, and S. Kobbe, "Invasive manycore architectures." in ASP-DAC, 2012, pp. 193–200.

- [CES13] S. Kobbe, L. Bauer, D. Lohmann, W. Schröder-Preikschat, and J. Henkel, "Distrm: distributed resource management for on-chip many-core systems," in *Proceedings of the seventh IEEE/ACM/IFIP international conference on Hardware/software codesign and system synthesis.* ACM, 2011, pp. 119–128.

## Abstract

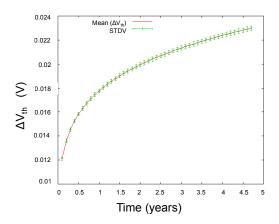

Today's fabrication technology, operating at technology nodes of 22 nm and below, allows the integration of several billion transistors on a single chip. A major drawback of the high integration density, is the resulting increase in power per chip area. This power density directly results in elevated on-chip temperatures. The small structure sizes also lead to a number of reliability issues, of which the most concerning are again dependent on temperature. Examples of such issues are electromigration and NBTI ("Negative Bias Temperature Instability") aging mechanisms. Recently, NBTI has emerged as the most dominant in current technologies.

Initially, this thesis addresses the reliability issues from a thermal perspective, focusing mostly on NBTI. This includes an explanation and analysis of models developed together with our partners from the semiconductor industry, in order to show the relationship between reliability and temperature. Additionally multiple thermal management strategies are examined in order to analyze their effects on reliability. This analysis shows that it is possible to double chip lifetime by choosing the suitable thermal management strategy.

Subsequently, multiple novel methods for on-chip thermal management are introduced aiming to optimize thermal properties. This includes both methods for reducing peak temperatures as well as for reducing both spatial and temporal thermal variation. The State-of-the-Art divides thermal management methods into two classes: so-called *reactive* methods act when a given temperature threshold is hit; *proactive* methods, on the other hand, rely on thermal or statistical models to make predictions on expected future temperatures, and act based on these predictions (i.e. before a threshold is hit).

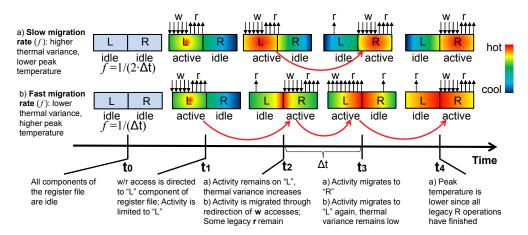

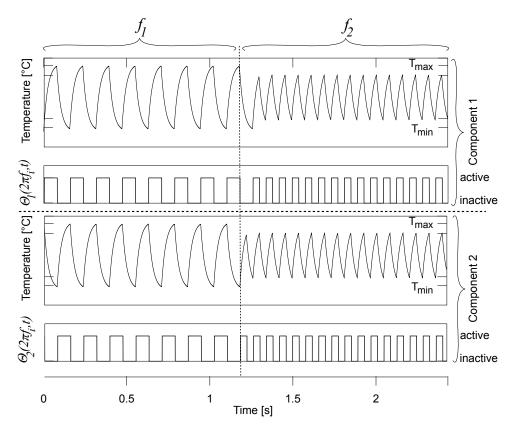

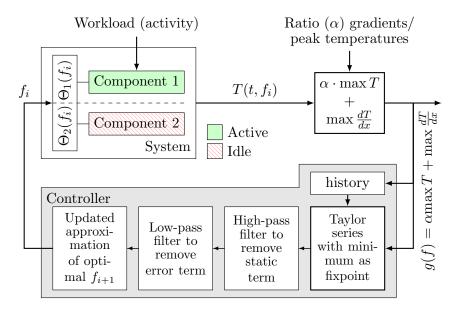

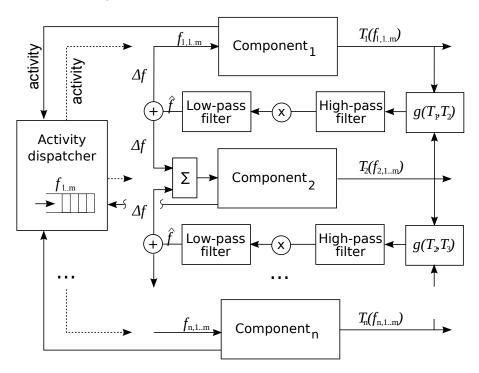

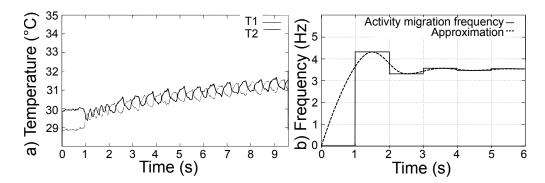

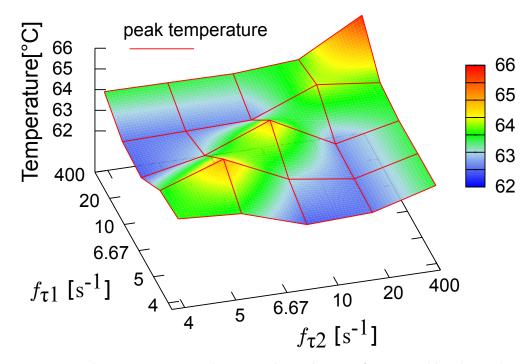

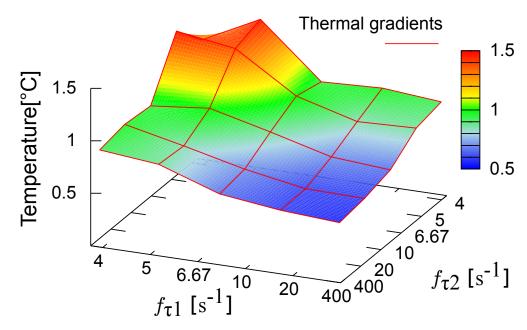

The presented methods are first applied to the processor microarchitecture. Here, the Control-Based Optimization of Load-Balancing (COOL) is examined whose goal it is to distribute computational activity among individual components of a processor in order to minimize both peak temperatures and thermal variations. This is realized by partitioning a component and performing a self-optimizing assignment of computational activity to each component part.

Next, thermal management methods for multi-core processors are presented and analyzed. These are designed to exhibit a high degree of scalability to remain applicable to computer

xii 0. Abstract

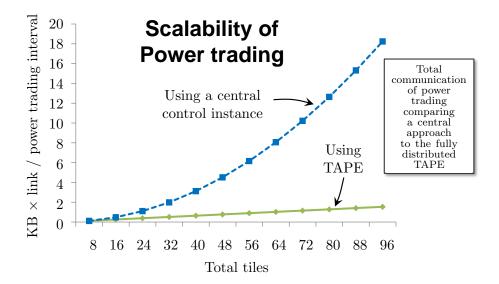

architectures with a high number of processing cores. This means avoiding a central "bottleneck" and reducing communication and computational overhead. The underlying mechanism employed is an agent-based system that operates distributed over the chip. Thus the problem complexity can be reduced by exploiting locality when making thermal management decisions.

The most important methods, that were developed are the following:

- Thermal-Aware Agent-Based Power Economy (TAPE): A completely decentralized approach where each processor core is assigned a power budget. This budget is traded by agents of neighboring cores based on supply and demand (i.e. how much power is currently being used to run application tasks and how much additional power is available). The temperature influences this trading by increasing the cost of the power budget. The power budget can be distributed throughout the entire chip through propagation from core to core over multiple successive trading intervals.

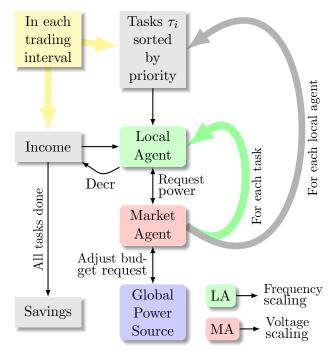

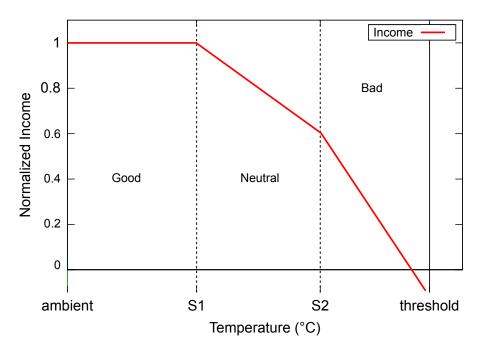

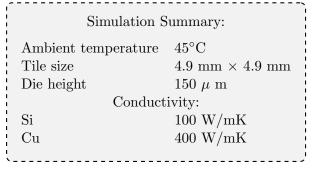

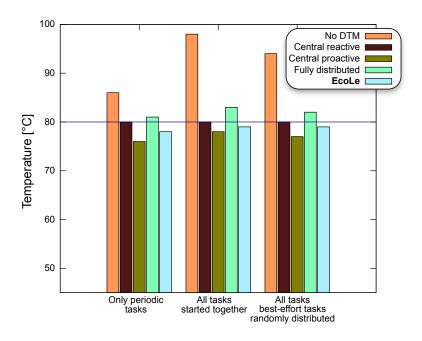

- Economic Learning for Thermal-Aware Power Budgeting (EcoLe): A hierarchical approach where power budget is distributed among clusters. In this context, a cluster is a grouping of a subset of cores located in a defined continuous region of the chip. Agents acting at cluster-level are responsible for both the power budget within the cluster as well as providing information to higher hierarchy levels which can in turn disseminate this information among other clusters. This allows exploiting locality for management decisions within a cluster while also retaining access to global system knowledge (e.g. the temperature distribution).

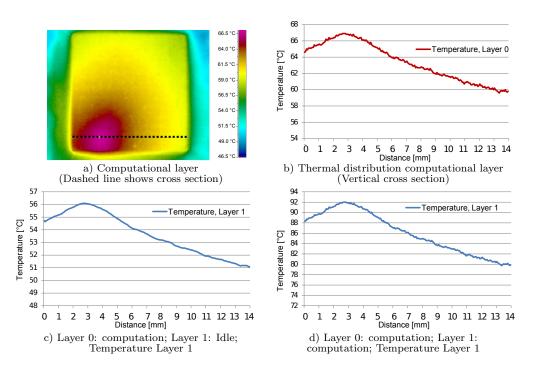

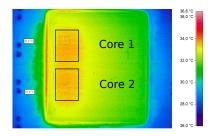

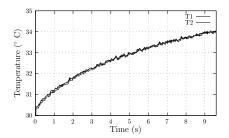

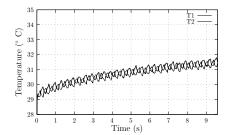

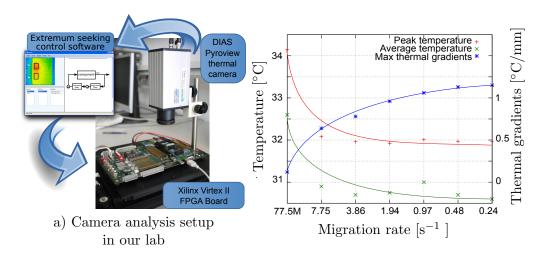

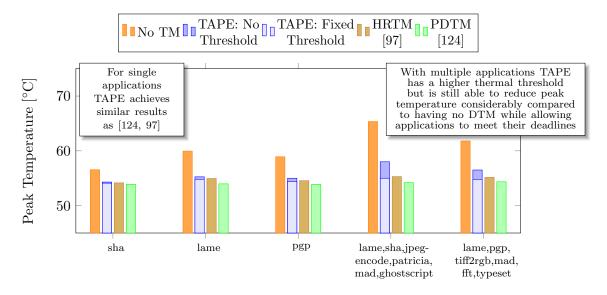

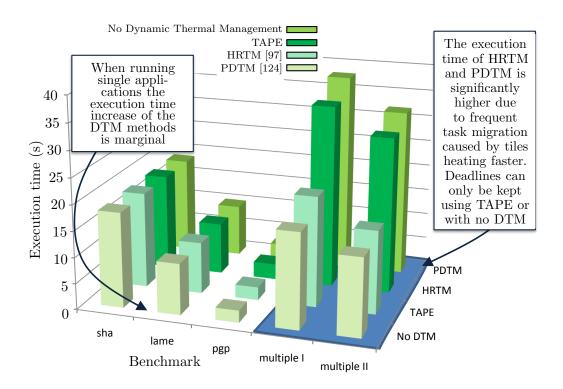

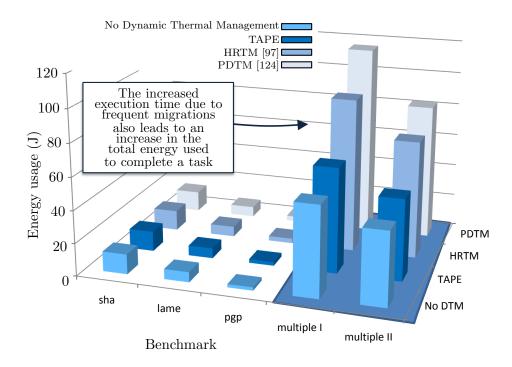

Analysis of the methods is done partially through simulation and partially through implementation on an FPGA-based hardware platform whose thermal behavior is captured using both on-chip sensors and an infrared thermal camera. This allows evaluation of the methods under real operating conditions. On average, the methods for multi-core architectures achieve a reduction of peak temperature by 15°C with only a small decrease in performance. The method optimizing the microarchitecture reduces the peak temperature by 13°C. This reduction is slightly smaller, as a smaller area footprint of the processor is affected. Through these methods, chip lifetime can be increased by at least a factor of two.

## Zusammenfassung

Heutige Fertigungstechnologien, welche Strukturgrößen von 22 nm und darunter haben, erlauben es, mehrere Milliarden Transistoren auf einem einzelnen Chip zu integrieren. Ein großer Nachteil hoher Integrationsdichte ist es, dass sich der Leistungsverbrauch pro Chipfläche ebenfalls erhöht ("Leistungsdichte"), was direkt steigende Temperaturen auf dem Chip mit sich bringt. Mit kleinen Strukturgrößen treten auch eine Reihe von Zuverlässigkeitsproblemen auf, von denen die mit den gravierendsten Auswirkungen wiederum von der Temperatur abhängig sind. Als Beispiel hierfür gelten z.B. Elektromigration und NBTI ("Negative Bias Temperature Instability"), von denen vor allem letzteres in jüngster Zeit immer häufiger in den Vordergrund rückt. Die vorgestellte Arbeit befasst sich zunächst mit diesen Zuverlässigkeitsproblemen und setzt dabei einen Schwerpunkt auf NBTI. Diesbezüglich werden die von uns, in Zusammenarbeit mit unserem industriellen Partner entwickelten Modelle erläutert und analysiert, um das Verhältnis zwischen Temperatur und Zuverlässigkeit zu verdeutlichen. Weiterhin werden verschiedene Temperaturmanagement-Strategien und deren Auswirkungen auf die Zuverlässigkeit der Chips untersucht. Hierbei wird gezeigt, dass es möglich ist, durch eine geeignete Temperaturmanagement-Strategie die Lebensdauer von Chips zu verdoppeln.

Zunächst werden mehrere neue Methoden zum Management der Chiptemperatur vorgestellt, mit dem Ziel Temperatureigenschaften zu optimieren. Dies betrifft sowohl Methoden zur Senkung der Höchsttemperatur wie auch Methoden zur Reduzierung der räumlichen und zeitlichen Variation der Temperatur. Der Stand der Forschung teilt entsprechende Methoden in zwei Klassen auf: sogenannte reaktive Methoden agieren wenn ein vorgegebener Temperaturschwellwert übertroffen wird; proaktive Methoden setzen hingegen auf thermische oder statistische Modelle um Vorhersagen über zu erwartende Temperaturen zu treffen und agieren dann, um den vorhergesagten Zustand zu vermeiden. Zunächst werden die vorgestellten Methoden angewandt auf der Mikroarchitektur eines Prozessors. In diesem Rahmen wird ein Verfahren (Control-Based Optimization of Load-Balancing, COOL) vorgestellt welches zum Ziel hat, die Rechenaktivität auf individuelle Komponenten des Prozessors zu verteilen, so dass sich dessen Höchsttemperatur wie auch dessen Temperaturvariationen minimieren. Dies erfolgt durch eine Partitionierung einer Komponente und einer selbst-optimierenden Zuweisung der Rechenaktivität an diese Teilkomponenten.

Des Weiteren werden Methoden für Multiprozessorsystemen vorgestellt und analysiert.

Diese sind dazu konzipiert, einen hohen Grad an Skalierbarkeit zu erzielen, um auf Architekturen mit einer Vielzahl von Prozessorkernen anwendbar zu bleiben, d.h. ohne einen (zentralen) "Flaschenhals" zu haben bzgl. sowohl Kommunikations- als auch Rechenaufwand. Der zugrunde liegende Mechanismus hierfür ist ein agenten-basiertes System, welches über den gesamten Chip verteilt arbeitet. Dadurch wird die Problemkomplexität durch die Ausnutzung von Lokalität auf einem kleineren Suchraum reduziert. Die wichtigsten Methoden, welche entwickelt wurden:

- Thermal-Aware Agent-Based Power Economy (TAPE): Ein komplett dezentrales Verfahren, in welchem jeder Prozessorkern ein Energiebudget zugewiesen bekommt. Dieses Budget wird dann, basierend auf Angebot und Nachfrage (d.h. wie viel Energie gerade gebraucht wird um Anwendungen auszuführen bzw. wie viel Energie verfügbar ist) zwischen benachbarten Kernen getauscht. Die Temperatur beeinflusst diesen Austausch durch eine Erhöhung der Kosten der Energie. Durch mehrere aufeinander folgende Tauschintervalle ist es möglich, Energiebudgets von Kern zu Kern über den gesamten Chip zu propagieren.

- Economic Learning for Thermal-Aware Power Budgeting (EcoLe): Ein hierarchisches Verfahren welches Energiebudgets auf Clusterebene verteilt. Hierbei bezeichnet ein Cluster eine Gruppierung von einer Menge von Kernen innerhalb eines definierten Bereichs des Chips. Agenten, welche einen Cluster verwalten, sind dafür zuständig sowohl das Energiebudget in ihrem Cluster zu verteilen, als auch den Informationsaustausch über höher gelegene Hierarchieebenen mit entsprechenden Agenten anderer Cluster durchzuführen. Somit kann auch hierbei räumliche Lokalität ausgenutzt werden und das System hat dennoch Zugriff auf die globalen Temperaturinformationen der höheren Ebenen.

Die Analyse der Verfahren verlief teilweise durch Simulationen, teilweise aber auch durch eine Implementation auf einer FPGA-basierten Hardwareplattform, dessen thermisches Verhalten von einer Infrarotkamera erfasst wurde. So war es möglich, die Verfahren unter realen Bedingungen zu evaluieren. Die Verfahren erzielen im Durchschnitt eine Senkung der Höchsttemperaturen um etwa 15°C bei geringer Steigerung der Laufzeiteffizienz (vergleichbare Verfahren benötigen 44% mehr Laufzeit). Bei der Optimierung der Mikroarchitektur werden die Höchsttemperaturen im Durchschnitt um 13°C gesenkt (die Reduktion ist hier etwas geringer, da die betroffene Chipfläche insgesamt kleiner ist als bei dem Management von Multiprozessorsystemen), ohne Erhöhung der Laufzeit. Die Lebensdauer des Chips wird durch die Verfahren um mindestens einen Faktor zwei erhöht.

# Contents

| Tł  | ierma                | I Management for Dependable On-Chip Systems                                                                                                                                                                                                                                                                                                                                                                   |                                                                |

|-----|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| Lis | 1.<br>2.             | Own Publications Included in this Thesis  Major contributions to thesis                                                                                                                                                                                                                                                                                                                                       |                                                                |

| Tł  | ne Big               | g Picture                                                                                                                                                                                                                                                                                                                                                                                                     | vi                                                             |

| ΑŁ  | strac                | t                                                                                                                                                                                                                                                                                                                                                                                                             | x                                                              |

| Zι  | ısamn                | nenfassung                                                                                                                                                                                                                                                                                                                                                                                                    | xii                                                            |

| 1.  | 1.1.<br>1.2.<br>1.3. | Key Challenges                                                                                                                                                                                                                                                                                                                                                                                                | 8                                                              |

| 2.  | 2.1.<br>2.2.         | Thermal Simulation Thermal measurement  2.2.1. Soft On-Chip Sensor 2.2.1.1. Temperature Sensors of the Intel SCC  2.2.2. Infrared Thermal Cameras Examining the Microarchitecture: SRAM Cell  Multi-Core Systems  2.4.1. Related Work: Thermal Management in Multi-Core Systems  2.4.2.1. Related Work: Thermal Management in 3D Architectures  2.4.2.1. Related Work: Thermal Management in 3D Architectures | 11<br>13<br>14<br>15<br>17<br>18<br>19<br>21<br>21<br>22<br>24 |

| 2   |                      | Summary                                                                                                                                                                                                                                                                                                                                                                                                       | 26                                                             |

| 3.  | On 3.1.              | Temperature-related Dependability  Reliability Concerns from a Thermal Perspective                                                                                                                                                                                                                                                                                                                            | 28<br>28<br>30<br>31                                           |

Contents

|    |                                | 3.1.4. Hot Carrier Injection                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3                                                |

|----|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|

|    |                                | 3.1.5. Time Dependent Dielectric Breakdown                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4                                                |

|    |                                | 3.1.6. Thermal Cycling                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4                                                |

|    |                                | 3.1.7. Timing errors                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4                                                |

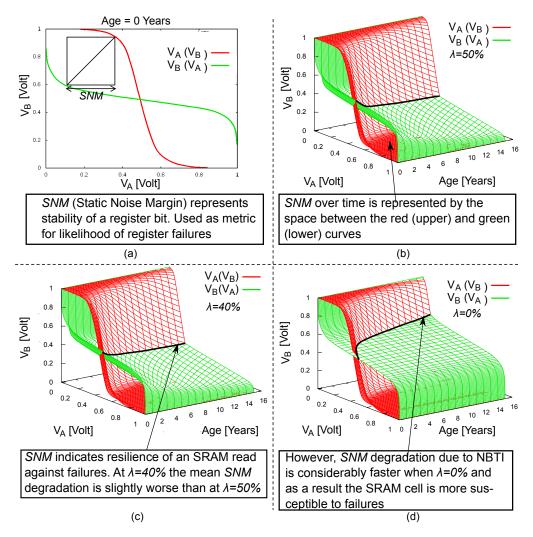

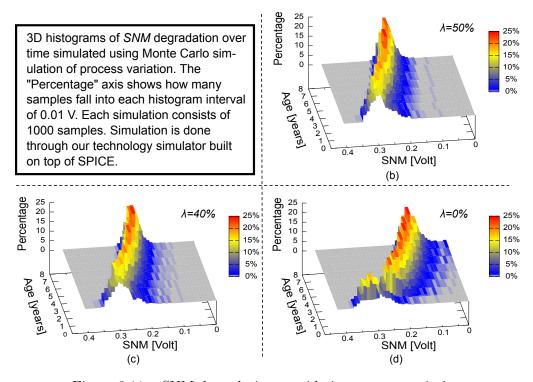

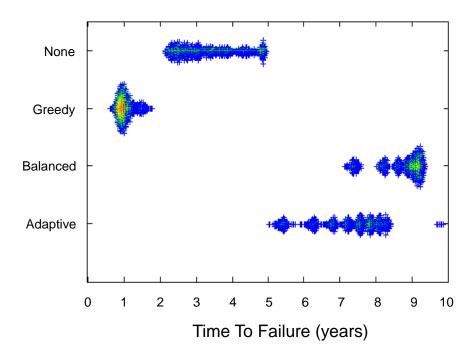

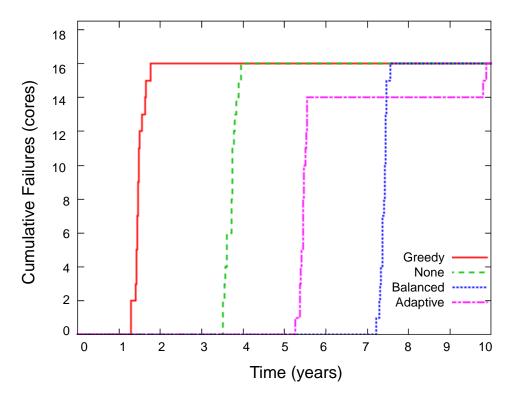

|    | 3.2.                           | Aging Effects and Reliability: Analysis of Effects on SRAM                                                                                                                                                                                                                                                                                                                                                                                                                               | 6                                                |

|    |                                | Tackling Dependability Through Thermal Management                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                  |

|    | 0.0.                           | 3.3.1. Aging Budgeting                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                  |

|    |                                | 3.3.2. Correcting Aging Budget at Runtime                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                  |

|    |                                | 3.3.3. Power Profiles                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                  |

|    |                                | 3.3.4. Thermal Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                  |

|    | 3.4.                           | Experimental Setup and Results                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                  |

|    |                                | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                  |

|    | 0.0.                           | Summary +                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | J                                                |

| 4. | Con                            | trol of Thermal Systems 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5                                                |

|    | 4.1.                           | Optimizing Performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5                                                |

|    | 4.2.                           | Optimizing Temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 6                                                |

|    | 4.3.                           | COOL: Control-based Optimization Of Load-balancing for Thermal Behavior 4                                                                                                                                                                                                                                                                                                                                                                                                                | 6                                                |

|    | 4.4.                           | Activity and Thermal Models                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 6                                                |

|    |                                | Application of Extremum-Seeking Control                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 7                                                |

|    |                                | 4.5.1. Extension to higher-dimensional problem space 5                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1                                                |

|    | 4.6.                           | Thermal Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3                                                |

|    |                                | 4.6.1. A Look at Specific Components: The Register File 5                                                                                                                                                                                                                                                                                                                                                                                                                                | 7                                                |

|    | 4.7.                           | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                  |

|    |                                | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                  |

| 5. |                                | active Techniques for Multi-Core Systems 6                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                  |

|    | 5.1.                           | Thermal Management and Multiple Cores 6                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                  |

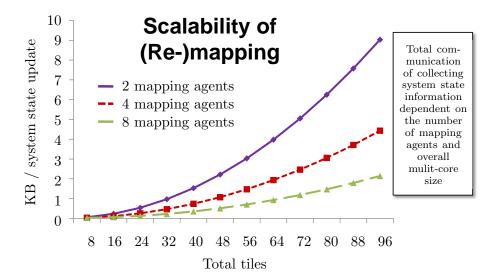

|    | 5.2.                           | On the Importance of Scalability                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                  |

|    |                                | 5.2.1. Related Work: Distributed Decision Making 6                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                  |

|    |                                | 5.2.2. Agents and Agent Systems 6                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                  |

|    | 5.3.                           | TAPE - Thermal-aware Agent-based Power Economy 6                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                  |

|    | 5.4.                           | Problem Formulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3                                                |

|    | 5.5.                           | System Models                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                  |

|    |                                | 5.5.1. Determining Power Budgets 6                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4                                                |

|    | 5.6.                           | Agent-based Power Economy 6                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5                                                |

|    |                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | _                                                |

|    |                                | 5.6.1. Agent Negotiation                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 6                                                |

|    |                                | 5.6.1. Agent Negotiation                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                  |

|    |                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 9                                                |

|    |                                | 5.6.2. Weights and Buy/Sell Value Characteristics 6                                                                                                                                                                                                                                                                                                                                                                                                                                      | 9                                                |

|    | 5.7.                           | 5.6.2. Weights and Buy/Sell Value Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                        | 9<br>1<br>2                                      |

|    | 5.7.<br>5.8.                   | 5.6.2. Weights and Buy/Sell Value Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                        | 9<br>1<br>2                                      |

|    |                                | 5.6.2. Weights and Buy/Sell Value Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                        | 9<br>1<br>2<br>3<br>4                            |

|    | 5.8.<br>5.9.                   | 5.6.2. Weights and Buy/Sell Value Characteristics65.6.3. Runtime Application (Re-)Mapping75.6.4. An Exemplary Runtime Scenario explaining TAPE's Functionality7Implementation Details and Hardware Prototype7Experimental Setup and Results7                                                                                                                                                                                                                                             | 9<br>1<br>2<br>3<br>4<br>8                       |

|    | 5.8.<br>5.9.<br>5.10           | 5.6.2. Weights and Buy/Sell Value Characteristics65.6.3. Runtime Application (Re-)Mapping75.6.4. An Exemplary Runtime Scenario explaining TAPE's Functionality7Implementation Details and Hardware Prototype7Experimental Setup and Results7On the Stability of Distributed Techniques7                                                                                                                                                                                                  | $9 \\ 1 \\ 2 \\ 3 \\ 4 \\ 8 \\ 1$                |

|    | 5.8.<br>5.9.<br>5.10.<br>5.11. | 5.6.2. Weights and Buy/Sell Value Characteristics       6         5.6.3. Runtime Application (Re-)Mapping       7         5.6.4. An Exemplary Runtime Scenario explaining TAPE's Functionality       7         Implementation Details and Hardware Prototype       7         Experimental Setup and Results       7         On the Stability of Distributed Techniques       7         EcoLe - Economic Learning       8                                                                 | $9 \\ 1 \\ 2 \\ 3 \\ 4 \\ 8 \\ 1 \\ 2$           |

|    | 5.8.<br>5.9.<br>5.10.<br>5.11. | 5.6.2. Weights and Buy/Sell Value Characteristics       6         5.6.3. Runtime Application (Re-)Mapping       7         5.6.4. An Exemplary Runtime Scenario explaining TAPE's Functionality       7         Implementation Details and Hardware Prototype       7         Experimental Setup and Results       7         On the Stability of Distributed Techniques       7         EcoLe - Economic Learning       8         System Models       8                                   | $9 \\ 1 \\ 2 \\ 3 \\ 4 \\ 8 \\ 1 \\ 2 \\ 3$      |

|    | 5.8.<br>5.9.<br>5.10.<br>5.11. | 5.6.2. Weights and Buy/Sell Value Characteristics       6         5.6.3. Runtime Application (Re-)Mapping       7         5.6.4. An Exemplary Runtime Scenario explaining TAPE's Functionality       7         Implementation Details and Hardware Prototype       7         Experimental Setup and Results       7         On the Stability of Distributed Techniques       7         EcoLe - Economic Learning       8         System Models       8         Agent Negotiation       8 | $9 \\ 1 \\ 2 \\ 3 \\ 4 \\ 8 \\ 1 \\ 2 \\ 3 \\ 4$ |

| $\frac{Cc}{c}$ | ontents                                            | X         | vii                              |

|----------------|----------------------------------------------------|-----------|----------------------------------|

|                | 5.13. 3D Architectures                             | · · · · · | 88<br>89<br>89<br>89<br>90<br>91 |

| 6.             | Outlook and Conclusion                             | 9         | 97                               |

| Bi             | bliography                                         | 9         | 99                               |

| Αŗ             | ppendices                                          | 1         | 15                               |

| Α.             | SPICE model of NBTI circuit                        | 1         | 17                               |

| В.             | OpenMPI Implementation of TAPE-Agent Communication | 1:        | 21                               |

123

Glossary

## 1. Introduction

Temperature has long been a limiting factor in electronics, defining boundaries on performance and power consumption as well as limiting dependable operation. This holds particularly true in current VLSI design where the market demands ever-increasing performance. Temperature management is a means for dealing with these limits and pushing the performance envelope by altering power consumption or increasing heat dissipation. The first line of defense lies in packaging design. Adding a heat sink greatly increases heat dissipation – even more so the use of active cooling methods, e.g. using fans or liquid cooling. While designing these physical means for removing heat from a chip are indispensable, the means themselves are often limited due to cost or area constraints. As the power per area grows, e.g. cooling fans have increased in both size and in their own power consumption, incurring high energy cost. This particularly presents a problem in systems where space is severely limited, e.g. as is the case in embedded systems. All this makes it necessary to add another layer of temperature management: system-level Dynamic Thermal Management (DTM) with the goal of managing temperature by controlling the power usage of a chip during runtime. This need for DTM is continually rising as temperatures and dependability concerns increase, largely due to the effects of technology scaling.

In 1965, G. Moore published his seminal work predicting the trend in sizing and complexity of semiconductor devices. Often referred to as Moore's law, this prediction calls for the doubling of the number of transistors every two years [91]. It remains valid until the present day as feature sizes have steadily shrunk over the past decades. Technology scaling has opened up the path to ever increasingly complex systems. The large amount of transistors available allow placing multiple processors or even whole systems consisting of several components joined together by an on-chip network on a single chip, for instance.

The exponential growth comes at a price due to the pitfalls that accompany small structure sizes. These structures are inherently less robust and as a result, more susceptible to failure than larger ones. Small cracks or erosions that were unnoticeable at the micrometer level are catastrophic regarding failures in nano-scale devices. These defects can occur during the manufacturing process, but may also occur due to degradation over time caused by temperature-dependent aging effects. The small structures are also plagued by a great deal of variability. While the absolute variance has remained the same or decreased, it is

1. Introduction

its relative impact that is concerning. While size variations of a few nm were negligible in larger structures (i.e. > 45 nm), these can have a great impact as sizes fall below 20 nm. Device characteristics are no longer deterministic at design time, necessitating wider safety margins to deal with the expected range of characteristics.

The problems arising from both aging-effects as well variability are compounded by the decrease in voltage bias. Where a large potential difference may be able to compensate some of these effects (e.g. when developing defects increase resistance and thereby reduce currents), a small voltage bias fails a lot sooner. Since the difference between supply and threshold voltages is also shrinking, the potential barrier hindering charge carriers is lower. As a result safety margins are considerably reduced, thereby for instance decreasing the critical charge  $Q_{crit}$  of a circuit and increasing susceptibility to soft errors. In a sense, this is a double edged sword. While on the one hand a higher voltage is able to compensate device degradation, on the other it also accelerates its effects by increasing power consumption and thereby temperature.

While in general the power consumption of a specific design decreases when moving from one technology node to the next, the power *densities* can increase dramatically due to the decrease in occupied area. Typically, however, designs in smaller technology nodes also contain more features – either the designs are inherently more complex or contain duplications (as is the case in multi-core architectures) – and thereby also increase the overall power consumption, especially if these also target higher frequencies. Together this means elevated temperatures which can threaten dependability.

There is also a great deal of complexity incurred when managing systems running on designs consisting of billions of transistors. This creates a high-dimensional problem space where solutions are sought for problems that are inherently complex – many management problems, i.e. assigning resources, already being in the realm of NP-hard problems. This calls for solutions which offer a large degree of scalability, oftentimes based on heuristics which aim to find approximations for optimal solutions where finding optimal solutions is not feasible.

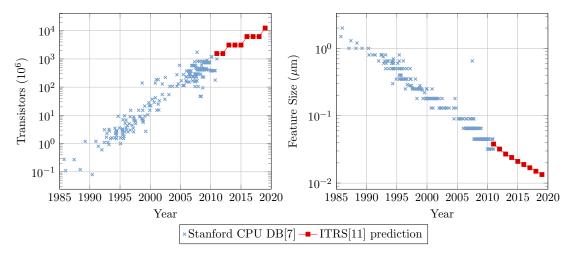

Figure 1.1.: Trends in number of transistors and feature size. Each point from the CPU DB represents a unique processor.

#### 1.1. A Closer Look at Processor Trends

The Stanford CPU DB [7] affords us with a repository of statistics on a large portion of current and past processors. Additionally, the International Technology Roadmap for Semiconductors (ITRS) regularly publishes predictions on the future of semiconductor devices. Together, these sources provide data which can give many insights on technology development and future trends. From a thermal perspective it is of particular interest how these trends affect the power consumption of a chip.

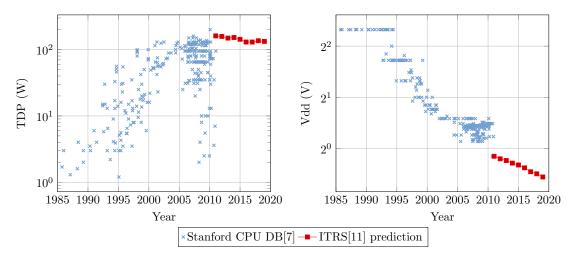

Figure 1.2.: Trends in Thermal Design Power (TDP) and supply voltage (Vdd)

Concerning general scalability, Figure 1.1 corroborates the validity of Moore's law. The amount of transistors has indeed experienced an exponential growth. The same holds true for the used feature sizes over time, although these are limited to discrete values corresponding to technology nodes. As we can see, the ITRS predicts this trend to continue into the future. More importantly, when considering temperature is how technology scaling affects Thermal Design Power (TDP). TDP is a metric supplied by chip manufacturers that represents the power consumed when the chip is under maximum workload. This serves as a guide for designers of temperature management by giving the maximum power that needs to be removed from the chip when transferred into heat. As can be seen, the TDP underwent exponential growth up until around 2005, but has since begun to level out in its maximum. Why this is the case is explained in conjunction with the discussion of voltage below. It is also evident that current processors exhibit a wide spectrum of TDPs, especially compared to past generations. This demonstrates a current trend of diversification of processors as many now specifically target low power (for battery-powered mobile devices, for instance) while others target high performance.

The voltage of a processor determines how fast parasitic capacitances can be charged and thus determines how fast, e.g. logic gates can operate. Smaller feature sizes result in smaller capacitances, meaning a given design will require less voltage to operate at the same speed compared to larger feature sizes. As a result, the required voltage for a given feature size depends on the desired frequency. Initially, as can be seen in Figure 1.2, supply voltage (Vdd) was fixed at 5 V. Theoretically this convention would have allowed everincreasing frequencies, but fixing the voltage became less and less feasible as the number of transistors grew causing power consumption to explode.

4 1. Introduction

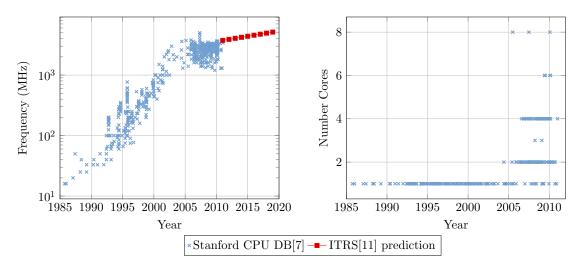

Figure 1.3.: Trends in operating frequency and typical number of cores per design

Typically voltage by itself scales with the square root of feature size. However, the demand for extra performance has historically called for an increase in operating frequency which again means increasing the reduced voltage. Thus, the voltage decrease from one technology node to the next has typically been reduced, i.e. the potentially attainable voltage decrease was sacrificed for the sake of performance. An interesting change happens in Figure 1.3 after 2005. As can be seen, at this time frequency begins to rise at a much lower rate. At the same time processors begin to incorporate multiple cores. This paradigm shift represents the beginning of the multi-core era where increased performance demands are additionally met through parallelization. This was made necessary to avoid hitting a power wall where the produced power is unable to be dissipated as heat.

As a continuation of this trend the ITRS predicts the number of cores to double each 18 months [11] analog to Moore's predicted doubling of transistors. Current front runners in this domain include the Intel Single-chip Cloud Computer (SCC) with 48 cores [10] and the Tilera TILE-Gx family of processors with up to 72 cores [51]. Future multicore architectures are predicted to integrate thousands of cores [26] on a single chip. The performance of these architectures will depend largely on the amount of parallelization that can be achieved which is limited by Amdahl's law [59]. Theoretically, a large improvement is possible in terms of performance per Watt for highly parallelizable applications.

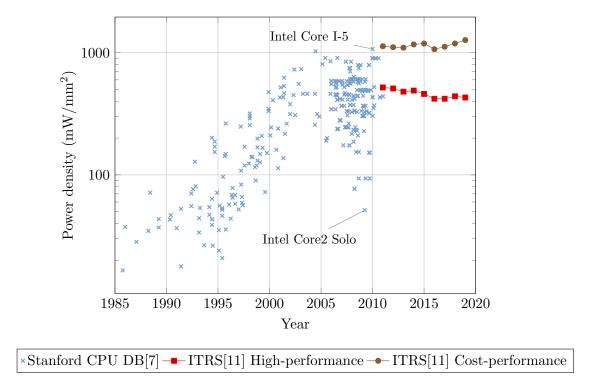

The most relevant trend when regarding temperature is the development of power densities over time. Figure 1.4 depicts the average worst-case power densities, i.e. the average power density on chip when under a worst-case workload. The presented graph is similar to that of TDP, indicating that overall chip area has largely remained the same. Power densities also grew continuously until around 2005.

To achieve a complete picture of predicted future trends, however, it is necessary to adopt a more differentiated view of processor technologies. To this effect, the ITRS defines two processor classifications: *high-performance* and *cost-performance*.

For high-performance processors, the severe increase in power density that was predicted at that time has failed to come into effect. Instead, due to the aforementioned paradigm shift to multi-cores along with the research into new technologies (high-k dielectrics, FinFET), power densities have stopped increasing and are predicted by the IRTS to level out around

Figure 1.4.: Development of power density over time calculated using data from [7] and ITRS [11] predicted future stabilization of power density

$0.42 \text{ W/mm}^2$  in the coming years. While this is true on average, a higher integration density can still result in higher peak power densities. For instance, these can range from around  $2 \text{ W/mm}^2$  in the 65 nm technology node to  $7.2 \text{ W/mm}^2$  for 45 nm [81].

Unfortunately, although it is possible to manufacture high-performance processors with little or no increase in power density, this comes with inhibitive design and production costs that are contrary to ubiquitous computing demands. As such, a large number of future processors will instead be optimized for cost-performance. For these, the future trend in Figure 1.4 predicts further rise in power density. This in itself presents a number of challenges to hardware-software co-design to be able to utilize a chip to its full potential – for instance leveraging supply voltage with dark silicon [111]. Regardless whether power densities increase or not, the growing susceptibility of small structure sizes mean thermal management will still grow in importance from a dependability viewpoint. Only the employed strategies may shift to favor ones that minimize long-term aging effects.

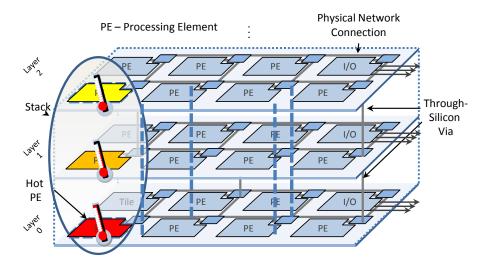

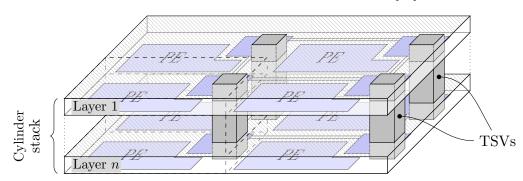

More recently, 3D chip architectures have emerged to increase performance per chip area. So far, the most common manufacturing technique involves multiple individual chip layers stacked on top of each other and connected through Through Silicon Vias (TSVs). Unfortunately, surface power densities are compounded in these 3D architectures. In the general case, heat must first travel through multiple layers before reaching the heat sink, which is only located at the top most layer.

### 1.2. Key Challenges

Dependable system operation has long been expected from hardware. In this context, dependability is a property that encompasses both reliability and availability. That is,

6 1. Introduction

execution is expected to terminate correctly and resources are expected to remain available throughout the lifetime of a chip. The temperature-dependent aging effects typically first threaten reliable operation. These gradually degrade device parameters, altering their operating characteristics, e.g. such as circuit delay. Eventually, they may lead to failures of components and thereby limit their availability.

Typically DTM techniques target optimizing performance within given thermal constraints. Little work has been done examining the effects of different thermal management strategies on system lifetime. Intuitively, any form of thermal management will reduce most temperature-dependent aging effects. Thus, constraining temperatures has the added bonus of increased general dependability. Not all strategies are equal, though. One that achieves the highest performance may not necessarily be the same one that minimizes aging. Moreover, reducing one aging mechanism may result in worsening the effects of another.

• Therefore, it is necessary to **bridge the gap between thermal management** and **dependability**. In this scope, considering the effects of temperature on multiple aging mechanisms is required to determine the overall lifetime of a chip. In particular this means analyzing thermal management strategies and their effect on aging mechanisms. This can be used to determine situations where minimizing one aging effect will worsen another, for instance as is the case with Negative Bias Temperature Instability (NBTI) and thermal cycling.

As mentioned, the main consideration of DTM is keeping temperatures within predefined bounds which are deemed to be a safe range. When optimizing for performance, the system generally operates at maximum allowable power that keeps temperatures as close to a specified fixed threshold as possible. This is far from optimal when targeting dependability, however. New strategies need to be developed that reduce temperature, ideally with little impact on performance.

• Management strategies targeting dependability to increase system lifetime must minimize aging effects. From a thermal standpoint this means a shift from optimizing performance within thermal constraints to **optimizing temperature** while keeping performance constraints. This entails both reducing peak temperatures as well as thermal gradients, as both can have a negative impact on dependability (cf. Chapter 3).

Processors in the multi-core era offer a great deal of potential for dynamic thermal management. Apart from traditional methods such as Dynamic Voltage and Frequency Scaling (DVFS), they allow controlling the power density distribution through the migration of tasks to cores. Management problems such as these are typically computationally expensive. Even when considering single cores, in its simplest form, the assignment of tasks reduces to the np-hard<sup>1</sup> knapsack problem [27]. Expanded to multiple cores, it becomes the even more complex multiple knapsack problem. In this sense, general thermal man-

$<sup>^{1}</sup>$ While determining if a solution to the knapsack problem exists is np-complete, finding the solution itself is np-hard

agement through task mapping can be expressed as the following:

maximize:

$$\sum_{i=1}^{m} \sum_{j=1}^{n} p_{i,j} x_{i,j},$$

$$x_{i,j} \in \{0,1\}$$

subject to:

$$\text{MAX}_{i=1}^{m} T(\sum_{j=1}^{n} x_{i,j}) < T_{\text{max}},$$

$$(1.1)$$

when mapping n tasks to m cores.  $x_{i,j} = 1$  if task j is mapped to core i.  $p_{i,j}$  is the value of mapping task j to core i, i.e. in terms of performance. Here, T is a temperature function which determines the temperature of each core (i.e. for a static mapping this would correspond to a steady-state temperature). In reality, of course, determining temperatures is more difficult, as heat is also conducted to and from the surroundings of a core. Furthermore, when performing dynamic thermal management, the knapsack problem needs to be solved periodically during runtime. This also entails continuously updating the temperature function. In practice, this requires either the use of models for predicting future temperatures or continuous observational feedback and control.

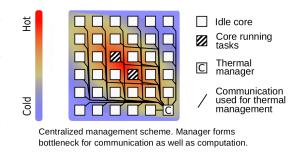

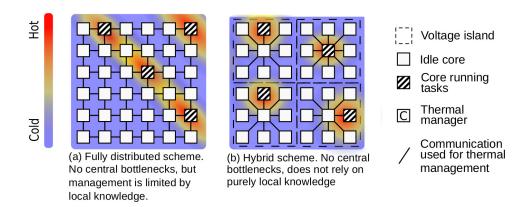

Typically, State-of-the-Art thermal management is done by a central instance. This creates both a central point of failure as well as a communication bottleneck. To be able to make DTM decisions, the central instance must be kept up-to-date on the state of each core, which requires continuous transmission of temperature data. The only way to deal with these problems is shifting DTM to novel distributed techniques.

Even with the large communication overhead, the major advantage of a central instance is the availability of global system knowledge. It will have information about all tasks and all cores and their current state, e.g. temperature, currently running tasks, etc. As such, a central instance always has more potential for finding optimal solutions than a distributed one. However, the algorithmic complexity rapidly grows, as architectures with several cores running several tasks create a large problem space. Centralized approaches quickly become infeasible even when using a heuristic solution.

A major challenge is thus finding a way to efficiently provide access to global system knowledge while reducing problem complexity – combining the benefits of a centralized approach with those of distributed ones.

- Novel management techniques are required which scale to large multi-core architectures. These techniques should be distributed to reduce bottlenecks (both in communication as well as computation) and avoid having a central point of failure. Furthermore, techniques for distributing and aggregating system knowledge need to be developed to allow distributed DTM to achieve a similar quality as is possible in centralized ones. A general obstacle hindering the adoption of distributed techniques is the difficulty to verify their stability. It is thus necessary to analyze these techniques in this respect to guarantee that the individual instances do not contradict each other in their actions. Local optimizations should not lead to e.g. localized temperature minima that diverge too far from, and thus prevent, a global optimization.

- Furthermore, **emerging 3D architectures** exacerbate all temperature problems. Herein, the challenge lies in adapting DTM techniques for planar multi-core archi-

8 1. Introduction

tectures to ones with multiple layers stacked on top of each other. This requires consideration of the high vertical heat conductance.

While DTM has been a necessity for some time, the above challenges reflect the change in requirements brought on by the recent trends in semiconductor devices and the shift in focus from performance optimization to increasing dependability – all while dealing with the complexity of large-scale multi-core architectures.

#### 1.3. Thesis Contribution

In the scope of this thesis, the above key concerns are addressed with the following:

- This thesis presents an overview of the effects of temperature on key reliability concerns, covering the most dominant aging mechanism as well as timing errors. Here particular emphasis is placed on the analysis of Negative Bias Temperature Instability (NBTI). The studied effects are then used to evaluate the overall effect of thermal management on system lifetime.

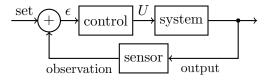

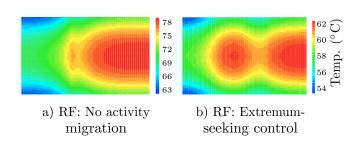

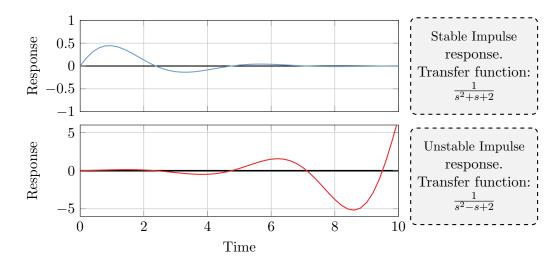

- Thermal management is in essence a control problem. Temperatures are observed by the DTM infrastructure which in turn changes system configuration. This can either occur as a reaction to the observed temperatures directly, or proactively by considering predicting temperatures based on observations. Using control-theory principles, a management method is presented which optimizes temperatures using extremum-seeking control to drive the output temperature function of a system to a minimum.

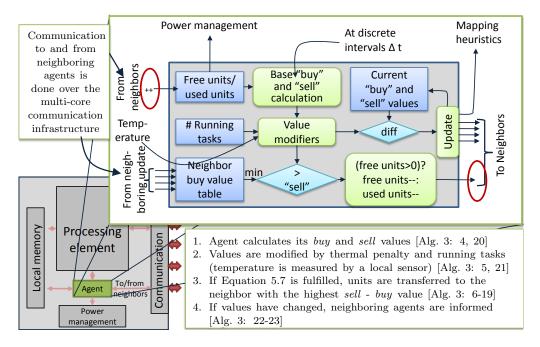

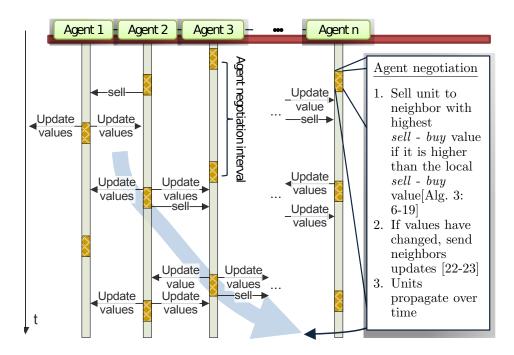

- Scalability is addressed using a fully distributed agent-based system to manage temperature. This system is based on economic principles to distribute a limited power budget among the cores of a multi-core architecture. It exploits the concept of *locality*, making management decisions only in local regions in order to keep the problem space small. Additionally, an analysis of stability is presented to be able to guarantee proper functionality.

- The fully distributed approach is augmented by a hierarchical one. This has been designed with the goal of facilitating access to global system knowledge while sacrificing as little locality as possible. The approach also contains a basic learning technique to be able to increase knowledge about local thermal states. Additionally, this approach is extended to cover the realm of 3D multi-core architectures.

#### 1.4. Thesis Structure and Overview

The rest of this thesis is organized into five chapters; each one dedicated to its own facet of thermal analysis and management. First, Chapter 2 examines the basics of the temperature development and analysis techniques employed in today's systems. This includes a look at the physics underlying heat generation and heat transfer. The analysis section focuses on different forms of temperature measurement – from on-chip sensors to infrared thermal cameras – and thermal simulation techniques. Additionally, an overview of thermal management techniques in multi-core architectures is presented including a glimpse into 3D architectures and their particular thermal caveats.

Chapter 3 explores the link between chip temperature and key reliability concerns. Initially, an overview of some of the most pressing temperature-related aging effects is given. In this context, particular focus is given to Negative Bias Temperature Instability (NBTI) which includes our own models. Afterwards, the effect of thermal management on dependability is examined by taking different DTM strategies and quantifying their impact on chip lifetime. The content of this chapter is based on and expanded from my work in [56] and [15].

Chapter 4 examines thermal temperature from a control-theoretic standpoint and presents an approach for optimizing temperature that first appeared in [44]. This approach specifically targets microarchitectural components where the performance overhead of migrating computation can be kept low. Analysis is performed using measurements of an FPGA-based implementation as well as through simulation of an implementation in a superscalar register file.

Chapter 5 carries thermal management concepts into the realm of multi-core systems. This chapter presents two proactive thermal management approaches. The first of these is a fully distributed approach based on the economic principle of supply and demand. The second is a hierarchical approach based on auctions that encompasses rudimentary learning. This approach also deals with the challenge of managing temperature in 3D multi-core architectures. The approaches were first introduced in [43] and [45], respectively.

Chapter 6 presents a summary of this thesis and provides an outlook into future work.

## 2. Thermal Basics and Related Work

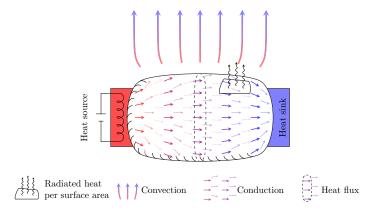

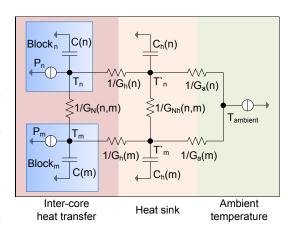

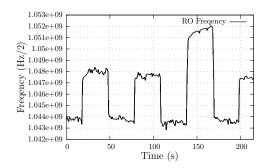

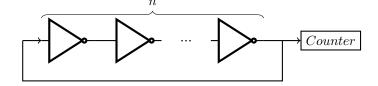

Before analyzing the effects of temperature on dependability, it is first necessary to examine the thermal characteristics of a chip. It must be clear how and where heat is created and how it spreads. In this chapter we take a look at these issues and present both theoretical and experimental methods for quantifying these characteristics.

Temperature distribution itself is a well-studied topic, and its development over time can be expressed by the first law of thermodynamics: a change in system temperature is equal to the amount of heat energy supplied/removed to the system (Q) plus the work (W) done by the system. In semiconductor devices, this work equates to power consumption. In the form of a differential equation, the first law of thermodynamics is the following [30]:

$$dT = \delta Q + \delta W \tag{2.1}$$

For CMOS circuits, the power consumption consists of both dynamic and static power, which are dominated by switching and leakage power, respectively. Switching power, which is expressed as [87]

$$P_{switch} = \alpha C f v^2, \tag{2.2}$$

is determined by the load capacitance C of a circuit, the operating frequency f, and the voltage V. Here  $\alpha$  is an *activity* factor that states the fraction of the capacitance affected, i.e. which logic gates of the circuit are switching and what fraction of C they represent.

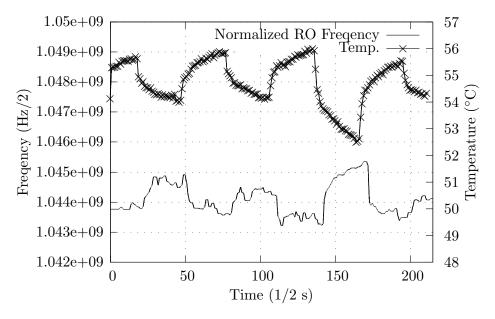

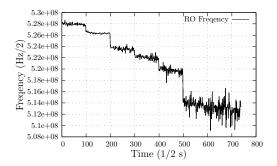

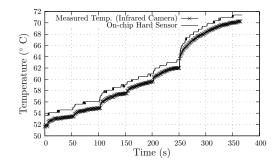

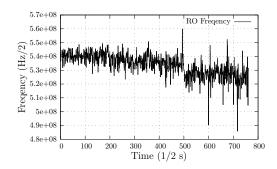

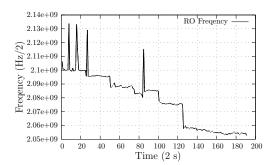

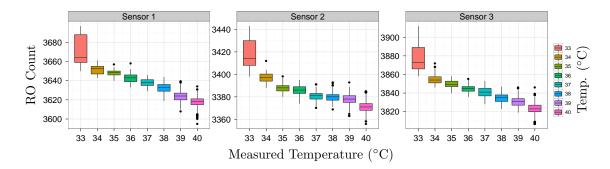

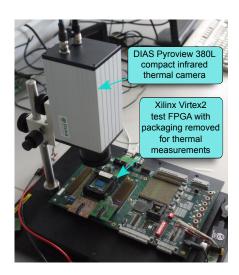

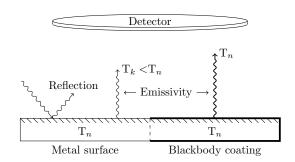

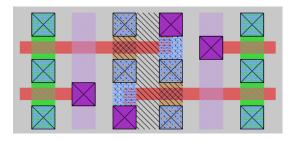

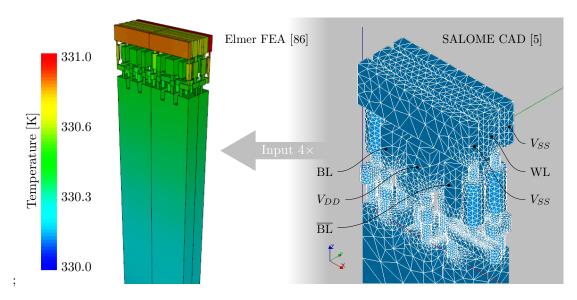

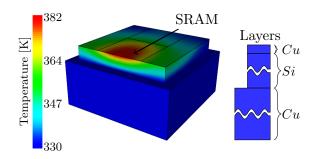

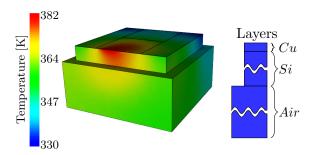

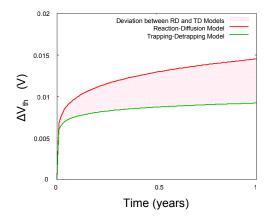

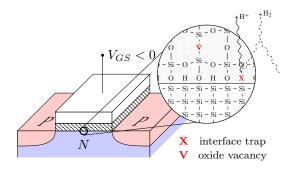

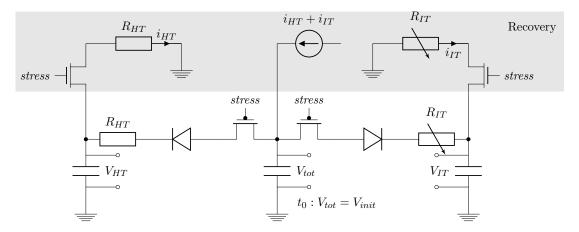

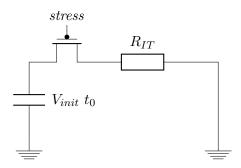

It becomes evident from Equation 2.2 what parameters can be adjusted to perform thermal management based on switching power. Since it factors in quadratically, reducing voltage is the most efficient way of reducing temperature. Reducing activity is possible by changing the physical hardware design or distributing activity over a larger area<sup>1</sup>. Of course, these parameters exhibit interdependencies. For instance voltage and frequency have a quasi-linear relationship since the voltage determines how fast capacitances can be charged. Thus a given frequency will have a minimum required voltage and a given voltage will have a maximum possible frequency.