# Cross-Layer Resiliency Modeling and Optimization: A Device to Circuit Approach

Zur Erlangung des akademischen Grades eines

Doktors der Ingenieurwissenschaften

an der Fakultät für Informatik des Karlsruher Instituts für Technologie (KIT)

genehmigte

Dissertation

von

Saman Kiamehr

Tag der mündlichen Prüfung: 11.05.2015

Referent: Prof. Dr. Mehdi Baradaran Tahoori

KIT, Karlsruhe, Germany

Korreferent: Dr. Sani Nassif

Radyalis, Austin, TX, USA

| Saman Kiamehr<br>Dragonerstr. 9<br>76185 Karlsruhe                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Hiermit erkläre ich an Eides statt, dass ich die von mir vorgelegte Arbeit selbstständig verfasst habe, dass ich die verwendeten Quellen, Internet-Quellen und Hilfsmittel vollständig angegeben haben und dass ich die Stellen der Arbeit - einschlielich Tabellen, Karten und Abbildungen - die anderen Werken oder dem Internet im Wortlaut oder dem Sinn nach entnommen sind, auf jeden Fall unter Angabe der Quelle als Entlehnung kenntlich gemacht habe. |

| Karlsruhe, Mai 2015                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Saman Kiamehr                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

#### ACKNOWLEDGEMENT

I am using this opportunity to express my gratitude to everyone who supported me throughout my Ph.D. study.

Foremost, I would like to express my sincere gratitude to my advisor Prof. Mehdi Tahoori for his continuous support, patience, motivation and enthusiasm. His guidance and support helped me overcome many difficulties throughout my research and finish this dissertation. He has been a tremendous mentor for me and I could not have imagined having a better advisor and mentor for my Ph.D. study.

I am also grateful to my co-advisor Dr. Sani Nassif. He provided me with direction, technical support and became more of a friend, than a co-advisor. Dr. Nassif is the one who truly made a difference in my life.

A special thanks to my family. Words cannot express how grateful I am to my mother and father for all of their exceptional sacrifices through my entire life. I would like to express appreciation to my beloved wife Hajar who has been always my support.

I would also like to thank all of the colleagues from the Chair of Dependable Nano Computing (CDNC) for their discussions, feedback, invaluably constructive criticism and friendly advices. In particular, I want to thank Farshad Firouzi, Fabian Oboril and Mojtaba Ebrahimi.

# CONTENTS

| wledgement                                                                                                                                                                                                                                                                        | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                   | vii<br>xi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| f Figures                                                                                                                                                                                                                                                                         | xiii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| f Tables                                                                                                                                                                                                                                                                          | χV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Own Publications Included in Thesis                                                                                                                                                                                                                                               | xvii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| act                                                                                                                                                                                                                                                                               | xix                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| nmenfassung                                                                                                                                                                                                                                                                       | xxi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Sources of unreliability                                                                                                                                                                                                                                                          | 1<br>3<br>5<br>7<br>8                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| ackground                                                                                                                                                                                                                                                                         | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Basic terminology of CMOS technology 2.1.1. MOSFET transistors 2.1.2. Basic CMOS gates 2.1.3. FinFET transistors Reliability issues Process variation 2.3.1. Sources of front-end variability 2.3.2. Process variation in emerging technologies 2.3.3. Process variation modeling | 133<br>133<br>155<br>166<br>177<br>199<br>200<br>200<br>200<br>200<br>27                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                   | f Figures  f Tables  f Own Publications Included in Thesis  act  nmenfassung  roduction  Sources of unreliability  Challenges for modeling and mitigation of unreliability  Contribution of this thesis  Outline  ackground  ckground  ckground  ckground  ckground  Reliability issues  Process variation  2.3.1 Sources of front-end variability  2.3.2 Process variation in emerging technologies  2.3.3 Process variation modeling  Transistor aging  2.4.1 Bias Temperature Instability (BTI) |

#### CONTENTS

|     | 2.5.       | Voltage droop                                                                  | 29        |

|-----|------------|--------------------------------------------------------------------------------|-----------|

|     |            | 2.5.1. Voltage droop metrics and important parameters                          | 30        |

|     |            | 2.5.2. Voltage droop model                                                     | 30        |

|     | 2.6.       | Soft error                                                                     | 31        |

|     |            | 2.6.1. Sources of radiation                                                    | 32        |

|     |            | 2.6.2. Basic physical mechanism of soft error                                  | 33        |

|     | 2.7.       | Summary                                                                        |           |

|     |            |                                                                                |           |

| 11. | <i>ر</i> پ | oss-Layer Modeling and Prediction of Reliability Issues                        | 35        |

|     |            |                                                                                | 33        |

| 3.  | •          | o-level Modeling and Analysis of Electrical Masking of Soft Errors Overview    | <b>37</b> |

|     |            | Introduction, motivations and contributions                                    | 37        |

|     | 3.3.       |                                                                                |           |

|     |            | Overall flow                                                                   |           |

|     |            | Pulse propagation modeling                                                     | 39        |

|     |            | Pulse propagation and SER estimation                                           | 42        |

|     | 5.0.       | 3.6.1. Backward transient pulse propagation                                    | 42        |

|     |            | 3.6.2. SER estimation algorithm                                                | 43        |

|     | 3.7.       | Experimental results                                                           | 44        |

|     | 0.1.       | 3.7.1. Accuracy of LUT-based method                                            | 44        |

|     |            | 3.7.2. Effect of voltage droop on overall SER                                  | 46        |

|     |            | 3.7.3. Runtime                                                                 | 46        |

|     | 3.8        | Summary                                                                        |           |

|     | 0.0.       | Summerly 1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.                                |           |

| 4.  | Rad        | ation-induced Soft Error Analysis of SRAMs in SIO-FinFET Technology            | 49        |

|     | 4.1.       | Overview                                                                       | 49        |

|     | 4.2.       | Introduction, motivations and contributions                                    | 49        |

|     | 4.3.       | Related work                                                                   | 50        |

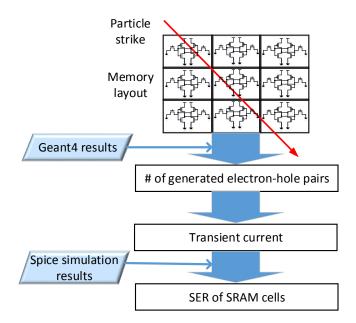

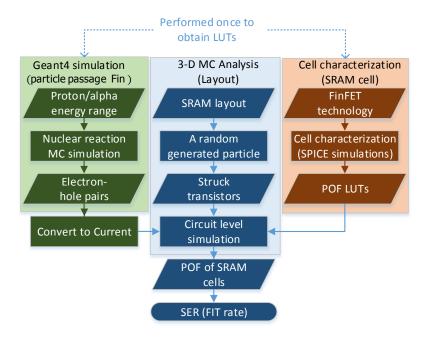

|     | 4.4.       | Overall flow                                                                   | 51        |

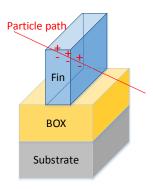

|     | 4.5.       | 3-D Analysis of particle strike with fin structure                             |           |

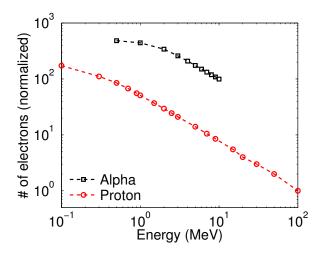

|     |            | 4.5.1. Interaction of particles and material                                   | 52        |

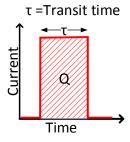

|     |            | 4.5.2. Radiation-induced parasitic transient current pulse                     | 52        |

|     | 4.6.       | SRAM cell soft error characterization                                          | 54        |

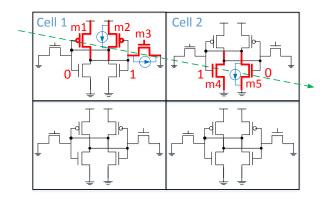

|     | 4.7.       | 3-D memory array analysis                                                      | 55        |

|     |            | 4.7.1. Probability Of Failure (POF) due to a particle strike with a particular |           |

|     |            | energy range                                                                   | 55        |

|     |            | 4.7.2. Failure In Time (FIT) rate calculation                                  | 56        |

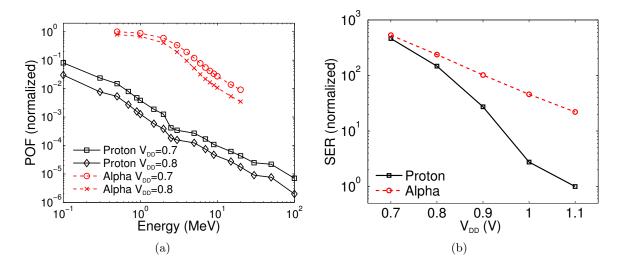

|     | 4.8.       | Simulation results                                                             | 57        |

|     | 4.9.       | Summary                                                                        | 59        |

| _   | The        | Import of Duncasa Variation and Stanbastic Asims in Namassala VI SI            | 61        |

| 5.  | 5.1.       | Impact of Process Variation and Stochastic Aging in Nanoscale VLSI  Overview   | <b>61</b> |

|     | 0          |                                                                                |           |

|     | 5.2.       | Introduction, motivations and contributions                                    | 61        |

|     | 5.3.       | Related work                                                                   | 62        |

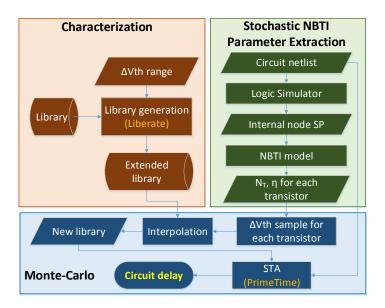

|     | 5.4.       | Circuit level simulation flow                                                  | 63        |

|     |            | 5.4.1. Library cell characterization                                           | 63        |

|     |            | 5.4.2. Stochastic NBTI parameter extraction                                    | 64        |

|     |            | 5.4.3. Monte-carlo simulation                                                  | 64        |

| Bi | hliog | raphy                                                                  | 105 |

|----|-------|------------------------------------------------------------------------|-----|

| 8. | Sum   | nmary and conclusions                                                  | 103 |

|    | 7.7.  | Summary                                                                | 102 |

|    | 7.6.  | Experimental results                                                   | 100 |

|    |       | 7.5.2. HCI reduction                                                   | 100 |

|    | - '   | 7.5.1. NBTI reduction                                                  |     |

|    | 7.5.  | Reordering methodology                                                 |     |

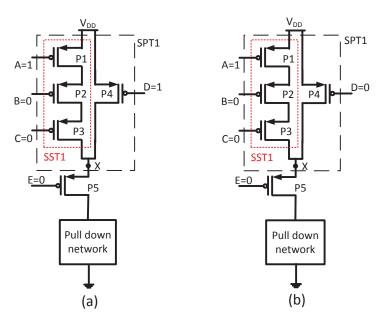

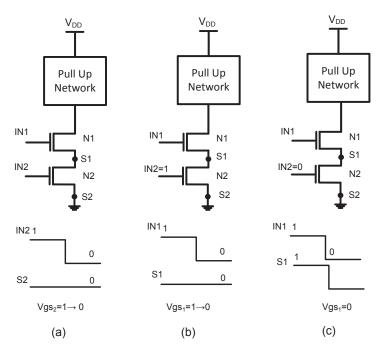

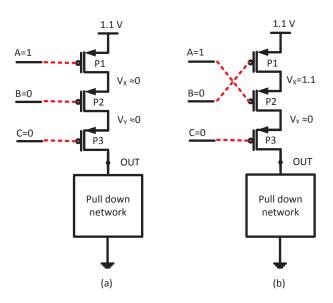

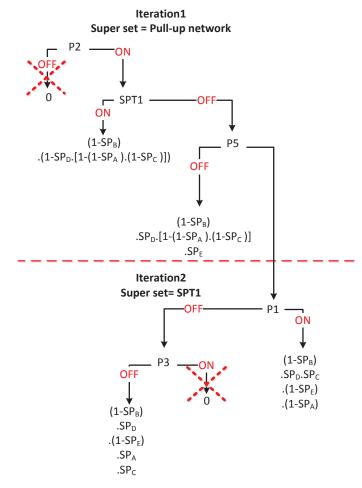

|    |       | 7.4.2. Stacking effect on HCI                                          |     |

|    | 1.4.  | 7.4.1. Stacking effect on NBTI                                         |     |

|    |       | Related work                                                           |     |

|    |       | Introduction, motivations and contributions                            |     |

|    |       | Overview                                                               |     |

| 7. |       | at and Transistor Reordering for Aging Reduction in Complex CMOS Gates | 91  |

|    | _     |                                                                        | _   |

|    | 6.6.  | •                                                                      |     |

|    |       | 6.5.4. Effect of voltage and temperature variation                     |     |

|    |       | 6.5.3. Library size                                                    |     |

|    |       | 6.5.2. Aging mitigation                                                |     |

|    | 0.5.  | Simulation results                                                     |     |

|    | 6.5.  | 6.4.2. Technology mapping using aging-aware standard cell library      |     |

|    |       | 6.4.1. Aging-aware cell library                                        |     |

|    | 6.4.  | Cell library redesign and mapping                                      |     |

|    | 6.3.  |                                                                        |     |

|    |       | Related work                                                           |     |

|    |       | Overview                                                               |     |

| 6. |       | ability-aware Standard Cell Library Design                             | 77  |

|    | . 110 | liability-aware Cell and Circuit Design                                | 13  |

|    | Do    | liability aware Call and Circuit Design                                | 75  |

|    |       |                                                                        |     |

|    | 5.6.  | Summary                                                                |     |

|    |       | 5.5.6. Runtime of the proposed variation-aware timing analysis         |     |

|    |       | 5.5.5. Effect of workload                                              |     |

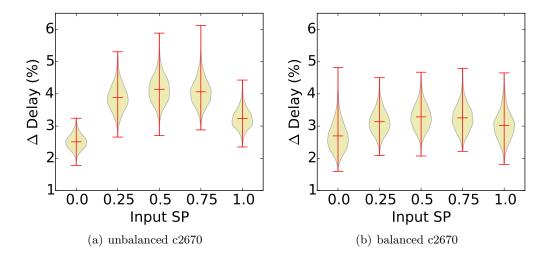

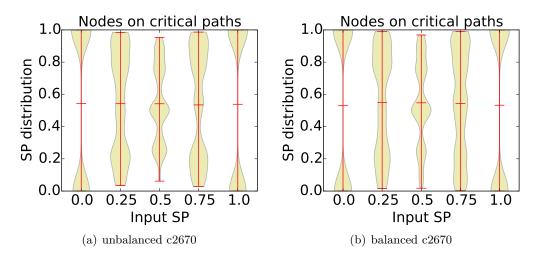

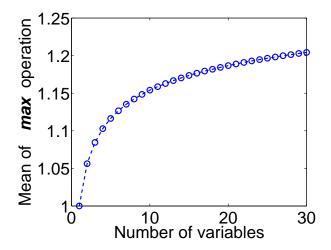

|    |       | 5.5.4. Effect of balanced paths in complex circuits                    |     |

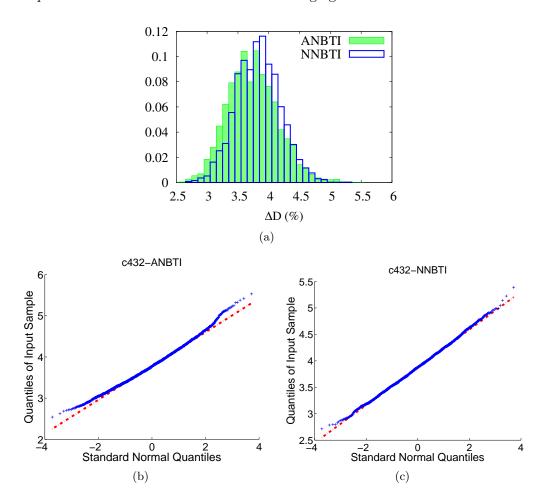

|    |       | 5.5.2. Atomistic NBTI model vs equivalent normal NBTI model            |     |

|    |       | 5.5.1. Simulation setup, terms and definitions                         |     |

|    | 5.5.  | Results and discussion                                                 |     |

|    | 5 5   | Pagulta and dispussion                                                 | 65  |

## $Symbols \;|\; B \;|\; C \;|\; D \;|\; E \;|\; F \;|\; H \;|\; L \;|\; M \;|\; N \;|\; P \;|\; R \;|\; S \;|\; T \;|\; V$

#### **Symbols**

$V_{DD}$  Supply voltage.

$V_{DS}$  Drain-source voltage of transistor.

$V_{GS}$  Gate-source voltage of transistor.

$V_{SB}$  Source-body voltage of transistor.

$\tau_c$  capture time.

$\tau_c$  capture time.

В

**BTI** Bias Temperature Instability.

C

Capture time Time needed to charge a gate oxide defect during the stress phase.

**CHC** Channel Hot Carrier.

**CMOS** Complementary metal-oxide-semiconductor.

**CNTFET** Carbon Nanotube Field Effect Transistors.

D

Duty cycle Ratio of the time in which transistor is under stress to the total time.

Ε

**EM** Electromigration.

**Emission time** Time needed for the defect to re-emit its charge during the recovery phase.

F

**FinFET** Fin Filed Effect Transistor.

```

FIT Failure In Time.

Н

HCI Hot Carrier Injection.

L

LER Line-edge Roughness.

Μ

MBU Multiple Bit Upset.

MOSFET Metal-oxide-semiconductor field effect transistor.

Ν

NBTI Negative Bias Temperature Instability.

NMOS n-type transistor.

Р

PBTI Positive Bias Temperature Instability.

PMOS p-type transistor.

R

RD Reaction-Diffusion.

RDF Random Dopant Fluctuation.

S

SCE Short Channel Effect.

SER Soft Error Rate.

SEU Single-Event Upset.

SOI Silicon On Insulator.

SP Signal Probability.

Т

TD Trapping-Detrapping.

TDDB Time Dependent Dielectric Breakdown.

٧

VLSI Very Large Scale Integration.

```

# LIST OF FIGURES

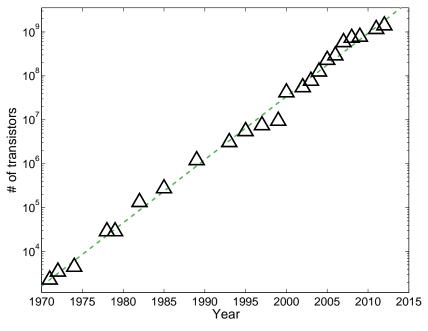

| 1.1.  | The number of transistors of Intel processors                                            | 1  |

|-------|------------------------------------------------------------------------------------------|----|

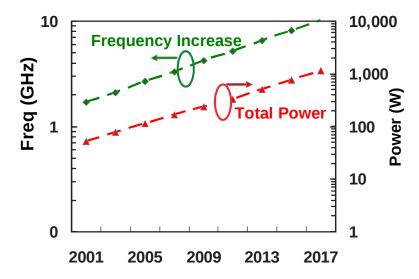

| 1.2.  | Frequency and power consumption trend for different technology nodes over time           | 2  |

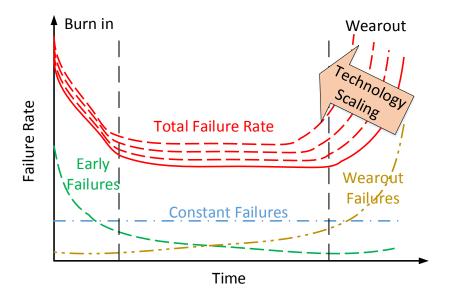

| 1.3.  | Failure rate Bathtub curve                                                               | 3  |

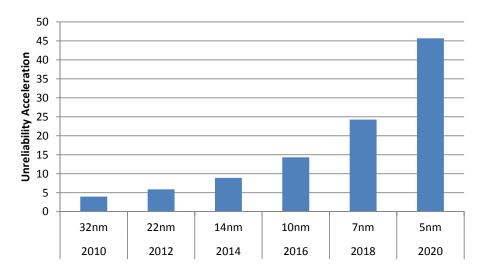

| 1.4.  | Unreliability acceleration due to scaling for different technology nodes                 | 3  |

| 1.5.  | SRAM cell memory affected by a soft error                                                | 4  |

| 1.6.  | Timing failure due to variation in the path delay                                        | 4  |

| 1.7.  | Guard-banding to avoid failures due to process and runtime variation                     | 5  |

| 1.8.  | Contribution of different reliability issues on the total unreliability of VLSI circuits | 5  |

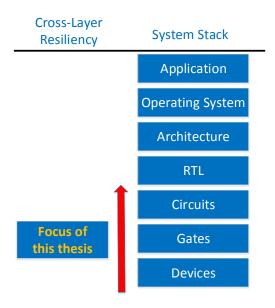

| 1.9.  | System stack and cross layer resiliency                                                  | 6  |

| 2.1.  | MOSFET structure                                                                         | 13 |

| 2.2.  | Transistors as switches                                                                  | 14 |

| 2.3.  | Different states of transistor operation                                                 | 14 |

| 2.4.  | Transistor level implementation of CMOS gates                                            | 15 |

| 2.5.  | Definition of the gate delay and signal transition time                                  | 15 |

| 2.6.  | Dependency of an inverter delay to load capacitance and inputs transition time           | 16 |

| 2.7.  | Short Channel Effect of different transistor structures                                  | 17 |

| 2.8.  | Structure of a SOI FinFET                                                                | 17 |

| 2.9.  | Components of chip guard-band for the IBM Power<br>7+ $\dots$                            | 18 |

| 2.10. | Line-edge Roughness (LER) definition in the transistor                                   | 20 |

| 2.11. | Different BTI mechanisms                                                                 | 21 |

| 2.12. | NBTI-induced $V_{th}$ shift                                                              | 23 |

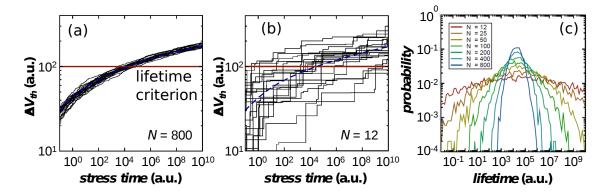

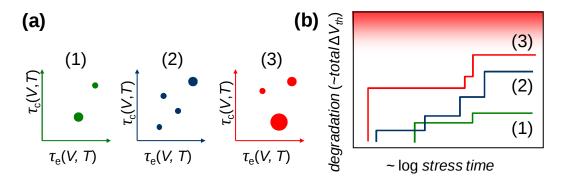

| 2.13. | Deterministic and stochastic BTI                                                         | 24 |

| 2.14. | Stochastic atomistic BTI model                                                           | 24 |

| 2.15. | CET and occupancy probability maps                                                       | 25 |

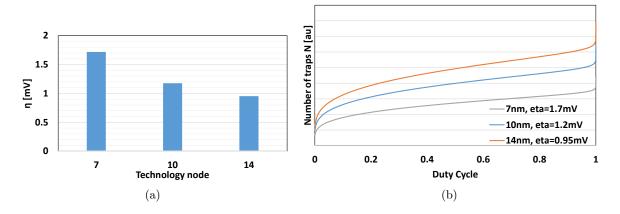

| 2.16. | Parameters of stochastic BTI model for different technology nodes                        | 27 |

| 2.17. | Hot Carrier Injection (HCI) physical mechanism                                           | 28 |

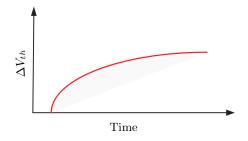

| 2.18. | HCI-induced $\Delta V_{th}$ over time                                                    | 28 |

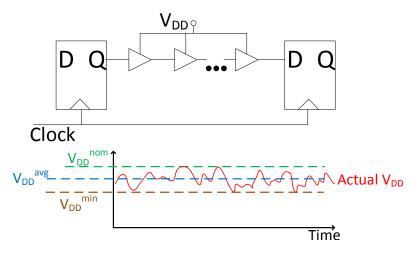

| 2.19. | The supply voltage seen by the gates inside the circuit                                  | 29 |

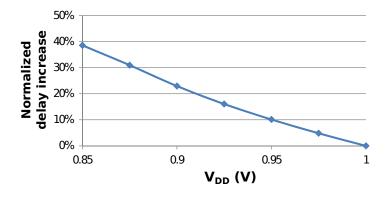

| 2.20. | The effect of voltage droop on the gate delay                                            | 29 |

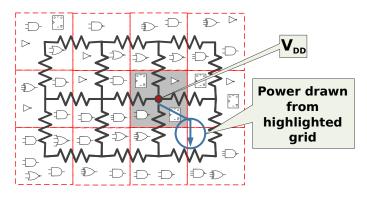

| 2.21. | Equivalent R network model of power grid                                                 | 30 |

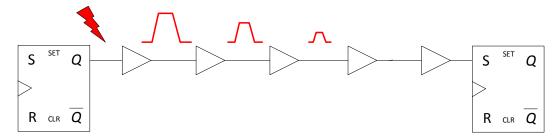

| 2.22. | Electrical masking in logical gates                                                      | 32 |

| 2.23. | Logical and Latching window maskings                                                     | 32 |

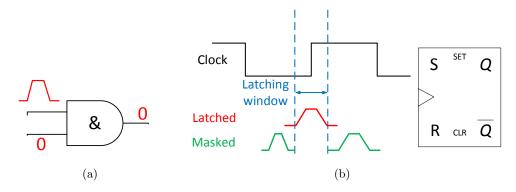

| 2.24. | The spectrum of different sources of radiation at ground level                           | 33 |

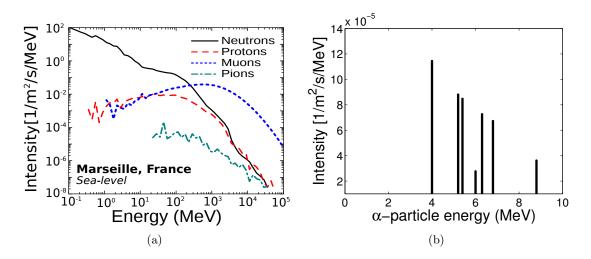

| 2.25. | Physical mechanism of soft error caused by the passage of a charged particle             | 34 |

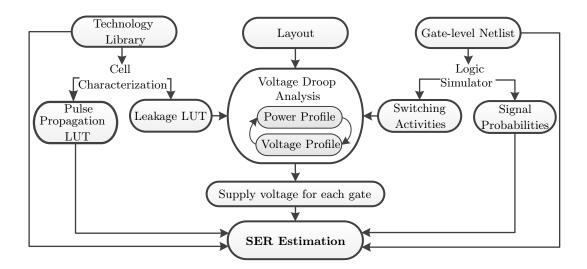

| 3.1.  | The overall flow of the proposed SER estimation considering voltage droop                | 39 |

#### LIST OF FIGURES

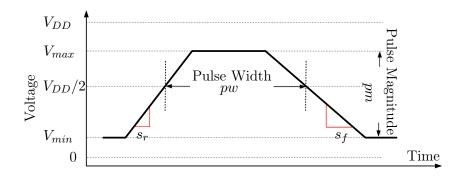

| 3.2.  | Important parameters of trapezoidal model for transient pulse                         | 40  |

|-------|---------------------------------------------------------------------------------------|-----|

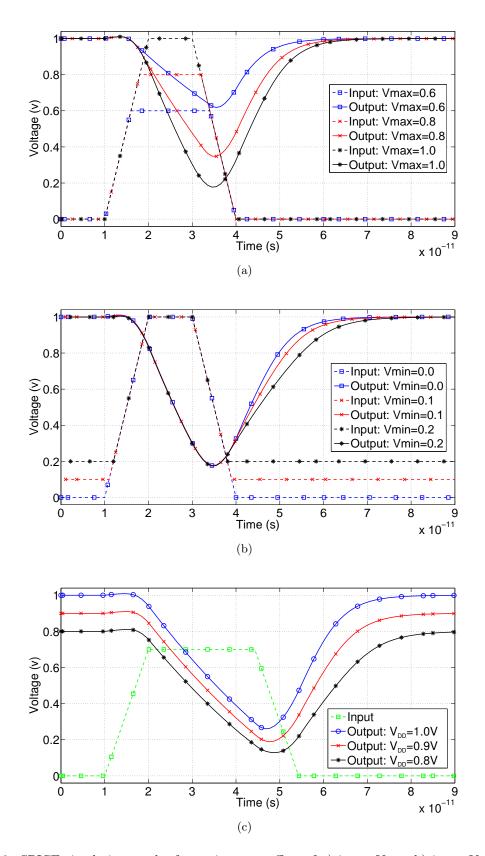

| 3.3.  | The effect of different parameters on the shape of output transient pulse             | 41  |

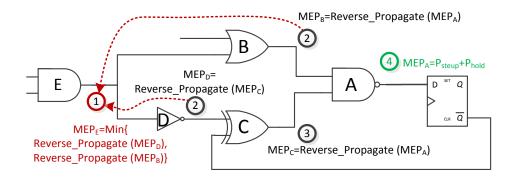

| 3.4.  | An Example of Backward Propagation of MEPs                                            | 43  |

| 4.1.  | The overall flow of SER estimation                                                    | 51  |

| 4.2.  | 3-D structure of SOI FinFET                                                           | 52  |

| 4.3.  | Number of electrons generated by the interaction of particles with a Fin              | 52  |

| 4.4.  | Parasitic current model                                                               | 53  |

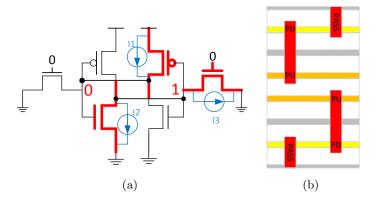

| 4.5.  | 6T SRAM cell and its layout                                                           | 54  |

| 4.6.  | Overall flow SER estimation of memory array for SOI FinFET technology                 | 55  |

| 4.7.  | Flow of obtaining probability of failure of different SRAM cells                      | 56  |

| 4.8.  | Probability of failure and FIT rate of memory cells                                   | 57  |

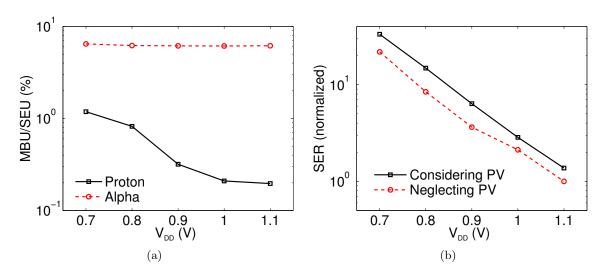

| 4.9.  | MBU vs. SEU and the effect of process variation the SER estimation                    | 58  |

| 5.1.  | Flow of proposed stochastic NBTI and process variation aware timing analysis .        | 63  |

| 5.2.  | $\Delta D$ distributions for atomistic NBTI (ANBTI) and normal NBTI (NNBTI)           | 66  |

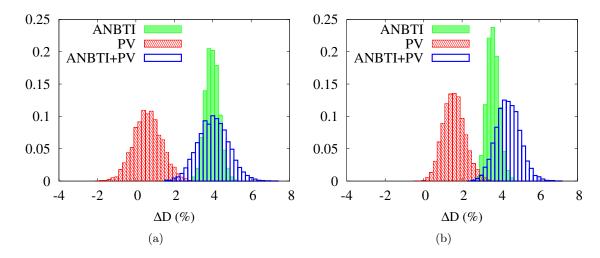

| 5.3.  | $\Delta D$ distributions for atomistic NBTI, process variation and combined effects . | 68  |

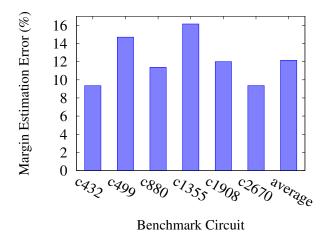

| 5.4.  | Timing margin error due to separately consideration of different variation effects    | 68  |

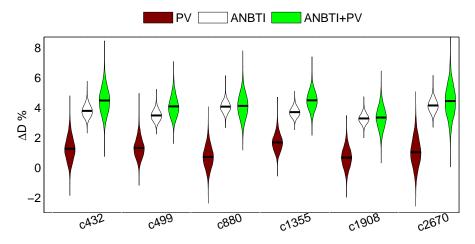

| 5.5.  | Violin plot of NBTI and process variation-induced $\Delta D$                          | 69  |

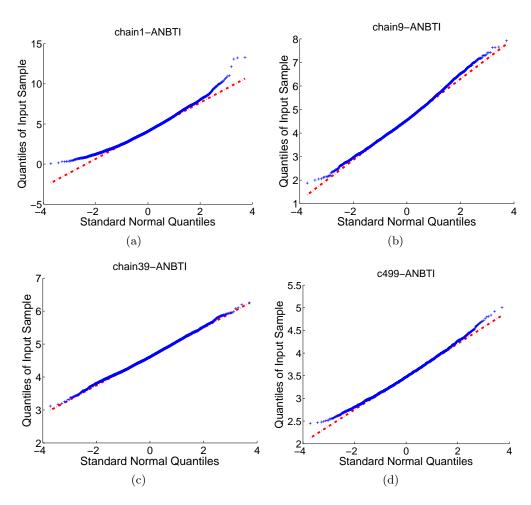

| 5.6.  | QQ-plot of different circuits with different number of levels and critical paths .    | 70  |

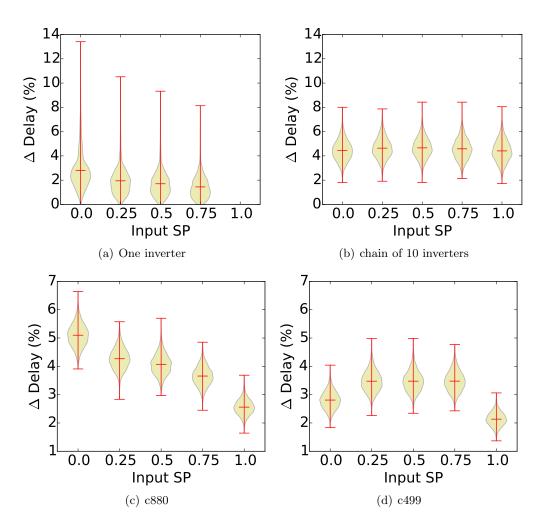

| 5.7.  | Effect of workload on ANBTI-induced $\Delta D$ distribution of the circuit            | 71  |

| 5.8.  | Effect of workload on ANBTI-induced $\Delta D$ distribution of c2670 circuit          | 71  |

| 5.9.  | Effect of workload on signal probability distribution of nodes on critical paths .    | 72  |

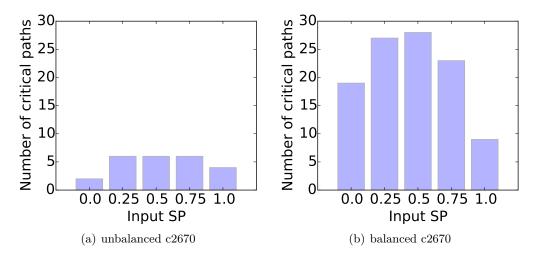

| 5.10. | Number of critical paths for c2670 circuit                                            | 72  |

| 5.11. | The mean value of the maximum of $n$ random variables                                 | 73  |

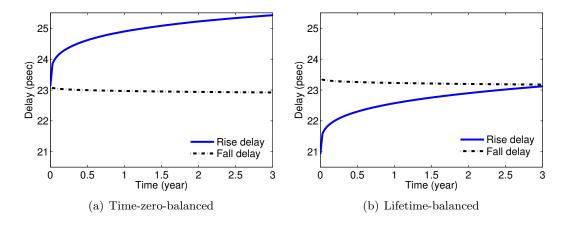

| 6.1.  | Effect of $Wp/Wn$ optimization on NBTI-induced delay degradation                      | 78  |

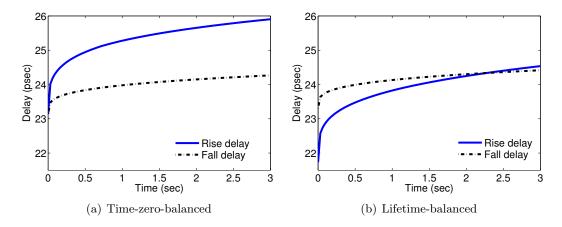

| 6.2.  | Effect of $Wp/Wn$ optimization on BTI-induced delay degradation                       | 79  |

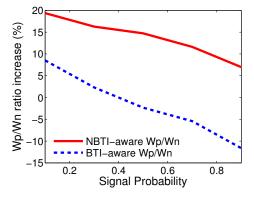

| 6.3.  | Optimized $Wp/Wn$ ratio increase for different signal probabilities                   | 79  |

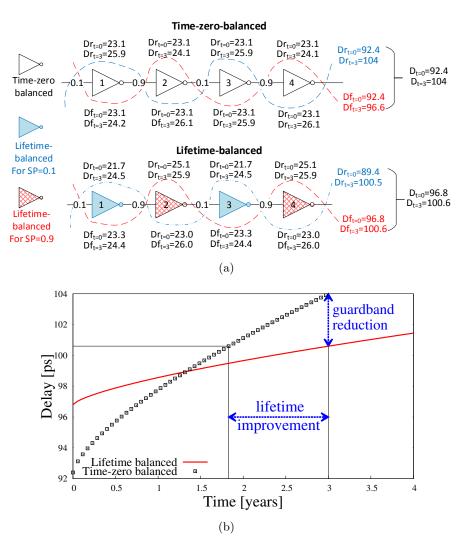

| 6.4.  | A simple circuit to show the efficiency of aging-aware standard cell sizing           | 81  |

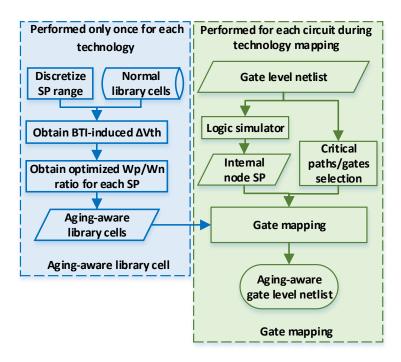

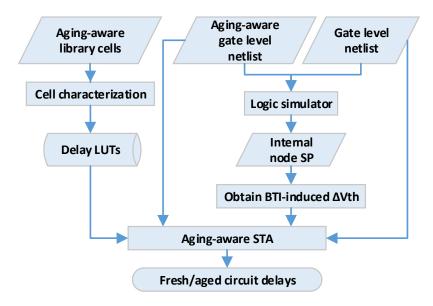

| 6.5.  | Overall flow of proposed aging-aware standard cell library design                     | 82  |

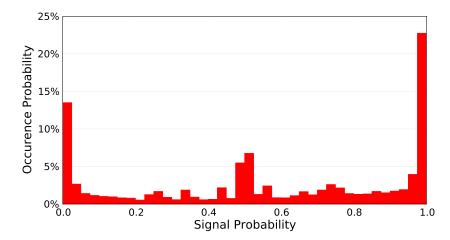

| 6.6.  | The histogram of internal node SP distribution for ISCAS89 benchmark circuits         | 83  |

| 6.7.  | Overall flow to obtain simulation results                                             | 85  |

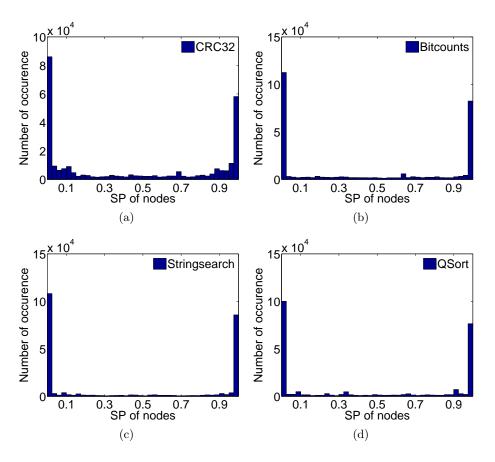

| 6.8.  | Histogram of the internal node SPs of different applications                          | 88  |

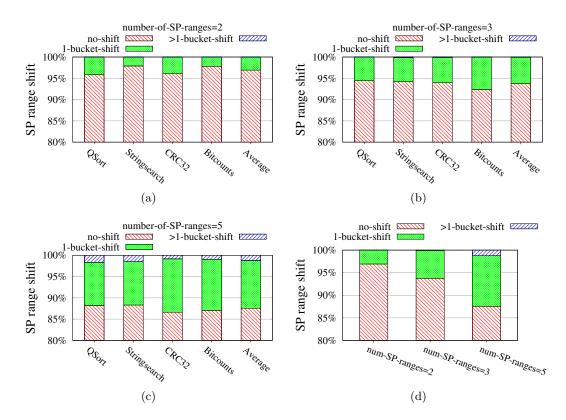

|       | Effect of different workload on the SP range of internal nodes                        | 89  |

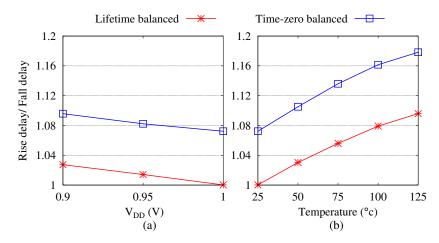

| 6.10. | Effect of voltage and temperature variation on the rise/fall delay ratio              | 90  |

| 7.1.  | Stacking effect in a 3 input NOR gate                                                 | 94  |

| 7.2.  | Stacking effect in a complex gate                                                     | 94  |

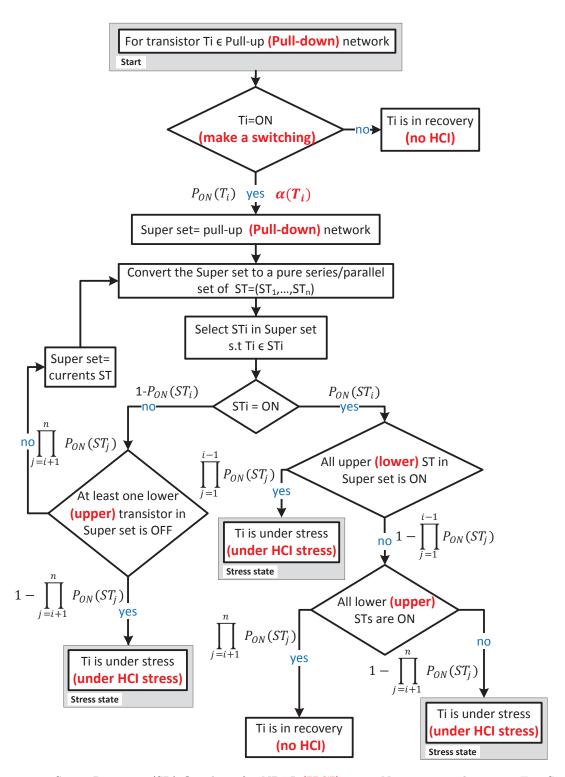

| 7.3.  | Stress-Recovery (SR) flowchart for NBTI and HCI in an N input complex gate            | 96  |

| 7.4.  | Stacking effect in a NAND gate                                                        | 97  |

| 7.5.  | Input reordering in a 3 input NOR gate                                                | 98  |

| 7.6.  | Stress-probability tree: effective duty cycle calculation                             | 99  |

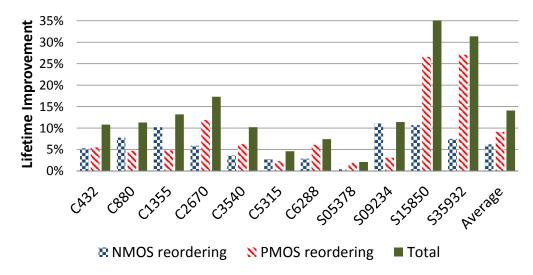

| 7.7.  | Lifetime improvement using the proposed input and transistor reordering technique     | 101 |

# LIST OF TABLES

| 2.1.       | RD model of NBTI-induced $\Delta V_{th}$                                             | 23  |

|------------|--------------------------------------------------------------------------------------|-----|

| 3.1.       | Sampling Points of LUT-based Method for 45 nm Standard Cell Library                  | 45  |

| 3.2.       | Accuracy/runtime of LUT-based model in comparison with SPICE simulation .            | 45  |

| 3.3.       | Error due to Neglecting Voltage Droop on SER                                         | 46  |

| 3.4.       | Runtime of Proposed Electrical Masking Method                                        | 46  |

|            |                                                                                      |     |

| 5.1.       | Information of the normalized $\Delta D$ distribution induced by runtime and process |     |

|            | variations and the combined effect                                                   |     |

| 5.2.       | Runtime of proposed variation-aware timing analysis                                  | 73  |

| <b>ፍ</b> 1 | Efficiency of proposed aging-aware standard cell design technique                    | 96  |

| 0.1.       | Emiciency of proposed aging-aware standard cen design technique                      | 80  |

| 7.1.       | Effective Activity Factor of a 2-input NAND gate                                     | 99  |

| 7.2.       | Delay degradation of benchmark circuits                                              | 100 |

| 7.3.       | Effect of Input Reordering on Lifetime                                               | 101 |

#### LIST OF OWN PUBLICATIONS INCLUDED IN THESIS

#### Journal Papers:

[1] S. Kiamehr, M. Ebrahimi, F. Firouzi, and M. Tahoori, "Extending Standard Cell Library for Aging Mitigation," in *IET Computers & Digital Techniques*, 2015.

#### Conference Papers:

- [2] S. Kiamehr, F. Firouzi, and M. Tahoori, "Stacking-based Input Reordering for NBTI Aging Reduction," in *Proceedings of Zuverlässigkeit und Entwurf (ZuE)*, 2011, Germany.

- [3] S. Kiamehr, F. Firouzi, and M. Tahoori, "Input and Transistor Reordering for NBTI and HCI Reduction in Complex CMOS Gates," in *Proceedings of Great Lake Symposium on VLSI (GLSVLSI)*, 2012, USA.

- [4] S. Kiamehr, F. Firouzi, and M. Tahoori, "Aging-aware Timing Analysis Considering Combined Effects of NBTI and PBTI," in *Proceedings of International Symposium on Quality Electronic Desing (ISQED)*, 2013, USA.

- [5] S. Kiamehr, M.Ebrahimi, F. Firouzi, and M. Tahoori, "Chip-level Modeling and Analysis of Electrical Masking of Soft Errors," in *Proceedings of VLSI Test Symposium (VTS)*, 2013, USA.

- [6] S. Kiamehr, F. Firouzi, M. Ebrahimi, and M. Tahoori, "Aging-aware Standard Cell Library Design," in *Proceedings of Design, Automation & Test in Europe (DATE)*, 2014, Germany.

- [7] S. Kiamehr and M. Tahoori, "A Cross-Layer Approach for Soft Error Analysis of SRAMs in SOI FinFET Technology," in *Workshop on Silicon Errors in Logic-System Effects (SELSE)*, 2014, USA.

- [8] S. Kiamehr, T. Osiecki, M.B. Tahoori, and Sani Nassif, "Radiation-Induced Soft Error Analysis of SRAMs in SOI FinFET Technology: A Device to Circuit Approach," in *Proceedings of Design Automation Conference (DAC)*, 2014, USA.

- [9] S. Kiamehr, P. Weckx, M.B. Tahoori, B. Kackzer, H. Kukner, P. Raghavan, G. Groeseneken, and F. Catthoor, "The Impact of Process Variation and Stochastic Aging in Nanoscale VLSI," Submitted to International Test Conference (ITC), 2015, USA.

Very-large-scale integration (VLSI) circuits have changed our life. We use them in a wide range of applications such as personal computers, smart TVs, and cars. The VLSI circuits are also being used in critical domains, such as air-plains and medical sectors. Therefore, their *reliability*, defined as performing consistently according to their specifications, is very important.

The never ending demand for higher performance and lower power consumption pushes the VLSI industry to further scale the technology down. However, further downscaling of technology at nano-scale leads to major challenges. Reduced reliability is one of them, arising from multiple sources e.g. runtime variations, process variation, and transient errors.

System failures caused by unreliability sources can lead to a wide range of consequences: from financial loses, when the faulty system is used for example for banking application, to even loss of human life when the system is used in transportation or medical sector. To avoid/minimize these consequences, the reliability needs to be modeled, predicted, and mitigated. This mandates the circuit designers to consider reliability as another constraint on top of the conventional constraints such as power and performance.

Designers tried to model different sources of unreliability in order to predict the lifetime of the system. Reliability can be modeled and predicted at different levels of abstractions: from device level, which leads to an accurate but high runtime analysis, up to application level which leads to a fast but inaccurate analysis. However, unreliability sources at nanoscale are more sophisticated and their modeling is more challenging for two main reasons. Firstly, some of the unreliability sources are interdependent and they interact which each other in the way they affect system behavior. If they are modeled and considered separately, it may lead to a wrong reliability prediction. Therefore, there is a need to consider all these sources and their interdependencies to accurately predict the lifetime of the system. Secondly, by technology scaling into deep nano-meter era some of the unreliability sources, e.g. transistor aging, have some intrinsic variabilities. This makes the device level models more complex. Due to this complexity, the runtime of detailed device level analysis becomes even larger which makes it infeasible to be used for large circuits. Therefore, it is important to abstract the stochastic device-level reliability models to be used at higher levels of abstraction.

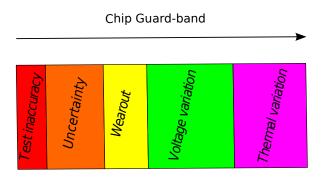

In order to mitigate the reliability challenges such as transistor aging and process variation, one common approach is to add margins (guard-banding) to the design specifications (e.g. clock cycle) to guarantee the correct performance of the circuit. However, the required margin is increasing by technology scaling which erodes the benefit obtained from down-scaling. Therefore the reliability not only needs to be considered at the end of design flow (where the reliability is predicted and a suitable guard-banding is considered), but also it needs to be addressed in the entire design flow (a reliability-aware circuit design flow) in order to mitigate the unreliability and hence to reduce the amount of the required margin.

The objective of this thesis is to tackle unreliability with a cross layer approach from device up to circuit level. The contribution of this thesis is twofold: i) cross-layer modeling and prediction of reliability and ii) reliability-aware cell and circuit design.

In the first part of the thesis a cross layer modeling approach is proposed to cover a wide

range of reliability challenges (combined effect of process and runtime variations, together with transient errors) affecting the system behavior during lifetime operation. In our cross-layer approach, the information from the device level is abstracted to analyze the reliability at circuit level in order to make a trade-off between accuracy and runtime. Our hierarchical approach enables us to perform reliability analysis with a reasonable runtime while maintaining high accuracy. We try to address the interdependent unreliability sources together in order to reduce the inaccuracy of reliability analysis caused by separate consideration of the interdependent unreliability sources. Moreover, the intrinsic variability of unreliability sources, e.g. transistor aging, is considered in our approach and the stochastic information is abstracted to circuit level information which can be used for the analysis at higher levels of abstraction (e.g. architecture level).

In the second part of the thesis, two novel reliability-aware cell and circuit design techniques are proposed to mitigate the issue of accelerated transistor aging, which can significantly impact the circuit lifetime and the system reliability. In both techniques, the device and the gate level aging information is analyzed, and according to this information, the circuit is modified in order to mitigate the effect of transistor aging on the performance of the circuit. With the help of our proposed aging mitigation techniques, the lifetime of the circuit can be improved with very low amount of area and power overheads.

The results of this study show that our cross-layer modeling approach can accurately capture the combined effect of interdependent unreliability sources and their intrinsic variations on the reliability of the circuit. It is shown that considering the interdependent sources of unreliability separately (like state-of-the-art approaches) might lead to a large inaccuracy in the reliability estimation of the circuit which can eventually lead to an over-design (large overhead) or underdesign (low reliability). Moreover, the results of the proposed circuit-level reliability analysis can be used at higher abstraction levels such as architecture level. In addition, it is shown that the proposed reliability-aware cell and circuit design techniques can effectively mitigate the aging effect and hence lead to a lower guard-band with negligible overheads.

Hochintegrierte digitale Schaltkreise haben unser tägliches Leben stark verändert und kommen in einem sehr weiten Anwendungsspektrum zum Einsatz, z.B. in PCs, Fernsehern oder Autos. Darüber hinaus werden sie auch in kritischen Domänen verwendet, etwa in Flugzeugen oder im medizinischen Bereich, weshalb ihre Zuverlässigkeit von besonderer Bedeutung ist.

Die ständig steigenden Anforderungen an die Leistungsfähigkeit und Energieeffizienz zwingt die Schaltkreis-Industrie dazu die Transistorabmessungen immer weiter zu verkleinern. Allerdings bringt dies auch zahlreiche Herausforderungen mit sich. Eine dieser Herausforderungen ist die sinkende Zuverlässigkeit der Schaltkreise verursacht durch eine Vielzahl von Effekten wie z.B. Parameterschwankungen zur Laufzeit, Prozessschwankungen während der Herstellung und transiente Fehler.

Systemfehler die durch solche Zuverlässigkeitsprobleme hervorgerufen werden, können dabei weitreichende Konsequenzen nach sich ziehen, angefangen von finanziellen Verlusten (z.B. im Bankensektor) bis hinzum Verlust von menschlichem Leben falls Systeme im Transportoder Medizin-Sektor betroffen sind. Um derartige Konsequenzen zu vermeiden ist es daher notwendig, die Zuverlässigkeit zu modellieren, etwaige Probleme vorherzusagen und zu verhindern. Deshalb müssen Schaltkreisentwickler die Zuverlässigkeit als einen weiteren Design-Aspekt, neben den traditionellen Parametern wie Leistungsfähigkeit oder Energiebedarf, miteinbeziehen.

Die Zuverlässigkeit kann dabei auf unterschiedlichen Abstraktionsebenen modelliert werden, angefangen bei der Transistorebene, die zwar sehr genau aber dafür sehr zeitaufwändige Analysen erlaubt, bis hinauf zur Anwendungsebene, die eine schnelle dafür aber auch weniger exakte Untersuchung ermöglicht. Erschwerend kommt hinzu, dass die Zuverlässigkeitsprobleme oftmals eng miteinander verbunden sind, so dass eine unabhängige Modellierung mehrerer Faktoren zu einem falschen Ergebnis führen kann. Deshalb ist es notwendig alle Problemquellen und ihre gegenseitigen Einflüsse mit in die Zuverlässigkeitsbetrachtung einzubeziehen. Eine weitere Schwierigkeit in diesem Zusammenhang sind die intrinsischen Schwankungen einiger Zuverlässigkeitsphänomene (z.B. Transistoralterung) bei Verwendung von extrem kleinen Transistoren. Diese führen dazu, dass die Modelle noch komplexer werden, da stochastische Aspekte mitberücksichtigt werden müssen, was wiederum zu steigenden Analysezeiten führt. Daher ist es sehr wichtig die stochastischen Modelle auf Transistorebene zu abstrahieren um auch auf höheren Abstraktionsebene schnelle aber dennoch akkurate Analysen durchführen zu können.

Um Zuverlässigkeitsprobleme verursacht etwa durch die beschleunigte Transistoralterung oder Prozessvariationen zu vermeiden, führen Designer üblicherweise zusätzliche Sicherheitsmargen ein. Allerdings werden diese Margen mit zunehmender Verkleinerung der Transistorabmessungen immer größer, so dass die Vorteile von kleineren Strukturbreiten immer geringer ausfallen. Aus diesem Grund muss die Zuverlässigkeit der Schaltung bereits während des Designprozesses als zusätzlicher Aspekt miteinbezogen werden, damit die Sicherheitsmargen verkleinert werden können und somit eine höhere Leistungsfähigkeit der Schaltung erreicht werden kann.

Das Ziel dieser Doktorarbeit ist es die Zuverlässigkeitsprobleme mit einem Cross-Layer Ansatz zu adressieren, d.h. unter Berücksichtigung der Abstraktionsebenen zwischen Transistor-

und Schaltkreisebene. Die wesentlichen Beiträge dieser Arbeit sind dabei: i) Cross-Layer Modellierung und Vorhersage von Zuverlässigkeitsproblemen, und ii) Design-Methoden für Gatter und Schaltkreise unter Berücksichtigung der Zuverlässigkeit.

Im ersten Teil der Arbeit wird dazu ein Cross-Layer Modellierungsansatz vorgestellt, der zahlreiche Zuverlässigkeitsprobleme umfasst (Prozess- in Kombination mit Laufzeitschwankungen und transienten Fehlern). Für diesen Ansatz werden Informationen auf Transistorebene abstrahiert um eine Zuverlässigkeitsuntersuchung auf Schaltkreisebene zu ermöglichen, die sowohl schnell als auch hinreichend genau ist. Wir berücksichtigen dabei die Zusammenhänge der einzelnen Zuverlässigkeitsprobleme, um die Ungenauigkeiten einer unabhängigen Betrachtungsweise zu reduzieren. Darüber hinaus werden intrinsische Schwankungen von Zuverlässigkeitsproblemen wie etwa der Transistoralterung mit in die Betrachtung einbezogen, und stochastische Modelle auf Schaltkreisebene entwickelt.

Im zweiten Teil der Arbeit werden zwei neue Designansätze für den Gatter- und Schaltkreis-Entwurf vorgestellt, die die Zuverlässigkeit als Designparameter miteinbeziehen. Hierfür wird insbesondere die beschleunigte Transistoralterung untersucht, die die Lebensdauer und Zuverlässigkeit der Schaltung signifikant beeinträchtigen kann. Basierend auf den gewonnenen Alterungserkenntnissen werden die Gatter und Schaltkreise derart modifiziert, dass die Alterungseinflüsse abgeschwächt werden, und gleichzeitig nur geringe Energie- und Flächenkosten entstehen.

Die Ergebnisse dieser Arbeit zeigen, dass der Cross-Layer Modellierungsansatz den kombinierten Einfluss von sich beeinflussenden Zuverlässigkeitsproblemen sehr genau erfassen kann. In diesem Zusammenhang zeigen die Ergebnisse auch, dass eine unabhängige Untersuchung dieser Zuverlässigkeitsprobleme (wie in der Literatur üblich) zu großen Ungenauigkeit führen kann, was schlussendlich entweder die Zuverlässigkeit beeinträchtigt oder zu unnötig großen Sicherheitsmargen führt. Darüber hinaus wird gezeigt, dass die Gatter- und Schaltkreis-Entwurfsmethoden sehr effektiv sind, und damit deutlich kleineren Sicherheitsmargen verwendet werden können.

## INTRODUCTION

There are more and more electronics in our nowadays life. Most prominent examples are obviously the devices that connect us, such as smart phones and iPads. However, there is the other class of embedded devices where many people are not aware of how much electronics is involved. Cars wouldn't drive, planes wouldn't fly, factories wouldn't manufacture without the electronic devices. Electronics needs to be reliable, otherwise it would result in minor discomforts (Facebook not working) or catastrophes (planes falling from sky).

Very Large Scale Integration (VLSI) technology is the enabling technology for the wide range of electronic devices we use in our daily life which have changed the way we live nowadays [2]. The VLSI devices now is being used in the personal entertainment systems, automotive industry, medical electronic systems and financial sector. The range of applications is continuously growing which pushes the design and manufacturing to scale the VLSI technology (transistor dimensions) down to obtain more complex systems with smaller size (portable devices), lower power consumption, higher performance and reduced cost [2]. For this purpose, the microelectronic industry has been trying to follow the Moore's law [3], to shrink the device feature size (transistor dimensions) in a way that the number of transistors on a die doubles approximately

Figure 1.1.: The number of transistors of Intel processors [1]

Figure 1.2.: Frequency and power consumption trend for different technology nodes over time [10]

every two years. Figure 1.1 illustrates the number of transistors of Intel processors since 1970 which perfectly shows the consistency with Moore's law.

Although technology scaling provides many opportunities which enables building extremely complex gates and achieving better computing performance, it faces many challenges [4]. Power issue [5] (see Figure 1.2), short channel effect [6], and in particular yield and *reliability* issues [4, 7, 8] are the most important challenges that the VLSI technology is faced due to the technology scaling. Due to the wide range of the VLSI chips applications, the unreliability of these chips can lead to a broad range of consequences from computer crashes and loss of data to financial losses and even loss of human life [9].

Reliability, as an important nano-scale technology issue, can be quantified by the probability that a system operates correctly without a failure until time t [11]:

$$R(t) = P(T > t) = \int_{t}^{\infty} f(x)dx \tag{1.1}$$

where T is the duration of normal system operation without a failure and f(x) is the failure probability density function.

A failure occurs when for example there is an error in the functionality of the system or a wrong bit value is read or written in the memory cell [12]. The failures happen due to faults which can be categorized into two categories [11, 13]: i) permanent faults: is caused due to physical defects in the components of a circuit (such as wearout) which can permanently alter the circuit function [11–14]. ii) temporal faults: which is caused by transient or intermittent disturbances which affect the circuit for a short period of time (not permanently) [11, 13, 14]. In general these faults can affect the reliability of the VLSI chip as shown in the bathtub curve depicted Figure 1.3.

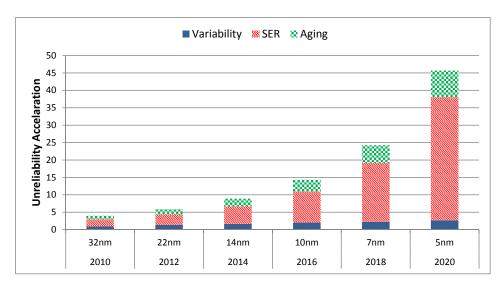

Technology scaling deep into nanometer era, makes the reliability issues more pronounced. Figure 1.4 shows the predicted unreliability acceleration (increase of failure rate) for different technology nodes. According to the figure, the failure rate increases exponentially as the technology scales down. This bring us to the domain in which the traditional design flows do not work [4] and the designers should rethink how to change the design flow in order to not only optimize the power and performance but also meet the reliability and yield constraints. However, designing a reliable system out of unreliable component is very challenging. For this purpose, the reliability issues need to be well understood, modeled and mitigated.

Figure 1.3.: Failure rate Bathtub curve

# 1.1. Sources of unreliability

Among all the reliability issues in nano-meter technology, process variation, time dependent variation and soft error are some of the most important issues [7–9].

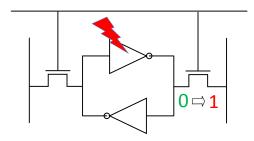

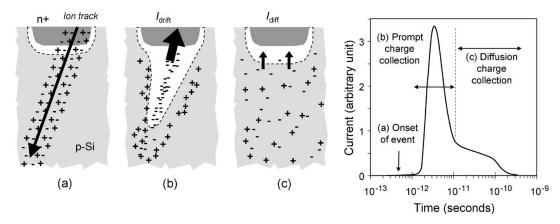

Soft error is a temporal failure caused by cosmic ray radiation and alpha particle generated from packaging materials. It can cause a flip in the status of memory (see Figure 1.5) or sequential elements of the circuit (e.g. latch and flip-flops). Therefore, several methods have been proposed to protect memory [16, 17] and sequential elements [18] against this type of error. Soft errors can also affect the combinational logic part of the circuit by generating a transient pulse which may be propagated to sequential elements. Although the combinational logic soft error was not a big issue in the previous technology nodes, its contribution is sharply increasing by scaling in deep nano-meter regime [9, 15].

Process variation and time dependent variation lead to a variation in the properties of the

Figure 1.4.: Unreliability acceleration due to scaling for different technology nodes normalized to the failure rate at 32 nm technology node [15]

Figure 1.5.: SRAM cell memory affected by a soft error

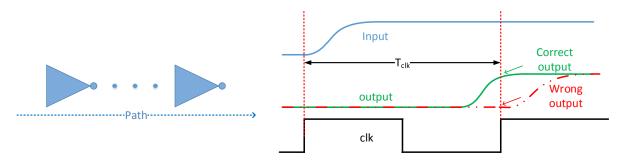

circuit (e.g. delay and power) compared to the indented specification during the design time. If the timing and/or power constraints are not met due to these variations, a failure might happen. Figure 1.6 shows a simple example in which the timing constraint is not met and a wrong value is stored in the memory or sequential elements leading to a failure.

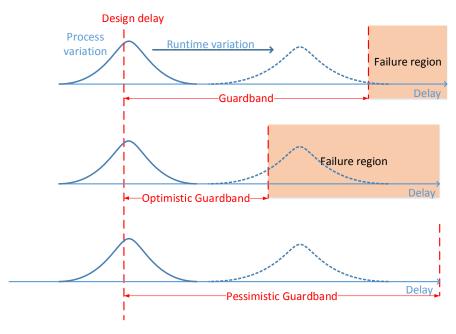

Process variation is a natural device (transistors) parameter variation (e.g. threshold voltage) among different devices [19]. There are many physical issues leading to process variation, however, the statistical fluctuation of channel dopant is a major cause of variation among devices in deep nano-meter technology [19]. Due to process variation, the performance of the fabricated circuit (e.g. circuit delay) becomes a statistical value as shown in Figure 1.7.

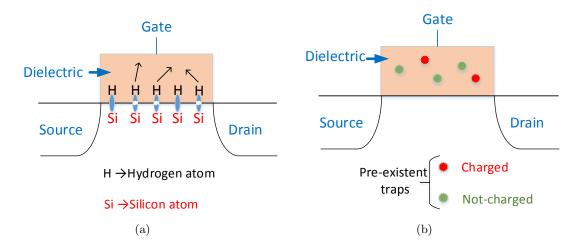

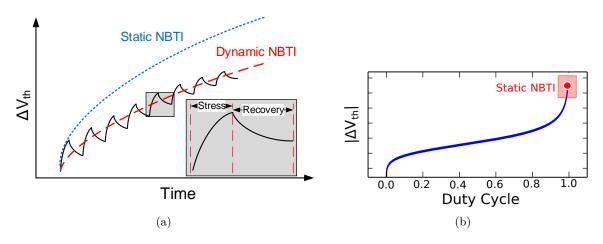

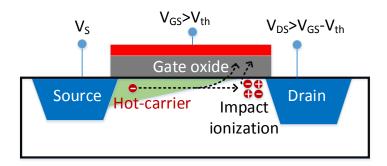

The other set of variability is the time dependent variation. Due to this variation, even two completely identical devices (transistors) with the same initial characteristics may have different characteristics over time according to their different working conditions such as temperature and workload [7]. Transistor aging as one of the most important sources of time dependent variability [7–9] is due to different degradation mechanisms: Negative Bias Temperature Instability (NBTI), Positive Bias Temperature Instability (PBTI) and Hot Carrier Injection (HCI).

In order to address different types of variability, a safety timing margin (guard-band) is added to the design to guarantee the reliable operation of the designed system. However, an optimistic or pessimistic guard-banding may lead to a large failure rate or an over design (less performance), respectively (see Figure 1.7).

In summary, all the aforementioned reliability issues are threatening the reliable operation of the system and the situation becomes worse by technology scaling. Figure 1.8 shows the contribution of different reliability issues on the total failure rate of the VLSI circuit for different technologies. According to the figure, the failure rate is increasing. Therefore it is very important to model and mitigate these sources of reliability issues.

Figure 1.6.: Timing failure due to variation in the path delay

Figure 1.7.: Guard-banding to avoid failures due to process and runtime variation

# 1.2. Challenges for modeling and mitigation of unreliability

The reliability can be addressed at different levels of abstraction from device level up to application level (see Figure 1.9). At the device level, the reliability is modeled with complex and detailed models which are very hard (almost infeasible) to be used at high levels of abstraction, e.g. architecture level, due to the very large runtime of analysis for large circuits. The situation becomes worse by technology scaling since some of the reliability issues, e.g. transistor aging, have some intrinsic variability [20]. This means that stochastic models need to be used for these reliability issues which makes the models even more complex.

Moreover, some of the unreliability sources have interdependencies. In other words, they affect each other which means that the impact of one issue may be aggravated or alleviated in the presence of other issues. For example, the impact of transistor aging is affected in

Figure 1.8.: Contribution of different reliability issues on the total unreliability of VLSI circuits [15]

Figure 1.9.: System stack and cross layer resiliency

the presence of process variation. Therefore, it is important to consider the interdependent sources of unreliability together since considering these sources separately may lead to an overestimation or underestimation of the reliability impacts.

Due to the aforementioned complexity of device level modeling and interdependency of different sources of unreliability, it is very challenging to come up with some models which can be used at higher levels of abstraction. Using the complex and time-consuming models considering these interdependencies makes it infeasible to be used for large circuit (e.g. an entire processor) due to issues such as simulation runtime. Therefore, the models need to be simplified, however, the simplification is obtained at the cost of inaccuracy. Putting all together, it is important to come up with scalable models which give a good trade-off between runtime and accuracy.

If the reliability is accurately modeled and predicted, suitable countermeasures can be applied to guarantee the correct performance of the chips. One common practice in the current technologies is to add timing margin (guard-banding) to avoid circuit failures due to reliability challenges such as runtime and process variabilities. However, by technology scaling, the additional required timing margin increases (i.e. lower performance) which erodes the benefit obtained from down-scaling. Therefore, the reliability needs to be considered in the early stages of the design as a constraint in addition to conventional constraints (such as power and delay).

The objective of this thesis is to model and optimize the circuit reliability in the presence of nanoscale unreliability effects with a cross layer approach from device level up to circuit level. The interdependent reliability challenges are addressed together in order to reduce the inaccuracy of circuit reliability analysis caused by separate consideration of the interdependent unreliability sources. In the proposed cross layer approach, the knowledge at different levels of abstraction from device up to circuit level is combined. The hierarchical approach enables us to perform reliability analysis with a reasonable runtime while maintaining high accuracy.

Moreover, several novel techniques to mitigate the issue of accelerated transistor aging, which can significantly impact the circuit lifetime resiliency and the system reliability, are proposed. For this purpose, the standard cells and the circuit are redesigned in a way that the aging effect is reduced. With the help of our proposed aging-aware cell and circuit design, the lifetime of the circuit can be improved with a very low amount of area/power overheads.

#### 1.3. Contribution of this thesis

As mentioned before, the contribution of this thesis is two-fold: i) cross-layer modeling and prediction of reliability. In the proposed modeling, the interdependency of reliability challenges is considered. Moreover, the intrinsic variation of them is also considered. Using our cross-layer approach, the information from device level is abstracted at circuit level which provides suitable information to be used at higher abstraction levels such as architecture level. ii) reliability-aware cell and circuit design in which we try to consider transistor aging, as an important reliability issue, in early stages of cell and circuit design to make them more resilient against aging effect. Using proposed techniques at gate/circuit level, we can either improve the lifetime of the circuit or decrease the amount aging-induced timing guard-band with negligible area and power overheads. In particular, the new contributions of this thesis are as follows:

#### Cross-Layer Modeling and Prediction of Reliability Issues

- Chip-Level Modeling and Analysis of Electrical Masking of Soft Errors: With continuous downscaling of VLSI technologies, logic cells are becoming more susceptible to radiation-induced soft error. Moreover, increasing complexity of VLSI chips at nanoscale results in voltage droop, which is an important source of runtime variabilities, across the chip. The soft error rate of the chip is dependent on the value of supply voltage which is seen by its gate. Therefore, voltage droop may affect the soft error rate of the chip. To consider this dependency, we present a chip-level soft error analysis which accurately considers the impact of voltage droop across the chip.

- Radiation-Induced Soft Error Analysis of SRAMs in SOI-FinFET technology: A Device to Circuit Approach: A comprehensive analysis of radiation-induced soft errors of SRAMs designed in SOI FinFET technology is presented. For this purpose, we propose a cross layer approach starting from a 3D simulation of particle interactions in FinFET structures up to circuit level analysis by considering the layout of the memory array. This approach enables us to consider the effect of different factors such as supply voltage and process variation on soft error rate of FinFET SRAM memory arrays.

- The Impact of Process Variation and Stochastic Aging in Nanoscale VLSI: With the down-scaling of CMOS technology into deep nano-scale era, the aging effect becomes stochastic due to its widely distributed defect parameters leading to more non-determinism in the functionality of the deeply-scaled circuits. A framework is presented to comprehensively investigate the combined effect of stochastic aging effect and process variation on the performance of the VLSI design at circuit level, by abstracting atomistic aging models (for the stochastic behavior) to the circuit timing analysis flow.

#### Reliability-aware Cell and Circuit Design

• Reliability-aware Standard Cell Library Design: In current VLSI design flow, for each technology node, the building blocks are pre-designed and optimized (at both netlist and layout) and placed in a library, so called *standard cell library*. Then, the circuits are designed and synthesized using these building blocks. Typically, the standard cells are designed considering the area, power and delay without considering the reliability issues, however, the first step to design a reliable circuit is to have reliability-aware standard cell library. In this study, we propose a technique to consider the aging effect in the standard cell library design. Then, we propose a method to adjust the mapping flow according to the new reliability-aware standard cell library.

• Input and Transistor Reordering for Aging Reduction in Complex CMOS Gates: In this study, first we show that the order of cell input connections has a considerable impact on transistor aging. Based on this, we redesign the cell connections in order to reduce the aging effect with no effect on the functionality of the circuit and minimal area and power overheads.

### 1.4. Outline

The rest of this thesis is organized as follows. Chapter 2 as the background chapter is followed by twofold contributions of this thesis: i) cross-layer modeling and prediction of reliability Issues (Chapters 3-5) and ii) reliability-aware cell and circuit design (Chapter 6, 7). Finally the thesis is wrapped out with conclusion and summary in Chapter 8.

After the introduction, in Chapter 2, the necessary background of this thesis is provided. In this chapter, a basic information of transistor structure and functionality is discussed followed by some basic information about the structure of the logic gates and their important properties. Finally, at the end of the section, the important reliability issues and their corresponding models are provided.

After the background section, the thesis continues with its twofold contribution. The first part of contributions (Chapters 3-5) contains a cross-layer modeling and prediction of reliability issues.

In Chapter 3, a new method is proposed to estimate the soft error rate considering voltage droop as an important runtime variability issue which affects the estimation of soft error rate. In this chapter, first the motivation of the work is provided. Afterwards, the related work is discussed. Next, the proposed methodology of soft error rate estimation considering voltage droop is introduced. Then, the experimental results are provided showing the importance of considering voltage droop in soft error estimation. Finally we conclude the chapter.

Chapter 4 provides a cross-layer approach to estimate the soft error rate in SOI-FinFET technology which considers other important issues such as process variation and the effect of supply voltage. In this chapter, first the motivation and contributions of the study are provided. Then, the related work is discussed. Afterwards, the proposed cross-layer approach is provided in three consecutive sections describing the device level, cell level and circuit level analysis, respectively. Then simulation results are provided and finally we conclude the chapter.

At the end of the first part of thesis contribution, Chapter 5 introduces a framework to investigate the combined effect of process variation and stochastic aging effect in FinFET technology at circuit level. In this chapter, after a short introductory about the motivation and contributions of the study, the related work is discussed. Next, the proposed circuit level simulation flow is introduced to obtain the combined effect of stochastic aging and process variation on the circuit delay. Afterwards, the results are provided with a comprehensive discussion about the observations. Finally the achievements are summarized and the chapter is concluded.

The second part of this thesis contributions (Chapter 6, 7) provides new reliability-aware cell and circuit design techniques in order to alleviate the aging effect as an important reliability issue in nano-scale technology nodes.

This part starts with Chapter 6 in which a reliability-aware standard cell library design technique is provided to mitigate the aging effect. In this chapter, first the related work is discussed. Then, the proposed reliability-aware standard cell library is provided. The next section provides a methodology to remap the circuits using the new reliability-aware standard cell library in order to make the circuit more resilient against aging effect. The experimental results are provided afterwards which is followed by conclusion section to summarize the

achievements.

Chapter 7 provides a new input and transistor reordering technique in order to reduce the effect of aging. The first part of the section is an introduction of study including the motivation and contributions. Next, the related work is briefly discussed providing what is missing in state-of-the art. Then, the effect of input and transistor orders on the aging effect of cells are investigated and we show that the order of inputs and transistors has a huge impact on the amount of cell degradation. According to this cell level investigation, the next section provides a circuit level technique to redesign the cell connections and transistors in order to make the circuit more resilient against aging effect. Next, the simulation results are provided and at the end of the chapter, the achievements are summarized and the chapter is concluded.

At the end of this thesis, Chapter 8 is provided which summarizes the achievements and concludes the thesis.

# Part I. Background

## BACKGROUND

# 2.1. Basic terminology of CMOS technology

Complementary metal-oxide-semiconductor (CMOS) is the main technology being used for constructing integrated circuits. In this section a brief fundamental background of CMOS technology is provided. Further details can be found in [21].

#### 2.1.1. MOSFET transistors

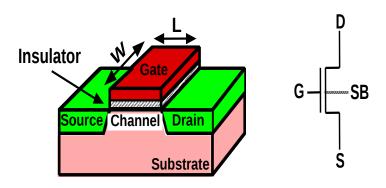

Metal-oxide-semiconductor field effect transistor (MOSFET) is a type of transistor mainly used in CMOS technology. Figure 2.1 shows the structure of a MOSFET transistor. As shown in this figure, a MOSFET consists of Gate (G), Drain (D), Source (S) and Substrate (SB) terminals.

There are two types of MOSFET transistors: n-type MOSFET (referred here as NMOS) and p-type MOSFET (referred here as PMOS). NMOS (PMOS) transistors are made with a p-type (n-type) substrate and their channel contains electrons (holes) as the carriers. The substrate of NMOS (PMOS) transistors are normally connected to ground ( $V_{DD}$  node).

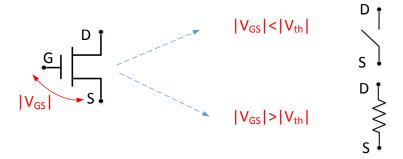

MOSFETs are used as switches as shown in Figure 2.2. When the magnitude of the gatesource voltage of the transistor ( $|V_{GS}|$ ) is less than the magnitude of the transistor threshold voltage ( $|V_{th}|$ ), the MOSFET is OFF and there is no connection between source and drain. Otherwise, if  $|V_{GS}|$  is bigger than  $|V_{th}|$ , the transistor is ON and there is a connection between the source and the drain. However, the transistors are not ideal switches. When the transistor

Figure 2.1.: MOSFET structure

Figure 2.2.: Transistors as switches

is OFF, still a small current is leaked between the drain and the source (so called sub-threshold or leakage current) which is a function of different factors:

$$I_{DS}^{subthreshold} = I_{DS0} \cdot e^{\frac{V_{GS} - V_{th} + \eta V_{DS} - k_{\gamma} V_{SB}}{n\nu_T}} \left(1 - e^{\frac{-V_{DS}}{\nu_T}}\right)$$

(2.1)

where n is a process-dependent term,  $I_{DS0}$  is an empirical parameter,  $\nu_T$  is the thermal voltage,  $\eta$  is a coefficient reflecting drain-induced barrier lowering (DIBL) effect and  $k_{\gamma}$  is a coefficient reflecting body effect. Moreover,  $V_{GS}$ ,  $V_{DS}$ , and  $V_{SB}$  are gate-source, drain-source and source-body voltages, respectively.

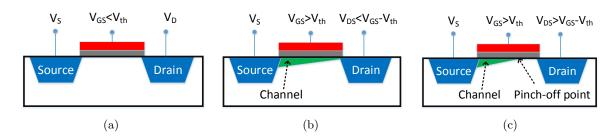

On the other hand, when the transistor is ON, there is a resistance between the source and the drain. In this case, transistor could have two different states according to its drain-source voltage (see Figure 2.3):

• Linear model  $(V_{DS} < V_{GS} - V_{th})$ : In this mode the drain-source current is a function of both  $V_{GS}$  and  $V_{DS}$ .

$$I_{DS}^{ON-lin} = \mu C_{ox} \frac{W}{L} \left( V_{GS} - V_{th} - V_{DS}/2 \right) V_{DS}$$

(2.2)

• Saturation model  $(V_{DS} > V_{GS} - V_{th})$ : In this mode the drain-source current is almost independent of  $V_{DS}$ :

$$I_{DS}^{ON-sat} = \frac{1}{2}\mu C_{ox} \frac{W}{L} (V_{GS} - V_{th})^2$$

(2.3)

where  $\mu$  is the mobility of the carriers (electrons in NMOS and holes in PMOS) and  $C_{ox}$  is the capacitance per unit area of the gate oxide. W and L are the transistors width and length, respectively.

Figure 2.3.: Transistor a) OFF state b) ON state linear mode and c) ON state saturation mode

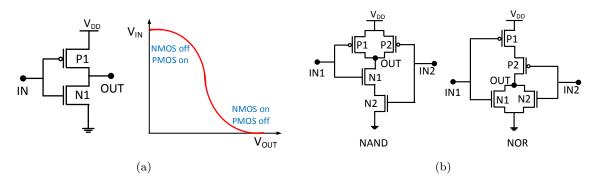

Figure 2.4.: a) CMOS inverter and its DC plot b) two input NAND and NOR CMOS gates

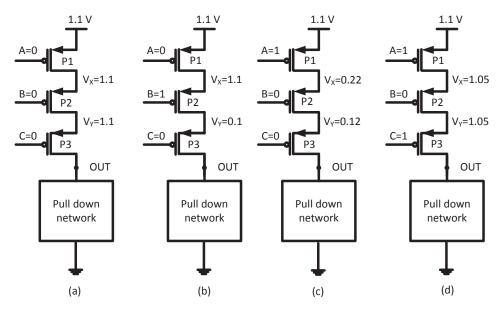

## 2.1.2. Basic CMOS gates

NMOS can only transfer logic 0 (V = 0) ideally and cannot ideally transfer logic 1 ( $V = V_{DD}$ ). For PMOS transistor, the case is the other way around meaning that it can only transfers logic 1 ( $V = V_{DD}$ ) ideally. For this reason, a combination of NMOS and PMOS transistors are used to implement complementary MOS (CMOS) gates. Figure 2.4(a) shows the implementation of a CMOS inverter. As shown in this figure, a PMOS transistor is used as pull-up network to make the output equal to logic 1, when the input is equal to logic 0. On the other hand, an NMOS transistor is used as the pull-down network to convey a logic 0 at the output when the input is equal to logic 1.

Similarly, other types of CMOS gates such as NAND and NOR can be implemented using PMOS and NMOS transistors (see Figure 2.4(b)).

#### Gate delay

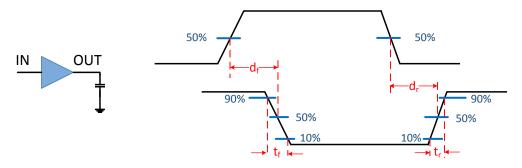

The circuit needs to be designed in way that its delay meets the timing constraint. Therefore, the circuit delay is an important parameter in the design. The circuit delay in turn is a function of its internal gate delays. Therefore, it is important to define the gate delay accurately. For this purpose, the gate propagation delay and the signal transition time are defined as follows (see Figure 2.5):

- Gate propagation delay: Gate delay is defined as the time required for the output to reach 50% of its final output level (50% of supply voltage value) when the input changes to 50% of its final input level (50% of the supply voltage value).

- **Signal transition time**: This term is a representative for the slope of the signal transition. There are two types of transition times:

Figure 2.5.: Definition of the gate delay and signal transition time

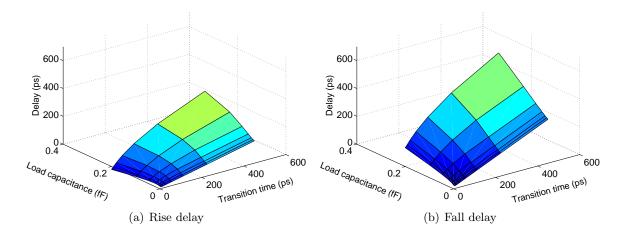

Figure 2.6.: The dependency of a) Rise and b) fall delay of an inverter (using Nangate 45 nm technology library [22]) to output load capacitance and inputs transition time.

- 1. Rise transition time  $(t_r)$ : it is defined as the time required for a signal to reach from 10% (30% for more advanced technology nodes) to 90% (70% for more advanced technology nodes) of its final value when the signal has a rise transition.

- 2. Fall transition time  $(t_f)$ : it is the time required for a signal to reach from 90% (70% for more advanced technology nodes) to 10% (30% for more advanced technology nodes) of its final value when the signal has a fall transition.

The delay of a gate is function of many parameters. On one side, it is a function of gate internal transistors properties, i.e. transistor width, length and threshold voltage. Therefore, the delay of different gates with different internal transistors properties will be different. Moreover, the gate delay is a function of the gates input transition time and the output load capacitance (see Figure 2.6). This means that the delay of similar gates would be different if they have different load capacitances and input signal transition time. Therefore, in a standard library cell, the delay of each standard cell (gate) is provided as a 2-dimensional look-up table (LUT) where one dimension is for output load capacitance and the other one is for input signal transition time.

On top of that, the gate delay is also a function of environmental parameters, e.g. temperature and supply voltage. Temperature affects both carriers mobility and transistor threshold voltage and hence it affects the delay of the gate. The supply voltage impacts the current drawn from transistor (see Equations 2.2 and 2.3) and hence the gate delay.

## 2.1.3. FinFET transistors

According to the Moore's Law, the number of transistors per chip doubles every two years [3]. In order to keep up with the Moor's law, the semiconductor industry have been scaling the dimension (gate length) of MOSFET transistors for more than 40 years. At the end of 1990's the semiconductor companies started manufacturing a new type of transistors called *Silicon On Insulator (SOI)* [23]. In this technology, a layered silicon-insulator-silicon substrate is used in place of conventional silicon substrates and it has two advantages of reduced parasitic capacitances and enhanced current drive compared to conventional MOSFET [23].

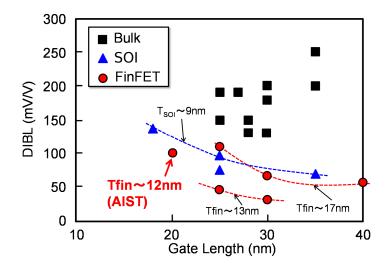

The technology scaling is slowed down recently due to different issues such as *Short Channel Effect (SCE)* and excessively large variations in device properties [25] which makes it infeasible to follow the Moore's law with conventional MOSFET and SOI devices. Therefore, VLSI industry is researching new device structures in order to be able to continue scaling. Among

Figure 2.7.: Drain-induced barrier lowering (DIBL) effect in FinFET, SOI and conventional planar bulk transistor structures [24]

different candidates (such as Carbon Nanotube Field Effect Transistors (CNTFET), multi-gate transistors) Fin Filed Effect Transistor (FinFET) is one of the most promising structures which is already fabricated by Intel [26], GlobalFoundries [27, 28] and TSMC [29]. This is due to the fact that FinFET exhibits superior immunity to short channel effects. Figure 2.7 shows the drain-induced barrier lowering (DIBL) effect, as an important SCE issue, in three different transistor structures [24]. As shown in this figure, FinFET shows the smallest DIBL (highest SCE immunity). Moreover, the effect of process variation on FinFET device performance is less compared with conventional bulk devices [30, 31].

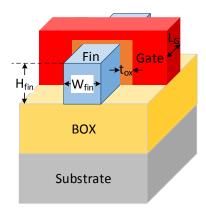

FinFETs can be fabricated as a bulk device or on SOI. Figure 2.8 shows the structure of a SOI FinFET. As shown in this figure, the gate is wrapped around the channel which provides a better control over the channel and as a result the SCE is less in this type of transistors compared to the conventional planar MOSFET and SOI structures.

## 2.2. Reliability issues

With down-scaling of CMOS technology into deep nanometer, reliability has become a major issue [32]. In this section, the general sources of reliability issues in current technology nodes are briefly explained.

Figure 2.8.: Structure of a SOI FinFET

#### 2. Background

The sources of unreliability in current technology nodes can be categorized into three different categories: i) variability issues, ii) transient faults and soft errors iii) permanent faults.