# Predicting Errors in Concurrent Systems

zur Erlangung des akademischen Grades eines

# Doktors der Ingenieurwissenschaften

der KIT-Fakultät für Informatik des Karlsruher Instituts für Technologie (KIT)

genehmigte

# **Dissertation**

von

# Luis M. Carril Rodríguez

aus A Coruña, Spanien

Tag der mündlichen Prüfung: 04-05-2017

Erstgutachter: Prof. Dr. Walter F. Tichy

Zweitgutachter: Prof. Dr. Andreas Oberweis

This work is licensed under a Creative Commons "Attribution-NonCommercial-NoDerivatives 4.0 International" license

## Abstract

The unstoppable popularity of multicore chips has made concurrent programming ubiquitous. Parallel programming is difficult; multiple control flows and non-determinism make the development error-prone. Additionally, it introduces a new set of errors such as data races, deadlocks, or order violations. These errors are difficult to find due to the large number of possible interleavings in a parallel program.

Dynamic analysis techniques execute a program and perform some checks on the observed execution. Dynamic analysis is precise, as it relates to an actual execution with real values and states. These approaches generate false negatives due to non-explored paths and interleavings. The different interleavings are manifested with varying frequency because of external factors such as compilers, processors, or workloads.

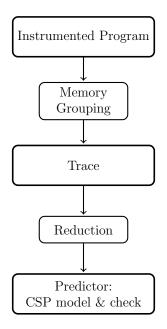

In this work we present an approach that predicts errors from a single trace of a parallel program. We compute alternative interleavings off-line to reduce the timing effects of the observed execution. Using a process algebra, we build a model that generalizes the ordering of the trace, extrapolating possible interleavings. The model is explored for different concurrency errors. A predicted error is accompanied by a schedule, which is enforced in the program to manifest the error.

The approach has been evaluated for deadlock and data race detection, and compared with other dynamic approaches. While maintaining or increasing precision, between 50% and 86% fewer false warnings were produced. The presented tool and its model are also customizable to support other kinds of ordering failures. These failures require a specification that defines the relevant events in the program and describes their valid or invalid orderings. This feature is demonstrated in seven use cases.

# Kurzfassung

Die Verbreitung von Multikernprozessoren hat die parallele Programmierung allgegenwärtig gemacht. Parallele Programmierung ist schwierig, da sie die Entwicklung auf Grund vielfacher Kontrollflüsse und Nicht-Determinismus fehleranfällig macht. Zusätzlich gibt es neue Arten von Fehlern, wie z.B. Wettläufe, Verklemmungen oder Reihenfolgeverletzung. Diese Fehler sind wegen der großen Anzahl von möglichen Verschränkungen schwer zu finden.

Dynamische Analyseansätze führen das Programm aus und untersuchen die beobachtete Ausführung. Dynamische Analyse ist präzise, da sie eine tatsächliche Ausführung mit realen Werten und Zuständen beobachtet. Diese Ansätze erzeugen falsch Negative, wegen nicht erforschter Wege und Verschränkungen. Die unterschiedlichen Verschränkungen treten mit unterschiedlicher Häufigkeit auf, wegen externer Faktoren, wie z.B. Compiler, Prozessor oder Arbeitslast.

In dieser Arbeit präsentieren wir einen Ansatz, der Fehler aus einer einzigen Spur eines parallelen Programms vorhersagt. Wir berechnen off-line alternative Verschränkungen, um den Zeitmessungseffekt der beobachteten Ausführung zu reduzieren. Wir bauen ein Modell mit Hilfe einer Prozessalgebra, das die Reihenfolge der Spur verallgemeinert; es extrapoliert mögliche Verschränkungen. Im Modell wird nach verschiedenen Nebenläufigkeitsfehlern gesucht. Ein vorhergesagter Fehler wird von einer Verschränkung begleitet, die in dem Programm erzwungen wird, um den Fehler zu reproduzieren.

Der Ansatz wurde für Verklemmungs- und Wettlauferkennung im Vergleich zu anderen dynamischen Ansätzen evaluiert. Die Verringerung von falschen Warnungen bewegt sich im Bereich von 50% bis 86%, mit gleicher oder höherer Präzision. Das vorgestellte Werkzeug und sein Modell sind anpassbar für andere Reihenfolgeverletzungen. Diese Fehler erfordern eine Spezifikation, die die relevanten Ereignisse im Programm definiert und die gültigen oder ungültigen Ordnungen beschreibt. Wir zeigen dieses Vorgehen an sieben Anwendungsbeispielen.

# Contents

|    |      |         | res                                     |   |

|----|------|---------|-----------------------------------------|---|

| 1  |      | oductio |                                         | 1 |

| 1. | 1.1. |         |                                         | 1 |

|    |      |         |                                         | _ |

|    | 1.2. |         |                                         | 5 |

|    | 1.3. |         | 3                                       | 8 |

|    | 1.4. | Struct  | ure of the Thesis                       | 9 |

| 2. | Basi | c Conc  | epts 1                                  | 1 |

|    | 2.1. | Concu   | rrent Systems                           | 1 |

|    |      | 2.1.1.  | Trace                                   | 1 |

|    |      | 2.1.2.  | Synchronization Mechanisms              | 2 |

|    |      | 2.1.3.  | Ad-Hoc Synchronization                  | 7 |

|    | 2.2. | Concu   | rrency Failures                         | 8 |

|    |      | 2.2.1.  | Deadlock                                | 8 |

|    |      | 2.2.2.  | Data Race                               | 0 |

|    |      | 2.2.3.  | Atomicity Violation                     | 0 |

|    |      | 2.2.4.  | Order Violation                         | 2 |

|    | 2.3. | Race I  | Detection Algorithms                    | 2 |

|    |      | 2.3.1.  | Happens-Before Algorithm                | 2 |

|    |      | 2.3.2.  | Lockset Algorithm                       |   |

|    | 2.4. | _       | unicating Sequential Processes          | _ |

|    |      | 2.4.1.  | Sequential Operators                    |   |

|    |      | 2.4.2.  | Concurrency Operators                   |   |

|    |      | 2.4.3.  | Expanding Event and Process Definitions |   |

|    |      | 2.4.4.  | Semantic Models                         |   |

|    |      | 2.4.5.  | Refinement                              |   |

|    |      | 2.4.6.  | Practicalities in Model Checking        |   |

|    | 2.5. |         | G-Oriented Programming                  |   |

|    | 2.5. | Aspect  | 0 0                                     |   |

| 3. | Rela | ted Work 41                                            |

|----|------|--------------------------------------------------------|

|    | 3.1. | Race Detection                                         |

|    |      | 3.1.1. Static Analysis                                 |

|    |      | 3.1.2. Dynamic Analysis                                |

|    |      | 3.1.3. Influencing the Scheduler                       |

|    | 3.2. | Deadlock Detection                                     |

|    | 3.3. | Runtime Verification                                   |

|    | 3.4. | Summary                                                |

| 4. | Race | eQuest and Deadlock Detection 51                       |

|    | 4.1. | Overview                                               |

|    | 4.2. | Motivational Deadlock Example                          |

|    | 4.3. | Trace Model                                            |

|    |      | 4.3.1. Example of a Non-Deadlocked Trace               |

|    |      | 4.3.2. Capturing the Trace                             |

|    | 4.4. | CSP Model                                              |

|    |      | 4.4.1. CSP Model Example                               |

|    | 4.5. | Error Checking                                         |

|    |      | 4.5.1. Deadlock Checking                               |

|    |      | 4.5.2. Deadlock Check Example                          |

|    | 4.6. | Counterexample Reproduction                            |

|    |      | 4.6.1. Deadlock Reproduction Example                   |

|    | 4.7. | Limitations                                            |

|    |      | 4.7.1. Unsupported Concurrency Mechanisms              |

|    |      | 4.7.2. Infeasible Reordering                           |

|    |      | 4.7.3. Scalability & Trace Windowing                   |

|    | 4.8. | Deadlock Detection Evaluation                          |

|    |      | 4.8.1. Experimental Setup                              |

|    |      | 4.8.2. Benchmark & Results                             |

|    |      | 4.8.3. Additional Detailed Examples 82                 |

|    |      | 4.8.4. Summary                                         |

| 5. | Data | a Race Detection 91                                    |

|    | 5.1. | Motivational Data Race Example                         |

|    | 5.2. | · · · · · · · · · · · · · · · · · · ·                  |

|    |      | 5.2.1. Capturing Memory Events                         |

|    |      | 5.2.2. Memory Grouping in Intervals                    |

|    |      | 5.2.3. Extending the Trace Model with Memory Events 97 |

|    |      | 5.2.4. Example of a Trace                              |

|    | 5.3. | CSP Model & Data Race Checking                         |

|    |      | 5.3.1 Data Race Checking 98                            |

|    |              | 5.3.2. Model Example                           | )1         |

|----|--------------|------------------------------------------------|------------|

|    | 5.4.         | Counterexample and Reproduction                |            |

|    |              | 5.4.1. Reproduction Example                    |            |

|    |              | 5.4.2. No Race Under Feasible Reordering       | )3         |

|    | 5.5.         | Reduction Techniques                           | )5         |

|    |              | 5.5.1. On-Line Redundant Accesses Removal      | )5         |

|    |              | 5.5.2. Hybrid Algorithm Data Race Filtering 10 | 16         |

|    |              | 5.5.3. Same Thread Segment Reduction           | )Ç         |

|    | 5.6.         | Evaluation                                     | .(         |

|    |              | 5.6.1. Experimental Setup                      | . 1        |

|    |              | 5.6.2. Unit Test Benchmark                     | . 1        |

|    |              | 5.6.3. Application Benchmark                   | 2          |

|    |              | 5.6.4. Scalability Comparison                  | 21         |

|    | 5.7.         | Summary                                        | 22         |

| _  | _            |                                                | _          |

| 6. |              | ection of Custom Ordering Errors 12            |            |

|    |              | Motivational Example                           |            |

|    | 6.2.         | Customizing the Trace Model                    |            |

|    |              | 6.2.1. Example of a Custom Instrumentation     |            |

|    | 6.3.         | CSP Model & Custom Properties                  |            |

|    |              | 6.3.1. Custom Properties                       |            |

|    |              | 6.3.2. Counterexample Reproduction             |            |

|    |              | 6.3.3. Example of a Custom Property            |            |

|    | 6.4.         | Use Cases                                      | 34         |

|    |              | 6.4.1. Deadlock                                | 34         |

|    |              | 6.4.2. Custom Race Detector                    | 55         |

|    |              | 6.4.3. Rover Uplink                            | 66         |

|    |              | 6.4.4. SQLite Core API                         | 37         |

|    |              | 6.4.5. Atomicity Violation                     | <b>3</b> 9 |

|    |              | 6.4.6. Resource Management System              | 1          |

|    | 6.5.         | Summary                                        | 13         |

| 7  | C            | clusion 14                                     | <b>E</b>   |

| ί. |              |                                                | _          |

|    |              | Summary                                        |            |

|    | <i>(</i> .2. | Future Work                                    | FC.        |

| Αp | pend         | lices 14                                       | .9         |

| Α. | Exai         | mple Models in $CSP_M$ 15                      | 1          |

|    |              | $\mathrm{CSP}_M$ Language                      |            |

|    |              | 1,1 0 0                                        |            |

| A.2.6. Custom Race Detector Example in Figure 6.10            | 159 |

|---------------------------------------------------------------|-----|

| A.2.7. Rover Example in Figure 6.13                           | 160 |

| A.2.8. SQL Example in Figure 6.15                             | 161 |

| A.2.9. Atomicity Violation Example in Figure 6.18             | 162 |

| A.2.10. Resource Management Example in Figure $6.21 \ldots$ . | 163 |

| B. Data Race Unit Test Results                                | 165 |

| Bibliography                                                  | 171 |

# List of Figures

| 1.1.  | Non-deterministic and racy program                                                                                                           |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 1.2.  | Protected non-deterministic increment example                                                                                                |

| 1.3.  | Concurrent use of file API                                                                                                                   |

| 1.4.  | Ordered use of file API                                                                                                                      |

| 1.5.  | Interleaving with no happens-before detectable race                                                                                          |

| 1.6.  | Interleaving with happens-before detectable race                                                                                             |

| 2.1.  | Mutex example                                                                                                                                |

| 2.2.  | Condition variable example                                                                                                                   |

| 2.3.  | Barrier example                                                                                                                              |

| 2.4.  | Semaphore example                                                                                                                            |

| 2.5.  | Ad-hoc synchronization loop                                                                                                                  |

| 2.6.  | Deadlock example                                                                                                                             |

| 2.7.  | Data race example                                                                                                                            |

| 2.8.  | Atomicity violation example                                                                                                                  |

| 2.9.  | Order violation example                                                                                                                      |

| 2.10. | Interleaving with a race                                                                                                                     |

|       | Graph with vector clocks                                                                                                                     |

| 2.12. | Basic lockset algorithm                                                                                                                      |

|       | Interleaving with inconsistent lockset                                                                                                       |

| 2.14. | Update of candidate set $C(x)$                                                                                                               |

|       | Summary of CSP grammar                                                                                                                       |

|       | "Hello world" in LLVM IR $\dots \dots \dots$ |

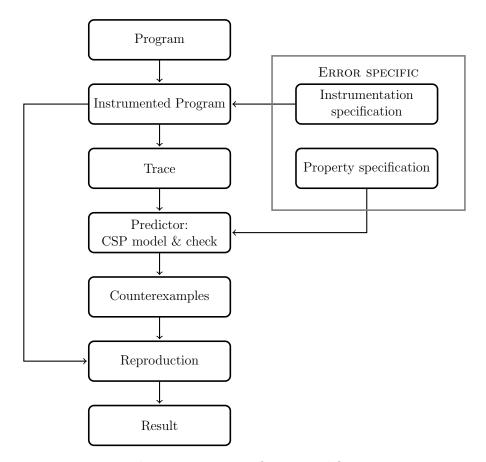

| 4.1.  | RaceQuest workflow                                                                                                                           |

| 4.2.  | Program with possible deadlock                                                                                                               |

| 4.3.  | Different interleavings for program in Figure 4.2                                                                                            |

| 4.4.  | Trace with no deadlock                                                                                                                       |

| 4.5.  | Program with instrumented wait loop                                                                                                          |

| 4.6.  | Wait loop instrumentation algorithm                                                                                                          |

| 4.7.  | Trace of a signal-wait program                                                                                                               |

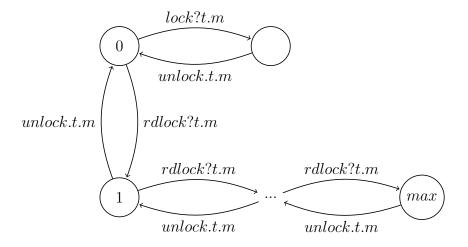

| 4.8.  | Labeled transition system for process $MUTEX_m$                   | 64           |

|-------|-------------------------------------------------------------------|--------------|

| 4.9.  | Labeled transition system for process $RWMUTEX_{m,max}$           | 65           |

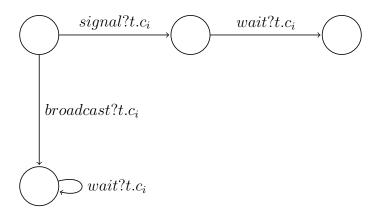

| 4.10. | Labeled transition system for process $SIGNAL_{c_i}$              | 66           |

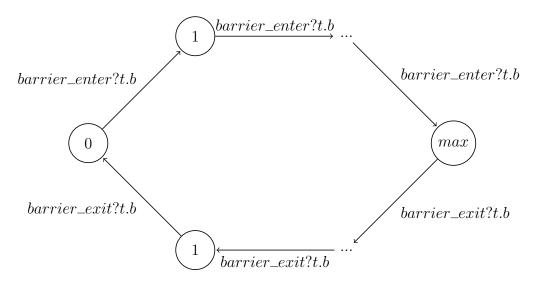

| 4.11. | Labeled transition system for process $BARRIER_{b,max}$           | 67           |

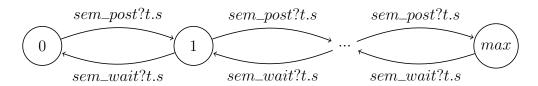

| 4.12. | Labeled transition system for process $SEMAPHORE_{s,init,max}$    | 68           |

| 4.13. | . CSP model of the trace in Figure 4.4                            | 69           |

| 4.14. | . CSP model of the trace in Figure 4.4 with deadlock refinement   | 73           |

| 4.15. | Scheduling point enforcing algorithm                              | 75           |

| 4.16. | Program with multiple control flow                                | 77           |

| 4.17. | Different interleavings for program in Figure 4.16                | 78           |

|       | Program with different lock orders and a barrier                  | 84           |

| 4.19. | Trace of program in Figure 4.18                                   | 85           |

| 4.20. | . CSP model of the trace in Figure 4.19 with multiple lock orders |              |

|       | and a barrier                                                     | 86           |

| 4.21. | Program with different lock orders and a barrier                  | 88           |

| 4.22. | Trace of program in Figure 4.21                                   | 88           |

| 4.23. | . CSP model of the trace in Figure 4.22 with a semaphore $$       | 89           |

| 5.1.  | Auxiliary steps in RaceQuest workflow                             | 92           |

| 5.2.  | Program with a data race                                          | $92 \\ 93$   |

| 5.3.  | Different interleavings for program in Figure 5.2                 | 93<br>94     |

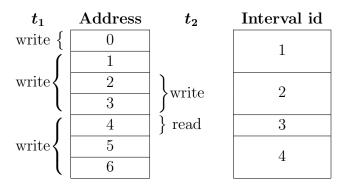

| 5.4.  | Memory interval algorithm                                         | 96           |

| 5.5.  | Memory interval example                                           | 97           |

| 5.6.  | Trace of program in Figure 5.2                                    | 98           |

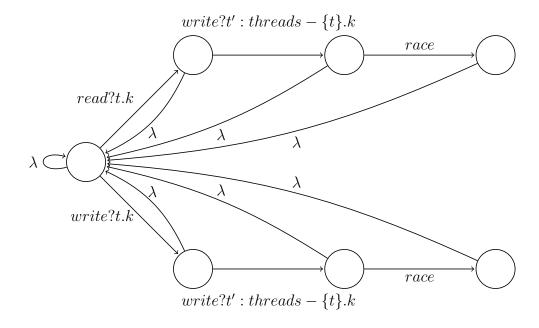

| 5.7.  |                                                                   | 100          |

| 5.8.  |                                                                   | 100          |

| 5.9.  |                                                                   | $102 \\ 104$ |

|       |                                                                   | 105          |

|       |                                                                   | 106          |

|       |                                                                   | 107          |

| 5 14  |                                                                   | 108          |

|       |                                                                   | 109          |

|       | Thread segment reduction example                                  | 110          |

|       | 2                                                                 | 122          |

|       |                                                                   | 100          |

| 6.1.  | ( )                                                               | 126          |

| 6.2.  | 0 1 0                                                             | 127          |

| 6.3.  |                                                                   | 128          |

| 6.4.  | 1                                                                 | 130          |

| 6.5.  | 1                                                                 | 131          |

| 6.6.  | CSP model of the trace in Figure 6.5                              | 133          |

### List of Figures

| 6.7. File access property                                                |

|--------------------------------------------------------------------------|

| 6.8. Deadlock property                                                   |

| 6.9. Instrumentation specification for custom race detector 13-          |

| 6.10. Data race property                                                 |

| 6.11. Rover uplink API                                                   |

| 6.12. Instrumentation specification for rover example                    |

| 6.13. Rover example property                                             |

| 6.14. Instrumentation specification for the SQLite core API 139          |

| 6.15. SQLite example property                                            |

| 6.16. Atomicity violation example                                        |

| 6.17. Instrumentation specification for an atomicity violation check 143 |

| 6.18. Atomicity property                                                 |

| 6.19. Resource management API                                            |

| 6.20. Resource management                                                |

| 6.21. Resource management property                                       |

# List of Tables

| 4.1. | Synchronization events                                         | 54  |

|------|----------------------------------------------------------------|-----|

| 4.2. | Deadlock detection benchmark results                           | 81  |

| 5.1. | Memory access events                                           | 97  |

| 5.2. | Data race detection unit test benchmark results                | 112 |

| 5.3. | Application benchmark characteristics                          | 113 |

| 5.4. | Number of racy locations                                       | 114 |

| 5.5. | Time and number of executions equivalent to a single RaceQuest |     |

|      | execution                                                      | 115 |

| 5.6. | Counterexample feasibility                                     | 117 |

| 5.7. | Trace reduction: cache and memory intervals                    | 119 |

| 5.8. | Trace reduction: hybrid filter & segment merge                 | 120 |

| 5.9. | Detection time(s) with different number of iterations          | 123 |

| 6.1. | Valid <i>field</i> elements in each join-point                 | 129 |

| A.1. | $\mathrm{CSP}_M$ symbol equivalence                            | 152 |

| R 1  | Data race detection unit test benchmark results - detailed     | 166 |

### 1. Introduction

### 1.1. Motivation

In the past programmers relied on the ever increasing speed of new hardware to make their sequential programs run faster without effort. Around 2005 several issues started to limit that trend: dissipation issues due to power consumption growth, limitations in instruction level parallelism, and mismatches between processor speed and memory speed, as described in Sutter's article [Sut05]. The industry switched from packaging a single powerful processor on a chip to putting together multiple but slower processors.

To benefit from the new architecture, the programs need to execute their tasks in parallel. But concurrent programs suffer from concurrency failures<sup>1</sup>, a new class of errors, such as data races, deadlocks, atomicity violations, and order violations. Program correctness means that a given program matches its specification. Some specifications are universal, e.g. no data races or no deadlocks, and all programs should comply with them. These failures have a general description that can be used to detect them. However, there are failures such as some atomicity and order violations, which are specific to a program or domain. To detect them, the intended semantics of the program are needed. In this case the developer provides a description of the desired behavior or of the failure, which is checked against the program.

In general correctness is undecidable, and property checking tools rely on approximations, sacrificing precision or completeness for the sake of practicality.

<sup>&</sup>lt;sup>1</sup> A failure or fault is the deviation of the behavior of the software from the specification. A defect or bug is a deficiency in the source code that can lead to a failure. A mistake is a human action that causes a defect. An error can refer to any of these three terms.

A sequential program requires the appropriate input, so in testing techniques the responsibility to provide a set of relevant data rests with the developer. A concurrent program also needs an interleaving that orders the tasks executed in parallel under an input to observe a specific property. Concurrent programs are naturally non-deterministic to make the most of a multicore processor, and the number of interleavings grows exponentially with the number of instructions. For the developer it is very difficult to find or enforce an erroneous interleaving.

Figure 1.1 presents an example of non-determinism and a data race in a program.

```

1

int x = 0, y = 0, z = 0;

void main() {

3

fork (worker);

4

x = x + 2;

5

y = x;

6

join(worker);

7

assert(x == 3);

8

}

9

10 void worker() {

11

x = x + 1;

12

z = x;

13

}

```

Figure 1.1.: Non-deterministic and racy program

Two threads, main and worker, concurrently update variable x. Depending on the executed interleaving, the result varies drastically. If we assume that the thread main is executed completely (reaching the join) before the thread worker starts, then y = 2 and z = 3. But if worker is faster, the end values are y = 3 and z = 1. Other results are possible; if main is preempted before executing the instruction y = x, and then worker is completed, we obtain y = z = 3 at the end. In any of these cases the final value of x in memory is always going to be 3. Here the developer expects that the values of y and z are going to differ because of non-determinism, but the developer also expects that the value of x is the same, independently of the interleaving.

A more intricate interleaving is the following: worker loads the value of x from memory to execute the increment x = x + 1. But before the increment stores the result, which is 1 in memory, main completely executes the increment x = x + 2, effectively storing a value of 2 in memory. Then worker

overwrites x with its own result of 1, thanks to the store operation of x = x + 1. At the end the value of y, z and x is 1. A similar interleaving, but reversing the order between the threads, would result in x = y = z = 2. These outputs are completely unexpected and could be the cause of other failures in the program.

This failure – a data race – is produced by a misunderstanding of the developer, namely that the increments are executed atomically. The programmer must explicitly ensure that they are executed without interruption by other threads. A mechanism to solve this problem is to use *locks* to establish a mutually exclusive area, as shown in Figure 1.2.

```

int x = 0, y = 0, z = 0;

2

mutex m;

3

void main() {

4

fork (worker);

5

6

lock (m);

7

x = x + 2;

8

y = x;

9

unlock (m);

10

11

join(worker);

12

assert(x == 3);

13

14

15

void worker() {

16

lock (m);

17

x = x + 1;

18

z = x;

19

unlock (m);

20

```

Figure 1.2.: Protected non-deterministic increment example

Both threads use the synchronization primitives lock and unlock on a variable m. These primitives ensure that the instructions executed between a call to lock and a call to unlock by one thread cannot be preempted by other instructions in a similar block on another thread. In this case the final result of x is always 3. Thanks to the use of the mutex, no data race happens. But the non-determinism in thread execution stands, as the values of y and z can still be 2 and 3, or 3 and 1. In fact the synchronization reduces the total number

of possible interleavings in the program to two: main reaches the join first or worker completes first.

Figure 1.3 shows a program with a domain-specific concurrency error.

```

1

file f;

2

void main() {

3

fork (worker);

f = open_file("foo");

4

5

6

some_work();

7

8

join (worker);

9

close file(f);

10

}

11

12

void worker() {

13

char[] data = compute();

14

write_file(f, data);

15

clear (data);

16

```

Figure 1.3.: Concurrent use of file API

The thread main has the task of opening and closing a file, with the functions open\_file and close\_file. Meanwhile at some point the thread worker writes to the file with the function write\_file. The expected behavior by the programmer is that write\_file happens between the opening and the closing of the file. The programmer relies on undefined time periods between the three calls for a correct order. The correct order only occurs when worker spends enough time in the function compute so main has time to open the file. But no mechanism ensures that worker executes write\_file in-between. The thread worker can be faster than the thread main and perform write\_file before the file is open. This situation could produce an immediate failure or be the root of subsequent failures, e.g. data loss.

This failure is an order violation. The programmer assumes that due to the amount of work done by both threads, the call to write\_file always occurs in the middle. This error is also domain specific: the file-related API in this example requires the file to be open and closed explicitly. Another API could perform or check the opening and closing implicitly in write\_file. Thus, the API developer needs to define the valid or invalid orders.

The associated defect is solved defining an explicit order between the threads, with a signal - wait mechanism, as in Figure 1.4.

```

file f;

2

cond v;

3

void main() {

4

fork (worker);

5

f = open_file("foo");

6

signal(v);

7

some work();

8

join (worker);

9

close_file(f);

10

}

11

12

void worker() {

13

char[] data = compute();

14

wait(v);

write_file(f, data);

15

16

clear(data);

17

```

Figure 1.4.: Ordered use of file API

The thread executing a wait call is blocked until the other thread executes a corresponding call to signal on the same variable v. This synchronization forces the thread worker to execute the function write\_file at some point after the file has been opened. In general all concurrency failures imply an interleaving not expected by the developer.

#### 1.2. Problem Statement

There are two fundamental techniques to detect concurrency failures. Static techniques analyze the source code and perform diverse analyses to find defects, such as control flow, data-flow, or problem specific algorithms, e.g. *lockset* for data races. These techniques produce many false positives; they have to make approximations, because the discovery of the required properties in a non-running program is undecidable.

Dynamic analyses however execute a program and perform some checks on the observed execution. They limit themselves to the observed execution, which generates false negatives due to non-explored paths and interleavings, but they

are less noisy as they relate to an actual execution with real values and states. These analyses use a monitor to check the fulfillment or violation of a desired property; data-race-specific algorithms are *lockset* and *happens-before* algorithms. Lockset assumes that all shared accesses must be consistently protected by the same lock, while happens-before establishes a logical order between instructions based on synchronization primitives.

For example, the interleaving shown in Figure 1.5 is a specific observed execution of a program. Two threads access the two variables x and y, but only the accesses to the second one are correctly protected by a lock.

| thread 1   | thread 2   |

|------------|------------|

| x = 1      |            |

| lock(m)    |            |

| y = y + 2  |            |

| unlock (m) |            |

|            | lock(m)    |

|            | y = y + 1  |

|            | unlock (m) |

|            | x = 2      |

Figure 1.5.: Interleaving with no happens-before detectable race

In the described interleaving a happens-before detector does not find the possible data race between both accesses to x. This happens because the critical sections protected by the lock m are happens-before-ordered, and they extend the order to the accesses on x, because the happens-before relationship is transitive. A happens-before detector finds the race if the observed interleaving is the one in Figure 1.6.

| thread 1   | thread 2   |

|------------|------------|

|            | lock(m)    |

|            | y = y + 1  |

|            | unlock (m) |

|            | x = 2      |

| x = 1      |            |

| lock(m)    |            |

| y = y + 2  |            |

| unlock (m) |            |

Figure 1.6.: Interleaving with happens-before detectable race

In this case the critical sections do not propagate the happens-before order to the accesses on x, and the race is detected.

The problem here with a happens-before detector is its dependency on the timing of the observed interleaving. Different interleavings manifest with varying frequency due to the influence of compilers, processor architectures, operating systems, or workload in the machine. The developer can consistently observe the same behavior across dozens of executions, but any change of any factor or in the source code could lead the program to exhibit another set of interleavings more frequently. Gait [Gai86] named this problem the *probe effect*. The program during testing, or under a race detector, could exhibit the interleaving in Figure 1.5 regularly; but in production the interleaving in Figure 1.6 could be more frequent. Or the race detector executes the interleaving where the race is easy to find, but when the developer tries to observe the race with debugging techniques, the debugger influences the scheduling, making it difficult to reproduce the race situation.

Two issues arise: one is the number of alternative interleavings observed by the algorithm, the other is the reproducibility of the reported failure. For a happens-before detector the reproducibility can be solved by storing the whole trace, or at least the synchronization events, of each execution, so the order observed by the detector can be replayed. If the detector explores the same set of interleavings, the same traces are stored each time. Each analysis of an already explored interleaving now suffers additional execution and storage overheads due to the trace logging. More time spent per execution implies less time to perform additional executions, which could increase the interleaving coverage. The number of interleavings is still limited, and the race in Figure 1.5 would not be found. The application of the lockset algorithm (alone or combined with happens-before) in this case detects the race in both interleavings, but does not build an order of events that can be used to reproduce the race.

Other failures, such as the order violation shown in Figure 1.3, require a specific monitor that tracks the desired events and describes the valid orderings. Happens-before can be used to check if the observed event order is one of the valid orders, but cannot reason about completely different interleavings. But lockset offers a more limited utility, as the algorithm can only report if a pair of events takes place without the protection of the same lock. The lockset algorithm cannot be used to increase the number of explored interleavings on general properties as in race detection.

### 1.3. Thesis Objectives

The objective of this work is to present a dynamic automatic approach to detect concurrency failures that:

- Covers non-observed interleavings, exploring reorderings of a trace and maximizing the number of detected failures in a single recording.

- Enables reproduction of erroneous interleavings, so the developer can re-execute the program and pinpoint causes.

- Does not produce false positives, relieving developers from chasing false alarms.

- Minimizes the size of the trace, as size directly impacts the overhead. A smaller trace also reduces the probe effect.

- Is extensible, allowing the definition of different failure patterns, so not only generic failures can be detected, but also domain-specific ones.

With these requirements, we present our research hypothesis:

Model-based analysis can predict failures from a single observed trace and generate reproducible witnesses without false positives and few false negatives.

The key idea of this work is to execute a program under a defined input, such as a test case, and record the minimum necessary events for the target failure type, e.g. only the synchronization instructions for a deadlock. Then we build a formal model using a process algebra to represent the partial orders in the threads. A process algebra is naturally suited to describe a concurrent system by its transitions, which are determined by the events performed in the trace. The model represents all possible reorderings of the events in the trace while maintaining the order of the synchronization instructions, such as mutual exclusion for locks or a complete happens-before order for signal-wait. The failures are also defined in terms of the process algebra; they are checked against the model extracted from the program through model checking. We provide the definitions of data races and deadlocks. For other types of failures that depend on program semantics, the developer must provide a description of the property to be checked – the erroneous or the correct behavior. The events will be extracted automatically from the program. Model checking provides examples of how the property was violated. The example is used to force the program to follow the same scheduling.

The idea of this thesis has been introduced in our publications [CT15a] and [CT15b]. We implemented the technique in our tool called RACEQUEST. Race-Quest performs the steps mentioned above automatically: trace capture, model

generation, checking, and reproduction. RaceQuest works on parallel programs written in C/C++ using the POSIX threads library.

#### 1.4. Structure of the Thesis

The rest of this thesis is structured in the following way: Chapter 2 presents some concepts and algorithms, and introduces the CSP process algebra. Chapter 3 describes prior work on concurrency error detection. Chapter 4 describes the different steps of RaceQuest in detail: trace, model, checking, and reproduction; it also uses deadlock detection as a motivating example. Chapter 5 extends the trace and model used for deadlock detection to data race detection. Chapter 6 facilitates the extension of the trace, model, and check by the user, to detect domain-specific failures. Finally, Chapter 7 concludes the thesis along with ideas for future work.

# 2. Basic Concepts

In this chapter we introduce some concepts, e.g. synchronization constructs and concurrency errors. We also describe several algorithms and technologies: data race detection algorithms, CSP process algebra, Aspect-Oriented Programming, and LLVM.

### 2.1. Concurrent Systems

A concurrent system is one that performs multiple tasks simultaneously. In a sequential system, only one task is performed at a given point, and it must end before starting the next task. The most popular concurrency model is multithreading with shared memory. Languages such as C/C++ or Java use this model. In multithreading a program is composed of several instruction flows, threads, that access the same data, the shared memory. Lee [Lee06] states that it is difficult to reason about a multithreading program, hence developers easily make mistakes. Multithreading suffers from new types of failures, which are not present in sequential programs, such as data races and deadlocks. There are alternative concurrency models, such as message-passing or data parallelism. Adopting any of these other models prevents some of these errors.

#### 2.1.1. Trace

A trace is a record of the operations performed by an executed program. In a sequential program a trace is a sequence of operations with a total order. But in a parallel program a trace only provides a partial order of operations. For each

individual thread the order is total, but operations by different threads can take place simultaneously. Synchronization primitives create an order among operations in different threads.

#### Thread segment

A thread segment is the set of operations by a single thread in a trace between two synchronization operations. Thread segments do not include any synchronization operations; thread segments are the frontiers between segments. The thread in the trace consists of a sequence of ordered thread segments, where each segment is a sequence of ordered instructions. The synchronization operations define the order among thread segments in two different threads.

Thread segments are useful to group instructions with the same logical ordering in respect to instructions in other threads. If two thread segments are concurrent, then all the instructions in both thread segments are concurrent.

#### 2.1.2. Synchronization Mechanisms

Threads run concurrently and non-deterministically, and they work on the same shared data. Threads can conflict in using the same data by overwriting the work of other threads. To avoid such failures, the programmer must regulate the thread accesses to the shared memory, using synchronization mechanisms. A synchronization mechanism creates a logical order between source code blocks. This order makes a set of instructions non-concurrent. Synchronization reduces the non-determinism in the program.

#### Mutex

A critical section is a block of code that accesses a shared resource and must not be concurrently accessed by more than one thread.

A mutex or lock is a synchronization mechanism that enforces mutual exclusion on critical sections. A mutex starts in a free state. Any thread can acquire, lock, the mutex, which goes into a locked state. While locked no other thread is able to acquire it. Other threads trying to acquire the mutex are blocked. A mutex becomes free again after a release operation, unlock. Only the thread that has acquired the lock can release it. Once the mutex is free, another thread can acquire it.

The source code located between the acquire-release calls for the same mutex in a multithreaded program will never be executed in parallel. Mutexes are unaware of the operations done while they are being held, and they do not check or enforce any behavior on the protected operations.

Figure 2.1 describes a program with two parallel functions and a mutex. The calls to lock and unlock with the mutex m ensure that the lines 5 and 11 are never executed in parallel. The first thread reaching a lock acquires the mutex. The other thread cannot complete its own call to lock until the mutex is released by the other thread.

```

1

int x = 0;

2

mutex m;

void thread_1() {

4

lock (m);

5

x++;

6

unlock (m);

7

}

8

9

void thread 2() {

10

lock (m);

11

x = 3;

12

unlock (m);

13

```

Figure 2.1.: Mutex example

There are variations of mutexes and their primitives. A try\_lock primitive is a variation of the acquire operation; if the mutex is already in the locked state, the calling thread is notified and aborts the operation. A timed\_lock is another acquire operation variant; the blocked thread will abort the acquire operation after waiting for the specified time. A read-write mutex is a variation of the mutex with the additional state read-locked. Threads can read-acquire or acquire the read-write mutex. A normal acquire still transitions the mutex to the locked state. But a read-acquire goes from the free state to the read-locked state. In the read-locked state multiple threads can read-acquire the mutex. It is not possible to go from read-locked state to normal lock without going through the free state. The use case behind read-write mutexes is to allow multiple threads to read shared data concurrently but to write them exclusively. The read-write mutex avoids reading and writing happening in parallel. It is the responsibility of the developer to ensure that only read operations are executed while doing a read-acquire.

#### Ordering threads

A mutex does not specify which source code block must be executed first, it allows any order. Another use case is when a specific operation must always take place following another operation, such as the use of a variable after its initialization. Several mechanisms impose such an order.

Thread creation and destruction operations impose an order between the involved threads. A thread spawns a new thread, its child thread, with access to the same memory with a *fork* operation. The operations of the parent thread after the fork are parallel to all the instructions of the child thread. Parent thread operations prior to the fork cannot be parallel to the child thread operations, as the thread did not exist before that point. Matching the fork operation there is the *join* operation. A parent thread waits in a join call until the specified child thread ends. All instructions in the parent thread after the join happen after the operations in the child thread, as that no longer exists.

#### Signal-wait

Arbitrary orderings between two threads, similar to those provided by a join, can be specified with the *signal-wait* combination. A thread executing a *wait* is blocked on a condition variable c until another thread wakes it up with a *signal* on c. The operations in the signaler thread before the signal take place before the operations in the waiter thread after the wait.

In practice the wait operation depends on a predicate; the signaling thread must ensure that the predicate is satisfied. The wait call is preceded by a conditional branch with the predicate as condition. If the predicate is already met before reaching the wait call, then the wait call is skipped. Otherwise the wait occurs. To achieve efficient implementation, the wait allows sporadic wake-ups of blocked threads. The preceding conditional check must be reevaluated and, if the check is not passed, the thread must wait again. Multiple threads could be blocked on the same condition variable c with the same or different predicates.

Figure 2.2 contains a program with two parallel functions using the signal-wait mechanism. We want to ensure that the function <code>second\_task</code> is always executed after the function <code>first\_task</code>. The predicate is represented by the variable flag. The thread waiter checks the variable flag and waits until flag turns true. Concurrently to the wait, the thread <code>signaler</code> executes the function <code>first\_task</code>, sets flag to true, and signals on c. Only then will waiter continue and perform the function <code>second\_task</code>. Note that the variable flag is accessed in parallel by both threads; it is protected by the

mutex m. The function wait takes the mutex m as an argument and internally unlocks and locks m before and after being blocked.

```

1 boolean flag = false;

mutex m;

3

cond_var c;

void waiter() {

5

lock (m);

while(flag == false) {

6

7

wait(c, m);

8

9

unlock (m);

10

second_task();

11

}

12

13

void signaler() {

14

first_task();

15

lock (m);

16

flag = true;

17

signal(c);

18

unlock (m);

19

```

Figure 2.2.: Condition variable example

A signal call wakes up a single thread waiting on c. A call to broadcast wakes up all threads waiting on c. Signal and broadcast are not buffered; they only wake up threads already waiting on c. A variant of the wait call is the timed\_wait, where the waiting thread is automatically woken up after a specific period of time.

Detecting signal-wait orders is not easy; the order between the threads exists even if the wait call is not executed at all, i.e. the predicate is already met. We use additional instrumentation to detect the signal-wait orderings, as described in Section 4.3.2.

#### Barrier

A barrier is a multithread synchronization mechanism. A barrier allows multiple threads to synchronize together at a specific point, a call to barrier\_wait. The threads are blocked in the barrier\_wait call. A barrier starts closed and must be initialized with a number. The number indicates how many threads

must reach the barrier, call barrier\_wait, to open it. When the barrier opens the threads return from the barrier\_wait primitive and resume their execution. All operations of the threads before the barrier take place before all operations after the barrier. After a barrier is used, it is automatically reset and can be reused.

Figure 2.3 displays a program with two parallel functions and a barrier. Both pre\_task functions are executed concurrently. When both threads have reached the function barrier\_wait, the threads resume their execution. The post\_task functions also run in parallel, but no pre\_task runs at the same time as any post\_task.

```

1 barrier b = barrier init(2);

2

void thread_1() {

3

pre_task();

4

barrier_wait(b);

5

post_task();

6

}

7

8

void thread_2() {

9

pre_task();

10

barrier_wait(b);

11

post_task();

12

```

Figure 2.3.: Barrier example

#### Semaphore

A semaphore is a counter with two operations, sem\_post and sem\_wait. If the value of the semaphore is greater than zero, a thread executing a sem\_wait will decrease the counter by one and go forward. But if the value is zero, the thread will block on the sem\_wait call until the counter is increased. The counter is only increased with sem\_post. A semaphore has an initial value for the counter.

Figure 2.4 depicts a program with two parallel functions and a semaphore s. The semaphore counter starts at zero. The thread waiter will be blocked until the thread poster increases the value of the semaphore. The functions pre\_task and post\_task never run in parallel.

The primitive *sem\_try\_wait* is a variation of the sem\_wait operation; if the semaphore counter is zero, the calling thread does not wait, otherwise it be-

```

semaphore s = sem_init(0,10);

2

void poster() {

3

pre_task();

4

sem post(s);

5

}

6

void waiter() {

7

8

sem_wait(s);

9

post_task();

10

```

Figure 2.4.: Semaphore example

haves as sem\_wait. Another sem\_wait operation variant is *sem\_timed\_wait*: the blocked thread will abort the wait operation after waiting the specified time. A mutex is a special semaphore: it is initialized to zero, the maximum value of the counter is one, and there is ownership associated with the counter.

#### Atomic operations

Atomic operations are indivisible operations that appear to the rest of the threads to occur instantaneously. Atomic operations can be enforced in software with the use of mutexes or in hardware with specific instructions, such as test-and-set or fetch-and-add. Concurrent atomic operations on the same memory address do not produce any data race.

### 2.1.3. Ad-Hoc Synchronization

Ad-hoc synchronization is a synchronization mechanism constructed by the developers. This synchronization is not part of any standard library or language, but usually imitates some standard synchronization mechanism.

Ad-hoc synchronization commonly consists of a tight loop and a shared variable that works as condition, as the example in Figure 2.5. The threads waiter and signaler run in parallel. We define x as an atomic variable to avoid races on x, as well as compiler and processor reorderings. The thread waiter cannot leave the while-loop until the thread signaler modifies the value of x. The ad-hoc synchronization works as a signal-wait, and the function first\_task is always executed before the function second\_task.

Most concurrency error detection tools rely on standard synchronization primitives to detect inter-thread communication. The use of ad-hoc synchronization

```

1

atomic x = 0;

2

void waiter() {

3

while (x == 0) {

4

vield();

5

6

second_task();

7

}

8

9

void signaler() {

10

first_task();

11

x = 1;

12

```

Figure 2.5.: Ad-hoc synchronization loop

is a challenge for these tools, and becomes a source of false warnings. Our work does not detect ad-hoc synchronization. There are techniques to add support of ad-hoc synchronization. Xiong et al. [XPZ<sup>+</sup>10] presented an automatic static technique to annotate ad-hoc synchronization, together with a study about its harmful effects. A runtime approach to detect ad-hoc synchronization was presented by Janeesari et al. [JT10].

### 2.2. Concurrency Failures

#### 2.2.1. Deadlock

A deadlock is a situation that occurs when two or more competing actions of a program require the exclusive use of two or more resources. Each action acquires a different resource, but they cannot acquire another because it is already held by the other action. In this situation the actions cannot complete, and the program cannot progress further. Coffman et al.[CES71] defined four necessary and sufficient conditions for a deadlock:

- 1. Mutual exclusion: the resources involved cannot be shared; only one action can use the same resource at the same time.

- 2. Hold and wait of resources: an action retains a requested resource while requesting additional resources.

- 3. No preemption: a resource cannot be taken away from the current holder.

- 4. Circular wait: there is a circular chain of actions holding resources and requesting other resources.

Prevention of any of these four conditions is enough to avoid the deadlock situation. In multithreaded systems the actions are usually, but not necessarily, threads. A single thread can deadlock itself, e.g. request the same non-recursive mutex twice.

A communication deadlock occurs where the shared resource is a communication channel: two or more threads are waiting to receive a message from another thread. Communication deadlocks can occur while waiting for a lock release or the opening of a semaphore. Our work detects this kind of deadlocks.

Figure 2.6 shows an example of a program that can exhibit a deadlock. The two threads want to acquire the mutexes m and p. The thread main can be preempted just after acquiring the mutex m by the thread worker. In this case worker acquires the mutex p, but it is unable to acquire the mutex m. Likewise, main wants to acquire the mutex p, which is already held by worker. Both threads are deadlocked waiting for the release of the other mutex. This situation does not always manifest itself in the program, only under the described interleaving and a symmetric interleaving where the thread worker acquires the mutex p first.

```

mutex m, p;

2

void main() {

3

fork(worker);

4

5

lock (m);

6

lock(p);

7

unlock (p);

8

unlock (m);

9

10

join(worker);

11

12

13

void worker() {

14

lock(p);

15

lock (m);

16

unlock (m);

17

unlock (p);

18

```

Figure 2.6.: Deadlock example

#### 2.2.2. Data Race

A data race is a concurrent access by two threads to the same memory location where at least one access is a write.

Figure 2.7 displays an example of a data race on variable x. Depending on the interleaving, the final value of x can be 3. If the read and write on x by both threads takes place concurrently, these instructions can overwrite each other's results, so x could be 1 or 2.

```

int x = 0;

2

void main() {

3

fork (worker);

4

x = x + 2;

5

join(worker);

6

}

7

void worker() {

9

x = x + 1;

10

}

```

Figure 2.7.: Data race example

Narayanasamy et al. [NWT<sup>+</sup>07] differentiate between benign and harmful data races, based on the influence on program correctness. Boehm [Boe11] argues against 'benign' races and considers that all data races are harmful at source code level. Memory models of mainstream imperative languages, such as C and Java, describe data races explicitly as undefined behavior. In this work we look for data races originated by source code defects, so we side with Boehm and aim for race-free programs.

A data race can be solved by transforming the racy accesses into atomic operations or protecting them with a common lock. These solutions do not guarantee that there is no higher-level failure, such as an order violation or an atomicity violation. A data race can be a symptom of any of these failures.

### 2.2.3. Atomicity Violation

An atomicity violation happens when a critical region is not executed atomically, and another thread concurrently executes a conflicting memory access. This is caused by the developer overlooking the need of explicitly enforcing atomicity for a set of instructions, e.g. with a lock.

A data race can be seen as an atomicity violation, i.e. the developer assumed atomicity of all memory instructions. Data races are dependent on the memory model of the language. In this work atomicity violations are only related to the intended semantics of the program, not the language. A race-freedom in a program does not imply absence of atomicity violations.

Figure 2.8 shows an example of a program with an atomicity violation. The intended operation is that both threads increment the value on x, but the thread main uses an intermediate variable. If the thread worker executes its critical section between the critical sections of main, its increment at line 22 will be overwritten by the assignment x=temp at line 14. Note that each access to the shared variable x is correctly protected, so the program is race-free. In this case the whole execution of the thread main needs to be atomic. The intended operation is not explicit in the program. Without user assistance it is difficult to define where an atomic region should start and end.

```

int x = 0;

2

mutex m;

3

void main() {

4

fork (worker);

5

int temp;

6

7

lock (m);

8

temp = x;

9

unlock (m);

10

11

temp++;

12

13

lock (m);

14

x = temp;

15

unlock (m);

16

17

join(worker);

18

}

19

20

void worker() {

21

lock (m);

22

x++;

23

unlock (m);

24

```

Figure 2.8.: Atomicity violation example

## 2.2.4. Order Violation

An order violation is the execution of two sets of instructions in an unexpected order. Similar to atomicity violations, the developer overlooks the need to explicitly define an order through synchronization primitives, such as a signal-wait. Order violations are also dependent on the intended semantics on the program.

Figure 2.9 shows an example of an order violation. The thread main initializes a pointer x to a custom structure. The thread worker uses some content of the structure referenced by x as an argument for the function compute. If worker tries to dereference the pointer before its initialization, it will generate a runtime fault, e.g. a segmentation fault. The developer assumed that the structure would be initialized by the time worker uses the pointer. But there is nothing to ensure this behavior. The solution would be a signal-wait pair ordering both the initialization and the dereference.

```

1

my_struct *x;

2

void main() {

3

fork(tid, worker);

5

x = create_my_struct();

6

7

join(tid);

8

}

9

10

void worker() {

11

some_work();

12

compute (x->value);

13

}

```

Figure 2.9.: Order violation example

# 2.3. Race Detection Algorithms

In this section we describe the two main algorithms for race detection, the *happens-before* algorithm and the *lockset* algorithm. We use both algorithms as filters to reduce the number of candidates during race detection in Section 5.5.2.

# 2.3.1. Happens-Before Algorithm

We define a race as two parallel accesses to the same variable, and two events occurring in parallel if the program does not define a specific order between them. Knowing the logical order of the events in a trace is useful for race detection.

Lamport's happens-before relationship [Lam78] establishes a partial order between events in a concurrent system. The events executed by a single thread are naturally happens-before ordered by their execution order. In a message-passing system, a message sending event a and its corresponding receiving event b by another thread are happens-before ordered; the message cannot arrive before being sent. In shared memory systems the ordering is defined by the causal relationships of the thread synchronization constructs, such as fork-start, end-join, and unlock-lock pairs. We define that event a happens before event b as  $a \xrightarrow{hb} b$ .

The happens-before relation has the following properties:

- Transitivity  $\forall a, b, c$  if  $a \xrightarrow{hb} b$  and  $b \xrightarrow{hb} c$ , then  $a \xrightarrow{hb} c$ . The relationship determines that if for three events a, b, c, a happens before b and b before b, then b must happen before b.

- Irreflexivity  $\forall a, a \xrightarrow{hb} a$ . An event cannot happen before itself.

- Antisymmetry  $\forall a, b \ a \neq b$ , if  $a \xrightarrow{hb} b$  then  $b \not\xrightarrow{hb} a$ . If event a happens before another event b, then b does not happen before a.

Two events occur in parallel,  $a \parallel b$ , if they are not ordered, then based on the happens-before relationship:

$$a \parallel b \Leftrightarrow a \xrightarrow{hb} b \wedge b \xrightarrow{hb} a$$

Two events, such as two memory accesses, can happen concurrently if none of the two happens-before relationships between the two events is true, i.e. one relationship in each direction.

#### Vector clocks

The happens-before relationship can be computed using vector clocks. A vector clock is a logical timestamp of an event, similar to Lamport timestamps. The vector clocks of two events can be compared to determine the happens-before relation between the events.

A vector clock VC is a vector of length N, where N is the number of threads in the system. VC(x) denotes the vector clock for event x. Each of the N positions of the vector is a clock, i.e. a counter that describes the last known

state of a particular thread. We reference the position z of a particular vector clock as  $VC(x)_z$ . Each thread t maintains an internal vector clock  $VC^t$  which is updated with the following rules:

- Initially all positions of all thread vectors are initialized to zero:  $VC_z^t = 0 \,\forall t, z$ .

- Each time a thread t performs an event, it increases the counter of its own position on the clock array of its vector clock by one:  $VC_t^t = VC_t^t + 1$ .

- Each time a thread t sends a message, it sends its current vector clock along with the message m:  $VC(m) = VC^t$ .

- Each time a thread t receives a message m, it updates each position of its own vector clock with the maximum between its vector clock and the vector clock sent along with the message for that position:  $VC_z^t = max(VC_z^t, VC(m)_z) \,\forall z$ .

From the vector clocks, we can derive if there is a happens-before relationship between two events, a condition needed to avoid a data race. In general  $a \xrightarrow{hb} b \Leftrightarrow VC(a) < VC(b)$ , and by extension two events are parallel:

$$a \parallel b \Leftrightarrow VC(a) \not< VC(b) \land VC(b) \not< VC(a)$$

A vector clock is strictly smaller < than another if:

$$VC(a) < VC(b) \Leftrightarrow VC(a)_z \le VC(b)_z \, \forall z \land \exists y | VC(a)_y < VC(b)_y$$

A vector VC(a) is strictly smaller than another vector VC(b), if all the values in VC(a) are equal or smaller than the corresponding in VC(b) and at least one value is strictly smaller. Intuitively this means that, for an event a to happen before another event b, the known states at the execution of a cannot be bigger that any known state at the execution of b, and at least the state of one thread is smaller.

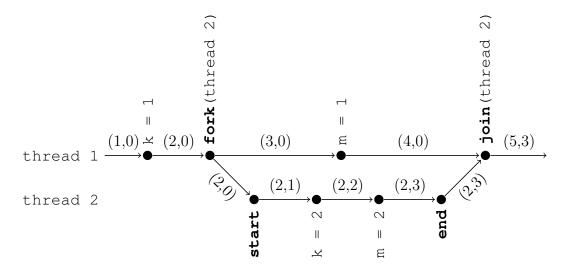

The interleaving in Figure 2.10 contains four write memory accesses on two distinct variables, k and m. The graph in Figure 2.11 represents the internal and inter-thread transitions in the interleaving with the corresponding vector clocks. In this example the only send-receiving message equivalents in multi-threading are fork-start and end-join synchronizations. We see the evolution of the different values of the vector clocks for the different internal and inter-thread events.

With the calculated vector clocks, we can check the happens-before relationship of the accesses to k and m. For k we have VC(k=1)=(1,0) and VC(k=2)=(2,1), where k=1 was performed by thread 1 and k=2 by thread 2. As VC(k=1) < VC(k=2), then by the previous definition k=1  $\stackrel{hb}{\longrightarrow}$  k=2, so both accesses are happens-before ordered and no race is possible. For m we have VC(m=1)=(3,0) and VC(m=2)=(2,2), where m=1 was performed by thread 1 and m=2 by thread 2. In this case  $VC(m=1) \not< VC(m=2)$  and also  $VC(m=2) \not< VC(m=1)$ , so there is no happens-before order in any direction. Without any happens-before ordering both events take place in parallel, which can lead to a data race.

| thread 1                  | thread 2              |

|---------------------------|-----------------------|

| k = 1                     |                       |

| <pre>fork(thread 2)</pre> |                       |

|                           | start                 |

|                           | k = 2                 |

|                           | k = 2<br>m = 2<br>end |

|                           | end                   |

| m = 1                     |                       |

| <pre>join(thread 2)</pre> |                       |

Figure 2.10.: Interleaving with a race

Figure 2.11.: Graph with vector clocks

## 2.3.2. Lockset Algorithm

The lockset algorithm, presented by Savage [SBN<sup>+</sup>97], assumes that all accesses to a shared variable v must always be protected by a common lock. This algorithm only pays attention to lock/unlock synchronizations and does not consider any other construct, which is a source of false positives in the algorithm. The lockset algorithm can be applied dynamically or statically without changes in the algorithm itself. The algorithm is show in Figure 2.12

```

Let locks\_held_t be the set of locks held by thread t for each shared variable v do

initialize C(v) to the set of all locks

end for

for each access to variable v by thread t do

C(v) := C(v) \cap locks\_held_t

if C(v) = \emptyset then

issue a warning

end if

end for

```

Figure 2.12.: Basic lockset algorithm

The algorithm maintains a set C(v) of candidate common locks for each shared variable v. At the beginning it is unknown which the common lock should be, so C(v) is initialized with all locks. Each thread t maintains a set  $locks\_held_t$  with the locks that it holds during a specific instruction. For each access to v, the current thread updates C(v), intersecting it with the current  $locks\_held_t$ . The intersection only reduces the candidate set, it cannot increase it. As long as the resulting C(v) has at least one element, then all accesses seen until the current instruction share at least this lock. If the set C(v) is empty, then the last access does not share a common lock with the previous accesses, and the algorithm emits a warning.

An example of the algorithm for the interleaving in Figure 2.13 is displayed in Figure 2.14. At the start C(x) is composed of both locks m and n. The first to access x is thread 1 with lock m. The update  $C(x) := C(x) \cap \{m\}$  leaves the lock m as the content of C(x). When thread 2 accesses x with lock n, then  $locks\_held(t_2) = \{n\}$ ; it is using a lock that is no longer part of C(x). So  $C(x) := C(x) \cap \{n\} = \{m\} \cap \{n\} = \emptyset$ . With an empty C(x), a warning is issued about the inconsistent access by thread 2.

There are further improvements of the algorithm to reduce the number of false positives. One improvement removes false positives, adding a state machine for each variable to differentiate the case of unprotected variable initialization. Another adds support to read-write locks, using an additional candidate set per variable to track the accesses under read-locks.

|   | thread 1   | thread 2   |

|---|------------|------------|

| 1 | lock (m)   |            |

| 2 | X++        |            |

| 3 | unlock (m) |            |

| 4 |            | lock(n)    |

| 5 |            | X++        |

| 6 |            | unlock (n) |

Figure 2.13.: Interleaving with inconsistent lockset

|   | Access to x | $locks\_held_{thread\ 1}$ | $locks\_held_{thread\ 2}$ | C(x)      |

|---|-------------|---------------------------|---------------------------|-----------|

| 0 | -           | Ø                         | Ø                         | $\{m,n\}$ |

| 2 | read        | $\{m\}$                   |                           | $\{m\}$   |

| 2 | write       | $\{m\}$                   |                           | $\{m\}$   |

| 5 | read        |                           | $\{n\}$                   | Ø         |

| 5 | write       |                           | $\{n\}$                   | Ø         |

Figure 2.14.: Update of candidate set C(x)

# 2.4. Communicating Sequential Processes

Communicating Sequential Processes (CSP) is a formal system to describe concurrent systems and reason about them. CSP was first presented by Hoare in 1978 [Hoa78]; since then it has been expanded and studied. CSP has influenced hardware architectures, e.g. the Transputer T9000, and programming languages such as Go and Erlang. CSP is a process algebra, a mathematical theory that describes a system by the interactions performed, without enumerating its internal states. CSP is used to refine a system iteratively. The system is described with the same syntax in all the iterations, independently of the abstraction level. The formal semantics of CSP enable automatic checks on whether a detailed description follows the behavior of a more abstract description, i.e. if the detailed behavior refines the abstract behavior.

The following presents a brief introduction to the *blackboard* CSP syntax used in this work. Figure 2.15 depicts the relevant CSP grammar. The books by

```

\langle Process \rangle ::= STOP

SKIP

\langle event \rangle \rightarrow \langle Process \rangle

\langle Process \rangle \square \langle Process \rangle

\langle Process \rangle \setminus \langle event\text{-}set \rangle

\langle Process \rangle \upharpoonright \langle event\text{-}set \rangle

\langle Process \rangle; \langle Process \rangle

\langle Process \rangle \Theta_{\langle event-set \rangle} \langle Process \rangle

\langle Process \rangle \mid \mid \mid \langle Process \rangle

\langle Process \rangle \quad \mathop{|||}_{\langle event-set \rangle} \ \langle Process \rangle

\langle Process \rangle \triangle \langle Process \rangle

::= identifier \langle field \rangle^*

\langle event \rangle

\langle field \rangle

::= . identifier

! identifier

? identifier [:\langle event\text{-}set\rangle]

\langle event\text{-}set\rangle ::= \{ \langle event\rangle^* \}

|\{|\langle event\rangle|\}

```

Figure 2.15.: Summary of CSP grammar

Roscoe [Ros10] and Schneider [Sch99] contain more in-depth descriptions of modern CSP.

In CSP the system and each subcomponent is described as a process. CSP is compositional; processes can be combined with different operators to generate more complex processes. Each process performs events, which are atomic and instantaneous. When a process emits or performs an event, we say that the process communicates with the environment, i.e. the event can be observed externally. Some operators enable communication between two processes. The communication is done by a synchronous share of an event (rendezvous), i.e. both processes must agree to execute the same event simultaneously. Processes are denoted in uppercase and events in lowercase.

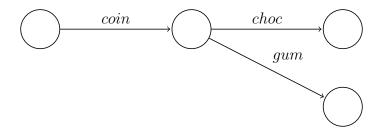

For example, we want to define a CSP description of a vending machine. The process will be called VENDING. This machine will only provide a chocolate bar, the event choc, after receiving a coin, the event coin, afterwards the machine will stop working. It only provides a single bar during its lifetime.

The description of this vending machine in CSP is as follows:

$$VENDING = coin \rightarrow choc \rightarrow STOP$$

At the beginning only the event coin can happen. Afterwards only the event choc is possible. After delivering the chocolate bar the process behaves like the process STOP.

The process STOP is a process that does nothing. In CSP terms it is *dead-locked*. It is the most basic process in CSP, the fixed point in the algebra.

The equivalent labeled transition system for VENDING is as follows:

The process VENDING can be composed as a series of processes:

$$VENDING = coin \rightarrow MIDDLE$$

$MIDDLE = choc \rightarrow STOP$

The prefix operator  $\rightarrow$  composes an event a and a process P into a new process Q, where  $Q = a \rightarrow P$ . Q is a process that performs a and then behaves like P.

The process  $VENDING\_REC$  describes a vending machine that never stops. It always serves a chocolate bar for a coin.

$$VENDING\_REC = coin \rightarrow choc \rightarrow VENDING\_REC$$

This process uses recursion. Instead of terminating with STOP, it returns to the beginning and behaves like  $VENDING\_REC$  again, offering the event coin.

The set of events emitted by a process P is the alphabet of the process, and it is denoted as  $\alpha(P)$ . The set of all events in a system is denoted  $\Sigma$ . In our example  $\Sigma = \{coin, choc\}$ .

## 2.4.1. Sequential Operators

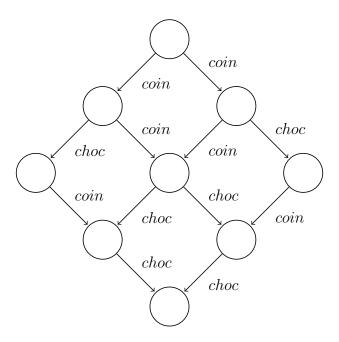

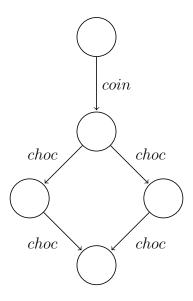

Branching or letting the environment choose between two processes, is done with the external choice operator  $\Box$ .  $VENDING\_GUM$  is a new vending machine that offers a chocolate bar or a chewing gum, the event gum, for a coin and then stops.

$$VENDING\_GUM = coin \rightarrow (choc \rightarrow STOP)$$

$\Box gum \rightarrow STOP)$

The equivalent labeled transition system for  $VENDING\_GUM$  is: