## A High-Performance Data Acquisition System for Smart Cameras in Science

zur Erlangung des akademisches Grades eines

Doktors der Ingenieurwissenchaften

der Fakultät für Elektrotechnik und Informationstechnik des Karlsruher Instituts für Technologie (KIT)

genehmigte

**DISSERTATION**

von

**UROS STEVANOVIC**

Referent: Prof. Dr. Marc Weber

Korreferent: Prof. Dr.-Ing. Jürgen Becker Tag der mündlichen Prüfung: 12.12.2017

#### Zusammenfassung

Diese Dissertation führt eine neuartige intelligente Kameraplatform ein, die als flexibles Datenerfassungssystem für wissenschaftliche Anwendungen dient. Durch den aktuellen technologischen Fortschritt wurde die Leistung in den für uns relevanten Bereichen erhöht, diese sind hoher Datendurchsatz, Datenverarbeitung und Detektorenleistung. Aktuell Datenakquisitionslösungen konzentrieren sich in der Regel auf einen dieser Aspekte. Aber die Anforderungen wissenschaftliche Experimente an Datendurchsatz, Geschwindigeit und Flexibilität steigen, getrieben durch die Forschung, stetig an.

In dieser Dissertation stellen wir ein System vor, das neben einer High-Speed-Datenübertragung auch in der Lage ist eingehenden Daten frühzeitig zu interpretieren.

Um das volle Potenzial der Kameraplattform zu demonstrieren legen wir den Fokus auf Röntgenbildgebung mit Synchrotron-Lichtquellen. Anwendungen der Röntgenbildgebung können die Merkmale der technologischen und biologische Prozesse über Mikrosekunden bei der Röntgenographie und Millisekunden bei Tomographie Anwendungen untersuchen. Diese Anwendungen können unterschiedliche Sensoren und komplexe Experiment erfordern.

Die neue intelligente Kameraplattform ist Teil eines größeren Projektes, mit namen UFO, das ein neues Konzept für die Röntgenbildgebung einführt. Die Online-Datenbewertung wird verwendet, um ein datengesteuertes Feedback und aktives Management sowohl des Prozesses als auch der Datengewinnung zu ermöglichen. Dies wird mit einer GPU-Plattform zur schnellen Rekonstruktion, integrierte Datenverarbeitung auf der Kamera erreicht und Integration der Smart-Kamera in ein Datenerfassungssystem mit hoher Durchsatzrate.

Das endgültige Design der Smart-Kamera-Plattform besteht aus einer speziell angefertigten Hochleistungs-FPGA-Platine, die kontinuierliche Datenübertragung bietet, eingebettet Bildverarbeitung und eine flexible Eingangsstufe. In der IMAGE-Strahllinie von ANKA, die Kamera ist in das neue

Steuerungssystem integriert und wird in realen Anwendungen eingesetzt.

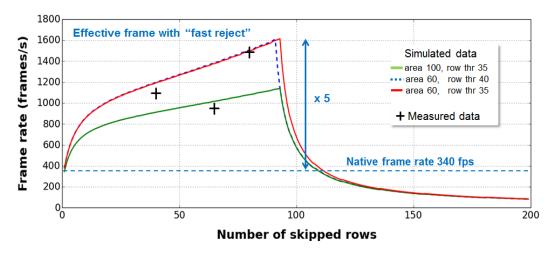

Ein maximaler Datendurchsatz von bis zu 8 GB/s wird erreicht. Ein angepasster Bild-basierte Algorithmus, mit strengen Echtzeit-Anforderungen, ist

in dem FPGA implementiert und erhöht die native Sensorgeschwindigkeit

bis zu Faktor fünf, wobei die Menge übermittelten Datenmenge gleichzeitig

reduziert wird. Mehrere Bildsensoren finden verwendung, jeweils mit einer

Auflösungen von bis zu 20 Megapixel und Bildraten von bis zu 5 kfps. Die

intelligente Kameraplattform fand auch Verwendung in nicht-bildgebenden Anwendungen, die aus der flexiblen Eingangsstufe resultieren. Die vorgeschlagene Kameraarchitektur ermöglicht es dem Benutzer, das System an jede Anwendung mit hoher Durchsatzrate anzupassen und die Verarbeitungsalgorithmen anzupassen oder spezifisch zu implementieren.

### **Abstract**

This dissertation proposes a novel smart camera platform serving as a flexible data acquisition system for scientific applications. Current technological progress offers increasing performance in the areas we consider, namely high data-throughput, data processing, and detector performance. Prevalent data acquisition solutions typically focus on one of these aspects. However, driven by science, experiments experience increasing demands in terms of data throughput, speed and flexibility. In this dissertation, we introduce a system which, in addition to being able to provide high-speed data transfer, is also capable of interpreting the incoming information at an early stage.

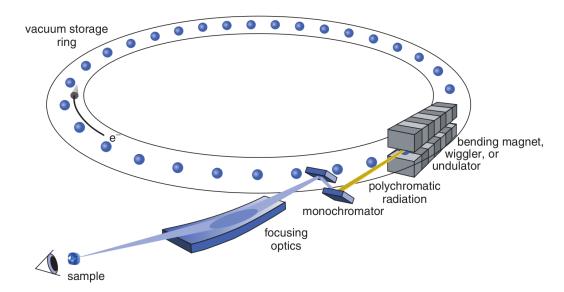

In order to demonstrate the full potential of the smart camera platform, we focus on X-ray imaging with synchrotron light sources. X-ray imaging applications can investigate the traits of technological and biological processes over microseconds for radiography, and milliseconds for tomography applications. These applications may require different sensors, and include complex experiment operations.

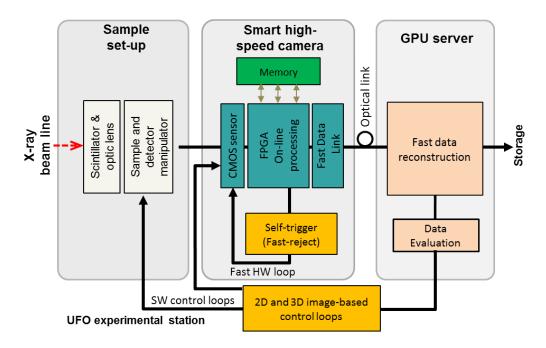

The new smart camera platform is part of a larger project, UFO, which introduces a new concept for X-ray imaging. On-line data assessment is used to provide a data-driven feedback and active management of both the process and data acquisition procedure. This is accomplished using a GPU platform for fast reconstruction, embedded on-camera data processing, and integrating smart camera in a high-throughput data acquisition system.

The final design of the smart camera platform consists of a custom high-performance FPGA board, providing continuous data transfer, embedded image processing, and a flexible input stage. In the IMAGE beamline of ANKA, camera is integrated in the new control system, and used in real-life applications. A maximum data-throughput of up to 8 GB/s is achieved. A custom image-based algorithm is implemented in the FPGA, with stringent real-time requirements, able to increase native sensor speed up to five times while reducing the amount of transfered data. Several image sensors are used, with resolutions of up to 20 megapixels and frame rates of up to 5 kfps. The smart camera platform was also used in non-imaging applications, stemming from the flexible input stage. The proposed camera architecture enables the user to modify the current system for any kind of high data-throughput applications, and to modify and implement custom processing algorithms.

#### Acknowledgement

I have many kind memories over the years it took me to finish my dissertation. There were certainly more than a few low moments, but I am confident that in the future I will remember them fondly. I am very grateful to Prof. Marc Weber, for giving me this opportunity, and for the patience and guidance during my work on the dissertation. I would also like to thank Dr. Andreas Kopmann and Dr. Michele Caselle, for their help in forming the dissertation and finding answers to relevant questions. Naturally, I would like to mention my colleagues Dr. Matthias Vogelgesang, Dr. Suren Chilingaryan, Dr. Lorenzo Rota and Timo Dritschler with whom I've spent many hours. For the numerous discussions we had, and for their friendship, I will always be thankful.

Last, but not least, my biggest gratitude and unending love to Reiko, for everything.

For Reiko

# **Contents**

| 1 | Intr | roduction                                     | 1   |

|---|------|-----------------------------------------------|-----|

| 2 | Sma  | art camera platform concept                   | 7   |

|   | 2.1  | History of the digital cameras                | 7   |

|   | 2.2  | Smart cameras — definition and classification | 8   |

|   | 2.3  | Smart camera platform for UFO project         | 10  |

|   | 2.4  | Custom smart camera platform concept          | 13  |

| 3 | Sma  | art camera platform implementation            | 17  |

|   | 3.1  | Data processing using FPGAs                   | 17  |

|   | 3.2  | Smart camera architecture design              |     |

| 4 | Det  | ector module — pixel detectors                | 49  |

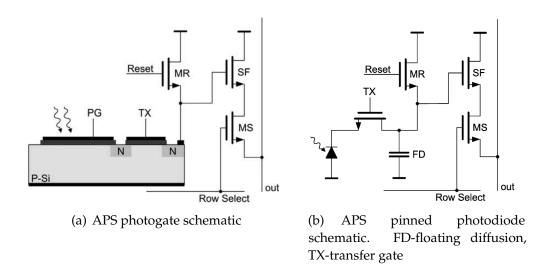

|   | 4.1  | Principle of operation                        | 49  |

|   | 4.2  | Charged-Coupled Devices (CCD) image sensors   | 60  |

|   | 4.3  | Monolithic CMOS image sensors                 | 62  |

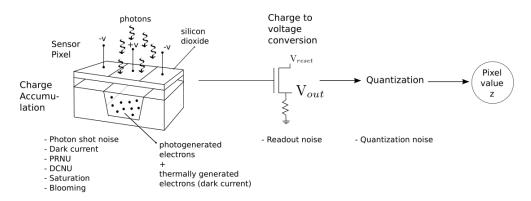

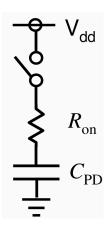

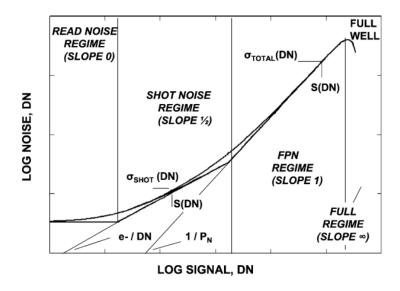

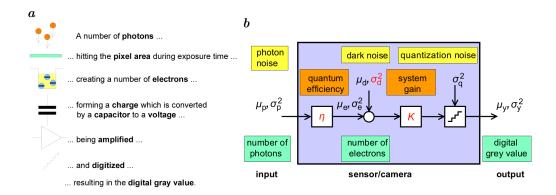

|   | 4.4  | Acquisition process and noise sources         | 67  |

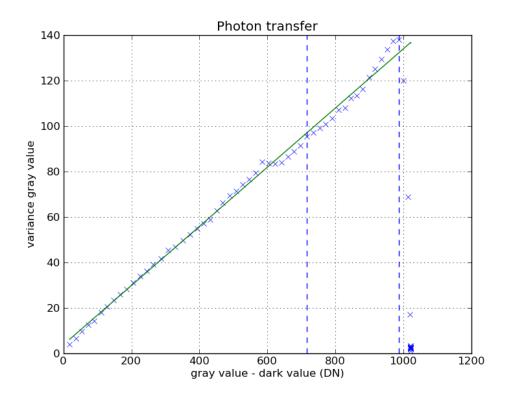

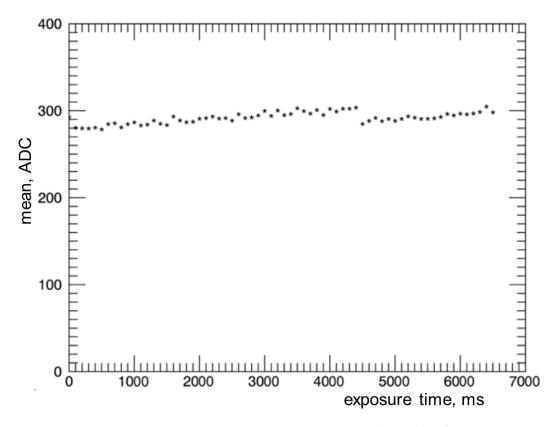

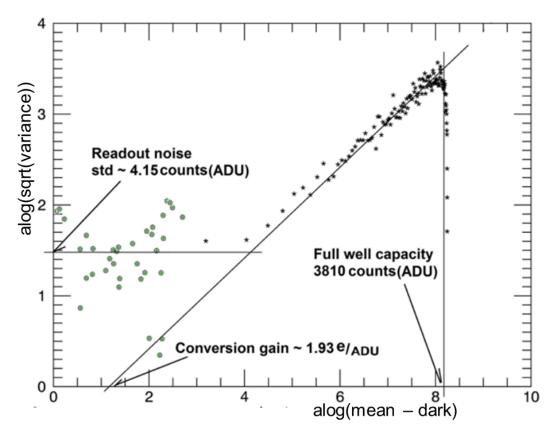

|   | 4.5  | Sensor characterization and comparison        | 71  |

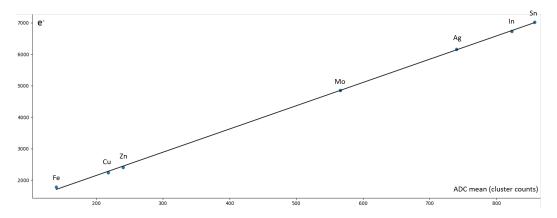

|   | 4.6  | Image sensors characterization results        | 74  |

| 5 | App  | olications                                    | 85  |

|   | 5.1  | X-ray applications                            | 85  |

|   | 5.2  | The UFO project                               | 91  |

|   | 5.3  | Fast reject algorithm                         | 97  |

|   | 5.4  | Expansion of the streaming platform           |     |

| 6 | Cor  | nclusion                                      | 113 |

## 1 Introduction

For the last several decades, Moore's law [1] has accurately predicted the advancement in the development of integrated circuits. In short, Moore's law states that every one to two years, the number of transistors in the same floor area will double. Even though the Moore's law is effectively ending [2], new design techniques still keep the technological progress active. With the decrease in size of transistors, the performance and speed of the integrated circuits have increased, while power consumption, size, and costs of the computing devices have decreased. This in turn has caused substantial performance improvements and the development of new concepts in computing, data transfer, and data acquisition.

For data intensive scientific imaging applications, there has been continuous progress in both data processing and digital sensors. For data processing, the initial setback caused by the power consumption [3, 4] and higher clock frequency was overcome by further scaling down of the technology (currently at 7 nm) and by the development of multithreaded and multi-core architectures. Beside multi-core processors, technological progress has led to the increased performance in large-scale parallel data tasks using massively parallel architectures such as Graphics Processing Units (GPU) and Field Programmable Gate Arrays (FPGAs).

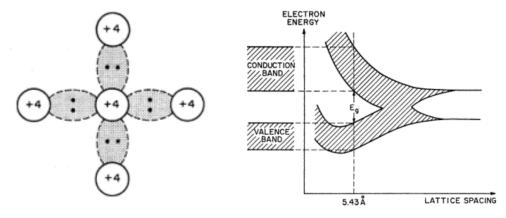

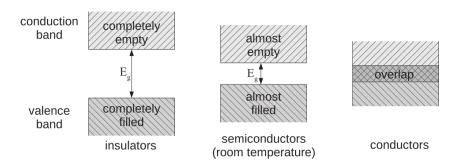

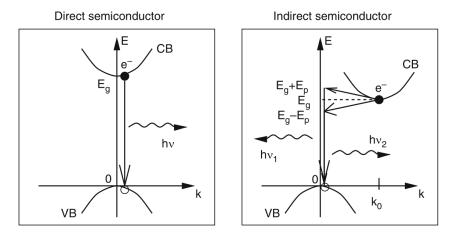

For visible photon detectors, the dominant technology up to the 2000s was the Charge Coupled Device (CCD) [5] due to its sensitivity and low noise performance. However, in the past decade, the maturity of the Complementary Metal Oxide Semiconductor (CMOS) technology provides attractive features, especially in terms of on-chip functionality, low power consumption, and high-speed imaging [6]. For high-speed imaging especially, modern CMOS sensors perform in tens of thousands frames per second (fps), with the data rates in several Giga Bytes per second (GB/s). This has led to new possibilities in scientific imaging applications, and to new challenges in obtaining and processing such high volumes of data.

The ongoing technological development, for the high-speed sensors and data processing capabilities, has not always been fully exploited so far. Up to now, there is no general technological solution that provides the user with the ability to easily couple sensors and data processing, while keeping the processing throughput that modern GPUs or FPGAs are capable of achiev-

2 Introduction

ing. Furthermore, commonly it is not possible to use the same data acquisition chain in applications with differing, sometimes even conflicting requirements. Present scientific imaging applications and experiments use a single device, a camera, to obtain visual data and transfer it to processing stage. Usually, the device is used with emphasis on one particular property, i.e. either the device focuses on the image sensor properties, data throughput, or internal data processing, but not all features are attained in a single device or camera.

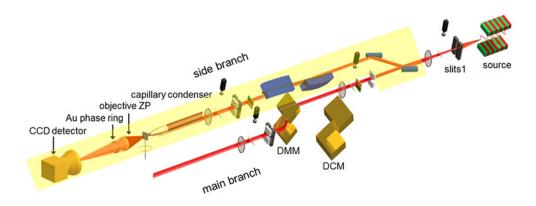

In this dissertation, we will present a smart camera platform for scientific vision applications capable of providing both high data throughput and performant data processing. As an example for scientific applications, X-ray imaging was selected, where synchrotron radiation light serves as a valuable tool for scientific and technological research and development. Synchrotron-based X-ray imaging is a powerful method for non-destructive, high-resolution investigations of a broad range of samples for life and material sciences. At the ANKA synchrotron radiation source, located at the Karlsruhe Institute of Technology [7], a new beamline is under construction for high-speed and high-precision X-ray imaging. The focus of the new beamline is on the non-invasive research of materials and biological samples. The high-brilliance and high-coherence synchrotron radiation facility allows sub-micrometer, quantitative, 2D and 3D imaging at micro- or nano-second time scale. Unlike conventional imaging applications, X-ray imaging experiments have challenging requirements for high data rate and streamed data processing.

Currently available high-speed commercial cameras have several draw-backs in terms of data transfer, recording time, and data processing. For example, at ANKA, for high-speed X-ray imaging applications a camera [8] is used, where most of the operating time is spent on the data transfer, rather than the data acquisition. This is due to the large discrepancy between the image sensor speed and the data transfer rate of the camera. Images are stored in the camera's internal buffer before being sent further. A new data acquisition is only possible when all data is transferred. This type of operation is typical for most commercial cameras. Consequently, commercial cameras are usually not able to provide online data processing, due to the limited or non-existent streaming capabilities.

Next common drawback of commercial cameras is in their construction as close systems, where firmware is not open to the users. Therefore adaptation, modification, and optimization of the cameras functionality to the application requirements is generally not possible. Additionally, image sensors within the camera are not interchangeable, and sensor parameters are

commonly hidden from the user, with very few parameters available for optimization. This in turn limits the usage of a camera, and typically more than one cameras with different sensor parameters are needed for experiments with divergent requirements.

This dissertation will present the architectural reasoning of the smart camera platform in order to answer the presented demands. The platform takes advantage of the current technological progress, leading to significant increases in the performance and speed. The platform is able to work with different sensors, or data inputs, and at the same time to provide high throughput data processing. We also provide a general data acquisition chain that can be used in other non-vision high throughput applications. The flexible design of the smart camera platform expands the possibilities of current scientific applications and at the same time serves as a tool for the development of new applications.

#### Research points and goals

High-performance and high-speed applications are not only needed for image applications. The goal of the smart camera platform is to provide a flexible approach for high-performance and high-throughput data acqui-The ANKA accelerator consists of a 53 MeV microtron as a preaccelerator, a 500 MeV booster synchrotron and a 2.5 GeV storage ring [9]. For X-ray imaging applications, KIT's ANKA IMAGE beamline [10] provides high-energy and high-coherence X-ray beams, which are suitable for a data acquisition with a high sampling rate and high spatial resolution. The IMAGE beamline is developed as a part of a new project called UFO ("Ultra-Fast X-ray Imaging of Scientific Processes with On-line Assessment and Data-driven Process Control") [11]. The main project goals are to provide fast feedback based on data, and fast online reconstruction, in order to optimize the beam and actively control the experiments. This enables, for example, the investigations of processes at a micrometer level, and studying changes that occur on a microsecond scale. Additionally, it provides the ability to scan more samples and items within the same time period. High spatial resolution was initially achieved using "indirect detection" and cameras with CCD sensors, however, in order to achieve the highest frame rates, in the order of thousand fps, the most promising idea is to use CMOS sensors instead [12]. With this, commercial components can also be employed.

For high-speed imaging, approaches were to either use custom made devices [13], or more commonly, to use commercial cameras [14, 15]. However, commercial systems impose a hard limit on the users, i.e. there is no cur-

4 Introduction

rently available detector that is capable to continuously stream data at a millisecond or sub-millisecond time range to the processing stage. The current devices usually poses an internal memory that is used to store the data at the highest rate, and data is subsequently transferred further. The streaming capability is necessary in order to optimize the performance, such as increasing the duration of the experiment, improving beam time usage, obtaining all the desired results, or implementing novel data-based feedback loops.

Increasing the data throughput, spatial and temporal resolution, requires a flexible detector that is able to cope with the large amount of data and different experiment requirements. Besides, the lack of embedded data processing prevents novel experiments based on event-triggered feedback, or the ability to control the experiment based on the data processing results.

Advancing reactive, fast experiments necessitates a detector capable of high-throughput data acquisition, data processing, as well as versatility in operating image sensors. So far, none of the experiment setups provide the necessary solutions to such requirements. Instead, the usual approach is to use commercial systems or solutions tailored to one particular experiment that may limit the achievable results. Since the detector, or a camera, is intended to be used by scientists who do not necessarily have an engineering background, it is important to provide interface to the camera that "feels" familiar, and is not complicated to use. Therefore, the camera must work as commercial ones, and must provide simple access to its more sophisticated features such as embedded processing.

Focusing on these identified current limitations, the main questions addressed in this dissertation are:

- **Flexible and exchangeable input stage.** X-ray imaging experiments have differing requirements in terms of speed, data throughput, and spatial and temporal resolution. The requirement for the new camera platform is *modularity*, where sensors can be interchanged as necessary, or replaced with a custom input stage for non-vision applications.

- **High-throughput data streaming.** High-speed imaging applications, with framerate in hundreds of fps and sensor resolution in megapixels (MPix), have demanding requirements for data transfer. Typically, this would necessitate data transfers that exceeds several GB/s. The smart camera platform has a hard imperative to handle this throughput.

- Embedded processing. In order to achieve data-driven fast feedback, real-time data processing near the sensor is needed. The data processing is required to extract the relevant scientific information and to re-

duce the amount of raw data. Furthermore, depending on the application, different data processing algorithms can be implemented.

These questions led to the problems and design considerations further delineated in the remaining chapters. The focus of a novel smart camera framework is to to improve the current limitations of existing solutions, and to enable easy customization for experiments. The main design goals of the smart camera platform are modularity, streaming capability, and embedded data processing. With modularity, the sensor or detecting device can be chosen according to experiment demands, and access to its all parameters is available to the user. Streaming removes the bottleneck of acquiring the data at full image sensor speed, with further benefits of beam usage optimization and eliminating the hard experiment time limits. Using the embedded processing capabilities, it is possible to have preprocessing close to the sensor, or implement image processing algorithms, or to have a feedback based event capture, or any combination of the three.

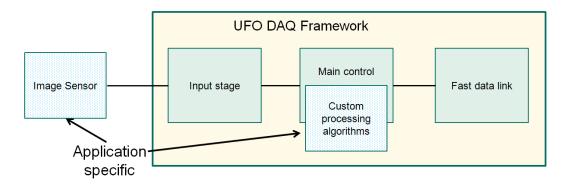

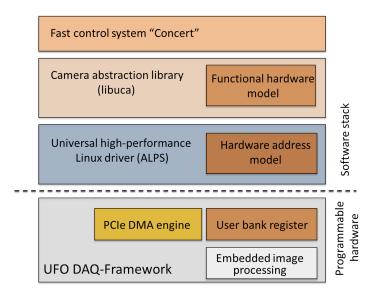

The smart camera platform is part of the general UFO DAQ framework [11], and it is accompanied by the readout PC and GPU servers for enhanced processing. This setup allows the partitioning of functions in programmable logic, readout PC or accelerators (like GPUs or FPGAs). As mentioned, the camera will be used for X-ray imaging, and the benefits of such camera is further highlighted with the integration in the IMAGE beamline control setup [16]. The following chapter provides an overview of the existing smart camera solutions, explains in more details the concept behind the smart camera platform, and makes the case for the architectural solutions used in its final design.

# 2 Smart camera platform concept

A smart camera is a vision system that can perform tasks far beyond simply taking photos and recording videos. Smart cameras are not simple vision devices but they are embedded systems that can process and extract the information from the incoming data. Smart cameras combine video sensing, processing, and communication. Their area of applications has vastly expanded in recent years, and includes, among others, industrial vision, robotics, traffic control, security systems, high-performance imaging. They can detect motion, measure objects, interpret human behavior. The ever increasing demands in speed, amount of information, and real-time data processing have caused a growing interest in the research communities for the development and expansion of smart cameras. The advantages of the smart cameras over conventional cameras is in providing image analysis with the image acquisition, often in one compact system. This chapter will present the history and development of the smart and, naturally, digital cameras, as well as the goals and rationale for the implemented smart camera platform.

#### 2.1 History of the digital cameras

Digital cameras capture and store images in digital form on digital memory cards, internal storage memory, or transfer data directly to the receiving device. The concept of digitizing video signals was initially used in scanners [17]. The history of the digital cameras starts with the development of the first practical videotape recorder (VTR). Charles Ginsburg led the development of the first practical implementation at Ampex Corporation [18, 19]. It converted the incoming electrical impulses and stored the information onto magnetic tape.

The advancement of digital photography was influenced by the US space program and military spy applications. Early spy satellites used airborne retrieval of photographs on film, which was complicated. This created a need for an electronic image capturing device that could replace film. NASA switched to digital technology in the 1960s, during the development of the Apollo Lunar Exploration Program. The first time the "digital photography" was mentioned was in 1961 by Eugene F. Lally of the Jet Propulsion Laboratory, when he published the first description of how to produce digital

still photos using a mosaic photosensor [20]. The purpose was to provide onboard navigation information to astronauts on missions to planets.

Solid state imaging started in 1960s, when different research groups were working on NMOS, PMOS, and bipolar processes with varying degree of success. In 1963, a structure that allowed the determination of the spatial position of a light spot was mentioned [21]. IBM presented in 1964 the *Scanistor* [22], which used an array of npn junctions. The term "pixel" was mentioned for the first time in 1964 [23]. A monolithic mosaic of photon sensors was presented in 1966, with a monolithic 50 x 50 pixel array of phototransistors [24].

All of these sensors operated without integration, and their sensitivity was very low. Weimer et al. [25] introduced in 1967 a 180 x 180 pixel sensor array using CdS/CdSe thin-film transistors. Noble [26] described in 1968 several configurations of self-scanning silicon image detector arrays, and also documented the issue of fixed pattern noise [27]. The first charge-coupled device (CCD) chip was proposed by Boyle and Smith in 1969 [28]. The first confirmed attempt at building an actual digital camera was in 1975 by Kodak [29]. The camera consisted of the solid state CCD image sensor chips developed by Fairchild Semiconductor in 1973 [30]. The camera recorded black and white images to a cassette tape, with a resolution of 0.01 MPix, and took 23 seconds to record an image. In 1981 Sony launched *Mavica* electronic still camera. In 1985 Fairchild introduced the first line scan camera, using a sensor array with pixels in one row only. The first megapixel image sensor was introduced by Kodak in 1986 [31].

The development of the digital cameras, and consequently smart cameras, was closely related to the progress of digital electronics. More advanced features were only made possible with the recent advancement in processing capabilities of integrated circuits.

#### 2.2 Smart cameras — definition and classification

The earliest commercial smart cameras can be traced back to the 1980s, with the invention of optical mouse [32]. The sensing and processing capabilities of early smart cameras were very limited. Their applications were very limited as well, mostly to perform simple machine vision tasks.

When we speak about what are "smart cameras", there is no clear definition of the term smart camera. According to *Belbachir et al.* [31], the first publication of the term was in 1975 [33]. There are many established descriptions of smart cameras, but they differ between manufacturers, areas of applications, and academic groups. In most definitions, the image process-

ing feature is stressed as the crucial one, however, many cameras have some kind of processing capabilities. Most modern consumer cameras provide processing such as auto-focus, automatic white-balance, or image compression, among others. This does not, however, make them "smart". The processing functions are provided with the purpose of improving image quality, or for data reduction and more efficient data transfer. The main purpose of image processing in smart cameras is to generate events, react, or to provide decisions for other devices, all in an automated fashion, depending on the extracted information from the incoming images.

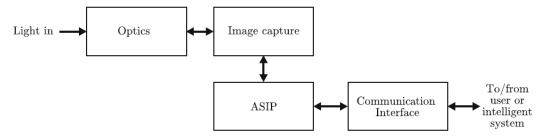

A simplified representation of the smart camera structure, found in one of the seminal books on the subject [31], is shown in Figure 2.1. The *optics*

**Figure 2.1.** Simplified functional structure of a smart camera, from [31].

provide the proper illumination of the image sensor. The *image capture* block consists of a solid-state image sensor (CMOS or CCD) and associated circuits or components that ensure conversion from light to digitized image array. The application-specific information processing (ASIP) block is what makes the camera smart. The goal of ASIP is not only to provide better image quality, for example by removing noise, but to process and extract the information from the incoming images and react or propagate the information to the user or for further processing. The *communication interface* receives commands or instructions from a user or a host, and sends out data or decisions to a user or an intelligent system.

Belbachir et al. [31] defines three important aspects for a smart or "intelligent" camera:

- *Frame acquisition* defines the ability of the camera to acquire images. The images do not necessarily have to be in visible light (e.g. infrared cameras).

- *Embedded processing* in cameras is achieved using FPGA, Digital Signal Processor (DSP), or a CPU/GPU combination. Embedded memory and communication interface are also needed for the camera to operate in autonomous and automatic way.

• Event generation means that the camera utilizes the built-in processing capabilities not only for improving the image quality, but also to detect a predefined event, and to be able to properly react to it.

This can be compared to the concept of *Trigger* in High Energy Physics (HEP), where *Frame acquisition* corresponds to data acquisition, *Embedded processing* to processing of the initial data, and *Event generation* to event building, used to define when and which data should be stored for offline analysis [34].

As with the absence of the common definition of the smart cameras, there is also no general classification of the smart cameras. One way of classifying smart cameras can be based on their functionality. This has the advantage to provide clear indication where the smart cameras are used, e.g. smart cameras can be used in machine vision, robotics, surveillance, etc., and they can be categorized accordingly. The classification used in [35] classifies the camera whether the processing occurs in sensors itself ("artificial retinas"), in the PC which is connected to the camera ("PC-based systems"), or the camera possesses internal processing capability ("stand-alone cameras"). This however, does not include the distributed smart cameras.

In [36], cameras are organized in three general groups: single smart cameras, distributed smart cameras, and pervasive smart cameras. For single smart cameras, processing could be realized in the image sensor [37], DSP [38, 39], FPGA [40], or using processors [41]. Distributed smart cameras are formed when multiple smart cameras are integrated in a single common network. One of the benefits is the extended sensor coverage. Here too, exists several classification whether the smart cameras are organized in a centralized or decentralized manner, with various architectures and applications [42, 43, 44, 45]. Pervasive smart cameras integrate flexibility and autonomy to distributed smart cameras [46, 47, 48].

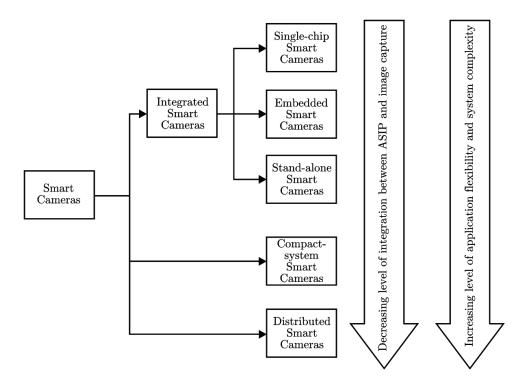

Belbachir et al. classification is shown in Figure 2.2. Similar classification can be found in other publications, e.g. [49]. It is similar to already mentioned classifications with more detailed information. Main three categories are: integrated smart cameras, compact-system smart cameras, and distributed smart cameras. Integrated smart cameras are further classified in three types: single chip smart cameras, embedded smart cameras, and stand-alone smart cameras. Their structure and common field of usage is shown in Table 2.1.

#### 2.3 Smart camera platform for UFO project

The project Ultra Fast X-ray imaging of scientific processes with On-line assessment and data-driven process control (UFO) aims to develop the next

**Figure 2.2.** Smart camera classification. From top to bottom, cameras have decreasing level of integration (from [31])

generation of a X-ray computer tomography experimental station optimized for 3D and 4D imaging. The improved time resolution will give insight into the temporal evolution, allows scientists to better understand functional units of devices and organisms and helps to optimize technical processes. The whole setup consists of three sections: the beamline providing X-rays, the UFO experimental station, and a high-performance data storage system (more details in 5.2).

In order to establish high-speed volumetric imaging, some of the identified bottlenecks and limitations are embedded data processing, high-speed readout, and data transfer. Most modern cameras are a "black box", meaning that modifications of the existing functionality is not supported. Furthermore, it is not possible to implement any data processing on-camera. The other mentioned bottleneck in commercial cameras is in their relatively slow data transfer (usually, less than 1 GB/s) [50]. This is true even for high-speed cameras, which use internal memory to store the data at their highest speed, e.g. PCO [8]. These limitations exclude most commercial high-speed cameras, and smart camera platform was designed to overcome the limitations.

The smart camera platform extends the original definition of smart cam-

| Туре                                | Structure                                                                           | Applications                                                                                                     |  |

|-------------------------------------|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--|

| Single chip<br>smart camera         | ASIP on the same chip as<br>the image sensor,<br>extremely low power,<br>small size | Toys, sensors                                                                                                    |  |

| Embedded smart cameras              | Camera is embedded in another device such as a mobile phone                         | Optical mice, fingerprint readers, smart camera phones                                                           |  |

| Stand-alone<br>smart cameras        | "Normal" smart cameras, single camera casing                                        | Industrial machine vision,<br>human computer<br>interfaces                                                       |  |

| Compact-<br>system smart<br>cameras | ASIP in a separate embedded system (e.g. PC)                                        | Security, traffic surveillance, machine vision                                                                   |  |

| Distributed smart cameras           | Part of the system ASIP rendered by the network topology                            | Intelligent and pervasive video surveillance, industrial machine vision, pervasive information gathering systems |  |

**Table 2.1.** Structure and example applications of smart cameras (from [31])

eras (in Chapter 2.2) by adding the modularity, with the exchangeable sensors for front-end modification. Additionally, it removes the identified bottlenecks with high-throughput streaming to eliminate the latency between the frames coming from the sensor and the processing stage, and provides embedded processing. This is illustrated in Figure 2.3.

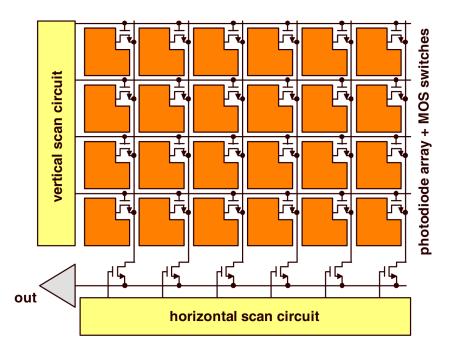

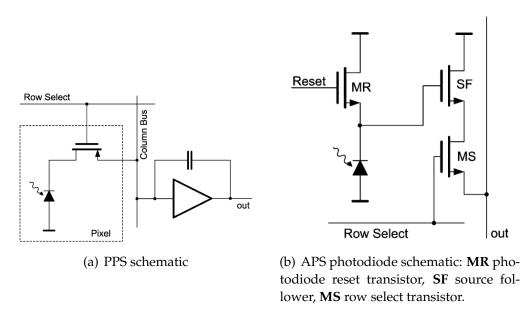

FPGAs are selected for the smart camera design, due to their flexibility to interface with other hardware periphery, their modifiability and parallel processing capabilities [51, 35, 40]. As imaging components, CMOS image sensors were selected, due to their advantages over CCDs, in terms of high-speed and ease of operation. The structure and the functionality of the basic building blocks are explained in more detail in subsequent chapters.

**Figure 2.3.** Smart camera platform concept. The application specific areas are easily modifiable to fit the applications requirements. The underlying basic structure and interface do not have to be modified.

#### 2.4 Custom smart camera platform concept

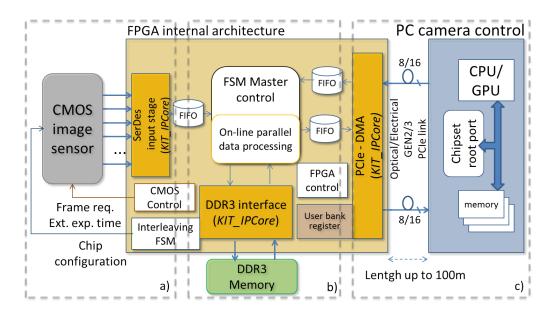

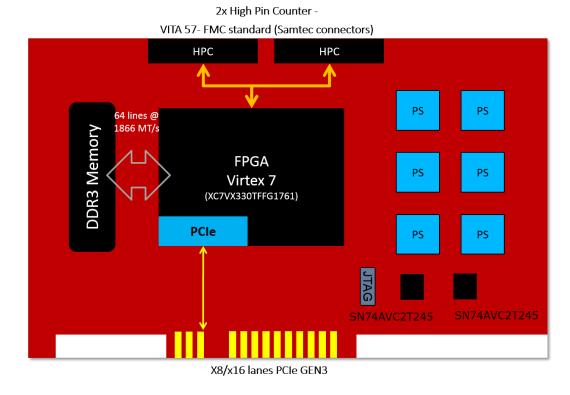

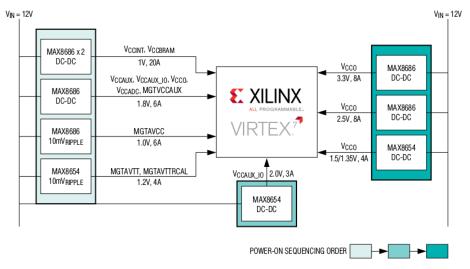

Many definitions of smart cameras emphasize the built-in image processing ability [31]. Smart cameras are capable of extracting application-specific information from the captured images. The technological progress in integrated circuit design provide special effectiveness for smart camera design, producing speed, flexibility and parallel processing capabilities. Flexible camera architectures can be adapted to a large number of applications. FPGAs provide dedicated functional blocks and task parallelism that can perform complex processing operations with real time constraints [40] and are successfully used to accelerate computing applications [51]. This dissertation proposes a modular FPGA-based high-throughput platform that is intended for scientific high-speed imaging applications [52, 53]. The architecture of the camera is presented in Figure 2.4. The CMOS image sensors are selected as the image sensing devices, located on the interchangeable daughter carrier cards. The main readout board contains a Virtex-based Xilinx [54] FPGA and Dual-Data Rate (DDR) Random Access Memory (RAM) memory. The FPGA architecture contains the interface to the CMOS sensor, data readout and the custom logic.

#### Concept of modularity

For the selected field of usage for the smart camera platform, X-ray synchrotron imaging, there are different, and sometimes mutually exclusive requirements for experiments. Third generation synchrotron sources are almost ideal instruments for a large number of applications, like structural biology and material science. The possibilities for the improvement and the development of new studies have only expanded in recent years with

**Figure 2.4.** Smart camera architecture. We can identify three main areas: a) modularity, with the CMOS sensor and input stage, b) embedded processing stage, and c) fast streaming readout.

the technological development [55]. Depending which techniques are employed (e.g. crystallography and tomography), and on the desired observed processes, the requirements in terms of speed, resolution, amount of data differ. The usual approach in resolving these conflicting demands was to have several different cameras with image sensors attuned for one specific condition. This may complicate the operation of the beamline, since each camera needs to be integrated in the beamline.

The modular design of the smart camera offers the opportunity to select the CMOS image sensors according to the application requirements and the respective sensor characteristics, while the means of operating the camera has not changed. Furthermore, as we can see in Figure 2.4, the camera platform can be used as a data acquisition platform, where input stage can be decoupled from the rest of the architecture. More information will be provided in the subsequent chapters.

#### **Embedded processing**

FPGAs for image acquisition and preprocessing were already existing in the 1990s [56, 57, 58]. With the technological advancements, FPGAs were applied for more complex operations [58, 59]. Field programmable devices provides flexibility, reconfigurability, and parallel processing, which are especially suitable for smart camera design. FPGAs provide dedicated func-

tional blocks and task parallelism that can perform or accelerate complex processing operations with real-time constraints [40]. Our smart camera platform was used to implement a custom image processing algorithm, fast reject, of which more details are provided in Chapter 5.3.

#### High data throughput

Modern high-speed image sensors provide a large amount of data, e.g. AM1X5 image sensor [60] has a speed of 5kfps with 1Kx1K pixels, which corresponds to 50Gb/s of data. As shown in Figure 2.4, a standard PCI Express (PCIe) connection is provided to transfer the data from the camera directly to the computer. The benefits of using PCIe are low overhead and a high data throughput. For example, PCIe GEN3 x8 (8-lanes connection of generation 3) provides a bandwidth of 64 Gb/s [61]. A custom PCIe-DMA (Direct Memory Access) module, operating as a Bus Master, i.e. it can request a control of the PCIe bus, is used for a continuous data transfer to the system memory. The principle of operation of the custom DMA module will be explained later.

# 3 Smart camera platform implementation

Smart camera platform was designed with flexibility and versatility as main features. In the first part of the chapter, we will present the history and features of the FPGAs, and present their suitability for embedded processing. We will also review current smart camera implementations. In the second part, we will present the final implementation of the smart camera platform, in the form of a custom FPGA board, designed and produced in IPE, KIT. We will explain how the functionalities of the platform are partitioned, and the reasoning behind it.

#### 3.1 Data processing using FPGAs

Reconfigurable hardware (RH), which is what FPGAs essentially are, provides flexibility for implementing features and functionalities in hardware. The hardware consist of a set of logic and routing resources controlled by configuration memory. Originally, reconfigurable hardware was used as a glue logic, connecting functionalities implemented in Application Specific Integrated Circuits (ASIC). As the price per unit and functionalities of the FPGAs are improving, the fixed-design ASICs are becoming less appealing [62]. Many applications benefit from the ability for fine grained tailoring of the functionalities to the application, or, e.g. the ability to reconfigure the hardware at runtime [63]. The applications of interest to us are scientific data acquisition and analysis [64, 65], and image and video applications. As mentioned in [63], for image and video applications, design can be easily changed to fit the application [66, 67].

#### FPGAs — History and structure

A Field-Programmable Gate Array (FPGA) is a large-scale integrated circuit that can be programmed after it is manufactured rather than being limited to a predetermined, unchangeable hardware function. The term "field-programmable" refers to the ability to change the operation of the device "in the field", while "gate array" is a somewhat dated reference to the basic internal architecture that makes this after-the-fact reprogramming possible

[68]. FPGAs have become one of the key digital circuit implementation media over the last decade. A crucial part of operating FPGAs lies in their architecture, which controls their programmable logic functionality and their programmable interconnect ability [69]. One main advantage of the FPGAs over the conventional computers and their Arithmetic Logic Units (ALU) is that the functionalities are implemented and executed as a parallel process, rather than sequential. More information about this is presented later in the dissertation.

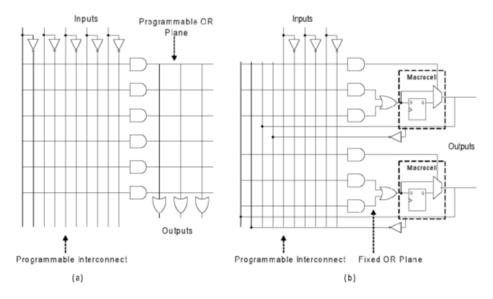

The origin of the FPGAs is related to the development of the integrated circuits in the 1960s. The ability to change the logic function of a chip after the fabrication process was achieved with the introduction of cellular arrays [70]. The functionality of each logic cell in the array could be determined by setting programmable fuses, with the use of programming currents or photo-conduction exposure. In the 1970s, devices based on read-only memory (ROM) were produced. These first circuits, programmable logic arrays (PLA), and later, programmable array logic (PAL), relied on the AND-OR logic planes to achieve the desired functionality [71], as shown in Figure 3.1. The first modern FPGA was manufactured by Xilinx in 1984 [72]. It con-

**Figure 3.1.** PLA(a) and PAL(b) structure. [69]

tained 64 logic blocks and 58 inputs and outputs (I/O). Current FPGAs contain around 2 million logic cells and have around 1200 I/O pins [73, 74]. They have sufficient logic resources (and associated interconnect routing) to implement many complex applications on a single chip [75]. More recent trends have led to the integration of specific functional blocks within the FPGA, including multipliers, memories, high speed input-output interfaces,

and even serial processor cores [76].

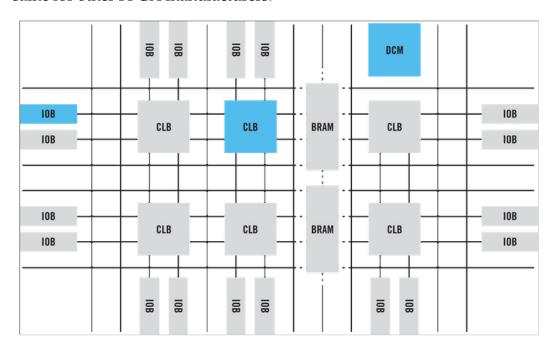

FPGAs are based around a matrix of Configurable Logic Blocks (CLBs) connected through programmable interconnects. As opposed to Application Specific Integrated Circuits (ASICs), where the device is custom built for the particular design, FPGAs can be programmed to the desired application or functionality requirements. Although One-Time Programmable (OTP) FPGAs are available, the dominant type are SRAM-based, which can be reprogrammed as the design evolves. While the structure of the FPGA shown in Figure 3.2 uses Xilinx terminology, i.e. CLB, the principle is the same for other FPGA manufacturers.

*Figure 3.2.* FPGA block structure, from Xilinx [77]

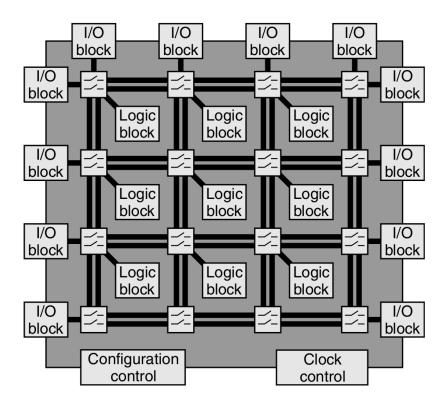

Another, more general representation of the FPGas can be found in Figure 3.3. The basic logic blocks are usually based on look-up table (LUT) structure, making them being able to implement any logical function. The logic blocks are usually organized in a grid structure and interconnected via a programmable routing matrix that enables the blocks to be connected in arbitrary configurations. This also means that any signal can be connected to virtually any I/O pin of the device, with some limits in the performance. FPGAs also have to provide clock synchronization to control the timing of the clock signal relative to an external source. A clock distribution network provides clock signals to all parts of the FPGA while limiting the clock skew between different sections of a design. There is also some dedicated logic for loading the configuration into the FPGA. This logic does not directly form

Figure 3.3. FPGA basic architecture, from [75]

part of the users design, but is required for FPGAs to be programmable [75]. The flexibility of the FPGAs leads to an increase in area, delay, and power consumption versus ASIC: an FPGA requires approximately 20 to 35 times more area than a standard cell ASIC, has a speed performance roughly 3 to 4 times slower than an ASIC and consumes roughly 10 times as much dynamic power [78]. These disadvantages arise largely from an FPGA's programmable routing fabric which trades area, speed, and power in return for ease of use and reconfigurability. However, despite these disadvantages FPGAs are increasingly used in the digital design. With the advances in the Moore's law and by the current state of the art of deep submicron ASIC technology, it is becoming increasingly demanding in terms of time and money to design an ASIC. The Computer Aided Design tools (CAD) necessary for synthesis, rooting, simulation, and etc. are becoming increasingly expensive, as are the production costs. This makes FPGA design a common choice when a small volume and a fast turnaround are required.

#### Programming principles of the FPGAs

Each FPGA uses some programming technology to control the switches that provides the programmability of the FPGAs. There are several pro-

gramming technologies and their differences have a significant effect on programmable logic architecture. The approaches that have been used historically include EPROM [79], EEPROM [80], flash [81], static memory [72] and anti-fuses [82]. Of these approaches, only the flash, static memory and anti-fuse approaches are widely used in modern FPGAs [69].

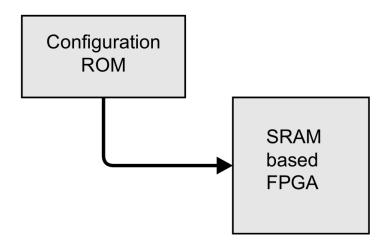

FPGAs are programmed by loading the configuration file into the internal memory. The configuration file is previously generated by the user and streamed onto the FPGA. When using the external flash memory, shown in Figure 3.4, FPGA boards can be set-up in a such way that they are automatically configured on power-on. Naturally, FPGAs can be reconfigured at any time, also serially (usually by JTAG), or by loading a new configuration file in the flash memory [75].

**Figure 3.4.** FPGA configuration [75]

The two main FPGA manufacturers in terms of market share are Xilinx and Altera, although there are several others that provide FPGAs. The basic structure of these FPGA providers always correspond to what was already described, FPGA vendors also provide custom functionalities, in the form of Intellectual Property (IP) designs. These can be in the form of hard IP, where the functionality is already present as an on-die structure, and soft IP, where the core is delivered in a Hardware Description Language (HDL) or as a synthesizable netlist. With the recent technological developments the functionalities, and therefore internal structure, have experienced greater diversification. In the case of Xilinx and Altera, for example, modern FPGA chips provide multiple on-die designs, such as hard-IP processors, or PCIe IP designs.

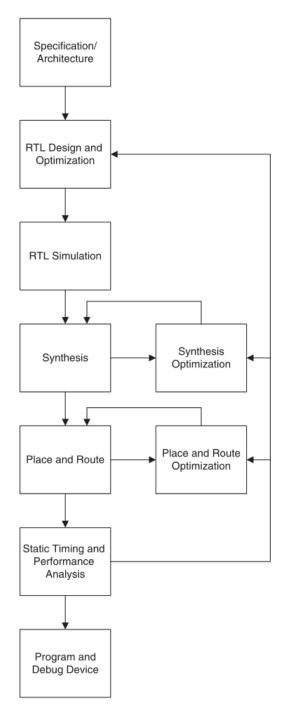

Typical FPGA design flow is presented in Figure 3.5. It consists of several key steps. The design must be presented in an easy to read form. While

Figure 3.5. FPGA design flow [83]

originally the hardware was designed using schematics, the complexity of modern systems makes that impractical. Now design is typically done using HDLs. The two most common languages employed in logic circuit designs are Very high speed integrated circuits (VHSIC) Hardware Description Lan-

guage (VHDL) [84] and Verilog [85]. Using these languages, the user can describe the hardware architecture at different levels of abstraction, using a hierarchical and modular approach [86]. It is important to notice the difference between the behavioral HDL and synthesized HDL. Only the latter will actually produce an exact representation of the final circuit.

Register Transfer Level (RTL) design and simulation describes circuits at a higher level of abstraction. The lowest level is the transistor-level design, which involves connecting transistors into circuits to build gates and components. Next higher level is logic-level design, whose building blocks are logic gates. RTL design is the next abstraction level, which describes the data transfer between registers, through other logical components [87]. Simulation results are bit and cycle accurate, which means that the simulation results should match the hardware representation [86].

Synthesis is the next step in the flow, which creates a netlist representing the actual hardware from the logic described using HDLs. Usually this representation is in Electronic Design Interchange Format (EDIF) [88], which is vendor neutral. Synthesis constraints control aspects of the synthesis process, and help optimize design for speed, area, power consumption [75].

Mapping, placing, and routing the design are the next step. First, the logic is mapped to actual available components. Afterwards, these components are placed in particular logical blocks of the FPGA, and the routing is determined to connect them. Previously mentioned constraints are here also used to define the critical timing, as well as actual Input/Output (I/O) pins. This is an interactive phase of the design, and it can be run several times, also with changes in the RTL design if needed, to achieve desired results. In the final step, a configuration file needed to program the FPGA is generated [75].

#### Overview of the image processing algorithms for FPGA

Image processing and accelerating image processing using FPGAs is not a new concept. Naturally, FPGAs are not the only devices applied for such purpose. There is a large body of research comparing FPGAs with not just CPUs, but also GPUs [89]. For many applications, GPUs provide better performance [90, 91]. GPUs are a good fit for applications where the processing algorithm can be efficiently mapped in high-level languages, and when there is no inter-dependency in the data flow. FPGAs are a good fit for applications that may involve a lot of detailed low-level hardware control operations and when taking advantage of data streaming and pipelining is especially important [92]. For embedded applications, and for this work, FPGAs are a more natural fit.

Embedded systems are usually dedicated to a specific task or purpose [93]. However, FPGAs with programmability and reconfigurability provide flexibility in developing the desired applications [94]. As mentioned, FPGAs also have the ability for parallel execution and data processing. Embedded image processing on FPGAs is, naturally, a subset of more general digital signal processing that is possible with FPGAs. Digital signal processing has many applications, in telecommunication, speech, audio, robotics, and, as mentioned, image and video processing [95].

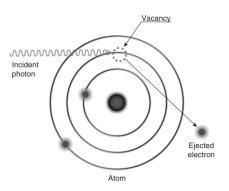

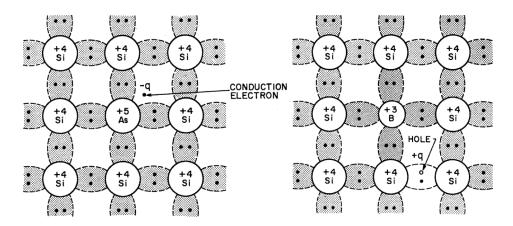

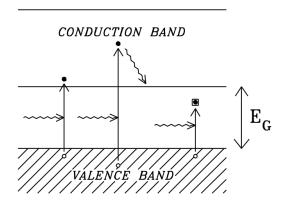

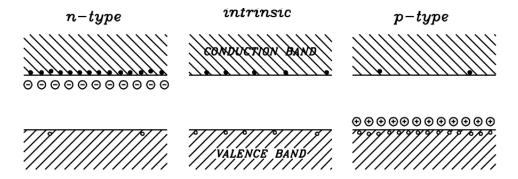

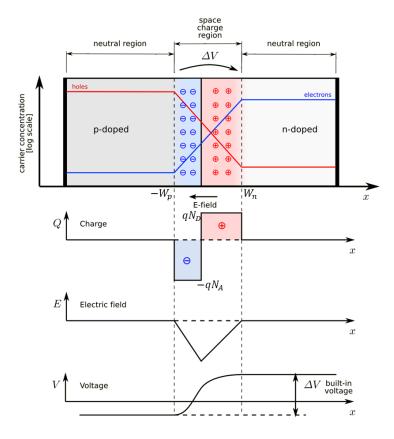

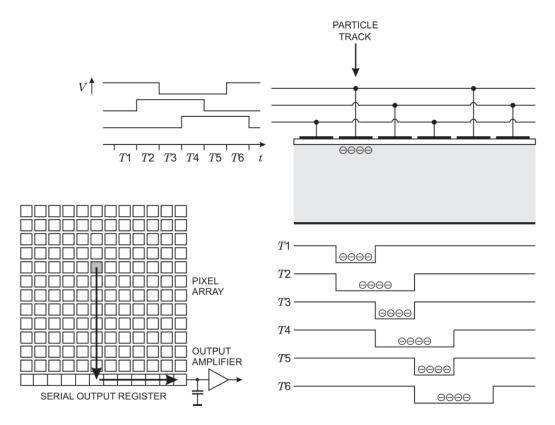

When the light reaches the image sensor, it is converted to an electrical signal. Digital image sensors transfer the signal as an already digitized information. The methods of operation of CCDs and CMOS active pixel sensors are explained in Chapter 4. This chapter will present the image processing operations conducted when the digitized image reaches the FPGA.

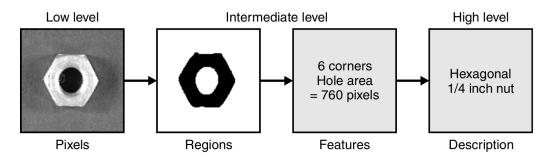

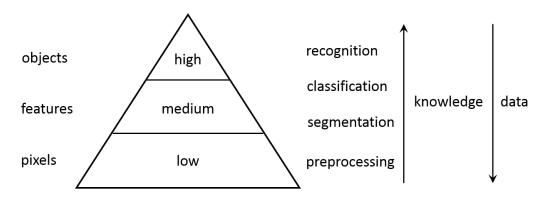

In "Design for Embedded Image Processing of FPGAs", by Donald Bayes, image processing algorithm is defined as "the sequence of image processing operations used to process an image from one state to another" [75]. Digital image processing, or image vision techniques, can be classified into three classes, low-level image processing algorithms, intermediate-level image processing algorithms, and high-level image processing algorithms [96]. For the low-level algorithms, input and output is still a digital image. With the intermediate processing algorithms, the input is a digital image, but the output can be a low-level symbolic representation of the image features, e.g. contour of the object, or a label associated with a region. High-level algorithms utilize symbolic representation as both input and output [96].

The classification of image processing algorithms is depicted in Figure 3.6. At the low level, the image is represented as a group of pixels. On their own, individual pixel may posses low information, which can be of high volume, however. If we move to a higher, intermediate level, with grouping the corresponding pixels in meaningful regions, they may provide more information. The part of images, or a group of pixels, can carry more information than just the value of their pixels. Features may be extracted, e.g. the location of an object, or extricating different objects from one another. At the high level, the extracted data is usually about distinguished regions that may carry the information used to classify an object into a category, or, be used to describe an object [75].

The classification of image processing operations can also be represented as an image processing pyramid, where the algorithms are classified into three levels: low, intermediate, and high [97, 98, 99], shown in Figure 3.7.

Low-level operations are at the bottom of the pyramid, and usually, they are preprocessing operations. They are typically pixel-based operations, such

**Figure 3.6.** Image transformation example, from low level to high level of information (from [75])

Figure 3.7. Image processing pyramid (from [99] and [75])

as filtering and edge detection [100]. The purpose of these operations is enhancing the relevant information and removing irrelevant data, e.g. noise [75]. These operations typically work on large volumes of data, and include simple computation, like multiplication and addition.

At the medium level, algorithms process digital image, and produce set of lines or regions [99]. These can be segmentation and classification algorithms. Segmentation operations can be thresholding or color detection, and these algorithms are at the boundary between the low and intermediate levels. The purpose of segmentation is to detect objects or regions of interest, which have a desired quality.

After segmentation comes classification, where features of regions may determine or classify objects. Classification transforms the data from regions to features, and then to labels. The data is no longer image based, but position information can be contained within the features, or be associated with the labels. At the highest level, processing operations produce objects from symbolic inputs such as image features. One such operation is recognition, which derives a description or some other interpretation of the scene [75].

Depending on what type of image processing operations perform on, they

can be grouped in histogram operations, point operations, and filters [101]. Histograms are statistic representation of the image. In case of gray scale images, histograms represent the frequency of occurrence of gray levels [102]. For example, in case of 8-bit gray scale images, a histogram may contain a maximum of  $2^8 = 256$  entries. Operations on histograms may include image enhancements, such as those involving contrast and dynamic range. Since no information of about where each pixel is located in the image, histograms do not present any visual information about the appearances of the objects inside the image. Therefore, reconstruction of the image from a histogram is in general not possible [101]. Considering that in this dissertation we place emphasis on identifying and extracting information about objects, histogram operations are not of interest for this work.

Filter operations need more than one pixel from the source image for computing a new value of the pixel [101]. Usually, these multiple pixel values, or area or a window, are in the vicinity of the desired output pixel. The window size is arbitrary, and depends on the chosen operation and the intended result. Typically, filters are divided into linear and nonlinear filters. Some filter operations include smoothing of the picture, or detection of simple local structures (like edges). Furthermore, filter operations can detect motion, or be used for reconstruction and restoration of images, and noise reduction [103]. Since multiple pixels are needed for filters, for stream processing, parts of the images may be partly or wholly buffered [104]. This may impose constraints on the performance.

Unlike with filter operations, point operations are performed on a single pixel [101]. The value of the pixel depends only on the corresponding pixel value of the input image or input images, since point operations may be applied between multiple images [75]. In case of a single image, typical operations are modifying brightness and contrast, thresholding, and intensity transformations.

Of particular interest for this work are operations on multiple images, especially image subtraction and image comparison, since high performance point operations can be implemented in hardware [75]. Image subtraction is used to match one image against another. One commonly used operations to determine the similarity is the sum of absolute differences (SAD):

$$SAD(x, y, i, j) = \sum_{l=0}^{M-1} \sum_{k=0}^{N-1} \left| A_{(x+l, y+k)} - B_{(x+i+l, y+j+k)} \right|$$

(3.1)

where at the current block location, i.e. (x,y),  $A_{(x+l,y+k)}$  and  $B_{(x+i+l,y+j+k)}$  represent blocks of pixels of the current and certain reference frame, respectively [105]. Values (x,y,i,j) are pixel locations within an image, or spatial

coordinates, while values (l,k) represent frame numbers, or temporal coordinates.

A second technique to ascertain the similarity between images is the sum of squared differences (SSD):

$$SSD(x, y, i, j) = \sum_{l=0}^{M-1} \sum_{k=0}^{N-1} \left( A_{(x+l, y+k)} - B_{(x+i+l, y+j+k)} \right)^2$$

(3.2)

SAD or SSD techniques can be used to detect changes in images. SAD is commonly used in fast motion estimation algorithms [106]. This is portrayed in Figure 3.8. Using SAD, the zero difference between pixels signifies

Figure 3.8. Illustration of image difference for change detection (from [75]). Left image is the original; in centre is the new image, with highlighted changes; right image represents the difference (with the difference highlighted). Offset is used to represent zero difference as mid-gray.

no changes, while non-zero results indicates difference in the image [107]. The absence of objects can be detected, but also the shifts in the position of the objects. One important caveat when using SAD is that the presence of noise, camera vibrations, or the variable illumination between images will also result in a difference. There are several possible approaches to these problems. One approach for illumination difference is to establish a stable, possibly artificial, lighting. Furthermore, if the images are acquired with small exposure time, the lighting difference between images will be low. Small exposure time may also reduce the influence of some sources of noise. Additional approach is to provide a dynamic estimation of the background, which can adapt if conditions change, and may serve to remove the influence of variable illumination and noise [75]. For camera vibrations, for the applications we consider in this work, the experimental setup precludes the occurence of vibrations.

For an adaptive background, which may include the presence of noise, the approach might be to start from the initial static background, and provide

a dynamic estimate of the succesive backgrounds [108]. Simple models can be determing mean value [109], or median value of previous images [110]. Limitiation of the mean approach is the sensitivity of the parts of images which are variable by default, such as outdoors scenes. More robust models are using bimodal and multimodal backgrounds, with complex modeling for each pixel value [111].

An additional approach might combine SAD methods with thresholding, where values below certain thresholds might be considered as noise or background, or simply the lower values might indicate movement that can be disregarded. This is especially the case with complex scenes and backgrounds. Double differencing can be used to detect changes between images. It uses data from three successive images. This type of algorithms has been implemented to detect human motion [112], and also for vehicle detection using FPGA [113].

For stream processing, considering that each pixel can be processed independently, point operations may be implemented in parallel. This is particularly well suited for hardware implementations. With stream processing, we can convert spatial parallelism to temporal parallelism. The image is read and stored row by row, as explained in Chapter 4, but pixels can be processed while being read-out. When needed for more complex processing, operations can be pipelined in order to maintain the needed throughput. This is especially important for high-throughput applications. With point operations, small or no neighborhood is used, therefore caching requirements are low. With stream operations, latency requirements can be fine-tuned, and specialized hardware, like FIFO, can be used to synchronize outputs from multiple different operations. In this case, when operation latency is much smalled than loading of the whole image, the algorithm execution time is determined by the frame rate [75].

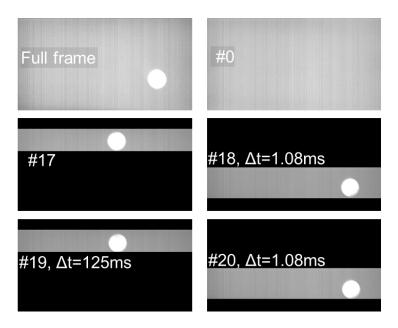

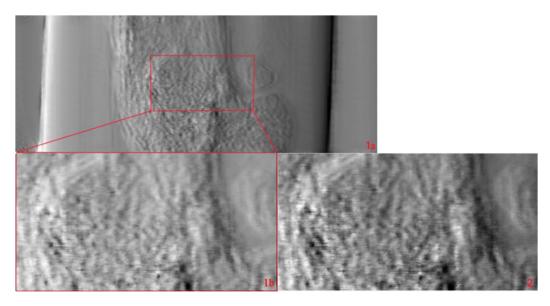

Taking these details into account, as well the initial requirements of stream data processing, high-data throughput, and fast feedback, in this dissertation we opt for implementing a stream point data processing algorithm in smart camera platform. In Chapter 5.3, an implementation of the custom stream processing algorithm, named fast reject, is presented. This algorithm relies on point operations using thresholding and SAD to detect changes in multiple part of images.

## 3.2 Smart camera architecture design

X-ray imaging is a key technology for providing advances in medical diagnostics, homeland security, materials research and biology. Non-destructive

X-ray imaging at synchrotron light sources enables micrometer and sub-micrometer resolutions. Typical applications are micro-tomography, fast radiography (radioscopy) and holotomography.

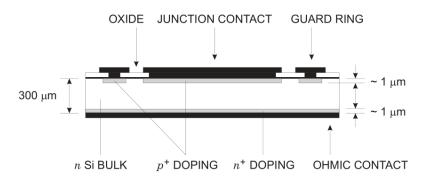

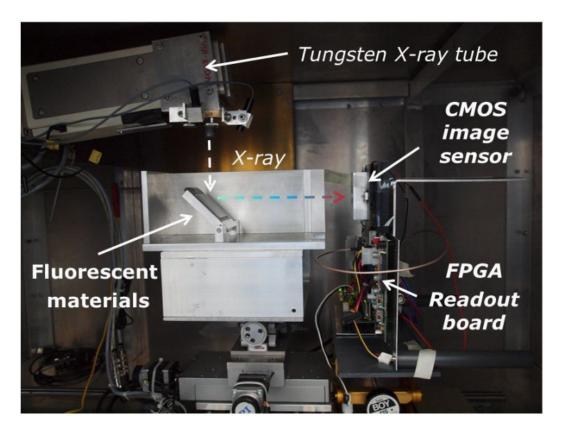

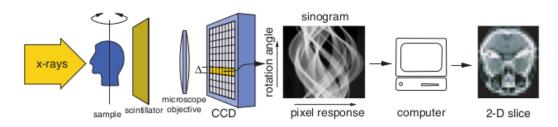

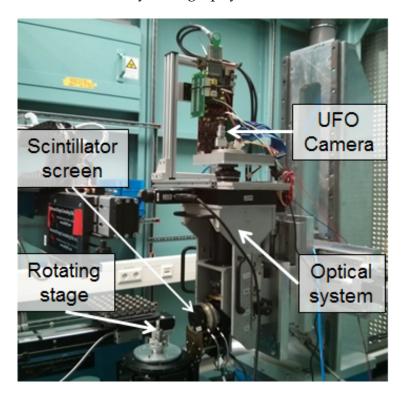

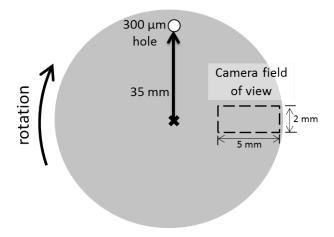

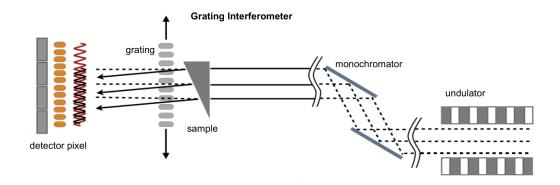

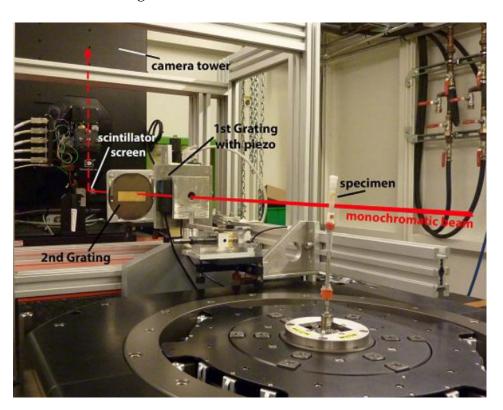

Charge-Coupled Device (CCD) and hybrid pixel detectors which are commonly used in direct X-ray imaging are limited in terms of pixel size, radiation resistance and X-ray stopping power [114, 115]. In order to improve the X-ray absorption, indirect detection methods, coupling CCD or Complementary Metal-Oxide-Semiconductor (CMOS) image sensors to a scintillator, are used [116]. Fast X-ray detectors and a short exposure time are necessary requirements for investigating fast processes in real-time or reducing the samples' radiation dose during in vivo experiments [12]. Also, in order to conduct experiments with a large number of samples there is a need to reduce the required time for a micro-tomography sequence [117], [118]. Within the framework of the UFO project [11] an experimental station is built in the IMAGE beamline of KIT's ANKA synchrotron radiation facility. The station will cover a large variety of scan geometries and contrast mechanism. The UFO project aims to push the present limits of high-speed X-ray imaging and introduces a novel concept with on-line data assessment, data driven feedback, and active control of both the sample and the measuring procedure.

### Architecture description

The UFO Data Acquisition (DAQ) chain consists of three main elements: a smart high-speed camera platform, real-time high-performance Graphics Processing Units (GPU) computing stage and feedback control loops. Fast volumetric X-ray imaging has already been achieved in the range of a few tens of ms but is presently limited to a few seconds of total acquisition time. The low acquisition time is caused by the limited internal memory storage and the high recording frame rate of commercial cameras. Subsequent data transfer from the internal camera memory to the external computer is performed at a much lower speed [119].

By removing on-camera memory buffers on our smart camera, the duration of the acquisition is prolonged and limited only by the size of the main memory (RAM) of the recording computer. The smart camera also serves as a platform for embedded image processing which can be used to increase the effective frame rate or as an internal feedback loop. With frames being streamed directly to system RAM, a high-performance GPU-based computing stage can process the data in real-time. On-line data evaluation is used as an image-based control loop for the sample manipulator and for controlling the experiment conditions.

The detector setup consists of a transparent single crystal scintillator coupled to a CCD or a CMOS image sensor readout through diffraction-limited magnifying optics [120, 121]. Indirect detection methods in X-ray imaging have been extensively explored and applied in synchrotron light sources since the early 1990s [122].

The new DAQ framework enables continuous data acquisition at the highest speed and offers real-time data assessment. This novel concept of databased feedback leads provides opportunities for new experiments.

A key feature of the smart camera are built-in embedded processing capabilities able to extract application-specific information from the captured images [53]. FPGAs are used in smart camera designs because of the flexibility to interface with other hardware periphery and their parallel processing capabilities. The camera uses a daughter carrier board to host the image sensor, which is based on Monolithic Active Pixel CMOS sensor. In order to satisfy the main goals mentioned in Chapter 2.4, namely *Modularity*, *Embedded processing*, *and High-data throughput*, the camera also needs to be fully configurable. Full access to the image sensor or other detector properties are provided to the user. This is crucial in order to adapt the pixel response to any experiment condition. Parameters such as adjustable gain, or image exposure time, noise threshold can be adjusted by the user.

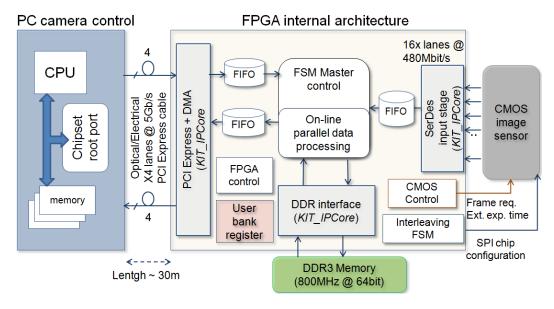

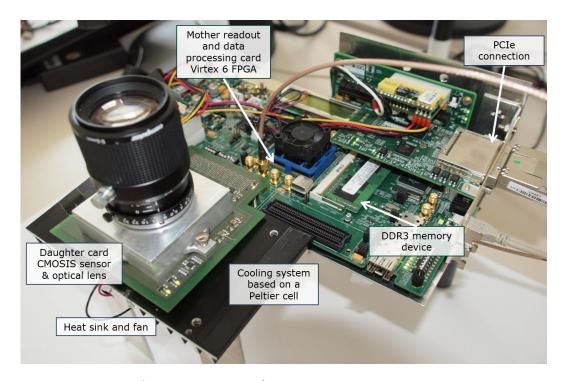

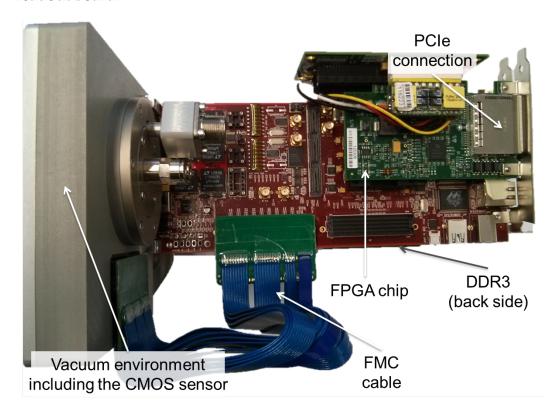

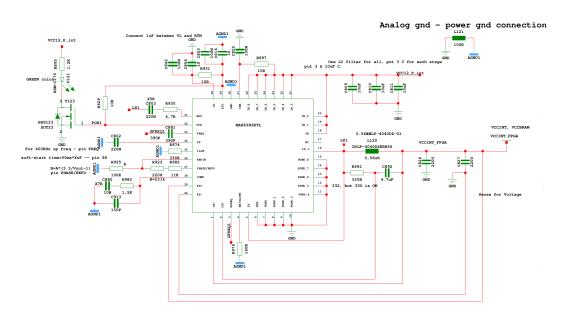

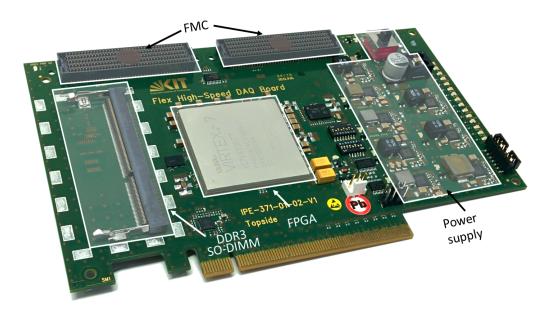

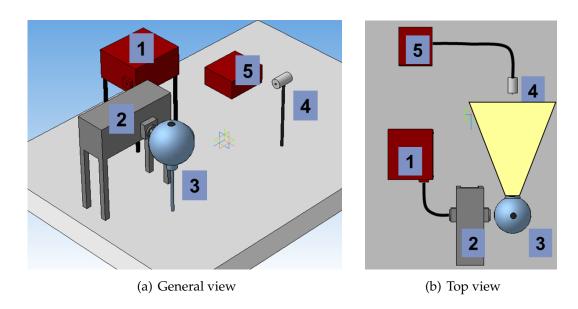

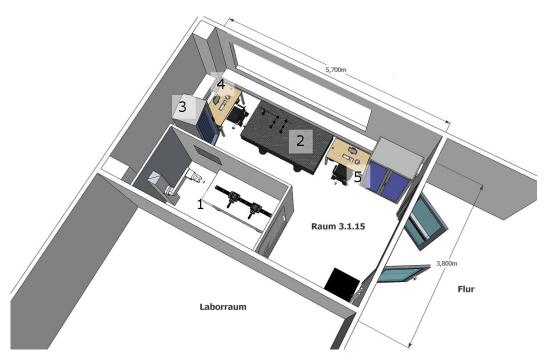

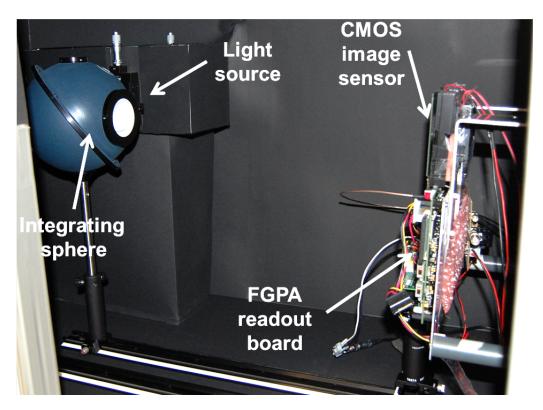

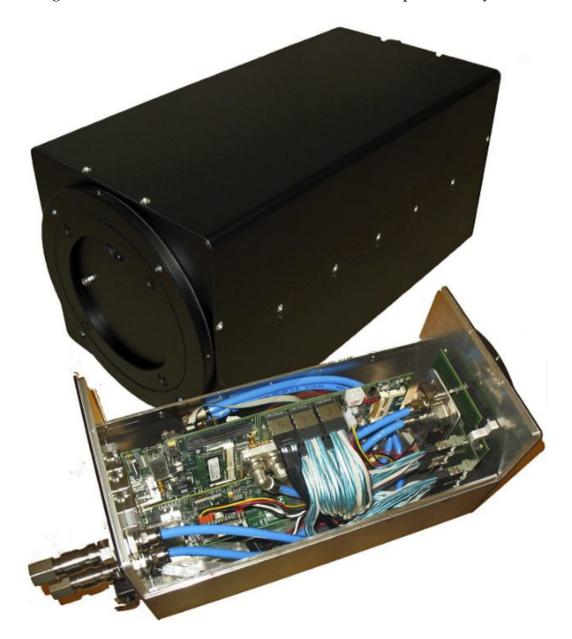

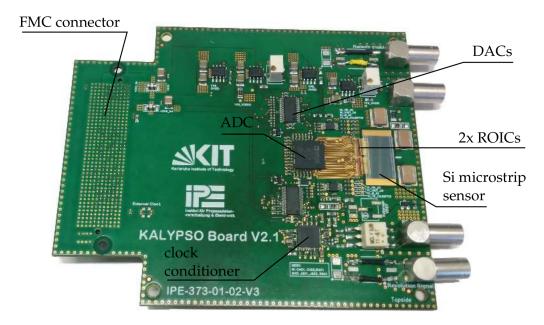

The development was split in two versions, with the first iteration being developed using commercially available components, while the second version was realized on a custom Printed Circuit Board (PCB) FPGA board. The reasoning for these steps is to speed up the development while focusing on the new concepts, and to provide a proof-of-concept relatively soon. The initial architecture is shown in the Figure 3.9. The architecture is divided into three main parts: CMOS-image sensor, Xilinx Virtex-6 FPGA board [123] and a PC used for controlling the camera and for storing and for further data processing. The modular design of the camera provides the ability to select the CMOS image sensors. Image sensors are connected to the board using an FPGA Mezzanine Card (FMC) connector [124]. A custom image-based self-event trigger algorithm is also implemented in the FPGA. The initial accomplished smart camera prototype is shown in Figure 3.10.

### **Initial Data Acquisition Architecture**

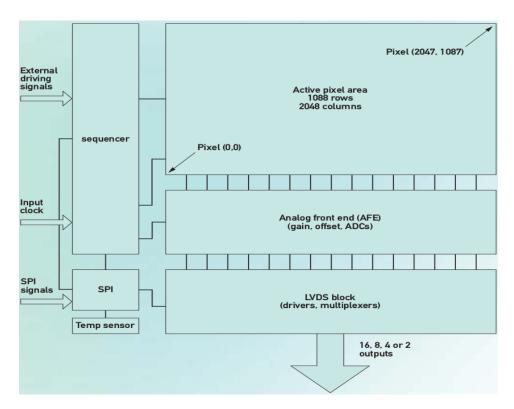

The initial CMOS image sensor selected was CMOSIS CMV2000 [125], with its architecture shown in Figure 3.11. The CMV2000 has a pixel size of 5.5  $\mu$ m x 5.5  $\mu$ m and a nominal frame rate of 330 frames per second (fps) at 2.2 MPixels. It is provided as a monochromatic or color sensor with 10 to 12 bits resolution. More information about the sensor is provided in the chapter on

*Figure 3.9. Smart camera platform* — *Initial architecture*

Figure 3.10. Initial smart camera prototype

sensor characterization.

Communication with the sensor is done using Serial Peripheral Interface (SPI). Clock and control signals are provided by the FPGA. All sensor parameters, like gain, offset, exposure time, are stored in control registers, and programmed using SPI. When the exposure or integration time is provided

Figure 3.11. CMV2000 architecture, from [125]

to the sensor, and the FPGA issues a frame request command, the image is stored in the pixel-matrix (with a global electronic shutter). The pixel values are passed through the Analog Front End (AFE) and digitized. These values are transfered using Low Voltage Differential Signal (LVDS) channels. Each LVDS channel is responsible for a group of adjacent columns of the pixel matrix.

In order to read out the camera system as fast as possible, a standard PCI Express (PCIe) cable connection is used to transfer the data from the camera directly to the main computer memory. In the first camera design, a 4 lanes connection is utilized. There are passive copper cables and active optical links available for this interface. The PCIe x4 lane generation 2 connection has a theoretical bandwidth of 16 Gbit/s. Direct Memory Access (DMA) is used to transfer the data from the camera to the main computer memory and vice versa. By using PC memory, we avoid the bottleneck of "dead time" between data acquisitions. Also, by not being limited by an in-camera memory, we can acquire much more data, considering that the memory available for PCs are much larger and can therefore hold much more data. Third benefit is that the data processing can start immediately after acquiring data.

Addressable 32-bit user bank registers are implemented in the dedicated

Base Address Register (BAR) space. Bank registers are used to read/write the status/configurations of DMA engines, CMOS sensor and FPGA logic. Further bank locations can be used for additional user applications. The DDR memory device is used for both temporary frame data storage and for image processing algorithms.

The three main blocks, as seen in Figure 3.9 present the foundation of the smart camera platform. Embedded processing and flexibility is built on top of it. The next chapters will explain the initial implementation of these hardware building blocks.

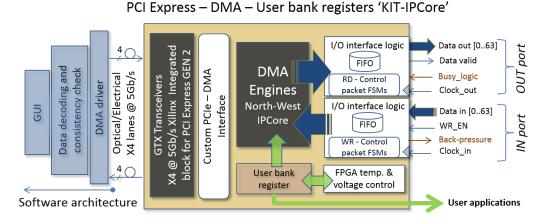

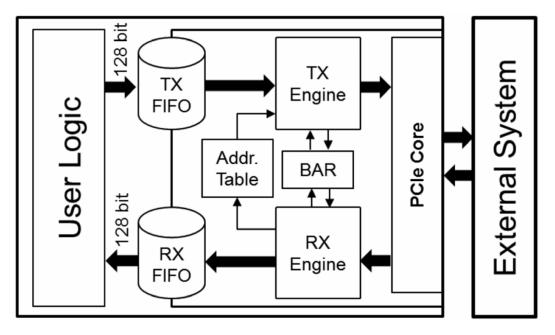

### First DMA-PCIe Architecture

The first module handles the communication via the PCIe interface. The term "Bus Master", used in the context of PCIe, indicates the ability of a PCIe port to initiate PCIe transactions, typically memory read and write transactions. The most common application for "Bus Mastering Endpoints" is for DMA. DMA is a technique for efficient data transfer to and from host CPU system memory. This implementation has many advantages over standard Programmed Input/Output (PIO) data transfers. In addition, the DMA engine offloads the CPU from directly transferring the data, resulting in better overall system performance through lower CPU utilization. The initial PCIe-DMA architecture is presented in Figure 3.12. Two IP cores are employed in combination with the logic blocks developed at KIT. An integrated Endpoint Xilinx-IP core for PCIe [126] and two Northwest Logic DMA [127] engines are used to move the data from the FPGA board to the PC central memory and vice versa. A custom PCIe-DMA interface logic has been developed to adapt the Xilinx PCIe interface to the DMA engines.

Figure 3.12. PCIe-DMA Architecture using Northwest IP

The interface with the internal FPGA logic is provided by two I/O logic

blocks. Each logic block includes a data First-In First-Out (FIFO) memory block and a Finite State Machine (FSM) to provide the control for the received and transmitted data packets. The FSMs generate the start and end of packet signals for DMA and manage the situation when the PC is not able to receive the data packets. This is important, since no data packets should be lost.

The FIFOs are used as a temporary data storage during streaming and, when needed, for communication and transferring data between different clock domains. In this way the defined clocks,  $Clock\_in$  and  $Clock\_out$ , can be used to send and receive data even though operating on a different frequencies. The  $Data\_out$  and  $Data\_valid$  signals are synchronized with the user defined  $Clock\_out$  domain. The  $Data\_valid$  signal is used to inform the rest of the logic when the valid data are present on the data out bus. A busy signal is used to temporary stop the data flow received from the FPGA internal logic. The  $WR\_EN$  signal allows writing a data word at the  $Data\_in$  bus using  $Clock\_in$  frequency. The  $Back\_pressure$  signal informs the FPGA logic that the PC is busy, and not presently able to receive the data.

### Input stage logic

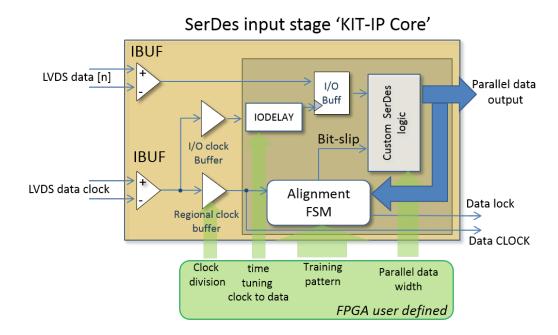

The SerDes (serializer/deserializer) module is used for communication between image sensor and FPGA. SerDes are devices that take parallel, single-ended signal buses and transforms them them to a few, typically one, differential signal that works at a much higher frequency rate than a wide single-ended data bus. SerDes provides a point-to-point transfer of of data. The clock division, parallel data width, and the training pattern are configurable according to the CMOS image sensor specifications. The image sensor used in the camera prototype has 16 parallel high-frequency LVDS serial lines to move data from the pixel-matrix to the FPGA. Each line provides data at a double data rate with 480 Mbits/s. Furthermore, the ADC resolution of 10 bits or 12 bits per pixel can be selected. This has an impact on the SerDes logic that must translate serial input to 10-bit or 12-bit parallel output. To overcome the SerDes logic limitations in the Virtex6 FPGA [123], a new SerDes input stage module has been developed. The basic architecture of a single SerDes channel is shown in Figure 3.13.

To cover all image sensor outputs, 16 parallel SerDes input stages are utilized. A common FPGA regional clock for all 16 input stages has been defined as a division of the LVDS data clock according to the parallel data width. An individual programmable absolute delay primitive block, IODE-LAY [128], is used for a precise 80 ps step time synchronization between data and clock. The LVDS input data line is converted from double data rate

**Figure 3.13.** SerDes architecture

to two single-ended data lines by a double data rate (IDDR) register [128]. Lines are then combined for parallel data output by the custom SerDes logic. The dedicated word alignment FSM checks the correct position of the Most Significant Bit (MSB) in the parallel data output by comparing it with the training pattern. A bit-slip signal is generated from the alignment FSM and received from the custom SerDes and used to shift the wrong MSB bit to the correct position. A data lock signal informs the rest of the logic about the correct alignment of the parallel data.

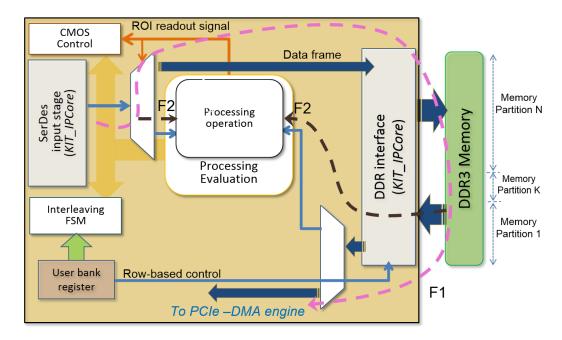

### **DDR3 RAM Memory Interface**

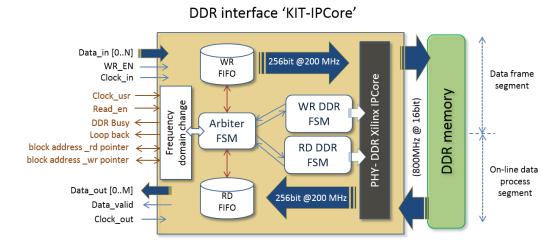

The new memory interface logic combines a Xilinx physical layer (PHY) for DDR3 devices with custom additional logic. The new development extends the memory interface Xilinx IP core [129] features and overcomes the limitations present in the DDR3 IP core provided by the Xilinx, shown in Figure 3.14. The  $WR\_EN$  signals writing a data word with a user defined data width present at the  $Data\_in$  bus. A WR-FIFO block is used as a temporary data storage and for a clock domain change between user clock frequency,  $Clock\_in$ , and internal logic clock domain. The Arbiter FSM continuously checks if the WR-FIFO is empty. If not, the enable signal for the write operation is propagated to the WR-DDR FSM. The WR-DDR FSM receives a write command and generates the address and all necessary control signals for the PHY logic. The PHY logic receives the command and writes the incoming

data in the address position specified by the WR-DDR FSM.

Figure 3.14. RAM memory interface

The Arbiter FSM can receive a read request for the DDR3 device. In this case, the Arbiter inquires if the WR-DDR FSM is in "idle" state. If true, a read command is transmitted to the RD-DDR FSM. The RD-DDR FSM receives a read command and as in write cycle, generates the necessary signals for the PHY logic. The output data from the PHY are stored in the RD-FIFO. According to the user defined data width, a data word is present at the  $Data\_out$  port. A  $Data\_valid$  signal informs the user logic that the data is ready. All signals are synchronized to the user defined  $Clock\_out$ .

The internal read and write paths work with a data width of 256 bits at 200 MHz internal clock that corresponds to a bandwidth of 51 Gbit/s in a half-duplex mode. This bandwidth limitation is imposed by the PHY logic in the used Virtex 6 FPGA speed-grade. Nevertheless, a quasi full-duplex data flow is achieved with the proposed architecture. Balancing the amount of the data in both FIFOs is managed by the Arbiter FSM. With this, an intelligent burst write and read commands can be alternatively issued to the PHY. This in effect provides a full-duplex DDR3 interface with a mean bandwidth of 25 GBit/s for both read and write.

### Evolution of the hardware architecture

The initial smart camera platform was successfully implemented. It was used in real X-ray radiography and tomography experiments and it was successfully integrated in the control system. As a proof-of-concept, image-based self-trigger algorithm was implemented and demonstrated the applicability of the smart camera platform for embedded processing. The second

phase of the development aimed to increase the performance and capabilities of the initial design and stress the main qualities of the smart camera platform.

### Modular approach — multiple CMOS image sensors

The modular design of the smart camera offers the opportunity to select the CMOS image sensors according to the experimental requirements and the respective sensor characteristics such as spatial and temporal resolution, dynamic range, noise influence, etc. Figure 3.15 shows the physical camera architecture for a particular sensor daughter board and the fixed FPGA readout board.

**Figure 3.15.** The smart camera system with exchangeable image sensors and the FPGA readout board

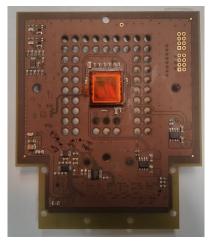

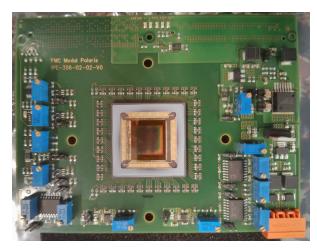

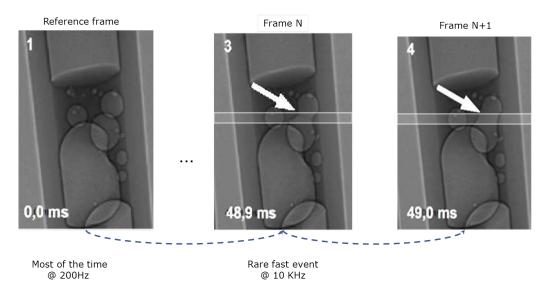

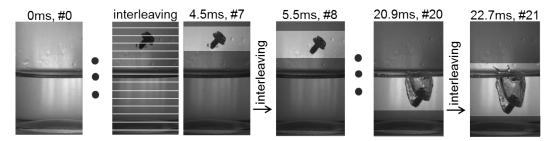

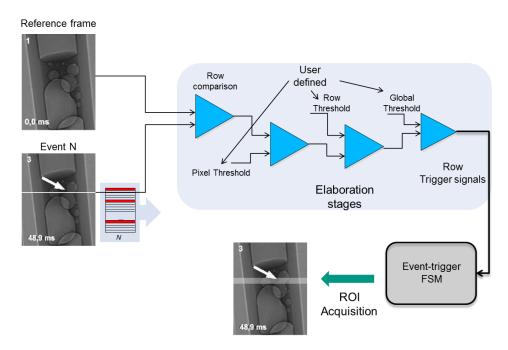

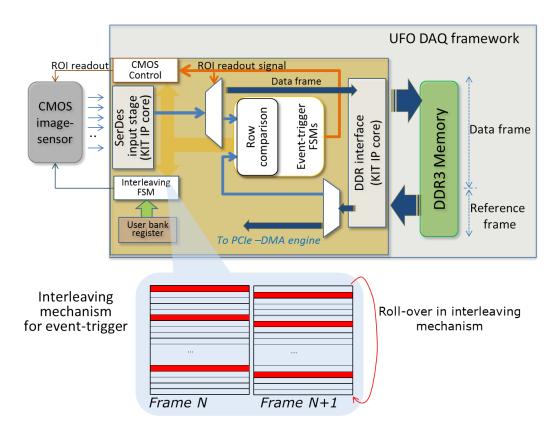

Three types of CMOS image sensors are provided. The first type of the image sensors, as previously mentioned, has a pixel size of 5.5  $\mu$ m x 5.5  $\mu$ m and a nominal frame rate of 330 frames per second (fps) at 2.2 MPixels [125]. It is provided as a monochromatic or color sensor with a maximum frame size of 4 MPixels and 10 to 12 bits resolution. The 4MP sensor is shown in Figure 3.16(a). The second type has a high frame rate of 2000 fps at 1 MPixels. Pixel size is 7  $\mu$ m x 7  $\mu$ m, with 10 bits per pixel. Finally, for applications that