# Cross-Layer Dependability for Runtime Reconfigurable Architectures

zur Erlangung des akademischen Grades eines

## Doktors der Ingenieurwissenschaften

von der Fakultät für Informatik des Karlsruher Instituts für Technologie (KIT)

genehmigte

Dissertation

von

Hongyan Zhang aus Shanghai/China

Tag der mündlichen Prüfung:11.Erster Referent:ProfZweiter Referent:Prof

11. Mai 2017 Prof. Dr.-Ing. Jörg Henkel Prof. Dr. rer. nat. habil. Hans-Joachim Wunderlich

Hongyan Zhang Steinenbergstr. 40 72764 Reutlingen

Hiermit erkläre ich an Eides statt, dass ich die von mir vorgelegte Arbeit selbstständig verfasst habe, dass ich die verwendeten Quellen, Internet-Quellen und Hilfsmittel vollständig angegeben habe und dass ich die Stellen der Arbeit — einschließlich Tabellen, Karten und Abbildungen — die anderen Werken oder dem Internet im Wortlaut oder dem Sinn nach entnommen sind, auf jeden Fall unter Angabe der Quelle als Entlehnung kenntlich gemacht habe.

Hongyan Zhang

## Contents

| A  | cknov                                         | wledgn                                                                                  | nents                          | v                                                                                                 |  |

|----|-----------------------------------------------|-----------------------------------------------------------------------------------------|--------------------------------|---------------------------------------------------------------------------------------------------|--|

| Li | st of                                         | Own P                                                                                   | ublications                    | vii                                                                                               |  |

| Li | List of Figures                               |                                                                                         |                                |                                                                                                   |  |

| Li | _ist of Tables                                |                                                                                         |                                |                                                                                                   |  |

| A  | Acronyms                                      |                                                                                         |                                |                                                                                                   |  |

| Κι | urzfa                                         | ssung                                                                                   |                                | xvii                                                                                              |  |

| AI | ostra                                         | ct.                                                                                     |                                | xxi                                                                                               |  |

| 1  | <b>Intro</b><br>1.1<br>1.2<br>1.3<br>1.4      | Depen<br>1.1.1<br>1.1.2<br>1.1.3<br>Thesis<br>DFG                                       | on and Motivation              | <b>1</b><br>2<br>3<br>4<br>6<br>7<br>8<br>9                                                       |  |

| 2  | Bac                                           |                                                                                         | nds                            | 11                                                                                                |  |

|    | <ul><li>2.1</li><li>2.2</li><li>2.3</li></ul> | 2.1.1<br>2.1.2<br>2.1.3<br>2.1.4<br>2.1.5<br>2.1.6<br>Fine-C<br>2.2.1<br>2.2.2<br>2.2.3 | Programmable Gate Arrays       | $ \begin{array}{c} 11\\ 11\\ 12\\ 14\\ 14\\ 15\\ 16\\ 17\\ 17\\ 18\\ 20\\ 21\\ 23\\ \end{array} $ |  |

|    |                                               | $2.3.2 \\ 2.3.3 \\ 2.3.4 \\ 2.3.5$                                                      | Biased Temperature Instability | 23<br>24<br>25<br>26<br>27                                                                        |  |

|   | 2.4  | Fault, Stress and Aging Models Used in the Thesis         | 28 |

|---|------|-----------------------------------------------------------|----|

|   |      | 2.4.1 Stress Model for Aging Effects                      | 28 |

|   |      | 2.4.2 Stress Properties                                   | 30 |

|   |      | 2.4.3 Aging Models                                        | 30 |

|   |      | 2.4.4 Fault Model for Soft Errors                         | 31 |

|   | 2.5  | Basic Dependability Techniques                            | 32 |

|   |      | 2.5.1 FPGA Test and Diagnosis                             | 33 |

|   |      | 2.5.2 Concurrent Error Detection in FPGAs                 | 36 |

|   |      | 2.5.3 Scrubbing of Configuration Memory                   | 39 |

|   | 2.6  | Related Work                                              | 40 |

|   |      | 2.6.1 FPGA-Based Reconfigurable Architectures             | 40 |

|   |      | 2.6.2 Online Test and Diagnosis of Reconfigurable Systems | 41 |

|   |      | 2.6.3 Fault Tolerance in Reconfigurable Systems           | 42 |

|   |      | 2.6.4 Aging Mitigation in Reconfigurable Systems          | 43 |

|   |      | 2.6.5 Handling Soft-Errors in the Configuration Memory    | 44 |

|   |      |                                                           |    |

| 3 | Sys  | stem Overview and Cross-Layer Dependability               | 47 |

|   | 3.1  | Application Model                                         | 47 |

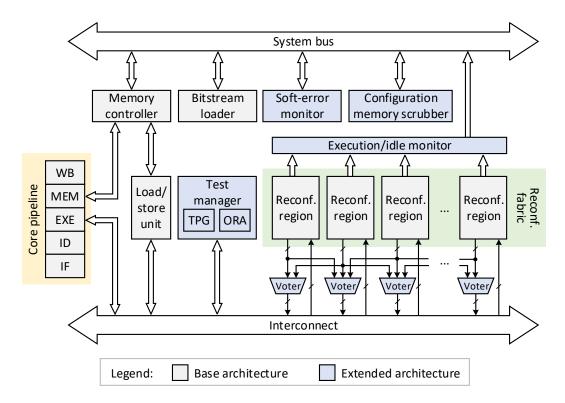

|   | 3.2  | Target Architecture                                       | 48 |

|   |      | 3.2.1 Base Architecture                                   | 48 |

|   |      | 3.2.2 Architectural Extension                             | 49 |

|   | 3.3  | Architectural Assumptions                                 | 51 |

|   | 3.4  | Cross-Layer Dependability                                 | 51 |

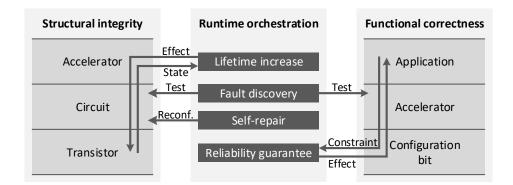

|   |      | 3.4.1 Lifetime Increase                                   | 53 |

|   |      | 3.4.2 Fault Discovery                                     | 54 |

|   |      | 3.4.3 Self-Repair                                         | 54 |

|   |      | 3.4.4 Reliability Guarantee                               | 55 |

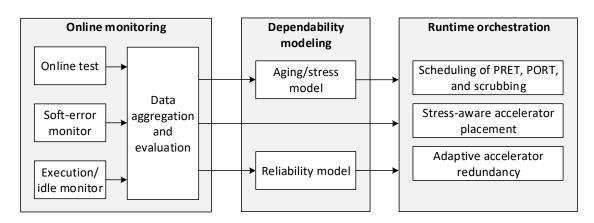

|   |      | 3.4.5 Runtime Orchestration                               | 55 |

|   | 3.5  | Evaluation Platform                                       | 56 |

| 4 | Fau  | It Discovery through Strategic Online Testing             | 59 |

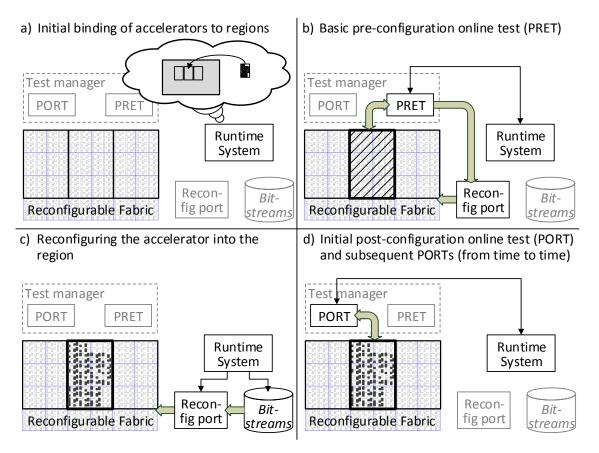

|   |      | Overview of Online Test Strategies                        | 60 |

|   | 4.2  | Integration of Online Tests                               | 61 |

|   | 4.3  | Scheduling of Online Tests                                | 63 |

|   |      | 4.3.1 PRET Scheduling                                     | 63 |

|   |      | 4.3.2 PORT Scheduling                                     | 63 |

|   | 4.4  | Experimental Evaluation                                   | 65 |

|   |      | 4.4.1 Fault Models of Tests                               | 65 |

|   |      | 4.4.2 Test Configurations for PRET                        | 66 |

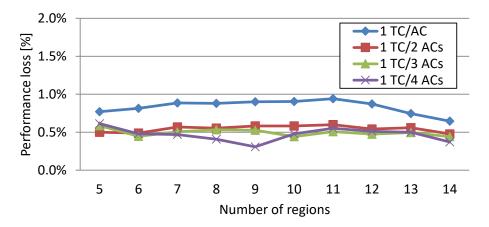

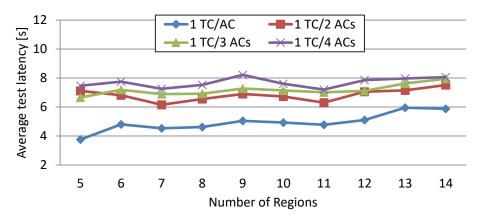

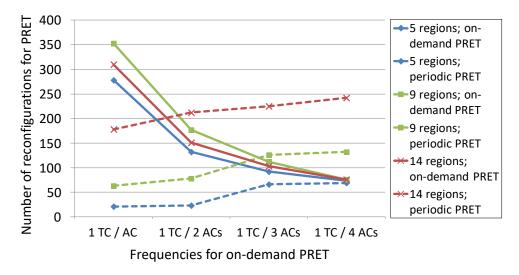

|   |      | 4.4.3 PRET Scheduling                                     | 67 |

|   |      | 4.4.4 PORT Scheduling                                     | 69 |

|   |      | 4.4.5 Combined PRET and PORT Scheduling                   | 70 |

| 5 | Self | f-Repair by Module Diversification                        | 73 |

| - | 5.1  | Overview of the Module Diversification Method             | 73 |

|   | 5.2  | Diversified Configurations                                | 74 |

|   | 5.4  | 5.2.1 Matrix Representation of Configurations             | 74 |

|   |      | 5.2.2 Properties of Diversified Configurations            | 74 |

|   |      |                                                           |    |

|   | 5.3  | Generation Algorithm                                                     | 5 |

|---|------|--------------------------------------------------------------------------|---|

|   | 5.4  |                                                                          | 7 |

|   | 5.5  |                                                                          | 8 |

|   | 5.6  | Implementation Flow                                                      | 8 |

|   | 5.7  | Experimental Evaluation                                                  | 9 |

|   |      |                                                                          | 9 |

|   |      | 5.7.2 Reliability Improvement                                            | 0 |

| 6 | Pro  | Ionging Lifetime via Stress Balancing                                    | 3 |

| • | 6.1  | Overview of the Stress-Aware Placement Method                            |   |

|   | 6.2  | Representation of Stress                                                 |   |

|   |      | •                                                                        | 5 |

|   |      | 6.2.2 Stress Accumulation                                                |   |

|   |      |                                                                          | 6 |

|   | 6.3  | Runtime Accelerator Placement                                            |   |

|   |      | 6.3.1 Placement Profit                                                   |   |

|   |      |                                                                          | 9 |

|   |      | 0                                                                        | 0 |

|   | 6.4  |                                                                          | 0 |

|   |      |                                                                          | 1 |

|   |      | 6.4.2 Stress Distribution Results                                        |   |

|   | 6.5  | Extended Runtime Accelerator Placement with Module Diversification 9     | 3 |

|   | 6.6  |                                                                          | 4 |

|   |      | -                                                                        | 4 |

|   |      |                                                                          | 6 |

|   |      | -                                                                        | 6 |

| 7 | Reli | iability Guarantee with Adaptive Modular Redundancy                      | 9 |

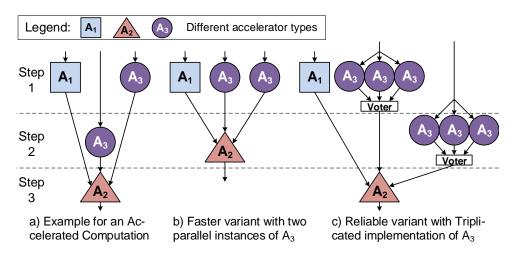

|   | 7.1  | Overview of Adaptive Modular Redundancy 10                               | 0 |

|   | 7.2  | Reliability of Accelerated Functions                                     |   |

|   | 7.3  | Reliability Guarantee of Accelerated Functions                           | 3 |

|   |      | 7.3.1 Maximum Resident Time                                              | 4 |

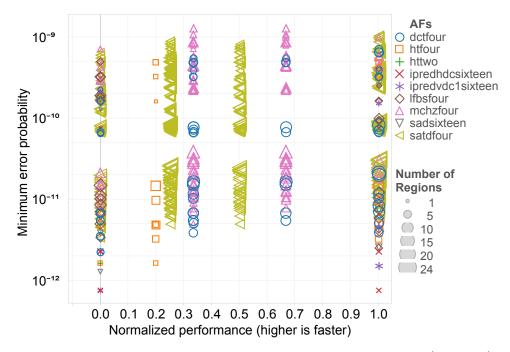

|   |      | 7.3.2 Acceleration Variants Selection                                    | 5 |

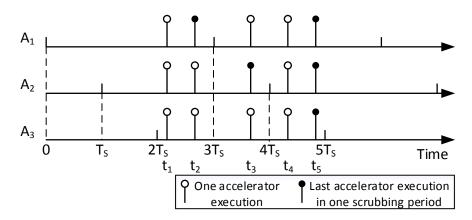

|   |      | 7.3.3 Non-uniform Accelerator Scrubbing                                  | 7 |

|   | 7.4  | Reliability Guarantee of Applications                                    | 8 |

|   |      | 7.4.1 Effective Critical Bits of Accelerators                            | 9 |

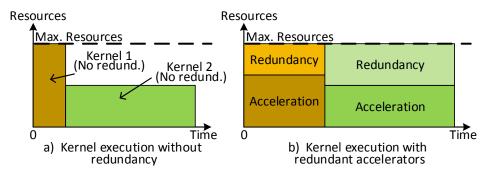

|   |      | 7.4.2 Reliability of Accelerated Kernels                                 | 9 |

|   |      | 7.4.3 Effective Critical Bits of Accelerated Kernels and Applications 11 | 1 |

|   |      | 7.4.4 Budgeting of Effective Critical Bits                               | 2 |

|   | 7.5  | Experimental Evaluation                                                  | 4 |

|   |      | 7.5.1 Performance Improvement                                            | 5 |

|   |      | 7.5.2 Runtime Overhead                                                   | 6 |

| 8 | Ove  | erall Evaluation and Comparison                                          | 7 |

|   | 8.1  | Structural Integrity                                                     |   |

|   |      | 8.1.1 Accelerator Diversification                                        |   |

|   |      | 8.1.2 Aging Resilience and Fault Tolerance                               |   |

|   | 8.2  | Functional Correctness                                                   |   |

| 9  | Conclusion and Future Work                                    | 127 |  |

|----|---------------------------------------------------------------|-----|--|

| A  | Proof of the Minimal Set Generation in Module Diversification | 131 |  |

| В  | Terrestrial Soft Error Rates in a Virtex-5 FPGA               | 137 |  |

| Bi | Bibliography                                                  |     |  |

### Acknowledgments

First and foremost, I would like to express my sincere gratitude to my Ph.D. advisor Prof. Dr.-Ing. Jörg Henkel who not only guided and supported me in the research work but also has had a significant impact on my personal development. By asking the right questions, casting insightful doubts and encouraging me to formulate clear and precise answers, he showed me the proper way of thinking for scientific problems, which was absolutely essential to the accomplishment of this work and any other work in my future carrier path.

My sincere thanks also goes to Prof. Dr. rer. nat. habil. Hans-Joachim Wunderlich from the University of Stuttgart for agreeing to be my second reviewer and for his support of the OTERA project through discussion of proposals and reviewing our joint papers.

Next, I would like to thank Dr.-Ing. Lars Bauer who provided precious support and lead at key times. He helped me in thinking through some of the difficult ideas. This work was greatly influenced by the intriguing discussions with him and his suggestions in writing styles. The evaluation platform used in this work is based on his great achievements during his Ph.D.

My special thanks go to the project partners from the University of Stuttgart: Dr. rer. nat. Michael Kochte for his fruitful discussions and guiding suggestions during the writing of OTERA papers, Eric Schneider for his implementation of stress models for lookup tables, Dr. rer. nat. Claus Braun and Michael Imhof for their excellent collaboration in our first OTERA papers. Their influence is of great importance to the success of this work and it has always been a great pleasure to work with them.

I would also like to thank my colleagues at CES who provided me a comfortable and trustful work environment: Artjom Grudnitsky for the collaboration on the demonstrator and help on the the setup of the RotMan simulator; Dr.-Ing. Hussam Amrouch and Victor van Santen for their support on the aging models; Martin Buchty for his technical support and help on the lab supervision; Usman Karim and Anuj Pathania for their fun talks in the office; Semeen Rehman and Florian Kriebel for their company during the trip to SPP meetings; Marvin Damschen, Thomas Ebi, Fazal Hameed, Chih-Ming Hsieh, Anton Ivanov, Heba Khdr, Sebastian Kobbe, Farzad Samie, Sammer Srouji, Manyi Wang and Volker Wenzel for their support, friendship and advice during my stay at CES.

This work was supported in parts by the German Research Foundation (DFG) as part of the priority program "Dependable Embedded Systems" (SPP 1500), where I was given the opportunity to examine my work in a wider scope.

Finally, I would like to express my deepest gratitude to my parents for their constant support, encouragement and understanding, and to my wife Xin Liu for sustaining me through challenging times and enriching my life with light and meaning. I could have never have done this work without you.

## **List of Own Publications**

#### **Publications Providing Major Contributions to This Thesis**

- [ZBK<sup>+</sup>17] H. Zhang, L. Bauer, M. A. Kochte, E. Schneider, H. J. Wunderlich, and J. Henkel, "Aging Resilience and Fault Tolerance in Runtime Reconfigurable Architectures," *IEEE Transactions on Computers, Special Section on Inno*vation in Reconfigurable Computing Fabrics: from Devices to Architectures, 2017 (to appear).

- [ZBH16] H. Zhang, L. Bauer, and J. Henkel, "Resource budgeting for reliability in reconfigurable architectures," in *Proc. 53rd Annual Design Automation Conference (DAC)*, 2016, pp. 111:1–111:6.

- [ZKS<sup>+</sup>15] H. Zhang, M. A. Kochte, E. Schneider, L. Bauer, H.-J. Wunderlich, and J. Henkel, "STRAP: Stress-aware placement for aging mitigation in runtime reconfigurable architectures," in *Proc. IEEE/ACM International Conference on Computer-Aided Design (ICCAD)*, 2015, pp. 38–45.

- [ZKI<sup>+</sup>14] H. Zhang, M. A. Kochte, M. E. Imhof, L. Bauer, H.-J. Wunderlich, and J. Henkel, "GUARD: GUAranteed reliability in dynamically reconfigurable systems," in *Proc.* 51st Annual Design Automation Conference (DAC), 2014, pp. 32:1–32:6.

- [ZBK<sup>+</sup>13] H. Zhang, L. Bauer, M. A. Kochte, E. Schneider, C. Braun, M. E. Imhof, H.-J. Wunderlich, and J. Henkel, "Module diversification: Fault tolerance and aging mitigation for runtime reconfigurable architectures," in *Proc. IEEE International Test Conference (ITC)*, 2013, pp. 1–10.

- [BBI<sup>+</sup>13] L. Bauer, C. Braun, M. E. Imhof, M. A. Kochte, E. Schneider, H. Zhang, J. Henkel, and H.-J. Wunderlich, "Test Strategies for Reliable Runtime Reconfigurable Architectures," *IEEE Transactions on Computers*, vol. 62, no. 8, pp. 1494–1507, 2013.

### **Publications Providing Minor Contributions to This Thesis**

- [BHH<sup>+</sup>15] L. Bauer, J. Henkel, A. Herkersdorf, M. A. Kochte, J. M. Kühn, W. Rosenstiel, T. Schweizer, S. Wallentowitz, V. Wenzel, T. Wild, H.-J. Wunderlich, and H. Zhang, "Adaptive multi-layer techniques for increased system dependability," *it - Information Technology*, vol. 57, no. 3, 2015.

- [HBGZ14] J. Henkel, L. Bauer, A. Grudnitsky, and H. Zhang, "Adaptive embedded computing with i-Core," ACM SIGBED Review, vol. 11, no. 3, pp. 20–21, 2014.

- [HBZ<sup>+</sup>14] J. Henkel, L. Bauer, H. Zhang, S. Rehman, and M. Shafique, "Multi-layer dependability: From microarchitecture to application level," in *Proc. 51st Annual Design Automation Conference (DAC)*, 2014, pp. 1–6.

- [ABB<sup>+</sup>12] M. S. Abdelfattah, L. Bauer, C. Braun, M. E. Imhof, M. A. Kochte, H. Zhang, J. Henkel, and H.-J. Wunderlich, "Transparent structural online test for reconfigurable systems," in *Proc. IEEE 18th International On-Line Testing Symposium (IOLTS)*, 2012, pp. 37–42.

- [BBI<sup>+</sup>12] L. Bauer, C. Braun, M. E. Imhof, M. A. Kochte, H. Zhang, H.-J. Wunderlich, and J. Henkel, "OTERA: Online test strategies for reliable reconfigurable architectures — Invited paper for the AHS-2012 special session "Dependability by reconfigurable hardware"," in *Proc. NASA/ESA Conference on Adaptive Hardware and Systems (AHS)*, 2012, pp. 38–45.

## List of Figures

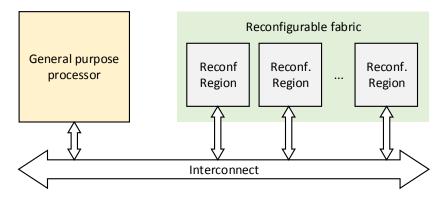

| 1.1        | Illustrative example of a reconfigurable architecture                                                                                                          |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

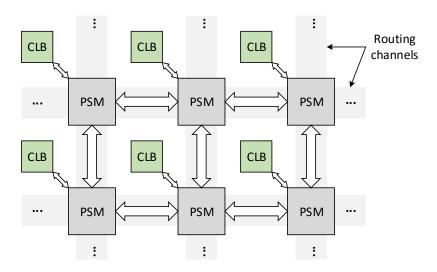

| 2.1        | Island-style FPGA architecture                                                                                                                                 |

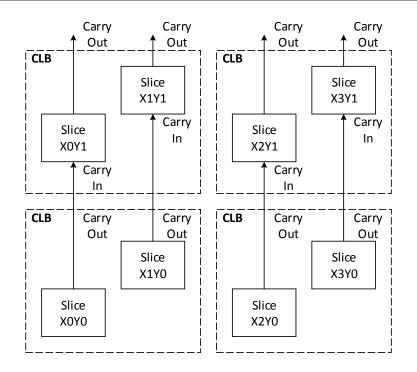

| 2.2        | Xilinx-style CLB structure [Xil12d] 13                                                                                                                         |

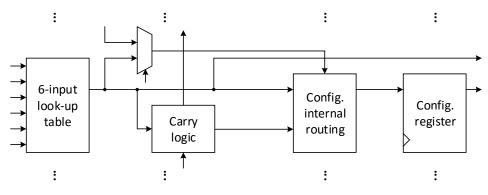

| 2.3        | Reconfigurable resources in a slice                                                                                                                            |

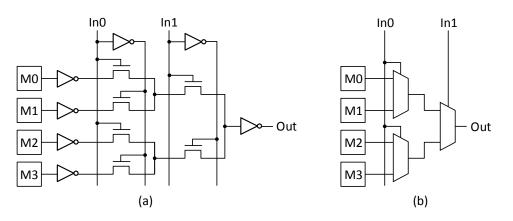

| 2.4        | Internal structure of a 2-input LUT                                                                                                                            |

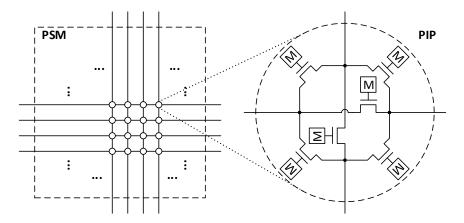

| 2.5        | Internal structure of a $PSM$ and a $PIP$ [HCJ+90]                                                                                                             |

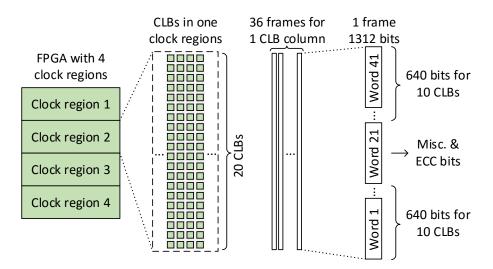

| 2.6        | Configuration frames in a Xilinx Virtex-5 FPGA                                                                                                                 |

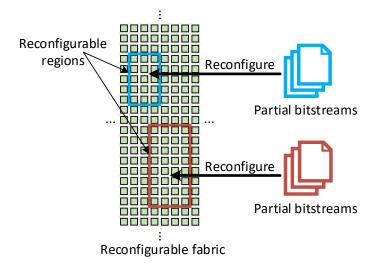

| 2.7        | Partial reconfiguration with partial bitstreams                                                                                                                |

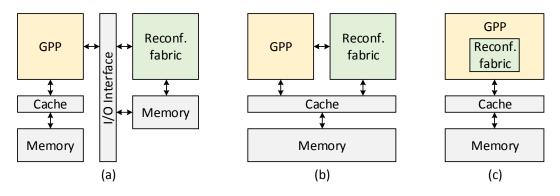

| 2.8        | Three degrees of coupling between FPGA and GPP: (a) loosely cou-                                                                                               |

|            | pled, (b) co-processor and (c) tightly coupled                                                                                                                 |

| 2.9        | Basic structure of a NMOS transistor                                                                                                                           |

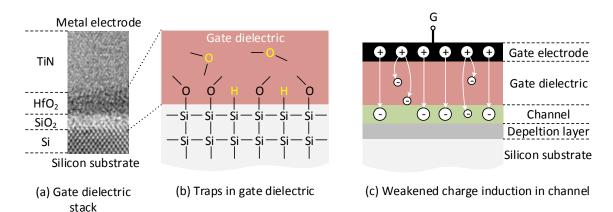

| 2.10       | Physical mechanism of BTI in NMOS                                                                                                                              |

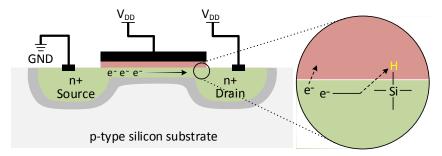

|            | Physical mechanism of HCI in NMOS                                                                                                                              |

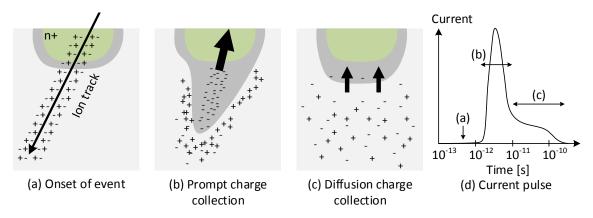

|            | Physical mechanism of SEU in MOSFET [Bau05]                                                                                                                    |

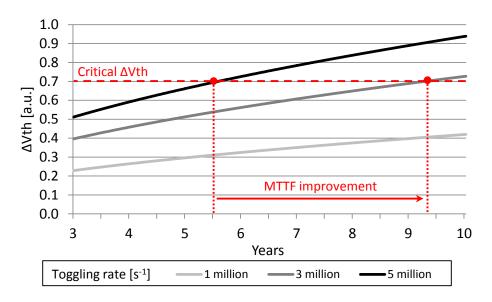

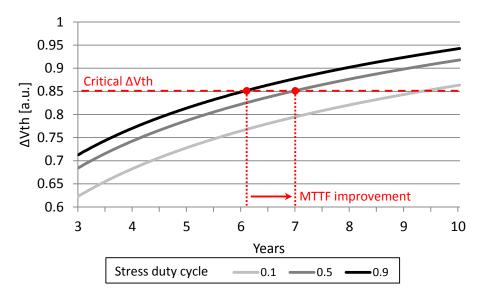

|            | Threshold voltage increases over time due to HCI under different                                                                                               |

|            | toggling rates                                                                                                                                                 |

| 2.14       | Threshold voltage increases over time due to BTI under different                                                                                               |

|            | stress duty cycles                                                                                                                                             |

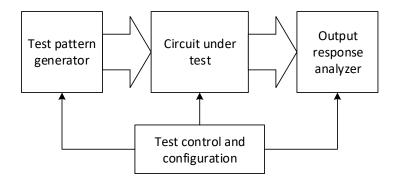

| 2.15       | A general test structure for digital circuits                                                                                                                  |

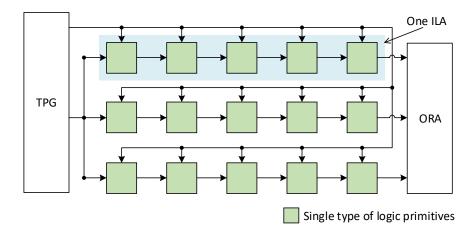

|            | Array-based test structure for FPGAs                                                                                                                           |

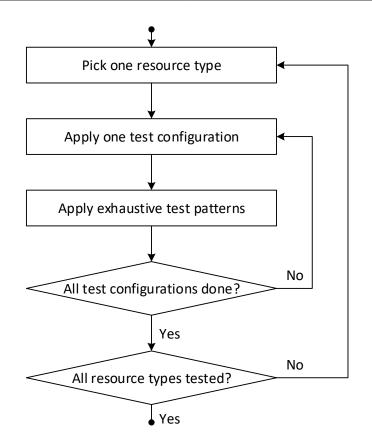

|            | Array-based test process for FPGAs                                                                                                                             |

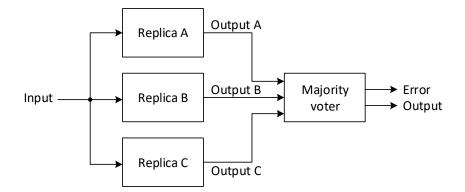

|            | Triple modular redundancy                                                                                                                                      |

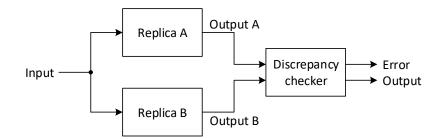

|            | Duplication with comparison                                                                                                                                    |

|            |                                                                                                                                                                |

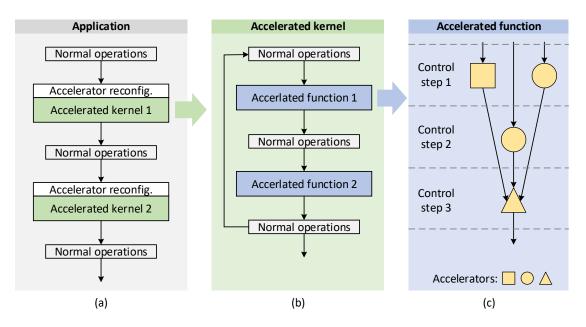

| 3.1        | The application model used in this thesis                                                                                                                      |

| 3.2        | Target reconfigurable architecture48                                                                                                                           |

| 3.3        | System layers and their interaction with the dependability approaches                                                                                          |

|            | proposed in this thesis $\ldots \ldots \ldots$ |

| 3.4        | Runtime orchestration of dependability techniques                                                                                                              |

| 4.1        | Test flow with PRET and PORT                                                                                                                                   |

| 4.1<br>4.2 |                                                                                                                                                                |

| 4.2<br>4.3 | 0 0                                                                                                                                                            |

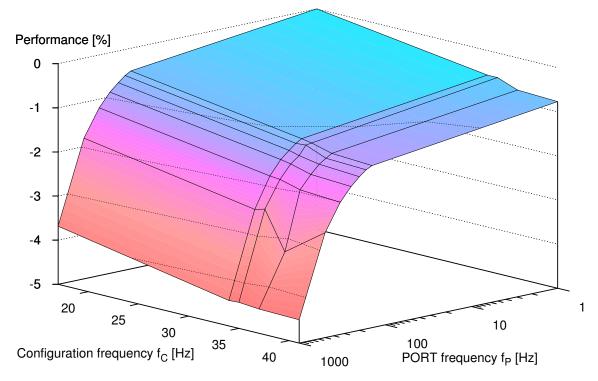

| 4.0        | Performance loss of the video encoder application under different on-                                                                                          |

| 4 4        | demand PRET frequencies and number of regions                                                                                                                  |

| 4.4        | Average test latency under different PRET frequencies and number                                                                                               |

| 4 5        | of regions                                                                                                                                                     |

| 4.5        | Comparison of the number of on-demand and periodic tests for dif-                                                                                              |

| 1.0        | ferent on-demand PRET frequencies and number of regions 68                                                                                                     |

| 4.6        | Performance loss when both PRET and PORT are applied for a re-                                                                                                 |

|            | $configurable system with 5 regions \dots \dots$         |

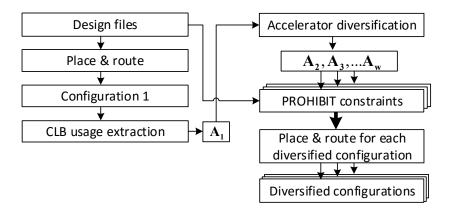

| 5.1        | Generation of diversified configurations using the module diversifica-<br>tion method                                                                                                                                                                                                                                  | 78       |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

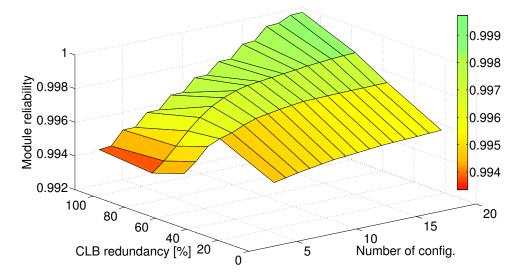

| 5.2        | Module reliability of apex4 for different ratios of CLB redundancy<br>and number of configurations with CLB reliability 0.999                                                                                                                                                                                          | 81       |

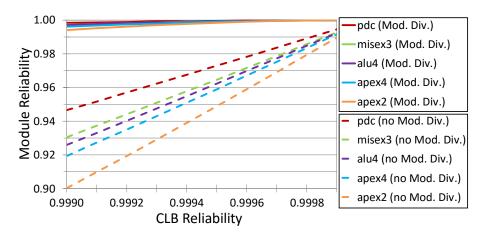

| 5.3        | Module reliability <i>with</i> and <i>without</i> module diversification for different CLB reliabilities. Reliabilities of des_perf and aes_core are not shown in the figure for clarity, but discussed in the text.                                                                                                   | 81       |

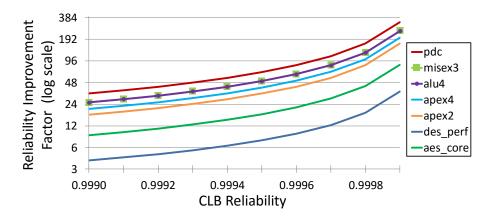

| 5.4        | Reliability improvement factor for the modules when module diversi-<br>fication is applied                                                                                                                                                                                                                             | 82       |

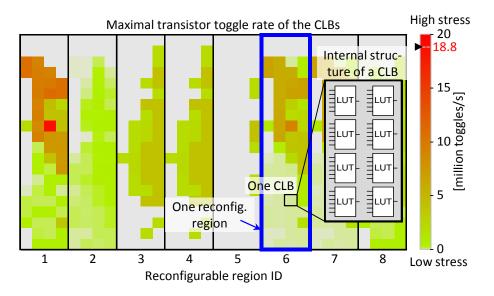

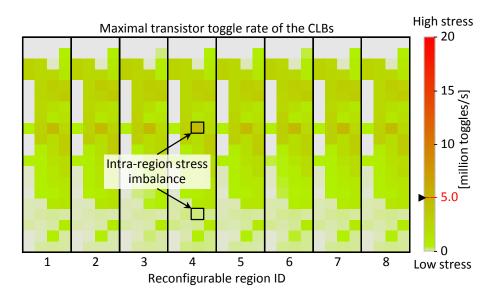

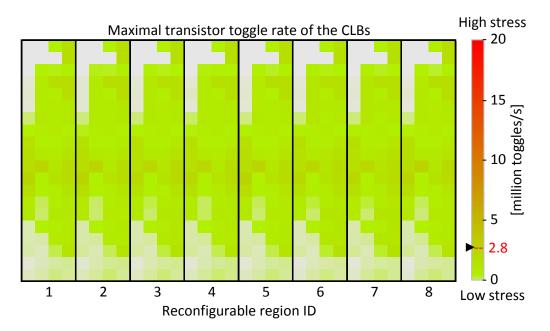

| 6.1        | Transistor stress distribution in a reconfigurable fabric with 8 regions; each region consists of $4 \times 20$ CLBs with 8 LUTs each (same setup as for evaluation); the color of a CLB corresponds to the highest toggle rate of any of its transistors; the symbol $\blacktriangleright$ on the right scale denotes |          |

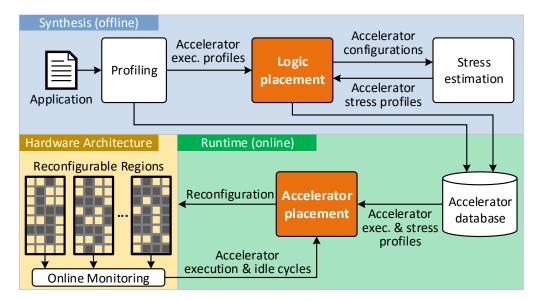

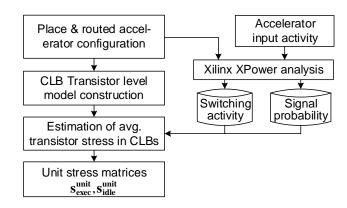

| 6.2        | the maximum stress over all regions                                                                                                                                                                                                                                                                                    | 84<br>85 |

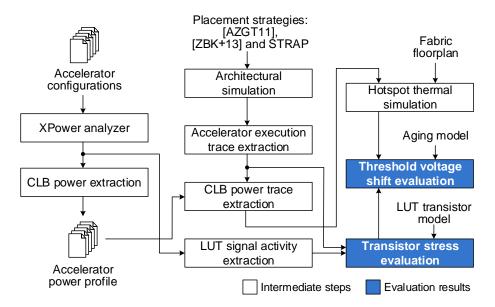

| 0.2<br>6.3 | Overview of the stress-aware placement method                                                                                                                                                                                                                                                                          | 87       |

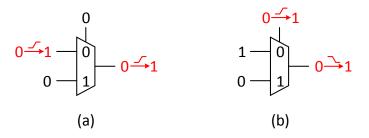

| 6.4        | Toggle propagation (a) and generation (b) in multiplexers                                                                                                                                                                                                                                                              | 87       |

| 6.5        | Transistor stress distribution using stress-aware runtime accelerator                                                                                                                                                                                                                                                  | 01       |

|            | placement                                                                                                                                                                                                                                                                                                              | 91       |

| 6.6        | Transistor stress distribution using both stress-aware runtime accelerator placement and synthesis time stress diversification                                                                                                                                                                                         | 93       |

| 6.7        | Experimental flow to evaluate the transistor stress and threshold volt-<br>age shift                                                                                                                                                                                                                                   | 95       |

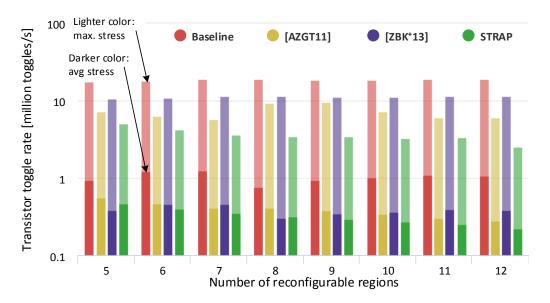

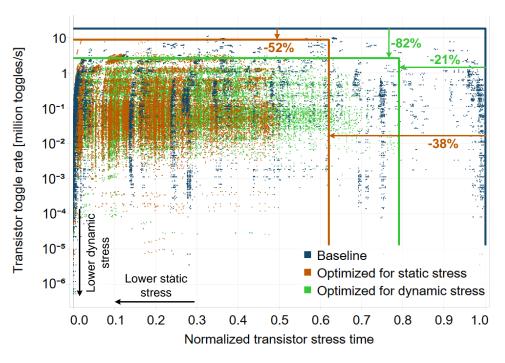

| 6.8        | Comparison to related work for dynamic stress in systems with dif-<br>ferent number of reconfigurable regions                                                                                                                                                                                                          | 97       |

| 6.9        | Comparison to related work for static stress in systems with different<br>number of reconfigurable regions                                                                                                                                                                                                             | 97       |

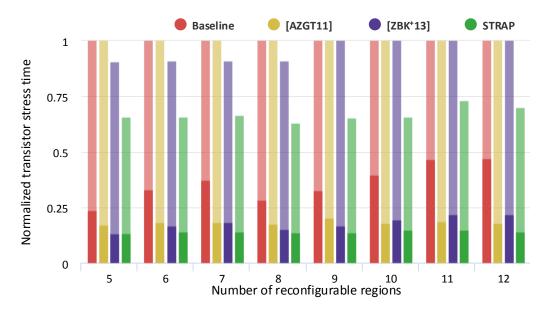

| 6.10       | Transistor stress for different STRAP optimization goals                                                                                                                                                                                                                                                               | 98       |

| 7.1        | Different hardware implementation variants of an Accelerated Function (AF)                                                                                                                                                                                                                                             | 100      |

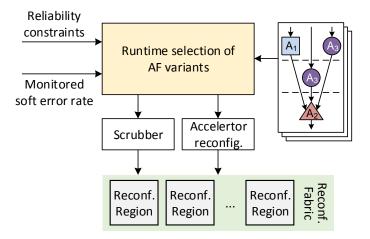

| 7.2        | Overview of proposed adaptive modular redundancy                                                                                                                                                                                                                                                                       | 101      |

| 7.3        | Variants selection space for an error rate of 10 errors $Mb^{-1}month^{-1}$ .                                                                                                                                                                                                                                          | 105      |

| 7.4        | Execution of kernels with different degrees of redundancy                                                                                                                                                                                                                                                              | 108      |

| 7.5        | Illustrative execution series of an accelerated function                                                                                                                                                                                                                                                               | 110      |

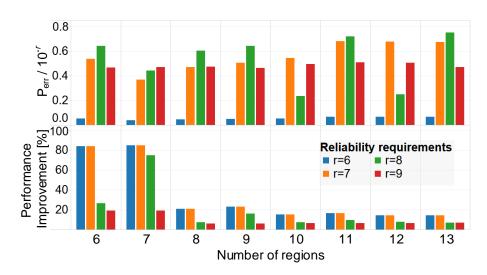

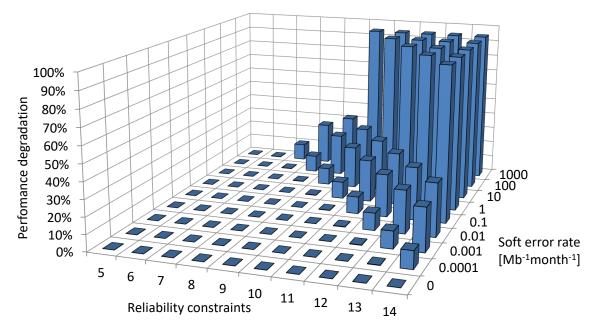

| 7.6        | Ratios of error probability and performance improvement under dif-<br>ferent numbers of regions and reliability requirements                                                                                                                                                                                           | 115      |

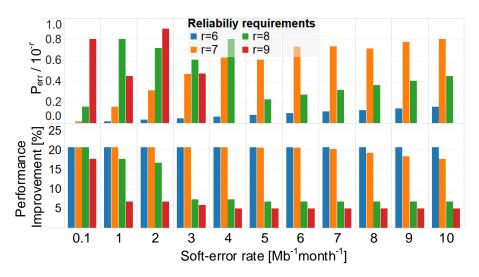

| 7.7        | Ratios of error probability and performance improvement under dif-<br>ferent soft-error rates and reliability requirements                                                                                                                                                                                             | 116      |

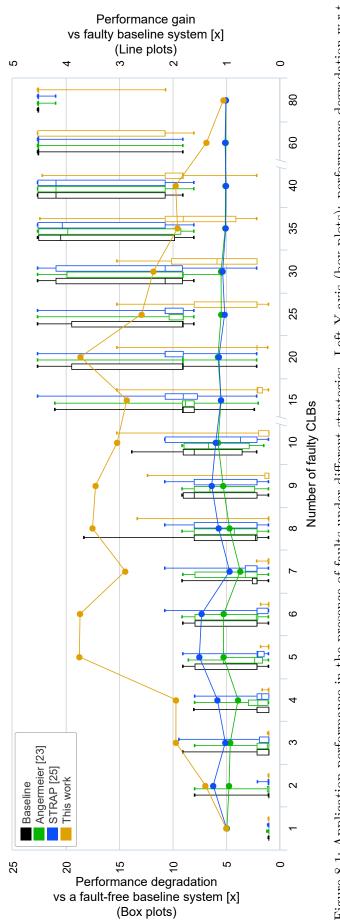

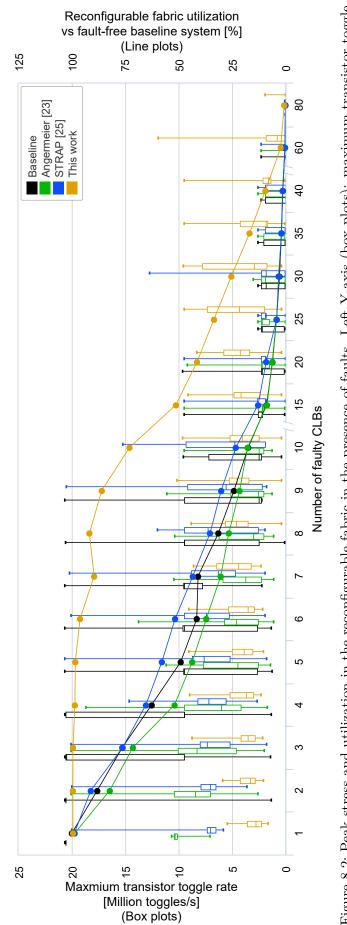

| 8.1        | Application performance in the presence of faults under different strategies. Left Y-axis (box plots): performance degradation w.r.t. a fault-free baseline system. Right Y-axis (line plots): performance gain w.r.t. to the faulty baseline system                                                                   | 121      |

| 8.2 | Peak stress and utilization in the reconfigurable fabric in the presence |     |

|-----|--------------------------------------------------------------------------|-----|

|     | of faults. Left Y-axis (box plots): maximum transistor toggle rate.      |     |

|     | Right Y-axis (line plots): utilization of the reconfigurable fabric for  |     |

|     | acceleration w.r.t. a fault-free baseline system                         | 123 |

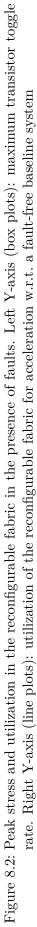

| 8.3 | Performance under varying soft error rate                                | 125 |

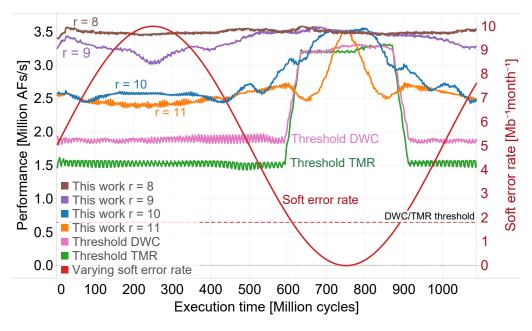

| 8.4 | Average AF error probability for different fault tolerance methods       |     |

|     | under varying soft error rate                                            | 125 |

| 8.5 | Performance degradation over a wide range of soft error rates and        |     |

|     | reliability constraints                                                  | 126 |

| D 1 |                                                                          |     |

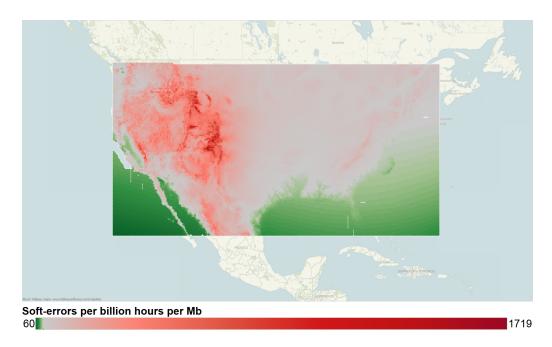

| B.1 | This figure shows how the soft error rate varys depending on the         |     |

|     | altitude. The neutron flux is lower at low altitude regions due to       |     |

|     | atmospheric shielding. It is almost 30 times higher at mountain peaks    | 137 |

| Бυ  | in the US than it is at sea level                                        | 197 |

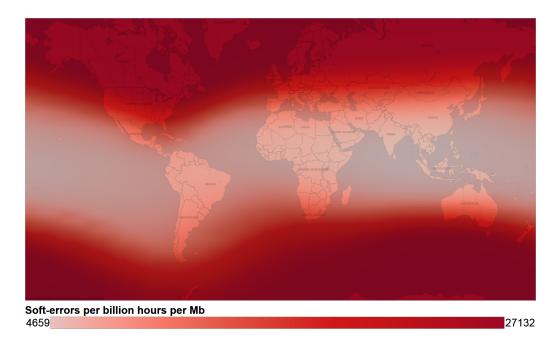

| B.2 | The neutron flux also varys in the geomagnetic field. This figure        |     |

|     | shows the resulted variation of soft error rate around the globe at      |     |

|     | 10 km altitude, where commercial flights typically cruise. In the equa-  |     |

|     | tor regions, the soft error rate is roughly 6 times lower than it is in  |     |

|     | other regions.                                                           | 138 |

## List of Tables

| 3.1        | Short description of accelerators implemented for H.264                                                            | 57       |

|------------|--------------------------------------------------------------------------------------------------------------------|----------|

| 4.1<br>4.2 | Test configurations for CLBs and interconnects: Overhead, size, fre-<br>quency and length                          | 66<br>69 |

| 5.1        | Configurations for different region sizes and maximal frequency of original (Orig.) and diversified (Div.) modules | 80       |

| 6.1<br>6.2 | Change in maximum frequency of accelerators                                                                        | 96<br>98 |

| 8.1        | Properties of reconfigurable accelerators and their change in maxi-<br>mum frequency of diversified configurations | 118      |

| 8.2        | Compared strategies in the experiments                                                                             | 118      |

| 8.3        | Reduction of maximum transistor toggle rate w.r.t. the baseline sys-                                               |          |

|            | tem $[\%]$                                                                                                         | 119      |

| 8.4        | MTTF improvement w.r.t. the baseline system $[\times]$ (e.g. $2 \times$ improve-                                   |          |

|            | ment means the MTTF is doubled) $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                 | 120      |

| 8.5        | Performance and error probability results                                                                          | 126      |

## Acronyms

| AC                                                         | Accelerator Configuration.                                        |

|------------------------------------------------------------|-------------------------------------------------------------------|

| AF                                                         | Accelerated Function.                                             |

| ASIP                                                       | Application-Specific Instruction set Processor.                   |

| BIST                                                       | Built-In-Self-Test.                                               |

| BTI                                                        | Bias Temperature Instability.                                     |

| CED                                                        | Concurrent Error Detection.                                       |

| CGRA                                                       | Coarse-Grained Reconfigurable Architectures/Arrays.               |

| CLB                                                        | Configurable Logic Block.                                         |

| CPU                                                        | Central Processing Unit.                                          |

| CUT                                                        | Circuit Under Test.                                               |

| DPPM                                                       | Defective Parts Per Million.                                      |

| DSP                                                        | Digital Signal Processor.                                         |

| DWC                                                        | Duplication with Comparison.                                      |

| $\begin{array}{c} \mathbf{ECC} \\ \mathbf{EM} \end{array}$ | Error Correcting Code.<br>Electro-Migration.                      |

| FPGA                                                       | Field-Programmable Gate Array.                                    |

| FSM                                                        | Finite State Machine.                                             |

| $\mathbf{GPU}$                                             | Graphic Processing Unit.                                          |

| HCI                                                        | Hot Carrier Injection.                                            |

| ICAP                                                       | Internal Configuration Access Port.                               |

| ILA                                                        | Iterative Logic Array.                                            |

| $\mathbf{LUT}$                                             | Look-Up Table.                                                    |

| MBE                                                        | Multi-Bit Error.                                                  |

| MOSFET                                                     | Metal-Oxide-Semiconductor Field-Effect Transistor.                |

| MTTF                                                       | Mean Time to Failure.                                             |

| NMOS                                                       | n-type MOSFET.                                                    |

| ORA                                                        | Output Response Analyzer.                                         |

| OTERA                                                      | Online Test Strategies for Reliable Reconfigurable Architectures. |

| PIP                                                        | Programmable Interconnection Point.                               |

| PMOS                                                       | p-type MOSFET.                                                    |

| PORT<br>PRET<br>PSM | Post-configuration Test.<br>Pre-configuration Test.<br>Programmable Switching Matrix. |

|---------------------|---------------------------------------------------------------------------------------|

| RAM                 | Random Access Memory.                                                                 |

| RDP                 | Random Dopant Fluctuation.                                                            |

| RIF                 | Reliability Improvement Factor.                                                       |

| SBE                 | Single-Bit Error.                                                                     |

| SER                 | Soft Error Rate.                                                                      |

| SEU                 | Single Event Upset.                                                                   |

| SoC                 | System-on-Chip.                                                                       |

| STRAP               | STRess-Aware Placement.                                                               |

| TC                  | Test Configuration.                                                                   |

| TDDB                | Time-Dependent Dielectric Breakdown.                                                  |

| $\mathbf{TMR}$      | Triple Modular Redundancy.                                                            |

| TPG                 | Test Pattern Generator.                                                               |

## Kurzfassung

Rekonfigurierbare Rechensysteme kombinieren die Effizienz der Hardware mit der Flexibilität der Software und werden konkurrenzfähig gegen herkömmliche Rechnerarchitekturen wie Allzweckprozessoren (CPUs) und Grafikprozessoren (GPUs). Sie bieten eine Hardwareorganisation, die noch nach der Herstellung durch Benutzer für verschiedene Anwendungen dynamisch angepasst werden kann. Rekonfigurierbare Architekturen, die auf Feld-Programmierbaren Gatter-Anordnungen (FPGAs) basieren, treten in den letzten Jahren dank stets wachsender Kapazität der FPGAs und einem vereinfachten FPGA-Entwurfsprozesses als eine vielversprechende Technologie für rekonfigurierbare Rechensysteme auf.

Eine typische rekonfigurierbare Architektur besteht aus einem Allzweckprozessor, einer rekonfigurierbaren Struktur und einer Kommunikationsinfrastruktur, die beide miteinander verbindet. Die rekonfigurierbare Struktur kann sich auf einem oder mehreren FPGAs befinden. Hardware-Beschleuniger, die rechenintensive Funktionen realisieren, können zur Laufzeit in der rekonfigurierbaren Struktur instanziiert werden. Die Arbeitslast auf dem Prozessor kann dann auf den FPGA ausgelagert werden, der das Rechnen in Hardware mit hoher Leistung und Energieeffizienz durchführt. Die stetige Weiterentwicklung in der Halbleiterindustrie ermöglicht die nachhaltige Verkleinerung der Transistorgröße in den Nanobereich, was zu höherer Transistordichte, schnellerer Schaltgeschwindigkeit und niedrigerem Energieverbrauch führt. Um diese Vorteile der Skalierung der Transistorgröße auszunutzen, werden moderne FPGAs in neusten Technologien hergestellt. Zum Beispiel wird der jüngste MPSoC von Xilinx mit vier ARM-Kernen und einer rekonfigurierbaren Struktur auf einem einzigen Chip mit 16 nm FinFET Technologie hergestellt.

Allerdings kommt die Skalierung mit Herausforderungen, die den zuverlässigen Betrieb von FPGAs bedrohen. Fehler können beim Herstellungstest unbemerkt bleiben und in ausgelieferten Geräten latent vorhanden sein, da die wachsende Schaltungskomplexität und neue Defektmechanismen die Wirksamkeit der Tests begrenzen. Während des Betriebs der Schaltungen verschlechtern verschiedene mikroskopische Phänomene die physikalischen und elektrischen Eigenschaften der Materialien, aus denen die Transistoren bestehen. Solche Effekte werden durch weitere Skalierung verschlimmert. Die Transistoren funktionieren nicht für ewig sondern altern. Die Schwellwertspannung der Transistoren verschiebt sich mit der Zeit, was die Stromstärke durch die Transistoren verringert und schließlich zu einem kompletten Ausfall führen kann. Darüber hinaus wechselwirkt die Hintergrundstrahlung aus der Umgebung mit den Materialien des Chips. Die Konfigurationsbits in einem FPGA können dadurch verändert werden, was im Wesentlichen die Funktionsdefinition der auf dem FPGA implementierten Schaltungen modifiziert. Die Rechenergebnisse vom FPGA sind dann fehlerhaft. In einem zuverlässigen System, insbesondere bei sicherheits- und missionskritischen Anwendungen, sollen Fehler in kürzester Zeit erkannt, lokalisiert und vermieden werden, um ihre Einflüsse auf das Gesamtsystem zu minimieren. Außerdem sollen Gegenmaßnahmen proaktiv eingeleitet werden, um das Eintreten von Fehler überhaupt zu vermeiden. Folgende Schlüsseltechniken sind im Rahmen dieser Arbeit entwickelt worden, um eine hochzuverlässige rekonfigurierbare Architektur zu verwirklichen:

- Für das Erkennen von Fehler in der rekonfigurierbaren Struktur werden bedarfsgesteuerte und periodische Tests während des funktionalen Systembetriebs eingesetzt. Vor der Instanziierung von Beschleunigern werden die grundlegenden rekonfigurierbaren Ressourcen gründlich durch strukturelle Tests geprüft. Nach der Konfiguration der Beschleuniger wird ihre Funktionalität periodisch durch funktionelle Tests geprüft. Die Kombination von beiden Teststrategien erzielt eine hohe Fehlerbedeckung und niedrige Testlatenz bei minimalem Leistungsaufwand. Experimentelle Ergebnisse zeigen, dass die rekonfigurierbare Struktur alle 4 Sekunde bei weniger als 4,4% Leistungsaufwand gründlich getestet werden kann.

- Wenn Teile der rekonfigurierbaren Struktur als fehlerhaft erkannt werden, können die fehlerhaften Ressourcen für die Berechnung vermieden werden ohne die Systemleistung zu verändern. Dies wird durch eine neuartige Entwurfsmethode namens Modul-Diversifikation erreicht. Für jeden Beschleuniger oder Modul wird eine Menge an Konfigurationen generiert, die bezüglich der Ressourcenbenutzung diversifiziert sind. Alternative Konfigurationen, die die fehlerhaften Ressourcen nicht benötigen, können benutzt werden, um den normalen Systembetrieb sogar in Gegenwart von Fehlern aufrechtzuhalten. Zuverlässigkeitsverbesserungsfaktoren zwischen 19 und 330 wurden in den Experimenten erreicht.

- Die Verwendung der rekonfigurierbaren Struktur erzeugt elektrischen Stress für die einzelnen Transistoren, der zur Alterung der Transistoren führt. In dieser Arbeit wurde eine neuartige Technik zur Stressesbalancierung entwickelt. Sie ist in der Lage, den durch Arbeitslast erzeugten Stress gleichmäßig auf alle rekonfigurierbaren Ressourcen zu verteilen, so dass der Stress auf einzelne Transistoren minimiert wird. Die Kombination aus Beschleuniger-Platzierung zur Laufzeit und Logik-Platzierung zur Synthese-Zeit bringt eine gleichmäßige Stressverteilung, was die Lebensdauer des Systems bei geringfügigen Laufzeitkosten erheblich verlängert. Im Vergleich zum Stand-der-Technik werden die dynamischen und statischen Stresse jeweils um bis zu 64% und 35% reduziert, was einer Verländerung der Lebensdauer jeweils um bis zu 177% und 15% entspricht.

- Maßnahmen wie modulare Redundanz sind unerlässlich, um die korrekte Berechnung von Beschleunigern vor zufälligen Bitfehlern im Konfigurationsspeicher (aufgrund der Umgebungsstrahlung) zu schützen. Eine Lösung, die auf den schlimmsten Fall ausgerichtet ist, hat hohe Flächen- und Energiekosten durch den übertriebenen Schutzes gegen eine sich verändernde Umgebung. Diese Arbeit stellt ein neuartiges Laufzeitsystem vor, das dynamisch den effi-

zientesten Schutzmechanismus für unterschiedliche Beschleuniger bestimmen kann, abhängig von der Anfälligkeit der Beschleuniger, Zuverlässigkeitsrandbedingung der Anwendung und der Strahlungsstärke in der Umgebung. Im Vergleich zu einer verwandten Arbeit, die die Schutzmechanismen statisch festlegt, bietet die vorgestellte Methode bis zu 68% Leistungssteigerung bei derselben Zielzuverlässigkeit an.

Durch die Ausnutzung der inhärenten Flexibilität rekonfigurierbarer Architekturen erarbeitet diese Arbeit eine umfassende Lösung für Fehlerentdeckung, Fehlertoleranz und Verlangsamung der Alterung, die die Zuverlässigkeit des Systems gegen permanente und transiente Fehler verteidigt.

## Abstract

Reconfigurable computing combines the efficiency of hardware with the flexibility of software and is becoming competitive against conventional processor architectures like Central Processing Units (CPUs) and Graphic Processing Units (GPUs). It features a hardware organization that can be dynamically customized after manufacturing by the user for different application requirements. Reconfigurable architectures based on Field-Programmable Gate Arrays (FPGAs) are emerging over the recent years as a promising technology for reconfigurable computing, thanks to the growing logic capacity of FPGAs and the ease of FPGA design process driven by FPGA vendors.

A typical reconfigurable architecture consists of a general purpose processor, a reconfigurable fabric and a communication infrastructure interconnecting them. The reconfigurable fabric can reside on one or multiple FPGAs. Hardware accelerators, which implement the compute-intensive functions, can be instantiated in the reconfigurable fabric during runtime. The workload on the processor can then be offloaded to the FPGA which performs high performance and high energy efficient computation in hardware.

Continued advancement in the semiconductor industry enables sustained downscaling of transistor size into the nano-scale regime, which translates to higher transistor density, faster switching speed and lower energy consumption. To take these advantages of technology scaling, modern FPGA devices are manufactured in latest technology nodes. For instance, the newest MPSoC from Xilinx with four ARM cores and a reconfigurable fabric on a single die is built on 16 nm FinFET process technology.

However, the technology scaling is accompanied by challenges that threaten the dependable operation of FPGAs. Faults may escape the manufacturing test and remain latent in the shipped devices, as the growing complexity of circuits and new defect mechanisms limit the test effectiveness. During circuit operation, various microscopic phenomena degrade the physical and electrical properties of the materials that compose the transistors, which are further aggravated with down-scaling. The transistors do not operate forever, but they ages. The threshold voltage of transistors drifts over time, which weakens their current drive capability and may eventually cause them to fail entirely. In addition, the environmental background radiation interacts with the silicon and may induce bit-flip in the configuration memory of FPGAs. The resulted erroneous configuration bits essentially alter the functional definition of the circuits implemented on the FPGA, which renders the computation results from the FPGA corrupted.

In a dependable system, particularly for safety- and mission-critical applications, faults shall be discovered with small detection latency, be located and avoided to block them from affecting the whole system. Furthermore, proactive countermeasures shall be taken to prevent the emerging of faults in the first place. To realize a dependable reconfigurable architecture, the following key dependability techniques are developed in this thesis:

- To detect faults in the reconfigurable fabric, on-demand and periodic testing are scheduled along with the functional workload. Before the instantiation of accelerators, the underlying reconfigurable resources in the fabric are exercised by exhaustive structural test. After the accelerators are configured into the fabric, their correct functionality is periodically checked by functional test. The combination of both test schemes achieves a high fault coverage and low test latency at minimal performance overhead. Experimental results show that the reconfigurable fabric can be exhaustively tested every 4 seconds at a performance cost of less than 4.4%.

- When part of the reconfigurable fabric is detected to be faulty, it can be avoided, i.e. do not participate in computation, while the system performance is not adversely affected. This is achieved by a novel design method Module Diversification. For each accelerator/module, it generates a set of configurations that are diversified in terms of resource usage. Alternative configurations that do not require the faulty resources can be used to maintain the system operation, even in the presence of faults. Reliability improvement factors between 19 and 330 were achieved in the experiments.

- Computation using the reconfigurable fabric induces electrical stress on individual transistors, which leads to the aging of transistors. A novel stress balance technique is developed that is able to distribute the stress induced by workload uniformly over all resources in the fabric, such that the stress on individual transistors is minimized. A combined approach with runtime accelerator placement and synthesis-time logic placement delivers uniform stress distribution that significantly prolongs the system lifetime at negligible runtime cost. Compared to state-of-the-art methods, this work reduces dynamic and static stress by up to 64% and 35%, which translates to a lifetime improvement up to 177% and 14%, respectively.

- In order to guard the correct functionality of accelerators against random bitflip in the configuration memory due to environmental radiation, countermeasures such as modular redundancy are indispensable. A worst-case solution incurs high area and energy overhead due to over-protection under a varying environment. This work proposes a novel runtime system that dynamically chooses the most efficient protection mechanisms for different accelerators, depending on the vulnerability of individual accelerators, reliability constraints of the application and environmental radiation level. Compared to related work with statically optimized redundancy techniques, the proposed method provides up to 68% higher performance at the same target reliability.

As a result, by exploiting the flexibility that is inherent in reconfigurable architectures, this work presents a comprehensive solution for fault discovery, fault tolerance and aging mitigation, defending against both permanent and transient faults.

## **1** Introduction and Motivation

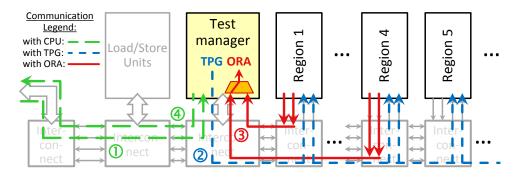

Runtime reconfigurable architectures based on Field-Programmable Gate Arrays (FPGAs) are emerging over the recent years as a promising augment to conventional processor architectures such as Central Processing Units (CPUs) and Graphic Processing Units (GPUs). Their essential feature, runtime reconfiguration, enables dynamic customization of the hardware organization for changing application requirements. A typical structure of reconfigurable architectures is shown in Fig. 1.1. It consists of a general purpose processor and a reconfigurable fabric, which are interconnected over a communication infrastructure. The reconfigurable fabric is partitioned into multiple reconfigurable regions, which can reside on multiple FPGAs or in one FPGA. During runtime, these reconfigurable regions can be reconfigured to implement accelerators that perform compute-intensive functions to speedup the execution of applications using hardware. Such an approach takes the advantages of high performance and low energy consumption only achievable in hardware, while providing the flexibility of software to customize the hardware function at runtime.

With the aggressive advancement of semiconductor industry, feature size of modern microelectronic devices continues shrinking in the nano-scale regime. While higher transistor density, higher performance and lower energy consumption are the major benefits and the driving force of ever shrinking nano-CMOS devices, dependability poses as a serious challenge lying ahead of continued scaling. A paradigm shift is happening that a dependable system has to build upon components of undependable natures. Manufactured in latest technology nodes, modern FPGAs are increasingly prone to various dependability issues, which threaten the dependable acceleration in the reconfigurable fabric.

Latent defects not discovered during manufacturing, soft errors in the sequential elements caused by single event upsets and transistor degradation caused by various aging effects are the major dependability concerns in safety and mission critical

Figure 1.1: Illustrative example of a reconfigurable architecture

applications. A dependable system shall be able to discover a fault with small detection latency, to tolerate the discovered fault with minimal performance degradation and even to prevent the fault in the first place.

This thesis addresses these requirements by answering the following questions: How can we test the system when its hardware organization changes during runtime? If part of the FPGA is tested to be faulty, how can we exploit runtime reconfiguration to isolate those faulty resources such that the system continues operation with minimal performance degradation? How can we further prolong the system lifetime by delaying the failure time of the FPGA? When high reliability of correct computation is required, how can we tailor the accelerator organization to defend the soft errors caused by single-event-upset, even when the environmental condition is changing? And how all of these can be accomplished with minimal hardware and runtime overhead?

First of all, let's discuss which dependability challenges we are facing and where they come from.

#### 1.1 Dependability Challenges in the Nano-CMOS Era

The continued down-scaling of feature sizes of digital integrated circuits still follows the trends envisioned more than 40 years ago by Gordon Moore [Moo75]. The initial motivation of scaling was to reduce the cost per electronic function, or rather the cost per transistor. As more transistors can be integrated in one chip and more chips can be fabricated with one wafer, the cost of manufacturing a wafer is now shared among hundreds of billions of transistors<sup>1</sup>. Although the cost per wafer rose exponentially with technology node scaling due to the ever more sophisticated manufacturing process towards the physical limit, in fact, the decreasing trend of cost per transistor has been sustained thanks to the accelerated trend in the increase of transistor density [Hol16]. In addition to the economical benefits, transistor scaling also helps the circuit to operate at higher frequencies and with lower energy consumption as transistor switching activities require less charge transport at smaller geometric scales. The soaring transistor density allows the high integration of rich functionalities at affordable price, which leads to the deep penetration of nanoelectronic devices in every corner of our daily life. High demand from traditional markets such as data-centers and mobile devices and from emerging innovations such as internet of things and autonomous vehicles are further driving the down-scaling in favor of lower cost, higher performance and lower energy consumption.

On the other hand, the down-scaling of the geometry of transistors is accompanied by a two-fold up-scaling of the products composed of nanoelectronic devices: 1) the complexity of the products grows exponentially with deep functional integration; and 2) the volume of shipped products grows with increasing demand and new markets enabled by nano-device innovations. For instance, around 100 electronic control units with 7000 semiconductor components are concurrently operating in a

<sup>&</sup>lt;sup>1</sup>More than 400 billion transistors on a 300 mm wafer for the Intel Xeon E5-2600 v3 18-core processor  $[BSN^+15]$ .

modern passenger car [ALHS12] for the powertrain, safety, comfort and infotainment functions under a wide range of environmental conditions. And the global passenger car sale number has reached 70 million in 2015 [Sta16]. However, the up-scaling of complexity and volume poses a great challenge to the dependability and quality of the products, particularly for safety-critical systems like vehicles where a single functional failure may be life-threatening.

#### 1.1.1 Challenges from Up-Scaling

As the number of components or integrated functions (that could be implemented with multiple components) of a system increases, the requirements to the dependability of individual components or functions is becoming increasingly stringent as well. The dependable operation of a system relies on the correct collaborative functioning of all sub-components and the failure of any one of them may manifest as a critical malfunction of the whole system. The more functions reside in a system and the complexer their interactions are, the more sources of failure exist and the higher the probability that the system fails. Because it is commonly assumed that technology advances would always benefit all aspects of a system including dependability, the dependability specification (e.g. mean time to failure) of a system desired by customers would at least remain the same or become even higher, regardless of the increased internal complexities due to functional integration. Therefore, the dependability of individual functions needs to be accordingly improved to meet the system-level dependability specification.

Extensive test during production and thorough verification during design are indispensable to guarantee the dependability of complex systems and devices. The up-scaling of functional complexity also has made a dramatic impact on the test of nanoelectronic devices containing billions of transistors. Given limited monetary and time budget for test, new defect mechanisms emerged from advanced nano-manufacturing technologies and ever sophisticated circuit designs, e.g. Systemon-Chip (SoC), may render certain defects escaping from manufacturing tests and remaining in the shipped products [Zor13].

The new defect mechanisms are mainly resulted from the process variation at nano-scale (e.g. random dopant fluctuation) and from the introduction of new materials (e.g. cobalt for copper encapsulation), new structures (e.g. 3D, FinFET) and new power management techniques (e.g. voltage scaling). These defects could yet be captured by the fault models in current automatic test equipments.

An SoC is composed of a set of distinct Intellectual Property (IP) cores, e.g. multi-core processors, graphic processing unit, embedded memories, radio frequency circuits for wireless connectivity, etc. Each type of IP cores needs to be tested in individual sessions with dedicated test methods, which leads to extended test time. Moreover, on account of the intellectual protection, IP vendors provide only limited IP structural information and impose additional test constraints, e.g. specific rules for applying test patterns [WST08]. These complications lower the test efficiency and increase the test time further, which translates to the climbing cost of test.

As the volume of shipped products scales up, if the dependability of one product, typically measured in Defective Parts Per Million (DPPM), would linger on the same level as the time of the small-scale production, the cost of rejection, repair and the loss of customer satisfaction would ultimately damage the profitability and the reputation of a company. A zero DPPM target shall be met if the product is to be deployed in high-volume and safety-critical systems, such as in automotive systems [Con15].

To summarize, the up-scaling of the internal complexity and the shipping volume urges the semiconductor industry to address the aforementioned dependability challenges before continuing the down-scaling of the transistor size. Unfortunately, these challenges are being further aggravated as the manufacturing process approaches the physical limits.

#### 1.1.2 Challenges from Down-Scaling

Nowadays, the smallest feature size (e.g. 10 nm) manufactured on a chip is well below the wavelength of the light source (193 nm) used in the most advanced available photolithography technique, i.e. immersion lithography [GBF<sup>+</sup>04]. The pattern transfering process from the mask<sup>2</sup> to the wafer experiences significant fidelity degradation due to the limited resolution in the optical systems which have received no resolution improvement since 2007 [STY<sup>+</sup>15]. The desired precise geometries on the wafer can thus only be approximated by auxiliary methods such as multiple patterning, optical proximity correction and phase-shift masks. These approximations rely on the interference and diffraction of light to create sub-wavelength features, which exhibit wide shape variations both locally in the feature itself and globally across the wafer [DLW09]. For example, a square shape definition on the mask will be transferred into an irregular rounded rectangle with curvy edges. The roundness and curviness will variate depending on the surrounding shapes and the surface properties of the photoresist and wafer in the shape definition region. This geometry variability caused by the inaccurate shape definition is one of the major sources of variability that impact the deterministic nature of transistor characteristics; e.g. the threshold voltage of transistors at different locations on a wafer may vary randomly in a wide range  $[ALWA^+14]$ .

Another major source of variability stems from the atomistic level fluctuation of dopants in the channel region of transistors, so-called Random Dopant Fluctuation (RDP). During the fabrication of transistors, impurity atoms (dopants) from group III/V elements are intentionally introduced (doped) into the intrinsic silicon substrate to modulate it into the p/n-type semiconductor. In addition, doping into the channel region of transistors can also be employed to adjust the threshold voltage or control short-channel effects [Shi16]. As the dimension of transistors scales down, the total number of dopants in the channel region decreases to an extent that a change of just only a few atoms would have significant impact on the transistor characteristics. In 45 nm CMOS technology, the average number of dopant atoms

$<sup>^{2}</sup>$ Masks are fabricated using electron beam lithography, which offers very high resolution (below 5 nm) but very low throughput and thus is not suitable for mass chip production.

in the channel region decreases below 100, where RDP contributes to around 60% of the total variation in the PMOS threashold voltage [KKK<sup>+</sup>08]. Moreover, not only the number but the spatial variation in the position of dopants also affects the transistor performance [Shi16]. State-of-the-art FinFET technologies exhibit around 20 mV standard deviation in the threshold voltage [BDB<sup>+</sup>13, ALWA<sup>+</sup>14].

To cope with the variability inherent in the manufacturing process, a large timing margin is applied during design time such that the circuit could work at a specified frequency under the most unfavorable variability conditions. Unfortunately, another variability mechanism that requires a comparable amount of margin is becoming crucial for the transistors to survive through time. It is aging, a kind of temporal variability that changes the transistor characteristics over time.

Aging effects originate from the degradation in the electrical or physical properties in the material resulting from continued operation of the device. For instance, traps which restrict the free movement of electrons or holes may form at the interface between the gate oxide and the channel of a transistor as a result of the undesired tunneling of carriers from the channel into the gate oxide when the transistor is operating. These traps are positively or negatively charged in PMOS or NMOS, respectively and shift the threshold voltage of transistors in a harmful way, i.e. increase in NMOS and decrease in PMOS. This lowers the current drive capability of the transistor under a fixed supply voltage and may eventually lead to the timing violation in sequential circuits. Major aging effects in nano-CMOS transistors include Bias Temperature Instability (BTI), Hot Carrier Injection (HCI) and Time-Dependent Dielectric Breakdown (TDDB) [RBC<sup>+</sup>13, CVS<sup>+</sup>14], while Electro-Migration (EM) is considered as a major aging issue affecting the interconnects with high current densities, e.g. power delivery networks [Lie13].

With the technology down-scaling, these aging effects are expected to persist as a major dependability challenge. 10 nm FinFETs shall continue to suffer from aging and the device susceptibility to different aging mechanisms shall also change with the introduction of new device structures and materials  $[SWS^{+}14]$ . There is also evidence that nano-FinFETs experience degradation more severely than planer devices [LKC<sup>+</sup>13, LWL<sup>+</sup>14]. A continuous decreasing trend in transistor lifetime across advancing technology nodes [HCF<sup>+</sup>15] calls for efficient countermeasures against aging. Typical guardband techniques lower the target frequency at design time such that the system can still operate at the end of lifetime, although at the beginning of lifetime the system is capable of operating at a higher frequency. For the current technology nodes, aging, in particular NBTI, leads to an even higher shift (50 mV in average) in the threshold voltage  $[CKR^{+}15]$  in the worst case than the variation caused by the manufacturing process. Therefore, a larger timing margin would be required on top of the margin tailored for the process variation. This pessimistic over-design may eventually offset the performance benefit enabled by the technology scaling.

### 1.1.3 Addressing the Challenges

The challenges from up-scaling lie in the conflict between the growing demand of high dependability product and the increasing difficulty in manufacturing a defectfree chip. Down-scaling enables higher performance which is however diminished by the introduction of large guardbands against the spatial and temporal variability in the transistor characteristics.

Besides Moore's Law in the visionary paper [Moo75], it was also recognized that system reliability was improved dramatically along with the increasing functional integration. In the 90's, Texas Instruments and Intel are striving to reach the reliability goal of 0.1 FIT<sup>3</sup> [Gha91] and 10 FIT [STW98] by the year 2000, respectively. However, the efforts to improve the product reliability still fall behind the imminent challenges in the nano-CMOS technology. Following the current down-scaling trend, the complications in the manufacturing process are envisioned to become more challenging in the future [Kuh12, SAB<sup>+</sup>13]. Merely relying on the improvement in the manufacturing process is therefore determined not to be able to meet the dependability goals desired by the upper tier vendors such as automotive suppliers [vT08] which expect zero defect in product and zero failure in time. New solutions in addition to the extensive testing during production and verification during design are necessary to address these challenges.

Runtime dependability management opens a new level of freedom to address the above nano-era dependability issues. A runtime strategy has the following advantages: 1) Latent faults not detected during manufacturing and permanent faults caused by aging can be detected using online tests; 2) The system is able to adapt itself to changing environment conditions in a way that optimized decisions, trading-off performance and dependability, can be made during runtime, instead of a static pessimistic design decision that targets the worst environment condition; and 3) A further optimization potential can be exploited that takes into account the different dependability requirements of workloads and the impact of them on the system states.

In this thesis, runtime self-defense mechanisms including online monitoring, runtime dependability modeling and the orchestration of dependability countermeasures are developed to increase the system reliability and availability. Escaped faults from manufacturing tests are detected and localized by online testing. Concurrent error detection captures random hardware failure and prevent them from propagating into other functional units in the system. Fault-tolerance techniques are developed to isolate permanent or transient faults such that the system continues delivering service even in an impaired state. Transistor aging effects are mitigated to allow for an extended system lifetime or a tighter guardband at the beginning of the system lifetime.

<sup>&</sup>lt;sup>3</sup>Failure-In-Time: 1 FIT = 1 failure in 1 billion hours

#### 1.2 Thesis Contributions

The contributions of this work are summarized as follows:

**Pre- and Post-configuration Test**: The correct operation of runtime reconfigurable architectures essentially relies on the dependability of the reconfigurable fabric on the FPGA. This requires that the underlying hardware structures are fault-free and the accelerator reconfiguration process completes without errors. In this work, these are ensured by on-demand and periodic testing: Pre-configuration test (PRET) checks the structural integrity of the underlying hardware before the instantiation of accelerators and Post-configuration test (PORT) periodically checks the correct functionality of configured accelerators after they are instantiated. The strategic scheduling of PRET and PORT delivers high fault coverage and low test latency at marginal performance cost.

Module Diversification: If part of the reconfigurable fabric is detected to be faulty, system breakdown is avoided by employing the novel design method called module diversification. Alternative configurations of accelerators that have diversified resource usage are generated during design time. Self-repairing is achieved by circumventing the faulty resources with accelerator configurations that do not require the faulty resources. The module diversification process is able to generate minimal number of diversified configurations of each accelerator in order to minimize the storage overhead of configuration bitstreams.

**Stress-aware Placement**: System degradation threatened by aging effects is addressed by stress-aware runtime accelerator placement and design time logic placement. During runtime, the stress induced by accelerators is uniformly distributed over all available reconfigurable resources. At design time, the overlapping of high stress regions among individual accelerators is minimized to further improve the runtime stress distribution. Both together balance the intra- and inter-region stress induced by the application workload at negligible performance cost, which leads to significant maximum stress reduction and prolonged system lifetime.

Adaptive Modular Redundancy: For applications with strict reliability constraints, highly reliable operation of accelerators is required, which is however threatened by soft-errors in the configuration memory. A single bit-flip in the configuration memory may impair the functionality of the accelerators. Concurrent error detection techniques such as modular redundancy are obligatory, which may incur high resource usage and performance loss due to over-protection. To guarantee the required reliability at minimal performance cost, the runtime system dynamically selects appropriate redundancy degree of accelerators, depending on the vulnerability of individual accelerators, reliability constraints of the application and environmental radiation level.

By exploiting the inherent flexibility provided by runtime reconfigurable architectures, this thesis addresses the nano-era dependability challenges in a cross-layer fashion, from transistor layer over circuit layer till accelerator layer, from design time to runtime. With strategic online testing, self-repairing, stress balancing and adaptive modular redundancy, a resilient and highly dependable runtime reconfigurable architecture is accomplished at minimal hardware and runtime overhead.

#### 1.3 DFG Research Program SPP-1500 and InvasIC