## Reliable Design of Three-Dimensional Integrated Circuits

For obtaining the academic degree of

Doctor of Engineering

Department of Informatics Karlsruhe Institute of Technology (KIT) Karlsruhe, Germany

#### Approved

#### Dissertation

by

Master of Science Shengcheng Wang

From Tianjin, China

Date of Oral Examination: 04.05.2018

Supervisor: Prof. Dr. Mehdi Baradaran Tahoori, Karlsruhe Institute of Technology

Co-supervisor: Prof. Dr. Said Hamdioui, Delft University of Technology

Shengcheng Wang Haid-und-Neu Str. 62 76131 Karlsruhe

Hiermit erkläre ich an Eides statt, dass ich die von mir vorgelegte Arbeit selbstständig verfasst habe, dass ich die verwendeten Quellen, Internet-Quellen und Hilfsmittel vollständig angegeben haben und dass ich die Stellen der Arbeit - einschließlich Tabellen, Karten und Abbildungen - die anderen Werken oder dem Internet im Wortlaut oder dem Sinn nach entnommen sind, auf jeden Fall unter Angabe der Quelle als Entlehnung kenntlich gemacht habe.

Karlsruhe, Mai 2018

Shengcheng Wang

## **Abstract**

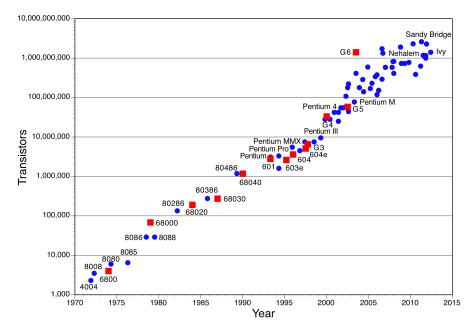

Beginning with the invention of the first Integrated Circuit (IC) by Kilby and Noyce in 1959, performance growth in IC is realized primarily by geometrical scaling, which has resulted in a steady doubling of device density from one technology node to another. This observation was famously known as "Moore's law". However, the performance enhancement due to traditional technology scaling has begun to slow down and present diminishing returns due to a number of imminent show-stoppers, including fundamental physical limits of transistor scaling, the growing significance of quantum effects as transistors shrink, and a mismatch between transistors and interconnects regarding size, speed and power. As a result, a new paradigm shift in IC technology and architecture is required to sustain the historical IC performance growth.

Three-Dimensional Integrated Circuit (3D IC), which refers to a vertical (or horizontal) stack consisting of multiple ultra-thin IC layers, has emerged as a promising option to overcome the challenges related to conventional geometrical scaling. 3D IC can achieve device density multiplication without aggressive scaling by stacking IC layers in the third dimension. In a 3D IC, multiple IC layers can be vertically/horizontally interconnected by various interconnect techniques, in which Through-Silicon Via (TSV) is a critical one. More specifically, TSV is a vertical electrical connection passing completely through a silicon wafer or die, which is a key enabler for 3D integration. By using TSVs, the interconnection length between stacked IC layers can be significantly reduced compared to conventional two-dimensional counterparts. This reduction further translates into less wire delay and higher performance. However, 3D integration scheme also results in new challenges in the fields of physical design and testing mechanism. In this dissertation, a set of reliability-aware and testability-driven design and optimization techniques have been proposed in order to enable reliable designs of 3D ICs, as well as enhance physical design quality.

The first contribution of this dissertation is to develop a holistic Computer-Aided Design (CAD) platform for 3D Power Delivery Network (PDN), which can be integrated seamlessly within commercial electronic design automation development flows. The design of 3D PDN is a constrained optimization problem. An ideal PDN must: i) limit voltage drop which originates in switching circuits transients, and ii) satisfy the constraints that arise from reliability limits. In addition, these problems are further constrained by the requirement to minimize additional hardware overhead introduced by TSVs in 3D ICs. In this dissertation, a CAD platform has been developed to handle the trade-off between 3D PDN design qualities and hardware design cost under the constraints of required reliability metrics.

The second contribution of this dissertation is to develop a comprehensive framework for TSV repair in order to enhance yield and improve reliability in 3D ICs. As critical enablers for 3D ICs, TSVs can deliver signals from one layer to another. However, during fabrication and normal operations, they may suffer from various reliability issues. Due to the large number of TSVs in a chip, these issues in turn translate into low yields and reduced lifetimes. In order to fix failed TSVs, a simple but effective way is to add redundant TSVs into 3D designs to increase chip yield and overall reliability with additional hardware overheads. By considering the trade-off between chip qualities (in terms of manufacturing yield and operation lifetime), hardware overhead, and performance, a framework has been proposed to improve chip yield and extend TSV lifetime significantly with well-managed TSV redundancy.

The third contribution of this dissertation is to develop a novel test architecture for interposer-based 3D ICs (also knowns as Two-and-a-Half-Dimensional Integrated Circuits (2.5D ICs)), which is emerging as a precursor to TSV-based ones at the present time. In a 2.5D IC, multiple dies are placed side by side on a passive silicon interposer, and all of them must be adequately tested for product qualification. However, due to the special structure of 2.5D IC, new testing challenges have emerged such as: i) reduced number of test pins, ii) higher test power consumption, and iii) increased test-application time. In this dissertation, the research targets the above challenges, and effective solution has been developed to test dies with minimum test cost in terms of power consumption and test-application time.

As demands accelerate for increasing device density, higher bandwidths, and lower power consumption, the semiconductor community is focusing on 3D ICs, which promise "More-than-Moore" integration by packing a great deal of functionality into small form factors, while reducing cost and improving performance. However, due to several significant technical hurdles, volume production and commercial exploitation of 3D ICs are not feasible yet, and still in the early phases. For instance, the standard definitions in 3D ICs are still lacking, the supply chain ecosystem is still unstable, and design, verification and test challenges need to be resolved. In this dissertation, we focus on the reliability and testability challenges in 3D IC design. A set of reliability-aware and testability-driven techniques in the aspects of automating the physical-design process for 3D ICs have been proposed. Significant improvements for reliability and performance were demonstrated for 3D ICs. Therefore, the proposed solutions and developed frameworks in this dissertation can act as important building blocks for 3D ICs and push them toward mainstream acceptance in the near future.

## Contents

| Li | List of Figures |         |                                                            | xi   |

|----|-----------------|---------|------------------------------------------------------------|------|

| Li | st of           | Tables  |                                                            | χV   |

| Li | st of           | Acrony  | vms                                                        | xvii |

| Li | st of           | Publica | ations                                                     | xxi  |

| 1  | Intr            | oductio | on                                                         | 1    |

|    | 1.1             | Benefi  | its of 3D Integration Technologies                         | . 4  |

|    |                 | 1.1.1   | Interconnect delay reduction                               | . 4  |

|    |                 | 1.1.2   | Memory bandwidth improvement                               | . 6  |

|    |                 | 1.1.3   | Heterogeneous integration                                  |      |

|    | 1.2             | Challe  | enges in 3D Integration Technologies                       | . 9  |

|    |                 | 1.2.1   | Thermal management challenges                              | . 9  |

|    |                 | 1.2.2   | 3D power delivery network design challenges                | . 10 |

|    |                 | 1.2.3   | TSV-related reliability and yield challenges               | . 11 |

|    |                 | 1.2.4   | Testing challenges                                         |      |

|    | 1.3             | Disser  | ctation Contributions and Outline                          | . 12 |

|    |                 | 1.3.1   | Contributions to reliable 3D power delivery network design |      |

|    |                 | 1.3.2   | Contributions to TSV self-repair of 3D ICs                 |      |

|    |                 | 1.3.3   | Contributions to cost-effective testing of 3D ICs          |      |

|    |                 | 1.3.4   | Dissertation outline                                       | . 16 |

| 2  | Bac             | kgroun  | d                                                          | 17   |

|    | 2.1             | Interc  | onnect Hierarchy in 3D Integration                         | . 17 |

|    | 2.2             | 3D In   | tegration Technology Landscape and Applications            | . 18 |

|    |                 | 2.2.1   | 3D system-in-package                                       | . 19 |

|    |                 | 2.2.2   | 3D stacked integrated circuit                              | . 21 |

|    |                 | 2.2.3   | 3D monolithic integrated circuit                           | . 27 |

|    | 2.3             | Fabric  | cation of TSVs                                             | . 27 |

|    |                 | 2.3.1   | Via-first process                                          | . 27 |

|    |                 | 2.3.2   | Via-middle process                                         | . 28 |

|    |                 | 2.3.3   | Via-last process                                           |      |

|    | 2.4             | Reliab  | pility Issues Related to TSVs                              | . 30 |

|    |                 | 2.4.1   | Stresses in TSVs                                           | . 30 |

|    |                 | 9.4.2   | Electromigration in TSVs                                   | 31   |

#### Contents

|   | 2.5  | Testin        | ng of 3D ICs                                                      | 3          |

|---|------|---------------|-------------------------------------------------------------------|------------|

| 3 |      |               | tress-aware Power/Ground TSV Planning                             | 3          |

|   | 3.1  |               |                                                                   | 3          |

|   |      | 3.1.1         | · · · · · · · · · · · · · · · · · · ·                             | 3          |

|   |      | 3.1.2         | · ·                                                               | 3          |

|   | 3.2  | Motiv         |                                                                   | 3          |

|   | 3.3  | Metho         | odology                                                           | 4          |

|   |      | 3.3.1         | Problem statement                                                 | 4          |

|   |      | 3.3.2         | Power/ground TSV-induced delay change                             | 4          |

|   |      | 3.3.3         | Voltage constraints                                               | 4          |

|   |      | 3.3.4         | Power and stress profiles redistribution                          | 4          |

|   |      | 3.3.5         | Scalability                                                       | 4          |

|   | 3.4  | Exper         | rimental Results                                                  | 4          |

|   |      | 3.4.1         | Experimental setup and flow                                       | 4          |

|   |      | 3.4.2         | Impact of design parameters on delay variation                    | 4          |

|   |      | 3.4.3         | Comparison with previous technique                                | 4          |

|   |      | 3.4.4         | Accuracy and Runtime                                              | 4          |

|   | 3.5  | Concl         | usion of Chapter                                                  | 4          |

| 4 | Elec | tromig        | ration-aware Local-via Allocation in Power/Ground TSV             | 5          |

|   | 4.1  | _             | ninaries and Related Work                                         | 5          |

|   |      | 4.1.1         | Via-first TSV-based 3D power delivery network design challenges . | 5          |

|   |      | 4.1.2         | Electromigration reliability of TSVs                              | 5          |

|   |      | 4.1.3         | Electromigration-induced resistance increase of via-first TSV     | 5          |

|   |      | 4.1.4         | Related prior works                                               | 5          |

|   | 4.2  |               | sed Electromigration-aware Local-via Allocation                   | 5          |

|   |      | 4.2.1         | Problem statement                                                 | 5          |

|   |      | 4.2.2         | Assumption and notation                                           | 5          |

|   |      | 4.2.3         | Integer linear programming formulation                            | 5          |

|   |      | 4.2.4         | Scalability analysis                                              | 6          |

|   |      | 4.2.5         |                                                                   | 6          |

|   | 4.3  |               |                                                                   | 6          |

|   | 1.0  | 4.3.1         |                                                                   | 6          |

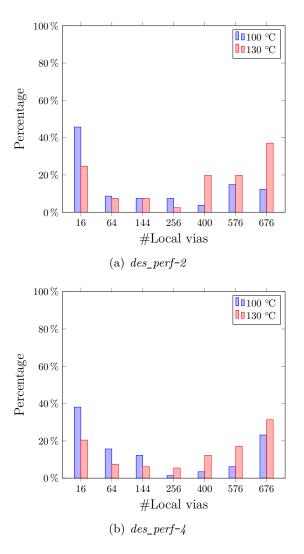

|   |      | 4.3.2         | Impact of temperature on local-via allocation                     | 6          |

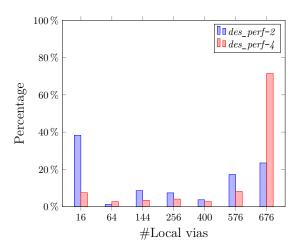

|   |      | 4.3.3         | Impact of circuit partitioning on local-via allocation            | 6          |

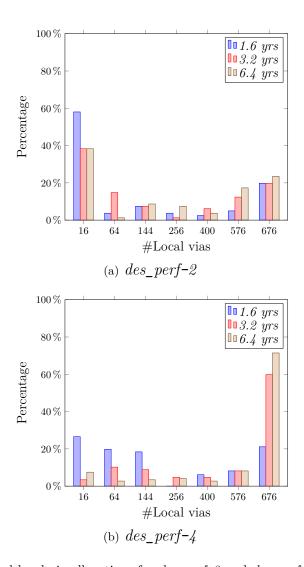

|   |      | 4.3.4         | Impact of target lifetime on local-via allocation                 | 6          |

|   |      | 4.3.4 $4.3.5$ | Comparison with prior work                                        | 7          |

|   |      | 4.3.6         | Runtime analysis                                                  | 7          |

|   | 4.4  |               | ·                                                                 |            |

|   | 4.4  | Conci         | usion of Chapter                                                  | 7          |

| 5 |      |               | stering-aware TSV Repair for Yield Enhancement                    | <b>7</b> . |

|   | 5.1  |               | ninaries and Related Work                                         | 7          |

|   |      | 5 1 1         | TSV fault tolerance                                               | 7          |

|          |                                                           | 5.1.2 S                                                                                                                                                           | pare TSV allocation in different TSV placements                |

|----------|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

|          |                                                           | 5.1.3 T                                                                                                                                                           | SV-induced stress and stress-induced delay overhead 79         |

|          |                                                           | 5.1.4 T                                                                                                                                                           | SV defect clustering                                           |

|          |                                                           | 5.1.5 R                                                                                                                                                           | elated prior work                                              |

|          | 5.2                                                       | Motivation                                                                                                                                                        | onal Example                                                   |

|          | 5.3                                                       | Spare TS                                                                                                                                                          | V Allocation Considering Defect Clustering 82                  |

|          |                                                           | 5.3.1 P                                                                                                                                                           | roblem statement                                               |

|          |                                                           | 5.3.2 N                                                                                                                                                           | otation                                                        |

|          |                                                           | 5.3.3 A                                                                                                                                                           | ssumptions related to metrics                                  |

|          |                                                           | 5.3.4 O                                                                                                                                                           | verview of the proposed methodology                            |

|          |                                                           | 5.3.5 F                                                                                                                                                           | ault-map generation                                            |

|          |                                                           | 5.3.6 G                                                                                                                                                           | lobal partitioning                                             |

|          |                                                           | 5.3.7 D                                                                                                                                                           | etailed insertion of spare TSVs                                |

|          | 5.4                                                       | Simulation                                                                                                                                                        | on Results                                                     |

|          |                                                           | 5.4.1 S                                                                                                                                                           | mulation setup                                                 |

|          |                                                           | 5.4.2 In                                                                                                                                                          | npact of design knobs on spare TSV allocation                  |

|          |                                                           | 5.4.3 In                                                                                                                                                          | npact of process variation on spare TSV allocation 99          |

|          |                                                           | 5.4.4 C                                                                                                                                                           | omparison with prior work                                      |

|          |                                                           | 5.4.5 R                                                                                                                                                           | untime analysis                                                |

|          |                                                           | 5.4.6 D                                                                                                                                                           | iscussion                                                      |

|          | 5.5                                                       | Conclusion                                                                                                                                                        | on of Chapter                                                  |

|          |                                                           |                                                                                                                                                                   |                                                                |

| <b>-</b> | <b>-</b>                                                  |                                                                                                                                                                   | to Decrease TCV Decret for Delichtin Income 105                |

| 6        |                                                           | _                                                                                                                                                                 | ion Recovery-aware TSV Repair for Reliability Improvement  105 |

| 6        | <b>Elec</b> 6.1                                           | Prelimin                                                                                                                                                          | aries and Related Work                                         |

| 6        |                                                           | Prelimina 6.1.1 E                                                                                                                                                 | aries and Related Work                                         |

| 6        | 6.1                                                       | Prelimina 6.1.1 E 6.1.2 R                                                                                                                                         | aries and Related Work                                         |

| 6        | 6.1                                                       | Prelimina<br>6.1.1 E<br>6.1.2 R<br>Motivation                                                                                                                     | aries and Related Work                                         |

| 6        | 6.1                                                       | Prelimina<br>6.1.1 E<br>6.1.2 R<br>Motivation<br>Design-time                                                                                                      | aries and Related Work                                         |

| 6        | 6.1                                                       | Prelimina<br>6.1.1 E<br>6.1.2 R<br>Motivation<br>Design-ti<br>6.3.1 E                                                                                             | aries and Related Work                                         |

| 6        | 6.1                                                       | Prelimina<br>6.1.1 E<br>6.1.2 R<br>Motivation<br>Design-ti<br>6.3.1 E<br>6.3.2 F                                                                                  | aries and Related Work                                         |

| 6        | 6.1                                                       | Prelimina 6.1.1 E 6.1.2 R Motivation Design-ti 6.3.1 E 6.3.2 F 6.3.3 S                                                                                            | aries and Related Work                                         |

| 5        | 6.1                                                       | Prelimina 6.1.1 E 6.1.2 R Motivatic Design-ti 6.3.1 E 6.3.2 F 6.3.3 S 6.3.4 N                                                                                     | aries and Related Work                                         |

| 6        | 6.1<br>6.2<br>6.3                                         | Prelimina 6.1.1 E 6.1.2 R Motivation Design-ti 6.3.1 E 6.3.2 F 6.3.3 S 6.3.4 N 6.3.5 D                                                                            | aries and Related Work                                         |

| 6        | 6.1                                                       | Prelimina 6.1.1 E 6.1.2 R Motivation Design-ti 6.3.1 E 6.3.2 F 6.3.3 S 6.3.4 N 6.3.5 D Run-time                                                                   | aries and Related Work                                         |

| 6        | 6.1<br>6.2<br>6.3                                         | Prelimina 6.1.1 E 6.1.2 R Motivatic Design-ti 6.3.1 E 6.3.2 F 6.3.3 S 6.3.4 N 6.3.5 D Run-time 6.4.1 R                                                            | aries and Related Work                                         |

| 6        | 6.1<br>6.2<br>6.3                                         | Prelimina 6.1.1 E 6.1.2 R Motivation Design-ti 6.3.1 E 6.3.2 F 6.3.3 S 6.3.4 N 6.3.5 D Run-time 6.4.1 R 6.4.2 R                                                   | aries and Related Work                                         |

| 6        | 6.1<br>6.2<br>6.3                                         | Prelimina 6.1.1 E 6.1.2 R Motivation Design-ti 6.3.1 E 6.3.2 F 6.3.3 S 6.3.4 N 6.3.5 D Run-time 6.4.1 R 6.4.2 R 6.4.3 O                                           | aries and Related Work                                         |

| 5        | <ul><li>6.1</li><li>6.2</li><li>6.3</li><li>6.4</li></ul> | Prelimina 6.1.1 E 6.1.2 R Motivation Design-ti 6.3.1 E 6.3.2 F 6.3.3 S 6.3.4 N 6.3.5 D Run-time 6.4.1 R 6.4.2 R 6.4.3 C Numerica                                  | aries and Related Work                                         |

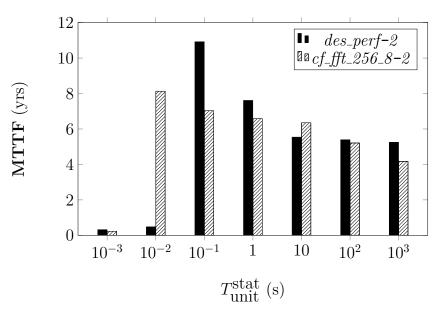

| 5        | <ul><li>6.1</li><li>6.2</li><li>6.3</li><li>6.4</li></ul> | Prelimina 6.1.1 E 6.1.2 R Motivation Design-ti 6.3.1 E 6.3.2 F 6.3.3 S 6.3.4 N 6.3.5 D Run-time 6.4.1 R 6.4.2 R 6.4.3 O Numerica 6.5.1 E                          | aries and Related Work                                         |

| 6        | <ul><li>6.1</li><li>6.2</li><li>6.3</li><li>6.4</li></ul> | Prelimina 6.1.1 E 6.1.2 R Motivation Design-ti 6.3.1 E 6.3.2 F 6.3.3 S 6.3.4 N 6.3.5 D Run-time 6.4.1 R 6.4.2 R 6.4.2 R 6.4.3 O Numerica 6.5.1 E 6.5.2 In         | aries and Related Work                                         |

| 6        | <ul><li>6.1</li><li>6.2</li><li>6.3</li><li>6.4</li></ul> | Prelimina 6.1.1 E 6.1.2 R Motivation Design-ti 6.3.1 E 6.3.2 F 6.3.3 S 6.3.4 N 6.3.5 D Run-time 6.4.1 R 6.4.2 R 6.4.2 R 6.4.3 O Numerica 6.5.1 E 6.5.2 In 6.5.3 B | aries and Related Work                                         |

### Contents

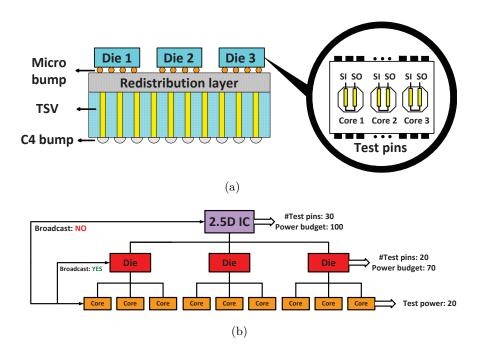

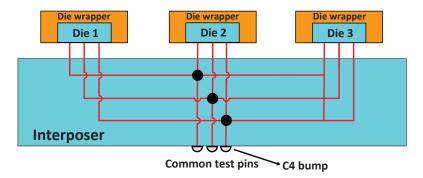

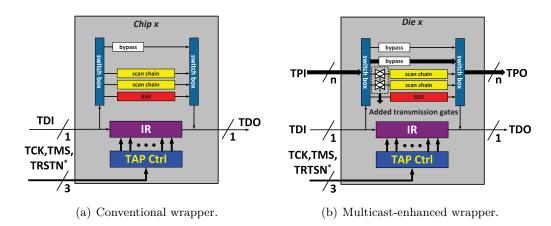

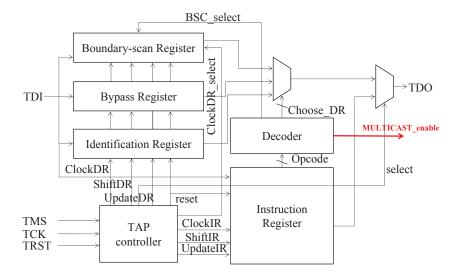

| 7 | Cost | t-efficient Multicast Testing for Interposer-based 3D ICs  |

|---|------|------------------------------------------------------------|

|   | 7.1  | Related Prior Work                                         |

|   | 7.2  | Motivation for Proposed Work                               |

|   | 7.3  | Proposed Test Architecture                                 |

|   |      | 7.3.1 Requirement and design                               |

|   |      | 7.3.2 Overhead analysis                                    |

|   | 7.4  | Test-scheduling Method                                     |

|   |      | 7.4.1 Problem statement                                    |

|   |      | 7.4.2 Notation and assumption                              |

|   |      | 7.4.3 Integer linear programming formulation               |

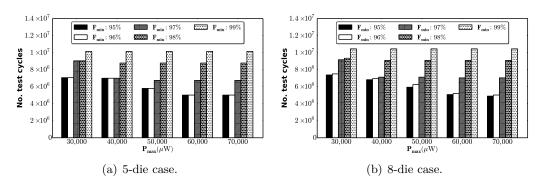

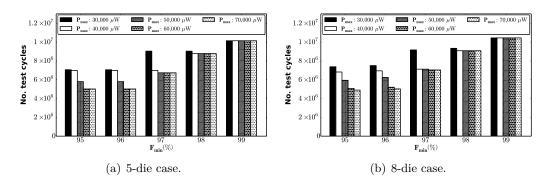

|   | 7.5  | Simulation Results                                         |

|   |      | 7.5.1 Simulation setup                                     |

|   |      | 7.5.2 Impact of design knobs on test schedule              |

|   |      | 7.5.3 Comparison with prior work: BIST-based approach      |

|   |      | 7.5.4 Comparison with prior work: scan-based approach      |

|   |      | 7.5.5 Runtime analysis                                     |

|   |      | 7.5.6 Discussion                                           |

|   | 7.6  | Conclusion of Chapter                                      |

| 8 | Con  | clusions                                                   |

|   | 8.1  | Summary of Contributions                                   |

|   | 8.2  | Future Work                                                |

|   |      | 8.2.1 Leverage 3D integration for internet of things       |

|   |      | 8.2.2 Leverage 3D integration for neuromorphic engineering |

# **List of Figures**

| 1.1  | Transistor count per leading edge CPU chip over last 45 years [2]                | 2   |

|------|----------------------------------------------------------------------------------|-----|

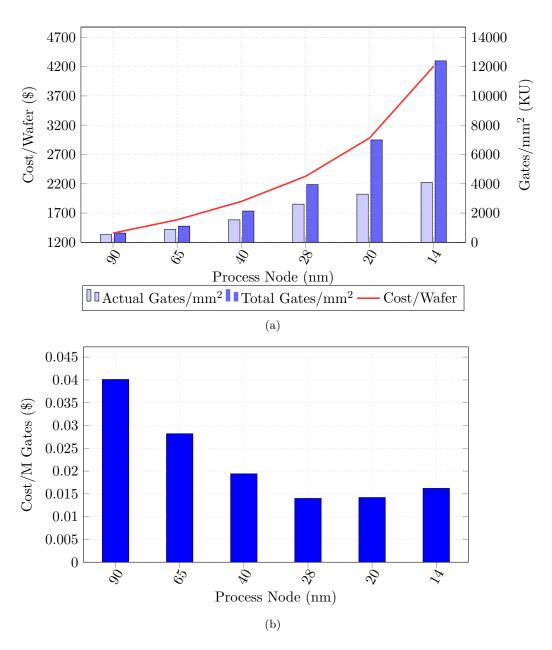

| 1.2  | (a) Gate count and wafer cost per process node leading to trend change           |     |

|      | in (b) cost per gate for different process node. Reproduced from data [8].       | 3   |

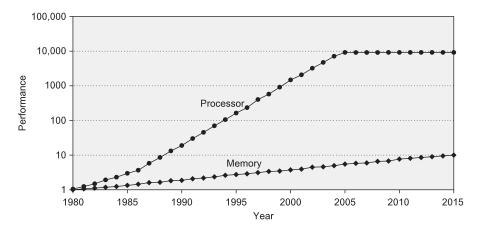

| 1.3  | The gap in performance measured as the difference in the time between            |     |

|      | process memory requests (for a single processor or core) and the latency         |     |

|      | of a DRAM access [9]                                                             | 4   |

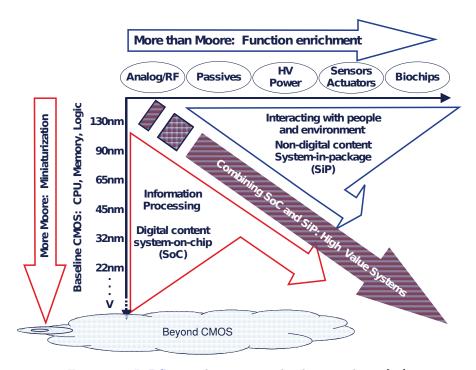

| 1.4  | ITRS nanoelectronics technology roadmap [10]                                     | 5   |

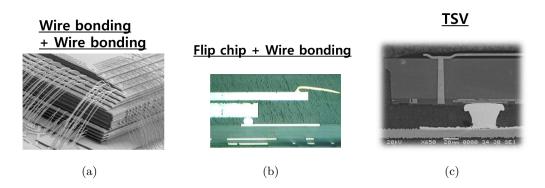

| 1.5  | Various 3D integration paradigms: (a) 3D stacking with wire-bonding, (b)         |     |

|      | 3D stacking with wire-bonding and flip-chip bonding, and (c) 3D stacking         |     |

|      | with TSV. Adapted from [11]                                                      | 5   |

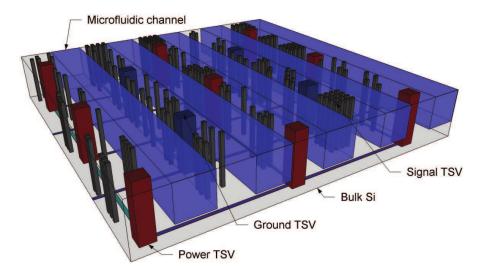

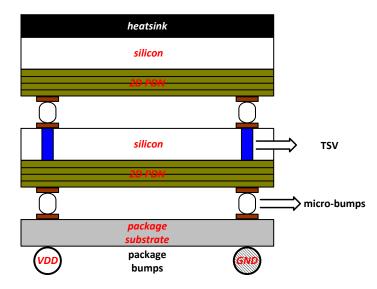

| 1.6  | The structure of 3D IC with P/G and signal TSVs [12]                             | 6   |

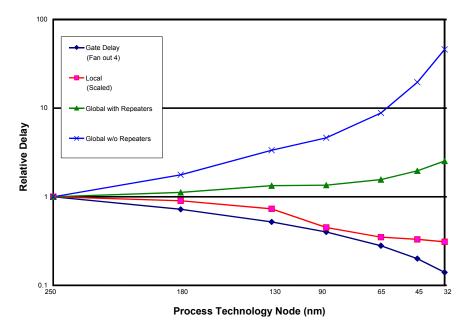

| 1.7  | Relative delay for local and global interconnects and for logic gates in         |     |

|      | sub-micron technology nodes [14]                                                 | 7   |

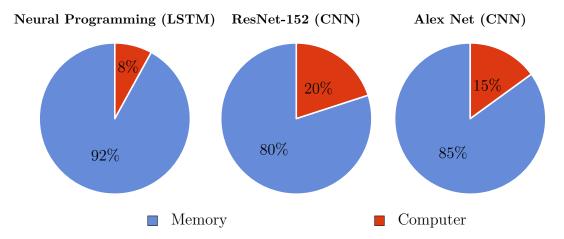

| 1.8  | Comparison of clock cycles spent during computation and in memory                |     |

|      | access for three deep neural network algorithms as run on a machine              |     |

|      | learning accelerator executed in 7 nm CMOS technology. Reproduced                |     |

|      | from data by [17]                                                                | 8   |

| 1.9  | Two-tier 3D IC using face-to-back TSVs                                           | 11  |

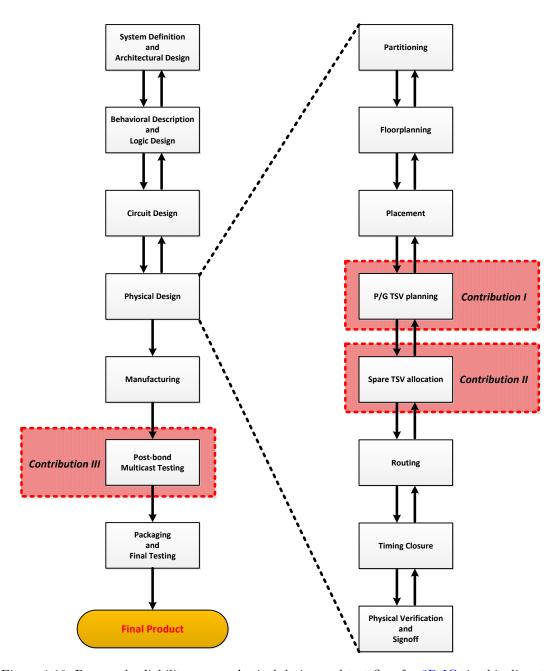

| 1.10 |                                                                                  | 1.0 |

|      | dissertation                                                                     | 13  |

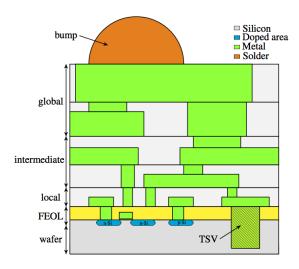

| 2.1  | Classification of interconnects in a 3D system [36]                              | 18  |

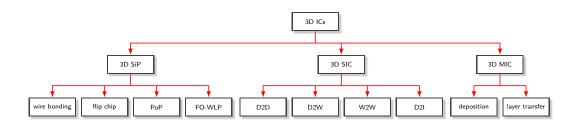

| 2.2  | Classification of 3D integration technologies                                    | 19  |

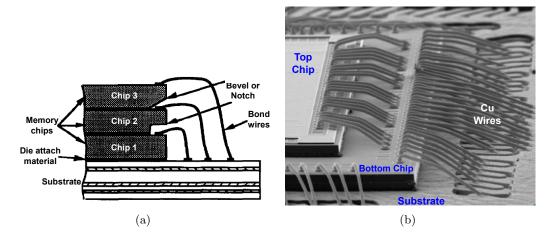

| 2.3  | (a) nCHIP's 3D memory stacked using gold wire-bonding [38] (b)                   |     |

|      | AMKOR's 3D IC packaging stacked by copper wire-bonding [37]                      | 20  |

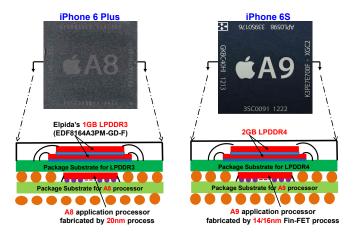

| 2.4  | Top-view and cross-sectional view of the PoP for mobile DRAM and ap-             |     |

|      | plication processor [40]                                                         | 21  |

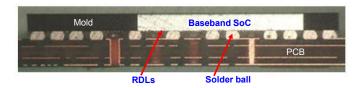

| 2.5  | Cross-sectional view of the eWLB from Infineon [40]                              | 21  |

| 2.6  | Classification of 3D integration according to different stacking ap-             |     |

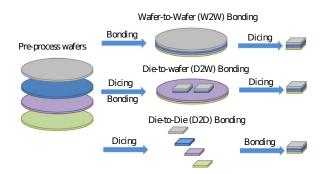

|      | proaches [47]                                                                    | 22  |

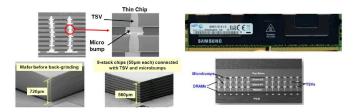

| 2.7  | Samsung's 64 GB DDR4 DRAM module for server farm [40]                            | 23  |

| 2.8  | Micron's sample on HMC [53]                                                      | 24  |

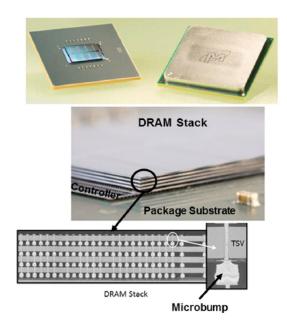

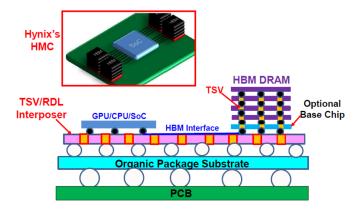

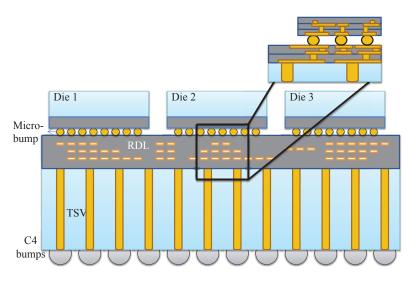

| 2.9  | Schematic of Hynix's HBM                                                         | 25  |

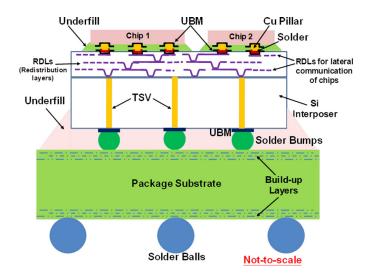

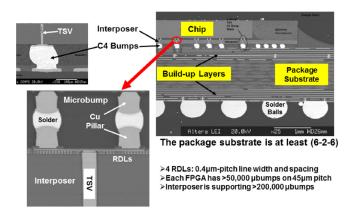

| 2.10 | A passive interposer which consists of TSV and RDL supporting chips on           |     |

|      | package substrate [37]                                                           | 26  |

| 2.11 | ,                                                                                | 26  |

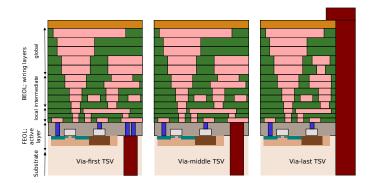

| 2.12 | Illustration of via-first, via-middle, and via-last TSV technology process [62]. | 28  |

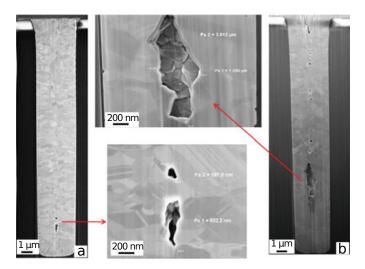

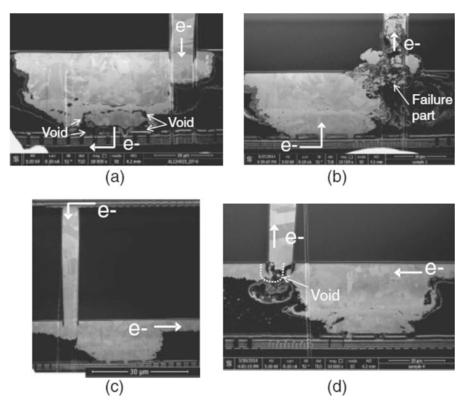

| SEM images of TSVs showing centerline void after annealing at: (a) 150 °C and (b) 300 °C [81]                                                  | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

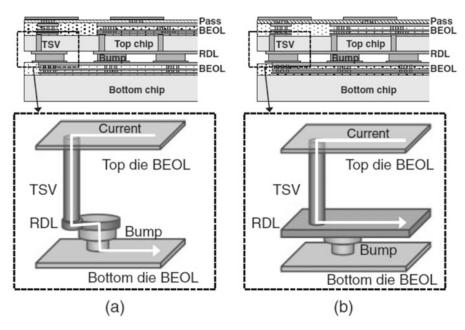

| (b) up-stream current with TSV+BEOL, (c) down-stream current with                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| TSV+RDL, and (d) up-stream current with TSV+RDL [86]                                                                                           | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| with up-stream current, and (g,h) thick line with down-stream current [87].                                                                    | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

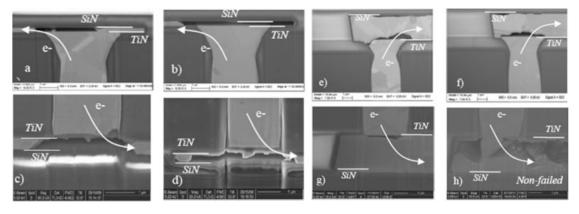

| (a) On-chip power distribution network. (b) Three-dimensional uniform                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| power distribution network                                                                                                                     | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

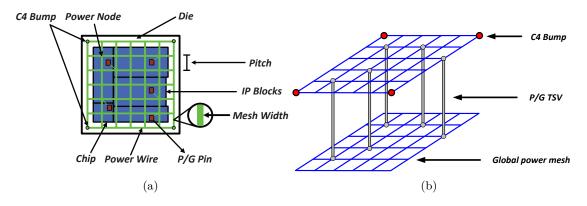

| Illustration of TSV layout parameters                                                                                                          | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

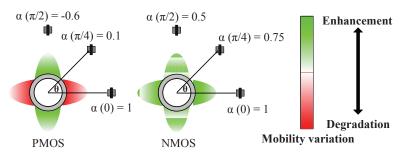

| Carrier mobility variation surrounding TSVs                                                                                                    | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

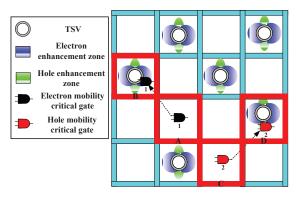

|                                                                                                                                                | 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

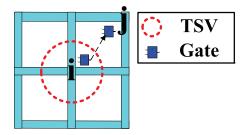

| <u> </u>                                                                                                                                       | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

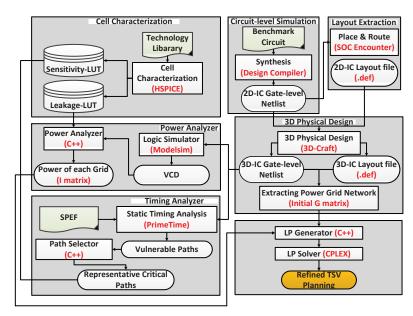

|                                                                                                                                                | 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

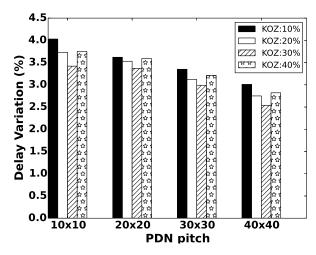

| Impact of KOZ and PDN pitch on induced delay variation                                                                                         | 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

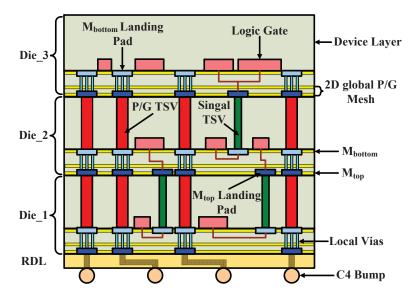

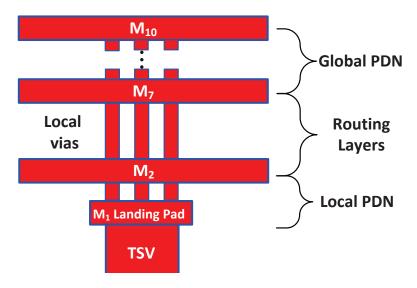

| PDN of 3D ICs with via-first TSVs                                                                                                              | 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

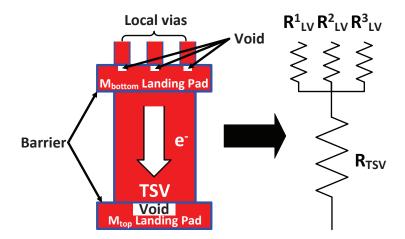

| Illustration of a via-first P/G TSV with local vias and its equivalent re-                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| sistance network                                                                                                                               | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

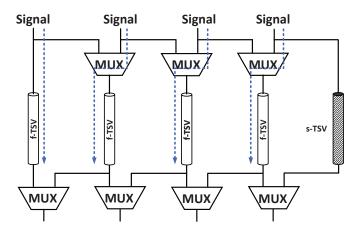

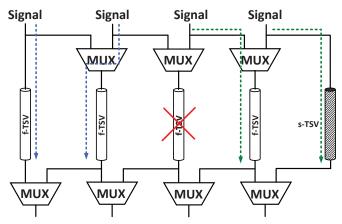

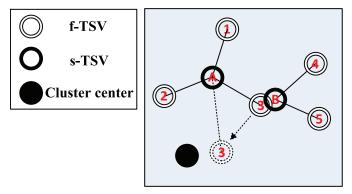

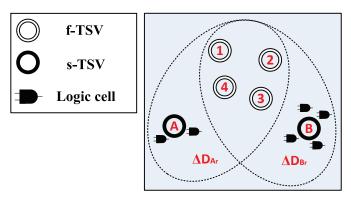

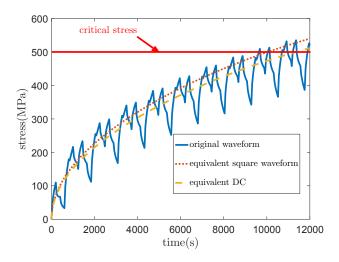

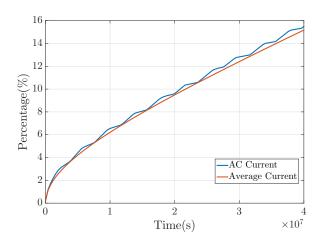

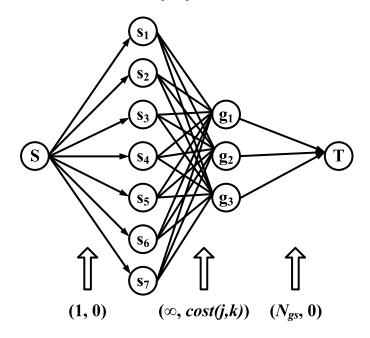

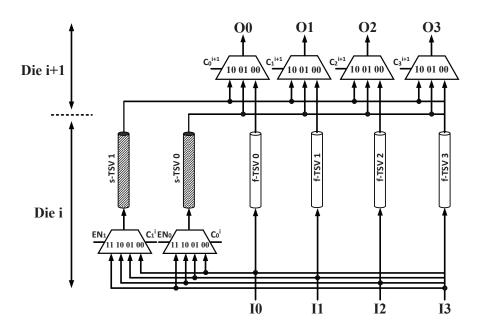

|                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |