# Transparent Memory Extension for Shared GPUs

zur Erlangung des akademischen Grades eines

## **Doktors der Ingenieurwissenschaften**

von der KIT-Fakultät für Informatik des Karlsruher Instituts für Technologie (KIT)

genehmigte

## **Dissertation**

von

## Dipl.-Inform. Jens Kehne

aus Frankfurt am Main

Tag der mündlichen Prüfung: 07.02.2019

Hauptreferent: Prof. Dr. Frank Bellosa

Karlsruher Institut für Technologie

Koreferent: Prof. Dr. Jörg Nolte

**BTU Cottbus**

This document is licensed under a Creative Commons

Attribution-ShareAlike 4.0 International License (CC BY-SA 4.0):

https://creativecommons.org/licenses/by-sa/4.0/deed.en

## **Abstract**

Over the last few years, graphics processing units (GPUs) have become popular in computing. Consequently, all major cloud providers have included GPUs in their platforms. These platforms typically use virtualization to share physical resources between users, which increases the utilization of these resources. Utilization can be increased even further through oversubscription: Since users tend to buy more resources than are actually needed, providers can offer more resources than physically available to their customers, hoping that the customers will not fully utilize the resources that were promised all the time. In case customers do fully utilize their resources, however, the provider must be prepared to keep the customers' applications running even if the customers' resource demands exceed the capacity of the physical resources.

The memory of modern GPUs can be oversubscribed easily since these GPUs support virtual memory not unlike that found in CPUs. Cloud providers can thus grant large virtual address spaces to their customers, only allocating physical memory if a customer actually uses that memory. Shortages of GPU memory can be mitigated by evicting data from GPU memory into the system's main memory. However, evicting data from the GPU is complicated by the asynchronous nature of today's GPUs: Users can submit kernels directly into the command queues of these GPUs, with the GPU handling scheduling and dispatching autonomously. In addition, GPUs assume that all data allocated in GPU memory is accessible at any time, forcefully terminating any GPU kernel that tries to access unavailable data.

Previous work typically circumvented this problem by introducing a software scheduler for GPU kernels which selects the next kernel to execute in software whenever a previous kernel finishes execution. If data from the next kernel's address space has been evicted, the scheduler returns that data to GPU memory before launching the next kernel, evicting data from other applications in the process. The main disadvantage of this approach is that scheduling GPU kernels in software bypasses the GPU's own, highly efficient scheduling and context

switching and therefore induces significant overhead in applications even in the absence of memory pressure.

In this thesis, we present GPUswap, a novel approach to oversubscription of GPU memory which does not require software scheduling of GPU kernels. In contrast to previous work, GPUswap evicts data on memory allocation requests instead of kernel launches: When an application attempts to allocate memory, but there is insufficient GPU memory available, GPUswap evicts data from the GPU into the system's main memory to make room for the allocation request. GPUswap then uses the GPU's virtual memory to map the evicted data directly into the address space of the application owning the data. Since evicted data is thus directly accessible to the application at any time, GPUswap can allow applications to submit kernels directly to the GPU without the need for software scheduling. Consequently, GPUswap does not induce any overhead as long as sufficient GPU memory is available. In addition, GPUswap eliminates unnecessary copying of data: Only evicted data that is actually accessed by a GPU kernel is transferred over the PCIe bus, while previous work indiscriminately copied all data a kernel might access prior to kernel launch. Overall, GPUswap thus delivers consistently higher performance than previous work, regardless of whether or not a sufficient amount of GPU memory is available.

Since accessing evicted data over the PCIe bus nonetheless induces non-trivial overhead, GPUswap should ideally evict rarely-accessed pages first. However, the hardware features commonly used to identify such rarely-accessed pages on the CPU – such as reference bits – are not available in current GPUs. Therefore, we rely on off-line profiling to identify such rarely-accessed pages. In contrast to previous work on GPU memory profiling, which was based on compiler modification, our own profiling uses the GPU's performance monitoring counters to profile the application's GPU kernels transparently. Our profiler is therefore not limited to specific types of application and does not require recompiling of third-party code such as shared libraries. Experiments with our profiler have shown that the number of accesses per page varies mostly between an application's memory buffers, while pages within the same buffer tend to exhibit a similar number of accesses.

Based on the results of our profiling, we examine several possible eviction policies and their viability on current GPUs. We then design a prototype policy which allows application developers to assign a priority to each buffer allocated by the application. Based on these priorities, our policy subsequently decides which buffer's contents to evict first. Our policy does not require hardware features not present in current GPUs, and our evaluation shows that the policy is able to relocate significant amounts of application data to system RAM with minimal overhead.

# **Contents**

| 1 | Intr | oductio | on                              | 1  |

|---|------|---------|---------------------------------|----|

|   | 1.1  | Extend  | ding the GPU Memory             | 2  |

|   | 1.2  |         | butions                         | 5  |

|   | 1.3  | Thesis  | Organization                    | 6  |

| 2 | Bac  | kgroun  | d and Literature Review         | 9  |

|   | 2.1  | Virtua  | l Memory Systems                | 9  |

|   |      | 2.1.1   | Virtual Address Spaces          | 9  |

|   |      | 2.1.2   | Paging                          | 11 |

|   |      | 2.1.3   | Virtual Memory and DMA          | 14 |

|   |      | 2.1.4   | Swapping                        | 15 |

|   | 2.2  | Graph   | ics Processing Units            | 16 |

|   |      | 2.2.1   | Compute Model                   | 16 |

|   |      | 2.2.2   | Command Submission              | 19 |

|   |      | 2.2.3   | Command Processing              | 20 |

|   |      | 2.2.4   | Virtual Memory                  | 21 |

|   |      | 2.2.5   | Performance Monitoring Counters | 24 |

|   | 2.3  | Relate  | d Work                          | 27 |

|   |      | 2.3.1   | GPU Virtualization              | 27 |

|   |      | 2.3.2   | GPU Resource Management         | 34 |

|   | 24   | Summ    | arv                             | 40 |

x Contents

| 3 | An E | viction  | n Mechanism for GPUs                       | 43 |

|---|------|----------|--------------------------------------------|----|

|   | 3.1  | Goals    |                                            | 43 |

|   | 3.2  | Design   | n                                          | 44 |

|   |      | 3.2.1    | Overview                                   | 44 |

|   |      | 3.2.2    | Memory Relocation                          | 46 |

|   |      | 3.2.3    | Returning Data to the GPU                  | 49 |

|   |      | 3.2.4    | Memory Accounting                          | 50 |

|   | 3.3  | Protot   | Type Implementation                        | 51 |

|   |      | 3.3.1    | Driver Integration                         | 51 |

|   |      | 3.3.2    | Memory Relocation                          | 52 |

|   |      | 3.3.3    | Suspending Applications                    | 53 |

|   |      | 3.3.4    | Memory Accounting                          | 56 |

|   |      | 3.3.5    | Limitations                                | 58 |

|   | 3.4  | Discus   |                                            | 59 |

|   |      | 3.4.1    | Generality and Transparency                | 59 |

|   |      | 3.4.2    | Performance                                | 60 |

| 4 | Prof | filing M | lemory Access Patterns of GPU Applications | 63 |

| • | 4.1  | _        | · · · · · · · · · · · · · · · · · · ·      | 63 |

|   | 4.2  |          | n                                          | 64 |

|   |      | 4.2.1    | Overview                                   | 65 |

|   |      | 4.2.2    | Repeating Kernel Runs                      | 67 |

|   |      | 4.2.3    | Separating Pages                           | 70 |

|   | 4.3  |          | Type Implementation                        | 71 |

|   |      | 4.3.1    | Repeating Kernel Runs                      | 72 |

|   |      | 4.3.2    | Separating Pages                           | 72 |

|   |      | 4.3.3    | The Performance Monitoring Counters        | 73 |

|   | 4.4  | •        | ng Results                                 | 74 |

|   |      | 4.4.1    | Profiling Setup                            | 74 |

|   |      | 4.4.2    | Observations                               | 75 |

|   |      | 4.4.3    | Profiling Duration                         | 80 |

|   |      | 4.4.4    | Implications on Policy                     | 83 |

Contents xi

| 5   | Pote  | ential Eviction Policies for GPUs           | 85  |

|-----|-------|---------------------------------------------|-----|

|     | 5.1   | Goals                                       | 85  |

|     | 5.2   | Policy Ideas                                | 86  |

|     |       | 5.2.1 Victim Selection                      | 86  |

|     |       | 5.2.2 Chunk Selection                       | 90  |

|     | 5.3   | Prototype Policy                            | 94  |

|     |       | 5.3.1 Overview                              | 95  |

|     |       | 5.3.2 Priority Assignment                   | 96  |

|     |       | 5.3.3 Passing Priorities to GPUswap         | 97  |

|     |       | 5.3.4 Selecting Chunks for Eviction         | 98  |

|     |       | 5.3.5 Returning Data to the GPU             | 99  |

|     |       |                                             | 100 |

|     | 5.4   | Hardware Wishlist                           | 102 |

| 6   | Perf  | Formance Evaluation of GPU Memory Extension | 105 |

|     | 6.1   |                                             | 105 |

|     | 6.2   |                                             | 107 |

|     | 6.3   |                                             | 114 |

|     |       |                                             | 115 |

|     |       |                                             | 116 |

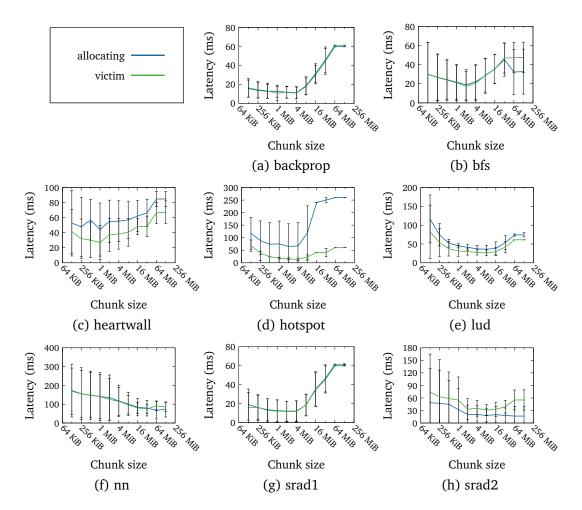

|     | 6.4   | Chunk Size                                  | 121 |

|     | 6.5   |                                             | 125 |

| 7   | Con   | clusion                                     | 127 |

|     | 7.1   | Future Work                                 | 129 |

| De  | utsc  | he Zusammenfassung                          | 131 |

| Lis | st of | Figures                                     | 135 |

| Bi  | bliog | raphy                                       | 137 |

# **Chapter 1**

## Introduction

Graphics processing units (GPUs) have become increasingly popular in computing. The freely-programmable nature of modern GPUs combined with their unprecedented levels of performance and low power consumption make these GPUs a perfect fit for applications like machine learning [1], computer vision [17], cryptography [32], network packet processing [22] and even processing of general web requests [5]. However, despite their obvious benefits, GPU adoption is often hindered by hardware costs: The price for a high-end GPU model can reach five-digit numbers<sup>1</sup>.

An increasingly popular alternative to buying dedicated hardware is to integrate these high-end GPUs into shared environments, such as clouds. Sharing a GPU in this manner allows the cloud provider to increase the GPU's utilization - and thus offer GPU computation time at a lower price – for two reasons: First, applications tend to have a finite execution time. After an application finishes, a customer with exclusive access to a GPU may take a while to start the next application, which forces the GPU to idle. In contrast, a shared GPU can execute multiple applications concurrently and thus does not fall idle if a single application exits. Second, running GPU applications may not fully utilize the GPU's resources: Most applications perform I/O or CPU computation from time to time, during which a dedicated GPU would idle. In contrast, a shared GPU can simply execute code from another application during these periods, which increases utilization. Furthermore, GPU applications may not launch a sufficient number of threads to fully utilize all of the GPU's cores, thus leaving some of these cores unused. In that situation, some GPUs have the ability to execute threads from more than one application in parallel to increase utilization.

Integrating a GPU into a cloud environment, however, requires the cloud provider to efficiently virtualize the GPU, which creates interesting new challenges. GPUs

<sup>&</sup>lt;sup>1</sup> At the time of this writing, the prices for an Nvidia Tesla V100 in German web shops ranged from €8,780.66 to €18,194.99.

were designed to be used exclusively by a single application, and modern-day GPUs inherited the basic design principles of their ancestors. As a result, GPUs are difficult to share between applications – especially if these applications do not cooperate with each other, which is the common case in a cloud environment. While some support for sharing – such as GPU virtual address spaces – has been added in recent years, hardware support for GPU virtualization is still in its infancy.

Virtualizing a GPU in software has been a major focus of research in recent years. These efforts, however, have largely focused on the efficiency of virtualization [18, 21, 56, 62] – i.e., on reducing the virtualization overhead – or on expanding the functionality of virtual GPUs [13, 58, 61, 64, 67] – e.g., on enabling full virtualization. More recently, some research efforts have also considered the problem of achieving fairness between multiple, mutually untrusted GPU applications [38, 44, 54, 58, 61].

A topic that has been mostly overlooked in previous research, however, is how to deal with the memory of a virtualized GPU. As for the GPU's computational power, it is desirable for a cloud provider to oversubscribe that memory to increase its utilization. While this oversubscription can be achieved simply by promising customers a larger amount of memory than is actually available, doing so can easily lead to a shortage of GPU memory if customers actually do allocate all the memory promised to them. On the CPU, this situation is typically handled by swapping data to disk; however, this technique does not apply to current GPUs since these GPUs lack important features – most notably page fault support – that are necessary to implement classical swapping.

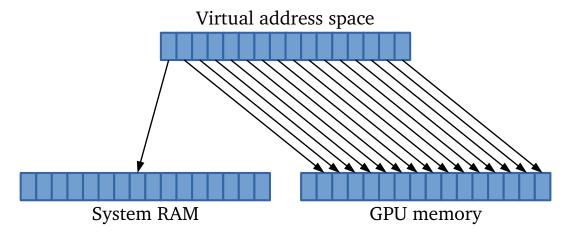

## 1.1 Extending the GPU Memory

One approach to alleviating shortages of GPU memory is to use system RAM in its place. Current GPUs typically have the ability to access system RAM directly. This access is transparent to the applications running on the GPU: The GPU driver can map system RAM into the GPU address space of the application, which the application can then read and write as usual. When the available GPU memory is running low, the operating system can thus prevent applications from failing by transparently allocating system RAM instead of GPU memory. However, each access to system RAM translates to a transaction on the PCIe-bus. Accessing system RAM is therefore significantly slower than accessing GPU RAM: The GDDR5X memory of current GPUs reaches transfer rates of up to 448 GiB/s and latencies of about 10 ns [33], whereas the PCIe-bus limits transfers to and from system RAM to a bandwidth of 16 GiB/s and a latency of several hundred nanoseconds [42]. Therefore, any application using system RAM instead of GPU memory will suffer

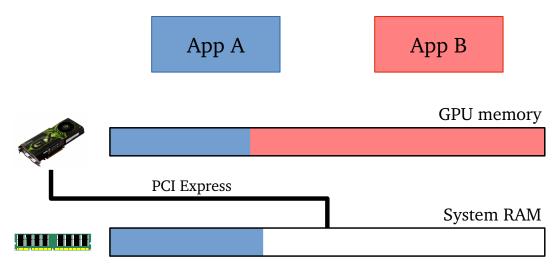

Figure 1.1: Unfairness with first-come-first-served-allocation. Both applications have allocated the same amount of memory. However, application B receives a larger amount of GPU memory simply because it allocated its memory first.

a severe performance hit. However, this performance degradation is arguably preferable to applications failing altogether due to lack of memory.

While a performance penalty is unavoidable when extending GPU memory with system RAM, it is the operating system's task to at least minimize that performance penalty. Specifically, this leads to two main goals for such a system:

- 1. **Utilization:** The system should maintain high utilization of the available GPU memory. Specifically, applications should not have to use system RAM until all GPU memory is exhausted.

- 2. **Fairness:** If using system RAM is unavoidable, applications should still benefit equally from the GPU memory available. Thus, each application should be guaranteed an equal share of the available GPU memory.

The allocation strategies for GPU memory found in most current research projects on GPU virtualization typically fall short on at least one of these goals. In fact, current research largely uses rather simple allocation strategies like first-comefirst-served (FCFS) or static partitioning. In the following, we will examine these allocation strategies in more detail.

#### **First-Come-First-Served Allocation**

FCFS allocation is probably the simplest strategy imaginable: Allocation requests are fulfilled immediately on arrival, without considering any other requests, past or future. Requests are fulfilled from GPU memory when sufficient GPU memory

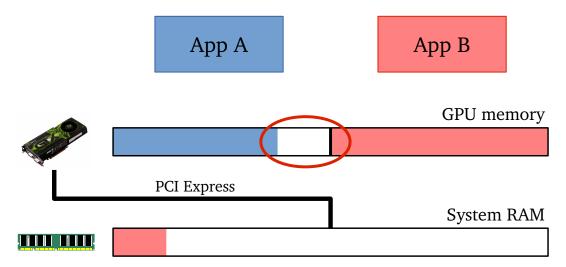

Figure 1.2: Poor utilization with static partitioning. Some GPU memory is reserved for application A. Therefore, application B is forced to use slower system RAM, even though there would be enough free GPU memory available.

is available; if not, system RAM is used instead. This strategy does maintain good utilization – system RAM is never used while GPU memory is available. However, the fact that FCFS only considers requests individually easily leads to unfairness, as illustrated in Figure 1.1: Two applications, A and B, both allocated the same amount of memory. However, application B allocated its memory first, and therefore received only GPU memory, which was abundantly available at the time. When application A allocated the same amount of memory later on, system RAM was used for part of the allocation request because there was not enough GPU memory available. The result is an unfair distribution of GPU memory: Application A must keep some of its data in system RAM and thus suffers performance degradation, whereas application B can keep all its data in the much faster GPU memory.

#### **Static Partitioning**

A seemingly obvious solution for the unfairness problem of FCFS is to statically partition the available GPU memory between applications: For n applications,  $^1/_n$  of the available memory is reserved for each application exclusively. While this scheme achieves good fairness – each application is guaranteed to receive the same share of GPU memory – it also requires the number of applications to be known beforehand. In addition, this scheme can lead to poor utilization if an application does not actually use all of its share, as illustrated in Figure 1.2: Two applications are using the GPU concurrently, with half of the GPU's memory reserved for each application. However, application A uses slightly less memory

1.2 Contributions 5

than it would be entitled to, while application B uses slightly more. As a result, application B is forced to use system RAM – and thus suffers from degraded performance – even though there is still unused GPU memory available.

#### **Swapping**

Besides FCFS and static partitioning, there are some recent research projects taking more sophisticated approaches. Most notably, Gdev [39] and its extension GDM [63] include a swapping mechanism integrated with a software scheduler for GPU kernels: The scheduler decides in software which GPU kernel to launch next, and the swapping mechanism subsequently moves all data that this kernel might need to the GPU – potentially evicting data from other applications in the process – before the kernel is actually launched. While this approach is successful in enabling oversubscription of GPU memory, it also suffers from two fundamental drawbacks: First, scheduling GPU kernels in software can induce considerable overhead in GPU applications even in the absence of memory pressure since it implicitly disables the GPU's internal, highly efficient scheduling and context switching [38]. Second, copying all data a GPU kernel might need prior to kernel launch may lead to unnecessary data transfer if the kernel does not actually need all the copied data.

### 1.2 Contributions

The goal of the work presented in this thesis is to extend GPU memory with system RAM with minimal overhead while maintaining both fairness and high utilization of GPU memory. Specifically, this thesis makes the following contributions:

**Memory extension mechanism for GPUs** We present an extension mechanism for GPU memory, called GPUswap, which transparently extends GPU memory with system RAM without relying on software scheduling of GPU kernels. GPUswap evicts application data from the GPU to system RAM whenever an allocation request cannot be satisfied due to insufficient GPU memory. In contrast to previous work, GPUswap's operation is triggered by allocation requests rather than GPU kernel launches, which has two main advantages: First, GPUswap does not add any overhead to GPU kernel launches. Therefore, GPUswap's overhead is virtually zero in the absence of actual memory pressure. Second, GPUswap keeps the evicted data directly accessible to the application. Therefore, during GPU computation, only data that is actually touched by the application is transferred over the PCIe bus.

**Profiling mechanism for GPU memory accesses** The eviction policy accompanying GPUswap requires information about the applications' memory accesses to operate. Since this information cannot be collected at runtime on current GPUs due to lack of hardware support, we instead develop a memory profiling mechanism which is based on the GPU's performance monitoring counters and GPUswap. Our mechanism offers two main advantages over previous work: First, our mechanism does not assume a specific type of application, but can instead count memory accesses from arbitrary applications. Second, our mechanism is able to gather information about memory regions outside the application's direct control, such as those allocated by the GPU runtime library.

Using our mechanism, we observe that page-level eviction, as done on the CPU, is often not necessary on the GPU since GPU applications display a higher degree of uniformity in their memory accesses due to their data-parallel nature.

**Eviction policy** We present a proof-of-concept policy based on hints generated from profiling of GPU applications to demonstrate the general benefit of an eviction policy for GPUs. In addition, we discuss other possible eviction policies for GPUswap and their applicability to current GPUs. Some of these policies are not actually viable on current GPUs since these GPUs lack many hardware features commonly found in CPUs, such as page faults or reference bits. However, as GPUs are growing ever closer to CPUs in terms of features [59], one of these strategies may well become state of the art in the future. Therefore, we also discuss how the hardware of current GPUs would have to change to enable more efficient eviction policies for GPUs.

**Performance considerations** Finally, we evaluate the overhead induced by both GPUswap and the use of system RAM in general. In case GPU memory is scarce, we analyze the overhead induced by GPUswap's evictions. Using GPUswap, there are two main sources of overhead: i) Copying data between CPU and GPU in response to memory pressure, and ii) frequent accesses to system RAM after data has been swapped out. We quantify both types of overhead, and assess to what extent these overheads can be alleviated by an eviction policy.

## 1.3 Thesis Organization

The remainder of this thesis is organized as follows:

**Chapter 2 – Background and Literature Review** describes the hardware of current GPUs, and how the design of that hardware affects our goal of extending GPU memory with system RAM. In addition, we review related work on GPU virtualization and GPU memory management in this chapter.

**Chapter 3 – An Eviction Mechanism for GPUs** introduces GPUswap, our novel memory extension mechanism for GPUs, which is the main contribution of this thesis. We describe both GPUswap's design and implementation in this chapter.

**Chapter 4 – Profiling Memory Access Patterns of GPU Applications** presents our method for profiling the memory access patterns of GPU applications. We first describe our methodology for measuring GPU memory accesses of GPU applications, which is based on GPUswap. Then, we describe the memory access patterns we observed in several GPU applications, and the implications of these patterns for eviction policies.

**Chapter 5 – Potential Eviction Policies for GPUs** discusses possible eviction strategies and their viability on current GPUs. We also assess how the hardware of current GPUs should be extended for better memory management – i.e., what additional features GPUs would need to enable more efficient eviction decisions. Finally, we present a proof-of-concept policy which works on GPUs that are in use today.

**Chapter 6 – Performance Evaluation of GPU Memory Extension** quantifies the overhead that eviction has on GPU applications. In this chapter, we also use our proof-of-concept policy to assess to what extent the overhead associated with using system RAM in place of GPU memory can be alleviated through an eviction policy. Finally, we show that GPUswap induces no overhead unless actual memory pressure is present.

**Chapter 7 – Conclusion** summarizes the main points of the thesis, as well as the contributions and limitations of the presented work. Finally, we also discuss possible future research directions in this chapter.

## **Chapter 2**

# **Background and Literature Review**

Modern GPUs support paged virtual memory similar to that used on the CPU: Applications are confined to virtual address spaces, and virtual addresses from these spaces are translated to physical addresses by a dedicated MMU via a page table. However, current GPUs are trailing behind CPUs in terms of features: For example, GPUs are only starting to support page faults, and the page tables of current GPUs do not include reference or dirty bits. Therefore, well-known techniques for memory management on the CPU are typically not applicable to GPUs.

## 2.1 Virtual Memory Systems

In the first computer systems, programs were loaded directly into physical memory. With the advent of multiprogramming, however, this approach turned out to be insufficient: Since each physical address can be used by only one program at a time, programmers had to manually ensure that each program – and even multiple concurrent instances of the same program – used different parts of the available memory, which proved to be a cumbersome and error-prone task.

### 2.1.1 Virtual Address Spaces

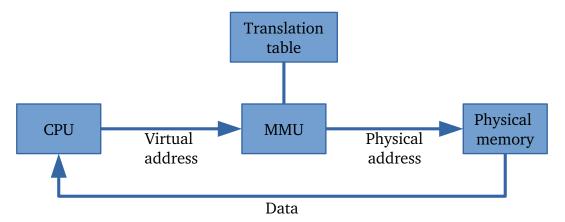

As many other problems in computer science, the problem of multiplexing memory addresses among applications was eventually solved by adding another level of indirection. On today's computers, programs operate exclusively on **virtual addresses**. Whenever a program accesses a virtual address, a dedicated coprocessor, called the **memory management unit (MMU)**, transparently translates this virtual address into a physical address using a translation table, as shown in Figure 2.1. Since each application has its own translation table, different

Figure 2.1: Address translation on current CPUs. Programs running on the CPU access virtual addresses, which the MMU translates into physical addresses using a translation table.

applications are free to use the same virtual addresses. It is the operating system's task to configure each application's translation table appropriately so that each application's data actually resides in a different physical location.

The set of all virtual addresses available to a program forms the program's **virtual address space**. This virtual address space is not conceptually different from the physical address space; its addresses can be used in machine instructions directly just like physical addresses, which any necessary translation being performed transparently by the MMU. However, since the virtual address space is an abstraction of the physical memory, it provides three key benefits over accessing physical memory directly:

- 1. Applications are given the illusion of owning the entire physical memory. Since each application has a dedicated virtual address space, each application is free to access any virtual address, without any danger of overwriting data other than its own.

- 2. Applications are protected from each other. Since each memory access has to go through the MMU and translation table, applications are unable to access physical memory for which no translation exists in their virtual address space. As a result, the operating system can guarantee that applications cannot access each other's data by ensuring that each physical address is mapped in at most one address space. Note that it is also possible to relax this protection by establishing mappings to the same physical address in multiple address spaces, but this is typically done only if explicitly requested by the application.

- 3. Applications need not care about the amount of physical memory available. Instead, they are free to use their entire virtual address space as they see fit; it is the operating system's task to provide appropriate translations

into physical memory. If the applications' demand for memory exceeds the capacity of the physical memory, the operating system must decide how to respond to that condition, for example by terminating one or more applications to free physical memory for use by other applications.

The virtual address space is typically larger than the physical address space. As a consequence, not every virtual address has a corresponding translation to a physical address. Normally, addresses without a translation are not a problem since applications typically do not use their entire virtual address space. However, the operating system must be able to handle accesses to virtual addresses without a translation – typically either by allocating memory at the address that was accessed and restarting the faulting instruction (lazy allocation) or by terminating the program if the operating system determines that the memory access was the result of faulty or malicious application behavior.

#### 2.1.2 Paging

As address spaces can be quite large on current computer systems, providing virtual-to-physical translations for each individual address is infeasible. As a result, paged virtual memory [15] was introduced. With paged virtual memory, the virtual address space is composed of **pages**, which are contiguous and indivisible regions of memory. The size of a page ranges from a few kilobytes to several gigabytes, with the starting address of each page being aligned to the page's size. For example, the x86-64 CPUs in use today typically offer a page size of 4 KiB, but also support **huge pages** of 2 MiB or 1 GiB [2]. Other architectures, like PowerPC, support page sizes of up to 16 GiB [30].

With paged virtual memory, the translation table – which is called the **page table** in this context – specifies a translation for each page. To translate a virtual into a physical address, the MMU uses the page table to map the highest bits of the virtual address to the starting address of a physical page. The remainder of the virtual address is then added to the physical page's starting address to obtain the address of the specific byte to be read or written.

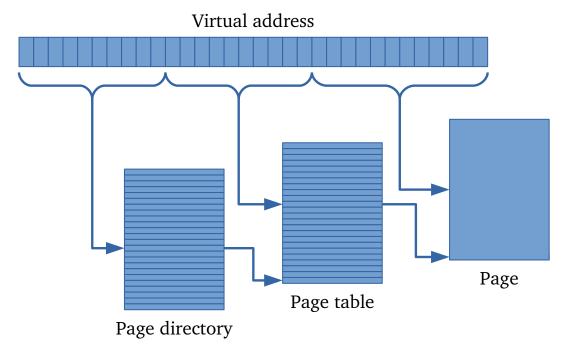

Even though page tables must only store one entry per page, the entire table can still be prohibitively large for large virtual address spaces. For example, a complete page table for a virtual and physical address space of 64 bit and a page size of 4 KiB would be 32 PiB in size. As a result, various schemes have been developed to reduce the size of the page table in memory [31]. On x86 CPUs, for example, page tables consist of multiple levels: The first level, called the **page directory**, contains addresses to second-level page tables, which in turn may hold physical page addresses or addresses of yet another level of page tables. This scheme can be extended to an arbitrary nesting depth – today, three to four levels are commonplace – with only the last level of page tables holding physical page

Figure 2.2: Virtual address translation for a two-level page table and 32-bit virtual addresses, as found in an x86 CPU without physical address extension. The first 10 bits of the virtual address serve as an index into the page directory, yielding the address of the second level page table. The second 10 bits of the virtual address are then used as an index into the second-level page table, which yields the starting address of the physical page. The remaining 12 bits of the virtual address then serve as an index into the physical page.

addresses. The advantage of this design is that only page tables actually in use must be held in memory. Other hardware architectures use different designs, such as **inverted page tables** holding physical-to-virtual address translations, thus scaling with the size of the physical memory rather than that of the virtual address space, **hashed page tables** using a hash of the virtual address to index the table or **software-walked page tables** allowing the operating system to define an arbitrary page table structure. To reduce the cost of resolving virtual-to-physical translations, most architectures also feature a **translation lookaside buffer (TLB)** which caches frequently-used translations.

Figure 2.2 shows the address translation process for a two-level page table and 32 bit addresses. In this example, the MMU uses the first 10 bits of the virtual address as an index into the page directory. The page directory entry at this index holds the starting address of a second-level page table. The next 10 bits of the virtual address are then used as an index into that second-level page table, with the referenced entry holding the starting address of a physical page. The

| 31 | 30 | 29 | 28 | 27  | 26  | 25  | 24  | 23 | 22  | 21 | 20  | 19 | 18 | 17  | 16  | 15 | 14 | 13 | <br> | 10  | - |   | - | - |   | - | _ | - | - |  |

|----|----|----|----|-----|-----|-----|-----|----|-----|----|-----|----|----|-----|-----|----|----|----|------|-----|---|---|---|---|---|---|---|---|---|--|

|    |    |    | 4  | 4 I | KiB | 3-a | lig | ne | d p | hy | sic | al | ad | ldr | ess | 5  |    |    |      | res | G | S | D | Α | С | W | U | R | P |  |

Figure 2.3: Page table entry on 32 bit x86

remaining 12 bits of the virtual address then serve as an index into the physical page, referencing a specific byte to be read or written.

Besides a physical address, a page table entry holds various other information about the physical page it references. As an example, Figure 2.3 shows the format used on 32 bit x86 for both page table and page directory entries. Since pages are 4 KiB in size with each page's starting address aligned to its size, each entry only needs to hold the upper 20 bits of the physical page- or page table address, which leaves 12 bits for additional information. These bits are used for various flags describing the page referenced by the entry:

- **Present (P)** indicates whether this page table entry is currently valid. If this bit is zero, the MMU ignores the remainder of the entry.

- **Read/Write (R)** determines whether the page can be written to. Somewhat counterintuitively, a value of one prevents the page from being written.

- **User (U)** controls if the page is accessible to unprivileged code. If this bit is not set, only the operating system kernel may access the page.

- Write-through (W) controls the cache's behavior for this page. If the bit is set, write-through caching is used for the page. Otherwise, write-back caching is used.

- Cache (C) disables caching for this page altogether if set.

- Accessed (A) is automatically set by the MMU if the page is read from or written to. This bit is also known as the reference bit.

- **Dirty (D)** behaves similar to accessed, but is only set when the page is written to.

- **Size (S)** is only present in page directory entries. If set, it indicates that this page directory entry does not hold the address of a second-level page table, but of a physical page of larger size (often called a huge page). For last-level page tables, this bit is always zero.

- **Global (G)** indicates that this entry should not be removed from the TLB when the TLB is flushed.

When the MMU encounters an entry with the present bit set to zero while translating an address, raises an exception. This exception is called a **page fault**. Page faults are processed by the operating system, which usually handles them in one of two ways: If the faulting address should be valid, the operating system typically responds by making the accessed memory available to the application and then retrying the faulting instruction. This technique is often used in conjunction with

large application buffers to allocate only those parts of the buffer that are actually accessed – a technique called **demand paging**. If, however, the application is not supposed to access the faulting address, the operating system typically reacts by terminating the application since an access to an invalid address is typically caused by either a programming error or malicious application behavior.

#### 2.1.3 Virtual Memory and DMA

Today's computers often include devices which transfer large amounts of data to and from the system's main memory, such as hard disks or network controllers. To speed up these large transfers, these devices typically support **direct memory access (DMA)**, which allows them to access data in the system's main memory autonomously, leaving the CPU free to perform other work. Traditionally, these DMA operations used to operate on physical memory addresses, which without remedy allowed each DMA-enabled device to access any data in memory, including that of other applications or the kernel.

To mitigate this issue, current CPUs include an **input/output memory management unit (IOMMU)** which applies virtual memory to DMA operations. DMA operations now target **bus addresses** instead of physical addresses, and the IOMMU translates these bus addresses to physical addresses using a set of perdevice page tables maintained by the operating system. If a device accesses a bus address for which no page table entry exists, the DMA operation is typically aborted. By setting up the IOMMU's page tables appropriately, the operating system can thus prevent the device from accessing data it is not supposed to access without verifying the target address of each individual DMA request.

More recently, the IOMMUs in both Intel [29] and AMD [3] CPUs have begun to support direct access to I/O devices from user space. To allow user space applications to perform DMA in a safe way, these IOMMUs translate bus addresses to physical addresses in two steps. For **first-level translation**, which is optional, devices can attach an address space identifier to their DMA requests. The IOMMU uses this identifier to select one of several page tables attached to the device, and subsequently uses this page table to translate the bus address to an intermediate address. The page tables used in first-level translation conveniently share the same format as the regular MMU's page table. If the device tags each DMA request with an identifier for the application the request originated from, the IOMMU can thus use the regular MMU's page tables to allow each application to perform DMA using its own virtual addresses. If a device does not support address space identifiers, the IOMMU skips first-level translation altogether.

Once first-level translation is complete, **second-level translation** translates the intermediate address – or the bus address if first-level translation is skipped – to a physical address using another, dedicated page table global to the device.

This translation is transparent to the device, and is unconditionally applied to all DMA requests. Second-level translation is particularly useful in virtualized contexts: The hypervisor can use second-level translation to control which memory is accessible to an entire virtual machine, and subsequently allow that virtual machine to manage first-level translation itself.

#### 2.1.4 Swapping

Since virtual address spaces make applications oblivious to the amount of physical memory available, it is possible for applications to allocate more memory than available. Modern operating systems handle this situation through **swapping**: If a new memory allocation request cannot otherwise be satisfied, the operating system pushes some application data out to secondary storage. To that end, the operating system copies a set of pages – not necessarily from the allocating application's address space – to another storage device – typically a hard disk or SSD. Once copying is complete, the operating system clears the present bit in the page table entries pointing to the swapped pages, and stores the location of each page in secondary storage – e.g., a block number on the hard disk – in the remainder of the page's page table entry. Once that process is complete, the operating system can use the swapped physical pages to fulfill the outstanding allocation request.

Since data that has been swapped to secondary storage is not directly accessible to the application, the operating system must be able to return swapped pages to physical memory if the application accesses those pages. When the application accesses a swapped page, the MMU raises a page fault since the present bit of swapped pages is set to zero. The page fault handler then reads the location of the swapped page from the page table entry – the rest of which the MMU conveniently ignores after reading the present bit – copies the content of the swapped page from secondary storage to a physical page, and updates the page table entry to point to the new location of the data in memory. If memory is still contended, the page fault handler may have to swap another page in the process to make room for the page the application tried to access.

When an operating system practices this kind of swapping, finding the right pages to swap to secondary storage is a major problem [60]: Both pushing pages out to secondary storage and getting them back into RAM induces significant latency. Swapping frequently-accessed pages can therefore lead to significant overhead. When memory pressure occurs, the operating system must therefore find rarely-accessed pages to swap to preserve application performance. Current MMUs typically provide tools to aid the operating system in this task – the most common such tool is the reference bit described in Section 2.1.2. Based on these tools, various algorithms are available for selecting appropriate pages [60].

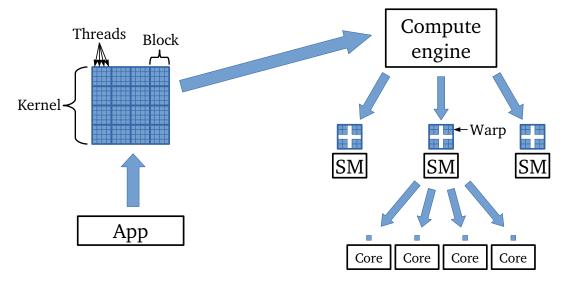

Figure 2.4: The compute model of contemporary GPUs. The application launches kernels consisting of a large number of threads grouped in thread blocks. The kernel is sent to the GPU's compute engine, which schedules each block to run on a streaming multiprocessor (SM) with free capacity. The SMs internally divide each block into warps, and then execute the threads in each warp on their compute cores in a single instruction, multiple thread (SIMT) fashion. Though not shown in the figure for simplicity, SMs may execute multiple blocks concurrently, and the cores interleave between threads of different warps with instruction granularity.

## 2.2 Graphics Processing Units

GPUs can be used for various purposes other than rendering graphics. In fact, current GPUs are small many-core computer systems capable of executing arbitrary code. Due to their massively-parallel nature, these GPUs can deliver tremendous levels of performance for applications that can be parallelized to a sufficient degree. As a result, the use of GPUs is growing ever more widespread, and GPUs have long found their way into the computers in present-day datacenters, even though these computers typically have no screens attached.

### 2.2.1 Compute Model

Today's GPUs function as asynchronous accelerators: Applications submit multithreaded programs called **kernels** to the GPU and are then free to perform other work, while the GPU processes these kernels autonomously. For each kernel, the application can optionally ask to be notified once the kernel has finished execution. Data transfers between CPU and GPU over the PCIe bus are typically expensive – sometimes even more expensive than the GPU computation itself. For best performance, GPU applications should therefore perform as much work as possible on the GPU between data transfers [47, Section 5.3.1]. As a consequence, applications using the GPU often execute in cycles: The application first copies data to the GPU, then executes one or more GPU kernels, and finally copies the result of the GPU computation back into system RAM.

GPU kernels consist of many **threads** which process the kernel's input in parallel. These threads are light-weight compared to CPU threads, and each GPU thread typically performs much less work than a typical CPU thread. For a typical matrix multiplication, for example, each GPU thread computes just one element of the result matrix. Since GPUs often have hundreds of compute cores, this fine-grained parallelization is necessary to fully utilize the GPU's resources.

Figure 2.4 illustrates the compute model used by current GPUs. Application developers must group the threads of each kernel into **thread blocks**. When the kernel is started, the GPU's compute engine then assigns each of these blocks to one of the GPU's **streaming multiprocessors** (SM). Each thread block is executed by exactly one SM – which allows threads in a block to share the SM's resources – but one SM may execute threads from multiple blocks concurrently. The latest generation of Nvidia GPUs features 80 SMs composed of 64 individual cores each [50].

Internally, the SMs subdivide each block into warps. A warp typically consists of 32 threads, but smaller warps may exist if the number of threads in a block is not an exact multiple of the warp size. Threads within a warp use a single instruction, multiple thread (SIMT) execution model [43]: In each cycle, all threads in the warp execute the same instruction, though possibly with different parameters. To load data from memory, for example, all threads in the warp must simultaneously execute a load instruction, but each thread may load a word from a different address. Different warps can execute independently on the same SM, and SMs with a sufficient number of cores can execute multiple warps in parallel. An SM-internal warp scheduler multiplexes the SM's cores among all active warps with instruction granularity. In principle, the SMs can thus execute an instruction from a different warp in each cycle, which allows the warp scheduler to hide memory latency by switching to a different warp after issuing a load instruction. The scheduler also offers a low-overhead barrier synchronization primitive to allow for coordination between warps.

Using a SIMT model greatly simplifies the SMs' design – for example, threads within a warp can share the same instruction decoder. However, this model can also lead to severe performance degradation if the control flow diverges within a warp: If multiple threads in the same warp execute different sides of a branch, the SM must execute both sides of the branch sequentially, discarding the result of

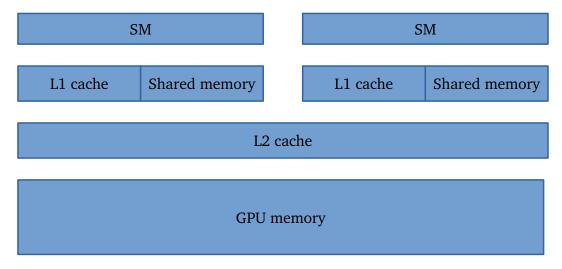

Figure 2.5: The cache hierarchy found in current GPUs. Each streaming multiprocessor (SM) includes its own L1 cache and shared memory, both of which are backed by the same physical memory. The L1 cache is transparent to the application, whereas the shared memory is a scratchpad managed explicitly by the threads running on the SM. In addition, the GPU includes an L2 cache which is shared between all SMs.

one side in each thread. To achieve good performance, developers must therefore carefully structure the code of their GPU applications to fit the GPU's compute model.

Each SM typically includes a large register file, which can be several kilobytes in size. Local variables of GPU threads are thus stored mostly in registers, but can be spilled to a stack in GPU memory if there is insufficient space in the register file. In addition, each SM includes an L1 cache and several kilobytes of **shared memory**. This shared memory serves as a scratchpad shared between all threads in a block which is accessible at the same speed as the L1 cache<sup>1</sup>. Finally, the GPU includes an L2 cache which is shared between all SMs. The entire cache hierarchy is depicted in Figure 2.5.

Nvidia recommends that data local to a thread block should be placed in shared memory whenever possible [47, Section 3.2.3]. Thread blocks therefore often repeat the application's GPU execution cycle: GPU threads copy data from GPU memory into shared memory, perform as much computation as possible on that data, and copy the result of the computation back into GPU memory.

<sup>&</sup>lt;sup>1</sup> In fact, L1 cache and shared memory are backed by the same physical memory, which is partitioned between the two by the GPU's firmware. The tradeoff can be set at runtime using the CUDA runtime API function cudaDeviceSetCacheConfig.

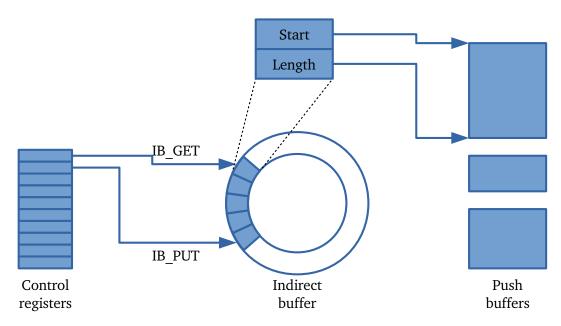

Figure 2.6: A GPU command submission channel. After writing a block of commands into the push buffer, the application places a descriptor item containing the starting address and length of the block in the indirect buffer. Then, the application updates the control register IB\_PUT to inform the GPU that new commands have been submitted. IB\_GET is updated by the GPU after fetching a block of commands.

#### 2.2.2 Command Submission

Current GPUs communicate with the applications using them through in-memory data structures which Nvidia calls **command submission channels**. Modern Nvidia GPUs support multiple such channels, while some Intel and AMD GPUs are limited to one. Command submission channels are used to submit a stream of high-level commands – like "launch kernel" or "start DMA transfer" – to the GPU for execution. Note that these channels do not contain the actual code of the GPU kernels. Instead, kernel launch commands specify the address of a kernel's code in GPU memory.

The basic structure of a command submission channel is depicted in Figure 2.6. Each channel consists of a ring buffer – dubbed the **indirect buffer (IB)** – and a set of device registers [14]. Inside that register set, two particular registers – called IB\_GET and IB\_PUT – specify which parts of the indirect buffer currently contain valid entries. Specifically, IB\_GET points to the head of the queue – i.e., the end of the queue the GPU *gets* entries from – while IB\_PUT points to the tail – i.e., the end where new entries are *put*.

The entries of the indirect buffer are themselves pointers to **push buffers (PB)**, which in turn contain the actual commands. Each IB entry contains the starting

address and length of a single PB, while a PB contains a block of commands that logically belong together. A kernel launch, which actually requires a sequence of multiple commands, is thus represented by a single IB item. Although PBs can be stored at arbitrary locations in GPU memory, GPU drivers typically implement the PBs as another ring buffer to facilitate memory management.

The command submission channels found in Nvidia's GPUs can be mapped directly into the CPU address space of an application. Since these GPUs support multiple channels, each application can be given a dedicated channel. The application can then submit commands to the GPU by writing these commands into the push buffer, appending an item referencing these commands to the end of the indirect buffer, and then setting IB\_PUT to point to the newly added IB item. IB\_PUT, being a device register, doubles as a doorbell, informing the GPU that a new set of commands has been submitted. The main advantage of mapping channels directly into the application's address space is that applications need not enter the kernel to submit commands to the GPU. This approach therefore reduces the overhead of command submission considerably. At the time of this writing, Nvidia's binary GPU driver and the open-source PathScale Nvidia Graphics Driver (pscnv) [53] implement command submission this way, whereas the Nouveau driver [65] still requires applications to call into the kernel to submit commands.

#### 2.2.3 Command Processing

The GPU includes several **engines** which process the commands submitted by the applications [14]. Three of these engines are relevant in the context of this thesis: **PFIFO** which implements the GPU's internal scheduling and context switching, **PCOPY** which handles asynchronous DMA, and **PGRAPH** which can execute arbitrary code and thus handles all CUDA kernels. Besides these three engines, the GPU also includes a number of engines for specialized tasks, such as video encoding and decoding. Since these engines are not relevant in the context of this thesis, we omit detailed descriptions here for brevity. In general, applications can choose which engine should execute a given command – however, not all commands can be executed on each engine, and submitting a command to an incompatible engine results in an error.

The PFIFO engine implements the GPU's internal scheduler and is thus the first to process every new command. In essence, PFIFO executes a loop consisting of four steps: i) fetch a single entry from one of the GPU's indirect buffers, ii) read the corresponding commands in the push buffer, iii) forward these commands to one of the other engines for processing, and iv) switch to the next indirect buffer. Since a set of commands referenced by a single IB entry typically represents a high-level command from the application – e.g., a GPU kernel launch – PFIFO thus implements simple round-robin scheduling of GPU kernels. The main advantage of this scheme is that the scheduling latency is completely hidden: Fetching

commands and switching to the next channel takes place while the previous kernel is still executing in a different engine.

PFIFO typically forwards CUDA kernels to PGRAPH for processing. PGRAPH is a general-purpose engine capable of executing arbitrary code on the GPU's SMs, and thus the only engine capable of executing CUDA kernels. However, PGRAPH is also capable of performing other tasks, such as DMA. This feature is often used when synchronous DMA is desired: Since each engine can only execute one command at a time, executing a DMA operation on PGRAPH ensures that the next kernel does not start before the DMA operation completes. For asynchronous DMA, a dedicated engine named (PCOPY) is available: Since different engines can execute commands in parallel, PCOPY allows the GPU to perform a DMA operation while a GPU kernel is running.

Since the GPU's engines operate asynchronously to the CPU, GPU commands are typically processed without any interaction with the application that submitted the commands. In some cases, however, the application may need to know whether one of its GPU kernels has finished execution. Polling IB GET is insufficient in that case since PFIFO advances IB\_GET immediately after fetching the last command in a block, and thus before this commands has been processed by one of the other engines. Instead, the GPU offers a special fence command which the application can submit to one of its command submission channels. This fence command takes a memory address and a value as parameters, prompting the engine executing the command – which can be any engine – to write the value to the memory address. Since each engine processes only one command at a time and commands from the same command submission channel are processed in order, execution of a fence command guarantees that all preceding commands from the same channel and targeting the same engine have finished execution. The application can thus wait for a command to complete by writing a fence command to one of its channels and subsequently polling the memory location passed to the command. In case polling is undesirable, the application can optionally pass a third parameter to the fence command, prompting the GPU to raise an interrupt upon executing the command. The GPU driver typically offers a corresponding system call which blocks until this interrupt is received. In case multiple fence commands are outstanding, the application can then read the memory addresses passed to all of its outstanding fence commands to determine which one was executed.

### 2.2.4 Virtual Memory

Modern GPUs support virtual memory similar to that found on the CPU. Each application using the GPU is confined to a dedicated virtual address space on the GPU. This confinement is implemented by attaching the application's command submission channels to the application's address space at creation time. GPU kernels launched via a given channel can then only access memory from the

| 31                | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21  | 20  | 19 | 18 | 17  | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------------------|----|----|----|----|----|----|----|----|----|-----|-----|----|----|-----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

|                   |    |    |    |    |    |    |    |    |    |     |     | A  | dd | res | SS |    |    |    |    |    |    |   |   |   |   |   |   | Е | R | S | P |

| U Compression tag |    |    |    |    |    |    |    |    |    | Sto | ora | ge | ty | рe  |    | U  | Ta | rg | U  |    |    |   |   |   |   |   |   |   |   |   |   |

Figure 2.7: Page table entry of an Nvidia Fermi GPU

address space attached to that channel. The GPU's virtual address spaces are essential for allowing applications to submit GPU kernels without operating system intervention: Once address spaces are set up, there is no need for the operating system to examine each command submitted to the GPU since the GPU can autonomously ensure that applications cannot access each other's memory.

As on the CPU, the GPU's address spaces are composed of pages. Current Nvidia GPUs support two distinct page sizes: **Small pages** of 4 KiB and **large pages** of 128 KiB [14]. Whenever a GPU kernel accesses a virtual memory address, a dedicated MMU translates that virtual address to a physical address using a page table set up by the GPU driver. The process of translating virtual to physical addresses is similar to that described in Section 2.1.2.

The page table of a recent Nvidia GPU consists of two levels. The top level consists of a page directory which is 64 KiB in size, stored in 16 contiguous pages in physical GPU memory. Each entry in this page directory is 64 bits long and holds pointers to two distinct second-level page tables: A **small page table** which contains translations for small pages, and a **large page table** containing translations for large pages. Each page directory entry contains pointers to both of these page tables, allowing the driver to mix small and large pages within the memory region covered by a single page directory entry. The driver can also mark either page table as not present if only one page size is required within a page directory entry's memory region, or both if a region is not in use at all. A given virtual address is considered valid if either second-level page table is present and contains a valid mapping for that address; if both page tables contain a valid mapping, the large page table takes precedence.

Each of the GPU's second-level page tables covers 128 MiB of virtual address space, holding a physical address for each virtual page within that region. Since the small and large page tables use different page sizes, the page tables themselves are different in size to cover the same region of memory: Each large page table is 8 KiB long, while each small page table occupies 256 KiB. Like the page directory, both types of page table are stored in contiguous physical pages.

Figure 2.7 shows the entry format used by an Nvidia Fermi GPU for both the large and the small page table. The most important field in each page table entry is the address field, which holds the upper 28 bits of a physical address; for the large page table, the lower 5 bits of this field are always zero. During address translation, the MMU replaces the upper bits of a translated virtual address with the contents of this address field while leaving the lower 12 bits unchanged to

obtain the corresponding physical address. Note that both virtual and physical address space of current GPUs are only 40 bits wide.

The field labeled *Targ* is particularly relevant in the context of this thesis. This field controls which memory – GPU memory or system RAM – the physical address in the address field is located in. Specifically, three values are possible for this field:

- VRAM indicates that the physical address is located in the GPU's internal memory.

- SYSRAM\_NO\_SNOOP indicates that the physical address is located in system RAM. Whenever an address corresponding to this page table entry is accessed, the GPU performs a DMA transaction using the translated physical address as a PCIe bus address. This bus address may be further translated by the host system's IOMMU.

- SYSRAM behaves like SYSRAM\_NO\_SNOOR, but enables cache coherence between CPU and GPU. When the GPU issues a write operation over the PCIe bus, all entries in the CPU's cache which correspond to the operation's target address are invalidated. This mode is useful if the same physical memory is mapped into both a CPU and a GPU address space, which is sometimes used to exchange data between CPU and GPU.

It is important to note that code executing on the GPU is oblivious to the type of physical memory backing its virtual address space. If the driver maps system RAM in place of GPU memory into a GPU address space, accessing this system RAM is thus completely transparent to the application.

Besides the two fields described above, various other fields exist in each page table entry:

- **Present (P)** indicates whether this page table entry is currently valid. If this bit is zero, the MMU ignores the remainder of the entry.

- **Supervisor (S)** indicates whether regular GPU operations from applications can access the memory referenced by this page table entry. If set to 1, only code executing in a special supervisor mode which is only available to the GPU driver can access this page.

- **Read-only (R)** determines whether the page can be written to. A value of one prevents the page from being written.

- **Encrypted (E)** determines whether the contents of this page are transparently encrypted by the GPU. This encryption is useful if GPU data is stored in system RAM but should not be accessed by the CPU.

- **Storage Type** allows the driver to choose between linear addressing and various tiling modes used primarily in graphics contexts.

- **Compression Tag** is used in conjunction with texture compression.

In addition, Figure 2.7 includes some fields labeled "U". While these fields are in use on current GPUs, their exact meaning is currently not publically known.

While GPUs do support several memory-related features not commonly found in CPUs - such as transparent encryption or texture compression - they also lack a number of features that are commonly taken for granted on the CPU. For example, the GPU's page tables do not contain the reference and dirty bits found in CPU page tables. Neither the GPU nor the GPU's driver can thus determine which of the GPU's memory pages are accessed frequently. In addition, most GPUs currently in use do not support transparent page faults as found on the CPU. Instead, these GPUs treat an access to a page for which no page table entry exists as a fatal error, forcefully aborting the GPU kernel the access originated from and raising an interrupt to the GPU driver. Although the driver could update the GPU's page table in response to that interrupt, current GPUs do not support restarting a kernel where it was interrupted – typically, it is not even possible to restart a kernel from the beginning since that kernel may have changed the contents of the GPU's memory before it was aborted, making the result of a repeated execution unpredictable. Due to these restrictions, the most common techniques for memory management - most notably demand paging and swapping of data to secondary storage – cannot be used on current GPUs.

More recently, however, these restrictions of GPU hardware have been diminishing: The Pascal generation of Nvidia GPUs includes limited page fault support [49]. Upon encountering a page fault, these GPUs are able to stop the faulting GPU kernel and raise an interrupt. The fault is then handled in the GPU driver, typically by adding a mapping to the faulting application's GPU page tables and signalling the GPU to resume the faulting kernel's execution. However, details about this process are not publicly known since no documentation on the hardware of current GPUs is available. Therefore, page fault support is currently only available in Nvidia's proprietary driver, but not in any of the open-source GPU drivers currently available.

### 2.2.5 Performance Monitoring Counters

Programming on current GPUs often requires extensive tuning to achieve maximum performance. To assist these tuning efforts, current Nvidia GPUs feature a set of performance monitoring counters. Although these counters can monitor a variety of events from all parts of the GPU, they also come with one significant limitation: Due to the hardware structure of the performance monitoring counters, it is often impossible to count multiple related events simultaneously – for example, read and write accesses to memory cannot be counted at the same time. Nvidia's own profiling tools work around this problem by executing each GPU kernel launched by the profiled application multiple times on the same input, counting one event in each repetition.

On Nvidia GPUs, the performance monitoring counters are grouped together in a dedicated engine named **PCOUNTER** [14]. Handling the performance monitoring counters is the only task of PCOUNTER; specifically, PCOUNTER never executes any code.

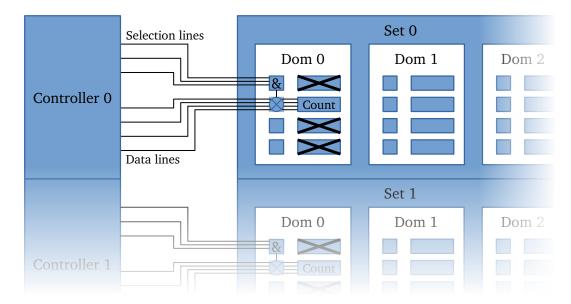

PCOUNTER is internally divided into **domain sets**. Most sets are connected to either a partition of the GPU's SMs or one of the GPU's memory controllers, the only exception being one dedicated set handling events related to neither computation nor memory. As a consequence, each set sees events from only a portion of the GPU – in particular, memory accesses are spread across multiple sets since the GPU interleaves these accesses across all memory controllers for increased performance. To capture all events of a certain type for the entire GPU, it is therefore necessary to use counters from all sets, summing up the counters' results after the profiled GPU kernel finishes execution.

Each domain set is further divided into eight **domains**. Each of these domains is connected to a set of 256 **signal lines**. Each signal line is associated with a specific event – such as the completion of an instruction – or state – such as whether or not a certain engine is currently busy or idle. To support more than 256 distinct signals, most signal lines are connected to only one domain per set. In addition to the signal lines, there are some lines connecting the domains, allowing an output of one domain to serve as input for another.

Each domain contains four **counters** operating on a shared clock. On each clock tick, each of these counters can sample up to four of the domain's signal lines. The counter combines these four lines using a freely-configurable **logic function**, increasing its count in each clock tick if this logic function yields true. Combining multiple signal lines in this way is often necessary since usable events are typically composed of more than one signal.

Even though each domain includes multiple counters, it is often impossible to count multiple related events concurrently since the domains feature different **operating modes**, some of which require multiple counters to work in tandem. In the simplest operating mode, each of the four counters of a domain independently counts events from its configured signal lines. In another mode, it is possible to start the actual counting only after a certain number of events of a certain type have occurred. To that end, one of the four counters counts down from a configured value, enabling another counter once the value of the first counter reaches zero.

Some events – such as memory accesses, which are always performed by all threads in a warp – can occur multiple times per clock tick. For such events, the GPU's engines have the ability to submit an integer value for each clock tick using multiple signal lines, with each line representing one bit of the total number. Conversely, the performance monitoring counters have an operating mode which sums up these integers: Instead of using the logic function, the counter interprets

Figure 2.8: Counting memory accesses using the GPU's performance monitoring counters. Each of the GPU's memory controllers periodically transmits a four-bit number for each type of access using four signal lines (called data lines in the figure). The type of access is indicated by three more signal lines, called selection lines in the figure. PCOUNTER uses two counters from the first domain in each set to interpret these signals: The logic function of the first counter is connected to the selection lines, while the second counter sums up the values carried by the data lines whenever the first counter's logic function yields true. Note that only the first domain in each set is connected to the lines required for counting memory accesses, and that only the first two counters in that domain can be used with this type of signal.

its four input signal lines as a four-bit integer and adds the integer's value to its count in each clock tick. On the downside, however, these modes can use only one counter of each domain. Each domain can thus account for only one such event at the same time, which can occur up to 15 times per clock tick.

To reduce the number of signal lines required for such multi-line events, the GPU multiplexes some four-bit signals among multiple events as shown in Figure 2.8. For these events – which include memory accesses – the four signal lines carry a count for a different event in each clock tick, which yet other signal lines indicating the meaning of the current value. Another special operating mode exists to interpret this type of signal. In this mode, two of the four counters in a domain work in tandem while the remaining two counters remain unused: The first counter is used to configure which events should be counted, while the second one sums up the values for these events. To count read accesses to system

2.3 Related Work 27

RAM, for example, the first counter is configured to combine three signal lines – one corresponding to memory accesses in general, one denoting a read access, and one indicating a PCIe bus transaction – using a simple, three-way logical and function. The second counter then adds a four-bit value to its internal count whenever the first counter's logic function yields true.

Although this scheme is quite complex, it also offers great flexibility. If, for example, the sum of both read and write accesses to system RAM should be counted, the only change required to the scheme described above would be to omit the read access line from the first counter. Although the domain still sees read and write accesses as distinct events in that case, the first counter's logic function would yield true for both events, causing the second counter to sum up both counts as desired. On the downside, however, all complex operating modes can only count one type of event at a time even if some of the domains' counters remain unused. As a consequence, separate counts for read and write accesses cannot be obtained in parallel since both are only countable by one domain of each set.

To enable convenient access to the GPU's performance monitoring counters, Nvidia provides an API named the **CUDA Profiling Tools Interface (CUPTI)** [48]. CUPTI provides a library interface to monitor both the GPU's performance monitoring counters and the CUDA operations (e.g., kernel launches or memory copy operations) issued by applications. CUPTI is intended as a tool to build more sophisticated profiling tools for GPUs – in fact, Nvidia's own profiling tools for GPUs are built on top of CUPTI. However, it is also possible for an application to profile itself by using CUPTI functionality. Most of our own knowledge about GPU performance monitoring counters was obtained by tracing GPU register accesses of such CUPTI-enabled applications.

### 2.3 Related Work

In this section, we review past research efforts relevant to this thesis. We discuss techniques for GPU virtualization – which must multiplex memory between multiple VMs – in Section 2.3.1, followed by a discussion of more general techniques for memory management on current GPUs in Section 2.3.2.

### 2.3.1 GPU Virtualization

Previous work on GPU virtualization largely falls into one of four categories [11]: Fixed passthrough, API remoting, device emulation, or mediated passthrough. In this section, we first describe these categories in general, before discussing specific research projects in more detail.

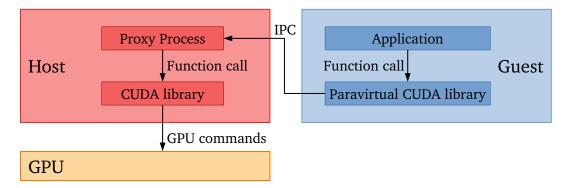

Figure 2.9: Basic principle of API remoting. The guest application calls the function of a paravirtual CUDA library. This library forwards the calls to a proxy process in the host, which executes the call on the application's behalf.

### **Fixed Passthrough**

Fixed passthrough is a simple yet efficient method of virtualizing PCI and PCIe devices: The hypervisor maps the device's memory-mapped I/O registers into the guest-physical address space of the VM. The VM can then access these registers directly, without further intervention from the hypervisor. Fixed passthrough therefore allows the VM to access the device at native speed. On the downside, however, this approach requires that the device is given to a single virtual machine exclusively since fixed passthrough offers no way of coordinating multiple VMs accessing the same device.

To mitigate this issue, **single-root I/O virtualization (SR-IOV)** [10] was introduced. Devices supporting SR-IOV can be split into multiple virtual devices called **virtual functions**. To applications, these virtual functions appear identical to the original device, and each virtual function can be safely passed through to a different VM. Support for SR-IOV is found in many server-grade network adapters, but we are not aware of any GPUs supporting this feature.

### **API Remoting**

The basic principle of API remoting is shown in Figure 2.9. To implement API remoting, applications running inside a virtual machine are linked with a paravirtual GPU runtime library. This library implements the same interface as the real runtime library in the host – e.g., CUDA, OpenCL or OpenGL – and is thus indistinguishable from the real runtime library to the application. Instead of implementing the functionality of the original runtime library, however, the paravirtual library forwards all calls to a proxy process running in the host system, typically using some kind of IPC or RPC mechanism. Each application is associated with a separate proxy process which encapsulates all GPU state associated

with the application; isolation between applications is then implemented by the operating system and GPU driver in the host. The proxy process executes the forwarded calls on the application's behalf by calling into the real runtime library, and sends the result of the call back to the paravirtual library, which returns it to the application.

The main advantage of API remoting is its ease of implementation: Since the proxy process simply calls into the real runtime library, no special knowledge about the inner workings of the GPU is required. However, this approach is also highly inflexible: Each implementation is tied closely to the runtime library in use. Consequently, an entirely new implementation must be created to support a new runtime library. In addition, API remoting requires a large amount of communication between the application and its proxy process. Since this communication crosses VM boundaries, API remoting tends to induce high overhead in applications.

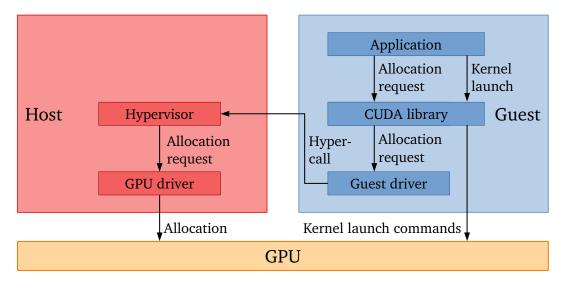

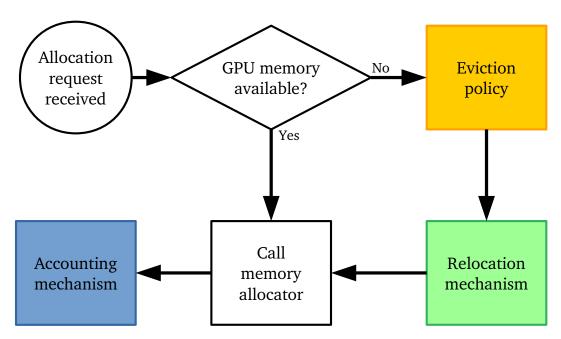

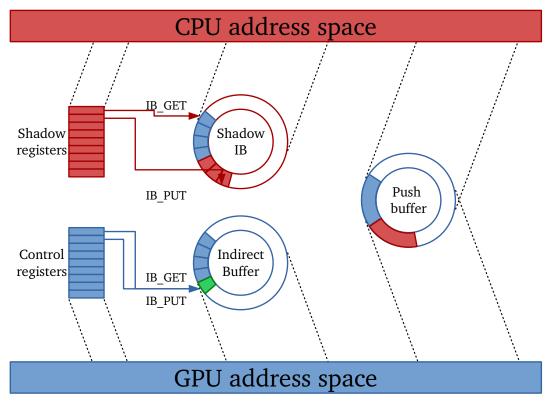

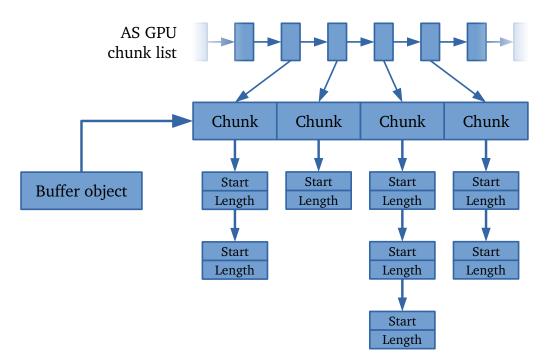

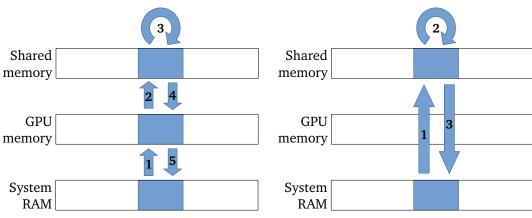

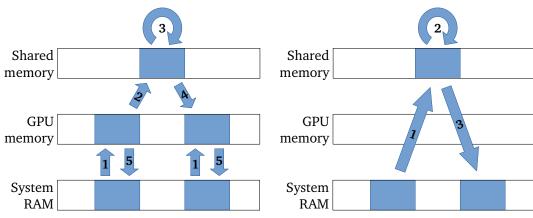

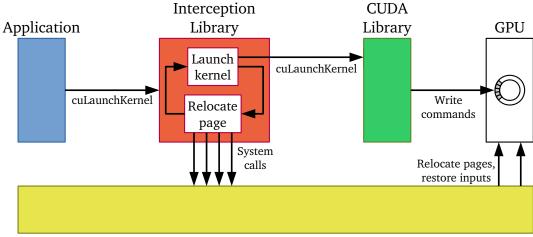

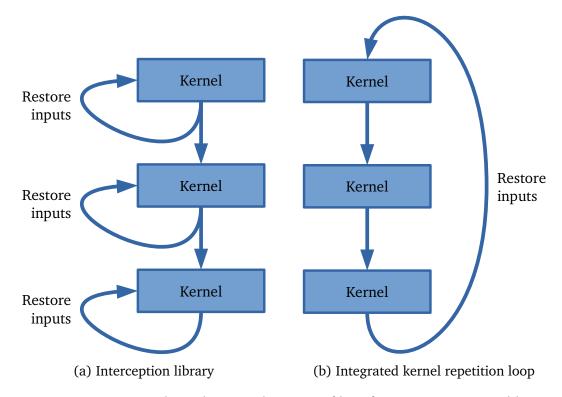

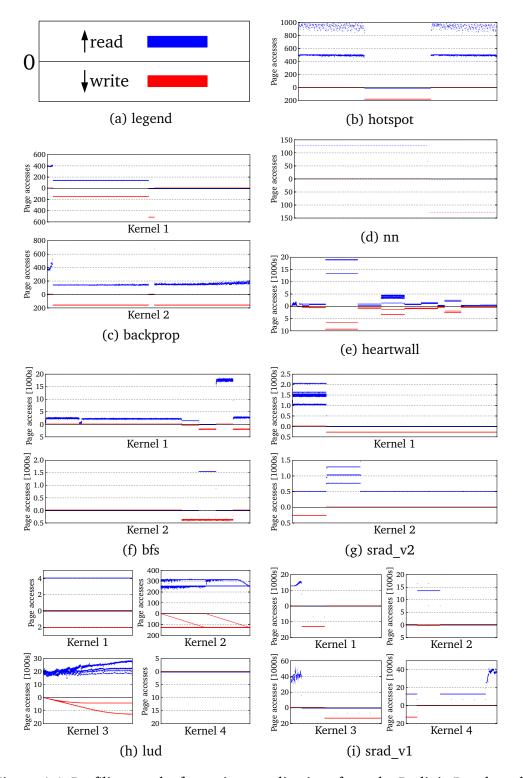

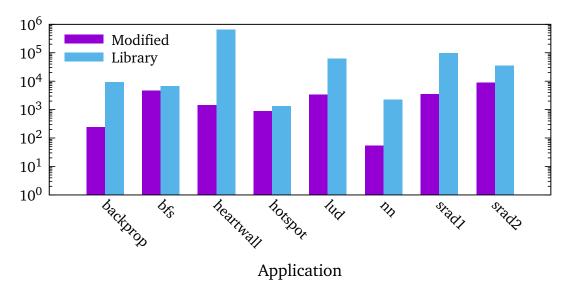

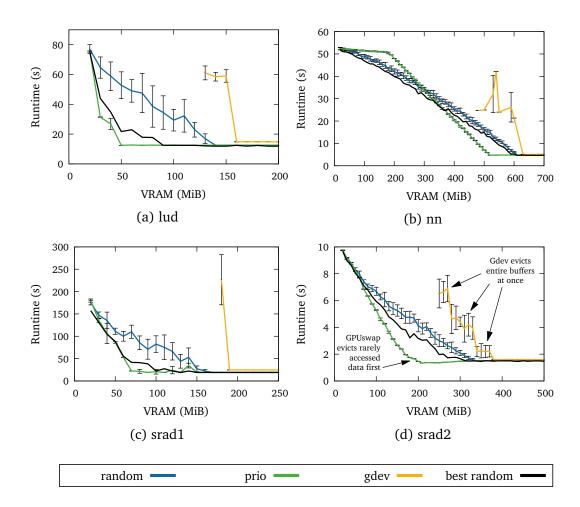

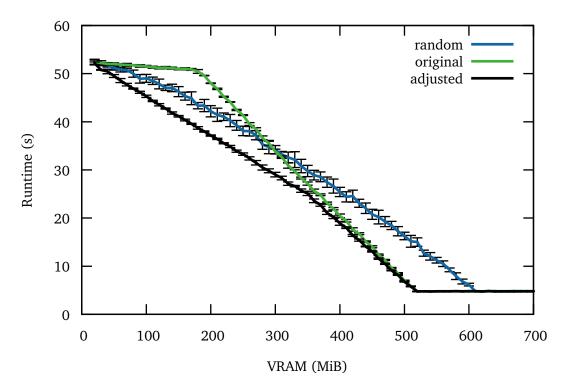

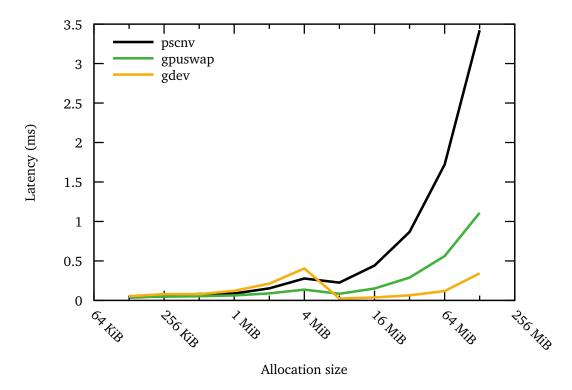

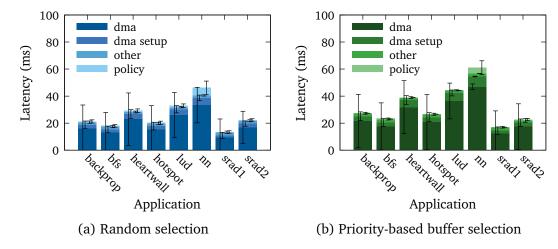

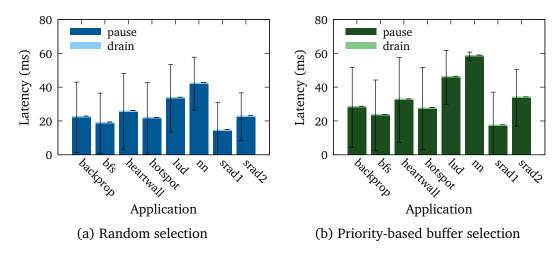

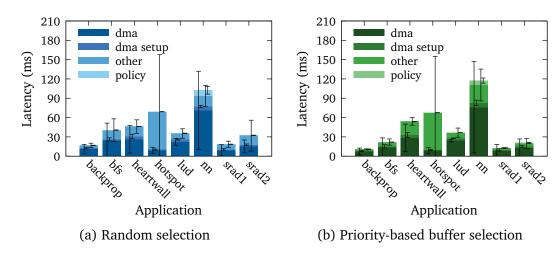

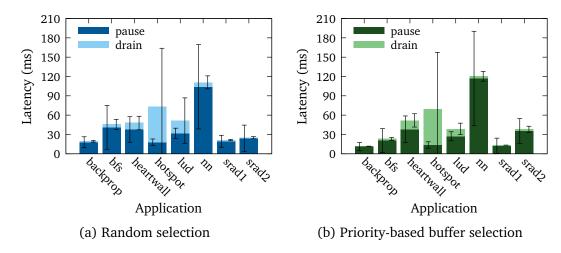

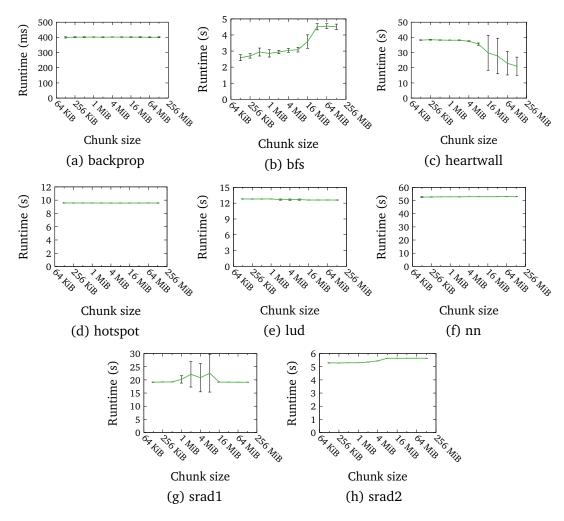

#### **Device Emulation**