# A high-voltage pulsed power modulator for fast-rising arbitrary waveforms

Zur Erlangung des akademischen Grades eines

#### **DOKTOR-INGENIEURS**

von der KIT-Fakultät für Elektrotechnik und Informationstechnik des Karlsruher Instituts für Technologie (KIT)

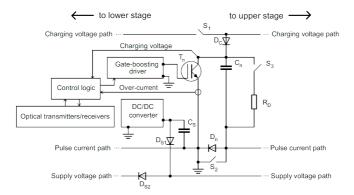

genehmigte

#### DISSERTATION

von

M.Sc. Martin Christian Hochberg

geb. in Karlsruhe

Tag der mündlichen Prüfung: 17.07.2019

Hauptreferent: Prof. Dr.-Ing. Georg Müller Korreferent: Prof. Dr.-Ing. Thomas Leibfried

This document is licensed under a Creative Commons Attribution-ShareAlike 4.0 International License (CC BY-SA 4.0): https://creativecommons.org/licenses/by-sa/4.0/deed.en

## Zusammenfassung

Die Verwendung gepulster Elektronenstrahlen zur thermischen Oberflächenbehandlung bietet Vorteile in vielen Bereichen der Energieproduktion, da durch den Prozess eine Verbesserung der Verschleiß- und Korrosionsbeständigkeit metallischer Werkstücke erzielt werden kann. Für den erfolgreichen Einsatz einer gepulsten Elektronenstrahl-Anlage (GESA) ist dabei der verwendete Hochleistungsimpuls-Generator entscheidend, der den benötigten Hochleistungsimpuls von 120 kV, 600 A bei einer Pulslänge von bis zu 100 µs bereitstellt. Der bisher verwendete funkenstreckenbasierte Generator limitiert durch seine begrenzte Flexibilität (rechteckige Ausgangsspannungsform, schwer einstellbare Pulslänge und Amplitude) die Anwendung stark. eine Weiterentwicklung der Technologie zur vollständigen Industriereife zu ermöglichen, wurde im Rahmen dieser Arbeit erstmalig ein halbleiterbasierter Hochleistungsimpuls-Generator entwickelt, gebaut und getestet, der zur Ansteuerung einer GESA-Anlage verwendet werden kann. Er zeichnet sich durch die feine Modulierbarkeit seiner Ausgangsspannung in Stufen von unter 1 % der maximalen Ausgangsspannung während des Pulses aus, welche durch den modularen Aufbau mit einer Stufenspannung von bis zu 1000 V erreicht wurde. Die Kombination aus den Pulsparametern und der Notwendigkeit eines schnellen Spannungsanstiegs von 10<sup>12</sup> V/s am Ausgang des Generators stellte eine besondere Herausforderung dar, die bisher nicht mit konventionell angesteuerten Leistungshalbleitern realisiert wurde. Zur drastischen Erhöhung der Schaltgeschwindigkeit spannungsgesteuerter Leistungshalbleiter wurde hierzu eine neuartige "Gate-boosting" Schaltung entwickelt. Weiterhin wurde durch einen speziellen Platinenentwurf eine niederinduktive Verbindung sowohl der Pulskondensatoren zu den Schaltelementen als auch der Platinen untereinander erreicht. Um einen schnellen Spannungsanstieg zu gewährleisten, wurden neben der Induktivität des Aufbaus auch die zu erwartenden Streukapazitäten mittels 3D elektro- und magnetostatischen Simulationen analysiert und im Entwurf berücksichtigt. Eine erhebliche Reduktion der Komplexität der Kontrolleinheit konnte durch die dezentrale Ansteuerung der Schaltelemente durch Mikroprozessoren und schnelle Logik lokal auf der Platine erzielt werden. Zugleich wird dadurch eine schnelle Reaktion des Generators auf Überstromfehler ermöglicht. Die effiziente Kommunikation aller Stufen untereinander gelingt durch die Implementierung eines spezialisierten optischen Bussystems, welches die Synchronisierung aller Stufen mit einer Genauigkeit von unter 11 ns erlaubt. Es konnte gezeigt werden, dass das zum Schutz der Elektronik entworfene Schirmkonzept eine Beeinflussung durch die beim Betrieb des Generators auftretenden elektromagnetischen Störungen verhindert. Neben neuen technischen Ansätzen enthält das entwickelte Design auch mehrere Konzepte zur starken Reduktion der Projektkosten. Nach erstmaliger Validierung der Generatorparameter im kleinen Maßstab von 8 Platinen wurde der vollständige Generator mit 149 Stufen erfolgreich aufgebaut und mit zuvor unerreichten Pulsparametern in Betrieb genommen. An einer der GESA-Anlage ähnlichen Last konnte die geforderte Spannungssteilheit bei voller Ausgangsspannung von 120 kV um 20 % übertroffen werden. Es wurde gezeigt, dass durch sukzessives Zuschalten von Ersatzstufen die Spannungsabnahme der Pulskondensatoren effektiv kompensiert werden kann. Der neu entwickelte Generator steht nun zur Integration in das GESA-Versuchsfeld zur Verfügung.

## **Abstract**

Pulsed electron beam treatment for thermal surface modification offers new possibilities in many fields of energy technology, as it allows the enhancement of the wear and corrosion resistance of metals. A critical element of the process is the employed pulsed power modulator driving the pulsed electron beam device (GESA). It supplies the necessary high-power pulse with a total output voltage of 120 kV and a total current of 600 A for a duration of up to 100 µs. The currently employed spark-gap based modulator restricts the applications of the process due to its limited flexibility in terms of output voltage shape, amplitude and duration. To enable a maturing of the technology to large-scale industry level, a semiconductor-based pulsed power modulator capable of driving a GESA device was developed, build and tested for the first time in the scope of this work. It allows for a step-wise arbitrary output waveform of up to 120 kV and a maximum current of 600 A. By selecting a modular concept and a stage voltage of 1000 V, the output voltage can be modulated in fine steps below 1 % of the maximum output voltage. Besides the unique pulse parameters, the required fast rise rate of the output voltage of 10<sup>12</sup> V/s posed a special challenge, as it has not been realized with presently available power semiconductors using standard gate-drive technologies. To overcome this limitation, a new "gate-boosting" circuit was developed, allowing a tremendous increase in switching speed for commercial voltage-controlled power semiconductors. Additionally, the circuit inductance was kept low using a special board layout for reduced inductance between the pulse capacitors and the pulse switches on the one hand, as well as between adjacent stages on the other hand. Together with the parasitic inductive properties of the assembly, the parasitic capacitances were analyzed based on 3D electro- and magneto-static simulations and considered in the design for meeting the voltage rise time requirement. The employed decentralized control of the pulse switches by microprocessors and fast logic locally on each board drastically reduces the complexity of the main control unit while ensuring a fast reaction time of the modulator to overcurrent conditions. An efficient communication between all stages is achieved by implementing a specialized optical bus system, enabling a synchronization of all stages within 11 ns. The designed electro-magnetic shielding for the sensitive electronics on each stage was tested successfully. Complementing the new solutions for technical challenges, the presented work implements approaches for drastically cutting the project costs. After a successful validation of the design parameters in a proof-of-concept assembly consisting of eight stages, the full-scale modulator was assembled and tested with unprecedented pulse parameters. Connected to a load similar to the GESA device, the required output voltage rise rate at full output voltage of 120 kV could be exceeded by 20 %. The subsequent activation of spare stages proved efficient in counteracting the pulse capacitor voltage droop. The modulator is now ready for integration into the GESA experiment.

## **Table of Contents**

| Zι | ısam  | menfa   | ssung                                            | i   |

|----|-------|---------|--------------------------------------------------|-----|

| ΑI | ostra | ct      |                                                  | iii |

| Li | st of | Abbrev  | viations                                         | ix  |

| 1  | Intr  | oductio | on                                               | 1   |

|    | 1.1   |         | ation                                            | 1   |

|    | 1.2   | Structi | ure of this thesis                               | 2   |

| 2  | Ger   | nerator | design study                                     | 5   |

|    | 2.1   | Design  | n parameters                                     | 5   |

|    |       | 2.1.1   | GESA pulse parameters                            | 5   |

|    |       | 2.1.2   | Homogeneous cathode ignition                     | 7   |

|    |       | 2.1.3   | Parasitic device properties                      | 9   |

|    | 2.2   | The se  | emiconductor-based Marx generator                | 10  |

|    |       | 2.2.1   | Topology                                         | 10  |

|    |       | 2.2.2   | Increasing the energy efficiency of the process  | 15  |

|    |       | 2.2.3   | Comparison to state-of-the-art pulse generators  | 16  |

|    | 2.3   | Genera  | ator component requirements                      | 18  |

|    |       | 2.3.1   | Pulse switches and parasitic properties          | 18  |

|    |       | 2.3.2   | Pulse switch control                             | 21  |

|    |       | 2.3.3   | Dimensioning of pulse capacitors                 | 22  |

|    |       | 2.3.4   | Protection against electro-magnetic interference | 25  |

|    |       | 2.3.5   | Physical and mechanical constraints              | 28  |

|    | 2.4   | Chargi  | ing and supply voltage distribution              | 28  |

|    |       | 2.4.1   | Pulse capacitor charging                         | 29  |

|    |       | 2.4.2   | Generating the supply voltage                    | 31  |

|   |      | 2.4.3   | Protective elements                                   | 3  |

|---|------|---------|-------------------------------------------------------|----|

|   | 2.5  | Related | 1 metrology                                           | 5  |

|   |      | 2.5.1   |                                                       | 7  |

|   |      | 2.5.2   |                                                       | 8  |

|   |      | 2.5.3   |                                                       | 9  |

| 3 | Gat  | e-boos  | ting investigations                                   | 1  |

|   | 3.1  |         |                                                       | -1 |

|   |      | 3.1.1   |                                                       | 2  |

|   |      | 3.1.2   |                                                       | 4  |

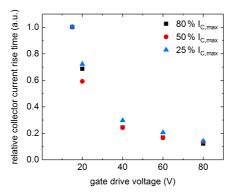

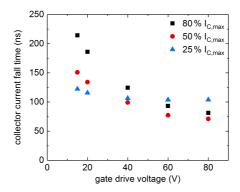

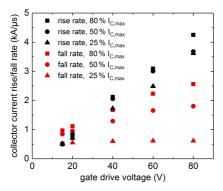

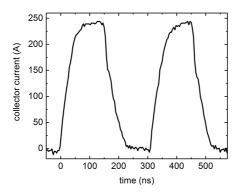

|   | 3.2  | Fast sw |                                                       | 6  |

|   |      | 3.2.1   |                                                       | 6  |

|   |      | 3.2.2   |                                                       | 8  |

|   | 3.3  | Fast sw |                                                       | 0  |

|   |      | 3.3.1   |                                                       | 0  |

|   |      | 3.3.2   | Circuit considerations                                | 5  |

|   |      | 3.3.3   | Determining the device parameters 5                   | 8  |

|   |      | 3.3.4   | $\mathcal{E}$                                         | 3  |

|   |      | 3.3.5   | Reduction of switching losses                         | 3  |

|   |      | 3.3.6   | Long term stability                                   | 6  |

| 4 | Stag | ge desi | gn process                                            | 9  |

|   | 4.1  |         |                                                       | 9  |

|   |      | 4.1.1   | Fast, cost-efficient switches                         | 0  |

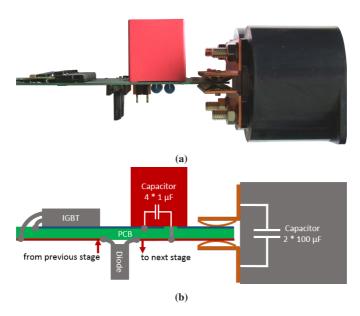

|   |      | 4.1.2   | Pulse capacitors and capacitor connection 8           | 2  |

|   |      | 4.1.3   | Arrangement and selection of free-wheeling diodes . 8 | 6  |

|   | 4.2  | Protect | ion circuits                                          | 8  |

|   |      | 4.2.1   | Parasitic turn-on                                     | 8  |

|   |      | 4.2.2   | Overvoltage protection                                | 9  |

|   |      | 4.2.3   | Overcurrent protection                                | 1  |

|   |      | 4.2.4   | Discharging the pulse capacitors                      | 4  |

|   | 4.3  | Contro  | 8                                                     | 4  |

|   |      | 4.3.1   | 1                                                     | 5  |

|   |      | 4.3.2   | Switching signal generation                           | 8  |

|   |      | 433     | EMI testing                                           | 9  |

|   | 4.4 | Design  | n validation                                          | 104 |  |

|---|-----|---------|-------------------------------------------------------|-----|--|

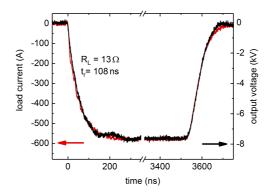

|   |     | 4.4.1   | Pulse circuit qualification                           | 104 |  |

|   |     | 4.4.2   | Fast current rise time measurement                    | 107 |  |

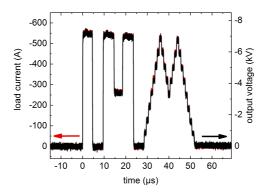

|   |     | 4.4.3   | Arbitrary switching sequence                          | 108 |  |

| 5 | Pro | of-of-c | oncept assembly                                       | 111 |  |

|   | 5.1 | The M   | farx module                                           | 111 |  |

|   |     | 5.1.1   | One stage equivalent circuit                          | 111 |  |

|   |     | 5.1.2   | Combination of stages via an optical bus system       | 112 |  |

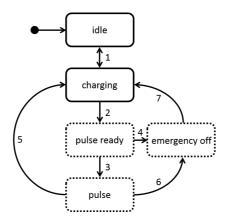

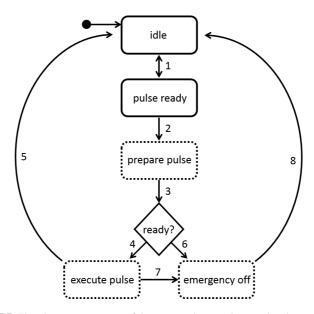

|   |     | 5.1.3   | Software control                                      | 115 |  |

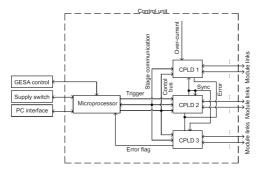

|   | 5.2 | The m   | ain control unit                                      | 117 |  |

|   |     | 5.2.1   | Interfacing the generator to the experiment's control | 117 |  |

|   |     | 5.2.2   | Implementation of the main functionalities            | 118 |  |

|   | 5.3 | Design  | n validation                                          | 122 |  |

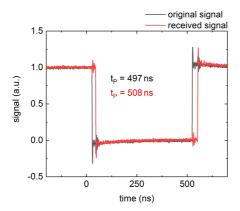

|   |     | 5.3.1   | low-jitter triggering                                 | 122 |  |

|   |     | 5.3.2   | Pulse circuit qualification                           | 123 |  |

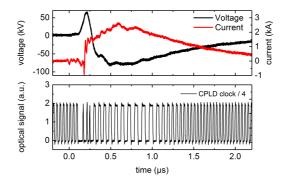

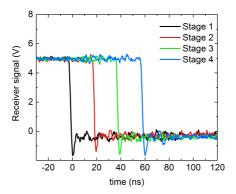

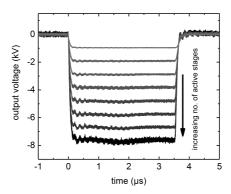

|   |     | 5.3.3   | Arbitrary output waveform generation                  | 127 |  |

|   |     | 5.3.4   | Overcurrent protection                                | 128 |  |

| 6 | Ger | nerator | implementation                                        | 133 |  |

|   | 6.1 | Electri | ical properties                                       | 133 |  |

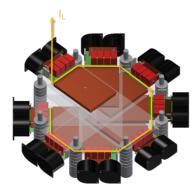

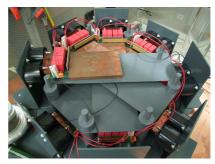

|   |     | 6.1.1   | Stage arrangement                                     | 134 |  |

|   |     | 6.1.2   | Stray inductance estimation                           | 135 |  |

|   |     | 6.1.3   | Simulating the parasitic capacitance                  | 137 |  |

|   |     | 6.1.4   | Generator connected to the GESA device                | 139 |  |

|   | 6.2 |         |                                                       |     |  |

|   |     | 6.2.1   | Hardware discharge switch                             | 142 |  |

|   |     | 6.2.2   | Determination of pulse parameters                     | 143 |  |

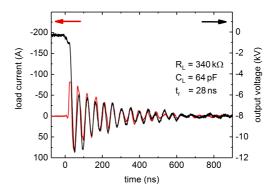

|   |     | 6.2.3   | Measurement qualification                             | 145 |  |

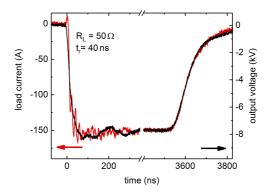

|   |     | 6.2.4   | Meeting the voltage rise time requirement             | 147 |  |

|   |     | 6.2.5   | A 120 kV, 600 A semiconductor-based Marx generator    |     |  |

|   |     |         | for step-wise arbitrary output waveforms              | 149 |  |

|   |     | 6.2.6   | Active droop compensation                             | 151 |  |

| 7 | Cor | nclusio | n and outlook                                         | 153 |  |

#### Table of Contents

| References              | 155 |

|-------------------------|-----|

| Acknowledgments         | 165 |

| Awards and publications | 167 |

## **List of Abbreviations**

**ADC** Analog-to-digital converter

Be Beryllium

**Bi** Bismuth

**CAD** Computer-aided design

**CPLD** Complex programmable logic device

**CPU** Central processing unit

Cu Copper

**DC** Direct current

**DUT** Device-under-test

**EMI** Electro-magnetic interference

**FPGA** Field programmable gate array

**FS** Field-stop

GaN Gallium-nitride

**GESA** Gepulste Elektronenstrahl-Anlage, German for "Pulsed electron

beam device"

**HVPS** High-voltage power supply

**IGBT** Insulated-gate bipolar transistor

IHM Institut für Hochleistungsimpuls- und Mikrowellentechnik

KIT Karlsruher Institut für Technologie

LC Inductor-capacitor combination

**LED** Light-emitting diode

**LPF** Low-pass filter

**LTD** Linear transformer driver

MMC Modular multilevel converter

MOSFET Metal-oxide-semiconductor field-effect transistor

**NPT** Non-punch-through

Pb Lead

**PCB** Printed circuit board

**PSM** Pulse Step modulator

**RC** Resistor-capacitor combination

**RF** Radio-frequency

**RL** Resistor-inductor combination

**RLC** Resonant circuit with resistive, inductive and capacitive

properties

**RMS** Root-mean-square

**SEM** Scanning electron microscope

Si Silicon

**SiC** Silicon carbide

**SMD** Surface-mounted device

**SOA** Safe operating area

TC Timer-counter

TTL Transistor-transistor logic

TVS Transient voltage suppressor diode

**ZCS** Zero-current switching

**ZVS** Zero-voltage switching

## 1 Introduction

#### 1.1 Motivation

The surface modification of metal targets by means of intense pulsed electron beams (GESA process) is one of the main research interests at the Institute for Pulsed Power and Microwave Technology (IHM), Karlsruhe Institute of Technology (KIT). The high energy deposition in the topmost surface layer of the sample by the intense electron beam causes the surface to melt - the associated high heating and cooling rates lead to a restructuring of the surface layer. Thereby, the process can be used to either enhance the surface properties in terms of surface hardness and wear resistance or even change the surface composition by alloying thin films of material into the surface, both without affecting the bulk material beneath it [1]. Especially for structural materials in contact with liquid metals (as used in concentrated solar power plants or accelerator-driven transmutation reactors [2], [3]) an increased corrosion resistance can be achieved [4]. The electron beam is created using the GESA (German acronym "Gepulste ElektronenStrahl-Anlage", "pulsed electron beam device"), a high-current electron accelerator for large area surface treatment, originally developed in cooperation with the Efremov Institute St. Petersburg, Russia, starting in 1996. The device operates in pulsed mode with a pulse length of up to several tens of microseconds. It requires an acceleration voltage of up to 120 kV at a beam current of up to 600 A. The high peak power in the range of 72 MW is supplied by a specialized pulsed power supply. Currently, the device is equipped with a spark-gap based power supply with very limited flexibility. Due to its design, the output voltage is rectangular and any change of pulse length or pulse amplitude requires a physical manipulation of components. Recent progress in the development of power semiconductor devices offers new possibilities for their use in high-voltage pulsed power sources with respect to active pulse shaping. For a deeper understanding of the processes governing the GESA device physics and, subsequently, enabling

a maturing of the technology to industry level, it is the scope of this thesis to develop, build and test a new type of semiconductor-based pulsed power modulator capable of active pulse shaping. The requirements for future experiments include a flexible output voltage of up to  $120\,\mathrm{kV}$ , that can be modulated with a step-size below 1% of the maximum voltage. At a nominal current of  $250\,\mathrm{A}$ , the maximum pulse length should be  $100\,\mu\mathrm{s}$ . The most important figure of merit is the output voltage rise rate when connected to the GESA device, specified to  $10^{12}\,\mathrm{V/s}$ .

While specialized pulsed power sources meeting one of the requirements or another have been presented before, the combination of the requested parameters renders this project very challenging. On the one hand, the GESA device requires a very fast output voltage rise rate, on the other hand it demands for a comparably long high-current pulse. Both requirements are conflicting, since long pulses require big energy storage capacitors which, in turn, increase the circuit inductance (for a given volume) and therefore slow down the output voltage rise rate. Currently, cost-efficient power semiconductor devices meeting the speed requirement for this project are not available. In the presented design, the fine step-size in combination with the fast rise rate requires many individual switching elements, all controlled independently from each other at minimal financial and fabrication effort. Due to the high output voltage and current, the sensitive electronics need to be shielded appropriately against electro-magnetic interference. During the design process, all parasitic circuit parameters such as stray inductance and stray capacitance need to be simulated to meet all the requirements. Finally, the project has to be planned according to the manufacturing capabilities of the institute's workshop and within a limited budget.

The presented thesis describes the design process to meet all the abovementioned requirements and their validation with first measurements on the full-scale version of the modulator.

#### 1.2 Structure of this thesis

In this work, the development of a new semiconductor-based pulsed power modulator for the GESA device is presented. In contrast to the former generator, the voltage amplitude, pulse length, and pulse shape of the output pulse are controlled by software.

After an overview over the GESA experiment and the deduction of the pulsed power source requirements, chapter 2 describes the generator design study. The selected generator topology is presented and compared to other approaches found in literature. As no generator for the required set of pulse parameters has been demonstrated before, the resulting challenges with respect to the circuit components are outlined.

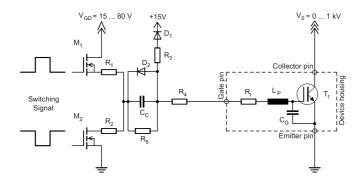

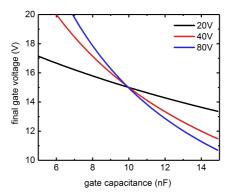

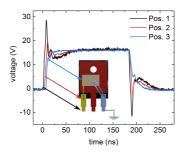

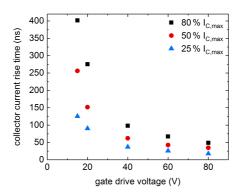

A very strict requirement of the device is an output voltage rise rate in the order of  $10^{12}$  V/s. As this parameter cannot be met in a cost-efficient way with currently available power semiconductors, chapter 3 presents a new "gate-boosting" circuitry, which allows the speed-up of commercial devices by a factor of up to eight.

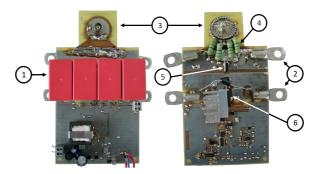

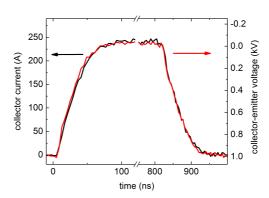

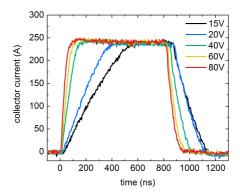

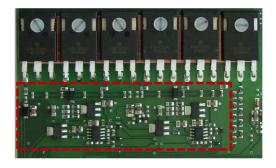

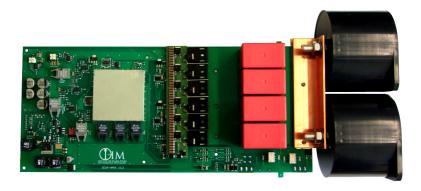

The investigated topology is modular and consists of identical stages connected in series to achieve the required full output voltage. Chapter 4 describes the design and validation process of one stage and covers all important circuit elements: selection and parallel operation of IGBTs using a gate-boosting circuit, low-inductive energy storage, switching signal generation, and related protection circuitry.

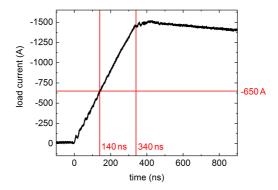

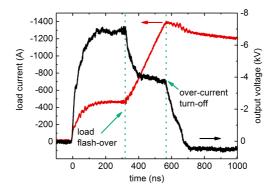

In chapter 5, the combined operation of up to eight stages (maximum output voltage of  $8\,\mathrm{kV}$ ) in a generator arrangement is presented. As interface between the user (PC) and the generator, a control unit has been developed. For reducing its complexity, the stages communicate via a new optical bus system, allowing for a low-jitter synchronization of all stages. All features of the generator, namely the arbitrary waveform generation at full output voltage, maximum load current (600 A), and fast rise time as well as an efficient overcurrent protection scheme have been validated in the full control chain.

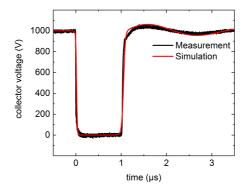

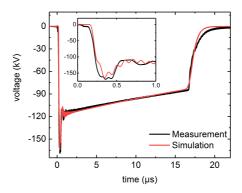

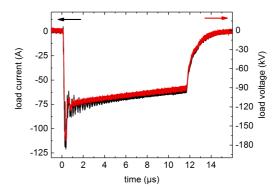

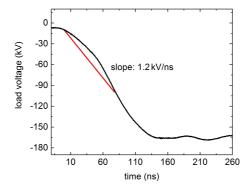

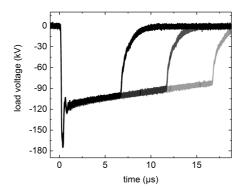

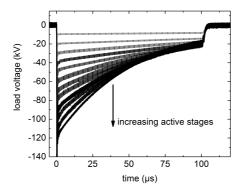

Finally, the full-scale generator has been constructed and operated in a test-bed. The measured output pulse shape is in good agreement with the simulations and shows a voltage rise time even exceeding the required  $10^{12}\,\text{V/s}$  by around 20 %. In addition, active pulse shaping could be demonstrated to achieve droop compensation at full output voltage.

## 2 Generator design study

For high-voltage, high-current pulsed power sources, several architectures are known. The generator topology investigated in this work is the semiconductor-based Marx generator. It was chosen due to its scalable design, allowing for achieving all pulse parameter requirements at reasonable costs. The following chapter starts with a short overview over the GESA device and deduces the required pulse parameters. Consecutively, it presents the selected generator architecture and compares it to previous work described in literature. Subsequently, the design study covering the pulsed power components, the logic and auxiliary circuitry necessary to achieve all requirements in the presented architecture is discussed. Selected results of this work presented in the following chapter have already been published as [5].

### 2.1 Design parameters

In the Institute for Pulsed Power and Microwave Technology (IHM) at the Karlsruhe Institute of Technology, Germany, several devices exist for treatment of samples with a wide parameter range. Whereas the applications are similar for all devices, the pulse parameters differ significantly. A comprehensive overview is given in [6] and [7]. All values given in this work refer to the GESA I device, to which the generator-under-development will be connected.

#### 2.1.1 GESA pulse parameters

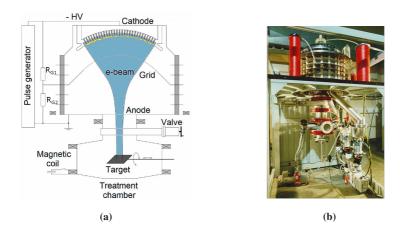

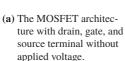

The basic concept behind the GESA device is a vacuum tube in a triode configuration, consisting of a cathode, a control grid, and an anode. A schematic can be seen in Fig. 2.1a. A pulse generator delivers a negative high-voltage pulse of around  $-120\,\mathrm{kV}$  to the cathode. The cathode, consisting of an array of

carbon fiber bundles, ignites a plasma serving as electron emitter. By means of the potential difference between cathode and control grid, an intense electron beam of up to 600 A can be extracted from the plasma and is accelerated towards the anode. Several magnetic coils generate a guiding magnetic field in the device [8] to focus the beam through an opening in the anode and onto a metal target beneath it. In the photograph shown in Fig. 2.1b, the upper part of the image shows the cathode on high-voltage potential, whereas the lower part shows the treatment chamber and the required vacuum system on ground potential.

Figure 2.1: Schematic (a) and photo (b) of the pulsed electron beam device (GESA).

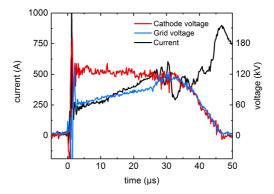

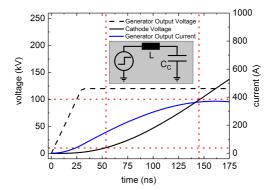

The operating voltage for the cathode is in the range of 50...150 kV [9], whereas a value of  $120\,kV$  is preferred. The typical potential distribution and the resulting beam current are depicted in Fig. 2.2. A part of the beam current (in the range of  $10\,\%$ ) hits the grid and is deflected via the resistive network  $R_{\rm G1}$  and  $R_{\rm G2}$ , implementing a negative feedback - an increase in beam current will decrease the potential difference between cathode and grid. However, this mean of control has proven to be unsatisfactory, limiting the maximum achievable pulse length to  $50\,\mu s$ . For a better control of the process and future research on the plasma dynamics, the generator will be required to supply a maximum output voltage of  $120\,kV$ , adjustable in steps below  $1\,\%$ .

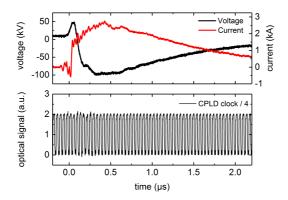

**Figure 2.2:** A typical pulse of the GESA device. The electron beam is extracted by the potential difference between cathode voltage and grid voltage.

Additionally, the topology has to allow for a direct control of the grid voltage. The nominal current of the generator is specified to  $250\,\mathrm{A}$  with a maximum pulse duration of  $100\,\mu\mathrm{s}$ . Due to the dynamic load behavior of the GESA device, a complete short may occur. Therefore an overcurrent protection has to be implemented if the beam current significantly exceeds  $600\,\mathrm{A}$ . The maximum repetition rate will be one shot every  $30\,\mathrm{s}$  and thereby comparable to the current design. This work assumes implicitly a deterministic and stable behavior of the process. As result, an open-loop control is implemented in the generator. However, the developed hardware includes the possibility of upgrading the generator to a closed-loop control system if this assumption proves wrong in the course of future experiments.

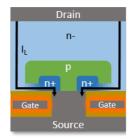

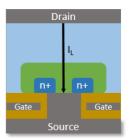

#### 2.1.2 Homogeneous cathode ignition

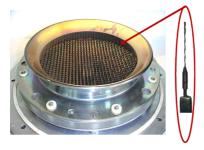

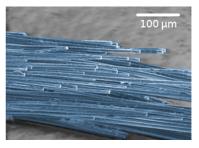

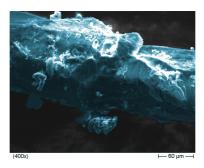

As electron emitter, the GESA device uses a "multipoint explosive emission cathode". Depicted in Fig. 2.3a, the cathode is an arrangement of individual carbon fiber bundles. A magnification of one bundle is shown in the SEM image in Fig. 2.3b. Typically, field emission starts at electric fields of around  $10^5$  V/cm [10]. By using fibers with a diameter of  $10\,\mu m$ , the on-set of field emission can be reduced to a field strength of  $10^2$  V/cm [10] due to field

enhancement. When the pulse generator (compare Fig. 2.1) turns on, the threshold for field emission is exceeded. The cold carbon fibers start to emit electrons near their Fermi level, whereas the replacement electrons from the pulse generator enter the carbon fibers at the highest unoccupied energy level. The energy difference between these states is dissipated causing a heating of the fiber ("Nottingham effect") [11]. With increasing temperature, electron emission is facilitated. The increasing electron current causes ohmic heating of the fiber, changing the emission mechanism to thermionic emission [12]. If the voltage rise is fast enough an evaporation of the emitting fiber tip [10] occurs within several nanoseconds ("explosive electron emission") [13]. The thereby formed plasma layer expands and acts as emission surface.

(a) The GESA cathode consists of an array of carbon fiber bundles, each with an individual resistor for current balancing.

(b) The tips of the individual carbon fibers have a diameter of 10 µm and serve as electron emission centers.

**Figure 2.3:** Photograph of the cathode arrangement with 700 individual carbon fiber bundles and scanning electron microscope (SEM) image of one bundle showing the individual fibers.

To foster a homogeneous cathode plasma ignition, a voltage rise in the order of  $10^{12}$  V/s is required [10].

Whereas some applications are very sensitive against overvoltage [14], the GESA device was designed for voltages of 150 kV and is operated at nominal voltage of 120 kV. Any occurring overvoltage due to parasitic capacitances/inductances of the generator will increase the voltage rise rate and foster a homogeneous plasma ignition. Once the plasma has ignited, the drop in the cathode's impedance will dissipate the energy stored in the parasitic

capacitances and, therefore, limit the duration of the overvoltage. Since the currently employed pulse generator cannot achieve the required rise time, a peaking circuit is implemented [10]. To reduce the circuit complexity, the generator under development has to meet the demand for the voltage rise time across the cathode without the need of a peaking circuit. The figure of merit for the design of the generator used in this work is therefore the voltage rise rate from the beginning of the pulse (10 %, i.e.  $10\,\mathrm{kV}$ ) to  $100\,\mathrm{kV}$ , regardless of a possible voltage overshoot.

#### 2.1.3 Parasitic device properties

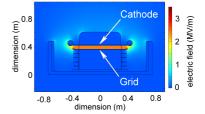

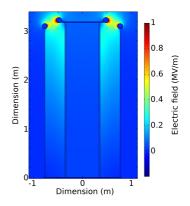

(a) A photo of the GESA cathode and field grading rings in its shielding enclosure.

**(b)** Simplified 3D model and resulting electric field.

**Figure 2.4:** Photo and corresponding 3D model used for FEM static electric field simulations to estimate the cathode-to-ground stray capacitance.

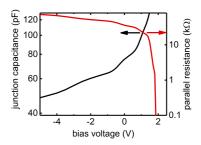

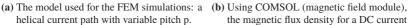

Apart from the inherent device physics, the mechanical dimensions of the device determine its behavior in an electric circuit. Especially for the voltage rise time calculations, the parasitic properties such as device inductance, and device capacitance are crucial. Fig. 2.4a shows a photo of the GESA cathode in its lead-reinforced metal shielding enclosure. In order to avoid a time-consuming precise modeling of all internal components, a worst-case estimation was performed to derive the parasitic values of the device. Concerning the parasitic capacitance of the device, Fig. 2.4b illustrates static electric field simulations performed using COMSOL (AC-DC module). The outside of the device was modeled according to its physical dimensions, with the cathode simulated at a constant voltage of 120 kV. As worst-case scenario, the control grid was simulated to be on ground potential. From the electric field energy, the total resulting equivalent capacitance was calculated to 150 pF. A crude estimation

concerning the device's parasitic inductance can be performed on basis of its geometric dimensions. When connected to the center of the cathode and the edge of the shielding enclose, the resulting current loop will have a total length of about 4 m. Due to the large diameter, the coupling between the conductors is not significant. Therefore, an approximate inductance of  $10\,\text{nH/cm}$  [15] can be assumed, yielding a total inductance of  $4\,\mu\text{H}$ .

## 2.2 The semiconductor-based Marx generator

The semiconductor-based Marx generator is a member of a group of topologies of a step-wise arbitrary voltage sources not limited to the field of pulsed power. Conceptually similar, but with different parameters and much slower switching speeds, are the Modular Multilevel Converter (MMC, [16], [17]) or the Pulse Step Modulator (PSM, [18]).

#### 2.2.1 Topology

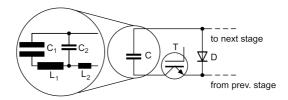

The Marx generator, a circuit patented 1923 by Erwin Marx [19], was originally invented to create high-voltage impulses for insulator testing. The modular concept is illustrated in Fig. 2.5: each of the n stages consists of a pulse capacitor  $C_{\rm P}$ , a charging impedance  $Z_{\rm C}$  and a pulse switch  $S_{\rm P}$ . Prior to pulse execution, all capacitors are connected in parallel via the charging impedances and charged to the same voltage  $V_0$ . When the pulse switches are closed, the capacitors are connected in a series arrangement causing a voltage multiplication to  $n\cdot V_0$  across the load impedance  $Z_{\rm L}$ . The charging impedances  $Z_{\rm C}$  decouple adjacent stages during the discharge time of the capacitors, preventing a significant short circuit current. Since all stages are floating during the pulse, the maximum voltage each component has to withstand is solely the charging voltage  $V_0$ , even if the output voltage is n times higher. Thereby, the generator can by composed of very cost-efficient components.

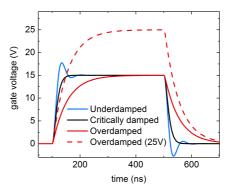

When erected, the presented circuit (Fig. 2.5b) effectively is an RLC circuit composed of the load impedance (circuit resistance and inductance) and the series connection of all pulse capacitors. Depending on the degree of damping, the pulse into the load can be over-damped, critically damped or oscillating.

(a) During charging, all capacitors are connected in a parallel configuration.

(b) By closing the pulse switches, the capacitors are arranged in a series configuration and discharge via the load impedance  $Z_{\rm L}$ .

Figure 2.5: The Marx generator comprised of n identical cells, each consisting of a pulse capacitor  $C_P$ , a pulse switch  $S_P$  and a charging impedance  $Z_C$  for transient decoupling during the pulse.

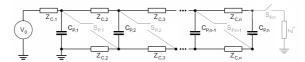

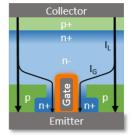

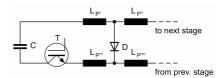

The same concept can also be used to create rectangular pulses by replacing the capacitors by an LC-network (see Fig. 2.6) and is currently used to drive the GESA device. Each stage of pulse capacitor  $C_{\rm P}$  and pulse inductor  $L_{\rm P}$  is charged via a decoupling impedance  $L_{\rm C}$  to the same voltage  $V_0$ . Upon closing the pulse switches, the networks are arranged in a series configuration. To avoid reflections at the load, the load impedance  $Z_{\rm L}$  must be equal to the series connection of the characteristic impedance of all stages  $Z_{\rm S}$  according to Eq. 2.1.

$$Z_{L} = n \cdot \sqrt{\frac{L_{P}'}{C_{P}'}}$$

(2.1)

As result, the load voltage  $V_n$  =  $n \cdot V_0/2$  across the load impedance is only half of the sum charging voltage of all stages.

For short pulse lengths, the LC-network can be replaced by a coaxial cable, whereas for longer pulse lengths in the tens of microsecond range the physical dimensions of a cable become unpractical and the networks are implemented using discrete elements. Matching dynamic loads, such as the GESA device, directly to the generator is not possible [20]. Instead, the device is connected in parallel to a matched load impedance. An influence of the GESA impedance on the pulse shape can only be neglected if the current through the load impedance significantly exceeds the current drawn by the GESA device. In the current design, the value of the load impedance is around  $40\,\Omega$ , corresponding to a

load current of 3 kA as compared to the nominal current of the device of 250 A.

Figure 2.6: A rectangular pulse can be created using LC-chains instead of capacitors in the Marx generator.

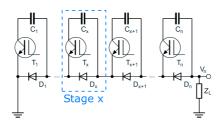

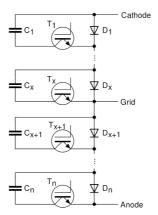

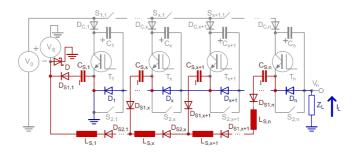

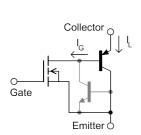

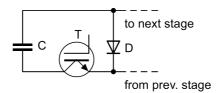

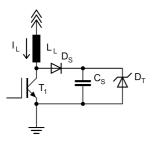

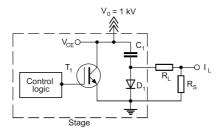

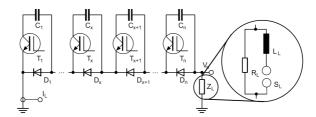

Historically, spark gaps have been used as pulse switches for both circuits, triggered either by exceeding their standoff voltage or by using an external trigger circuit [15]. Usually only a few spark gaps are triggered and, consecutively, all remaining spark gaps follow due to an overvoltage caused by ground stray capacitances [15]. As a result, the generator can only be erected completely and cannot be switched off without external means before the voltage across the spark gaps falls below their arcing voltage, i.e. before the pulse capacitors are nearly completely discharged. Whereas spark gaps are still economical for large scale industry applications [21] due to their easy manufacturing, highcurrent capability and robustness, many researchers work on replacing them by semiconductor-based switching elements. Thereby, trigger delay, jitter, and electrode wear associated with certain spark gap designs can be omitted. Semiconductor switches with current interruption capability furthermore offer the possibility of active pulse shaping [22]. The simplified circuit of the generator investigated in this work is shown in Fig. 2.7. All pulse capacitors C are charged in parallel comparable to Fig. 2.5 (charging path not shown). The pulse switch consists of an active semiconductor switch T and a free-wheeling diode D as passive switch.

**Figure 2.7:** The semiconductor-based Marx generator topology, each of the n stages has a pulse capacitor C, a semiconductor switching element T and a free-wheeling diode D (charging path not shown).

In contrast to the spark-gap based Marx generator, the output voltage  $V_n(t)$  can now be modulated during the pulse by changing the number of active switching elements. By assigning each switching element  $T_i$  a switching function  $T_i(t)$  ( $T_i$  = 1: switching element  $T_i$  closed;  $T_i$  = 0: switching element  $T_i$  open),  $V_n(t)$  is given by Eq. 2.2 using the present capacitor voltage of stage i,  $V_{C,i}(t)$ . During an inactive period of stage i, the pulse current will by-pass the inactive stage via the free-wheeling diode  $D_i$ .

$$V_{n}(t) = -\sum_{i=1}^{n} V_{C,i}(t) \cdot T_{i}(t)$$

(2.2)

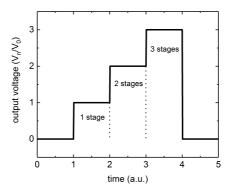

Other researchers [24] use active semiconductor switches anti-parallel to the free-wheeling diodes. After the end of the pulse, these switches are activated for a fast discharging of the load capacitance. As only a fast rising edge is important in this application, these additional switching elements have been omitted in this design. Fig. 2.8 shows an example of a step-wise arbitrary output voltage waveform  $V_{\rm n}$  in steps of the capacitor charging voltage of one stage  $V_0$ , when one, two and three pulse switches are turned on with a time delay.

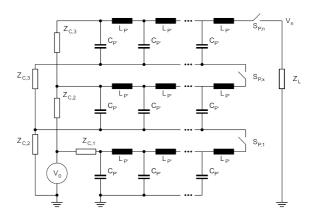

When operated in combination with the GESA device, it may be necessary to use the generator to control not only the output voltage (i.e. cathode-anode voltage), but also the cathode-grid voltage. Due to the modular nature of the presented topology, cathode, anode, and grid can be connected to it as depicted

in Fig. 2.9: thereby, one part of the generator controls the cathode-grid voltage and one part of the generator controls the grid-anode voltage. Simultaneously deactivating stages in the upper part and activating stages in the lower part, the acceleration voltage can be kept constant while the extraction voltage is reduced. Since the grid current is below  $10\,\%$  of the beam current, the unequal discharging of both parts will not be significant.

Figure 2.8: The output voltage  $V_n$  of the generator can be modulated in steps of the capacitor charging voltage  $V_0$ .

**Figure 2.9:** By adding a grid connection, one part of the generator can be used to control the cathode-grid voltage, whereas the other part of the generator can be used to control the grid-anode voltage.

#### 2.2.2 Increasing the energy efficiency of the process

As discussed in the preceding section, the GESA currently is connected in parallel to the matched load of the LC-chain Marx generator. For achieving the nominal output voltage, it uses four stages charged to  $60\,kV$  with a total capacitance of  $12\,\mu F$  and is discharged completely during each pulse. The resulting total stored energy is given in table 2.1.

**Table 2.1:** Stored energy and energy loss comparison of both generator types.

| Generator                          | Stored energy | Energy loss per pulse |

|------------------------------------|---------------|-----------------------|

| LC-chain Marx generator            | 21 kJ         | 21 kJ                 |

| Semiconductor-based Marx generator | 15 kJ         | 1.5 kJ                |

A comparison with the energy required by the device of  $1.5 \, kJ$  ( $120 \, kV$ ,  $250 \, A$  for  $50 \, \mu s$ ) yields an efficiency of the process of close to  $7 \, \%$ . Since the new generator does not discharge completely in the course of the pulse, only the

pulse energy needs to be resupplied. The conduction losses of approximately 3 J (1  $\Omega$  internal resistance, 250 A for 50  $\mu s$ , see Sec. 6.2.2) can be neglected. Thereby, this technology offers the potential for huge energy savings by avoiding the need for a matched load.

The calculation neglects the supply voltage necessary to operate both generators, which are in the same order of magnitude. Additionally, for a highly efficient operation, the generator needs to be operated continuously without complete discharging. In the GESA experiment, the sample has to be changed after a few shots and, therefore, the generator has to be discharged for safety reasons. In future industry applications, this limitation can be avoided by automated sample manipulation.

#### 2.2.3 Comparison to state-of-the-art pulse generators

Semiconductor-based pulsed power sources are currently of great research interest within the pulsed power community. Due to the complexity of their design, however, each power source is build according to the specific requirements of the respective application. The special challenge of building a pulsed power supply with a flexible output voltage of up to  $120\,kV$ , a maximum of  $600\,A$  pulsed current at durations of up to  $100\,\mu s$  with a fast rise time of around  $100\,ns$  has not been addressed before. There are several power supplies exceeding the mentioned specification in one parameter or another, but combining them in one generator is demonstrated in this work for the first time.

A much investigated approach for fast rise time, high-current, high-voltage pulses is the so-called Linear Transformer Driver (LTD) technology. The main idea behind the technology is to distribute the primary winding of a transformer on several boards, each driving a current through a single loop. The modules can be triggered simultaneously or arbitrarily to achieve a flexible output waveform. Prof. Jiang et al. [25] heavily investigated this technology and could successfully demonstrate a stack of 30 stages with 29 kV output voltage, 240 A load current and a rise time below 80 ns. While being scalable to some extend, the design relies on magnetic cores that can pose a major cost factor. The compact generator presented in [25] could only deliver a pulse of up to 170 ns in length before showing saturation effects of the core. Upscaling of the pulse length by a factor of 600 while also doubling the output current is not an economic solution.

Creating high-voltage, high-current generators with pulse lengths in the microsecond range, many companies developed interesting circuits based on the Marx generator topology investigated in this work. A very high-voltage version was presented by Applied Energetic [26], being able to charge a capacitive load up to 700 kV in several microseconds. The output waveform could be modulated by individual switching of each module. As the designed load was capacitive, the nominal charging current of 20 A lacks behind the requirement for the GESA application.

Semiconductor-based Marx generators have been investigated as replacement for thyratron-driven pulse circuits for microwave sources. A high-voltage generator under development by Diversified Technologies [27] was designed for a total output voltage of  $100...500\,kV$  and a pulse current of up to  $500\,A$  for a duration of up to  $5\,\mu$ s. The design could be validated up to an output voltage of  $40\,kV$  and a rise time of  $300\,ns$  was achieved. Individual control of all stages enables the possibility of active pulse shaping [14], but the high stage voltage of around  $12\,kV$  allows only for a coarse voltage adjustment. The lack in rise time and the high module voltage render this setup uninteresting for this project. Stangenes Industries [22] presented a generator able to deliver pulses of  $50\,kV$  at  $250\,A$  pulsed current for a duration of  $5\,\mu$ s. Again, the design is scalable, but since all parameters are inadequate for our application, a complete new design would be required. Additionally, the output rise rate is limited to  $150\,ns$ .

A very promising approach is currently investigated by Redondo et al. [28] as driving source for kicker magnets: Employing many paralleled very fast SiC MOSFET switches, a semiconductor-based Marx generator is under development with a module voltage of 800 V for a total output voltage of 40 kV and 3.2 kA load current. The current design is for a pulse length up to 3  $\mu$ s, but the current is well above the requirements. Therefore, the stage capacitance is in the required range for this project. Until present, a prototype with an output voltage of 3.2 kV at a load current of 2.7 kA was demonstrated for a pulse duration of 2  $\mu$ s. The rise time was measured to be 50 ns. The scalability of this design remains object to further studies, since a generator constructed after the prototype will be in the 4 m range for 40 kV already. In combination with the high price of the employed switching elements, this design is not suitable for investigated application.

## 2.3 Generator component requirements

In the course of the development of the generator, many challenges have be to overcome. The following sections define the requirements for the employed pulse components (switches and capacitors) and their control logic. Subsequently, an overview over the expected fast-varying electro-magnetic fields the circuitry has to withstand and the spacial constraints the generator has to meet is given.

#### 2.3.1 Pulse switches and parasitic properties

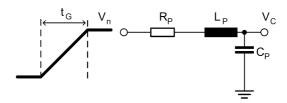

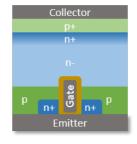

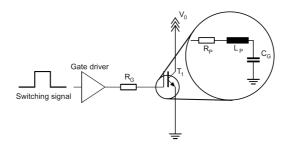

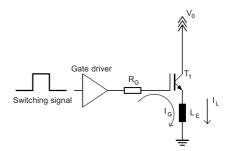

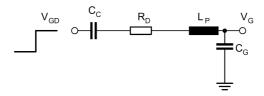

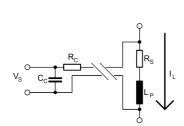

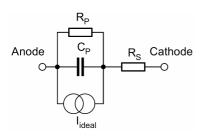

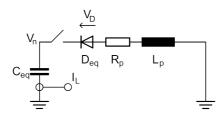

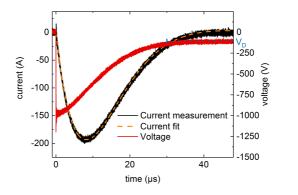

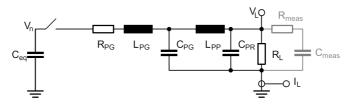

As mentioned in Sec. 2.1.2, the very fast voltage rise rate across the GESA cathode of  $100\,\text{kV}/100\,\text{ns}$  is one of the most challenging requirements to meet. The output voltage rise time can be expressed as geometric addition of the rise time contribution of the sub-components [29]. In first approximation, the generator can be considered a voltage source with limited rise time  $t_G$  connected to an RLC circuit. As worst-case simplification, all parasitic values of the circuit can be combined in lumped elements as depicted in Fig. 2.10. The resistive component includes all losses of the circuit, such as ohmic losses and radiated losses.  $L_P$  combines the parasitic inductive properties of the generator itself, the connection of the generator to the GESA and the GESA device.

Figure 2.10: The equivalent circuit of generator and connected GESA device: the generator output voltage has a limited rise time  $t_{\rm G}$  and is connected to an RLC circuit with lumped elements containing all parasitic resistive components of the circuit  $R_{\rm P}$  and all inductive components (generator, connection and GESA device), charging all parasitic capacitive components of the circuit (generator, connection and GESA cathode).

As discussed in Sec. 2.1.3, the GESA cathode has a substantial capacitive component that needs to be charged. For the worst-case estimation, all stray capacitances to ground are added to the cathode capacitance to form one component  $C_{\rm P}$ , including the stray capacitance of the generator and the capacitance of the connecting leads. The presented equivalent circuit is only valid as long as the cathode plasma has not ignited. Afterwards, a substantial current flows across the cathode-anode gap, shunting the cathode capacitance. Therefore, this picture is only valid to estimate the slowest voltage rise rate that can be expected with the given circuit parameters.

As first step in the design process, fast enough switching elements have to be selected as not to hinder the cathode charging process. Since the circuit parameters are not known a-priori, a target speed has to be defined for the development of the switching circuitry.

Each stage has an inherent rise time  $t_{\rm S}$ . Due to many individual stages, an additional timing jitter  $t_{\rm J}$  has to be assumed. A worst-case estimation for the rise time of the idealized generator  $t_{\rm G}$  is the sum of both rise times as in Eq. 2.3.

$$t_{G} = t_{S} + t_{J} \tag{2.3}$$

The precise rise time of the connected RLC network  $t_{\rm RLC}$  will be dependent on the generator layout and physical dimensions. However, the cathode voltage rise time  $t_{\rm C}$  can be calculated by the geometric sum of the components following Eq. 2.4 (compare Sec. 2.5). The resulting simulations to meet the requirements of the GESA device are presented in Sec. 6.1.4.

$$t_{\rm C} = \sqrt{t_{\rm G}^2 + t_{\rm RLC}^2}$$

(2.4)

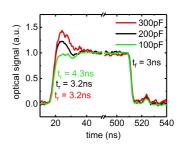

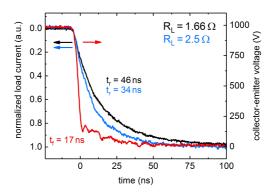

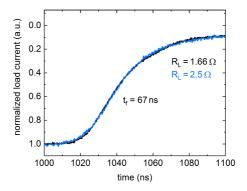

A target rise time  $t_{\rm S}$  of 50 ns at 600 A load current in hard switching conditions was chosen for a single stage in order to allow for a sufficient safety margin in the design process. As the current will ramp up slowly in an RLC circuit, the expected rise time in the application will be much faster. Thereby, the generator output voltage rise time is mainly dependent on the circuit parameters (resistance, stray capacitance and stray inductance) instead of the switching elements. Unfortunately, commercially available semiconductor switching elements meeting these specifications are very expensive. Therefore, Sec. 3 presents a novel approach to speed up cost-efficient voltage-controlled power semiconductor devices to meet the specifications.

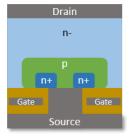

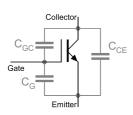

Using fast pulse switches also has an influence on the choice of free-wheeling

diodes. The steep voltage rise across them will lead to a capacitor short during the reverse recovery time of p-n diodes, possibly destroying the device. To overcome this limitation, using fast SiC Schottky-diodes as free-wheeling diodes is imperative when employing fast pulse switches.

Resulting from the requirement of an adjustability of the output voltage in steps of 1 % of the nominal 120 kV output voltage, the maximum permissible stage voltage is around 1 kV. For avoiding failure of the employed devices, a sufficient safety margin from the maximum expected voltage across the device to its specified maximum blocking voltage has to be chosen. Increasing the voltage rating of the device, however, increases the system costs both directly, since the devices are more expensive and indirectly, since higher voltage ratings require thicker substrates with increased losses [30]. Manufacturers of power semiconductor devices intended for use in distributed supply networks recommend a safety factor up to 2.5 (device blocking voltage / expected line voltage) [30]. Due to the schematic of the generator investigated in this work (see Sec. 2.2), the voltage across the switching device is clamped by the stage capacitor in close vicinity. The manufacturer's recommendation for this DClink-like architectures still includes a safety-factor of around 50 % due to the absence of larger network disturbances such as lightnings [30]. For a bus voltage of 1 kV, the recommendation is to use devices rated for 1.7 kV. One major effect related to the voltage de-rating is the avalanche breakdown initiated by cosmic radiation [30]. The chance of an avalanche breakdown is strongly dependent on the time integral of electric field inside the device and grows exponentially with increased voltage close to the rated voltage [30]. Felgemacher et al. could show an increased failure rate for 1.2 kV Si-IGBTs operated at 1 kV DC voltage [31]. However, since the generator presented in this work is only powered during experiments and is located under a solid concrete ceiling, both exposure time to DC voltage and cosmic ray intensity are low. Out of economical considerations, for a bus voltage of 1 kV devices with a maximum blocking voltage of 1.2 kV were used. This dimensioning of power semiconductors is commonly used in literature for pulsed power applications ([32], [33], [34], [35]). Therefore, 120 stages are required to achieve the nominal output voltage of 120 kV. If an active grid control with a 30 kV voltage swing is to be implemented, additional stages will be required. As result, the total amount of stages will be in the range of 150.

#### 2.3.2 Pulse switch control

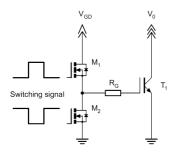

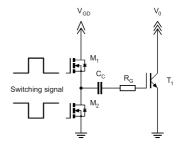

In multi-stage semiconductor-based pulse generators, the most efficient method of pulse switch control depends on the application. If all switches are to be switched simultaneously, a direct inductive charging of each gate is the option with the least amount of auxiliary circuitry required [36]. On the other hand, an overcurrent protection or safety relevant functions can only be implemented into the control unit. Dedicated drivers for the power semiconductors are to be used to achieve fast switching speeds; the control signal may be coupled magnetically to the stage and processed by logic on the stage [37]. The same transformer can be used to transfer both the trigger signal and the supply current [37]. However, magnetic coupling also comes with certain drawbacks: the employed transformers need to isolate the full output voltage (i.e. 120 kV) and increase the stray capacitance to ground. Secondly, no data return channel is available for detecting faults on a stage during the pulse. Most importantly, in order to drive all stages individually, many individual transformers have to be fabricated.

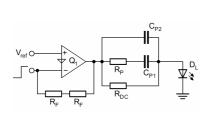

Instead of magnetic coupling, the presented generator uses optical signal transmission for galvanically isolated duplex communication with each stage. Details on the transmission circuit are given in Sec. 4.3.1. Thereby, stray capacitances to ground can be minimized [22].

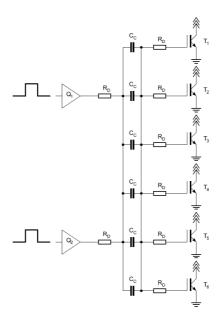

Since every stage has to perform an individual switching sequence in the course of a pulse, there are basically two means of switching signal distribution. The first being a localized control circuitry on ground potential, controlling directly the ON/OFF sequence of every stage with no or little logic circuitry on each stage. The second method is for each stage to generate its own switching commands and the control unit only being used for starting and ending the pulse. Many researchers favor the first approach (e.g. [22], [25], [14], [34]) for its obvious advantages. Having one control circuitry for all stages allows for direct control over the switching process, necessary to implement a closed-loop control of the output voltage. If the stages are reduced to merely switches, all protection circuits have to be implemented in the control unit. Any error in the optical signal, either by EMI or wrong data from the control unit, can potentially lead to a destruction of the generator. The high number of optical connections from the control unit to each generator stage (around 150 in the presented design), all controlled simultaneously during the pulse and synchronized with respect to pulse start pose a great challenge for the control unit,

both on the hardware and the software side. Moreover, approximately 300 optical fibers (two per stage to allow for duplex communication) outside of the generator increase the project complexity from a manufacturing point of view. In order to reduce the complexity of the control unit, a novel approach is investigated in this work: the switching signal generation during the pulse is not performed localized on the control unit, but is rather distributed on each single stage. Equipping each stage with a fast programmable logic, the switching signals can be pre-programmed before the pulse and executed once a synchronization signal has been sent. The control unit handles the optical distribution to enable communication with the stages. By introducing a novel optical bus system in Sec. 5.1.2, the optical connections from and to the control unit can be drastically reduced. Thereby, communication with the complete generator is possible using only 17 fiber optic connections. The logic on every stage incorporates safety functions such as maximum pulse duration monitoring, overcurrent protection, temperature measurement, and a pulse capacitor discharge functionality. The optical return channel allows for a generator emergency turn-off if any stage detects an error. For details on the control scheme, see Sec. 5.

The design was developed under the presumption that the GESA device will behave deterministically with respect to the required drive voltage pulse shape. However, since this hypothesis needs to be validated in future works, the generator was built with the possibility to use the stages also with a localized control circuitry in case a closed-loop control will become necessary in the future.

#### 2.3.3 Dimensioning of pulse capacitors

To drive the GESA cathode, a long flat top pulse is required. For achieving the desired flat top quality of  $1\,kV$  for a pulse duration of at least  $75\,\mu s$  at maximum output current of  $600\,A$ , the capacitor droop needs to be minimized. The obvious solution is to employ very big stage capacitances  $C_S$ . Since all stage capacitances are connected in series during the pulse, the equivalent capacitance  $C_{\rm eq,const.}$  of an erected Marx generator using a constant number of mactive stages can be calculated according to Eq. 2.5.

$$C_{\text{eq,const.}} = \frac{C_{S}}{m}$$

(2.5)

The maximum pulse duration  $t_{P,const.}$  after which the output voltage has dropped by  $\Delta V_n$  at constant pulse current  $I_P$  is, hence, given by Eq. 2.6.

$$t_{P,const.} = \frac{C_{eq,const.} \cdot \Delta V_n}{I_P}$$

(2.6)

With the above formulas  $^1$ , individual stage capacitances  $C_{\rm S}$  of 5.4 mF for a nominal output voltage  $120\,kV$  at  $1\,kV$  stage voltage are required. The total capacitance of such an arrangement would amount to 648 mF with a total stored energy of  $324\,kJ$ . On the one hand, using such large stage capacitances is a huge cost factor, on the other hand the spacial dimensions of these capacitances become impractical. In addition, most of the stored energy needs to be dumped after the experiment, increasing the complexity of the discharge circuit and being detrimental to the device efficiency.

The generator topology presented in this work enables the opportunity to use m stages necessary to achieve the required output voltage and to incorporate additional x spare stages in the design that can be activated upon demand, i.e. after the voltage has dropped by the stage charging voltage of 1 kV. The equivalent capacitance after the activation of i stages then is calculated following Eq. 2.7.

$$C_{eq,i} = \frac{C_S}{m+i}$$

$i = 0...x$  (2.7)

The maximum achievable pulse length given the pulse parameters then calculates according to Eq. 2.8.

$$\begin{split} t_{\mathrm{P,var.}} &= \frac{C_{\mathrm{eq,const.}} \cdot \Delta V_{\mathrm{n}}}{I_{\mathrm{P}}} + \frac{C_{\mathrm{eq,1}} \cdot \Delta V_{\mathrm{n}}}{I_{\mathrm{P}}} + \frac{C_{\mathrm{eq,2}} \cdot \Delta V_{\mathrm{n}}}{I_{\mathrm{P}}} + \dots \\ &= t_{\mathrm{P,const.}} + \sum_{\mathrm{i=1}}^{x} \frac{C_{\mathrm{eq,i}} \cdot \Delta V_{\mathrm{n}}}{I_{\mathrm{P}}} \\ &= \sum_{\mathrm{i=1}}^{x} \frac{C_{\mathrm{eq,i}} \cdot \Delta V_{\mathrm{n}}}{I_{\mathrm{P}}} \end{split} \tag{2.8}$$

$<sup>^{-1}</sup>$   $\Delta V_{\rm n}$  = 1 kV,  $I_{\rm P}$  = 600 A,  $t_{\rm P,const.}$  = 75  $\mu$ s, m = 120

With the same design pulse length, the stage capacitance sizes for the case of constant active stage count (const.) and varying stage count (var.) can be compared as in Eq. 2.9.

$$\begin{split} t_{P,const.} &= t_{P,var.} \\ \frac{\frac{C_{S,const.}}{m} \cdot \Delta V_n}{I_P} &= \sum_{n=1}^{\infty} \frac{\frac{C_{S,var.}}{m+i} \cdot \Delta V_n}{I_P} \end{split} \tag{2.9}$$

Eq. 2.10 expresses the simplified ratio between the stage capacitance values in both cases.

$$\frac{C_{S,const.}}{C_{S,var.}} = 1 + \sum_{i=1}^{x} \frac{m}{m+i}$$

(2.10)

The total capacitance values  $C_{\rm total,const.}$  in case of constant stage number and  $C_{\rm total,var.}$  scale according to Eq. 2.11 for m >> x as do the stage capacitance values.

$$\frac{C_{\rm total,const.}}{C_{\rm total,var.}} = \frac{m}{m+x} \cdot \frac{C_{\rm S,const.}}{C_{\rm S,var.}} \approx \frac{C_{\rm S,const.}}{C_{\rm S,var.}}, m >> x \tag{2.11}$$

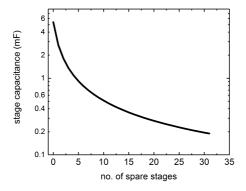

Figure 2.11: Stage capacitance value in dependence on the number of available spare stages ( $\Delta V_n = 1 \, kV, \, I_P = 600 \, A, \, t_{P, \rm const.} = 75 \, \mu s, \, m = 120$ ).

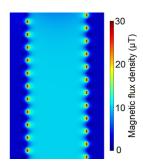

Fig. 2.11 illustrates the necessary stage capacitance value with respect to the available spare stages. Zero spare stages corresponds to the value of  $C_{\rm S,const.}$ . As visible, the reduction in necessary stage capacitance is very pronounced for small numbers of spare stages but becomes less pronounced for higher numbers. Whereas more stages reduce the stage capacitance size, they increase the system costs associated with using more electronic components.

The design of this work therefore uses 29 spare stages as balance between flexibility of more stages, mechanical dimensions of the generator and stage capacitance size. The individual stage capacitances have a size of around  $200\,\mu F$ , and the total energy stored in the generator is equal to  $15\,kJ$ .

#### 2.3.4 Protection against electro-magnetic interference

The great amount of high-speed logic devices involved in this project demands for adequate shielding of all components against electro-magnetic interference (EMI). A special challenge with respect to shielding in semiconductor-based Marx generators is based on the strong capacitive coupling into the control circuitry of each stage since it transiently operates at high-voltage potential during the pulse. For a low inductance, the control circuitry additionally has to be in close vicinity to the pulsed current passing through the switching elements, requiring measures against magnetic coupling. Without detailed information on parasitic oscillations that may only become measurable in the final assembly of the experiment, a rough estimation on the expected frequency content can be performed based on the expected output pulse shape.

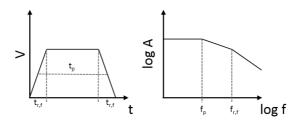

Figure 2.12: Pulse shape in time (left) and frequency domain (right). The high-frequency content of the pulse is predominantly determined by its rise and fall time. [38]

For a single trapezoidal pulse, the amplitude spectral density is determined by the pulse width  $t_P$  and the finite rise and fall time  $t_{\rm r,f}$ . After the two related cutoff frequencies  $f_P=1/\pi t_P$  and  $f_{\rm r,f}=1/\pi t_{\rm r,f}$  the amplitude spectral density drops with 20 dB/decade and 40 dB/decade, respectively [38].

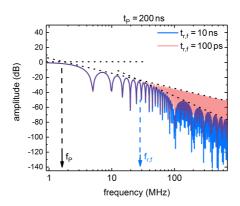

**Figure 2.13:** The amplitude spectral density for a pulse length of 200 ns with a rise and fall time of 100 ps (red) and 10 ns (blue). The dashed lines have a slope of -20 dB/decade and -40 dB/decade, respectively.

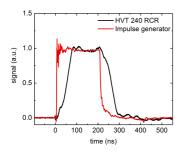

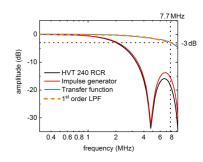

The assumption of a constant amplitude spectral density thereby overestimates the frequency content of the pulse as can be seen from the calculated spectrum of a trapezoidal pulse with  $t_{\rm P}$  = 200 ns and varying rise and fall time as depicted in Fig. 2.13.

Whereas the generator will be build for a total rise time in the order of 100 ns, the individual switching elements switch significantly faster. As worst-case estimation, a rise time of 30 ns has be assumed based on measurements presented in Sec. 5. The corresponding cut-off frequency for this rise time is in the order of 10 MHz, being equal to a wavelength of 30 m. Compared to the physical dimensions of the generator (i.e. a few meters), the large wavelength necessitates predominantly shielding against quasi-electro- and magneto-static interference. For inserting the optical fibers, holes in the shielding enclosures are necessary. While the holes can be considered as waveguides, their cut-off frequency is much higher (for diameters in the centimeter range) than the

frequency content emitted from the generator. To ensure proper damping of the interference signal, only the fraction between length L and diameter D of the opening is important. According to [39], a signal with a frequency below the cut-off frequency of an opening is attenuated by S (in dB) according to Eq. 2.12.

$$S = 32 \frac{L}{D} \tag{2.12}$$

Typically, an attenuation of 100 dB is considered largely sufficient for shielding enclosures [40]. Therefore, a length to diameter ratio of greater than four was chosen for all holes throughout this project, so the influence of holes can be neglected.

At low frequencies, shielding compartments made from highly conductive material such as copper or aluminum are more effective than low-conductive, high-permeability materials such as iron [38]. Using the maximum pulse duration of  $100\,\mu s$  of the generator,  $f_P$  equals to  $3.2\,kHz$ . Non-magnetic materials such as copper and aluminum weaken an external non-static magnetic field purely by the counter-action of induced currents whereas in magnetic materials, such as iron, the effect is magnified by their permeability when the skin-depth is smaller than the material thickness [38]. The skin-depth of a material can be calculated according to Eq. 2.13 from the exciting frequency f, the material's permeability  $\mu$  and resistivity  $\rho$  - table 2.13 gives an overview over the skin depth for the relevant materials in this work.

$$\delta = \sqrt{\frac{\rho}{\pi \cdot f \cdot \mu}} \tag{2.13}$$

| γ π·1·μ |  |

|---------|--|

|         |  |

|         |  |

|         |  |

| Material | Resistivity                               | Relative permeability | Skin-depth (at 3.2 kHz) |

|----------|-------------------------------------------|-----------------------|-------------------------|

| Cu       | $1.8 \cdot 10^{-8} \Omega\mathrm{m}$ [41] | 1                     | 1.2 mm                  |

| Al       | $2.8\cdot 10^{-8}\Omega\mathrm{m}$ [41]   | 1                     | 1.5 mm                  |

| Fe       | $5.5 \cdot 10^{-7} \Omega\mathrm{m}$ [41] | ca. 1000 [41]         | 200 μm                  |

Table 2.2: Skin depth for different commonly used materials.

Unfortunately, the limited resistivity of magnetic materials is detrimental to their shielding effectiveness. Additionally, saturation effects have to be taken into account when using magnetic materials. Therefore, shielding based on a combination of different materials may be advisable, with a non-magnetic layer on the outside reducing the magnetic field and protecting a inner magnetic (saturable) layer. In the following work, copper and aluminum shielding enclosures have been used, both due to their good shielding qualities (over a wide frequency range, independent of field strength) and ease of manufacturing with wall thicknesses of at least 1 mm and 2 mm, respectively. Sensitive parts, such as microprocessors and CPLDs, have been protected using an inner tinplate cabinet as second shielding (see Sec. 4.3.3).

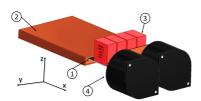

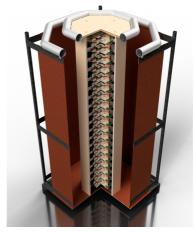

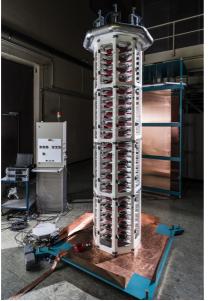

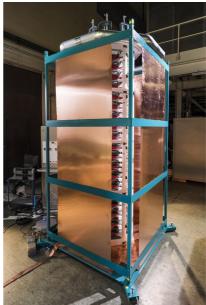

#### 2.3.5 Physical and mechanical constraints

Besides the electrical constraints, also mechanical constraints have to be considered. The final location of the generator will be inside an experimenting area with little ground space but a lot of headroom. The ground area for the generator is approximately 1.8 m x 1.8 m. The output of the generator will be connected to the topmost part of the GESA cathode, being at a height of approximately 2.2 m. Building the generator output to be as close as possible to this height will reduce the additional inductance introduced by wiring. For measurements, the generator should be quickly movable from the GESA experimenting site to a dedicated generator test stand located in the same building. To this end, the whole generator is designed with crane attachment points for easy movement within the building.

Being a prototype generator, easy maintenance is a major requirement. Therefore, oil insulation is not possible. All circuit boards must be quickly accessible for measurements, hence all connections are realized by plugs.

Due to the limited budget of the project, all materials used must be machinable within the institute's workshop - prohibiting the use of high-strength materials such as fiber-reinforced plastic or ceramics.

## 2.4 Charging and supply voltage distribution

Distribution of the pulse capacitor charging voltage is very simple in the classical Marx generator arrangement. Using active switches, new possibilities are enabled in a semiconductor-based Marx generator for transiently isolating

one stage from the next. Since the circuit boards need to be powered, also the auxiliary supply voltage needs to be distributed in a similar fashion. The following section compares approaches found in literature to the most promising solution implemented in this work.

#### 2.4.1 Pulse capacitor charging

In a Marx configuration, the charging path from one stage to the next for the pulse capacitors has to be isolated transiently during the pulse in order to avoid a short circuit [15]. Charging each stage using a transformer avoids this issue effectively [26]. On the other hand, a transformer isolating the total output voltage of 120 kV is required. Beside a strong increase in stray capacitance to ground and being a substantial cost factor, this counter-acts the idea of a Marx circuit: each component only has to withstand the stage charging voltage. Therefore, one stage is usually decoupled from the next with a high-impedance isolation element (compare Fig. 2.5). The permissible current via the isolation element thereby is dependent on the application, but should not cause a significant voltage droop of the capacitors in the course of a pulse. Under the assumption of a maximum leakage current of 10 % of the nominal pulse current of 600 A, the 1 kV potential difference from stageto-stage necessitates an impedance of at least  $R_C = 16 \Omega$  between the stages. Using charging resistors as decoupling elements Z<sub>C</sub>, the Marx generator as depicted in Fig. 2.5 resembles a series connection of a stage capacitor  $C_S$  and a resistor  $R_C = 2Z_C$ . The charging time  $\tau_{RC}$  of such an arrangement consisting of n stages can be approximated by Eq. 2.14 [15].

$$\tau_{\rm RC} = R_{\rm C} \cdot C_{\rm S} \cdot n^2 \tag{2.14}$$

Taking the high number of around 149 stages and the high stage capacitance of  $200\,\mu\text{F}$  of the design into account, the charging time can be approximated to  $72\,\text{s}$ . In reality this time is even longer since the formula assumes charging with a voltage source. The charging current in the first instant then amounts to  $62\,\text{A}$ , necessitating an expensive power supply. Charging the arrangement with a less powerful voltage source would, in turn, also increase the charging time.

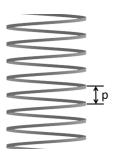

Instead of charging resistors, charging inductors are used in commercial sparkgap based Marx generators [15]. This concept has also been demonstrated successfully in semiconductor-based devices [37]. In first approximation, the current will start to increase linearly through the inductor during the pulse. To allow for the same amount of charge loss during the pulse of duration  $t_{\rm P}$  as compared to the previous case, a parasitic current  $I_{\rm P}$  of twice the value as for the charging resistors can be permitted (120 A). The necessary charging inductance  $L_{\rm C}$  can be calculated according to Eq. 2.15.

$$L_{\rm C} = \frac{V_0 \cdot t_{\rm P}}{I_{\rm p}} \tag{2.15}$$

With a stage voltage of  $V_0$  = 1 kV,  $L_{\rm C}$  calculates to 0.8 mH. As an air-cored inductor is required to avoid saturation effects, the physical dimensions of 149 individual inductors would become impractically large.

Employing active switches is a promising way to modulate the impedance of the charging path from low impedance during charging to high impedance during pulsing. Semiconductor switches have been demonstrated to work for several applications (see [42], [35]). The switching element used in this position has to block the current in both directions. IGBTs are in principle suitable if they are not co-packaged with a free-wheeling diode. Also MOSFETs can be used if their body-diode (compare Sec. 3.1.1) is eliminated by an additional external diode. Both possibilities, IGBT and MOSFET plus diode have a forward voltage drop in the order of 1...2 V. For generators with low stage count, this can be neglected. If 149 stages are used, however, the charging voltage of the top-most stage is reduced by a significant amount. In principle, the voltage drop per stage can be compensated using a small voltage source on each stage, powered from the supply voltage. With a charging current in the 1 A range, the required power of 1...2 W per stage, however, strains the supply voltage distribution system.

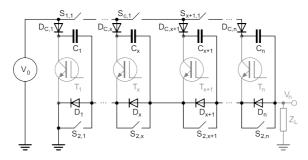

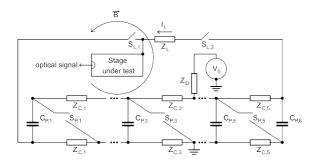

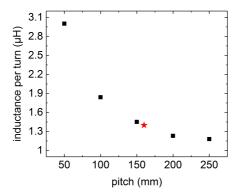

The requirement of a very low operation frequency (see Sec. 2.1.1) enables the possibility to use mechanical switches instead of semiconductors. High-voltage SMD relays are available, offering a contact resistance below  $100\,\mathrm{m}\Omega$  and can block voltage surges of up to  $2.5\,\mathrm{kV}$  (or  $1500\,\mathrm{V}$  RMS) [43]. They can carry a maximum current of  $2\,\mathrm{A}$ , but even  $1\,\mathrm{A}$  is enough to charge 149 stages to  $1\,\mathrm{kV}$  within the required  $30\,\mathrm{s}$ . Therefore, high-voltage SMD relays offer the most benefits of all available switches and were chosen as isolation components in the charging path of the stages. The resulting circuit is depicted in Fig. 2.14. During charging, the relay contacts  $S_{1,x}$  and  $S_{2,x}$  are closed, connecting the current-limited voltage source  $V_0$  to every pulse capacitor.

While in principle the free-wheeling diodes  $D_{\rm x}$  can be used to carry the return current during charging, any voltage drop across them is avoided by shorting them with relay contact  $S_{2,\rm x}.$  When a pulse is executed, all relays open and the circuit is equivalent to Fig. 2.7. After the pulse, the capacitors may be charged unevenly. To prevent any equalizing current from one capacitor to the next, diodes  $D_{\rm C,x}$  are in place. Using this configuration, a negative output voltage can be generated using a positive charging voltage for the capacitors.

Figure 2.14: The proposed Marx circuit including the charging path, consisting of a current-limited voltage source providing a positive voltage  $V_0$ , a charging diode  $D_{C,x}$ , and two high-voltage relay contacts  $S_{1,x}$  and  $S_{2,x}$ .

#### 2.4.2 Generating the supply voltage

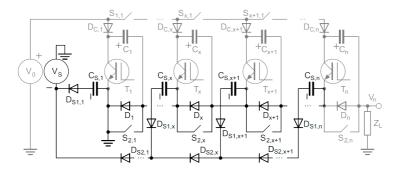

In addition to the power transfer to the pulse capacitors, also the logic on each stage needs to be powered and transiently isolated. A rough estimation of the required power, taking the microprocessors, the charging relays, and the optical fiber transmission (see Sec. 5.1.3) into account, the required current at  $5\,\mathrm{V}$  level will be in the  $500\,\mathrm{mA}$  range. For 149 stages, the required power accumulates to approximately  $400\,\mathrm{W}$ .

As for the pulse capacitor charging voltage discussed in the previous section, distributing the voltage via a transformer is an option and has been successfully demonstrated [37]. The same arguments as in the previous section still hold true, namely the need for an expensive custom-made transformer and increased stray capacitances to ground.

Since a solution for the pulse capacitor charging voltage was already presented,

one option for the supply voltage would be a step-down converter, creating the needed supply power from the pulse capacitor voltage. To transfer the required power at a current level of 1 A (absolute maximum rating: 2 A) necessitates a charging voltage of around 400 V. Realizing a DC-DC converter with those specifications is easily possible but, in turn, demands for the pulse capacitors to be charged to nearly half the nominal voltage. Especially during the first tests of the device and trouble-shooting, the charged pulse capacitors pose a risk to the operator and necessitate additional safety measures.

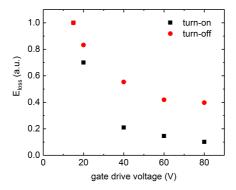

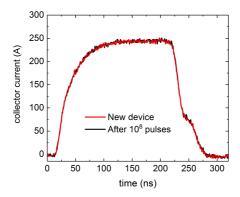

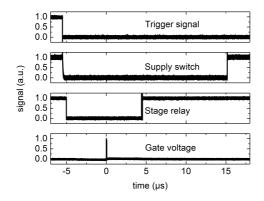

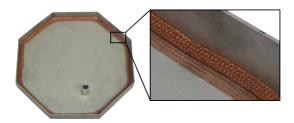

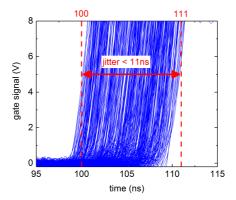

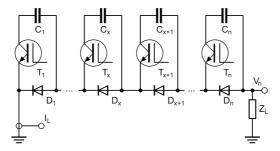

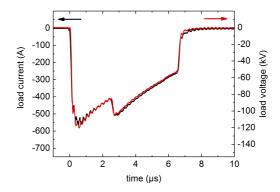

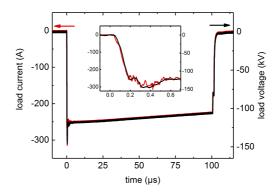

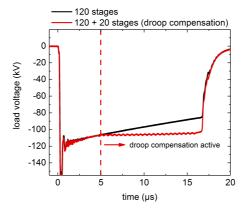

Comparing the challenge of the supply voltage distribution to the challenge of pulse voltage distribution, their similarity suggest a similar solution. As mentioned before, distributing the supply power at elevated voltage levels is necessary. Since a DC-DC converter is necessary in every case, it can be designed to have a wide range of input voltages. Thereby, in contrast to the pulse voltage, a certain parasitic voltage drop across the isolation elements can be tolerated. The most efficient solution therefore is to use diodes for transient stage decoupling. Fig. 2.15 shows the circuit diagram including the current-limited voltage source providing  $V_{\rm S}$ , negative with respect to ground.