# Circuit Design and Compact Modeling in Printed Electronics Based on Inorganic Materials

Zur Erlangung des akademischen Grades eines

Doktors der Ingenieurwissenschaften

von der KIT-Fakultät für Informatik des Karlsruher Instituts für Technologie (KIT)

genehmigte

# Dissertation

von

# M.Eng. Gabriel Cadilha Marques

aus Nürnberg

Tag der mündlichen Prüfung: 24.04.2020

Erster Gutachter: Prof. Dr. Mehdi Baradaran Tahoori, KIT

Zweiter Gutachter: Prof. Dr. Michael Beigl, KIT

Dritter Gutachter: Prof. Dr. Jasmin Aghassi-Hagmann, KIT

To my parents, for their continuous encouragement.

Gabriel Cadilha Marques Hermann-von-Helmholtz-Platz 1 76344 Eggenstein-Leopoldshafen

Hiermit erkläre ich an Eides statt, dass ich die von mir vorgelegte Arbeit selbstständig verfasst habe, dass ich die verwendeten Quellen, Internet-Quellen und Hilfsmittel vollständig angegeben haben und dass ich die Stellen der Arbeit - einschließlich Tabellen, Karten und Abbildungen - die anderen Werken oder dem Internet im Wortlaut oder dem Sinn nach entnommen sind, auf jeden Fall unter Angabe der Quelle als Entlehnung kenntlich gemacht habe.

Eggenstein-Leopoldshafen, 24.04.2020

Gabriel Cadilha Marques

# **Acknowledgments**

Firstly, I would like to thank my advisers, Prof. Mehdi Tahoori and Prof. Jasmin Aghassi-Hagmann for the great time I have had during my doctoral studies. I am very grateful for the support and encouragement given to me. The discussions we had over the past years have helped me to grow as a researcher.

Secondly, I would like to thank Prof. Michael Beigl for being the second referee of my thesis.

Thirdly, I am very thankful to Prof. Horst Hahn for the wonderful collaboration with his group. Although I myself was not a member of the group, I always felt considered as part of the group.

My thanks goes also to the current and former group leaders of the printed electronics group at the Institute of Nanotechnology (INT), Dr. Ben Breitung and Prof. Subho Dasgupta, for our fruitful discussions and for sharing the facilities with me.

I am additionally thankful to Dr. Suresh Garlapati and Dr. Falk von Seggern for introducing me to the printing process and the characterization equipment.

My special thanks goes to Simone Dehm. Without her help, the preparation of the devices would have taken much more time.

To my PhD fellows, Ahmet Erozan, Xiaowei Feng, Farhan Rasheed, Felix Neuper, Alexander Scholz, Parvathy Sukkurji and Dennis Weller, I would like to thank them for their being some of my best critics, therefore helping me to improve my work. In this regard, I especially want to thank Surya Singaraju for our many discussions and for helping me with maintenance tasks.

Furthermore, I want to thank the undergraduate students Anushka Birla, Tongtong Fu, Ferdous Imam, Luca Kosche, Sana Jain, Adrianus Sukuramsyah, Guan Ying Wang and Kevin Wang for their great work.

I am very thankful to Prof. Klaus Schmidt for introducing me to the field of printed electronics and for establishing the contact with the Karlsruhe Institute of Technology (KIT), during my undergraduate studies.

I am also very thankful for the support of my friends over the past years. I want to thank my girlfriend, Alexandra, for her love and being my motivation and inspiration. She always encouraged me and helped me a lot in improving my English.

I also want to thank my parents, Dagoberto and Maria da Conceição, for their endless support.

The Karlsruhe House of Young Scientists (KHYS) supported my stay abroad at the University of Minnesota, for which I am very grateful.

Lastly, I thankfully acknowledge the financial support of the Helmholtz Gemeinschaft in the form of the Helmholtz Virtual Institute VI530.

# **Abstract**

The field of printed electronics (PE) is a young research area, relative to conventional silicon technology. The idea behind PE is to print electronic components, including microelectronic circuits, through out of solution processable materials which are fabricated in an additive process. The additive printing process brings some benefits with it, like avoiding any expensive mask and on demand fabrication. Currently, organic materials are state of the art for realizing printed devices. Semiconductors, conductors and dielectrics are available as organic based materials. These organic materials are used to print solar cells, diodes, resistors, capacitors as well as field-effect transistors (FETs) on rigid (glass, silicon) or flexible substrates (paper, plastic).

However, organic electronics mostly uses p-type devices and field-effect mobility values are lower than in silicon based devices, where threshold voltages are much lower. Also, all printed circuits based on organics are rare. For future applications, eg. Internet of Things (ITO), soft electronics for robotics or smart sensors, it is essentially to develop a fully printed technology together with suitable circuit designs.

An interesting alternative to organic semiconductors are oxide semiconductors. For example, indium oxide provides intrinsic mobility values of approximate  $100~\rm cm^2\,V^{-1}\,s^{-1}$ . Higher mobility values lead to higher current densities and enhance the overall speed of the devices. Oxide semiconductors are inkjet printable, integrateable into a nontoxic fabrication process, and optically transparent. In oxide electronics, n-type oxide semiconductors are common, while p-type oxide semiconductors are rather rare. The exhibited intrinsic mobility of p-type metal oxides is three orders of magnitude lower than the values shown by n-type metal oxide semiconductors. Unfortunately, metal oxides, typically, require high annealing temperatures ( $\sim 400~\rm ^{\circ}C$ ), to form the desired transition phase. This is a disadvantage compared to organic semiconductors where room temperature processes are frequent.

The goal of this thesis is therefore to develop an inorganic printed electronics technology with corresponding modeling methodologies to capture device behavior for industry standard circuit simulators as well as circuit designs as building blocks for future applications. To reduce the high supply voltage requirements ( $\geq 5$  V) in PE, alternative gating approaches for FETs are considered. One approach is to replace the dielectric with an electrolyte. Due to the formation of a Helmholtz double layer (HDL), a FET with a high gate-capacitance ( $\sim 5~\mu F \, {\rm cm}^{-2}$ ) is expected, reducing the voltage requirements to  $\sim 1~{\rm V}$ . By combining the indium oxide channel with the electrolyte-gating approach, high performance devices with low voltage requirements are available in PE.

The structure of this thesis is to firstly characterize electrolyte-gated field-effect transistors (EGFETs) with indium oxide channels, and secondly create a predictive model which is able to be integrated into a circuit simulator. Following, reliable design topologies for the presented transistor technology are shown. The evaluation of the design topologies will take place on basic microelectronic digital logic cells and ring

oscillator structures.

To model EGFETs, different modeling approaches for the different transistor regions are needed. The above threshold region is modeled accurately through the Curtice model. Furthermore, the Curtice model only requires a few parameters and depict the linear and saturation regions with only one equation. For the subthreshold region, the conventional silicon subthreshold model predicts the electrical characteristic of the EGFET very well. Smoothness and continuity between the simulated below and above threshold regions are ensured with an interpolation scheme that models the near threshold region. This modeling approach provides a good match between the measured and simulated data.

The developed model is integrated into a simulation program with integrated circuit emphasis (SPICE) and into a process design kit (PDK) to support the development of new applications. Therefore, the behavior of microelectronic circuits based on EGFETs are predictable through simulation. In addition, simulations are used to evaluate the performance of circuits under different environmental conditions, i.e. effects of humidity on EGFETs based applications.

Since p-type oxide semiconductors, which have equal performance than n-type semiconductors are not available, complementary circuit designs are not feasible in oxide electronics. For this reason, the pull-up network, which is based on p-type FETs in conventional microelectronics, is replaced through either a resistor or an n-type EGFET. The pull-down network is based on one or more n-type EGFETs in both cases.

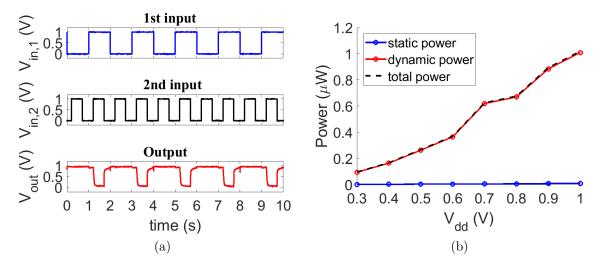

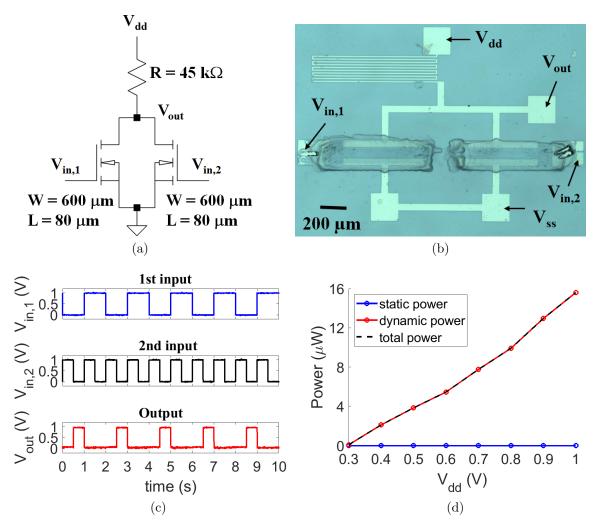

The first approach to replace the p-type EGFET is demonstrated on an inverter designed within the transistor-resistor logic (TRL) topology. As result, the inverter has a gain of around -5 and a propagation delay time of  $\sim 0.9$  ms, measured at a supply voltage of 1 V. At the same voltage level, the sequentially built three stage ring oscillator, oscillates at a frequency of 296 Hz. Standard logic gates (NAND, NOR and XOR) are likewise feasible with EGFETs in TRL.

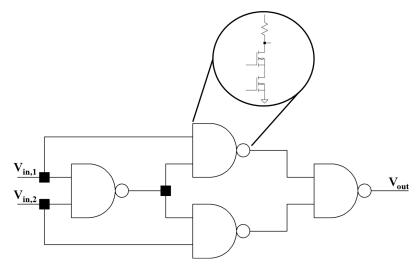

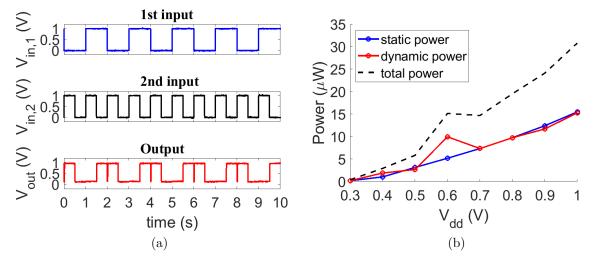

It is also possible to design microelectronic circuits within the transistor-transistor logic (TTL) topology. In TTL, the resistor in the pull-up network is supplanted by a depletion mode EGFET. All logic gates, show similar performance to the TRL based cells, but the ring oscillator operates in the sub-kHz regime. Furthermore, in a NAND gate, the power consumption is shown to be reduced by a factor of 6.

# Zusammenfassung der Arbeit

Die gedruckte Elektronik ist ein im Vergleich zur konventionellen Siliziumtechnologie junges Forschungsgebiet. Die Idee hinter der gedruckten Elektronik ist es elektronische Bauteile wie Widerstände, Kapazitäten, Solarzellen, Dioden und Transistoren mit gängigen Druckmethoden herzustellen. Dabei ist es möglich die elektronischen Bauteile auf unbiegsamen Substrate, wie Glas oder Silizium, als auch auf biegsamen Substrate, wie Papier und Folie, zu drucken. Aufgrund des Druckprozesses, sind die Herstellungskosten gering, da drucken ein additiver Prozess ist und somit teure Masken obsolet sind.

In einem Feldeffekttransistor, wird der Halbleiter zwischen zwei Elektroden (Drainund Source) gedruckt. Die Drain- und Source-Elektroden werden dabei durch einen Vakuum- oder Druckprozess abgeschieden und strukturiert. Der halbleitende Kanal wird durch einen Dielektrikum von der Gate-Elektrode isoliert. Auch für das Dielektrikum und die Gate-Elektrode sind ein Vakuum- oder Druckprozess denkbar. Standardmäßig finden organische Materialien Einsatz in der gedruckten Elektronik. Leider weisen organische Halbleiter, in einem Feldeffekttransistor, nur eine geringe Ladungsträgerbeweglichkeit ( $\leq 1~{\rm cm}^2\,{\rm V}^{-1}\,{\rm s}^{-1}$ ) auf. Die niedrige Ladungsträgerbeweglichkeit führt zu einer geringen Ladungsträgerdichte im Halbleiter und als Resultat zu geringen Stromdichten. Auch sind größtenteils nur p-leitende Halbleiter für den Einsatz in Schaltungen vorhanden, weswegen die meisten Schaltungen nur p-leitende Feldeffekttransistoren besitzen. Ein weiterer Nachteil der organischen Elektronik ist, dass die eingesetzten Dielektrika mit dem Halbleiter eine mangelhafte Grenzfläche bildet. Deshalb sind Versorgungsspannungen in Bereich von 5 V keine Seltenheit.

Eine interessante Alternative zu organischen Halbleitern sind Materialien die der Kategorie der Oxide zugeordnet sind. Zum Beispiel in Indiumoxid (In<sub>2</sub>O<sub>3</sub>) ist eine Ladungsträerbeweglichkeit um die 100 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> messbar. Leider sind durch Oxide realisierte p-leitende Feldeffekttransistoren sehr selten, weshalb die meisten Schaltungen auf n-leitenden Feldeffekttransistoren basieren. Ein weiterer Nachteil von Metalloxidhalbleitern is das hohe Glühtemperaturen ( $\sim 400$  °C) benötigt werden um die richtige Kristallstruktur zu erzielen.

Durch den Einsatz eines Elektrolyten, anstatt eines Dielektrikum, werden die benötigten hohen Versorgungsspannungen auf 1 V reduziert. Der Grund für die Reduzierung der Versorgungsspannung liegt in der hohen Kapazität ( $\sim 5~\mu F\, cm^{-2}$ ), die sich zwischen der Gate-Elektrode und dem Kanal ausbildet. Die optimale Grenzfläche zwischen der Gate-Elektrode und dem Elektrolyten sowie als auch zwischen dem Elektrolyten und dem Kanal, wo sich eine Helmholtz-Doppelschicht ausbildet, ist der Grund für die hohe Kapazität.

In dieser Arbeit, werden die Vorteile der hohen Ladungsträgerbeweglichkeit, resultierend von einem Indiumoxid-Kanal, und der niedrigen Versorgungsspannungen, durch den Einsatz eines Elektrolyten als Isolator, in einem gedruckten Transistor kombiniert. Daher ist das Ziel zunächst Transistoren basierend auf einem Elektrolyten und

Indiumoxid-Kanal zu charakterisieren und zu modellieren. Auch werden Möglichkeiten zum Schaltungsentwurf mit der hier vorgestellten Transistortechnologie ausgearbeitet. Der Schaltungsentwurf wird anhand mikroelektronischen Zellen und Ringoszillator-Strukturen verifiziert.

Wichtig für den Schaltungsentwurf sind Modelle die fähig sind die elektrischen Eigenschaften eines Transistors abzubilden. Dabei muss die simulierte Kurve Stetigkeit und Kontinuität aufweisen um Konvergenzprobleme während der Simulation zu verhindern. Zur Modellierung der elektrischen Eigenschaften und Ströme der Transistoren wird ein Modell basierend auf den Curtice-Modell entwickelt. Der Bereich über der Schwellwertspannung wird daher durch das Curtice-Modell abgebildet und der Bereich unter der Schwellspannung durch ein aus Siliziumtransistoren bekanntes Standard-Modell beschrieben. Kontinuität und Stetigkeit wird durch eine Interpolation zwischen den beiden Transistormodellen gewährleistet. Ein Verglich zwischen gemessenen und simulierten Daten zeigt das das Modell die hier vorgestellte Transistortechnologie sehr gut abbilden kann.

Das entwickelte Transistormodel wird zur unterstützung des Schaltungsentwurf in einem Prozesskit (PDK) integriert. Dadurch ist das Verhalten einer Schaltung durch Simulation vorhersehbar. In der Simulation können auch der Einfluss der Umwelt, z.B. Luftfeuchtigkeit, auf die Transistoren analysiert werden.

In der digitalen Schaltungstechnik wird ein p-leitender Feldeffekttransistor verwendet um ein Eingangssignal hochzusetzen, während um ein Signal runterzusetzen, ein n-leitender Feldeffekttransistor von Vorteil ist. Da p-leitende Oxide selten und unzuverlässig sind, wird der p-leitende Feldeffekttransistor durch einen Widerstand (Transistor-Widerstand-Logik (TRL)) oder einen n-leitenden Feldeffekttransistor (Transistor-Transistor-Logik (TTL)) ersetzt. Ein Inverter in TRL weist bei einer Versorgungsspannung von 1 V einen Verstärkungsfaktor von ungefähr -5 auf und eine Signalverzögerung von 0.9 ms. Die Oszillatorfrequenz im entsprechend Ringoszillator beträgt 296 Hz. Weitere Logikgatter (NAND, NOR und XOR) sind ebenfalls realisierbar mit TRL-Entwürfe.

In TTL wird der p-leitende Feldeffekttransistor durch einen n-leitenden Verarmungstyps Feldeffekttransistor ersetzt. Die in der TTL entworfene Logikgatter verhalten sich identisch zu den TTR-Zellen aber die Frequenz vom Ringoszillator steigt bis in den unteren kHz-Bereich an. In TTL ist es ebenfalls möglich die Verlustleistung um einen Faktor von 6 zu reduzieren.

# List of publications

# **Journals**

- G. C. Marques, A. M. Sukuramsyah, A. Arnal, S. Bolat, A. Aribia, X. Feng, S. A. Singaraju, E. Ramon, Y. Romanyuk, M. Tahoori and J. Aghassi-Hagmann, "Fabrication and Modeling of pn-Diodes Based on Inkjet Printed Oxide Semiconductors", *IEEE Electron Devices Letters*, vol. 41, no. 1, pp. 187-190, 2020.

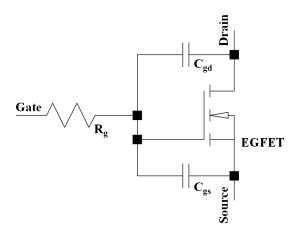

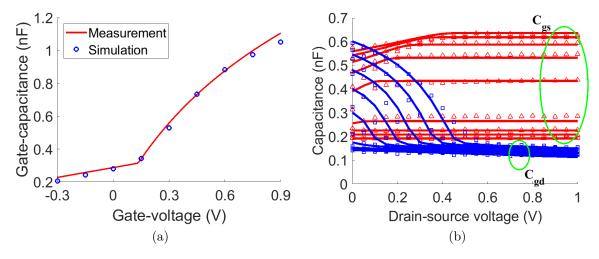

- X. Feng, G. C. Marques, F. Rasheed, M. B. Tahoori and J. Aghassi-Hagmann, "Nonquasi-Static Capacitance Modeling and Characterization for Printed Inorganic Electrolyte-Gated Transistors in Logic Gates", *IEEE Transactions on Electron Devices*, vol. 66, no. 12, pp. 5272-5277, 2019.

- J. Jeong, G. C. Marques, X. Feng, D. Boll, S. A. Singaraju, J. Aghassi-Hagmann, H. Hahn and B. Breitung, "Ink-Jet Printable, Self-Assembled, and Chemically Crosslinked Ion-Gel as Electrolyte for Thin Film, Printable Transistors", *Advanced Materials Interfaces*, vol. 6, no. 21, pp. 1901074, 2019.

- X. Feng, C. Punckt, **G. C. Marques**, M. Hefenbrock, M. B. Tahoori and J. Aghassi-Hagmann, "Impact of intrinsic capacitances on the dynamic performance of printed electrolyte-gated inorganic field effect transistors", *IEEE Transactions on Electron Devices*, vol. 66, no. 8, pp. 3365 3370, 2019.

- G. C. Marques, F. von Seggern, S. Dehm, B. Breitung, H. Hahn, S. Dasgupta, M. B. Tahoori and J. Aghassi-Hagmann, "Influence of humidity on the performance of composite polymer electrolyte-gated field-effect transistors and circuits", *IEEE Transactions on Electron Devices*, vol. 66, no. 5, pp. 2202 2207, 2019.

- G. C. Marques, D. Weller, A. T. Erozan, X. Feng, M. Tahoori and J. Aghassi-Hagmann, "Progress report on 'From printed electrolyte-gated metal-oxide devices to circuits'", *Advanced Materials*, vol. 31, no. 26, p. 1806483, 2019.

- A. T. Erozan, G. C. Marques, M. S. Golanbari, R. Bishnoi, S. Dehm, J. Aghassi-Hagmann, M. B. Tahoori, "Inkjet printed EGFET-based physical unclonable function design, evaluation, and fabrication", *IEEE Transactions on Very Large Scale Integration Systems*, vol. 26, no. 12, pp. 2935 2946, 2018.

- D. Weller, **G. C. Marques**, J. Aghassi-Hagmann, and M. B. Tahoori, "An inkjet printed low-voltage latch based on inorganic electrolyte-gated transistors", *IEEE Electron Device Letters*, vol. 39, no. 6, pp. 831 834, 2018.

- S. K. Garlapati, G. C. Marques, J. S. Gebauer, S. Dehm, M. Bruns, M. Winterer, M. B. Tahoori, J. Aghassi-Hagmann, H. Hahn and S. Dasgupta, "High performance printed oxide field-effect transistors processed using photonic curing", *Nanotechnology*, vol. 29, no. 23, pp. 235205, 2018.

- F. Rasheed, M. S. Golanbari, G. C. Marques, M. Tahoori and J. Aghassi-Hagmann, "A smooth EKV-based DC model for accurate simulation of printed transistors and their process variations", *IEEE Transactions on Electron Devices*, vol. 65, no. 2, pp. 667 673, 2018.

- G. C. Marques, S. K. Garlapati, S. Dehm, S. Dasgupta, H. Hahn, M. Tahoori, and J. Aghassi-Hagmann, "Digital power and performance analysis of inkjet printed ring oscillators based on electrolyte-gated oxide electronics", *Applied Physics Letters*, vol. 111, no. 10, pp. 102103, 2017.

- G. C. Marques, S. K. Garlapati, D. Chatterjee, S. Dehm, S. Dasgupta, J. Aghassi, and M. B. Tahoori, "Electrolyte-gated FETs based on oxide semiconductors: fabrication and modeling", *IEEE Transactions on Electron Devices*, vol. 64, no. 1, pp. 279 285, 2017.

# **Conferences**

• G. C. Marques, F. Rasheed, B. Breitung, H. Hahn, M. Tahoori and J. Aghassi-Hagmann, "Modeling and characterization of low voltage, inkjet printed devices and circuits", in *Proceedings of the Large-area, Organic & Printed Electronics Convention*, 2018, München.

# Workshops

- X. Feng, G. C. Marques, F. Rasheed, M. B. Tahoori and J. Aghassi, "Analog properties of printed electrolyte-gated FETs based on metal oxide semiconductors", in 59. MPC Workshop, IEEE German Section Solid-State Circuit Society, pp. 67-71, 2018. (Best Paper Award)

- G. C. Marques, S. K. Garlapati, S. Dehm, S. Dasgupta, J. Aghassi and M. B. Tahoori, "Compact modeling of inkjet printed, high mobility, electrolyte-gated transistors", in 55. MPC Workshop, IEEE German Section Solid-State Circuit Society, pp. 29 32, 2016. (Best Paper Award)

# **Invited Papers**

• G. C. Marques, F. Rasheed, J. Aghassi-Hagmann and M. B. Tahoori, "From silicon to printed electronics: A coherent modeling and design flow approach based on printed electrolyte gated FETs", in Proceedings of the Asia and South Pacific Design Automation Conference, pp. 658 - 663, 2018.

# **Contents**

| Ac  | know  | vledgments                                                                      | ١   |

|-----|-------|---------------------------------------------------------------------------------|-----|

| Αb  | strac | pt .                                                                            | vi  |

| Zu  | ısamı | menfassung der Arbeit                                                           | ix  |

| Lis | st of | publications                                                                    | x   |

| Co  | nten  | ts                                                                              | xii |

| ۱.  | Int   | troduction                                                                      | 1   |

| 1.  | Prin  | ted electronics technology                                                      | 3   |

| 11. | Th    | neory                                                                           | g   |

| 2.  | Thir  | n film technology                                                               | 11  |

|     | 2.1.  | Printed transistors                                                             | 11  |

|     | 2.2.  | Metal oxide electronics                                                         | 16  |

|     |       | 2.2.1. Conductors                                                               |     |

|     |       | 2.2.2. Dielectrics                                                              |     |

|     |       | 2.2.3. Semiconductors                                                           |     |

|     | 2.3.  | Electrolyte-gating                                                              | 21  |

| 3.  | Mod   | deling in printed electronics                                                   | 25  |

|     | 3.1.  | Unified model and parameter extraction                                          | 25  |

|     | 3.2.  | AIM-SPICE Level 15 transistor model                                             | 27  |

|     | 3.3.  | Variable range hopping model                                                    | 28  |

|     | 3.4.  | Charge drift model for electrolyte-gated field-effect transistors $\dots \dots$ | 29  |

|     | 3.5.  | Drift-diffusion modeling approach                                               | 30  |

|     | 3.6.  | Table model                                                                     | 31  |

|     | 3.7.  | Modeling the transition region                                                  | 31  |

# CONTENTS

| Ш   | . Re                 | esults                                                                                                                                                                                                                                             | 33                                           |

|-----|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

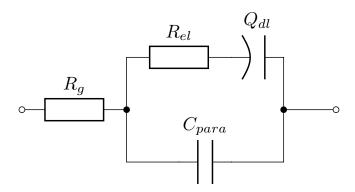

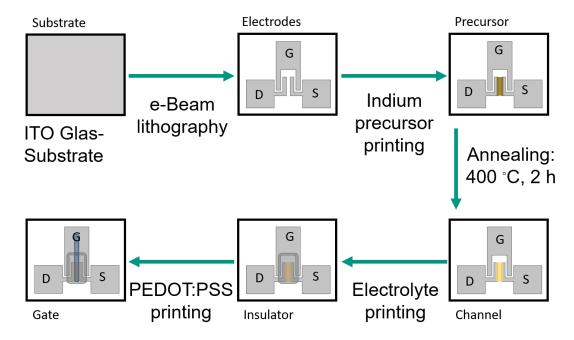

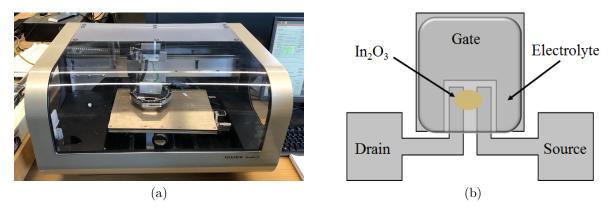

| 4.  | 4.1.<br>4.2.<br>4.3. | Fabrication routine                                                                                                                                                                                                                                | 35<br>36<br>37<br>40<br>44                   |

| 5.  | 5.1.                 | Standard cells in transistor-resistor logic  5.1.1. NAND gate  5.1.2. NOR gate  5.1.3. XOR gate  5.1.4. Ring oscillator  Standard cells in transistor-transistor logic  5.2.1. Enhancement load configuration  5.2.2. Depletion load configuration | 49<br>53<br>54<br>55<br>57<br>60<br>61<br>64 |

| 6.  | 6.1.                 | del-hardware correlation  Humidity effects                                                                                                                                                                                                         | <b>75</b> 76 82                              |

| I۷  | '. Su                | ımmary, conclusions and outlook                                                                                                                                                                                                                    | 91                                           |

| 7.  | Sum                  | nmary and conclusions                                                                                                                                                                                                                              | 93                                           |

| 8.  | Out                  | look                                                                                                                                                                                                                                               | 97                                           |

| V.  | Inc                  | dex and references                                                                                                                                                                                                                                 | 99                                           |

| Gl  | ossar                | у                                                                                                                                                                                                                                                  | 101                                          |

| Lis | st of                | Figures                                                                                                                                                                                                                                            | 109                                          |

| Lis | t of                 | Tables                                                                                                                                                                                                                                             | 113                                          |

| Bil | bliog                | raphy                                                                                                                                                                                                                                              | 115                                          |

# Part I. Introduction

# 1. Printed electronics technology

In this modern age, our lives are highly governed by microelectronics. In most of the everyday electronic devices, data is processed, even without the user's notice. For instance, in cars or refrigerators, physical quantities are measured by sensors and processed through a microcontroller to make our lives safer and more convenient. Recently, the internet of things (IOT) domain, where a variety of sensors and actuators communicate with each other and without any human interference, is gaining in popularity all over the world. For eg., a smartwatch and a heartbeat monitor can communicate with a smartphone during a workout in a way which allows the user to monitor and improve his performance with greater ease.

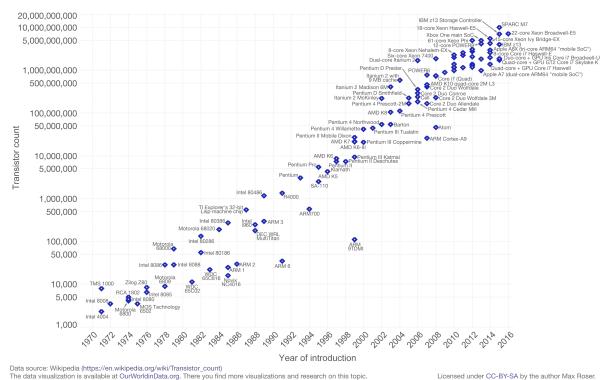

One of the most basic electronic components in modern microelectronic circuits are silicon (Si) based field-effect transistors (FETs), which are the basis of logic gates. Logic gates, in turn, are the most essential building blocks of integrated circuit based applications. In 1965, Gordon E. Moore predicted that the component count is doubled every year in an integrated circuit. [1, 2] Later, in 1975, the Moore's Law was slightly revised to double components every two years. [3, 4] In fact, this prediction turned out to become true, as seen from Figure 1.1. [5]

The continuous increase of transistor density is achieved mainly by scaling down the feature size of the transistors. The first microprocessor (Intel® 4004 4-bit microprocessor) came into the market in 1971 and is designed with 2300 transistors, of which the minimal feature size is 10 µm. Obeying Moore's Law, a processor presented by Intel® in 2010, designed within the 32 nm technology node, is based on 560 million transistors. [6] Besides increasing the component density on a chip, scaling down the transistor size improves the performance and reduces the power dissipation of microelectronic devices. Naturally, reducing the transistor size is limited due to atomic and quantum mechanical effects, leading to increases in leakage current and power consumption. [7, 8] Therefore, to satisfy the demand for higher integration density, new device architectures or even materials must be developed. [9, 10]

While the Si industry is attempting to shrink the feature size of their devices for aforementioned reasons, printed electronics (PE) is fine with large area applications. The thoughts behind PE is to have versatile electric components or applications directly printed on demand and at low fabrication costs. Ideally, the substrate on which the devices are printed should not play a role and rigid substrates, like glass, or flexible substrates, like plastic foils, are feasible. [11] However, the minimum feature size of a FET is bound to the printing resolution. For eg., the resolution of an inkjet printer is between 2 - 50  $\mu$ m. [12, 13] Besides that, the performance of printable FETs, in terms of field-effect mobility ( $\mu_{fet}$ ), are close to two orders of magnitude lower than in the state of the art Si technology. For that reason, the aim of PE is to complement, rather than to replace the Si based FETs. In an application, when manufacturing costs take precedence over the performance of the individual devices; PE can become an interesting alternative

### 1. Printed electronics technology

Figure 1.1.: Evolution of transistor counts on integrated chips from 1971 to 2016. Reprint from [5] under license CC-BB-BY-SA.

to conventional Si technology. The low fabrication costs in PE result from the fact that the devices are fabricated in an additive process, by which the functional materials are deposited on top of each other with inexpensive printing methods and without requiring any expensive mask. [11]

People have been printing, and improving the printing technology since early 3500 BCE. Today, we are used going into shops and to buy books or newspapers. Furthermore, households have one or more printers available where various kinds of documents are printed. It is obvious to use this well known and cheap technology to fabricate microelectronic circuits. For printing microelectronic circuits, different printing technologies are available and are categorized in the following types. In jetting based technologies, like inkjet printing, aerosol-jet printing, and electrohydrodynamic printing, the ink is pushed through a nozzle. If high throughput and scaleability is required, replecation type printing, like gravure printing, flexography, screen printing or reverse offset printing is favorable. However, replication type printing typically require masks which can become very expansive. Some key parameters of the presented printing technologies are summarized in Table 1.1. [14]

The jetting type printing technique is a digital and non-contact method, which allows for high flexibility in selecting the printing patterns and reducing contact contamination, hence, suitable for PE. [14] For that reason, the focus of this thesis is on inkjet printed

Table 1.1.: Comparison of different printing techniques suitable for PE. [14]

| -                       | •               |                      |                 |

|-------------------------|-----------------|----------------------|-----------------|

| Printing technique      | Resolution (µm) | Film thickness (nm)  | Line width (µm) |

| Inkjet                  | 2 [12]          | 100-500 [12, 15]     | 2-8 [16]        |

| Aerosol jet             | 10 [17]         | 30-150 [18, 19]      | 10 [17]         |

| Electrohydrodynamic     | 2[20]           | 20-180 [20, 21]      | 2[20, 21]       |

| Gravure                 | 2[22, 23]       | 10-400 [24, 25]      | 35 [24]         |

| Flexography             | 1 [26]          | 5-50 [26, 27]        | 3 [26]          |

| Screen printing         | 100 [28]        | 14000-25000 [29, 30] | 40 [30]         |

| Reverse offset printing | 1 [31]          | 90-400 [31, 32]      | 2[33]           |

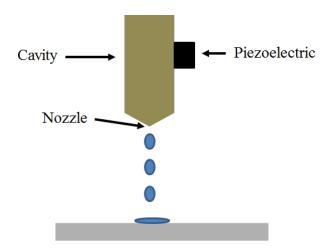

devices. In addition, inkjet printing combines feasible resolution with inexpensive fabrication routines. In an inkjet printer, a pulse is applied to the piezoelectric actuator which changes the volume of the piezo crystal. This causes a pressure wave moving in direction of the nozzle, leading the ink to be jetted, if the transferred kinetic energy is higher than the surface energy. [34] Figure 1.2 depicts the schematic of one nozzle.

Figure 1.2.: Schematic of a nozzle in an inkjet printer

With regards to FETs, organic-based materials are common in PE. Although much optimization has been done since the publication of the first organic field-effect transistor (OFET) in 1986, organic semiconductors show relatively low carrier mobility values, thereby harming the performance of applications. [35] Furthermore, OFETs and applications based on these OFETs typically require high supply voltages ( $\geq 5$  V). The reason for the high voltage requirements lies in the fact that conventional dielectrics are inefficient gating materials in printed transistors. [11, 36, 37] Depositing of the high- or low-k dielectric results in the formation of a solid dielectric, independent of the deposition method. Consequently, the interface quality between the rough channel surfaces, as it is expected for a printed film, and the dielectric decreases. [38] Nevertheless, a few examples of low voltage applications ( $\leq 5$  V), by sacrificing performance, are found in literature. [39] A seven-stage ring oscillator with only p-type OFETs is able to oscillate at 106 kHz, with a stage delay of 0.68 µs and require a supply voltage of -80 V. [40] Already by reducing the supply voltage to 10 V, the oscillating frequency drops to 1 kHz in a five stage ring oscillator, translating to a stage delay of 100 µs. [41, 42] The frequency drops

### 1. Printed electronics technology

further to 1.7 Hz by reducing the supply voltage to 3 V, corresponding to a stage delay of 42 ms in a seven stage ring oscillator. [39, 43]

Circuit designs with p-type only OFETs are not limited to ring oscillators. Radio frequency identification (RFID) transponders realized with p-type OFETs have been highly investigated. The operating frequency of 13.56 MHz seems not to be an obstacle. [44] Also in Active Matrix Organic Light Emitting Diode (AMOLED) displays, OFETs are used for designing the backplane. [45] Marien et al. show that analog designs, based on OFETs, have potential for future applications. [46]

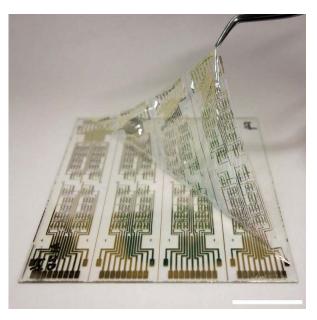

The low performance of devices in PE is not exclusive due to the low field-effect mobility of organic semiconductors or the inefficient gating approach. Also, the lack of reliable n-type semiconductors reduces the performance of applications in PE, causing the circuit designs to be in p-type logic only. [39, 47] The reason for the lack of n-type semiconductors is due to the fact that electrons got trapped at the semiconductor/dielectric-interface by hydroxyl groups in organic semiconductors. [48] A complementary metal oxide semiconductor (CMOS) and organic based seven stage ring oscillator is shown to oscillate at a frequency of  $\sim 285$  Hz, which is equal to a stage delay of 250  $\mu$ s, and at a supply voltage of 15 V. [49] A storage element with complementary OFETs is also reported; Takeda et al. show that flip flops are achievable with OFETs by printing D-flip flops on a one micron thick plastic substrate (Figure 1.3). [50]

Figure 1.3.: A circuit based on organic FETs printed on a flexible substrate. Reprinted from [50] under license CC-BY-4.0.

To overcome the limitations of the organic semiconductor, inorganic oxides are introduced in PE. [51] In comparison to organic semiconductors, inorganic oxide semiconductors typically show orders of magnitude higher mobility values, making them ideal for increasing the performance of devices in PE. Higher mobility values are desired to increase the switching speed of FETs. Unfortunately, unlike organic semiconductors, which can be processed at room temperature (RT), oxide semiconductors mostly require a post-annealing step with temperatures around 300 - 400 °C, limiting the choice of

the substrate. [52] Also, high performance p-type oxide semiconductors, comparable to n-type oxides, are not available. For that reason, most of the circuit designs are made only with n-type FETs. [53] In a seven stage ring oscillator with n-type only FETs, based on indium gallium zinc oxide, as semiconductor, and silicon dioxide as gate-dielectric, the frequency is measured to be 33 kHz, corresponding to a stage delay of 2.2 µs, at a supply voltage of 10 V, over-performing organic semiconductors. [54]

On the other hand, the high supply voltage requirements of printed FETs are overcome by using an electrolyte as gate-dielectric. Electrolytes are liquids containing mobile ions, able to form a Helmotz double layer (HDL) together with the charge carriers located at the gate-electrode and the channel. The formation of a HDL results in a high gate-capacitance, drastically lowering the supply voltages to values  $\sim 2.0$  V. [55, 56] However, the general opinion regarding electrolyte-gating is that parasitic effects decrease the speed of the targeted applications. Nevertheless, theoretical calculations have shown that electrolyte-gated FETs are able to operate in the sub-MHz region, which is more than sufficient for PE. [57] On the experimental side, Xia et al. show a five stage ring oscillator, based on organic FETs, oscillating at a frequency of 150 Hz, which is a stage delay of 0.7 ms, and reducing the supply voltage to  $\sim 2$  V.

In this thesis, the benefits of high carrier mobility, resulting from the oxide semiconductor, and low voltage requirements, resulting from the electrolyte-gating, are combined in transistor structures. [58, 59] Indium oxide is used as the channel material because it demonstrates high intrinsic mobility values ( $\geq 100 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ ). [14] With this approach, it is possible to have high performance applications with low voltage requirements in the field of PE. [60, 61] Literature also indicates that this transistor technology is feasible for analog applications. [62] Moreover, a direct current (DC) model, is presented, which is able to predict the behavior of such electrolyte-gated field-effect transistor (EGFET), with indium oxide  $(In_2O_3)$  channel. [63] Developing predictive models is essential for building a process design kit (PDK). A PDK includes all the design rules and models that a circuit designer needs for designing and simulating circuits. The development of a PDK for the following presented transistor technology is ongoing work. [64] Besides fabricating and modeling EGFETs, the aim of this work is to study design typologies suitable for digital applications based on these EGFETs. Since p-type metal oxides are not able to be combined with n-type metal oxides, typologies with a resistor or a n-type EGFET, replacing the p-type EGFET, are evaluated. The circuit design is evaluated on microelectronic cells as well as ring oscillator structures. This transistor technology, in combination with reliable modeling as well as design methodologies, may forge the way for high performance and low voltage applications in the field of PE.

The organization of the presented thesis is as follows: After this introduction, the background of this thesis is discussed in Chapter 2 and Chapter 3. Thereby, Chapter 2 focuses on the architecture as well as working principles of thin film, printed FETs. As discussed, metal oxides turned out to be very interesting for applications in PE. Therefore, some metal oxides suitable for PE are also reviewed and compared in this chapter. Next, the concept of electrolyte-gating is explained by studying the characteristics of the Helmholtz double layer in more detail. A large number of models are available to model printed FETs and suitable for circuit simulation; therefore, the most important modeling approaches suitable for PE are reviewed in Chapter 3. Chapter 4 introduces the studied EGFET transistor technology and initiates the result part of this thesis. Besides

### 1. Printed electronics technology

demonstrating the electrical characteristics of such EGFETs, this chapter purposes a modeling methodology for describing the DC behavior of EGFETs. In Chapter 5, logic gates and ring oscillator structures based on EGFETs are designed. As design topology the so called transistor-resistor logic, where a resistor is used in the pull-up network and an EGFET in the pull-down network, is compared with the transistor-transistor logic, where the pull-up and pull-down networks are based on EGFETs. A correlation between the measured and simulated ring oscillator data is made in Chapter 6. Furthermore, measurements show that the EGFETs and circuits based on EGFETs are influenced by moisture. This dependency on the moisture is understood with the help of simulations. Finally, the work is concluded and an outlook into future tasks is given in Chapters 7 and Chapter 8, respectively.

Part II.

Theory

# 2. Thin film technology

Before introducing the EGFET technology, an overview on thin film transistors (TFTs) is given. In addition, interesting materials suitable for thin film based devices are discussed. TFTs are very popular in liquid crystal display (LCD) or other display technologies because of a straight forward and well established manufacturing process. For instance, in a LCD matrix, the individual pixels are selected through a TFT. [65] Amorphous or polycrystalline silicon are state of the art materials used in TFTs. On the other hand, metal oxides are getting more attention because of their high intrinsic mobility values and easy manufactureability.

The concept of a TFT is adopted in PE, where the functional materials are printed on top of each other. In general, it is possible to integrate metal oxides into a solution process and deposited these materials through a printer. [53] Unfortunately, because of the used materials, high supply voltages and low performance are expected in PE. As shown in the following, metal oxides in combination with electrolytes reduce the expected supply voltage range, while enhancing the performance of applications.

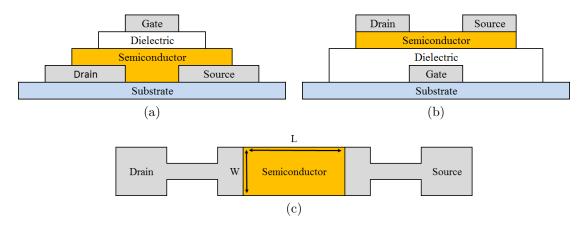

### 2.1. Printed transistors

Organic-based compounds are widely used to fabricate TFTs/FETs in PE. In this regard, organic based semiconductors, conductors and insulators are found in literature. [11, 13, 66] To fabricate a printed TFT, the organic materials are either stacked in the top gate (TG) (Figure 2.1a) or the bottom gate (BG) (Figure 2.1b) configurations. The semiconductor, which forms the channel, is always placed between the source-and the drain-electrodes. The vertical distance between the drain- and the source-electrode is known as the channel length (L) and the height of the semiconductor layer in the horizontal direction as the channel width (W) (Figure 2.1c). However, in the TG configuration, the dielectric and the gate-electrode are placed on top of the semiconductor. Conversely, in the BG configuration, the gate-electrode and the dielectric are placed below the semiconductor. [11]

There is a typical distinction between semi and fully printed devices. Semi printed devices, where the transistor terminals and interconnects, preferable based on gold or silver, deposited through a vacuum process, are more common. Printing conductive lines is, however, still a demanding task. Also, in most of the cases, the printed conductive lines require a post annealing step at higher temperatures ( $\sim 200$  °C) than most of the flexible substrates can sustain. [11, 67] Nevertheless, in recent days, researchers are moving towards fully printed devices where everything is printed. [68, 69]

The domain of printed TFTs grows with the progress made in the organic semiconductor research. However, pentacene ( $C_{22}H_{14}$ ) is still one of the most popular semiconductors in this field. The field-effect mobility is a very important parameter in a FET/TFT and

Figure 2.1.: Graphical representation of a TFT in (a) TG and (b) BG configuration. (c) Top view of the channel printed between the source- and drain-electrodes without dielectric and gate-electrode.

describes how fast the charge carriers can travel from the drain- to the source-electrode, under the influence of an electric field. The field-effect mobility of a printed p-type pentacene based OFET can be up to  $0.68 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ . [70]. Another important organic semiconductor is poly(3-hexylthiophene-2,5-diyl) (P3HT) which has a field-effect mobility value of  $0.12 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  in a p-type OFET. [71] Nevertheless, field-effect mobility values around  $10 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  are feasible with other organic p-type semiconductors. [72] Bisthienoisatin derivatives are interesting candidates for n-type OFETs. In this regard, a n-type OFET with dicyanomethylene 2-ethylhexyl (BTICN-EH) has a field-effect mobility of around  $0.2 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ . [73] Unlike in conventional electronics, there are an endless number of semiconductors suitable for PE, therefore, only the most important organic semiconductors are mentioned here. Nevertheless, in Section 2.2.3, oxide semiconductors are introduced where field-effect mobility values  $\sim 100 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  are measured. It is desirable to maximize the field-effect mobility to increase the driver capability of a TFT, as well as the cut-off frequency  $(f_t)$ : [57]

$$f_t = \frac{\mu_{fet} V}{2 \pi L^2},\tag{2.1}$$

where V is the driving voltage.

The choice of the dielectric material turned out to be very crucial. Conventional high or low-k dielectric, like silicon dioxide (SiO<sub>2</sub>) and zirconium dioxide (ZrO<sub>2</sub>), respectively, are well known in PE. [11, 74] Due to the bad interface properties between the semiconductor and the dielectric, high supply voltages is a characteristic of applications based on printed TFTs. By introducing an electrolyte as gate-dielectric, not only does the supply voltage goes down, but also the field-effect mobility value increases, due to the improved surface interface between the gate-dielectric material and the semiconductor. The field-effect mobility value of the P3HT based OFET increases to  $\sim 18~\rm cm^2~V^{-1}~s^{-1}$  and the pentacene based OFET to  $\sim 5.6~\rm cm^2~V^{-1}~s^{-1}$  with an electrolyte as insulator. [75]

The working principle of printed/organic TFTs is identical to conventional silicon based TFTs. By increasing the potential between the gate- and the source-electrode (gate-source voltage  $(V_{as})$ ), charges accumulate at the surface of the semiconductor,

forming a conductive channel between the source- and drain-electrode. The reason for the accumulation of charges lies in the fact that the dielectric builds a plate-capacitorlike-structure together with the gate-electrode and the channel. Therefore, by polarizing the dielectric, the charge carrier density on the surface of the semiconductor is tuned by an electric field. A TFT is, in general, either operating in the cut off, the linear or the saturation region. In the cut off region, where the gate-source voltage is lower than the threshold voltage  $(V_t)$ , a leakage off-current  $(I_{off})$  flows from the drain-electrode to the source-electrode. As soon as the gate-source voltage becomes equal to, or larger than the threshold voltage, charge carriers begin to accumulate at the surface of the semiconductor, forming a conductive channel between the source- and the drain-electrode. A current, the drain-source current  $(I_{ds})$ , is able to flow through the formed channel and rises with the gate-source voltage. In addition, as long as the voltage drop between the drain- and source-electrode (drain-source voltage  $(V_{ds})$ ) is smaller than or equal to the saturation voltage  $(V_{ds,sat} = V_{gs} - V_t)$ , the TFT behaves like a resistor and the drain-source current rises linearly with the drain-source voltage. If the drain-source voltage is further increased to values larger than the saturation voltage, the drain-source current saturates, since the channel is pinching off. At this pinch off point, the region on the drain side becomes depleted; however, electrons can still drift from the source-electrode to the drain-electrode because of the presented high electrical fields, as well as high carrier velocity at the drain-electrode. [76]

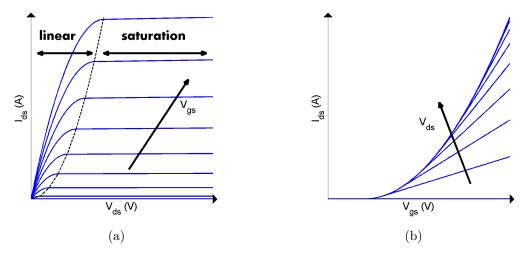

The output curve (Figure 2.2a) of a transistor shows the different operating regions. To obtain the output curve, the gate-source voltage is fixed at a certain value and the drain-source current is plotted against the drain-source voltage. The saturation current of a transistor is ideally dependent on the gate-source voltage, rather than on the drain-source voltage. In the case of the transfer curve (Figure 2.2b), the drain-source voltage is kept constant while the drain-source current is plotted against the gate-source voltage. Thereby, the drain-source current is described by the following equation, well known from literature and implemented in the Shichman-Hodges transistor model (Level 1 model): [76, 77]

$$I_{ds} = \begin{cases} I_{off} \exp\left(-\frac{\ln 10}{SS} \left(V_{gs} - V_{0}\right)\right) & V_{gs} < V_{t}, \\ \frac{W}{L} \mu_{fet} C_{g} \left(V_{gs} - V_{t} - \frac{V_{ds}}{2}\right) V_{ds} \left(1 + \lambda V_{ds}\right), & V_{gs} \ge V_{t} \text{ and } V_{ds} \le V_{ds,sat}, \\ \frac{1}{2} \frac{W}{L} \mu_{fet} C_{g} \left(V_{gs} - V_{t}\right)^{2} \left(1 + \lambda V_{ds}\right) & V_{gs} \ge V_{t} \text{ and } V_{ds} > V_{ds,sat}, \end{cases}$$

(2.2)

where SS is the subthreshold slope and the onset voltage  $(V_0)$  determines at which gate-source voltage level the drain-source current of the transistor starts to rise. In some cases, an increase in the drain-source current with drain-source voltage is observed in saturation. This is where, due to the pinch off effect, the effective channel length of the transistor reduces with increasing the drain-source voltage and described through the channel length modulation parameter  $(\lambda)$ .

However, by using Equation 2.2, the extracted values for the field-effect mobility are only valid in either the linear, or the saturation region. In the saturation region, the

Figure 2.2.: Exemplary (a) output and (b) transfer curves of a TFT.

field-effect mobility is discribed by:

$$\mu_{fet} = \left(\frac{d\sqrt{I_{ds}}}{dV_{gs}}\right)^2 \frac{2L}{WC_g}.$$

(2.3)

Nevertheless, it is more suitable to calculate the field-effect mobility value in the linear region. The value of the field-effect mobility might be underestimated in the saturation region because of parasitic effects. Therefore, it is suggested to estimate the field-effect mobility value in the linear region: [11]

$$\mu_{fet} = \frac{dI_{ds}}{dV_{gs}} \frac{L}{WC_g V_{ds}}.$$

(2.4)

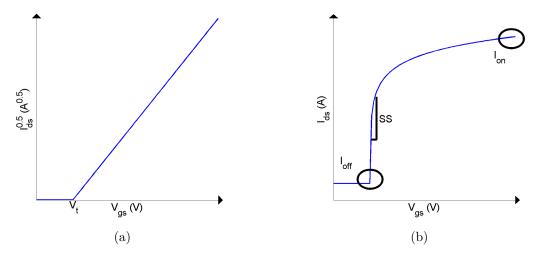

To extract the threshold voltage, the square root of the drain-current is plotted against the gate-source voltage, at the highest drain-source voltage. At the maximum slope, the linear part of the  $\sqrt{I_{ds}}$ -plot is extrapolated until intercepting with the x-axis, which is the value of the threshold voltage (Figure 2.3a). By plotting the drain-source current in logarithmic scale (Figure 2.3b), at the highest drain-source voltage, the subthreshold slope, the off-current, as well as the on-current, are extracted. The off-current and the on-current ( $I_{on}$ ) are the minimum and maximum current values, respectively. However, an important parameter is the  $I_{on}/I_{off}$ -ratio which shows over how many orders of magnitude the current changes in a TFT. The steepest slope over one decade of the logarithmic  $I_{ds}$ -curve is known as the subthreshold slope, which is an indicator of how quickly the TFT switches from the off-state to the on-state.

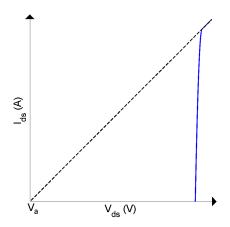

The parameter  $\lambda$  is extracted from the output curve at the maximum gate-source voltage, where the saturation region is extrapolated until crossing with the x-axis. At the intercept with the x-axis, the voltage value  $V_a$  is obtained (Figure 2.4) and used to estimate the parameter  $\lambda$ : [11, 76]

$$\lambda = \frac{1}{V_a}.\tag{2.5}$$

Figure 2.3.: (a) Extracting the threshold voltage of a TFT by plotting  $\sqrt{I_{ds}}$  versus the gatesource voltage. (b) Transfer curve in logarithmic scale, at highest potential, to estimate key parameters in TFTs

Figure 2.4.: Output curve of a FET at maximum gate-source voltage with extrapolated saturation region.

A further important parameter of a TFT is the transconductance  $(g_m)$  (Equation 2.6). The transconductance demonstrates how a small change in the gate-source voltage affects the drain-source current and is useful in a small signal replacement circuit of a TFT, where the TFT is considered to be a current source:

$$g_m = \left. \frac{dI_{ds}}{dV_{gs}} \right|_{V_{ds} > V_{ds,sat}}.$$

(2.6)

# 2.2. Metal oxide electronics

Recently, transparent conducting oxides (TCOs), and transparent semiconducting oxides (TSOs) have proven to be an interesting alternative to organic materials in PE. The reason for the popularity of these oxides lies in the fact that these materials show better electrical characteristics than organic based materials. Although, high performance oxides are found for vacuum processed oxides in literature [53], the focus will remain on oxides that are incorporated into a solution process, since the devices presented in this thesis are fabricated with an inkjet printer. As seen in the following subsections, dielectrics, conductors, as well as semiconductors are available as oxides, which enables the possibility of oxide only circuit designs.

## 2.2.1. Conductors

In an all oxide TFT, the drain- and source-electrodes are based on a TCO. Also, in microelectronic circuits, TCOs are used as contact pads and conductive interconnects. [53] In a different application, a window coated with a TCO is easily defrosted by driving a high current through the TCO film. [78]

The conduction type of TCOs are chosen in accordance to the application. In a pn-junction, the p-type TSO is in contact with a p-type TCO, while the n-type TSO is contacted through an n-type TCO, in order to avoid offsets in the band structure, or recombination centers. However, achieving either p-type TCOs or TSOs is still challenging because of the strongly localized oxygen orbitals in oxides, as will be discussed in more detail in Section 2.2.3. [53, 79] Unfortunately, solution processed TCOs are lacking in conductivity, which is the reason that TCO based structures are mainly fabricated with a vacuum process. [80, 81]

Although a wide variety of n-type TCOs are found in literature [53, 82], the focus will stay on indium tin oxide (ITO). ITO is essentially indium doped tin oxide (Sn:In<sub>2</sub>O<sub>3</sub>) and exhibit conductivity values as high as 5900 S cm<sup>-1</sup>. [80] However, Jeong et al. reports a conductivity of  $\sim 65$  S cm<sup>-1</sup> for an inkjet printed ITO film. [83] The conductivity of p-type TCO is lower compared to their n-type counterparts. One of the highest conductivity values for p-type TCO is achieved with nickel (II) oxide (NiO) based films ( $\sim 7$  S cm<sup>-1</sup>). [80, 84]

### 2.2.2. Dielectrics

In TFTs or, in a more general point of view, FET structures, the charge carrier density inside the semiconductor channel is controlled by an electrical field. As discussed before, a capacitor is formed between the gate and the channel of the TFT. [76] The dielectric is polarized by the electrical field separating the charges, where the positive charge carriers align in the direction of the electrical field and the negative charge carriers in the opposite direction. [85] The dielectric of choice, in TFTs, has been  $SiO_2$  because of its favorable insulating characteristics, e.g. the band gap  $(E_g)$  is  $\sim 9$  eV and breakdown occurs at values > 10 MV cm<sup>-1</sup>. Nevertheless,  $SiO_2$  has a low dielectric constant of 3.9. [53]

In all kind of TFTs, the driver capability is directly proportional to the gate-capacitance  $(C_q)$ . The equation for estimating the capacitance value (C) of a parallel capacitor

clearly suggests that, to increase the capacitance, either the thickness of a dielectric is reduced, or the value of the dielectric constant is increased:

$$C = \frac{\kappa e_0}{d},\tag{2.7}$$

where  $\epsilon_0$  is the electronic constant and  $\kappa$  is the dielectric constant. However, reducing the thickness of the dielectric is demanding because defects in the film leads to shorts. For that reason, high- $\kappa$  dielectrics are introduced to increase the gate-capacitance of TFTs while maintaining thick dielectric films, which in addition relaxes the fabrication. Unfortunately, high- $\kappa$  dielectrics typically have a lower band gap, since the dielectric constant is inversely proportional to the band gap. The low band gap can give rise to the leakage gate-current  $(I_g)$  of a TFT. Additionally, the offset between the valence band maximum (VBM), in p-type TFTs, or conduction band minimum (CBM), in n-type TFTs, of the dielectric and the semiconductor is  $\geq 1$  eV, to reduce leakage due to Schottky emission. [53, 85]

Table 2.1 summarizes important high- $\kappa$  dielectrics, beneficial in increasing the gate-capacitance of TFTs fabricated through a solution process. With a band gap of 8.8 eV, aluminum oxide (Al<sub>2</sub>O<sub>3</sub>) is a high- $\kappa$  dielectric feasible for TFTs. [53] The group of Prof. Park is able to fabricate solution-based Al<sub>2</sub>O<sub>3</sub> films with dielectric constant values of 8.37, at annealing temperatures of only 60 °C. [86] Since the process temperature of these Al<sub>2</sub>O<sub>3</sub> films is relatively low, paper or plastic foils are conceivable substrate choices. The band gap of yttrium oxide (Y<sub>2</sub>O<sub>x</sub>) is slightly lower ( $\sim$  6.5 eV), but the dielectric constant is nearly doubled compared to Al<sub>2</sub>O<sub>3</sub> dielectric; however, the process temperature is within 300 - 500 °C, which is considerably high. [87] By further decreasing the band gap to values around 6 eV, spin coated hafnium oxide (HfO<sub>2</sub>) films, annealed at 200 °C, with a dielectric constant of 10.2, are found to be suitable for TFTs. [53, 88] Titanium (IV) oxide (TiO<sub>2</sub>) has the lowest band gap value ( $\sim$  3.5 eV). In addition, a dielectric constant value of 27 is found in literature for TiO<sub>2</sub> spin coated films annealed at 250 °C. [53, 88]

| Material          | Temperature (°C) | $E_g$ (eV) | Breakdown (V cm <sup>-1</sup> ) | $\kappa$  | Reference |

|-------------------|------------------|------------|---------------------------------|-----------|-----------|

| $SiO_2$           | 200-300          | 9          | $> 10 \times 10^6$              | 3.9       | [53]      |

| $Al_2O_3$         | 60               | 8.8        | $> 6 \times 10^{6}$             | 8.37      | [53, 86]  |

| $Y_2O_x$          | 300-500          | $\sim 6.5$ | -                               | $\sim 16$ | [53, 87]  |

| $\mathrm{HfO}_2$  | 200              | 6          | $\sim 6 \times 10^6$            | 10.2      | [53, 88]  |

| -TiO <sub>2</sub> | 250              | $\sim 3.5$ | -                               | 27        | [53, 89]  |

Table 2.1.: Popular dielectrics used in solution processed TFTs.

### 2.2.3. Semiconductors

Besides a conductor and a dielectric, TFTs are also based on a semiconductor. It is well known that a TFT with an oxide semiconductor channel exhibits a higher field-effect mobility value than with amorphous silicon or an organic semiconductor. [53, 90, 91] Furthermore, oxide semiconductors are printable, show high optical transparency, and are stable under ambient conditions. [53] In the following, a few n- and p-type oxide semiconductors, suitable as channel material in TFTs, are presented. In general, n-type

TFTs are used for high performance applications, while p-type TFTs lack in performance. As consequence, n-type only circuit designs are very common in oxide electronics. [80]

The purpose of the following subsections is to give an overview on the most popular oxide semiconductors used in TFTs, rather than to compare the performance of these TFTs. For a more complete overview on oxide semiconductors, literature is referred to [53, 92, 93]. Nevertheless, the complete material stack must be taken into account when TFTs are evaluated, since all materials, especially their interfaces with each other, defines the electrical characteristics of such TFTs. [94] Although electrolyte-gating is a more efficient gating method (Section 2.3), just dielectric-gating is considered here, since the focus is on the oxide semiconductor itself.

### n-type oxide semiconductors

The unique band structure of metal oxides provides n-type oxide semiconductors with good conductivity, large mobility and high optical transparency. In general, the valence band of metal oxides is formed by the bonding, as well as by the non-bonding occupied oxygen 2p orbital and the conduction band by the anti-bonding metal ns orbital (n denotes the quantum number) interaction with the oxygen 2p orbital. Herein, the metal ns orbitals are spatially wide-spread, while the oxygen 2p orbitals are strongly localized. Neighboring metal ns orbitals can easily overlap with each other and raise the electronic properties of such metal oxides. Due to strongly localized oxygen 2p orbitals, p-type conduction is difficult in metal oxides and, for the same reason, TFTs based on metal oxides do not operate in inversion mode. [53, 79, 95–98]

Binary compounds like zinc oxide (ZnO) or indium oxide have excellent electrical properties, making them beneficial as channel material in TFTs. [53] As an example, a TFT fabricated at RT with sputtered ZnO channel and silicon oxynitride (SiO<sub>x</sub>N<sub>y</sub>) gate-insulator shows a field-effect mobility of around 70 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>. The threshold voltage and the subthreshold slope are 1.8 V and 0.68 V dec<sup>-1</sup>, respectively. Also the on-current  $(\sim 10^{-3} \text{ A})$  and the off-current  $(\sim 10^{-9} \text{ A})$  are reasonable. It is also possible to integrate the ZnO into a solution process. Neverthless, the field-effect mobility of the TFT drops to  $1.02 \times 10^{-3}$  cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> when the ZnO is solution-processed and thermally annealed at 180 °C. A reduction of the field-effect mobility is expected for solution-processed TFTs, since these thin films have a less beneficial microstructure, e.g. grain size, porosity and crystallization, compared to vacuum processed thin films. In addition, SiO<sub>2</sub> is used as gate-insulator, which further reduces the field-effect mobility, since the interface between the insulator and the channel plays a crucial role in defining the field-effect mobility of a TFT. [94] On the other hand, Han et al. proves that indium oxide is a very interesting material as an active layer (semiconductor) for solution-processed TFTs. A solution-processed TFT with an In<sub>2</sub>O<sub>3</sub> channel annealed at 500 °C achieves field-effect mobility values around 55  $\text{cm}^2 \, \text{V}^{-1} \, \text{s}^{-1}$ . [91]

Also, tertiary and quaternary compounds like zinc tin oxide (ZnSnO) or indium gallium zinc oxide (InGaZnO), respectively, are used in solution-processed and/or printed TFTs. Sykora et al. shows in a TFT with printed ZnSnO channel a field-effect mobility value of  $7.8~\rm cm^2~V^{-1}~s^{-1}$ , annealed at a high temperature of  $500~\rm ^{\circ}C$ . [99] On the other hand, indium gallium oxide (InGaO) films cured at  $350~\rm ^{\circ}C$  are utilized in TFT structures in combination with scandium zirconium oxide ( $S_{c1}Z_{r1}O_x$ ) dielectric. Measurements on

these printed InGaO based TFTs show excellent electrical properties, e.g. the field-effect mobility is reported to be 12 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>. [100] It has been proven that indium zinc oxide (InZnO) films are very interesting for low temperature processes (250 °C), exhibiting field-effect mobility values around 11 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>. [101] Less beneficial is that the InZnO TFTs operate in depletion mode (negative threshold voltage), probably because of the large charge carrier density inside the channel. The quaternary compound InGaZnO, heated at 300 °C and implemented in a TFT, has a field-effect mobility as low as 1.41 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>. The electrical performance of the InGaZnO based TFT is further improved by confining a layer of indium tin zinc oxide (InSnZnO) between the channel and the dielectric. With this confining layer, the field-effect mobility is improved to 12 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, at an annealing temperature of 350 °C. The reason for the improvement is that the band structure of the InSnZnO and InGaZnO align very well, since a barrier controlling the electron flow is formed at the InSnZnO/InGaZnO interface. [102]

All electrical parameters of the before-presented TFTs are summarized in Table 2.2. Besides that, also the required annealing temperatures are considered in order to be compatible to the assigned substrates. If flexible substrates like plastic or paper are desired, then annealing temperatures of  $\sim 150~^{\circ}\mathrm{C}$  are acceptable. [103] Nevertheless, flexible polyimide substrates can also sustain temperatures up to 350  $^{\circ}\mathrm{C}$ . Higher temperatures up to 600  $^{\circ}\mathrm{C}$  are only allowed for rigid substrates. [104]

|  | Table 2.2.: Material stack | and kev electrical | properties of different n-type | e oxide based TFTs. |

|--|----------------------------|--------------------|--------------------------------|---------------------|

|--|----------------------------|--------------------|--------------------------------|---------------------|

| Channel   | Insulator           | Stack            | $\mu_{fet}$                                          | $V_t$       | $I_{on}/I_{off}$    | SS             | Year       |

|-----------|---------------------|------------------|------------------------------------------------------|-------------|---------------------|----------------|------------|

|           |                     |                  | $({\rm cm}^2{\rm V}^{\text{-}1}{\rm s}^{\text{-}1})$ | (V)         | • •                 | $(V dec^{-1})$ |            |

| ZnO       | $SiO_xN_y$          | BG               | 70                                                   | 1.8         | $2 \times 10^5$     | 0.68           | 2004 [105] |

| ZnO       | $SiO_2$             | $_{\mathrm{BG}}$ | 0.001                                                | 18          | -                   | -              | 2008 [94]  |

| $In_2O_3$ | $SiO_2$             | $_{\mathrm{BG}}$ | 55.26                                                | -           | $\sim 10^7$         | -              | 2011 [91]  |

| ZnSnO     | $SiO_2$             | $_{\mathrm{BG}}$ | 7.8                                                  | 7.0         | $3.2 \times 10^8$   | 0.35           | 2016 [99]  |

| InGaO     | $S_{c1}Z_{r1}O_{x}$ | TG               | 12                                                   | $\sim 0.0$  | $5.8 \times 10^6$   | 0.12           | 2018 [100] |

| InZnO     | $SiO_2$             | $_{\mathrm{BG}}$ | $\sim 11$                                            | $\sim -1.0$ | $\sim 10^6$         | $\sim 0.42$    | 2010 [101] |

| InGaZnO   | $\mathrm{SiO}_2$    | $_{\mathrm{BG}}$ | 1.41                                                 | 1.0         | $4.3 \times 10^{7}$ | 0.37           | 2011 [106] |

| InSnZnO/  | $\mathrm{SiO}_2$    | $_{\mathrm{BG}}$ | 22.16                                                | $\sim 5.29$ | $\sim 10^7$         | 0.51           | 2014 [102] |

| InGaZnO   |                     |                  |                                                      |             |                     |                |            |

### p-type oxide semiconductors

At the same time at which the band structure is beneficial to n-type oxide semiconductors, it is disadvantageous to the electronic properties of p-type metal oxides. The reason for that lies in the fact that the valance band is formed by strongly localized oxygen 2p orbitals. Oxygen, in general, has a high electronegativity, causing a large effective hole mass and low carrier mobility. [53, 79, 95–98]

To overcome the limitations of p-type metal oxides, the band structure of the oxides needs to be changed. One popular approach is to introduce a metal with a fully filled 3d shell, which has a similar energy level as the oxygen 2p orbital. In this regard, copper is a promising candidate. The valence band of copper (II) oxide (CuO) is formed by the

copper 3d orbital and the oxygen 2p orbital, while the conduction band is formed by the copper 4s orbital. [53, 79, 95, 96]

Therefore, the main focus in p-type metal oxides lies in copper compounds. [79, 107] For example, Sung et al. reports on a TFT with a sputtered, 200 °C annealed CuO thin film channel and a field-effect mobility of 0.40 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>. [108] A TFT with sputtered copper (I) oxide (CuO<sub>2</sub>) film, annealed at 200 °C, with a field-effect mobility as high as  $3.6 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ , but a low  $I_{on}/I_{off}$ -ratio of only  $\sim 2 \times 10^{-2}$ , is also found in literature. [109] The  $I_{on}/I_{off}$ -ratio is reduced, since the CuO<sub>2</sub> films show high intrinsic conductivity, resulting in a higher off-current. [108] In CuO<sub>2</sub> based TFTs, it is demonstrated that it is possible to integrate copper oxide based TFTs in a solution process. However, due to the solution process, the field-effect mobility drops to 0.16 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, although the film is annealed at 400 °C. [110] Also, copper chromate (CuCrO<sub>4</sub>), cuprous thiocyanate (CuSCN), and/or copper (I) iodide (CuI) are considered to be channel materials, but do not add any significant progress in improving the field-effect mobility of copper oxide based p-type TFTs; the field-effect mobility is, in all presented cases, below 1 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>. [95, 111, 112]

Next, tin (I) oxide (SnO) based devices have proven to be an interesting p-type semiconductors for TFT applications. The reason for the increasing popularity of SnO is that this material shows reasonable hole mobility, as well as high charge carrier density because of the spherically spread 5s orbitals. [97] As one example, an ambipolar TFT with pulsed laser deposited SnO channel and SiO<sub>2</sub> dielectric is reported in literature. The field-effect mobility in this TFT is 0.78 cm<sup>2</sup> V<sup>-1</sup>s<sup>-1</sup>, slightly higher compared to similar stacked CuO based TFTs. [97] Nevertheless, by optimizing the crystalline structure, it is even possible to achieve field-effect mobility values upwards to 6 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> in SnO based TFTs. [113] Although tin (IV) oxide (SnO<sub>2</sub>) phase is thought to be n-type in nature, p-type conduction is achieved by tuning the annealing temperature. The SnO<sub>2</sub> phase is already achieved by annealing the films at 100 °C, but the field-effect mobility is only 0.011 cm<sup>2</sup> V<sup>-1</sup>s<sup>-1</sup>, in comparison to SnO-based TFTs. In addition, the TFT based on SnO<sub>2</sub> operates in depletion mode, which is attributed to the high carrier density inside the material. [114] However, a solution-processed SnO based TFT shows a field-effect mobility of 0.13 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, which is too low for the use in printed oxide based CMOS-like designs. [115] Also here, the threshold voltage is large ( $\leq -10 \text{ V}$ ) but tunable by the choice of the dielectric. In this regard, the threshold voltage of SnO based TFTs is lowered by changing the gate-dielectric, e.g. the threshold voltage is reduced to -0.3 V with a  $Al_2O_3$ -based dielectric. [116]

Recently, Kim et al. made a huge step in optimizing the performance of p-type oxide semiconductors. The compound of copper (I) iodide and tin (I) oxide (a-CuSnI) shows p-type behavior with a hall mobility ( $\mu_{hall}$ ) around 9 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>. The obtained high hall mobility value is the result of the spatially spread large p-orbitals in a-CuSnI. [117] Therefore, a-CuSnI is an interesting candidate for p-type TFTs; however, this material is not employed in a TFT yet.

Table 2.3 summarizes the electrical properties of all discussed oxide p-type TFTs. One can see that some of the TFTs have a very low threshold voltage compared to the others. Over the last 10 years, many efforts have been made to improve the performance of p-type oxide TFTs but by comparing Table 2.2 and 2.3, it is obvious that it is difficult to design complementary circuits (e.g. CMOS like structures) in oxide electronics, since the p-type

| Channel              | Insulator          | Stack            | $\mu_{fet}$                                          | $V_t$   | $I_{on}/I_{off}$  | SS             | Year       |

|----------------------|--------------------|------------------|------------------------------------------------------|---------|-------------------|----------------|------------|

|                      |                    |                  | $({\rm cm}^2{\rm V}^{\text{-1}}{\rm s}^{\text{-1}})$ | (V)     |                   | $(V dec^{-1})$ |            |

| CuO                  | $SiO_2$            | BG               | 0.40                                                 | -       | $1 \times 10^{4}$ | -              | 2010 [108] |

| $Cu_2O$              | $Al_2O_3$          | $_{\mathrm{BG}}$ | 3.60                                                 | -12.0   | $2 \times 10^2$   | -              | 2010 [109] |

| $Cu_2O$              | $SiO_2$            | $_{\mathrm{BG}}$ | 0.16                                                 | -       | $1 \times 10^{2}$ | -              | 2013 [110] |

| CuI                  | $\mathrm{SiO}_2$   | $_{\mathrm{BG}}$ | 0.44                                                 | 35      | $5 \times 10^2$   | -              | 2018 [111] |

| $CuCrO_2$            | $SiO_2$            | $_{\mathrm{BG}}$ | 0.59                                                 | - 32.81 | $1 \times 10^5$   | 5.66           | 2018 [95]  |

| CuSCN                | PVDF               | TG               | 0.18                                                 | - 1.7   | -                 | 1.6            | 2018 [112] |

| $\operatorname{SnO}$ | $SiO_2$            | $_{\mathrm{BG}}$ | 0.78                                                 | -3.8    | -                 | 1.19           | 2011 [97]  |

| $\mathrm{SnO}_2$     | $SiO_2$            | $_{\mathrm{BG}}$ | 0.011                                                | 30.4    | $\sim 10^3$       | $\sim 2.0$     | 2008 [114] |

| SnO                  | $\mathrm{HfO}_{2}$ | $_{\mathrm{BG}}$ | 5.87                                                 | -1.0    | $\sim 10^3$       | 7.63           | 2013 [113] |

| $\mathrm{SnO}_x$     | $Al_2O_3$          | $_{\mathrm{BG}}$ | 1.6                                                  | -0.3    | $\sim 10^4$       | -              | 2018 [116] |

| SnO                  | $SiO_2$            | $_{\mathrm{BG}}$ | 0.13                                                 | -1.9    | 85                | -              | 2012 [115] |

Table 2.3.: Material stack and key electrical properties of different p-type oxide TFTs.

TFTs are lacking in performance compared to their n-type counterparts. Furthermore, TFTs with indium oxide as channel material shows the best electrical characteristics among the oxide semiconductors and is therefore preferably used to fabricate devices in this thesis.

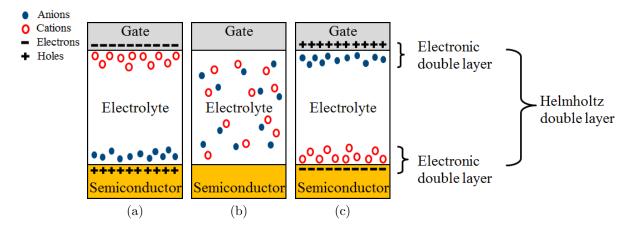

# 2.3. Electrolyte-gating

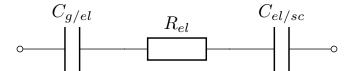

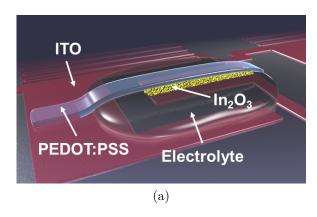

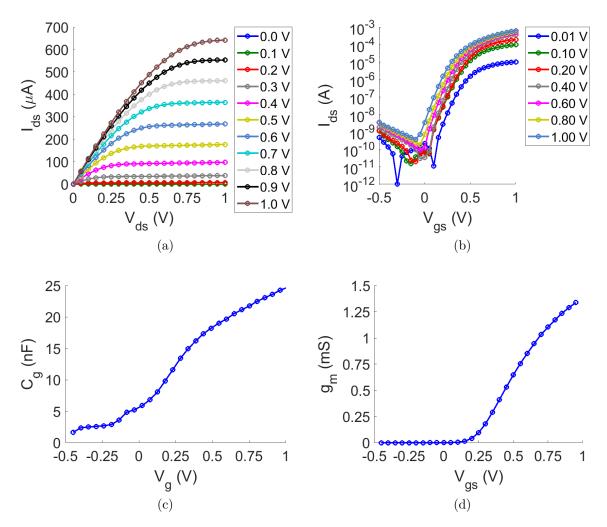

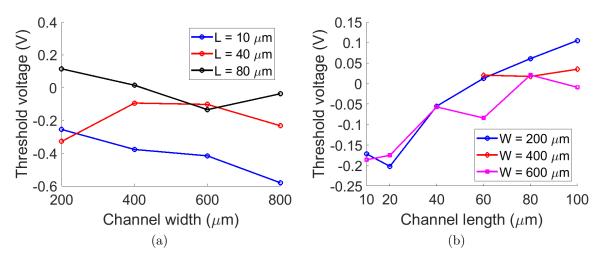

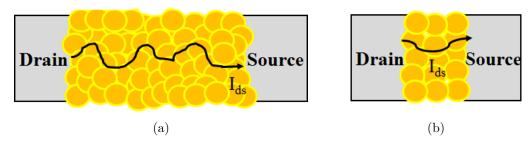

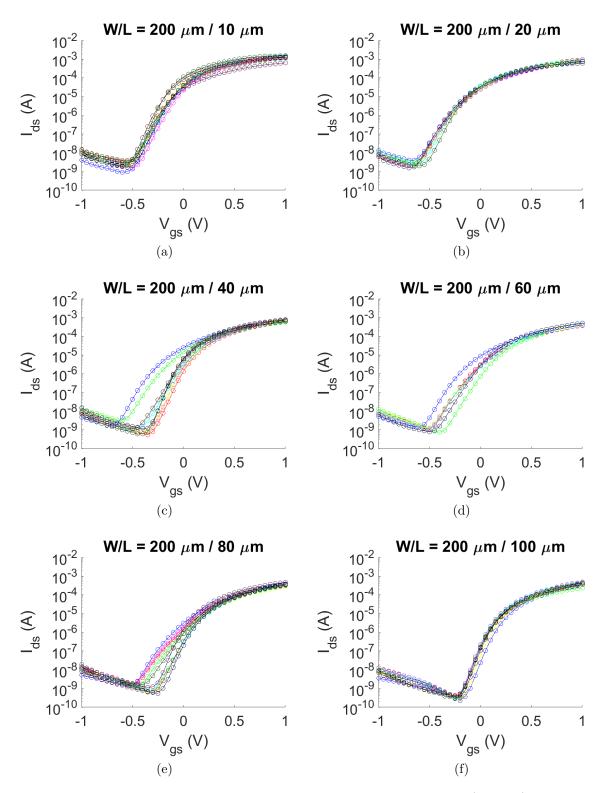

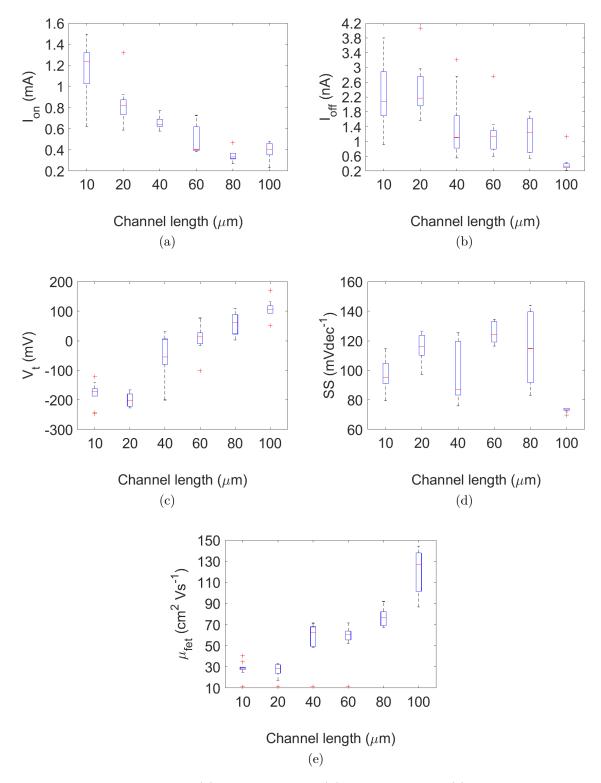

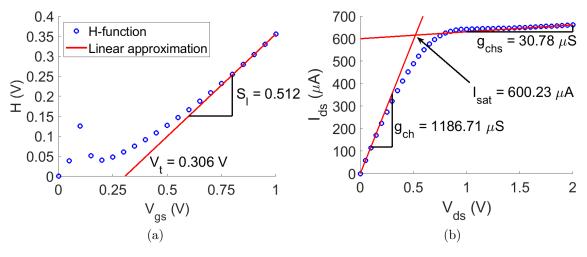

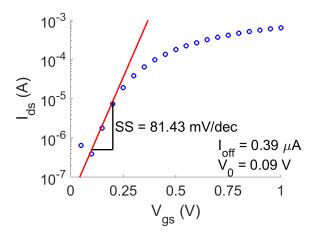

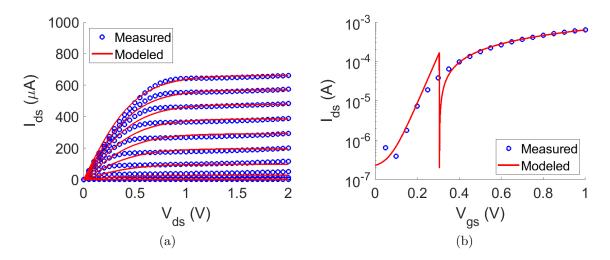

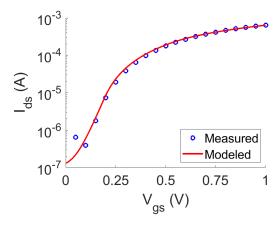

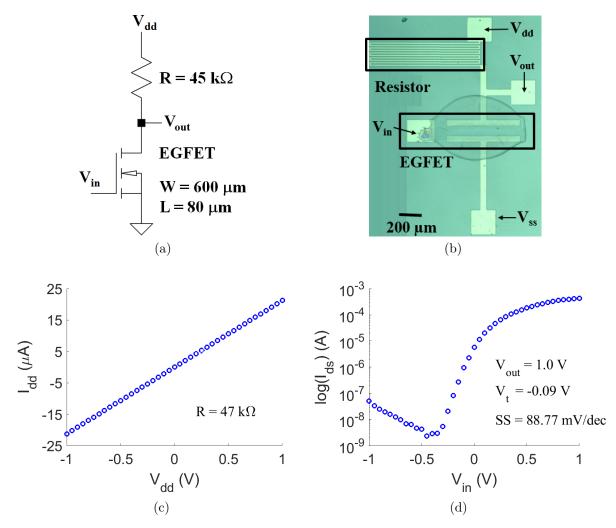

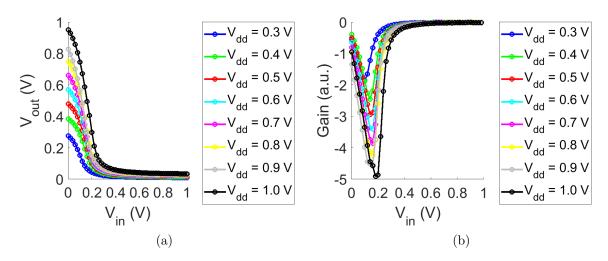

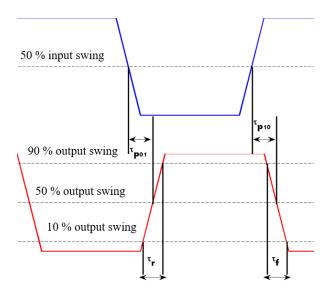

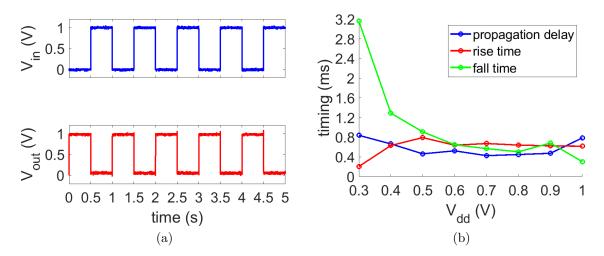

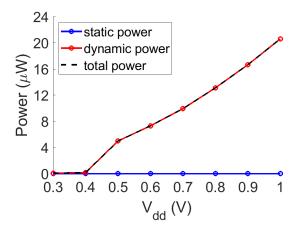

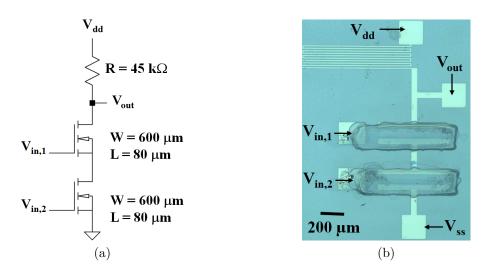

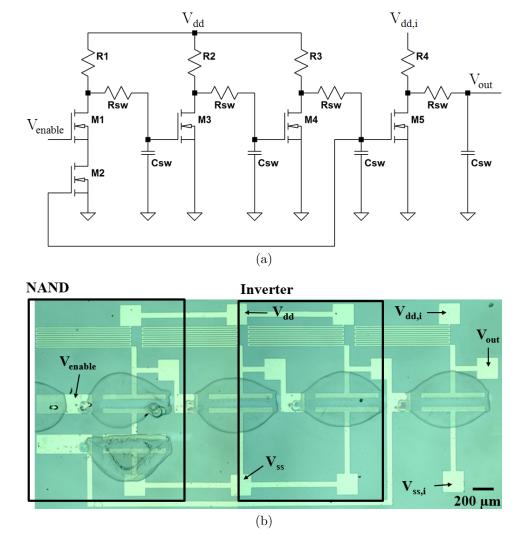

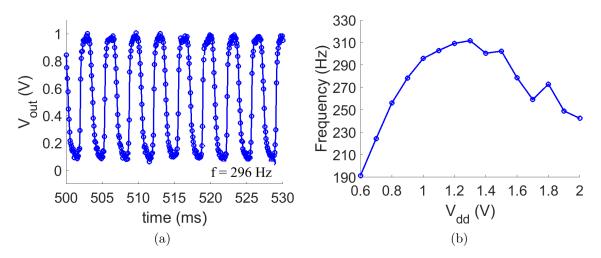

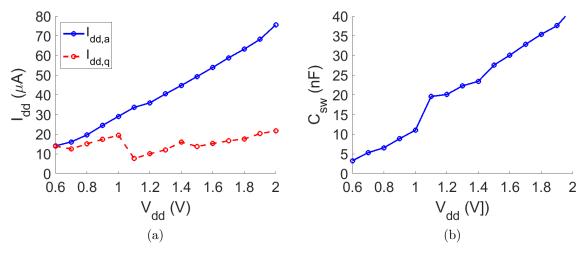

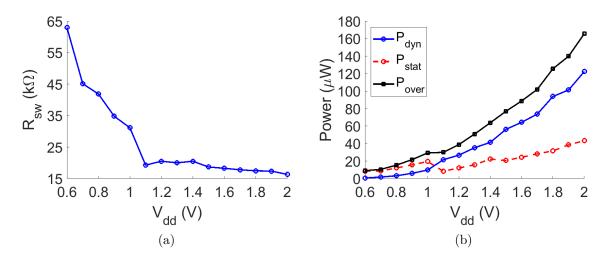

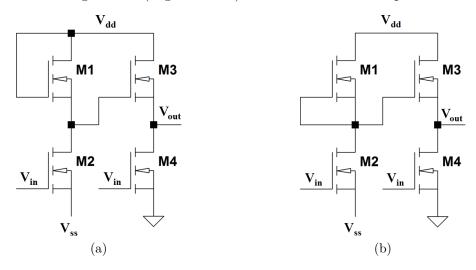

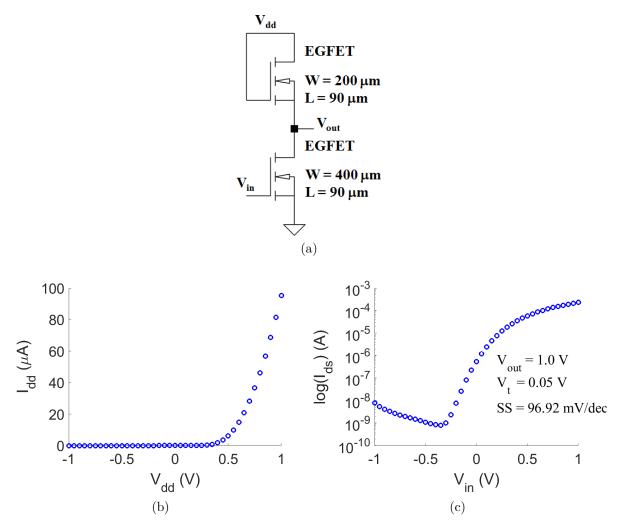

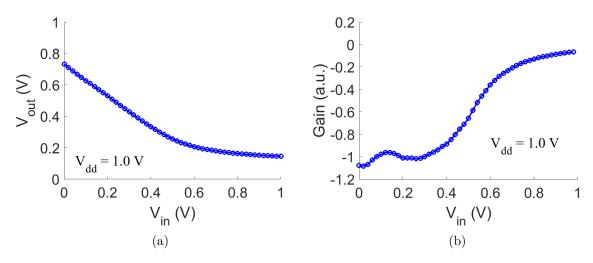

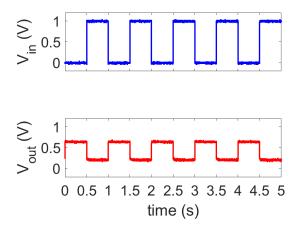

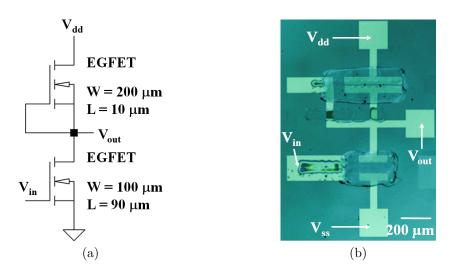

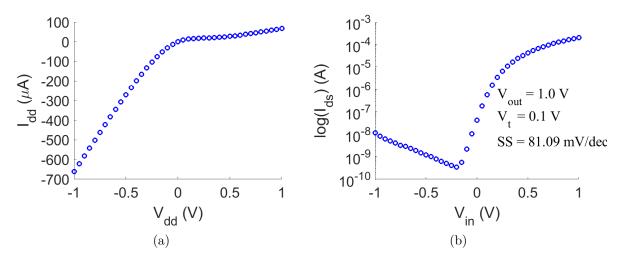

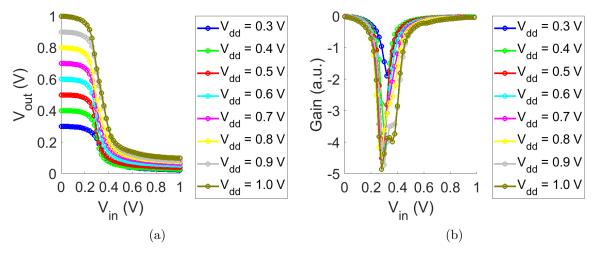

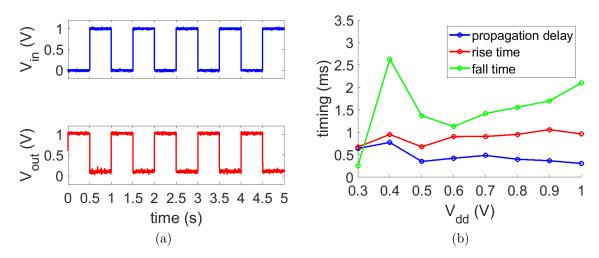

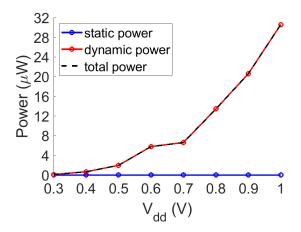

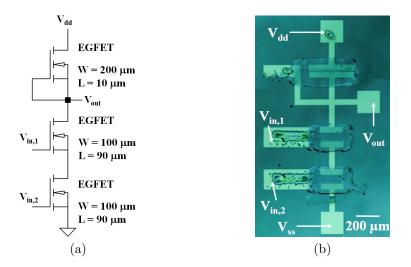

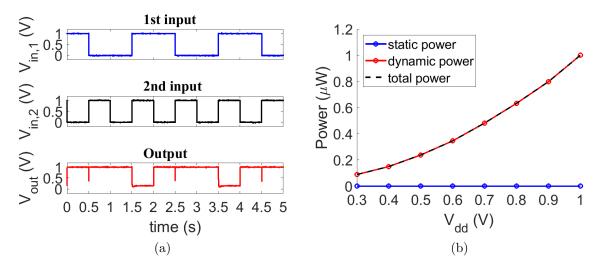

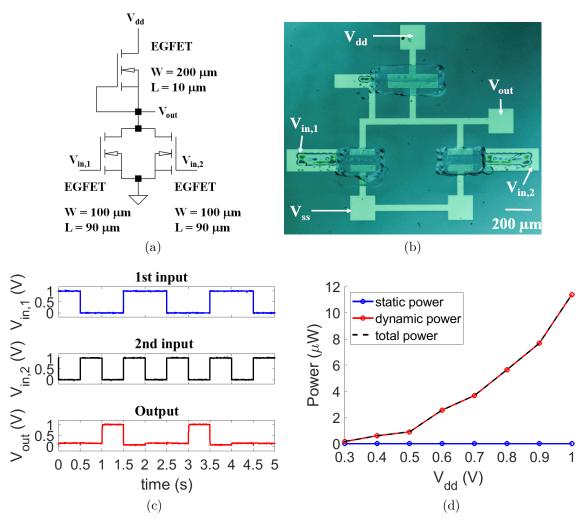

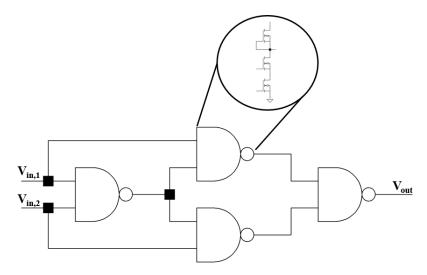

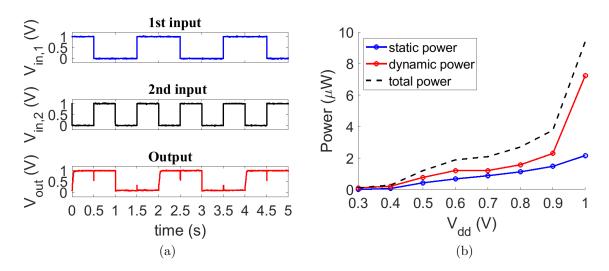

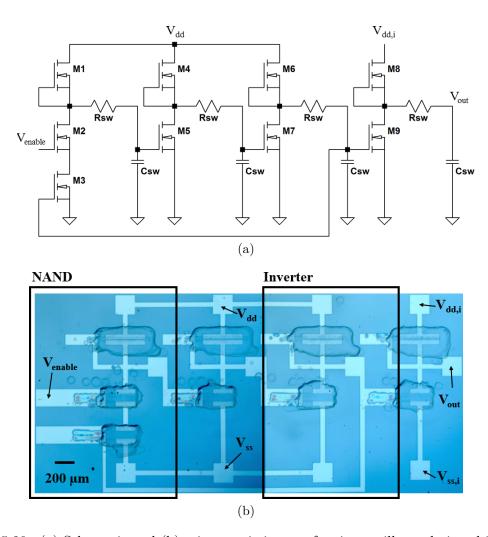

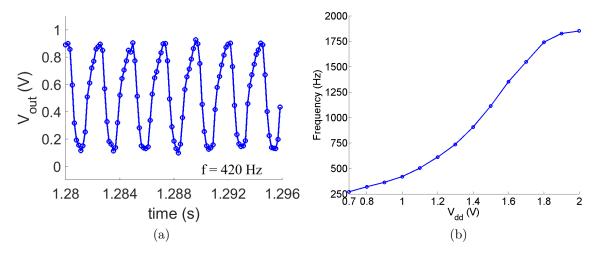

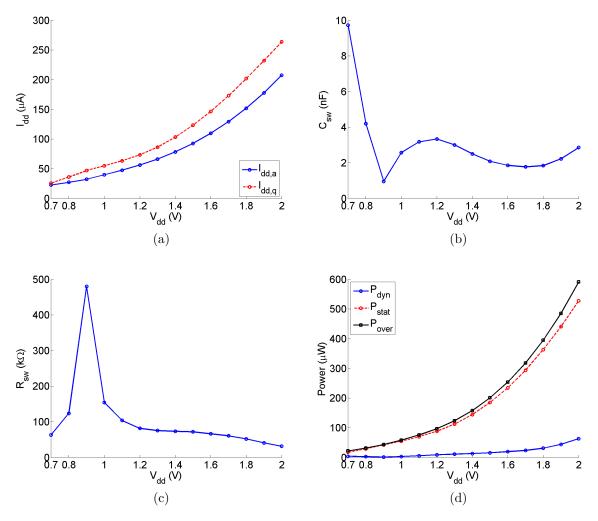

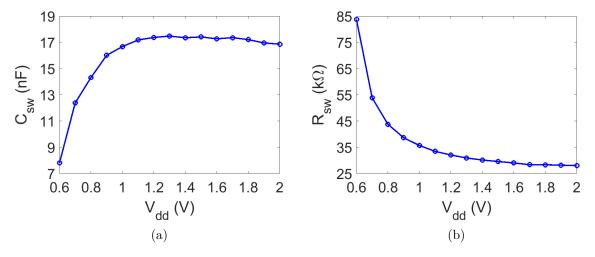

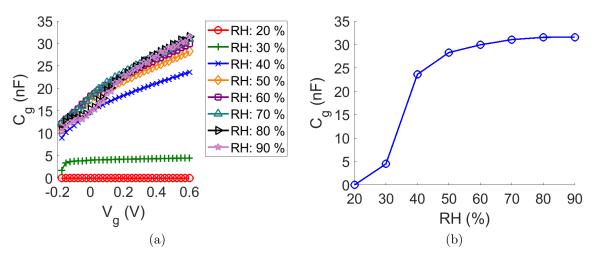

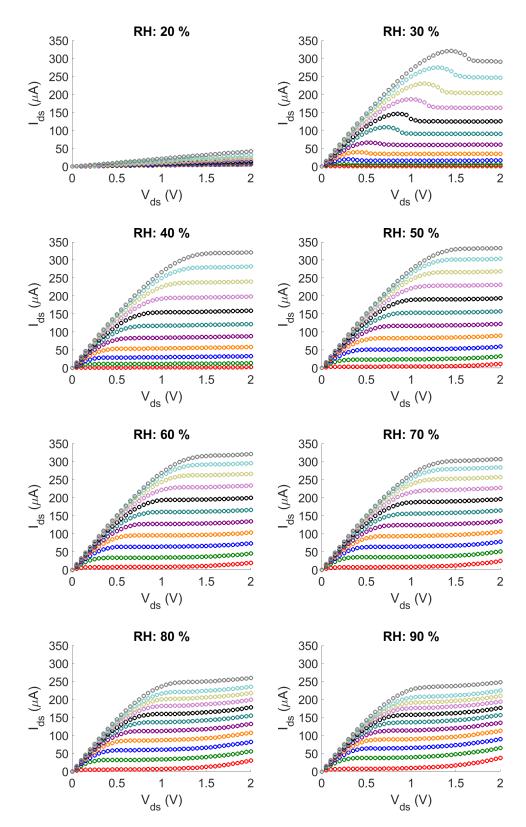

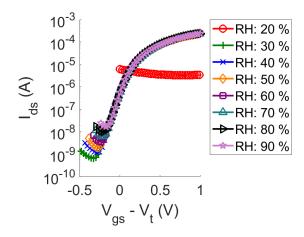

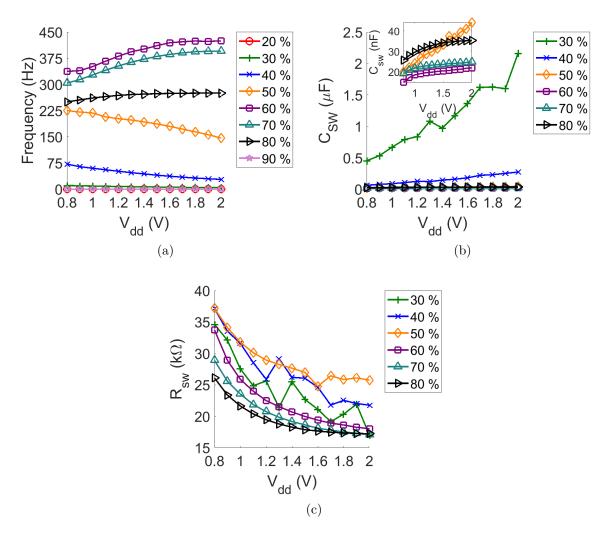

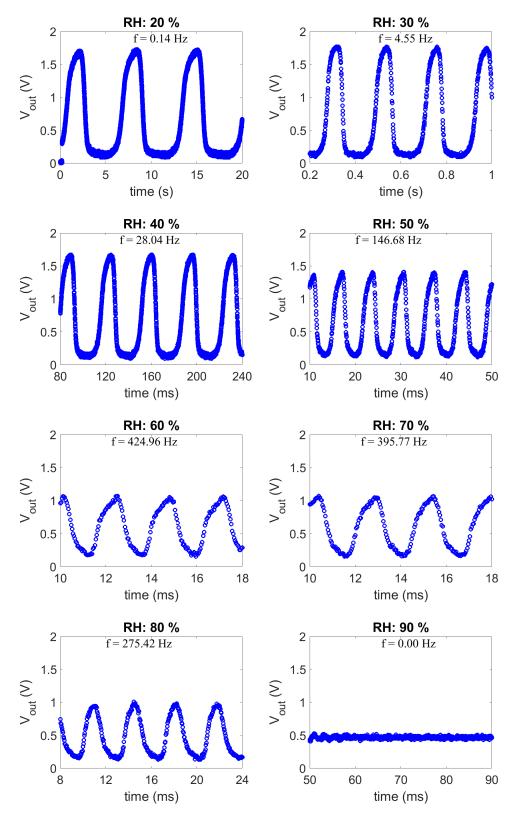

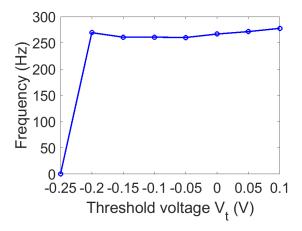

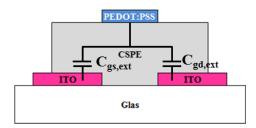

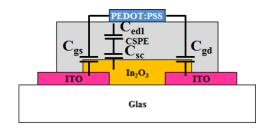

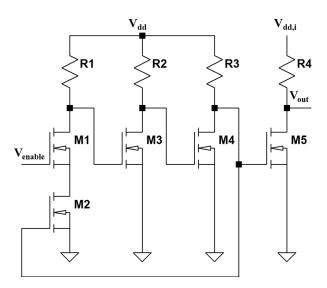

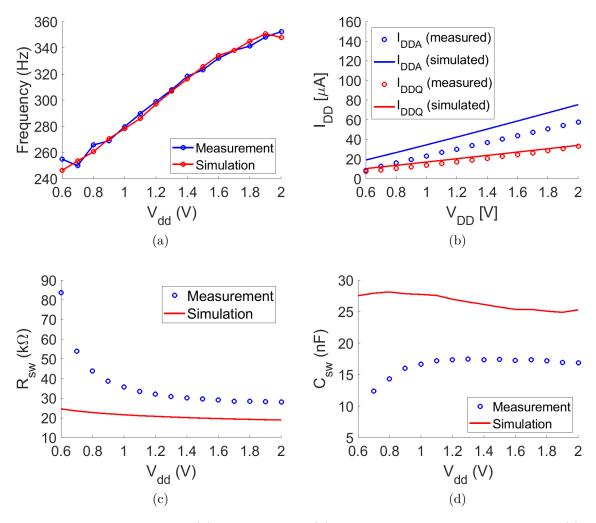

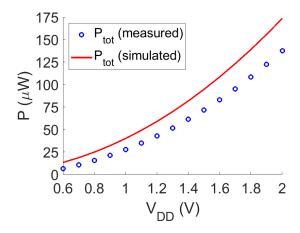

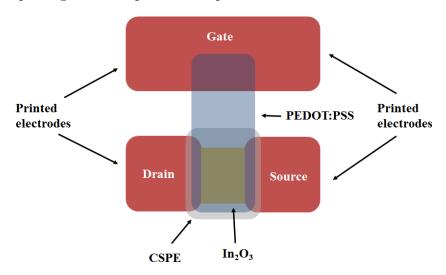

As previously mentioned, electrolytes are an interesting alternative to the dielectrics introduced in Section 2.2.2. These electrolytes can easily take into account the surface roughness of the printed semiconductor, improving the interface properties. TFTs with an electrolyte as the gating approach show high gate-capacitance values (1-10  $\mu$ Fcm<sup>-2</sup>), reducing the supply voltage requirements to  $\sim 1$  V. An electrolyte is a salt dissolved in a polar solvent, and is in liquid phase. Inside the solvent, the negatively charged ions (anions) got disassociate form the positively charged ions (cations), due to a force  $(F = q \cdot E)$  applied to the ions, and caused by an electrical field. By adding a polymer to the electrolyte, it is possible to solidify the electrolyte such that it is used as the gating material in TFT structures. However, by mixing a polymer into the electrolyte it must be ensured that the ion mobility stays sufficiently high. [38] Various kind of electrolytes are found in literature, where the main difference lies in the size of the ions or the level of solidification of the electrolyte. [57, 79, 110, 118]