# Security Aspects of Printed Electronics Applications

Zur Erlangung des akademischen Grades eines

Doktors der Ingenieurwissenschaften

von der KIT-Fakultät für Informatik des Karlsruher Instituts für Technologie (KIT)

genehmigte

### Dissertation

von

## Ahmet Turan Erozan

aus Sivas, Türkei

Tag der mündlichen Prüfung:06.07.2020Referent:Prof. Dr. Mehdi Baradaran Tahoori,<br/>Karlsruhe Institute of TechnologyKorreferent:Prof. Dr. Jasmin Aghassi-Hagmann,<br/>Offenburg University of Applied Sciences,<br/>Karlsruhe Institute of Technology

To my family

Ahmet Turan Erozan Tivoliplatz 1 76137 Karlsruhe

Hiermit erkläre ich an Eides statt, dass ich die von mir vorgelegte Arbeit selbstständig verfasst habe, dass ich die verwendeten Quellen, Internet-Quellen und Hilfsmittel vollständig angegeben haben und dass ich die Stellen der Arbeit - einschlielich Tabellen, Karten und Abbildungen die anderen Werken oder dem Internet im Wortlaut oder dem Sinn nach entnommen sind, auf jeden Fall unter Angabe der Quelle als Entlehnung kenntlich gemacht habe.

> Karlsruhe, May 2020 Ahmet Turan Erozan

## Acknowledgment

I would like to sincerely thank my advisers, Prof. Mehdi Tahoori and Prof. Jasmin Aghassi-Hagmann who continuously supported and encouraged me during my doctoral studies. I am grateful for insightful discussions we had throughout my research.

Words cannot express my gratitude to my family. Without them, this thesis would have been not possible. I am deeply grateful to my wife for her continuous support, understanding and technical discussions. My parents have always believed in me and encouraged me throughout my life for which I am thankful for. Besides, I thank my son who cheer me up in the last year of my PhD. I am indebted to them for their sacrifices to see me achieve this goal.

I would like to thank all of my colleagues in the Chair of Dependable Nano Computing and in MERAGEM Graduate School at Karlsruhe Institute of Technology for their technical as well as personal support. I especially thank Dr. Rajendra Bishnoi, Farhan Rasheed, Dr. Gabriel Cadilha Marques, Dr. Mohammad Saber Golanbari, Dennis Weller, Michael Hefenbrock, Dr. Arunkumar Vijayan, Dr. Shengcheng Wang, Dr. Anteneh Gebregiorgis, Sarath Mohanachandran Nair and Dr. Nour Sayed for their contributions, numerous technical discussions and invaluable support to my research.

I am thankful to Ms. Iris Schröder-Piepka and Ms. Siri Weiße for their friendly support and handling all the required documents during my PhD. I also thank Ms. Audrey Bohlinger for her help with the paperwork in the last months of my PhD.

Finally, I would like to thank The Ministry of Science, Research and Arts of the state of Baden-Württemberg for their financial support to my research in the form of MERAGEM Graduate School.

## Abstract

Printed Electronics (PE) is an emerging technology that complements conventional technologies with its unique features, hence, the market of PE technology has rapidly increased from US\$6B in 2010 to US\$41B in 2019, and projected to grow US\$153B in 2027. PE technology combines additive manufacturing and electronic functionality to enable the usage of various materials in the electronic components fabricated in the point-of-use, cost-effectively and environmentally friendly on a wide range of substrates that can be flexible, lightweight, transparent, large-area, and implantable. Therefore, PE technology enables the realization of envisioned applications such as smart packaging, disposables, smart labels, and electronic skin.

The progress of PE technology faces several challenges in yield, reliability, and performance that are primarily focused to advance PE technology. However, in recent years, the importance of security aspects of hardware platforms has been highlighted by numerous hardware-based attacks. Since the target PE applications can perform vital functionalities and contain sensitive information such as implantable devices and health monitoring patches, security flaws and trust issues in the supply chain can cause serious problems including fatality. Moreover, the unique features of PE technology such as additive manufacturing, larger feature sizes, fewer layers, and limited process steps result in more vulnerability to hardware-based attacks and new trust issues such as reverse engineering, counterfeiting, and hardware trojans. Besides, the adoption of countermeasures in conventional technologies is unsuitable and inefficient as such countermeasures introduce comparably high overhead to low-cost PE applications. Hence, this thesis provides a technology-specific assessment of hardware-level threats and their countermeasures in the form of resource-constrained hardware primitives to secure the supply-chain and functionalities of PE applications.

In the first contribution of this dissertation, we propose a printed Physical Unclonable Function (pPUF) design to provide secure keys that are used in several countermeasures such as authentication and fingerprinting. Also, we optimize the multi-bit pPUF design and achieve 31% area save for 16-bit key generation. Moreover, we develop an analysis framework including a Monte Carlo simulation flow for pPUF and perform simulation and fabrication-based analyses. The results show that pPUF has sufficient uniqueness and reliability metrics, and operates at the supply voltage of down to 0.5 V.

In the second contribution of this dissertation, we propose a compact printed True Random Number Generator (pTRNG) design to generate unpredictable keys for cryptographic functions and random authentication challenges. The pTRNG design mitigates the process variation using a printed resistor tuning method enabled by the customizable fabrication feature of PE so that the generated bits are mostly based on the random noise in the circuit, providing a true random behaviour. The simulation results demonstrate that the overall process variation of the TRNGs is mitigated by 110 times, and the generated bitstreams of TRNGs pass the National Institute of Standards and Technology Statistical Test Suite. Moreover, the characterization results of fabricated TRNGs prove that the TRNGs generate random bitstreams at the supply voltage of down to 0.5 V.

The third contribution of this dissertation is to describe the unique features of PE circuit design and fabrication which differ from conventional technologies resulting in the necessity of a new reverse engineering (RE) methodology. Hereof, we propose a robust RE methodology based on supervised learning for PE circuits to demonstrate their vulnerabilities to RE attacks. The RE results show that the proposed methodology reverse engineers numerous PE circuits without complex and expensive tools.

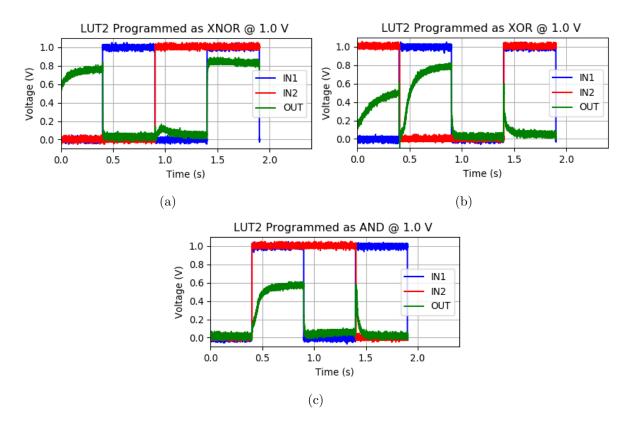

In the last contribution, we propose a one-time programmable printed Look-up Table (pLUT) that implements any printed digital circuits and enables countermeasures such as camouflaging, split manufacturing, and watermarking against various hardware-level attacks. The comparison of the PE implementation of the existing and the proposed pLUT designs shows that the proposed pLUT outperforms other designs in terms of area usage, worst-case delay, and power consumption. The proposed pLUT design is simulated, fabricated, and programmed with inkjet-printed conductive ink to implement XNOR, XOR, and AND gates to prove the programmability of the proposed design. The simulation and characterization results prove the functionality of the pLUT at 1 V.

## Zusammenfassung

Gedruckte Elektronik (Printed Electronics (PE)) ist eine neu aufkommende Technologie welche komplementär zu konventioneller Elektronik eingesetzt wird. Dessen einzigartigen Merkmale führten zu einen starken Anstieg von Marktanteilen, welche 2010 \$6 Milliarden betrugen, \$41 Milliarden in 2019 und in 2027 geschätzt \$153 Milliarden. Gedruckte Elektronik kombiniert additive Technologien mit funktionalen Tinten um elektronische Komponenten aus verschiedenen Materialien direkt am Verwendungsort, kosteneffizient und umweltfreundlich herzustellen. Die dabei verwendeten Substrate können flexibel, leicht, transparent, großflächig oder implantierbar sein. Dadurch können mit gedruckter Elektronik (noch) visionäre Anwendungen wie Smart-Packaging, elektronische Einmalprodukte, Smart Labels oder digitale Haut realisiert werden.

Um den Fortschritt von gedruckten Elektronik-Technologien voranzutreiben, basierten die meisten Optimierungen hauptsächlich auf der Erhöhung von Produktionsausbeute, Reliabilität und Performance. Jedoch wurde auch die Bedeutung von Sicherheitsaspekten von Hardware-Plattformen in den letzten Jahren immer mehr in den Vordergrund gerückt. Da realisierte Anwendungen in gedruckter Elektronik vitale Funktionalitäten bereitstellen können, die sensible Nutzerdaten beinhalten, wie zum Beispiel in implantierten Geräten und intelligenten Pflastern zur Gesundheitsüberwachung, führen Sicherheitsmängel und fehlendes Produktvertrauen in der Herstellungskette zu teils ernsten und schwerwiegenden Problemen. Des Weiteren, wegen den charakteristischen Merkmalen von gedruckter Elektronik, wie zum Beispiel additive Herstellungsverfahren, hohe Strukturgröße, wenige Schichten und begrenzten Produktionsschritten, ist gedruckte Hardware schon per se anfällig für hardware-basierte Attacken wie Reverse-Engineering, Produktfälschung und Hardware-Trojanern. Darüber hinaus ist die Adoption von Gegenmaßnahmen aus konventionellen Technologien unpassend und ineffizient, da solche zu extremen Mehraufwänden in der kostengünstigen Fertigung von gedruckter Elektronik führen würden. Aus diesem Grund liefert diese Arbeit eine Technologie-spezifische Bewertung von Bedrohungen auf der Hardware-Ebene und dessen Gegenmaßnahmen in der Form von Ressourcen-beschränkten Hardware-Primitiven, um die Produktionskette und Funktionalitäten von gedruckter Elektronik-Anwendungen zu schützen.

Der erste Beitrag dieser Dissertation ist ein vorgeschlagener Ansatz um gedruckte Physical Unclonable Functions (pPUF) zu entwerfen, welche Sicherheitsschlüssel bereitstellen um mehrere sicherheitsrelevante Gegenmaßnahmen wie Authentifizierung und Fingerabdrücke zu ermöglichen. Zusätzlich optimieren wir die multi-bit pPUF-Designs um den Flächenbedarf eines 16-bit-Schlüssels-Generators um 31% zu verringern. Außerdem entwickeln wir ein Analyse-Framework basierend auf Monte Carlo-Simulationen für pPUFs, mit welchem wir Simulationen und Herstellungs-basierte Analysen durchführen können. Unsere Ergebnisse haben gezeigt, dass die pPUFs die notwendigen Eigenschaften besitzen um erfolgreich als Sicherheitsanwendung eingesetzt zu werden, wie Einzigartigkeit der Signatur und ausreichende Robustheit. Der Betrieb der gedruckten p<br/>PUFs war möglich bis zu sehr geringen Betriebsspannungen von nur<br/>  $0.5\,\mathrm{V}.$

Im zweiten Beitrag dieser Arbeit stellen wir einen kompakten Entwurf eines gedruckten physikalischen Zufallsgenerator vor (True Random Number Generator (pTRNG)), welcher unvorhersehbare Schlüssel für kryptographische Funktionen und zufälligen "Authentication Challenges" generieren kann. Der pTRNG Entwurf verbessert Prozess-Variationen unter Verwendung von einer Anpassungsmethode von gedruckten Widerständen, ermöglicht durch die individuelle Konfigurierbarkeit von gedruckten Schaltungen, um die generierten Bits nur von Zufallsrauschen abhängig zu machen, und damit ein echtes Zufallsverhalten zu erhalten. Die Simulationsergebnisse legen nahe, dass die gesamten Prozessvariationen des TRNGs um das 110-fache verbessert werden, und der zufallsgenerierte Bitstream der TRNGs die "National Institute of Standards and Technology Statistical Test Suit"-Tests bestanden hat. Auch hier können wir nachweisen, dass die Betriebsspannungen der TRNGs von mehreren Volt zu nur 0.5 V lagen, wie unsere Charakterisierungsergebnisse der hergestellten TRNGs aufgezeigt haben.

Der dritte Beitrag dieser Dissertation ist die Beschreibung der einzigartigen Merkmale von Schaltungsentwurf und Herstellung von gedruckter Elektronik, welche sehr verschieden zu konventionellen Technologien ist, und dadurch eine neuartige Reverse-Engineering (RE)-Methode notwendig macht. Hierfür stellen wir eine robuste RE-Methode vor, welche auf Supervised-Learning-Algorithmen für gedruckte Schaltungen basiert, um die Vulnerabilität gegenüber RE-Attacken zu demonstrieren. Die RE-Ergebnisse zeigen, dass die vorgestellte RE-Methode auf zahlreiche gedruckte Schaltungen ohne viel Komplexität oder teure Werkzeuge angewandt werden kann.

Der letzte Beitrag dieser Arbeit ist ein vorgeschlagenes Konzept für eine "one-time programmable" gedruckte Look-up Table (pLUT), welche beliebige digitale Funktionen realisieren kann und Gegenmaßnahmen unterstützt wie Camouflaging, Split-Manufacturing und Watermarking um Attacken auf der Hardware-Ebene zu verhindern. Ein Vergleich des vorgeschlagenen pLUT-Konzepts mit existierenden Lösungen hat gezeigt, dass die pLUT weniger Flächenbedarf, geringere worst-case Verzögerungszeiten und Leistungsverbrauch hat. Um die Konfigurierbarkeit der vorgestellten pLUT zu verifizieren, wurde es simuliert, hergestellt und programmiert mittels Tintenstrahl-gedruckter elektrisch leitfähiger Tinte um erfolgreich Logik-Gatter wie XNOR, XOR und AND zu realisieren. Die Simulation und Charakterisierungsergebnisse haben die erfolgreiche Funktionalität der pLUT bei Betriebsspannungen von nur 1 V belegt.

# **Table of Contents**

| A  | cknov        | vledgment                                                                                                                                 | v             |

|----|--------------|-------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| Al | ostrad       | ct                                                                                                                                        | viii          |

| Ζι | usamı        | nenfassung                                                                                                                                | x             |

| Ta | able o       | of Contents                                                                                                                               | xiii          |

| Li | st of        | Figures                                                                                                                                   | xviii         |

| Li | st of        | Tables                                                                                                                                    | xix           |

| 1  |              | oduction<br>Problem Statement and Objective                                                                                               | <b>1</b><br>3 |

|    | $1.1 \\ 1.2$ | Thesis Contributions                                                                                                                      | 3<br>5        |

|    | 1.2          | 1.2.1       Inkjet-Printed Physical Unclonable Function         1.2.2       Compact True Random Number Generator based on Inkjet-Printing | 5             |

|    |              | Technology                                                                                                                                | 5             |

|    |              | 1.2.3 Reverse Engineering of Printed Electronics Circuits                                                                                 | 6             |

|    |              | 1.2.4 Printed Look-Up Table-based Programmable Printed Digital Circuit                                                                    | 6             |

|    | 1.3          | Outline                                                                                                                                   | 6             |

| 2  | Bac          | kground                                                                                                                                   | 9             |

|    | 2.1          | Printed Electronics                                                                                                                       | 9             |

|    | 2.2          | Physical Unclonable Function                                                                                                              | 13            |

|    | 2.3          | True Random Number Generator                                                                                                              | 14            |

|    | 2.4          | Reverse Engineering                                                                                                                       | 15            |

| 3  | Inkj         | et-Printed Physical Unclonable Function                                                                                                   | 17            |

|    | 3.1          | Proposed Printed PUF                                                                                                                      | 18            |

|    |              | 3.1.1 Single-bit Printed PUF                                                                                                              | 19            |

|    |              | 3.1.2 Multi-bit Printed PUF                                                                                                               | 19            |

|    | 3.2          | Simulation-based Analysis Framework                                                                                                       | 21            |

|    |              | 3.2.1 Overall Printed PUF Analysis Flow                                                                                                   | 21            |

|    |              | 3.2.2 Variation Modelling                                                                                                                 | 22            |

|    |              | 3.2.3 Temperature and Noise Modeling                                                                                                      | 24            |

|    | 3.3          | Simulation Results                                                                                                                        | 25            |

|    |              | 3.3.1 Design Parameters                                                                                                                   | 25            |

|    |              | 3.3.2 PUF Metrics and Design Space Exploration                                                                                            | 26            |

|    | 3.4          | Fabrication Results                                                                                                                       | 28            |

|    |              | 3.4.1 Fabrication Parameters                                                                                                              | 29            |

|   |      | 3.4.2   | Measurement Setup                                                                                                       |

|---|------|---------|-------------------------------------------------------------------------------------------------------------------------|

|   |      | 3.4.3   | Measurement Results                                                                                                     |

|   | 3.5  | Summ    | ary 31                                                                                                                  |

| 4 | Con  | npact T | rue Random Number Generator based on Inkjet Printing Technology 33                                                      |

|   | 4.1  |         | ive Printing of Resistors $\ldots \ldots 34$             |

|   | 4.2  | Propo   | sed Inkjet-Printed TRNG Design                                                                                          |

|   |      | 4.2.1   | TRNG Circuit   36                                                                                                       |

|   |      | 4.2.2   | Resistor Tuning Flow                                                                                                    |

|   | 4.3  | Simula  | ation-based Analysis                                                                                                    |

|   |      | 4.3.1   | Simulation Setup                                                                                                        |

|   |      | 4.3.2   | Resistor Tuning Flow Results    40                                                                                      |

|   |      | 4.3.3   | Analysis of Temperature Effect on Generated Bits 41                                                                     |

|   |      | 4.3.4   | NIST-STS Test Results                                                                                                   |

|   | 4.4  | Fabric  | ation-based Analysis                                                                                                    |

|   |      | 4.4.1   | Fabrication and Characterization Setup 43                                                                               |

|   |      | 4.4.2   | Results                                                                                                                 |

|   |      | 4.4.3   | Discussion on comparison with existing TRNGs                                                                            |

|   |      | 4.4.4   | Suitability of TRNG postprocessing techniques                                                                           |

|   | 4.5  | Summ    | $ary \dots \dots$ |

| 5 | Rev  | erse En | igineering of Printed Electronics Circuits 49                                                                           |

|   | 5.1  | Motiva  | ation of This Work                                                                                                      |

|   | 5.2  | Revers  | se Engineering Methodology of Printed Electronics                                                                       |

|   |      | 5.2.1   | Supervised Machine Learning                                                                                             |

|   |      | 5.2.2   | Image Preprocessing and Training Label Preparation                                                                      |

|   |      | 5.2.3   | Extracting and Labeling of Patches                                                                                      |

|   |      | 5.2.4   | Feature Engineering                                                                                                     |

|   |      | 5.2.5   | Component Detection using Ensembles of Random Forests 56                                                                |

|   |      | 5.2.6   | Post-processing                                                                                                         |

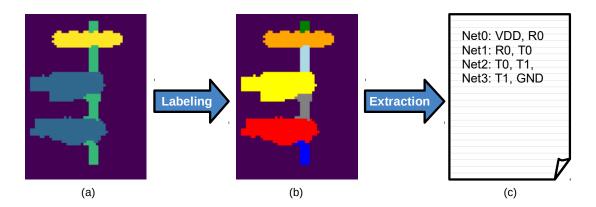

|   |      | 5.2.7   | Extraction of Netlist from Patches                                                                                      |

|   | 5.3  | Evalua  | ation Results                                                                                                           |

|   |      | 5.3.1   | Test Setup                                                                                                              |

|   |      | 5.3.2   | Evaluation Metrics                                                                                                      |

|   |      | 5.3.3   | Discussion of Results                                                                                                   |

|   | 5.4  | Summ    | ary and Future Work                                                                                                     |

| 6 | Prin |         | ok-Up Table-based Programmable Printed Digital Circuit 67                                                               |

|   | 6.1  | -       | sed Printed Look-up Table (pLUT)                                                                                        |

|   |      | 6.1.1   | Existing LUT designs 69                                                                                                 |

|   |      | 6.1.2   | Proposed pLUT circuit                                                                                                   |

|   |      | 6.1.3   | Overall system Architecture    71                                                                                       |

|   |      | 6.1.4   | Fabrication and Configuration Flow    71                                                                                |

|   | 6.2  | -       | imental Results                                                                                                         |

|   |      | 6.2.1   | Simulation, Fabrication and Characterization Setup                                                                      |

|   |      | 6.2.2   | Simulation-based Comparison of LUT Circuits                                                                             |

|   |      | 6.2.3   | Circuit Synthesis Results with pLUT2                                                                                    |

|     | 6.3    | 6.2.4 Fabrication Results of Proposed pLUT |    |

|-----|--------|--------------------------------------------|----|

|     |        |                                            |    |

|     | 6.4    | Summary                                    | 79 |

| 7   | Con    | clusions and Outlook                       | 81 |

|     | 7.1    | Conclusions                                | 81 |

|     | 7.2    | Outlook                                    | 82 |

| Bi  | oliogr | raphy                                      | 82 |

| Lis | t of   | Publications                               | 95 |

# List of Figures

| 1.1<br>1.2 | Reported and predicted market growth of Printed Electronics [1, 2] Examples of Printed Electronics applications. (a) Printed electrochromic display on flexible substrate [3]. (b) Tacttoo: thin and feel-through tattoo for on-skin tactile output [4]. (c) BodyNet sticker: wireless sensors that stick to skin to track health indicators [5]. (d) Printed energy harvesting circuit [3]. (e) PrintSense: on-surface sensing technique for planar, curved and flexible surfaces [6]. (f) Comfortable, disposable health patch with long battery life to measure | 1  |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

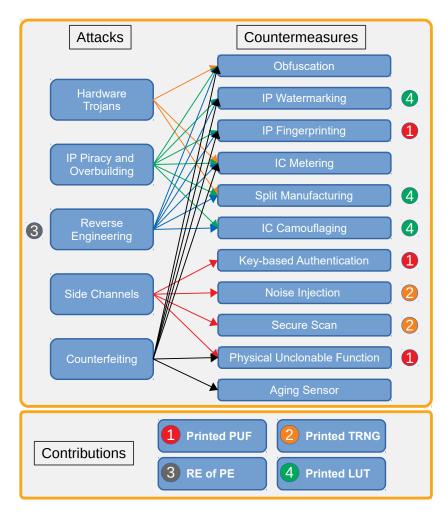

| 1.3        | vital signs [7]. (g) Flexible tags that communicate with standard touch screens [8, 9]. (h) Intelligent shoe sole that measures distribution of pressure of foot [10]. Overview of hardware-level attacks, countermeasures, and contributions of this thesis in different security aspects of printed electronics. (1) Printed Physical Unclonable Function, (2) Printed True Random Number Generator, (3) Reverse Engineering of Printed Electronics, (4) Printed Look-up Table                                                                                   | 2  |

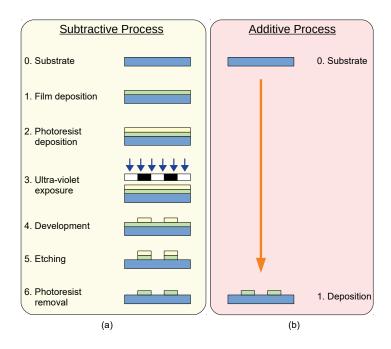

| 2.1        | Processing steps to pattern a structure in a typical (a) subtractive process in-<br>volving etching, (b) fully-additive process [11].                                                                                                                                                                                                                                                                                                                                                                                                                              | 10 |

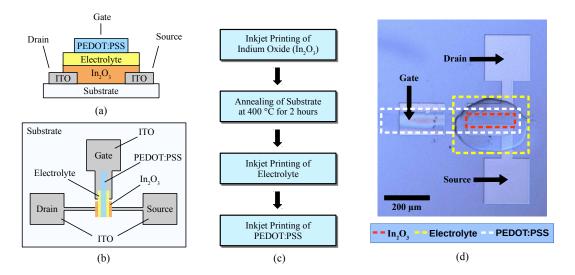

| 2.2        | Description of Electrolyte-gated transistor (EGT) technology. (a) Cross-sectional view of EGT. (b) Top view of EGT. (c) Fabrication process of EGT. (d) Optical                                                                                                                                                                                                                                                                                                                                                                                                    |    |

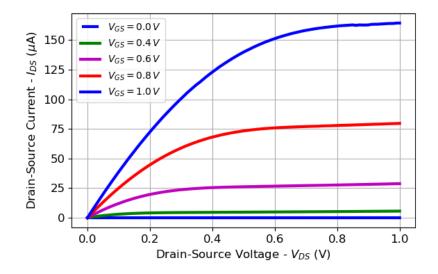

| 2.3        | image of a fabricated EGT device $[12, 13]$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 11 |

| 2.4        | an EGT (width = $100 \mu m$ , length = $40 \mu m$ )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 11 |

|            | Probe Station used for characterization.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 12 |

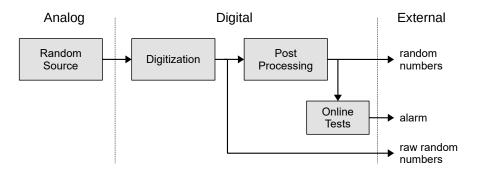

| 2.5        | Generic architecture of True Random Number Generator (TRNG)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 15 |

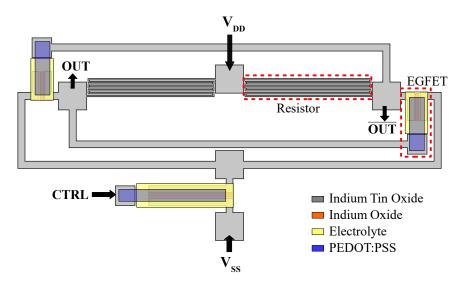

| 3.1        | (a) Proposed single-bit pPUF circuit. (b) Simulated timing diagram of a single-<br>bit pPUF circuit (A sample from Monte Carlo simulation using parameters:                                                                                                                                                                                                                                                                                                                                                                                                        |    |

|            | $R_1 = R_2 = 20 k\Omega,  W_1 = W_2 = 100 \mu m,  W_3 = 200 \mu m,  L_1 = L_2 = L_3 = 40 \mu m).  \dots  \dots$                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 18 |

| 3.2        | Layout of proposed single-bit printed PUF circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 19 |

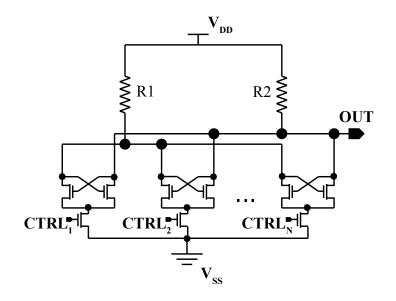

| 3.3        | Proposed multi-bit printed PUF circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 20 |

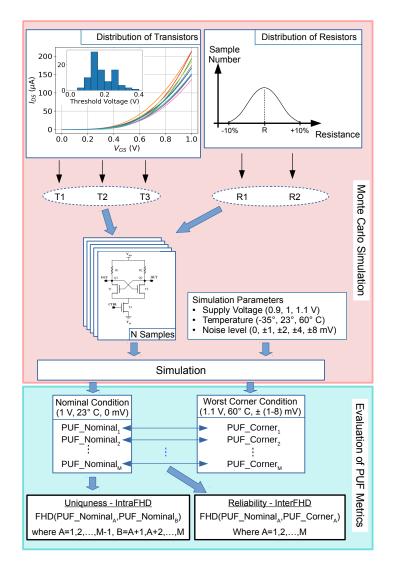

| 3.4        | Analysis flow for proposed printed PUF that contains Monte Carlo simulation<br>and evaluation of PUF metrics.                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 21 |

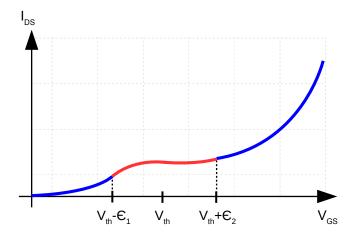

| 3.5        | An example interpolation problem of fixed near threshold regime boundaries in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

|            | transfer curve $(I_{DS}-V_{GS})$ of an EGT modeling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 22 |

| 3.6        | Flow for finding optimal epsilon values, $\epsilon_1$ and $\epsilon_2$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 23 |

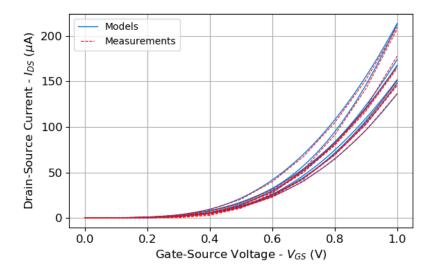

| 3.7        | Transfer curves $(I_{DS}-V_{GS})$ of measurement and model of EGTs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 24 |

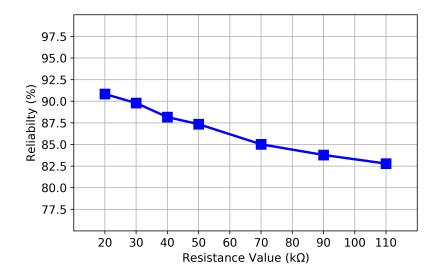

| 3.8        | Reliability results where $\pm 8mV$ noise is introduced for various resistance values .                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 25 |

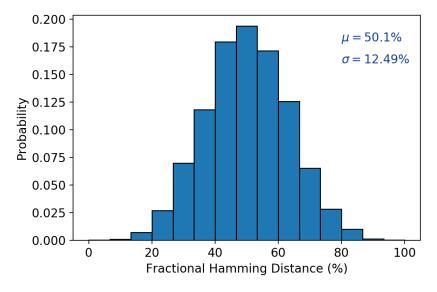

| 3.9        | Uniqueness (inter-FHD) of the proposed printed PUF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 26 |

| 3.10       | Reliability (intra-FHD) of the proposed printed PUF with different noise levels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

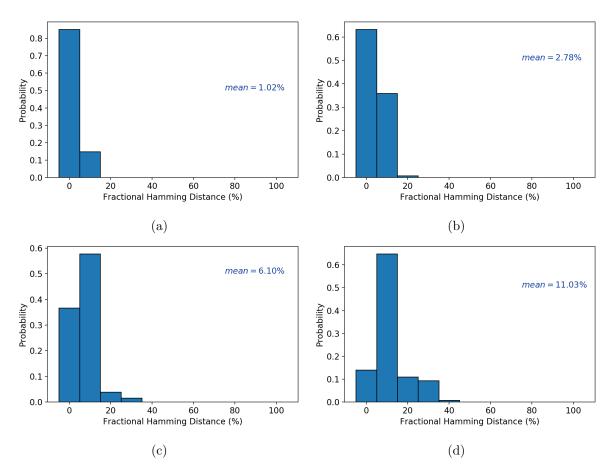

|            | a) $\pm 1  mV$ b) $\pm 2  mV$ c) $\pm 4  mV$ d) $\pm 8  mV$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 27 |

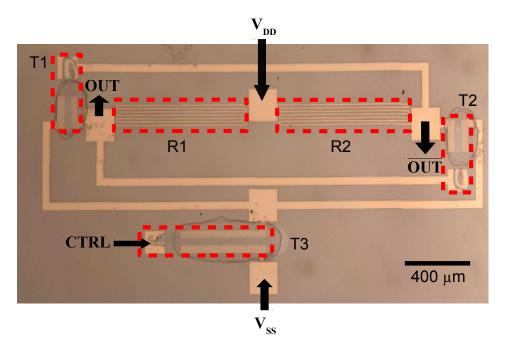

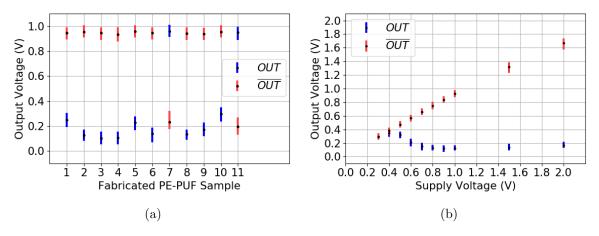

| 3.12         | Optical image of a fabricated single-bit printed PUF circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 28<br>29 |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

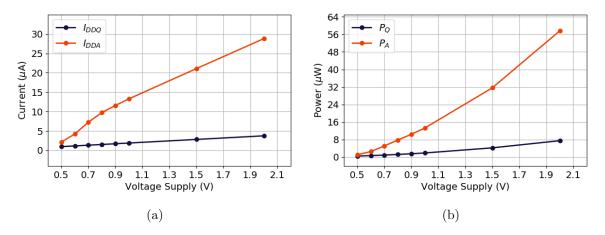

| 3.14         | at supply voltage of 1 V. (b) Measured output voltage range of fabricated single-<br>bit printed PUF at supply voltage of 2 V down to $0.3 V$ (a) Quiescent and active currents $(I_{DDQ}, I_{DDA})$ of fabricated single-bit printed<br>PUF at various supply voltages. (b) Quiescent and active power consumption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 30       |

|              | $(P_Q, P_A)$ of fabricated single-bit printed PUF at various supply voltages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 31       |

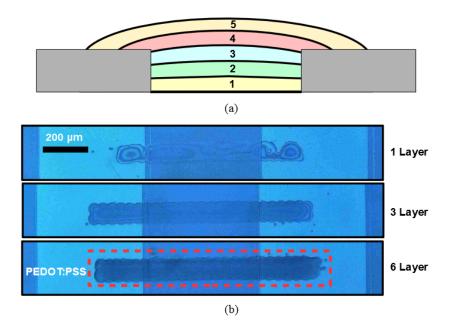

| 4.1          | (a) Illustration of additively printed layers. (b) Top-view photos of fabricated printed resistors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 34       |

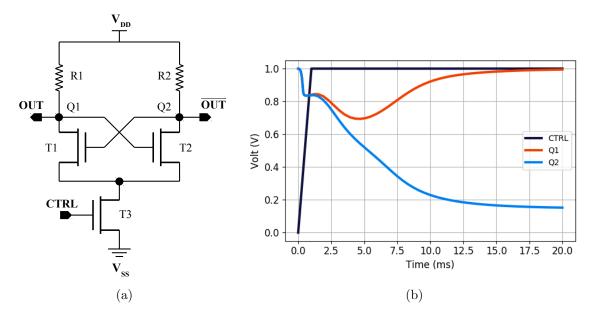

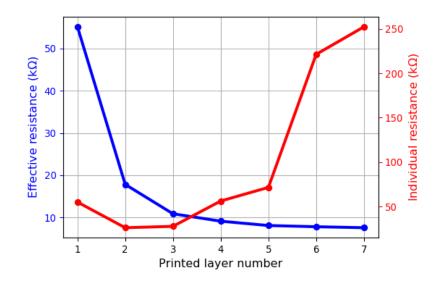

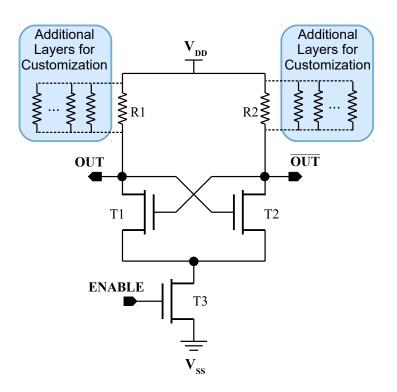

| $4.2 \\ 4.3$ | Effective and individual resistance of printed resistors with different layers Proposed TRNG circuit with customizable resistors. Overall process variation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 34<br>35 |

|              | of circuit is mitigated using additional layers for customization of printed resistors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 36       |

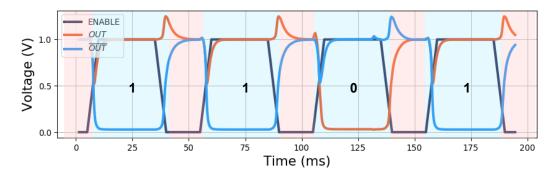

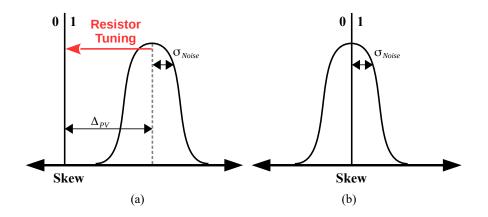

| $4.4 \\ 4.5$ | Example simulated timing diagram of output of an inkjet-printed TRNG circuit.<br>Illustration of behavior of (a) skewed, (b) non-skewed circuit ( $\Delta_{PV}$ : skew be-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 37       |

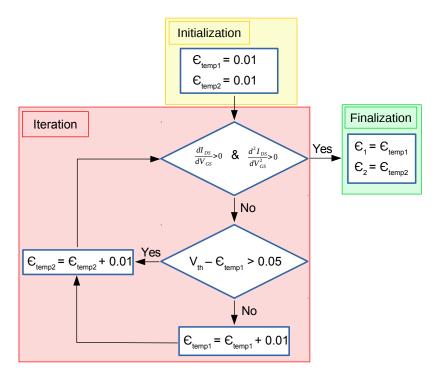

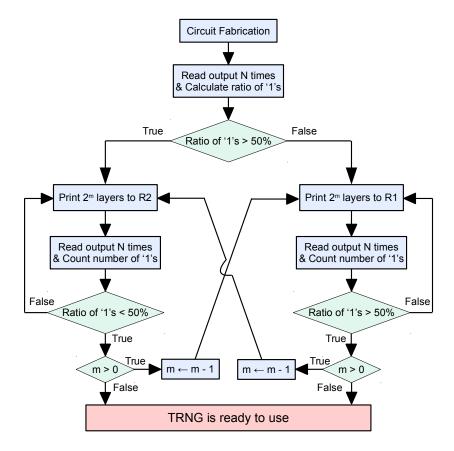

| 4.6          | cause of process variation, $\sigma_{Noise}$ : standard deviation of noise) [14]<br>Optimized resistor tuning flow to mitigate process variation of proposed TRNG<br>design. Resistors are additively tuned to converge ratio of ones to 50%. m and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 37       |

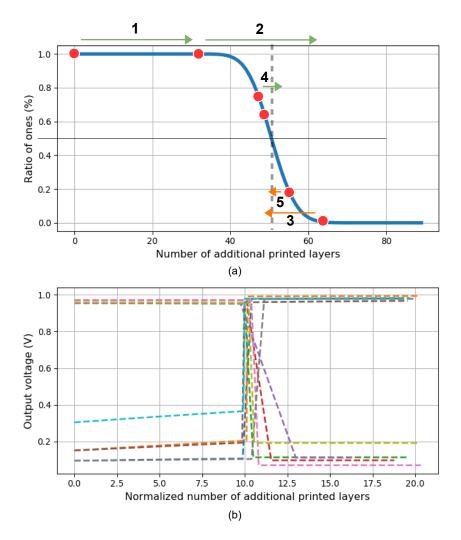

| 4.7          | N are flow parameters.       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       . <td>38</td> | 38       |

|              | TRNG instance under noise ( $\mu = 0V, \sigma = 3mV$ ). Red dots indicate TRNG state and orange and green arrows represent change of TRNG state by printing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |

|              | additional layers to $R1$ and $R2$ respectively, based on the tuning flow presented<br>in Figure 4.6. (b) Output voltage level vs. normalized number of additionally                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |

|              | printed layers of 10 TRNG instances (layer numbers where output is flipped are normalized to 10.).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 39       |

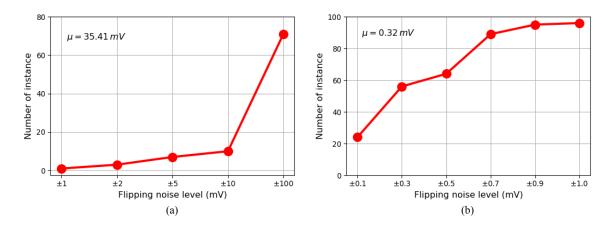

| 4.8          | Number of TRNG instances between various flipping noise levels (a) before                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |

| 4.9          | resistor tuning, (b) after resistor tuning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 40       |

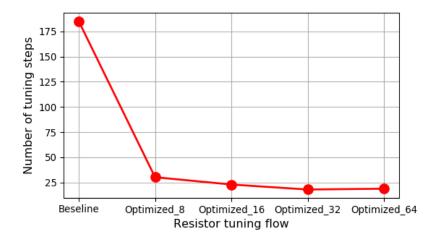

|              | one by one additional layer printing flow. 8, 16, 32 and 64 denote initial $2^m$ value.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 41       |

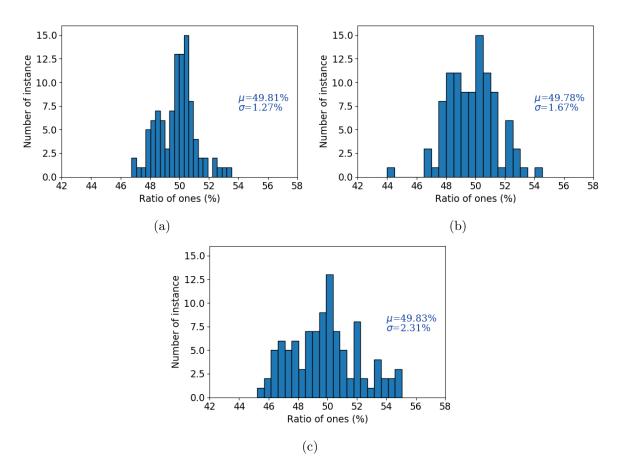

| 4.10         | Distribution of ratio of ones out of 100 bits for tuned 100 Monte Carlo TRNG samples at (a) 25°C, (b) 60°C, (c) -35°C. Sigma values are similar in distributions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |

| 4 1 1        | indicating that temperature effect on randomness is negligible. $\dots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 42       |

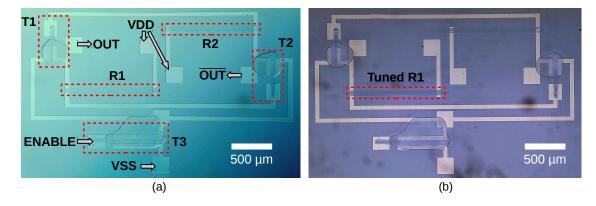

|              | Images of a fabricated TRNG (a) Before resistor tuning. (b) After resistor tuning.<br>Timing manuform of a fabricated TRNC or parting at 1 V after resistor tuning.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 43       |

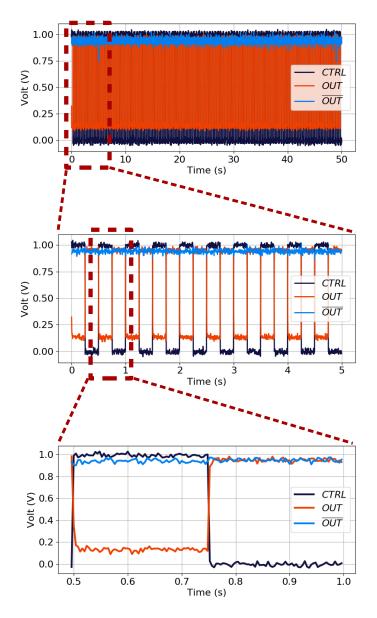

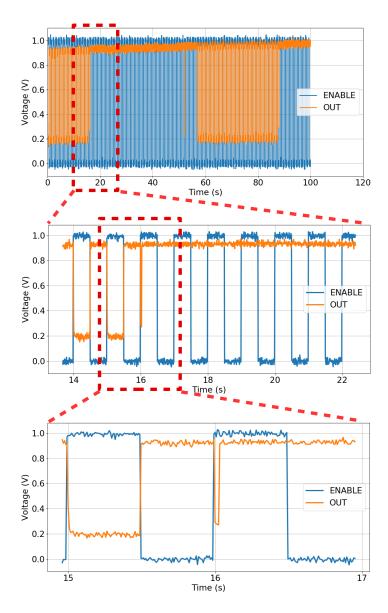

|              | Timing waveform of a fabricated TRNG operating at 1 V after resistor tuning.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 44       |

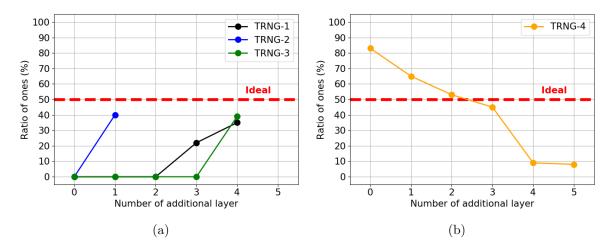

| 4.13         | Ratio of ones of out of 100 bits of fabricated TRNGs. (a) Ratio of ones for three TRNG converges to 50%. Bias due to process variation is mitigated by printing additional layer to corresponding printed resistor. (b) Ratio of ones for another                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |

|              | TRNG converges to 50%. While more layers are printed to same resistor, it converges to 0%.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 45       |

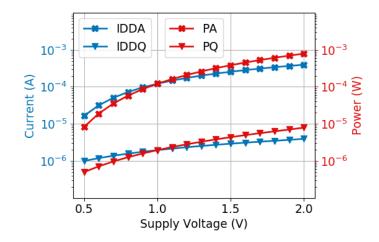

| 4.14         | Current and power measurements of tuned TRNG-3 at various supply voltages.<br>(left axis) Quiescent and active currents (IDDQ, IDDA), (right axis) quiescent                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 40       |

|              | and active power consumption (PQ, PA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 46       |

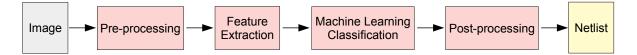

| 5.1          | Overview of reverse engineering methodology of printed electronics circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 51       |

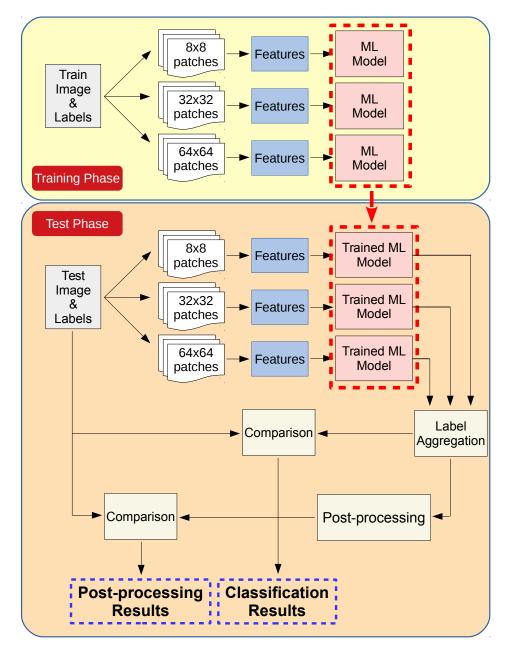

| 5.2  | Training and test processes of proposed reverse engineering methodology of              |    |

|------|-----------------------------------------------------------------------------------------|----|

|      | printed electronics circuits.                                                           | 52 |

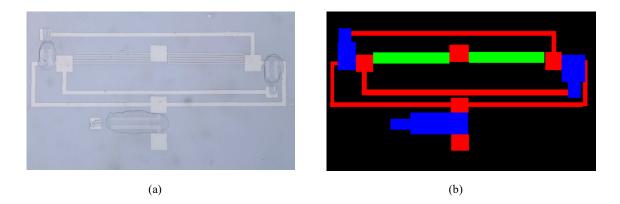

| 5.3  | (a) $PUF_2$ circuit image (b) Label of $PUF_2$ image; green: wire, blue: transistor,    |    |

|      | yellow: resistor, dark blue: blank                                                      | 54 |

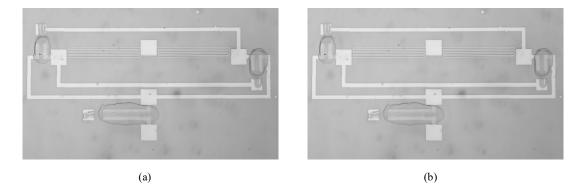

| 5.4  | Preprocessing of $PUF_2$ image, (a) Denoised $PUF_2$ image using bilateral filtering    |    |

|      | (b) Normalized $PUF_2$ (c) The Edges of $PUF_2$ extracted using Roberts cross           |    |

|      | operator (d) The result of Adaptive histogram equalization on $PUF_2$                   | 54 |

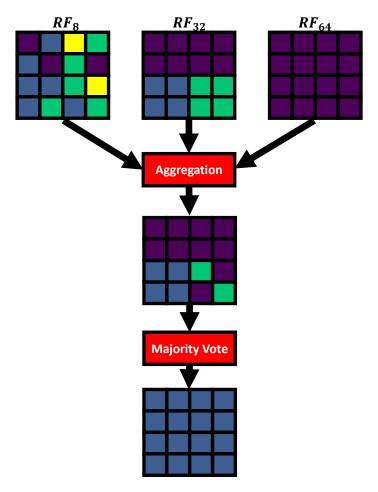

| 5.5  | A schematic illustration of the procedure used to aggregate the predicted labels        |    |

|      | of the three Random Forest models into a single label. The labels of $RF_8$ where       |    |

|      | unified to $16 \times 16$ blocks for readability. Note that even though the majority of |    |

|      | all smallest resolution patches are labeled $B$ (blank) after the aggregation, the      |    |

|      | second most frequent label, namely $T$ (transistor), is assigned after majority         |    |

|      | voting due to $B$ being ignored in this step                                            | 58 |

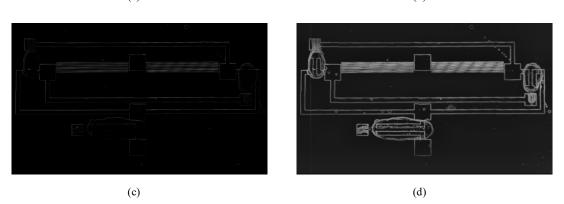

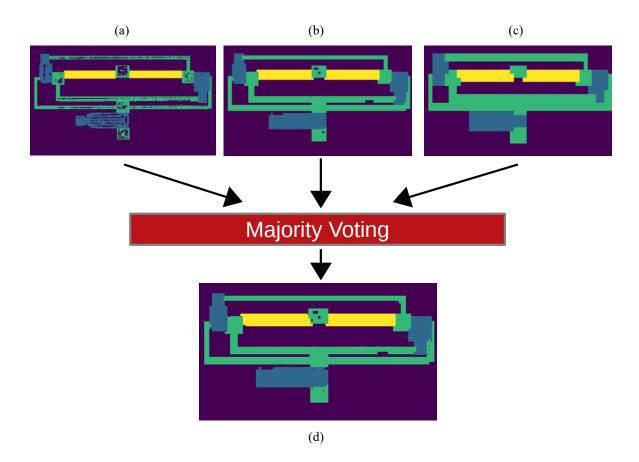

| 5.6  | Random forest prediction results, (a) Prediction of $RF_8$ (b) Prediction of $RF_{32}$  |    |

|      | (c) Prediction of $RF_{64}$ (d) Combination of three predictions by majority voting.    | 59 |

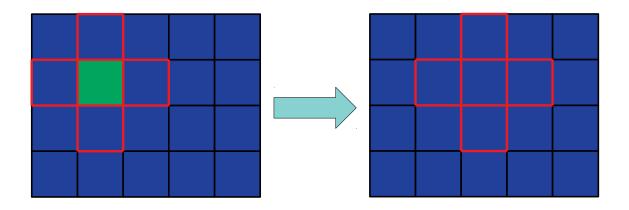

| 5.7  | The filter kernel set up around the green patch. The label is adjusted based on         |    |

|      | its value and the labels of the four horizontally and vertically adjoint patches.       |    |

|      | This is done for every patch in the image.                                              | 60 |

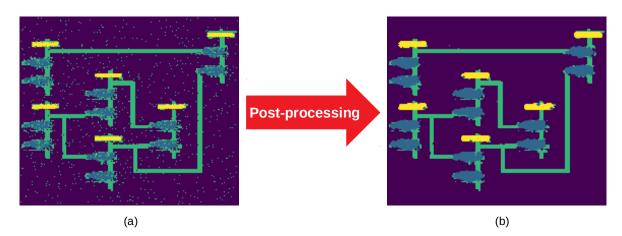

| 5.8  | Illustration of classification and post-processing results of $C17_1$ circuit. (a)      |    |

|      | classification results, (b) post-processing results                                     | 60 |

| 5.9  | Netlist extraction from patches to netlist. (a) Classified patches, (b) Labeled         |    |

|      | patches for annotation, and (c) Netlist of NAND gate                                    | 61 |

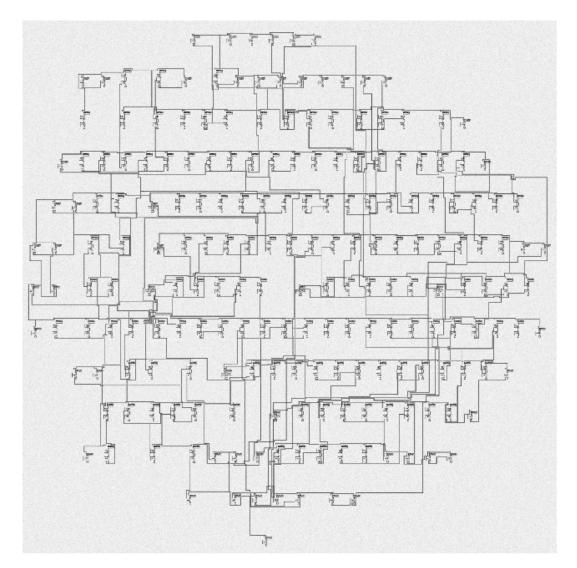

| 5.10 | Negative semi-real image of a C432 circuit. Randomly selected the preprocessed          |    |

|      | images of circuit elements are placed to noisy blank image, and connected using         |    |

|      | wires.                                                                                  | 61 |

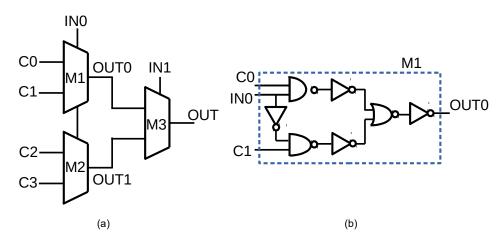

| 6.1  | Logic Gate(LG)-based Look-up Table. (a) LUT2 implementation, (b) LG-based               |    |

| 0.1  | multiplexer implementation                                                              | 68 |

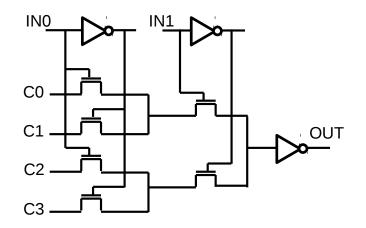

| 6.2  | Pass Transistor(PT)-based Look-up Table                                                 | 69 |

| 6.3  | (a) Proposed 1-input printed look-up table (pLUT1) in which functionality is set        | 03 |

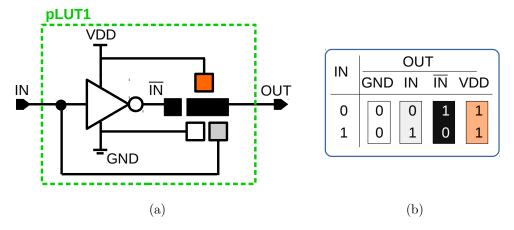

| 0.0  | using inkjet-printed conductive inks, (b) Illustration of pLUT1 programmability         |    |

|      | in table form. (pad colors indicate corresponding configuration in table.)              | 69 |

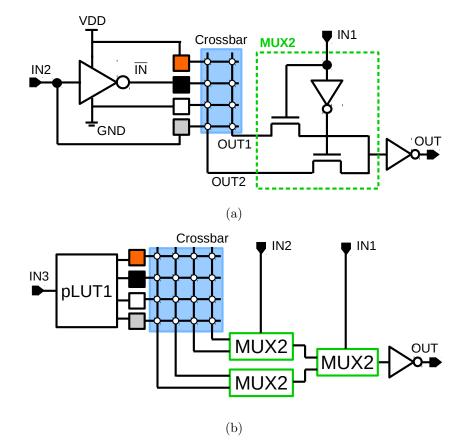

| 6.4  | (a) Proposed 2-input printed look-up table (pLUT2) containing multiplexer               | 00 |

| 0.1  | (MUX2). Crossbar is used to program LUT2 to desired functionality, (b) Pro-             |    |

|      | posed 3-input pLUT3                                                                     | 70 |

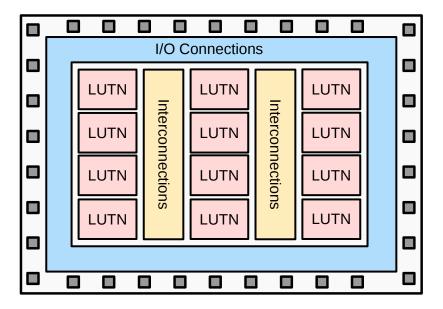

| 6.5  | Illustration of a programmable printed chip using N-input Look-up Tables (LUTNs)        |    |

|      | Number of input, N, can be chosen based on requirements. Interconnections and           | /  |

|      | I/O connections contains crossbars that are programmable and connects LUTNs             |    |

|      | and I/Os.                                                                               | 71 |

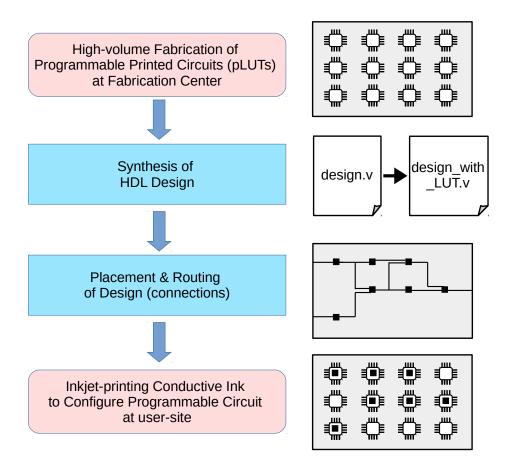

| 6.6  | Fabrication and configuration flow of pLUT based programmable printed chip.             |    |

|      | A programmable printed chip is fabricated in high-volume at fabrication center.         |    |

|      | At the user site, the target design HDL is synthesized, and then placed and             |    |

|      | routed (P&R) according to programmable chip. Finally, the programmable                  |    |

|      | chip is configured using inkjet printing at point-of-use                                | 72 |

| 6.7  | Comparison of various LUT implementations with different number of inputs               |    |

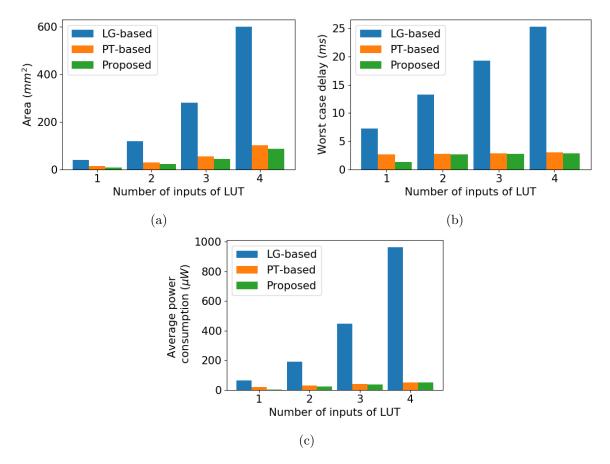

|      | in terms of (a) area, (b) worst-case delay, and (c) power consumption                   | 73 |

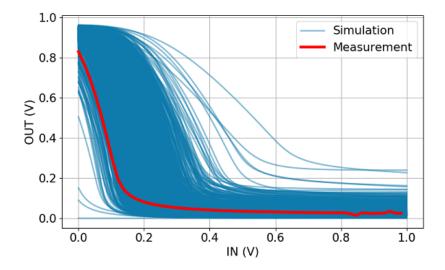

| 6.8  | Monte Carlo simulation and measurement of CLUT1 programmed as inverter    |    |

|------|---------------------------------------------------------------------------|----|

|      | $(\overline{IN})$                                                         | 74 |

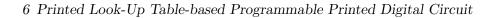

| 6.9  | LUT2s programmed with inkjet-printed conductive inks as (a) XOR gate, (b) |    |

|      | AND gate                                                                  | 76 |

| 6.10 | Timing diagram of fabricated programmable LUT2s programmed as (a) XNOR,   |    |

|      | (b) XOR, (c) AND at 1 V                                                   | 77 |

# List of Tables

| $2.1 \\ 2.2$        | Comparison of printing methods used in the manufacturing of PE [15]<br>Purposes for Reverse Engineering [16]                                                                                                                                                            | 10<br>16                               |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| $3.1 \\ 3.2 \\ 3.3$ | The mean saturated drain current of fabricated transistors with various widths<br>Saturated drain current ratios extracted from [17] for corner temperatures<br>Area usage of single-bit and multi-bit PE-PUF, and area improvements for                                | $\begin{array}{c} 20\\ 25 \end{array}$ |

|                     | various number of bits                                                                                                                                                                                                                                                  | 28                                     |

| 4.1                 | Design parameters of transistors and resistors used in simulation of TRNG de-<br>sign. Resistance of resistors is initial value before resistor tuning                                                                                                                  | 40                                     |

| 4.2                 | NIST test results. Generated bitstream includes 10000 bits from 100 simulated TRNG instances. (A test requires the P-value greater than 0.001 and the proportion greater than 96/100 to pass.                                                                           | 43                                     |

| $5.1 \\ 5.2$        | Circuit images used in evaluation, their explanations, and types                                                                                                                                                                                                        | 63                                     |

| 5.3                 | Classification indicates the accuracy before post-processing steps while post-<br>processing indicates the accuracy after post-processing steps. $\ldots \ldots \ldots \ldots$<br>$C17_1$ circuit precision and recall results before (Classification) and after (Post- | 64                                     |

| 0.0                 | processing) post-processing steps                                                                                                                                                                                                                                       | 64                                     |

| 5.4                 | Number of detected and total transistors, resistors and connections                                                                                                                                                                                                     | 65                                     |

| 6.1                 | Comparison of various LUT2 implementations in EGT technology in terms of area, delay, power and voltage level quality at 1 V.                                                                                                                                           | 74                                     |

| 6.2                 | Comparison of synthesis results of several ISCAS'85 and EPFL benchmark circuits with standard cells (NOT, NOR and NAND gates) and proposed pLUT2                                                                                                                        |                                        |

|                     | cell                                                                                                                                                                                                                                                                    | 75                                     |

## **1** Introduction

In the era of digitalization, products enabled by the advances in electronics have massively driven the market in almost every application fields such as communication, household appliances, automotive, internet of things, education, research, medical, and security. Moreover, the rapid growth in the semiconductor field, as projected in Moore's law, has enabled the development of new products or upgrading the existing ones in terms of functionality, speed and compactness [18, 19, 20]. However, conventional electronics has become incapable in addressing the increased demand for emerging applications such as the internet of disposable things (IoDT) [21] and electronic skin (e-skin) [22] due to their complex fabrication processes, mechanical properties, and minimum cost limitations.

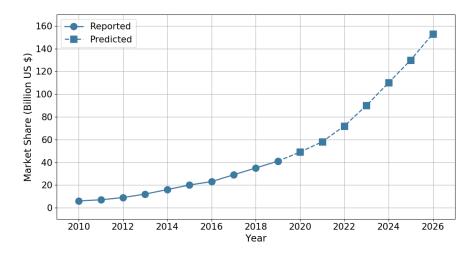

Figure 1.1: Reported and predicted market growth of Printed Electronics [1, 2].

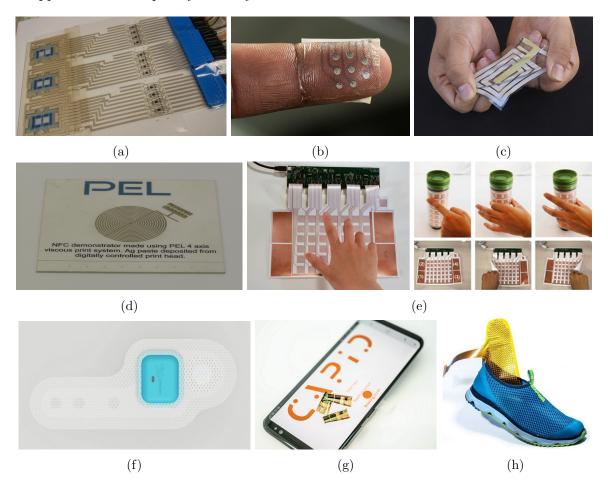

Printed Electronics (PE) is a complementary technology of conventional silicon-based electronics, targeting several emerging applications. The market for PE has increased from US\$ 6B in 2010 to US\$ 41B in 2019, and is projected to grow US\$ 153B in 2027 [1, 2], as shown in Figure 1.1. PE employs additive printing techniques, broadly known for conventional printing, in the manufacturing of electronics. The combination of additive manufacturing and electronic functionality allows the usage of various functional materials in fabricating electronic components on a broad range of substrates such as glass, flexible foil, textiles, and paper. This provides advantages or new functionalities such as low-cost, on-demand, customizable fabrication, and mechanical flexibility that are unachievable by other manufacturing processes. PE applications can be flexible, stretchable, lightweight, transparent, large-area, bio-compatible, and/or implantable and manufactured in point-of-use, cost-effective, and environmentally friendly processes. Therefore, the realization of several envisioned applications such as smart packaging [23], e-skin [22], health monitoring patches [24], smart cards [25], smart labels [26] and IoDT [21] can benefit from the promising features of PE [27]. Figure 1.2 presents some examples of

#### 1 Introduction

#### PE applications developed by industry and research institutions.

Figure 1.2: Examples of Printed Electronics applications. (a) Printed electrochromic display on flexible substrate [3]. (b) Tacttoo: thin and feel-through tattoo for on-skin tactile output [4]. (c) BodyNet sticker: wireless sensors that stick to skin to track health indicators [5]. (d) Printed energy harvesting circuit [3]. (e) PrintSense: on-surface sensing technique for planar, curved and flexible surfaces [6]. (f) Comfortable, disposable health patch with long battery life to measure vital signs [7]. (g) Flexible tags that communicate with standard touch screens [8, 9]. (h) Intelligent shoe sole that measures distribution of pressure of foot [10].

PE components are manufactured using several printing processes instead of complex photolithography based subtractive process which are expensive as well as environmentally hazardous. Some prominent examples of additive printing processes are screen printing, flexography printing, offset printing, gravure printing, and inkjet printing [27]. Depending on the application, one or multiple printing methods can be used in the manufacturing process. Due to their maskless fabrication process, some of these processes such as inkjet printing enable a highly demanding feature that is customizable/personalized fabrication at the point-of-use [27, 28]. Personalized fabrication allows users to select their material and substrate according to their application, and fabricate fully custom designs without profound expertise, sophisticated and extremely expensive manufacturing tools.

Various printed transistors such as p-type organic-based thin-film transistors (OTFTs) [29], organic field-effect transistors (OFETs) [30], and n-type organic transistors [31, 32] are demonstrated to construct functional PE circuits. However, these transistors mostly suffer from the

high supply voltage and low mobility making them unsuitable for low-power applications. On the other hand, inorganic semiconductor-based transistors combined with an electrolyte gate, called electrolyte-gated transistors (EGTs), provide high mobility and require low supply voltage ( $\leq 1 \text{ V}$ ), paving the way for low-power PE applications [12]. Due to their promising electrical characteristics, the fabrication of proposed circuits in this thesis are performed using EGTs.