# Simon Thomas Reder

Compileroptimierung und parallele Code-Generierung für zeitkritische eingebettete Multiprozessorsysteme

# Compileroptimierung und parallele Code-Generierung für zeitkritische eingebettete Multiprozessorsysteme

Zur Erlangung des akademischen Grades eines

#### **DOKTOR-INGENIEURS**

von der KIT-Fakultät für Elektrotechnik und Informationstechnik des Karlsruher Instituts für Technologie (KIT) genehmigte

#### DISSERTATION

von

M. Sc. Simon Thomas Reder

geb. in Konstanz

Tag der mündlichen Prüfung: 27. August 2020

Hauptreferent: Prof. Dr.-Ing. Dr. h. c. Jürgen Becker Korreferent: Prof. Dr. Theo Ungerer

# Zusammenfassung

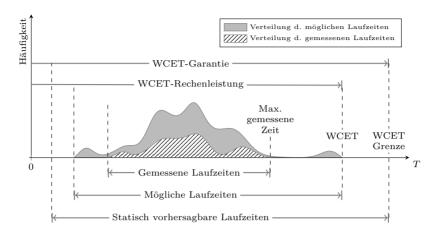

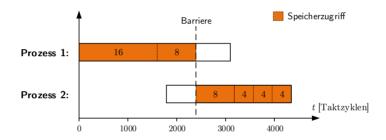

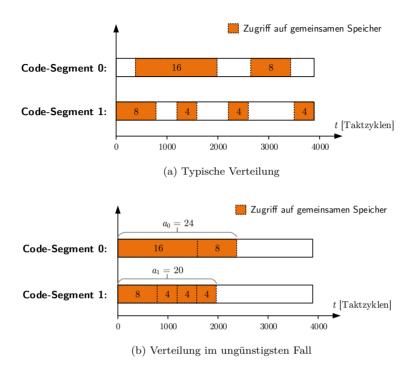

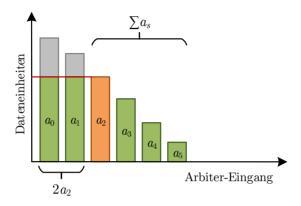

Durch den voranschreitenden Trend der Digitalisierung gewinnen intelligente digitale Systeme in vielen Bereichen des täglichen Lebens zunehmend an Bedeutung. Dies betrifft insbesondere auch den Bereich sicherheitskritischer Echtzeitsysteme, für deren sicheren Betrieb die Echtzeitfähigkeit nachgewiesen werden muss. Im Gegensatz zu Anwendungsfeldern ohne diese Anforderung sind effiziente Mehrkernprozessoren in Echtzeitsystemen derzeit noch kaum verbreitet. Der Hauptgrund für die bisherige Dominanz der Einzelkernprozessoren sind fehlende Methoden und Werkzeuge, um parallele Echtzeit-Software für Mehrkernprozessoren zu entwickeln und selbst im ungünstigsten Fall noch eine maximale Ausführungszeit (englisch Worst Case Execution Time, kurz WCET) garantieren zu können. In diesem Kontext besteht eines der wesentlichen Probleme darin, dass sich parallel ablaufende Software-Routinen im Hinblick auf ihre Laufzeit gegenseitig beeinflussen können. In Mehrkernprozessoren geschieht dies vor allem bei gleichzeitigen Zugriffen mehrerer Kerne auf eine gemeinsam genutzte Hardware-Ressource. Geeignete Methoden, um den Einfluss dieser als Interferenz bezeichneten Effekte bei der Software-Entwicklung präzise vorherzusagen und sichere Garantien für die Ausführungszeit abzuleiten, sind Gegenstand aktueller Forschung. Gleiches gilt für Software-Werkzeuge zur automatischen Parallelisierung, die auf harte Echtzeitanwendungen spezialisiert sind.

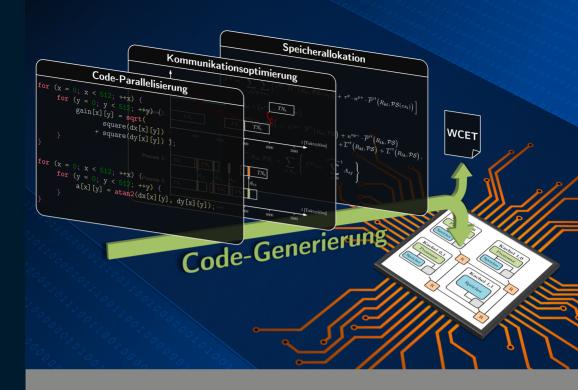

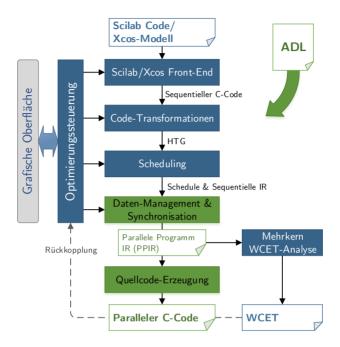

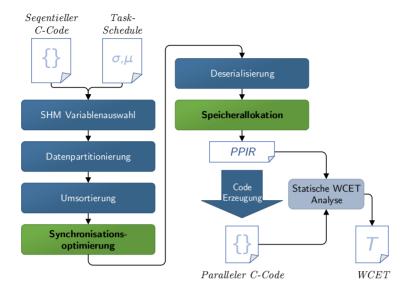

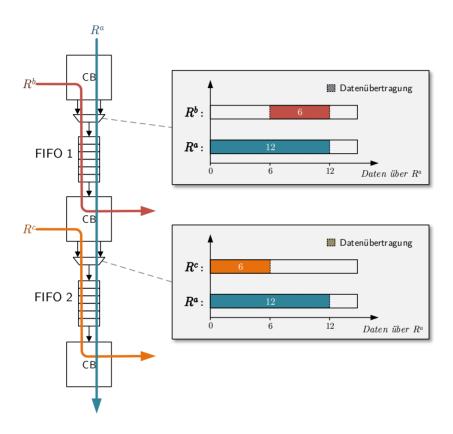

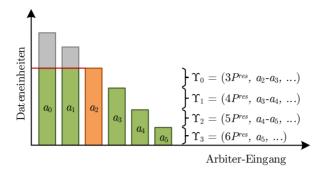

Diese Arbeit zielt darauf ab, die Anwendbarkeit von Mehrkernprozessoren in Echtzeitsystemen durch Beiträge in den Bereichen der automatischen Software-Parallelisierung, Code-Optimierung und Hardware-Modellierung signifikant zu verbessern. Als Bestandteil einer Werkzeugkette zur automatischen Parallelisierung von sequentieller Echtzeit-Software wird in dieser Arbeit ein Compiler-Werkzeug zur WCET-optimierten parallelen Code-Generierung und ein zugehöriges paralleles Programmiermodell vorgestellt. Hierdurch können – weitgehend ohne Zutun eines Endanwenders – gut vorhersagbare parallele Programme erzeugt werden. Durch das Programmiermodell wird dabei sichergestellt, dass die Ausführungszeit, einschließlich der Interferenzeffekte, mit Hilfe einer statischen WCET-Analyse sicher nach oben abgeschätzt werden kann. Als Teil der Code-Generierung stellt die vorliegende Arbeit zwei Optimierungsmethoden vor, die zum einen den Kommunikations- und Synchronisationsaufwand zwischen den Prozessorkernen reduzieren und zum anderen die optimierte Allokation verteilter Speicher in heterogenen Speicherhierarchien ermöglichen. Erstere ist auf des

parallele Programmiermodell abgestimmt und erlaubt die optimierte Platzierung von Kommunikations- und Synchronisationsoperationen sowie das Entfernen redundanter Synchronisation auf einer feingranularen Ebene. Die Optimierung der Speicherallokation ergänzt den Ansatz um ein formales Optimierungsmodell zur Zuweisung der Datenfelder eines generierten Programms zu den Speicherbereichen der Zielplattform. Das Modell bezieht dabei sowohl die Kosten für Interferenzeffekte als auch die Speicherhierarchie von Zielplattformen mit verteilten und heterogenen Speichern mit ein. Um die Schritte zur Generierung, Optimierung und Analyse von paralleler Echtzeit-Software weitgehend plattformunabhängig aufbauen zu können, beinhaltet die vorliegende Arbeit außerdem einen Ansatz zur generischen Modellierung von Mehrkernprozessorarchitekturen. Dieser erlaubt es, die Zielplattform mit Hilfe einer entsprechend erweiterten Architekturbeschreibungssprache (ADL) zu beschreiben, wodurch sich die darauf aufbauenden Entwicklungswerkzeuge mit überschaubarem Aufwand auf ein breites Spektrum von Hardware-Plattformen anwenden lassen.

Mit dieser neuartigen Kombination erweitert die vorliegende Arbeit den Stand der Technik um einige wesentliche Bausteine, die die weitgehend automatisierte Parallelisierung von Echtzeit-Software ohne stark einschränkende Annahmen bezüglich der Struktur des Eingabeprogramms ermöglichen. Zu den weiteren Neuerungen dieser Arbeit zählen die Plattformunabhängigkeit bei der WCET-optimierten Software-Parallelisierung und die Berücksichtigung von Interferenzeffekten bei der Speicherallokation in Echtzeitsystemen.

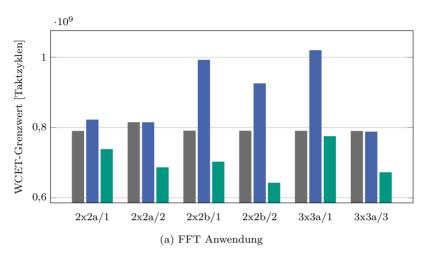

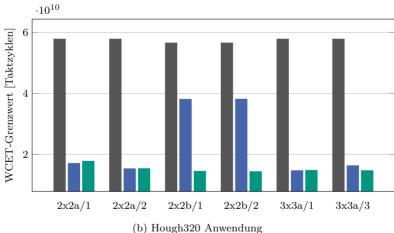

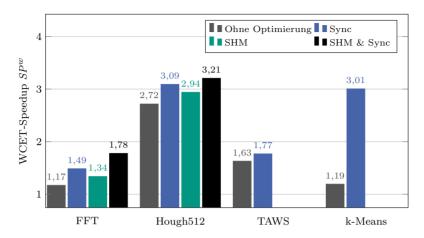

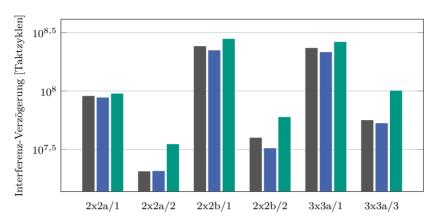

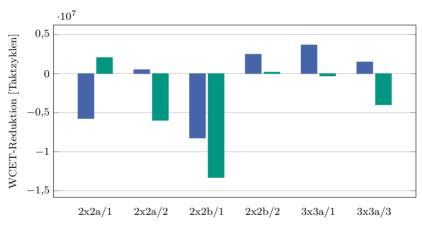

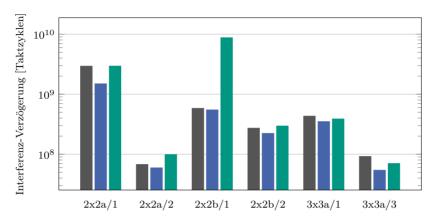

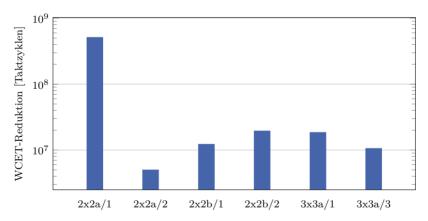

Die experimentelle Evaluation der vorgestellten Methoden und deren prototypischer Umsetzung zeigt, dass die WCET aller betrachteten Testanwendungen von der Parallelisierung profitieren kann. Auf einer Plattform mit vier Prozessorkernen konnte z. B. die WCET einer Anwendung aus dem Bereich der Bildverarbeitung (konkret eine Implementierung der Hough-Transformation) durch die Parallelisierung im Vergleich zum sequentiellen Eingabeprogramm um Faktor 3,21 verbessert werden. Auch die Optimierungsansätze für Kommunikation und Speicherallokation führen größtenteils zu einer deutlichen Verbesserung der WCET. So konnten die durch Interferenzen verursachten Kosten im Zuge der Speicherallokation z. B. um bis zu 49 % reduziert werden.

Insgesamt haben die Ergebnisse dieser Arbeit damit das Potential, die effiziente und kostengünstige Nutzung von Mehrkernprozessoren im Bereich harter Echtzeitsysteme wesentlich voranzutreiben.

## **Abstract**

Driven by the ongoing trend of digitalization, intelligent digital systems become increasingly important in various areas of daily life. That includes the field of safety-critical real-time systems, which must satisfy real-time constraints to ensure their safe operation. In contrast to application domains without these requirements, efficient multi-core processors are still uncommon in stateof-the-art real-time systems. The main reasons for the dominance of singlecore processors are missing methods and tools to develop and analyze parallel real-time software for multi-core processors. In particular, specialized analysis tools are needed to provide guarantees for the Worst-Case Execution Time (WCET) of parallel software. The major problem in that context is that parallelly executed software routines may affect each other's execution times. In multicore processors, this happens, e.g., when multiple processor cores concurrently access the same shared hardware resource. Suitable methods to precisely predict the impact of these so-called *interference effects* during design time and derive guarantees for the execution time are subject to ongoing research. That is equally true for software-tools to automatically parallelize programs, which are subject to hard real-time constraints.

The goal of this work is to significantly improve the applicability of multicore processors in real-time systems by contributing to the state-of-the-art in automated software parallelization, code optimization, and hardware modeling. As part of a tool-chain to automatically parallelize sequential real-time software, this work introduces a compiler tool for WCET-aware parallel code generation and a corresponding parallel programming model. Based on this combination, well-predictable parallel programs can be generated, mostly without requiring end-user interventions. In the process, the programming model ensures that software execution times, including interference effects, can be tightly bounded using a static WCET analysis. As part of the code generation, this work presents two optimization methods that, on the one hand, reduce communication and synchronization overhead and, on the other hand, optimize the allocation of memories within heterogeneous memory hierarchies. The former is adjusted to the programming model and allows for the optimized placement of communication and synchronization operations with a fine granularity. Moreover, redundant synchronization can be detected and removed in the process. The memory allocation scheme supplements the approach with a formal optimization model

for mapping the data fields of the application onto the memory segments of the target platform. This model explicitly accounts for the costs of interference effects as well as the memory hierarchy of multi-core processors with distributed and heterogeneous memories. To keep the steps of generating, optimizing, and analyzing the code independent of the target platform, this work includes a generic model for multi-core processor architectures. The latter describes the target platform with an architecture description language (ADL) and allows the corresponding development tools to be applied to a wide range of target platforms without much effort.

With this novel combination, the present work extends the state-of-the-art by several essential building blocks that enable a mostly automated parallelization of real-time software without strong assumptions regarding the structure of the input program. Further novelties of this work are the platform-independence in WCET-aware code parallelization and the inclusion of interference while allocating memories for real-time systems.

The experimental evaluation of the presented methods and their implementation shows that the WCET of all considered test applications can benefit from parallelization. For a platform with four cores, the parallelization method, e.g., improved the WCET of an application from the image-processing domain (more precisely an implementation of the Hough Transformation) by factor 3.21 compared to the sequential input program. The two optimization methods for communication and memory allocation result in significant improvements of the WCET in the vast majority of cases as well. The memory allocation, for instance, reduced the costs caused by interference by up to 49 %.

Overall, the results of this work have the potential to significantly facilitate the efficient and cost-effective use of multi-core processors in the domain of hard real-time systems.

## Vorwort

Die vorliegende Arbeit entstand während meiner Zeit am Institut für Technik der Informationsverarbeitung (ITIV) des Karlsruher Instituts für Technologie (KIT). In einigen spannenden Jahren als wissenschaftlicher Mitarbeiter hatte ich die Gelegenheit, Einblicke in interessante Forschungsthemen und die Hochschullehre zu erhalten. Während der Arbeit am ITIV und der Mitwirkung an Forschungsprojekten durfte ich zahlreiche Kollegen und Projektpartner kennenlernen, bei denen ich mich an dieser Stelle für den stets konstruktiven Austausch und die kollegiale Zusammenarbeit bedanken möchte.

Besonderen Dank möchte ich Prof. Jürgen Becker für die Möglichkeit zur Forschung an dem hier präsentierten Promotionsthema, die hervorragende Betreuung und die Übernahme des Hauptreferats bei dieser Dissertation aussprechen. Bedanken möchte ich mich auch für das entgegengebrachte Vertrauen, das mir ermöglicht hat, Verantwortung in Forschungsprojekten, Projektanträgen und verschiedenen anderen Bereichen des Instituts zu übernehmen.

Weiterhin möchte ich mich bei Prof. Theo Ungerer für die Übernahme des Korreferats und die Begutachtung der Arbeit bedanken. Auch den Professoren Trommer, Ulusoy und Perić danke ich für ihre Mitwirkung am Prüfungsausschuss.

Diese Arbeit wäre nicht möglich gewesen ohne das motivierende, kreative und humorvolle Arbeitsumfeld am ITIV. Dafür möchte ich all den einzigartigen Freunden und Kollegen danken, die mich in den vergangenen Jahren am ITIV begleitet haben. Sie sorgten stets für einen abwechslungsreichen Arbeitsalltag und hatten ein offenes Ohr für Diskussionen und neue Ideen. Ich möchte mich besonders bei meinen langjährigen Wegbegleitern & Bürokollegen Christoph Roth und Harald Bucher, aber auch bei den vielen anderen Kollegen (Steffen, Timo, Hannes, Lidia, Fabian, Florian, Augusto, ...), einschließlich derer, die das ITIV vor mir verlassen haben (Oliver, Michael, Falco, Lukas, Timo, ...), für die gemeinsame Zeit bedanken. Auch abseits der Arbeit – sei es bei den obligatorischen Kaffee- und Mittagspausen, dem Bau von Doktorhüten oder den vielfältigen Freizeitaktivitäten – wurde es mit den Kollegen niemals langweilig. Dafür danke ich besonders den Organisatoren (Steffen, Lidia, Fabian, ...) der zahlreichen Kino- & Restaurantbesuche, Grillabende und anderer Aktivitäten.

Weiterhin möchte ich allen danken, die durch Korrekturen, Anregungen, konstruktive Kritik oder in anderer Weise zum Gelingen dieser Arbeit beigetragen haben. Nicht unerwähnt bleiben sollen dabei auch alle Studenten, die als HiWis, Bacheloranden oder Masteranden am ITIV wichtige Vorarbeiten geleistet haben.

Nicht zuletzt möchte ich auch meiner Familie für ihre kontinuierliche Unterstützung einen ganz besonderen Dank aussprechen. Vor allem meinen Eltern Edith und Wolfgang danke ich dafür, dass sie mich in Ausbildung und Studium unterstützt und mir dadurch auch den Weg zur Promotion geebnet haben.

Karlsruhe, im September 2020 Simon Reder

# Inhaltsverzeichnis

| 1.                                                | Einle | Einleitung 1                              |                                                     |    |  |  |

|---------------------------------------------------|-------|-------------------------------------------|-----------------------------------------------------|----|--|--|

|                                                   | 1.1.  | Motiva                                    | ation                                               | 1  |  |  |

|                                                   |       | 1.1.1.                                    | Cyber-Physikalische Systeme                         | 2  |  |  |

|                                                   |       | 1.1.2.                                    | Echtzeitanforderungen                               | 3  |  |  |

|                                                   |       | 1.1.3.                                    | Mehrkernprozessoren                                 | 5  |  |  |

|                                                   | 1.2.  | Zielset                                   | zung und Beiträge dieser Arbeit                     | 7  |  |  |

|                                                   | 1.3.  | Aufba                                     | u der Arbeit                                        | 10 |  |  |

| 2.                                                | Grui  | ndlagen                                   | 1                                                   | 13 |  |  |

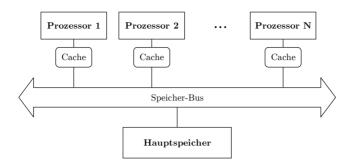

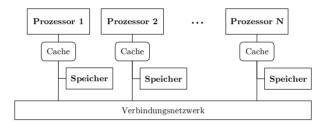

|                                                   | 2.1.  | erarchitekturen für Mehrkernprozessoren 1 | 13                                                  |    |  |  |

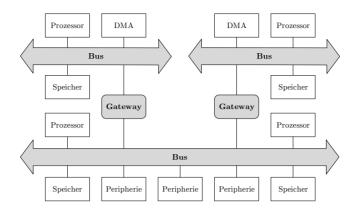

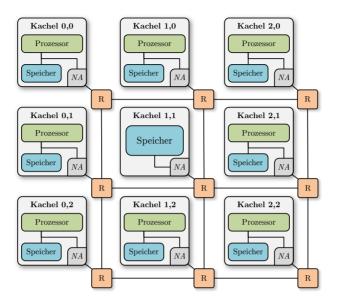

|                                                   |       | 2.1.1.                                    | Architekturen mit gemeinsam genutzten Speichern 1   | 15 |  |  |

|                                                   |       | 2.1.2.                                    | Architekturen mit verteilten Speichern              | 16 |  |  |

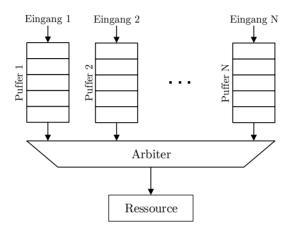

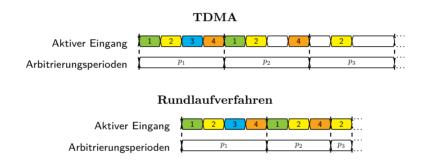

|                                                   |       | 2.1.3.                                    | Chip-interne Kommunikation in Mehrkernprozessoren 1 | 17 |  |  |

|                                                   | 2.2.  | 2.2. Parallele Programmierung             |                                                     |    |  |  |

|                                                   |       | 2.2.1.                                    | Tasks, Prozesse und Schedules                       | 25 |  |  |

|                                                   |       | 2.2.2.                                    | Klassifizierung von Abhängigkeiten                  | 27 |  |  |

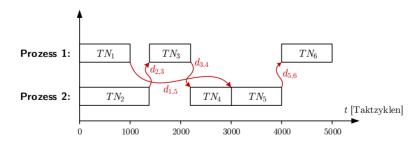

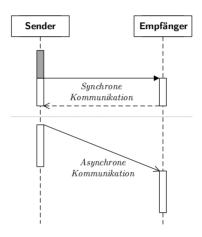

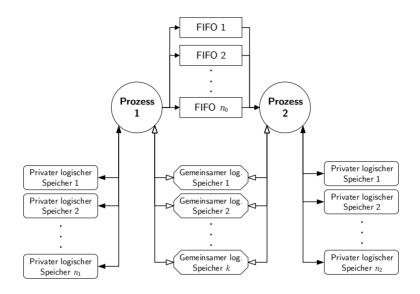

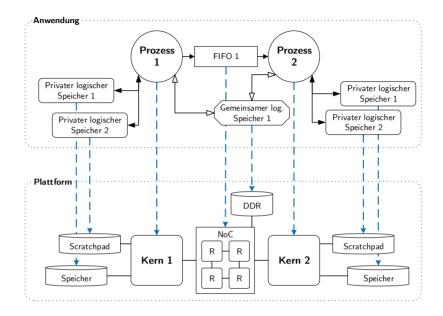

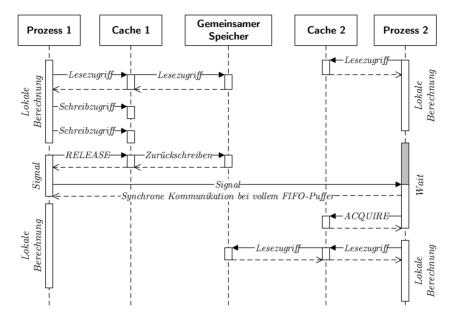

|                                                   |       | 2.2.3.                                    | Kommunikation und Synchronisation                   | 28 |  |  |

|                                                   |       | 2.2.4.                                    | Deadlocks                                           | 31 |  |  |

|                                                   |       | 2.2.5.                                    | Parallele Berechnungsmodelle                        | 32 |  |  |

| 2.3. Compiler-Werkzeuge und Zwischendarstellungen |       |                                           |                                                     |    |  |  |

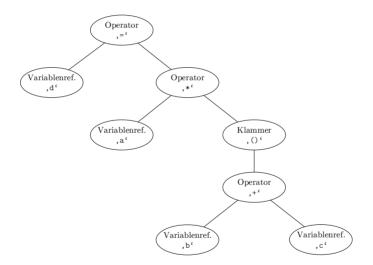

|                                                   |       | 2.3.1.                                    | Abstrakter Syntaxbaum                               | 33 |  |  |

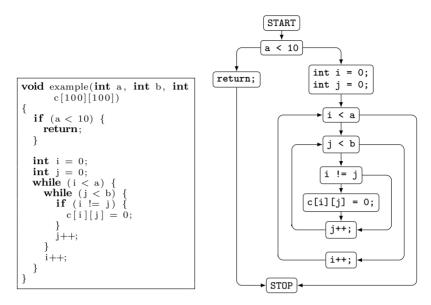

|                                                   |       | 2.3.2.                                    | Kontrollflussgraph                                  | 35 |  |  |

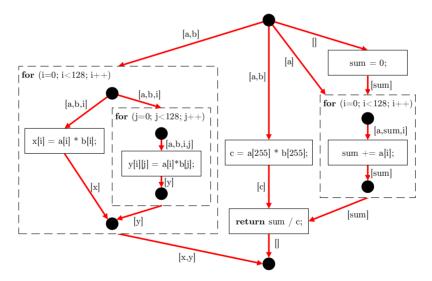

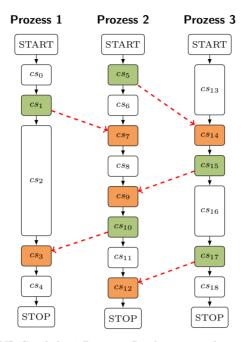

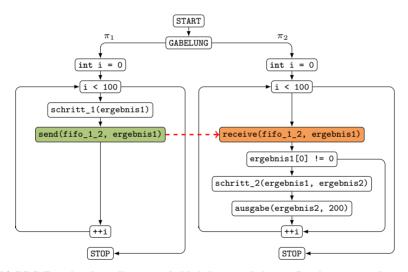

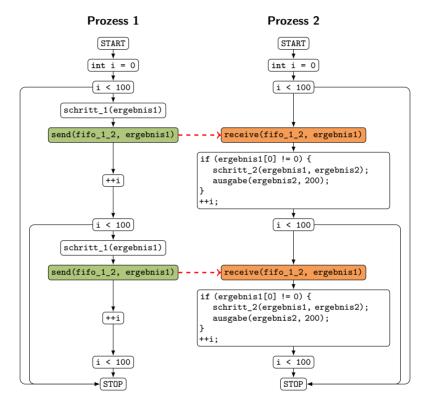

|                                                   |       | 2.3.3.                                    | Parallele Programmgraphen                           | 37 |  |  |

|                                                   |       | 2.3.4.                                    | Static Single Assignment Form                       | 37 |  |  |

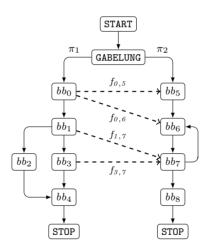

|                                                   |       | 2.3.5.                                    | Hierarchische Task-Graphen                          | 39 |  |  |

|                                                   |       | 2.3.6.                                    | Compiler-Optimierung                                | 10 |  |  |

|                                                   | 2.4.  | Echtze                                    | eit-Software                                        | 13 |  |  |

|                                                   |       | 2.4.1.                                    | Statische WCET-Analyse                              | 13 |  |  |

|    |          | 2.4.2.                          | Echtzeitbetriebssysteme                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 44  |  |

|----|----------|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|

| 3. | Stan     | ıd der <sup>-</sup>             | Technik                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 47  |  |

|    | 3.1.     | Mehrk                           | sernprozessoren in Echtzeitsystemen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 47  |  |

|    |          |                                 | Ansätze zur Interferenz-Analyse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 51  |  |

|    |          |                                 | Modellierung von Mehrkernprozessoren                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 52  |  |

|    | 3.2.     |                                 | Γ-optimierte Compiler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 56  |  |

|    |          | 3.2.1.                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 57  |  |

|    | 3.3.     | Auton                           | natische Software-Parallelisierung                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 61  |  |

|    |          |                                 | Parallelisierung für eingebettete Systeme ohne Echtzeitan-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |  |

|    |          |                                 | forderungen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 62  |  |

|    |          | 3.3.2.                          | Automatische Parallelisierung für Echtzeitsysteme                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 65  |  |

|    |          | 3.3.3.                          | Die ARGO-Werkzeugkette                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 69  |  |

|    | 3.4.     | Zusam                           | nmenfassung und Abgrenzung                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 78  |  |

| 4  | <b>-</b> | . C-                            | Constitution of Constitution o | 83  |  |

| 4. |          |                                 | tomatisierung für parallele Echtzeitprogramme                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |  |

|    | 4.1.     | _                               | aralleles Programmiermodell für harte Echtzeitanwendungen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |  |

|    |          |                                 | Zielsetzung und Anforderungen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |  |

|    |          | 4.1.2.                          | Spezifikation des Programmiermodells                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |  |

|    | 4.0      |                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |  |

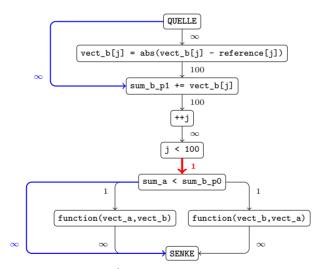

|    | 4.2.     |                                 | gung parallelisierter Programme                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |  |

|    |          | 4.2.1.                          | Aufbau des Transformations-Werkzeugs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |  |

|    | 4.9      |                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |  |

|    | 4.3.     | гахи                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 110 |  |

| 5. | Mod      | lellierui                       | ng zeitkritischer Hardware-/Software-Systeme                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 113 |  |

|    | 5.1.     | . Zielsetzung und Anforderungen |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |  |

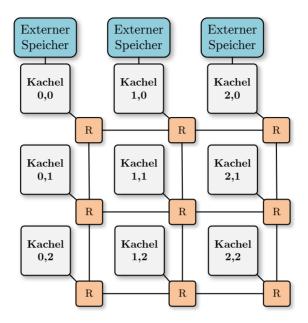

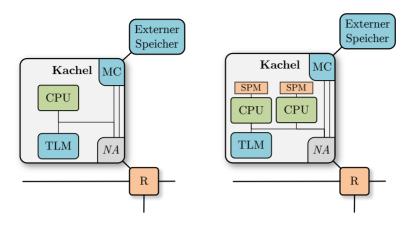

|    | 5.2.     | 2. Aufbau des Plattformmodells  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |  |

|    |          | 5.2.1.                          | Annahmen & Einschränkungen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 115 |  |

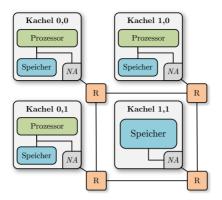

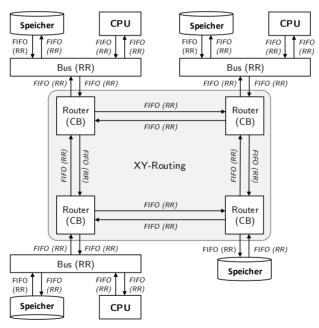

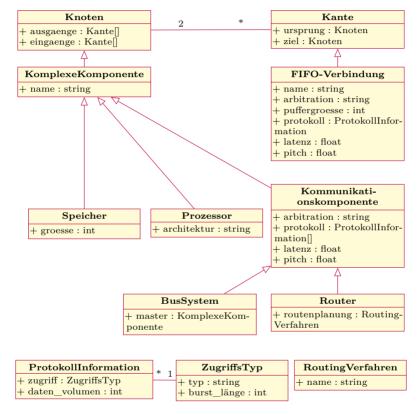

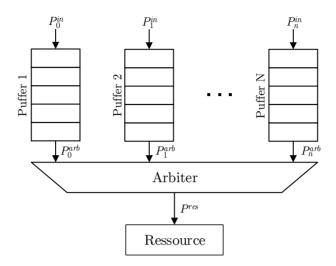

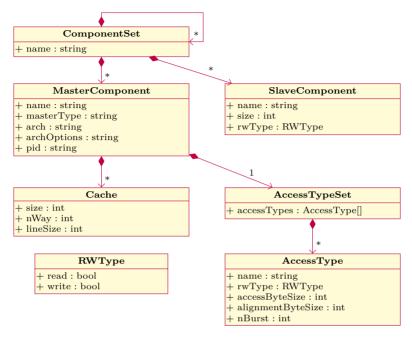

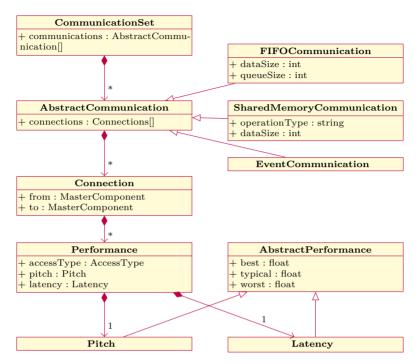

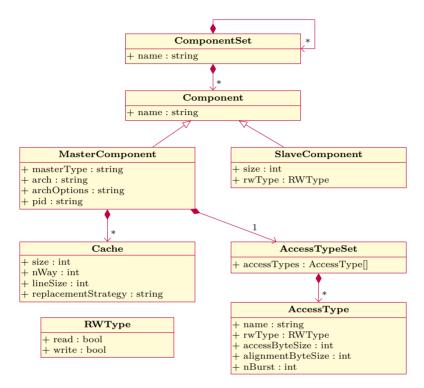

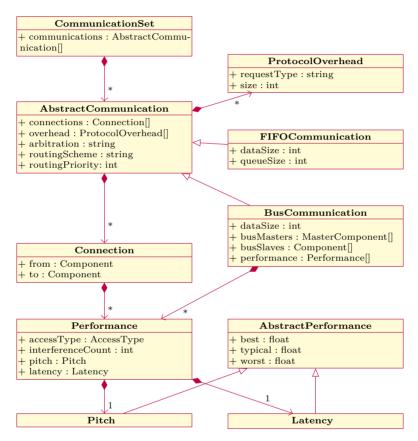

|    |          | 5.2.2.                          | Plattform-Komponenten-Graph                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 117 |  |

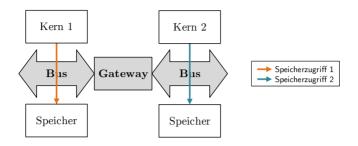

|    |          | 5.2.3.                          | Speicherzugriffe und Routenplanung                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 124 |  |