#### RESEARCH ARTICLE

WILEY

# Engineering faster sorters for small sets of items

# Timo Bingmann | Jasper Marianczuk | Peter Sanders

Institute of Theoretical Informatics, Karlsruhe Institute of Technology, Karlsruhe, Germany

#### Correspondence

Timo Bingmann, Institute of Theoretical Informatics, Karlsruhe Institute of Technology, Am Fasanengarten 5, 76131 Karlsruhe, Germany. Email: bingmann@kit.edu

#### **Funding information**

Open access funding enabled and organized by Projekt DEAL

#### **Abstract**

Sorting a set of items is a task that can be useful by itself or as a building block for more complex operations. That is why a lot of effort has been put into finding sorting algorithms that sort large sets as efficiently as possible. But the more sophisticated and complex the algorithms become, the less efficient they are for small sets of items due to large constant factors. A relatively simple sorting algorithm that is often used as a base case sorter is insertion sort, because it has small code size and small constant factors influencing its execution time. We aim to determine if there is a faster way to sort small sets of items to provide an efficient base case sorter. We looked at sorting networks, at how they can improve the speed of sorting few elements, and how to implement them in an efficient manner using conditional moves. Since sorting networks need to be implemented explicitly for each set size, providing networks for larger sizes becomes less efficient due to increased code sizes. To also enable the sorting of slightly larger base cases, we adapted sample sort to Register Sample Sort, to break down those larger sets into sizes that can in turn be sorted by sorting networks. From our experiments we found that when sorting only small sets of integers, the sorting networks outperform insertion sort by a factor of at least 1.76 for any array size between six and 16, and by a factor of 2.72 on average across all machines and array sizes. When integrating sorting networks as a base case sorter into Quicksort, we achieved far less performance improvements over using insertion sort, which is probably due to the networks having a larger code size and cluttering the L1 instruction cache. The same effect occurs when including Register Sample Sort as a base case sorter for IPS<sup>4</sup>o. But for x86 machines that have a larger L1 instruction cache of 64 KiB or more, we obtained speedups of 12.7% when using sorting networks as a base case sorter in std::sort, and of 5%-6% when integrating Register Sample Sort as a base case sorter into IPS<sup>4</sup>o, each in comparison to using insertion sort as the base case sorter. In conclusion, the desired improvement in speed could only be achieved under special circumstances, but the results clearly show the potential of using conditional moves in the field of sorting algorithms.

#### KEYWORDS

base case sorting, sample sort, sorter, sorting, sorting algorithm, sorting networks

This is an open access article under the terms of the Creative Commons Attribution License, which permits use, distribution and reproduction in any medium, provided the original work is properly cited.

© 2020 The Authors. Software: Practice and Experience published by John Wiley & Sons Ltd.

Softw: Pract Exper. 2020;1–40. wileyonlinelibrary.com/journal/spe

#### 1 | INTRODUCTION

### 1.1 | Motivation

Sorting, that is rearranging elements of an input set into a specific order, is a fundamental algorithmic challenge. At universities around the globe, basic sorting algorithms are taught in introductory computer science courses as examples for theoretical analysis of algorithms. We learn that bubble sort and insertion sort have quadratic asymptotic running time, Quicksort expected  $\mathcal{O}(n \log n)$  but worst-case quadratic time, and merge sort always runs in  $\mathcal{O}(n \log n)$  time. These algorithms are analyzed by the number of comparisons they require, both asymptotically, up to constant factors, and sometimes also exactly for small input sizes n. But later, practical experience shows that pure theoretical analysis cannot tell the whole story. In real applications and on real hardware factors such as average cases, cache effects, modern CPU features like speculative execution, and of course constant factors actually matter, a lot. Any well-founded choice on which sorting algorithm to use (for a particular use case) should be influenced by all factors.

The usual playing field for developing new sorting algorithms is to sort a *large number* of items as quickly as possible. We will call these *complex* sorting algorithms and many follow the divide-and-conquer paradigm. However, the algorithmic steps for large sets in these complex sorters do not perform well when sorting small sets of items, because they have good asymptotic properties but larger constant factors that become more important for the small sizes. However also sorting small inputs can be relevant for performance. This happens for the *base case* of complex sorting algorithms or when many sorting problems have to be solved. The latter case for example occurs when the adjacency lists of a graph should be sorted by some criterion in order to support some greedy heuristics. For example, the *heavy edge matching* heuristics<sup>1</sup> repeatedly looks for the heaviest unmatched edge of a vertex.

The most common choice for sorting small inputs is insertion sort, which has a worst-case running time of  $\mathcal{O}(n^2)$ , but small constant factors that make it suitable to use for small n. When the sorter is executed many times, the total running time does add up to a substantial part of the computing time of an application. In this article we therefore attempt to optimize or replace this quadratic sorting algorithm at the heart of most complex sorters and other applications.

Put plainly: what is the fastest method to sort up to 16 elements on actual modern hardware?

We investigate two approaches: first to optimize sorting networks and the second to adapt sample sort to small numbers of items. When optimizing sorting networks, the most important aspects are how to execute the conditional swap operations on modern CPUs and which sorting network instances to use: the best/shortest known ones, or recursive locality-aware constructions such as Bose–Nelson's.<sup>2</sup> Optimizing sorting networks has previously been addressed by Codish, Cruz–Filipe, Nebel, and Schneider–Kamp³ in 2017, but we go much further into the hardware details of the conditional swap operations and use hand-coded assembly employing conditional move instructions. We focused on using "simple" nonvectorized instructions, because they are available on a wider range of architectures. For slightly larger sets of items (e.g., up to 256), we present Register Sample Sort (RSS), which is an adaptation of Super Scalar Sample Sort⁴ to use the registers in the CPU for splitters. As items we focus on sorting pairs of an integer as key and an associated reference pointer or value. This enables the sorting of items with complex payload values. Integers keys fit into a register and can easily be compared using a simple instruction. Our results can be applied directly to other keys like float and doubles, but not necessarily to larger objects. However, some of our sorting network implementations are fully generic and can be translated to any data type.

For our experimental evaluation we used four machines: two with Intel CPUs, one with an AMD Ryzen, and a Rockchip RK3399 ARM system on a chip. It turns out that sorting networks with hand-coded conditional move assembly instructions perform much better (a factor 2.4–5.3 faster) and have a much smaller variance in running time than insertion sort. However, when integrating sorting networks into Quicksort we unexpectedly saw only a speedup of 7%–13% depending on the machine and base algorithm. We attribute this to the larger code size of sorting networks and thus L1 instruction cache misses. Register Sample Sort is also faster than insertion sort for 256 items: up to a factor 1.4 over std::sort. We then integrated both sorting networks and Register Sample Sort into IPS<sup>4</sup>o, a fast complex comparison-based sorter by Axtmann et al..<sup>5</sup> Our experiments validate the authors measurements that IPS<sup>4</sup>o is some 40%–60% faster than std::sort, and were able to show that our better base case sorters improve this by another 1.3% on Intel CPUs, 5% on AMD CPUs, and 7% on the ARM machine. The ARM machine has higher variance in running time but less outliers than the Intel and AMD ones. We conclude that the larger code size of sorting networks is a disadvantage, and that Intel and AMD's instruction scheduling and pipelining units are good at accelerating insertion sort. For ARM machines, better algorithms however make a difference because the CPUs are simpler.

This article is based on the bachelor's thesis of Jasper Marianczuk.<sup>6</sup>

#### 1.2 | Overview of the article

Section 2 is dedicated to sorting networks: Section 2.1 starts with the general basics of sorting networks and inline assembly code. After that, we look at different ways of implementing sorting networks efficiently in C++ in Section 2.2.

In Section 3 we regard Super Scalar Sample Sort and develop an efficient modified version for sets with 256 elements or less by holding the splitters in general purpose registers instead of an array. The resulting algorithm is called Register Sample Sort.

Section 4 discusses the results and improvements of using sorting networks we achieved in our experiments, measuring the performance of the sorting networks and Register Sample Sort individually, and also including them as base cases into Quicksort and IPS<sup>4</sup>o. After that we conclude the results of this article in Section 5.

#### 1.3 | Related work

Sorting is a large and well-studied topic in computer science and the many results fill entire volumes<sup>7,8</sup> of related work. We can focus only on the most relevant here.

Sorting networks are considered in more detail in the following section. The most well-known sorting networks are Bose–Nelson's recursive construction,<sup>2</sup> Batcher's bitonic and odd-even merge sorts,<sup>9</sup> and the AKS (Ajtai, Komlós, and Szemerédi's) sorting network.<sup>10</sup> The publication closest to our work is the paper by Codish et al.,<sup>3</sup> who optimized sorting networks for locality and instruction-level parallelism.

Sorting networks were used by many authors to vectorize base-case sorting using single-instruction multiple-data (SIMD) instructions in wide registers, as part of larger vectorized sorters. Inoue et al. proposed AA-sort<sup>11</sup> first in 2007, which is both multicore parallelized and SIMD vectorized but processes larger blocks of items which are then merged. Furtak, Amaral, and Niewiadomski used code generation and developed three SIMD implementations, <sup>12</sup> for x86-64's SSE2 and G5's AltiVec instruction sets. Xiaochen, Rocki, and Suda proposed two algorithms for AVX-512 SIMD, <sup>13</sup> one sorting 16 items in one register, and one sorting 31 items in two registers, both based on bitonic sorting networks. More recently, Bramas came up with an alternative way to used bitonic sorting networks to sort up to 16 elements with AVX-512 SIMD instructions. <sup>14</sup> Hou, Wang, and Feng developed an entire framework <sup>15</sup> which automatically translates abstract sorting networks into vectorized code for different instruction sets. For example, they support Bose–Nelson, Batcher's bitonic, and Hibbard <sup>16</sup> networks and can output AVX, AVX2, and IMCI code. In 2019, Yin et al. presented a both parallelized and vectorized sorting algorithm, <sup>17</sup> which contains a 16×16 SIMD sorting kernel based on bitonic sorting for blocks of 256 items. Beyond SIMD, sorting networks were also used in various FPGA hardware. <sup>18,19</sup>

Compared with previous work, we consider how to optimize sorting networks without special vectorized instructions or wide registers. We also consider the variance or standard deviation of running time of our implementations, which is interesting for more accurately predicting code execution time. None of the referenced papers consider this interesting aspect of sorting networks and branchless execution.

#### 2 | SORTING NETWORKS

### 2.1 | Introduction

Sorting algorithms can be classified into two groups: those of which the comparison behavior depends on the input and those of which the behavior is *not* influenced by the particular configuration of the input. Examples of the former are Quicksort, one merge sort, insertion sort, while the latter are called *data-oblivious*.

One example of data-oblivious sorting algorithms are *sorting networks*. A sorting network operates on a fixed number n of *channels* enumerated from 1 to n, each representing one input variable, and connections between the channels, called *comparators*. When two channels are connected by a comparator then the values are compared and conditionally swapped: if the channel with the lower number holds a value that is greater than the value of the channel with the higher number then the values in the variables are exchanged.

The comparators are given in a fixed order that determines the sequence of executing these *conditional swaps*, such that in the end the channels contain *a permutation* of the original input, and the values held by the channels are in

*nondecreasing order*. Sorting networks are data-oblivious because all comparisons are always performed in the same order, no matter which permutation of an input is given.

The two most important metrics to quantify sorting networks are their *size* and *depth*. A network's size refers to the *total number of comparators* it contains, and a network's depth describes the *minimal number of levels* a network can be divided into.

Each individual comparator is located on a singleton *level*. When two comparators do not share a channel and are consecutive, then they can be combined into a common *level*. Inductively, multiple consecutive comparators can be merged into a level, if their channels are not shared with any other comparator in the level. Most importantly for performance, since all the comparators in a level are independent from one another, they can be executed in parallel.

### 2.1.1 | Networks in practice

There are many methods to come up with sorting networks which correctly order any input.

- **Best known networks:** Sorting networks with proven *optimal sizes* and *optimal depths* are known only for small numbers of input channels. To date, the optimal depth is known only for n up to seventeen,  $^{7,22-25}$  while the optimal size only for n up to  $10.^{24}$  For example, a network for 10 elements with optimal size 29 has depth nine, and one with optimal depth seven has size  $31.^{7,24}$  For larger networks individual upper and lower bounds on size or depth are known. These optimal networks were initially optimized by hand and nowadays are searched for with the help of computers and evolutionary algorithms.  $^{26}$

- Recursively generated networks: Besides elaborate algorithms searching for optimal networks, there are also much simpler methods to generate correct (but nonoptimal) networks. The most commonly used paradigm is recursive divide-and-conquer: split the input into two parts, sort each part recursively, and merge the two parts together in the end. Representatives for this kind of approach are the constructions of Nelson and Bose<sup>2</sup> and the algorithms by Batcher.<sup>9</sup>

Bose and Nelson split the input sequence into first and second half, while Batcher partitions it into elements with an even index and elements with an odd index. The advantage of these recursive networks over the specially optimized ones is that they can easily be created even for large network sizes. While the generated networks may have more comparators than the best known networks, the number of comparators in a network acquired from either Bose–Nelson or Batcher of size n has an upper bound of  $\mathcal{O}(n (\log n)^2)$ . This was improved by Ajtai, Komlós, and Szemerédi<sup>10</sup> to optimal  $\mathcal{O}(\log n)$  depth with the much-cited AKS sorting network, which however have prohibitively high constants and are thus unusable for small n.

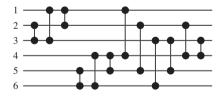

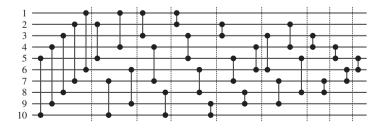

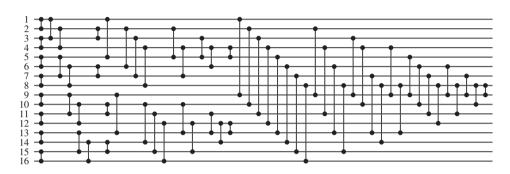

Sorting networks are customarily depicted by using horizontal lines for the channels, and undirected vertical connections between these lines for the comparators. A network by Bose and Nelson for six elements is illustrated in this manner in Figure 1, and Figure 2 shows a network with optimal size for 10 elements. The dotted vertical lines indicate the nine levels in the network.

FIGURE 1 Recursively generated sorting network by Bose and Nelson for six elements

**FIGURE 2** Sorting network with optimal size for 10 elements

### 2.1.2 | Improving the speed of sorting through sorting networks

The central question to our investigation in this section is how sorting networks can improve the sorting speed on a set of elements (on average), if they cannot take any shortcuts for "good" inputs, like an insertion sort that would leverage an already sorted input and do one comparison per element. The answer to this question is avoiding penalties introduced by *branching*. Because the compiler and CPU know in advance which comparisons are going to be executed in which order, the control flow does not contain conditional branches, which in particular gets rid of expensive branch mispredictions and allows instruction level (superscalar) parallelism. On uniformly distributed random inputs, the chances that any number is smaller than another is 50% on average, making branches unpredictable. In the case of insertion sort that means not knowing in advance with how many elements the next one has to be compared until it is inserted into the right place (on average it would be half of them).

Even though with sorting networks the compiler knows in advance when to execute which comparator, implementing the conditional-swap operation in a naive way (as seen in Section 2.1.3) the compiler might still generate branches. In that case, the sorting networks are no faster than insertion sort, or even slower. Hence, we investigated the use of assembly code in this article.

Another interesting use of sorting networks may be in the field of cryptography and security-focused applications. The time it takes to sort with non-data-oblivious algorithms (e.g., Quicksort) may introduce side channels allowing an attacker to infer the order of the input elements.

### 2.1.3 | Conditional swap

For sorting networks, the basic operation is to compare two values against each other and swap them if they are in the wrong order (the "smaller" element occurs after the "larger" one in the sequence). This *conditional-swap* operation can be implemented straight-forwardly in C++ with an if and a swap:

```

void ConditionalSwap(Type& left, Type& right) {

if (right < left) { std::swap(left, right); }

}</pre>

```

Here Type is a template and can be instantiated with any type that implements the < operator. As suggested by Codish et al.,<sup>3</sup> the same piece of code can be rewritten like this:

```

void ConditionalSwap2(Type& left, Type& right) {

Type temp = left;

if (right < temp) { left = right; }

if (right < temp) { right = temp; }

}</pre>

```

At first glance it appears as if there are now two conditional branches. But since the statement executed when the condition is true now only consists of a single assignment each, these can be expressed in x86-architecture with a *conditional move* instruction. In AT&T syntax (see Section 2.1.4), a conditional move (cmov a,b) will write the value of register a into register b, if a condition is met. If the condition is not met, no operation takes place (but still taking the same number of CPU cycles as the move operation would have). Since the address of the next instruction no longer depends on the previous condition, the control flow now does not contain branches. This avoids the large cost of *branch mispredictions* which require the execution pipeline of the CPU to be flushed and many speculative operations to be undone. The only downside of conditional moves is that they may take longer to evaluate than a normal move instruction on certain architectures, and can only be executed when the comparison has performed and its result is available. They can also only operate on register entries.

When the elements to be swapped are plain integers, some compilers do generate code with conditional moves for those operations while others default to jump branches. In the experiments in Section 4 we consider pairs of an unsigned 64-bit integer key and an unsigned 64-bit reference value, which could be a pointer to data or an address in an array. To force the usage of conditional moves, we investigated use of *inline assembly*,<sup>27</sup> a feature of gcc and other compilers that allows the programmer to specify small amounts of assembly code to be inserted into the generated machine code. This technique and the notation is further explained in the following Section 2.1.4.

### 2.1.4 | Inline assembly code

In this section we introduce the reader to a relatively obscure feature in modern C/C++ compilers: inline assembly code. We will use it in the next section to hard-code conditional swap operations and thus bypass the compiler's optimizations for these operations.

The machine instructions executed by the CPU are also called *assembly code*, which can be expressed as the actual op-codes or as human-readable text. There are two competing conventions for the textual representation: the Intel syntax or MASM syntax and the AT&T syntax.

The main differences are the parameter order and operand size. In Intel syntax the destination parameter is written first, then the source of the value: mov dest, src, while the size of the operands need not be specified. In AT&T syntax on the other hand, the source parameter is written first, followed by the destination: movq src, dest. The size of the operand must be appended to the instruction: "b" (byte = 8 bit), "1" (long = 32 bit), "q" (quad-word = 64 bit). In this article only the AT&T syntax will be used, because it is used internally by gcc.

The gcc and clang C++ compilers have a feature that allows the programmer to write assembly instructions in between regular C++ code, called "inline assembly" (asm).<sup>27</sup> This inline code consists of a continuous piece of assembly code, together with a specification of how it should interact with the surrounding C++ code. This specification communicates to the compiler what happens inside the asm block and consists of a definition for *input* and *output* variables and a list of *clobbered registers*. Gcc does not optimize the given assembly statements, they are added into the generated assembly code verbatim and translated to machine code by the GNU Assembler.

A variable listed as output means that the value will be modified, a clobbered register is one where gcc cannot assume that the value it held before the asm block will be the same as after the block. In this article, the clobbered registers will almost always be the conditional-codes registers ("cc"), which include the carry flag, zero flag, and the signed flag, which are modified during a compare-instruction. This way of specifying the input, output, and clobbered registers is also called *extended asm*.

Taking the code from Section 2.1.3, and assuming Type = uint64\_t, the statement

```

1 uint64_t temp = left;

2 if (right < temp) {

3  left = right;

4 }</pre>

```

can now be written with extended inline x86 assembly as

In extended asm, one can define C++ variables as input or output operands. For inputs the compiler will assign a register if it has the "r" modifier and load the value into it. For outputs, a register is allocated and the value is written back to the given variable after the asm block or used immediately in further steps. The names in square brackets are symbolic names only valid in the context of the assembly instructions and independent from the names in the C++ code before. The link between the C++ names and the symbolic names is defined in the input and output declarations, which may or may not be the same.

For conditional moves it is important to properly declare the input and output variables, because they perform a task that is a bit unusual: an output variable may or may not be overwritten. In the case of the output register for left used above, two things must apply: if the condition is false, it must hold the value of left, and if the condition is true, it must hold the value of right.

For optimizations purposes, the compiler might reduce the number of registers used by placing the output of one operation into a register that previously held the input for some other operation. To prevent this, the declaration for the output [left] "=&r" (left) has the "&" modifier added to it, meaning it is an "early clobber" register and that no other input can be placed in that register. In combination with "0" (left) in the input definition, the same register is additionally tied to an input, such that the previous value of left is loaded beforehand, in case the conditional move

is not executed. Because left was already declared as output, instead of giving it a new symbolic name we tie it to the input by referencing its index "0" in the output list.

The "=" in the output declaration only means that this register will be written to. Any output needs to have the "=" modifier. Each assembly instruction is postfixed with "\n\t" because the strings are appended into a single long line by the C++ compiler and the line breaks separate instructions for the assembler.

The cmov instruction is postfixed with "b" in this example, which stands for *below*, such that the move is executed if right is below temp (unsigned comparison right < temp). Apart from *below* we will also see *not equal* ("ne") and *carry* ("c") as a postfix in further examples. Furthermore, both the cmpand the cmovb are postfixed with "q" (quad-word) to indicate that the operands are 64-bit values.

When a subtraction (minuend – subtrahend) is performed and subtrahend is larger than minuend (interpreted as unsigned numbers), the operation causes an underflow which results in the carry flag being set. The carry flag can be used as a condition by itself (postfix "c") and it also influences condition checks like *below*. This property of the comparison setting the carry flag will be used in Section 3.1.

# 2.2 | Implementation of sorting networks

We now consider how to actually implement sorting networks for performance.

### 2.2.1 | Providing the network frame

We collected the following sorting networks for small inputs: For sizes of up to 16 elements the best known networks were taken from John Gamble's Website<sup>28</sup> and are size-optimal up to 10 elements. The Bose–Nelson networks have been generated using the instructions from their paper.<sup>2</sup> We did not use any Batcher odd-even network because Codish et al.<sup>3</sup> showed that there was no difference between Batcher and Bose–Nelson in practice.

For sizes of eight and below the best and generated networks have the same amount of comparators and levels. For sizes larger than eight the generated networks are at a disadvantage because they have more comparators and/or levels. As a trade-off their recursive structure makes it possible to leverage a different trait: *locality*. Instead of optimizing them to sort in as few levels as possible, we can first sort the first half of the set, then the second half, and then apply the merger. Thus chances are higher that all  $\frac{n}{2}$  elements of the first half may fit into the processor's general purpose registers. To determine if there is an achievable speedup, the networks were generated optimizing for (a) *locality* and (b) *parallelism*.

Furthermore, we investigated two implementations of locality-optimizing recursively defined Bose–Nelson networks: one where the entire network is rolled out for each input size individually, and a second were the functions of each input size may call smaller sorters for parts of the input. The first unrolled variant retains the name *locality*, while we call the second one a *recursive* implementation.

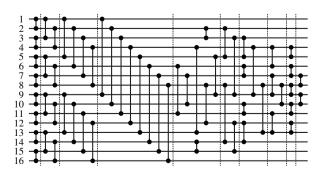

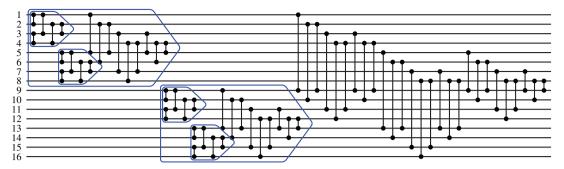

Examples of networks for 16 elements can be seen in Figures 3, 4, and 5.

All networks are implemented such that they have an entry method that takes a pointer to an array A and an array size n as input and delegates the call to the specific method for that number of elements. To measure different implementations for the conditional swaps, the sorting networks are templated with both the swap and the item type.

Our approach differs from most previous work<sup>3</sup> in the type of elements that were sorted. While most experiments measured the sorting of plain ints, which are usually 32-bit sized integers, we made the decision to sort elements that

**FIGURE 4** Bose–Nelson network for 16 elements optimizing locality (unrolled or recursive implementations). The subnetworks marked blue sort eight and four items, respectively [Color figure can be viewed at wileyonlinelibrary.com]

**FIGURE 5** Bose–Nelson network for 16 elements optimizing parallelism

consist of a 64-bit integer key and a 64-bit integer reference value. This enables not only sorting of numbers but also of complex payloads, by giving a pointer or an array index as the reference value. This was implemented by creating a struct that contain a key and reference value each, having the following structure:

```

struct SortableRef {

uint64_t key, ref;

}

```

We also defined the operators >, >=, ==, <, <=, and != for usability. Other keys than integers are also possible: floats or doubles also fit into a single register and can be compared using a single CPU instruction.

# 2.2.2 | Implementing the conditional swap

ConditionalSwap is implemented as a templated method like this:

```

1 template <typename Type>

2 inline void ConditionalSwap(Type& left, Type& right) {

3     // body

4 }

```

Our goal is thus to find the best instructions to implement this method, either by convincing the compiler to produce good code or by writing inline assembly instructions directly. The following variants will represent the body of one specialization of the template function for a specific struct. Each of them was given a three to four letter abbreviation to name them in the results. We implemented the following approaches:

ISwp (if and std::swap):

This is the simplest way of writing the conditional-swap operation, without any inline assembly as a C/C++ if statement with a std::swap (Figure 6). We already saw this code in Section 2.1.3.

TCOp (ternary conditional operators):

This is an alternative portable C/C++ implementation without inline assembly. It uses two *ternary conditional*

Tie (std::tie with std::tuple):

JXhq (imp and xchg):

4 Cm (four cmovs and temp variables):

6Cm (six cmovs and temp variables):

4 CmS (four cmovs split and temp variables):

2CPm (move pointers with two cmovs):

operators ("?:") and a temporary variable (Figure 7). The goal of this method is to try to convince the compiler to generate conditional moves, which seems to happen more often for the ternary operator.

This is another portable C/C++ implementation using an assignment of a pair of variables using structured bindings. In the current C++ versions this can be expressed with std::tupleand std::tie(Figure 8). Again this is portable, and the compiler is tasked to generate efficient code from it.

This is a straight-forward inline assembly version implemented using a comparison, a conditional jump, and two exchange (xchq) instructions. If right key is above left keyor equal to it, the xchq instructions are skipped (jump above or equal, jae). xchq swaps the contents of two registers. The "%=" directive generates a unique label for each asm instance (Figure 9).

This is the shortest assembly implementation with a comparison and four conditional move (cmov) operations. Since we need to swap a key-reference pair of 64-bit integers, we need four cmovs and two temporary variables (Figure 10). The left key and value are stored in the temporary variables, unconditionally. Then the two keys are compared in assembly and the result is stored in the flags register. If the items need to swapped, then the four cmovs first move the right item to the left, and then the temporary item into the right. The issue with this version is that there is an unconditional copy of the left pair into the temporary variables.

In 4Cm the temporary variables are unconditionally assigned outside the assembly block. This is unnecessary if the condition is false, such that we proposed this variant with six cmovs (Figure 11). As before, the keys are compared in assembly, but this time, six cmovs are necessary to swap the items: first copy the left pair into temporary variables, then replace the left with the right pair, and then move the temporaries into the right. If the items need not be swapped, then the temporary variable is not changed. Since the C++ compiler cannot reorder operations inside inline assembly blocks, we attempted to split these such that the compiler can *interleave* load/store operations from multiple consecutive conditional-swaps to avoid memory stalls. There is obviously a limit to this reordering, which requires the asm blocks to be declared volatile such that these stay in order among themselves. The cmovs are the same as in the 4Cm version, except they are split into different blocks (Figure 12).

The following two variants are based on applying cmov to pointers to the SortableRefinstead of moving a pair of key and value. The idea is based on assembly code generated by the clang compiler for the Conditional Swap2 method in Section 2.1.3. First we declare two pointers to the items, and copy the left item into a temporary variable.

17);

After the comparison, the right pointer is copied into the left pointer using a cmov, and then the temporary pointer into the right pointer. After the assembly block, the pointers are used to actually swap the key and value pairs using assignments in C/C++, unconditionally. We split the assembly into two blocks and let the compiler optimize and interleave load and store operations (Figure 13).

### 2CPp (move pointers with two cmovs and predicate):

Instead of performing the comparison inside the asm block, which requires knowledge of the datatype of the key, it can also be done using an indicator predicate. This predicate is simply an integer variable that is passed into the assembly code. Combining predicates with the pointer swapping technique from 2CPm delivers this variant which can operate on keys with custom comparators and any data payload (Figure 14). The goal is simply to see how much slower the external predicate is.

```

if (right < left)</pre>

ISwp (if and std::swap) [Color figure can be viewed at wileyonlinelibrary.com]

std::swap(left, right);

FIGURE 6

1 bool r = (right < left);</pre>

2 auto temp = left;

FIGURE 7 TCOp (ternary conditional operators) [Color figure can be viewed at

3 left = r ? right : left;

wileyonlinelibrary.com]

4 right = r ? temp : right;

std::tie(left, right) = (right < left)</pre>

? std::make_tuple(right, left)

FIGURE 8 Tie (std::tie with std::tuple)

: std::make_tuple(left, right);

1 __asm__(

"cmpq %[left_key],%[right_key]\n\t"

"jae f \in f

"xchg %[left_key],%[right_key]\n\t"

"xchg %[left_ref],%[right_ref]\n\t"

"%=:\n\t"

: [left_key] "=&r"(left.key),

[right_key] "=&r"(right.key),

[left_ref] "=&r"(left.ref),

[right_ref] "=&r"(right.ref)

10

: "0"(left.key), "1"(right.key),

11

"2"(left.ref), "3"(right.ref)

12

FIGURE 9

JXhq (jmp and xchg) [Color figure can be viewed at

: "cc"

13

wileyonlinelibrary.com]

14);

uint64_t tmp = left.key;

2 uint64_t tmp_ref = left.ref;

3 __asm__(

"cmpq %[left_key],%[right_key]\n\t"

"cmovbq %[right_key],%[left_key]\n\t"

"cmovbq %[right_ref],%[left_ref]\n\t"

"cmovbq %[tmp],%[right_key]\n\t"

"cmovbq %[tmp_ref],%[right_ref]\n\t"

: [left_key] "=&r"(left.key),

[right_key] "=&r"(right.key),

10

[left_ref] "=&r"(left.ref),

11

[right_ref] "=&r"(right.ref)

12

13

: "0"(left.key), "1"(right.key),

"2"(left.ref), "3"(right.ref),

14

[tmp] "r"(tmp), [tmp_ref] "r"(tmp_ref)

15

FIGURE 10 4Cm (four cmovs and temp variables) [Color figure can be

16

viewed at wileyonlinelibrary.com]

```

**FIGURE 11** 6Cm (six cmovs and temp variables) [Color figure can be viewed at wileyonlinelibrary.com]

```

uint64_t tmp;

2 uint64_t tmp_ref;

3 __asm__ (

"cmpq %[left_key],%[right_key]\n\t"

"cmovbq %[left_key],%[tmp]\n\t"

"cmovbq %[left_ref],%[tmp_ref]\n\t"

"cmovbq %[right_key],%[left_key]\n\t"

"cmovbq %[right_ref],%[left_ref]\n\t"

"cmovbq %[tmp],%[right_key]\n\t"

10

"cmovbq %[tmp_ref],%[right_ref]\n\t"

: [left_key] "=&r"(left.key),

11

[right_key] "=&r"(right.key),

[left_ref] "=&r"(left.ref),

[right_ref] "=&r"(right.ref),

[tmp] "=&r"(tmp), [tmp_ref] "=&r"(tmp_ref)

15

: "0"(left.key), "1"(right.key), "2"(left.ref),

"3"(right.ref), "4"(tmp), "5"(tmp_ref)

17

: "cc"

19);

```

**FIGURE 12** 4CmS (four cmovs split and temp variables) [Color figure can be viewed at wileyonlinelibrary.com]

```

uint64_t tmp = left.key;

2 uint64_t tmp_ref = left.ref;

3 __asm__ volatile (

"cmpq %[left_key],%[right_key]\n\t"

: [left_key] "r"(left.key),

[right_key] "r"(right.key)

: "cc"

9);

10 __asm__ volatile (

"cmovbq %[right_key],%[left_key]\n\t"

: [left_key] "=&r"(left.key)

: "0"(left.key), [right_key] "r"(right.key)

14

15);

16 __asm__ volatile (

"cmovbq %[right_ref],%[left_ref]\n\t"

: [left_ref] "=&r"(left.ref)

: "0"(left.ref), [right_ref] "r"(right.ref)

19

20

21);

22 __asm__ volatile (

"cmovbq %[tmp],%[right_key]\n\t"

: [right_key] "=&r"(right.key)

: "0"(right.key), [tmp] "r"(tmp)

26

27);

28 __asm__ volatile (

"cmovbq %[tmp_ref],%[right_ref]\n\t"

: [right_ref] "=&r"(right.ref)

: "0"(right.ref), [tmp_ref] "r"(tmp_ref)

33 );

```

In Sections 4.2 and 4.3 we report on our experiments with these conditional swap operations.

We also tried a variant with XOR (see also Codish et al.<sup>3</sup>), where the left item is first stored in a temporary variable and then conditionally overwritten with the right in case the values have to be swapped. The right item is then calculated using an XOR of the right, the original left, and current left (which was possibly replaced with the right). In case no swap occurs, the original left and current left are the same and cancel out. In case a swap occurs, the current left and right are the same and cancel out, leaving the original left as the new value of right. We experimented with this variant, but it turned

```

Type* left_pointer = &left;

2 Type* right_pointer = &right;

3 Type temp = left;

4 __asm__ volatile(

"cmpq %[tmp_key],%[right_key]\n\t"

"cmovbq %[right_pointer],%[left_pointer]\n\t"

: [left_pointer] "=&r"(left_pointer)

: "0"(left_pointer),

[right_pointer] "r"(right_pointer),

[tmp_key] "r"(temp.key),

10

[right_key] "r"(right.key)

11

: "cc"

12

13);

14 left = *left_pointer;

15 left_pointer = &temp;

16 __asm__ volatile(

"cmovbq %[left_pointer],%[right_pointer]\n\t"

17

: [right_pointer] "=&r"(right_pointer)

: "0"(right_pointer),

[left_pointer] "r"(left_pointer)

20

21

22 );

23 right = *rightPointer;

Type* left_pointer = &left;

2 Type* right_pointer = &right;

3 Type temp = left;

4 int cmp_result = (int)(right < temp);</pre>

5 __asm__ volatile(

"cmp $0,%[cmp_result]\n\t"

"cmovneq %[right_pointer],%[left_pointer]\n\t"

: [left_pointer] "=&r"(left_pointer)

: "0"(left_pointer),

[right_pointer] "r"(right_pointer),

10

[cmp_result] "r"(cmp_result)

: "cc"

12

13);

14 left = *left_pointer;

15 left_pointer = &temp;

16 __asm__ volatile(

"cmovneq %[left_pointer], %[right_pointer] \n\t"

: [right_pointer] "=&r"(right_pointer)

18

: "0"(right_pointer),

19

[left_pointer] "r"(left_pointer)

20

21

22 );

23 right = *rightPointer;

```

**FIGURE 13** 2CPm (move pointers with two cmovs) [Color figure can be viewed at wileyonlinelibrary.com]

**FIGURE 14** 2CPp (move pointers with two cmovs and predicate) [Color figure can be viewed at wileyonlinelibrary.com]

out to be much slower (by a factor of 2–3) in preliminary results. Another variant with XOR would be to use  $x = x \oplus y$ ,  $y = x \oplus y$ ,  $x = x \oplus y$ . This however requires a conditional branch and is thus only a more complicated replacement for a swap.

#### 3 | REGISTER SAMPLE SORT

After initial positive experimental results of our investigation of sorting networks for small inputs, we decided to turn to *sample sort* for slightly larger inputs. Our preliminary experiments showed that sorting networks were indeed faster, but

they also required a lot of instructions, leading to large instruction decoding times and L1 cache misses. Another motivation was that the base cases issued by In-Place Parallel Super Scalar Samplesort (IPS $^4$ o) $^5$  were considerably larger than 16 items. Hence, instead of extending sorting networks beyond 16 elements, we close this gap by providing a completely different basic algorithm for small to medium size inputs:  $Register\ Sample\ Sort\ (RSS)$ . Our new algorithm is based on Super Scalar Sample Sort (S $^4$ ) $^4$  and can reduce large base case sizes down to blocks of 16 or less in an efficient manner. The central idea is to place the splitters not into an array, as described in the original S $^4$ , but to hold them in general purpose registers for the whole duration of the element classification.

### 3.1 | Basic sequential sample sort

Sample sort<sup>29</sup> is a sorting algorithm that follows the divide-and-conquer principle. The input is split into k disjoint intervals of the total ordering defined by k+1 splitters  $s_0, \ldots, s_k$ . These are chosen by first selecting a sample subset S of  $a \cdot k$  items with oversampling factor a and sorting the sample S. Afterward the splitters  $\{s_0, s_1, \ldots, s_{k-1}, s_k\} = \{-\infty, S_a, S_{2a}, \ldots, S_{(k-1)a}, \infty\}$  are taken equidistant from S. Oversampling is used to get better splitters to achieve more evenly sized partitions, trading balance for the additional time to select and sort the larger sample.

Given the splitters, all elements  $e_i$  are then *classified* by placing them into buckets  $b_j$ , where  $j \in \{1, ..., k\}$  and  $s_{j-1} < e_i \le s_j$ . If k is a power of 2, this placement can be achieved by viewing the splitters as a perfect binary tree, with  $s_{k/2}$  being the root, all  $s_l$  with l < k/2 representing the left subtree and those with l > k/2 the right one. To classify an element, one must only traverse this binary tree in logarithmic time, resulting in a binary search on k+1 elements instead of a linear one.<sup>4</sup>

Quicksort<sup>20</sup> can be seen as a specialization of sample sort with fixed parameter k = 2. Sample sort is very popular for sorting large amounts of items on distributed systems, <sup>30-32</sup> on GPUs, <sup>33</sup> and also for strings. <sup>34,35</sup>

# 3.2 | Implementing register sample sort for medium-sized sets

In this section we explain how to implement sample sort using registers in a CPU. The main issue is that, other than memory, registers *cannot be accessed using an index* on most popular architectures.

### 3.2.1 | Traversing A tree in registers

In implementations of S<sup>4</sup> splitters are organized in memory as a perfect binary search tree t:= [ $s_{k/2}$ ,  $s_{k/4}$ ,  $s_{3k/4}$ ,  $s_{3k/8}$ ,  $s_{5k/8}$ ,  $s_{7k/8}$ ,  $s_{7k/8}$ , ...]. Traversal of the splitter tree is then performed using an index j: the children of splitter j are at positions 2j and 2j + 1. If an element is smaller than  $t_j$ , it must be compared with  $t_{2j}$ , otherwise to  $t_{2j+1}$ , in the next step. This allows an easy branchless traversal of the tree by multiplying j with two and conditionally incrementing it. But this way of accessing the splitters does not work when they are placed in registers, because we cannot access registers by index.

Our solution is to create *an unconditional complete copy* of the left subtree, and to use cmov operations to *conditionally overwrite it* with the complete right subtree should the element be greater than the root node. The next comparison is then performed against the root of the copied tree that now contains the correct splitters. This way we traverse the tree until a leaf node is reached. The copying of subtrees is obviously expensive and only viable for small trees. For three splitters this requires one conditional move, and for seven splitters it requires three conditional moves after the first comparison and one additional after the second comparison, per element.

# 3.2.2 | Calculating the final bucket index

However, after finding the correct splitters to compare to, we are left with yet another problem: how to determine the index of the bucket the element is to be placed into. In S<sup>44</sup> this bucket index is calculated directly from the index of the last splitter. For Register Sample Sort, we choose an approach similar to creating this index using the correlation between

binary numbers and the tree-like structure of the splitters. We view the splitters not as a binary tree but just as a list where the middle of the list represents the root node of the tree, its children being the middle element of the left and the middle element of the right list.

If an element  $e_i$  is larger than the first splitter  $s_{k/2}$  (with k-1 being the number of nonsentinel splitters,  $s_0$  and  $s_k$  are handled implicitly), it must be placed in a bucket  $b_j$  with  $j \ge \frac{k}{2}$  (assuming 0-based indexing for b). This also means that the index of that bucket, represented as a binary number, must have its bit at position  $l := \log \frac{k}{2}$  set to 1. Hence the result of the comparison ( $e_i > s_{k/2}$ ) can be interpreted as an integer (1 for true, 0 for false) and added to j. If it was not the final comparison, j is then multiplied by 2 (meaning its bits are shifted left by one position). This means the bit from the first comparison makes its way "left" in the binary representation while the comparison traverses down the tree, and so forth with the other comparisons. After traversing the splitter tree to the end,  $e_i$  will have been compared with the correct splitters and j will hold the index of the bucket that  $e_i$  belongs into. A similar method is used in S<sup>4</sup> when calculating the index during tree traversal. These operations can be implemented without branches by making use of the way the comparisons are performed:

At the end of Section 2.1.4 we explained that when comparing (unsigned) numbers (which is nothing but a subtraction), and the subtrahend being greater than the minuend, the operation causes an underflow and the carry flag is set. We also notice that when converting the result of the predicate  $(e_i > s_{k/2})$  to an integer value, the integer will be 1 for true and 0 for false. So in assembly code, we can compare the result from evaluating the predicate to the value 0: cmp [result], [result], where zero is just a register that holds the value 0. This trick is needed because the cmp instruction needs the second operand to be a register. This will execute 0 - result, which underflows for the predicate returning true. This way we can postfix the cmov needed for moving the next splitters with "c" checking for a set carry flag. The second instruction we make use of is the *rotate carry left* (rcl) instruction, which performs a *rotate left* instruction on j, but includes the carry flag as an additional bit after the least significant bit of the integer. This exactly takes the predicate result and puts it at the bottom of j, with the previous content being shifted one to the left beforehand. That means it performs two necessary operations at once.

# 3.2.3 Putting things together: Determining parameters and pseudocode

With the previous two challenges of classification solved, we can now design the parameters for our Register Sample Sort. As with S<sup>4</sup>, when processing items from the input we can *interleave classification* of multiple elements, allowing for all the registers in the machine to be used. This additional parameter is called *block size*.

The main constraint on the parameters of Register Sample Sort is the *number of registers* in the CPU. The keys of the splitters (since we only need a splitter's key for classifying an element) must be small enough to fit into a general purpose register. Needing more than one register per key would mean running out of registers more quickly and also spending extra time to conditionally move the splitter keys around. For three splitters the number of registers needed for block sizes 1 to 5 are shown in Table 1. We can see that the trade-off for classifying multiple elements at the same time is the amount of registers needed.

|                       | Thi | ree spli | tters b | lock siz | ze | Seven splitters block size |    |    |    |    |  |  |

|-----------------------|-----|----------|---------|----------|----|----------------------------|----|----|----|----|--|--|

|                       | 1   | 2        | 3       | 4        | 5  | 1                          | 2  | 3  | 4  | 5  |  |  |

| Splitters             | 3   | 3        | 3       | 3        | 3  | 7                          | 7  | 7  | 7  | 7  |  |  |

| Buckets pointer       | 1   | 1        | 1       | 1        | 1  | 1                          | 1  | 1  | 1  | 1  |  |  |

| current element index | 1   | 1        | 1       | 1        | 1  | 1                          | 1  | 1  | 1  | 1  |  |  |

| Element count         | 1   | 1        | 1       | 1        | 1  | 1                          | 1  | 1  | 1  | 1  |  |  |

| Index                 | 1   | 2        | 3       | 4        | 5  | 1                          | 2  | 3  | 4  | 5  |  |  |

| Predicate result      | 1   | 2        | 3       | 4        | 5  | 1                          | 2  | 3  | 4  | 5  |  |  |

| splitterX             | 1   | 2        | 3       | 4        | 5  | 3                          | 6  | 9  | 12 | 15 |  |  |

| Sum                   | 9   | 12       | 15      | 18       | 21 | 15                         | 20 | 25 | 30 | 35 |  |  |

**TABLE 1** Number of registers required by register sample sort with three or seven splitters

If we were to use seven splitters instead of three, the number of registers required for classifying just one element at a time would go up to 15. Furthermore, if we get recursive subproblems with just slightly over 16 items, classifying into eight buckets would be greatly inefficient, resulting in many empty buckets. This is why we decided to only use *exactly three splitters* for this particular sorter.

Instead of inline assembly from our implementation, we present pseudocode of the classification for block size = 1 in Algorithm 1. The index j is here called index, and the temporary subtree consists in this case of one splitter, which we gave the name splitterX. For our branchless implementation we used cmovne together with a test instruction to move the right hand splitter into splitterX and just assigned the integer result of the comparison to index in the first step (lines 9 and 11). At the second and last level of classification no more movement of splitters is required, so instead of performing a comparison against the predicate's result and using rcl, we can just shift index left by one position and add the predicate's result to it (line 13). Alternatively we could use a bit-wise OR or XOR after the shift, which would have the same result. But we decided that adding the predicate result was more readable.

For sorting the splitter sample, the same sorting method can be used as for the base case, which in our case is to use a sorting network from Section 2.

### Algorithm 1. Register Sample Sort classification pseudocode for three splitters

```

void RegisterSampleSortClassification(Type* array, unsigned array size) {

Type [splitter0, splitter1, splitter2] = determineSplitters();

Type* [b_0, b_1, b_2, b_3] = allocateBuckets(array size);

for (int i = 0; i < array size; ++i) {</pre>

int index = 0;

int cmp result = (int) (splitter1 < array[i]);</pre>

splitterx = splitter0;

// copy left tree into splitterx

if (cmp result) {

// first and only decision in a tree with three splitters

splitterx = splitter2;

// overwrite using a cmovne

10

index = cmp {r}esult;

11

cmp {r}esult = (int) (splitterx < array[i]);</pre>

12

index = (index << 1) + cmp {r}esult;

13

b<sub>index</sub>.push {b}ack(array[i]);

15

16 }

```

#### 4 | EXPERIMENTAL RESULTS

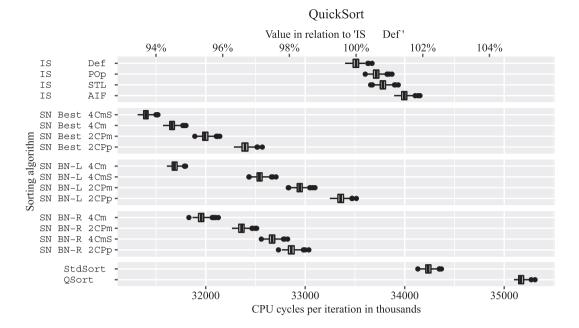

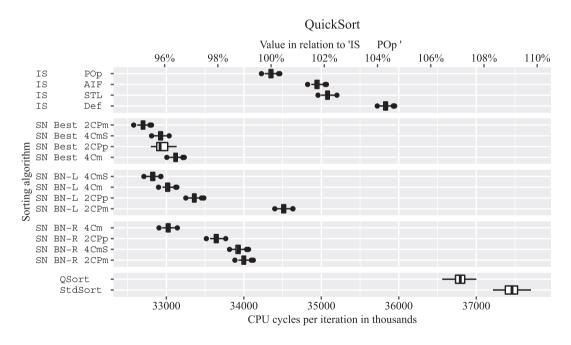

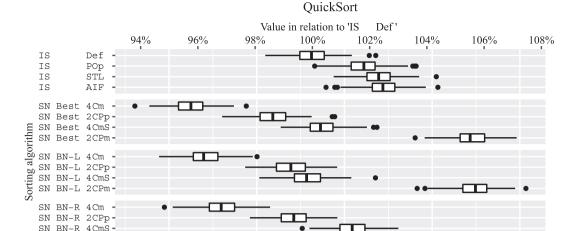

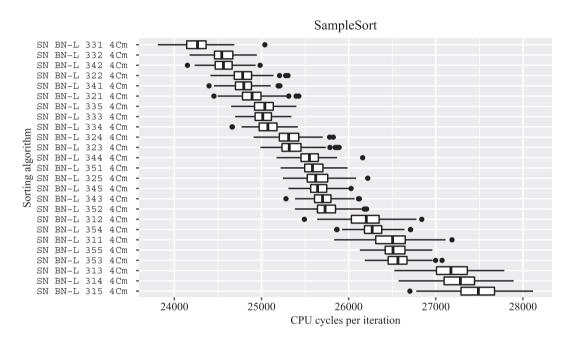

In this section we report on four sets of experiments with sorting networks and Register Sample Sort. The first are pure performance measurements of sorting networks, either sorting the same array repeatedly or sorting a larger array containing many independent small problems. The second experiments are on the performance of Quicksort with sorting networks as base case, the third on finding good parameters for Register Sample Sort, and the last on integrating Register Sample Sort and sorting networks into IPS<sup>4</sup>o.

### 4.1 | Parameters, machines, inputs, methodology

### 4.1.1 | Machines and compiler

We used four different machines to perform the measurements, including Intel, AMD, and ARM CPUs. Their labels and hardware properties can be seen in Table 2. In the table "I" and "D" refer to dedicated L1 instruction and data caches. While the AMD Ryzen's L3 cache has a total size of 16 MiB, it is divided into two 8 MiB caches that are exclusive to four

TABLE 2 Hardware properties of the machines used in our experiments

| Machine name            | Intel-2650               | Intel-2670               | Ryzen-1800X           | RK3399                                                   |

|-------------------------|--------------------------|--------------------------|-----------------------|----------------------------------------------------------|

| CPU                     | 2 x Intel XeonE5-2650 v2 | 2 x Intel XeonE5-2670 v3 | AMD Ryzen 1800X       | Rockchip RK3399                                          |

|                         | 8-core, 2.6 GHz          | 12-core, 2.3 GHz         | 8-core, 3.6 GHz       | ARM Cortex-A53   -A72                                    |

|                         |                          |                          |                       | $4 \times 1.5 \text{ GHz} \mid 2 \times 2.0 \text{ GHz}$ |

| RAM                     | 128 GiB DDR3-1600        | 128 GiB DDR4-2133        | 32 GiB DDR4-2133      | 4 GiB LPDDR4                                             |

| L1 cache (KiB per core) | 32 I + 32 D (8-way)      | 32 I + 32 D (8-way)      | 64 I + 32 D (4/8-way) | 32 I + 32 D   48 I + 32 D                                |

| L2 cache (KiB per core) | 256 (8-way)              | 256 (8-way)              | 512 (8-way)           | 512   1024                                               |

| L3 cache (MiB total)    | 20                       | 30 (20-way)              | 16 [8] (8-way)        | _                                                        |

| Linux Distribution      | Ubuntu 18.04             | Ubuntu 18.04             | Ubuntu 18.04          | Armbian (Debian) Buster                                  |

| Compiler                | gcc 7.3.0                | gcc 7.3.0                | gcc 7.3.0             | gcc 8.3.0                                                |

cores each. Since all measurements were done on a single core, the L3 cache size in brackets is the one available to the program.

For compiling our experiment code we used the gcc C++ compiler in version 7.3.0 or 8.3.0 with -O3 and -march=native flags. We did not experiment with LLVM or other compilers because this increases the parameter space by another dimension.

The measurements were done with only essential processes running on the machine apart from the measurement. To prevent the process from being swapped to another core during execution it was run with the command "taskset 0x1" as prefix, which pins it to the first core.

### 4.1.2 | Inputs: Random numbers

In order to measure the time needed to sort some data, we first have to generate data. For all experiments the data type consisted of a pair of one 64-bit unsigned integer key and one 64-bit unsigned integer reference value. Items were generated as uniformly distributed random numbers by a lightweight implementation of the  $std::minstd_rand$  generator from the C++ <random> library that works as follows: First a seed is set, taken, for example, from the current time. When a new random number is requested, the generator calculates  $seed=(seed\cdot48271) \mod 2147483647$  and returns the current seed. The numbers generated by this generator does not use all 64 bits available, which however has no effect on the experiment results.

For each measurement i, a new seed<sub>i</sub> is taken from the current time. The same seed<sub>i</sub> is then set before the execution of each sorter, to provide all sorters with the same random inputs.

We only experimented with random inputs. In future work, "easy" inputs such as sorted and reverse sorted inputs, and others should also be included.

### 4.1.3 | Measurement of cycles with perf\_event

The actual measurement was done via linux's perf\_event interface that allows to do fine-grained measurements using hardware counters. We measured the number of CPU *cycles* spent on sorting. This also means that our results do not depend on clock speeds (e.g., when overclocking), but only on the CPU's architecture. On the ARM machine RK3399 we resorted to simply measuring time, because the CPU cycles event interface was not available.

### 4.1.4 Checking results: Permutation check

For compilation, the optimization flag -O3 was used to achieve high optimization and speed. This also meant that, without using the sorted data in some way, the compiler would deem the result unimportant and skip the sorting altogether. That is why after each sort, to generate a side-effect, the set is checked for two properties: That it is sorted, and that it is a

permutation of the input set. The first can easily be done by checking for each value that it is not greater than the value before it.

The permutation check is done probabilistically: At design time, a (preferably large) prime number p is chosen. Before sorting,  $v = \prod_{i=1}^{n} (z - a_i) \mod p$  is calculated for an arbitrary number z and values  $a = \{a_1, \ldots, a_n\}$ . To check the permutation after sorting and obtaining  $a' = \{a1', \ldots, an'\}$ ,  $w = \prod_{i=1}^{n} (z - a'_i) \mod p$  is calculated. If  $v \neq w$ , a' cannot be a permutation of a. If v = w, we claim that a' is a permutation of a.

To minimize the chances of a' not being a permutation of a, but v being equal to w, v = 0 was disallowed in the first step. If v is zero, z is incremented by one and the product calculated again, until  $v \neq 0$ .

We do this kind of check because in each iteration the input array is overwritten with new random numbers, and using an easier algorithm to sort the array afterward and then checking for equality would include copying the unsorted array, sorting, and checking, which adds extra time and variation to a measurement consisting of many of these iterations. The permutation check on the other hand is branch-free, and the sorted check is effectively branch-free for any sorted array, because the compiler is told to expect the sorted condition to be true, and will speculatively execute the branch in which it is, not leading to any flushing of the pipeline. This way we can run the sorted and permutation check in a second measurement with the same number of iterations, and subtract that time from the original measurement, giving only the time needed for sorting.

### 4.1.5 | Multiple source file compilation

Initially, the experiments were a single source file (.cpp) with an increasing amount of headers that were all included in that single file. This was mostly due to the fact that templated methods cannot be placed in source files because they need to be visible to all including files at compile time. The increasing amount of code and the many different templates, however, brought the compiler to a point where it took over a minute to compile the program. The problem we encountered was that the compiler apparently allots less time to optimization the longer the compilation runs on a source file. Hence, once our experiment program became reasonably large, the optimizations became poor. We saw measurements being slower for no apparent reason. To solve that problem, we used code generation to create source files that contain a smaller amount of methods that initiate part of a measurement in a wrapper method. From the main source file we thus only need to call the correct wrapper methods to perform the measurements, and this way we were able to achieve results that were more stable and reproducible. In our case that means one file for the OneArrayRepeat experiment (Section 4.2), one for ArrayInRow (Section 4.3), one for QuickSort (Section 4.4), one for SampleSort (Section 4.5), and an individual file for each configuration of the IPS<sup>4</sup>0 measurement (Section 4.6).

### 4.1.6 Measurement loops and warm-up

As the sorting algorithm on a small number of items is very fast, we measured many iterations and divided by the number of repetitions. Since in this scenario we have to generate new random inputs for each iteration, we decided to first measure the three steps (a) data generation, (b) sorting, and (c) checking, and then measure only (a) data generation and (c) checking on the same inputs. By subtracting the two running times we receive the pure sorting time. We call this measurement loop *OneArrayRepeat*.

More details on the method are now discussed: At the beginning a random seed is selected and the generator initialized. To reduce the chance of cache misses at the beginning of the measurement, one warm-up run of random generation, sorting, and checking is performed before starting the clock. After the warm-up round, the array is then filled, sorted, and checked numberOfIterations times. The random generator is not reseeded each round. After the main measurement, a second phase is run with the same data. But this time only the generation of the random numbers and the checking is measured to later subtract the time from the previously measured one, resulting in the time needed for the sorting alone. To generate and check the same input again, the random generator is reseeded with the previously selected seed. Obviously, the checking of the unsorted data (usually) fails but it has to performed to measure the time. Hence, we devised a simulated checking method, which does the exact same comparisons and permutation calculations, but ignores the result.

Nevertheless there are random nondeterministic fluctuations in running time even on the same code. And since both measurement parts are subject to their own deviation, it can occasionally happen that the second measurement takes

longer than the first, leading to negative running times for sorting. We received negative values more often for the sorters with small array sizes, where the sorting itself takes relatively little time compared with the random generation and sorted checking. The negative times show up as outliers in the results.

The measurement loop itself is repeated numberOfMeasures times for each arraySize that is sorted.

For the measurements shown in Section 4.3 the method was slightly modified. The goal was to better highlight cacheand memory-effects by creating one longer array that does not fit into the CPU's L3-cache and then sorting disjoint short subsequences of size arraySize in order. We call this modified measurement loop *ArrayInRow*.

Because we can create the whole array at the beginning, we can generate the numbers before and check for correct sorting after measuring, hence there is no need to do a second measurement like in the OneArrayRepeat benchmark. As in the prior benchmark, one warm-up round is performed prior to running the measured loop.

For ArrayInRow, instead of giving a numberOfIterations parameter to indicate how often the sorting is to be repeated, we provide a numberOfArrays value that prescribes how many arrays of size arraySize are to be created contiguously. This parameter is chosen for each arraySize in a way that (numberOfArrays · arraySize) does not fit into the L3 cache of the machine the measurement is performed on.

### 4.1.7 | Generating plots

Due to the high number of dimensions in the measurements (machine the measurement is run on, type of sorting network, conditional swap implementation, array size) the results could not always be plotted two-dimensionally. We used box plots where applicable to show more than just an average value for a measurement. The box encloses all values between the first quartile  $q_1$  and third quartile  $q_3$ . The line in the middle shows the median. Further the inter-quartile-range  $\overline{q}$  is calculated as the distance between first and third quartile. The lines (called whiskers) left and right of the boxes extend to the smallest value greater than  $q_1 - 1.5\overline{q}$  and the greatest value smaller than  $q_3 + 1.5\overline{q}$ , respectively. Values below these ranges are called *outlier* and shown as individual dots.

# 4.2 | Sorting sets of 2–16 items

In this and the following subsection we report on experiments comparing sorting algorithms and conditional-swap implementations. For the details about the different sorters and swaps refer to Section 2.2.

The algorithm variants in the tables and figures are labeled in an abbreviatory way such as "SN BN-R 4CmS". The abbreviations are composed from the following three parts:

- First, IS or SN indicate if the algorithm is insertion sort or a sorting network.

For IS we evaluated four variants: Def is a textbook implementation with array indices, POpuses pointers as iterators, STL is copied from gcc's STL implementation, and AIF is Def with an additional check if the next item is smaller than the first

- 2. In case of sorting networks, the algorithms are labeled as Best networks or Bose-Nelson networks (BN). The Bose-Nelson sorters are further available optimized for *locality* (BN-L), *parallelism* (BN-P), or written as *recursively* called sorting functions (BN-R) (see Section 2.2.1).

- 3. And as last component, the name of the conditional swap implementation is appended for sorting networks (see Section 2.2.2 for their abbreviations).

As an example consider "SN BN-R 4CmS". This implementation is a Bose-Nelson sorting network generated using recursively constructed functions which perform the conditional-swap using the 4CmS variant.

Table 3 shows the binary x86 code size of each insertion sort and sorting network variant (size 2–16). We determined their binary x86 code size by compiling the code (with -O3 optimization) and then disassembling the object file and identifying which functions therein belong to the algorithm. In Table 3 we also included the code size of std::sort, Register Sample Sort (RSS), and IPS<sup>4</sup>o, each excluding any subsorters.

To determine the fastest algorithm variant, we ran the OneArrayRepeat experiment with the following parameters on all machines and algorithms: numberOfIterations=100, numberOfMeasures=500, and array- $Size \in \{2, ..., 16\}$ .

**TABLE 3** Size in bytes of binary x86 assembly code of sorters generated by gcc (with optimization)

| Algorithm          | Size   | Algorithm    | Size   | Algorithm    | Size   | Algorithm    | Size   | Algorithm    | Size   |

|--------------------|--------|--------------|--------|--------------|--------|--------------|--------|--------------|--------|

| IS Def             | 91     | SN Best ISwp | 17,936 | SN BN-L ISwp | 19,264 | SN BN-P ISwp | 19,216 | SN BN-R ISwp | 12,880 |

| IS POp             | 122    | SN Best Tie  | 33,328 | SN BN-L Tie  | 34,400 | SN BN-P Tie  | 35,920 | SN BN-R Tie  | 19,072 |

| IS STL             | 188    | SN Best JXhg | 12,080 | SN BN-L JXhg | 10,160 | SN BN-P JXhg | 12,880 | SN BN-R JXhg | 6144   |

| IS AIF             | 200    | SN Best 4Cm  | 19,008 | SN BN-L 4Cm  | 17,456 | SN BN-P 4Cm  | 20,640 | SN BN-R 4Cm  | 9584   |

| std::sort          | 1283   | SN Best 4CmS | 19,472 | SN BN-L 4CmS | 17,312 | SN BN-P 4CmS | 20,704 | SN BN-R 4CmS | 10,720 |

| RSS 332            | 1280   | SN Best 2CPm | 24,064 | SN BN-L 2CPm | 25,360 | SN BN-P 2CPm | 25,696 | SN BN-R 2CPm | 14,096 |

| IPS <sup>4</sup> o | 42,689 | SN Best 2CPp | 26,912 | SN BN-L 2CPp | 28,416 | SN BN-P 2CPp | 28,736 | SN BN-R 2CPp | 14,640 |

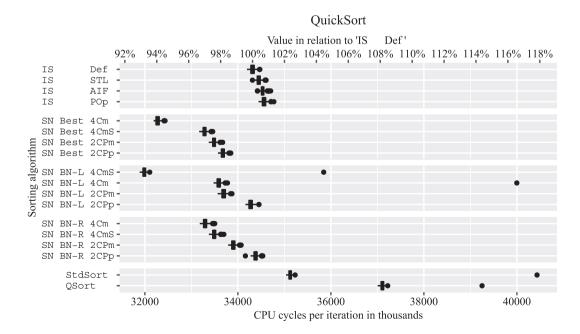

Table 4 shows our results as a ranking of the algorithms by geometric mean, individually and across all machines, of the slowdown relative to the best on the particular machine. Table 5 summarizes the fastest sorting network over the fastest insertion sort implementation. Further results are shown in the Appendix Tables A1, A2, A3, and A4; there we show the name of the sorter and the average number of cycles per iteration, over the total of all measurements, for all machines. The algorithm that performed best in a column is marked in bold font, and for each column the slowdown relative to the best in that column was calculated. For each row the geometric mean "GeoM" is shown over these relative slowdown values and the mean is used to rank the algorithms.

The tables show that the implementations without conditional branches (4Cm, 4CmS, 2CPm, 2CPp) and those with (ISwp, Tie, JXhg) are clearly separated by rank in the overall result, the former occupy the lower share of the ranks, while the latter all the higher ranks. To improve readability, the variants TCOpand 6Cm are omitted. Variant 6Cm was similar to the other variants without conditional branches, and TCOp was close to the results of JXhg. We omitted them because they are probably executed very similarly by the processors.

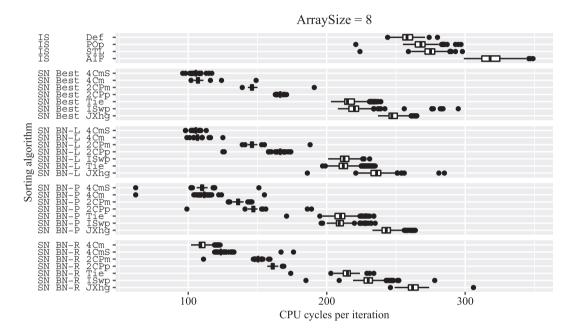

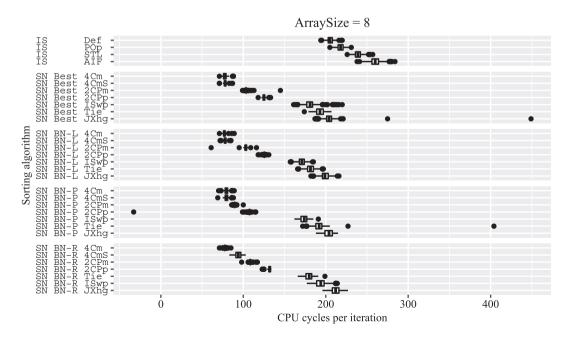

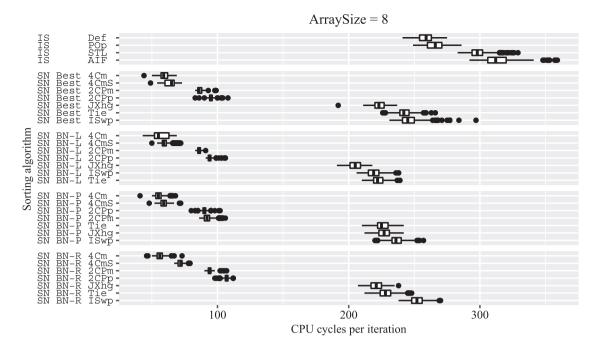

Comparing the machines in Table 4, we see that our hypothesis that the 4CmS conditional swap is better than the 4Cm was shown to be true for machines Intel-2650 and Intel-2670, but not for machines Ryzen-1800X and RK3399. We believe this is due to the first machines having better support for interleaving load and store operations. We also see in Table 4 that the first five ranks have very similar geometric means, which implies the Bose—Nelson networks (BN-L and BN-R) can compete (due to their locality) with the optimized networks (Best) that have fewer comparators.

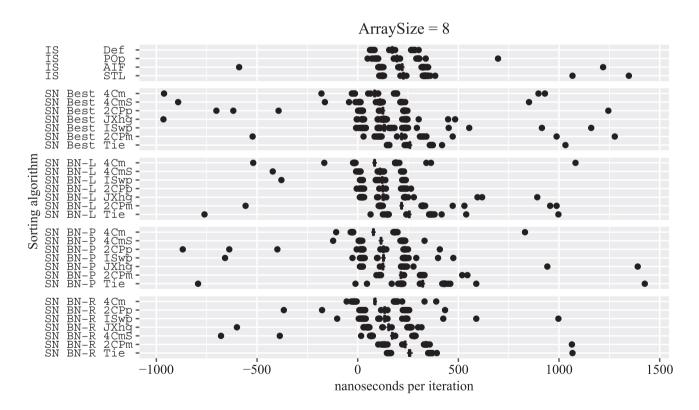

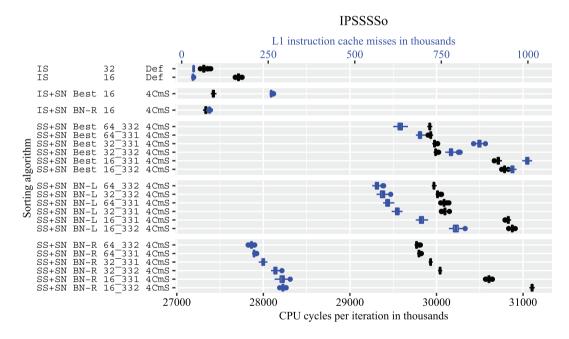

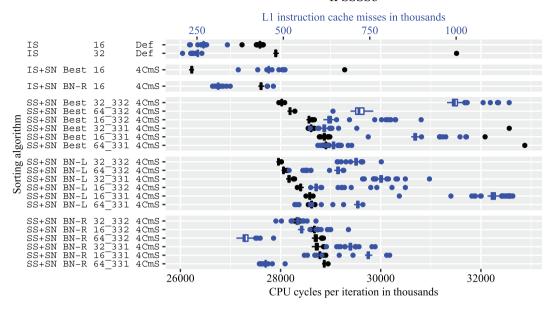

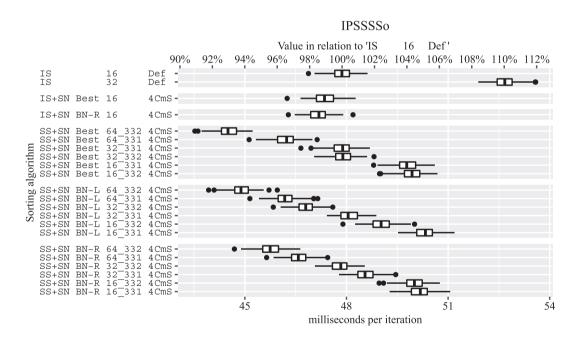

Figures 15, 16, 17, and 18 show box plots of the CPU cycle measurement for array size 8 on each machine. These plots highlight that the best sorting network implementations are not only faster on average, but that their distribution is almost entirely faster than any of the insertion sort implementations, together with a lower variance. As in the tables, the variants TCOp and 6Cm are omitted to improve readability. Furthermore, one outlier was removed from data set of machine Intel-2670 for the SN BN-P 4CmS sorter with value -228.55 such that the plot has a scale similar to those of the other two machines, to improve comparability. It is remarkable that on the RK3399 machine the variance of the sorting networks is much higher than on the other platforms. However, this may be an effect due to measuring nanoseconds wallclock time on the machine (due to lack of performance counters or support for them) versus CPU cycles on the others.

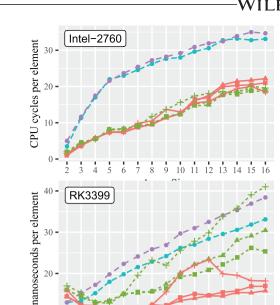

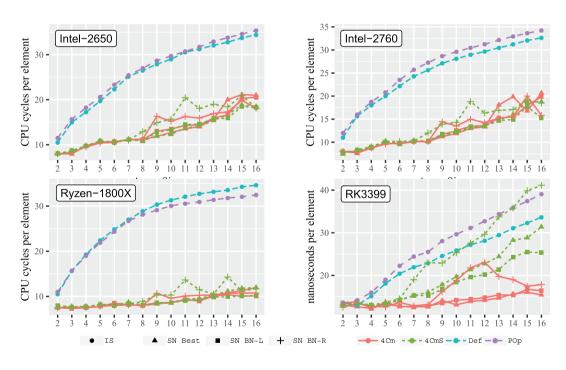

To see a trend in increasing array size, we chose a few conditional-swap implementations that do best for more than one network and array size on all machines. These series increase as expected from the  $\mathcal{O}(n\log^2 n)$  asymptotic growth rate of the sorting networks. Their average sorting times with OneArrayRepeat can be seen in Figure 19. For better readability, we omitted the Bose–Nelson parallel (BN-P) networks in these plots. The figures underline the results already shown in the tables: the 4Cm and 4CmS implementations have good performance and are almost always faster on average than insertion sort (apart from arraySize = 2 on machine RK3399).

These results indicate that there is potential in using sorting networks, showing that the best insertion sort is slower by a factor of 1.79 on average on machine RK3399, up to a factor of 4.47 on average on machine Ryzen-1800X (see Table 5 for details). The issue with the OneArrayRepeat experiment is that the same memory area is sorted over and over again, which is rarely a use case when sorting a base case. Because of this, the results probably reflect unrealistic conditions regarding cache accesses and cache misses. To get closer to realistic base case sorting, the next section regards the ArrayInRow pattern.

**TABLE 4** Ranking of sorting algorithms by geometric mean of relative slowdowns for the OneArrayRepeat experiment across all machines

| Sorter       | Overall |      | Intel-26 | 50   | Intel-26 | 70   | Ryzen-1 | .800X | RK3399 |      |

|--------------|---------|------|----------|------|----------|------|---------|-------|--------|------|

|              | Rank    | GeoM | Rank     | GeoM | Rank     | GeoM | Rank    | GeoM  | Rank   | GeoM |

| SN BN-L 4Cm  | 1       | 1.09 | 4        | 1.12 | 1        | 1.08 | 1       | 1.08  | 3      | 1.07 |

| SN Best 4Cm  | 2       | 1.12 | 6        | 1.14 | 5        | 1.10 | 5       | 1.19  | 2      | 1.04 |

| SN BN-P 4Cm  | 3       | 1.13 | 8        | 1.17 | 8        | 1.14 | 4       | 1.18  | 1      | 1.03 |

| SN BN-R 4Cm  | 4       | 1.15 | 3        | 1.11 | 4        | 1.09 | 3       | 1.15  | 4      | 1.25 |

| SN BN-L 4CmS | 5       | 1.18 | 2        | 1.09 | 3        | 1.09 | 2       | 1.14  | 5      | 1.45 |

| SN Best 4CmS | 6       | 1.23 | 1        | 1.09 | 2        | 1.09 | 6       | 1.23  | 15     | 1.57 |

| SN BN-P 4CmS | 7       | 1.27 | 5        | 1.13 | 7        | 1.14 | 7       | 1.24  | 18     | 1.64 |

| SN BN-R 4CmS | 8       | 1.33 | 7        | 1.15 | 6        | 1.12 | 8       | 1.29  | 21     | 1.89 |

| SN Best 2CPp | 9       | 1.53 | 12       | 1.35 | 13       | 1.43 | 12      | 1.86  | 6      | 1.50 |

| SN BN-P 2CPp | 10      | 1.55 | 13       | 1.38 | 14       | 1.45 | 13      | 1.87  | 7      | 1.54 |

| SN Best 2CPm | 11      | 1.55 | 9        | 1.19 | 9        | 1.18 | 10      | 1.62  | 23     | 2.54 |

| SN BN-P 2CPm | 12      | 1.58 | 10       | 1.21 | 10       | 1.22 | 9       | 1.61  | 27     | 2.62 |

| SN BN-L 2CPm | 13      | 1.68 | 11       | 1.32 | 11       | 1.31 | 11      | 1.82  | 24     | 2.56 |

| SN BN-L 2CPp | 14      | 1.68 | 15       | 1.54 | 15       | 1.61 | 15      | 2.10  | 11     | 1.55 |

| SN BN-R 2CPp | 15      | 1.81 | 16       | 1.67 | 16       | 1.73 | 16      | 2.38  | 16     | 1.57 |

| SN BN-R 2CPm | 16      | 1.82 | 14       | 1.43 | 12       | 1.41 | 14      | 2.06  | 28     | 2.66 |

| SN BN-P ISwp | 17      | 2.32 | 17       | 2.03 | 18       | 2.13 | 26      | 4.32  | 8      | 1.54 |

| SN Best ISwp | 18      | 2.33 | 19       | 2.05 | 17       | 2.10 | 30      | 4.41  | 12     | 1.55 |

| SN BN-L ISwp | 19      | 2.37 | 23       | 2.15 | 21       | 2.19 | 27      | 4.33  | 10     | 1.54 |

| SN BN-R ISwp | 20      | 2.40 | 24       | 2.17 | 25       | 2.25 | 29      | 4.37  | 13     | 1.56 |

| SN BN-L JXhg | 21      | 2.41 | 28       | 2.29 | 27       | 2.38 | 17      | 3.92  | 14     | 1.57 |

| SN Best JXhg | 22      | 2.45 | 27       | 2.29 | 28       | 2.41 | 22      | 4.24  | 9      | 1.54 |

| IS Def       | 23      | 2.45 | 22       | 2.13 | 22       | 2.21 | 19      | 4.14  | 20     | 1.84 |

| SN BN-P JXhg | 24      | 2.49 | 29       | 2.32 | 29       | 2.45 | 20      | 4.23  | 17     | 1.60 |

| SN BN-R JXhg | 25      | 2.53 | 30       | 2.38 | 30       | 2.50 | 18      | 4.10  | 19     | 1.68 |

| IS POp       | 26      | 2.62 | 26       | 2.24 | 26       | 2.32 | 21      | 4.23  | 22     | 2.13 |

| SN Best Tie  | 27      | 2.83 | 18       | 2.05 | 19       | 2.16 | 28      | 4.34  | 30     | 3.32 |

| SN BN-R Tie  | 28      | 2.86 | 25       | 2.20 | 23       | 2.22 | 25      | 4.31  | 29     | 3.17 |

| SN BN-L Tie  | 29      | 2.86 | 21       | 2.09 | 24       | 2.22 | 23      | 4.24  | 31     | 3.40 |

| SN BN-P Tie  | 30      | 2.93 | 20       | 2.08 | 20       | 2.17 | 24      | 4.25  | 32     | 3.85 |

| IS STL       | 31      | 3.02 | 31       | 2.46 | 31       | 2.59 | 31      | 5.09  | 26     | 2.59 |

| IS AIF       | 32      | 3.08 | 32       | 2.48 | 32       | 2.69 | 32      | 5.27  | 25     | 2.57 |

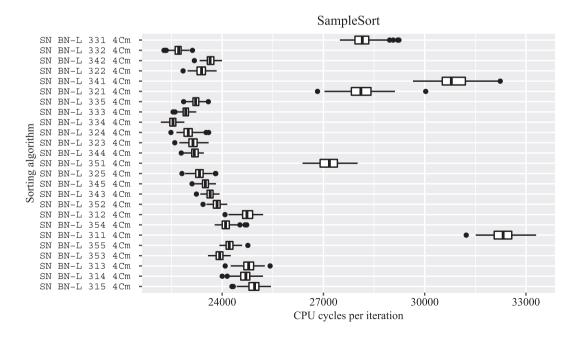

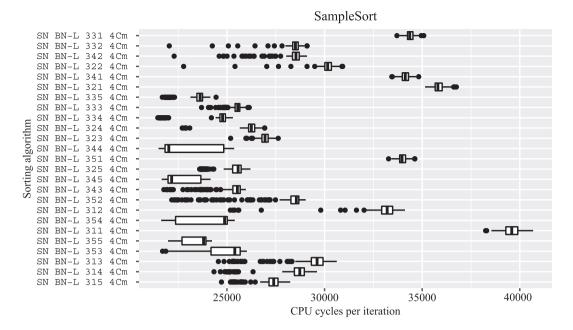

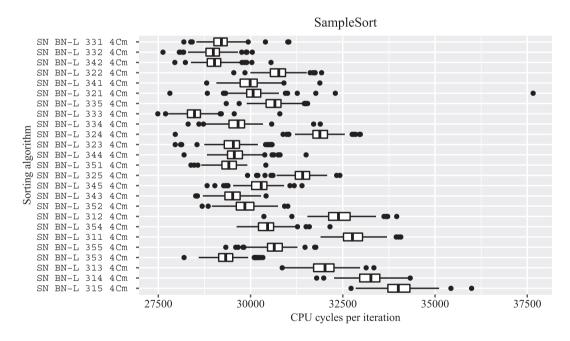

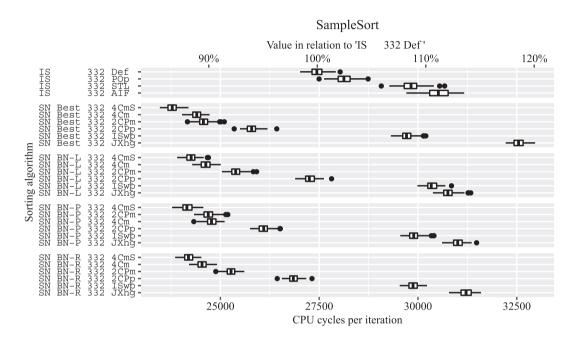

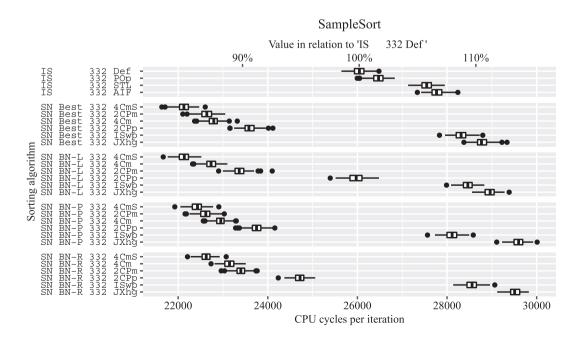

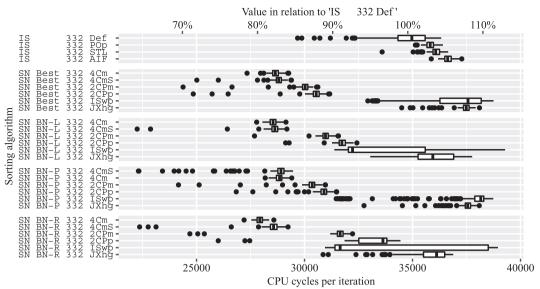

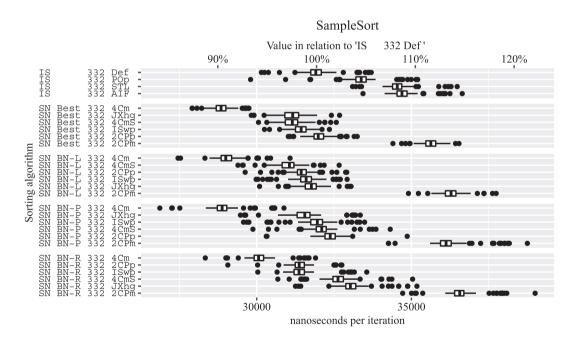

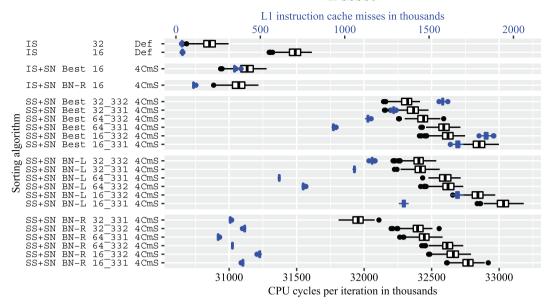

# 4.3 | Sorting many continuous sets of 2–16 items