# High-Voltage CMOS Active Pixel Sensor

# I. Peric, M. Benoit

To be published in "IEEE JOURNAL OF SOLID-STATE CIRCUITS"

March 2021

# Physics Department

# **Brookhaven National Laboratory**

# **U.S. Department of Energy**

USDOE Office of Science (SC), High Energy Physics (HEP) (SC-25)

Notice: This manuscript has been authored by employees of Brookhaven Science Associates, LLC under Contract No. DE-SC0012704 with the U.S. Department of Energy. The publisher by accepting the manuscript for publication acknowledges that the United States Government retains a non-exclusive, paid-up, irrevocable, world-wide license to publish or reproduce the published form of this manuscript, or allow others to do so, for United States Government purposes.

## **DISCLAIMER**

This report was prepared as an account of work sponsored by an agency of the United States Government. Neither the United States Government nor any agency thereof, nor any of their employees, nor any of their contractors, subcontractors, or their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or any third party's use or the results of such use of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise, does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government or any agency thereof or its contractors or subcontractors. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States Government or any agency thereof.

# High-Voltage CMOS Active Pixel Sensor

Ivan Perić<sup>®</sup>, Attilio Andreazza, Heiko Augustin, Marlon Barbero, Mathieu Benoit<sup>®</sup>, Raimon Casanova, *Member, IEEE*, Felix Ehrler, Giuseppe Iacobucci, Richard Leys, Annie Meneses Gonzalez, *Member, IEEE*, Patrick Pangaud<sup>®</sup>, Mridula Prathapan, Rudolf Schimassek, André Schöning, Eva Vilella Figueras, Alena Weber, Michele Weber, Winnie Wong, and Hui Zhang

Abstract—The high-voltage CMOS (HVCMOS) sensors are a novel type of CMOS active pixel sensors for ionizing particles that can be implemented in CMOS processes with deep n-well option. The pixel contains one sensor electrode formed with a deep n-well implanted in a p-type substrate. CMOS pixel electronics, embedded in shallow wells, are placed inside the deep n-well. By biasing the substrate with a high negative voltage and by the use of a lowly doped substrate, a depleted region depth of at least 30  $\mu m$  can be achieved. The electrons generated by a particle are collected by drift, which induces fast detectable signals. This publication presents a 4.2-cm² large HVCMOS pixel sensor implemented in a commercial 180-nm process on a lowly doped substrate and its characterization.

Index Terms—Active pixel sensors, ionizing radiation sensors, particle beam measurements, particle tracking, position-sensitive particle detector, radiation imaging, radiation monitoring, silicon radiation detectors, smart pixels.

Manuscript received September 20, 2020; revised December 11, 2020; accepted February 14, 2021. This article was approved by Associate Editor David Stoppa. This work was supported in part by the Federal Ministry of Education and Research (BMBF) under Grant 05H18VKRD1, in part by the Program Matter and Technology of Helmholtz Association of German Research Centers, in part by the Heidelberg Karlsruhe Strategic Partnership HeiKA, and in part by the European Union's Horizon 2020 Research and Innovation Program under Grant 654168 (AIDA-2020). (Corresponding author: Ivan Perić.)

Ivan Perić, Felix Ehrler, Richard Leys, Rudolf Schimassek, and Hui Zhang are with the Institute for Data Processing and Electronics (IPE), Karlsruhe Institute of Technology (KIT), 76131 Karlsruhe, Germany (e-mail: ivan.peric@ kit.edu).

Attilio Andreazza is with the Dipartimento di Fisica, Università di Milano, 20133 Milan, Italy, and also with INFN, 20133 Milan, Italy.

Heiko Augustin, Annie Meneses Gonzalez, André Schöning, and Alena Weber are with the Physics Institute, University of Heidelberg, 69120 Heidelberg, Germany.

Marlon Barbero and Patrick Pangaud are with CNRS/IN2P3, CPPM, Aix-Marseille University, 13288 Marseille, France.

Mathieu Benoit was with the Department of Nuclear and Particle Physics (DPNC), University of Geneva, 1205 Geneva, Switzerland. He is now with the Brookhaven National Laboratory, New York, NY 11973 USA.

Raimon Casanova is with the Institut de Fisica d'Altes Energies (IFAE), 08193 Barcelona, Spain.

Giuseppe Iacobucci is with the Department of Nuclear and Particle Physics (DPNC), University of Geneva, 1205 Geneva, Switzerland.

Mridula Prathapan was with the Institute for Data Processing and Electronics (IPE), Karlsruhe Institute of Technology (KIT), 76131 Karlsruhe, Germany. She is now with IBM Research–Zurich, 8803 Rüschlikon, Switzerland.

Eva Vilella Figueras is with the Department of Physics, University of Liverpool, Liverpool L69 7ZE, U.K.

Michele Weber is with the Laboratory for High Energy Physics (LHEP), University of Bern, 3012 Bern, Switzerland.

Winnie Wong was with the Department of Nuclear and Particle Physics (DPNC), University of Geneva, 1205 Geneva, Switzerland. She is now with Mercury Systems, 1212 Lancy, Switzerland.

Color versions of one or more figures in this article are available at https://doi.org/10.1109/JSSC.2021.3061760.

Digital Object Identifier 10.1109/JSSC.2021.3061760

#### I. Introduction

THE described active pixel sensor is designed for detection of ionizing particles and measurement of their trajectories—particle tracking. The possible applications are experimental particle physics, medicine (particle therapy beam monitoring), gamma-ray astrophysics (sensor for a Compton camera), and electron microscopy. The described sensor is based on a novel pixel structure that can be produced in a standard CMOS triple-well process. The readout electronics is embedded inside the pixel electrode (n-well implanted in p-substrate) used to collect the electrons generated by traversing particles. In this way, the electronics is isolated from substrate and the substrate can be biased with a high voltage, which improves sensor properties such as signal amplitude, charge collection speed, or radiation tolerance. We refer to such a pixel diode as the active or "smart" diode. With this name, we emphasize that the cathode of the diode (n-well) contains active circuits and logic gates. The high-voltage CMOS (HVCMOS) sensors, based on smart diodes, may also be suitable for other applications, such as construction of fully depleted back-side illuminated optical sensors or fast sensors for time-of-flight measurements.

## A. Technical Requirements for Particle Tracking Sensors

Particle tracking can be performed by means of several layers of thin pixel sensors. Particles move through the layers and generate signals. In this way, 3-D coordinates of the tracks are recorded in order to reconstruct the particle trajectories. The most important technical requirements for particle tracking sensors are: small amount of material in the detector layers, low-power dissipation, high detection efficiency, radiation tolerance, good time resolution, and uniformly sensitive large detector area.

The amount of material should be minimized since thick and dense structures cause particles to scatter and deteriorate particle tracking accuracy. For the same reason, cooling structures should have as little material as possible. This puts constraints to sensor chip thickness and its power dissipation. On the other hand, since charged particles penetrate sensor and ionize semiconductor along their tracks, the amount of generated electron–hole pairs is proportional to track length within the sensing layer and thus roughly its thickness.

Particles of high energies damage the electronics and sensor by ionization (total ionizing dose (TID) damage) and by

0018-9200 © 2021 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See https://www.ieee.org/publications/rights/index.html for more information.

non-ionizing energy loss (NIEL) that leads to displacement of the silicon or dopant atoms [1]. The main damage mechanism in the case of TID is ionization in  $SiO_2$  that is used to isolate transistors from each other (field oxide). The use of guard rings and circular gate geometry can mitigate these effects.

Displacement of Si-atoms leads to interstitials and vacancies and generates localized energy levels in the bandgap that leads to several negative effects: a larger leakage current, more probable recombination and trapping, and change of the dopant density and type. Since different particles have different NIELs, we use the unit  $n_{\rm eq}/{\rm cm}^2$  to express the fluence of arbitrary particles that causes the same displacement damage as 1-MeV neutron/cm<sup>2</sup> in silicon. A sensor for particle tracking should be tolerant to the expected ionizing dose and displacement damage.

A depleted active sensor layer is desirable because the high electric field separates electrons from holes and makes them drift quickly toward the sensor electrodes. This improves time resolution and radiation tolerance. Since a larger depleted region leads to a larger signal, our goal was to increase the depleted layer depth as much as possible. This was achieved by the use of high reverse bias voltage and lowly doped substrate.

A high time resolution is desirable in order to be able to assign particle signals in different detector planes to a certain track by measuring time coincidence. A detector area with insensitive regions is in most cases not acceptable because it would lead to poor tracking efficiency. A pixel size in the order of 100  $\mu$ m is for many applications sufficient. The sensor area of modern silicon tracking detectors can be  $\approx 200 \text{ m}^2$  [2], [3].

Standard silicon-based technologies for particle tracking are strip- and hybrid-pixel detectors [1], [4]. They use customized passive sensors that are arrays of diodes on a lowly doped substrate. Often, a double-sided process is required since the substrate bias voltage is applied from the backside. In both cases, external readout chips are required. The sensor pixels of a hybrid pixel detector are connected to an external pixel-readout chip by bump bonds. A disadvantage of these detectors is the need for customized sensor technology. Further drawbacks are high cost and large amount of material in the case of hybrid pixel detectors and, in the case of strip sensors, the need for two sensor layers to achieve 2-D resolution and measurement ambiguities when the particle flux is high. Two layers are required because the long and narrow sensor segments—strips—provide only one coordinate of the particle hit.

# B. Development of CMOS and HVCMOS Sensors for Particle Tracking

The first monolithic active pixel sensors (MAPSs) for particle tracking implemented in a commercial CMOS technology have been presented in [5]. The MAPS used an undepleted low resistivity epitaxial layer as sensing volume. Signal electrons move by diffusion and get collected by a small n-well. The pixel electronics is made only with NMOS transistors. The MAPSs were sensitive to displacement damage and did not provide high time resolution because of slow charge collection and the used rolling-shutter readout.

The HVCMOS sensor structure has been for the first time described in [6]. After more than 30 small-size prototypes produced in several CMOS processes ranging from 65-nm CMOS to 350-nm HVCMOS (with pixel sizes down to 2.5  $\mu$ m) [7]–[10], the first monolithic HVCMOS sensor with a full reticle size matrix *ATLASpix3* has been designed. ATLASpix3 contains several novel circuits that are explained in this publication. The main project goal is to demonstrate that it is possible to construct a large detector layer for the new ATLAS Inner Tracker [2] with the HVCMOS sensors.

We would like to mention several published results that are relevant for ATLASpix3.

- Measurements of radiation tolerance of HVCMOS smart diode detectors with a similar structure as ATLASpix3 have been presented in [11] and [12].

- 2) Measurements of depleted layer thickness and charge signal with passive test diodes and the influence of displacement damage caused by protons and neutrons have been presented in [13]–[15]. The test diodes were implemented on different substrates in the resistivity range 20–1000 Ω·cm, some of them on the same 200-Ω·cm substrate as ATLASpix3. It was observed that radiation causes both removal of existing acceptors and introduction of new acceptor states, which has the effect that after fluence ~10<sup>15</sup> n<sub>eq</sub>/cm², all investigated substrates behave similarly. The 200-Ω·cm substrate showed the smallest changes in terms of resistivity and signal amplitude as a function of NIEL.

- 3) Sultan *et al.* [16] presented radiation-induced leakage current measurements.

- 4) A depletion depth of 166  $\mu$ m and a full depletion of the substrate have been achieved with an HVCMOS sensor described in [17].

The experience gained with these developments has been used to design ATLASpix3.

Also, the MAPS structure has been developed in the past decade. Based on the structure from [5], a series of MIMOSA sensors has been designed, such as MIMOSA26 and ULTI-MATE [18], [19]. Signal-to-noise ratio (SNR) and radiation tolerance have been improved by use of high-resistivity depleted epitaxial layer [20].

A deep p-well was introduced (quadruple well process) in isolated n-wells MAPS (INMAPS) [21], which allowed for the use of PMOS transistors in pixels and implementation of complex pixel electronics able to distinguish particle signals from noise. A sensor based on this structure ALPIDE has been developed for the tracking detector of ALICE experiment [22]. ALPIDE uses high-resistivity epitaxial layers (e.g., thickness 25  $\mu$ m and resistivity 8 k $\Omega$ ·cm), which are partially depleted by applying moderate substrate bias. Radiation tolerance was further improved by process modifications [23], which allowed for full depletion of the epitaxial layer. Radiation-hardened MAPS were proposed for application in ATLAS experiment [24].

Another particle pixel sensor structure with depleted sensing volume that is based on the commercial CMOS process is the SOI sensor [25], [26].

A CMOS sensor with fully depleted substrate has been presented in [27].

This article is organized into six sections. Section II describes the overall ATLASpix3 chip architecture. Section III describes the pixel structure and its components such as charge-sensitive amplifier (CSA) and comparator. Section IV describes the digital circuits of the chip. Section V presents the experimental results and Section VI summarizes the presented material.

## C. Technical Requirements for ATLASpix3

A detector for particle tracking should be thin, it should have certain spatial and time resolution and it should stay within specifications during the operating time, i.e., after exposure to a certain radiation dose and fluence. The required time resolution is application-dependent. For ATLAS, it is 25 ns [2]. This requirement originates from the working principle of the Large Hadron Collider. The particle bunches collide every 25 ns. The duration of one bunch collision is <1 ns. It is required that a sensor precisely assigns a hit to its particle bunch collision in order to ease the track reconstruction.

The front-end electronics of ATLASpix3 is based on a CSA and a comparator. The comparator provides a detection threshold. A small threshold improves detection efficiency and time resolution. The threshold is limited by noise since too low thresholds lead to a high noise hit rate. The minimum threshold also depends on the pixel-to-pixel threshold mismatch (dispersion). If the threshold distribution is wider, the threshold voltage, which is common for all pixels, must be set larger in order to assure that all pixels have their local thresholds above the temporal noise floor. Threshold dispersion can be reduced by use of DACs (threshold tuning) as will be discussed later.

Time resolution is limited by time walk (TW) caused by the variation of the signal. Because of time constants of the amplifier and comparator, signals with larger amplitudes cause faster response. Signals that are just above threshold lead to excessive delay. A certain ratio between minimum signal and threshold is required to keep TW below the required limit. This ratio can be estimated by simulations. For the amplifier in ATLASpix3, it is 2.06. This leads to the requirement

## S > 2.06 Th.

This requirement should hold for nearly all (e.g., 99%) signals and pixels. Table I summarizes the most important requirements for ATLASpix3.

## II. CHIP ARCHITECTURE

ATLASpix3 pixel detector is a system-on-chip that contains  $132 \times 372$  pixels of  $150~\mu m \times 50~\mu m$  size. The chip area is  $20.2~mm \times 21~mm$ . The chip is implemented in a 180-nm HVCMOS technology. To enhance signal amplitude, a p-type Czochralski substrate with resistivity in the range 200– $400~\Omega$ -cm has been used instead of the standard wafer. The only high-voltage device used is the high-voltage deep n-well designed to have a breakdown voltage of about 65 V with respect to the substrate potential. The used technology

TABLE I ATLASPIX3 SPECIFICATIONS

| Chip area/thickness   | 2 cm × 2 cm / 250 μm                                                                     |

|-----------------------|------------------------------------------------------------------------------------------|

| Pixel size            | 50 μm × 150 μm                                                                           |

| Detection efficiency  | 99% in 25 ns time window                                                                 |

| Noise rate per pixel  | 5 Hz – 40 Hz/pixel                                                                       |

| Power consumption     | <500 mW/cm <sup>2</sup> (preferably 150 mW/cm <sup>2</sup> )                             |

| Current consumption   | $<240 \text{ mA/cm}^2$                                                                   |

| Radiation doses       | $800 \text{ kGy TID } \& 1.5 \ 10^{15} \ \text{n}_{\text{eq}}/\text{cm}^2 \ \text{NIEL}$ |

| Operating temperature | - 25 °C (maximum ratings - 55 °C to +60 °C)                                              |

| Signal, Noise and     | S > 2.06 Th for 99% of signals and pixels                                                |

| threshold             |                                                                                          |

ATLASpix3 specifications.

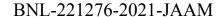

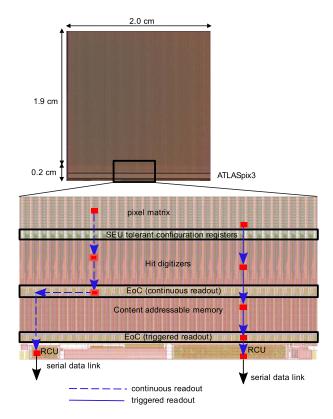

Fig. 1. Block diagram of ATLASpix3 chip.

offers seven metal layers. The top metal layer is thick and it was used for distribution of power and time-critical signals.

The main chip part is organized into 132 columns. One column consists of 372 pixels, 372 hit digitizers (HDs) with attached 80 content addressable memory (CAM) cells, and two end-of-column multiplexers (EoC muxs), as shown in Fig. 1. The chip periphery also contains the readout control unit (RCU), the clock generator based on phase-locked loop (PLL), configuration registers, DACs, linear regulators, and IO pads. There is an on-chip shunt and low dropout linear regulator that can be used to generate 1.8-V power supply voltage from a current and, in this way, allow for serial powering scheme [28]. The pixel matrix extends to three die borders making the chip three-side buttable. The distances from the sensor diodes (deep n-well) to the chip edges are 96  $\mu$ m (top), 184  $\mu$ m (left), and 147  $\mu$ m (right).

The pixels comprise analog circuits such as a CSA followed by a comparator. They detect particles traversing the sensor—particle hits. Particle HDs include digital circuits that receive the output signal of the pixel comparator and generate time, amplitude, and spatial information of the particle hit. The HDs

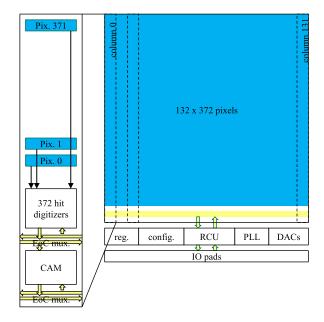

Fig. 2. Photograph of ATLASpix3. The chip area is 20.2 mm × 21 mm.

are spatially separated from the pixels and placed at the bottom edge of the chip. The layout of the HD was done full custom and optimized to be small (75  $\mu$ m  $\times$  4  $\mu$ m). The periphery of the chip occupies a tenth of the area occupied by the pixels.

The approach of separating the digital parts (HDs and CAM) from the analog pixel electronics has several advantages: the noise caused by digital activity is confined to the chip periphery where the digital parts are placed. The power consumption caused by clocked digital lines is smaller as no digital signals are distributed over the entire chip area. Pixel electronics is reduced to the minimum, which leads to smaller capacitance of the sensor electrode. Implementing of digital CMOS gates in pixels that are permanently clocked would lead to a crosstalk to the sensor electrodes. There are, however, a few disadvantages of this approach. A large number of lines are needed to connect the pixels to their HDs. There are, in our case, 49 104 traces each with a length of 1.8 cm and a pitch of  $0.8~\mu m$  (line spacing  $0.52~\mu m$ ) on the chip.

Fig. 2 shows the photograph of the ATLASpix3 chip.

#### III. PIXEL

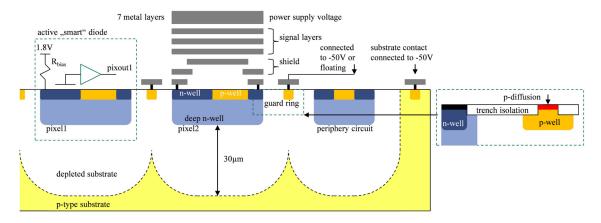

The drawing of the pixel cross section is shown in Fig. 4. The pixel electronics are embedded in shallow n- and p-wells. A deep n-well is used to isolate the shallow wells from the p-type substrate. The deep n-well also serves as the sensor electrode that collects electrons generated by ionization. The substrate around the deep n-well is depleted by applying a high negative voltage of about -50 V at the p-doped substrate contacts that are located at the periphery of the chip. The deep n-well is biased employing a circuit that acts as a resistance  $R_{\rm bias}$  connected between the positive power supply rail (1.8 V) and the n-well. The dc potential of the deep n-well is close to 1.8 V. For fast signals, the n-well behaves as a capacitance  $C_i$ . The main contributions to  $C_i$  are the deep n-well capacitance to the metal structures (simulated 120 fF), the n-well/p-well, and the n-well/p-substrate junction capacitances (90 and 20 fF) and the capacitances between the n-well and PMOS transistor electrodes. Simulated total  $C_i$  value is approximately 250 fF. The size of the deep n-well is 121  $\mu$ m  $\times$  21  $\mu$ m. There is

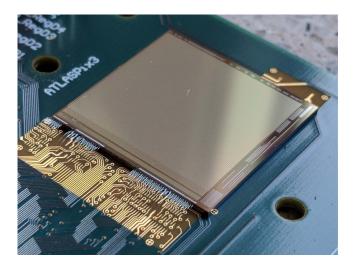

Fig. 3. Block diagram of the pixel. The main parts are the sensor diode, the ac-coupled CSA, and the comparator. Voltages BL and TH are generated at the chip periphery.

a guard ring formed with p-well, p-diffusion, and metal 1 between the deep n-wells of neighboring pixels.

The block diagram of the pixel is shown in Fig. 3. The main parts are the sensor diode, the ac-coupled CSA, and the comparator. The negative signal charge, which is collected by the n-well, is amplified by the CSA. The comparator compares the positive amplifier output signal to a threshold. The comparator output signals are transmitted to the HDs using long signal lines. These lines are implemented using three metal layers (metals 4-6), as shown in Fig. 4. Line extensions assure that all lines have nearly the same length (1.8 cm) and thus similar capacitance, independent of pixel position in the column. In this way, we equalize the rise times of the output signals. Two metal layers are available to shield the deep n-wells from the comparator signals. There is a circuit for threshold tuning (offset compensation) connected to the comparator. This circuit consists of a 3-bit differential current-steering DAC and SRAM cells to store the DAC value. A test signal circuit allows injection of a defined charge into the n-well by discharging metal-metal capacitor  $C_{\rm inj}$ . This makes electrical tests without ionizing particle sources possible. The test signal is produced at the chip periphery, and its amplitude can be varied by an on-chip DAC with 8 bits. The test signal is distributed to all pixels. It is possible to enable and disable the injection to each pixel individually.

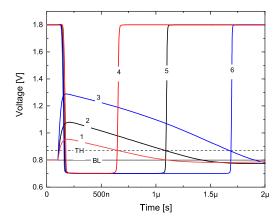

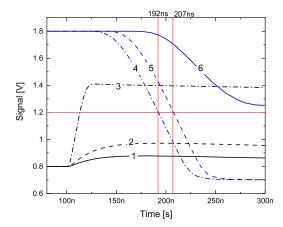

Simulated signals outac from Fig. 3 for the input signals of 2100 e<sup>-</sup>, 3500 e<sup>-</sup>, and 7000 e<sup>-</sup> and the corresponding comparator responses are shown in Fig. 5.

## A. Charge Sensitive Amplifier

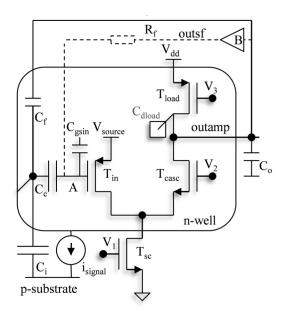

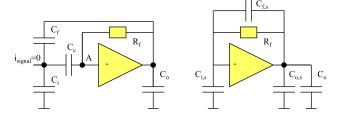

The schematic of the CSA is shown in Fig. 6. The CSA uses a folded cascode amplifier as active part. Since the gate of transistor  $T_{\rm in}$  (node A) has a different dc potential than the n-well, ac coupling  $C_c$  is used.  $C_c$  has been implemented as a PMOS transistor.

There is a capacitive coupling of every p-diffusion to the deep n-well due to their parasitic junction capacitances. In standard CMOS circuits with the n-well at a fixed potential, these capacitances would only introduce capacitive loads. In our case, the n-well is the input node of the amplifier

Fig. 4. Cross-sectional view shows two pixels and chip periphery. The pixel electronics are embedded in n- and p-wells. A deep n-well is used to isolate the shallow wells from the p-type substrate and serves as the sensor electrode.

Fig. 5. Simulated waveforms. Waveforms 1–3 are the amplifier responses (signals outac from Fig. 3) for input signal charge of  $2100~e^-$ ,  $3500~e^-$ , and  $7000~e^-$ , respectively. Waveforms 4–6 are the corresponding comparator output signals (outcomp).

and the parasitic capacitances cause feedback. The junction capacitance between the drain of  $T_{\rm load}$  and the n-well ( $C_{\rm dload}$ ) is important since  $T_{\rm load}$  drain (amplifier output) experiences large voltage variations.  $C_{\rm dload}$  is used as the capacitive feedback of CSA. We sum  $C_{\rm dload}$  and the parasitic capacitance of line outamp to n-well into the equivalent feedback capacitance  $C_f$ . The CSA includes also a resistive feedback circuit  $R_f$ , which will be explained in Section III-B.  $R_f$  is driven by an NMOS-based source follower B.  $C_o$  is the capacitance of the output node (outamp). Deep n-well is modeled with its capacitance  $C_i$  and the signal current source  $i_{\rm signal}$ .

If we consider only the short time scale, where the current through  $R_f$  can be neglected,  $C_c$  influences CSA solely through the reduction of the open-loop gain. It is caused by the voltage divider consisting of  $C_c$  and  $C_{\rm gs}$  of  $T_{\rm in}$  ( $C_{\rm gsin}$ ). If  $C_c$  is sufficiently large, the maximum output signal voltage is  $V_{\rm max} \approx -Q/C_f$ . Q is the negative input signal charge.

The CSA is affected by thermal and 1/f noise of its transistors and by shot noise of the sensor leakage current  $I_{\text{leak}}$  [29]. In the case of the not irradiated chip,  $I_{\text{leak}}$  is small ( $\sim$ 10 pA) and it does not contribute significantly to overall

Fig. 6. Schematic of the CSA. Voltages  $V_1$ – $V_3$  are generated at the chip periphery.  $V_{\rm dd}=1.8~{\rm V}$  and  $V_{\rm source}=1.2~{\rm V}$  are power supply voltages. On-chip regulator can be used to generate  $V_{\rm source}$ .

noise. In this case, the main noise source is the input transistor with its thermal noise. The contribution of  $T_{\rm in}$  to total noise simulated with the analog simulator is about 50%, followed by the noise contribution of  $T_{\rm sc}$  with 25%. Contributions of other devices are significantly smaller.

After lifetime fluence, we expect  $I_{\text{leak}}$  to increase to  $\sim 10 \text{ nA}$  at room temperature or  $\sim 1 \text{ nA}$  at the operational temperature of  $-25 \text{ }^{\circ}\text{C}$  [16].

#### B. Resistive Feedback Circuit

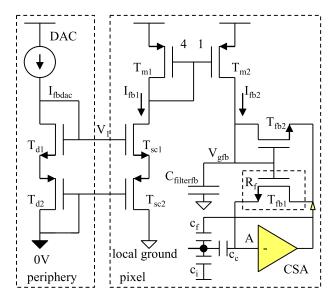

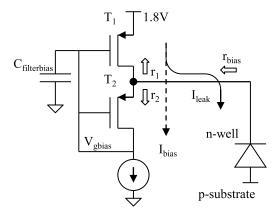

After signal amplification, the capacitances of the CSA should be discharged (reset) to the original voltages; otherwise, consecutive particle signals would cause the amplifier to saturate. This is achieved with device  $T_{\rm fb1}$  acting as a resistive feedback with equivalent resistance  $R_f$ , as shown in Fig. 7. The gate voltage for  $T_{\rm fb1}$  ( $V_{\rm gfb}$ ) is generated in each pixel

Fig. 7. Implementation of the resistive feedback circuit with bias network.

locally by the diode-connected transistor  $T_{\rm fb2}$  that is biased with current  $I_{\rm fb2}$ . A similar bias circuit was used in [30]. Current  $I_{\rm fb2}$  is small (60 pA) and  $T_{\rm fb1}$  and  $T_{\rm fb2}$  operate in weak inversion.  $C_{\rm filterfb}$  keeps  $V_{\rm gfb}$  at a constant level.  $T_{\rm fb1}$  behaves as a nearly linear resistance  $R_f = U_T/I_{\rm fb2}$  for signal amplitudes at the amplifier output smaller than the thermal voltage ( $U_T = kT/e \approx 25$  mV). For larger amplitudes, the current of  $T_{\rm fb1}$  saturates at the value  $I_{\rm fb2}$ . Capacitances are discharged with a nearly constant current until the voltage across  $T_{\rm fb1}$  decreases to  $U_T$ . Afterward, the discharge follows an exponential decay. To avoid signal loss, the discharge time should be sufficiently longer than the rise time of the amplifier (1). The formula for the discharge time will be derived in Section III-C.

#### C. Time Constants of the Output Signal

The difference between the ac-coupled CSA and the standard CSA is the usage of  $C_c$ . If  $C_c$  is short-circuited, the ac-coupled CSA takes the form of the standard one. The standard CSA has an impulse response described with the exponential function with two time constants: rise time  $T_r$  and discharge time  $T_f$ , [29]

$$T_r \approx \frac{C_{o,s}C_{i,s}}{C_{f,s}g_m}; T_f = R_f C_{f,s} \tag{1}$$

where  $g_m$  is the transconductance of  $T_{\rm in}$  and subscript s denotes the capacitances of the standard CSA. In order to estimate the time constants of the ac-coupled CSA, we can analyze its simplified schematics for the case  $I_{\rm signal}=0$ . By using the formulas for Y to  $\Delta$  conversion, we can rearrange the capacitances in the way that the ac-coupled CSA (for  $I_{\rm signal}=0$ ) takes the form of the standard CSA, as shown in Fig. 8. It holds

$$C_{i,s} = \frac{C_i C_c}{C_{sum}}; C_{f,s} = \frac{C_f C_c}{C_{sum}}; C_{o,s} = \frac{C_f C_i}{C_{sum}}; C_{sum} = C_i + C_f + C_c.$$

(2)

Fig. 8. Transformation of the capacitances of the ac-coupled CSA using of Y to  $\Delta$  conversion. The case  $I_{\text{signal}} = 0$  is considered. Left: original circuit. Right: transformed circuit.

TABLE II Simulated Values of the Amplifier Parameters

| 2.6 μA 250 fF 22 ns 1.6 fF 59μS 600 fF 0.63 μs 79 e | I <sub>bias</sub> | $C_{i}$ | $T_{\rm r}$ | $C_{\rm f}$ | $g_{m}$ | $C_c$  | T <sub>f</sub> | Ni   |

|-----------------------------------------------------|-------------------|---------|-------------|-------------|---------|--------|----------------|------|

|                                                     | 2.6 μΑ            | 250 fF  | 22 ns       | 1 6 tH      | 59µS    | 600 fF | 0.63 μs        | 79 e |

Simulated values of the amplifier parameters.

By substituting (2) into (1), we obtain the time constants for the ac-coupled CSA

$$T_r \approx \frac{C_o C_i}{C_f g_m}; T_f = R_f \frac{C_f C_c}{C_i + C_f + C_c}.$$

(3)

We assumed that  $C_c \gg C_{gsin}$  and  $C_o \gg C_{o,s}$ .

According to (3), the rise time is equal as in the case of the standard CSA. The discharge time is smaller if  $C_c < C_i$ .

As mentioned in Section III-B,  $R_f$  has been implemented using transistor  $T_{\text{fb1}}$ . For signals across  $T_{\text{fb1}}$  with amplitudes larger than  $U_T$ ,  $C_{f,s}$  is discharged with the constant current.

Table II summarizes the simulated amplifier parameter values.

$N_i$  is the input-referred rms value of temporal noise determined as the noise at the input of the comparator (line outac from Fig. 3) divided by the corresponding gain.

### D. Small Current Sources

The current  $I_{\rm fb1}$  is generated by means of a series of NMOS  $T_{\rm sc1}$  and PMOS  $T_{\rm sc2}$ , as can be seen in Fig. 7. The bias voltage  $V_1$  is generated at the chip periphery by a current steering DAC  $I_{\rm fbdac}$  and distributed over the pixel matrix. The use of PMOS transistor  $T_{\rm c2}$ , which operates in saturation, assures that the replicated bias current  $I_{\rm fb1}$  is independent of the local ground potential since the ground line is connected to the *drain* of  $T_{\rm c2}$ . If we used a single NMOS transistor to generate  $I_{\rm fb1}$ , a small voltage drop at its source would affect the current significantly. In our case, the voltage drops in the ground and power rails can be in the order of 50 mV.

Radiation-induced damage, particularly TID effects, may influence the current source and the pixel electronics. To make the pixel electronics more robust, we have implemented all NMOS transistors that operate in the subthreshold region with annular gates. The channel region of such transistors is not adjacent to the field oxide where positive space charge is generated by radiation. Radiation tolerance of transistors with annular gate has been investigated in [31].

The simulated  $I_{\rm fb1}$  current change caused by local ground variation of 50 mV is about 1%.

Fig. 9. Bias circuit.  $C_{filterbias}$  keeps  $V_{gbias}$  at a constant level.

We have simulated the influence of the additional PMOS transistor in the current source to the mismatch of currents. The simulated precision of the current source, defined as sigma over mean value of the Monte Carlo-sampled  $I_{\rm fb1}$  values for a constant voltage  $V_{\rm 1}$ , is 8.95%. As a comparison, a standard NMOS-based current source would have the precision of 7.50%.

Simulated  $I_{\rm fb2}$  for  $V_1=0$  is about 5.3 pA ( $I_{\rm fb1}=6.7$  pA) when cascaded current source is used. For the standard NMOS-based current source, we simulate  $I_{\rm fb2}=27$  pA ( $I_{\rm fb1}=86$  pA) for  $V_{\rm GS}=0$ .

#### E. n-Well Bias Circuit

Since the CSA is connected to the n-well only capacitively, it cannot define its dc potential. The purpose of the bias circuit is to hold the dc potential of the n-well in the pixel at nearly 1.8 V. The dynamic resistance of the bias circuit  $r_{\rm bias}$  should be high enough that the time constant caused by it is larger than the maximum discharge time of the amplifier. This leads to  $r_{\rm bias} > 10~{\rm M}\Omega$ . The difficulty is that the sensor leakage current  $I_{\rm leak}$  may increase to values  $\approx 10~{\rm nA}$  after radiation damage. Simpler circuits such as a diode-connected transistor would have a dynamic resistance  $\approx U_T/I_{\rm leak}$ , which is lower than the required one. A polysilicon resistor would be too large in layout. The schematic of the bias circuit we used is shown in Fig. 9.  $R_{\rm bias}$  can be decomposed to the contributions of  $T_1$  and  $T_2$

$$r_{\text{bias}} = r_1 || r_2 = r_{\text{ds}1} || \frac{1}{g_{\text{m}2}}$$

(4)

with  $r_{\rm ds1}$  being the drain-source resistance of  $T_1$  and  $g_{m2}$  the trans-conductance of  $T_2$ . || is the symbol for parallel connection. Since  $T_1$  is in saturation,  $r_{\rm ds1}$  is large. Since  $T_2$  is biased with a small current  $I_{\rm bias}$  of typically 10 pA,  $1/g_{m2}$  and  $r_{\rm bias}$  are large as well. The sensor leakage current flows through  $T_1$  and does not influence  $r_{\rm ds1}$  significantly. Since  $T_2$  conducts a current independent of sensor leakage, which leads to a constant  $g_m$ ,  $r_{\rm bias}$  remains nearly independent of leakage current. The current source  $I_{\rm bias}$  is implemented in the same way as  $I_{\rm fb}$  source in Fig. 7.

Fig. 10. Comparator with 3-bit DAC. Voltages  $V_1$ ,  $V_{\rm driver}$ ,  $V_{\rm gate}$ , and  $V_{\rm DAC}$  are generated at the chip periphery. Digital inputs of the DAC D and Db are stored in SRAM cells placed in the pixel. Transistors  $T_{\rm dacc}$  are introduced to reduce the capacitive load of nodes  $o_{p1}$  and  $o_{n1}$ .

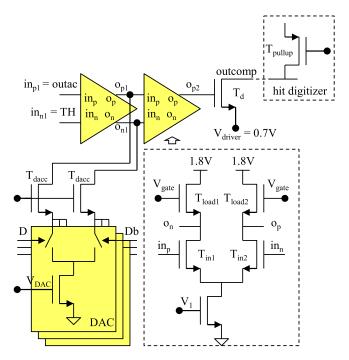

#### F. Comparator

The amplifier output and the non-inverting comparator input are ac coupled with  $C_{\rm ac}$ , as shown in Fig. 3. The dc voltage at the comparator input is defined by the resistance  $R_{\rm ac}$  connected to a voltage BL. The inverting comparator input is connected to a threshold voltage TH. The purpose of the ac coupling is to eliminate the influence of voltage drops, temperature, and low-frequency noise. Analog signals at the positive comparator input above the value TH-BL cause signals at the comparator output and are recorded as particle events in the digital periphery. The leading edge of the comparator output signal contains the time information regarding the particle hit. Due to saturation of the feedback current, the signal length is nearly linearly proportional to the pulse amplitude for signal amplitudes larger than one thermal voltage.

To avoid crosstalk to the n-well, the comparator uses only NMOS transistors since they are isolated from the deep n-well by its p-well. The schematic of the comparator is shown in Fig. 10. It is based on two differential stages with the diodeconnected NMOS transistors  $T_{load1}$  and  $T_{load2}$  as active load. The gain of one stage is defined by the  $g_m$  ratio of the load and input transistors  $(T_{in})$ . Two stages are used to provide sufficient gain. There is a driver transistor  $T_d$  attached to the comparator that generates a negative signal on the signal line outcomp when a particle signal is detected. A pull-up transistor  $T_{\text{pullup}}$ is placed in the HD. The source voltage for the driver transistor  $V_{\rm driver}$  is generated by an on-chip linear regulator. The gates of the load transistors are connected to a bias voltage  $V_{\text{gate}}$  that is about 300 mV larger than the main power supply voltage of 1.8 V, in order to increase the high output level at node  $o_p$ and assure low ON-resistance of  $T_d$ .  $V_{\text{gate}}$  must be provided

Fig. 11. Simulated TW. Waveforms 1–3 are the amplifier responses (signals outac) for input signal charge of Th $_i=1125~{\rm e^-}$ ,  $S_{\rm min}=2.312~{\rm e^-}$ , and  $S_{\rm max}=20~{\rm ke^-}$ , respectively. Waveforms 4–6 are the corresponding comparator output signals (outcomp). Signal Th $_i=1125~{\rm e^-}$  is the minimum signal that causes comparator response, the input-referred threshold. The TW between outcomp signals for input signals of  $S_{\rm min}=2.312~{\rm e^-}$  and  $S_{\rm max}=20~{\rm ke}$  is 15 ns. The ratio  $S_{\rm min}/{\rm Th}_i\approx2.06$ .

externally. The comparator dc-gain defined as  $V_{\rm op2}/V_{\rm inp1}$  was simulated to be 17. The gain of the full circuit that includes  $T_d$  and  $T_{\rm pullup}$  is  $V_{\rm outcomp}/V_{\rm inp1} \approx -590$ .

AC coupling between CSA and comparator prevents that baseline variations at the amplifier output influence threshold. According to the Monte Carlo simulations, the comparator offset causes the threshold voltage mismatch of rms 4.3 mV. The simulated CSA gain variation is rms 2.9%. These variations contribute to the measured input-referred threshold mismatch.

The outputs of the 3-bit differential current steering DAC are connected to  $o_n$  and  $o_p$  outputs of the first stage, as shown in Fig. 10. Nonequal DAC output currents introduce a programmable voltage offset. By adding a programmable offset, we act against threshold variations. The tune-DAC current step can be adjusted using a 6-bit bias-DAC placed at the chip periphery that generates voltage  $V_{\text{DAC}}$ . The simulated programmable offset range for the settings we used in the measurements is up to  $\sim$ 115 mV.

In order to verify the timing requirement from Table I, we have simulated the minimum ratio between signal and threshold that leads to a TW below 15 ns when the signal amplitude is increased from  $S_{\min}$  to 20 ke<sup>-</sup> ( $S_{\max}$ ); 15 ns has been chosen based on measurement results: The delay dispersion contributes with an additional 10 ns (6 sigma value) to the timing error that should be smaller than 25 ns. The simulated ratio is  $S_{\min}/\text{Th}_i \approx 2.06$ , as shown in Fig. 11 (Th<sub>i</sub> is the minimum signal that causes comparator response, the input-referred threshold). According to the simulation, the contributions of the comparator and the amplifier to TW are nearly equal.

#### IV. DIGITAL CIRCUITS

Digital circuits in ATLASpix3 perform several tasks; for instance, they digitize arrival time and amplitude of particle hits and they filter the hits using a trigger signal, format the data, and transmit it off the chip. Hit time is measured with a digital 10-bit time stamp (TS) signal.

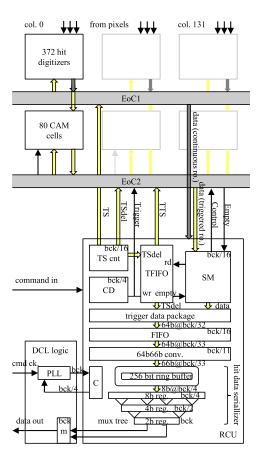

Fig. 12. Readout electronics in ATLASpix3 and signal flow in the case of continuous and triggered readout.

ATLASpix3 supports two readout modes, continuous and triggered readout, as shown in Fig. 12. In the case of continuous readout, all data are transmitted. Triggered readout is useful for data reduction. Many particle experiments (among them ATLAS) use trigger signals to filter data. These signals are generated by dedicated detectors (calorimeters and muon detectors) and their data processing electronics when a signal signature of a particle interaction of interest is recognized. Since data processing takes time, the trigger signal can only be generated with a relatively long and fixed trigger delay. As mentioned, in LHC, the particle collisions occur during particle bunch crossings every 25 ns. TS and trigger signals are synchronized with 25-ns clock that is in phase with the bunch crossing frequency. The trigger delay can be expressed as the number of clock periods and can be up to  $\sim 1000$  clock cycles. The trigger is distributed to the tracking detectors. These detectors keep all particle hit data for the duration of the trigger delay. A hit will be transmitted only if the difference between hit and trigger TS (TTS) equals the trigger delay. This assures selective readout of the data from the bunch crossings with particle interactions of interest.

As mentioned, the main chip part is organized into columns. One column consists of 372 pixels, 372 HDs, a pool of 80 CAM cells, and two EoC muxs. The RCU performs several tasks; it controls data readout and receives and performs commands, including the trigger command. The RCU generates three TS signals: the main TS, the delayed TS (TSdel), and the TTS.

TS is generated by a 10-bit counter with the nominal clock period of 25 ns. TS should be in phase with the

Fig. 13. Digital parts of ATLASpix3. Label bck/n indicates clock frequency of the corresponding block. Label mb@bck/n indicates that m bits are transferred at the frequency bck/n.

bunch crossings. TS is used to measure the arrival time of the particle signal. When a signal is detected, the current TS-value is stored as a part of the hit-data word. TSdel is equal to TS reduced by the counter delay setting (CDS). CDS is programmable and it should be equal to the trigger delay expressed as the number of 25-ns clock periods. TTS is the stored value of TSdel in the moment when the trigger signal is received. It is used for addressing the hit-data words from the memory.

Fig. 13 shows the block diagram of the digital parts.

The HD is an asynchronous digital circuit, designed as a full custom block. It comprises a hit flag (sr-latch), control logic, and dynamic memory cells. The HD works as follows. The hit flag is set when a pixel comparator signal is received. At its leading and trailing edge, TS value is stored. The pulse length can be reconstructed by using these TSs. The data from the HDs are transferred to EoC1 (continuous readout) or the CAM cells (triggered readout). The data word includes the stored TS values and the pixel address.

In the following, we will focus on the triggered readout. This readout mode has been used in the presented measurements. The CAM cell [32] comprises hit flags, control logic, memory cells, and two digital comparators. One comparator compares the hit TS with TSdel. Another comparator compares the hit TS with TTS and allows content addressing. The CAM cell performs the following tasks: Data from the HDs are

stored in the first empty cell. The output signal of the first comparator marks the clock cycle when the age of the hit equals CDS and, therefore, the trigger delay. If a trigger is received, the hit is selected for readout by setting a flag. Otherwise, the CAM cell is emptied. After a while, the CAM block may contain data that originate from many triggers. The second comparator is used for readout of these data words in the order their triggers arrived.

The RCU is the most complex digital part and it has been synthesized. The block diagram of the RCU is shown in Fig. 13.

Its function can be briefly described as follows. Upon receiving the trigger command, the RCU stores TSdel-value into the trigger FIFO (TFIFO) memory. This FIFO is necessary because sometimes a burst of triggers arrives which is processed with delay. The state machine of the RCU (SM) reads the entries from TFIFO and uses stored TSdel-numbers (referred to as TTS) for addressing CAM cells that contain the data of these triggers. The data are read out via EoC2-multiplexer. The SM groups the data in the trigger data packages. They are encoded according to the 64-to-66-bit conversion scheme described in [33]. The words are serialized by the block called hit-data serializer and sent off the chip at a rate of up to 1.28 Gbit/s. The RCU includes a command decoder (CD) as well. The CD receives commands made of 16-bit command, address, or data words at a rate of up to 160 Mbit/s. Customized encoding described in [34] is used.

ATLASpix3 has a clock generator based on a ring oscillator and a PLL. This full custom block is implemented with differential current-mode logic (DCL) gates. The clock generator receives an externally generated command clock and generates the fast bit clock (bck) used by the RCU, as shown in Fig. 13. The hit-data serializer operates in double data rate (DDR) mode. The last stages of the serializer use a binary tree structure made with  $2\rightarrow 1$  multiplexers (mux tree) and registers to perform  $8\rightarrow 1$  multiplexing. The last multiplexer (m) is placed outside the RCU and implemented with DCL gates. The RCU has several clock domains with the clock signals derived from bck by block C.

The chip contains several configuration registers. Every register cell contains a triple-redundant data latch followed by majority logic. Triple redundancy makes the register tolerant to single bit flips that can be caused by ionization (single event upset). The cells have an *auto-refresh* feature. When a logic detects a single flip in three data latches, the majority output is reloaded into the latches. These registers store settings for the DACs that generate bias, threshold, baseline, and injection voltages. The registers are also used to control the injection and the pixel RAM.

#### V. EXPERIMENTAL RESULTS

A modular characterization setup has been developed. The setup can be configured for single-chip tests or particle tracking operation with up to four planes. It is based on chip carrier PCBs, main PCB, FPGA development board, and PC. Lab measurements and measurements at high-energy beam facilities were performed.

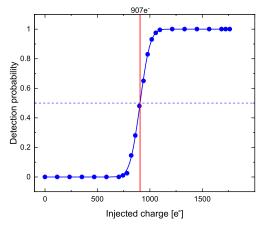

Fig. 14. Detection probability versus injected charge. The error function fit to data has mean value  $\mu=907~\rm e^-$  and sigma value  $\sigma=76.3~\rm e^-$ .

The main goal of the lab studies was to verify full functionality of the sensor. These measurements were performed by means of the test injection circuit based on  $C_{\rm inj}$  shown in Fig. 3. Capacitance  $C_{\rm inj}$  was estimated by using the parasitic capacitance extraction tool. It was additionally verified by measuring the output signal amplitudes when the sensor is irradiated with a  $^{55}$ Fe radioactive source that generates X-ray photons with known energies and comparing them with the injection response.

An S-curve measurement is a simple way to investigate both signal and noise, even of a large pixel matrix for every individual pixel. To obtain an S-curve, test signals of variable amplitudes are injected into a pixel and the detection probability is determined. The starting value of injected charge is chosen to be significantly above the threshold resulting in a probability of one. The injected charge is then gradually reduced and the probability is measured for every step until it reaches zero. Plotting probability over injected charge results in the S-curve, which can be fitted by a Gaussian error function. Triggered readout has been used. The trigger signal has been issued with a fixed delay with respect to the injection. Two parameters can be extracted from an S-curve. First, the input-referred detection threshold is the point of an S-curve with 50% detection probability. It depends on the signal amplification (amplifier gain) and the threshold value in the measured pixel. The second parameter is the transition width of the S-curve. It is a measure for the input-referred noise. The measured S-curve is shown in Fig. 14.

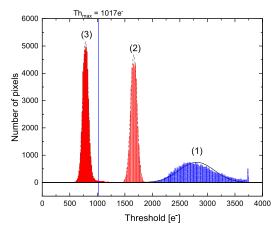

Fig. 15 shows the histograms of the measured pixel thresholds. Transistor mismatch renders the distribution Gaussian. The mean value of the distribution of untuned thresholds (histogram 1) is 2806 e<sup>-</sup> and the sigma value is 318 e<sup>-</sup>. For optimal operation with an acceptable noise rate, the detection threshold should be set as small as possible. Consequently, a reduced threshold distribution width improves the detector performance because a lower threshold can be set. As already mentioned, ATLASpix3 has a compensation mechanism installed; the local comparator threshold can be adjusted by a value stored in RAM for every pixel individually. This process called tuning is used to reduce threshold distribution width. S-curves based on test signal injections are a convenient

Fig. 15. Histograms of the threshold values for every pixel obtained from S-curve measurements with the test injection circuit. High-voltage bias was -50 V. Histogram 1 shows the untuned threshold values (all tune DACs at maximum setting). Histograms 2 and 3 show tuned thresholds with high and low target mean values, respectively. Gaussian fit to untuned thresholds has mean value  $\mu=2806$  e $^-$  and sigma value  $\sigma=318$  e $^-$ . Gaussian fits to tuned thresholds have  $\mu=1663$  e $^-/\mu=785$  e $^-$  and  $\sigma=58$  e $^-/\sigma=52$  e $^-$  for histograms 2 and 3, respectively.

way to tune the pixel matrix. Fig. 15 shows the histograms of tuned thresholds. Histograms 2 and 3 show tuned thresholds with high and low target mean values, respectively. The corresponding Gaussian fits have mean values  $\mu = 1663 \text{ e}^-/\mu = 785 \text{ e}^-$  and  $\sigma = 58 \text{ e}^-/\sigma = 52 \text{ e}^-$  for histograms 2 and 3, respectively.

The average noise value for all pixels in the matrix obtained by S-curve measurements is about 71 e<sup>-</sup> rms, which matches well with simulated 79 e<sup>-</sup>.

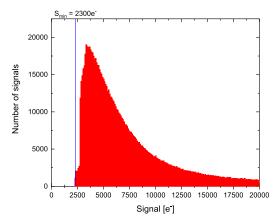

The signals produced by charged particles are Landaudistributed. The mean value of energy loss can be calculated from the Bethe equation [35]. The most probable value (MPV) of energy loss is below the mean. The energy loss depends on particle type, particle energy, and the thickness of the active detector volume. There is a minimum of energy loss for particles with a certain energy. Particles with this energy are referred to as minimum ionizing particles (MIPs). The MPV of the energy loss of MIPs is used as the standard signal for an SNR calculation. In our case, signal values were measured at the test beam facility at DESY, Hamburg, Germany, in the 3-GeV electron beam; 3-GeV electrons generate signals sufficiently close to the ones of MIPs. The signal spectrum can be measured by recording time over threshold (ToT), which can be translated to signal amplitudes. Fig. 16 shows the electron spectrum obtained by measuring ToT. The x-axis was calculated by using a calibration curve of ToT versus input signal obtained with the injection circuit. The MPV is about 3660 e<sup>-</sup>. The MPV signal-to-average-noise ratio is 52.

The depleted region depth estimated by TCAD simulations is about 32  $\mu m$  for -50-V bias voltage and  $300\text{-}\Omega\text{-cm}$  substrate resistivity.

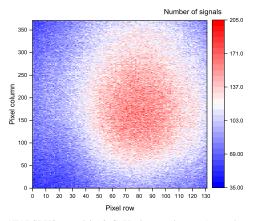

Fig. 17 shows the number of signals for every pixel during one measurement session. The position of the beam can be recognized.

A detailed study of time resolution is beyond the scope of this publication. It will require additional measurements at beam facilities. As mentioned in Section I-C, the time

Fig. 16. ATLASpix3 tested in 3-GeV electron beam. Signal spectrum obtained by measuring ToT and by calibrating ToT with the injection circuit. High-voltage bias was -50 V.

Fig. 17. ATALSPX3 tested in 3-GeV electron beam. A number of signals for every pixel during one measurement run. The position of the beam can be recognized. High-voltage bias was  $-50~\rm V$ .

resolution is to a large extent limited by TW, an effect caused by the fluctuation of the input signal, as shown in Fig. 16. Since the amplified signal has a finite rise time  $T_r$  (3), the threshold crossing occurs later for weaker signals.

TW can be estimated by measuring the relation of the injection pulse delay and generated TS value for different injection amplitudes. Average TW for all pixels between the injected signal of 3500 e<sup>-</sup>, which corresponds to the MPV of the spectrum in Fig. 16, and the signal of 7000 e<sup>-</sup> is about 7.5 ns. Tuned delay distribution for all pixels has a sigma of 1.7 ns. The average input-referred threshold during this measurement was about 980 e<sup>-</sup>. Reducing rise time constant  $T_r$  would diminish TW. A smaller  $T_r$  can be achieved by reduction of the n-well capacitance  $C_i$ . A large part of this capacitance is caused by the metal shield, which can be optimized in the next chip version. Nevertheless, the TW achieved in this measurement is within the value specified for ATLAS (<25 ns).

As mentioned in Section I-C, one figure of merit for the time resolution is the ratio between signal S and threshold Th: S/Th should be larger than 2.06 for 99% of signals and pixels. Instead of measuring the ratio S/Th for each pixel and signal, we will examine the input-referred threshold and signal distributions shown in Figs. 15 and 16, respectively.

The maximum tuned threshold for 99% pixels with smallest thresholds (99% quantile) is  $Th_{i,max} \approx 1.02$  ke (histogram 3, Fig. 15). The minimum signal from Fig. 16 is  $S_{min} = 2.30$  ke. The ratio  $S_{min}/Th_{i,max}$  is 2.25, which is greater than required 2.06.

The typical current consumption of the chip is 230 mA from 1.8 V and 130 mA from 1.2-V power supply voltage. The corresponding power dissipation is 570 mW. The measured substrate current at -50-V bias voltage was 60 nA for the whole chip. This value can increase significantly after irradiation.

#### A. Comparison With Measurements on Similar Sensors

This simulated value for depleted region depth roughly matches to the measurement results in [13]–[15]. These measurements have been performed on passive deep n-well in p-substrate diodes, some of them implemented in a 350 nm HVCMOS technology on the same substrate as used for ATLASpix3 (the substrates have been acquired by us and used by both foundries). Cavallaro *et al.* [13], Hiti *et al.* [14], and Anders *et al.* [15] showed radiation tolerance of the passive diodes. Benoit *et al.* [11] and Kiehn *et al.* [12] investigated the radiation tolerance of the active HVCMOS pixels. A smart diode detector implemented in a similar 180-nm process as ATLASpix3 provided by different foundries on the same substrate was found to be tolerant with the detection efficiency of 99.4% to radiation damage (ionizing and non-ionizing effects) up to fluences in the order of 10<sup>15</sup> n<sub>eq</sub>/cm<sup>2</sup>.

#### VI. CONCLUSION

ATLASpix3 is an active pixel sensor designed for detection and tracking of high-energy charged particles. It is a systemon-a-chip that consists of a matrix of  $132 \times 372$  pixels, each  $150 \ \mu \text{m} \times 50 \ \mu \text{m}$  in size and a periphery with complex digital circuits, voltage generators, and IO pads. The chip area is 20.2 mm  $\times$  21 mm. The pixels use deep n-well in p-substrate sensor diodes with the pixel electronics embedded in the deep n-wells. The diodes are depleted by biasing the substrate with a negative voltage of typically -50 V with respect to the n-wells. ATLASpix3 has been implemented in a 180-nm HVCMOS process and produced within an engineering run. Lowly doped (high resistivity) substrates of 200–400  $\Omega$ ·cm have been used. The use of high-voltage and high-resistivity substrates leads to a depleted region depth of at least 30  $\mu$ m. The design was described and measurements presented. The chip was tested by means of electrical signals and at a high-energy electron beam facility. SNR of > 50 was measured when electrons of 3 GeV are detected. Input-referred threshold distribution can be tuned down to  $\sigma \approx 58 \text{ e}^-$  and the average input-referred noise rms is 71 e<sup>-</sup>.

#### REFERENCES

- F. Hartmann, Evolution of Silicon Sensor Technology in Particle Physics (Springer Tracts in Modern Physics), vol. 275. 2017, pp. 1–372, doi: 10.1007/978-3-319-64436-3.

- [2] ATLAS Collaboration, "Technical design report for the ATLAS inner tracker pixel detector," CERN, Geneva, Switzerland, Tech. Rep. CERN-LHCC-2017-005, ATLAS-TDR-025, 2017. [Online]. Available: http://cds.cern.ch/record/2257755

- [3] CMS Collaboration, "The phase-2 upgrade of the CMS tracker—Technical design report," CERN, Geneva, Switzerland, Tech. Rep. CERN-LHCC-2017-009, CMS-TDR-014, 2017. [Online]. Available: https://cds.cern.ch/record/2272264

- [4] H. Spieler, Semiconductor Detector Systems. Oxford, U.K.: Oxford Univ. Press, 2005, doi: 10.1093/acprof:oso/9780198527848.001.0001.

- [5] W. Dulinski et al., "Particle tracking using CMOS monolithic active pixel sensor," Nucl. Instrum. Methods Phys. Res. A, Accel. Spectrom. Detect. Assoc. Equip., vol. 465, pp. 120–124, Jun. 2001, doi: 10.1016/S0168-9002(01)00368-0.

- [6] I. Perià, "A novel monolithic pixelated particle detector implemented in high-voltage CMOS technology," *Nucl. Instrum. Methods Phys. Res. A, Accel. Spectrom. Detect. Assoc. Equip.*, vol. 582, no. 3, pp. 876–885, Dec. 2007, doi: 10.1016/j.nima.2007.07.115.

- [7] I. Peric, "Active pixel sensors in high-voltage CMOS technologies for ATLAS," J. Instrum., vol. 7, Aug. 2012, Art. no. C08002, doi: 10.1088/1748-0221/7/08/C08002.

- [8] I. Periá et al., "High-voltage pixel detectors in commercial CMOS technologies for ATLAS, CLIC and Mu3e experiments," Nucl. Instrum. Methods Phys. Res. A, Accel. Spectrom. Detect. Assoc. Equip., vol. 731, pp. 131–136, Dec. 2013, doi: 10.1016/j.nima.2013.05.006.

- [9] R. Blanco et al., "HVCMOS monolithic sensors for the high luminosity upgrade of ATLAS experiment," J. Instrum., vol. 12, no. 4, Apr. 2017, Art. no. C04001, doi: 10.1088/1748-0221/12/04/C04001.

- [10] I. Periá et al., "A high-voltage pixel sensor for the ATLAS upgrade," Nucl. Instrum. Methods Phys. Res. A, Accel. Spectrom. Detect. Assoc. Equip., vol. 924, pp. 99–103, Apr. 2019, doi: 10.1016/j.nima.2018.06.060.

- [11] M. Benoit et al., "Testbeam results of irradiated AMS H18 HV-CMOS pixel sensor prototypes," J. Instrum., vol. 13, no. 2, Feb. 2018, Art. no. P02011, doi: 10.1088/1748-0221/13/02/P02011.

- [12] M. Kiehn et al., "Performance of the ATLASPix1 pixel sensor prototype in AMS aH18 CMOS technology for the ATLAS ITk upgrade," J. Instrum., vol. 14, no. 8, Aug. 2019, Art. no. C08013, doi: 10.1088/1748-0221/14/08/C08013.

- [13] E. Cavallaro et al., "Studies of irradiated AMS H35 CMOS detectors for the ATLAS tracker upgrade," J. Instrum., vol. 12, no. 1, Jan. 2017, Art. no. C01074, doi: 10.1088/1748-0221/12/01/C01074.

- [14] B. Hiti et al., "Charge collection in irradiated HV-CMOS detectors," Nucl. Instrum. Methods Phys. Res. A, Accel. Spectrom. Detect. Assoc. Equip., vol. 924, pp. 214–218, Apr. 2019, doi: 10.1016/j. nima.2018.07.022.

- [15] J. Anders et al., "Charge collection characterisation with the transient current technique of the AMS H35DEMO CMOS detector after proton irradiation," J. Instrum., vol. 13, no. 10, Oct. 2018, Art. no. P10004, doi: 10.1088/1748-0221/13/10/P10004.

- [16] D. Sultan et al., "Electrical characterization of AMS aH18 HV-CMOS after neutrons and protons irradiation," J. Instrum., vol. 14, no. 05, May 2019, Art. no. C05003, doi: 10.1088/1748-0221/14/05/C05003.

- [17] T. Hirono et al., "CMOS pixel sensors on high resistive substrate for high-rate, high-radiation environments," Nucl. Instrum. Methods Phys. Res. A, Accel. Spectrom. Detect. Assoc. Equip., vol. 831, pp. 94–98, Sep. 2016, doi: 10.1016/j.nima.2016.01.088.

- [18] C. Hu-Guo et al., "First reticule size MAPS with digital output and integrated zero suppression for the EUDET-JRA1 beam telescope," Nucl. Instrum. Methods Phys. Res. A, Accel. Spectrom. Detect. Assoc. Equip., vol. 623, no. 1, pp. 480–482, Nov. 2010, doi: 10.1016/j.nima.2010.03.043.

- [19] I. Valin et al., "A reticle size CMOS pixel sensor dedicated to the STAR HFT," J. Instrum., vol. 7, no. 1, Jan. 2012, Art. no. C01102, doi: 10.1088/1748-0221/7/01/C01102.

- [20] A. Dorokhov et al., "Improved radiation tolerance of MAPS using a depleted epitaxial layer," Nucl. Instrum. Methods Phys. Res. A, Accel. Spectrom. Detect. Assoc. Equip., vol. 624, no. 2, pp. 432–436, Dec. 2010, doi: 10.1016/j.nima.2010.03.124.

- [21] J. Ballin et al., "Monolithic active pixel sensors (MAPS) in a quadruple well technology for nearly 100% fill factor and full CMOS pixels," Sensors, vol. 8, no. 9, pp. 5336–5351, Sep. 2008, doi: 10.3390/s8095336.

- [22] G. Aglieri Rinella, "The ALPIDE pixel sensor chip for the upgrade of the ALICE inner tracking system," Nucl. Instrum. Methods Phys. Res. A, Accel. Spectrom. Detect. Assoc. Equip., vol. 845, pp. 583–587, Feb. 2017, doi: 10.1016/j.nima.2016.05.016.

- [23] W. Snoeys et al., "A process modification for CMOS monolithic active pixel sensors for enhanced depletion, timing performance and radiation tolerance," Nucl. Instrum. Methods Phys. Res. A, Accel. Spectrom. Detect. Assoc. Equip., vol. 871, pp. 90–96, Sep. 2017, doi: 10.1016/j.nima.2017.07.046.

- [24] R. Cardella et al., "MALTA: An asynchronous readout CMOS monolithic pixel detector for the ATLAS high-luminosity upgrade," J. Instrum., vol. 14, no. 6, Jun. 2019, Art. no. C06019, doi: 10.1088/1748-0221/14/06/c06019.

- [25] J. Marczewski et al., "Monolithic silicon pixel detectors in SOI technology," Nucl. Instrum. Methods Phys. Res. A, Accel. Spectrom. Detect. Assoc. Equip., vol. 549, nos. 1–3, pp. 112–116, Sep. 2005, doi: 10.1016/j.nima.2005.04.035.

- [26] Y. Arai et al., "Development of SOI pixel process technology," Nucl. Instrum. Methods Phys. Res. A, Accel. Spectrom. Detect. Assoc. Equip., vol. 636, no. 1, pp. S31–S36, Apr. 2011, doi: 10.1016/j.nima.2010. 04.081.

- [27] K. Stefanov, A. Clarke, J. Ivory, and A. Holland, "Design and performance of a pinned photodiode CMOS image sensor using reverse substrate bias," *Sensors*, vol. 18, no. 2, p. 118, Jan. 2018, doi: 10.3390/s18010118.

- [28] T. Stockmanns et al., "Serial powering of pixel modules," Nucl. Instrum. Methods Phys. Res. A, Accel. Spectrom. Detect. Assoc. Equip., vol. 511, pp. 174–179, Sep. 2003, doi: 10.1016/S0168-9002(03)01787-X.

- [29] P. Fischer et al., "The front-end electronics," in Pixel Detectors Particle Acceleration and Detection. Berlin, Germany: Springer, 2006, p. 171, doi: 10.1007/3-540-28333-1 3.

- [30] L. Blanquart et al., "Pixel analog cells prototypes for ATLAS in DMILL technology," Nucl. Instrum. Methods Phys. Res. A, Accel. Spectrom. Detect. Assoc. Equip., vol. 395, pp. 313–317, Jun. 1997, doi: 10.1016/S0168-9002(96)01238-7.

- [31] G. Anelli et al., "Radiation tolerant VLSI circuits in standard deep submicron CMOS technologies for the LHC experiments: Practical design aspects," *IEEE Trans. Nucl. Sci.*, vol. 46, no. 6, pp. 1690–1696, Sep. 1999, doi: 10.1109/23.819140.

- [32] M. Prathapan et al., "SISSA: ATLASpix3: A high voltage CMOS sensor chip designed for ATLAS Inner Tracker," in Proc. Sci. Conf., Santiago de Compostela, Spain, vol. 370, Sep. 2019, pp. 2–6, doi: 10.22323/1.370.0010.

- [33] (2014). Aurora 64B/66B Protocol Specification, SP011 (v1.3). [Online]. Available: https://www.xilinx.com/support/documentation/ip\_documentation/aurora\_64b66b\_protocol\_spec\_sp011.pdf

- [34] (2019). The RD53A Integrated Circuit. [Online]. Available: https://cds.cern.ch/record/2287593

- [35] D. E. Groom and S. R. Klein, "Passage of particles through matter," Eur. Phys. J. C, vol. 15, nos. 1–4, pp. 163–173, Mar. 2000, doi: 10.1007/BF02683419.

Ivan Perić was born in Bonn, Germany, in 1976. He received the Diploma degree in electrical engineering from the University of Belgrade, Belgrade, Serbia, in 2000, the Ph.D. degree in physics from the University of Bonn, Bonn, in 2004, and the Habilitation degree from the University of Heidelberg, Heidelberg, Germany, in 2010.

From 2004 to 2006, he was a Post-Doctoral Researcher with the University of Mannheim, Mannheim, Germany. From 2006 to 2014, he was with the University of Heidelberg. Since 2014,

he has been a Full Professor with the Department of Electrical Engineering and Information Technology (ETIT), Karlsruhe Institute of Technology (KIT), Karlsruhe, Germany. He teaches courses on analog and digital integrated circuit design. He is currently the Deputy Director of the Institute for Data Processing and Electronics (IPE) and he leads the ASIC and Detector Laboratory (ADL). He is member of several particle physics collaborations where he contributes to the detector development. He is the author or the coauthor of two book chapters, more than 150 articles, and one patent. His research interests include the development of novel integrated circuits and silicon sensors, semiconductor device modeling, particle physics, astrophysics, and medical imaging.

**Attilio Andreazza** was born in Milan, Italy, in 1967. He received the Ph.D. degree in physics from the University of Milan, Milan, in 1995.

He has been a fellow with CERN, Geneva, Switzerland, working in the DELPHI experiment at LEP, and a Research Associate with the University of Bonn, Bonn, Germany, before going back to the Particle Physics Group, University of Milan, in 2000. Since then he has been a member of the ATLAS experiment at the LHC. He is currently a Full Professor with the Department of Physics,

University of Milan, and the Istituto Nazionale di Fisica Nucleare, Milan. One of his main research topics is the development of highly segmented tracking detectors, for application in particle physics experiments.

Raimon Casanova (Member, IEEE) received the B.Sc. degree in physics, the B.Sc. degree in electronics engineering, the M.Sc. degree in electronics engineering, and the Ph.D. degree in physics from the University of Barcelona, Barcelona, Spain, in 2001, 2002, 2007, and 2010, respectively.

He held a post-doctoral position at the SIC Group, Department of Electronics, University of Barcelona, until 2014 when he joined IFAE.

He is currently working on the microelectronic design for particle detectors. Since 2018, he has been

teaching courses on electronics at the Universitat Autonoma de Barcelona, Barcelona. He has authored or coauthored more than 60 publications in journals and international conferences. His research interests are focused on monolithic pixel detectors for high-energy physics and X-ray and APDs for biomedical applications.

Heiko Augustin received the B.Sc. degree in physics and the M.Sc. degree from the University of Heidelberg, Heidelberg, Germany, in 2012 and 2014, respectively, where he is currently pursuing the Ph.D. degree with a focus on the development of a High Voltage Monolithic Active Pixel Sensors (HV-MAPS) for the Mu3e experiment.

He is involved in the development and characterization of HV-MAPS for the application in particle physics experiments at the high-energy and high-intensity frontier.

Felix Ehrler was born in Künzelsau, Germany, in 1988. He received the B.Sc. and M.Sc. degrees in physics from the Karlsruhe Institute of Technology (KIT), Karlsruhe, Germany, in 2012 and 2015, respectively, where he is currently pursuing the Ph.D. degree with the ASIC and Detector Laboratory (ADL).

From 2015 to 2020, he was a Research Assistant with ASIC and Detector Laboratory (ADL), KIT. He is the author or the coauthor of more than 30 articles. He is a member of or works on the

following projects: High-Luminosity Upgrade of ATLAS ITk, CLICdp, Belle II VXD, and KATRIN. He is also a member of the Karlsruhe School of Elementary Particle and Astroparticle Physics (KSETA). His research interests include HVCMOS sensor development and their characterization, comprising development of hardware, firmware and software, and data analysis.

Marlon Barbero was born in Paris, France, in 1973. He received the Ph.D. degree in physics from the University of Basel, Basel, Switzerland, and the Paul Scherrer Institute, Villigen, Switzerland, in 2003, with a focus on the pixel detector for the CMS experiment, CERN, Geneva, Switzerland, and attached electronics.

From 2003 to 2006, he held a post-doctoral position in HI, USA, working on the Belle experiment (KEK-B, Japan). He then became an Assistant Professor at the University of Bonn, Bonn, Germany,

working on the ATLAS pixel detector (CERN), a topic that he has pursued while becoming a Full Professor at Aix-Marseille University, Marseille, France, in 2012. He is currently the Head of the ATLAS Pixel Detector Team, Centre de Physique des Particules de Marseille (CPPM). His research interests are mostly high-energy physics, particle physics silicon-based novel detectors, electronics, and radiation effects in electronics.

**Giuseppe Iacobucci** was born in San Valentino, Abruzzo Citeriore, Italy, in 1960. He graduated in physics at the University of Bologna, Bologna, Italy, in 1985

From 1987 to 2010, he was a Researcher with the Section of INFN, Bologna. Since 2011, he has been a Full Professor with the University of Geneva, Geneva, Switzerland, where he directed the Department of Particle Physics and is currently the President of the Physics Section. He is a particle physicist. After a thesis in hadronic interactions at

the CERN ISR, Geneva, he worked in electron–proton collisions at the HERA collider of DESY, Hamburg, Germany. He is a member of the ATLAS and FASER experiments at the LHC of CERN, where he contributes to the silicon tracker detectors. Since 2013, his research group is working on monolithic silicon pixel detectors for particle-physics experiments. In 2015, he initiated research on monolithic sensors with SiGe Bi-CMOS frontend for sub-nanosecond time resolutions.

Mr. Iacobucci received the H2020 ERC Advanced Grant (the MONOLITH project) for his research in 2019.

**Mathieu Benoit** received the B.Sc. and master's degrees in physics from the University of Montreal, Montreal, QC, Canada, in 2006 and 2008, respectively, and the Ph.D. degree in high-energy physics from Université Paris-XI, Paris, France, in 2011

From 2011 to 2014, he was with CERN, Geneva, Switzerland, as a fellow. He was with the University of Geneva, Geneva, as a Senior Scientist from 2014 to 2020, working on the development of hybrid and monolithic pixel detectors for the CLIC and the

ATLAS experiment. In 2020, he joined the Brookhaven National Laboratory, New York, NY, USA, to work as an Associate Scientist, where his work focus on the development of high-speed electronics for data acquisition system for high-energy physics.

**Richard Leys** was born in Croix, France, in 1986. He received the M.S. degree in embedded systems engineering from the ECE University, Paris, France, in 2009, and the Ph.D. degree in computer science from the University of Heidelberg, Heidelberg, Germany, in 2015.

From 2009 to 2014, he worked on a highperformance computing networking ASIC. He then joined the ASIC and Detector Laboratory, Karlsruhe Institute of Technology (KIT), Karlsruhe, Germany. He currently works on mixed-signal particle sensor

detectors design as well as measurement systems.

Annie Meneses Gonzalez (Member, IEEE) was born in Havana, Cuba, in December 1992. She received the five-year Diploma degree in nuclear physics from the Higher Institute of Technologies and Applied Sciences (InSTEC), Havana, in 2015. She is currently pursuing the Ph.D. degree in natural sciences with the University of Heidelberg, Heidelberg, Germany.

From 2015 to 2017, she was a Junior Researcher with the Radiation Damage Laboratory, Center of Applied Technology and Nuclear Development

(CEADEN). Since 2018, she has been working at the Physikalisches Institut, University of Heidelberg. Her research interest includes the research and development for the development of HV-MAPS technologies through simulation and analysis of test beam data.

Patrick Pangaud was born in Lyon, France, in 1966. He received the master's degree in electronics engineering from CNAM, Lyon, in 1998.

Since the beginning of the 1990s, he has worked on the conception and construction of detectors, with special emphasis on the design of complex electronics systems. He mainly worked within international collaborations in experiments realized at CERN, Geneva, Switzerland, for the LHC: CMS calorimeter and micro-strip detectors, ATLAS pixel detector, and so on. He has also participated in

innovative experimental techniques for hybrid pixel detectors for imaging and biomedical applications. He has covered various roles of responsibility in several French national and international research and development projects, aimed at the conception of and/or at applying new experimental solutions. During the year 2010–2016, he was one of the founders of ImXPAD, La Ciotat, France, company spin-off, to develop X-Ray imaging solutions using hybrid pixels development. Since 2014, he has been leading the Electronics' Department, Centre de Physique des Particules de Marseille (CPPM), Marseille, France, and has participated in the new effort concerning the very promising monolithic CMOS sensor for HEP experiments.

Mridula Prathapan received the B.S. degree in electronics and communication engineering from the Cochin University of Science and Technology, Kochi, India, in 2010, the M.S. degree in VLSI design from the Vellore Institute of Technology, Vellore, India, in 2012, and the Ph.D. degree in electrical engineering from the Karlsruhe Institute of Technology (KIT), Karlsruhe, Germany, in 2020.

From 2012 to 2016, she worked as a Component Design Engineer at Intel Corporation, Bengaluru, India, where she developed timing and power char-

acterization methodology for memory compilers for SoC and mobile platforms. She was awarded a doctoral fellowship from the Karlsruhe School of Elementary Particle and Astroparticle Physics: Science and Technology (KSETA) in 2016, where she developed the readout circuitry for a novel radiation sensor. She joined IBM Research–Zurich, Rüschlikon, Switzerland, as a Post-Doctoral Researcher on circuit design for quantum computing in 2020. Her current research interests include data converter design for high-speed I/O links, cryogenic CMOS device characterization, and circuit design for qubit control and readout.

**Rudolf Schimassek** was born in Reutlingen, Germany, in 1991. He received the B.Sc. and M.Sc. degrees in physics from the Karlsruhe Institute of Technology (KIT), Karlsruhe, Germany, in 2014 and 2016, respectively.

Since 2017, he has been with the ASIC and Detector Laboratory, KIT, for his Ph.D. thesis, where he is working in the field of silicon detector development and characterization.

**André Schöning** was born in Hamburg, Germany, in 1968. He graduated in physics at DESY, Hamburg, and Hamburg University, Hamburg, in the field of particle physics in 1996.

As a fellow with CERN, Geneva, Switzerland, from 1997 to 1999, he was a Researcher at the OPAL experiment at the e+ e-collider LEP and a member of the LHCb collaboration. From 1999 to 2008, he was a Scientific Assistant with ETH Zürich, Zürich, Switzerland, and the University of Zurich, Zürich. The main research interest was the study of

electron–proton collisions at the HERA accelerator at DESY. Since 2009, he has been a Professor for experimental physics at the University of Heidelberg, Heidelberg, Germany. His research group is studying proton–proton collisions at the highest energies at the Large Hadron Collider, CERN, and contributing to the development and construction of the Mu3e experiment at the Paul Scherrer Institute, Geneva. Since 2011, the research group has also developing monolithic pixel sensors for the instrumentation of particle detectors.

**Eva Vilella Figueras** received the B.S. and M.S. degrees in electronic engineering and the Ph.D. degree in engineering and advanced technologies from the University of Barcelona, Barcelona, Spain, in 2009, 2010, and 2013, respectively.

In 2014, she joined the Department of Physics, University of Liverpool, Liverpool, U.K., as a Post-Doctoral Researcher. In 2019, she was awarded a U.K. Research and Innovation Future Leaders Fellowship and started her own Research and Development Group. She has authored or coauthored more

than 30 articles in peer-reviewed journals and given over 50 presentations in international conferences and workshops. She holds one patent in the field of image sensors. Her research interests focus on position-sensitive silicon sensors, in particular on highly performance high-voltage CMOS sensors for future experiments in physics and medical applications.