# Characterization and compact modeling of printed electrolyte-gated thin film transistors and circuits

Zur Erlangung des akademischen Grades eines

Doktors der Ingenieurwissenschaften (Dr.-Ing.)

von der KIT-Fakultät für Elektrotechnik und Informationstechnik des Karlsruher Instituts für Technologie (KIT)

genehmigte

Dissertation

von

### M.Sc. Xiaowei Feng

aus Shanghai, China

Tag der mündlichen Prüfung: 30.07.2021 Hauptreferent: Prof. Dr. rer. nat. Ulrich Lemmer 1. Korreferentin: Prof. Dr. rer. nat. Jasmin Aghassi-Hagmann

2. Korreferent: Prof. Dr. Mehdi Baradaran Tahoori

This document is licensed under a Creative Commons Attribution 4.0 International License (CC BY 4.0): https://creativecommons.org/licenses/by/4.0/deed.en

## **Acknowledgments**

I would like to sincerely thank my advisers, Prof. Jasmin Aghassi-Hagmann and Prof. Mehdi Tahoori, who continuously supported and encouraged me during my doctoral studies. I would also like to thank Prof. Ulrich Lemmer for acting as my first supervisor.

My biggest thank goes to Prof. Jasmin Aghassi-Hagmann for introducing me to the world of research. From her, I acquired most of the hard and soft skills during these four years of my Ph.D., which will be guiding me through life. Also, I am very thankful to Prof. Horst Hahn for the wonderful collaboration with his group.

I wish to show my appreciation to all my colleagues at the Karlsruhe Institute of Technology and the University of Applied Sciences Offenburg for their support. I wish to extend my special thanks to Dr. Christian Punckt for teaching me how to write and think scientifically. To Dr. Gabriel Cadilha Marques, I would like to thank him for inspiring new ideas and giving me guidance in the Lab. My thanks go also to Alexander Scholz, Dennis Weller, Surya Singaraju, Palak Gupta, Ahmet Turan Erozan and Farhan Rasheed for fruitful discussions.

Furthermore, I appreciate the assistance provided by undergraduate students Esha Jindal, Tongtong Fu and Hongrong Hu. I am also thankful to Ms. Siri Weiße and Ms. Iris Schröder-Piepka for their friendly support.

Words cannot express my gratitude to my family. Especially, I would like to my wife, Chang Zhang, for the endless support and encouragement. I owe so much thanks to my mother, Jie Ni, who is continuously supporting me throughout my life.

Finally, I would like to thank the Ministry of Science, Research, and Arts of the state of Baden Württemberg, Germany for their financial support to my research activities in the form of the MERAGEM scholarship as well as the German Federal Ministry of Education and Research (BMBF) through the project 2HORISONS.

### **Publication list**

#### **Journals**

- Feng, X., Singaraju, S. A., Hu, H., Marques, G. C., Fu, T., Baumgartner, P., Secker, D., Tahoori, M. B., and Aghassi-Hagmann, J. (2021).

Low-frequency Noise Characteristics of Inkjet-Printed Electrolytegated Thin-Film Transistors. *IEEE Electron Device Letters*, 42(6), 843-846.

- Feng, X., Scholz, A., Tahoori, M. B., and Aghassi-Hagmann, J. (2020). An Inkjet-Printed Full-Wave Rectifier for Low-Voltage Operation Using Electrolyte-Gated Indium-Oxide Thin-Film Transistors. *IEEE Transactions on Electron Devices*, 67(11), 4918-4923.

- Feng, X., Marques, G. C., Rasheed, F., Tahoori, M. B., and Aghassi-Hagmann, J. (2019). Nonquasi-Static Capacitance Modeling and Characterization for Printed Inorganic Electrolyte-Gated Transistors in Logic Gates. *IEEE Transactions on Electron Devices*, 66(12), 5272-5277.

- Feng, X., Punckt, C., Marques, G. C., Hefenbrock, M., Tahoori, M. B., and Aghassi-Hagmann, J. (2019). Impact of intrinsic capacitances on the dynamic performance of printed electrolyte-gated inorganic field effect transistors. *IEEE Transactions on Electron Devices*, 66(8), 3365-3370.

- Wang, Z., Cui, H., Li, S., Feng, X., ... and Levkin, P. (2021). A Facile Approach to Conductive Polymer Micro-electrodes for Flexible Electronics. ACS Applied Materials & Interfaces Manuscript, 13(18), 21661-21668.

- Ulianova, V., Rasheed, F., Bolat, S., Sevilla, G. T., Didenko, Y., Feng, X., ... and Aghassi-Hagmann, J. (2020). Fabrication, Characterization and Simulation of Sputtered Pt/In-Ga-Zn-O Schottky Diodes for Low-Frequency Half-Wave Rectifier Circuits. *IEEE Access*, 8, 111783-111790.

- Marques, G. C., Sukuramsyah, A. M., Rus, A. A., Bolat, S., Aribia, A., Feng, X., ... and Aghassi-Hagmann, J. (2019). Fabrication and Modeling of pn-Diodes Based on Inkjet Printed Oxide Semiconductors. *IEEE Electron Device Letters*, 41(1), 187-190.

- Cadilha Marques, G., Weller, D., Erozan, A. T., Feng, X., Tahoori, M., and Aghassi-Hagmann, J. (2019). Progress Report on "From Printed Electrolyte-Gated Metal-Oxide Devices to Circuits". Advanced Materials, 31(26), 1806483.

- Jeong, J., Marques, G. C., Feng, X., Boll, D., Singaraju, S. A., Aghassi-Hagmann, J., ... and Breitung, B. (2019). Ink-Jet Printable, Self-Assembled, and Chemically Crosslinked Ion-Gel as Electrolyte for Thin Film, Printable Transistors. *Advanced Materials Interfaces*, 6(21), 1901074.

### Workshops

Feng, X., Marques, G. C., Rasheed, F., Tahoori, M. B., and Aghassi-Hagmann, J. (2018). Analog Properties of Printed Electrolyte-Gated FETs based on Metal Oxide Semiconductors. 59. MPC Workshop, IEEE German Section Solid-State Circuit Society. Best Paper Award.

### **Conference contributions**

#### **Posters**

• Feng, X., Tahoori, M. B., and Aghassi-Hagmann, J. (2019). An Extended Meyer Capacitance Model of Inkjet-Printed Electrolytegated Inorganic Transistors. *Trade fair and conference for printed electronics (LOPEC)*.

### **Presentations**

- Feng, X., Scholz, A., Tahoori, M. B., and Aghassi-Hagmann, J. (2020). A printed rectifier based on inkjet-printed electrolyte-gated inorganic transistors. *Trade fair and conference for printed electronics (LOPEC)*.

- Feng, X., Lukosiunas, J., Strunk, K., ... and Aghassi-Hagmann, J. (2021). Process Design Kit for Printed Organic Electronics within an Integrated Sensor Platform. *Trade fair and conference for printed electronics (LOPEC)*.

### **Abstract**

The manufacturing of conventional electronics has become a highly complicated process, which requires intensive investment. In this context, printed electronics keeps attracting attention from both academia and industry. The primary reason is the simplification of the manufacturing process via additive printing technology such as ink-jet printing. Consequently, advantages are realized such as on-demand fabrication, minimal material waste and versatile choice of substrate materials. Central to the development of printed electronic circuits are printed transistors. Recently, metal oxide semiconductors such as indium oxide have become promising materials for the fabrication of printed transistors due to their high charge mobility. Furthermore, electrolyte-gating also provides benefits such as the low-voltage operation in sub-1 V regime due to the large gate capacitance provided by electrical double layers. This opens new possibilities to fabricate printed devices and circuits for niche applications.

To facilitate the design and fabrication of printed circuits, the development of compact models is necessary. However, most of the current works have focused on the study of the static behavior of transistors, while the in-depth understanding of other characteristics such as the dynamic or noise behavior is missing. To this end, the purpose of this work is the comprehensive study on capacitance and noise properties of inkjet-printed electrolyte-gated thin-film transistors (EGT) based on indium oxide semiconductors. Proper modeling approaches are also proposed to capture accurately the electrical behaviour, which can be further utilized to enable advanced analysis of digital, analog and mixed-signal circuits.

In this work, the capacitance of EGTs is characterized using voltagedependent impedance spectroscopy. Intrinsic and extrinsic effects are carefully separated by using de-embedding test structures. Also, a dedicated equivalent circuit model is established to offer accurate simulations of the measured frequency response of the gate impedance. Based on that, it is revealed that top-gated EGTs have the potential to reach operation frequency in the kHz regime with proper optimizations of materials and printing process. Furthermore, a Meyer-like model is proposed to accurately capture the capacitance-voltage characteristics of the lumped terminal capacitance. Both parasitic and nonquasi-static effects are considered. This further enables the AC and transient analysis of complex circuits in circuit simulators.

Following, the study of noise properties in the field of printed electronics is conducted. Low-frequency noise of EGTs is characterized using a reliable experimental setup. By examining measured noise spectra of the drain current at various gate voltages, the number fluctuation with correlated mobility fluctuation has been determined as the primary noise mechanism. Based on that, normalized flat-band voltage noise can be determined as the key performance metrics, which is only  $1.08\times10^{-7}~V^2~\mu\text{m}^2$ , significantly lower in comparison with other thin-film technologies, which are based on dielectric gating and semiconductors such as IZO and IGZO. A Plausible reason could be the large gate capacitance offered by the electrical double layers. This renders EGT technology useful for low-noise and sensitive applications such as sensor periphery circuits.

Last but not least, various circuit designs based on EGT technology are proposed, including basic digital circuits such as inverters and ring oscillators. Their performance metrics such as the propagation delay and power consumption are extensively characterized. Also, the first design of a printed full-wave rectifier is presented by using diode-connected EGTs, which features near-zero threshold voltage. As a consequence, the presented rectifier can effectively process input voltage with a small amplitude of 100 mV and a cut-off frequency of 300 Hz, which is particularly attractive for the application domain of energy harvesting. Additionally, the previously established capacitance models are verified on those circuits, which provide a satisfactory agreement between the simulation and measurement data.

## Zusammenfassung

Die Herstellung konventioneller Elektronik ist ein hochkomplexer Prozess, der hohe Kosten erfordert. In diesem Zusammenhang gewinne die gedruckte Elektronik sowohl in der Wissenschaft als auch in der Industrie eine erhöhte Aufmerksamkeit. Der Hauptgrund dafür ist die Vereinfachung des Herstellungsprozesses durch additive Drucktechnologien wie Inkjet-Druck. Dies hat Vorteile wie die bedarfsgerechte Herstellung und minimaler Materialverbrauch. Außerdem wird eine vielfältige Auswahl verschiedener Substratmaterialien ermöglicht. Im Zentrum der Entwicklung von Schaltungen auf Basis gedruckter Elektronik stehen gedruckte Transistoren. In letzter Zeit sind Metalloxidhalbleiter wie Indiumoxid aufgrund ihrer hohen Ladungsbeweglichkeit zu vielversprechenden Materialien für die Herstellung gedruckter elektronischer Bauelemente geworden. Darüber hinaus bietet der Elektrolyt-Gate-Ansatz aufgrund der großen Gate-Kapazität, die durch die elektrischen Doppelschichten bereitgestellt wird, auch die Vorteile, einen Niederspannungsbetrieb im Sub-1 V-Bereich zu erreichen. Dies eröffnet neue Möglichkeiten für die Herstellung gedruckter Bauteile und Schaltungen in Nischenanwendungen.

Um das Design und die Herstellung von gedruckten Schaltungen zu erleichtern, ist die Entwicklung kompakter Modelle erforderlich. Die meisten existierenden Arbeiten haben sich bisher auf die Untersuchung des statischen Verhaltens von Transistoren konzentriert. Hierbei wird das dynamische und das Rauschverhalten der Bauteile häufig vernachlässigt. Ziel dieser Arbeit ist es daher, die umfassende Untersuchung der Kapazitäts sowie Rauscheigenschaften Tintenstrahl-gedruckter Dünnschichttransistoren mit einem flüssig-prozessierbaren Feststoffelektrolyten als Isolator

(EGT) und einem Indiumoxid-Halbleiter als Kanalmaterial durchzuführen.. Es werden geeignete Modellierungsansätze vorgeschlagen, um das elektrische Verhalten genau zu erfassen. Dies ermöglicht eine erweiterte Analyse analoger, digitaler sowie gemischter analog-digitaler Schaltungen.

In dieser Arbeit wird die Kapazität von EGTs mittels spannungsabhängiger Impedanzspektroskopie charakterisiert. Intrinsische und extrinsische Effekte werden durch Verwendung von De-Embedding-Teststrukturen getrennt. Des Weiteren wird ein Ersatzschaltbild erstellt, um genaue Simulationen des gemessenen Frequenzgangs der Gate-Impedanz zu ermöglichen. Auf dieser Grundlage zeigt sich, dass Top-Gate EGTs das Potenzial haben, eine Schaltfrequenz im kHz-Bereich zu erreichen, wenn die Materialien und der Druckprozess weiter optimiert werden. Darüber hinaus wird ein Meyer-ähnliches Modell vorgeschlagen, um die Kapazitäts-Spannungs-Eigenschaften der Anschlusskapazität genau zu erfassen. Es werden sowohl parasitäre Kapazitäten als auch nicht-quasistatische Effekte berücksichtigt. Die resultierenden Modelle ermöglichen weitere AC- und transiente Simulationen komplexer Schaltungen in der EGT-Technologie.

Im Folgenden werden Untersuchungen zu den Rauscheigenschaften gedruckter EGTs durchgeführt. Das Niederfrequenzrauschen wird anhand eines eigens dafür optimierten Versuchsaufbaus charakterisiert. Durch Untersuchung der gemessenen Rauschspektren im Transistor-Drainstrom bei verschiedenen Gate-Spannungen wurde die Ladungsträgerschwankung mit korrelierter Mobilitätsschwankung als primärer Rauschmechanismus bestimmt. Auf dieser Grundlage kann das normalisierte Flachband-Spannungsrauschen als Hauptleistungsmetrik berechnet werden, was im Vergleich zu anderen Dünnschichttechnologien, die auf Dielektrika und Halbleitern wie IZO und IGZO basieren, einen erheblich niedrigeren Wert aufweist.. Ein plausibler Grund könnte die große Gate-Kapazität sein, die durch die elektrische Doppelschicht erzeugt wird. Daher eigenen sich gedruckte EGTs für beispielsweise rauscharme Anwendungen in der Sensorik.

Abschließend werden verschiedene Schaltungsdesigns vorgeschlagen, die auf EGT-Technologie basieren. Dies beinhaltet grundlegende digitale Schaltungen wie Inverter Strukturen und Ringoszillatoren. Ihre Leistungsmetriken, einschließlich der Gatterlaufzeit und dem Stromverbrauch, werden ausführlich charakterisiert. Des Weiteren wird das erste Design eines gedruckten Brückengleichrichters unter Verwendung von EGTs mit eine nahe-null-Volt-Schwellspannung in einer Dioden-Konfiguration vorgestellt. Der vorgestellte Gleichrichter ist in der Lage, Eingangsspannungen mit kleiner Amplitude von circa 100 mV effektiv zu verarbeiten. Dies ist besonders im Anwendungsbereich des Energy-Harvestings von Interesse. Zusätzlich werden die zuvor etablierten Kapazitätsmodelle auf diesen Schaltungen verifiziert. Ein Vergleich der Simulations- und Messdaten zeigt deren sehr gute Übereinstimmung und verifiziert die entwickelten Kapazitätsmodelle.

# **Contents**

| Ac  | know    | ledgments                               | 3  |

|-----|---------|-----------------------------------------|----|

| Pι  | ıblica  | ion list                                | 5  |

| Co  | nfere   | nce contributions                       | 7  |

| ΑĿ  | strac   | t e e e e e e e e e e e e e e e e e e e | 9  |

| Zu  | ısamn   | nenfassung                              | 11 |

| Lis | st of F | igures                                  | v  |

| Li  | st of T | ables                                   | ix |

| 1   | Intr    | oduction                                | 1  |

|     | 1.1     | Overview of Printed electronics         | 1  |

|     |         | 1.1.1 History                           | 1  |

|     |         | 1.1.2 Material aspect                   | 3  |

|     |         | 1.1.3 Application domains               | 4  |

|     | 1.2     | Motivation                              | 5  |

|     | 1.3     | Structure of this thesis                | 7  |

| 2   | Bacl    | ground                                  | 9  |

|     | 2.1     | MOS capacitor                           | 9  |

|     |         | 2.1.1 Operation modes                   | 9  |

|     |         | 2.1.2 C-V characteristics               | 12 |

|     | 2.2     | MOSFET                                  | 14 |

|   |      | 2.2.1    | I-V characteristics          | 15 |

|---|------|----------|------------------------------|----|

|   |      | 2.2.2    | C-V characteristics          | 17 |

|   |      | 2.2.3    | Noise characteristics        | 20 |

|   | 2.3  | Printe   | ed thin-film transistor      | 23 |

|   |      | 2.3.1    | Printing technology          | 24 |

|   |      | 2.3.2    | Metal oxide semiconductors   | 26 |

|   |      | 2.3.3    | Electrolyte-gating approach  | 28 |

|   | 2.4  | EGT t    | echnology                    | 31 |

|   |      | 2.4.1    | Fabrication                  | 32 |

|   |      | 2.4.2    | I-V modeling                 | 33 |

| 3 | Capa | acitance | e in EGTs                    | 35 |

|   | 3.1  | Backg    | ground                       | 35 |

|   | 3.2  |          | acterization method          | 36 |

|   |      | 3.2.1    | Impedance Spectroscopy       | 36 |

|   |      | 3.2.2    | Measurement Setup            | 38 |

|   | 3.3  | Dynai    | mic performance              | 40 |

|   |      | 3.3.1    | Experiment configuration     | 40 |

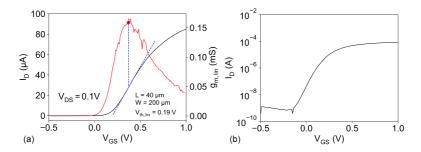

|   |      | 3.3.2    | Static I-V characteristics   | 42 |

|   |      | 3.3.3    | Capacitance characteristics  | 43 |

|   |      | 3.3.4    | Equivalent circuit models    | 46 |

|   |      | 3.3.5    | Parameter extraction         | 48 |

|   |      | 3.3.6    | Frequency response           | 52 |

|   | 3.4  | Comp     | pact capacitance modeling    | 55 |

|   |      | 3.4.1    | Experiment configuration     | 56 |

|   |      | 3.4.2    | Extrinsic capacitance        | 57 |

|   |      | 3.4.3    | Intrinsic capacitance        | 59 |

|   |      | 3.4.4    | Nonquasi-static effect       | 63 |

|   | 3.5  | Concl    | usion                        | 64 |

| 4 | Nois | e in EG1 | Ts .                         | 65 |

|   | 4.1  | Backg    | ground                       | 65 |

|   | 4.2  |          | er noise theory              | 66 |

|   |      | 4.2.1    | Carrier number fluctuation   | 66 |

|   |      | 422      | Carrier mobility fluctuation | 69 |

|     | 4.3    | Characterization method                   | 70  |

|-----|--------|-------------------------------------------|-----|

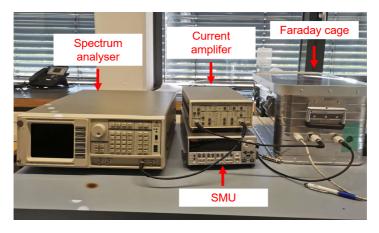

|     |        | 4.3.1 Measurement setup                   | 70  |

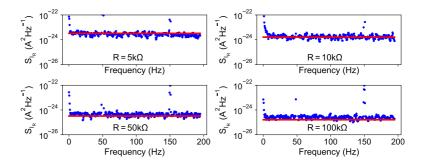

|     |        | 4.3.2 System validation                   | 72  |

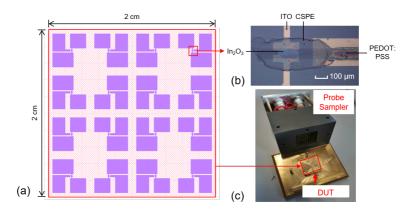

|     |        | 4.3.3 Experiment configuration            | 75  |

|     | 4.4    | Results and discussions                   | 75  |

|     |        | 4.4.1 Low-frequency noise characteristics | 75  |

|     |        | 4.4.2 Noise generation mechanism          | 77  |

|     |        | 4.4.3 Benchmark of noise level            | 79  |

|     | 4.5    | Conclusion                                | 82  |

| 5   | Circ   | uits and applications                     | 83  |

|     | 5.1    | Background                                | 83  |

|     | 5.2    | Printed inverter                          | 83  |

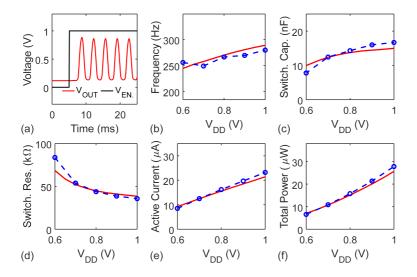

|     | 5.3    | Printed ring oscillator                   | 87  |

|     | 5.4    | Printed full-wave rectifier               | 90  |

|     | 5.5    | Conclusion                                | 99  |

| 6   | Sum    | mary and outlook                          | 101 |

|     | 6.1    | Summary                                   | 101 |

|     | 6.2    | Outlook                                   | 103 |

| Bil | bliogr | aphy                                      | 105 |

| A   | Glos   | sary                                      | 119 |

# **List of Figures**

| 1.1  | Moore 8 law                                                                          |

|------|--------------------------------------------------------------------------------------|

| 1.2  | Manufacturing of conventional electronics and printed elec-                          |

|      | tronics                                                                              |

| 2.1  | Cross-section view of a planar n-type MOS capacitor 10                               |

| 2.2  | Energy band diagram for MOS capacitor base on p-type sub-                            |

|      | strate under different conditions $\ \ \ldots \ \ \ldots \ \ \ \ \ \ \ \ \ \ \ \ \ $ |

| 2.3  | C-V characteristics of the MOS capacitor                                             |

| 2.4  | MOSFET in different bias conditions                                                  |

| 2.5  | Typical I-V characteristics of the n-type MOSFET 1                                   |

| 2.6  | Capacitance in MOSFET                                                                |

| 2.7  | C-V characteristics of MOSFET                                                        |

| 2.8  | Thermal noise model                                                                  |

| 2.9  | Noise components in MOSFET                                                           |

| 2.10 | Various configurations of thin-film transistors                                      |

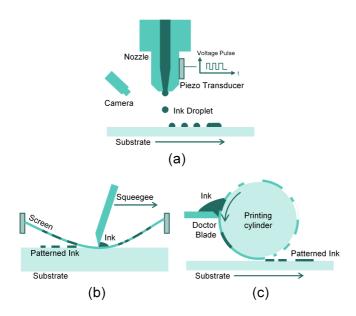

| 2.11 | Illustration of various printing techniques                                          |

|      | Schematics of charge mechanism                                                       |

| 2.13 | Basic equivalent circuit model of electric double layers 29                          |

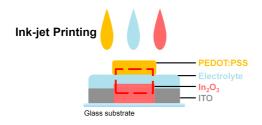

| 2.14 | Material stack of EGT                                                                |

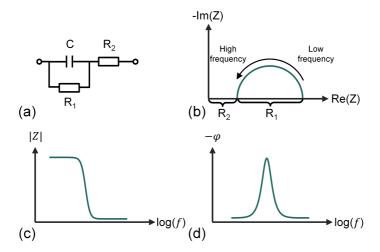

| 3.1  | Complex network, Nyquist plot and Bode plot                                          |

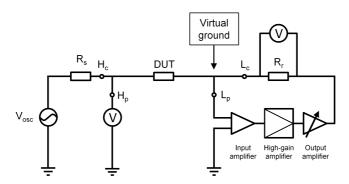

| 3.2  | Auto-balancing bridge method                                                         |

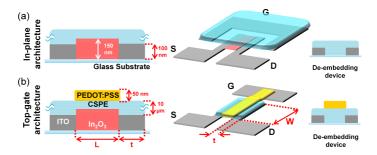

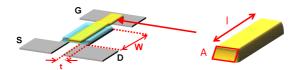

| 3.3  | In-plane and top-gate architectures 4                                                |

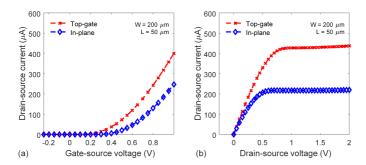

| 3.4  | I-V characteristics of EGTs with top-gate and in-plane archi-                        |

|      | tecture                                                                              |

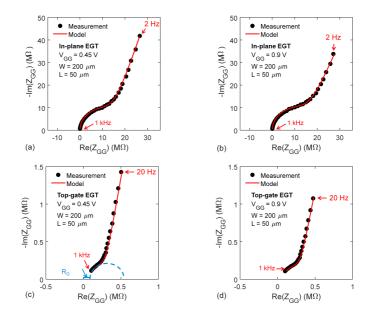

| 3.5  | Measured and modelled gate impedance in Nyquist plots 4                              |

| 3.6  | Structure of the printed top-gate material 4                                         |

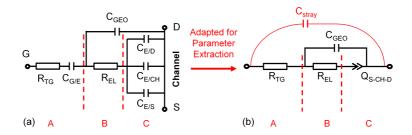

| 3.7  | Equivalent circuit model of EGTs                                          | 46 |

|------|---------------------------------------------------------------------------|----|

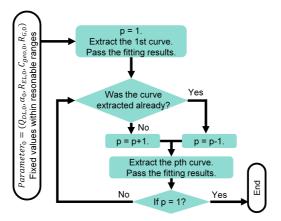

| 3.8  | Parameter extraction routine                                              | 50 |

| 3.9  | Measured and modelled frequency response of gate capacitance              | 53 |

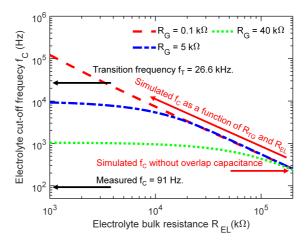

|      | Simulation of the electrolyte cutoff frequency                            | 54 |

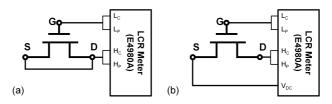

|      | Measurement setup of terminal capacitance                                 | 56 |

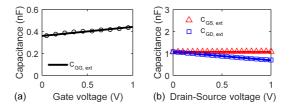

|      | Measured extrinsic overlap capacitance                                    | 58 |

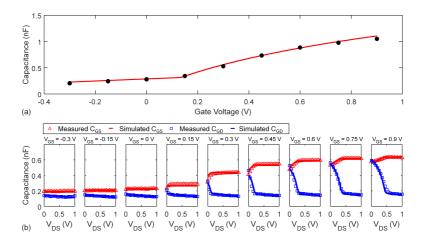

|      | Terminal capacitance of EGT                                               | 60 |

|      | Two-component-model of intrinsic gate capacitance                         | 61 |

| 3.15 | Quasi-static and nonquasi-static capacitance model                        | 63 |

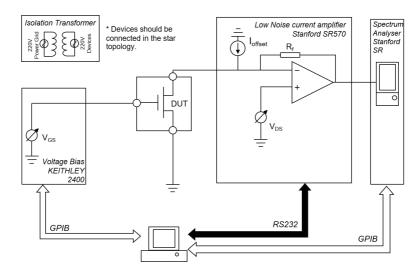

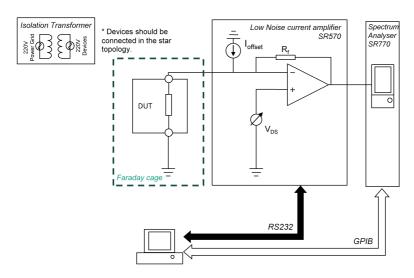

| 4.1  | Low-frequency noise measurement for transistors                           | 72 |

| 4.2  | Low-frequency noise measurement for resistors                             | 73 |

| 4.3  | Photo of measurement setup                                                | 73 |

| 4.4  | Measured and modelled thermal noise of thin-film resistors .              | 74 |

| 4.5  | Layout of test structure                                                  | 74 |

| 4.6  | I-V characteristics of EGT                                                | 76 |

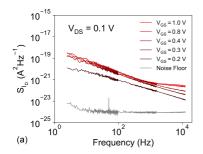

| 4.7  | Measured low-frequency noise characteristics of the EGT $$ . $$           | 77 |

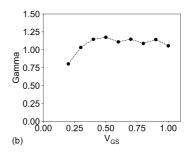

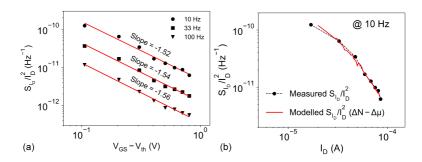

| 4.8  | Normalized drain current noise against gate-overdrive voltage             |    |

|      | and drain current                                                         | 78 |

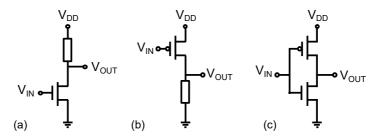

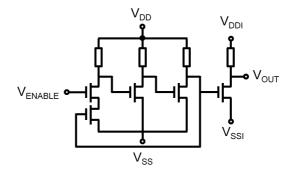

| 5.1  | Different kinds of inverter circuit                                       | 84 |

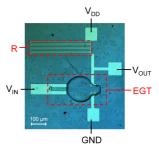

| 5.2  | Microscopic photo of the fabricated inverter                              | 84 |

| 5.3  | Measured and simulated output characteristics of inverter                 | 85 |

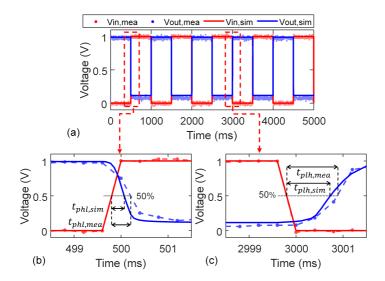

| 5.4  | Schematic of the printed 3-stage ring oscillator                          | 88 |

| 5.5  | Comparison of measured and simulated results of the ring                  |    |

|      | oscillator circuit                                                        | 89 |

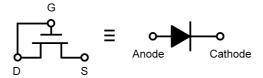

| 5.6  | Schematic of the diode-connected EGT                                      | 91 |

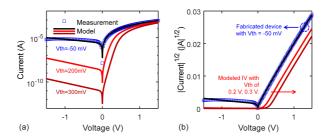

| 5.7  | $Measured\ and\ modelled\ I-V\ characteristics\ of\ the\ diode-connected$ |    |

|      | EGT                                                                       | 92 |

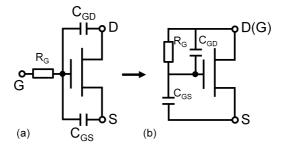

| 5.8  | Nonquasi-static capacitance model of diode-connected EGT .                | 93 |

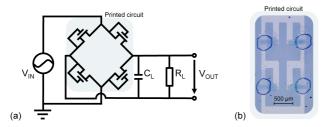

| 5.9  | Schematic and Microscopic photo of full-wave rectifier                    | 93 |

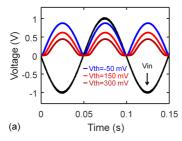

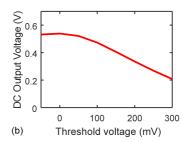

| 5.10 | Simulation of the rectifier output using different threshold              |    |

|      | voltage                                                                   | 94 |

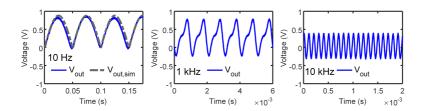

|      | Measured output waveform                                                  | 95 |

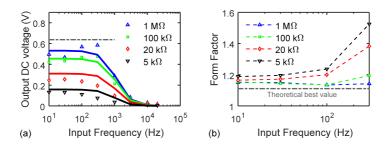

| 5.12 | Frequency response of DC output voltage and form factor                   | 96 |

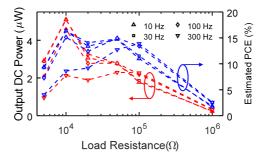

| 5.13 DC output power and estimated power conversion efficiency     | 98 |

|--------------------------------------------------------------------|----|

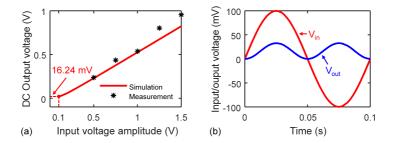

| 5.14 DC output voltage of the full-wave rectifier as a function of |    |

| the input voltage amplitude                                        | 98 |

# **List of Tables**

| 2.1 | Specification of various printing techniques                 | 26 |

|-----|--------------------------------------------------------------|----|

| 2.2 | Key electrical properties of printed TFTs with various metal |    |

|     | oxide semiconductors                                         | 27 |

| 2.3 | Comparison of the areal capacitance and layer thickness be-  |    |

|     | tween the dielectric and electrolyte materials               | 31 |

| 3.1 | Specification of various impedance measurement techniques    | 39 |

| 3.2 | Parameter extraction results                                 | 51 |

| 3.3 | Extrinsic parameters in capacitance model                    | 63 |

| 4.1 | Comparison of the noise level in various TFT technologies    | 80 |

| 5.1 | Evaluation of measured and simulated propagation delay       | 86 |

### 1. Introduction

### 1.1. Overview of Printed electronics

#### 1.1.1. History

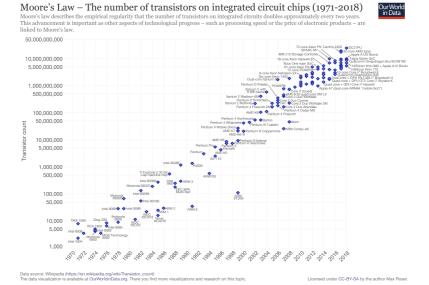

The history of humanity has already experienced three industrial revolutions. Central to the third revolution is the invention and widespread use of solid-state electronics. The deriving technologies such as integrated circuits, computers and the internet has changed almost every aspect of daily life since the latter half of the 20th century. At the same time, the semiconductor industry have undergone rapid growth, while the miniaturization of transistor devices is the key driving force. As predicted by "Moores Law", the number of transistors in integrated circuits increases by a factor of two in every two years (Fig. 1.1 [1]). This has been guiding the research and development of the semiconductor industry. In 1971, the world's first commercial microprocessor Intel 4004 integrates only 2300 transistors based on the 10 µm technology [2], while in 2019, the AMD's Zen 2 microprocessor contains 39.54 billion transistors using TSMC's 7 nm technology [3]. However, the manufacturing of conventional electronics has evolved into a highly complicated process, including multiple subtractive steps such as photo-lithography, etching, doping, cleaning. It has become an investment intensive business. Nowadays, the cost of building a new semiconductor fabrication plant, also called foundry, can easily exceed one billion U.S. dollars [4].

On the contrary, printed electronics (PE) offers a complementary solution to conventional electronics by simplifying the manufacturing process via

**Figure 1.1.:** The Moore's law predicts that the number of transistors in an integrated circuit doubles every 24 months. Reprint from [1] under license CC-BY-4.0.

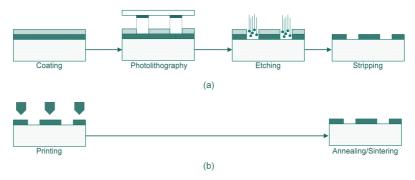

**Figure 1.2.:** (a) The manufacturing of conventional electronics is based on the subtractive process with complex fabrication steps involved. (b) The manufacturing of printed electronics is based on the additive process with much less fabrication steps involved.

additive printing technology. Fig. 1.2 illustrates the fundamental difference of the fabrication process between conventional and printed electronics. The functional materials such as metals and semiconductors are directly deposited and patterned on the substrate. Therefore, as compared with conventional electronics, printed electronics has the unique advantage of low-cost fabrication, which mainly originates from two factors: minimal material wastes and fewer fabrication steps during the process. Furthermore, it possesses more features such as the on-demand fabrication, which can hardly be accomplished by conventional electronics and thus keep attracting the attention from both research and industry.

#### 1.1.2. Material aspect

The history of printed electronics begins with organic electronics. It can be traced back to the discovery of conductive polymers in 1977 [5], followed by the development of organic semiconductors in 1983 [6] and organic field-effect transistors (OFETs) in 1986 [7]. Since organic materials can be naturally formed into inks, the idea of printed OFETs becomes reality in 1997 [8]. However, organic electronics suffer from the low charge mobility, which is an essential property to determine the speed and driving ability of transistors. Despite the research efforts in the past three decades, the charge mobility of printed organic semiconductor materials can barely exceed 5 cm $^2$  V $^{-1}$  s $^{-1}$  [9], which is almost three orders of magnitude lower than the single-crystalline silicon [10]. This has significantly limited the practical applications of printed organic electronics. Furthermore, some organic materials have the stability issue, including the sensitivity to the oxygen and water in the environment.

The limit of printed electronics is again pushed by the development of inorganic semiconductor materials, including metal oxide, carbon nanotube and graphene. These kinds of materials possess high charge carrier mobility even if printed, which can easily exceed  $10~\rm cm^2~V^{-1}~s^{-1}$  [11]. Recently, there have been even reports showing high charge mobility approaching  $100~\rm cm^2~V^{-1}~s^{-1}$  [12]. The road map published by Organic Electronics

Association (OE-A) predicts that the long term development of printed semiconductors relies on the innovation of inorganic and nano-materials [13].

However, there are also several disadvantages to those materials. One of them is the high post-processing temperature which hinders the realization of flexible electronics, because most flexible substrates cannot endure high temperature, such as polyethylene naphthalate (PEN) < 155 °C, and polyethylene terephthalate (PET) < 250 °C. Nevertheless, inorganic and nano-materials are still very promising candidates for printed electronics applications in the near future.

### 1.1.3. Application domains

Printed electronics has been gifted with lots of attractive features, such as mechanical flexibility, low-cost and on-demand fabrication. Therefore, it is exciting to imaging, how many kinds of new applications can be enabled by this emerging technology. Notably, printed electronics targets applications that can be hardly covered by conventional electronics.

Generally, printed electronics is increasingly recognized as a key enabler for various fields of application. For example, in the automobile industry, the utilization of organic light emitting diodes (OLEDs) can potentially reduce the weight and production costs, while the form-factor provided by flexible displays and printed sensors realize new designs of interaction and entertainment systems [14]. Also, medical applications are the potential market. The stretch-ability and mechanical flexibility of printed electronics can be fully utilized to make bio-compatible and wearable devices to monitor vital signs of human invasively [15, 16]. In another example, novel medical devices using disposable printed sensors are invented to measure the pressure distribution on occlusal surfaces, which facilitates the diagnosis of diverse symptoms [17]. Last but not the least, in the area of Internet of Things (IoT), printed electronics can play an important role to realize niche applications. There have already been demonstrations of

radio-frequency identification (RFID) tags consisting of organic transistors [18]. Additionally, due to the large number of sensors required by IoT, printed sensors are advantageous and competitive in the aspect of fabrication cost [19, 20].

As of 2018, the printed electronics has already its total market of 31.7 USD billion, where the categories of printed/flexible displays and sensors are the primary driving forces, with the shares of 26 USD billion and 3.6 USD billion, respectively. On the other hand, printed logic circuits, memories and batteries possess also strong growth potential [21]. It is forecasted by IDTechEx Research that, in 2029, the market of printed electronics can reach the total market of 74 USD billion [22].

#### 1.2. Motivation

In conventional electronics, proper tools are essential to design circuits and applications. In the semiconductor industry, this tool package is called process design kit (PDK), comprising design rules and model libraries for a certain technology. The former defines constrains and criteria of standardized physical and electrical manufacturability, whereas the latter accurately reproduces the electrical characteristics of electron devices using a set of mathematical equations in the circuit simulator. To assure the simulation speed, compact modeling is preferred where expensive math functions are often avoided. A standard transistor model library covers various aspects of the electrical characteristics of devices. For instance, the famous industry-standard Berkeley Short-channel IGFET Model (BSIM) consists of drain-current model, threshold voltage model, capacitance model, flicker noise model, just to name a few [23]. With the help of an accurate PDK, the design process can be largely facilitated.

Although PDK techniques have been widely introduced in the conventional silicon industry, PDK developed for printed electronics has been scarcely reported. For instance, the VLSI Group and Organic Electronics Group of University of Minnesota have developed an open-source

Organic PDK based on their Gel-Electrolyte-Gated Polymer Transistors in 2011 [24], which supports the layout design and basic circuit simulation. Another example is the PDK presented by the group of Nanyang Technological University based on their fully additive printing technology [25] with similar functionality as the aforementioned one. They have successfully demonstrated the design and fabrication of basic digital and analog circuits using the PDK.

In those early demonstrations of PDKs for printed electronics, one can conclude that most works regarding the compact modeling have only focused on the modeling of static current-voltage (I-V) characteristics. This enables direct current (DC) analysis of circuit simulation, while other models such as capacitance-voltage (C-V) and noise models are missing to support e.g. transient, alternating current (AC) and noise analysis. In the recent publication of M. Fattori, et al. in 2019 [26], capacitance and noise models are included in the PDK to enable a comprehensive analysis of the transimpedance amplifier. However, the modeling approaches and outcomes are still in a preliminary stage as presented in PDKs, lacking deep understanding of the device physics and careful validation of models with experimental data.

Indeed, the development of reliable models for printed transistors is a challenging task due to the large variety of devices in terms of materials and fabrication process. However, the everlasting evolution of compact modeling in design tools is essential for the development of circuits/applications/systems in printed electronics.

Apart from the PDK development, there have also been research works concentrating on compact modeling of printed electronics. However, the focus of most studies has been still on I-V modeling and the static performance of devices and circuits. On contrary, other kinds of characteristics have received less attention, which hinders more advanced circuit analysis.

In this context, the purpose of this thesis is to comprehensively characterize the electrical behavior of printed transistors to gain a deep understanding of the device physics, including the capacitance and noise. Based

on that, compact models are developed for accurate circuit simulation as a part of the standard PDK. Also, both basic and novel printed circuits are developed and characterized.

#### 1.3. Structure of this thesis

The rest of the thesis into five chapters are organized as listed below:

- Chapter 2 gives an introduction to field-effect transistors and the technical background of printed electronics. Also, the basic structure of printed transistors and their functionality will be extensively evaluated.

- Chapter 3 deals with characterization and modeling of capacitance in EGTs. Measurements Voltage-dependent impedance spectroscopy of transistors will analyzed, and the frequency response will be modelled by the equivalent circuit method. This reveals important information of the dynamic behavior in EGTs. Additionally, a Meyer-like nonquasi-static model is established to enable advanced circuit simulations.

- Chapter 4 presents the study on the low-frequency noise in printed electronics. The noise generation mechanism of EGTs will be comprehensively explained by comparing with the existing theories and experimental data. Figure of merit will be calculated to provide the benchmark of noise level with state-of-the-art thin-film technologies.

- Chapter 5 proposes various circuits based on the printed electronics, including printed inverter, ring oscillator and full-wave rectifier. Also, the compact modeling of the transistor capacitance is validated through the comparison between measurement and experimental data in the circuit level.

- Chapter 6 summarizes the whole thesis and gives an outlook for future works.

## 2. Background

Transistors are the basic building blocks of integrated circuits, the rapid development of which triggers the revolution in modern electronics since their first invention at Bell Labs in 1947. In the history of transistors, various types of transistors have been invented, such as bipolar junction transistors (BJTs), junction field-effect transistorss (JFETs) and metal-oxide-semiconductor field-effect transistors (MOSFETs). The last ones have become the most dominant semiconductor devices due to a set of advantages over the others, including the easy manufacturability, the high gate impedance and the low leakage current.

To effectively understand the principle of MOSFETs, in this chapter, a comprehensive introduction on metal-oxide-semiconductor (MOS) capacitors is firstly presented. Based on that, the device physics of MOSFETs will be explained in detail. Then, fundamentals in printed electronics will be focused on, including material properties and printed technologies. The final section gives the technical background of the main subject of study, namely EGTs.

### 2.1. MOS capacitor

### 2.1.1. Operation modes

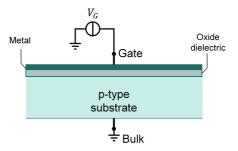

In Fig. 2.1, the cross-section view of an n-type MOS capacitor base on the ptype substrate is illustrated as an example. For p-type MOS capacitors, the polarization of the semiconductors is inverted. It has a sandwich structure

Figure 2.1.: Cross-section view of a planar n-type MOS capacitor.

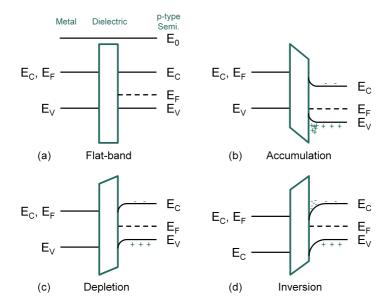

formed by the gate contact on the top, the body contact at the bottom and the oxide dielectric in between. Upon the application of the bias potential between gate and body, the operation of the MOS capacitor can be divided into four modes, namely the flat-band, accumulation, depletion and inversion mode. Here, the corresponding energy band diagrams as presented in Fig. 2.2 (a)-(d) are often used to help the understanding of the working modes.

- (a) Flat-band condition: The analysis starts with a special condition called the flat-band condition, as shown in Fig. 2.2(a), which is realized by applying a certain flat-band voltage  $V_{FB}$  to the gate voltage  $V_G$ . Here, the free electron level  $E_0$  is continuous since the electron can freely move between the crystal field of different materials. In the metal, the Fermi level  $E_F$  lies inside the conduction band  $E_C$ , while in the p-type semiconductor,  $E_F$  lies between the  $E_C$  and valence band  $E_V$ , which is closer to the  $E_V$  due to the doping. In the flat-band condition, the electric field in the three materials is zero.

- **(b) Accumulation condition**: If a gate voltage less than the flat-band voltage is applied as depicted in Fig. 2.2(b), the energy band of the gate metal shifts upwards. At the same time, the energy band of the semiconductor substrate bends upward. Due to bending, the Fermi level on the surface of the semiconductor is more closer to the valence band than

**Figure 2.2.:** Energy band diagram of MOS capacitor base on p-type substrate under different conditions: (a) flat-band, (b) accumulation, (c) depletion, (d) accumulation.

the Fermi level in the bulk, resulting in an excess of holes on the surface. Therefore, this is referred to as surface accumulation.

- **(c) Depletion condition**: On the contrary, if the applied gate voltage is higher than the flat-band voltage as shown in Fig. 2.2(c), the band bends downwards. When the Fermi level on the surface of the semiconductor is neither close to the conductance band nor the valence band, both electron and hole charge densities are significantly small. Now, a depletion region has been established, and this condition is called the depletion mode.

- **(d) Inversion condition**: Finally, when the gate voltage is increased more positively, the energy band bends further downwards. When the Fermi level is closer to the conduction band than the valence band, holes are

depleted from the surface, resulting in the electron concentration at the surface exceeding the hole concentration. At this point, the applied gate voltage is termed as threshold voltage  $V_{th}$ . After that, the operation of the MOS capacitor enters the inversion region, where the p-type substrate surface has been inverted to another polarity, not due to the doping but the applied electric field.

#### 2.1.2. C-V characteristics

The capacitance-voltage (C-V) characteristics of the MOS capacitor reveal important information such as the doping concentration, gate oxide thickness, flat-band voltage and threshold voltage. Furthermore, the C-V characteristics are also strongly related to the working principle of the MOSFET and its current-voltage (I-V) characteristics.

In the C-V analysis of the MOS capacitor, the capacitance is always referred as the small-signal capacitance, which is defined as:

$$C = \frac{dQ}{dV},\tag{2.1}$$

where the Q is the charge that the capacitor holds, and V is the voltage applied to it. Since the derivative of the charge with respect to the time, dQ/dt, is the current i(t), one can also measure the small-signal capacitance by applying an alternating voltage v(t) and measuring the resulting current i(t):

$$C = \frac{dQ}{dV} = \frac{dQ/dt}{dV/dt} = \frac{i(t)}{dv(t)/dt}.$$

(2.2)

Often, the small-signal capacitance is measured by the LCR meter. More details about the measurement techniques will be discussed later in chapter 3.

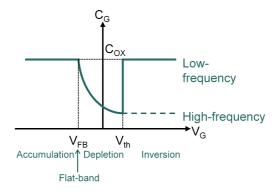

A simplified illustration of the C-V characteristics is presented in Fig. 2.3, where the four aforementioned bias conditions are reflected, namely accumulation, flat-band, depletion and inversion.

**Figure 2.3.:** C-V characteristics of the MOS capacitor.

- (a) Accumulation region: In the accumulation mode when  $V_G < V_{FB}$ , only the accumulation charge  $Q_{ACC}$  is present on the surface of the substrate. Therefore, the MOS capacitor behaves like a normal parallel plate capacitor. Consequently, in C-V characteristics, one can only see the gate oxide capacitor  $C_{OX}$  in the measurement in this region.

- **(b) Depletion region:** When the  $V_G$  exceeds  $V_{FB}$  and therefore the MOS capacitor enters the depletion region, one additional depletion capacitor  $C_{DEP}$  is introduced due to the creation of the depletion layer with the thickness of  $W_{DEP}$  as a function of the gate voltage. Therefore, the value of  $C_{DEP}$  can be calculated as:

$$C_{DEP} = \frac{\epsilon_{SUB}\epsilon_0}{W_{DEP}},\tag{2.3}$$

where  $\epsilon_{SUB}$  is the dielectric constant of the substrate material and  $\epsilon_0$  is the vacuum permittivity,.

As  $V_G$  increases, the depletion layer expands, and  $C_{DEP}$  becomes smaller. Electrically,  $C_{DEP}$  is in series connection with  $C_{OX}$ . Thus, the total capacitance can be calculate as:

$$\frac{1}{C_G} = \frac{1}{C_{OX}} + \frac{1}{C_{DEP}}. (2.4)$$

As shown in Fig. 2.3, its value decreases as the  $V_G$  increases in the depletion region.

(c) Inversion region: As  $V_G$  further increases and reaches the threshold voltage  $V_{th}$ , the inversion layer is formed. Now, the inversion charge  $Q_{INV}$  is present between the substrate and oxide dielectric interface, resulting in the inversion capacitance  $C_{INV}$ . Electrically,  $C_{INV}$  is in parallel connection with the depletion capacitance. Therefore, the calculation of the total gate capacitance  $C_{DEP}$  becomes:

$$\frac{1}{C_G} = \frac{1}{C_{OX}} + \frac{1}{C_{DEP} + C_{INV}}.$$

(2.5)

In the inversion region, the value of  $C_G$  increases aggressively due to the presence of  $C_{INV}$  until it approaches again the  $C_{OX}$ . However, since the inversion capacitance is originated from the minority charge carrier, it has a large time-scale and fails to respond to the high-frequency signal. Therefore, at high frequencies (for silicon MOSFET it is typically above  $100~\mathrm{Hz}$ ), less  $C_G$  can be measured in C-V characteristics.

### 2.2. MOSFET

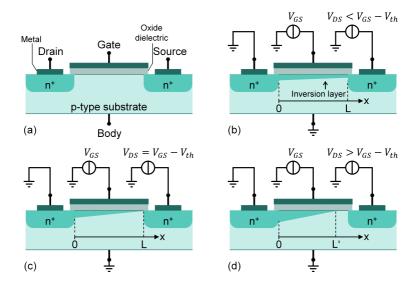

The MOSFET has a more complex three-terminal structure than the MOS capacitor. As shown in Fig. 2.4 (a), two additional source and drain electrodes are introduced as compared to the MOS capacitor. Upon the application of the gate voltage, the surface state of the channel is modified accordingly similar to the MOS capacitor. With the channel in the accumulation/depletion mode, the transistor is in OFF state, while it is turned

ON when the channel is in the inversion mode. This section explains the working principle of the MOSFET, its current-voltage characteristics in the on-state are studied.

#### 2.2.1. I-V characteristics

When the bias between gate and source  $V_{GS}$  exceeds the threshold voltage  $V_{th}$ , an inversion layer is induced at the channel-oxide interface. Supposing that a small drain-source bias  $V_{DS}$  is applied, the local voltage V(x) is distributed along the channel, yielding a local channel charge density:

$$Q_{INV} = -WC_{OX}(V_{GS} - V_{th} - V(x)), \tag{2.6}$$

where W is the channel width.

As discussed in the analysis of MOS capacitor,  $Q_{INV}$  is only present when:

$$V_{GS} - V_{th} - V(x) > 0, (2.7)$$

Consequently, the local current per unit length can be calculated using the field-effect mobility  $\mu_{FET}$  and local electric field E(x):

$$I_{DS} = \mu_{FET} Q_{INV} E(x)$$

=  $-\mu_{FET} W C_{OX} (V_{GS} - V_{th} - V(x)) E(x)$ . (2.8)

Noting that  $E(x) = -\frac{dV(x)}{dx}$ , the total current in the channel can be obtained by performing the integration on both sides of Eq. 2.8:

$$\int_{0}^{L} I_{DS} dx = \int_{0}^{L} \mu_{FET} W C_{OX} (V_{GS} - V_{th} - V(x)) \frac{dV(x)}{dx} dx$$

$$= \int_{0}^{V_{DS}} \mu_{FET} W C_{OX} (V_{GS} - V_{th} - V(x)) dV$$

$$= \mu_{FET} W C_{OX} ((V_{GS} - V_{th}) V_{DS} - \frac{1}{2} V_{DS}^{2}),$$

(2.9)

**Figure 2.4.:** (a) Cross-section view of a planar n-type metal oxide field-effect transistor. MOS-FET in different bias conditions: (b) Triode region, (b) Channel pinch-off and (c) Saturation region.

$$I_{DS} = \frac{W}{L} \mu_{FET} C_{OX} ((V_{GS} - V_{th}) V_{DS} - \frac{1}{2} V_{DS}^2), \tag{2.10}$$

where  $V_{DS}$  is the drain-source bias and L is the channel length. The Eq. 2.10 holds true for a small  $V_{DS}$ . This is the so-called triode region of the MOSFET operation as shown in Fig. 2.4 (b).

When the drain-source bias  $V_{DS}$  further increases to  $V_{GS} - V_{th}$ , the potential difference between oxide-channel interface becomes zero. It fails to support the depletion layer at the drain side. Thus, Eq. 2.7 cannot be satisfied any more. At this moment, the so-called channel "pinch-off" occurs as shown in Fig. 2.4(c). Now, the integration in Eq. 2.8 becomes:

$$\int_{0}^{L} I_{DS} dx = \int_{0}^{V_{GS} - V_{th}} \mu_{FET} W C_{OX} (V_{GS} - V_{th}) dV$$

(2.11)

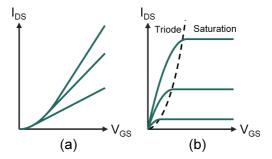

**Figure 2.5.:** Typical I-V characteristics of the n-type MOSFET. (a) Transfer characteristics. (b) Output characteristics.

$$I_{DS} = \frac{1}{2} \frac{W}{L} \mu_{FET} C_{OX} (V_{GS} - V_{th})^2.$$

(2.12)

Starting from the "pinch-off" point, the MOSFET is in its saturation region as shown in Fig. 2.4 (d). To calculate the  $I_{DS}$  after this point, Eq. 2.11 can still be used, where the length in the left side becomes shorter,  $L' = L - \Delta L$ . Based on the first order assumption,  $\frac{\Delta L}{L} = \lambda V_{DS}$  [27]. Consequently,  $I_{DS}$  can be calculated as:

$$I_{DS} = \frac{1}{2} \frac{W}{I} \mu_{FET} C_{OX} (V_{GS} - V_{th})^2 (1 + \lambda V_{DS})$$

(2.13)

This is called the channel-length modulation, where  $\lambda$  is the modulation coefficient. To this end, the whole regions when the MOSFET is turned on have been described with their I-V characteristics exemplified in Fig. 2.5.

### 2.2.2. C-V characteristics

In the previous section, the static I-V characteristics of the MOSFET have been described. To understand the dynamic behavior of the MOSFET, one needs knowledge of the transistor capacitance.

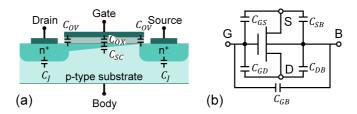

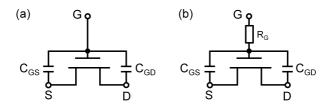

**Figure 2.6.:** (a) Physical structure of capacitance components in the MOSFET. (b) Representation of lumped terminal capacitance model in schematic level.

As shown in Fig. 2.6 (a), different capacitance components in the MOSFET are present at various material interfaces. Firstly, as discussed previously, the oxide capacitance  $C_{OX}$  is present between the gate and channel. Also, in the MOSFET device, it unavoidable to have the overlap region between the gate and source/drain electrodes. yielding the overlap capacitance  $C_{OV}$ . Additionally, considering the MOSFET in an ON-state, the depletion layer and the inversion layer are formed on the surface of the semiconductor, corresponding to the depletion capacitance and inversion capacitance. Since they are electrically in parallel connection as explained earlier, the semiconductor capacitance  $C_{SC}$  is used to represent their summation. Furthermore, since the n-type doped source and drain area creates a p-n junction at the interface with the p-type substrate, the junction capacitance  $C_J$  is formed there.

The aforementioned capacitance components can be categorized into two groups, namely intrinsic and extrinsic capacitance. Both  $C_{OX}$  and  $C_{SC}$  are considered as the intrinsic effects since they are associated with the state of the channel, while die others are extrinsic effects.

During the operation of the MOSFET, a non-zero  $V_{DS}$  is applied to the device. Often, this results in a non-uniform distribution of the inversion layer thickness on the semiconductor surface along the channel direction. Therefore, the  $C_{SC}$  is not always constant, but a function of the channel position, which also changes concerning the applied external bias voltage.

From the perspective of compact modeling, a practical approach is to treat the transistor capacitance as a lumped capacitance between terminals, which are described as voltage-dependent capacitors. Each of them contains both intrinsic and extrinsic effects. This idea is illustrated in Fig. 2.6 (b), among which the gate-source capacitance  $C_{GS}$  and gate-drain capacitance  $C_{GD}$  are the ones of highest interest. Here, a comprehensive investigation will be given to determine their values in different operation regions of the MOSFET. For simplicity, only intrinsic components are considered.

In principle, the terminal capacitance is the partial derivative of gate charge  $Q_G$  with respect to the terminal voltage:

$$C_{GS} = \frac{\partial Q_G}{\partial V_{GS}},\tag{2.14}$$

$$C_{GD} = \frac{\partial Q_G}{\partial V_{GD}}. (2.15)$$

The investigation starts by applying gate bias  $V_{GS}$  above the threshold voltage, while source-drain bias  $V_{DS}$  is zero. In this case, the inversion charge on the semiconductor surface is uniformly distributed along the channel length, and the total gate capacitance is  $C_{GG} = WLC_{OX}$ . Therefore, the MOSFET is now symmetric with respect to the source and drain. The terminal capacitance  $C_{GS}$  and  $C_{GD}$  shares equally the total gate capacitance:

$$C_{GS} = C_{GD} = \frac{1}{2} WLC_{OX}.$$

(2.16)

When the  $V_{DS}$  increases, in the channel, the charge density at the source side becomes more, while it drops to at the drain side, as illustrated in Fig. 2.4 (c). This leads to an increase of the  $C_{GS}$  and decrease of the  $C_{GD}$ . When  $V_{DS}$  equals the overdrive voltage  $V_{GS} - V_{th}$ , there are no inversion charges at drain side. At this point, the  $C_{GD}$  is zero and  $C_{GS}$  reaches the maximum.

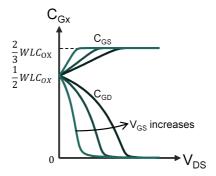

**Figure 2.7.:** Typical C-V characteristics of MOSFET as a function of drain-source voltage  $V_{DS}$  at various gate-source voltage  $V_{GS}$ .

To determine the values of  $C_{GD}$  and  $C_{GS}$ , the total gate charge needs to be studied. It can be proved that the local gate charge per channel length  $Q_i(x)$  can be expressed as a function of channel position x [28]:

$$Q_i(x) = WC_{OX}(V_{GS} - V_{th})\sqrt{1 - \frac{x}{L}}$$

(2.17)

The total charge at the gate can be then obtained by integrating the expression from channel position x = 0 to x = L:

$$Q_G = WC_{OX}(V_{GS} - V_{th}) \int_0^L \sqrt{1 - \frac{x}{L}} dx = \frac{2}{3} WLC_{OX}(V_{GS} - V_{th}).$$

(2.18)

Then, using the definition in Eq. 2.14, one can obtain  $C_{GS} = \frac{2}{3}WLC_{OX}$  and  $C_{GD} = 0$ . Fig. 2.7 shows both terminal capacitances as a function of and  $V_{DS}$ , when  $V_{GS}$  is changing.

#### 2.2.3. Noise characteristics

Apart from the I-V and C-V characteristics, noise characteristics is also an important aspect. On one hand, it is a powerful non-destructive tool to

study surface defects, surface roughness and interface properties of the MOSFET device. It also helps to understand the charge carrier transport mechanism. On the other hand, it is unwanted and degrades the signal quality, especially for analog and radio-frequency (RF) circuits. Accurate modeling is required to correctly predict the performance of MOSFET circuits such as signal-to-noise ratio.

Electrical noise is a statistical random process. As the value of a noise signal changes randomly, it is impossible to predict its value in the time domain. Therefore, a more practical way to quantify a noise signal is to inspect its power spectral density (PSD), which gives more versatile information in the frequency domain. For a noise voltage signal in the time domain v(t), the PSD is defined using the Fourier transformation as:

$$S(f) = |\int_{\infty}^{-\infty} e^{-2\pi i f t} v(t) dt|^{2}, \qquad (2.19)$$

which has the unit of  $V^2/Hz$ . It implies that the energy or power of a noise signal that is normalized to 1 Hz bandwidth at various frequency points.

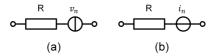

For MOSFET devices, there are two sources of noise, namely the thermal noise and the flicker noise. The thermal noise originates from the random motion of charge carriers inside conductors, which is independent of the external electric field. For resistors, the thermal noise can be described either by a voltage source  $v_n$  or a current source  $i_n$  in series connection with a noiseless resistor R, as depicted in Fig. 2.8. The power spectral density, namely  $S_V$  and  $S_i$  can be calculated as:

$$S_V = 4k_B T R \Delta f, \qquad (2.20)$$

$$S_I = \frac{4k_B T}{R} \Delta f, \tag{2.21}$$

where  $k_B$  is the Boltzmann constant, T is the temperature, R is the resistance and  $\Delta f$  is the frequency bandwidth. As can be seen from Eq. 2.20 and 2.21, the thermal noise is independent of the frequency. It shows a

Figure 2.8.: Thermal noise model in (a) voltage source and (b) current source representation.

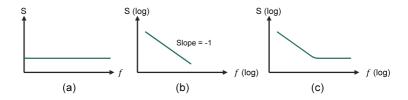

**Figure 2.9.:** Noise power density of (a) thermal noise and (b) flicker noise. In MOSFETs, both types of noise co-exist, resulting a noise behavior as shown in (c).

constant flat line in its PSD spectrum, as shown in Fig. 2.9 (a). For this reason, it is also called white noise.

The flicker noise has a power spectral density which is proportional to  $f^{-1}$ :

$$S(f) \propto \frac{1}{f},$$

(2.22)

Therefore, in the logarithmic plot of the PSD spectrum, it has a constant slope of -1 as displayed in Fig. 2.9 (b). In most MOSFET devices, both thermal and flicker noise co-exist. At low frequency, the flicker noise often dominates, while in high frequencies the thermal noise is more pronounced. A typical noise spectral density of MOSFET is shown in Fig. 2.9 (c).

The generation mechanism of flicker noise in MOSFETs is a complex topic. Until now, there is still an on-going discussion on its physical origin. In principle, two kinds of theories are popular in this field, namely carrier number fluctuation theory and mobility fluctuation theory. The first one was firstly proposed by McWhorter [29], who claims that the fluctuation

behavior originates from the random trapping and de-trapping events of charge carriers on the surface traps of oxide, which is a purely surface effect. On the other hand, an opposite opinion considers the origin of flicker noise as a bulk effect. The representative one is Hooge's model [30] proposed based on the observation that the normalized current power density is inversely proportional to the total number of charge carrier. A more detailed discussion will be introduced in Chapter 5.

### 2.3. Printed thin-film transistor

Currently, the microelectronics market is dominated by the silicon-based bulk technology. However, in the future generation of electronics, new types of materials and fabrication processes are required to meet the needs of niche applications such as Internet-of-Things (IoT), smart sensors and wearable/implantable devices. As compared with the conventional bulk technology, thin-film transistors (TFTs) offer a set of attractive features such as the possibility to realize flexible electronics. Especially, the deployment of additive printing process during the fabrication of TFTs further adds more contributes, including cost-effective manufacturing, on-demand design, large-area and environmentally friendly processability. Therefore, printed TFTs are considered as promising candidates to meet the new requirements of emerging applications, which are largely complementary to their silicon counterparts.

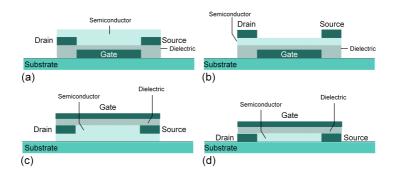

Thin-film transistors are multi-layer structural electronic devices, comprising the dielectric layer, semiconductor layer and source/drain/gate electrodes According to the relative position of electrodes, TFTs can be categorized into two four configurations [31], including bottom-gate/bottom-contact, bottom-gate/top-contact, top-gate/top-contact and top-gate/bottom-contact as shown in Fig. 2.10 from (a) to (d). Due to the better transferring path of charge carriers, the configurations of bottom-gate/top-contact and top-gate/bottom-contact often exhibit better performance [32].

**Figure 2.10.:** Various configurations of thin-film transistors regarding the relative position of source, drain and gate electrode: (a) bottom-gate/bottom-contact, (b) bottom-gate/top-contact, (c) top-gate/top-contact and (d) top-gate/bottom-contact.

### 2.3.1. Printing technology

In printed thin-film technology, materials such as metals, dielectrics and semiconductors can be directly deposited on the substrate. The deposition process can be accomplished by various additive printing techniques using solution-processable materials, as illustrated in Fig.2.11.

Generally, printing techniques can be classified into two groups [33]. One is the inkjet digital printing that utilizes the nozzle to deposit solutions on the substrate. It produces patterned thin-film on-demand in a non-contacting way without additional masks. Therefore, it is a convenient technique, especially for rapid prototyping. As shown in Fig. 2.11(a), the inkjet printing system comprises the jetting control system, the vision system, and a motion platform. The printing nozzle heads are connected to the ink cartridge or reservoir. The electrical pulse applied to the piezo transducer triggers the ejection of the droplets from nozzles. Their positions relative to the substrate are observed by the vision system and controlled by the motion system which moves the substrate. Then, well-defined ink patterns are obtained on the substrate.

**Figure 2.11.:** Illustration of various printing techniques: (a) inkjet printing, (b) screen printing and (c) gravure printing.

Another class is non-digital printing including e.g. screen, gravure and transfer printing, which is suitable for mass production. In screen printing as shown in Fig. 2.11(b), a screen mask with pre-defined patterns are required. Using the squeegee, ink materials are squeezed through the mask, resulting in patterned large-area thin-film on the substrate surface. In gravure printing as shown in Fig. 2.11 (c), ink materials are contained in the gravure cylinder with pre-patterned cavities, while excess ink materials are removed by a doctor blade. Then, ink patterns are transferred onto the substrate through the rolling of the gravure cylinder.

Each printing technique features different printing resolutions and printing speed, while their requirements for the solution viscosity also differs.

The specifications of various printing techniques are summarized [31, 34] in Tab. 2.1.

| Resolution                   | Printing speed                                                                              | Eilm thiolmoss               | 77' '1                        |

|------------------------------|---------------------------------------------------------------------------------------------|------------------------------|-------------------------------|

| $(\mu m)$                    | (m/min)                                                                                     | (μm)                         | (mPa s)                       |

| 30 - 50 $50 - 100$ $20 - 75$ | $     \begin{array}{r}       1 - 100 \\       10 - 100 \\       20 - 1000     \end{array} $ | 0.3 - 20 $3 - 100$ $0.1 - 5$ | 1 - 40 $500 - 5000$ $2 - 200$ |

|                              | 30 - 50 $50 - 100$                                                                          | 30 - 50                      | 30 - 50                       |

Table 2.1.: Specification of various printing techniques

#### 2.3.2. Metal oxide semiconductors

In printed thin-film technology, a wide variety of materials can be chosen for the fabrication of semiconductor, dielectric and electrode materials. Among them, the semiconductor materials are the most important one which determine the performance of the transistors. Potential printable semiconductors can be organic, inorganic metal oxide and 1-D/2-D materials. As introduced in chapter 1.1.1, organic semiconductors have been the leading force in the field of printable semiconductors, which feature low-temperature processability and good compatibility with flexible substrates. However, they suffer from low intrinsic mobility which limits the device performance and applications. As predicted by the OE-A roadmap [35], the upper limit of mobility of organic semiconductors in commercially available quantities lays merely around  $10\,\mathrm{cm^2\,V^{-1}\,s^{-1}}$ , while the further development to achieve higher mobility (>10 cm² V<sup>-1</sup> s<sup>-1</sup>), comparable with silicon-based semiconductor, needs to rely on inorganic and nanomaterials.

Alternatively, metal oxide semiconductors have been considered as promising materials due to their superior charge carrier mobility. Examples are crystalline oxide semiconductors such as CuO,  $\rm Cu_2O$ , ZnO and  $\rm In_2O_3$ , and amorphous oxide semiconductors such as ZTO, IZO and IGZO. Oxygen

vacancies and metal interstitials in metal oxides cause their semiconducting n-type and p-type behavior, respectively. In the energy band structure, the overlap of oxygen 2p and metal ns orbitals forms a localized valence band and a high dispersive valence band. Consequently, electrons have a low effective mass as compared with holes, leading to a high charge carrier mobility in n-type oxides than in p-type. I.e., in metal oxide semiconductor transistors, the p-type devices are still much inferior in performance in comparison to their n-type counterparts, which hinders the development of complementary metal-oxide-semiconductor (CMOS) logic. In Tab. 2.2, key electrical properties of printed TFTs with various metal oxide semiconductors are listed based on the literature research.

Table 2.2.: Key electrical properties of printed TFTs with various metal oxide semiconductors

| Semiconductor | Printing techniques | Mobility<br>(cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup> ) | $I_{on}/I_{off}$    | $V_{th}$ (V) | Ref. |

|---------------|---------------------|----------------------------------------------------------------|---------------------|--------------|------|

| IGZO          | Inkjet              | 10.2                                                           | $2 \times 10^{8}$   | 2            | [36] |

| IZO           | Inkjet              | 8                                                              | $1 \times 10^{5}$   | 2            | [37] |

| $Zn_2GeO_4$   | Transfer            | 25                                                             | $2.5 \times 10^{3}$ | 1            | [38] |

| $In_2O_3$     | Inkjet              | 13.7                                                           | $3.5 \times 10^6$   | -4           | [39] |

| ZnO           | Gravure             | 90                                                             | $1 \times 10^{5}$   | 0.25         | [40] |

| $Zn_3As_2$    | Transfer            | 305                                                            | $1 \times 10^{5}$   | -16          | [41] |

| $WSe_2$       | Inkjet              | 1                                                              | $3 \times 10^5$     | 0            | [42] |

Traditional fabrication methods of metal oxide semiconductors include atomic layer deposition and sputtering, which require a vacuum process. Alternatively, solution-processable precursors have also been widely investigated, which are suitable for printed electronics. However, they often require a high annealing temperature between 300 °C and 400 °C to achieve the complete conversion from precursors to stable metal-oxide-metal bonds. This significantly restricts the usage of flexible substrates that barely withstand high temperature over 300 °C [43, 44]. Recently, efforts have been made to allow the low-temperature process of the metal oxide

thin-film. Alternative strategies are the usage of aqueous solution [45], combustion chemistry [46] and photo-activation annealing [47].

# 2.3.3. Electrolyte-gating approach

In MOSFETs or TFTs, the gate is separated from the channel by the insulation layer, where dielectric materials are often used. As discussed in section 2.2, the unit gate capacitance  $C_{OX}$  per unit area generated by the dielectrics layer is an essential parameter for the functionality of MOSFET. From Eq. 2.13, one can deduce that the current driving ability scales linearly with the value of  $C_{OX}$ . I.e., with a higher  $C_{OX}$ , sufficient source-drain current can already be induced by the low bias voltage, which is important to realize the low-voltage operation of devices.

By assuming the parallel plate capacitor, the value of  $C_{OX}$  can be calculated as below:

$$C_{OX} = \frac{\epsilon_{DEL}\epsilon_0}{t_{OX}},\tag{2.23}$$

where  $\epsilon_{DEL}$  is the relative dielectric constant of the dielectric material and  $t_{OX}$  is the layer thickness. To increase  $C_{OX}$ , one can either increase  $\epsilon_r$  by utilizing so-call "high-k" dielectrics or reduces the effective thickness of the resulting layer. However, both approaches are difficult in the domain of printed electronics, since stable and solution-processable "high-k" dielectrics are rare, and the printing process limits the thickness of printed materials (normally between several hundreds of nm). Until now, TFTs with both dielectric and semiconductor materials printed are often operated at high voltages (> 10 V) [48, 49, 50]. This largely hinders the realization of printed low-voltage devices to satisfy the requirements of potential applications in e.g. IoT and wearable devices, where batteries that can supply high voltages are often not available.

Alternatively, solid electrolytes can be utilized to replace conventional dielectric materials. The so-called electrolyte-gating approach is especially beneficial for the development of printed electronics from various aspects.

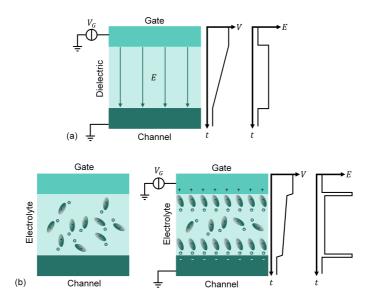

**Figure 2.12.:** Schematics of charge mechanism of (a) dielectric-gating and (b) electrolytegating approach.

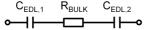

**Figure 2.13.:** Basic equivalent circuit model of electric double layers consisting of two double layer capacitance  $C_{EDL,1}$  and  $C_{EDL,2}$ , and the  $R_{BULK}$  representing the ionic resistance of the bulk electrolyte.

The primary motivation to deploy electrolytes as gating materials is the large gate capacitance produced by electric double layers (EDLs), effectively inducing a strong electric field at the channel surface already at low voltage. The advantage of electrolyte-gating can be seen by comparing with the distribution of electric field in conventional dielectric-gating.

As illustrated in Fig. 2.12(a), in conventional dielectric-gating, upon the application of the gate voltage  $V_G$ , the potential drops across the bulk of the dielectric layer, and a constant electric field is generated. In the electrolyte-gating system as shown in Fig. 2.12(b), as the positive gate voltage is applied, anions are attracted to the gate-electrolyte interface, while cations are repelled to the electrolyte-channel interface causing the charge carrier accumulation on the semiconductor surface. At the steady-state, almost all of the applied potential is dropped across those two interfaces, whereas the potential drop across the electrolyte bulk is small. Consequently, so-called EDLs are formed at the interfaces that possess a high electric field.

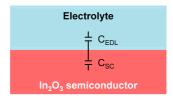

Furthermore, the electric double layer capacitor  $C_{EDL}$  can be considered as two parallel plate capacitors in series connection. In Fig. 2.13, the basic equivalent circuit model of EDLs is presented, where  $C_{EDL,1}$  and  $C_{EDL,2}$  are the two EDLs at each interface and  $R_{BULK}$  represents the ionic resistance of the bulk electrolyte. Since  $C_{EDL,1}$  and  $C_{EDL,2}$  are in series connection, the total capacitance in a double layer structure is:

$$\frac{1}{C_{EDL,total}} = \frac{1}{C_{EDL,1}} + \frac{1}{C_{EDL,2}}. (2.24)$$

In each capacitor, the thickness between two plates is in the nanometer range, defined as the Debye screening length  $\lambda_D$ . Based on the capacitance equation:

$$C_{EDL} = \frac{\epsilon_r \epsilon_0}{\lambda_D},\tag{2.25}$$

the double layer capacitance can easily exceed  $1\,\mu F\,cm^{-2}$  by assuming  $\lambda_D=1\,nm$  and  $\epsilon_r=10,$  which is at least one order of magnitude higher than the value that is attainable in conventional dielectric systems. More importantly, the high capacitance value is independent of the thickness of the resulting electrolyte layer. In Tab. 2.3, a comparison of the attainable unity capacitance and layer thickness is given between the dielectric and electrolyte materials used as gate insulators.

**Table 2.3.:** Comparison of the areal capacitance and layer thickness between the dielectric and electrolyte materials

| Material               | Areal capacitance $(\mu F cm^{-2})$ | Layer thickness<br>(nm) | Ref. |

|------------------------|-------------------------------------|-------------------------|------|

|                        | Dielecti                            | ric                     |      |

| $TiO_2$                | 0.373                               | 97                      | [51] |

| $Al_2O_3$              | 0.7                                 | 6.5                     | [52] |

| $Ta_2O_5$              | 0.136                               | 160                     | [53] |

|                        | Electrol                            | yte                     |      |

| PEO/LiCLO <sub>4</sub> | 5                                   | 400                     | [54] |

| Ionic Liquid           | 6                                   | $5 \cdot 10^4$          | [55] |

| Ionic Gel              | 12                                  | $2 \cdot 10^3$          | [56] |

Additionally, electrolyte-gating possesses more advantages. For example, many solid electrolytes are inherently printable [57, 58]. Also, it helps to realize unique material stacks to achieve new device architecture, such as the in-plane devices [59, 60]. In particular cases, electrolytes are conformable and can wet porous and rough structures effectively, which are the surface property often possessed by printed materials [61]. All those features make this technique a viable approach to fabricate printed TFT devices, which is suitable for low-voltage operation.

# 2.4. EGT technology

In this thesis, the key device under study is the electrolyte-gated field-effect transistors (EGT) incorporating indium oxide semiconductors. It utilizes precursor-derived inorganic semiconducting material which assures a high effective charge carrier mobility. Also, the deployment of electrolytes as the gate insulator provides a high gate capacitance to induce sufficient drain-source current already at low voltages. As a result, the advantages

Figure 2.14.: Material stack of EGT.

of high performance and low-voltage operation are combined in inkjetprinted transistors. Here, the technical background of EGT is explained, including its fabrication process and the I-V modeling approach.

#### 2.4.1. Fabrication

Fig. 2.14 illustrates the material stack of EGT. To fabricate the device, passive patterns for source, drain and gate electrodes are structured on ITO sputtered glass using e-beam lithography. Then, the precursor  $In(NO_3)_3 \cdot \times$ H2O ink is inkjet-printed between source and drain electrode. Through a subsequent annealing process at 400 °C, the In<sub>2</sub>O<sub>3</sub> channel is formed. Next, the lithium-ion based composite solid polymer electrolyte (CSPE) is prepared by mixing two solutions: 0.05 g of LiCLO<sub>4</sub> dissolved in 0.45 g propylene carbonate (PC), and 0.213 g of Polyvinyl alcohol (PVA) dissolved in 4.29 g of dimethyl sulfoxide (DMSO). The mixture solution is printed on top of the channel, fully covering the channel region and partially overlapping with source and drain electrodes. Until now, the EGT with in-plane architecture has been realized if CSPE also connects with the gate electrode. To fabricate the top-gate architecture, the additional conductive polymer poly(3,4-ethylenedioxythiophene) polystyrene sulfonate (PEDOT:PSS) is printed on the top of CSPE while connecting to the gate electrode.

### 2.4.2. I-V modeling

To enable the circuit simulation, the static I-V characteristics of EGTs have to be modelled. Here, the extended Enz–Krummenacher–Vittoz (EKV) model has been used [62, 63]. The drain-source current equation is defined as below:

$$I_{DS} = I_0 \cdot (ln(f_3 + e^{\frac{v_p - v_s}{2}})^{\gamma} - ln(f_3 + e^{\frac{v_p - v_d}{2}})^{\gamma}), \tag{2.26}$$

$$I_0 = 2nf_1 \frac{W}{L} \phi_t^2, (2.27)$$

$$n = \frac{1}{S \cdot \phi_t \cdot ln(10)},\tag{2.28}$$

where n is the slope factor and S is the sub-threshold slope;  $v_p$ ,  $v_s$  and  $v_d$  represent channel, source and drain voltage normalized by the thermal voltage  $\phi_t$ , which are expressed as below:

$$\phi_t = \frac{k_B T}{q} = \frac{V_D}{v_d} = \frac{V_S}{v_s},$$

(2.29)

$$v_p \approx \frac{V_{GS} - (V_{th} - f_4 V_{DS})}{\frac{n}{f_2} \phi_t},$$

(2.30)

with  $k_B$  as the Boltzmann constant, T the temperature, q the elementary charge and  $V_{th}$  the threshold voltage;  $f_{1-4}$  are fitting parameters which tune the modelled I-V characteristics in different regions.

# 3. Capacitance in EGTs

# 3.1. Background