The Karlsruhe Series on Software Design and Quality

32

Model-Based Performance

Prediction for Concurrent Software

on Multicore Architectures –

A Simulation-Based Approach

Markus Kilian Frank

#### Markus Kilian Frank

# **Model-Based Performance Prediction for Concurrent Software on Multicore Architectures**

A Simulation-Based Approach

# The Karlsruhe Series on Software Design and Quality Volume 32

Dependability of Software-intensive Systems group Faculty of Computer Science Karlsruhe Institute of Technology

and

Software Engineering Division Research Center for Information Technology (FZI), Karlsruhe

Editor: Prof. Dr. Ralf Reussner

# Model-Based Performance Prediction for Concurrent Software on Multicore Architectures

A Simulation-Based Approach

by Markus Kilian Frank

Dissertation, Universität Stuttgart Fakultät 5: Informatik, Elektrotechnik und Informationstechnik

Model-Based Performance Prediction for Concurrent Software on Multicore Architectures – A Simulation-Based Approach

von Markus Kilian Frank

Tag der mündlichen Prüfung: 15. März 2021 Hauptberichter: Prof. Dr.-Ing. Steffen Becker

Mitberichter: Prof. Dr. Ralf H. Reussner

#### Impressum

Karlsruher Institut für Technologie (KIT) KIT Scientific Publishing Straße am Forum 2 D-76131 Karlsruhe

KIT Scientific Publishing is a registered trademark of Karlsruhe Institute of Technology. Reprint using the book cover is not allowed.

www.ksp.kit.edu

This document – excluding parts marked otherwise, the cover, pictures and graphs – is licensed under a Creative Commons Attribution-Share Alike 4.0 International License (CC BY-SA 4.0): https://creativecommons.org/licenses/by-sa/4.0/deed.en

The cover page is licensed under a Creative Commons Attribution-No Derivatives 4.0 International License (CC BY-ND 4.0): https://creativecommons.org/licenses/by-nd/4.0/deed.en

Print on Demand 2022 - Gedruckt auf FSC-zertifiziertem Papier

ISSN 1867-0067 ISBN 978-3-7315-1146-5 DOI: 10.5445/KSP/1000139935

# Model-Based Performance Prediction for Concurrent Software on Multicore Architectures—A Simulation-Based Approach

Von der Fakultät für Informatik, Elektrotechnik und Informationstechnik der Universität Stuttgart zur Erlangung der Würde eines Doktors der Naturwissenschaften (Dr. rer. nat.) genehmigte Abhandlung

#### Vorgelegt von Markus Kilian Frank

aus Bensheim

Hauptberichter: Prof. Dr.-Ing. Steffen Becker

Mitberichter: Prof. Dr. Ralf H. Reussner

Tag der mündlichen Prüfung: 15. März 2021

Institut für Software Engineering, Abteilung Softwarequalität und -architektur 2021

### **Abstract**

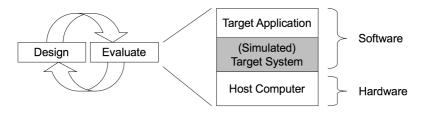

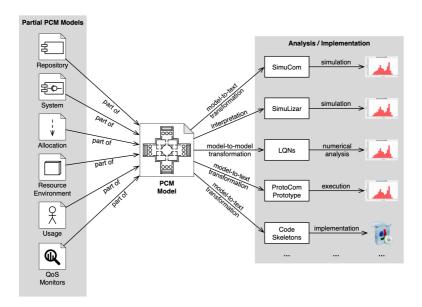

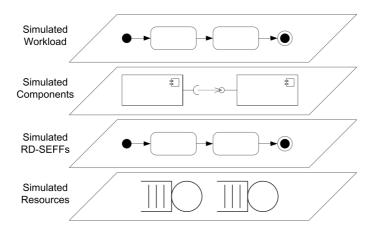

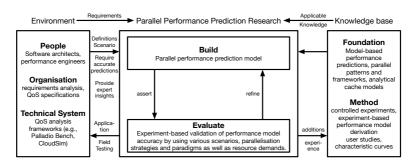

Model-based performance prediction is a well-known concept to ensure the quality of software. Thereby, software architects create abstract architectural models and specify software behaviour, hardware characteristics, and the user's interaction. They enrich the models with performance-relevant characteristics and use performance models to solve the models or simulate the software behaviour. Doing so, software architects can predict quality attributes such as the system's response time. Thus, they can detect violations of service-level objectives already early during design time, and alter the software design until it meets the requirements.

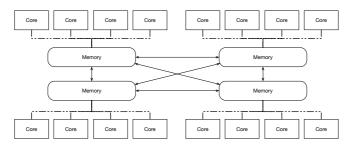

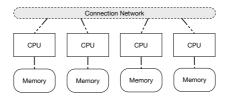

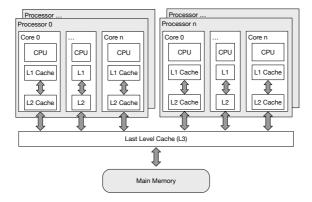

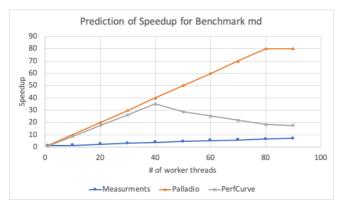

Current state-of-the-art tools like Palladio have proven useful for over a decade now, and provide accurate performance prediction not only for sophisticated, but also for distributed cloud systems. They are built upon the assumption of single-core CPU architectures, and consider only the clock rate as a single metric for CPU performance. However, current processor architectures have multiple cores and a more complex design. Therefore, the use of a single-metric model leads to inaccurate performance predictions for parallel applications in multicore systems.

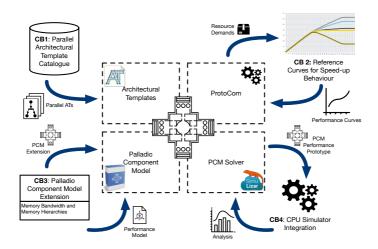

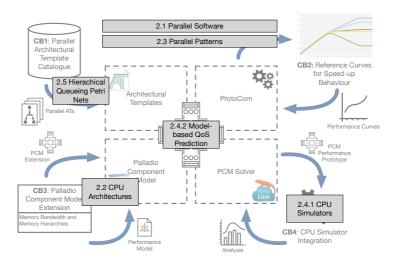

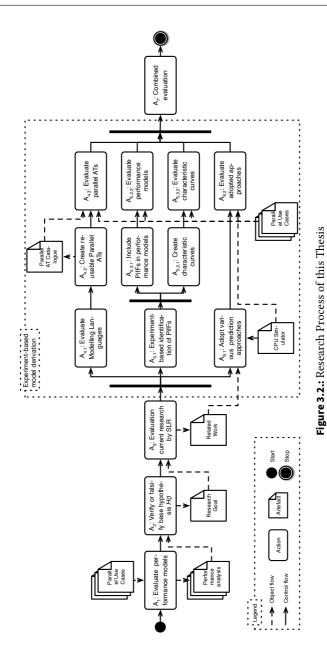

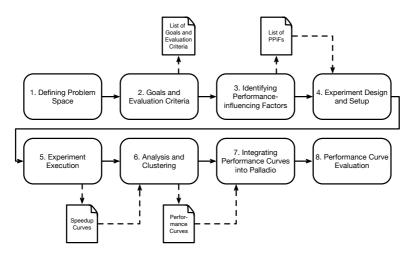

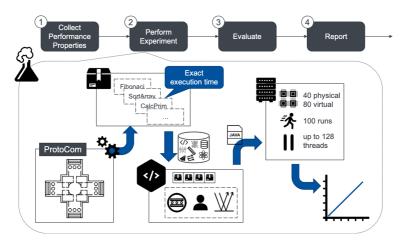

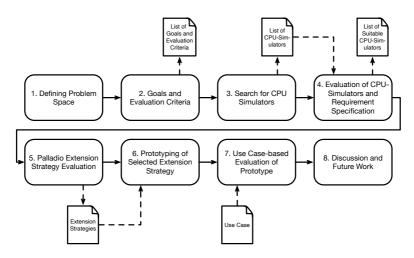

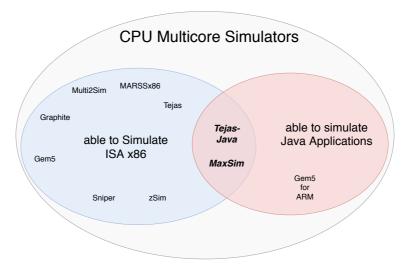

In the course of this thesis, we face the challenges for model-based performance predictions which arise from multicore processors, and present multiple strategies to extend performance prediction models. In detail, we (1) discuss the use of multicore CPU simulators used by CPU vendors; (2) conduct an extensive experiment to understand the effect of performance-influencing factors on the performance of parallel software; (3) research multi-metric models to reflect the characteristics of multicore CPUs better, and finally, (4) investigate the capabilities of software modelling languages to express massively parallel behaviour.

As a contribution of this work, we show that (1) multicore CPU simulators simulate the behaviour of CPUs in detail and accurately. However, when

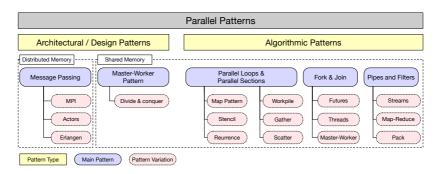

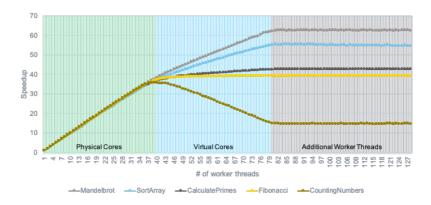

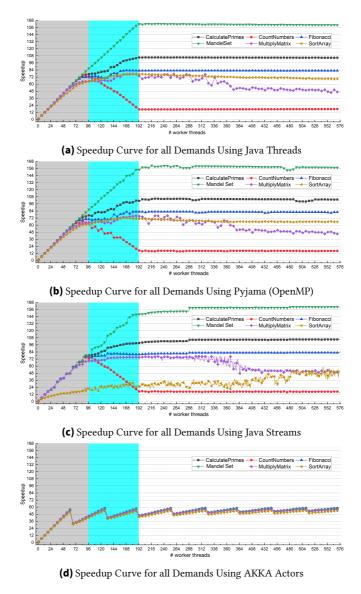

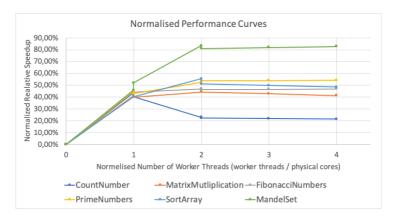

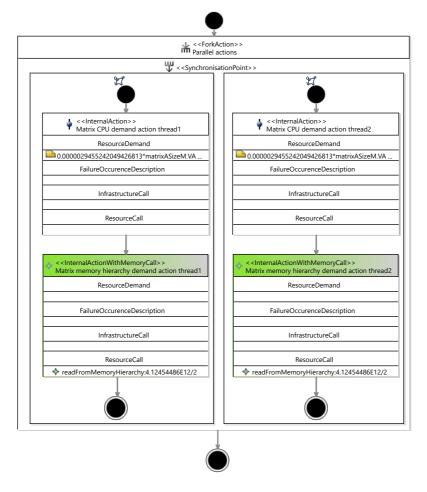

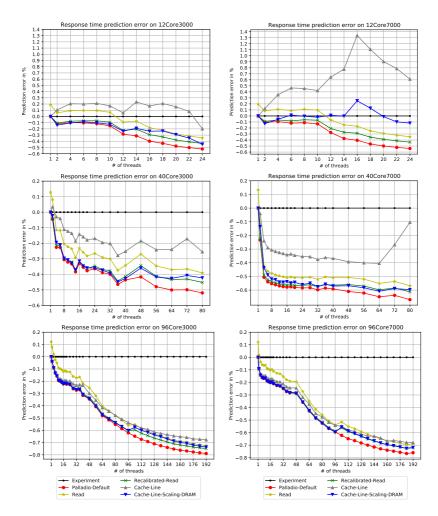

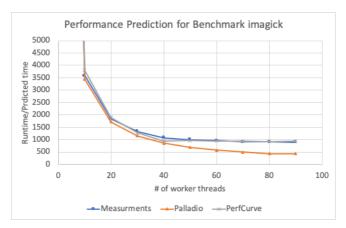

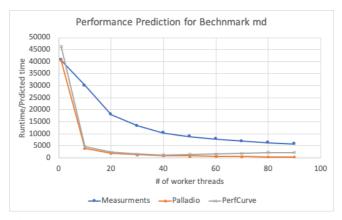

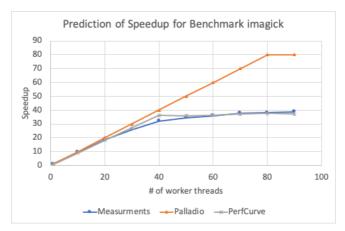

using architectural models as input, the simulation results are very inaccurate. (2) Due to extensive experiments, we present a set of performance curves that reflect the behaviour of characteristic demand types. We included the performance curves into Palladio and have increased the performance predictions significantly. (3) We present an enhanced multi-metric hardware model, which reflects the memory architecture of modern multicore CPUs. (4) We provide a parallel architectural pattern catalogue, which includes four of the most common parallelisation patterns (i.e., parallel loops, pipes and filter, fork/join, master worker). Through this catalogue, we enable the software architect to model the parallel behaviour of software faster and with fewer errors.

# Zusammenfassung

Modellbasierte Performancevorhersagen sind ein bekanntes Konzept zur Sicherung der Qualität von Software. Dabei erstellen Softwarearchitekten abstrakte Architekturmodelle und spezifizieren das Softwareverhalten, die Hardwareeigenschaften und die Interaktion der Nutzer. Sie reichern die Modelle mit leistungsrelevanten Eigenschaften an und verwenden Performancemodelle, um das Software-Verhalten zu simulieren oder durch analytische Methoden zu bestimmen. Auf diese Weise können die Software-Architekten Qualitätsmerkmale wie die Antwortszeit des Systems auf Benutzeranfragen vorhersagen. So können sie Verletzungen der Service-Level-Ziele bereits anhand des Entwurfs erkennen und den Software-Entwurf so lange verändern, bis er den Anforderungen entspricht.

Palladio ist ein Werkzeug, das dem aktuellen Stand der Technik entspricht und sich seit über einem Jahrzehnt bewährt hat. Palladio bietet eine genaue Performancevorhersage nicht nur für anspruchsvolle, sondern auch für verteilte Systeme. Dabei baut Palladio auf der Annahme von Single-Core-CPU-Architekturen auf und berücksichtigt nur die Taktrate als einzige Metrik. Aktuelle Prozessorarchitekturen haben jedoch mehrere Kerne und ein komplexeres Design. Daher führt die Verwendung eines Modells mit nur einer Metrik zu ungenauen Performancevorhersagen für parallele Anwendungen in Mehrkernsystemen.

Im Verlauf dieser Arbeit stellen wir uns den Herausforderungen für modellbasierte Performancevorhersagen, die sich aus Mehrkernprozessoren ergeben, und präsentieren mehrere Strategien zur Erweiterung von Performancevorhersagemodellen. Im Detail diskutieren wir (1) die Verwendung von Mehrkern-CPU-Simulatoren, die von CPU-Herstellern verwendet werden; (2) Wir führen ein umfangreiches Experiment durch, um den Einfluss von leistungsbeeinflussenden Faktoren auf die Performance paralleler Software zu verstehen; (3) Wir erforschen multimetrische Modelle, um die Eigenschaften

von Mehrkern-CPUs besser widerzuspiegeln; (4) und schließlich untersuchen wir die Fähigkeiten von Software-Modellierungssprachen, massiv paralleles Verhalten auszudrücken.

Als Beitrag dieser Arbeit können wir zeigen, dass (1) Multicore-CPU-Simulatoren das Verhalten von CPUs detailliert und genau simulieren. Wenn jedoch Architekturmodelle als Input für die Simulatoren verwendet werden, sind die Simulationsergebnisse von geringer Qualität. (2) Aufgrund der umfangreichen Experimente können wir eine Reihe von Referenzkurven präsentieren, die das Verhalten von charakteristischen Lasten widerspiegeln. Wir haben die Referenzkurven in Palladio integriert und können die Performancevorhersagen erheblich steigern. (3) Wir stellen ein verbessertes multimetrisches Hardware-Modell vor, das die Speicherarchitektur moderner Mehrkern-CPUs widerspiegelt. (4) Wir stellen einen Katalog paralleler Architekturmuster zur Verfügung, der vier der gängigsten Parallelisierungsmuster enthält. Durch diesen Katalog ermöglichen wir es dem Software-Architekten, das Parallelverhalten von Software wesentlich schneller und mit weniger Fehlern zu modellieren.

# **Acknowledgements**

Writing a doctoral thesis is a long and arduous journey with many ups and downs. Mastering the road alone is almost impossible. Therefore, I would like to take a moment and thank all the people who supported me during the past five years.

First of all, I would like to thank my amazing wife, Judith, for her unconditional support, her warm words, and her trust and belief in me. Her constant support did not only eased my mind when I needed to relax, but also gave me the strength to push forward. Deciding to continue my PhD and follow Steffen to Stuttgart forced us back into a long-distance relationship. But this did not stop you from loving me, giving me comfort, and finally marrying me. Judith, I love you more than anything!

No fewer thanks go to my parents: My father Klaus, who is a bright inspiration for me. If it were not for him, I never would have started my PhD and followed his example. Now I hope I am one step closer to being as great as you, Dad. My beloved mother, Anne, was there for me from the beginning. She supports me through all my life and always wants only the best for me. Mum, Dad, you are the best!

Next in line, I have to show my gratitude to all my workmates, first of all, my supervisor Steffen. He moved mountains and fought giants to make it possible for me to start at the university in the first place after my application e-mail was the victim of a spam filter and therefore missed the application deadline. But that is not all: His great feedback always guided me through the foggy journey of my PhD. Thank you for that!

In this context, I would like to thank all my colleagues in Chemnitz. Especially Marcus, who translated and taught me the rules of research as a young researcher. His long discussions helped me to understand the disastrous reviewer comments of rejected papers and helped me to improve. Marcus

is someone to push deadlines with until the last minute, even if that means working all night—or at least as long as there is coffee.

Of course, I also thank all my "Doktorgeschwister": Marina, Thomas, Henning, Floriment, Alireza, Vijayshree, Sebastian F., Sandro, Angelika, Stephan, Max, Maximilian, Sebastian K., Heiko as well as the rest of my colleagues André, Jörg, Robert, and Erik for their many hours of discussions, advice, reviews, feedback and research meetings. Especially I would like to highlight here the contributions of Floriment and Alireza—your feedback on the thesis helped me a lot.

Excellent research is not done alone. Thus, a great thanks go to all students I had the pleasure to work with in the past five years. In particular to Denis, Julian, Kim, Lukas, Philipp, and Sebastian. Your high interest in the topics was great, and it was a pleasure to work with you. Finally, I have to admit that writing a doctoral thesis, can be not only hard for the writer, but also his whole environment. In this sense, I would also like to thank all my dear friends for their support, motivational words, feedback, and time they spent drinking beer with me and listening to me grumbling about my work.

Thank you.

# **Contents**

| Ab | stract | i                                                      |

|----|--------|--------------------------------------------------------|

| Zu | samm   | enfassung                                              |

| Ac | knowl  | edgements                                              |

| l. | Intro  | oduction and Foundation                                |

| 1. | Intro  | oduction                                               |

|    | 1.1.   | Requirements for Model-based Performance Predictions 6 |

|    | 1.2.   | Problem Statement                                      |

|    | 1.3.   |                                                        |

|    | 1.4.   | Thesis Structure                                       |

| 2. | Four   | ndations                                               |

|    | 2.1.   |                                                        |

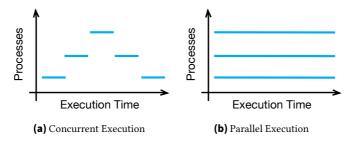

|    |        | 2.1.1. Parallel vs. Concurrent                         |

|    |        | 2.1.2. Shared vs. Distributed Memory                   |

|    |        | 2.1.3. Means to Parallelise                            |

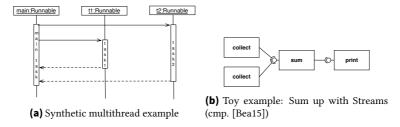

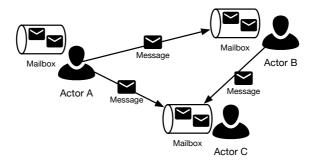

|    |        | 2.1.4. Thread-Based vs. Message-Based                  |

|    | 2.2.   |                                                        |

|    |        | 2.2.1. Architectural Design                            |

|    |        | 2.2.2. Common CPU Architecture Example                 |

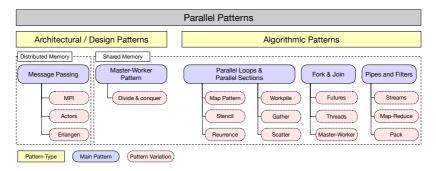

|    | 2.3.   | Parallel Programming Patterns                          |

|    |        | 2.3.1. Patterns for Parallel Programming               |

|    |        | 2.3.2. Parallel Architectural & Design Patterns 26     |

|    |        | 2.3.3. Algorithmic Patterns                            |

|    | 2.4.   |                                                        |

|    |        | 2.4.1. CPU Simulators                                  |

|    |      | 2.4.2.   | Model-Based Quality-of-Service Predictions on           |

|----|------|----------|---------------------------------------------------------|

|    |      |          | Architectural Level                                     |

|    | 2.5. | Hierar   | chical Queueing Petri Nets                              |

|    |      | 2.5.1.   | Petri Nets                                              |

|    |      | 2.5.2.   | Queuing Petri Nets                                      |

|    | 2.6. | Summ     | ary of Foundations                                      |

| 3. | Rese | earch De | sign                                                    |

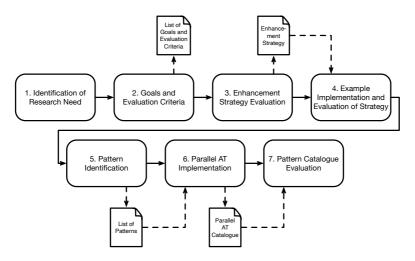

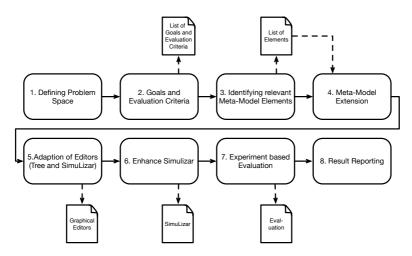

|    | 3.1. | Resear   | rch Method                                              |

|    | 3.2. | Resear   | rch Questions                                           |

|    |      | 3.2.1.   | $RQ_1$ : Performance Modelling of Parallel Behaviour 52 |

|    |      | 3.2.2.   | $RQ_2$ : Behaviour of Highly Parallel Applications 55   |

|    |      | 3.2.3.   | $RQ_3$ : Performance Prediction Models                  |

|    |      | 3.2.4.   | $RQ_4$ : CPU Simulators                                 |

|    | 3.3. | Resear   | rch Design Evaluation                                   |

|    | 3.4. | Design   | n Science Guidelines                                    |

| 4. | Rela | ted Wor  | <b>k</b>                                                |

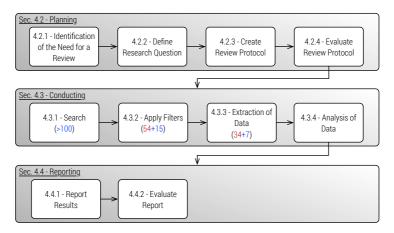

|    | 4.1. | SLR O    | verview                                                 |

|    | 4.2. | SLR Pl   | lanning                                                 |

|    |      | 4.2.1.   | -                                                       |

|    |      | 4.2.2.   | Review Protocol                                         |

|    |      | 4.2.3.   | Evaluate Review Protocol                                |

|    | 4.3. | SLR C    | onducting                                               |

|    |      | 4.3.1.   | Executing the Search                                    |

|    |      | 4.3.2.   | Applying the Filters                                    |

|    |      | 4.3.3.   | Extracting the Data                                     |

|    |      | 4.3.4.   | Analysing the Data                                      |

|    | 4.4. | SLR Re   | eporting                                                |

|    |      |          | Report Results                                          |

|    |      | 4.4.2.   | -                                                       |

|    | 4.5. | Threat   | ts to Validity                                          |

|    | 4.6. |          | ary                                                     |

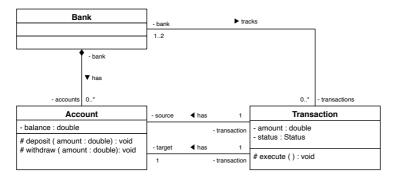

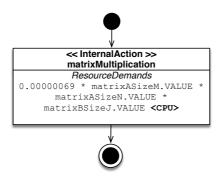

| 5. | Runi | ning Exa | imple: Resource Demands                                 |

|    | 5.1. | _        | rce Demanding Examples                                  |

|    |      | 5.1.1.   | 8 1                                                     |

|    |      | 5.1.2    | Mandelbrot Set                                          |

|     | 5.2. | 5.1.3.<br>5.1.4.<br>5.1.5.<br>5.1.6.<br>5.1.7.<br>Comp<br>5.2.1.<br>5.2.2. | Sorting Arrays86Calculating Primes88Counting Numbers89Matrix Multiplication90Summary91lex Examples91Bank Transaction Example92SPEC Benchmarks93 |

|-----|------|----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| II. | Cont | ributio                                                                    | <b>ns</b>                                                                                                                                       |

| 6.  | Cont | ributio                                                                    | n (CB) <sub>1</sub> : Parallel Architectural Pattern Catalogue 99                                                                               |

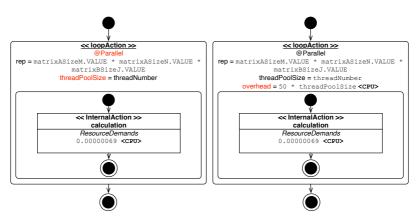

|     | 6.1. | Proble                                                                     | em Space                                                                                                                                        |

|     |      | 6.1.1.                                                                     | General Information                                                                                                                             |

|     |      | 6.1.2.                                                                     | Implementation                                                                                                                                  |

|     |      | 6.1.3.                                                                     | Modelling                                                                                                                                       |

|     |      | 6.1.4.                                                                     | Experiment Evaluation                                                                                                                           |

|     | 6.2. | Proble                                                                     | em Specification - Challenges and Goals 106                                                                                                     |

|     |      | 6.2.1.                                                                     | Goals                                                                                                                                           |

|     |      | 6.2.2.                                                                     | Evaluation Metrics                                                                                                                              |

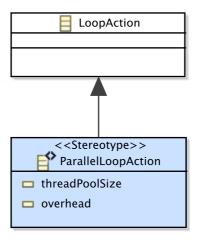

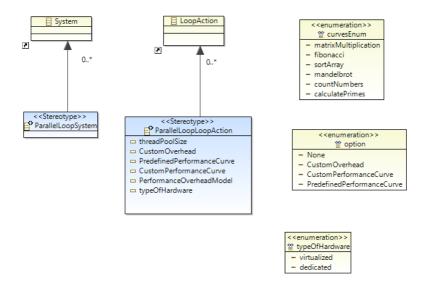

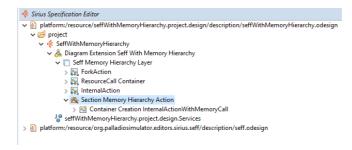

|     | 6.3. | Model                                                                      | lling Language Extension                                                                                                                        |

|     |      | 6.3.1.                                                                     | Diagram Types                                                                                                                                   |

|     |      | 6.3.2.                                                                     | Extension Concepts                                                                                                                              |

|     |      | 6.3.3.                                                                     | Diagram and Concept Evaluation                                                                                                                  |

|     |      | 6.3.4.                                                                     | Enhancement Process                                                                                                                             |

|     | 6.4. | Proof                                                                      | of Concept Evaluation                                                                                                                           |

|     |      | 6.4.1.                                                                     | Result-based Evaluation                                                                                                                         |

|     |      | 6.4.2.                                                                     | Goal-based Evaluation                                                                                                                           |

|     |      | 6.4.3.                                                                     | Metrics-based Evaluation                                                                                                                        |

|     | 6.5. | Buildi                                                                     | ng a Pattern Catalogue                                                                                                                          |

|     |      | 6.5.1.                                                                     | Pattern Identification                                                                                                                          |

|     |      | 6.5.2.                                                                     | Pattern Categorisation                                                                                                                          |

|     |      | 6.5.3.                                                                     | Pattern Selection                                                                                                                               |

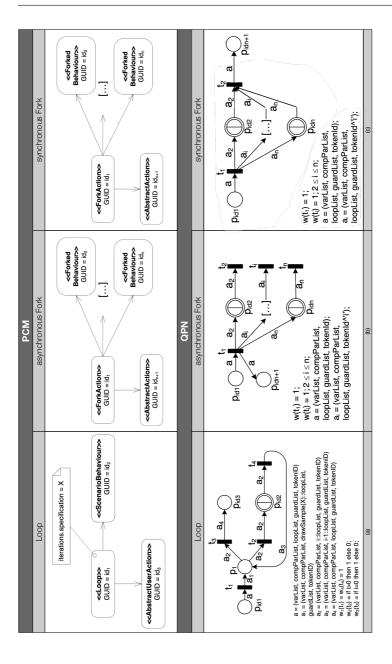

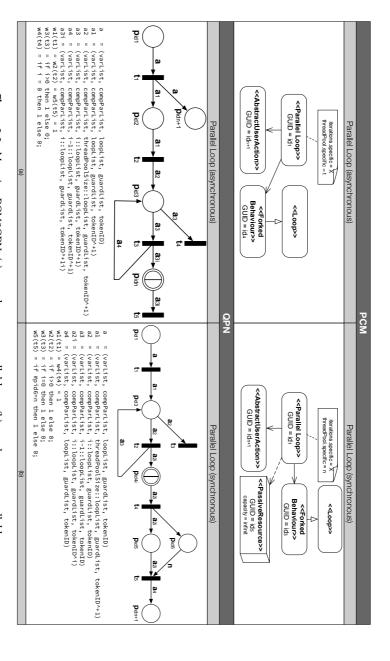

|     | 6.6. | Forma                                                                      | d Semantics for Parallel Behaviour in the PCM 129                                                                                               |

|     |      | 6.6.1.                                                                     | Mapping of general PCM Components 130                                                                                                           |

|     |      | 6.6.2.                                                                     | Mapping of Parallel Behaviour to Queuing Petri                                                                                                  |

|     |      |                                                                            | Net (OPN)                                                                                                                                       |

|    |                   | 6.6.3.  | Evaluation of the Mapping of Parallel Architectural |

|----|-------------------|---------|-----------------------------------------------------|

|    |                   |         | Template (AT)s to QPN                               |

|    |                   | 6.6.4.  | Upshot                                              |

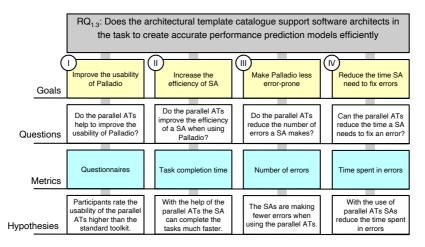

|    | 6.7.              | Empir   | ical Evaluation of the Parallel AT Catalogue 139    |

|    |                   | 6.7.1.  | Experiment Design                                   |

|    |                   | 6.7.2.  | Study Conduction                                    |

|    |                   | 6.7.3.  |                                                     |

|    | 6.8.              | Transf  | ferability and Limitations                          |

|    |                   | 6.8.1.  |                                                     |

|    |                   | 6.8.2.  | Limitations of the Parallel AT Catalogue 148        |

|    | 6.9.              | Summ    | nary of CB <sub>1</sub>                             |

| 7. | CB <sub>2</sub> : | Perforr | mance Curves for Parallel Behaviour                 |

|    | 7.1.              |         | em Space                                            |

|    |                   | 7.1.1.  | 1                                                   |

|    |                   | 7.1.2.  |                                                     |

|    |                   | 7.1.3.  | •                                                   |

|    | 7.2.              | Paralle | el Performance-influencing Factors                  |

|    |                   | 7.2.1.  | 5                                                   |

|    |                   |         | Collection                                          |

|    |                   | 7.2.2.  | Prioritising                                        |

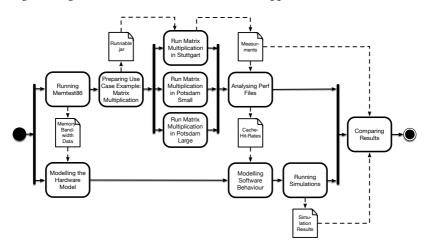

|    | 7.3.              | Experi  | iment-Based Performance Evaluation 161              |

|    |                   | 7.3.1.  | Experiment Design                                   |

|    |                   | 7.3.2.  | Experiment Environment                              |

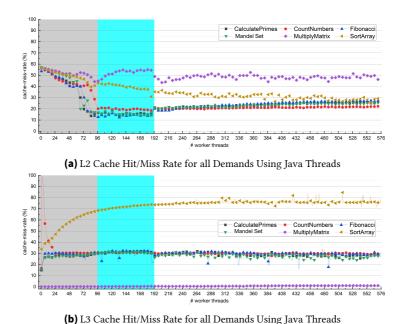

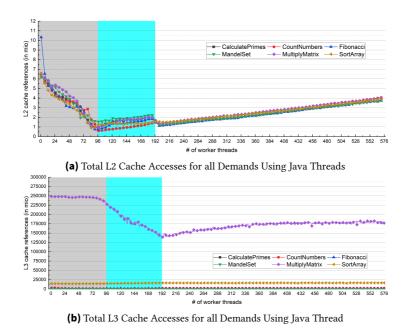

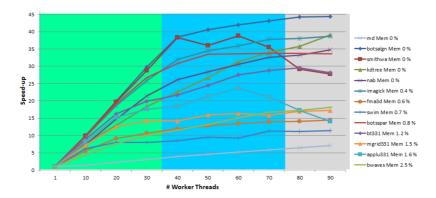

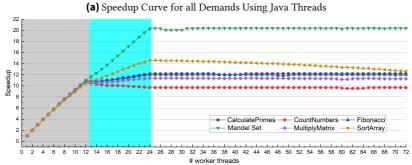

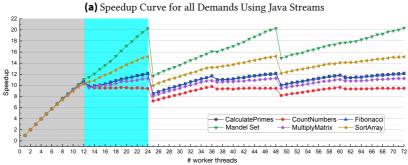

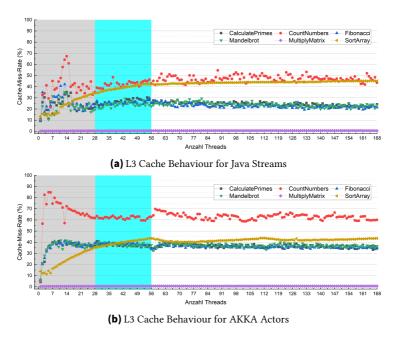

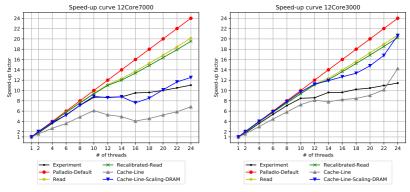

|    | 7.4.              | Measu   | rements and Results                                 |

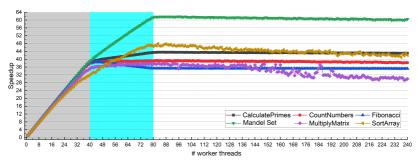

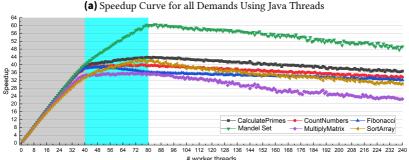

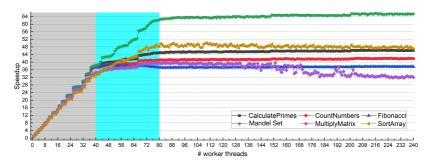

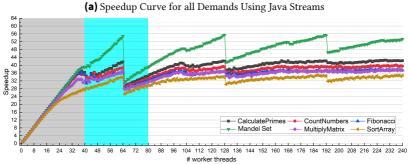

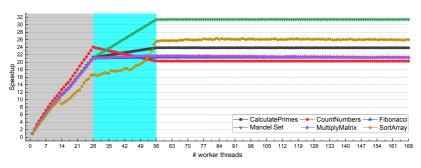

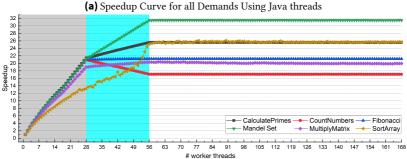

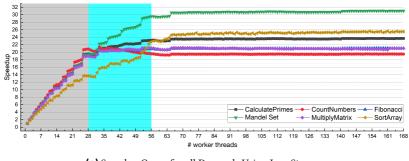

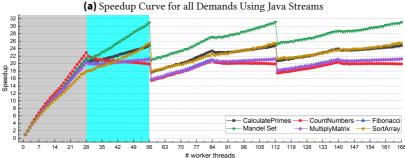

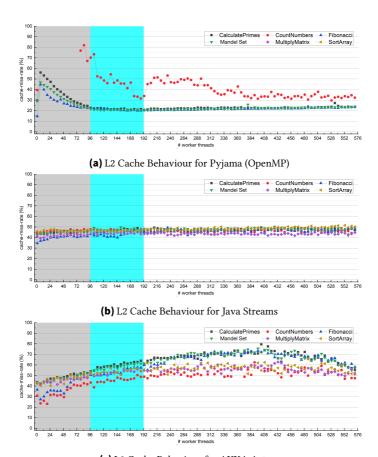

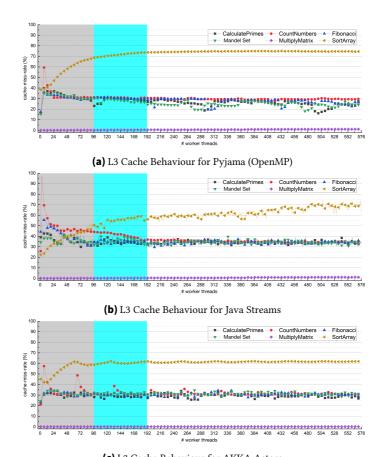

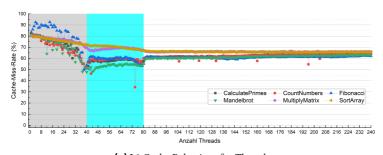

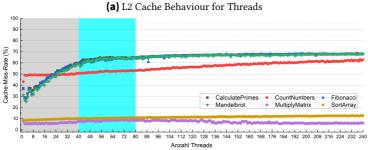

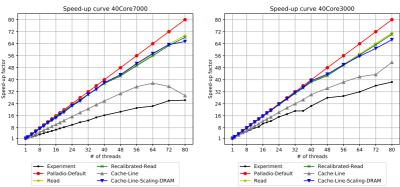

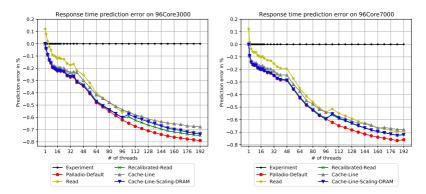

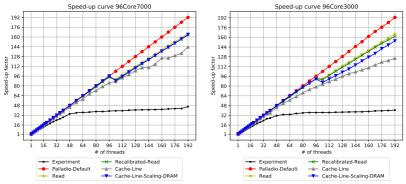

|    |                   | 7.4.1.  | Result Report Server Stuttgart                      |

|    |                   | 7.4.2.  | Comparison of Parallelisation Paradigms 171         |

|    |                   | 7.4.3.  | Comparison Server                                   |

|    |                   | 7.4.4.  | Lessons Learned                                     |

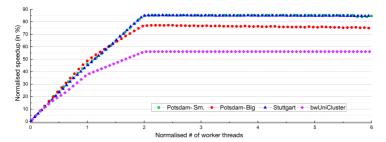

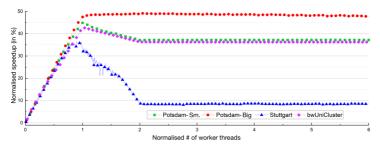

|    | 7.5.              | Extrac  | cting Performance Curves                            |

|    |                   | 7.5.1.  | Normalisation                                       |

|    |                   | 7.5.2.  | Clustering                                          |

|    |                   | 7.5.3.  | Staging                                             |

|    |                   | 7.5.4.  | Extraction                                          |

|    |                   | 7.5.5.  | Using Performance Curves: An Example 178            |

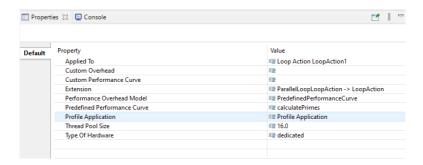

|    | 7.6.              | Pallad  | io Integration                                      |

|    |                   | 7.6.1.  | Profile Extension                                   |

|    |                   | 7.6.2.  | Workflow Adaptation                                 |

|    |                          | 7.6.3. OVT-o Transformation                        |

|----|--------------------------|----------------------------------------------------|

|    | 7.7.                     | Evaluation                                         |

|    |                          | 7.7.1. Method                                      |

|    |                          | 7.7.2. Results                                     |

|    | 7.8.                     | Assumptions & Threats to Validity                  |

|    | 7.9.                     | Summary of $CB_2$                                  |

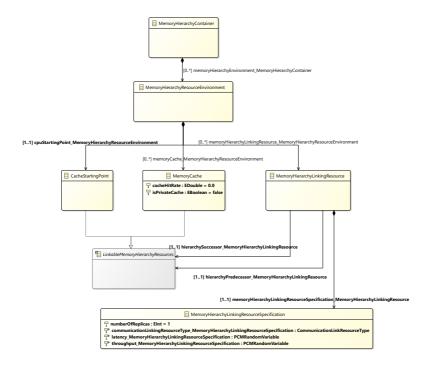

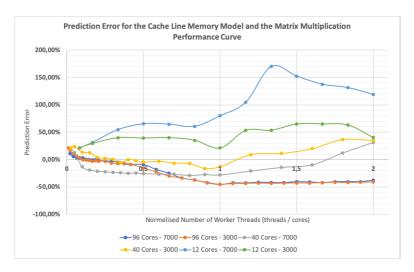

| 8. |                          | Meta-Model Extension for the PCM to Include Memory |

|    | Arch                     | <b>itectures</b>                                   |

|    | 8.1.                     | Problem Space                                      |

|    | 8.2.                     | Meta-Model Extension                               |

|    |                          | 8.2.1. Meta-Model Elements                         |

|    |                          | 8.2.2. Meta-Model Extension Strategies 200         |

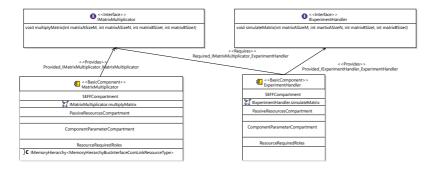

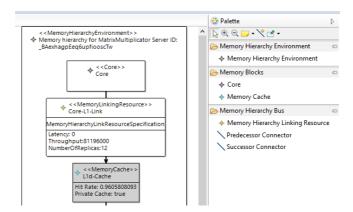

|    |                          | 8.2.3. Hardware Model Extension 201                |

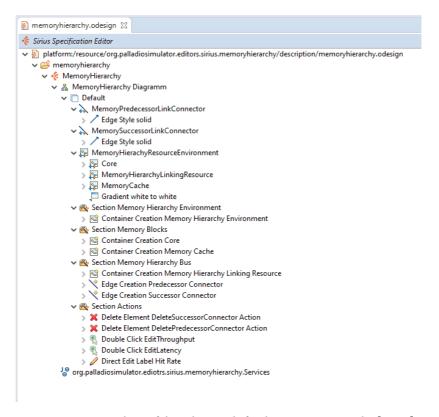

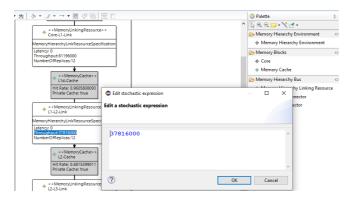

|    |                          | 8.2.4. Modelling Memory Behaviours 205             |

|    | 8.3.                     | Adaptation of PCM Solvers                          |

|    | 8.4.                     | Adaptation of Modelling Editors 209                |

|    | 8.5.                     | Evaluation of PCM Extension                        |

|    |                          | 8.5.1. Experiment Setup                            |

|    |                          | 8.5.2. Model Calibration                           |

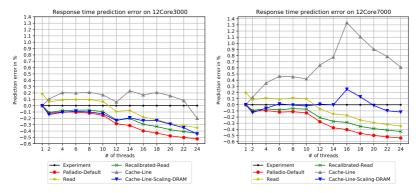

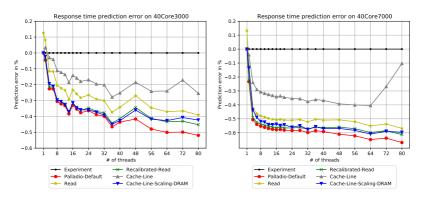

|    |                          | 8.5.3. Results                                     |

|    |                          | 8.5.4. Result Summary                              |

|    |                          | 8.5.5. Discussion and Lessons Learned 221          |

|    | 8.6.                     | Threats to Validity & Limitations                  |

|    | 8.7.                     | Summary of $CB_3$                                  |

| 9. | <b>CB</b> <sub>4</sub> : | CPU Simulators                                     |

|    | 9.1.                     | Problem Space                                      |

|    |                          | 9.1.1. Idea and Goal                               |

|    |                          | 9.1.2. Problem Specification                       |

|    | 9.2.                     | Overview of Multicore CPU Simulators 230           |

|    |                          | 9.2.1. Search Strategy                             |

|    |                          | 9.2.2. Trace-based Simulators                      |

|    |                          | 9.2.3. Source Code-based Simulators 233            |

|    |                          | 9.2.4. Evaluation and Selection                    |

|    | 9.3.                     | Palladio Extension Strategies                      |

|    | 9.4.                     | Trace-driven Strategy                              |

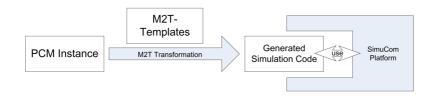

|    |                          | 9.4.1 SimuCom 241                                  |

|      |              | 9.4.2. Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

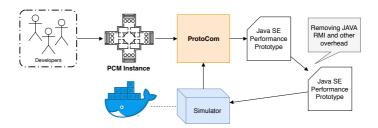

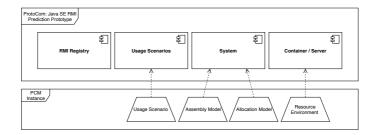

|      | 9.5.         | Source Code-Driven Strategy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

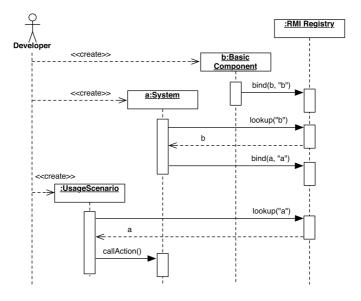

|      |              | 9.5.1. Removal of Java RMI Communication 243                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

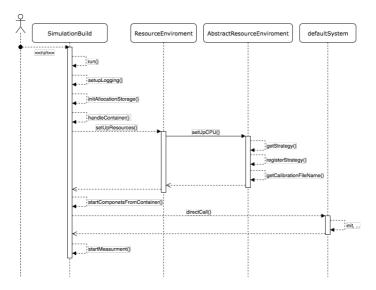

|      |              | 9.5.2. ProtoCom Calibration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      |              | 9.5.3. Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

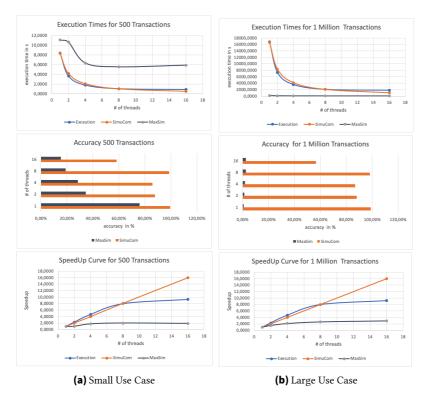

|      | 9.6.         | Execution and Use Case Evaluation 244                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|      |              | 9.6.1. Use Case and Process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      |              | 9.6.2. Setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|      |              | 9.6.3. Execution & Measurements 246                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|      |              | 9.6.4. Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      | 9.7.         | Summary of $CB_4$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| III. | Evalu        | action and Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 10.  | Evalu        | nation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

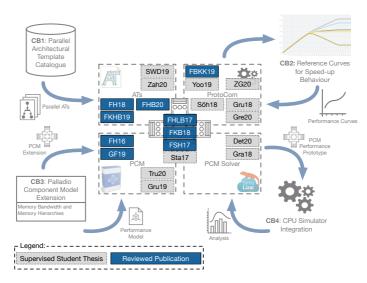

|      |              | Combination of Contributions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|      |              | 10.1.1. Combination of CB <sub>1</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|      |              | 10.1.2. Combination of $CB_2$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      |              | 10.1.3. Combination of CB <sub>3</sub> and CB <sub>4</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|      | 10.2.        | Research Goal Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      |              | 10.2.1. Answering the Research Questions 261                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|      |              | 10.2.2. Assess Requirement Fulfilment 261                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |