# Entwicklung und Charakterisierung von Integrierten Sensoren für die Teilchenphysik

Zur Erlangung des akademischen Grades eines

### DOKTORS DER NATURWISSENSCHAFTEN (Dr. rer. nat.)

von der KIT-Fakultät für Physik des Karlsruher Instituts für Technologie (KIT) angenommene

### **DISSERTATION**

von

M.Sc. Rudolf Schimassek

aus Reutlingen

Tag der mündlichen Prüfung: 03.12.2021

Referent: Prof. Dr. rer. nat. Thomas Müller Korreferent: Prof. Dr. rer. nat. Ivan Perić

Karlsruhe, den 16. Dezember 2021

## Deutsche Zusammenfassung

Siliziumsensoren werden in der Teilchenphysik für die Spurrekonstruktion in Beschleunigerexperimenten eingesetzt. Für künftige Experimente werden große Spurdetektoren benötigt.

Für derem Realisierung sind neue Technologien wie monolithische Hochspannungs-CMOSPixelsensoren (CMOS – komplementäre Metall-Oxid-Halbleiter), die in kommerziellen

Prozessen hergestellt werden [Per07] notwendig. Aufgrund der Integration von aktiven

Schaltungselementen (wie Verstärkern und Komparatoren) in die Pixel werden diese Sensoren auch als monolithische, aktive Pixelsensoren (MAPS) bezeichnet. Die Verwendung

einer hohen Depletionsspannung (im Vergleich zur Versorgungsspannung) wird im Präfix der Bezeichnung HV-MAPS kenntlich gemacht. Mit dieser Technologie können große

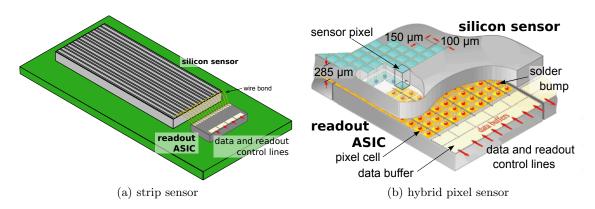

Sensorflächen relativ konstengünstig realisiert werden [Ehr21]. Im Vergleich zu den bisher

häufig genutzten hybriden Pixelsensoren ist kein Auslesechip notwendig, was auch zum

Wegfall des Bump-Bondprozesses führt und Kosten und Komplexität des Aufbaus senkt.

Dieser monolithische Sensortyp wird unter anderem am KIT ASIC- und Detektorlabor (KIT-ADL) entwickelt. Die Entwicklung beinhaltet die Konzeption und Umsetzung der Schaltungen auf dem Sensor-ASIC (anwendungsspezifischer integrierter Schaltkreis), sowie die Testkampagnen der produzierten Sensoren. Für letztere sind angepasste Testumgebungen notwendig, die ebenfalls in der Gruppe entwickelt werden. Die Ergebnisse der Untersuchungen werden für die Entwicklung der nächsten Generation der Sensoren genutzt.

In dieser Arbeit wurden Beiträge zu allen dieser Schritte in der Entwicklung eines Prototypen für die Spezifikationen für das ATLAS Inner-Tracker-Upgrade [ATL17] geleistet. Der entwickelte monolithische Sensor ist die dritte Generation für diese Anwendung, der ATLASPix3. Die Beiträge sind im Einzelnen:

- Die Konzeption der Systemebene von monolithischen Sensoren, für die ein Simulations-Framework "ReadOut Modelling Environment" (ROME) entwickelt und für den ATLASPix3 angewendet wurde.

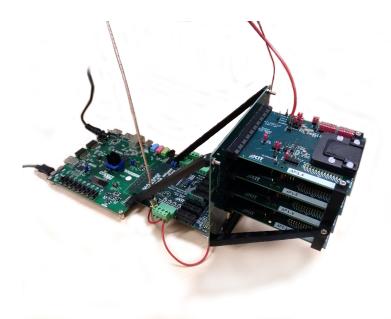

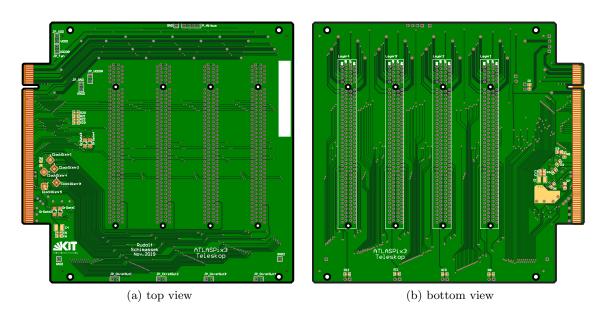

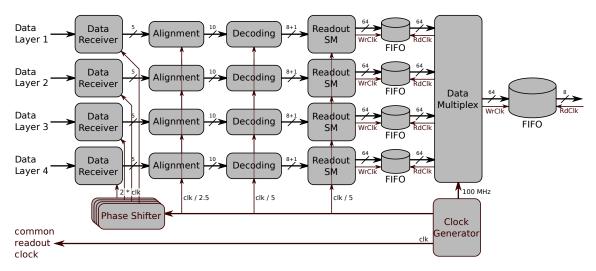

- Das "GEneric Configuration and COntrol" (GECCO) Testsystem wurde aufbauend auf bestehender Hardware [Ehr21] als schnell anzupassendes **Messsystem** entworfen. Darauf wurde sowohl ein Aufbau für einen einzelnen Sensor, als auch ein Strahlteleskop-Aufbau mit vier Sensorlagen konzipiert und umgesetzt.

- Außerdem wurde ein **Ausgleichsstrom-Messsystem** (TCT transient current technique) aufgebaut für Messungen, die sonst außerhalb von Teststrahlmessungen nicht durchführbar sind.

- Der ATLASPix3-Sensor wurde mit diesen Messsystemen charakterisiert. Dabei wurden **Messungen** im **Labor** und an **Teststrahl-Einrichtungen** wie dem Deutschen Elektronen-Synchrotron (DESY) oder dem Heidelberger Ionenthreapiezentrum (HIT) durchgeführt.

- Für die nötigen **Analysen**, um aus den gewonnenen Messdaten Schlüsse auf die Eigenschaften des Sensors zu ziehen, wurden Skripte und Programme entwickelt und bestehende Analyse-Frameworks erweitert.

- Die Verwendung des Messsystems mit dem ATLASPix3 an anderen Universitäten in Deutschland, Großbritannien, Italien und China zeigt zwei Dinge: Zum einen, dass der ATLASPix3 als Kandidat für einen Einsatz in Experimenten gehandelt wird, und zum anderen, dass das GECCO-System attraktiv für erste Studien ist. Damit sorgen der Sensor und das Messsystem zusammen für eine weitere Verbreitung der monolithischen HV-CMOS-Sensoren.

Im Folgenden wird auf die Punkte genauer eingegangen.

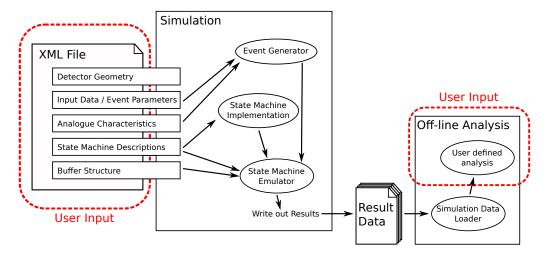

### Systemebenenkonzeption von Sensoren – ROME

Bei der Entwickung von monolithischen Pixelsensoren muss neben der elektrischen Funktionsfähigkeit auch sichergestellt werden, dass die detektierten Signale ausgelesen werden können. Bisher wurde dies durch statische Berechnungen der Datenrate und Simulationen des Entwurfs auf Hardware-Ebene abgeschätzt. Allerdings ist die Abschätzung der Fluktuationen um die Mittelwerte für die statisch berechneten Raten schwierig und die vollständige Simulation auf Hardware-Ebene sehr aufwändig. Diese Lücke wird durch ROME (Kapitel 5) geschlossen: ROME bildet die Auslesestruktur des Sensors ab und testet diese mit Signalfolgen, die beispielsweise in Monte-Carlo-Prozessen generiert werden können. Ein wichtiger Aspekt von ROME ist, dass die Beschreibung nicht direkt in einer Hardware-Beschreibungssprache geschrieben wird, sondern als XML-Baumstruktur. Dadurch ist die Simulation möglich bevor ein vollständiger Entwurf in einer Hardware-Beschreibungssprache existiert und unabhängig von Implementierungsproblemen derselben.

Damit können Abschätzungen getätigt und Optimierungen durchgeführt werden, bevor der eigentliche Hardware-Entwurf gestartet wird. Die abstrahierte Beschreibung ermöglicht es außerdem noch unerfahrenen Entwicklern Beiträge zu leisten. So wurde es erreicht, dass solche Untersuchungen auch im Rahmen von Bachelorarbeiten, deren Umfang dafür normalerweise nicht ausreicht, durchführbar werden. An dieser und den in Kapitel 5 beschriebenen Beispielen zeigt sich, dass die zu implementierenden Systeme durch kleine Änderungen der Strukturen stark beeinflusst werden können und die zuvor genutzten statischen Ratenberechnungen der Komplexität nicht gerecht werden können.

#### Messsystementwicklung – GECCO

Für die Charakterisierung von Siliziumsensoren gab es bereits vor der Entwicklung des GECCO-Systems verschiedene Messsysteme. Dazu gehören unter anderem das Caribou-System, das Basil-System und das YARR-System. Jedes dieser Systeme ist auf bestimmte Anwendungen hin ausgelegt.

Beim Caribou-System handelt es sich um ein vom Brookhaven National Lab, CERN und DESY entwickeltes System, das auf Open-Source-Komponenten aufbaut [LBC<sup>+</sup>19]. Allerdings hat die Variabilität des Systems zur Folge, dass die Komponenten teuer sind. So kostet das verwendete FPGA-Board des Caribou-Systems etwa zehn mal so viel wie das Board für das GECCO-System. Das GECCO-System ist außerdem auf sehr hardware-nahe Testszenarien ausgerichtet, die so direkt nicht mit dem Caribou-System möglich sind. Die

Integration der Software in den eingebetteten Prozessor des System-on-Chip ohne grafische Oberfläche erschwert die Fehlersuche zusätzlich.

Basil [SiL21] ist ein modulares Datennahme- und Systemtest-Framework. Dieses wird beispielsweise in der Auslese der ATLAS FEI4(A/B) Pixel-Auslesechips verwendet. Es zielt auf größere Systeme ab und ist im Zuge dessen ebenfalls nicht mit einer grafischen Nutzerschnittstelle ausgestattet. Entsprechend ist die unterstützte Hardware für Basil ebenfalls für den Test einzelner oder Gruppen weniger Sensoren überdimensioniert und entsprechend teurer.

YARR [Hei17] ermöglicht die Verschiebung der Komplexität der Auslese von der Firmware in die Software durch die Anbindung des FPGAs an den Rechner über den PCIe-Bus. Die hierfür verfügbare Hardware erschwert die hardware-nahe Fehlersuche und Inbetriebnahme von Sensoren und basiert wie die anderen Systeme auf höherpreisigen Systemen.

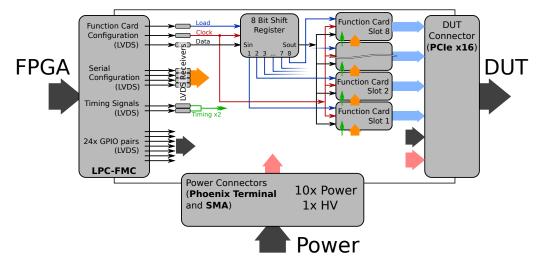

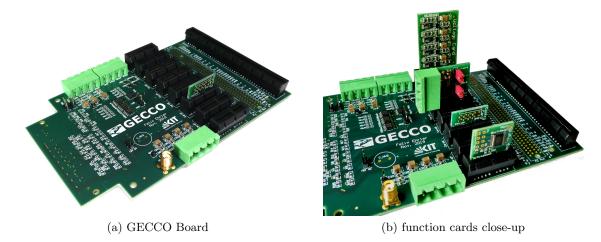

Das GECCO-System (siehe Kapitel 4.1) ist für den kostengünstigen und schnellen Aufbau von kleineren Sensor-Messsystemen gedacht. Um Probleme bei der ersten Inbetriebnahme von Sensoren schnell beheben zu können, ist das zentrale Element, die GECCO-Platine, mit Testpunkten für sämtliche Signale ausgestattet, die es ermöglichen Prüfspitzen zu befestigen.

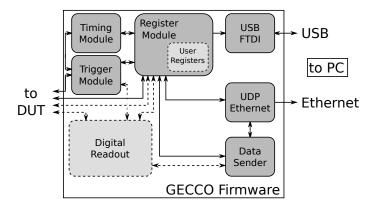

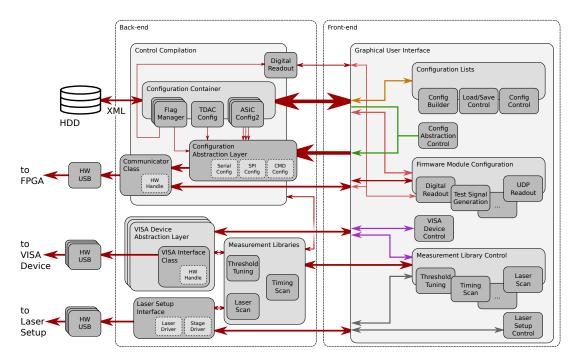

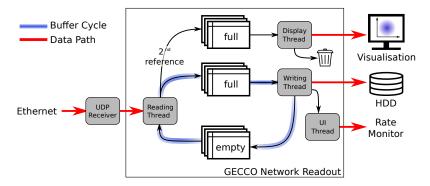

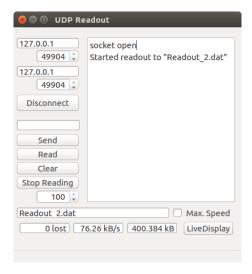

In der Soft- und Firmware wurden Strukturen geschaffen, die die Implementierung der Kommunikation und deren Konfiguration trennen, sodass bereits validierter Code genutzt werden kann, um die Entwicklungszeit zu reduzieren. Auch wurde die Datenübertragung um einen UDP-Datenkanal erweitert, der über Gigabit-Ethernet mehr Datendurchsatz ermöglicht, was beispielsweise für Teststrahl-Messungen eine signifikante Effizienzerhöhung bedeutet.

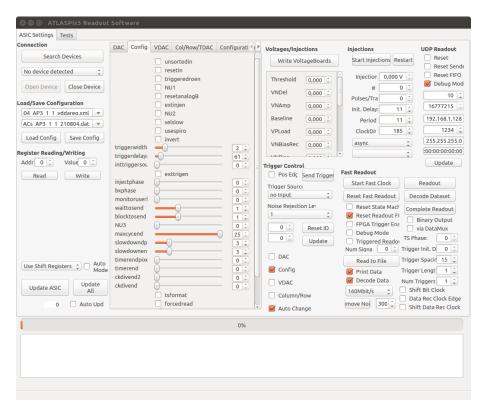

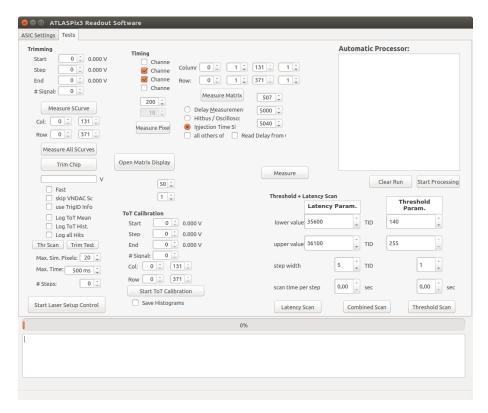

Aus der Konfiguration der Software für den zu testenden Sensor wird ebenfalls die grafische Nutzeroberfläche automatisch generiert, sodass diese fehleranfällige Aufgabe ebenfalls wegfällt. Die Konfigurationsstrukturen ermöglichen ebenfalls eine effizientere Verwaltung von Sensorkonfigurations- und Messdaten, womit die Durchführung von Messkampagnen erleichtert wird.

Das Messsystem wird auch von Arbeitsgruppen an anderen Universitäten in mehreren Ländern für den ATLASPix3-Sensor und Quad-Module aus ATLASPix3-Sensoren [RGS<sup>+</sup>21] und für acht verschiedene Sensoren in dieser Form am KIT-ADL erfolgreich eingesetzt. Für zwei weitere Sensoren wird die selbe Hardware benutzt, die Soft- und Firmware basieren aber noch auf älteren Projekten. Insgesamt wurden bisher 65 Systeme in mehreren Chargen produziert.

#### Ausgleichsstrom-Messsystem

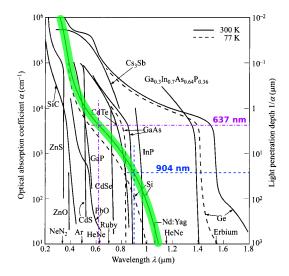

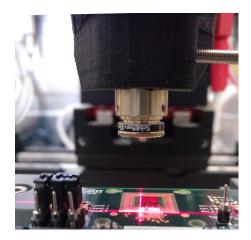

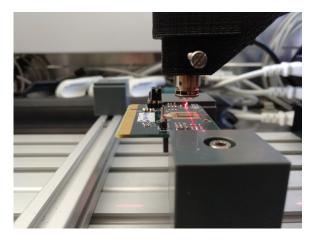

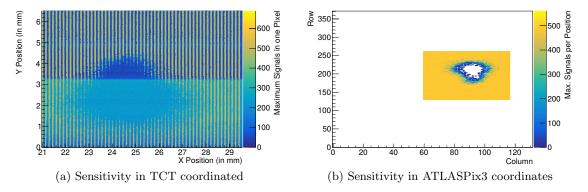

Das Ausgleichsstrom-Messsystem (transient current technique – TCT, Kapitel 4.2) wurde aus einzelnen Komponenten aufgebaut, da die erhältlichen Systeme – wie Beispielsweise das Compact TCT der Firma Alibava Systems – nicht alle Anforderungen erfüllen konnten. Für die kleinen Pixel der monolithischen HV-CMOS-Sensoren mit 25 – 200  $\mu m^2$  Kantenlänge sind Positionsgenauigkeit und Laserstrahlausdehnung von 10  $\mu m$ oder besser erforderlich, um Subpixel-Auflösung zu erreichen. Weiterhin sind präzise und kurze Lichtpulse nötig, um die Zeitauflösung der Sensoren vermessen zu können.

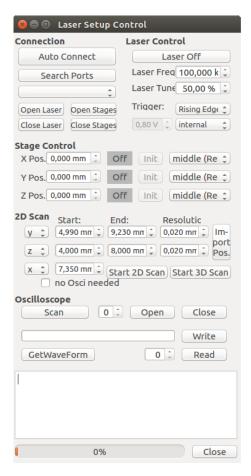

Der Aufbau ist nicht auf ein spezielles Messsystem zugeschnitten, sondern erlaubt die Verwendung von beliebigen Systemen, solange sie in die Einhausung des Systems passen. Aus diesem Grund ist die Steuersoftware für das System aus Lasertreiber und den drei Verfahrtischen zur Positionierung des Lasers ein eigenständiges Projekt, das in andere Software-Projekte integriert werden kann und in die Software für das GECCO-System integriert ist.

### ATLASPix3-Messungen und -Analysen

Die Anforderungen an einen Sensor für das ATLAS Inner-Tracker-Upgrade werden durch den entsprechenden Bericht [ATL17] festgelegt. Diese beinhalten Grenzwerte unter anderem zu Leistungsaufnahme, Homogenität der Matrix, Strahlungshärte und Randbedingungen für die Art der Auslese. Diese Eigenschaften wurden in Labormessungen und Teststrahlmessungen untersucht (Kapitel 6).

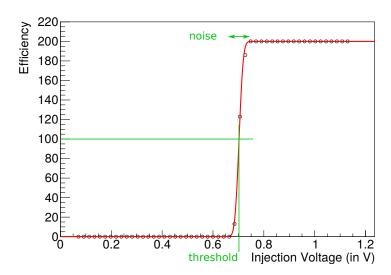

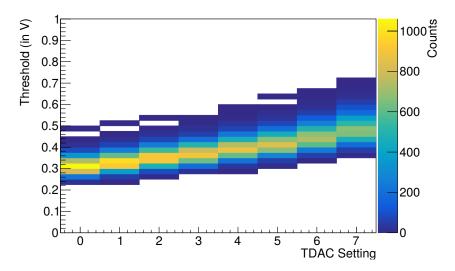

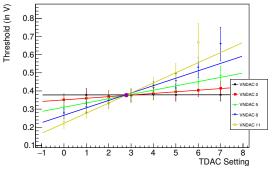

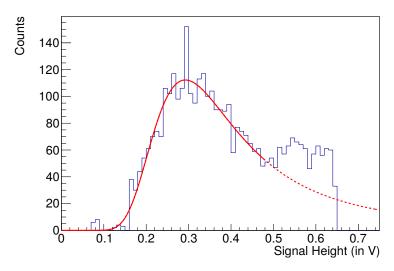

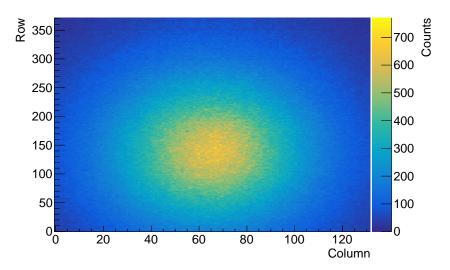

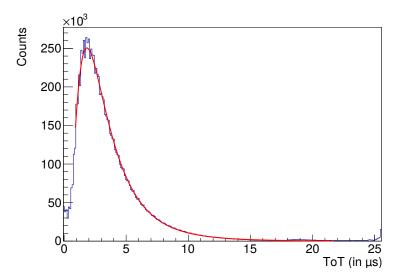

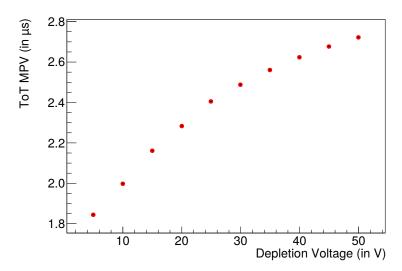

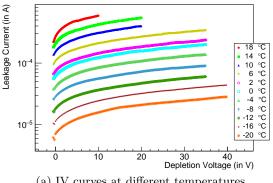

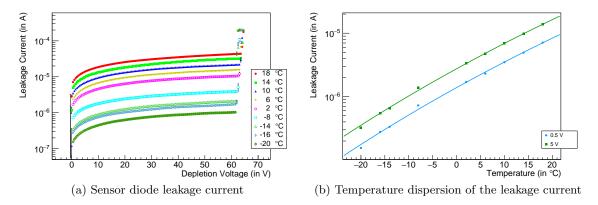

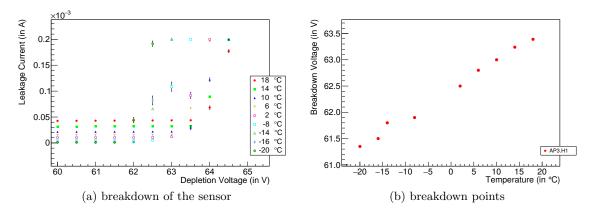

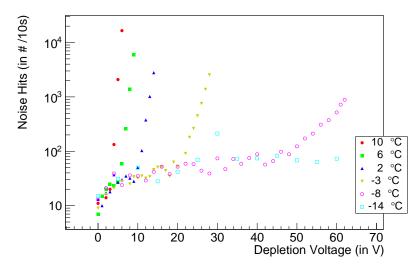

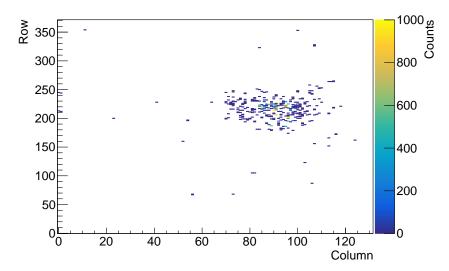

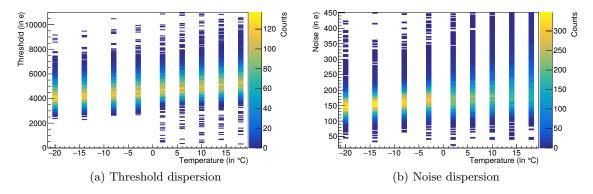

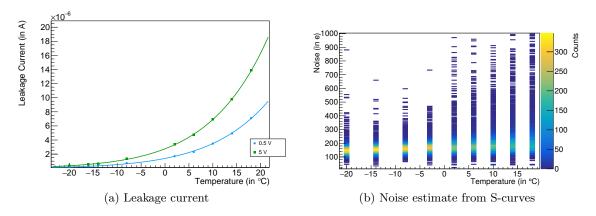

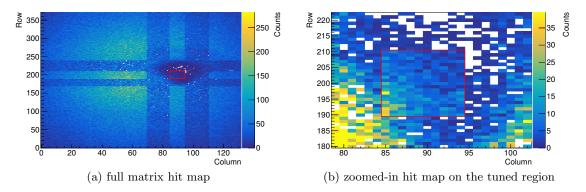

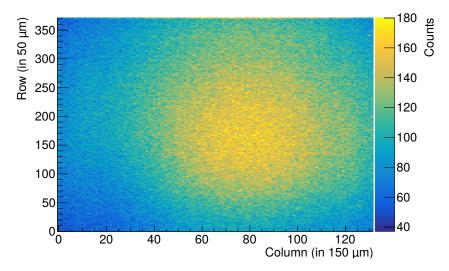

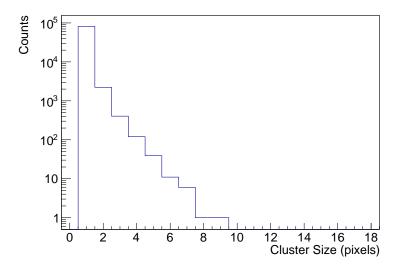

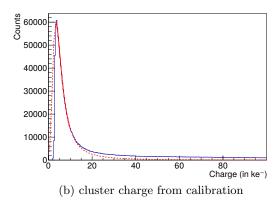

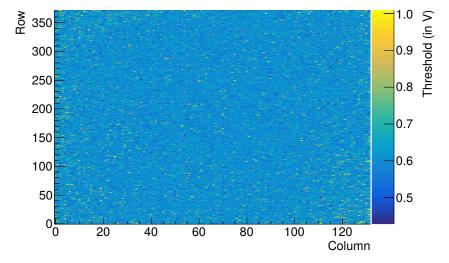

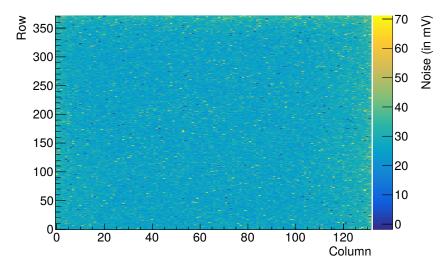

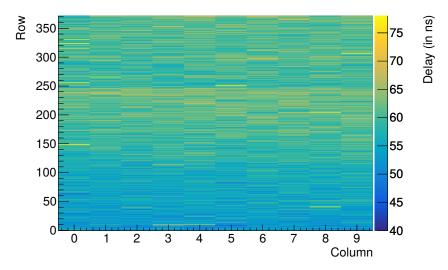

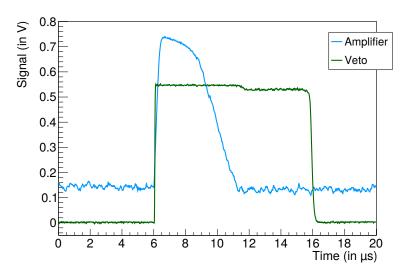

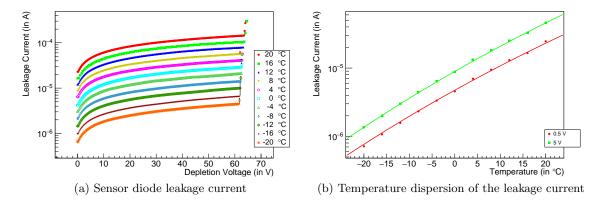

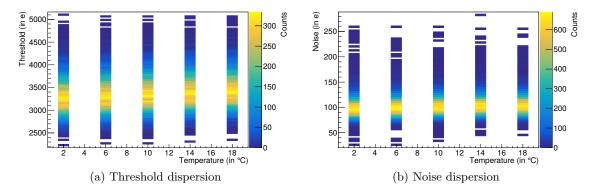

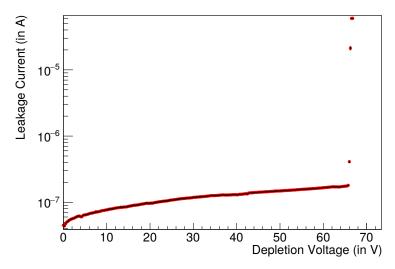

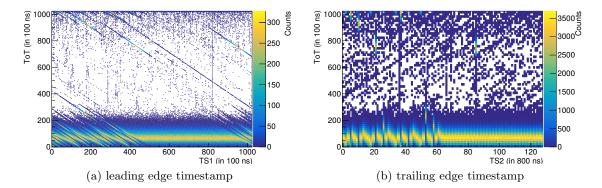

Die Sensordiode wurde durch deren Strom-Spannungs-Kennlinie und Messungen mit Elektronen aus <sup>90</sup>Sr-Zerfällen vermessen. Die dafür nötige Kalibrierung des Verstärkers erfolgte mit Röntgenstrahlung aus <sup>55</sup>Fe-Zerfällen. Mit Testsignalinjektionen, bei denen gezielt Ladung im Pixel erzeugt wird, wurde die Homogenität der Nachweiseffizienz und Kompensationsschaltung für die Schwellenanpassung untersucht, sowie Signalverzögerungen und die Amplitudeninformation (gemessen als Zeit über der Schwelle) über die Matrix vermessen. Für die Amplitudeninformation ist eine Offline-Kalibrierung vorgesehen. Die im Zuge dieser Kalibrierung gemessenen Unterschiede zwischen den Pixeln (von mehr als einem Faktor zwei) bestätigen deren Notwendigkeit. Außerdem konnten die, aus den ROME-Simulationen erwarteten, Überlastungseffekte der Auslese in Teststrahlmessungen beobachtet werden.

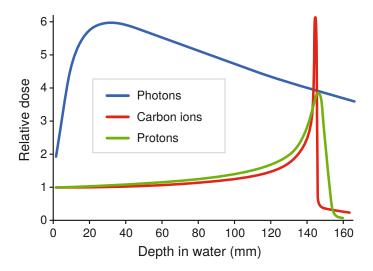

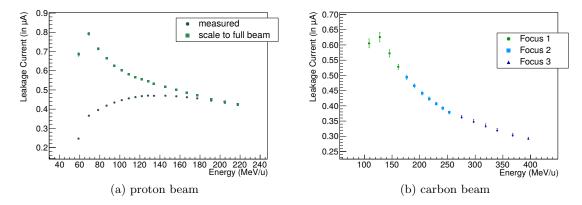

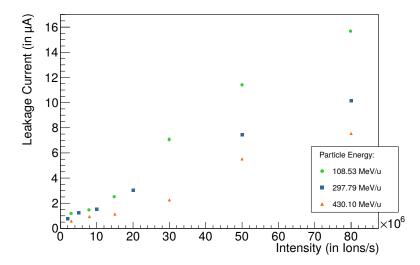

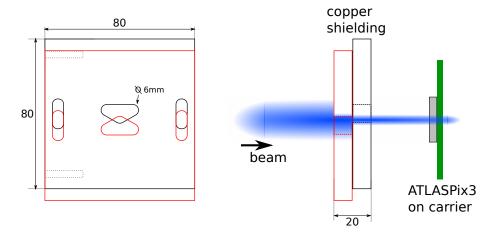

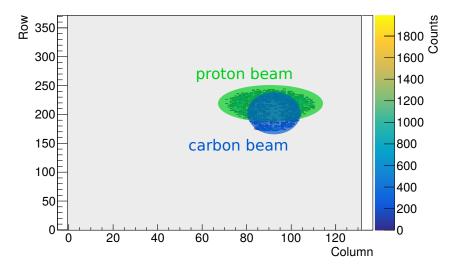

Zusätzlich wurde das Verhalten in Ionenstrahlen am Heidelberger Ionentherapiezentrum (HIT) untersucht, um die Entwicklung von Sensoren zur direkten Strahlbeobachtung vorzubereiten. Dabei wurde sowohl das Signal in Abhängigkeit der Teilchensorte und -Energie vermessen als auch der Einfluss inhomogener Bestrahlung untersucht. Die Ergebnisse dieser Untersuchungen werden in die Entwicklung der nächsten Prototypen für den Strahlmonitorsensor einfließen.

Die zur Analyse der aufgenommenen Daten notwendigen Skripte wurden in C++ unter Zurhilfenahme des Datenanalyse-Frameworks ROOT [BR97] geschrieben, um die Skalierbarkeit der Analysen und deren Wiederverwendbarkeit sicherzustellen. Die zur Aufbereitung der Teststrahldaten entwickelten Skripte haben die Grundstrukturen für die Analyse der Teststrahlmessungen mit den Strahlmonitorsensoren (zum Beispiel in [Web21]) gelegt.

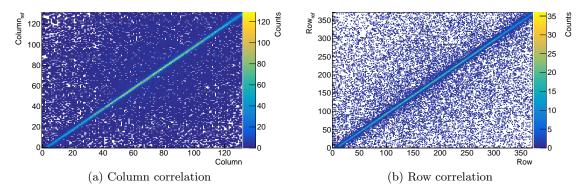

Der Strahlteleskopaufbau wurde für eine Teststrahlmessung am DESY in Betrieb genommen und die Analysekette für die Daten mit dem Corryvreckan-Framework [DDH<sup>+</sup>21] aufgebaut. Der Grund für diese Entwicklung ist, dass mit diesem System, in dem die Versorgungsspannungen und Signalleitungen geteilt werden, die Funktionsfähigkeit des ATLASPix3-Sensors in Systemen mit mehreren gekoppelten Sensoren gezeigt werden kann. Aufgrund der Einfachheit und des kompakten Aufbaus wurden Aufbau und Analysekette später auch für die Spurrekonstruktion von Sekundärteilchen, die bei der Bestrahlung mit Kohlenstoffionen am HIT entstehen, im Rahmen einer Masterarbeit [Kla22], die unter der Betreuung des Autors durchgeführt wurde, genutzt.

# Development and Characterisation of Integrated Sensors for Particle Physics

Zur Erlangung des akademischen Grades eines

### DOKTORS DER NATURWISSENSCHAFTEN (Dr. rer. nat.)

von der KIT-Fakultät für Physik des Karlsruher Instituts für Technologie (KIT) angenommene

### **DISSERTATION**

von

M.Sc. Rudolf Schimassek

aus Reutlingen

Tag der mündlichen Prüfung: 03.12.2021

Hauptreferent: Prof. Dr. rer. nat. Thomas Müller Korreferent: Prof. Dr. rer. nat. Ivan Perić

Karlsruhe, den 16. Dezember 2021

Eidesstattliche Versicherung gemäß § 13 Absatz 2 Ziffer 3 der Promotionsordnung des Karlsruher Instituts für Technologie (KIT) für die KIT-Fakultät für Physik:

- 1. Bei der eingereichten Dissertation zu dem Thema "Entwicklung und Charakterisierung von Integrierten Sensoren für die Teilchenphysik" handelt es sich um meine eigenständig erbrachte Leistung.

- 2. Ich habe nur die angegebenen Quellen und Hilfsmittel benutzt und mich keiner unzulässigen Hilfe Dritter bedient. Insbesondere habe ich wörtlich oder sinngemäß aus anderen Werken übernommene Inhalte als solche kenntlich gemacht.

- 3. Die Arbeit oder Teile davon habe ich bislang nicht an einer Hochschule des In-oder Auslands als Bestandteil einer Prüfungs-oder Qualifikationsleistung vorgelegt.

- 4. Die Richtigkeit der vorstehenden Erklärungen bestätige ich.

- 5. Die Bedeutung der eidesstattlichen Versicherung und die strafrechtlichen Folgen einer unrichtigen oder unvollständigen eidesstattlichen Versicherung sind mir bekannt.

Ich versichere an Eides statt, dass ich nach bestem Wissen die reine Wahrheit erklärt und nichts verschwiegen habe.

| <br>               |             |

|--------------------|-------------|

| $(\mathbf{Rudolf}$ | Schimassek) |

Karlsruhe, den 16. Dezember 2021

# Contents

| D | Deutsche Zusammenfassung iii |         |                                                      |    |  |

|---|------------------------------|---------|------------------------------------------------------|----|--|

| 1 | Intr                         | oductio | n                                                    | 1  |  |

| 2 | Part                         | icle Me | easurement – Applications for Tracking Detectors     | 5  |  |

|   | 2.1                          | Detect  | for Technologies for Tracking                        | 5  |  |

|   | 2.2                          | The L   | arge Hadron Collider and the High Luminosity Upgrade | 7  |  |

|   |                              | 2.2.1   | Structure of the ATLAS Detector                      | 9  |  |

|   |                              | 2.2.2   | The Inner Detector                                   | 11 |  |

|   |                              | 2.2.3   | The Inner Tracker Upgrade                            | 12 |  |

|   | 2.3                          | Treatn  | ment Monitoring in Ion Irradiation Therapy           | 14 |  |

|   |                              | 2.3.1   | Irradiation Therapy                                  | 14 |  |

|   |                              | 2.3.2   | Direct Beam Monitoring                               | 15 |  |

|   |                              | 2.3.3   | Secondary Particle Tracking                          | 16 |  |

| 3 | Silic                        | on Det  | ector Technology                                     | 17 |  |

|   | 3.1                          | Funda   | mentals of Semiconductors                            | 17 |  |

|   |                              | 3.1.1   | Theory of Semiconductors                             | 17 |  |

|   |                              | 3.1.2   | Doped Semiconductors                                 | 20 |  |

|   |                              | 3.1.3   | PN Junction                                          | 21 |  |

|   |                              | 3.1.4   | Metal-Oxide-Semiconductor Field-Effect Transistor    | 24 |  |

|   |                              | 3.1.5   | Production of Semiconductor Circuits                 | 26 |  |

|   | 3.2                          | Interac | ction of Particles with Silicon Detectors            | 28 |  |

|   |                              | 3.2.1   | Interaction with Photons                             | 28 |  |

|   |                              | 3.2.2   | Interaction with Heavy Particles                     | 29 |  |

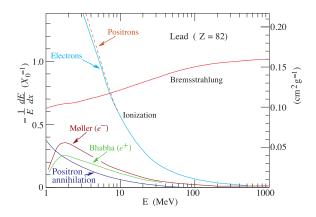

|   |                              | 3.2.3   | Interaction with Light Particles                     | 30 |  |

|   |                              | 3.2.4   | Charge Generation Fluctuation                        | 30 |  |

|   |                              | 3.2.5   | Particle Scattering                                  | 31 |  |

|   | 3.3                          | Radiat  | tion Damage in Semiconductors                        | 32 |  |

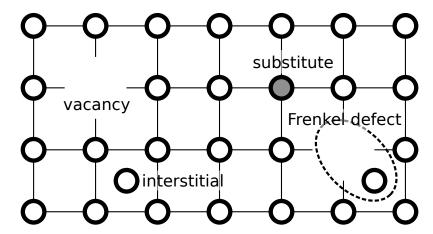

|   |                              | 3.3.1   | Bulk Damage                                          | 32 |  |

|   |                              | 3.3.2   | Surface Damage                                       | 33 |  |

|   | 3.4                          | Silicon | n-based Particle Detector Technologies               | 34 |  |

|   |                              | 3.4.1   | Sensor Technologies                                  |    |  |

|   |                              | 3.4.2   | Noise Sources in Silicon Sensors                     | 37 |  |

|   | 3.5                          | Monol   | ithic High-Voltage CMOS Sensors                      | 38 |  |

| 4 | Mea                          | sureme  | ent Infrastructure                                   | 41 |  |

|   | 4.1                          | Generi  | ic Configuration and Control (GECCO) System          | 41 |  |

|   |                              | 4.1.1   | Hardware                                             | 43 |  |

|   |                              | 4.1.2   | Firmware                                             | 45 |  |

|   |                              | 4.1.3   | Software                                             | 47 |  |

|   |                              |         | 4.1.3.1 Configuration-Data Container Structures      | 49 |  |

Contents

|   |                   |                                                                                                                                                                                                   |                                                                                                                                                                                                                            | Configura                                           |               |     |          |        |       |                                       |                                       |       |   |                                                                                                                                        |

|---|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|---------------|-----|----------|--------|-------|---------------------------------------|---------------------------------------|-------|---|----------------------------------------------------------------------------------------------------------------------------------------|

|   |                   |                                                                                                                                                                                                   |                                                                                                                                                                                                                            | Digital Re                                          |               |     |          |        |       |                                       |                                       |       |   |                                                                                                                                        |

|   |                   |                                                                                                                                                                                                   |                                                                                                                                                                                                                            | Measurem                                            |               |     |          |        |       |                                       |                                       |       |   |                                                                                                                                        |

|   |                   |                                                                                                                                                                                                   |                                                                                                                                                                                                                            | Measurem                                            |               |     |          |        |       |                                       |                                       |       |   |                                                                                                                                        |

|   |                   |                                                                                                                                                                                                   |                                                                                                                                                                                                                            | User Inter                                          |               |     |          |        |       |                                       |                                       |       |   |                                                                                                                                        |

|   |                   | 4.1.4                                                                                                                                                                                             | Readout v                                                                                                                                                                                                                  |                                                     |               |     |          |        |       |                                       |                                       |       |   |                                                                                                                                        |

|   | 4.2               | Laser                                                                                                                                                                                             | Measureme                                                                                                                                                                                                                  |                                                     |               |     |          |        |       |                                       |                                       |       |   |                                                                                                                                        |

|   |                   | 4.2.1                                                                                                                                                                                             | Hardware                                                                                                                                                                                                                   |                                                     |               |     |          |        |       |                                       |                                       |       |   |                                                                                                                                        |

|   |                   | 4.2.2                                                                                                                                                                                             | Software                                                                                                                                                                                                                   |                                                     |               |     |          |        |       |                                       |                                       |       | • | . 64                                                                                                                                   |

| 5 | Road              | dout Si                                                                                                                                                                                           | mulation                                                                                                                                                                                                                   |                                                     |               |     |          |        |       |                                       |                                       |       |   | 67                                                                                                                                     |

| 3 | 5.1               |                                                                                                                                                                                                   | ure of the                                                                                                                                                                                                                 | Simulation                                          | า             |     |          |        |       |                                       |                                       |       |   |                                                                                                                                        |

|   | 0.1               | 5.1.1                                                                                                                                                                                             | Detector 1                                                                                                                                                                                                                 |                                                     |               |     |          |        |       |                                       |                                       |       |   |                                                                                                                                        |

|   |                   | 5.1.2                                                                                                                                                                                             | Data Mar                                                                                                                                                                                                                   | _                                                   |               |     |          |        |       |                                       |                                       |       |   |                                                                                                                                        |

|   |                   | 5.1.2 $5.1.3$                                                                                                                                                                                     | Event Ger                                                                                                                                                                                                                  | _                                                   |               |     |          |        |       |                                       |                                       |       |   |                                                                                                                                        |

|   |                   | 5.1.4                                                                                                                                                                                             | Simulation                                                                                                                                                                                                                 |                                                     |               |     |          |        |       |                                       |                                       |       |   |                                                                                                                                        |

|   |                   | 5.1.4 $5.1.5$                                                                                                                                                                                     | User-Inpu                                                                                                                                                                                                                  | 0                                                   |               |     |          |        |       |                                       |                                       |       |   |                                                                                                                                        |

|   | 5.2               |                                                                                                                                                                                                   | arability of                                                                                                                                                                                                               |                                                     |               |     |          |        |       |                                       |                                       |       |   |                                                                                                                                        |

|   |                   |                                                                                                                                                                                                   | arabiiity oi<br>ed Readou                                                                                                                                                                                                  |                                                     |               |     |          |        |       |                                       |                                       |       |   |                                                                                                                                        |

|   | 5.3               | _                                                                                                                                                                                                 |                                                                                                                                                                                                                            |                                                     |               |     |          |        |       |                                       |                                       |       |   |                                                                                                                                        |

|   | 5.4               |                                                                                                                                                                                                   | ip Signal S                                                                                                                                                                                                                | _                                                   |               |     |          |        |       |                                       |                                       |       |   |                                                                                                                                        |

|   | 5.5               |                                                                                                                                                                                                   | pment of t                                                                                                                                                                                                                 |                                                     |               |     |          |        |       |                                       |                                       |       |   |                                                                                                                                        |

|   |                   | 5.5.1                                                                                                                                                                                             | State Mac                                                                                                                                                                                                                  | _                                                   |               |     |          |        |       |                                       |                                       |       |   |                                                                                                                                        |

|   |                   | 5.5.2                                                                                                                                                                                             | Buffer Dia                                                                                                                                                                                                                 |                                                     | _             |     |          |        |       |                                       |                                       |       |   |                                                                                                                                        |

|   | F C               | 5.5.3                                                                                                                                                                                             | Data Wor                                                                                                                                                                                                                   |                                                     |               |     |          |        |       |                                       |                                       |       |   |                                                                                                                                        |

|   | 5.6               | Insigni                                                                                                                                                                                           | ts from the                                                                                                                                                                                                                | Simulatio                                           | ons           |     |          |        |       |                                       | <br>•                                 | <br>• | • | . 95                                                                                                                                   |

|   |                   |                                                                                                                                                                                                   |                                                                                                                                                                                                                            |                                                     |               |     |          |        |       |                                       |                                       |       |   |                                                                                                                                        |

| 6 | The               |                                                                                                                                                                                                   | SPix3 Inte                                                                                                                                                                                                                 | _                                                   |               |     |          |        |       |                                       |                                       |       |   | 97                                                                                                                                     |

| 6 | <b>The</b> 6.1    |                                                                                                                                                                                                   | SPix3 Desi                                                                                                                                                                                                                 | gn                                                  |               |     |          |        |       |                                       |                                       |       |   | . 98                                                                                                                                   |

| 6 |                   | ATLA<br>6.1.1                                                                                                                                                                                     | SPix3 Desi<br>Matrix an                                                                                                                                                                                                    | gn<br>Id Columr                                     | <br>ı Structı | are |          |        |       |                                       |                                       |       |   | . 98<br>. 99                                                                                                                           |

| 6 |                   | ATLA<br>6.1.1<br>6.1.2                                                                                                                                                                            | SPix3 Desi<br>Matrix an<br>Pixel                                                                                                                                                                                           | gn<br>id Columr<br>                                 | Structi       | are | <br>     |        |       |                                       |                                       |       |   | . 98<br>. 99<br>. 101                                                                                                                  |

| 6 |                   | ATLA<br>6.1.1                                                                                                                                                                                     | SPix3 Desi<br>Matrix an<br>Pixel<br>Readout l                                                                                                                                                                              | gn<br>nd Columr<br><br>Buffers .                    | Structi       | are | <br>     |        |       | <br>                                  |                                       | <br>• |   | . 98<br>. 99<br>. 101<br>. 103                                                                                                         |

| 6 |                   | ATLA<br>6.1.1<br>6.1.2                                                                                                                                                                            | SPix3 Desi<br>Matrix an<br>Pixel<br>Readout l<br>Configura                                                                                                                                                                 | gn  d Columr  Buffers .  tion                       | Structi       | are | <br><br> |        |       | <br><br>                              | <br>                                  | <br>  |   | . 98<br>. 99<br>. 101<br>. 103<br>. 107                                                                                                |

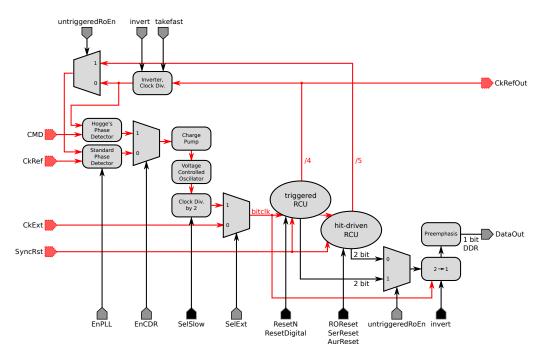

| 6 |                   | ATLA<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5                                                                                                                                                 | SPix3 Desi<br>Matrix an<br>Pixel<br>Readout l<br>Configura<br>Clocking                                                                                                                                                     | gn  d Column  Buffers .  tion  Scheme .             | Structi       | are | <br><br> |        |       |                                       | <br>                                  | <br>  |   | . 98<br>. 99<br>. 101<br>. 103<br>. 107<br>. 109                                                                                       |

| 6 |                   | ATLA<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4                                                                                                                                                          | SPix3 Desi<br>Matrix an<br>Pixel<br>Readout l<br>Configura                                                                                                                                                                 | gn  d Column  Buffers .  tion  Scheme .             | Structi       | are | <br><br> |        |       |                                       | <br>                                  | <br>  |   | . 98<br>. 99<br>. 101<br>. 103<br>. 107<br>. 109                                                                                       |

| 6 |                   | ATLA<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5                                                                                                                                                 | SPix3 Desi<br>Matrix an<br>Pixel<br>Readout l<br>Configura<br>Clocking                                                                                                                                                     | gn  Id Column  Buffers .  tion  Scheme .  Readout   | Structu       | ire |          |        |       |                                       | <br>                                  | <br>  |   | . 98<br>. 99<br>. 101<br>. 103<br>. 107<br>. 109                                                                                       |

| 6 |                   | ATLA<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>6.1.6                                                                                                                                        | SPix3 Desi<br>Matrix an<br>Pixel<br>Readout l<br>Configura<br>Clocking b<br>Hit-Drive                                                                                                                                      | gn ad Columr Bufferstion Scheme . n Readout Readout | Structu       | ure |          |        |       |                                       | <br>                                  | <br>  |   | . 98<br>. 99<br>. 101<br>. 103<br>. 107<br>. 109<br>. 110                                                                              |

| 6 |                   | ATLA<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>6.1.6<br>6.1.7                                                                                                                               | SPix3 Desi<br>Matrix an<br>Pixel<br>Readout l<br>Configura<br>Clocking<br>Hit-Drive<br>Triggered                                                                                                                           | gn                                                  | Structu       | ire |          |        |       |                                       | <br>                                  | <br>  |   | . 98<br>. 99<br>. 101<br>. 103<br>. 107<br>. 109<br>. 110<br>. 111                                                                     |

| 6 |                   | ATLA<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>6.1.6<br>6.1.7<br>6.1.8<br>6.1.9                                                                                                             | SPix3 Desi<br>Matrix an<br>Pixel<br>Readout l<br>Configura<br>Clocking<br>Hit-Drive<br>Triggered<br>Bias Block                                                                                                             | gn                                                  | Structu       | ire |          |        |       |                                       | <br>                                  | <br>  |   | . 98<br>. 99<br>. 101<br>. 103<br>. 107<br>. 109<br>. 110<br>. 111<br>. 112                                                            |

| 6 |                   | ATLA<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>6.1.6<br>6.1.7<br>6.1.8<br>6.1.9<br>6.1.10                                                                                                   | SPix3 Desi<br>Matrix an<br>Pixel<br>Readout l<br>Configura<br>Clocking !<br>Hit-Drive<br>Triggered<br>Bias Block<br>Regulator                                                                                              | gn                                                  | Structu       | ire |          |        |       |                                       |                                       | <br>  |   | 98<br>99<br>101<br>103<br>107<br>109<br>110<br>111<br>112<br>113                                                                       |

| 6 |                   | ATLA<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>6.1.6<br>6.1.7<br>6.1.8<br>6.1.9<br>6.1.10<br>6.1.11                                                                                         | SPix3 Desi<br>Matrix an<br>Pixel<br>Readout l<br>Configura<br>Clocking<br>Hit-Drive<br>Triggered<br>Bias Block<br>Regulator<br>Sensor La                                                                                   | gn                                                  | a Structu     | ire |          |        |       |                                       | · · · · · · · · · · · · · · · · · · · | <br>  |   | . 98<br>. 99<br>. 101<br>. 103<br>. 107<br>. 109<br>. 110<br>. 111<br>. 112<br>. 113<br>. 113                                          |

| 6 | 6.1               | ATLA<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>6.1.6<br>6.1.7<br>6.1.8<br>6.1.9<br>6.1.10<br>6.1.11<br>The A                                                                                | SPix3 Desi<br>Matrix an<br>Pixel<br>Readout l<br>Configura<br>Clocking<br>Hit-Drive<br>Triggered<br>Bias Block<br>Regulator<br>Sensor La<br>Design M                                                                       | gn                                                  | a Structu     | re  |          |        |       |                                       |                                       |       |   | . 98<br>. 99<br>. 101<br>. 103<br>. 107<br>. 109<br>. 110<br>. 111<br>. 112<br>. 113<br>. 114<br>. 115                                 |

| 6 | 6.1               | ATLA<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>6.1.6<br>6.1.7<br>6.1.8<br>6.1.9<br>6.1.10<br>6.1.11<br>The A                                                                                | SPix3 Desi<br>Matrix an<br>Pixel<br>Readout l<br>Configura<br>Clocking !<br>Hit-Drive<br>Triggered<br>Bias Block<br>Regulator<br>Sensor La<br>Design M<br>TLASPix3                                                         | gn                                                  | a Structu     | ure |          |        |       |                                       |                                       |       |   | . 98<br>. 99<br>. 101<br>. 103<br>. 107<br>. 109<br>. 110<br>. 111<br>. 112<br>. 113<br>. 114<br>. 115                                 |

| 6 | 6.1               | ATLA<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>6.1.6<br>6.1.7<br>6.1.8<br>6.1.9<br>6.1.10<br>6.1.11<br>The A'                                                                               | SPix3 Desi<br>Matrix an<br>Pixel<br>Readout l<br>Configura<br>Clocking<br>Hit-Drive<br>Triggered<br>Bias Bloc<br>Regulator<br>Sensor La<br>Design M<br>TLASPix3<br>issioning M                                             | gn                                                  | a Structu     | ure |          |        |       |                                       |                                       |       |   | . 98<br>. 99<br>. 101<br>. 103<br>. 107<br>. 109<br>. 110<br>. 111<br>. 113<br>. 113<br>. 114<br>. 115<br>. 117                        |

| 6 | 6.1               | ATLA<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>6.1.6<br>6.1.7<br>6.1.8<br>6.1.9<br>6.1.10<br>6.1.11<br>The A'<br>Comm<br>6.3.1                                                              | SPix3 Desi<br>Matrix and<br>Pixel<br>Readout I<br>Configura<br>Clocking I<br>Hit-Drivet<br>Triggered<br>Bias Block<br>Regulator<br>Sensor Lat<br>Design M<br>TLASPix3<br>issioning M<br>Power Co                           | gn                                                  | n Structu     | ure | ix3.1    |        |       |                                       |                                       |       |   | . 98<br>. 99<br>. 101<br>. 103<br>. 107<br>. 109<br>. 110<br>. 111<br>. 113<br>. 113<br>. 114<br>. 115<br>. 117<br>. 117               |

| 6 | 6.1               | ATLA<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>6.1.6<br>6.1.7<br>6.1.8<br>6.1.9<br>6.1.10<br>6.1.11<br>The A'<br>Comm<br>6.3.1<br>6.3.2<br>6.3.3                                            | SPix3 Desi<br>Matrix an<br>Pixel<br>Readout l<br>Configura<br>Clocking i<br>Hit-Drive<br>Triggered<br>Bias Block<br>Regulator<br>Sensor La<br>Design M<br>TLASPix3<br>issioning M<br>Power Co<br>On-Chip                   | gn                                                  | a Structu     | re  | ix3.1    |        |       |                                       |                                       |       |   | . 98<br>. 99<br>. 101<br>. 103<br>. 107<br>. 109<br>. 110<br>. 111<br>. 112<br>. 113<br>. 114<br>. 115<br>. 117<br>. 117<br>. 118      |

| 6 | 6.1<br>6.2<br>6.3 | ATLA<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>6.1.6<br>6.1.7<br>6.1.8<br>6.1.9<br>6.1.10<br>6.1.11<br>The A'<br>Comm<br>6.3.1<br>6.3.2<br>6.3.3                                            | SPix3 Desi<br>Matrix and<br>Pixel<br>Readout I<br>Configura<br>Clocking I<br>Hit-Driver<br>Triggered<br>Bias Block<br>Regulator<br>Sensor Lad<br>Design M<br>TLASPix3<br>issioning M<br>Power Co<br>On-Chip I<br>Depletion | gn                                                  | a Structu     | ure |          |        |       |                                       |                                       |       |   | 98<br>99<br>101<br>103<br>107<br>109<br>110<br>111<br>112<br>113<br>113<br>114<br>115<br>117<br>117<br>118                             |

| 6 | 6.1<br>6.2<br>6.3 | ATLA<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>6.1.6<br>6.1.7<br>6.1.8<br>6.1.9<br>6.1.10<br>6.1.11<br>The A'<br>Comm<br>6.3.1<br>6.3.2<br>6.3.3<br>Thresh                                  | SPix3 Desi Matrix an Pixel Readout I Configura Clocking Hit-Drive Triggered Bias Block Regulator Sensor La Design M TLASPix3 issioning M Power Co On-Chip Depletion hold Tuning                                            | gn                                                  | a Structu     | re  | ix3.1    | cteris |       |                                       |                                       |       |   | 98<br>99<br>101<br>103<br>107<br>110<br>111<br>112<br>113<br>113<br>114<br>115<br>117<br>117<br>118<br>122<br>125                      |

| 6 | 6.1<br>6.2<br>6.3 | ATLA<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>6.1.6<br>6.1.7<br>6.1.8<br>6.1.9<br>6.1.10<br>6.1.11<br>The A'<br>Comm<br>6.3.1<br>6.3.2<br>6.3.3<br>Thresh<br>6.4.1                         | SPix3 Desi Matrix an Pixel Readout l Configura Clocking Hit-Drive Triggered Bias Block Regulator Sensor La Design M TLASPix3 issioning M Power Co On-Chip Depletion hold Tuning Measurem                                   | gn                                                  | a Structu     | re  | ix3.1    | cteris | ation | · · · · · · · · · · · · · · · · · · · |                                       |       |   | 98<br>99<br>101<br>103<br>107<br>109<br>110<br>111<br>112<br>113<br>113<br>114<br>115<br>117<br>117<br>118<br>122<br>125<br>125        |

| 6 | 6.1<br>6.2<br>6.3 | ATLA<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>6.1.6<br>6.1.7<br>6.1.8<br>6.1.9<br>6.1.10<br>6.1.11<br>The A'<br>Comm<br>6.3.1<br>6.3.2<br>6.3.3<br>Thresh<br>6.4.1<br>6.4.2<br>6.4.3       | SPix3 Desi Matrix an Pixel Readout I Configura Clocking Hit-Drive: Triggered Bias Block Regulator Sensor La Design M TLASPix3 issioning M Power Co On-Chip Depletion hold Tuning Measurem Matrix Tu                        | gn                                                  | a Structu     | re  | ix3.1 .  | cteris | ation |                                       |                                       |       |   | 98<br>99<br>101<br>103<br>107<br>110<br>111<br>112<br>113<br>113<br>114<br>115<br>117<br>117<br>118<br>122<br>125<br>125               |

| 6 | 6.1<br>6.2<br>6.3 | ATLA<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>6.1.6<br>6.1.7<br>6.1.8<br>6.1.9<br>6.1.10<br>6.1.11<br>The A'<br>Comm<br>6.3.1<br>6.3.2<br>6.3.3<br>Thresh<br>6.4.1<br>6.4.2<br>6.4.3       | Matrix and Pixel Readout I Configura Clocking Hit-Driver Triggered Bias Block Regulator Sensor Lad Design MTLASPix3 issioning Measurem Matrix Tunoise Est.                                                                 | gn                                                  | a Structu     | re  | ix3.1    | cteris |       |                                       |                                       |       |   | 98<br>99<br>101<br>103<br>107<br>110<br>1110<br>1111<br>112<br>113<br>114<br>115<br>117<br>117<br>118<br>122<br>125<br>125<br>128      |

| 6 | 6.1<br>6.2<br>6.3 | ATLA<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>6.1.6<br>6.1.7<br>6.1.8<br>6.1.9<br>6.1.10<br>6.1.11<br>The A'Comm<br>6.3.1<br>6.3.2<br>6.3.3<br>Thresh<br>6.4.1<br>6.4.2<br>6.4.3<br>Time I | SPix3 Desi Matrix an Pixel Readout l Configura Clocking Hit-Drive Triggered Bias Bloc Regulator Sensor La Design M TLASPix3 issioning M Power Co On-Chip Depletion hold Tuning Measurem Matrix Tu Noise Est Resolution     | gn                                                  | a Structu     | re  | ix3.1 .  |        | ation |                                       |                                       |       |   | 98<br>99<br>101<br>103<br>107<br>110<br>111<br>112<br>113<br>113<br>114<br>115<br>117<br>117<br>118<br>125<br>125<br>125<br>131<br>131 |

Contents

|    | 6.6             | Measurements with Particle Sources                           | 138 |  |  |  |

|----|-----------------|--------------------------------------------------------------|-----|--|--|--|

|    | 0.0             | 6.6.1 Beta Particles from Strontium-90                       |     |  |  |  |

|    |                 | 6.6.2 X-rays from Iron-55                                    |     |  |  |  |

|    |                 | 6.6.3 Ion Beam Measurements                                  |     |  |  |  |

|    | 6.7             | Measurements on Irradiated Sensors                           |     |  |  |  |

|    | ٠.,             | 6.7.1 Homogeneous Proton Irradiation                         |     |  |  |  |

|    |                 | 6.7.2 Inhomogeneous Irradiation with Protons and Carbon Ions |     |  |  |  |

|    | 6.8             | The ATLASPix3 Beam Telescope                                 |     |  |  |  |

|    | 6.9             | Telescope Measurements                                       |     |  |  |  |

| 7  | Cond            | clusions                                                     | 183 |  |  |  |

| Αp | pend            | lix                                                          | 187 |  |  |  |

| ·  | Α               | Collection of alternatives to GECCO                          | 187 |  |  |  |

|    |                 | A.1 Caribou Readout System                                   | 187 |  |  |  |

|    |                 | A.2 Basil                                                    | 188 |  |  |  |

|    |                 | A.3 YARR                                                     | 188 |  |  |  |

|    | В               | Configuration of ATLASPix3                                   | 188 |  |  |  |

|    | $\mathbf{C}$    | ATLASPix3 Quad-Module                                        | 189 |  |  |  |

|    | D               | Threshold Tuning of a proton-irradiated ATLASPix3            | 190 |  |  |  |

|    | $\mathbf{E}$    | Matrix Timing on ATLASPix3                                   | 192 |  |  |  |

|    | $\mathbf{F}$    | Amplifier Saturation on ATLASPix3                            | 192 |  |  |  |

|    | G               | Further Leakage Current Measurements on ATLASPix3            | 193 |  |  |  |

|    | Η               | Threshold Dispersion on a non-irradiated ATLASPix3           |     |  |  |  |

|    | I               | ATLASPix3.1 Leakage Current                                  |     |  |  |  |

|    | J               | Timestamp Error Effects                                      | 195 |  |  |  |

| Αŀ | brevi           | ation Index                                                  | 197 |  |  |  |

| Pι | ıblicat         | tions                                                        | 199 |  |  |  |

| Bi | Bibliography 20 |                                                              |     |  |  |  |

# List of Figures

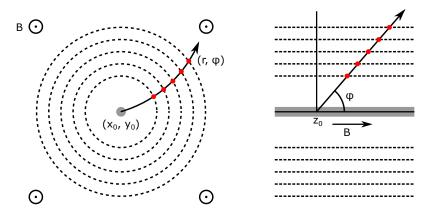

| 2.1  | Principle of particle identification with a tracker in a magnetic field | 6  |

|------|-------------------------------------------------------------------------|----|

| 2.2  | Structure of LHC overlayed on an aerial view of the region              | 8  |

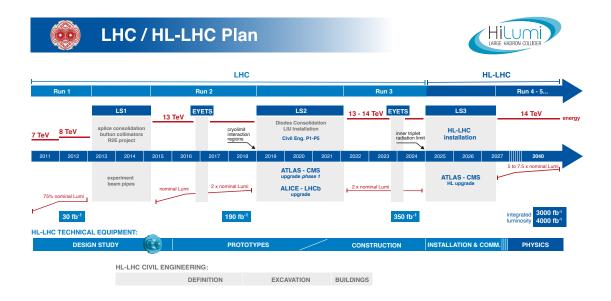

| 2.3  | Roadmap towards HL-LHC                                                  | 8  |

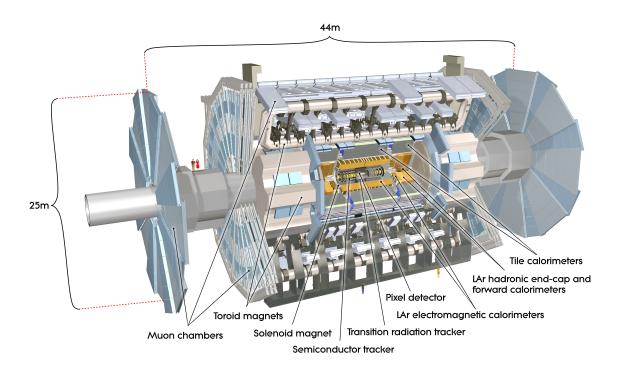

| 2.4  | ATLAS detector structure                                                | 10 |

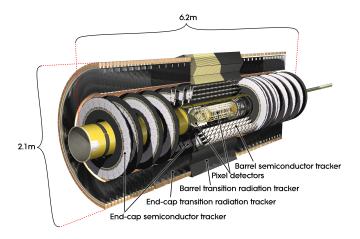

| 2.5  | Structure of the inner detector of ATLAS                                | 11 |

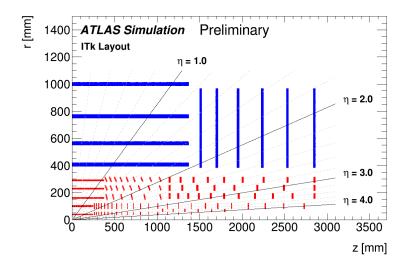

| 2.6  | Structure of the ATLAS ITk upgrade                                      | 12 |

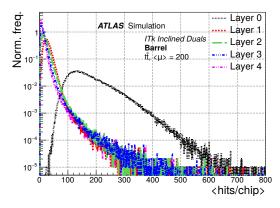

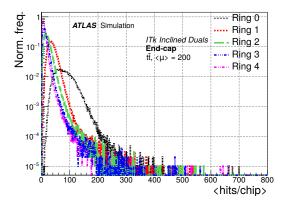

| 2.7  | Signal rate simulation for inclined modules in ATLAS ITk upgrade        | 13 |

| 2.8  | Energy deposition profiles of different particles in matter             | 15 |

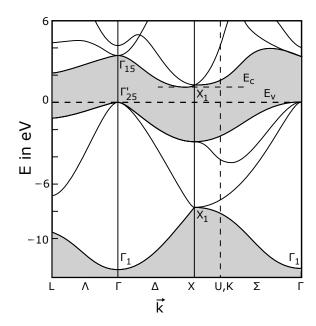

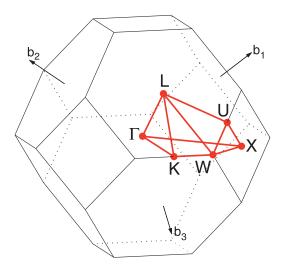

| 3.1  | Band structure of silicon                                               | 18 |

| 3.2  | Brillouin zone of silicon                                               | 19 |

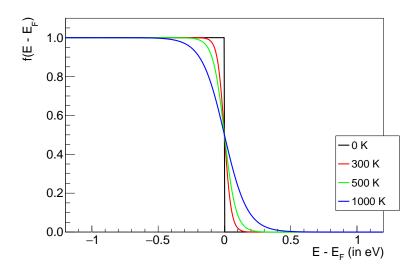

| 3.3  | Fermi distribution for different temperatures                           | 20 |

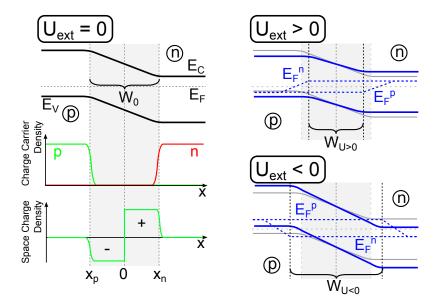

| 3.4  | Band model of the pn junction                                           | 22 |

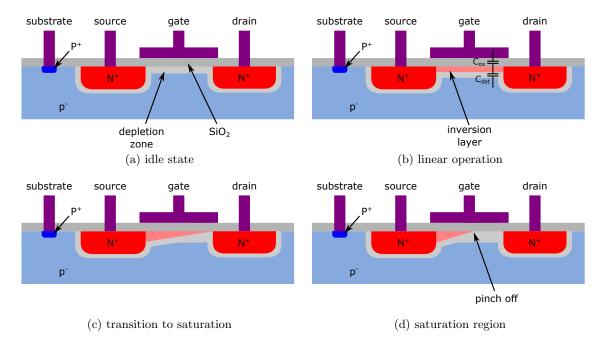

| 3.5  | Operation modes of a MOSFET                                             | 24 |

| 3.6  | IV characteristics of an n-channel MOSFET                               | 25 |

| 3.7  | Top view of the structure of a linear MOSFET                            | 26 |

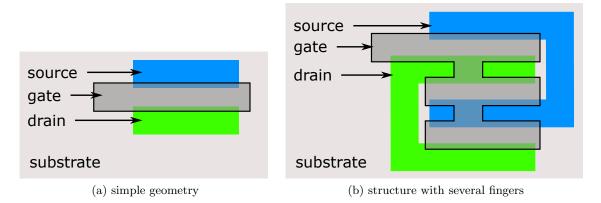

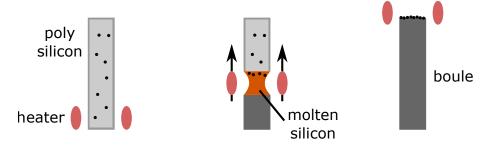

| 3.8  | Czochralski process for growing mono-crystal silicon                    | 26 |

| 3.9  | Zone melting scheme to convert poly-silicon into a mono-crystal         | 27 |

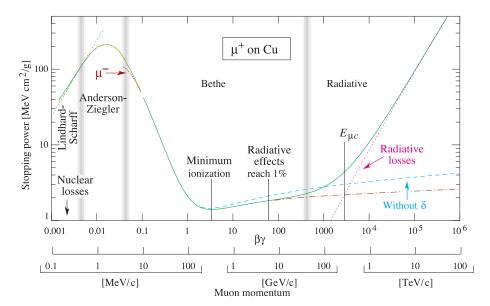

| 3.10 |                                                                         | 27 |

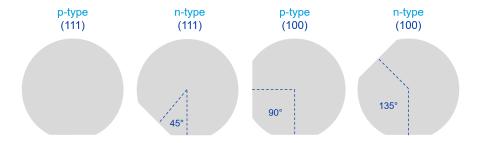

|      | cross section for photon interaction with carbon                        | 29 |

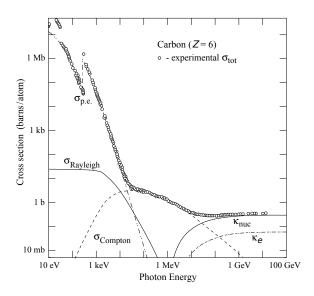

|      | Visualisation of the stopping power of copper for muons                 | 30 |

|      | Interaction processes of electrons with matter                          | 31 |

|      | Types of lattice defects                                                | 32 |

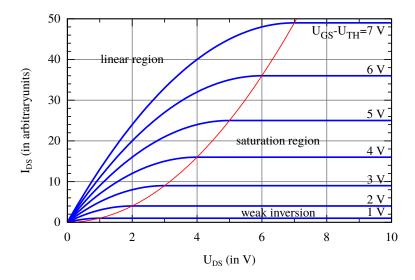

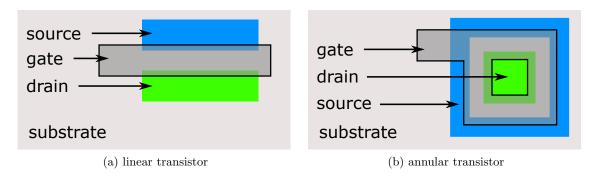

|      | MOSFET implementation shapes                                            | 34 |

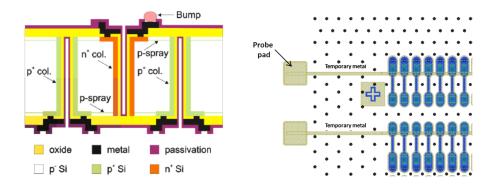

|      | Hybrid silicon detector types                                           | 35 |

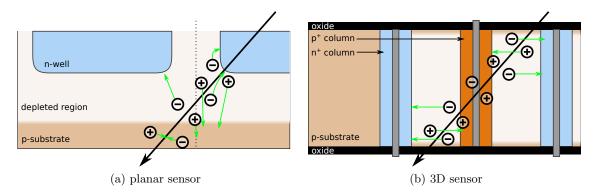

|      | Charged particle interaction with silicon sensors                       | 36 |

|      | Structure of a silicon 3D pixel sensor                                  | 36 |

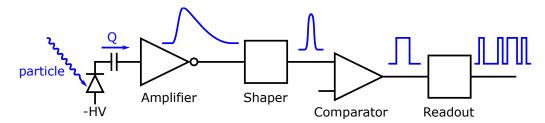

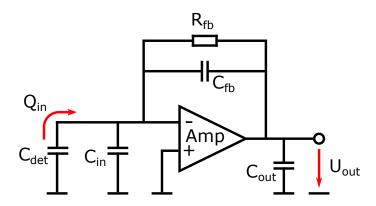

|      | Signal chain in a monolithic HVCMOS sensor                              | 38 |

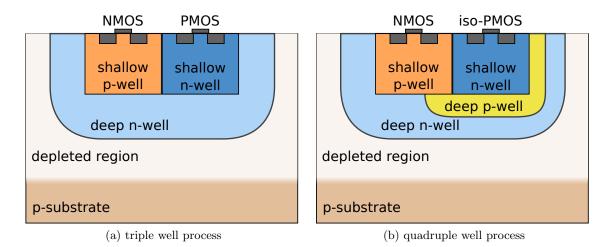

|      | Well structure of HVCMOS sensors                                        | 39 |

| 3.21 | Simplified schematics of the CSA                                        | 39 |

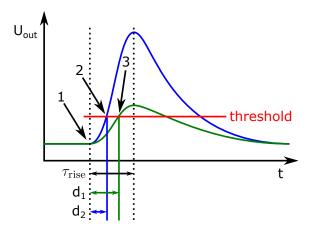

| 3.22 | Time-walk effect visualisation                                          | 40 |

| 4.1  | GECCO Logo                                                              | 43 |

| 4.2  | Signal Diagram of the GECCO board                                       |    |

| 4.3  | Photographs of the GECCO board                                          | 45 |

| 4.4  | GECCO Firmware Module Structure                                         | 46 |

| 4.5  | GECCO Software Structure                                                | 48 |

| 4.6  | User Interface of the GECCO software                                    | 55 |

| 4.7  | Tests section of the GECCO software user interface                      | 56 |

| 4.8  | Data processing structure of the UDP reaodut software                   | 57 |

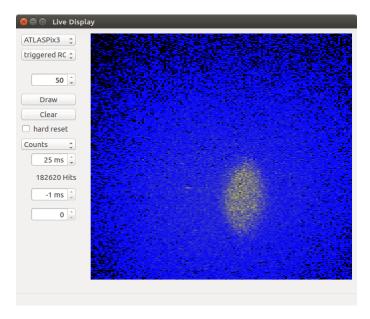

| 4.9  | UDP Readout User Interface                                              | 58 |

| 4 10 | UDP Readout Live Data Visualisation                                     | 59 |

xiv List of Figures

| 4.11 | Light absorption in semiconductors                                                | 60  |

|------|-----------------------------------------------------------------------------------|-----|

| 4.12 | Microfocus of the laser setup                                                     | 62  |

| 4.13 | Flanges on the Laser Setup box                                                    | 62  |

| 4.14 | Hardware inside the box of the laser setup                                        | 63  |

|      | The Laser Setup Control GUI                                                       | 65  |

|      |                                                                                   |     |

| 5.1  | ROME Logo                                                                         | 68  |

| 5.2  | ROME Processing Structure                                                         | 69  |

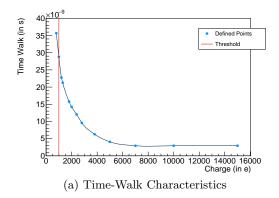

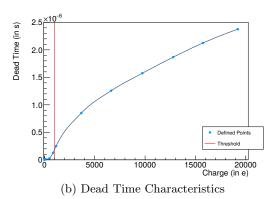

| 5.3  | Analogue Characteristics for Signal Generation                                    | 72  |

| 5.4  | Example State Machine Visualisation from ROME                                     | 73  |

| 5.5  | Comparison of pixel efficiency and particle efficiency                            | 76  |

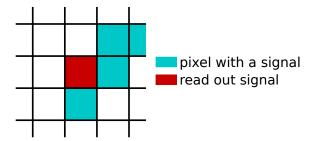

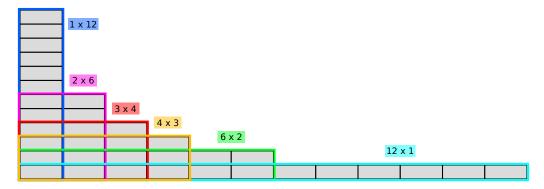

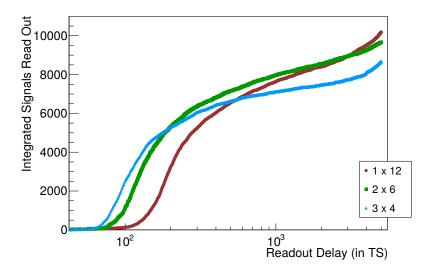

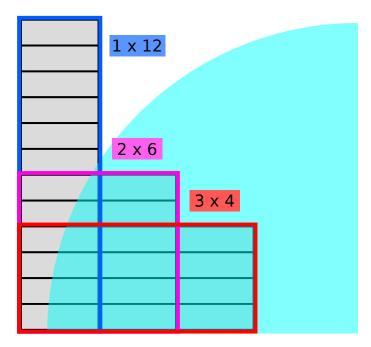

| 5.6  | Possible group shapes for 12 pixels                                               | 77  |

| 5.7  | Readout delay distribution for grouped readout                                    | 78  |

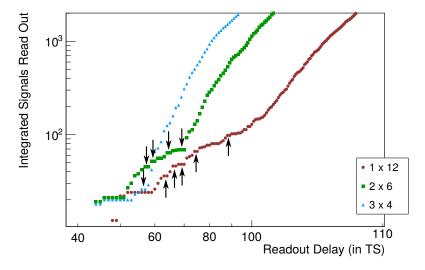

| 5.8  | Influence of the group shape on the readout speed                                 | 79  |

| 5.9  | Zoom-in on the readout delay distribution of grouped readout                      | 79  |

| 5.10 | Readout procedure comparison                                                      | 81  |

| 5.11 | Readout Performance depending on grade of time sorting                            | 82  |

| 5.12 | ROME architecture for the ATLASPix3 simulations                                   | 84  |

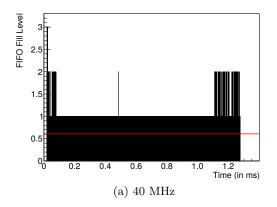

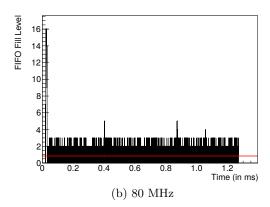

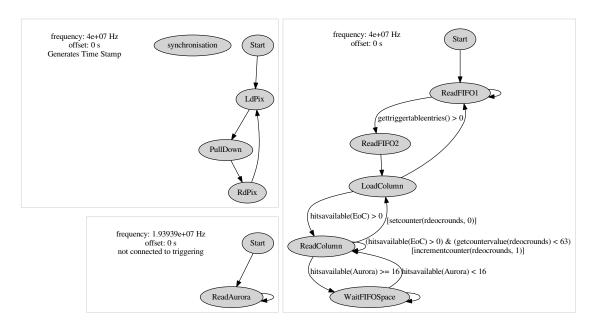

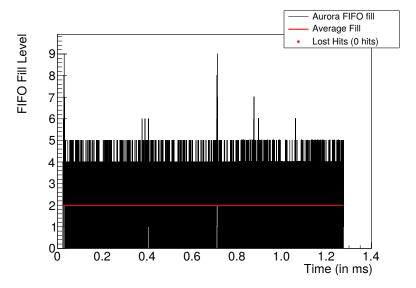

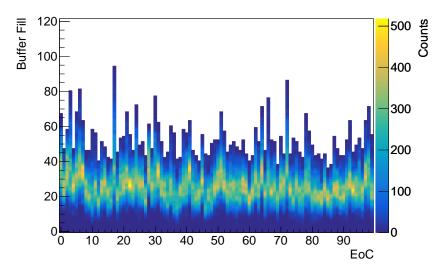

| 5.13 | Aurora first-in-first-out buffer (FIFO) fill state for state machine optimisation | 86  |

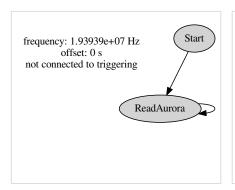

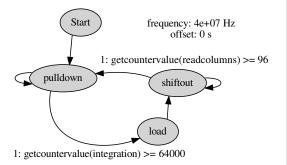

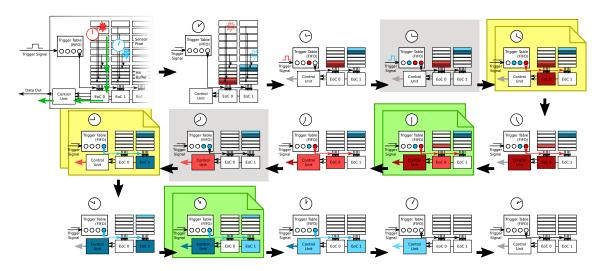

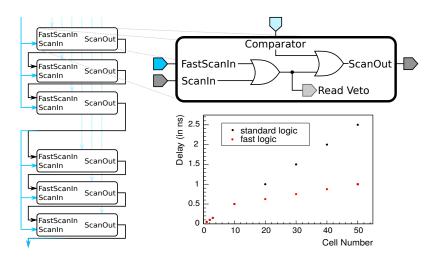

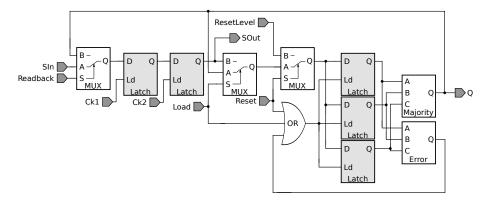

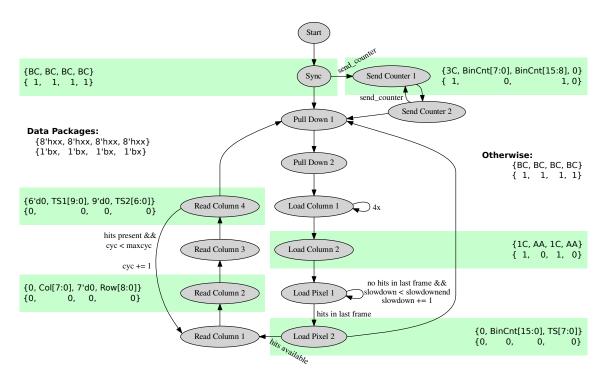

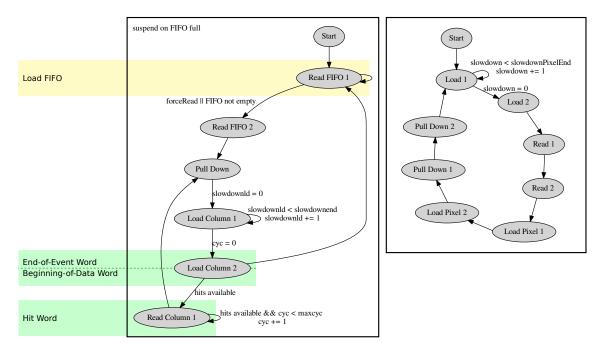

|      | State machines for the simulation of the reaodut architecture of ATLASPix3        | 87  |

| 5.15 | Encoder FIFO fill state over time                                                 | 89  |

|      | Column buffer content over time per column                                        | 89  |

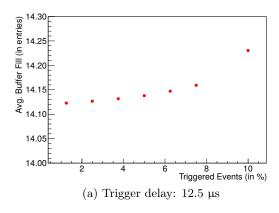

|      | Column buffer dependence on triggered fraction and trigger signal delay           | 90  |

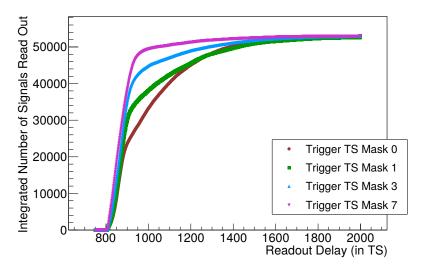

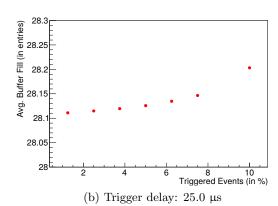

|      | Influence of the trigger table on the readout delay                               | 91  |

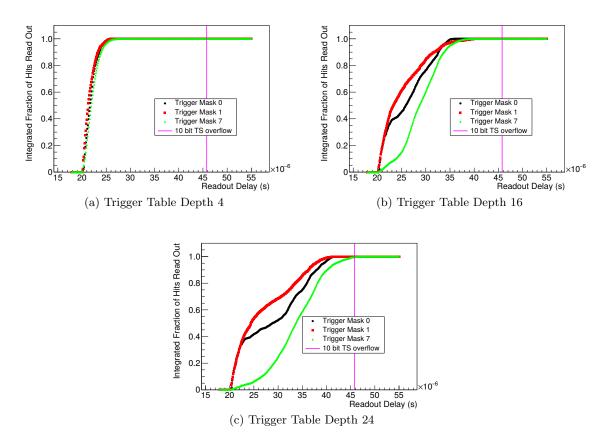

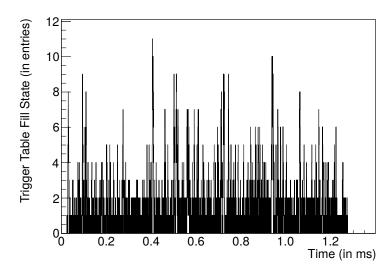

|      | Trigger Table Fill State in final design                                          | 92  |

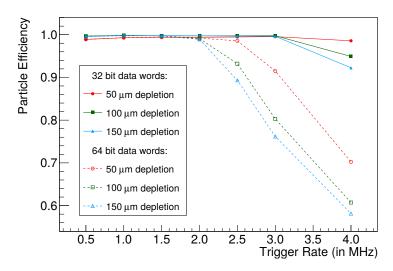

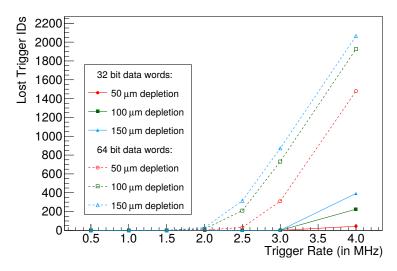

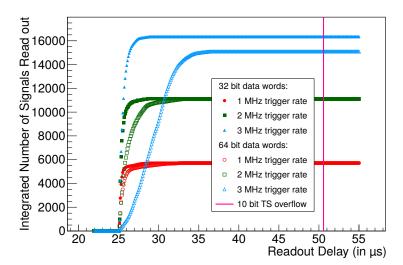

|      | Particle efficiency dependency on data word size                                  | 93  |

|      | Lost triggers in ATLASPix3 readout over trigger rate                              | 94  |

|      | Influence of the data word on the readout performance of ATLASPix3                | 94  |

| 0    | _                                                                                 | 0 1 |

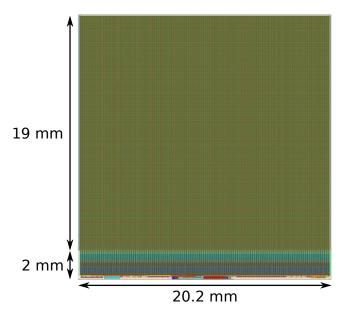

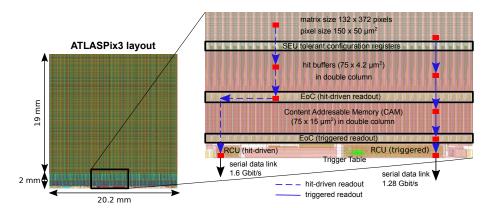

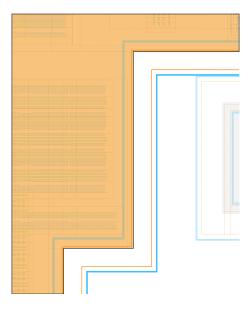

| 6.1  | Layout of ATLASPix3                                                               | 99  |

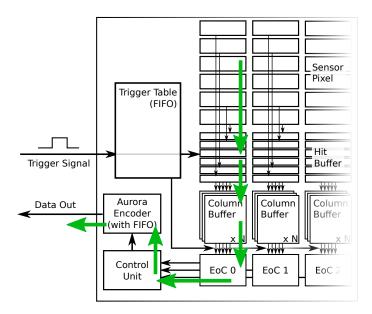

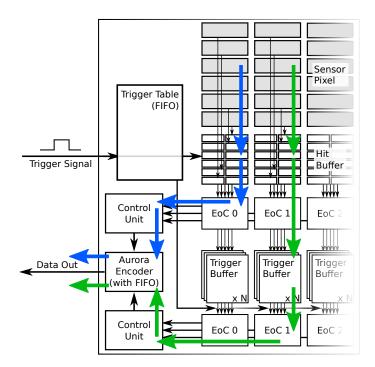

| 6.2  | Readout Architecture of ATLASPix3                                                 | 100 |

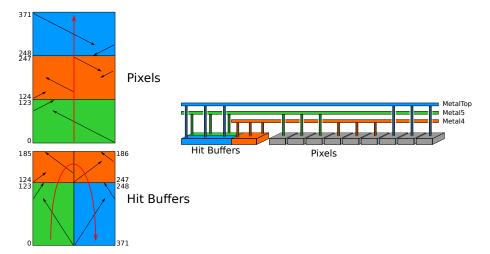

| 6.3  | Pixel to hit buffer connection layout on ATLASPix3                                | 101 |

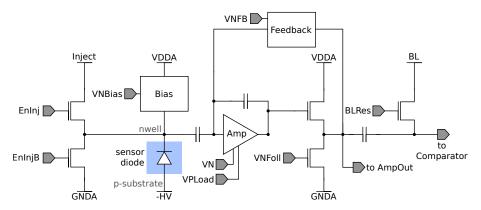

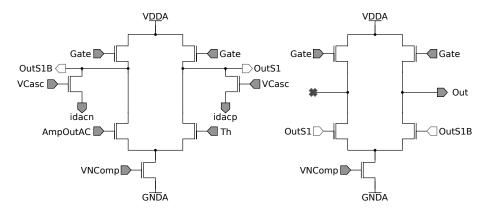

| 6.4  | Schematic of the Pixel Amplifier                                                  | 102 |

| 6.5  | Schematics of the in-pixel comparator of ATLASPix3                                |     |

| 6.6  | ATLASPix3 Pixel Layout                                                            |     |

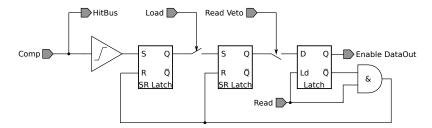

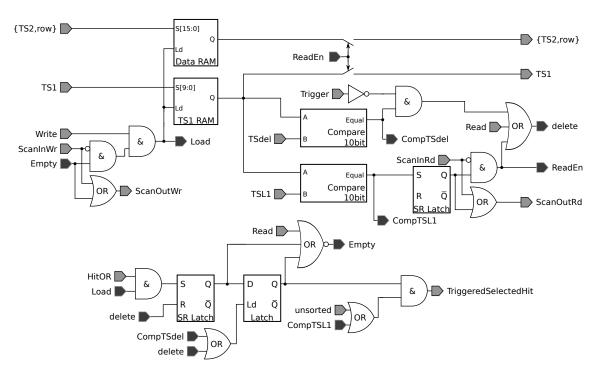

| 6.7  | Simplified Schematic of the hit buffer of ATLASPix3                               |     |

| 6.8  | Implementation of the priority chain on ATLASPix3                                 |     |

| 6.9  | Simplified schematics of the content addressable memory of ATLASPix3              |     |

|      | Schematic of a shift register bit for configuration                               |     |

|      | Clocking Scheme of ATLASPix3                                                      |     |

|      | Readout state machine for hit-driven readout on ATLASPix3                         |     |

|      | Readout state machine flow chart for triggered readout of ATLASPix3               |     |

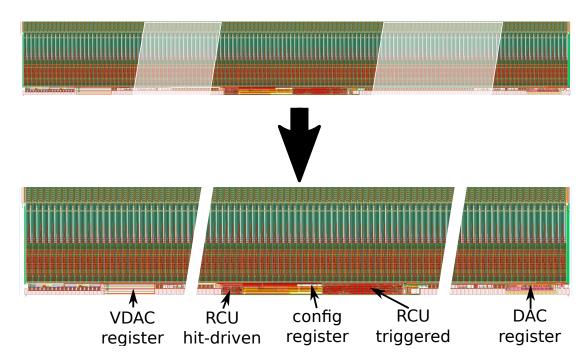

|      | Layout of the Readout Structures on ATLASPix3                                     |     |

|      | Layout of the periphery of ATLASPix3                                              |     |

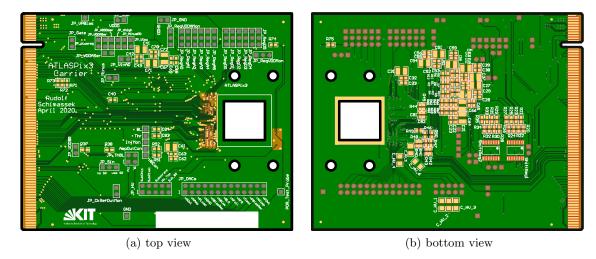

|      | Layout of the ATLASPix3 chip carrier for the GECCO measurement setup              |     |

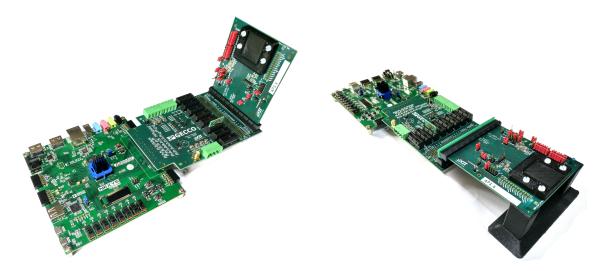

|      | Photograph of the ATLASPix3 measurement setup                                     |     |

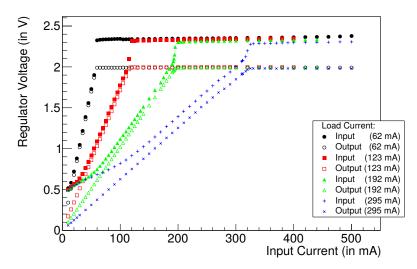

|      | VDDA Regulator on ATLASPix3.1                                                     |     |

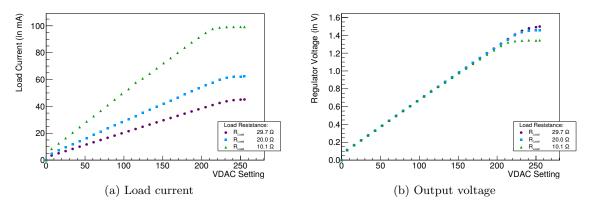

|      | Characteristics of the VSSA regulator on ATLASPix3                                |     |

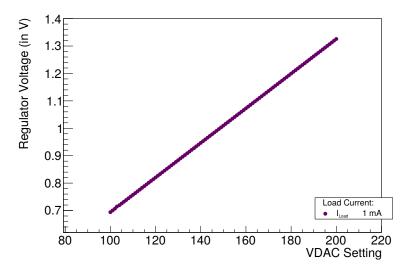

|      | V <sub>minus</sub> regulator output over the control DAC value                    |     |

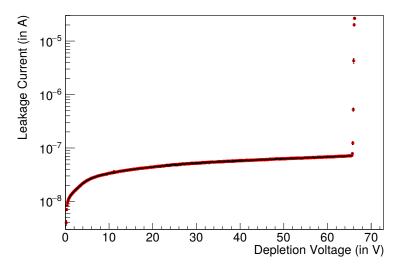

|      | IV Curve of the Sensor Diodes of ATLASPix3                                        |     |

|      | Well geometry of ATLASPix3                                                        |     |

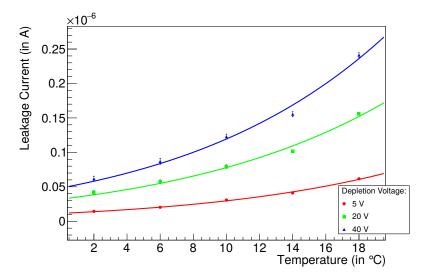

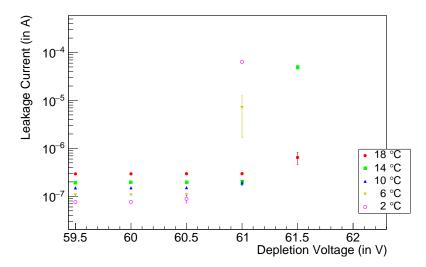

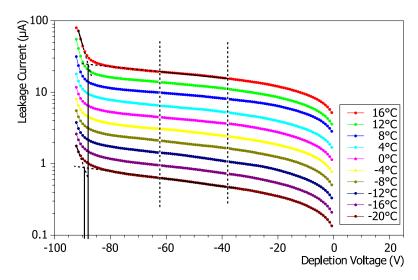

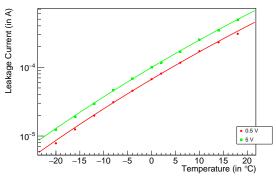

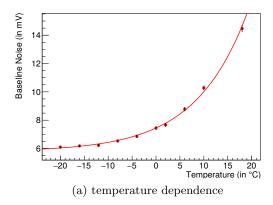

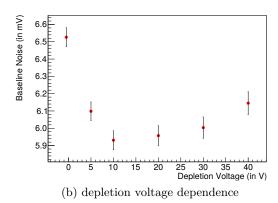

|      | Temperature dependence of the leakage current on ATLASPix3                        |     |

| 0.20 | remperature dependence of the leakage current on ATLASI ISS                       | 140 |

List of Figures xv

|      | Breakdown voltage shift with temperature on a non-irradiated ATLASPix3                                        |     |

|------|---------------------------------------------------------------------------------------------------------------|-----|

|      | IV characteristics of the HitPix detector ASIC                                                                |     |

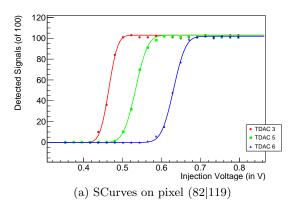

| 6.26 | Detection Threshold determination with an SCurve                                                              | 126 |

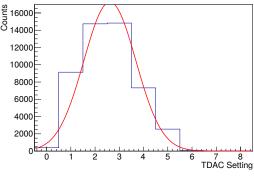

| 6.27 | TDAC Effect on Detection Threshold on ATLASPix3                                                               | 126 |

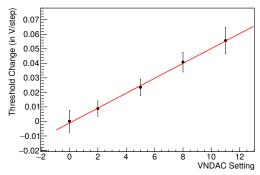

| 6.28 | Effect of VNDAC on the TDAC step size                                                                         | 127 |

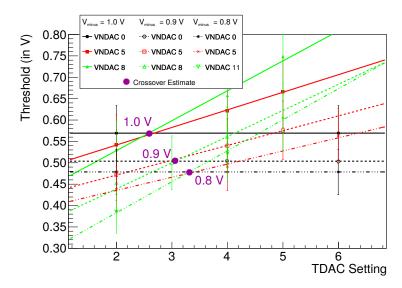

| 6.29 | $V_{minus}$ dispersion of the TDAC cross-over point                                                           | 127 |

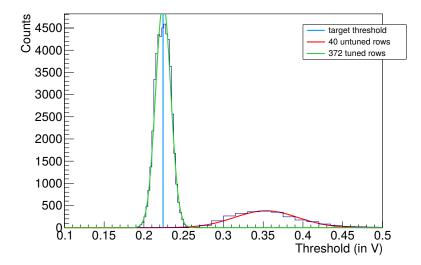

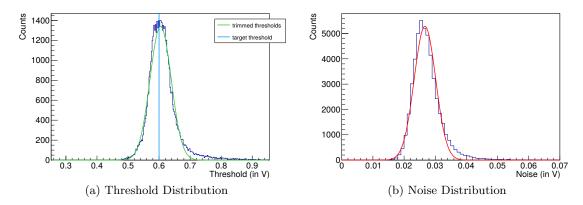

| 6.30 | Threshold tuning result on ATLASPix3                                                                          | 129 |

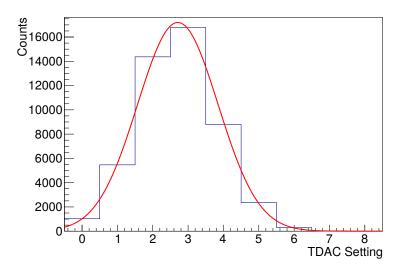

|      | TDAC setting distribution after threshold tuning                                                              |     |

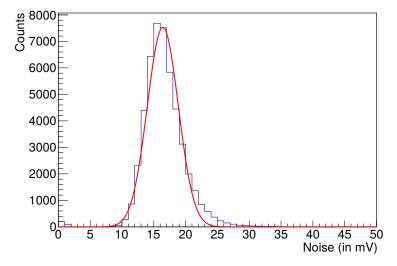

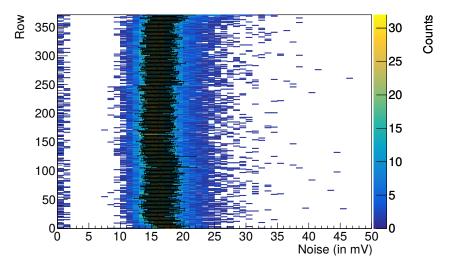

| 6.32 | Noise distribution after tuning on ATLASPix3                                                                  | 130 |

|      | Noise Correlation with row number on ATLASPix3                                                                |     |

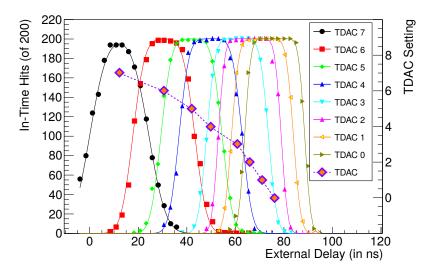

|      | Pixel Timing Key-Hole Measurement                                                                             |     |

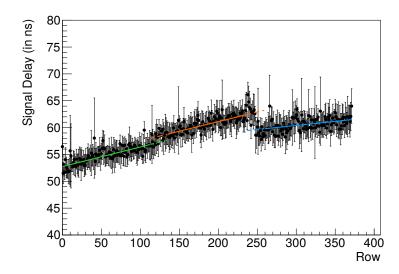

|      | Row Dependence of the Signal Delay                                                                            |     |

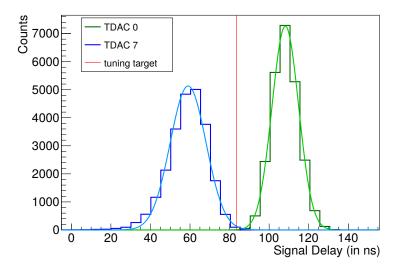

|      | Delay Range for Timing Optimisation of the Matrix with TDACs                                                  |     |

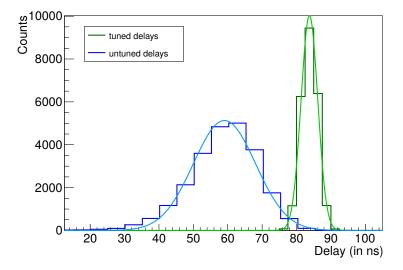

|      | Timing Tuning Result Comparison                                                                               |     |

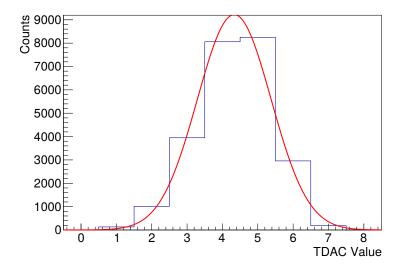

|      | Result TDAC Distribution for Timing Tuning                                                                    |     |

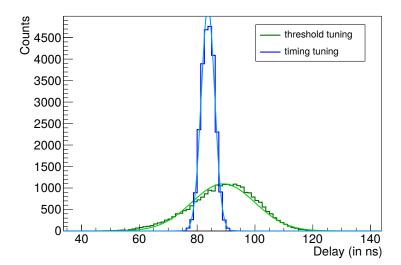

|      | Pixel Delay Comparison for Threshold and Timing Tuning                                                        |     |

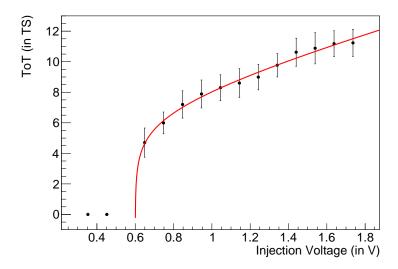

|      | ToT Dependence on Signal Size                                                                                 |     |

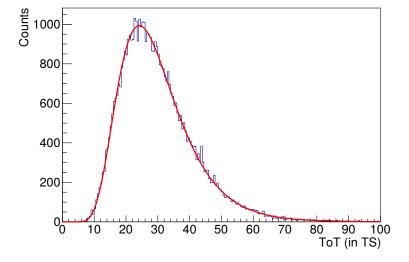

|      | ToT Distribution for a fixed signal size for the whole matrix                                                 |     |

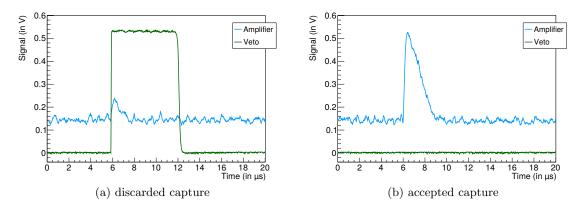

|      | Strontium measurement signal vetoing                                                                          |     |

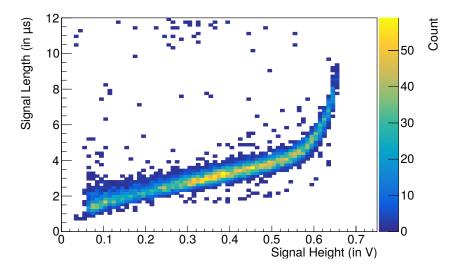

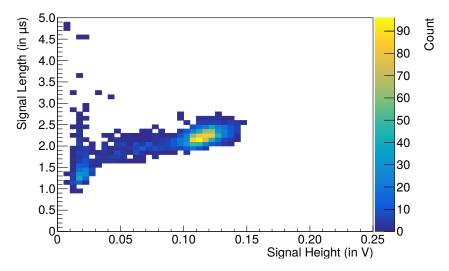

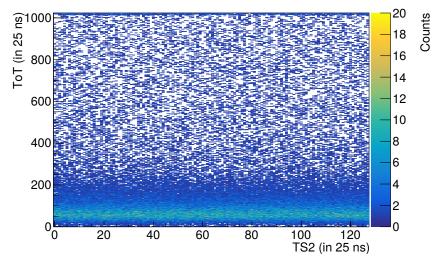

|      | Signal height and length correlation for <sup>90</sup> Sr electrons on ATLASPix3                              |     |

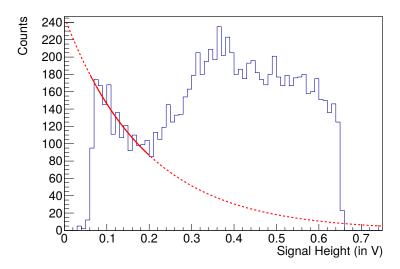

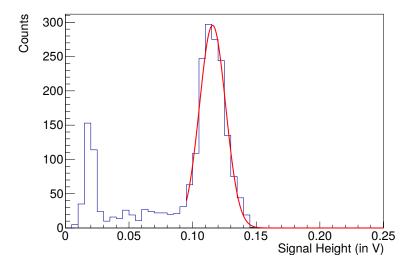

|      | Strontium-90 signal height distribution with background                                                       |     |

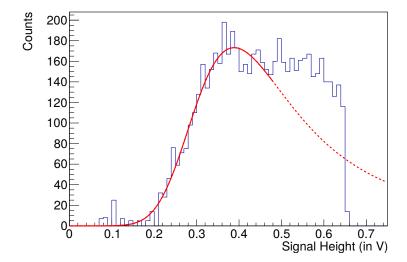

|      | Signal Height distribution from <sup>90</sup> Sr without background                                           |     |

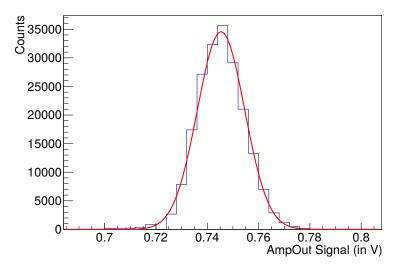

|      | Baseline histogrammed for the amplifier output on ATLASPix3                                                   |     |

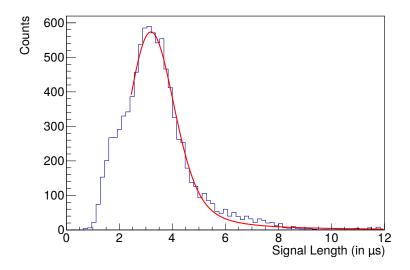

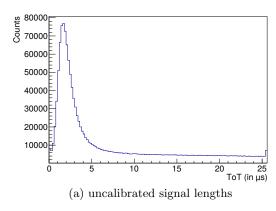

|      | Signal length distribution for <sup>90</sup> Sr signals on ATLASPix3                                          |     |

|      | Signal height distribution on ATLASPix3 for <sup>90</sup> Sr at 20 V depletion                                |     |

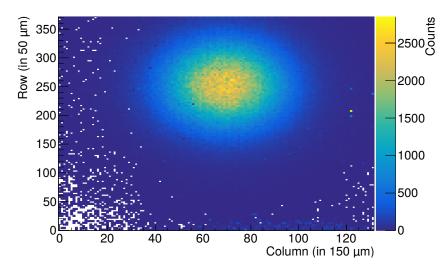

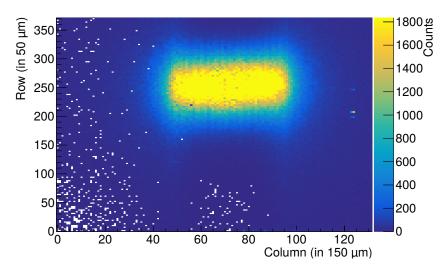

|      | Hitmap of <sup>90</sup> Sr on ATLASPix3                                                                       |     |

|      | ToT distribution for <sup>90</sup> Sr on ATLASPix3                                                            |     |

|      | ToT dispersion with depletion voltage for <sup>90</sup> Sr on ATLASPix3                                       |     |

|      | 55Fe Signal Height and Length Correlation                                                                     |     |

|      | 55Fe Signal Height Histogram                                                                                  |     |

|      | Test signal injection size correlation on ATLASPix3                                                           |     |

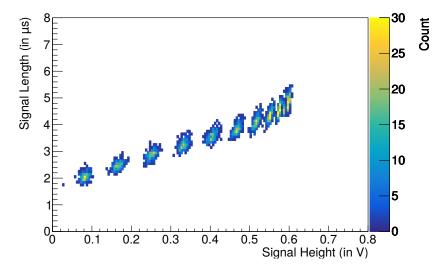

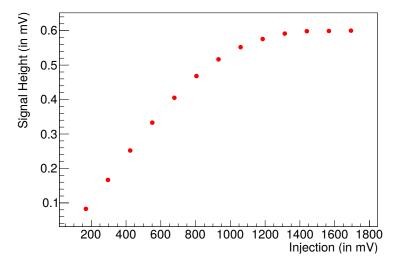

|      | Characteristics for the test signal injections on ATLASPix3                                                   |     |

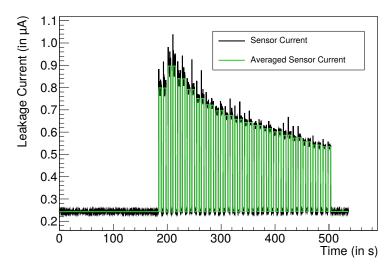

|      | Leakage current measurement on ATLASPix3 during a beam test                                                   |     |

|      | Beam induces leakage current for different beam energies                                                      |     |

|      |                                                                                                               |     |

|      | Leakage current on ATLASPix3 for different beam intensities                                                   |     |

|      | Sketch of the shielding used for the beam at HIT                                                              |     |

|      |                                                                                                               |     |

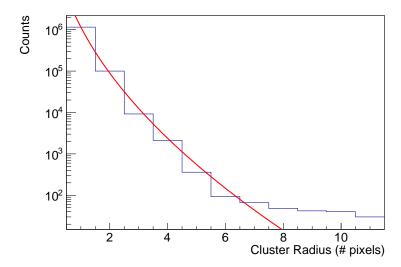

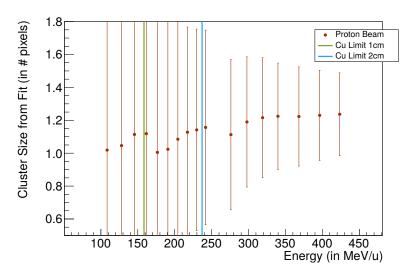

|      | Clustersize dependency on the particle energy for a proton beam on ATLASPix3                                  |     |

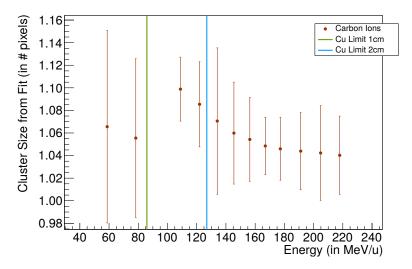

|      | Clustersize dependency on particle energy for a carbon ion beam                                               |     |

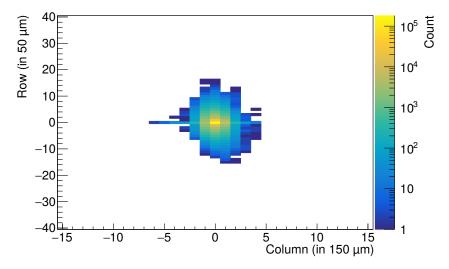

|      | Cluster shape for a carbon beam after the copper target in front of ATLASPix Carbon beam hitmap on ATLASPix 3 |     |

|      |                                                                                                               |     |

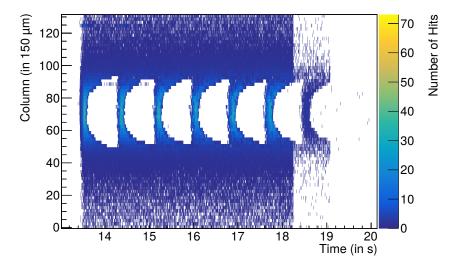

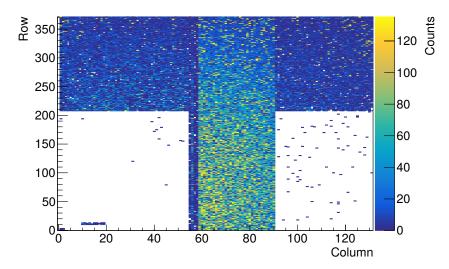

|      | Trigger buffer limited beam profile on ATLASPix3                                                              |     |

|      | Column readout over time on ATLASPix3                                                                         |     |

|      | Leakage Current IV curves for proton irradiated ATLASPix3                                                     |     |

|      | Noise dispersion on a proton irradiated ATLASPix3                                                             |     |

|      | SCurves on ATLASPix3 after proton irradiation                                                                 |     |

|      | Threshold and noise distribution on a tuned ATLASPix3 after irradiation .                                     |     |

|      | Hitmap of an iron-55 source on a proton-irradiated ATLASPix3                                                  |     |

|      | Irradiation spot shape for ion irradiation at HIT                                                             |     |

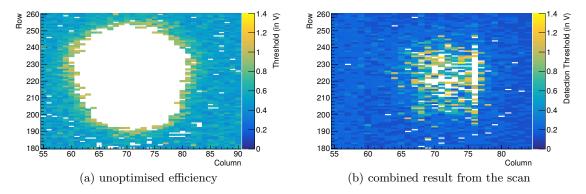

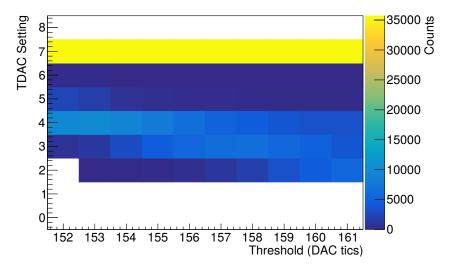

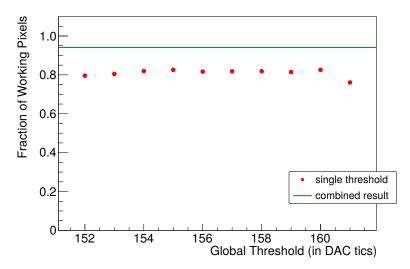

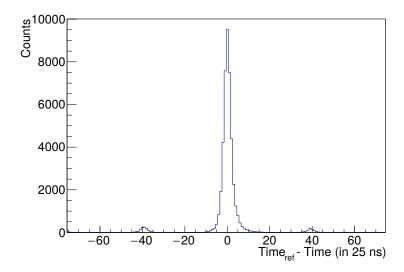

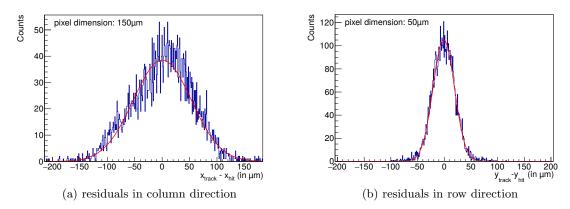

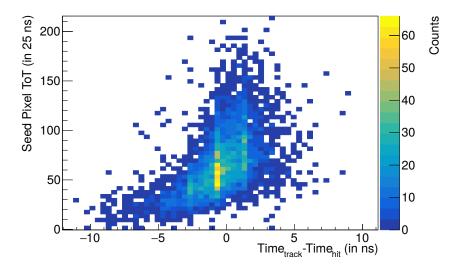

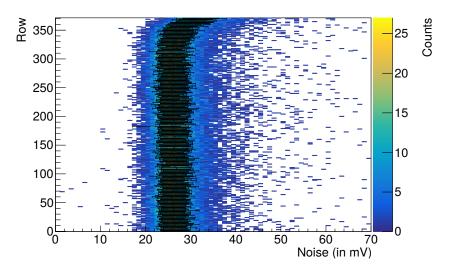

|      | Sensor leakage current on ion irradiated ATLASPix3 integrated sensors at HIT                                  |     |