# A Flexible FPGA-based Control Platform for Superconducting Multi-Qubit Experiments

Zur Erlangung des akademischen Grades eines Doktors der Naturwissenschaften (Dr. rer. nat.)

von der KIT-Fakultät für Physik des Karlsruher Instituts für Technologie (KIT)

angenommene

Dissertation

von

M. Sc. Richard Gebauer

Tag der mündlichen Prüfung: 17. Dezember 2021

Referent: Prof. Dr. Marc Weber

Korreferent: Prof. Dr. Martin Weides

Betreuer: PD Dr. Oliver Sander

## **Contents**

| 1 | Intr                     | oductio     | on                             |  |  |  |  |  |

|---|--------------------------|-------------|--------------------------------|--|--|--|--|--|

| 2 | Fun                      | undamentals |                                |  |  |  |  |  |

|   | 2.1                      | Quan        | tum Computing                  |  |  |  |  |  |

|   |                          | 2.1.1       | Quantum Bits                   |  |  |  |  |  |

|   |                          | 2.1.2       | Quantum Gates                  |  |  |  |  |  |

|   |                          | 2.1.3       | Quantum Registers              |  |  |  |  |  |

|   |                          | 2.1.4       | Quantum Algorithms             |  |  |  |  |  |

|   |                          | 2.1.5       | Quantum Error Correction       |  |  |  |  |  |

|   | 2.2                      | Super       | conducting Quantum Bits        |  |  |  |  |  |

|   |                          | 2.2.1       | Superconductivity              |  |  |  |  |  |

|   |                          | 2.2.2       | Two-Level Quantum Systems      |  |  |  |  |  |

|   |                          | 2.2.3       | Rabi Cycles                    |  |  |  |  |  |

|   |                          | 2.2.4       | Dispersive Readout             |  |  |  |  |  |

|   |                          | 2.2.5       | Transition Frequency Tuning    |  |  |  |  |  |

|   |                          | 2.2.6       | Example Implementation         |  |  |  |  |  |

|   |                          | 2.2.7       | Multi-Qubit Interaction        |  |  |  |  |  |

|   |                          | 2.2.8       | Quantum Software Tools         |  |  |  |  |  |

|   | 2.3                      | Typica      | al Experiment Setup            |  |  |  |  |  |

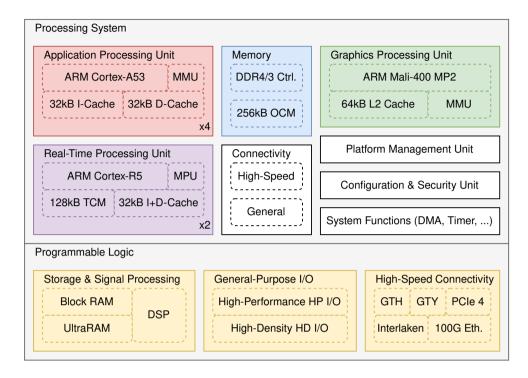

|   | 2.4                      | FPGA        | s and Heterogeneous Systems    |  |  |  |  |  |

|   |                          | 2.4.1       | Field-Programmable Gate Array  |  |  |  |  |  |

|   |                          | 2.4.2       | Multi-Processor System-on-Chip |  |  |  |  |  |

|   |                          | 2.4.3       | Radio Frequency System-on-Chip |  |  |  |  |  |

|   | 2.5                      | Sumn        | nary                           |  |  |  |  |  |

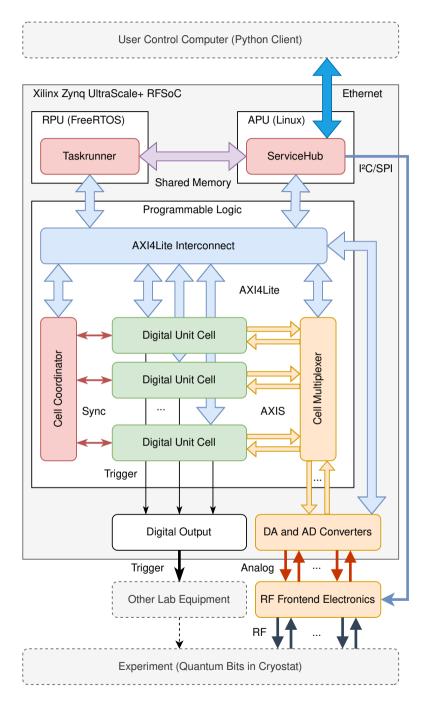

| 3 | Plat                     | form A      | architecture                   |  |  |  |  |  |

|   | 3.1                      | Funct       | ional Requirements             |  |  |  |  |  |

|   | 3.2 QiController Concept |             | ntroller Concept               |  |  |  |  |  |

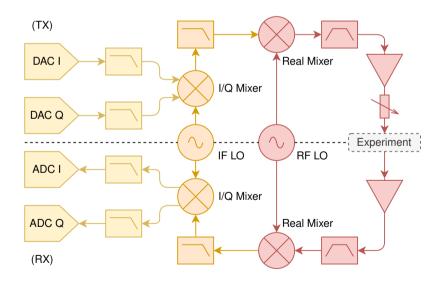

|   | 3.3                      | Analo       | g RF Frontend                  |  |  |  |  |  |

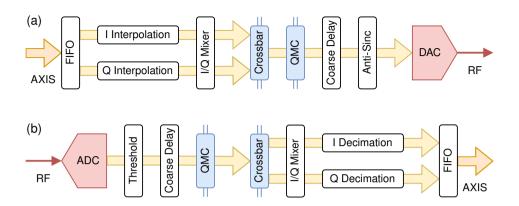

|   | 3.4                      | Progr       | ammable Logic                  |  |  |  |  |  |

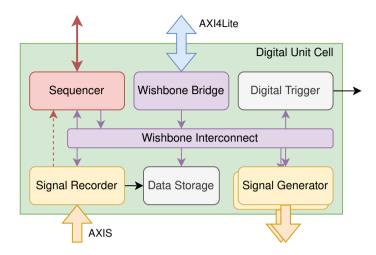

|   |                          | 3.4.1       | Digital Unit Cell              |  |  |  |  |  |

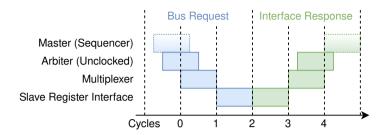

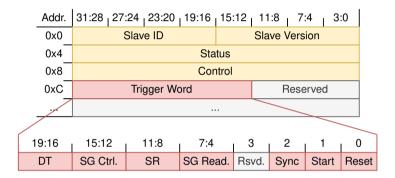

|   |                          | 3.4.2       | Wishbone Bus Infrastructure 50 |  |  |  |  |  |

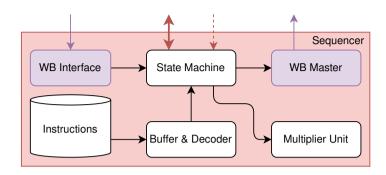

|                        |      | 3.4.3  | Sequencer                                   |

|------------------------|------|--------|---------------------------------------------|

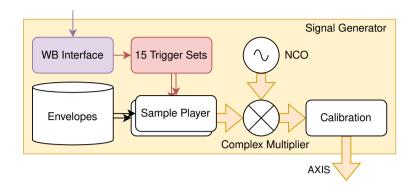

|                        |      | 3.4.4  | Signal Generator                            |

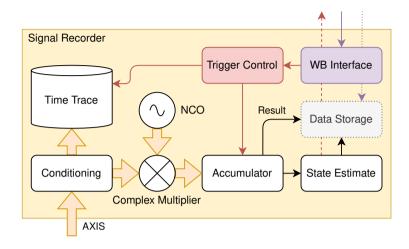

|                        |      | 3.4.5  | Signal Recorder                             |

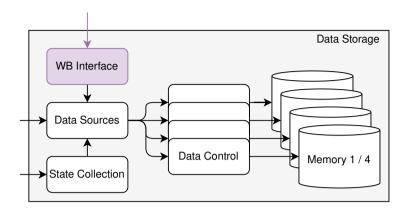

|                        |      | 3.4.6  | Data Storage                                |

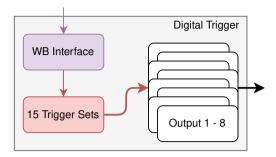

|                        |      | 3.4.7  | Digital Trigger Output 61                   |

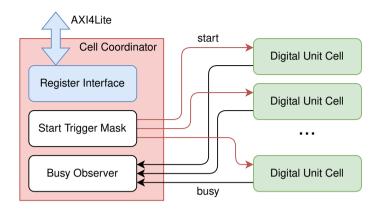

|                        |      | 3.4.8  | Cell Coordinator                            |

|                        |      | 3.4.9  | Cell Multiplexer                            |

|                        |      | 3.4.10 | Platform Information and Management Core 64 |

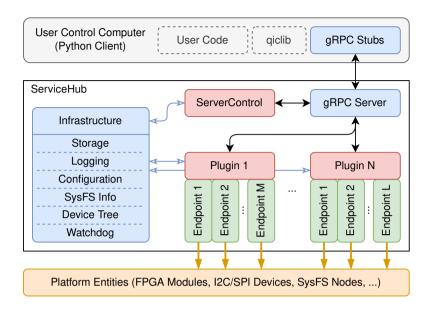

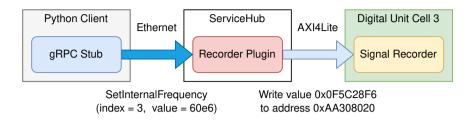

|                        | 3.5  | Softw  | are Stack                                   |

|                        |      | 3.5.1  | ServiceHub                                  |

|                        |      | 3.5.2  | Taskrunner                                  |

|                        |      | 3.5.3  | Boot and Initialization                     |

|                        |      | 3.5.4  | System Reliability                          |

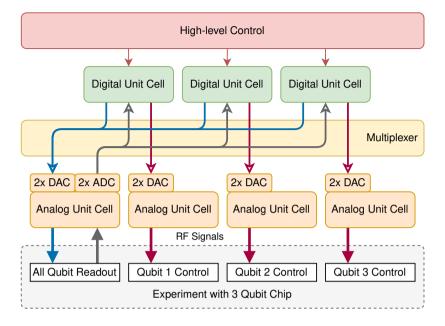

|                        | 3.6  | Scalab | bility                                      |

|                        |      | 3.6.1  | Single Platform                             |

|                        |      | 3.6.2  | Multiple Platforms                          |

|                        | 3.7  | Chara  | cterization Results                         |

|                        |      | 3.7.1  | Resource Utilization                        |

|                        |      | 3.7.2  | Analog Signal Properties                    |

|                        |      | 3.7.3  | Digital Signal Properties                   |

|                        | 3.8  | Summ   | nary                                        |

| 4                      | Plat | form I | nterface and Control                        |

|                        | 4.1  | Philos | sophy                                       |

|                        | 4.2  | Pytho  | n Client qiclib                             |

|                        | 4.3  | Typica | al Use Cases                                |

|                        |      | 4.3.1  | Setup and Initialization                    |

|                        |      | 4.3.2  | Pseudo-VNA Measurement                      |

|                        |      | 4.3.3  | Single-Qubit Characterizations              |

|                        |      | 4.3.4  | Single-Shot Resonator Response Plots        |

|                        |      | 4.3.5  | Multi-Qubit Characterizations               |

|                        | 4.4  | Exper  | iment Description Language QiCode           |

|                        |      | 4.4.1  | Concept                                     |

|                        |      | 4.4.2  | Available Commands                          |

|                        |      | 4.4.3  | Compilation                                 |

|                        |      | 4.4.4  | Execution                                   |

|                        |      | 4.4.5  | Custom Data Processing                      |

|                        |      | 4.4.6  | Current Limitations                         |

|                        | 4.5  | Qkit I | ntegration                                  |

| 4.6 Qiskit Integration |      |        | Integration                                 |

|                        | 4.7  | Summ   | nary                                        |

| 5  | Exp   | erimen  | tal Applications                                         |

|----|-------|---------|----------------------------------------------------------|

|    | 5.1   | Fast F  | eedback Control for State Preparation                    |

|    |       | 5.1.1   | Motivation and Physics Background 125                    |

|    |       | 5.1.2   | Experiment Setup                                         |

|    |       | 5.1.3   | QiController Setup                                       |

|    |       | 5.1.4   | Results and Discussion                                   |

|    | 5.2   | Quan    | tum Jumps Measurement                                    |

|    |       | 5.2.1   | Motivation and Physics Background                        |

|    |       | 5.2.2   | Experiment Setup                                         |

|    |       | 5.2.3   | QiController Setup                                       |

|    |       | 5.2.4   | Results and Discussion                                   |

|    | 5.3   | Detec   | ting and Changing the Speed of Light                     |

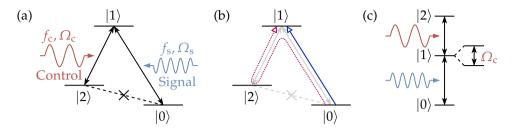

|    |       | 5.3.1   | Motivation and Physics Background                        |

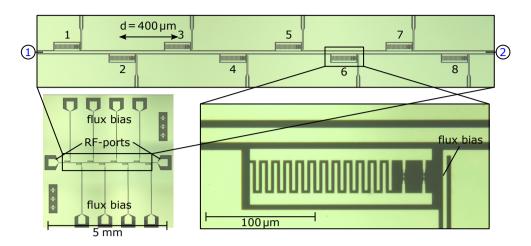

|    |       | 5.3.2   | Experiment Setup                                         |

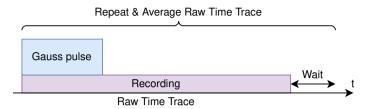

|    |       | 5.3.3   | QiController Setup                                       |

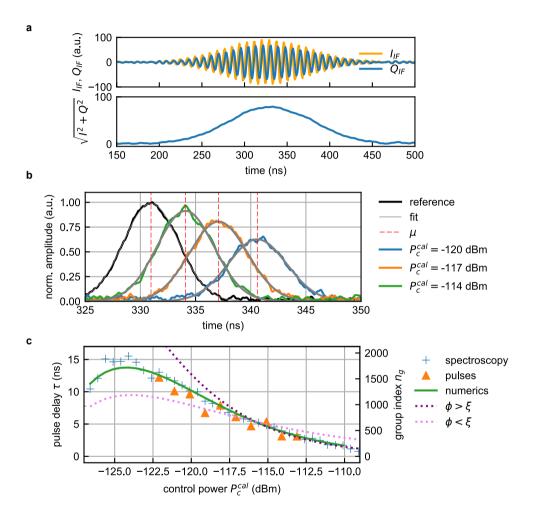

|    |       | 5.3.4   | Results and Discussion                                   |

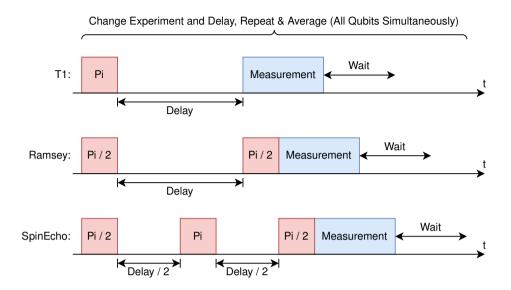

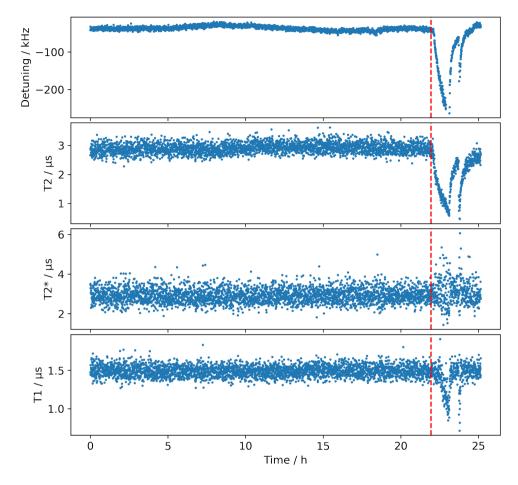

|    | 5.4   | Simul   | taneous, Time-Resolved Multi-Qubit Characterizations 139 |

|    |       | 5.4.1   | Motivation and Physics Background                        |

|    |       | 5.4.2   | Experiment Setup                                         |

|    |       | 5.4.3   | QiController Setup                                       |

|    |       | 5.4.4   | Results and Discussion                                   |

|    | 5.5   | Summ    | nary                                                     |

| 6  | Con   | clusio  | 1                                                        |

| ъ. |       |         | 4                                                        |

| В  | bliog | raphy   |                                                          |

| Li | st of | Publica | ations                                                   |

| Li | st of | Abbrev  | viations                                                 |

| A  | ppen  | dix     |                                                          |

|    | Α     |         | Processing                                               |

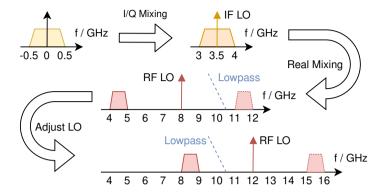

|    |       | A.1     | Quadrature Frequency Mixing                              |

|    |       | A.2     | Digital Down Conversion                                  |

|    |       | A.3     | Frequency-Division Multiplexing                          |

|    | В     | Progra  | ammable Logic                                            |

|    |       | B.1     | Sequencer Commands                                       |

|    |       | B.2     | Signal Generator Timing                                  |

|    |       | B.3     | Measurement-based Feedback Timing                        |

|    | C     | Taskrı  | unner                                                    |

|    |       | C.1     | Interface to the Taskrunner Firmware                     |

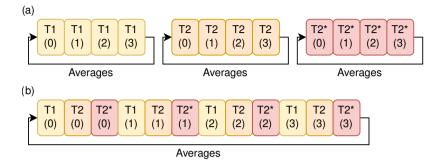

|       | C.2              | Interleaved Experiment Task for Multiple Qubits   | 184 |  |

|-------|------------------|---------------------------------------------------|-----|--|

|       | C.3              | Quantum Jumps Collection Task for Multiple Qubits | 187 |  |

| D     | Characterization |                                                   |     |  |

|       | D.1              | Phase Noise of Analog Output Signal               | 189 |  |

| Ackno | wledo            | ments                                             | 191 |  |

## 1 Introduction

Quantum computers promise to solve specific computational problems much faster than any conventional computer [1]. Their elementary building blocks are two-level systems called quantum bits (qubits) [2]. Like classical bits, they are comprised of two fundamental states, denoted as  $|0\rangle$  and  $|1\rangle$ . Two important effects distinguish qubits from their classical counterparts: superposition and entanglement. The former describes the ability of qubits to be in both fundamental states at the same time. The latter is defined between multiple qubits and means that the states of these no longer have to be independent of each other.

Superposition and entanglement lead to the enormous gain in computing performance for certain problems [3]. Potential applications of quantum computers are manifold, including integer factorization [4], quantum encryption [5], [6], database search [7], simulations of large and complex systems [8], [9], drug research and discovery [10], [11], material science [12], as well as general optimization problems [13] like quantum machine learning [14].

In the last 30 years, different physical realizations of qubits have been proposed. Well-known examples are ion traps [15], [16], individual photons [17]–[19], semiconductor quantum dots [20]–[22], and superconducting circuits [23]–[26]. Recently, especially the latter gained additional momentum due to the increasing interest and research activities of major information technology companies like Google, IBM, and Microsoft [27]. In March 2018, Google presented a superconducting quantum processor with 72 qubits [28]. One and a half years later, they successfully demonstrated quantum advantage [29] on 53 qubits by outperforming a classical supercomputer when sampling the result of a pseudo-random quantum circuit.

Eventually, many more qubits are necessary for a universal quantum computer [30], as they are subject to noise of the environment. Together with intrinsic imperfections, this distorts the qubit states leading to errors [31], [32]. To perform successful calculations, these must be accounted for using quantum error correction. In contrast to classical correction schemes, hundreds to thousands of physical qubits are needed to form a protected, so-called logical qubit [33]. A universal quantum computer will thus need thousands of physical qubits for a few logical ones [30].

Scaling of multi-qubit systems is currently one of the challenges on the path to quantum computation and it is still unclear how the architecture of a future quantum processor will look like. Research towards a universal quantum computer has to consider the full hardware and software stack. An essential component is the interface between quantum algorithm and quantum processor which requires sophisticated control electronics [29], [34].

For superconducting qubits, such electronics needs to cover the generation of microwave signals with frequencies of up to 10 GHz [35], [36], as well as data acquisition and processing of similar signals to read out the state of the qubits [37], [38]. With arbitrary pulse shaping necessary and pulse durations between a few and hundreds of nanosecond [39], [40], this also implies tight timing requirements. Some quantum processors furthermore depend on nanosecond-accurate flux pulses generated by currents with microampere strength [41], [42], or DC bias currents, spanning a broad range from microampere to multiple amperes for some special applications [43], [44]. Advanced experiment and control schemes, as well as online data processing and reduction are necessary to cope with the high input data rates of tens of gigabyte per second and to reach sufficient statistics in reasonable time [45]–[47]. Custom electronics based on a field-programmable gate array (FPGA) can be utilized to meet the high processing demands [48]–[50].

In this thesis, such a control electronics for the interface between quantum and classical processing domains, called QiController, is designed, implemented, and tested. Major objectives for its development have been applicability to different types of superconducting qubits, as well as usability, scalability, and flexibility. It is targeted at advanced research and near-term applications with quantum processors. It also explores concepts to control future quantum processors. To leverage its full capabilities, the QiController is complemented by a high-level programming language, called QiCode.

The QiController is extensively tested with various superconducting single- and multi-qubit chips. The experiments range from single-qubit characterization measurements, over continuous observations of quantum jumps and time-resolved multi-qubit characterizations, to high-precision online state preparations using a fast feedback scheme. Some of these experiments are infeasible or even impossible to implement with commercial laboratory equipment. They demonstrate the capabilities of the QiController, as well as its flexibility, scalability, and usability.

## 2 Fundamentals

Building electronics for quantum computing in general and superconducting quantum bits (qubits) in particular requires a solid understanding of the physical principles regarding these qubits and belonging measurement concepts. This chapter first introduces the basic principles of quantum computing before elaborating in more detail on its realization using superconducting materials. Then, field-programmable gate arrays (FPGAs) and heterogeneous systems are introduced.

## 2.1 Quantum Computing

Quantum computers operate fundamentally differently than their classical counterparts. Problems that seem to be impractical to solve on a classical computer might be no challenge at all for a quantum computer [1]. Its power essentially emerges from the laws of quantum mechanics, especially the phenomena of superposition and entanglement [3]. However, quantum computers will most likely not replace classical computers as general-purpose machines. Rather, they can act as complementing accelerators in a heterogeneous computing system for special problems that can be efficiently solved on a quantum computer [51], [52].

Harnessing the quantum mechanical nature of these systems, one area of application relates to the simulation of systems that behave according to quantum mechanical laws [8]. This includes atoms as well as molecules and can, for example, be used for material science [12]. But it also includes more complex structures like proteins and their folding mechanisms which are very complex and resource-intensive to simulate classically [10]. Molecule and protein simulations both offer extensive opportunities in the field of drug research and discovery [11]. Other applications can be formulated as optimization problems which can be efficiently solved on a quantum computer [13]. This includes the area of quantum machine learning [14]. It also covers the simulation of large and complex systems, like solving the Navier-Stokes nonlinear differential equations for a viscous fluid [9]. Yet other applications center around the Grover algorithm to search efficiently through an unstructured database [7] or quantum encryption [5], [6] and Shor's algorithm to

perform efficient integer factorization [4]. The latter can have a significant impact when universal quantum computers are available and powerful enough to break the security of modern cryptosystems like RSA [53].

However, right now, these applications are still in the future and it is not well-established when a universal quantum computer with sufficient qubit count will be available. Yet, a few basic conditions that any experimental setup needs to fulfill in order to build a universal quantum computer can already be formulated. These are called the DiVincenzo criteria [54] and require a setup that:

- 1. is a scalable physical system with well-characterized qubits,

- 2. has the ability to initialize the qubits into a well-defined state,

- 3. consists of qubits with long coherence times in comparison to gate operations,

- 4. supports a universal set of quantum gates, and

- 5. provides means to reliably measure the qubit states.

The following sections will therefore elaborate on the definition of a qubit, means to control and measure their state, and how they are scaled up in a quantum computing architecture.

#### 2.1.1 Quantum Bits

Classical computers process information in binary form. The unit of information are bits which can only be in one of the two elementary states 0 and 1, corresponding to two distinct voltage levels  $V_{\rm GND}$  and  $V_{\rm CC}$ , respectively. Likewise, their quantum computing counterpart, the qubits, have two fundamental states, labeled  $|0\rangle$  and  $|1\rangle$  [2]. In most cases, these are eigenstates of the Hamilton operator  $\hat{H}$  of the system with energy eigenvalues  $E_0$  and  $E_1$ .

As qubits behave according to quantum mechanical laws, they can also be in a linear superposition of these two eigenstates:

$$|q\rangle = \alpha |0\rangle + \beta |1\rangle$$

with  $\alpha, \beta \in \mathbb{C}$ ,  $|\alpha|^2 + |\beta|^2 = 1$ . (2.1)

$\alpha$  and  $\beta$  are complex-valued coefficients which are only limited by the normalization requirement

$$\langle q|q\rangle := \int \Psi_q^*(x)\Psi_q(x) \,\mathrm{d}x = 1$$

(2.2)

Therefore, the superposition state  $|q\rangle$  can be rewritten as follows:

$$|q\rangle = \cos\frac{\theta}{2}|0\rangle + e^{i\varphi}\sin\frac{\theta}{2}|1\rangle$$

(2.3)

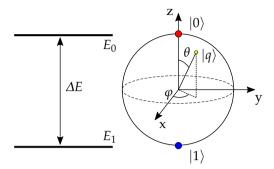

**Figure 2.1:** Schematic figure of the Bloch sphere, illustrating the possible states of a qubit. Next to it, the two energy levels  $E_0$  and  $E_1$  of the qubit corresponding to states  $|0\rangle$  and  $|1\rangle$  are shown. [43]

This representation emphasizes that there is a two-dimensional manifold of possible qubit states. These can be depicted as points on a spherical surface as shown in Figure 2.1. This representation is called Bloch sphere and states are depicted by a Bloch vector pointing from the origin onto the sphere's surface [55]. In this representation, the polar angle  $\theta$  describes the probabilities of the states and the azimuth angle  $\varphi$  expresses the relative phase between them. On the Bloch sphere,  $\theta$  defines the state component along the z axis and  $\varphi$  describes the component in the x-y plane. Accordingly, state  $|0\rangle$  is located at the north pole of the sphere, and  $|1\rangle$  on the south pole [56]. Consequently, operations on the qubit are in SU(2), i.e. rotations around the surface of the sphere.

In a physical system, the qubit is inevitably coupled to the environment. This coupling is necessary to interact with the qubit and manipulate and read out its state. It also leads to noise and decoherence of the qubit state [31]. To characterize these effects and thereby the quality of the qubit, two types of time constants are important: First, the energy relaxation time  $T_1$  which describes the decay time of the higher energy state  $|1\rangle$  back to the ground state  $|0\rangle$ . And second, the decoherence time  $T_2$  which defines the timescale on which the state of the qubit is lost. Besides the energy relaxation, this also includes when the phase  $\varphi$  between both states becomes blurred. Both times are related via a third constant,  $T_{\varphi}$ , called the pure dephasing time. They can be linked when expressed as decay rates [32]:

$$\frac{1}{T_2} = \frac{1}{2T_1} + \frac{1}{T_{\varphi}} \ . \tag{2.4}$$

#### 2.1.2 Quantum Gates

Quantum gates are linear operations used to manipulate the state of a qubit. To be able to perform all possible operations, one needs to define a universal set of gates [57]. Single-qubit gates are rotations on the surface of the Bloch sphere, i.e. can be represented as operations in SU(2) [58]. One possible set of single-qubit gates are rotations around the different basis axes. These are expressed as  $R_{x/y/z}(\theta)$  where x/y/z denotes the axis around which the rotation is performed and  $\theta$  the rotation angle. Special cases of such rotations are the Pauli gates X/Y/Z which are rotations around the respective axis with  $\theta=\pi$ . The X operation can be compared to a classical not operation, as it flips the qubit state from  $|0\rangle$  to  $|1\rangle$  and vice versa. In mathematical representation, gates acting on a state are interpreted the same way as matrices being multiplied with a vector. This means that  $AB |\psi\rangle$  says that gate B is applied onto the qubit state  $|\psi\rangle$  and, afterwards, gate A is applied.

Probably the most popular single-qubit gate is the Hadamard gate H [59]. It is defined by its behavior on the two fundamental states  $|0\rangle$  and  $|1\rangle$ :

$$H|0\rangle = \frac{|0\rangle + |1\rangle}{\sqrt{2}}$$

and  $H|1\rangle = \frac{|0\rangle - |1\rangle}{\sqrt{2}}$  (2.5)

creating a superposition state from the two basis states. It can be decomposed to rotations around the Bloch sphere as  $H=X\sqrt{Y}=R_x(\pi)R_y(\frac{\pi}{2})$ . This is a 90° rotation around the Y axis, followed by a 180° rotation around the X axis. An interesting property of the Hadamard gate is that it is an involution, i.e.  $H^2|\psi\rangle=|\psi\rangle$  for all qubit states  $|\psi\rangle$  of the computational subspace.

Besides the one qubit gates, a two-qubit gate is necessary to define a universal set of gates [57]. One candidate for such a two-qubit gate is the CNOT or CX gate (conditional not gate) [59]. It acts on two qubits where the first qubit is referred to as control qubit, and the second qubit as target qubit. When the control qubit is in state  $|0\rangle$  it leaves the target qubit unchanged. If the control qubit is in state  $|1\rangle$ , an X operation is performed on the target qubit, thereby flipping its state:

$$\text{CNOT} |00\rangle = |00\rangle$$

,  $\text{CNOT} |01\rangle = |01\rangle$  ,

$\text{CNOT} |10\rangle = |11\rangle$  ,  $\text{CNOT} |11\rangle = |10\rangle$  . (2.6)

In this notation, the single qubit states have been summarized, i.e.  $|01\rangle \equiv |0\rangle |1\rangle$ . A different two-qubit gate is the CZ or CPhase gate. It behaves exactly the same as the CNOT gate but instead of a conditional X rotation, it performs a conditional Z rotation on the target qubit.

Yet another popular two-qubit gate is the iSWAP gate. Contrary to the conditional gates, the iSWAP is symmetric. It swaps the qubit states between two qubits and

| v | values for qubit methine 12 and two-qubit gate nuclity. [62]-[67] |                       |               |              |                 |  |

|---|-------------------------------------------------------------------|-----------------------|---------------|--------------|-----------------|--|

|   | Qubit type                                                        | Lifetime $T_2$        | Gate fidelity | Gate time    | Gates per $T_2$ |  |

|   | Superconducting                                                   | $50 - 100 \mu s$      | 99.7 %        | 10 - 50  ns  | 1000 - 10000    |  |

|   | Trapped ions                                                      | $1 - 1000 \mathrm{s}$ | 99.9 %        | $3-100\mu s$ | $10000-10^8$    |  |

|   | Photons                                                           | 150 us                | 98 %          | 1 ns         | 150 000         |  |

**Table 2.1:** State of the art parameters for different qubit realizations. Values show the highest reported values for qubit lifetime  $T_2$  and two-qubit gate fidelity. [62]–[67]

adds a phase of i to the amplitudes of the  $|01\rangle$  and  $|10\rangle$  contributions [60]. Its action on the basis states of the two qubits is therefore defined as:

$$iSWAP |00\rangle = |00\rangle$$

,  $iSWAP |01\rangle = i |10\rangle$  ,  $iSWAP |10\rangle = i |01\rangle$  ,  $iSWAP |11\rangle = |11\rangle$  . (2.7)

Physically, the iSWAP gate is realized by a resonant exchange interaction  $X \otimes X + Y \otimes Y$  between the two qubits [61]. By cutting the interaction time in half, one can furthermore obtain a  $\sqrt{\text{iSWAP}}$  gate which is suitable as two-qubit gate for a universal set of gates.

What kind of gates are available depends on the physical implementations of the qubits and the coupling between them. When one elementary two-qubit gate is available, other gates can be constructed as a composition of this two-qubit gate and additional single-qubit gates, similar to classical logic.

Each gate will also take a finite duration to execute. When assessing the quality of a qubit or a quantum processor, it is important to determine how many gate operations can be successfully performed. This has to take into account both the real-world fidelity of a gate implementation, as well as its duration when compared to the decoherence time  $T_2$  of the qubits. Table 2.1 summarizes state of the art parameters for the three most popular qubit realizations to illustrate the current status and scale of these values.

#### 2.1.3 Quantum Registers

Combining multiple qubits together leads to a quantum register. Similar to a classical register with N bits, a quantum register is a collection of N qubits that can hold values ranging from 0 to  $2^N - 1$ . The single qubit states of a register are grouped together to shorten the necessary notation, e.g.:

$$|0\rangle |0\rangle |1\rangle |1\rangle |1\rangle |0\rangle |1\rangle |1\rangle \equiv |0011011\rangle \equiv |27\rangle . \qquad (2.8)$$

As qubits can be in a superposition, a quantum register  $(|q_{N-1}\rangle, \dots, |q_0\rangle)$  can hold all  $2^N$  possible values at the same time. If, for example, all qubits are in an equal superposition of both states, i.e.  $|q_n\rangle = H|0\rangle = \frac{1}{\sqrt{2}}(|0\rangle + |1\rangle)$ , one obtains:

$$|X\rangle = \frac{1}{2^{N/2}} \prod_{n=0}^{N-1} (|0\rangle + |1\rangle) = \frac{1}{2^{N/2}} (|0\dots00\rangle + |0\dots01\rangle + |0\dots10\rangle + \dots)$$

$$= \frac{1}{2^{N/2}} \sum_{m=0}^{2^{N-1}} |m\rangle .$$

(2.9)

This is an equal superposition of all classically possible register states [55].

If one uses this superposition state of the register to calculate the outcome of a classical function, one will thus calculate all possible outcomes at the same time. This can be further leveraged using quantum entanglement. When entangled, the qubit states within the register are no longer independent. An arbitrary, classical function of the form

$$f: \{0, 1, \dots, 2^N - 1\} \ni m \mapsto f(m) \in \{0, 1, \dots, 2^N - 1\}$$

(2.10)

can then be fully encoded using a register of 2N qubits in the following way:

$$|X\rangle_{\text{initial}} = \frac{1}{2^{N/2}} \sum_{m=0}^{2^{N}-1} |m\rangle |m\rangle \quad \stackrel{1 \otimes f}{\longrightarrow} \quad |X\rangle = \frac{1}{2^{N/2}} \sum_{m=0}^{2^{N}-1} |m\rangle |f(m)\rangle \quad . \tag{2.11}$$

In this operation, the register  $|X\rangle$  is initially prepared to represent the same number m twice in the first N and the second N qubits, i.e.  $|m\rangle\,|m\rangle$ . That means that the first N qubits of the register are now entangled with the second N qubits. Both parts will always hold the same number when read out, but all possible numbers with equal probability  $2^{-N}$ . Then, the function f is applied once to the second N qubits in the register. The first part of the register stays untouched, still holding the functions input values. Now, the first N qubits encode the possible input values  $|m\rangle$  and the second N qubits are entangled to represent the according function results  $|f(m)\rangle$ . With this mechanism, the whole function f is now encoded inside a 2N-sized quantum register.

In a classical computation, the function would have been executed for each possible input value, i.e.  $2^N$  times. Therefore, by preparing the quantum register in a superposition of all possible input values an exponential speedup is gained as the function only needs to be executed once. Additionally, while this takes only 2N bits in a quantum register, a classical computer would need  $N2^N$  bits to store the same function in a lookup table. Therefore, also exponentially less space was needed to store the same amount of information. For algorithms that require all possible

function values to be evaluated, this can have a major impact. This is especially the case if a global property of the function should be tested, like in the Deutsch-Jozsa algorithm which is introduced in the next section.

However, this example can also show a bottleneck of quantum computing. If the superimposed state of the register is read out, only one of the possible values will be returned. Moreover, the measurement projects the register to this result and the information of the whole function is lost. Generally speaking, while an N qubit quantum register can hold a large amount of information, a readout of such a register can only extract N classical bits of information. Therefore, it is essential that the register is prepared in a state where it contains the relevant information before it is read out. But measurements being projective is only one challenge for quantum algorithm engineers. Another challenge is the no-cloning theorem which states that it is not possible to copy an arbitrary qubit state to another qubit [68]. Therefore, classical algorithms are mostly not suited to be implemented the same way in a quantum computer.

#### 2.1.4 Quantum Algorithms

This yields for a new class of algorithms, specifically tailored to the capabilities and limitations of quantum computers. One of these is the Deutsch-Jozsa algorithm [69]. It is used to determine a global property of an unknown function  $f:\{0,1\}^N \to \{0,1\}$ . For the Deutsch-Jozsa algorithm, the task is to find out if the function is either constant, i.e. has the same output for every input, or balanced, i.e. returns 0 for half of the input values and 1 for the other half. It is guaranteed that f fulfills exactly one of these two global properties. While this problem is of little practical relevance, it was the first quantum algorithm that was proven to solve a specific problem exponentially faster than any classical algorithm can [3].

In a classical computer, solving this problem would require to calculate the outcome of up to one more than half of the  $2^N$  individual input values to be sure that it is really constant. Thus, it will need to execute the function up to  $2^{N-1}+1$  times. The quantum algorithm, on the other hand, only has to perform the calculation once due to a possible superposition of all input values. We thereby gain an exponential speedup in time complexity for this particular problem. Furthermore, the quantum computer can perform the whole algorithm with just N+1 qubits.

The working principle of the quantum algorithm is simple: Instead of checking every single result one by one, the resulting quantum register with the superposition of all results is further transformed. At the end, all qubits of the register will be in state  $|0\rangle$  if the function is constant. Otherwise, some or all of the qubits will be in

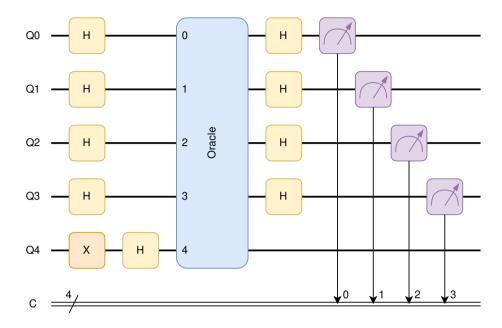

**Figure 2.2:** Circuit diagram of the Deutsch-Jozsa algorithm acting on N+1=5 qubits Q0 to Q4. All qubits are initialized in the ground state  $|0\rangle$  at the beginning. Then, different gate operations are applied, including Hadamard (H) and NOT (X) gates. The results of the final measurements (purple measurement blocks) are stored as bits of a classical register C. [70]

state  $|1\rangle$ . Then, the function is balanced. To determine which outcome is the case, the qubit states are measured once and thereby projected to a classical outcome. The algorithm is designed in a way, that the resulting state in the qubits is pure in both cases. That means that the projection of the measurement will not change the state in the quantum register. Thereby, one measurement is sufficient to determine this global property of the function. It should be noted that, while one learns about this property, one does not get any information about the single function output values [55], as opposed to the classical algorithm.

Algorithms acting on a quantum register are often depicted as circuits consisting of qubits (horizontal lines) and gates (boxes). The time sequence of the gates is the order along the horizontal axis. The circuit diagram of the Deutsch-Jozsa algorithm is shown in Figure 2.2 for N=4 data qubits and one ancilla qubit (Q4). Ancilla qubits are auxiliary qubits to assist during calculations. The data qubits are initialized in an equal superposition of all states by performing a Hadamard gate on each of them. The ancilla qubit is first prepared in the  $|1\rangle$  state by performing a X gate, before also being prepared in a superposition by a Hadamard gate. The oracle

is the function implemented in a specific way. Let  $|x\rangle = |q_0q_1q_2q_3\rangle$  be the data qubits and  $|y\rangle = |q_4\rangle$  the ancilla qubit, then the oracle performs the following operation:

$$|x\rangle |y\rangle \stackrel{\text{oracle}}{\longrightarrow} |x\rangle |y \oplus f(x)\rangle$$

. (2.12)

The operation  $\oplus$  denotes the addition with modulo 2. This entangles the data qubits with the ancilla qubit:

$$\frac{1}{\sqrt{2^4}} \sum_{m=0}^{2^4-1} |m\rangle \frac{|0\rangle - |1\rangle}{\sqrt{2}} \xrightarrow{\text{oracle}} \frac{1}{\sqrt{2^4}} \sum_{m=0}^{2^4-1} |m\rangle \frac{|0 \oplus f(m)\rangle - |1 \oplus f(m)\rangle}{\sqrt{2}} . \tag{2.13}$$

As an effect, it will add a negative global phase to all states  $|m\rangle$  in the data qubits where f(m) = 1, but not for those with f(m) = 0:

$$\frac{1}{\sqrt{2^4}} \sum_{m=0}^{2^4-1} (-1)^{f(m)} |m\rangle \frac{|0\rangle - |1\rangle}{\sqrt{2}} = \frac{1}{\sqrt{2^4}} \sum_{m=0}^{2^4-1} (-1)^{f(m)} |m\rangle |q_4\rangle . \tag{2.14}$$

Afterwards, a second Hadamard operation is performed on the data qubits. If no negative phases have been collected, this will return all zeros again. The same holds true if a negative phase was collected for all states, as it then only is a global constant in the state, i.e.  $(-1)^{const.} = \pm 1$ , const.  $\in \{0,1\}$  for all contributions:

$$\frac{\pm 1}{\sqrt{2^4}} \sum_{m=0}^{2^4-1} |m\rangle |q_4\rangle \stackrel{[H]^4 \otimes \mathbb{1}}{\longrightarrow} \pm \left[ \prod_{n=0}^{4-1} H \frac{|0\rangle + |1\rangle}{\sqrt{2}} \right] |q_4\rangle = \pm \left[ \prod_{n=0}^{4-1} |0\rangle \right] |q_4\rangle \quad . \tag{2.15}$$

In contrast, if negative phases have been collected in exactly half of the cases, the state will be orthogonal to the state before the oracle:

$$\langle x, y | x, y \oplus f(x) \rangle = \frac{1}{2^4} \sum_{n=0}^{2^4 - 1} \sum_{m=0}^{2^4 - 1} (-1)^{f(m)} \langle n | m \rangle \langle q_4 | q_4 \rangle = \frac{1}{2^4} \sum_{m=0}^{2^4 - 1} (-1)^{f(m)} = 0 .$$

(2.16)

Thus, in the constant case, the oracle keeps the data qubits untouched with exception of a non-measurable, global phase. In the balanced case, the data qubits will be orthogonal to the initial state and thereby also to the resulting state of the constant case. After applying the Hadamard gates in this balanced case, one obtains a new state  $|\Psi\rangle$  of the data qubits. In the constant case, one obtains  $\pm |0000\rangle$  as was shown. As the states after the oracle are orthogonal for both cases, this also applies for the states after the Hadamard gates, i.e.  $\langle 0000|\Psi\rangle=0$ . Thus, the probability to measure all zeros will vanish for the balanced case [71]:

$$P(|0000\rangle) = |\langle 0000|\Psi\rangle|^2 = 0$$

(2.17)

To summarize, after the Deutsch-Jozsa algorithm, one measurement of the data qubits is enough to determine if the investigated function is balanced (all qubits are in  $|0\rangle$ ) or not (at least one qubit is in  $|1\rangle$ ). This is achieved by applying the information of the function using the oracle onto the ancilla qubit. However, the ancilla qubit itself is not further investigated after the oracle. Instead, the operations will lead to a so-called phase kickback within the data qubits which is depending on the properties of the function. This is a common technique used in many quantum algorithms [71].

Grover's algorithm [7] is another well-known quantum algorithm which performs quantum searching. It provides quadratic speed up over a classical computer when searching through a large set of unstructured data. The underlying principle is called amplitude amplification technique and can also be used as part of a variety of other algorithms [72]. In essence, an equal superposition of all database entries is created in a quantum register. Subsequently, however, only the amplitudes of the relevant entries are amplified while the contributions of all other entries are reduced.

But the most famous quantum algorithm is probably Shor's algorithm [4] due to its relevance in cryptography. For a long time, it was assumed that the factorization of a composite number of two large primes cannot be performed in polynomial time. Composite integers are the product of two smaller integers. The security of many public key cryptography systems rely on this assumption. One of them is the RSA cryptosystem [53]. It is widely used for secure data transmission. While the assumption may still hold for classical computers, Shor's algorithm provides the means to factorize composite integers in polynomial time on a quantum computer. In future, quantum computers might thus be able to break these cryptosystems.

Shor's algorithm consists of two parts, one part which is performed on a classical computer and a quantum calculation. The classical part reduces the number factoring problem to the problem of order-finding. The latter is equivalent to finding the period of a function and can be efficiently solved by a quantum computer using a quantum Fourier transform. The result is then again post-processed classically to find one of the prime factors. Shor's algorithm is therefore a good example of a quantum computer acting as complementing accelerator in a heterogeneous computing system. The algorithm is furthermore probabilistic as, with a small probability, it will not return a prime factor. This is due to the fact that the algorithm relies on randomly picking a number as initial input. By repeating the algorithm multiple times with different inputs, the probability to not obtain a result is exponentially suppressed [73].

#### 2.1.5 Quantum Error Correction

In a classical computer, errors can happen in the form of bit flips, i.e. the value of a bit changing unintentionally between 0 and 1. For qubits, the energy relaxation time  $T_1$  would be the typical time scale on which such bit flip errors occur. But also other types of errors can occur due to the ability of arbitrary superpositions. Therefore, also the decoherence time  $T_2$  is an important figure. For most qubit realizations, these times are only a few magnitudes larger than the typical time to perform a gate operation [1]. Therefore, errors happen regularly during the calculation with such a system and an error correction mechanism is necessary.

Classical error correction is mostly handled by redundantly copying the information and performing checksum calculations to determine if a bit has flipped in one of the copies [74]. In quantum computation, this is not possible. The qubits can stay in arbitrary superpositions of the two fundamental states, but reading out the state will destroy this superposition and return only one of the two alternatives. More generally speaking, it is even impossible to copy the state of a qubit, which is also formulated as the no-cloning theorem [68]. Thus, classical error correction schemes cannot be applied.

Instead, entanglement is used to create an error correction code. The information of one logical qubit will be encoded in the entangled state of multiple physical ones, e.g. with three qubits [75]:

$$|q\rangle_{\rm L} = \alpha |0\rangle_{\rm L} + \beta |1\rangle_{\rm L} = \alpha |000\rangle + \beta |111\rangle$$

(2.18)

Now, if a bit flip occurs on one of these qubits, one can detect this error using syndrome measurements. By just comparing if the physical qubits are the same, but not checking the actual state they are in, one will not destroy the superposition but only determine if an error has happened or not. By performing multiple of these syndrome measurements, one can directly infer the qubit that has flipped and perform an appropriate correction gate. Furthermore, a continuous error on the Bloch sphere is projected onto just two discrete outcomes, i.e. state flipped or not. The correction algorithm used for this simple case is the bit-flip-code [75]. As the name suggests, it can only correct bit-flip-like errors within the logical qubit. A more sophisticated code which can fully correct a single qubit is the Shor code, which requires nine physical qubits to create one logical one [76].

A more general class of error correction codes are so-called stabilizer codes [77], [78]. In this case, the data qubits are appended by additional ancilla qubits. Then, one generates a highly entangled, encoded state for the logical qubit which corrects for local noisy errors. Regular, repetitive measurements of the ancilla qubits will stabilize the encoded quantum information. When an error happens, it is detected

by the ancilla qubits and can be tracked or even corrected. One example of such a code is the surface code [79], [80].

## 2.2 Superconducting Quantum Bits

Superconducting qubits are artificial atoms built from superconducting materials. For a better understanding, first some basic concepts of superconductivity are given, before the implementation of superconducting qubits is covered, as well as readout and control mechanisms.

#### 2.2.1 Superconductivity

First observed by Kamerlingh Onnes in 1911 [81], superconducting materials completely drop their electrical resistance below a critical temperature  $T_{\rm C}$ . Also, multiple other effects have been observed in superconductors which cannot be explained classically. This includes the Meissner effect where an external magnetic field is completely expelled from the interior of the superconductor or phenomenons like flux quantization [82].

It was only in 1957, that John Bardeen, Leon Cooper and John Robert Schrieffer (BCS) proposed a microscopic theory that was able to explain these behaviors [83]. According to this BCS theory, two electrons attract each other via the exchange of a virtual phonon, the quantum of lattice excitations in solids. With thermal fluctuations becoming weaker at lower temperature, two electrons can form a bound state, a so-called Cooper pair. These pairs do not obey the Pauli exclusion principle anymore and thus can all occupy the same ground state similar to a Bose-Einstein condensate. The binding energy of the two electrons also leads to an energy gap within the spectrum between this bound state and the state of free electrons. If scattering processes cannot transfer enough energy to break these Cooper pairs, scattering will be suppressed. Cooper pairs can then travel without friction through the superconducting material. As these consist of two electrons and are therefore charge carriers, a current can flow without any resistance but is limited by a critical current threshold. Above it, the Cooper pairs have enough kinetic energy to participate in scattering processes leading to non-vanishing electrical resistance [84].

In the common ground state of the Cooper pairs, the whole superconductor is described by a single, global wave function

$$\Psi(\mathbf{x}) = |\Psi(\mathbf{x})| \cdot e^{i\varphi(\mathbf{x})} . \tag{2.19}$$

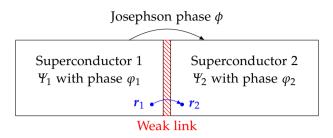

Figure 2.3: Schematic structure of a Josephson junction. [43]

This wave function can also be used to explain other effects observed in superconductors. One of these is the Josephson effect [85] which describes the behavior of two superconducting electrodes connected via a weak link called Josephson junction (see Figure 2.3). Each electrode has its own wave function  $\Psi_i$  due to the weak link, but both are related to each other via the Josephson phase

$$\phi = \varphi_2 - \varphi_1 - \frac{2\pi}{\Phi_0} \int_{r_1}^{r_2} A \, \mathrm{d}r \ . \tag{2.20}$$

Here,  $\varphi_i$  are the phases of the wave functions  $\Psi_i$  and  $\Phi_0 = h/2e$  is the superconducting flux quantum.

The Josephson phase is directly linked to observables via the Josephson equations [84] which describe the junction behavior:

$$U(t) = \frac{\Phi_0}{2\pi} \frac{\partial \phi}{\partial t} \tag{2.21}$$

$$I(t) = I_{c} \sin(\phi(t)) \tag{2.22}$$

where  $I_{\rm c}$  is the critical current through the junction. It is the highest possible current that can flow through the junction without causing any dissipation. As seen from the first equation, an applied voltage U(t) across the junction will lead to a constant drift in the Josephson phase. Vice versa, a change in  $\phi$  will also induce a voltage. By the second equation, the Josephson phase is directly linked to the current flowing through the junction I(t). Following from these equations, one can calculate the inductance  $L = U/\frac{\partial I}{\partial t}$  across the junction [31]:

$$L(\phi) = \frac{\Phi_0}{2\pi I_{\rm c}\cos(\phi)} \ . \tag{2.23}$$

As this inductance depends on the phase  $\phi$  across the junction, it can be utilized as a non-linear element to design specific circuits and corresponding energy structures. One example are superconducting qubits.

#### 2.2.2 Two-Level Quantum Systems

A fundamental concept of quantum mechanics is the discretization of energy. Systems like atoms, molecules, or the quantum harmonic oscillator all show discrete energy states in which they can be situated. For atoms, these can be different electron populations of the orbitals. For molecules, one can additionally observe discrete vibrational and rotational modes. A quantum harmonic oscillator shows equally spaced energy levels  $E_n = \hbar \omega (n + \frac{1}{2})$  corresponding to different excitation modes.

To build a qubit, only two states  $|0\rangle$  and  $|1\rangle$  are needed to form the computational subspace: a ground state  $|0\rangle$  with energy  $E_0$  and an excited state  $|1\rangle$  with energy  $E_1 > E_0$ . Spin 1/2 particles in a magnetic field, for example, fulfill this condition [2]. In general, also multi-level systems can be used when the different levels can be addressed independently. This requires that the anharmonicity  $\alpha = \Delta E_{1,2} - \Delta E_{0,1}$  is large enough. One example would be Rydberg atoms where two distinguished energy states are picked from the spectrum to define the required computational subspace [86], [87]. In contrast, the harmonic oscillator is not suited for this, as  $\alpha = 0$  and one cannot distinguish between the different energy levels.

Nevertheless, artificial two-level quantum systems are often based on a harmonic oscillator where a source of anharmonicity is added in order to reach the desired energy spectrum. For superconducting qubits, a simple implementation is a charge qubit [23]. It is constructed out of a classical LC harmonic oscillator where the inductance is replaced by a Josephson junction acting as non-linear element. The state of the charge qubit is determined by the number of Cooper pairs that have tunneled across the junction. It is therefore also quite sensitive to charge noise which limits its usability [88]. To alleviate this, different improved designs have been proposed, with the Transmon qubit currently being the most popular one.

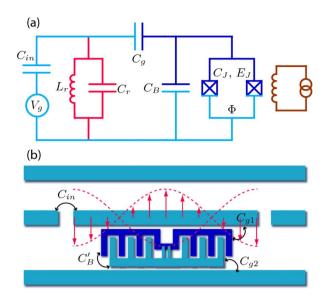

Transmon qubits are charge qubits shunted by a large capacitance [24]. This leads to a suppression of the system's susceptibility to charge noise. The first Transmon qubit was introduced by Koch *et al.* A sketch of it is depicted in Figure 2.4. Fluctuations in the charge will not significantly influence the qubit properties anymore due to the large capacitance. The effective Hamiltonian  $\hat{H}$  stays the same as for the charge qubit and is given by

$$\hat{H} = 4E_C(\hat{n} - n_g)^2 - E_J \cos \hat{\phi}$$

(2.24)

where  $\hat{n}$  is the number operator of the Cooper pairs tunneling through the junction,  $n_g$  is the effective offset charge induced by an external gate voltage  $V_g$  and  $\hat{\phi}$  is the operator of the Josephson phase which corresponds to the gauge-invariant phase difference between the two superconductors. The charging energy is defined as  $E_C = (2\mathrm{e})^2/2C$  and the Josephson energy as  $E_I = \Phi_0 I_c/2\pi$ .

**Figure 2.4:** (a) Effective circuit of the original Transmon qubit by Koch *et al.* (b) Design schematics of the same Transmon qubit. The single Josephson junction is replaced by a superconducting quantum interference device (SQUID) so the qubit frequency can be tuned by an external flux. The coil and the belonging current source to create this flux are sketched in brown on the right side of the SQUID. The crossed boxes in the SQUID loop represent the Josephson junctions characterized by the intrinsic capacitance  $C_J$  and the Josephson energy  $E_J \propto I_c$ . Clearly visible is the large interdigital capacitor  $C_B$  that shunts the charge qubit. The qubit is capacitively coupled  $(C_g)$  to a transmission line resonator  $(L_r$  and  $C_r$ , sketched in red). The resonator is coupled to the transmission line capacitively via  $C_{in}$ . The system can be controlled by applying an external gate voltage  $V_g$ . [24]

In contrast to the charge qubit, for the Transmon qubit it holds  $E_J \gg E_C$ . With increasing  $\sqrt{E_J/E_C}$ , the sensitivity to charge noise, i.e. fluctuations in  $\hat{n}$ , exponentially decreases. At the same time, the anharmonicity  $\alpha \approx -E_C$  also decreases. In order to obtain a useful qubit, the anharmonicity needs to remain sufficiently large,  $\alpha/h \gtrsim 100\,\mathrm{MHz}$ . Otherwise the system cannot be approximated as a two-level system anymore and higher levels play a significant role in the dynamics of the structure. Thus, a trade-off needs to be found between anharmonicity and the suppression of charge noise [24].

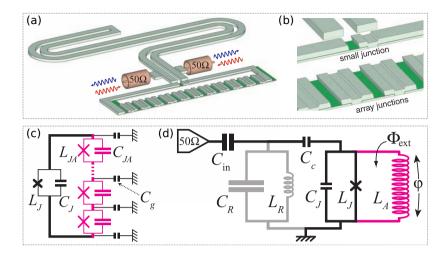

Another type of improved qubit is the Fluxonium [25]. Instead of a large capacitance, the charge qubit is shunted by a large inductance. As both sides of the junction are now electrically connected, charge noise is also effectively suppressed. For the Fluxonium qubit, the inductance is realized by a series array of Josephson junctions, see Figure 2.5. Using this technique, high energy relaxation times  $T_1$  of up to 1 ms have been achieved [89], [90]. Instead of fabricating a series of junctions, one can also use granular aluminum for the inductance [35]. It exhibits similar behavior due

**Figure 2.5:** (a) Sketch of a Fluxonium qubit coupled to a readout resonator and a  $50\,\Omega$  transmission line. (b) Structure of the series array of many Josephson junctions forming the large inductance. (c) Electric circuit representation of the qubit with the array of junctions. (d) Simplified circuit model of the Fluxonium qubit being a inductively-shunted charge qubit. The circuit also contains the readout circuitry (marked in gray). [25]

to the granular structure but is easier to fabricate. As the large inductance and the single Josephson junction form a loop, the qubit is tunable by an external magnetic flux  $\Phi_{\text{ext}}$ . This also becomes obvious when looking at the Hamiltonian [25]

$$\hat{H} = 4E_C \hat{n}^2 + \frac{1}{2}E_L \hat{\phi}^2 - E_J \cos\left(\hat{\phi} - 2\pi \frac{\Phi_{\text{ext}}}{\Phi_0}\right) . \tag{2.25}$$

On the downside, this dependency makes the qubit sensitive to flux noise. A mitigation strategy is to apply an external field to operate the qubit in the  $\Phi_{\rm ext}/\Phi_0=\pm 0.5$  sweet spot. There, the spectrum is first-order insensitive to flux-noise. Furthermore, energy relaxation due to non-equilibrium quasi-particles tunneling through the Josephson junction is suppressed [91].

## 2.2.3 Rabi Cycles

The states of an atom can be probed and populated using light-matter interaction. To excite an atom, i.e. transferring an electron to a higher state, a photon with the energy difference of the old and the new state can be absorbed:

$$\omega_{01} = \frac{E_1 - E_0}{\hbar} \ . \tag{2.26}$$

This scenario is well-studied in quantum optics. It is described by the Jaynes-Cummings model [92] where the Hamiltonian is split into three terms:

$$\hat{H} = \hbar \omega_{\rm r} \hat{a}^{\dagger} \hat{a} + \frac{\hbar}{2} \omega_{01} \hat{\sigma}_z + \hbar g \left( \hat{\sigma}^{\dagger} \hat{a} + \hat{\sigma}^{\dagger} \hat{a}^{\dagger} \right) . \tag{2.27}$$

In this model, the atom is located inside a cavity. The cavity is a harmonic oscillator represented by the first term and its resonance frequency  $\omega_r$ . Its creation and annihilation operators  $\hat{a}^\dagger$  and  $\hat{a}$ , respectively, create and destroy a single photon in the cavity. Each photon contributes  $\hbar\omega_r$  energy to the system. The first term therefore expresses the total energy of the cavity, with  $\hat{N}_r = \hat{a}^\dagger \hat{a}$  being the number operator of photons in the cavity. The second term describes an atom consisting of two energy levels. It thus can be represented like a spin using Pauli operators. When projected,  $\hat{\sigma}_z$  returns either +1 or -1. Thus, the energy difference of the two states is given by  $\hbar\omega_{01} = E_1 - E_0$ . Finally, the third term describes the interaction between atom and cavity with the constant g defining the coupling strength. The operators  $\hat{\sigma}^{+/-}$  excite and de-excite the qubit. The term can thus be interpreted in the following way: The qubit transitions from  $|0\rangle$  to  $|1\rangle$  (corresponding to  $\hat{\sigma}^+$ ) when a photon from the cavity is absorbed  $(\hat{a})$ . And it transitions back from  $|1\rangle$  to  $|0\rangle$  (corresponding to  $\hat{\sigma}^-$ ) by emitting a photon back into the cavity  $(\hat{a}^\dagger)$ .

This scheme also applies for artificial atoms like superconducting qubits. Typical resonance frequencies  $f_{\rm r}=\omega_{\rm r}/2\pi$  and qubit transition frequencies  $f_{01}=\omega_{01}/2\pi$  are located around a few gigahertz and thus in the microwave domain.

To alter the state of the qubit, a microwave pulse at drive frequency  $\omega_{\rm dr}$  and amplitude  $A \propto \omega_{\rm A}$  can be applied. This will result in so-called Rabi cycles where the qubit is periodically excited and de-excited. When starting in the ground state  $|0\rangle$ , the probability to end up in the excited state  $|1\rangle$  after a well-defined time t is given by:

$$P(|1\rangle) = \left(\frac{\omega_{\rm A}}{\Omega}\right)^2 \frac{1 - \cos(\Omega t)}{2} \tag{2.28}$$

with Rabi oscillation frequency  $\Omega=\sqrt{(\omega_{\rm dr}-\omega_{01})^2+\omega_{\rm A}^2}$  [93]. For the special case  $\omega_{\rm dr}=\omega_{01}$ , i.e. driving the qubit on resonance, this simplifies to:

$$P(|1\rangle) = \frac{1 - \cos(\omega_{A}t)}{2} = \sin^{2}\left(\frac{\omega_{A}t}{2}\right) . \tag{2.29}$$

By varying amplitude and length of the microwave pulse, one can periodically drive oscillations between the qubit's  $|0\rangle$  and  $|1\rangle$  state population. This corresponds to rotations around the Bloch sphere, as introduced in Section 2.1.1. E.g. fixing a certain amplitude  $\omega_{\rm A}$  and choosing the time t such that  $t=\pi/\omega_{\rm A}$ , or vice versa, one obtains a  $\pi$  rotation.

Furthermore, the phase of the drive tone will determine the axis on the equator of the Bloch sphere around which the rotation takes place [94]. Typically, one arbitrarily chooses one phase which will correspond to rotations around the x axis, e.g. the phase of the first drive pulse. Then, a relative phase of  $\pi/2$  with respect to this reference will lead to rotations around the y axis. A phase offset of  $\pi$  corresponds to counter clockwise rotations around the x axis, and so on. As the phase reference is only an arbitrary definition, one can also perform so-called virtual Z rotations [94]. That means that one intentionally changes the phase reference by a well-defined angle  $-\eta$ . This corresponds to a rotation of the reference frame by this angle around the z axis. As, obviously, the qubit state does not change by this redefinition, from the view of the adapted reference frame, the qubit has now itself rotated around the z axis by the angle  $+\eta$ . This can be used to perform error-free and instant rotations around the z axis. As this  $R_z(\eta)$  rotation does not require physical interaction with the qubit, it is called a virtual gate.

#### 2.2.4 Dispersive Readout

When a qubit is coupled to a harmonic oscillator, the state of the qubit will affect the properties of the oscillator. Transforming the Hamiltonian in Equation 2.27 using a unitary transformation and neglecting fast oscillating terms, one obtains an effective Hamiltonian which is diagonalized and time-independent. The approximation is a common element in quantum optics and called rotating wave approximation [95]. The diagonalized Hamiltonian can be written as

$$\hat{H}_{\text{eff}} \approx \frac{\hbar}{2} (\omega_{01} + \chi) \sigma_z + \hbar (\omega_r + \chi \hat{\sigma}_z) \hat{a}^{\dagger} \hat{a}$$

(2.30)

with dispersive shift  $\chi = g^2/\Delta$  and detuning  $\Delta = \omega_{01} - \omega_r$ ,  $|\Delta| \gg g$  [37].

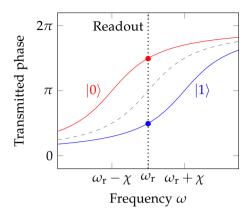

The second term represents the cavity. Due to the coupling, a shift in the resonance frequency  $\omega_r \to \omega_r \pm \chi$  is observed. Its sign depends on the qubit state as given by  $\hat{\sigma}_z$ . Therefore, by observing the cavity's resonance frequency  $f_r = \omega_r/2\pi$  one can infer the state of the qubit. This is also depicted in Figure 2.6.

In an experiment setup, one will most likely operate with fixed frequency pulses. Thus, the amplitude and phase response of such a pulse has to be evaluated. Depending on the resonator, the experiment setup, and the frequency used, the state can either be mostly encoded into an amplitude difference (when pulsing at frequency  $\omega_r \pm \chi$ ) or a phase difference (using  $\omega_r$ ). In Figure 2.6, this is visualized as dotted black lines. As the dispersive shift  $\chi$  is usually much smaller than depicted, it is typically beneficial to measure the phase. The first derivative of the amplitude vanishes around the resonance frequency which gives reduced sensitivity to small

- (a) Amplitude response of the resonator.

- (b) Phase response of the resonator.

**Figure 2.6:** Schematic picture showing the qubit chip response as a function of the frequency. Depending on the qubit state, the resonance frequency of the coupled resonator is shifted by plus (blue line, state  $|1\rangle$ ) or minus (red line, state  $|0\rangle$ ) the dispersive shift  $\chi$ . The response of the bare resonator without coupled qubit is indicated as dashed gray line. (a) Amplitude of a signal transmitted through the cryostat with a Lorentzian-shaped dip at the resonance frequency. (b) Phase of the transmitted signal.

frequency changes. Contrary, the first derivative of the phase exhibits an extremum at this point which makes it better suited to observe the qubit state [37].

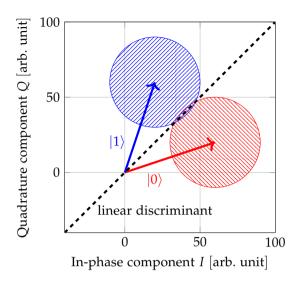

Performing measurements will project the qubit state to either state  $|0\rangle$  or  $|1\rangle$ . Thus, one can retrieve two discrete phase values,  $\varphi_0$  or  $\varphi_1$ , corresponding to these two qubit states. Depending on the measurement setup, the noise on the signal might exceed the difference of these values and averaging becomes a necessity. In this case, one cannot infer the qubit state for a single measurement outcome. By repeating the experiment and averaging, one obtains an approximation of the qubit population

$$P(|1\rangle) = \frac{\langle \varphi \rangle - \varphi_0}{\varphi_1 - \varphi_0} \ . \tag{2.31}$$

If the qubit stays in the detected state after the measurement, one furthermore calls the operation a quantum non-demolition (QND) measurement [96]. This is a special type of detection scheme that minimizes the disturbance introduced by the measurement process. It is an important concept in quantum physics. The dispersive readout scheme is a QND measurement, as long as the power of the readout tone is sufficiently small to not cause adverse side effects [38].

#### 2.2.5 Transition Frequency Tuning

Depending on the design of the superconducting qubits, their transition frequency  $f_{01}$  can either be fixed or influenced externally. Generally speaking, it is advantageous to have fixed-frequency qubits as otherwise additional noise channels can significantly increase qubit decoherence. However, depending on the experimental requirement and the realization of quantum gates, frequency tunability can sometimes be required, e.g. for an implementation of a two-qubit gate or to perform a physical Z rotation.

To be able to change the frequency, and equivalently the energy difference between  $|0\rangle$  and  $|1\rangle$ , one can replace the Josephson junction by a split-pair geometry, i.e. two parallel ones. These then form a loop in the circuit which is equivalent to a superconducting quantum interference device (SQUID). SQUIDs are very sensitive to magnetic flux passing through the loop due to flux quantization of the superconducting material. The properties of the junctions are then a function of external magnetic flux  $\Phi_{\rm ext}$  in this loop, and so is the transition frequency of the qubit. For Transmon qubits, this theoretically results in [97]:

$$f_{01}(\Phi_{\rm ext}) \propto \sqrt{\left|\cos\left(\frac{\pi\Phi_{\rm ext}}{\Phi_0}\right)\right|}$$

(2.32)

However, due to fabrication variations, the Josephson junctions in the SQUID loop will not be perfectly identical. This will result in a slightly deviating dependency with a reduced tunability range not reaching zero frequency. More details can e.g. be found in the supplementary material of [41].

By placing a bias current line close to the SQUID loop and applying a DC current through it, a controlled magnetic field can be created in the vicinity of the qubit. Thereby, the transition frequencies of individual qubits can be tuned independently by adapting these bias currents. Taking the Biot-Savart law into account, it is clear that there is a linear dependency between the current through the bias line and the magnetic flux  $\Phi$  within the SQUID loop.

#### 2.2.6 Example Implementation

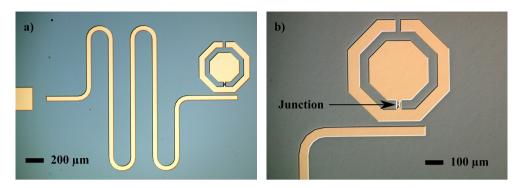

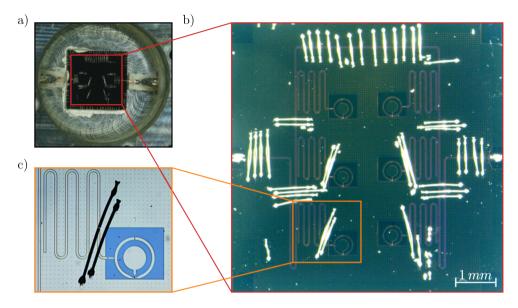

To illustrate typical scales for properties of superconducting qubits, one qubit is presented in the following as an example. It is a concentric Transmon qubit that has been designed and fabricated at the National Institute of Standards and Technology (NIST) in Boulder in the United States. The qubit properties mentioned in the following are taken from characterizations performed in [98]. A microscopic

**Figure 2.7:** Microscopic pictures showing a concentric Transmon qubit. Light areas are superconducting TiN layers. The remainder of the chip shows the silicon substrate. (a) Overview over the whole sample. The meandered structure in the center is a  $\lambda/2$  transmission line resonator used to dispersively read out the qubit state. It is capacitively coupled to the qubit and the input port on the left. (b) More detailed view of the Transmon qubit showing two capacitor islands that are connected by a single Josephson junction. [99]

photograph of the sample chip is shown in Figure 2.7. Its concentric design is advantageous to reduce the dipole moment of the structure and thereby the coupling to the environment via an electric field [41], [99]. The sample only has a single microwave port, hence all measurements are performed in reflection. A readout resonator is capacitively coupled to this port and the qubit. Its resonance frequency is  $f_{\rm r}=8.573\,{\rm GHz}$ . The qubit is controlled via microwave pulses over the same port. Its transition frequency is  $f_{01} = 4.755 \,\mathrm{GHz}$ . As the resonator acts as a band pass filter and mostly reflects the control pulses, their amplitude needs to be much stronger than the one for the readout [100]. The Transmon qubit is not a perfect two-level system. Indeed, it also shows higher energy levels. The quality of the qubit is characterized by its anharmonicity, i.e. the energy difference between the  $|0\rangle - |1\rangle$ and the  $|1\rangle - |2\rangle$  transition. In this case, it is  $\alpha/h = f_{12} - f_{01} = -197.7$  MHz. This is large enough to reliably distinguish the different energy levels but still leads to some leakage into higher states due to thermal excitations [43]. The coherence times of the qubit show fluctuations in time [36] with values up to  $T_1 \approx 30 \,\mu s$  and  $T_2 \approx 50 \,\mu s$ . The duration for an X gate, i.e. half a rotation around the Bloch sphere, is around 100 ns, depending on the strength of the control pulses.

#### 2.2.7 Multi-Qubit Interaction

Different mechanisms to implement two-qubit gates with superconducting circuits exist. Which one can be used essentially depends on the physical design of the chip

**Figure 2.8:** Two frequency-tunable Transmon qubits coupled to a common resonator acting as quantum bus. (a) Schematic representation of the sample. (b) Microscopic picture of a chip. The resonator is a coplanar waveguide interrupted by coupling capacitors (purple boxes). Two Transmon qubits are located at opposite ends of the resonator where the electric field shows maximum displacement and thus high coupling to the qubits. [97]

employed. One class is based on tuning the qubit's transition frequencies. Another one is all microwave induced [101].

For the first type, one requires frequency-tunable qubits which are coupled to a common resonator. An exemplary image of such an architecture is depicted in Figure 2.8. In this case, the resonator can act as a quantum bus where the qubit-qubit interaction is mediated by the exchange of a virtual photon [97]. Different gate schemes exist. By tuning the qubit's transition frequencies into resonance, they start to periodically exchange their excitations between  $|01\rangle$  and  $|10\rangle$ . Carefully choosing the interaction time, i.e. the time of both qubits being in resonance, one can create an iSWAP gate. Alternatively, by cutting the time in half, one obtains a  $\sqrt{\text{iSWAP}}$  gate [102].

Another gate that can be implemented with superconducting Transmon qubits is a cPhase gate. It leverages that the Transmon is no perfect two-level system but also has higher states. When adiabatically tuning the  $|0\rangle - |1\rangle$  transition frequency of one qubit close to the  $|1\rangle - |2\rangle$  transition frequency of the other one, the basis states will acquire a state-dependent phase. By engineering the rising and falling edge of the flux pulses to tune the qubit, as well as the interaction time, one can engineer a cPhase gate [42].

A different type of two-qubit gates are based on couplings solely induced by microwave drives [103]. A great advantage of these gates is that they do not require control over the qubit transition frequencies. Therefore, fixed frequency qubits can be used which eliminates one source of noise and decoherence. This scheme can also reduce the number of wires necessary to control a certain amount of qubits. One gate within this category is the cross-resonance gate [104], [105]. It requires separated microwave control lines for each qubit but no flux lines to tune the qubit. The scheme is conceptually simple: One irradiates a microwave pulse on the control line of one qubit but with the frequency matching the second qubit. If the qubits are weakly coupled to each other on the off-diagonal (e.g. XX-coupling), this coupling will be amplified by the cross-resonance pulse. The pulse thus effectively turns on the coupling between the two qubits and its strength will depend on the amplitude of the pulse (compare Eq. (14) in [104]). Furthermore, by changing the phase of the pulse, one can select different two-qubit gates. One example is the ZX gate which, together with one-qubit rotations, gives a universal gate set for quantum computation. The same way, a  $\sqrt{ZX}$  gate can be achieved, which is related to the CNOT gate by only one additional  $\pi/2$  rotation per qubit [104]:

$$CNOT = \left[ R_z(-\frac{\pi}{2}) \otimes \mathbb{1} \right] \sqrt{ZX} \left[ \mathbb{1} \otimes R_x(-\frac{\pi}{2}) \right] . \tag{2.33}$$

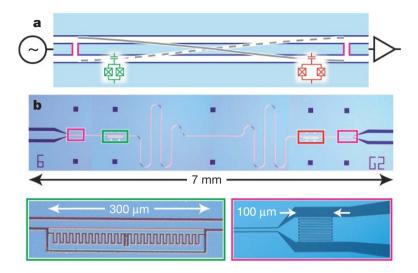

Yet another two-qubit gate is the parametric iSWAP gate. It can be used with fixed-frequency qubits but requires a tunable coupler between them [61]. An exemplary image of such an architecture is shown in Figure 2.9. Typically, these couplers are superconducting qubits themselves but with a SQUID-based junction and thus flux-tunable. With this architecture, it is possible to parametrically turn on the coupling between the two qubits via the coupler. This is achieved by oscillating the coupler at the qubit-qubit detuning, resulting in an oscillation between the states  $|01\rangle$  and  $|10\rangle$ . The oscillation time will determine the extend of the exchange, making it possible to obtain both an iSWAP and a  $\sqrt{\text{iSWAP}}$  gate.

#### 2.2.8 Quantum Software Tools

When working with superconducting qubits, different software tools exist to support the researchers and users to perform experiments, write quantum algorithms and simulate quantum computations. Specialized measurement frameworks are used to control laboratory instruments, perform experiments and persist the acquired data. One such framework designed for superconducting qubits is the open-source quantum measurement suite Qkit [106]. It is developed and actively used by the Institute of Physics at the Karlsruhe Institute of Technology. Qkit provides a

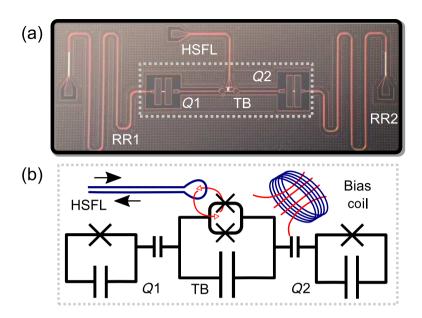

**Figure 2.9:** Two fixed-frequency Transmon qubits coupled to a third frequency-tunable qubit acting as tunable coupler. (a) Microscopic picture of a chip. Each Transmon qubit (Q1 and Q2) has its own readout resonator (RR1 and RR2). Both are coupled to a third qubit (TB) which is frequency-tunable using a high-speed flux line (HSFL) as well as a bias coil to adjust the working point of the coupler. (b) Schematic representation of the same circuit. [61]

collection of drivers to control laboratory instruments. Furthermore, it takes care of storing data in a standardized format and provides an interface to use this storage and work with the data. Additional modules encapsulate different measurement functionalities, data analysis capabilities and a graphical user interface to inspect the acquired data.

On a higher abstraction level, the open-source quantum development kit Qiskit [107] exists to work with quantum computers at the algorithm level. It is developed by IBM and widely used in the community when working with high-level applications of quantum computing. Qiskit provides tools to create quantum algorithms by combining quantum gates into a circuit (compare Section 2.1.4). These circuits can then be executed on various backends, mainly simulators and online systems provided by IBM. The quantum development kit is provided in Python which is the de facto language of choice when working in the field of quantum computing.

Qiskit is divided into multiple packages called Qiskit Aer, Terra, Ignis and Aqua. Aer provides low-level access to quantum hardware via pulsed experiments. It also contains various classical simulators to simulate the behavior of a quantum

processor classically. Different noise models to make these simulators more realistic and investigate the impact of different noise sources are also provided.

Terra includes the generation of quantum circuits using a gate-level programming language. It also provides methods to optimize such circuits to be executed with minimal possible error on an actual quantum processor. Terra also contains the interface to real quantum hardware provided by IBM, so-called backends. Cloud backends of IBM can be accessed by a so-called provider that establishes a connection to the IBM Quantum Experience. Multiple superconducting quantum processors of IBM are available online to be selected.

Ignis is used to perform qubit characterization experiments and to apply error correction and mitigation techniques. It also contains different benchmarks to verify the operation of an existing quantum processor.

Finally, Qiskit Aqua provides high-level access to a number of quantum algorithms which have been written in Qiskit Terra but can be used without the necessity to rewrite the algorithms again. This includes different algorithms for chemistry simulations, finance applications, machine learning, and optimization problems. As the different Qiskit packages interlock, one can write a high-level algorithm using Aqua which can then be executed using a Qiskit Terra provider.

## 2.3 Typical Experiment Setup

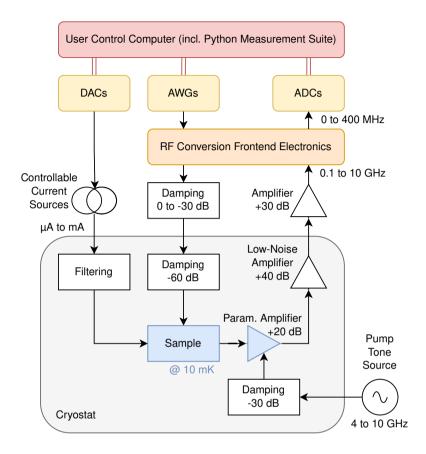

Superconducting qubits are typically read out and controlled using microwave pulses with frequencies up to  $10\,\mathrm{GHz}$ . Additionally, bias currents and fast current pulses might be necessary to tune the qubits or perform certain operations on them. Due to the utilization of superconductors like aluminum ( $T_{\mathrm{C}} = 1.2\,\mathrm{K}$  [108]) and the energy spacing of existing qubits, low temperatures on the order of  $10\,\mathrm{mK}$  are required [31]. Therefore, the chip on which the superconducting circuits are fabricated is located inside a cryostat, most commonly a dilution refrigerator. A schematic overview of a typical experiment setup is depicted in Figure 2.10.

The low temperature requirement imposes challenges concerning the microwave signal strength and noise thermalization. With control electronics being operated at room temperature, noise at room temperature is added onto the microwave signals. Thus, additional attenuation inside the cryostat is essential to thermalize this noise to the target temperature [31]. At the same time, the signal strength will also be reduced to a level of only a few photons on the chip. To obtain good signal fidelity, it is therefore paramount to have a good amplification chain for the return signal. Each amplifier has a specific noise temperature which needs to be taken

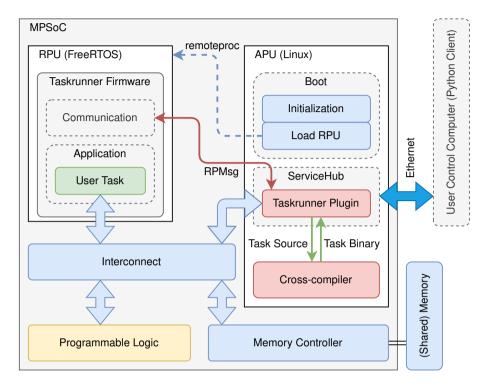

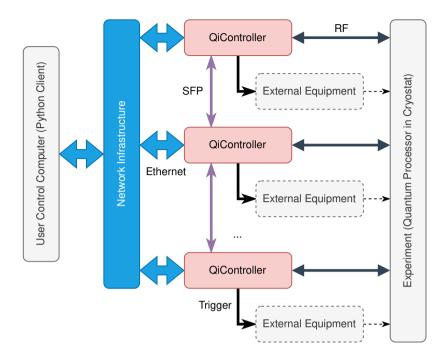

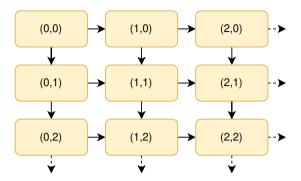

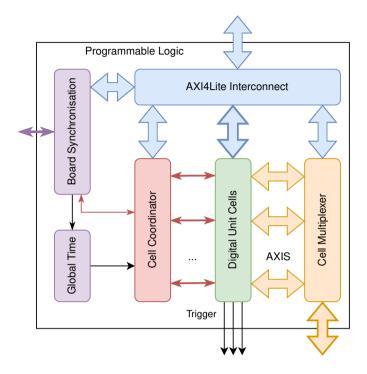

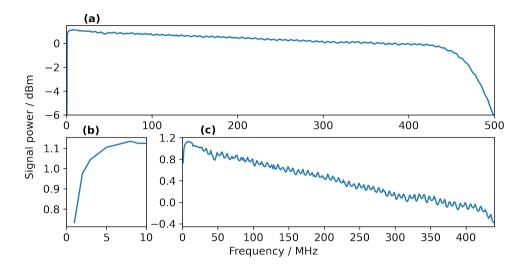

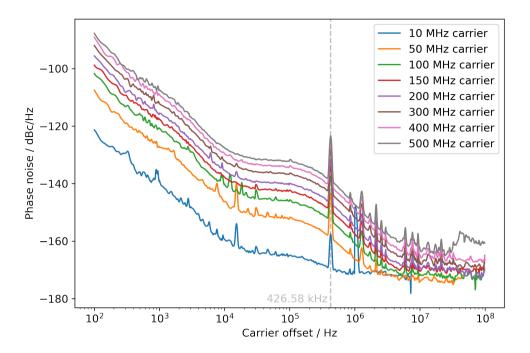

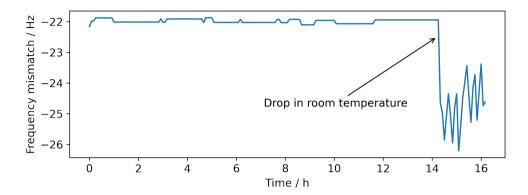

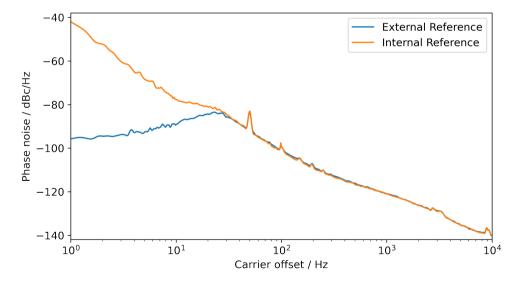

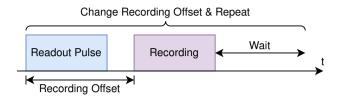

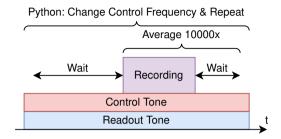

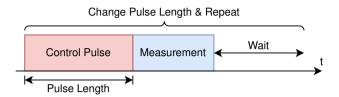

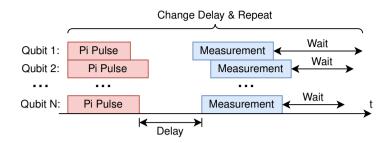

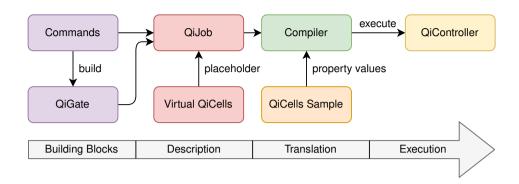

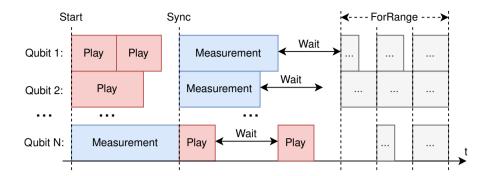

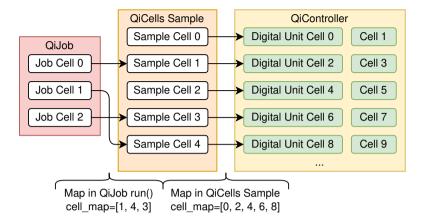

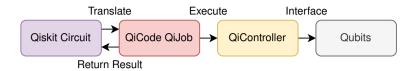

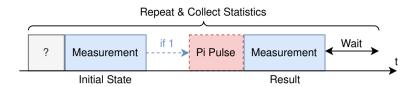

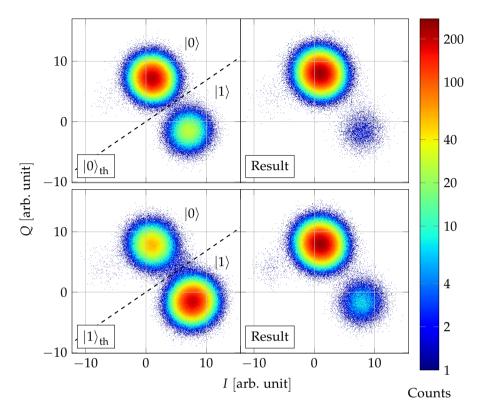

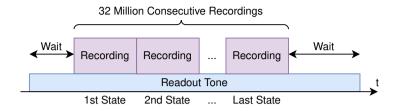

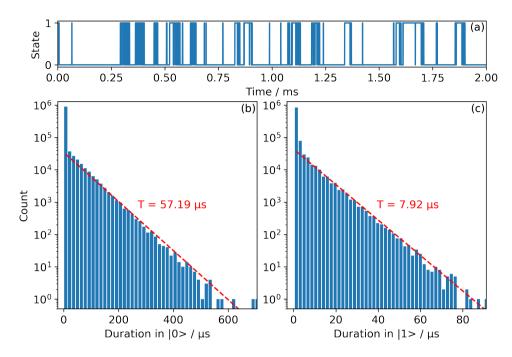

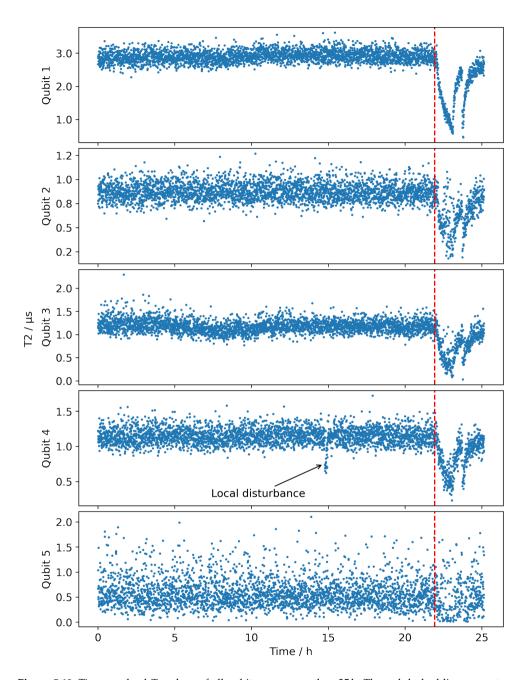

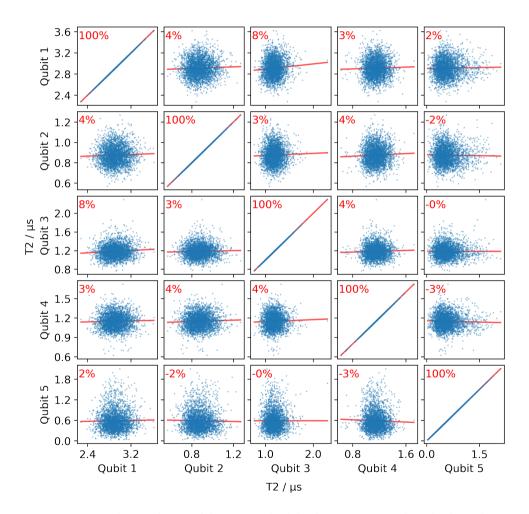

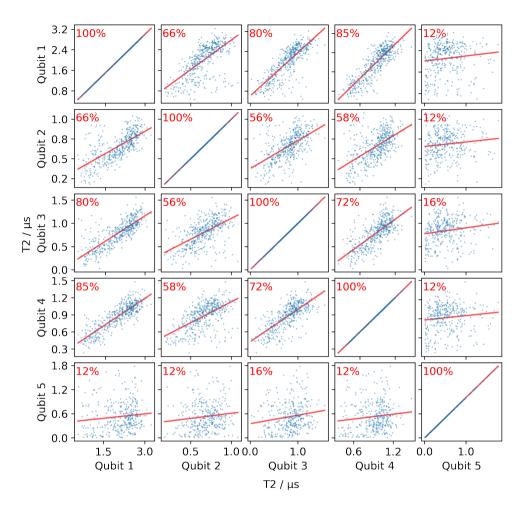

Figure 2.10: Schematic overview of a typical experiment setup for superconducting circuits.