# Entwicklung integrierter Detektoren für geladene Teilchen und Photonen

Development of integrated detectors for charged particles and photons

Zur Erlangung des akademischen Grades eines

## DOKTOR-INGENIEURS

von der KIT-Fakultät für Elektrotechnik und Informationstechnik des Karlsruher Instituts für Technologie (KIT) angenommene

### DISSERTATION

von

## M. Sc. Hui Zhang

geb. in: Xuzhou, Jiangsu, China

Tag der mündlichen Prüfung: Hauptreferent: Korreferent: 05.10.2021 Prof. Dr. Ivan Perić Prof. Dr. André Schöning

Das vorliegende Werk darf von der KIT-Bibliothek frei im Internet angeboten werden. Die Nutzung erfolgt ausschließlich zu wissenschaftlichen Zwecken und zum Eigengebrauch. Die Urheberrechte liegen bei den Autorinnen bzw. Autoren. Für den Inhalt sind alleine die Autorinnen und Autoren verantwortlich. Jegliche Formen der kommerziellen Nutzung und Abänderung der Publikation sind ohne vorherige Zustimmung und Absprache mit den Autorinnen bzw. Autoren ausdrücklich verboten, es sei denn, sie sind durch eine Creative-Commons- oder vergleichbare Lizenz explizit gestattet. Die Namen der Autorinnen und Autoren müssen stets genannt werden. Die Nutzerinnen und Nutzer sind für die Einhaltung der Rechtsvorschriften selbst verantwortlich und können bei Missbrauch haftbar gemacht werden.

# Zusammenfassung

Das Thema meiner Dissertation ist die Entwicklung von mehreren innovativen anwendungsspezifischen ICs (ASICs) für verschiedene wissenschaftliche und medizinische Anwendungen.

Der erste von mir entwickelte ASIC ist ein Auslesechip (MPROC) für einen Hybridpixeldetektor für medizinische Anwendung. Der Chip kann für die Auslese eines CdTe-Sensors verwendet werden. Der zweite ist ein Sensorchip für einen kapazitiv gekoppelten Pixeldetektor (CCPD) (CCPD53). Es könnte für die Innenlage des ATLAS-Pixeldetektors angewendet werden. Der dritte Chip ist ein monolithischer Pixeldetektor (HVMAPS25) mit kleinem Füllfaktor für CLIC- oder CEPC Teilchenphysik-Experimente.

Ich war auch an der Entwicklung von ASICs (CLIC v1/v2 und v3 High Dynamic Range) für PANDA- und CLIC-Experimenten beteiligt. Sie bieten eine präzise Flugbahnrekonstruktion sowie Energie- und Impulsmessungen. Ich habe ebenfalls an einigen weiteren Projekten gearbeitet, die in dieser Dissertation nicht beschrieben wurden: Sensoren lFoundry Prozess, ATLASPIX1 und ATLASPIX3, MUPIX8.

Auch wenn diese Projekte unterschiedlich sind, verwenden sie ähnliche Schaltungen.

Die Pixelelektronik von jedem ASIC enthält ladungsempfindlichen Verstärker, RC-Filter, Rückkopplungsschaltungen, Komparator mit Tune-DACs.

Die Ausleseschaltung wurde ursprünglich für monolithische Sensoren entwickelt. Dieselbe Schaltung wurde auch im MPROC verwendet.

Die Chipperipherie ist bei allen Designs ähnlich. Sie enthält eine synthetisierte Auslesesteuereinheit.

Die Designs sind aus mehreren Gründen innovativ und komplex.

Bei monolithischen Sensoren: niedriges Rauschen (wegen schwacher Signale), niedriger Stromverbrauch (wegen hoher Kanalzahl) und hohe Bandbreite (wegen der spezifizierten hohen Zeitauflösung) der Verstärker ist erforderlich. Die langen Verbindungen zwischen den Pixels und Auslesezellen stellen Herausforderung dar.

Im Fall von MPROC: Das Übersprechen zwischen den Signalen kann vermieden werden, da es keine langen Verbindungen gibt. Das Pixel ist jedoch ziemlich komplex und enthält analoge und digitale Schaltungen. Neben den vielen Gemeinsamkeiten, hat jeder Chip auch seine ganz besonderen Eigenschaften. Es gibt mehrere neuartige Schaltungen.

Beim MPROC-ASIC wurden in der Pixelelektronik zwei verschiedene Rückkopplungsarten entwickelt, damit der Chip Elektronen und Löcher verstärken kann. Es wurde eine spezielle Pixelanordnung implementiert, um einen kleinen Bonding-Pad-Abstand (55 Mikrometer) zu erreichen und die Ladungsteilung zu minimieren. Um eine hohe Energieauflösung zu erreichen, wurden die Spitzendetektoren und 10-Bit-Zählern implementiert. Eine hohe Zeitauflösung kann durch einen 7-Bit-TDAC erreicht werden. Sehr kleine Pixelgröße für eine 180nm Technologie wurde erreicht. Im Fall des CCPD-Projekts wurden auch einige Innovationen getestet. Eine tiefe p-Wanne wurde verwendet, um die Pixelelektronik vom Sensorsubstrat zu isolieren. Die Auslese von kleinen Pixels wurde durch Multiplexen von Signalen ermöglicht. Messungen mit kapazitiv gekoppelten Chips wurden gemacht.

Im Fall des HVMPAS25-Chips wurde eine kleine Ladungssammelelektrode im HVCMOS-Prozess implementiert. Sehr kleine Pixelgröße konnte erreicht werden. Die n-Wannen des Sensors sind mit den Verstärkern AC-gekoppelt und können an eine Vorspannung von 10 V gelegt werden.

Bei CLIC- und PANDA-ASICs werden verschiedene Versionen von Komparator und Verstärker beschrieben. Es wurden Schaltungen für mit einem hohen Dynamikbereich entwickelt.

Folgende Messungen wurden für alle ASICs durchgeführt.

- 1) Amplitudenmessung des Verstärkerausgangs mit Oszilloskop.

- 2) Chips-Bestrahlung mit Fe55-Quelle und Vergleich der Amplituden.

- 3) Schwelle-Scan-Messungen.

- 4) Messungen der Pulsbreite (ToT).

- 5) Messungen der Zeitwanderung (TW).

# Abstact

The contribution of my dissertation are designs of several CMOS application specific integrated circuits (ASICs) for different scientific and medical applications.

The first ASIC developed by me is the readout chip (MPROC) for a hybrid pixel detector for medical application. The chip can be used to read out a CdTe pixel sensor.

The second ASIC is a sensor chip for a capacitively coupled pixel detector (CCPD) (CCPD53). It could be applied in the inner layer of the ATLAS pixel detector.

The third chip that I developed is monolithic pixel detector (HVMAPS25) with small fill factor for CLIC or CEPC particle physic experiments.

I was also involved in the development of the ASICs (CLIC v1/v2 and v3 high dynamic range) that could be applied in PANDA and CLIC experiments. They provide precise trajectory reconstruction, energy and momentum measurements.

I also worked on several other projects that are not described in the thesis: sensors in lFoundry process, ATLASPIX1 and ATLASPIX3, MUPIX8.

Although the applications are different, the circuits have similarities.

The pixel electronics of each ASIC contains charge sensitive amplifier, RC filter, feedback circuits, comparator with tune DACs. The readout circuit was as first developed for a monolithic sensor. The same readout circuit has been used in the MPROC as well. The chip periphery is similar to all designs. It contains synthesized readout control unit.

The designs are from several reasons challenging.

In the case of monolithic sensors: low noise (because of low signals), low power consumption (because of high number of channels) and high bandwidth (because of specified high time resolution) of the amplifiers is required. The routing of long lines between pixels and readout cells is challenging. In the case of MPROC: the crosstalk between signals can be avoided because there are no long connections. However, the pixel is quite complex and it contains analog and digital circuits.

In addition to the similarities, each chip has its own special properties. There are several novel circuits.

In the case of MPROC ASIC, two various feedback types have been designed in pixel electronics so that the chip can amplify electrons and holes. A special pixel arrangement

has been implemented to achieve small pad pitch (55 mircometers) and to cope with charge sharing. High energy resolution could be achieved by use of peak detectors and 10 bit counter. High time resolution can be achieved by a 7 bit TDAC. Very small pixel size for a 180nm technology have been achieved.

Also in the case of CCPD project I have tested several novelties. The deep p-well has been implemented in the technology for the first time and used for isolation the pixel electronics from the sensor substrate. The readout of a small pixels was achieved using a special output signal encoding. Measurements with capacitively coupled ASICs have been performed.

In the case of HVMPAS25 chip, small charge collection electrode has been implemented in HVCMOS process. Very small pixel size could be achieved. The sensor n-wells are AC-coupled to the amplifiers and they can be biased with 10 V with respect to the p-substrate.

In the case of CLIC and PANDA ASICs, different versions of comparator and amplifier are described. Circuits for high dynamic range were implemented.

I have performed detailed characterization of the chips that included following measurements:

1) Amplitude measurement of amplifier output with oscilloscope.

2) Chips irradiation with Fe55 source and comparison of the signal amplitudes.

3) Threshold scan measurements and calculation of the mean as well as sigma of the threshold dispersion from the fit data.

- 4) Pulse width (ToT) measurements.

- 5) Time walk (TW) measurements.

# Contents

| Zu | samn    | nenfassu | ing                                                                               | iii |  |

|----|---------|----------|-----------------------------------------------------------------------------------|-----|--|

| Ab | Abstact |          |                                                                                   |     |  |

| 1  | Intro   | oduction |                                                                                   | 1   |  |

|    | 1.1     | My con   | tribution                                                                         | 1   |  |

|    | 1.2     | •        | Process                                                                           | 5   |  |

|    | 1.3     | 0        | OS Pixel Sensors                                                                  | 7   |  |

|    | 1.4     | Silicon  | detector                                                                          | 9   |  |

|    | 1.5     | Detecto  | r Electronics                                                                     | 11  |  |

|    | 1.6     | Charge   | Sensitive Amplifier                                                               | 13  |  |

|    |         | 1.6.1    | Folded Cascode Amplifier                                                          | 13  |  |

|    |         | 1.6.2    | Continuous reset and rising time optimization                                     | 13  |  |

|    | 1.7     | Time W   | Valk                                                                              | 15  |  |

|    |         | 1.7.1    | Noise analysis in Charge Sensitive Amplifier                                      | 17  |  |

| 2  | MPF     | ROC      |                                                                                   | 21  |  |

|    | 2.1     | Backgro  | ound                                                                              | 21  |  |

|    |         | 2.1.1    | Photon interaction with matter                                                    | 21  |  |

|    |         | 2.1.2    | X-rays interaction with matter                                                    | 22  |  |

|    |         | 4        | 2.1.2.1 Direct and Indirect X-ray conversion                                      | 23  |  |

|    |         | 2.1.3    | Unwanted Effects                                                                  | 24  |  |

|    |         | 2.1.4    | CdTe material and the application in X-ray imaging                                | 24  |  |

|    | 2.2     | Project  | Introduction                                                                      | 26  |  |

|    |         |          |                                                                                   | 26  |  |

|    |         | 2.2.2    | Different Operation Modes                                                         | 26  |  |

|    | 2.3     | Design   | and Implementation                                                                | 29  |  |

|    |         | 2.3.1    | Pixel Electronics                                                                 | 30  |  |

|    |         | 2.3.2    | Feedback Circuit                                                                  | 32  |  |

|    |         | 4        | 2.3.2.1 Influence from neighbor pixels                                            | 32  |  |

|    |         | 4        | 2.3.2.2 Peak Detector                                                             | 33  |  |

|    |         |          | 1                                                                                 | 35  |  |

|    |         |          |                                                                                   | 38  |  |

|    |         | 4        | 2.3.3.1 Hit Buffer                                                                | 38  |  |

|    |         |          | 2.3.3.2 Time to digital converter                                                 | 43  |  |

|    |         | 4        | 2.3.3.3 End of Column (EoC) $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 46  |  |

|    |         | 2.3.4    |                                                                                   | 48  |  |

|    |         |          |                                                                                   | 48  |  |

|    |         | 1        |                                                                                   | 49  |  |

|    |         | :        | 0                                                                                 | 51  |  |

|    | 2.4     |          |                                                                                   | 52  |  |

|    |         | 2.4.1    | Measurement setup                                                                 | 52  |  |

| 3 | CCF | PD 57                                                                                                                                                          |

|---|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 3.1 | Background of hybrid pixel concept                                                                                                                             |

|   | 3.2 | Project Introduction                                                                                                                                           |

|   | 3.3 | CCPD53 Sensor Chip                                                                                                                                             |

|   |     | 3.3.1 Design and Implementation                                                                                                                                |

|   |     | 3.3.1.1 Sensor chip structure                                                                                                                                  |

|   |     | 3.3.1.2 Sensor chip pixel electronics                                                                                                                          |

|   | 3.4 | PHOTON Readout Chip                                                                                                                                            |

|   |     | 3.4.1 Pixel electronics                                                                                                                                        |

|   | 3.5 | Measurements                                                                                                                                                   |

|   |     | 3.5.1 Standalone Sensor Chip Test                                                                                                                              |

|   |     | 3.5.1.1 Experimental Setup                                                                                                                                     |

|   |     | 3.5.1.2 Measurements with electrical test signals                                                                                                              |

|   |     | 3.5.1.3 Measurements with radioactive sources                                                                                                                  |

|   |     | 3.5.2 Both Chip Test                                                                                                                                           |

|   |     | 3.5.2.1 Experimental Setup                                                                                                                                     |

|   |     | 3.5.2.2 Counting                                                                                                                                               |

|   |     | 3.5.2.3 Threshold measurement for a signal pixel                                                                                                               |

|   |     | 3.5.2.4 Threshold measurement for whole matrix                                                                                                                 |

|   |     |                                                                                                                                                                |

| 4 |     | MAPS25 77                                                                                                                                                      |

|   | 4.1 | Project Introduction                                                                                                                                           |

|   | 4.2 | Design and Implementation                                                                                                                                      |

|   |     | 4.2.1 Pixel structure                                                                                                                                          |

|   | 4.9 | 4.2.2 Analog pixel electronics                                                                                                                                 |

|   | 4.3 | Measurements                                                                                                                                                   |

|   |     | 4.3.1 PCB Desgin                                                                                                                                               |

|   |     | 4.3.2 Measurement Results                                                                                                                                      |

|   |     | 4.3.2.1Measurement with injection circuit854.3.2.2Measurement with Fe55 radioactive source88                                                                   |

|   |     | 4.3.2.2 Measurement with Fe55 radioactive source                                                                                                               |

| 5 | CLI | C 89                                                                                                                                                           |

|   | 5.1 | Introduction                                                                                                                                                   |

|   | 5.2 | CLIC Experiment                                                                                                                                                |

|   |     | 5.2.1 Design and Implementation                                                                                                                                |

|   |     | 5.2.1.1 Comparator $\dots \dots \dots$                         |

|   |     | 5.2.1.2 Charge sensitive amplifier $\dots \dots 93$                                          |

|   | 5.3 | PANDA Experiment                                                                                                                                               |

|   |     | 5.3.1 The structure of PANDA ASIC                                                                                                                              |

|   | 5.4 | Measurement Overview                                                                                                                                           |

|   | 5.5 | Measurement results of PANDA ASIC (v3 high dymanic range) 100                                                                                                  |

|   |     | 5.5.1 Measurement with Fe55 radioactive source                                                                                                                 |

|   |     | 5.5.2 Amplitude and pulse width calibration with injection circuits 100                                                                                        |

|   |     | 5.5.3 Time walk measurement versus injection value                                                                                                             |

|   |     | 5.5.4 TDAC versus FPGA delay                                                                                                                                   |

|   |     | 5.5.5 Time versus Delay $\ldots \ldots \ldots$ |

|   |     | 5.5.6 ToT and TDAC calibration                                                                                                                                 |

|   |     | 5.5.7 Time and corrected time versus pulse width 109                                                                                                           |

|   |     | 5.5.8 Comparison of big and small pixels with large and small current 111                                                                                      |

|   |     | 5.5.9 Threshold scan $\ldots \ldots \ldots$    |

|   |     |                                                                                                                                                                |

|    | 5.6   | Meas    | urement results of CLIC ASIC (v1/v2 chip) $\ldots \ldots \ldots \ldots$ | <br>115 |

|----|-------|---------|-------------------------------------------------------------------------|---------|

| 6  | Con   | clusior | 1                                                                       | 117     |

| Ap | pend  | lix     |                                                                         | 119     |

|    | Α     | Radia   | ation Damage                                                            | <br>119 |

|    |       | A.1     | Displacement Damage                                                     | <br>119 |

|    |       | A.2     | Ionization Damage                                                       | <br>119 |

|    |       | A.3     | Radiation tolerant IC Desgin                                            | <br>120 |

| Pu | blica | tion    |                                                                         | 127     |

| Bi | bliog | raphy   |                                                                         | 129     |

# List of Figures

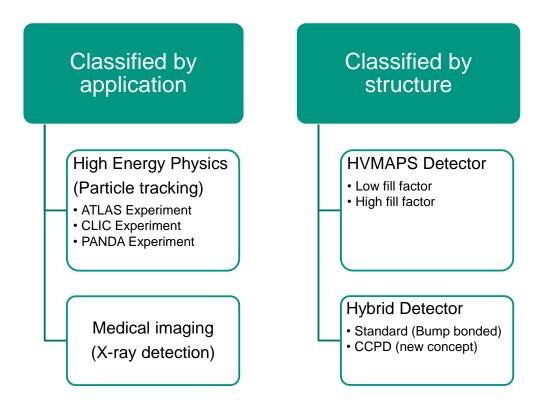

| 1.1  | Classification of pixel detectors according to applications and structures                                                                  |    |

|------|---------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | (covered in my thesis)                                                                                                                      | 3  |

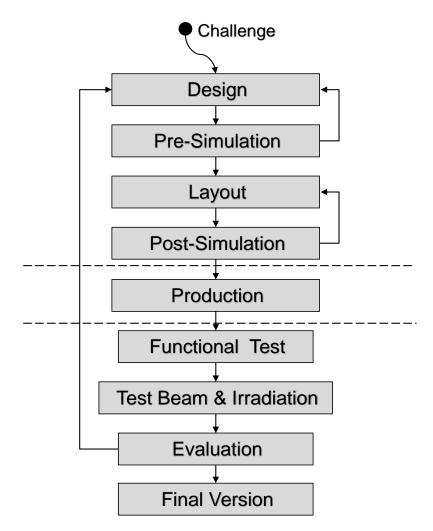

| 1.2  | Full custom chip design process                                                                                                             | 5  |

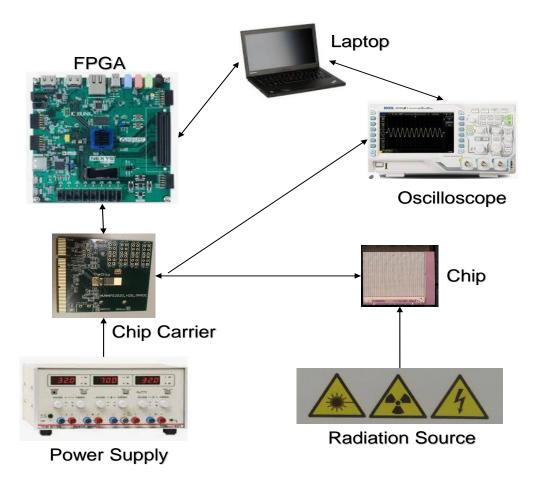

| 1.3  | General experiment setup                                                                                                                    | 6  |

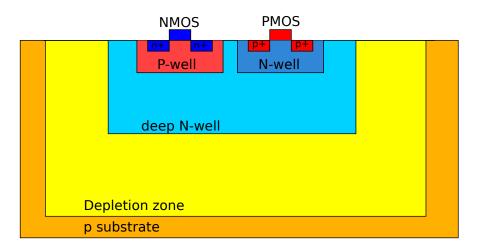

| 1.4  | HVCMOS sensor                                                                                                                               | 7  |

| 1.5  | Modified HVCMOS senosor with a deep P-well implant                                                                                          | 8  |

| 1.6  | Modified HVCMOS senosor with small charge collection electrode                                                                              | 8  |

| 1.7  | Detector electronics                                                                                                                        | 11 |

| 1.8  | Time diagram that describes ToT measurement                                                                                                 | 12 |

| 1.9  | Transistor level schematic of the amplifier                                                                                                 | 13 |

| 1.10 | Time walk definition and time walk of two input signals for different threshold                                                             |    |

|      | values                                                                                                                                      | 15 |

| 1.11 | Noise sources in charge sensitive amplifier with feedback                                                                                   | 17 |

|      |                                                                                                                                             |    |

| 2.1  | Three types of photon interactions depending on energy and atomic number                                                                    |    |

|      | $[29] \ldots \ldots$ | 22 |

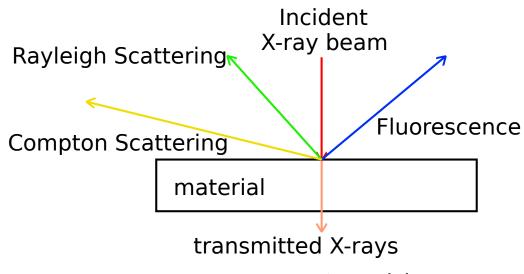

| 2.2  | X-ray interaction with matter [30]                                                                                                          | 22 |

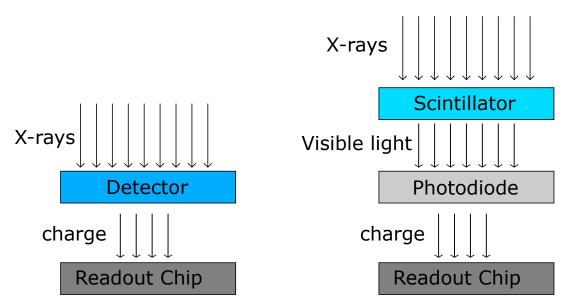

| 2.3  | Comparison between direct (left) and indirect (right) detection of X-rays                                                                   | 23 |

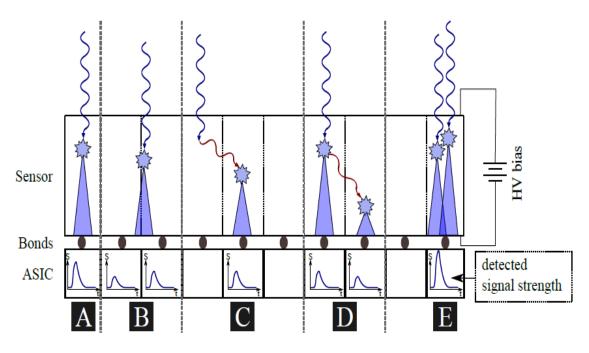

| 2.4  | Illustration of spectral distortion effects in pixel detectors [31]                                                                         | 25 |

| 2.5  | Three operation modes                                                                                                                       | 27 |

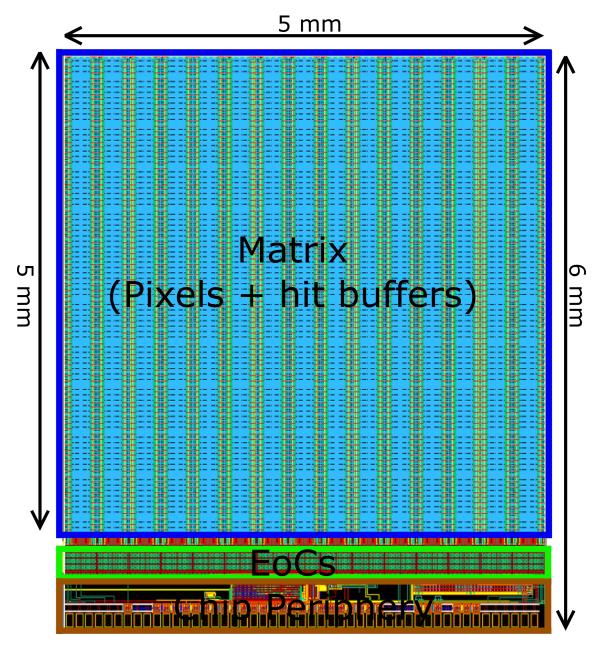

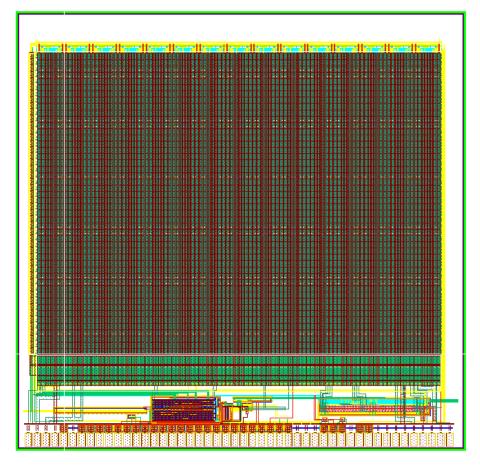

| 2.6  | Chip layout of MPROC                                                                                                                        | 29 |

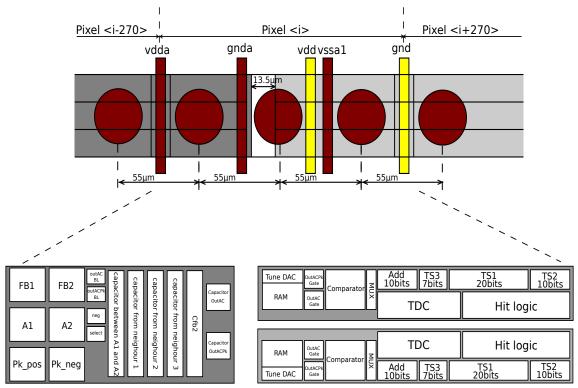

| 2.7  | The structure and layout of the pixel electronics                                                                                           | 30 |

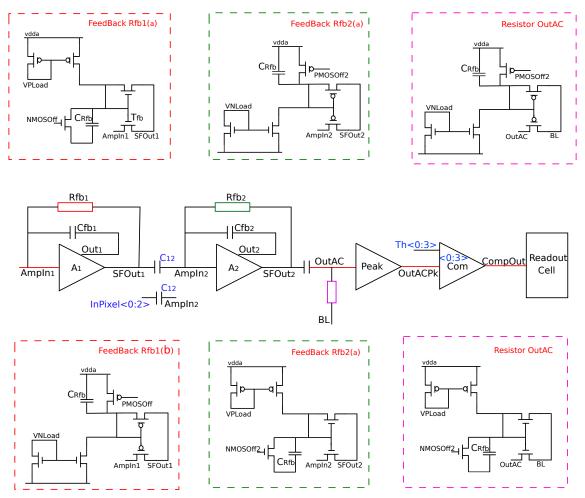

| 2.8  | Schematic of pixel electronics                                                                                                              | 31 |

| 2.9  | Model used for the estimation of cross talk to neighbor pixels                                                                              | 33 |

| 2.10 | The influence from neighbor pixels                                                                                                          | 33 |

| 2.11 | The peak detector for negative (a) and positive (b) polarities                                                                              | 34 |

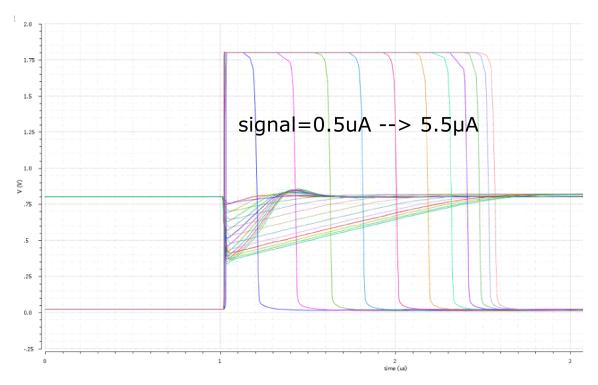

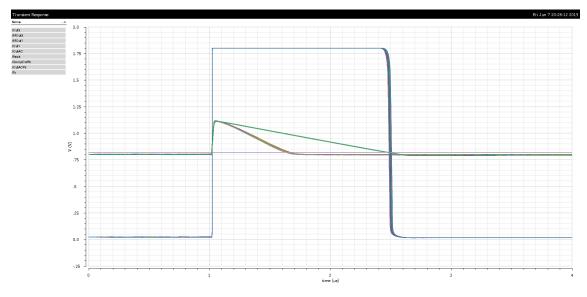

| 2.12 | Test of the functionality of amplifier, peak detector and comparator                                                                        | 35 |

| 2.13 | ToT response to different inputs                                                                                                            | 36 |

| 2.14 | Transient noise analysis                                                                                                                    | 36 |

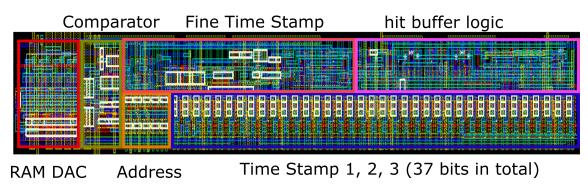

| 2.15 | Layout of readout cell                                                                                                                      | 38 |

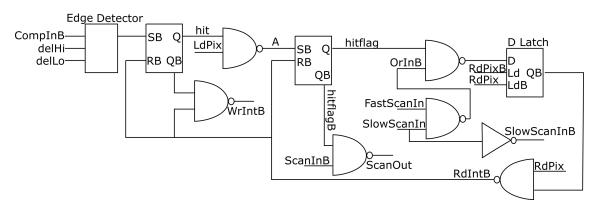

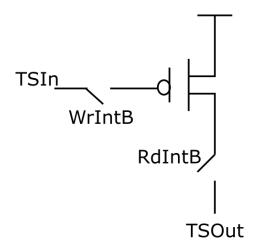

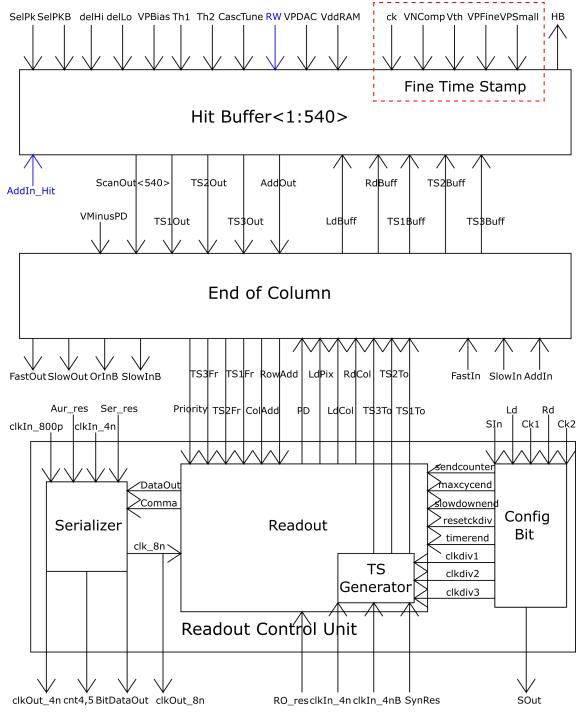

|      | The CMOS logic in hit buffer                                                                                                                | 38 |

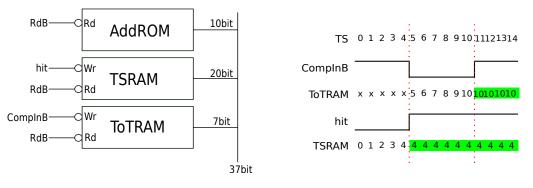

|      | DRAM for storing of time stamp                                                                                                              | 39 |

| 2.18 | DRAM loigc                                                                                                                                  | 39 |

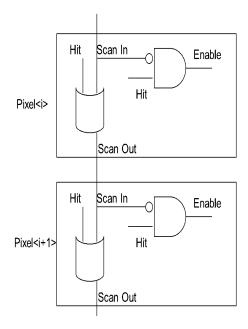

| 2.19 | Enable logic and ScanOut logic of priority in readout cell                                                                                  | 40 |

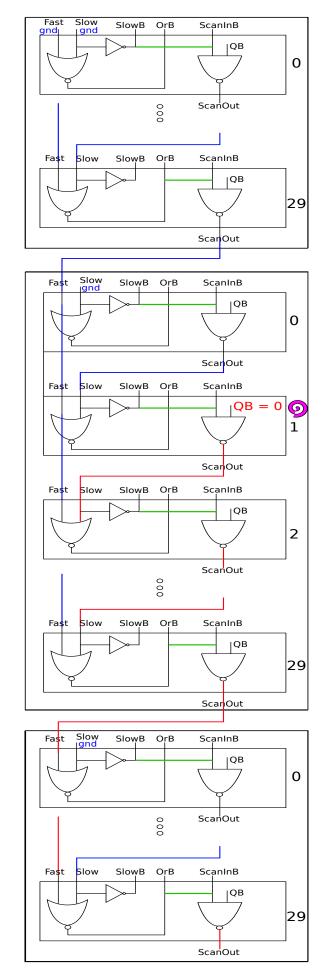

| 2.20 | Fast and slow logic of ScanOut in readout cell                                                                                              | 42 |

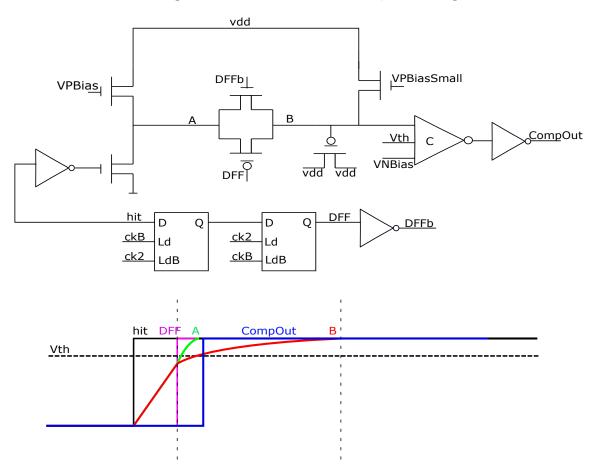

| 2.21 | Schematic of TDC (fine time stamp)                                                                                                          | 43 |

| 2.22 | Explanation of fine time stamp                                                                                                              | 44 |

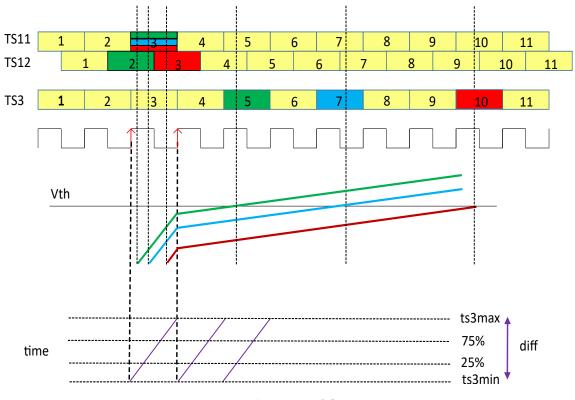

| 2.23 | The connection between hit buffer and EoC                                                                                                   | 47 |

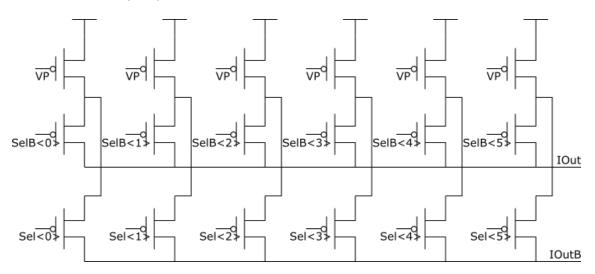

| 2.24 | Schmatic of bias DAC                                                                                                                        | 49 |

|      | Two types of bias diode depending on current polarities                                                                                     | 50 |

|      | Current divider designed between DAC and diode connected transistor                                                                         | 50 |

|      | Structure of one bit                                                                                                                        | 51 |

51

52

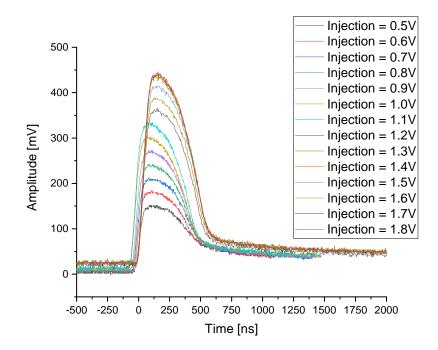

| 2.30    | Waveform of positive feedback (NMOS) (left) and negative feedback (PMOS)                                                                           | 50  |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 0.01    | (right)                                                                                                                                            | 53  |

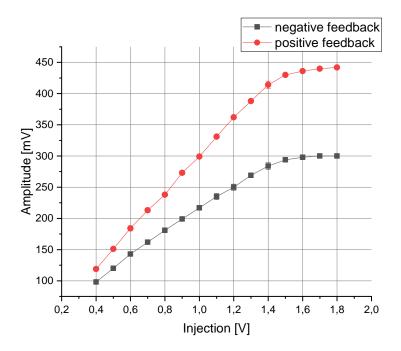

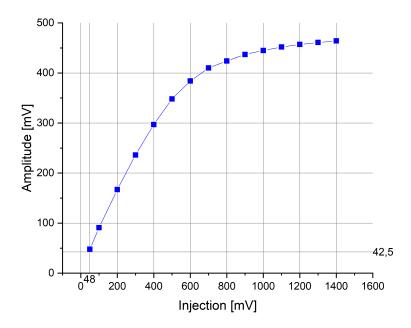

|         | Amplitude of amplifier output versus injection voltage (with positive feedback)                                                                    | 54  |

| 2.32    | Amplitude of amplifier output with positive feedback (NMOS feedback) and                                                                           | - 1 |

| 0.00    | negative feedback (PMOS feedback)                                                                                                                  | 54  |

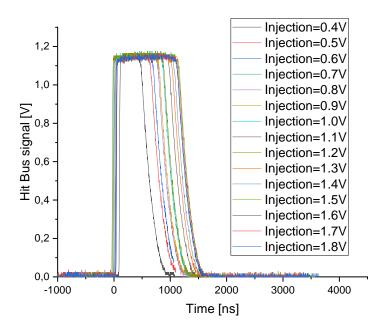

|         | Hit bus signal versus injection voltage                                                                                                            | 55  |

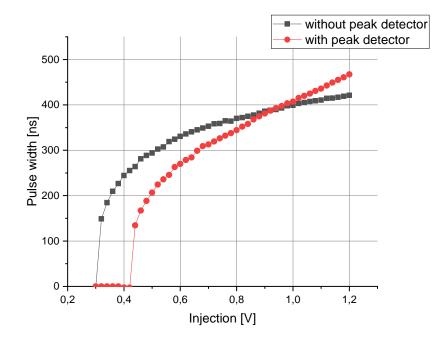

| 2.34    | Single pixel pulse width versus injection voltage, with and without peak                                                                           |     |

|         | detector                                                                                                                                           | 55  |

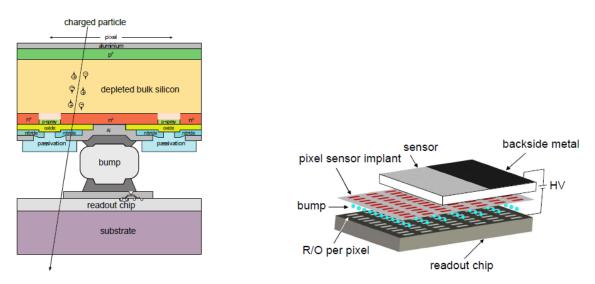

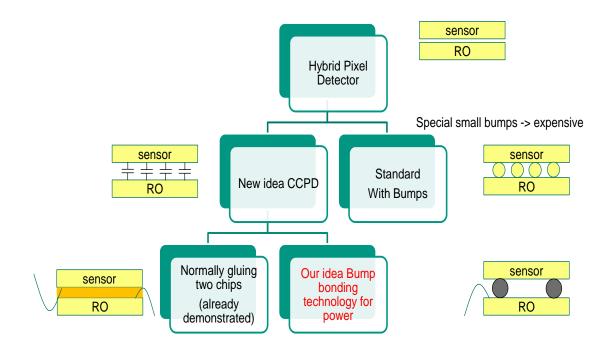

| 3.1     | Hybrid pixel detector                                                                                                                              | 57  |

| 3.2     | Hybrid pixel detector classification                                                                                                               | 59  |

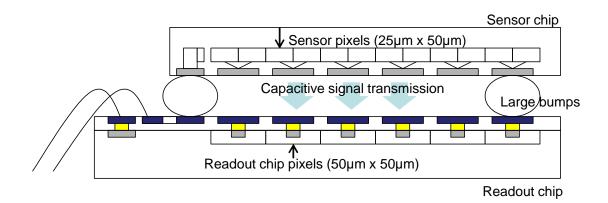

| 3.3     | A new concept of CCPD. Sensor and readout chip are connected with several                                                                          |     |

|         | large bumps, signals are transmitted capacitively [44]                                                                                             | 60  |

| 3.4     | Structure of the CCPD53 sensor chip                                                                                                                | 62  |

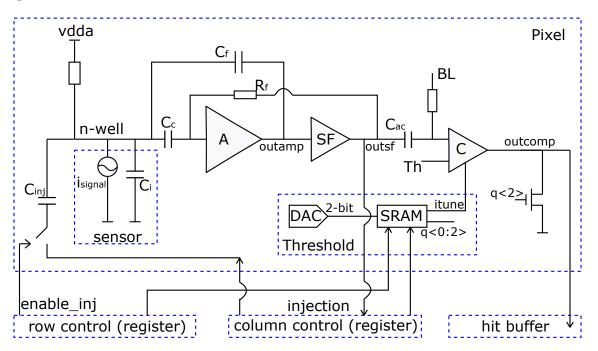

| 3.5     | Pixel schematic of the CCPD53 sensor chip                                                                                                          | 63  |

| 3.6     | Pixel layout of the CCPD53                                                                                                                         | 63  |

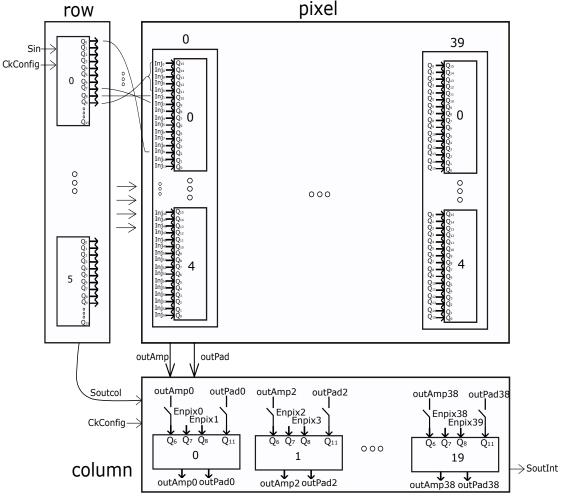

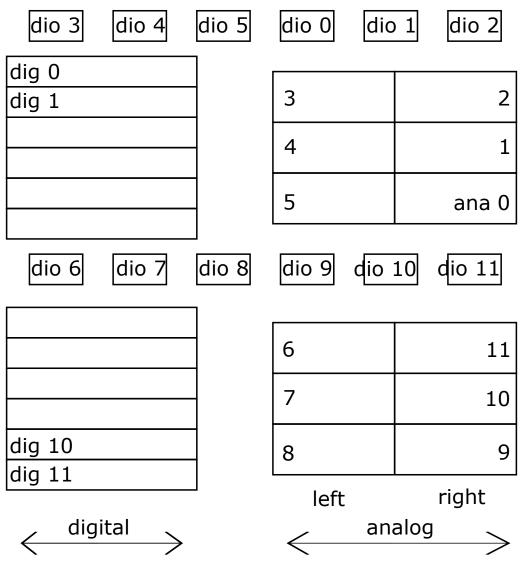

| 3.7     | Address encoding                                                                                                                                   | 64  |

| 3.8     | Schematic of a pixel in the PHOTON chip                                                                                                            | 65  |

| 3.9     | Experimental setup                                                                                                                                 | 66  |

| 3.10    | Photo of experimental setup for standalone chip test                                                                                               | 66  |

|         | Amplifier output versus injection voltages                                                                                                         | 67  |

| 3.12    | Signal amplitude versus injection voltage                                                                                                          | 68  |

| 3.13    | Fe55 spectrum obtained using a numerical filter at room temperature $\ldots$                                                                       | 69  |

|         | Fe55 spectrum obtained using peak to peak method at room temperature $% \mathcal{F}_{\mathrm{spectrum}}$ .                                         | 69  |

| 3.15    | Fe55 spectrum obtained using numerical filter at low temperature (Peltier                                                                          |     |

|         | cooler)                                                                                                                                            | 70  |

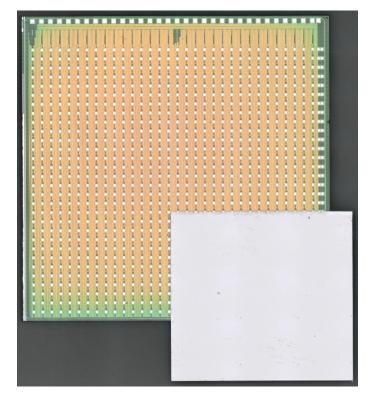

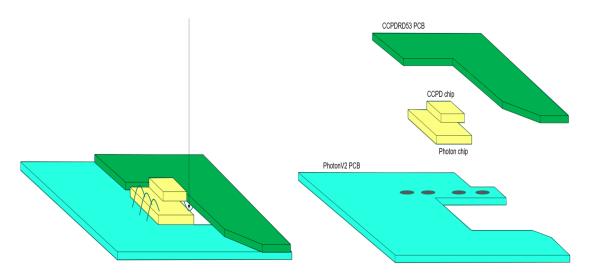

|         | Arrangement of the PHOTON readout chip and the CCPD53 sensor chip .                                                                                | 71  |

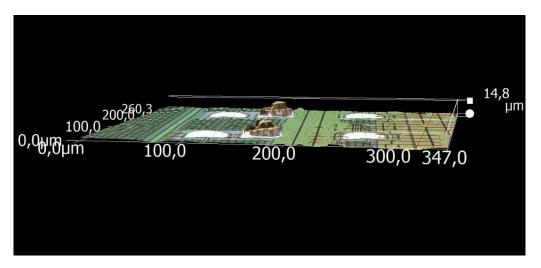

|         | The height of bumps                                                                                                                                | 72  |

|         | Photo of the assembly with the CCPD53 chip and the PHOTON chip $\ldots$                                                                            | 72  |

| 3.19    | Assembly with the CCPD53 chip and the PHOTON chip. The chips are                                                                                   |     |

| ~ ~ ~ ~ | wire bonded to different PCBs.                                                                                                                     | 73  |

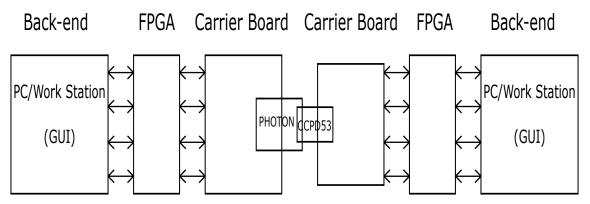

|         | Experimental setup for testing of both chips                                                                                                       | 73  |

|         | Photo of experimental setup for testing of both chips                                                                                              | 74  |

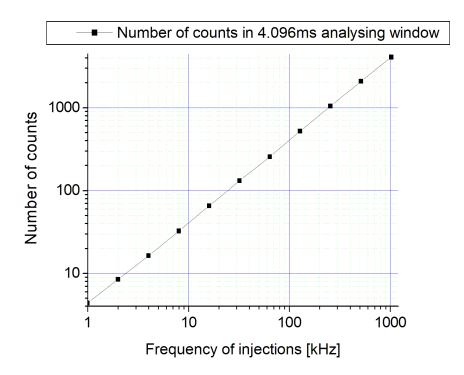

| 3.22    | Measurement result obtained with the CCPD53 that is read out using the                                                                             |     |

|         | PHOTON chip. Test signals were injected into the CCPD53 at different                                                                               |     |

|         | frequencies. The number of detected signals is shown over the generation                                                                           | 74  |

| റ റെ    | frequency                                                                                                                                          | 74  |

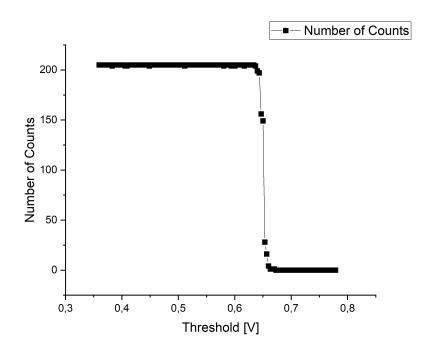

| 3.23    | Threshold scan for single pixel. 205 injections of 2600 e have been applied                                                                        |     |

|         | to one CCPD pixel sensor and the threshold voltage of PHOTON chip has<br>been varied. For each threshold setting the number of counted signals has |     |

|         | been plotted                                                                                                                                       | 75  |

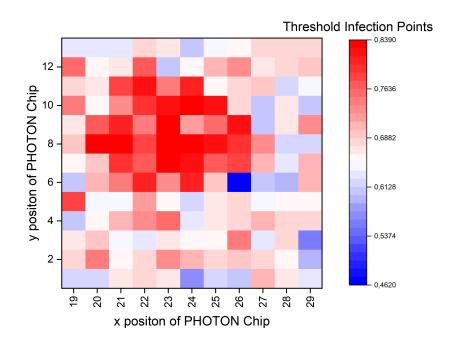

| 3.94    | Threshold scan for the whole PHOTON chip matrix. Injections of 2600 e                                                                              | 10  |

| 0.24    | applied to the pixels of the CCPD53. Threshold values in the pixels of the                                                                         |     |

|         | PHOTON chip required for detection the signals from CCPD53 with 50 %                                                                               |     |

|         | probability are plotted. X-position corresponds to pixel row and y-position                                                                        |     |

|         | to pixel column.                                                                                                                                   | 76  |

|         | •                                                                                                                                                  | . • |

| 4.1     | HVCMOS sensor with small fill factor                                                                                                               | 78  |

| 4.2     | Layout of HVMAPS25                                                                                                                                 | 79  |

| 4.3     | Pixel floor plan                                                                                                                                   | 80  |

|         |                                                                                                                                                    |     |

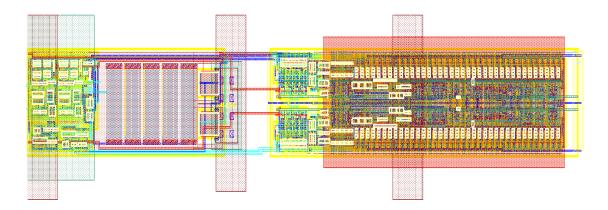

2.29 Test setup for MPROC

| 4.4  | Pixel structure of HVMAPS25 ASIC                                                                                                     | 81  |

|------|--------------------------------------------------------------------------------------------------------------------------------------|-----|

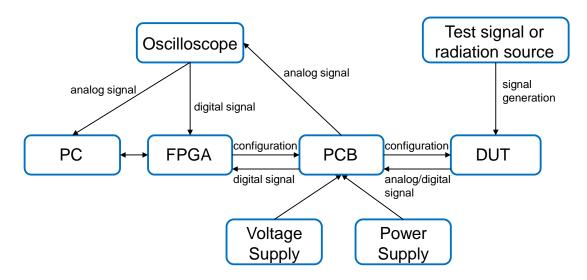

| 4.5  | A typical setup for characterization of a device under test (DUT)                                                                    | 82  |

| 4.6  | Components of the test system and development tools used to design                                                                   | 82  |

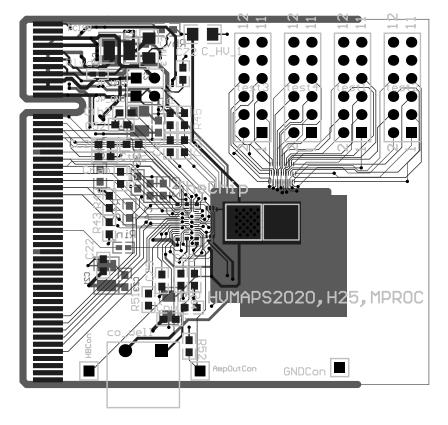

| 4.7  | PCB layout for both MPROC and HVMAPS25 chips                                                                                         | 83  |

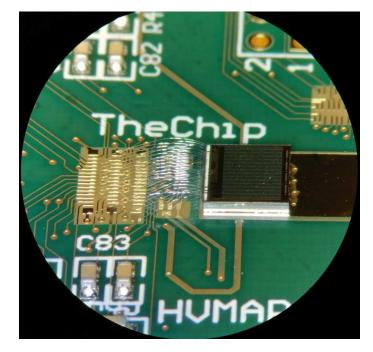

| 4.8  | Wire bonding                                                                                                                         | 84  |

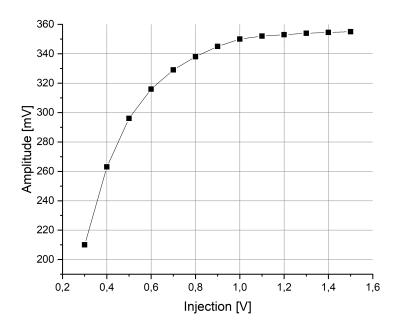

| 4.9  | Amplitude of amplifier output versus injection voltage (from 7029 e to 39829                                                         |     |

|      | e) (analogue signal)                                                                                                                 | 85  |

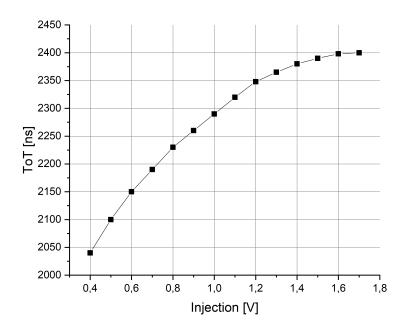

| 4.10 | ToT versus injection voltage (digital signal)                                                                                        | 86  |

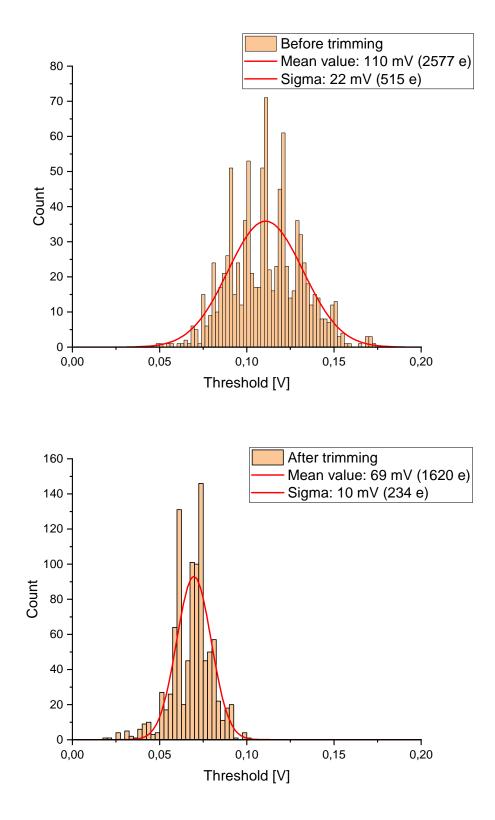

|      | Input referred threshold dispersion before trimming versus after trimming .                                                          | 87  |

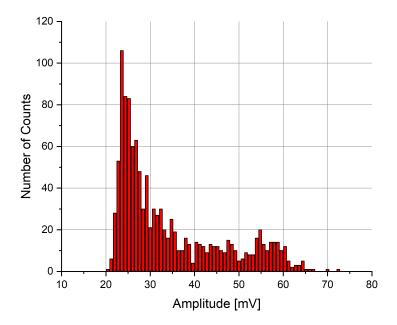

|      | Histogram of measured signal amplitudes when chip is irradiated with Fe55                                                            | 88  |

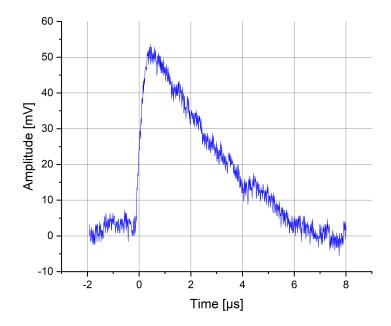

|      | Amplifier output waveform response to Fe55 photons                                                                                   | 88  |

|      |                                                                                                                                      |     |

| 5.1  | CMOS comparator                                                                                                                      | 92  |

| 5.2  | NMOS-based comparator                                                                                                                | 92  |

| 5.3  | Distributed comparator                                                                                                               | 93  |

| 5.4  | Transistor level of Charge Sensitive Amplifier with PMOS input transistor .                                                          | 93  |

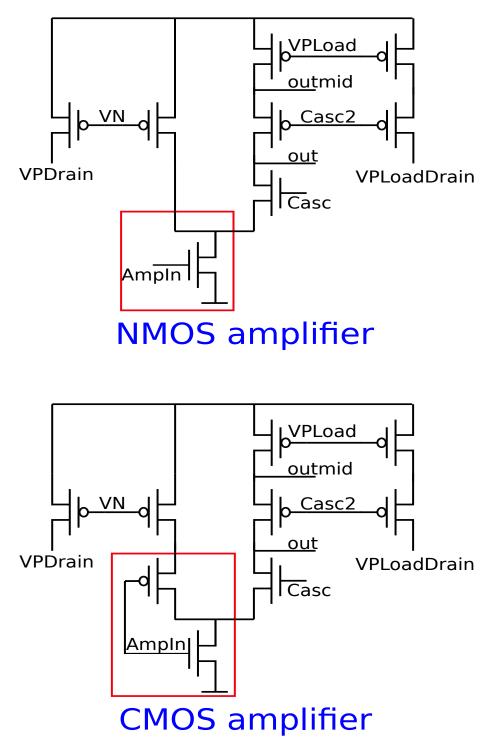

| 5.5  | NMOS and CMOS amplifier                                                                                                              | 95  |

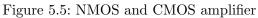

| 5.6  | The structure of CLIC ASIC                                                                                                           | 97  |

| 5.7  | Schematic of pixel electronics of CLIC                                                                                               | 98  |

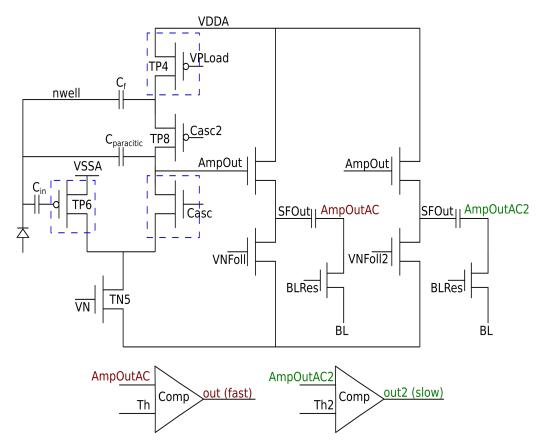

| 5.8  | Histogramm of measured signal amplitudes when chip is irradiated with Fe55                                                           |     |

| 5.9  | Amplitude of amplifier output versus injection voltage (from 1708 e to 47833 e)                                                      | 101 |

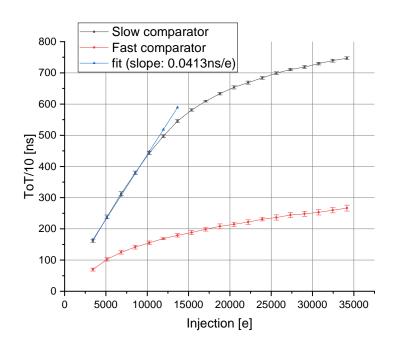

| 5.10 | Pulse width of the slow and fast comparator versus injected amplitude (from                                                          |     |

|      | injection = 50 mV and clock period = 10 ns) $\dots \dots \dots \dots \dots \dots$                                                    |     |

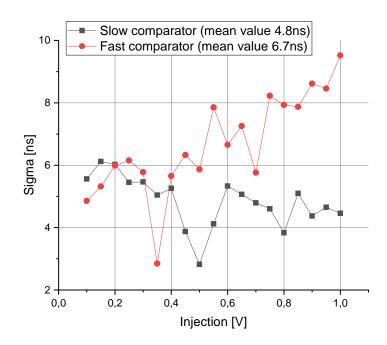

|      | Sigma of calculated pulse width versus injection amplitude                                                                           |     |

|      | Time walk definition                                                                                                                 | 103 |

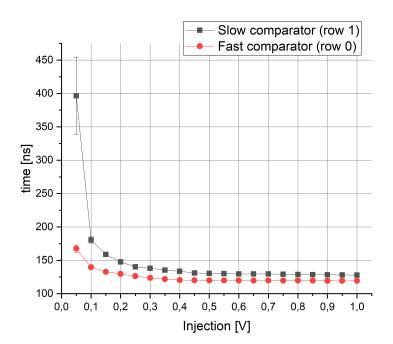

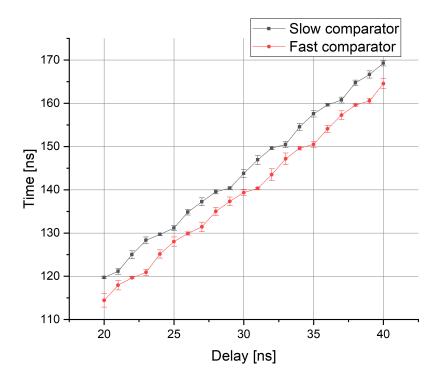

| 5.13 | Measured comparator response time versus different injections (clock period                                                          | 100 |

|      | $= 10 \text{ ns}) \dots \dots$ |     |

|      | Sigma of the calculated time versus injection amplitude                                                                              | 104 |

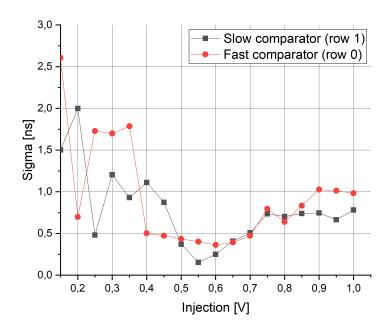

| 5.15 | Measured time stamp TS3 generated by TDAC versus delay of the injection                                                              | 105 |

| E 16 | pulse (setting in FPGA)                                                                                                              | 105 |

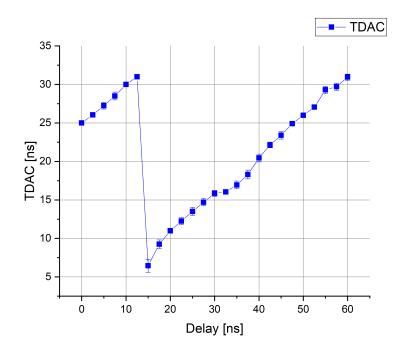

| 5.10 | FPGA) (clock period = $10 \text{ ns}$ )                                                                                              | 106 |

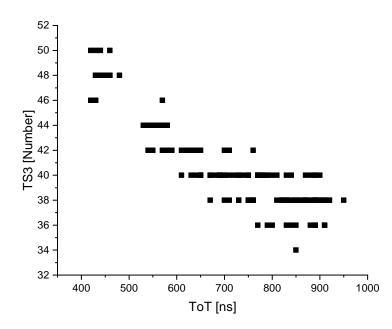

| 5 17 | TDAC values for different pulse widths. X coordinate of each point is                                                                | 100 |

| 0.17 | measured ToT (fast comparator) and y coordinate is measured TS3 (fast                                                                |     |

|      | comparator). Each point is result of one injection. Injections have been                                                             |     |

|      | varied from 0.3 V to 1 V                                                                                                             | 107 |

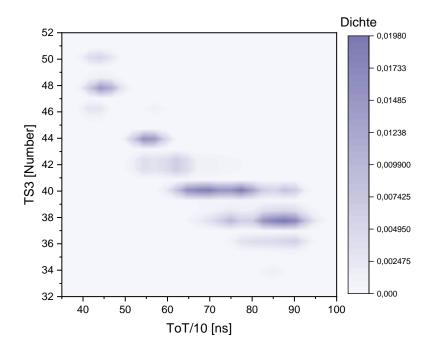

| 5 18 | The density of points instead of single point for figure 5.17                                                                        |     |

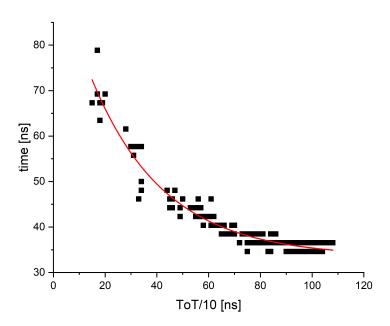

|      | Time versus different pulse widths. X coordinate of each point is measured                                                           | 101 |

| 0.10 | ToT with slow comparator and y coordinate is calculated response time                                                                |     |

|      | measured with fast comparator. Each point is result of one injection. The                                                            |     |

|      | injections have been varied from 150 mV to 800 mV with 50 mV step                                                                    | 109 |

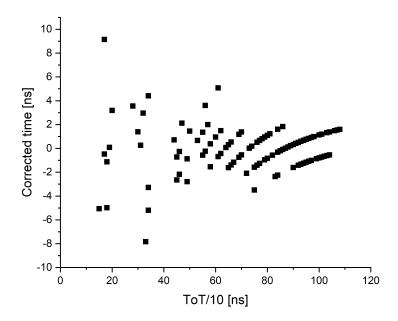

| 5.20 | The corrected time (distance to fit) versus measured ToT (TS2)                                                                       |     |

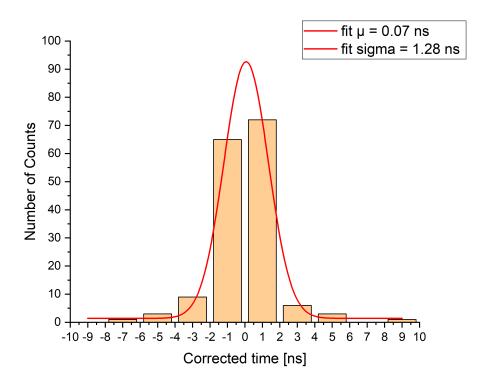

|      | Corrected time (the data from figure 5.20) shown as histogram                                                                        |     |

|      | Time walk versus different rows of VN10 (1.6 $\mu$ A) and VN20 (3.1 $\mu$ A)                                                         |     |

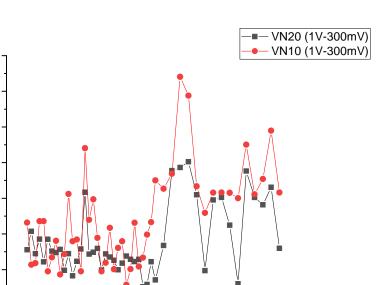

|      | Time walk versus different rows of VN30 (4.7 $\mu$ A) and VN60 (9.4 $\mu$ A)                                                         |     |

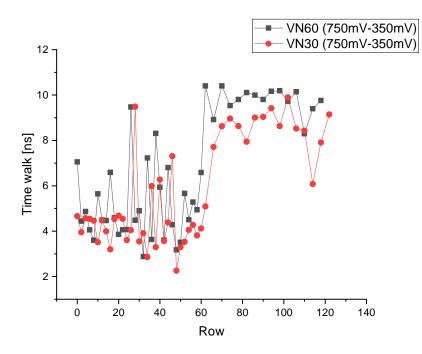

|      | Input referred threshold dispersion with fast comparator before trimming                                                             |     |

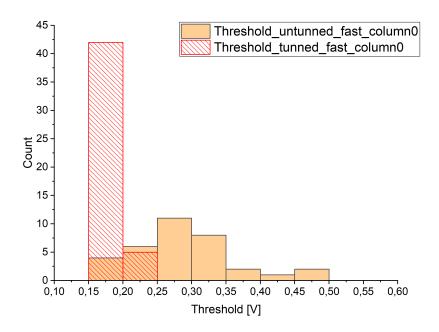

|      | versus after trimming                                                                                                                | 113 |

| 5.25 | Input referred threshold dispersion with slow comparator before trimming                                                             | -   |

| -    | versus after trimming                                                                                                                | 113 |

| 5.26 | Time walk versus different amplifier bias current setting of CLIC ASICs                                                              |     |

|      | SNR versus different amplifier bias current setting of CLIC ASICs                                                                    |     |

|      | Four variants threshold of CLIC ASICs                                                                                                |     |

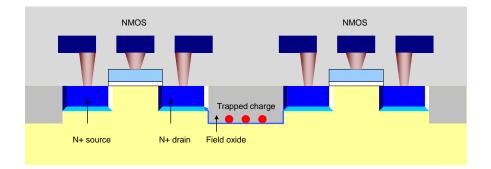

| A.1 | Radiation influence on IC structure                                       | 120 |

|-----|---------------------------------------------------------------------------|-----|

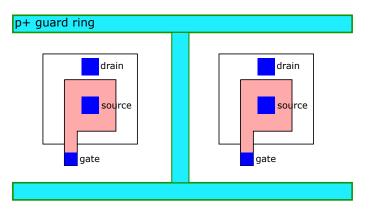

| A.2 | p+ guard ring is applied for preventing leakage current flows between two |     |

|     | NMOS transistors                                                          | 120 |

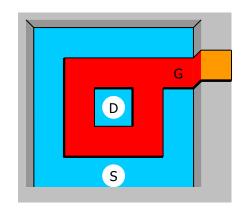

| A.3 | Annular gate electrode for preventing leakage current flows from drain to |     |

|     | source                                                                    | 120 |

# List of Tables

| 2.1 | Properties of the Semiconductor [33]                                       | 5 |

|-----|----------------------------------------------------------------------------|---|

| 2.2 | Main Characteristics of MPROC chip 2                                       | 6 |

| 2.3 | Simulation setup for pixel electronics                                     | 5 |

| 3.1 | Specifications for ATLAS vertex detector                                   | 1 |

| 4.1 | Specifications for HVMAPS25 ASIC                                           | 8 |

| 4.2 | Threshold dispersion                                                       | 6 |

| 5.1 | Different variants of CLIC/PANDA ASICs                                     | 9 |

| 5.2 | Tracking Detector of CLIC                                                  | 1 |

| 5.3 | Specifications for Micro-Vertex Detector for PANDA                         | 6 |

| 5.4 | Source amplitude correspond to input injection voltages 9                  | 9 |

| 5.5 | Threshold scan for the fast and slow comparators                           | 4 |

| A.1 | Rough comparison of displacement damage for several particles and energies |   |

|     | [18]                                                                       |   |

# 1 Introduction

This dissertation aims to present the development of Application Specific Integrated Circuits (ASICs) for scientific applications such as high energy physics and x-ray detection for medical application. The ASICs are used to build silicon pixel detectors.

Semiconductor detectors play a very important role in commercial applications and have experienced a rapid development in the last years. They are widely used in science such as elementary particle physics, optical and X-ray astronomy, nuclear physics, medicine and many other field. These applications demand extremely low-noise, low power, single-particle detection capability and some other properties such as 100 % fill factor, high time resolution, high readout speed, radiation tolerance as well as the precise measurement of energy and position of particles [10]. The development of intelligent semiconductor sensors in commercial complementary metal oxide semiconductor (CMOS) technologies is the focus of my work and also of our research group (KIT-ADL).

#### 1.1 My contribution

#### MAPS

Monolithic active pixel sensors (MAPS) in commercial high-voltage CMOS (HVCMOS) technology are one of our inventions. These monolithic ASICs have the potential to be the imaging lenses of current and future collider experiments consideration of many reasons [11]. They are one of the most advanced detectors for detecting high-energy particles. Examples of HVCMOS sensors are ATLASPix1, ATLASPix3, CLIC, HVMAPS25, etc. A monolithic pixel detector is essentially a system on chip (SoC). The sensor diode, analog and digital signal processing, storage, power regulation and test functions are implemented inside the same substrate. For some ASIC, the reverse bias up to -120 V could be achieved. The application of high voltage enhances the thickness of a depletion region and enlarges the active sensor volume. Following this idea, KIT-ADL develops HVCMOS pixel sensors in international collaboration.

My contribution to this invention was participation on ATLASPix1, ATLASPix3, and CLIC ASIC designs and design of LFoundary and HVMAPS25 sensors. Since the pixel electronic, readout cells, readout control unit (RCU) and pads are quite similar, I explain only the HVMAPS25 and the CLIC electronics, which are covered in chapter 4 and chapter 5. The concept of HVCMOS technology, general pixel electronics design, a special combination

between pixel electronics and readout cells, as well as some measurement results are presented.

#### Hybrid pixel detectors and CCPDs

Hybrid pixel detectors are another research theme that I followed. In the case of a standard hybrid pixel detector, each channel of a sensor chip and readout chip is connected via bump bond using flip-chip technology. Since the sensor and readout chip are separated, both can be tailored independently to meet the demands. In other word, the sensor can be optimized for radiation tolerance or for detection of x-rays, the readout chip can be made to process high particle hit rates of the order of  $MHz/mm^2$  [1].

The readout chip named MPROC for medical X-ray detection has been implemented and tested. The design details, the properties of CdTe material compared with silicon, noise analysis, crosstalk influence, several simulation as well as measurement results are describes in chapter 2.

I was also involved in the development of capacitvely coupled particle detector (CCPD). Compared with standard hybrid detectors, the signals are transferred through capacitive coupling instead of bump bonds. For this innovation, a new concept has been proposed without glue. The sensor chip and the readout chip are mechanically connected with a small number of relatively large bump bonds. The bumps provide mechanical stability to the detector and no double side wire bonding is needed.

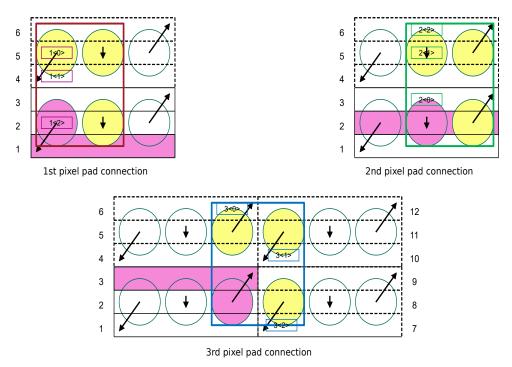

Two chips have been introduced in chapter 3 for proving the functionality of the new concept: CCPD53 sensor chip and PHOTON readout chip. The CCPD readout chip, which has not been produced, is also my contribution for this project. The design of CCPD53 sensor chip and PHOTON readout chip has been introduced with emphasis on special address encoding and arrangement of both chips.

Measurement setups, standalone sensor chip test, as well as both chip measurement results have been shown to prove the functionality of the new CCPD concept.

To summarize: Several developments have been introduced in my thesis. The developments can be classified as shown in figure 1.1. I have worked on a hybrid pixel readout ASIC for x-ray detection in medical imaging field. I have also worked on one hybrid pixel detector with new CCPD concept for high energy physics in ATLAS inner layer. Finally I developed monolithic pixel detectors with small and large diode sizes for particle detection.

#### Application and Requirements

Different applications lead to different requirements for the science-grade pixel sensors. In the case of high energy physics, pixel sensors are used to detect high-energy charged particles, more precisely to determine particle trajectories, their momenta and creation point [53]. Since particles tracking requires many layers of planar detectors, tracking sensors should be very thin and as transparent for particles as possible. Otherwise, the particles will be deflected by the inner-layers from their initial trajectories (multiple scattering) making impossible momentum, vertex and other measurements that require the data obtained by subsequent detector layers [2]. Silicon is the best material for such detectors since silicon-based technologies offer the possibility to implement any possible semiconductor device (from PN junction to the completed signal processing electronics) on the sensor. However, in the case of medical imaging, photon sensors should be thick enough to absorb the largest part of the radiation. Often another sensor material instead of silicon is chosen, due to its low absorption coefficient [33]. One example is CdTe material. X-ray detection is done in the CdTe pixel sensor. Since CdTe-based technologies do not allow implementation of electronic components, the sensor is connected to a silicon pixel readout chip.

Figure 1.1: Classification of pixel detectors according to applications and structures (covered in my thesis)

#### Comparison Hybrid versus Monolithic

Following factors should be taken into account to decide whether hybrid or monolithic structure is used: 1) spatial resolution. 2) radiation tolerance. 3) complexity of readout circuitry. 4) power consumption. 5) area and cost, etc. Some characteristics of monolithic and hybrid pixel detectors are listed [45]:

Monolithic

- Lower noise

- Lower power consumption because of a small sensor capacitance

- Lower material budget

- Smaller pixels, since electronics are designed outside of the charge collection region.

- Higher spatial resolution with simplified interconnections.

- Usually limited radiation hardness

- Numerous metal lines are needed for connection pixels and readout cells

#### Hybrid

- The choice of materials and technologies can be optimized depending on the applications.

- Higher readout speed, since the pixel signal are transmitted without multiplexing and they can be processed in parallel.

- Usually fully depleted sensors.

- Costly interconnection between sensor and electronics process (bump bonding).

- Material: sensor usually 200 250  $\mu \mathrm{m},$  electronics 100 200  $\mu \mathrm{m}$

- Spatial resolution is limited due to the sensor thickness and pixel size

- Higher power consumption due to a large sensor capacitance.

#### 1.2 Design Process

ASIC (Application Specific Integrated Circuit) design needs to be designed for the special needs of users, rather than intended for general-purpose use. According to different applications and customers, the challenge and requirements are quite different. Therefore, specific design ideas come into being for specific issues.

Figure 1.2: Full custom chip design process

Figure 1.2 presents the analog and full custom digital design flow.

The first step is to find a precise system architecture for a specific application. After that, pre-simulation step is indispensable. Even if the pre-simulation is not precise because for example, parasitic capacitances, cross talk, leakage currents are not considered, the fundamental functionality could be proved by this step. The layout is designed after that. In order to achieve compact, dense and short line routing, we need to optimize the layout in several steps. Voltage drops, crosstalk, shielding, antenna effects, matching should be taken into account. After both DRC (design rule check) and LVS (layout vs schematic) check passed, post-layout simulation is done. Cadence is suitable for the electrical simulation. For the readout architecture simulation, readout modelling environment (ROME) (designed by R. Schimassek, at KIT-ADL) [64] is normally applied for assess and optimize the overall architecture. This simulation framework was used to optimize the readout architecture of ATLASPIX chip. Our designs are produced by commercial vendors, for example: LFoundry, TSMC, AMS, TSI, UMC, etc. For different applications different production

technologies have been chosen. Before choosing a certain vendor, cost, production time, process characteristics, yield rate, should be considered.

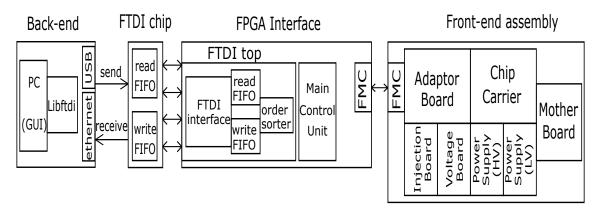

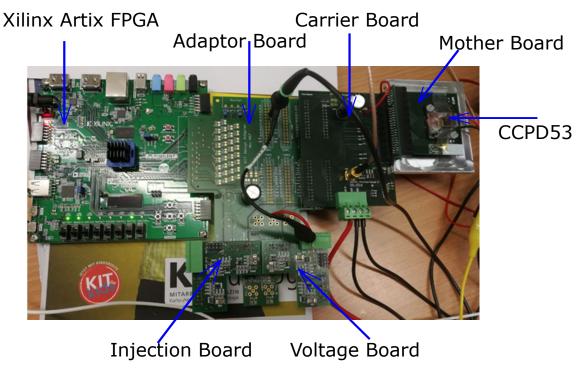

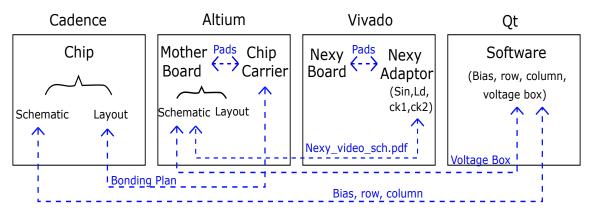

Figure 1.3: General experiment setup

Our test systems are based on test-PCB for the chip connected to adapter board (GECCO), connected to FPGA board, connected to PC (laptop) vias USB. The test-PCB is the carrier for the chip. The chip is directly bonded to the test-PCB. The test-PCB contains only passive components such as the PCI connector. It contains the bonding pads for the chip. The test-PCB is connected via PCI connector to the GECCO adapter board. GECCO board has an FMC connector for the FPGA board.

The GECCO system contains also firmware and software code written in Vivado and Qt. The code should be adjusted for different chips.

Figure 1.3 shows the general experiment setup. Laptop does data acquisition, storage and data analysis. Besides, it provides GUI and test environment. FPGA board performs data decoding and generate digital signals for ASIC. Oscilloscope measures and analysis the waveforms. Test PCB carries chip and routes power and signals. Power supply generates power supply voltages and some bias voltages. Test signals can be generated in many ways, for example, by charge injection via injection circuit, by radiation sources like 55Fe or 90Sr, by laser pulses, etc.

Typical measurements are: functional tests of all components in the signal chain, injection signal calibrations, pixel threshold measurements (threshold scan), threshold trimming, measurements of temporal and spatial resolution...

#### 1.3 HVCMOS Pixel Sensors

HVCMOS pixel sensors can be implemented in commercial CMOS technologies. A high voltage is used to increase the sensor volume, improve time resolution, detection efficiency and radiation hardness.

Unlike the standard MAPs structure, where the signals are generated in the epi-layer or undepleted lowly doped bulk and the charge is collected by diffusion, the signals of HVCMOS pixel sensors are generated in the depleted region and are collected mainly by drift because of the strong electrical field. Thus the detector is suitable for the applications where fast signals are needed.

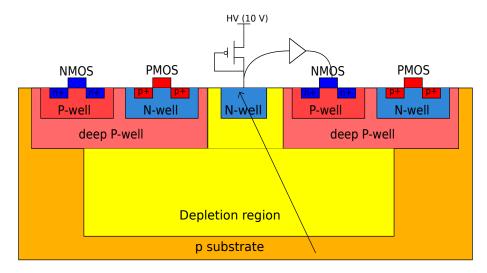

Figure 1.4: HVCMOS sensor

The HVCMOS sensor proposed here uses a lowly doped PN junction. The lower dopant concentration allows a higher reverse voltage bias than the typical PN junction in the standard CMOS process. The high negative bias voltage (up to -120V) is applied to p substrate.

The resistance of p-substrate depends on the doping concentration. It is typically 200  $\Omega$  for our design. Due to the high substrate resistivity, a depleted region up to 50  $\mu$ m can be achieved, which is one order of magnitude larger than that in a standard CMOS technology.

A high radiation tolerance is expected as well. Owing to the small charge collection distance (from p substrate to deep n-well), the possibility of charge trapping after radiation is decreased. HVCMOS prototypes have shown a radiation tolerance up to 100 MRad and 1 x  $10^{15}$  neq/ $cm^2$  with an efficiency of 99.7 % in test beam [14].

Both PMOS and NMOS transistors can be implemented in a pixel of a HVCMOS sensor. The PMOS transistors are placed in the shallow n-well, which are obmically connected with the deep n-well, the NMOS transistors are in the p-well which is inside the deep n-well. The deep n-well plays two roles. First, it is used for the charge collection. Second, the deep n-well is the substrate for PMOS transistors placed in it.

The pixel with deep n-well are arranged as matrix, their depleted region in this case partially overlap. When the particle hits the pixel, the charge below or between the n-wells will be collected to the nearest n-well. The pixel detector has therefore 100 % fill factor.

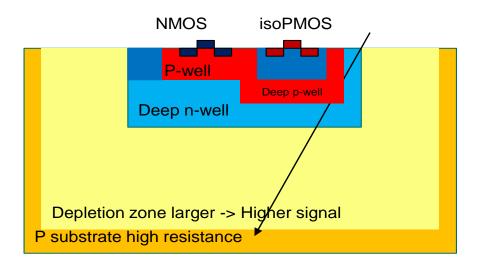

#### Modified HVCMOS Process with a implant deep P-well

Two improvements of HVCMOS sensor have been tested within this thesis: 1) implant a deep p-well and 2) to use a small charge collection electrode. Additionally a high resistivity

substrate of 200  $\Omega$ cm has been applied. This leads to a larger depletion region for a given reverse bias, which decreases detector capacitance, ensures low noise and increases input signal in the case of charged particle detection.

The deep p-well is implanted between the n-well and the deep n-well and is used to isolate PMOS transistor from the n-well. This structure is very helpful to reduce crosstalk from electronics to sensors. This is important when we have big amplitude of output signals. Deep p-well has been used in several designs presented in this thesis.

Figure 1.5: Modified HVCMOS senosor with a deep P-well implant

Figure 1.6: Modified HVCMOS senosor with small charge collection electrode

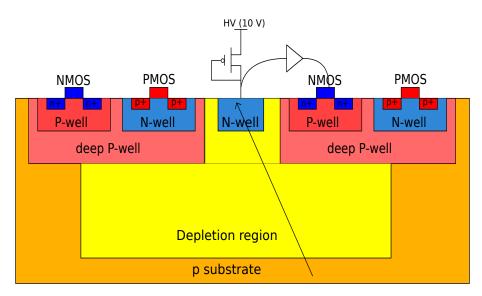

#### Modified HVCMOS Process with small charge collection electrode

Fig. 1.6 shows the modified HVCMOS sensor with small charge collection electrode (n-well). The electrode is biased to typically 10V. The sensor substrate is partially depleted. The pixel electronics is surrounded by a deep p-well that acts as potential barrier for electrons. In this way, the signal charge drifts towards charge collection electrode. The advantages of this design are: smaller input node capacitance and less crosstalk from electronics to sensor.

#### 1.4 Silicon detector

The working principle of a silicon detector is charge generation in silicon. Electron-hole pairs are generated when energy is deposited by charged particles or photons in the silicon substrate. The movement of charge towards the electrodes generates a signal.

The ionization energy of silicon is 3.6 eV, this means that per 3.6 eV deposited energy one electron-hole pair is generated.

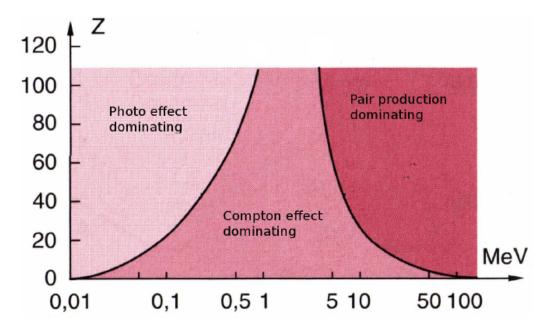

The mechanism of energy deposition depends on particle type. In the case of charged particles, the most important mechanism is interaction through electric field. In the case of photons, it is photo effect, Compton effect or pair production. High energy charged particles usually pass through the sensor and generate signal that is proportional to sensor thickness. The charge generated by a minimum ionizing particle is about 75 electron-hole pairs per  $\mu$ m path length in silicon.

#### Why do we need a large depletion region

Most silicon particle detectors are based on depleted PN junctions.

The electron hole pairs generated by particles within the depletion region are separated by electric field. This leads to a strong and fast signal.

A large depletion region is preferable from several reasons.

The depletion depth must be large enough in order to produce signals larger than noise level. These events are then detected with almost 100 % efficiency.

If a the response of semiconductor detector should be perfectly linear with energy, the depletion region should be sufficiently thick to completely stop all particles. Otherwise, a nonlinear response could be expected since the full energy is not totally deposited in the sensitive volume [17].

Furthermore, the depletion region behaves like a capacitor ( $\epsilon A=d$ ), since charges are built up on either side of the PN junction. Thus, the value of the capacitance is inversely proportional to the depletion width [18].

#### How to achieve large depletion region

The approximate formulas for the width of the n side and p side of the depletion layer are [19]:

$$x_n = \sqrt{\frac{2\epsilon_{Si}}{qN_D(1+N_D/N_A)}(\phi_0 - V_0)}$$

(1.1)

$$x_p = \sqrt{\frac{2\epsilon_{Si}}{qN_A(1 + N_A/N_D)}}(\phi_0 - V_0)$$

(1.2)

The total width of the depletion region is:

$$x_d = x_n + x_p = \sqrt{\frac{2\epsilon_{Si}}{q}(\frac{1}{N_A} + \frac{1}{N_D})(\phi_0 - V_0)}$$

(1.3)

If one side is more heavily doped than the other, the depletion zone will extend farther into the lighter doped side.

For example,  $N_D \gg N_A$ , then  $x_p \gg x_n$ . In other words, the depletion region is almost entirely on the p side of the junction. In our case, a shallow and highly doped n+ implant (n-well) in a low doped bulk realizes silicon sensor. Therefore, the term  $1/N_D$  in equation 1.3 can be neglected.

$$x_n \approx x_n = \sqrt{\frac{2\epsilon_{Si}}{qN_A}(\phi_0 - V_0)} \tag{1.4}$$

Thus equation 1.4 is widely used for calculating the depletion depth.

There are two methods to enlarge the width of the depletion region analysed from equation 1.4. A higher resistivity material is necessary, which means using higher purity semiconductors or compensated material to improve the density of  $N_A$  or  $N_D$ .

Moreover, a reverse bias voltage will have the effect of attracting the electrons in the n-region away from the junction towards the n contact and similarly for the holes in the p-region.

The higher the external voltage, the wider the depletion zone.

However, a higher external voltage brings a greater risk of breakdown. The maximal voltage which can be applied is limited by the resistance of the semiconductor.

#### **1.5 Detector Electronics**

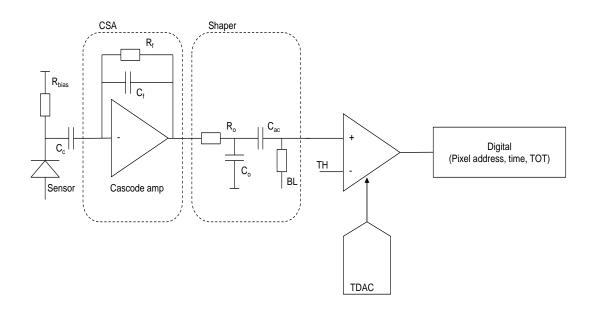

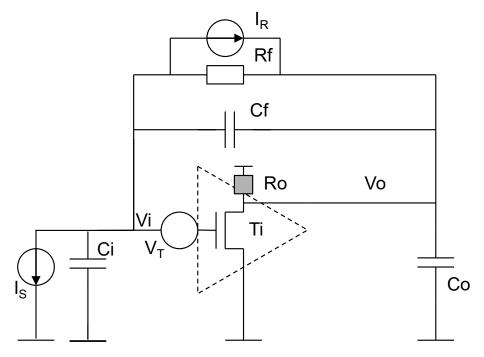

A general front end circuit of a particle detector chanel usually consists of a charge sensitive amplifier (CSA), a shaper, a comparator followed by digital processing cell.

Figure 1.7: Detector electronics

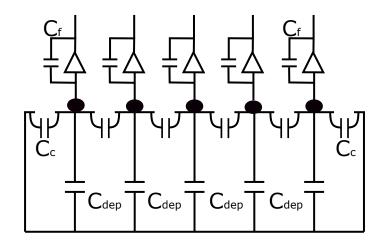

The sensor is represented as a reversely biased PN junction - the diode symbol in the figure. The electrons generated by particle are collected by the cathode of the diode. The signal charge is integrated in the CSA. The voltage step pulse at the output of the amplifier is proportional to the amount of the charge collected in the sensor and inversely proportional to the feedback capacitance  $C_f$ , which is discharged by a continuous rest. Moreover, the continuous rest architecture is also suitable for the leakage current compensation, if necessary.

In the case of HVCMOS sensors, we usually connect the CSA and the sensor by AC-coupling (device  $C_c$  in figure). In this case we use the bias element  $R_{bias}$ .

A shaper follows the CSA, which is responsible for shaping the step voltage generated form CSA according to the timing requirements of the application. The shaper usually acts as a combination of low pass and high pass filter. Both filters reduce noise. Moreover, the pulse duration is usually shortened by high pass filter in order to reduce pile-up of subsequent events.

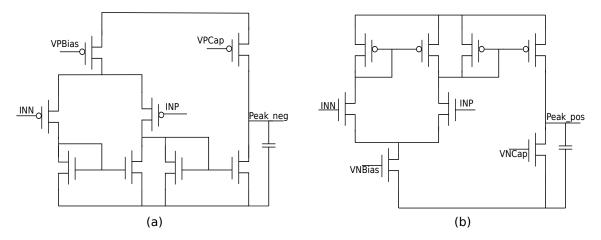

To digitize the signal, the output of a shaper is fed to a comparator. In this thesis different types of comparators were implemented, NMOS- and CMOS comparator.

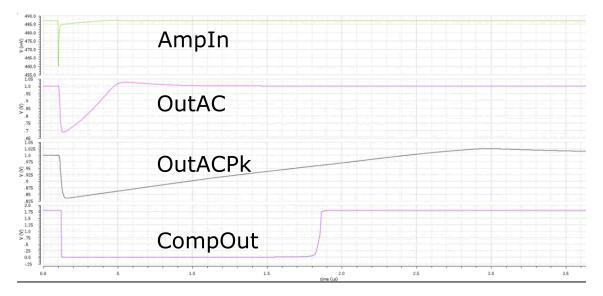

Additionally, a local threshold tune could be applied by an on-pixel DAC, controlled by configuration bits, in order to compensate for the pixel-to-pixel threshold difference, generated from several reasons, for example, power supply voltage drops, transistor mismatch, etc.

Different methods could be used to readout the output of the pixel. It can be directly readout, or stored in a local memory for further processing.

In the case where the signal is processed using digital logic implemented in the chip, the logic can be placed in pixel or in the periphery.

In case of monolithic detector, the digital logic is located in the chip periphery for the purpose of reducing crosstalk from electronics to charge collection electrode. However, numerous lines are needed to connect each pixel to its readout cell. Time delay and parasitic capacitance between two metal layers should be taken into account.

In case of hybrid detector the readout logic are normally designed in pixel. Complex line connection is avoided, however each pixel amplifier should be connected to its bump bond pad implemented in top metal layer.

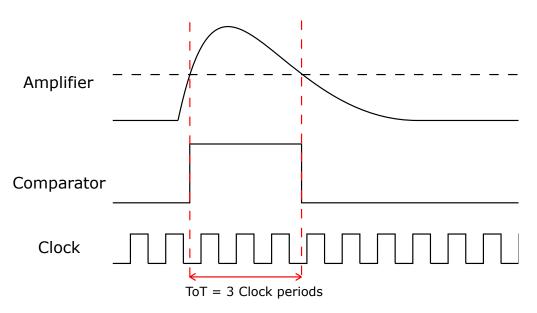

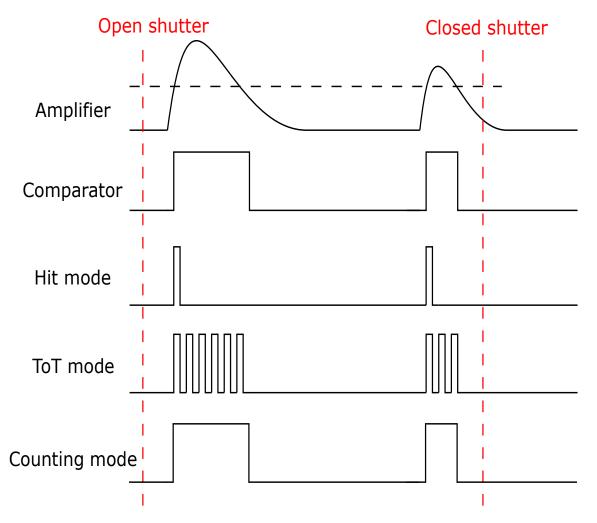

The information of the hit includes hit position, hit time and hit energy usually measured as time over threshold (ToT).

The spatial resolution of the detector depends on the pixel pitch and some other factors such as the charge sharing between neighboring pixels and the selected readout architecture. Binary readout is the simplest case, where the only information stored in the pixel is whether a hit was detected or not. The spatial resolution of a detector with binary readout is given by equation, where p is the pixel pitch [3].

$$\sigma_{position} = \frac{p}{\sqrt{12}} \tag{1.5}$$

To improve the spatial resolution and obtain more information about the timing and energy of the detected particle, ToT method is applied. The amount of time is proportional to the amount of charge generated in the sensor.

By knowing the information of the signal energy, the charge sharing can be studied. Analysing the amount of charge detected by each pixel at an event where the signal is induced to two or more neighbor pixels, can provide more information on the position of the hit, thus achieving sub-pixel spatial resolution.

Figure 1.8: Time diagram that describes ToT measurement

#### 1.6 Charge Sensitive Amplifier

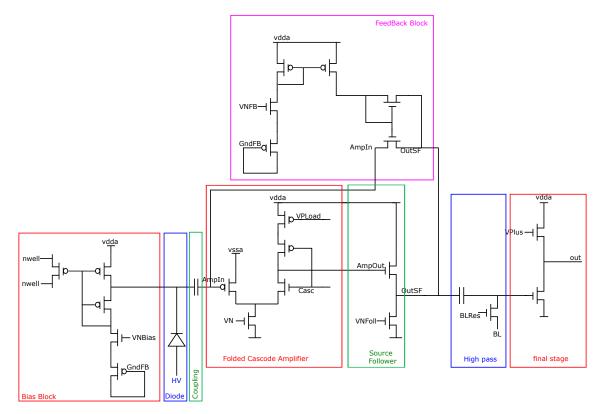

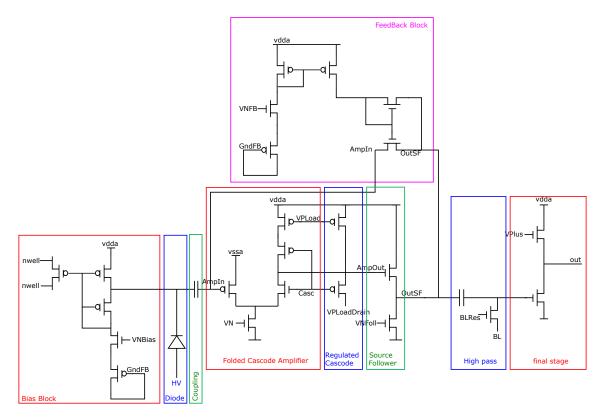

Transistor level schematics of a typical charge sensitive amplifier CSA used in this work is shown in fig. 1.9. The CSA contains of following blocks: folded cascode amplifier, feedback block, bias block, source follower, high pass filter and output amplifier stage. The folded cascode amplifier is used as the active part of CSA.

Figure 1.9: Transistor level schematic of the amplifier

#### 1.6.1 Folded Cascode Amplifier

Figure 1.9 shows the transistor level schematic of the folded cacode amplifier, which is a common choice for low-voltage and high gain amplifier.

A source follower is used as the output stage. It provides fast time constant and shifts voltage level. A quiet analogue supply VSSA is used to alleviate the impact of supply voltage fluctuation on CSA.

Current mirror in bias DAC at chip periphery is applied to provide the bias voltages VN and VPLoad. It makes sense to keep IPLoad relatively small and INBias large because IPLoad flows through the load PMOS transistor and the NMOS cascode. INBias flows through the NMOS bias source. The difference INBias - IPload flows through the input transistor. For a large  $g_m$ , the bias current (DC current) through the input transistor must be large. For a large load resistance, the bias current through load transistor must be small. Therefore, to some extent, the smaller the current IPLoad, the better. A good choice is normally IPload = 10 % INBias.

#### 1.6.2 Continuous reset and rising time optimization

The feedback capacitance  $C_f$  should be reset after each signal.

An NMOS transistor is chosen for the feedback device, because the input of the CSA has negative polarity and it generates a positive output pulse. The output and input potential of the CSA are equal in the stationary state. When the output pulse gets higher than few thermal voltages Ut, the current of feedback transistor saturates. The feedback capacitor is thus discharged by constant current, the output pulse has approximately a triangular shape. This feature can be used for the digitization of the output signal amplitude by measuring ToT.

The response function of CSA with feedback is given by equation (1.6 - 1.8). Factor gm is the transconductance of the input transistor,  $C_i$  and  $C_o$  are the capacitances of the input and output respectively and  $C_f$  is the feedback capacitance. Normally  $T_f$  is 10 times bigger than  $T_r$ .

$$A_{FB} = \frac{A_{in}A_{oL}}{1 - \beta AoL} = \frac{-1}{(s\tau_f + 1)(s\tau_r + 1)}$$

(1.6)

$$\tau_f = R_f C_f \tag{1.7}$$

$$\tau_r = R_o \frac{C_i C_f + C_f C_o + C_i C_o}{A C_f} \tag{1.8}$$

A short rise time  $T_r$  is essential for high time resolution and count rate. In order to reduce rise time and avoid time walk, increasing  $g_m$  and  $C_f$  or decreasing  $C_o$  are helpful, as seen from equation 1.8. Unfortunately increasing  $g_m$  is not always feasible because the transconductance is proportional to the DC current that flows through the input transistor of the CSA in the stationary state, given by equation 1.9. A higher bias current leads to a higher power dissipation, which is a problem.

$$g_m = \frac{I_D}{V_{gs}} = \frac{I_D}{nU_T} \tag{1.9}$$

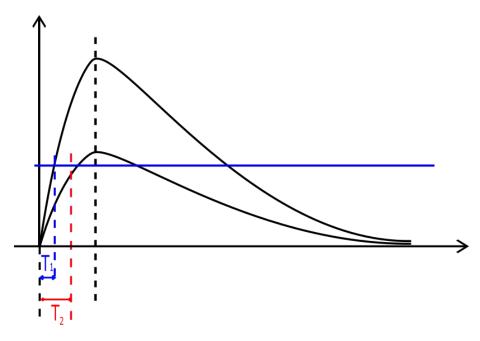

#### 1.7 Time Walk

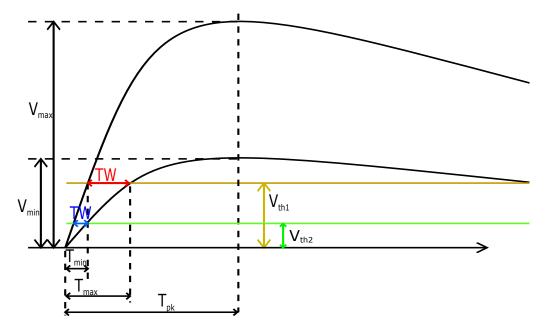

The output signal of the pixel amplifier is electronically compared with a threshold potential. The comparison is done by the circuit called comparator. A high time resolution required in most of particle detectors. For example, in the particle physics experiments at the LHC, hits must be associated to one particle bunch crossing with a precision better than 25 ns. Time resolution is to a large extent limited by the time walk, which is an effect caused by the fluctuation of the input charge signal. Figure 1.10 shows the time walk of two input signals and for two pixels with different thresholds. Vmin and Vmax are the minimum and maximum signal amplitude at the output of the amplifier. Vth1 and Vth2 are the random values of threshold. Tpk is the peak time. Tmin and Tmax are the minimum and maximum times of the signal crossing the threshold (Vth1). Hence, the difference between them is defined as time walk (TW), which can be estimated geometrically and expressed by the following equation [62].

$$TW = t_{max} - t_{min} = T_{pk} \left( \frac{V_{th}}{V_{min}} - \frac{V_{th}}{V_{max}} \right)$$

(1.10)

Intuitive analysis from equation 1.10 and figure 1.10 shows that either decreasing the signal rise time or decreasing the threshold value should be done for the purpose of ensuring the time walk smaller than 25 ns.

Shorter peak time is in favor of reducing time walk, which means fast rising time of the signal is required. Equation 1.8 shows that a larger value of  $C_f$  and smaller value of  $C_o$  are in favor of fast signal.

Additionally lower threshold value is also good for reducing time walk, which are demonstrated with red and blue color in figure 1.10. Shorter time walk corresponds to lower threshold. However, considering the influence of threshold dispersion, the minimal threshold value is limited.

Therefore, the threshold should be carefully adjusted that should not be too high to ensure low time walk and also not too low to avoid electronic noise.

Figure 1.10: Time walk definition and time walk of two input signals for different threshold values

We can deal with time walk effect in several ways [12]:

Using the peak height, the actual time of hit can be calculated. The signal height can be measured directly or by taking the time over threshold (ToT) into account.

A thicker depletion zone increases signals, reducing the time walk effect.

#### 1.7.1 Noise analysis in Charge Sensitive Amplifier

Figure 1.11 shows the equivalent circuit for the calculation of the nose at the output of the amplifier. The MOSFET thermal and flicker noise, the sensor shot noise and the Rf resistor thermal noise have largest contributions.

The total noise power is the sum of individual contributions.

$$\langle v_o^2 \rangle = \int_0^\infty (S_{IR}(f)|H_{IR}(jw)|^2 + S_{VT}(f)|H_{VT}(jw)|^2 + S_{IS}H_{IS}(jw))df$$

(1.11)

Figure 1.11: Noise sources in charge sensitive amplifier with feedback

Thermal noise of a resistor can be modeled by a parallel connection of current source and resistor. The spectral power density of feedback resistance  $R_f$  is:

$$S_{IR} = \frac{4kT}{R_f} \tag{1.12}$$

The transfer function from source  $I_R$  to amplifier output is:

$$H_{IR}(jw) = -Z_f = \frac{R_f}{1 + sR_fC_f}$$

(1.13)

The output noise (square mean value) caused by source  $I_R$  is:

$$\langle v_{oIR}^2 \rangle = \int_0^\infty \frac{4kT}{R_f} |\frac{R_f}{1+sR_fC_f}|^2 df$$

$$= \frac{4kTR_f}{2\pi} \int_0^\infty |\frac{1}{1+s\omega R_fC_f}|^2 df$$

$$= \frac{4kTR_f}{2\pi} \frac{\pi}{2} \frac{1}{R_fC_f}$$

$$= \frac{kT}{C_f}$$

$$(1.14)$$

MOS transistors exhibit thermal noise with the most significant source being the noise generated in the channel. The noise of the transistor can be modeled either with the current source between drain and source or with a voltage source at the gate.

Since for gate voltage Vg, a drain source current gm x Vg is generated, and since the power density is proportional to the square of the voltage, following applies:

$$S_{VT} = \frac{S_{IT}}{g_m^2} = \frac{4kT^2/3}{g_m}$$

(1.15)

Transfer function from source  $V_{T}$  to amplifier output is:

$$H_{VT}(jw) = \frac{1 + jw\tau_z}{(1 + jw\tau_r)(1 + jw\tau_f)}$$

(1.16)

with the time constants:

$$T_r = \frac{C_i C_o + C_i C_f + C_o C_f}{C_f g_m}$$

(1.17)

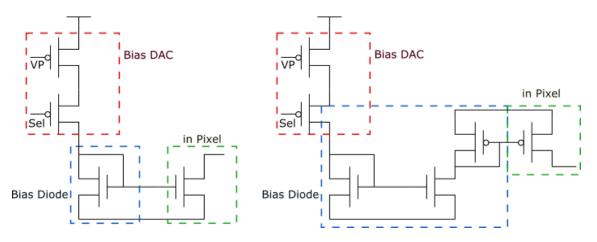

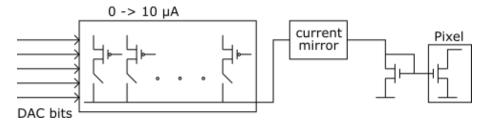

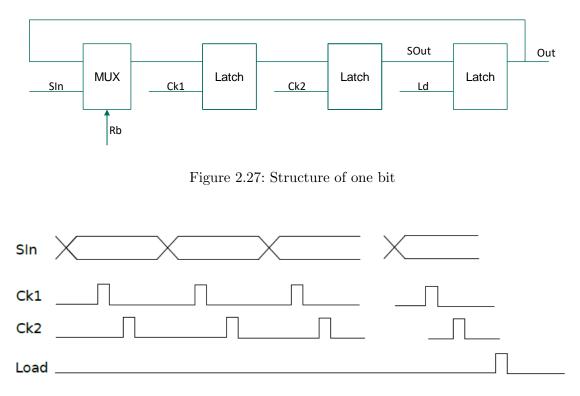

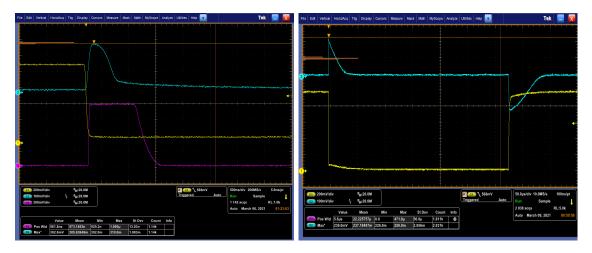

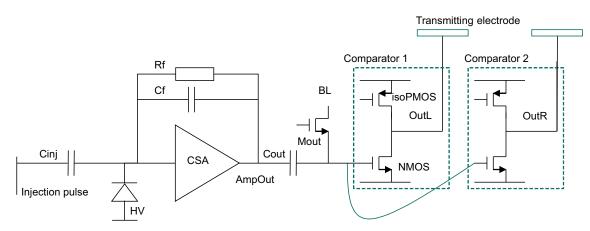

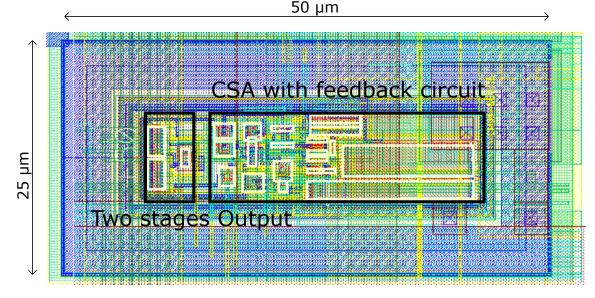

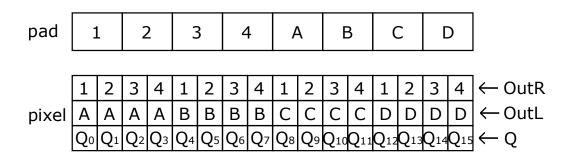

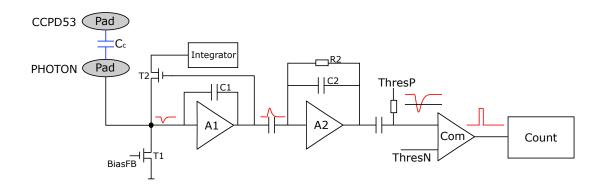

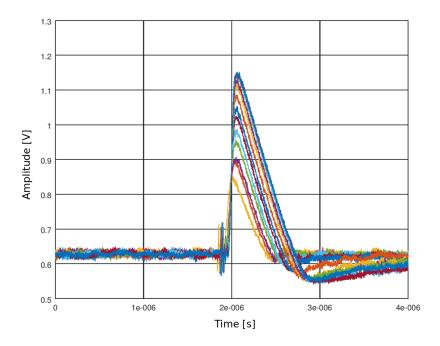

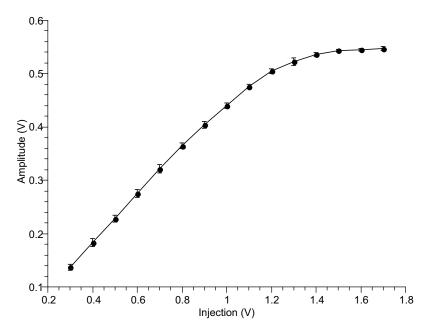

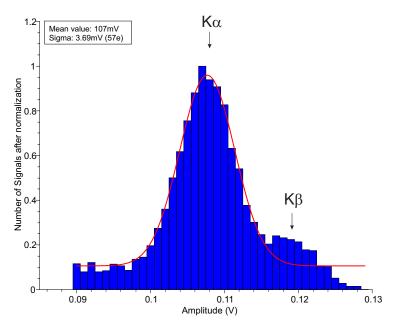

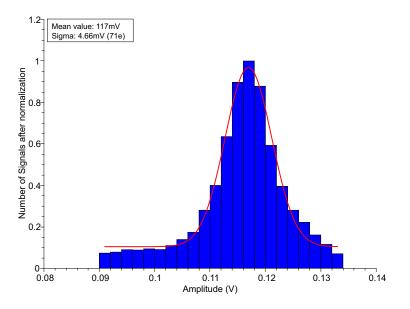

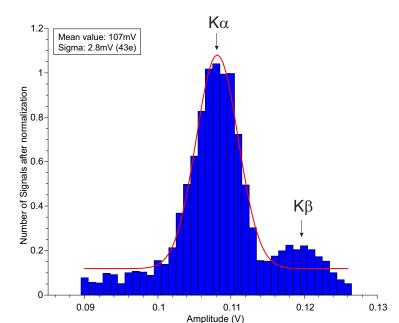

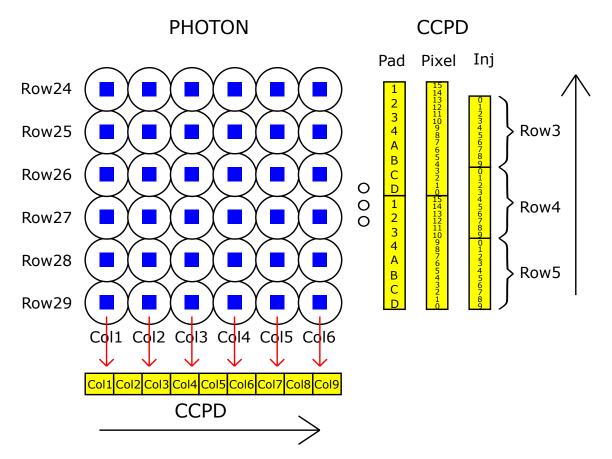

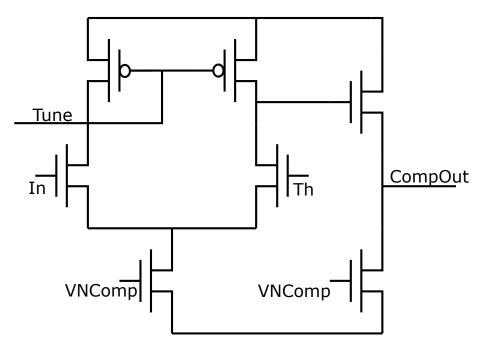

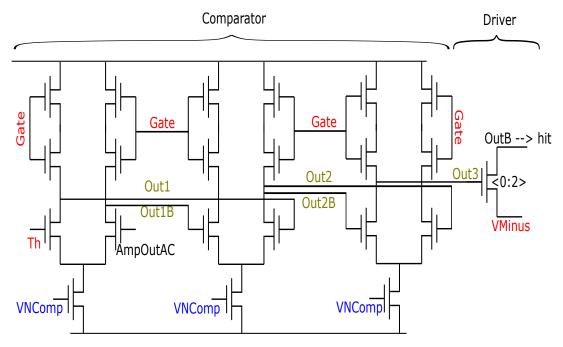

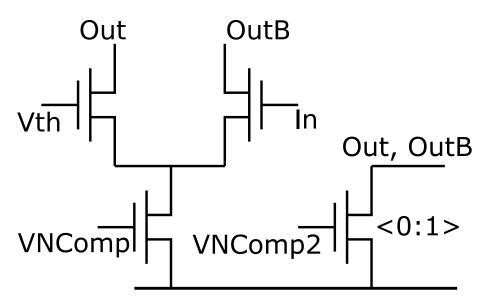

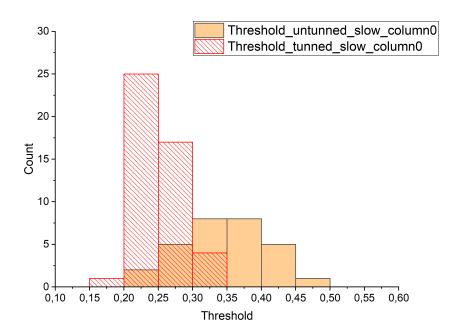

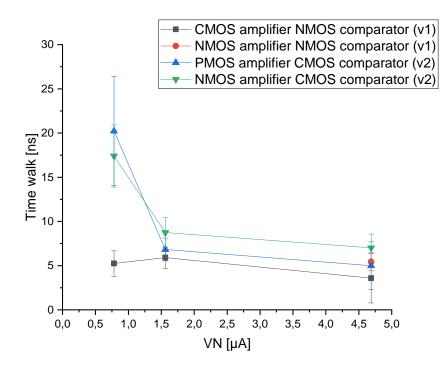

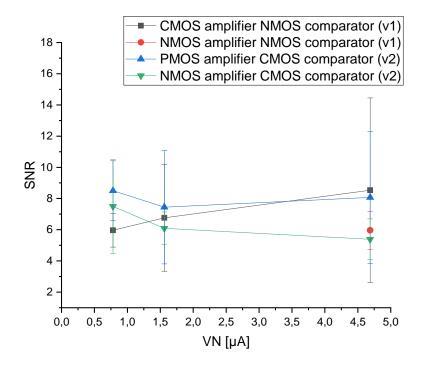

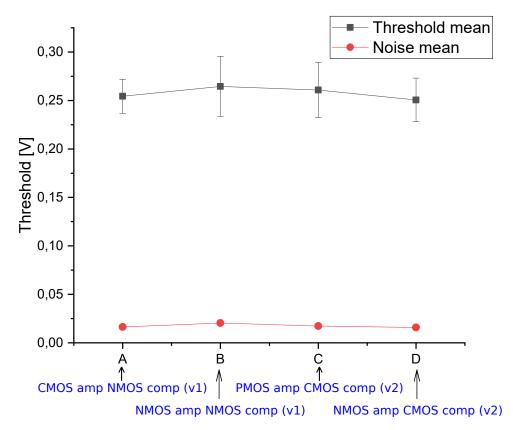

$$T_f = R_f C_f \tag{1.18}$$