# Low-Latency Track Triggering in High-Energy Physics

Zur Erlangung des akademischen Grades eines

DOKTORS DER INGENIEURWISSENSCHAFTEN (DR.-ING.)

von der KIT-Fakultät für Elektrotechnik und Informationstechnik des Karlsruher Instituts für Technologie (KIT)

genehmigte

**DISSERTATION**

von

Luis Eduardo Ardila Pérez, M.Sc.

geboren in Bogotá, Kolumbien

Tag der mündlichen Prüfung: 29.10.2021 Haupreferent: Prof. Dr. rer. nat. Marc Weber

Korreferent: Prof. Dr.-Ing. Dr. h. c. Jürgen Becker

This work is licensed under a Creative Commons "Attribution-NonCommercial-ShareAlike 4.0 International" license.

### **Abstract**

The Compact Muon Solenoid (CMS) is a general-purpose experiment at the Large Hadron Collider (LHC) designed to study a wide variety of high-energy physics phenomena. It employs a large silicon tracker within a homogeneous  $3.8\,\mathrm{T}$  magnetic field, which allows the precise measurement of the trajectories, including transverse momentum ( $p_{\mathrm{T}}$ ) and vertex position reconstruction of the charged particles emerging from the LHC collisions.

The High Luminosity (HL) upgrade of the LHC in 2025 will increase the simultaneous proton-proton collisions from the current average of 25 to up to 200 every 25 ns. The upgrade will completely replace the silicon tracker with one purposely built to discriminate on-module the charged particles whose  $p_{\rm T}$  is larger than 2 GeV, these hits are called 'stubs'. The stubs are forwarded to off-detector electronics for real-time track reconstruction under 4  $\mu$ s of latency. For the first time in any particle physics experiment, the reconstructed tracker primitives will be included in the first-level trigger with the aim of maintaining the trigger rate of CMS below 750 kHz.

This thesis describes various firmware and hardware developments for a real-time all FPGA-based track finder that employs a regionally segmented and fully time-multiplexed architecture. The Time-multiplexed Track Trigger (TMTT) reconstruction algorithm has four processing stages, two of which were implemented in Hardware Description Language (HDL) by the author and are detailed in this dissertation. Optimizations of such algorithms for increased clock frequency operation and resource utilization optimization are also presented. In addition, the development of specialized hardware utilizing the Advanced Telecommunications Computing Architecture (ATCA) form factor will be presented. The board has sufficient high-speed I/O to be used at the HL CMS tracker off-detector processing system. It implements a novel slow-control solution for ATCA systems by combining the Intelligent Platform Management Controller (IPMC), a Linux slow-control software, and an FPGA for custom slow-control tasks in a single Zynq Ultrascale+ (US+) System-on-Chip (SoC) module.

# Zusammenfassung

Das Compact Muon Solenoid (CMS) ist ein Experiment am Large Hadron Collider (LHC), mit dem eine Vielzahl von Phänomenen der Hochenergiephysik untersucht werden soll. Es verwendet einen großen Silizium Spurdetektor innerhalb eines homogenen 3,8 T -Magnetfelds, der die genaue Messung der Trajektorien, des Transversalimpulses ( $p_{\rm T}$ ) und die Rekonstruktion der Scheitelposition der geladenen Teilchen aus den LHC-Kollisionen ermöglicht.

Die Aufrüstung des LHC für hohe Luminosität (HL) im Jahr 2025 wird die Zahl der gleichzeitigen Proton-Proton-Kollisionen von derzeit durchschnittlich 25 auf bis zu 200 alle 25 ns erhöhen. Bei der Aufrüstung wird der Silizium Spurdetektor vollständig durch einen ersetzt, der speziell dafür gebaut wurde, die geladenen Teilchen auf den Modulen zu selektieren, deren  $p_{\rm T}$  höher als 2 GeV ist. Die Informationen dieser Treffer werden an eine Off-Detektor-Elektronik zur Echtzeit-Spur-Rekonstruktion mit einer Latenz von 4 µs weitergeleitet. Die rekonstruierten Tracker-Primitive werden erstmalig in einem Teilchenphysikexperiment in die First-Level-Trigger-Entscheidung einbezogen, mit dem Ziel, die Triggerrate von CMS unter 750 kHz zu halten.

In dieser Doktorarbeit werden verschiedene Firmware- und Hardware-Entwicklungen für einen FPGA-basierten Echtzeit-Spurensucher vorgestellt, der eine räumlich segmentierte und vollständig zeitmultiplexierte Architektur verwendet. Der Time-multiplexed Track Trigger (TMTT)-Rekonstruktionsalgorithmus enthält vier Verarbeitungsstufen, von denen zwei vom Autor in Hardwarebeschreibungssprache (HDL) implementiert wurden und in dieser Dissertation detailliert beschrieben werden. Optimierungen solcher Algorithmen, zur Erhöhung der Taktfrequenz und zur Reduktion der Ressourcennutzung, werden ebenfalls vorgestellt. Darüber hinaus wird die Entwicklung spezieller Hardware auf Basis des ATCA-Formfaktor (Advanced Telecommunications Computing Architecture) vorgestellt. Das Board verfügt über ausreichend Hochgeschwindigkeits-I/O für den Einsatz im HL CMS Tracker Off-Detector Processing System. Es implementiert eine neuartige

Slow-Control-Lösung für ATCA Systeme, die den Intelligent Platform Management Controller (IPMC), eine Linux Slow-Control-Software und einen FPGA für anwendungsspezifische Slow-Control-Aufgaben in einem einzigen Zynq Ultrascale+ (US+) System-on-Chip (SoC)-Modul integriert.

# Acknowledgments

I would like to take this opportunity to express the deepest appreciation to everyone who contributed to the development of this Thesis. I wish to specially thank my supervisors Prof. Marc Weber and Prof. Jürgen Becker for providing me with the opportunity to work on this challenging, yet very rewarding project. I would like to thank my receiving supervisors at RAL Claire Shepherd and Ian Tomalin, for providing an excellent working environment and for keeping the team highly motivated with the enjoyable and educational friday's pub visit. I want to thank Michele Caselle for his early guidance and introduction to the CMS tracker working group and for his unreserved enthusiasm and stimulus. I want to thank Oliver Sander for the countless hours we spent debugging the system at the beat of the crate-fans at CERN and for the unconditional support and encouragement in almost every aspect. I thank Matthias Balzer for his prompt assistance, specially during the writing of this thesis. I wish to thank Mark Pesaresi for providing me with valuable advises and trusting in my abilities, your encouragement was unquestionably motivating. I thank Greg Iles for the numerous discussions and insights about high-speed optical transceivers, as well as the nitty-gritty detailed suggestions related to FPGA time closure, for always receiving me with a warm welcome and never hesitating in providing what was needed when I visited your lab. I must thank the staff members at KIT Denis, Michael, Uwe and Alex for sharing your valuable expertise and allowing me to learn from you. I want to thank my KIT colleagues Lorenzo, Marvin, Meghana, Nick, Patrick, Timo, Thomas, and Torben for their careful and persistent work effort and for their friendship. I also wish to thank my colleagues at RAL Luigi, Davide, Kostas and Tom for always being diligent when questions arose and for their friendship. I thank Brian and Sven for the interesting discussions which fostered new research directions for the future. Last but not least, I would like to thank Belen for her wholeheartedly loving support and encouragement, specially when things were complicated, and to my family for their immense multivalent guidance which motivates me to go further every day.

This research acknowledges the support by the DFG-funded Doctoral School "Karlsruhe School of Elementary and Astroparticle Physics: Science and Technology"

The research leading to these results has received funding from the People Programme (Marie Curie Actions) of the European Union's Seventh Framework Programme FP7/2007-2013/ under REA grant agreement  $n^{\circ}$  [317446] INFIERI "INtelligent Fast Interconnected and Efficient Devices for Frontier Exploitation in Research and Industry"

## **Declaration**

I declare that I have developed and wrote the enclosed thesis entirely by myself, and that I did not use any sources or means that were not explicitly stated in the text. The algorithms and firmware developments in Chapter 4 are collaborative efforts of the community which led to the publications [1], [2] and the results shown in Chapter 6. My specific contributions to the TMTT algorithm and its firmware development are highlighted in Chapter 5. In a similar way Chapter 7 describes the overall community efforts related to the back-end hardware system and my specific contributions to the hardware R&D are highlighted in Chapters 8 and 9.

# **Contents**

| Al              | Abstract                          |         |                                       |    |  |  |  |  |

|-----------------|-----------------------------------|---------|---------------------------------------|----|--|--|--|--|

| Zusammenfassung |                                   |         |                                       |    |  |  |  |  |

| 1               | Introduction                      |         |                                       |    |  |  |  |  |

| 2               | The CMS experiment at the LHC     |         |                                       |    |  |  |  |  |

|                 | 2.1                               | The La  | arge Hadron Collider (LHC)            | 3  |  |  |  |  |

|                 | 2.2 Experimental sites at the LHC |         |                                       |    |  |  |  |  |

|                 | 2.3                               | The C   | ompact Muon Solenoid (CMS) Experiment | 7  |  |  |  |  |

|                 |                                   | 2.3.1   | Coordinate System                     | 9  |  |  |  |  |

|                 |                                   | 2.3.2   | The solenoid                          | 10 |  |  |  |  |

|                 |                                   | 2.3.3   | Silicon tracker                       | 10 |  |  |  |  |

|                 |                                   | 2.3.4   | Calorimeter                           | 12 |  |  |  |  |

|                 |                                   | 2.3.5   | Muon system                           | 16 |  |  |  |  |

|                 |                                   | 2.3.6   | Trigger and Data Acquisition          | 17 |  |  |  |  |

| 3               | Hig                               | h-lumi: | nosity LHC                            | 21 |  |  |  |  |

|                 | 3.1                               |         | es Motivation                         | 22 |  |  |  |  |

|                 | 3.2                               | •       |                                       |    |  |  |  |  |

|                 |                                   | 3.2.1   | Insertion region magnets              | 23 |  |  |  |  |

|                 |                                   | 3.2.2   | Collimation                           | 24 |  |  |  |  |

|                 |                                   | 3.2.3   | Crab cavities                         | 25 |  |  |  |  |

|                 | 3.3                               | The C   | MS Upgrade                            | 25 |  |  |  |  |

|                 | 3.4                               |         | MS Tracker Upgrade                    | 29 |  |  |  |  |

|                 |                                   | 3.4.1   | Requirements                          | 29 |  |  |  |  |

|                 |                                   | 3.4.2   | The Inner Tacker                      | 31 |  |  |  |  |

|                 |                                   | 3.4.3   | The Outer Tacker                      | 32 |  |  |  |  |

|                 | 3.5                               | Track   | Finding at the Level-1 Trigger        | 34 |  |  |  |  |

| 4               | The                               | Track l | Finding Algorithms                    | 37 |  |  |  |  |

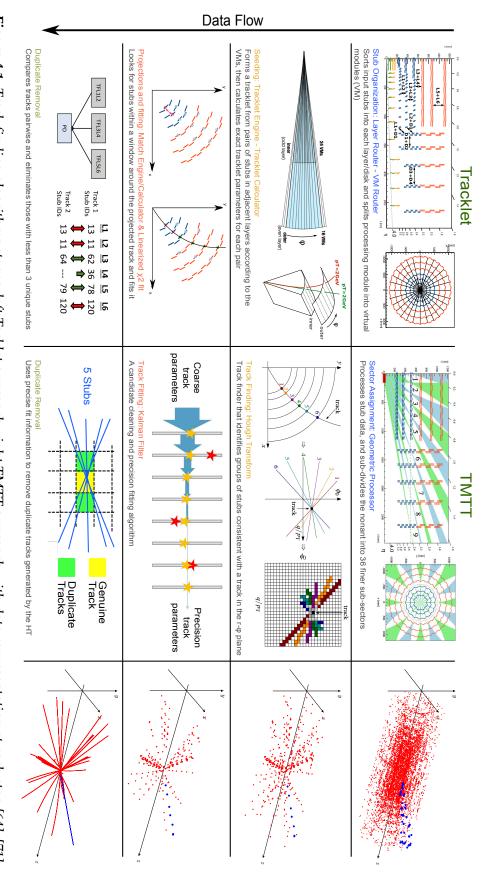

|                 | 4.1                               |         | racklet approach                      | 37 |  |  |  |  |

XII CONTENTS

|   |                                        | 4.1.1 Stub Organization: Layer Router - VM Router             | 38 |  |  |  |  |

|---|----------------------------------------|---------------------------------------------------------------|----|--|--|--|--|

|   |                                        | 4.1.2 Seeding: Tracklet Engine - Tracklet Calculator          | 38 |  |  |  |  |

|   |                                        | 4.1.3 Projections: Match Engine - Match Calculator            | 38 |  |  |  |  |

|   |                                        | 4.1.4 Fitting: Linearized $\chi^2$ fit                        | 39 |  |  |  |  |

|   |                                        | 4.1.5 Duplicate Removal: Purge Duplicate                      | 39 |  |  |  |  |

|   | 4.2                                    | The Time-Multiplexed Track Trigger (TMTT) approach            | 40 |  |  |  |  |

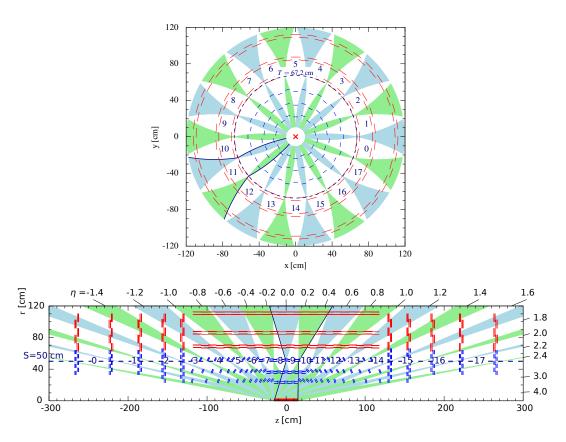

|   |                                        | 4.2.1 Sector Assignment: Geometric Processor                  | 40 |  |  |  |  |

|   |                                        | 4.2.2 Track Finding: Hough Transform                          | 41 |  |  |  |  |

|   |                                        | 4.2.3 Track Fitting: Kalman Filter                            | 42 |  |  |  |  |

|   |                                        | 4.2.4 Duplicate Removal                                       | 43 |  |  |  |  |

|   | 4.3                                    | The Hybrid approach                                           | 43 |  |  |  |  |

|   | 4.4                                    | Summary                                                       | 46 |  |  |  |  |

| 5 | Track Finder Algorithm Contributions 4 |                                                               |    |  |  |  |  |

|   | 5.1                                    | The TMTT Geometric Processor (GP)                             | 47 |  |  |  |  |

|   | 5.2                                    | The Duplicate Removal Algorithms for the TMTT approach        | 56 |  |  |  |  |

|   |                                        | 5.2.1 Pair-Wise Track comparison Duplicate Algorithm          | 56 |  |  |  |  |

|   |                                        | 5.2.2 A Duplicate Removal Algorithm based on the Hough Trans- |    |  |  |  |  |

|   |                                        | form (HT) parameter space                                     | 60 |  |  |  |  |

|   | 5.3                                    | Summary                                                       | 65 |  |  |  |  |

| 6 | The                                    | The TMTT Hardware Demonstrator 6                              |    |  |  |  |  |

|   | 6.1                                    | The Hardware Demonstrator Slice                               | 69 |  |  |  |  |

|   | 6.2                                    | Software Setup                                                | 71 |  |  |  |  |

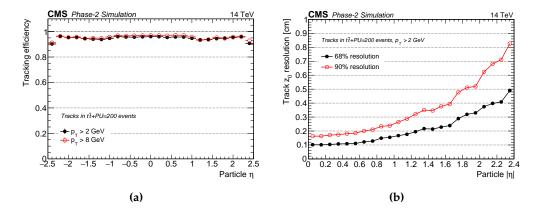

|   | 6.3                                    | Track Reconstruction Efficiency                               | 72 |  |  |  |  |

|   | 6.4                                    | Track Parameter Resolution                                    | 75 |  |  |  |  |

|   | 6.5                                    | Data Rates                                                    | 78 |  |  |  |  |

|   | 6.6                                    | Flexibility and Robustness of the System                      | 81 |  |  |  |  |

|   | 6.7                                    | Latency                                                       | 83 |  |  |  |  |

|   | 6.8                                    | Field Programmable Gate Array (FPGA) Resource Usage           | 84 |  |  |  |  |

|   | 6.9                                    | Summary                                                       | 85 |  |  |  |  |

| 7 | The                                    | The CMS Tracker Back-End System                               |    |  |  |  |  |

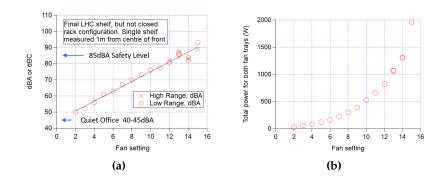

|   | 7.1                                    | CMS Tracker Rack Configuration                                | 87 |  |  |  |  |

|   | 7.2                                    | The ATCA Shelf                                                | 89 |  |  |  |  |

|   |                                        | 7.2.1 Hardware Platform Management                            | 90 |  |  |  |  |

|   |                                        | 7.2.2 Intelligent Platform Management Controller              | 90 |  |  |  |  |

|   | 7.3                                    | The CMS DAQ and TCDS Hub (DTH) Hub Prototype                  | 91 |  |  |  |  |

|   | 7.4                                    | Tracker Hardware Development Platforms                        | 93 |  |  |  |  |

|   |                                        | 7.4.1 Apollo                                                  | 94 |  |  |  |  |

CONTENTS XIII

|     |                                | 7.4.2 Serenity-Z                                                  | 95  |  |  |  |

|-----|--------------------------------|-------------------------------------------------------------------|-----|--|--|--|

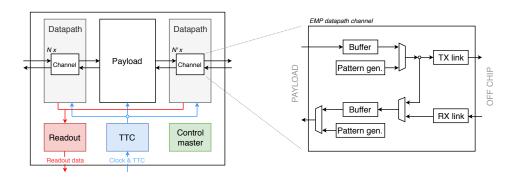

|     | 7.5                            | The EMP framework infrastructure firmware                         | 96  |  |  |  |

|     | 7.6                            | Summary                                                           | 99  |  |  |  |

| 8   | Hare                           | dware R&D Contributions                                           | 101 |  |  |  |

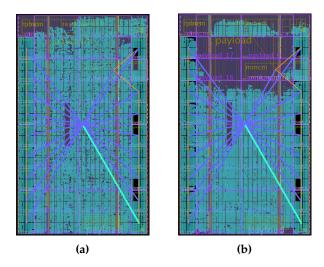

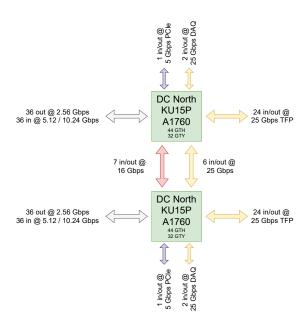

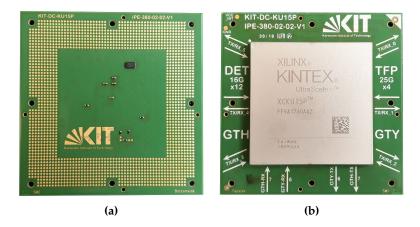

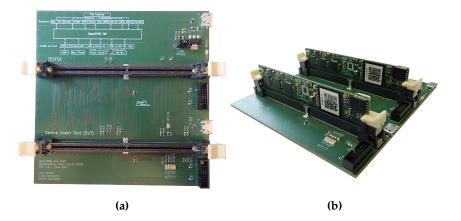

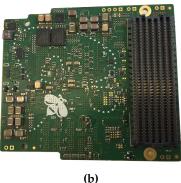

|     | 8.1                            | FPGA Daughtercard for Serenity-Z                                  | 101 |  |  |  |

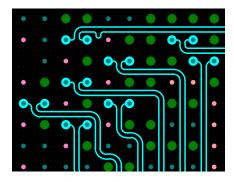

|     |                                | 8.1.1 PCB Layout High-Speed Differential Lines Tuning             | 103 |  |  |  |

|     |                                | 8.1.2 High-Speed Optical Transceiver Qualification                | 104 |  |  |  |

|     | 8.2                            | Trenz to Serenity Adapter                                         | 105 |  |  |  |

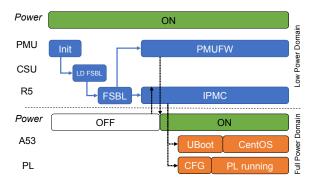

|     |                                | 8.2.1 The Unified slow control architecture                       | 105 |  |  |  |

|     |                                | 8.2.2 Hardware components of the Trenz-Serenity adapter           | 106 |  |  |  |

|     |                                | 8.2.3 IPMC Software Implementations                               | 108 |  |  |  |

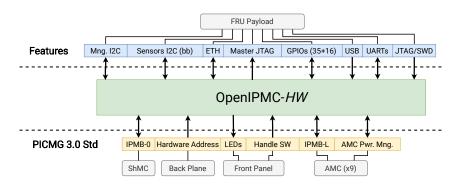

|     | 8.3                            | ATCA ZynqUS+ IPMC Test Board                                      | 111 |  |  |  |

|     | 8.4                            | OpenIPMC-HW DIMM                                                  | 113 |  |  |  |

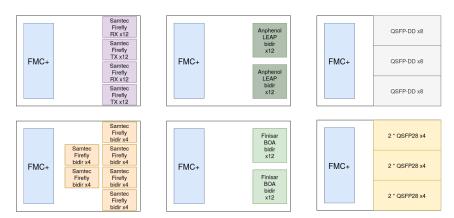

|     | 8.5                            | FMC+ Board for 25 Gb/s Optical Evaluation                         | 116 |  |  |  |

|     | 8.6                            | Summary                                                           | 121 |  |  |  |

| 9   | Sere                           | renity-A2577 ATCA Board                                           |     |  |  |  |

|     | 9.1                            | Serenity-A2577 Architecture                                       | 123 |  |  |  |

|     | 9.2                            | Integrated Slow Control Management Modules                        | 124 |  |  |  |

|     |                                | 9.2.1 FMC+ version                                                | 126 |  |  |  |

|     |                                | 9.2.2 CMX-EXT version                                             | 127 |  |  |  |

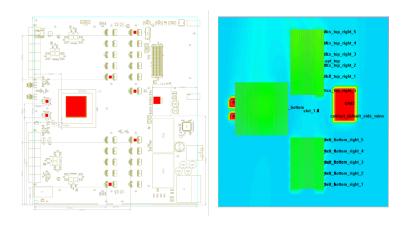

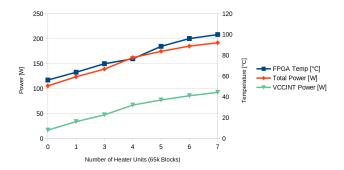

|     | 9.3                            | Thermal Analysis                                                  | 128 |  |  |  |

|     | 9.4                            | MGT performance                                                   | 131 |  |  |  |

|     |                                | 9.4.1 25 Gb/s Optical Evaluation with Samtec x12 alpha-v2 parts . | 132 |  |  |  |

|     |                                | 9.4.2 Bathtub analysis with 25 Gb/s Samtec x12 alpha-v2 parts     | 134 |  |  |  |

|     | 9.5                            | Timing Control and Distribution System (TCDS2)                    | 137 |  |  |  |

|     | 9.6                            | Summary                                                           | 140 |  |  |  |

| 10  | Con                            | clusion                                                           | 141 |  |  |  |

| Ac  | rony                           | ms                                                                | 143 |  |  |  |

| Lis | List of Figures List of Tables |                                                                   |     |  |  |  |

| Lis |                                |                                                                   |     |  |  |  |

| Bi  | Bibliography                   |                                                                   |     |  |  |  |

| Lis | List of Publications           |                                                                   |     |  |  |  |

XIV CONTENTS

### 1 Introduction

The Large Hadron Collider (LHC) located at the European Organization for Nuclear Research (CERN) is the largest particle accelerator in the world. It was commissioned in 2010 delivering proton-proton collisions with a 7 TeV center-of-mass energy. Only two years later, in July 2012 it announced the discovery of the Higgs boson at about 125 GeV by both of its general-purpose experiments A Toroidal LHC Apparatus (ATLAS) [3] and the Compact Muon Solenoid (CMS) [4]. This important discovery was long predicted by the Standard Model (SM) of particle physics [5]–[9], which is currently the best theory to describe the elementary building blocks of the universe.

The LHC has however been designed to go beyond the SM in the search of new physics like the existence, or not, of supersymmetry, the nature of dark matter, and the existence of extra dimensions [10]. To further extend its discovery potential, the LHC is planing a major upgrade [11] to increase its number of collisions per area and time, the so called luminosity, by a factor of five beyond its design value. The integrated luminosity design goal has also increased by a factor of ten to 3000 fb<sup>-1</sup> [10]. The LHC produces proton-proton (pp) collisions at a rate of 40 MHz, *i.e.* one bunch crossing every 25 ns. The typical event size during Run 1-2 for the ATLAS and CMS experiments was about 1 MB corresponding approximately to a data rate of 40 TB/s [12], for Phase-2 this value will increase to an expected event size of 7.4 MB for a total data rate of 296 TB/s [13], an amount impossible to be stored for later offline analysis.

High-energy Physics (HEP) experiments have a large experience acquiring and consequently reducing very large volumes of data. This is achieved by the use of complex and multiple stages of triggers, which perform different degrees of online data elaboration, with the aim of reducing the final data volume considerably [14]–[16], thus keeping only the events with potentially interesting physical phenomena. The expected trigger rate for the HL operations is 750 kHz which equates to about 50 Tb/s, the HLT is expected to reduce this to an output rate of 7.5 kHz to storage.

Under the challenging conditions of the HL operation, the CMS detector, particularly the silicon tracker, requires a data acquisition system with exceptional

2 Introduction

performance to collect the detector data and analyze it in real-time, therefore contributing with track candidates to the Level-1 (L1) trigger. The upgrade of the trigger system will enhance the physics selectivity and maintain the performance necessary throughout the 10 year long HL-LHC program.

This dissertation includes various fundamental developments to demonstrate the feasibility of reconstructing tracks under the tight latency requirements of the HL CMS L1-trigger system. Chapter 5 shows specifically the contributions to the Timemultiplexed Track Trigger (TMTT) algorithm by the author, which were completely implemented in hardware, using last generation FPGAs as a demonstration system, whose tracking results are shown in Chapter 6. Furthermore, this dissertation also includes several hardware developments to contribute to the overall research and development program aimed at designing the outer tracker back-end electronics system, which is based on the Advanced Telecommunications Computing Architecture (ATCA) standard and uses next generation FPGAs and cutting-edge high-speed optical transceivers. The contributions developed under this thesis for the hardware back-end system are specified in Chapter 8 and Chapter 9.

# 2 The CMS experiment at the LHC

### 2.1 The Large Hadron Collider (LHC)

The LHC is located at the border between France and Switzerland, nearby Geneva in a 26.7 km long tunnel at 100 m below the surface. It was built on the same tunnel that was previously used by the Large Electron-Positron Collider (LEP) [17]. The Lorentz force, in Equation 2.1, is responsible for particle acceleration and deflection. When charged particles travel in curved paths, synchrotron radiation is emitted, therefore decreasing the energy of the beam. The energy loss is inversely proportional to the mass ( $\Delta E \propto \frac{E^4}{m^4}$ ). For this reason, at the LHC a much greater center-of-mass energy can be achieved by using hadrons instead of electrons or positrons like at the LEP.

$$\dot{p} = -q \cdot (\vec{E} + \vec{x} \times \vec{B}) \tag{2.1}$$

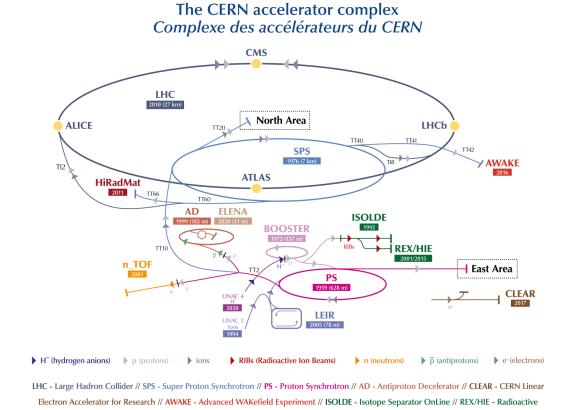

Protons at the LHC need to be accelerated in stages using the pre-accelerator complex shown in Figure 2.1. First, protons are extracted from an hydrogen source, ionized, and accelerated using Radio Frequency (RF) cavities to 50 MeV by the LINAC-2 linear accelerator. In 2020, as part of the upgrades for Run 3, LINAC-2 was replaced by LINAC-4 depicted in the Figure 2.1. The protons then enter the Proton Synchrotron Booster raising their energy to 1.4 GeV before they are transferred to the Proton Synchrotron which has a circumference of 628 m and uses conventional electromagnets for bending and focusing the beam. The Proton Synchrotron further raises the energy of the beam to 25 GeV and gives it the required bunch structure. Then, the beam is injected to the Super Proton Synchrotron (SPS), which has a circumference of about 7 km, further raising the energy to 450 GeV before it is transferred to the LHC ring in two opposing beams. At the LHC ring there are 2808 proton packets per particle beam, each of which contains about 10<sup>11</sup> protons. The protons travel almost at the speed of light and have a collision frequency of 40 MHz with an orbital frequency of around 11 kHz [11].

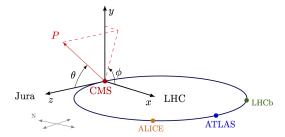

**Figure 2.1:** Schematic representation of the LHC with the four detectors: CMS, LHCb, ATLAS, and ALICE. The pre-accelerators complex is also shown containing the Proton Synchrotron Booster, Proton Synchrotron and the Super Proton Synchrotron (SPS) [18].

EXperiment/High Intensity and Energy ISOLDE // LEIR - Low Energy Ion Ring // LINAC - LINear ACcelerator // n\_TOF - Neutrons Time Of Flight //

HiRadMat - High-Radiation to Materials

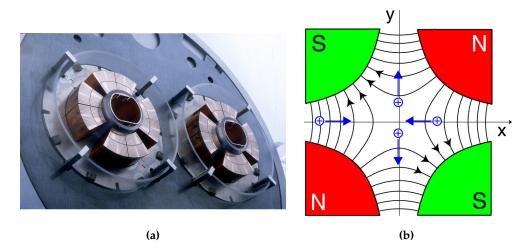

In order to keep particles with these high energies in the storage ring under control, the LHC is instrumented with 1232 dipole and 392 quadrupole superconducting magnets operating at a temperature of 1.9 K and each producing about 8 T [19]. The LHC ring is composed by eight straight sections, four of them are cross points of the beams equipped with experiments, and eight arcs. The primary job of the magnets is to bend the particle beam at those locations where arcs are present, and to focus the beam into compact packets to increase the probability of collision. The quadruple magnets, shown in Figure 2.2, are used to focus the beam transversely. The magnets act like a lens on light rays and focus the particle beam. A quadrupole magnet has a focusing effect in one direction, while it has a defocusing effect in the other direction. In order to achieve an even higher focus, several quadrupole magnets one behind the other, in the direction of flight, focus the particle beam, thus reaching a high level of luminosity.

**Figure 2.2:** a) Model of a superconducting quadrupole magnet for the LHC project [20]. b) Focusing magnet in cross section [21]. The blue arrows indicate the force acting on a positive charge moving into the plane.

The luminosity is an important parameter for the performance of a particle accelerator. It describes the interactions of the particles in a time interval and area. It is specially useful to quantify the event rate of rare phenomena with small production cross sections. There is a direct relationship between the event rate  $\dot{N}$ , the interaction cross section  $\sigma$  and the luminosity L.

$$\dot{N} = \sigma \cdot L \tag{2.2}$$

A storage ring has a luminosity of:

$$L = \frac{N_1 \cdot N_2 \cdot n \cdot f}{A},\tag{2.3}$$

where  $N_1$  and  $N_2$  are the number of particles in the two opposing bunches, n is the number of colliding packets, f is the frequency of the collisions and A is the cross-sectional area of the particle bunches. In order to obtain a high luminosity, the minimization of the cross-sectional area of the bunches is of enormous importance [22].

An often used quantity in storage ring experiments is the integrated luminosity.

$$L_{int} = \int L \, dt \tag{2.4}$$

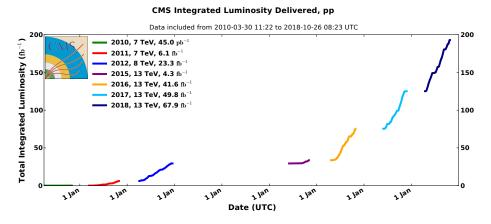

The LHC was designed for a total center-of-mass energy of  $\sqrt{s}=14\,\mathrm{TeV}$  and a peak instantaneous luminosity of  $10^{34}\,\mathrm{cm^{-2}s^{-1}}$ . Figure 2.3 shows the total integrated luminosity vs. time for the whole operation of the LHC. During the data taking period Run 1, between 2010 and 2012, the total integrated luminosity reached about  $30\,\mathrm{fb^{-1}}$  while the center-of-mass energy was  $\sqrt{s}=7\,\mathrm{TeV}$  for the first two years and  $\sqrt{s}=8\,\mathrm{TeV}$  in 2012. With Run 2, between 2015 and 2018, the total integrated luminosity reached almost 200 fb<sup>-1</sup>. In Run 2 the collider was operated at a center-of-mass of  $\sqrt{s}=13\,\mathrm{TeV}$ .

**Figure 2.3:** Cumulative delivered and recorded luminosity versus time for 2010-2012 and 2015-2018 during stable beams for pp collisions at nominal center-of-mass energy [23].

### 2.2 Experimental sites at the LHC

Several experiments are distributed along the ring of the LHC, the four principal ones are located exactly at the crossing points of the beams, two of the biggest experiments are A Toroidal LHC Apparatus (ATLAS) [16] and the Compact Muon Solenoid (CMS), explained in more detail in Section 2.3. Both of them are general-purpose detectors aimed to investigate different fundamental physics questions and complement the findings using measurements from each other. ATLAS is build around a hybrid magnet system which features a central solenoid and several toroids around it. Overall it has an impressive  $46 \times 25 \,\mathrm{m}^2$  in size. The ATLAS trigger system [14] is arranged in three distinct stages: the Level-1, based on specialized hardware, reduces the detector readout to  $75 \,\mathrm{kHz}$  while its trigger decision needs to reach the front-end detectors under  $2.5 \,\mathrm{\mu s}$ ; the Level-2, designed to reduce the trigger rate to approximately  $3.5 \,\mathrm{kHz}$  with an event processing time of about  $40 \,\mathrm{ms}$ ; and the 'event filter' which reduces the event rate to roughly  $200 \,\mathrm{Hz}$  with an event

size of approximately 1.3 MB [16]. The L2 and event filter are based on a large CPU farm, together are known as the High-Level Trigger (HLT).

The Large Hadron Collider beauty (LHCb) [24] experiment, as opposed to ATLAS and CMS, does not enclose completely the collision point with detector material but uses several layers of detectors to only cover the forward region. The first layer of detectors is located close to the interaction point. The other layers are assembled in only one direction in z with a total length of 20 meters. It is designed to specifically study the slight differences between matter and antimatter by focusing on the study of the beauty quark [25]. Initially, two trigger levels were applied at LHCb: a Level-0 using custom high-speed electronics operating synchronously with the machine clock to reduce the event rate down to 1 MHz; and a HLT trigger which is executed on a processor farm. After the Phase-1 upgrades in 2019-2021, the LHCb experiment is using a triggerless readout and a full software trigger in two stages, the HLT1 and HLT2 [26].

The LHC ring is capable of accelerating heavy ions in addition to protons. In such specialized runs one experiment called A Large Ion Collider Experiment (ALICE) [27] is used to primarily investigate the Quark-Gluon-Plasma (QGP) using lead ion collisions. The QGP is an extreme phase of matter that our universe is thought to have been just a few millionths of a second after the Big Bang, right before quarks and gluons were bound together to form protons and neutrons [28]. ALICE electronics are not pipelined in general and three levels of trigger systems are used to reduced the event rate: a Level-0 with a latency of 1.2 µs, a Level-1 at 6.5 µs, and a Level-2 after 100 µs implemented once data from the Time Projection Chamber (TPC) are received. Finally, a layer of software-based HLT triggers are run in a CPU farm.

### 2.3 The Compact Muon Solenoid (CMS) Experiment

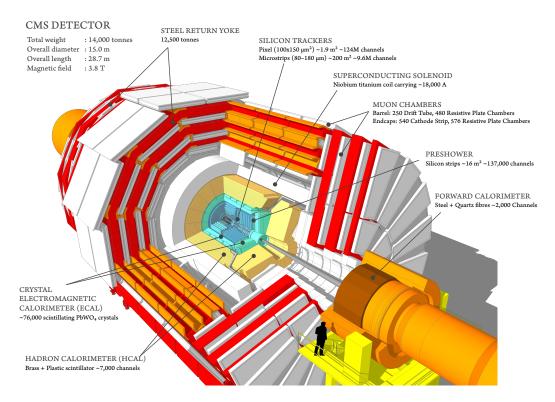

The CMS is a particle physics experiment at the LHC. Just like its counterpart, the ATLAS experiment, it is a general-purpose, cylindrical symmetric particle detector. The main design goals of CMS include carrying out precision measurements of the standard model, such as measuring the Higgs self-coupling, which influences the Higgs potential. The range of tasks of CMS include the implementation of Quantum Chromodynamics (QCD) tests, or the search for decay channels with four top quarks in the final state [29]. However, the research is not limited to the standard model. Future measurements will search for supersymmetrical coupled particles [30] with a  $\tau$ -lepton [31] and other space-time dimensions. The search for dark photons produced by the decay of a Higgs boson in association with a Z boson is a new

Figure 2.4: Modeled cutaway view of the CMS detector [34].

approach to study dark matter [32]. Finally, CMS also contributes to the analysis of heavy ions collisions [33].

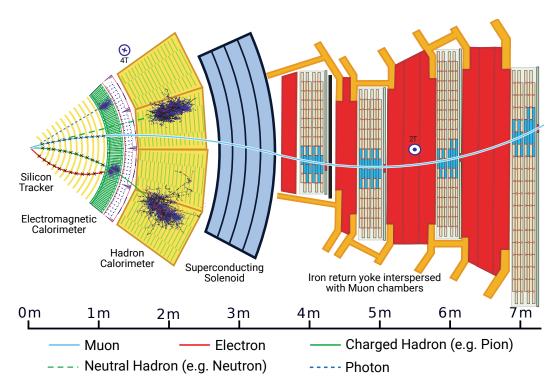

The data discussed in this section refers to the current CMS detector. The changes to the CMS detector after its upgrade in the year 2025 are shown in Chapter 3. The structure of the detector, shown in Figure 2.4, is as follows: starting from the center, the silicon tracker is located very close to the Interaction Point (IP). It uses two types of detectors, pixelated or strip detectors with a total sensitive area of 200 m<sup>2</sup>. Next, the crystal electromagnetic calorimeter is found using several PbW0<sub>4</sub> scintillating crystals. Immediately after, the hadron calorimeter is located using another type of scintillator material based on a polymer. The calorimeter detectors are enclosed by the next construction layer of the experiment and one of the fundamental components, the solenoid magnet, which uses a niobium titanium core. Finally, outside the solenoid and enclosed inside the steel return yoke, the muon drift chambers are located.

The purpose of the CMS detector is to measure the decay products resulting from proton-proton collisions. The CMS detector measures mainly photons, jets, hadrons, muons, electrons, and the missing transverse impulse. This is possible by reconstructing tracks with a transverse momentum of over  $p_{\rm T}>1\,{\rm GeV}$  in the

pseudorapidity range of  $|\eta| < 2.5$ . The total length of the detector is 21.6 m and it has a diameter of 14.6 m. With a total mass of 14000 t, it is very compact, compared to detectors of similar weight. Another component of the CMS experiment is the trigger system. It is responsible for selecting important events containing relevant physics phenomena, and prompting for its readout from the detectors and storage by the DAQ system. The enormous amount of data that arises from proton-proton collisions can neither be evaluated nor read out in its entirety. For this reason, it is absolutely necessary to select only the interesting events. At the moment it is possible to write to permanent storage with a data transfer rate of 1 Gb/s and a trigger rate of 1 kHz.

#### 2.3.1 Coordinate System

A right-handed coordinate system shown in Figure 2.5 is used on the LHC and therefore CMS. The x-axis points in the direction of the center of the LHC accelerator, the y-axis points vertically upwards and the z-axis runs along the beam axis. The origin of the coordinate system is the center of the CMS detector. As the CMS detector is symmetric around the beam axis, a cylindrical coordinate system is often used. Here  $\varphi$  is the azimuthal angle in the x-y plane. The distance from the beam axis is denoted by r. In addition, the angle  $\theta$  to the beam axis is introduced. The pseudorapidity, expressed in Equation 2.5, is a dimensionless quantity and serves as a measure for the angle between the flight direction and the jet axis. The number of particles produced per pseudorapidity interval is approximately constant, which is why the pseudorapidity  $\eta$  is preferred to the angle  $\theta$ .

$$\eta = -\ln \tan \left(\frac{\theta}{2}\right) \tag{2.5}$$

Figure 2.5: CMS coordinate system [35].

#### 2.3.2 The solenoid

The CMS detector is built around a solenoid magnet, with a 6 m in diameter coil formed by superconducting fibers. It is able to generate a homogeneous 3.8 T magnetic field when about 18 000 A are circulating through it, the magnetic field is used to measure the momentum of charged particles. The solenoid is the largest magnet of its type ever constructed. The windings of the solenoid are arranged in four layers of a superconductor made from a Rutherford-type cable using Niobium-Titanium (NbTi) that is co-extruded with Aluminum. Outside the solenoid, the generated magnetic field is enclosed by the iron yoke. In this way, a homogeneous magnetic field of 1.8 T in the central area and an inhomogeneous field of 2.5 T at the ends of the magnet are generated.

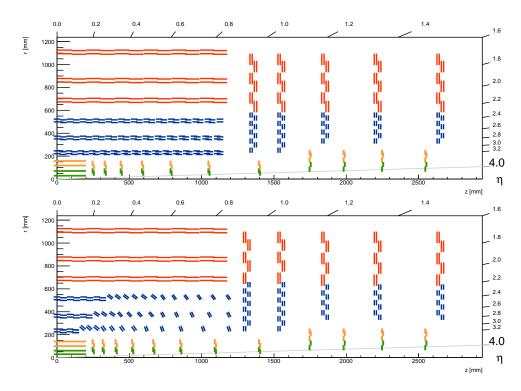

#### 2.3.3 Silicon tracker

The CMS tracker enables the precise measurement of the trajectories of charged particles emerging from the IP. Moreover, it can also determine the momentum with high accuracy by leveraging the homogeneous magnetic field produced by the solenoid and the track curvature as parameters. The tracker modules are constructed using silicon as the sensor material. Silicon sensors enable very fine granularity and fast signal readout, both of which are required to identify and disentangle the tracks of all charged particles produced in the proton-proton collisions. The high particle flux passing through the tracker material requires the use of radiation-hard sensors. This is accomplished by implementing an n+ pixel on n- substrate design, which allows for partial depletion even in close proximity to the beam pipe. Charged particles passing through a semiconducting silicon detector produce electron-hole pairs, resulting in an electric signal that can be readout by the detector front-end electronics. Figure 2.6 depicts an overview of all silicon tracker modules. Overall, the tracker measures 5.8 m in length and 2.2 m in diameter, it is arranged to cover the pseudorapidity range of  $|\eta|$  < 2.5. The tracking system is divided into two sections: the pixel detector on the inside and the strip detector on the outside. Finally, the entire tracker is run at a temperature of -20 °C to help protecting it from the negative effects of radiation damage.

#### **Pixel Detector**

The pixel detector is the innermost detector of the CMS experiment. The initial design was made up of three cylindrical layers of silicon pixel modules with radius of 4.4 cm, 7.3 cm, and 10.2 cm that surround the beam pipe. Each layer is composed

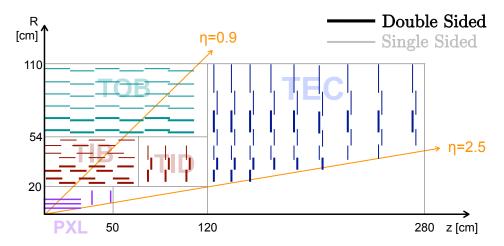

**Figure 2.6:** Layout of the CMS Tracker, showing the  $\frac{1}{4}$  view of the r-z plane [36]. Collisions occur at coordinate (0, 0), with the two beams traveling from the left and right of the collision point. Bold lines represent double sided module assemblies.

of 768 pixel modules, where each pixel has an area of  $100\times150\,\mu\text{m}^2$ . In addition to the three barrel layers, each side has two endcap disks with silicon pixel modules. They have a 6 cm inner radius and a 15 cm outer radius. The endcap disks are positioned at  $z=34.5\,\text{cm}$  and  $z=46.5\,\text{cm}$  from the center of the detector. Each disk has a geometry with 24 blades that are rotated by 20°. Each blade contains 7 pixel modules, for a total of 672 modules in the endcaps.

Since the pixel detector is the closest to the beam pipe, it received the most radiation damage and was replaced at the end of 2016 with one having four layers in the barrel region located at 2.9 cm, 6.8 cm, 10.9 cm, and 16.0 cm [37]. Similarly, the endcap region of the pixel detector is now a three layer construction located at z = 29.1 cm, z = 39.6 cm, and z = 51.6 cm measured from the center of the detector. The new inner tracker increased the number of pixels from 66 millions to 124 millions. It has a lower material budget and occupies a larger volume. Its innermost layer is situated closer to the interaction point, improving significantly the primary vertex resolution efficiency. Its outermost layer is closer to the stip detector, improving the overall tracking performance of the experiment by reducing the combinatorics during track reconstruction [38].

#### **Strip Detector**

The outermost component of the tracking system are the silicon strip detectors. Over 15 000 modules, each with a single-sided silicon strip, are used to construct the system. The strip detector has nearly 10 million readout channels in total. It is

divided into several subsystems, each of which covers a different region of radius and pseudorapidity in the detector layout as seen in Figure 2.6. The overall strip detector has the capability of identifying tracks with pseudorapidities  $|\eta| < 2.4$ .

According to the Figure 2.6, the outer tracker is comprised by the Tracker Inner Barrel (TIB), the Tracker Inner Disks (TID), the Tracker Outer Barrel (TOB), and the Tracker EndCaps (TEC). The TIB and TID are both located in the region of radii between 20 cm and 55 cm in diameter. The TIB is composed by four layers of modules and has a |z| < 65 cm. For the modules in the inner two layers, two modules are always mounted back-to-back with an angle of 100 mrad between their strips, these modules are shown in the Figure 2.6 with bolded lines. This enables dual measurements in both the r-z and the r-x directions at the same time. The TID is made up of three disks on each side, where the dual modules are installed on the inner two rings of each disk. The TID ocupy the range 65 cm < |z| < 118 cm. The TOB is made up of six concentric layers, the inner two are capable of allowing dual measurements. It is located within |z| < 118 cm and radii 55 cm and 116 cm. Finally, the forward regions TEC are covered by nine disks on each side of the detector. It occupies the area between 22.5 < r < 113.5 cm and 124 < |z| < 282 cm. Dual modules can be found on the two innermost rings and in the fifth ring of TEC.

TID and TEC modules have strips that point towards the beam pipe, whereas the barrel modules (TIB and TOB) have strips that are parallel to the beam pipe direction. Different strip pitches have been used in different parts of the detector. In the first two layers of TIB the pitch size is 80 µm, resulting in a single point resolution of 23 µm, in the layers 3 and 4 of TIB the pitch size is 120 µm for a resolution of 35 µm. For TID, the module strip pitch is between 100 µm and 141 µm. In TOB, pitch sizes are between 122 µm and 183 µm producing a single point resolution of 35 µm and 53 µm respectively. Finally, TEC can reach a resolution between 230 µm and 530 µm using modules with strip pitches between 97 µm to 184 µm. The single hit resolutions result in a momentum resolution of 1 to 2 % for the measurement of charged particles with a transverse momentum of  $p_{\rm T}$  >100 GeV.

#### 2.3.4 Calorimeter

In the CMS experiment, there are two calorimeter systems: the Electromagnetic Calorimeter (ECAL) [39] and the Hadronic Calorimeter (HCAL) [40]. The calorimeters are arranged in a symmetrical pattern between the tracker system and the magnet. They provide particle energy measurements and contribute to particle type classification. A scintillator detector is housed within the inner ECAL. Electrons,

positrons, and photons primarily deposit their energy in the scintillator material, whereas hadrons are first stopped in the outer HCAL material.

#### Electromagnetic calorimeter - ECAL

The ECAL measures the energy of electrons, positrons, and photons. A shower of electromagnetic particles is produced as a result of the subsequent emission of bremsstrahlung in the scintillator material and the formation of conversion pairs. The number of particles in this shower is proportional to the energy of the incoming electron, positron or photon. Shower particles excite molecules in the scintillator material, causing light to be emitted. This light is then detected by photo detectors at the other end of the scintillator. The scintillation light is emitted in the blue-green wavelength range (420-430 nm) with a light yield of 30 photons per MeV. Avalanche Photodiodes (aPDs) in the barrel and Vacuum Phototriodes (vPTs) in the endcaps collect the light and transform it into an electric signal which is then digitized.

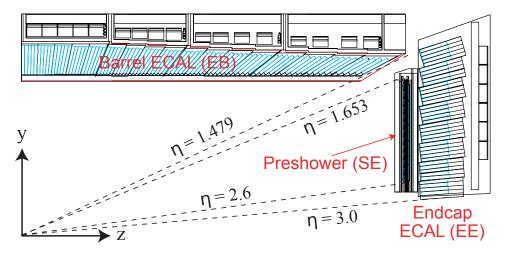

**Figure 2.7:** The electromagnetic calorimeter of the CMS experiment consists of the barrel (EB), the preshower (ES) and the endcap (EE) calorimeters [41].

The ECAL is made up of over  $68\,000$  crystals of lead tungstate (PbWO<sub>4</sub>). PbWO<sub>4</sub> is a transparent material with a high density of  $8.28\,\mathrm{g/cm^3}$ , a short radiation length of  $X_0=0.89\,\mathrm{cm}$ , and a Molière radius of  $R_H=2.2\,\mathrm{cm}$ . As a result, PbWO<sub>4</sub> can function as both an absorber and a scintillator at the same time. It also has a high radiation hardness and a fast scintillation decay time, with approximately  $80\,\%$  of the light emitted within 25 ns. Using this material, a compact design with fine granularity is possible. The ECAL is made up of two endcaps (EE) and a cylindrical barrel (EB). A preshower detector (SE) is installed in front of each endcap. Figure 2.7 shows the ECAL layout.

The EB has 61 200 PbWO<sub>4</sub> crystals and a pseudorapidity of  $|\eta| < 1.479$ . Each crystal covers a cross section of  $22 \times 22 \, \mathrm{mm}^2$  in the  $\eta$ - $\varphi$  plane. The EB inner radius is 1.29 m and each EB crystal is 230 mm long, corresponding to 25.8  $X_0$ . All crystals are oriented towards the interaction point. Avalanche photodiodes read the light emitted by high-energy electrons, positrons, or photons passing through the crystal.

The EE disks cover the range  $1.479 < |\eta| < 3.0$  in pseudorapidity. Each endcap has two halves. There are 3 662 crystals per half and the crystals are grouped in a  $5\times 5$  matrix called supercrystals with a 28.62 mm per side. The crystal has a total length of 220 mm corresponding to 24.7  $X_0$ .

Preshower detectors identify charged pions and improve electron and photon identification and localization in the pseudorapidity range 1.653<  $|\eta|$  <2.6. It is a sampling calorimeter. Electromagnetic showers are created by incoming electrons or photons. These are detected by silicon strips between the lead layers. The preshower detector is 20 cm thick.

#### Hadronic Calorimeter - HCAL

The HCAL structure differs from the ECAL, since the absorber and scintillator material are arranged alternately, the radiation length is significantly greater than the radiation length of the electromagnetic interaction. A massive  $50\,\mathrm{mm}$  brass plate, which is embedded in steel plates on both sides, serves as the absorber. Because the HCAL is placed inside the solenoid in a strong magnetic field, the nonmagnetic absorber material brass was chosen, which also has a reasonable hadronic interaction length of  $\lambda_I = 16.4\,\mathrm{cm}$ . As active material, the absorber is arranged in slices that are interspaced with plastic scintillators. Hadrons passing through the HCAL interact strongly with the absorber material, resulting in showers of secondary hadrons. These showers cause excitations of the active material and the emission of light, which is transported to photo-detectors outside the calorimeter via wavelength shifting fibers. This arrangement alternates 14 times. The scintillator consists of  $3.7\,\mathrm{mm}$  thick polymer tiles that detect the hadronic shower and are read out via hybrid photodiodes. A total of  $70\,000$  scintillator tiles were installed.

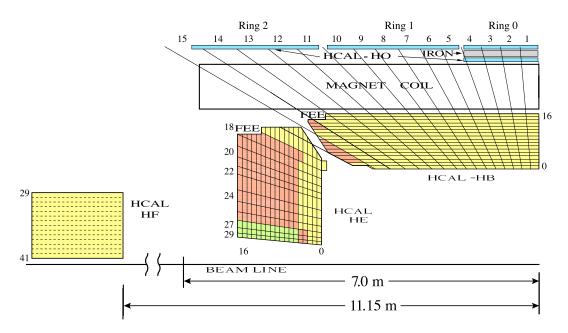

The HCAL, illustrated in Figure 2.8, has a particularly large coverage in order to determine the missing transverse impulse as precisely as possible. The transverse momentum is a conserved quantity. The sum of all transverse impulses before and after the protons collide is approximately zero. The observation of a non-zero transverse momentum therefore provides information about particles that do not interact with matter. Missing transverse momentum can be of crucial importance

**Figure 2.8:** Cross-section view in the r-z plane of the CMS HCAL. The HCAL barrel (HB) and the HCAL endcap (HE) are located inside the solenoid, the position of the front-end readout electronics (FEE) for HB and HE is indicated. The HCAL forward (HF) is located 11.15 m from the IP. The HCAL outer (HO) is installed outside the CMS solenoid coil [42].

for the detection of new physics. In order to determine the missing transverse momentum as precisely as possible, coverage over a large area is necessary.

The HCAL covers a range of  $\eta < 5.2$  thanks to the forward HF detector. The endcaps (HE) cover a range of  $1.3 < |\eta| < 3.0$ , the barrel (HB) cover the range of  $|\eta| < 1.3$ . Another part of the calorimeter, HO is located behind the solenoid coil. Due to the high penetration depth of charged hadronic particles, in some cases they are not fully absorbed in the actual calorimeter. To increase the energy resolution, two scintillator plates were installed behind the coil.

The HB is made up of 36 identical wedges that form two half-barrels. The absorber plates in the HB are parallel to the beam axis. The HB wedges are divided into towers in the  $\eta$ - $\varphi$  plane. The HB has an inner radius of 1.78 m and an outer radius of 2.88 m. The thickness of the total amount of absorber material in the HB corresponds to  $5.8\,\lambda_I$  for the central towers with  $|\eta|<0.087$  and up to  $10.6\,\lambda_I$  at  $|\eta|<1.3$ . The HB is followed by the HO, which increases the effective thickness of the absorber in the barrel region. The HO is divided into five rings based on the geometry of the muon chambers in the outermost part of the detector. The outer four rings each have a single scintillator slice with the solenoid material acting as an absorber. In the

central ring, an additional lead plate serves as an absorber between two active layers. This results in an absorber thickness of at least  $10\,\lambda_I$  over the entire barrel region, including about  $1\,\lambda_I$  from the ECAL. The HE is made up of 18 segments arranged in a radial symmetry around the beam pipe. The brass absorber in the HE has a total length of about  $10\,\lambda_I$ . The HF system is located outside the solenoid and is used to detect hadron showers in the very forward region of the CMS detector. The HF has a cylindrical structure that surrounds the beam pipe and has an inner radius of 12.5 cm and an outer radius of 130 cm. The HF must withstand high particle fluxes that occur in the forward region of high-energetic particle collisions. As a result, the HF is made up of steel absorber plates and quartz fibers as active material. When compared to plastic scintillators, quartz fibers are more radiation-hard. Cherenkov light produced in the quartz fibers by hadron showers is detected by photomultipliers.

#### 2.3.5 Muon system

Figure 2.9 shows in the right side the muon system that forms the outermost layer of the CMS detector. The muon system can only be reached by neutrinos, muons and leaking hadron showers. It is responsible for the detection of muons. The detection of muons proves to be particularly helpful in order to later reconstruct decays in which at least one muon is generated. The muon system can provide in real time the trigger with reconstructed muons. The reason for the easy penetration of the muons through the detector material lies in their large mass  $m_{\mu}=105.6\,\mathrm{MeV}$  and the fact that the radiated energy in the form of bremsstrahlung is proportional to the inverse of the square of the mass.

The detection of muons takes place via ionization chambers. A detection area of  $25\,000\,\mathrm{m}^2$  must be covered with these chambers. Since the particle density is lower in the outer detector layers, there is no need for a high granularity in the muon system as in the inner area. Smaller drift cells are used in the cylindrical area, which ultimately form the drift chambers (DT). Drift chambers show the trajectory of charged particles. The gas in the ionization chambers is ionized as the particle passes through it. Parallel wires with a high potential difference ensure that a current flows between the wire and the cathode. Using the current pulses and the drift time, it is possible to reconstruct the particle trajectories. The drift chambers are embedded in four groups in the magnet yoke. The first three groups consist of layers of eight muon chambers each. They are used to determine the position in the r- $\varphi$  plane. Four further drift chambers make it possible to determine the z coordinate. The spatial resolution in the muon detector is 250 µm. In contrast, in the endcaps a different technology has to be used. A smaller signal decay time is important because the

**Figure 2.9:** Cross-section through a slice of the CMS detector. The drift chambers of the muon spectrometer in the iron return yoke are shown in the outer area [43].

particle density is higher than in the radial area. For this reason, Cathode Strip Chambers (CSC) are used in the endcaps. The cathode strips are perpendicular to the beam axis and the anode wires are perpendicular to the cathode strips. The resolution in the radial direction is 6 mm. By forming the center-of-mass, the spatial resolution in the r- $\varphi$  plane can be improved to 150 µm.

Resistance plates (RPC) are also used to detect muons. There is no center-of-mass formation because the spatial resolution is not high. The RPCs offer the advantage of a good time resolution of 3 ns and help in the reconstruction of the muons. Due to the large distance to the beam axis, the muon system helps to increase the impulse resolution in the high impulse range. By combining information from the muon chambers with tracking information from the inner tracker, the momentum resolution can be significantly improved.

#### 2.3.6 Trigger and Data Acquisition

The LHC produces proton-proton collisions at a relatively high rate of  $40 \,\mathrm{MHz}$ , *i.e.* of one every 25 ns. At the designed instantaneous luminosity of  $10^{34} \,\mathrm{cm}^{-2} \,\mathrm{s}^{-1}$ , the accelerator is able to produce in average about 25 simultaneous collisions with a

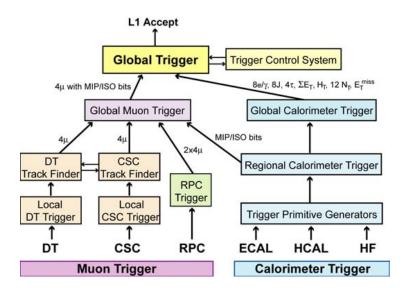

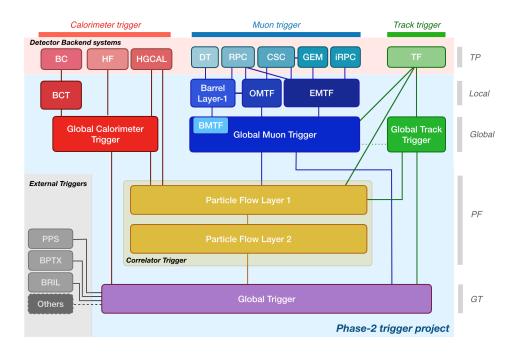

**Figure 2.10:** Architecture of the L1 trigger. The final decision is made when all hierarchies have been run through in the calorimeter trigger and the muon trigger. A decision is made for each of the local subsystems, on which the overall decision of the L1 trigger later depends [15].

massive number of about 1 000 particles penetrating the detector each bunch crossing. This massive number of events corresponds to a significant amount of data that cannot be stored without a filtering stage. As a result, the trigger system of CMS [15], [44] reduces the amount of data collected on a short time scale by deciding whether an event should be stored or rejected. The trigger system consists of two subsystems called Level-1 (L1) trigger and High-Level Trigger (HLT). The data collection rate is reduced to a frequency of several hundred hertz, corresponding to a reduction factor of about 10<sup>7</sup>. The signature of processes of physical interest is primarily used to determine which events are stored. It is critical, especially for the search for rare processes, that almost all events of an specific process are saved to permanent storage for offline analysis. As a result, the trigger system ensures that information about events involving one or more charged leptons or photons with high momentum, large missing transverse energy, or a high multiplicity of high-energetic hadron jets are identified within a low latency and saved on a relatively short time scale.

The original CMS L1 trigger design, represented in Figure 2.10, is a hardware-based trigger system with components at the local, regional, and global levels. All components are programmable electronic devices that only use coarsely segmented data from the calorimeter and muon modules. The local components are built around the front-end electronics, which are installed directly inside the experiment. The energy deposits in the calorimeters and hit patterns in the muon chambers are stored

as Trigger Primitive Generators (TPG) in the pipelined memories of the front-end electronics. Regional triggers combine TPG information in spatial regions to identify candidates such as muons or electrons. The global calorimeter and global muon triggers, respectively, combine information from the entire calorimeter and muon system. The global trigger, which is physically located 90 m underground from the CMS cavern, makes the final L1 decision. The L1 trigger system has a 3.2 µs latency and reduces the data rate to around 100 kHz. To cope with the new LHC conditions, the system was upgraded for Run 2 [45]. If the trigger thresholds were not changed, the increased collision centre-of-mass energy, increased instantaneous luminosity, and higher pileup would increase the trigger rate up to six times the allowed rate. The new system was designed to be intrinsically flexible, with the ability to change architectures and algorithms via high-speed optical links and large FPGAs.

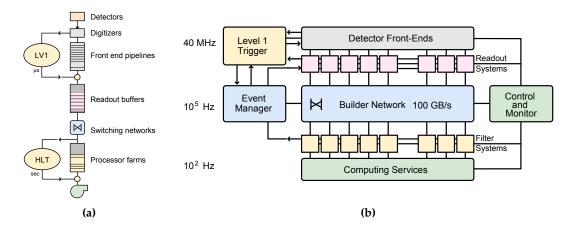

The HLT consists of a software-based trigger that runs on a computing farm. The data filtered by the L1 trigger is transferred to the HLT via a network connection capable of 100 GB/s data transfer volumes. The HLT employs algorithms that combine the L1 trigger objects with all detector module information. Physical objects such as muons, electrons, or jets are reconstructed with greater accuracy from the full detector information than objects reconstructed at the L1 trigger level. The HLT also provides trigger paths that combine data from multiple physical objects into a single event. These trigger paths include multi-lepton triggers and triggers that require the presence of a lepton as well as jets. All HLT filtering algorithms are based on a constant adaptation to collision conditions. The HLT reduces the overall rate of events stored to several hundred hertz. Figure 2.11 depicts a schematic representation of the trigger chain of the CMS experiment.

**Figure 2.11:** Data flow of the CMS Trigger (a) and the DAQ system (b) [46]. The CMS trigger system is divided into two layers: the Level 1 trigger, which reduces the data rate from 40 MHz to 100 kHz, and the HLT, which reduces the rate to 400 Hz.

The data collected by the CMS experiment and accepted by the trigger system must be saved and distributed. Despite the fact that the trigger has already significantly reduced the amount of data, the final data that must be stored corresponds to several tens of petabytes per year. The CMS computing model was created to distribute data as well as simulated events (so-called Monte Carlo samples) and to provide computing resources for data analysis to physicists worldwide. The Worldwide LHC Computing Grid (WLCG) [47], [48], a collaboration of the LHC experiments and several computing centers, organizes data distribution and computing resource allocation. The hierarchical structure of the WLCG is composed by Tier-0, Tier-1, and Tier-2 computing centers. The one-of-a-kind Tier-0 center is a computing facility located directly at CERN. The data is distributed from Tier-0 to Tier-1 centers (e.g. gridKA [49] at KIT). If improved reconstruction algorithms are available, the data can be reprocessed at Tier-1 computing centers. They also have massive storage capacities for data from LHC experiments as well as simulated data produced at either Tier-1 or Tier-2 facilities. Tier-2 centers are primarily intended to store copies of reduced data sets, which can then be accessed and analyzed directly by individual physicists or local analysis groups. Tier-3 sites are local computing devices that are connected to the grid for interactive analyses, despite the fact that they are not formally part of the WLCG. Each analyzer in the grid structure has access to any data set at any of the Tier-2 sites.

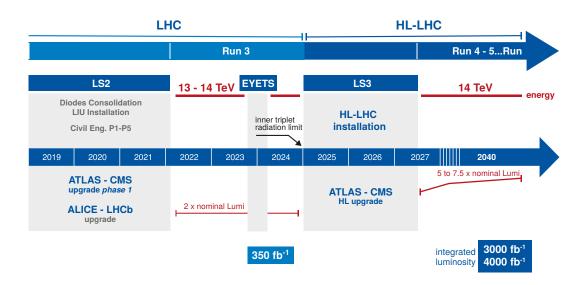

# 3 High-luminosity LHC

The High-luminosity Large Hadron Collider (HL-LHC) project aims to upgrade the LHC collider according to the long term schedule in Figure 3.1, the upgrades to the accelerator complex and the experiments are divided in two Long Shutdown (LS) periods from 2019-2021 (LS2) and 2025-2027 (LS3) after which the HL-LHC configuration is operating. The upgrades bring the luminosity of the LHC up to  $5\times10^{34}$  cm<sup>-2</sup> s<sup>-1</sup>, or even  $7.5\times10^{34}$  cm<sup>-2</sup> s<sup>-1</sup> in the ultimate performance scenario. To reach this goal, the HL-LHC is exploring new beam configurations and advanced technologies in the domain of superconductivity, cryogenics, radiation-hard materials, electronics and remote control, some of the upgrades to the accelerator complex are mentioned in Section 3.2. To prepare for the challenging conditions that are expected during the entire LHC operation period, the CMS experiment has planned two upgrade phases executed on the LS2 and LS3, which are described in Section 3.3. CMS will, in particular, design a completely new silicon tracking detector capable of discriminating high energetic particles and use that information to reconstruct tracks in real-time to contribute to the L1 trigger production. A detailed description of the new CMS tracking detector is provided in Section 3.4.

Figure 3.1: LHC operation and HL-LHC installation schedule, adapted from [50].

### 3.1 Physics Motivation

The upgrade for the HL-LHC opens exciting possibilities for beyond-SM discoveries, in spite of bringing substantial experimental challenges due to the increase in instantaneous luminosity. High radiation levels, particularly in the inner most detector layers, motivate a complete redesign of the silicon tracker with radiation tolerance and high spatial and time resolutions. Many other sub-detector systems would need to be significantly upgraded or be completely replaced to better exploit the discovery potential of the HL-LHC conditions.

One of the main challenges, particularly to CMS and ATLAS, is the substantial increase in the number of simultaneous proton-proton (pp) collisions per bunch crossing (pileup). The number of simultaneous collisions grows from the current average of 25 to 200 during the HL-LHC operations. The increment in pileup produces many more low energetic particles, increasing the background measurements in the calorimeter and generating an increased number of low-momentum muons, that could be miss-identified as high-momentum ones. Therefore, the trigger system needs to be improved with better handles to identify high-energy particles at the hardware L1 trigger, receiving tracker primitives at the collision rate.

These new trigger handles will help in the identification of extremely rare processes. A big part of the program for the HL-LHC will consist of more precise measurements of known phenomena, for example further precision of the W-mass, WW, WWZ, and  $WW\gamma$  couplings. Other mechanisms of great interest are the Higgs couplings to the second-generation fermions via the process  $H \to \mu\mu$ , which using measurements from Runs 1-2 was observed with a 3  $\sigma$  statistical significance [51] and finally, the Higgs self-coupling via the rare di-Higgs process  $H + H \to \mu\mu$ . The goal of the LHC is therefore to extend the measurements of the Higgs properties, and to reach a precision in the range of few percent by the end of the HL operations [11].

The above studies rely heavily on the ability to efficiently identify at the hardware L1 trigger all those physics objects by correlating information from various detectors. To maintain the triggering capability with a manageable data rate, the trigger system needs to be upgraded and improved with the inclusion of charged-particle track information as a critical component. The large input data rate from the silicon tracker, the reduced latency at which tracks need to be identified, and the significant processing requirements for track reconstruction are some of the technological challenges which motivate the design of the tracker back-end electronics system described throughout this thesis.

## 3.2 The HL-LHC Machine

The high-luminosity design involves the upgrade of multiple systems. Existing systems may not be able to withstand the increasingly harsh conditions that the highest luminosity performance will generate. Increasing wear and radiation damage are some of the primary concerns. Many modifications will be required simply to keep the machine running in a regime of nominal or ultimate luminosity. Replacements for certain systems may be made with better-performing equipment rather than spares of the same specification. This 'improvement' in performance goes far beyond the basic reconfiguration that is already planned for the LHC.

For other systems, replacement, while triggered by technical reasons, provides the opportunity to carry out a complete change in layout or performance and may be considered a true upgrade. The most striking example, and the cornerstone of the upgrade, is the replacement of the inner triplet magnets with new magnets based on a Niobium-tin (Nb<sub>3</sub>Sn) superconductor. Another example is the replacement of a significant portion of the current collimation system with a better design with lower impedance jaws.

In other cases, new equipment not currently included in the LHC layout will be installed to improve performance, either in terms of peak luminosity or availability. The most notable example is the superconducting RF crab cavities, which are constructed with a compact design as required for the HL-LHC, a completely novel development and the first for a proton collider. In this section, a brief description of some of the systems that will need to be upgraded or significantly improved in performance will be provided. This section is based on [10] and [11].

#### 3.2.1 Insertion region magnets

The LHC is expected to reach an integrated luminosity of around  $350 \, \mathrm{fb^{-1}}$  by 2025, resulting in doses of up to  $30 \, \mathrm{MGy}$  to some components in the high-luminosity interaction regions. Inner triplet quadrupoles should be able to withstand radiation up to an integrated lumunosity of  $400 \, \mathrm{fb^{-1}}$  to  $700 \, \mathrm{fb^{-1}}$ , but some nested-type corrector magnets may fail at around  $300 \, \mathrm{fb^{-1}}$  The most likely failure mode is a sudden electric breakdown, which will require extensive and time-consuming repairs. Replacement of the triplet must be planned for before radiation damage grows to the point where a serious failure may occur.

The replacement can be combined with an increase in the quadrupole aperture.

However, larger aperture inner triplet quadrupoles and an increased luminosity, imply higher radiation levels, needing a redesign of the entire interaction region zone. This redesign includes larger D1 and D2 dipoles, a new electrical feedbox (DFBX), and a much improved maintenance access to various components. Furthermore, a redesign of the collimation system in the high-luminosity insertions, will be required.

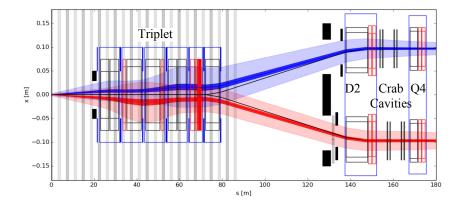

**Figure 3.2:** The overall configuration of the insertion region for the HL-LHC between the IP and the orbit corrector Q4. The two beam envelopes are represented by the dark blue and red areas. The light regions correspond to a beam envelope value of  $12 \sigma$  [10].

The modification of the inner triplets in the high luminosity insertions, as seen in the Figure 3.2, is absolutely the central component of the LHC upgrade. The decision for the HL-LHC has been to rely on the success of advanced Nb<sub>3</sub>Sn technology, which allows access to magnetic fields well beyond 9 T, allowing the aperture of the inner triplet quadrupoles to be maximized.

#### 3.2.2 Collimation

The collimation system was developed for the first phase of the LHC operation. It is currently operating in accordance with the plan. However, if beam instabilities are triggered at intensities close to or just above nominal, the impedance of the collimation system may need to be reduced. The safe handling of a beam of 1 A or more with beta functions at collision exceeding the design value will be uncharted territory. The triplet must be protected throughout the large change in collision beam parameters ( $\beta^*$  transition from 6 m to 10-15 cm). This will be one of the most critical phases of HL-LHC operation: the beam halo alone could exceed the damage limit. As a result, the collimation system must be upgraded. The main additional requirements associated with the upgrade are improved alignment precision and materials capable of withstanding higher power.

#### 3.2.3 Crab cavities

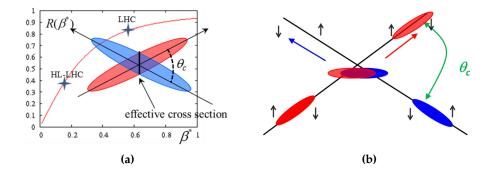

Superconducting RF crab cavities are required in the HL-LHC to compensate for the geometric reduction factor, shown in Figure 3.3, therefore increasing the effective cross section with a very low  $\beta^*$  angle. The unconventional, compact design of HL-LHC crab cavities cannot be achieved using current state-of-the-art technology based on elliptical cavities. It is also required the precise control the RF phase with a precision higher than 0.001 ° so that the beam rotation provided prior to the collision is precisely canceled on the other side of the Interaction Point (IP). As a result, machine protection will face new challenges with the installation of these new crab cavities. Compact crab cavities will be installed on both sides of IP1 (ATLAS) and IP5 (CMS). On each side of the IP, there are four crab cavities per beam. To rotate the beam in the crossing plane, all four cavities can be used; alternatively, a single cryomodule (two cavities) can be used, with the cavities in the second cryomodule providing a deflection in the orthogonal plane, enabling the so-called crab kissing scheme for reducing pileup density [52]. At the moment, the standard practice is to use all crab cavities for geometric compensation, i.e. rotation in the crossing plane as seen in Figure 3.3(b).

**Figure 3.3:** a) Geometrical luminosity reduction factor vs  $\beta^*$  for LHC and HL-LHC. b) Effect of the crab cavity on the beam. Small arrows indicate the torque on the bunch generated by the transverse radiofrequency field. [10].

# 3.3 The CMS Upgrade

The CMS experiment, as explained on Chapter 2.3, proposed an upgrade plan for the detector divided in two phases to cope with the LHC operation challenges. The Phase-1 upgrade was executed during the Extended Year-End Technical Stop (EYETS) between 2016 and 2017. For Run 2, a new pixel detector was installed, the HCAL forward (HF) readout was upgraded, and the upgraded L1 trigger was

included. Phase-1 upgrades continued in the LS2 period between 2019 and 2021. The upgrades included replacing the photo detectors on the HB and HE sections of the hadron calorimeter, exchanging the scintillating tiles in the HE, and installing new Front-End (FE) electronics in the Cathode Strip Chambers (CSC) of the endcap muon detector.

The Phase-2 upgrades motivated by the extreme new conditions with very high pileup are planned for the LS3 period between 2025 and 2027. As the beam width at the collision point is reduced, the luminosity increases to  $L=5\times 10^{34}\,\mathrm{cm^{-2}\,s^{-1}}$ . This leads to an increase in simultaneous inelastic proton-proton collisions up to 200. A negative side effect of this increased luminosity is a higher radiation exposure. To counteract this effectively, more radiation-resistant materials must be used in the construction of the detectors closer to the IP.

Another problem related to 200 pileup events is that individual tracks have to be distinguished from one another within 25 ns. This is countered with an increased granularity in the respective components. However, the increased granularity will also lead to a massive increase in data flow. Another factor that raises the amount of data is the increased coverage, which ensures that particles in the beam direction up to  $|\eta| < 4$  can be detected. The current trigger system would not be able to process the amount of data that arises, the trigger electronics have to be revised to be able to withstand the requirements mentioned above.

**Tracker** Due to radiation damage, the current CMS tracking system must be replaced during LS3 [53]. The new detector is made up of silicon sensors, pixels, and strips with significantly higher granularity and a wider forward acceptance. Furthermore, a significant new feature of the Phase-2 tracker is the ability to provide tracking information at the L1 trigger level at the collision rate of 40 MHz. Currently, the silicon tracker information is only available at the HLT. Including tracks for the L1 decision allows the trigger rates to be kept at a manageable level while preserving the physics potential. Section 3.4 contains a more detailed description of the CMS Phase-2 tracker upgrade.

**Timing detector** An extra detector layer between the outer tracker and the ECAL is being considered [54]. This will provide extremely accurate time measurements in the range of 30 ps for each track. The detector in the barrel will be based on lutetium-yttrium orthosilicate crystals, activated with cerium (LYSO:Ce) and read out with SiPMs. The endcap region will use MIP-sensitive silicon technology arranged in a hermetic single layer. Several studies have demonstrated the advantages that the timing layer can bring to object reconstruction and physics analysis, such as improved

track and vertex reconstruction abilities, mitigate extreme pileup conditions, higher lepton efficiencies and diphoton vertex location, and improved jet identification.

Barrel calorimeters Data from LHC runs indicate that radiation damage to the EB and HB calorimeters will be acceptable for full HL-LHC operations [55]. The upgraded HCAL detector is planned to be harder to radiation damage. The lead tungsten crystals in the ECAL are cooled down to a lower temperature. To maintain the exact same physics performance, the FE electronics of both sub-detectors must be improved to meet the new L1 trigger requirements. Furthermore, in the case of the EB, the new FE boards will enable the use of information from single crystals in the L1 trigger, providing more precise timing resolution and aiding in the reduction of photodetector noise.

Endcap calorimeters Endcap electromagnetic and hadronic calorimeters will suffer significant radiation damage and therefore replaced during the LS3 [56]. The new detector will be a sampling calorimeter with electromagnetic and hadronic sections that have excellent transverse and longitudinal segmentation, known as a High Granularity Calorimeter (HGC). The high granularity will allow for the reconstruction of a highly detailed 3D image of the electromagnetic and hadronic particle showers. A large portion of the endcap calorimeters use hexagonal silicon sensors with cell sizes ranging from 0.5 to  $1\,\mathrm{cm}^2$  as active elements, towards the back of the endcap in the z direction the calorimeter uses highly segmented scintillators with Silicon-Photo-Multiplier (SiPM) readout electronics.

**Muon detectors** Several studies have been conducted since 2015 to determine whether the current muon chambers can handle the increased particle rates of the HL-LHC [57]. Because no significant deterioration of key chamber parameters has been observed, the chambers can be used until the end of the HL-LHC operation. Some upgrades in the front end electronics are foreseen to improve radiation tolerance, readout speed, and performance. Furthermore, the muon system will be extended in the pseudorapidity region  $1.5 < |\eta| < 2.4$  with improved Resistive Plate Chambers (RPCs) and new chambers based on Gas Electron Multiplier (GEM) technology. The primary objectives of this forward upgrade are to add redundancy, improve triggering and reconstruction performance, and increase acceptance in the forward detector region.

**Trigger and data acquisition** Choosing interesting physics events at the L1 trigger stage becomes extremely difficult due to the increased trigger rate and greater complexity of the events in high pileup conditions. To meet the HL-LHC challenges,

the trigger and DAQ system will be upgraded [58], [59]. The L1 trigger latency will increase from approximately  $4\,\mu s$ , in the current system, to a maximum of  $12.5\,\mu s$ , allowing for track reconstruction in programmable hardware. Furthermore, the maximum readout rate will be increased to  $750\,kHz$  from the current  $100\,kHz$ . As a result, the trigger and DAQ system will be upgraded to accommodate the increased bandwidth and computing power required by the larger event sizes and the new L1 trigger rate.

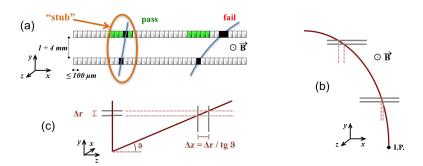

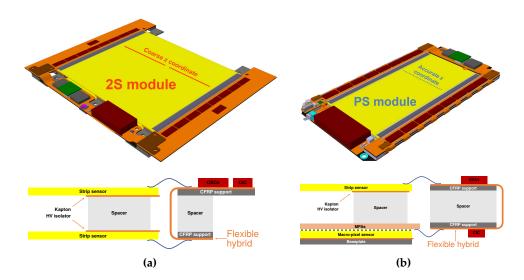

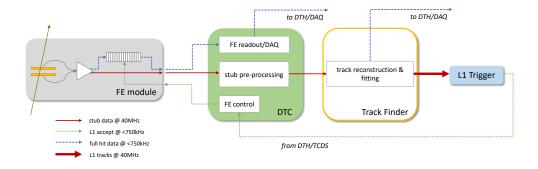

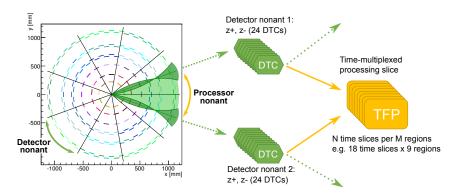

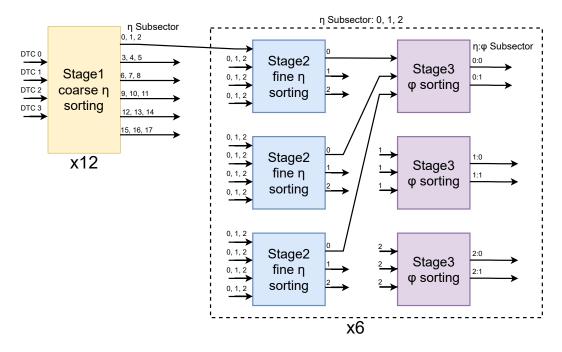

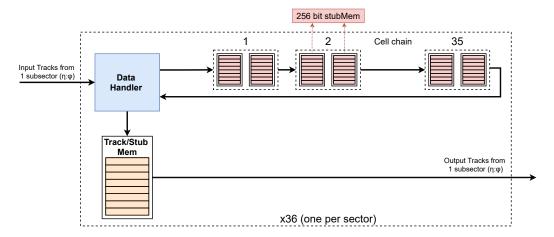

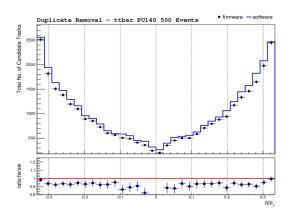

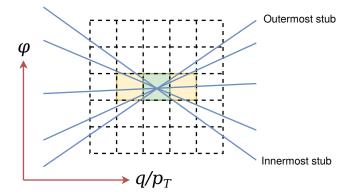

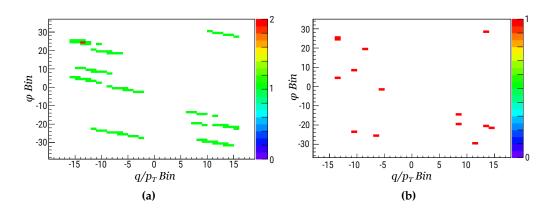

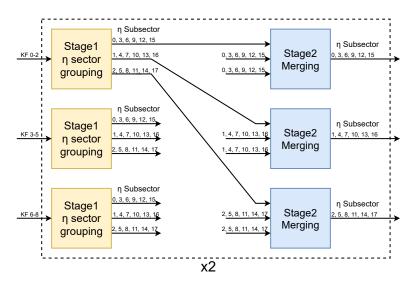

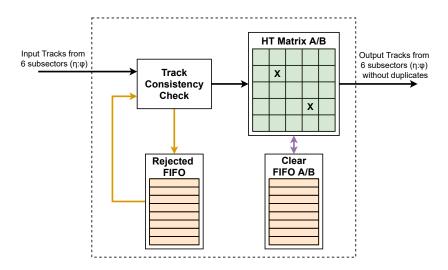

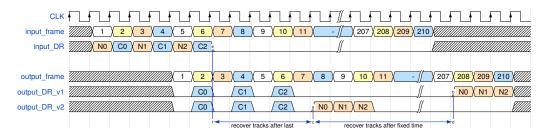

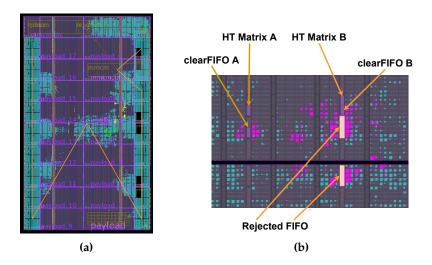

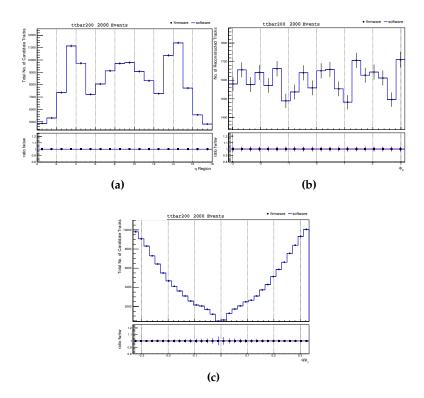

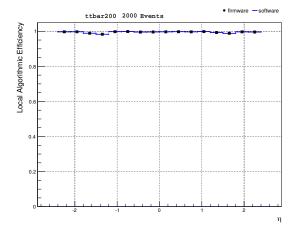

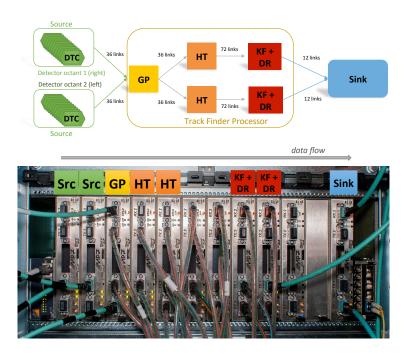

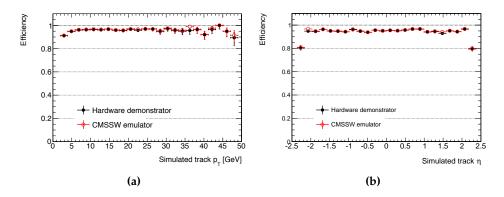

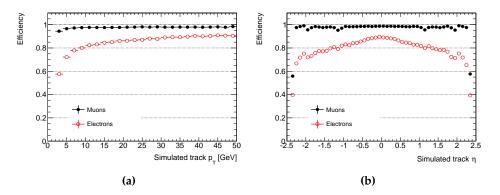

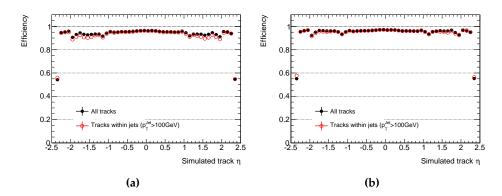

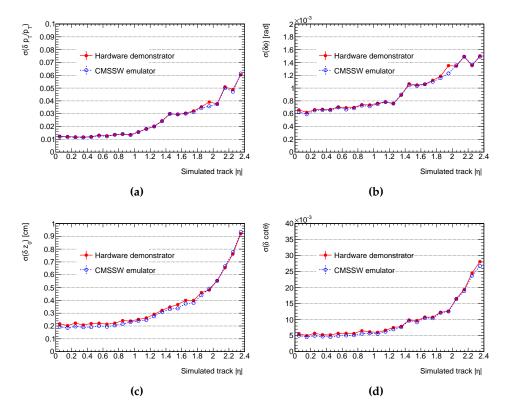

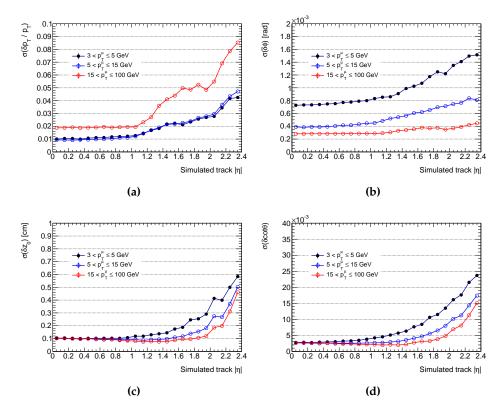

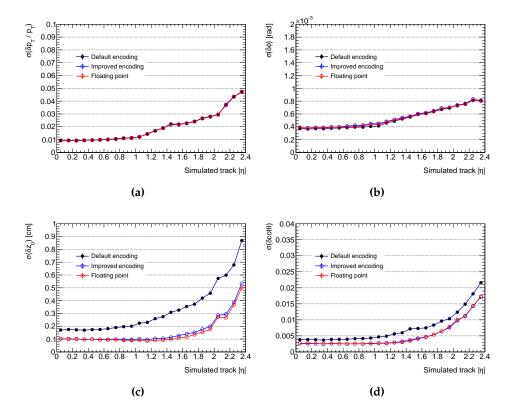

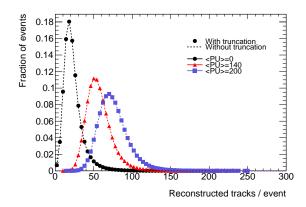

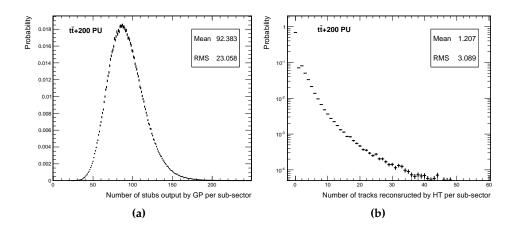

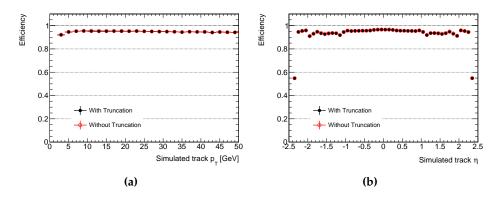

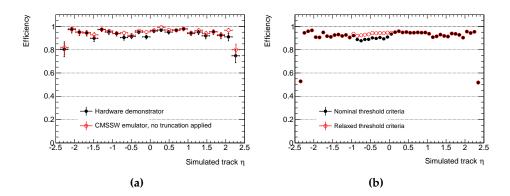

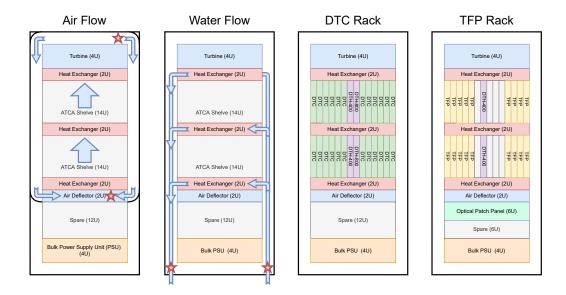

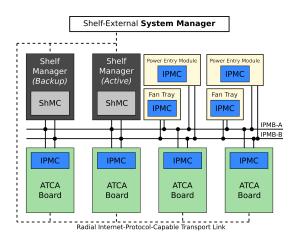

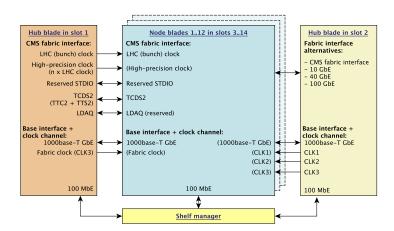

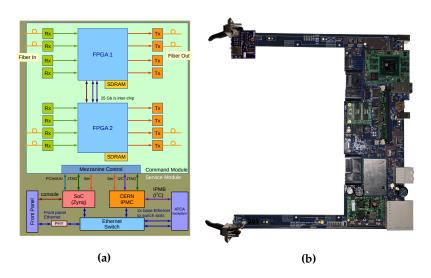

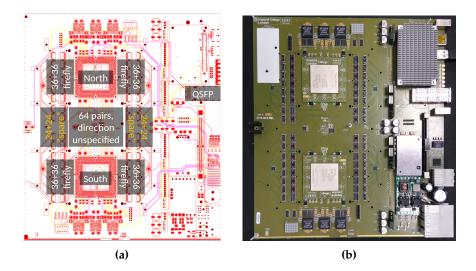

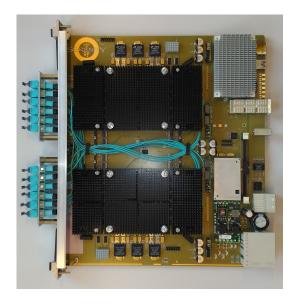

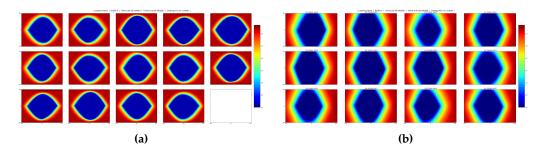

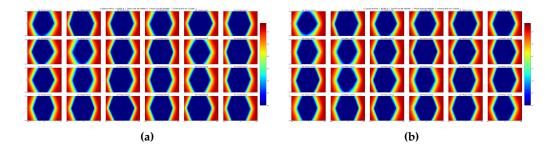

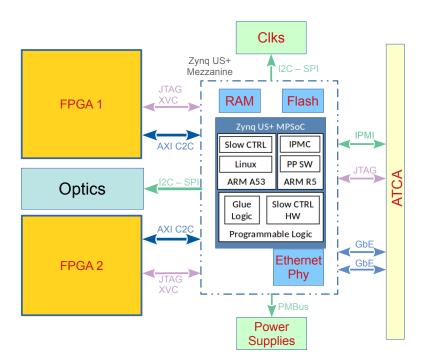

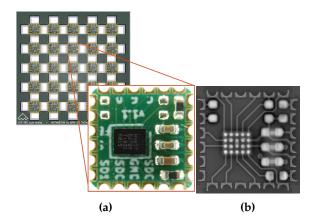

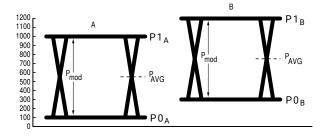

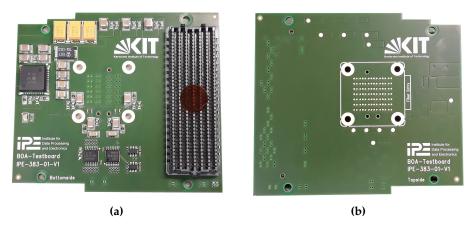

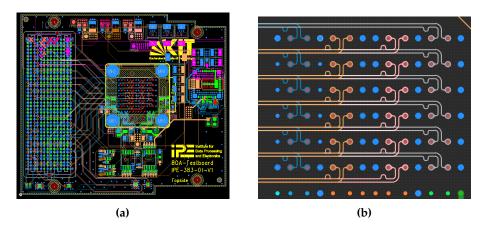

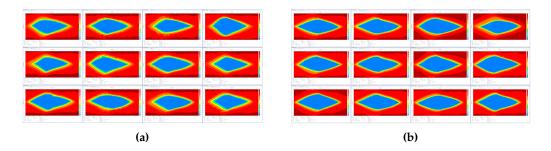

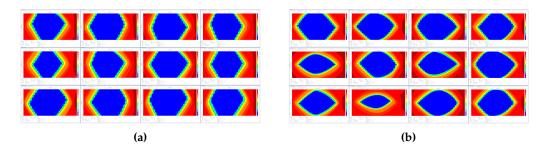

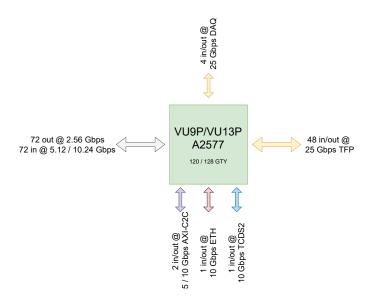

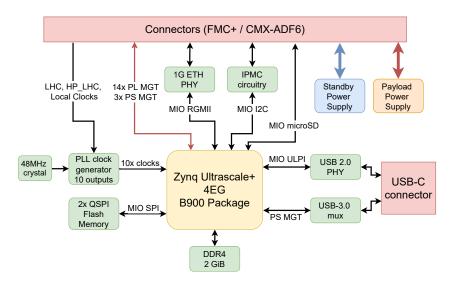

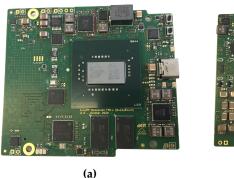

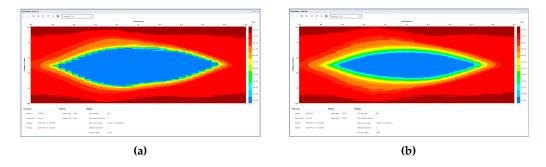

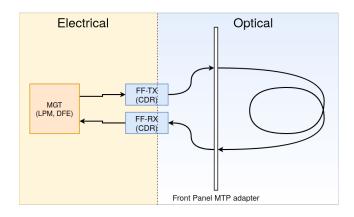

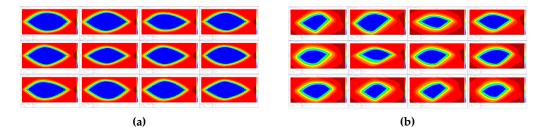

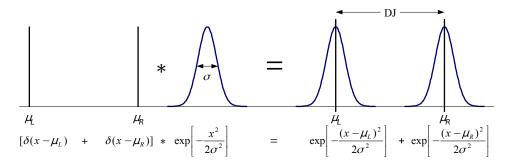

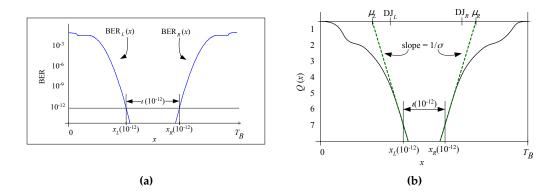

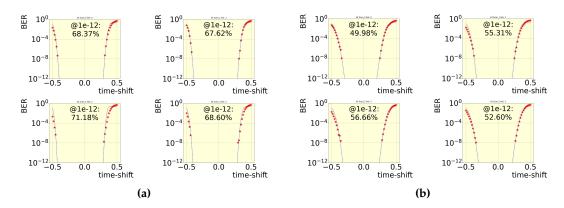

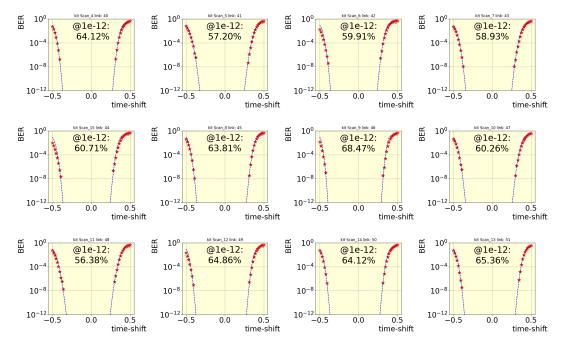

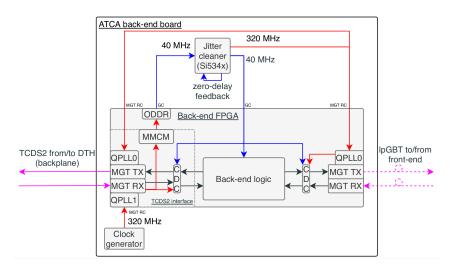

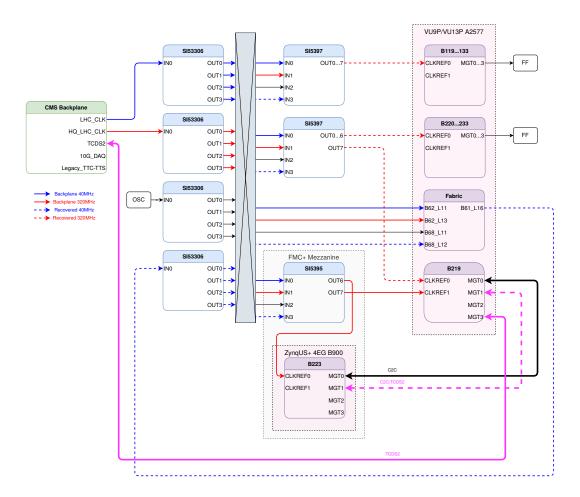

Figure 3.4: Functional diagram of the Phase-2 CMS L1 trigger system [60].