# Ausleseelektronik für magnetische Mikrokalorimeter im Frequenzmultiplexverfahren

Zur Erlangung des akademischen Grades eines

#### **DOKTOR-INGENIEURS**

von der KIT-Fakultät für Elektrotechnik und Informationstechnik des Karlsruher Instituts für Technologie (KIT)

genehmigte

#### DISSERTATION

von

M. Sc. Nick Karcher

geb. in Heidelberg

Tag der mündlichen Prüfung: 31.03.2022

Hauptreferent: Prof. Dr. Marc Weber

1. Korreferent: Prof. Dr.-Ing. Dr. h. c. Jürgen Becker

2. Korreferent: Priv.-Doz. Dr.-Ing. Oliver Sander

## Zusammenfassung

Magnetische Mikrokalorimeter (MMC) sind Tieftemperatur-Kalorimeter mit exzellenter Auflösung und hoher Linearität. Dadurch sind sie als Schlüsseltechnologie für eine Vielzahl an Experimenten und Instrumenten in der Grundlagenforschung prädestiniert. Das Sensorprinzip erfordert Betriebstemperaturen weit unter 100 mK. Bei einer großen Anzahl von mehreren hundert Detektoren mit paralleler Anbindung wird die Auslese zu einer hochgradig komplexen Aufgabe. Frequenzmultiplex-Verfahren wie der Mikrowellen-SQUID-Multiplexer sind in der Lage, die Auslese all dieser Detektoren mit wenigen Leitungen zu realisieren, und sind für MMCs geeignet. Die Auslese des Mikrowellen-SQUID-Multiplexers erfordert jedoch hohe Bandbreiten im Gigahertzbereich, leistungsfähige Hardware und mehrstufige Signalverarbeitung zur Datenreduktion. In der vorliegenden Arbeit wird erstmals ein optimiertes Raumtemperatur-Auslesesystem für 400 Multiplexer-Kanäle mit 4 GHz Bandbreite für MMCs vorgestellt. Ausgehend vom konzeptionierten Auslesesystem werden zwei Prototyp-Elektroniken realisiert und evaluiert. Mit dem Auslesesystem wurden in einem Testaufbau Energieauflösungen von 6,2 eV mit 16 und 10,7 eV mit 80 Kanälen im Bereich von 3,3 keV erreicht. Mit MMCs im Kryostaten und Achtkanalauslese wurden Auflösungen von 8,8 eV bei 5,9 keV erreicht. Die entwickelten Methoden und Prototypen werden darüber hinaus auf eine neuartige Multiplexer-Variante mit dc-SQUIDs übertragen und ferner wird eine Vierkanal-Auslese mit Tieftemperaturaufbau demonstriert. Mit den Ergebnissen der vorliegenden Arbeit steht nun ein hochoptimiertes Auslesesystem in einer ersten Version zur Verfügung.

#### **Abstract**

Magnetic calorimeters (MMC) are low-temperature calorimeters with excellent resolution and high linearity. This qualifies them as a key technology for a wide range of experiments and instruments in fundamental research. The detection principle requires temperatures far below 100 mK. With a large number of several hundred detectors with parallel interfacing, readout becomes a highly complex task. Frequency division multiplexing techniques such as the microwave SOUID multiplexer are able to realize the acquisition all these detectors with few readout lines and are suitable for MMCs. However, the readout of the microwave SOUID multiplexer requires high bandwidths in the gigahertz range, powerful hardware, and multistage signal processing for data reduction. In this thesis, an optimized room-temperature readout system for 400 multiplexer channels with 4 GHz bandwidth for MMCs is presented. Two prototype electronics are implemented and evaluated from the conceptualized readout system. The readout system shows energy resolutions of 6,2 eV with 16 and 10,7 eV with 80 channels in the range of 3,3 keV in a test setup. With MMCs in a cryostat, resolutions of 8,8 eV at 5,9 keV were achieved in an eight channel readout. The developed methods and prototypes are further applied to a novel multiplexer variant with dc-SQUIDs, and furthermore, a fourchannel readout with low-temperature setup is demonstrated. With the results of this thesis, a highly optimized fully functional readout system is now available in a first version.

## **Danksagung**

Die vorliegende Arbeit entstand in den Jahren 2017-2022 am Institut für Prozessdatenverarbeitung und Elektronik des Karlsruher Institut für Technologie. Ich möchte mich bei allen Personen bedanken, die in diesen Jahren auf vielfältige Weise zum erfolgreichen Abschluss dieser Arbeit beigetragen haben.

Mein allererster Dank gilt Herrn Prof. Marc Weber. Durch seine Unterstützung war es mir möglich, auf dem Gebiet der Auslese supraleitender Schaltkreise zu forschen und den vielschichtigen Entwicklungsprozess von Datenerfassungsystemen zu begleiten. Auch möchte ich mich bei Herrn Prof. Jürgen Becker für die Übernahme des Zweitgutachtens für diese Arbeit bedanken. Einen maßgeblichen Beitrag zum Gelingen dieser Arbeit leistete Oliver Sander. Die tiefgreifenden technischen Diskussionen und die hervorragende persönliche Betreuung werden mir über die Doktorarbeit hinaus positiv im Gedächtnis bleiben.

Ein umfangreicher Dank gilt den Kooperationspartnern am Kirchhoff-Institut für Physik in Heidelberg: Prof. Christian Enss und Daniel Richter; und am Institut für Mikro- und Nanoelektronische Systeme in Karlsruhe: Prof. Sebastian Kempf und Mathias Wegner. Ohne ihr Engagement bei den Messungen und die kompetente technische und fachliche Unterstützung zu den Kalorimetern und den Multiplexern wäre die Entwicklung des Auslesesystems in dieser Form nicht möglich gewesen.

Weiterhin möchte ich mich bei allen meinen Kollegen bedanken: Richard Gebauer für den Gedankenaustausch zu diversen Softwareentwicklungen und die ergiebigen und unterhaltsamen Diskussionen. Robert Gartmann für die technische Unterstützung bei zahlreichen Messungen und die Bereitstellung seiner Hochfrequenzelektronik. Oliver Krömer für den fachlichen Austausch. Michael Schleicher, Alexander Bacher und Uwe Bauer für deren hilfsbereiten Einsatz bei Layout, Herstellung und Inbetriebnahme der Elektronik. An dieser Stelle möchte ich mich auch für die unzähligen, wichtigen Beiträge aller Studenten bedanken. Ohne deren Resultate aus Masterarbeiten und HiWi-Tätigkeiten wäre eine solch umfangreiche Entwicklung in dieser Zeitspanne nicht realisierbar gewesen.

Einen herzlichen Dank an die Karlsruher Schule für Elementarteilchen- und Astroteilchenphysik (KSETA) für den finanziellen Beitrag in den ersten Jahren der Promotion.

Ein besonderes Dankeschön gilt meinen Eltern und meiner Frau Ricarda für ihr offenes Ohr, ihre Geduld und uneingeschränkte Unterstützung. Auch möchte ich meiner Tochter Amelie danken für die vielen gelungenen, schönen Ablenkungen.

Heidelberg, 31. Mai 2022 Nick Karcher

# Inhaltsverzeichnis

| 1 | Einl                                                        | nleitung                                                                                                                                                                                                                                                                                                             |                                 |  |  |  |

|---|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|--|--|--|

| 2 | Mag<br>2.1<br>2.2<br>2.3<br>2.4                             | • • • • • • • • • • • • • • • • • • •                                                                                                                                                                                                                                                                                | 5                               |  |  |  |

|   | 2.5                                                         | Zusammenfassung                                                                                                                                                                                                                                                                                                      |                                 |  |  |  |

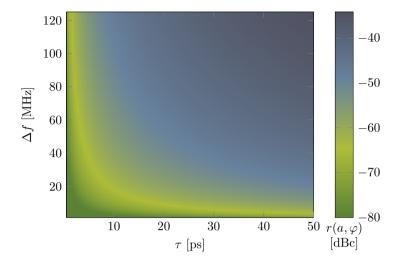

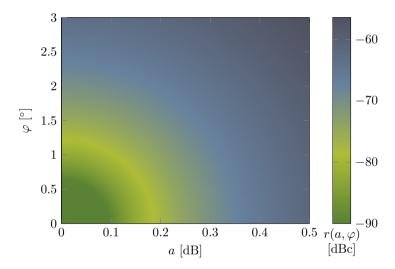

| 3 | 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6                      | Rauschleistung und Jitter                                                                                                                                                                                                                                                                                            | 7<br>1<br>5<br>1<br>5           |  |  |  |

| 4 | 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9 | lesekonzept und -elektronik47Multiplexer-Auslese mit SDR-System47Evaluierung existierender Ausleseelektroniken48Diskussion zu verfügbaren Elektroniken und ECHo-Anforderungen50Breitbandauslesesystem für ECHo53Hochfrequenzelektronik53Wandlerelektronik53Digitalelektronik63Hardware-Prototypen66Zusammenfassung68 | 7<br>8<br>0<br>3<br>5<br>7<br>5 |  |  |  |

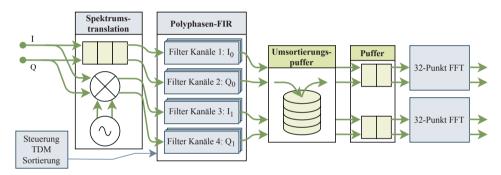

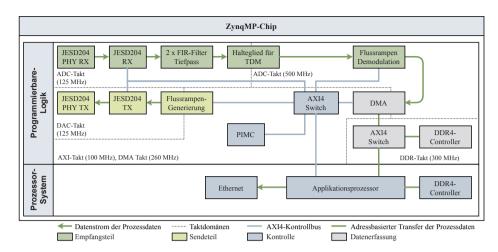

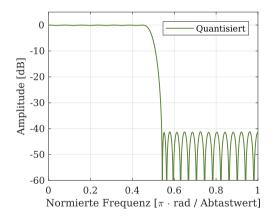

| 5 | <b>Digi</b> 5.1 5.2 5.3 5.4 5.5                             | tale Signalverarbeitung                                                                                                                                                                                                                                                                                              | 1<br>4<br>6<br>5                |  |  |  |

|     | 5.6                                        | Erkennung von Sensorereignissen            | 99  |  |  |  |  |  |

|-----|--------------------------------------------|--------------------------------------------|-----|--|--|--|--|--|

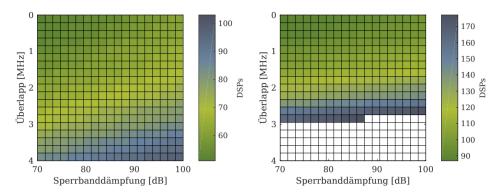

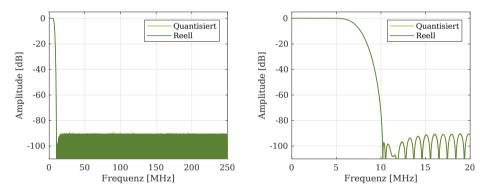

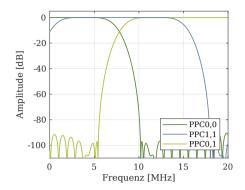

|     | 5.7                                        | Skalierbarkeit der Verarbeitungskette      | 106 |  |  |  |  |  |

|     | 5.8                                        | Zusammenfassung                            |     |  |  |  |  |  |

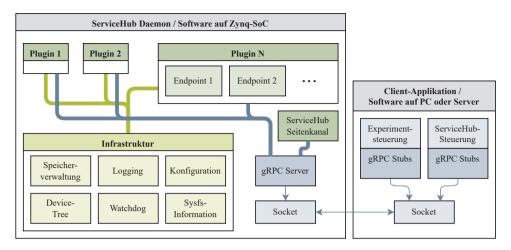

| 6   | Datenakquisition und Kontrollschnittstelle |                                            |     |  |  |  |  |  |

|     | 6.1                                        | Steuerungs- und Akquisitionsübersicht      | 111 |  |  |  |  |  |

|     | 6.2                                        | Sensordatenaggregation                     | 112 |  |  |  |  |  |

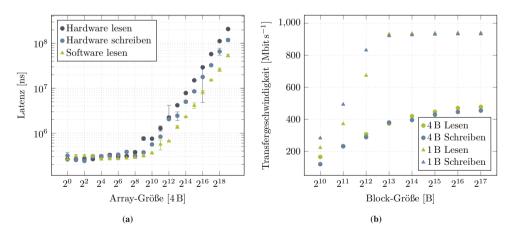

|     | 6.3                                        | Direct-Memory-Access                       | 114 |  |  |  |  |  |

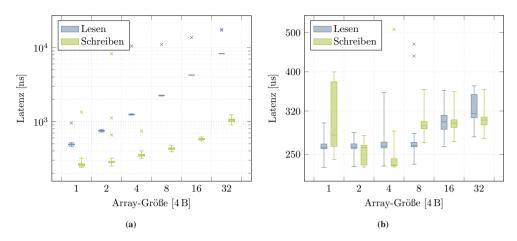

|     | 6.4                                        | Kontrollsoftware                           | 116 |  |  |  |  |  |

|     | 6.5                                        | Firmwareintegration                        | 124 |  |  |  |  |  |

|     | 6.6                                        | Zusammenfassung                            | 126 |  |  |  |  |  |

| 7   | Mes                                        | ssunganwendungen mit den Prototyp-Systemen | 127 |  |  |  |  |  |

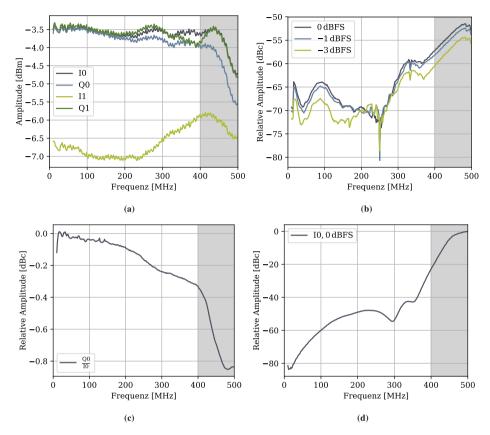

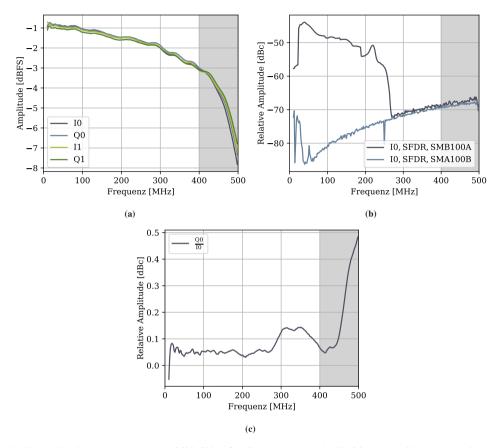

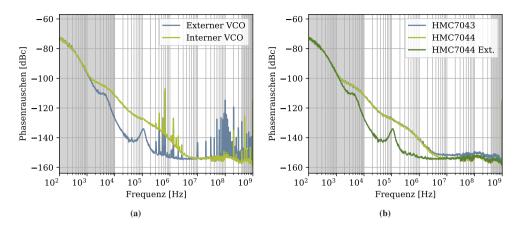

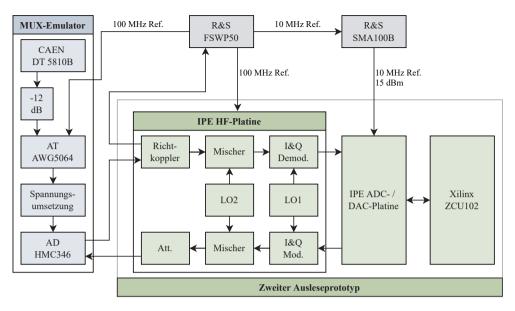

|     | 7.1                                        | Charakterisierung der Basisbandelektronik  | 127 |  |  |  |  |  |

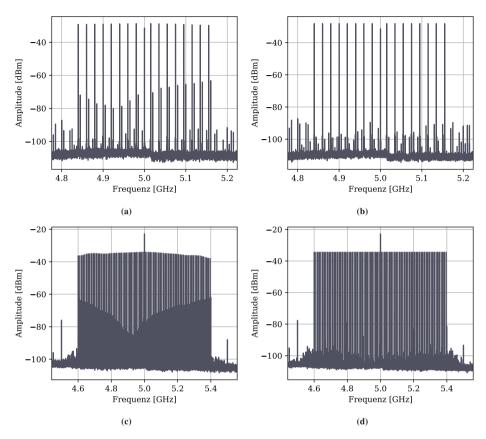

|     | 7.2                                        | Messungen mit Multiplexverfahren           | 132 |  |  |  |  |  |

|     | 7.3                                        | Messungen mit Tieftemperaturaufbau         | 145 |  |  |  |  |  |

|     | 7.4                                        | Bewertung des Systems                      | 147 |  |  |  |  |  |

|     | 7.5                                        | Zusammenfassung                            | 150 |  |  |  |  |  |

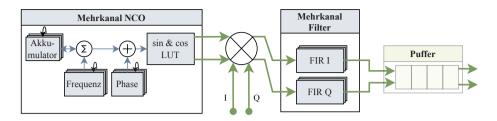

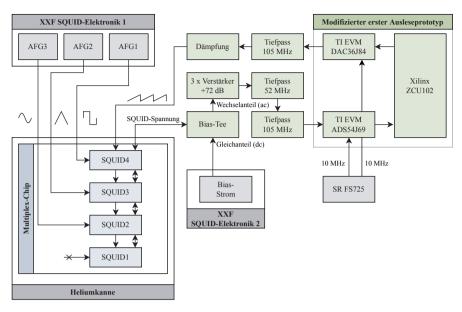

| 8   | Free                                       | Frequenzmultiplex mit dc-SQUIDs            |     |  |  |  |  |  |

|     | 8.1                                        | Theorie zum Multiplexverfahren             | 151 |  |  |  |  |  |

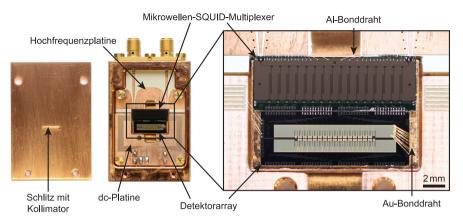

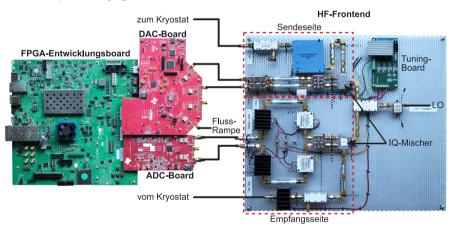

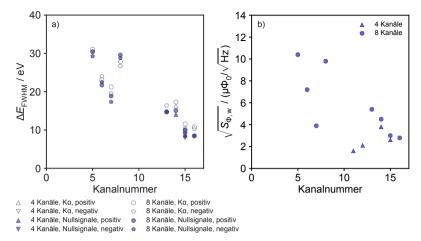

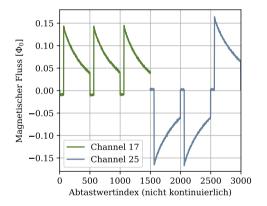

|     | 8.2                                        | Auslesehardware und Messprototyp           | 153 |  |  |  |  |  |

|     | 8.3                                        | Signalverarbeitungskette                   |     |  |  |  |  |  |

|     | 8.4                                        | Messung mit Frequenzmultiplex              |     |  |  |  |  |  |

|     | 8.5                                        | Bewertung des Systems                      |     |  |  |  |  |  |

|     | 8.6                                        | Zusammenfassung                            |     |  |  |  |  |  |

| 9   | Faz                                        | it und Ausblick                            | 165 |  |  |  |  |  |

| Lit | terati                                     | ur                                         | 167 |  |  |  |  |  |

|     |                                            |                                            |     |  |  |  |  |  |

| Ei  | gene                                       | Publikationen                              | 179 |  |  |  |  |  |

| Ve  | rzeic                                      | chnisse                                    | 181 |  |  |  |  |  |

|     | Abk                                        | ürzungsverzeichnis                         | 181 |  |  |  |  |  |

|     | Abb                                        | ildungsverzeichnis                         | 185 |  |  |  |  |  |

|     | Tabe                                       | ellenverzeichnis                           | 189 |  |  |  |  |  |

| Α   | Anh                                        | nang                                       | 191 |  |  |  |  |  |

|     | A.1                                        | Herleitungen und Berechnungen              | 191 |  |  |  |  |  |

|     | A.2                                        | Datenauswertung                            | 193 |  |  |  |  |  |

|     | A.3                                        | Tabellen                                   | 196 |  |  |  |  |  |

|     | A.4                                        | Grafiken                                   | 199 |  |  |  |  |  |

# 1 Einleitung

Sensoren sind essentiell für die Beobachtung unserer Natur und Erforschung vielfältiger Phänomene. Ihre Auflösung bestimmt, wie genau Messungen durchgeführt werden können, und entscheidet darüber, ob ein Phänomen messbar ist. Energiesensoren, sogenannte Kalorimeter, messen Energie, welche beispielsweise durch einen physikalischen Prozess wie einer Teilchenabsorption in Wärme umgewandelt wird. Zur Detektion niederenergetischer Elementarteilchen oder zur Auflösung kleinster Energieunterschiede bei hoher Energie werden hochpräzise Kalorimeter benötigt.

Tieftemperatur-Mikrokalorimeter sind Detektoren, die nahe des absoluten Nullpunkts betrieben werden. Die tiefen Temperaturen im Millikelvinbereich erlauben den Einsatz spezieller Sensorprinzipien, geringes thermisches Rauschen und den Einsatz rauscharmer Verstärker. Dadurch werden Auflösungen von bis zu 1,6 eV bei 6 keV erreicht [1, 2]. Dies unterschreitet die theoretisch erreichbare Auflösung von vergleichbaren Halbleitersensoren um etwa zwei Größenordnungen [3]. Beispiele sind die Kalorimeter mit Transition-Edge-Sensoren (TES), welche Energie über den Phasenübergang eines Supraleiters detektieren [4], und magnetische Mikrokalorimeter (MMC), welche Energie über eine Magnetisierungsänderung eines paramagnetischen Materials bestimmen [5]. Durch die hohen Auflösungen bieten sich die Sensortypen für verschiedenste Experimente und Instrumente an [1, 2].

Für viele Anwendungen der Kalorimeter ist eine räumliche Auflösung [6] für beispielsweise Bildsensoren oder eine hohe Ereignisrate notwendig, um hochauflösende Spektrographie in kurzer Messzeit zu erlauben [7, 8]. Beides erfordert Mehrsensor-Systeme mit hunderten bis zu zehntausenden Sensoren. Die parallele Anbindung der Sensoren in der Millikelvin-Stufe im Kryostaten an die Raumtemperatur-Auslese ist bei einer größeren Anzahl von Sensoren jedoch platz- und kostenintensiv, führt zu einem großen Wärmeeintrag und ist daher nicht praktikabel [9]. Ein vielversprechender Ansatz sind Multiplexmethoden, welche die Signale mehrerer Sensoren auf einem gemeinsamen Übertragungskanal vereinen. Neben dem Zeit- [10] und Codemultiplex [11] stellt der Frequenzmultiplex [12] eine attraktive Möglichkeit dar, die Anzahl der Verbindungen zwischen der Tieftemperatur- und Raumtemperaturelektronik erheblich zu reduzieren. Dabei werden die verschiedenen Sensorsignale auf unterschiedliche Intervalle des Frequenzspektrums des Auslesekanals verteilt. Dies ermöglicht eine gemeinsame Übertragung der Signale von hunderten bis tausenden Kanälen auf einer einzigen Rückleitung [13].

Eine aussichtsreiche Implementierungsvariante ist der Mikrowellen-SQUID-Multiplexer, der die Sensorsignale in die Resonanzverstimmung eines Mikrowellenresonators umsetzt. Der Resonator moduliert dadurch ein kontinuierliches Anregungssignal mit dem Sensorsignal [12, 14]. Eine weitere, neuartige Variante stellt der Frequenzmultiplexer mit dc-SQUIDs dar. Dieser nutzt die Periodizität der sinus-ähnlichen SQUID-Kennlinie, um Spannungssignale mit unterschiedlicher Frequenz zu erzeugen. Die Sensorsignale werden hierbei auf die Phasen der Spannungssignale moduliert [15].

Die erste Anwendung, in der der Frequenzmultiplex für MMCs zur Aufzeichung von Röntgenspektren eingesetzt werden soll, ist das Electron Capture in Holmium-163 (ECHo) Experiment [8]. ECHo untersucht die Masse des Elektron-Neutrinos durch die Auswertung des Energiespektrum des <sup>163</sup>Ho-Zerfalls. Das Spektrum wird mit 10<sup>4</sup> Sensoren mit einer Ereignisrate von 100 Kilobecquerel aufgezeichnet. Die Auslese für ECHo stellt hohe Bandbreitenanforderungen an das Messsystem. So wird beim Experiment ein Multiplex von 4 bis 8 GHz mit 4 GHz Echtzeitbandbreite angestrebt, um 800 Sensoren über 400 Resonatorkanäle auszulesen. Für die Auslese der analogen Signale werden eine Hochfrequenzelektronik, schnelle AD- und DA-Wandler benötigt. Der dabei zu erwartende Datenstrom liegt im Bereich von 100 Gbit s<sup>-1</sup> und kann durch stark parallelisierte Digitalelektronik wie Field-Programmable-Gate-Arrays (FPGAs) effizient verarbeitet werden.

Die vorliegende Arbeit untersucht Technologien und Methoden für die Auslese von MMCs mit Frequenzmultiplexverfahren. Der Mikrowellen-SQUID-Multiplexer und der dc-SQUID-Frequenzmultiplexer für MMCs sind zum Zeitpunkt dieser Arbeit völlig neue Technologien und ein breitbandiges Auslesesystem existiert bisher nicht. Ein Fokus dieser Arbeit liegt dabei auf der Entwicklung eines Auslesesystems für das ECHo-Experiment, welches Mikrowellen-SQUID-Multiplexer verwendet. Außerdem wird die Übertragung der entwickelten Komponenten auf den Multiplexer mit dc-SQUID-Verfahren diskutiert. Dabei geht die Arbeit auf die Fragestellungen ein, wie und mit welcher Segmentierung und mit welchen Hardware- und Firmwarebestandteilen ein breitbandiges Auslesesystem realisiert werden kann. Ein besonderes Augenmerk liegt zudem auf der digitalen Signalverarbeitungskette, die aus dem großen Eingangsdatenstrom die Sensorsignale in Echtzeit extrahieren und somit die Datenrate um Größenordnungen reduzieren kann. Weiterhin wird eine Software zur einfachen Konfiguration, zur Kalibrierung und zur Nutzung des Systems im Experiment entworfen und implementiert. Mit der entwickelten Firmware und Hardware wird ein Ausleseprototyp aufgebaut und erfolgreich evaluiert, der 80 Resonatorkanäle auslesen kann und sich auf 400 Kanäle hochskalieren lässt.

# 2 Magnetische Mikrokalorimeter und Multiplexverfahren

Für die Auslese der magnetischen Mikrokalorimeter ist ein grundlegendes Verständnis der Kalorimeter und des eingesetzten Multiplexverfahrens erforderlich. Dazu geht dieses Kapitel auf die in der Auslese verwendeten Quanteneffekte ein und behandelt die magnetischen Kalorimeter mit der klassischen Einkanal-Auslese sowie die Mehrkanalauslese mittels verschiedener Multiplexmethoden. Hierbei liegt der Fokus auf dem Frequenzmultiplex, welcher in Kombination mit dem in dieser Arbeit entwickelten Auslesesystem zur Anwendung kommt. Im Anschluss wird das ECHo-Experiment vorgestellt, welches als erstes Experiment eine große Anzahl von magnetischen Mikrokalorimetern in Kombination mit einem Frequenzmultiplex einsetzt.

## 2.1 Josephson-Kontakte und SQUIDs

Tieftemperatur-Kalorimeter sind häufig auf supraleitende Elemente angewiesen [3]. Beispiels-weise beruht das Sensorprinzip beim Transition-Edge-Sensor (TES) auf dem Übergang vom supraleitenden in den normalleitenden Zustand eines Materials und die Auslese der Kalorimeter stützt sich auf rauscharme supraleitende Quanteninterferenzdetektoren (SQUIDs). In diesem Sinne wird zunächst auf die Supraleitung eingegangen und danach auf die Quanteneffekte im Josephson-Kontakt und im SQUID.

#### 2.1.1 Supraleiter

Im Jahr 1911 konnte *Heike Kamerlingh Onnes* bei Widerstandmessreihen eines Quecksilberdrahtes bei tiefen Temperaturen ( $T = 4,15 \, \mathrm{K}$ ) eine sehr starke und sprunghafte Zunahme der Leitfähigkeit feststellen. Die damals entdeckte Supraleitung war ein vollständig überraschendes Phänomen und einer der ersten gemessenen Quanteneffekte überhaupt. Onnes erhielt für seine Arbeiten im Jahr 1913 den Nobelpreis. Das entdeckte Phänomen war zu diesem Zeitpunkt nicht theoretisch erklärbar und wurde erst 1957 durch die *BCS-Theorie*, benannt nach

Abbildung 2.1: Magnetfelder in Supraleitern des ersten Typs (links) und des zweiten (rechts) [16].

den Physikern *Bardeen*, *Cooper* und *Schrieffer*, mikroskopisch beschrieben. Seit der Entdeckung des ersten Supraleiters wurden zahlreiche weitere supraleitende Materialien gefunden und erforscht [16].

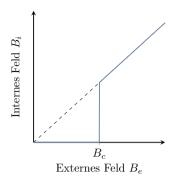

Supraleiter verlieren unterhalb ihrer Sprungtemperatur T<sub>c</sub> ihren elektrischen Gleichstrom-Widerstand. Die zugrundeliegenden Phänomene in den verschieden Supraleitern sind komplex und können nach Hirsch in 32 verschiedene Kategorien eingeteilt werden [17]. Näher betrachtet wird die Aufteilung in Typ I und Typ II bei konventionellen Supraleitern. Setzt man einen Supraleiter einem Magnetfeld aus, induziert dieses Abschirmströme an der Oberfläche des Materials. Dadurch entsteht innerhalb des Supraleiters ein entgegengesetztes Magnetfeld, welches das äußere Feld kompensiert. Das Material wirkt als perfekter Diamagnet; die magnetischen Feldlinien umströmen das Objekt. Dieser Effekt wurde durch Meissner und Ochsenfeld entdeckt und wurde nach den Entdeckern benannt. Die Abschirmströme bewirken einen exponentiellen Abfall des Magnetfelds an der Oberfläche des Supraleiters gemäß der London-Gleichungen [18]. Supraleiter des ersten Typs können den supraleitenden Zustand innerhalb eines Magnetfelds aufrechterhalten, bis die kritische Feldstärke  $B_c$  erreicht wird, danach bricht die Supraleitung zusammen. In Supraleitern des zweiten Typs gibt es zwei kritische Feldstärken  $B_{c1} < B_{c2}$  (vgl. Abbildung 2.1) [16]. Nach dem Überschreiten von  $B_{c1}$ kann das Magnetfeld in Form von Flussschläuchen in das Material eindringen, die wesentlichen supraleitenden Eigenschaften bleiben aber weiterhin erhalten. Bei der zweiten kritischen Feldstärke  $B_{c2}$  geht der Effekt der Supraleitung verloren. Die kritische Feldstärke definiert gleichzeitig die maximale Suprastromdichte des Supraleiters.

Konventionelle Supraleiter lassen sich nach der BCS-Theorie erklären [19]. Die BCS-Theorie beschrieb die Supraleitung erstmals auf mikroskopischer Ebene als einen Vielteilchenzustand. Durch die tiefen Temperaturen spielt die thermische Gitterschwingung eine untergeordnete Rolle und Elektronen können sich durch den Austausch von virtuellen Phononen zu sogenannten *Cooper-Paaren* verbinden. Der Zwei-Teilchen-Zustand führt dazu, dass diese Teilchen

einen ganzzahligen Spin annehmen. Daher zählen Cooper-Paare nicht mehr zur Klasse der Fermionen, sondern formen virtuelle Bosonen. Diese unterliegen nicht mehr dem *Pauliprinzip*, nach dem zwei Elektronen nicht in allen Quantenparametern übereinstimmen können. Durch die Bindungsenergie der Cooper-Paare entsteht im Zustandsraum des Supraleiters eine Energielücke zwischen dem niedrigem Energieniveau der Cooper-Paare und angeregter Zustände in höheren Energieniveaus [20]. Im Unterschied zu normalen Leitern können die Elektronen der Cooper-Paare nur mit einer Energie angeregt werden, die zumindest der Energielücke entspricht [16]. Liegt die Energie durch zufällige Streuung am Atom-Gitter darunter, führt dies zu einem verlustfreien Strom durch das Material. Als Bosonen können Cooper-Paare über dem Supraleiter, ähnlich wie Photonen über dem Raum, eine gemeinsame Wellenfunktion ausbilden [16]:

$$\Psi(r) = \Psi_0 e^{j\varphi(r)} \tag{2.1}$$

Die Supraleitung kann somit als makroskopischer Quantenzustand angesehen werden. Dieser definiert sich durch die Amplitude beziehungsweise Cooperpaardichte  $|\Psi_0|^2=n_s$  und die ortsabhängige Phase  $\varphi(r)$ . Diese Wellenfunktion erstreckt sich makroskopisch über das supraleitende Objekt.

Die Anwendung von Supraleitern erfordert neben der supraleitenden Eigenschaft auch spezielle Werkstoffeigenschaften; so müssen die Supraleiter für die Herstellung von SQUIDs und Mikrokalorimetern mikrostrukturierbar sein. Hierfür wird heutzutage sehr häufig Niob eingesetzt. Dieses Element weist eine Sprungtemperatur von 9,2 K auf und kann somit mit flüssigem Helium (T=4,2 K) gekühlt werden. Die kritische Stromdichte von über 2 MA cm $^{-1}$  der Supraleitung in Niob [21] erlaubt es dabei, die für den Betrieb von magnetischen Mikrokalorimetern benötigten hohen kritischen Ströme mit Leiterbahnen mit nur wenigen Mikrometern Strukturbreite zu erreichen. Weiterhin lässt Niob sich als Metall durch Sputtern auf Silizium- oder Saphir-Wafer aufbringen und kann mit gängigen Techniken der Mikrofabrikation verarbeitet werden. Dies ermöglicht beispielsweise die Herstellung von Josephson-Kontakten.

#### 2.1.2 Josephson-Kontakte

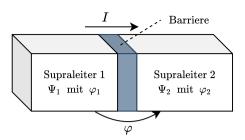

Der *Josephson*-Kontakt ist ein Verbund aus zwei Supraleitern, die durch eine sehr dünne Barriere, wie beispielsweise einen Isolator, räumlich voneinander getrennt sind (vgl. Abbildung 2.2). Dieser SIS-Kontakt (Supraleiter-Isolator-Supraleiter) ermöglicht ein kohärentes Tunneln der Cooper-Paare zwischen den zwei Supraleitern, falls die Schichtdicke des Isolators in der Größenordnung von ca. 1 nm liegt [16]. Durch die Isolationsschicht sind die makroskopischen Wellenfunktionen der zwei Supraleiter nicht starr gekoppelt wie bei einem direkten Kontakt der Materialien. Die an einer solchen Verbindung auftretenden Effekte wurden durch *Josephson* vorausgesagt [22].

Abbildung 2.2: Topologie eines Josephson-Kontakts

Der Kontakt ist durch einen kritischen Strom  $I_c$  charakterisiert. Dieser hängt von den Cooper-Paar-Dichten der zwei Supraleiter, deren Abstand zueinander und der Fläche des Kontakts ab. Ströme kleiner als  $I_c$  werden vollständig von Cooper-Paaren getragen und passieren daher den Josephson-Kontakt ohne einen Spannungsabfall zu erzeugen. Dies wird als Gleichstrom-Josephson-Effekt bezeichnet. Durch den angelegten Strom werden die Phasen der zwei Supraleiter  $(\varphi_1, \varphi_2)$  gegeneinander verschoben gemäß [22, 23]:

$$I_{\rm s} = I_{\rm c} \sin \varphi$$

, wobei  $\varphi = \varphi_2 - \varphi_1$  (2.2)

Wird der Strom über den kritischen Strom  $I_c$  hinaus weiter erhöht, kann der Strom nicht mehr allein durch die Cooper-Paare getragen werden und es fällt eine Spannung über dem Kontakt ab. Der Strom setzt sich aus dem Tunnelstrom aus Cooper-Paaren und aufgebrochenen Cooper-Paaren (Quasiteilchen) durch den Kontakt zusammen. Die zeitliche Entwicklung der Phasendifferenz über dem Josephson-Kontakt steht allein in Abhängigkeit zu der entstehenden Spannung [22]:

$$\frac{\partial \varphi}{\partial t} = \frac{2\pi}{\Phi_0} U \tag{2.3}$$

Hierbei bezeichnet  $\Phi_0 \approx 2,07 \cdot 10^{-15} \, \text{T m}^2$  das magnetische Flussquant. Bei einem konstanten Spannungsabfall über dem Josephson-Kontakt oszilliert aufgrund der sich zeitlich ändernden Phasendifferenz nach Gleichung 2.3 der durch die Cooper-Paare getragene Stromanteil. Dies wird als Josephson-Wechselstrom-Effekt bezeichnet. Der entstehende Strom

$$I_{\rm s.ac} = I_{\rm c} \sin(\omega_{\rm J} t - \varphi_0) \tag{2.4}$$

liegt mit  $\omega_{\rm J}=2\pi U\Phi_0^{-1}$  schon bei kleinen Spannungen von einigen Mikrovolt im Gigahertz-Bereich [16]. Dieser Effekt erlaubt es umgekehrt unter dem Einfluss von Mikrowellenstrahlung eine sehr genaue Gleichspannung zu erhalten [24] (inverser Wechselstrom-Josephson-Effekt).

Die Phasen-Spannungs-Relation aus Gleichung 2.3 gilt ebenfalls beim Anlegen eines Wechselstroms durch den Kontakt. Das Verhältnis zwischen einer zeitlichen Änderung des Stroms

und einer daraus resultierenden Spannungsänderung über dem Josephson-Kontakt kann als nicht-lineare Induktivität  $L_{\rm JJ}$  abhängig von der Phase und der Josephson-Induktivität  $L_{\rm J}$  beschrieben werden [23]:

$$U = L \frac{\partial I}{\partial t} \stackrel{(2.2)}{\Rightarrow} L_{\rm JJ} = L_{\rm J} \frac{1}{\cos \varphi} , \text{wobei } L_{\rm J} = \frac{\Phi_0}{2\pi I_c}$$

(2.5)

#### 2.1.3 Supraleitender Quanteninterferenzdetektor (SQUID)

Im Kontrast zu der einfach zusammenhängenden Topologie eines Supraleiters, welche ein magnetisches Feld im Inneren verdrängt, ist der durch einen geschlossenen, supraleitenden Ring fließende magnetische Fluss eine Erhaltungsgröße. Dieser Fluss wird durch die auftretenden Abschirmströme an der Oberfläche des supraleitenden Rings aufrechterhalten. Die makroskopische Wellenfunktion des Supraleiters (vgl. Gleichung 2.1) setzt voraus, dass die Phase  $\varphi$  über dem Supraleiter wohldefiniert ist. Daraus resultiert, dass die durch den Abschirmstrom entstehende Phasendrehung über dem Ring sich um Vielfache n von  $2\pi$  ändern muss [16]. Der Zusammenhang zwischen Phase und Stromdichte ist somit quantisiert und definiert einen magnetischen Fluss

$$\Phi = n \frac{h}{2e} = n\Phi_0 \ , \ n \in \mathbb{N}$$

(2.6)

durch den supraleitenden Ring. Der Fluss ist mit  $\Phi_0$ , dem magnetischen Flussquant, quantisiert.

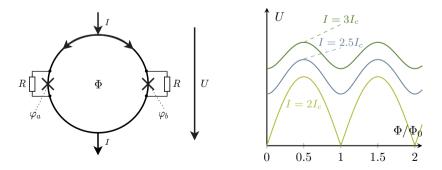

Falls der supraleitende Ring durch zwei Josephson-Kontakte unterbrochen wird, trennt sich die Wellenfunktion in zwei schwach gekoppelte Wellenfunktionen über die beiden Schenkel des Rings (siehe Abbildung 2.3). Diese Struktur wird supraleitender Quanteninterferenzdetektor (SQUID, engl. superconducting quantum interference device), oder auch dc-SQUID genannt.

Abbildung 2.3: Schematische Darstellung eines dc-SQUIDs (links) mit Shuntwiderständen parallel zu den Josehpshon-Kontakten, Fluss-Spannungs-Kennlinie des dc-SQUIDs bei verschiedenen Bias-Strömen (rechts).

Wird das dc-SQUID an eine Stromquelle angeschlossen, kann mithilfe der Gleichung des Josephson-Kontakts (2.2) der von Cooper-Paaren getragenen Stromanteil für identische Kontakte

$$I = I_{c}(\sin \varphi_{a} + \sin \varphi_{b}) = 2I_{c}\sin \frac{\varphi_{a} + \varphi_{b}}{2}\cos \frac{\varphi_{a} - \varphi_{b}}{2}$$

(2.7)

berechnet werden, der sich aus den zwei Strömen durch die Schenkel zusammensetzt. In Anwesenheit eines externen magnetischen Flusses  $\Phi_{\rm ext}$ , welcher den Ring durchströmt, wird ein Strom im Ring induziert. Dieser Strom führt zu einer Änderung der Phasendifferenzen an den Kontakten. Mittels Integration über die Kontur des Rings kann der Phasenunterschied in Abhängigkeit des gesamten magnetischen Flusses durch das dc-SQUID berechnet werden:

$$\varphi_{\rm b} - \varphi_{\rm a} = \frac{2\pi\Phi}{\Phi_0} \tag{2.8}$$

Eingesetzt in Gleichung 2.7 kann der maximale Suprastrom in Abhängigkeit vom magnetischen Fluss  $\Phi$ , der sich aus dem  $\Phi_{\rm ext}$  und dem Fluss durch die entstehenden Abschirmströme  $\Phi_{\rm L}$  zusammensetzt, ausgedrückt werden:

$$I_{\rm s} = 2I_{\rm c}\cos\frac{\pi\Phi}{\Phi_0}\sin\left(\varphi_{\rm a} + \frac{\pi\Phi}{\Phi_0}\right), \text{wobei } \Phi = \Phi_{\rm ext} + \Phi_{\rm L}$$

(2.9)

Wird der magnetische Fluss durch den Abschirmstrom vernachlässigt ( $\Phi \approx \Phi_{\rm ext}$ ), erhält man für die Flussabhängigkeit des maximalen Suprastroms Gleichung 2.9 nach [25]:

$$I_{\rm s,max} \approx 2I_{\rm c} \left| \cos \frac{\pi \Phi_{\rm ext}}{\Phi_0} \right|$$

(2.10)

Der externe magnetische Fluss  $\Phi_{\rm ext}$  wird somit mit dem Faktor  $\Phi_0^{-1}$  zu einer Stromänderung übersetzt; dadurch kann das SQUID für sehr genaue Messungen eines magnetischen Flusses eingesetzt werden. Um ein solches dc-SQUID als Magnetometer einzusetzen, kann beispielsweise der Strom I über eine externe Bias-Stromquelle eingestellt werden. Dieser liegt bei  $I \geq 2I_{\rm c}$  und bewirkt eine Spannung über dem SQUID. Die Fluss-Spannungs-Kennlinie kann für den vernachlässigten Fluss  $\Phi_L \ll \Phi_0$  und großer Kontaktdämpfung mit Parallelwiderstand R geschlossen ausgedrückt werden [25]:

$$V(\Phi_{\rm ext}) = I_{\rm c}R\sqrt{\left(\frac{I}{2I_{\rm c}}\right)^2 - \left(\cos\left(\frac{\pi\Phi_{\rm ext}}{\Phi_0}\right)\right)^2}$$

(2.11)

Die resultierende, nichtlineare periodische Fluss-Spannungs-Charakteristik ist in Abbildung 2.3 für verschiedene Bias-Ströme dargestellt. Das dc-SQUID-Magnetometer wird für die klassische Einkanalauslese und für das Multiplexverfahren in Kapitel 8 eingesetzt.

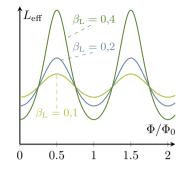

Abbildung 2.4: Struktur des rf-SQUIDs mit Koppelinduktivität (links) und die effektive Induktivität der Kombination für verschiedene Hysterese-Parameter (rechts).

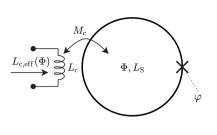

Neben dem dc-SQUID mit zwei Josephson-Kontakten kann eine Flussmessung ebenso mithilfe eines rf-SQUIDs erfolgen, dessen supraleitender Ring lediglich durch einen Josephson-Kontakt unterbrochen wird. Anders als beim dc-SQUID wird beim rf-SQUID der magnetische Fluss nicht mittels der Fluss-Spannungs-Charakteristik extrahiert, sondern mittels der Änderung der Induktivität des Josephson-Kontakts im Ring (vgl. Gleichung 2.5) . Diese Änderung kann mithilfe einer Koppelinduktivität  $L_{\rm c}$  gemessen werden (siehe Abbildung 2.4). Die Induktivität  $L_{\rm c}$  ist am SQUID angekoppelt, welches die Induktivität  $L_{\rm S}$  aufweist. Die Integration durch die Kontur des Rings liefert einen vom magnetischen Gesamtfluss  $\Phi$  abhängigen Phasenunterschied am Kontakt:

$$\varphi = -\frac{2\pi\Phi}{\Phi_0} \tag{2.12}$$

Dieser Gesamtfluss hängt vom externen magnetischen Fluss  $\Phi_{\rm ext}$  und induzierten Fluss bzw. Abschirmstrom  $\Phi_{\rm s}=L_{\rm S}I$  ab mit der SQUID-Induktivität  $L_{\rm S}$  [26]:

$$\frac{2\pi\Phi}{\Phi_0} = \frac{2\pi\Phi_{\rm ext}}{\Phi_0} + \frac{2\pi\Phi_{\rm s}}{\Phi_0}$$

(2.13)

$$\stackrel{(2.2)}{=} \frac{2\pi\Phi_{\rm ext}}{\Phi_0} - \beta_{\rm L} \sin\left(\frac{2\pi\Phi}{\Phi_0}\right) , \text{ wobei } \beta_{\rm L} = \frac{2\pi L_{\rm S} I_{\rm c}}{\Phi_0} \stackrel{(2.5)}{=} \frac{L_{\rm S}}{L_{\rm J}} \qquad (2.14)$$

Der Zusammenhang kann nur implizit ausgedrückt werden und äußert sich für einen Hystereseparameter  $\beta_L>1$  in einer Hysterese der Flusskennlinie. Durch die Fabrikationsparameter, wie beispielsweise einen zusätzlichen Shunt-Widerstand, kann die Hysterese eingestellt oder sogar für  $\beta_L<1$  gänzlich vermieden werden. Rf-SQUIDs können grundsätzlich im hysteretischen Regime betrieben werden; für die Anwendung im Multiplexer werden vorwiegend nicht-hysteretische SQUIDs mit  $\beta_L<1$  eingesetzt. Die resultierende Eingangsimpedanz

einer an das rf-SQUID gekoppelten Induktivität kann mittels Gleichung 2.5 für den nichthysteretischen Fall als

$$L_{\rm c,eff}(\Phi) = L_{\rm c} - \frac{M_{\rm c}^2}{L_{\rm S}} \frac{\beta_{\rm L} \cos(2\pi\Phi/\Phi_0)}{1 + \beta_{\rm L} \cos(2\pi\Phi/\Phi_0)}$$

(2.15)

angegeben werden [14] (vgl. Abbildung 2.4). Der magnetische Fluss kann somit über die effektive Induktiviät  $L_{\rm c,eff}$  ausgelesen werden. Eines der Ausleseverfahren für das Magnetometer stellt der Mikrowellen-SQUID-Multiplexer dar (vgl. Abschnitt 2.3.3). Das dc- und das rf-SQUID können unter anderem für die Auslese von Tieftemperatur-Kalorimetern eingesetzt werden.

## 2.2 Tieftemperatur-Kalorimeter

Kalorimetrische Sensoren messen die Wärmemenge, die durch den Eintrag von Energie durch beispielsweise einen physikalischen Prozess, wie eine Teilchenabsorption, freigesetzt wird. Die Wärmemenge kann dann mittels verschiedener Sensortypen in eine messbare Größe wie Strom, Spannung oder magnetischen Fluss umgewandelt werden.

#### 2.2.1 Kalorimetermodell und Sensortypen

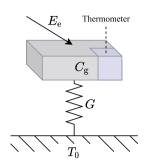

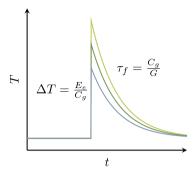

Das ideale Kalorimeter besteht aus drei elementaren Bestandteilen: dem Absorber, welcher eine Energie aufnimmt; einem Wärmebad, welches schwach mit dem Absorber gekoppelt ist und diesen zu einer Grundtemperatur  $T_0$  führt, und einem thermisch ideal am Absorber gekoppelten Sensor, der die Temperatur des Absorbers misst [3] (vgl. Abbildung 2.5). Eine Absorption einer Energie  $E_{\rm e}$  erhöht abhängig von der Wärmekapazität des Absorbers und Sensors, zusammen  $C_{\rm g}$ , die Temperatur:

$$\Delta T = \frac{E_{\rm e}}{C_{\rm g}} \tag{2.16}$$

Der Anstieg wird durch die ideale Kopplung zwischen Absorber und Thermometer bzw. Sensor als instantane  $\sigma$ -Heaviside-Funktion angenommen ( $\tau_{\rm r} \to 0$ ). Durch die schwache Kopplung G des Absorbers an das Wärmebad wird die Temperatur T mit der Abfallszeit  $\tau_{\rm f}$  danach wieder zur Grundtemperatur abkühlen. Dadurch ergibt sich die Systemantwort zu:

$$T(t) = \sigma(t) \cdot \Delta T e^{-t/\tau_{\rm f}} + T_0 + n_{\rm TFN}(t), \ \tau_{\rm f} = \frac{C_{\rm g}}{G}$$

(2.17)

Abbildung 2.5: Modell eines idealen Kalorimeters (links) und die thermische Systemantwort auf verschiedene Teilchenenergien  $E_{\rm e}$  ohne Rauschbeiträge (rechts) [3]. Eine hohe Teilchenenergie bewirkt einen größeren Temperaturanstieg.

Der Rauschbeitrag  $n_{\rm TFN}(t)$  (NFN, engl. thermal fluctuation noise) ist durch die thermodynamischen Fluktuationen zwischen Absorber und Bad gegeben. Diese sind durch die Amplitude  $\sqrt{k_BT^2C_{\rm g}}$  und das Tiefpassverhalten mit einer Grenzfrequenz von  $f_{\rm c}=G/(2\pi C_{\rm g})$  charakterisiert [3]. Die spektrale Rauschleistungsdichte ergibt sich mit [27]:

$$S_{\rm E} = k_{\rm B} C_{\rm g} T^2 \frac{4\tau_{\rm f}}{1 + (2\pi f \tau_{\rm f})^2}$$

(2.18)

Somit muss zur Messung von sehr kleinen Energien eine niedrige Temperatur und eine kleine Gesamtwärmekapazität erreicht werden. Beispielsweise führt ein Röntgenphoton mit  $10\,\mathrm{keV}$  Energie bei einer Wärmekapazität von  $1\,\mathrm{pJ}\,\mathrm{K}^{-1}$  zu einem Temperaturanstieg von etwa  $1\,\mathrm{mK}$ . Die Mikrokalorimeter werden daher bei Temperaturen im Millikelvin-Bereich betrieben, um eine ausreichende Energieauflösung zu erreichen. Es ist zu erwähnen, dass bei einem realen Kalorimeter die thermische Kopplung zwischen Sensor und Absorber auf endliche Werte beschränkt ist und die Systemantwort dadurch eine finite Anstiegszeit ( $\tau_\mathrm{r}>0$ ) aufweist. Die finite Anstiegszeit limitiert das Signal-zu-Rausch-Verhältnis bei hohen Frequenzen und beschränkt somit die maximal erreichbare Auflösung [27].

Zur Messung des Temperaturanstiegs werden verschiedene Sensor-Prinzipien verwendet. Beispielsweise können mittels einfacher Thermistoren Temperatur-Widerstandsmessungen durchgeführt werden [3]. Abhängig vom Ausleseverfahren setzt sich ein Messsystem hierfür aus einer Konstantspannungsquelle, einem Widerstand und einer Strommesseinheit zusammen. Eine im Widerstand deponierte Energie führt zu einer Änderung des spezifischen Widerstands und somit zu einer Änderung des Stroms durch den Aufbau. Der elektrische Strom durch den Widerstand sorgt systembedingt für weitere Rauschbeiträge. Insbesondere das thermische Rauschen, auch Johnson-Rauschen, stellt einen signifikanten Beitrag dar. Typischerweise werden halbleitende Sensormaterialien verwendet, mit deren hohen Temperaturkoeffizienten eine größere Signalamplitude zu erreichen ist.

Bei tiefen Temperaturen im Millikelvin-Bereich bildet der Übergang zwischen Normal- und Supraleitung besonders starke Gradienten der Widerstandsänderung; auf diesem Übergang basieren die Transition-Edge-Sensoren (TESs). Verglichen mit Halbleitersensoren ermöglicht dieses Prinzip es, kleinere Energien aufzulösen und Sensoren mit schnellerer Anstiegszeit zu konstruieren [3, 4]. Der Einsatz von TES war lange Zeit nicht praktikabel, da durch das intrinsische Johnson-Rauschen in der Messstrecke nicht das volle Potential des Sensors ausgeschöpft werden konnte. Das kleine Temperaturintervall der Übergangsregion muss eingehalten und der Sensor in diesem temperaturstabil betrieben werden. Fluktuationen der Grundtemperaturen führten zu großen Einbußen in der Auflösung und eine Überhöhung der Temperatur konnte durch das instabile Verhalten des Systems zu einer thermischen Zerstörung des Bauelements führen [4]. Diese anfänglichen Probleme konnten durch SQUID-Verstärker und ein elektrothermisches Feedback gelöst werden [28], was die breite Anwendung von TES unter anderem in Röntgenspektroskopie und in Bildsensoren für die Astronomie [1, 7] ermöglicht. TESs erreichen Auflösungsrekorde bis zu 1,6 eV bei 6 keV [29]. Das Sensorprinzip birgt jedoch das Problem, dass der Übergang zwischen supraleitenden und normalleitendem Zustand keine lineare Kennlinie aufweist. Außerdem ist die Anstiegszeit abhängig von der Pulshöhe. Die Nicht-Linearität schränkt die Anwendbarkeit für große Dynamikbereiche ein ist und stellt höhere Anforderungen an die Datenauswertung und Kalibrierung [30, 31]. Diese Problematik wird durch die MMCs gelöst, welche im nächsten Kapitel näher betrachtet werden.

Ein weiterer erwähnenswerter kryogener Sensortyp ist der Microwave-Kinetic-Inductance-Detektor (MKID). Das Sensorprinzip basiert auf der kinetischen Induktivität von Supraleitern, die in Abhängigkeit zu den vorhandenen Cooper-Paaren und Quasiteilchen (aufgebrochene Cooper-Paare) steht [32]. Eintreffende Photonen brechen die Verbindung zwischen den gepaarten Elektronen auf und führen zu einer Vergrößerung der Quasiteilchenmenge im Supraleiter und somit zu einer Erhöhung der kinetischen Induktivität. Die Induktivitätsänderung kann mittels eines Resonanzkreises und einer Anregungsfrequenz gemessen werden. Diese Auslese der Resonanzkreise ist ähnlich zum Mikrowellen-SQUID-Multiplexer, welcher für die Auslese von TESs und MMCs eingesetzt werden kann.

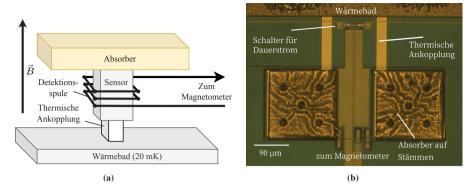

#### 2.2.2 Magnetische Mikrokalorimeter

Das magnetische Mikrokalorimeter (MMC) wurde erstmals 1986 durch W. Seidel der Technischen Universität München vorgeschlagen und in der heutigen Form 1993 durch S. Bandler und C. Enss [33] implementiert und untersucht. Das Sensorprinzip basiert auf der temperaturabhängigen Magnetisierung von paramagnetischen Materialien und setzt für hohe Auflösungen eine Betriebstemperatur deutlich unter 100 mK voraus. Eine Übersichtsskizze ist in Abbildung 2.6 gezeigt.

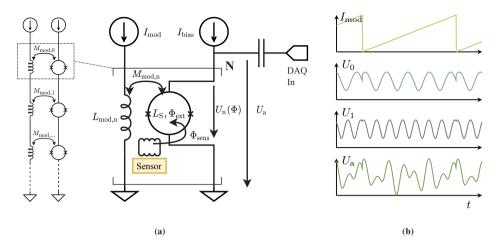

Abbildung 2.6: Schematischer Aufbau eines magnetischen Mikrokalorimeters (a): Der am Absorber gekoppelte paramagnetische Sensor wird durch ein äußeres Magnetfeld magnetisiert und ändert den magnetischen Fluss abhängig von der Temperatur. Die Flussänderung wird durch eine Detektionsspule zu einem Magnetometer weitergeleitet. Die Leiterschleife zum Magnetometer und die Detektionsspule werden dabei ebenfalls für die Erzeugung des Permanentmagnetfelds verwendet. Aufnahme zweier MMCs (b): unter jedem Absorber liegt eine Spule für das permanente Magnetfeld und die Einkopplung des Sensorflusses (Grafik nach [8, 34]).

Der Kernbestandteil des magnetischen Mikrokalorimeters ist ein Thermometer, welches aus einer paramagnetischen Legierung besteht [5]. Paramagnetische Stoffe weisen Elektronenorbitale mit polarisierbarem Spin auf [16]. Diese sogenannten Elementarmagnete richten sich bei der Anwesenheit eines Magnetfelds aus und verstärken den magnetischen Fluss durch das Material. Durch eine Änderung der Temperatur des Materials ändert sich dieser magnetische Fluss. Als Legierung werden vorzugsweise Gold oder Silber mit einer Dotierung von Erbium (typischerweise einigen hundert ppm) verwendet [5], wobei die paramagnetische Eigenschaft durch das unvollständig gefüllte 4f-Orbital des Erbium-Atoms gegeben ist. Zur Magnetisierung wird der Sensor einem permanenten Magnetfeld ausgesetzt. Dieses wird durch durch einen Dauerstrom in einer geschlossenen supraleitenden Spule erzeugt. Die Spule besitzt eine Abzweigung, an der mittels eines thermischen Schalters ein kleiner Teil der Leitung in den normalleitenden Zustand gewechselt werden kann. Durch das Aufbrechen des supraleitenden Rings kann ein Strom aufgeprägt werden, der nach einem Wechsel zurück in den supraleitenden Zustand permanent durch die Spule fließt. Der magnetische Fluss  $\Phi$  durch den Sensor kann durch einen sogenannten Fluss-Transformator (zwei elektrisch verbundene Spulen) zu einem SQUID-Magnetometer übertragen werden. Dieses wandelt das Flusssignal in eine messbare, physikalische Größe um und verstärkt sie gegebenenfalls. Das permanente Magnetfeld und der Fluss-Transformator werden meist mit der gleichen Leiterschleife realisiert. Für kalorimetrische Messungen wird an den Sensor ein Gold-Absorber gekoppelt, welcher die Energie der

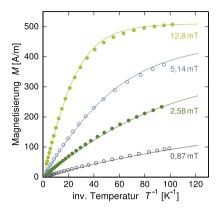

Abbildung 2.7: Gemessene temperaturabhängige Magnetisierung einer Gold-Erbium-Probe mit 300 ppm Erbium-konzentration. Die eingezeichneten Marker spiegeln die experimentellen Ergebnisse wider, welche um durchgezogene Linien aus Simulatonsergebnissen ergänzt sind [27].

eintreffende Teilchen, wie Photonen oder Elektronen, in Wärme umwandelt. Die Signalkette lässt sich nach der folgenden Formel beschreiben [35]:

$$\Delta\Phi \propto \Delta M = \frac{\partial M}{\partial T} \Delta T = \frac{\partial M}{\partial T} \frac{E_{\rm e}}{C_{\rm g}}.$$

(2.19)

Die Energie eines eintreffenden Teilches  $E_{\rm e}$  bewirkt eine relative Änderung der Temperatur  $\Delta T$  des Absorbers und des Sensors in Abhängigkeit der Wärmekapazität  $C_{\rm g}$  gegenüber dem Ausgangsniveau. Die Magnetisierung des Materials  $(\partial M/\partial T)$  ist temperaturabhängig (vgl. Abbildung 2.7) und der Gradient der Magnetisierung über der Temperatur wird im Arbeitspunkt als konstant angenommen. Mit der Erwärmung des Sensors nimmt die Magnetisierung ab und führt zu einer Änderung des magnetischen Flusses. Diese wird durch das Magnetometer gemessen. Über eine schwach angekoppelte Verbindung zu einem Wärmebad wird die Energie abgeführt und der Absorber kühlt wieder auf die Basistemperatur ab.

Der exponentielle Anstieg des Sensorsignals erreicht Werte von  $\tau_{\rm r} < 100\,\rm ns$ , welche durch die Kopplung von magnetischen Momenten und Leitungselektronen im Sensor limitiert sind [5]. Die Abfallszeit ist ein Entwurfsparameter und liegt typischerweise im Bereich von Millisekunden. Sie kann jedoch über eine geometrische Anpassung der thermischen Ankopplung zwischen Sensor und Wärmebad über einen weiten Bereich variiert werden. MMCs zeichnen sich genau wie TES durch eine sehr gute Energieauflösung von bis zu 1,58 eV ( $E_{\rm FWHM}$ ) bei 6 keV aus [2]. Gleichzeitig besitzen sie eine hohe Quanteneffizienz von mehr als 99 %. Das Kalorimeter erreicht hervorragende Linearitäten von 1 % zwischen 0 und 8 keV, wobei die Nicht-Linearität durch eine einfache quadratische Funktion gegeben ist [36]. Diese Merkmale machen das Mikrokalorimeter attraktiv für Anwendungsfelder wie Röntgen-Astronomie,

Nuklearforensik, Forschung zur Dunklen Materie und Massenspektroskopie [2]. Eines der Anwendungsfelder von MMCs, mit welchem sich diese Arbeit schwerpunktmäßig auseinandersetzt, ist die direkte Massenbestimmung des Elektron-Neutrinos. Abschnitt 2.4 dieses Kapitels geht näher auf die Massenbestimmung im Rahmen des ECHo-Experiments ein.

#### 2.3 Auslesemethoden

Um MMCs in Experimenten einsetzen zu können, muss das schwache Flusssignal des Sensors in eine andere Messgröße gewandelt und rauscharm verstärkt werden. Die Ausleseverfahren sollten dabei idealerweise für eine größere Anzahl von Sensoren skalierbar sein.

#### 2.3.1 MMC-Einkanalauslese mit dc-SQUID

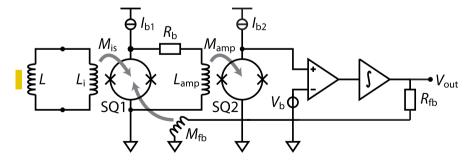

Das magnetische Flusssignal der paramagnetischen Sensoren kann mittels dc-SQUID-Magnetometern sehr genau bestimmt werden. Wie in Abbildung 2.8 zu erkennen ist, bildet die Detektionsspule L des MMCs und die Einkoppelspule  $L_{\rm i}$  eines dc-SQUIDs einen geschlossenen, supraleitenden Ring. Da in diesem Flusserhaltung gilt, muss die durch ein Detektorsignal verursachte Flussänderung mittels Abschirmströmen innerhalb des supraleitenden Rings kompensiert werden. Diese Abschirmströme koppeln schließlich in das dc-SQUID und erzeugen hierbei erneut eine Flussänderung, welche zu einer Spannungsänderung über dem dc-SQUID führt, wie bereits in Abschnitt 2.1.3 ausgeführt wurde. Durch die Verwendung zweier kaskadierter SQUIDs kann das Rauschen reduziert und der Verstärkungsfaktor und somit die Bandbreite erhöht werden [25, 5].

Abbildung 2.8: Schematischer Aufbau der zweistufigen MMC-Einkanal-Auslese, nach [5] (Grafik aus [8, 34]).

Hierbei wird das erste SQUID (SQ1) zur rauscharmen Umsetzung des Flussignals in ein Stromsignal verwendet und das zweite SQUID (SQ2) zur Nachverstärkung des Signals und Umwandlung in ein Spannungsignal [5]. Das erste SQUID wird im Spannungbias betrieben.

Dies kann mit einem Widerstand R<sub>b</sub> erreicht werden, welcher parallel zum SQUID geschaltet ist. Dieser ist deutlich kleiner als der normalleitende Widerstand des SQUIDs. Mit einer angeschlossenen Stromquelle  $I_{\rm b1}$  bildet sich somit, definiert durch  $R_{\rm b}$ , näherungsweise eine konstante Spannung aus. Der Strom durch das SQUID und durch den Widerstand R<sub>b</sub> variiert durch das Flussignal am SQUID. Die Stromänderung über  $R_{\rm b}$  wird mit der Spule  $L_{\rm amp}$  als magnetischer Fluss in das zweite SQUID eingekoppelt. Das zweites SQUID wird im Strombias  $I_{\rm b2}$  betrieben und der Eingangsfluss wird durch die SQUID-Charakteristik zu einer Spannung gewandelt (vergleiche Abschnitt 2.1.3). Das zweite SQUID wird meist durch mehrere SQUIDs realisiert und kann mit hohem kritischen Strom und Spannungsverstärkung ausgelegt werden. Die Ausgangsspannung wird im Anschluss über Leitungen aus dem Kryostaten zu einem Raumtemperaturverstärker geführt. Die Ausgangsspannung des SQUID-Magnetometers ist nicht-linear abhängig vom magnetischen Fluss und über dem Flussquanten  $\Phi_0$  periodisch (vgl. Abbildung 2.3). Für sehr kleine Flussänderungen ( $\lesssim \Phi_0/\pi$ ) lässt sich das SQUID-Magnetometer in einem Arbeitspunkt U- $\Phi$  betreiben, welcher für den höchsten Transfer-Koeffizienten  $U_{\Phi}$  gewöhnlich auf den steilsten Punkt der SQUID-Charakteristik gelegt wird. Dann gilt:  $\Delta U \approx U_{\Phi} \Delta \Phi$ .

Da der dynamische Bereich des SQUID-Magnetometers im Arbeitspunkt häufig nicht ausreicht, wird mittels einer Rückkopplungsschleife, der so genannten Flux-Locked-Loop (FLL), der Arbeitspunkt stabilisiert und das Signal linearisiert. Die Differenz zwischen dem Arbeitspunkt und einer Referenzspannung ( $V_{\rm b}$ ) wird einem Integrator zugeführt; das integrierte Signal wird invertiert in das erste SQUID rückgekoppelt und kompensiert somit die Auslenkung vom Arbeitspunkt durch das Eingangssignal (vgl. Abbildung 2.8). Abhängig von den Kabellänge und der damit verbundenen Verzögerung limitiert diese Form der Linearisierung die Auslesebandbreite auf 20 MHz bei einer Raumtemperaturauslese [25].

Die Auslese der magnetischen Mikrokalorimeter über individuelle dc-SQUIDs benötigt pro Einzelkanal mehrere Einzelverbindungen zwischen Raumtemperaturelektronik und dem Inneren des Kryostaten. Diese Zahl lässt sich durch die gemeinsame Nutzung von beispielsweise Bias-Strömen reduzieren; die dissipierte Leistung im Kryostaten und Anzahl der Leitungen skaliert allerdings nur linear mit der Anzahl von Kanälen [14]. Im folgenden Abschnitt werden Multiplexmethoden vorgestellt, die die Auslese einer größeren Sensoranzahl effizienter gestalten.

#### 2.3.2 Multiplexverfahren

Multiplexverfahren erlauben die Übertragung von Signalen über ein gemeinsames Medium. Dabei kann die Übertragung der Kanäle entweder zu unterschiedlichen Zeitintervallen (TDM, Time-Division-Multiplex), encodiert mittels orthogonaler Funktionen (CDM, Code-Division-Multiplex), über parallele, geteilte Verbindungen in einem Kabelstrang (SDM, Space-Division-Multiplex) oder über zugeordnete Frequenzintervalle in einem gemeinsamen Spektrum (FDM, Frequency-Division-Multiplex) erfolgen. Da das SDM-Verfahren die Sensorsignale nicht auf eine gemeinsame Leitung vereint, wird im Folgenden nur auf das TDM-, CDM- und FDM-Verfahren näher eingegangen.

#### Zeitmultiplex

Die Methode des zeitlichen Multiplexes (Time-Division-Multiplex) beruht auf der Zuweisung von Zeitintervallen, zu denen eine Signalübertragung stattfindet. Jedem Kanal wird ein separates Zeitfenster zugewiesen, zu dem er an die Ausleseelektronik durchgeschaltet wird. Als Signalleitung dient eine einzelne gemeinsame elektrische Verbindung sowie eine Leitung zur Auswahl der Kanäle; dadurch können bei dieser Methode die Anzahl an Verbindungen reduziert werden. Gängige Verfahren basieren auf dem Einsatz von supraleitenden Schaltern [37, 4, 10].

Ein Auslesesystem für ein TDM-Verfahren wird synchron mit den Umschaltvorgängen betrieben. Dadurch sind die Kanäle deterministisch den Ausleseintervallen zugeordnet und das Auslesefenster kann bezogen auf die Umschaltvorgängen feinjustiert werden. Ein wesentlicher Vorteil dieser Systeme ist der vergleichsweise geringe Signalverarbeitungsaufwand. Abgesehen von der Kalibrierung des Ausleseintervalls ist keine Decodierung oder Kanaltrennung nötig. Vorhandene Algorithmen für die Einkanalauslese können weitestgehend in einem TDM-System wiederverwendet werden. Weiterhin steht während des Ausleseintervalls dem Kanal der vollständige dynamische Bereich des Aufnahmegeräts zur Verfügung, da dieser exklusiv ausgelesen wird. Diese Form des Multiplexes wird allerdings durch zwei Faktoren limitiert: der kanalzahlabhängigen Abtastzeit und der endlich kleinen Umschaltzeit. Da jedem Kanal ein exklusives Zeitinvervall zugeordnet wird, kann dieser nach einer ersten Auslese erst nach der Summe der Zeitspannen aller weiteren Kanalintervallen ausgelesen werden. Dadurch teilt sich die System-Abtastrate durch die Anzahl der Kanäle. Weiterhin kann während der Umschaltung zwischen den Kanälen keine Auslese erfolgen, da kein stabiles Ausgangssignal zu erwarten ist. Die Umschaltzeit inklusive Messzeit moderner Systeme liegt bei 160 ns [10, 38]. Beide Faktoren führen dazu, dass bei größeren Kanalanzahlen die Abtastrate pro Kanal sinkt.

Jüngste Auslesesysteme, die auf TDM basieren, werden als Ersatzlösung für das Röntgenspektrometer Athena X-IFU entwickelt. Die Kanalzahl liegt bei über 1000 Pixeln pro Multiplexer, mit einem TDM-Faktor von 40 bei einer Umschaltzeit von ebenfalls 160 ns [38]. Unter der Annahme, dass ein Abtastwert pro Umschaltung gewonnen wird, resultiert dies zu einer Abtastrate von etwa 157 kHz pro Kanal.

#### Codemultiplex

Code-Division-Multiplex ist ein Multiplexverfahren, welches durch den Mobilfunkstandard UMTS populär wurde. Die Funktionsweise beruht auf zeitlich synchronisierten Sendern, welche ihre Information auf eine individuelle, orthogonale Funktion projizieren. Die Übertragung findet über einen gemeinsamen Kanal statt. Durch empfängerseitige Korrelation mit den individuellen Funktionen können die Informationen der Kanäle separiert werden. Als Orthogonalbasis werden häufig Walsh-Funktionen verwendet, da sie einfach generiert werden können und wenig Anforderungen an Schaltung und Hardware stellen. Die Information eines Abtastwertes oder Bits wird dabei auf die Periodenlänge der Orthogonalbasis gespreizt. Bei digitaler Übertragung mittels Walsh-Funktionen werden die durch die Projektion entstehenden Teilbits Chips genannt [39].

Bezogen auf Multiplexverfahren mit SQUIDs werden die Walsh-Funktionen verwendet, um die Flusskopplung der Sensoren am Verstärker-SQUID zu steuern. Die Funktionen können entweder aktiv über Schalter angewendet werden [11] oder in Kombination mit TDM, indem die Walsh-Funktionen fest in die Flusskopplung im Chip integriert werden. Mittels der Kombination kann eine Verbesserung des Auslesserauschens erzielt werden [40, 41]. Während eine Rohdatenaufzeichung beim CDM-Verfahren nicht maßgeblich modifiziert werden muss, ist eine Nachbearbeitung bzw. Dekodierung der Daten notwendig [11, 40]. Bei einer Echtzeitanalyse muss die Korrelation jedoch auf dem Auslessegerät erfolgen um die Sensorsignale trennen zu können. Prototypsysteme erreichen geringe Kanalzahlen von vier Kanälen für reines CDM [11] und 32 Kanälen bei einer Kombination von CDM und TDM [42].

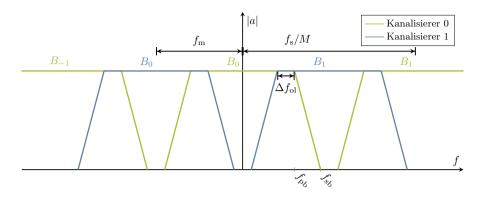

#### Frequenzmultiplex

Frequency-Division-Multiplex beschreibt das Verfahren, Kanäle über einen gemeinsamen Kanal in verschiedenen Frequenzintervallen zu übertragen. Die Übertragung findet gleichzeitig statt, indem die Signale auf verschiedene Trägerfrequenzen aufmoduliert werden. Die Bandbreite der Nutzsignale, deren Abstand zueinander und die Gesamtbandbreite des Auslesesystems definieren die maximale Anzahl der Kanäle, die über eine Leitung übertragen werden können. Für den Frequenzmultiplex gibt es verschiedene Verfahren. So kann der Sensor selbst als Teil eines Resonanzkreises wirken und die Frequenz oder Güte der Resonanz verändern. Wird der Resonator durch ein frequenzstabiles Signal angeregt, moduliert er das Signal abhängig von der Impedanzänderung. Typische Auslesefrequenzen sind im Megahertz-Bereich für TESs [4] und Gigahertzbereich für Microwave-Kinetic-Inductance-Detektoren (MKIDs) [43, 44]. Weiterhin kann ein rf-SQUID-Magnetometer als kaskadiertes Element verwendet werden, um die Signale eines Sensors in eine Resonanzverschiebung eines Resonators zu übersetzen. Der sogenannte Mikrowellen-SQUID-Multiplexer wird im nächsten Kapitel beschrieben. Ein neuere Realisierung ist der dc-SQUID-Flussrampen-Multiplexer, welcher in

Abschnitt 8.1 näher erläutert wird. Bei allen Frequenzmultiplexverfahren werden Filterbänke im Auslesesystem benötigt um eine Kanaltrennung vornehmen zu können. Diese Thematik wird in Kapitel 5 ausführlich behandelt.

#### 2.3.3 Mikrowellen-SQUID-Multiplexer

Die Aufteilung der Signale von Tieftemperatur-Detektoren in verschiedene Frequenzbänder wird durch den sogenannten Mikrowellen-SQUID-Multiplexer erreicht. In diesem Multiplexer verändert ein Detektorsignal mithilfe eines rf-SQUIDs die Resonanzfrequenz eines Resonanzkreises [12, 14]. Ein Resonanzkreis kann entweder mittels koplanarer Leitungsresonatoren oder mittels diskreter Elemente realisiert werden. Die klassische Realisierung des Mikrowellen-SQUID-Multiplexers verwendet jedoch Leitungsresonatoren.

Die Leitungsresonatoren werden anhand von Leiterbahnen geometrisch aufgebaut. Sobald die Geometrie in den Dimensionen der Signal-Wellenlänge liegt, können sich stehende Wellen (Resonanzen) ausbilden. Koplanare  $\lambda/4$ -Leitungsresonatoren bestehen aus Leiterbahnen mit einem offenen und einem kurzgeschlossen Ende. Die Resonanzbedingung für eine Länge l und der Wellenlänge  $\lambda$  ergibt sich nach:

$$l = (2m - 1)\frac{\lambda}{4} , m \in \mathbb{N}$$

(2.20)

Neben der Grundmode (m = 1) können sich auch höhere Moden auf der Leitung ausbilden. Abhängig von den Leitungsbelägen L' und C' ergeben sich die Resonanzfrequenzen [14]:

$$f_0^m = \frac{(2m-1)}{4l\sqrt{L'C'}} \tag{2.21}$$

Die Variation der Länge der Leiterbahn des Resonators ermöglicht eine gezielte Platzierung der Resonanzfrequenz. Für eine große Bandbreite im Frequenzmultiplex werden für gewöhnlich Resonanzfrequenzen von > 4 GHz verwendet, sodass die höheren Moden (m > 1) erst bei 12 GHz auftreten. Am einen Ende wird der Resonator kapazitiv mithilfe der Kopplungskapazität  $C_{\rm c}$  an eine gemeinsame koplanare Durchgangsleitung gekoppelt, wohingegen das andere Ende mit einer Induktivität  $L_{\rm c}$  abgeschlossen ist (siehe Abbildung 2.9). Mittels der  $\lambda/4$ -Leitungstransformation [45] ergibt sich für die Eingangsimpedanz des belasteten Resonators [14, 12]:

$$Z_{\rm in} = \frac{1}{j\omega C_{\rm c}} + Z_0 \frac{j\omega L_{\rm c} + Z_0 \tanh \gamma l}{Z_0 + j\omega L_{\rm c} \tanh \gamma l},$$

(2.22)

wobei  $Z_0 = \sqrt{L'/C'}$  die charakteristische Leitungsimpedanz ist und  $\gamma$  die Ausbreitungskonstante der Leiterbahn.

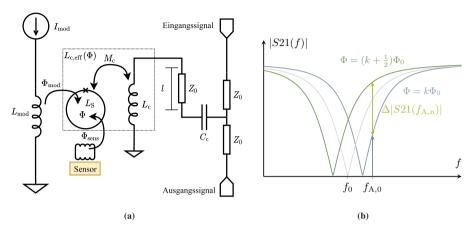

Abbildung 2.9: Einzelner Kanal eines Mikrowellen-SQUID-Multiplexers sowie ein an das rf-SQUID gekoppeltes magnetisches Mikrokalorimeter (a): Es wird die Resonanzfrequenz  $f_r$  durch die Länge l der Leiterbahn im Resonator, der Koppelkapazität  $C_{\rm c}$  und der effektiven Induktivität des gekoppelten Verbunds aus  $L_{\rm c}$  und dem rf-SQUID definiert. Die zusätzliche Modulationsspule  $L_{\rm mod}$  dient zur Linearisierung des Signals und wird in Abschnitt 2.3.4 erläutert. Die effektive Induktivität ist abhängig vom magnetischen Fluss und verschiebt die Resonanzfrequenz  $f_{\rm r}(\Phi)$  gegenüber der Grundfrequenz  $f_{\rm r}$ . Ein magnetisches Flusssignal des Sensors verschiebt die Resonanzkurve, wie am Absolutwert des  $S_{21}$ -Parameters (b) zu erkennen ist. Die Verschiebung führt zu einer Änderung der Transmission an der Auslesefrequenz  $f_{\rm A,0}$ .

Aus der Eingangsimpedanz des belasteten Resonators lässt sich der Streuparameter zur Vorwärts-Transmission  $S_{21}$  berechnen. Dieser kann in Abhängigkeit der Resonanzfrequenz  $f_r$ , der intrinsischen Güte des Resonantor  $Q_1$  und der minimalen Transmission  $S_{21}^{\min}$  ausgedrückt werden [46]:

$$S_{21} = \frac{S_{21}^{\min} + 2jQ_1 \frac{f - f_r}{f_r}}{1 + 2jQ_1 \frac{f - f_r}{f_r}}$$

(2.23)

Die Resonanzfrequenz kann unter den Vereinfachungen ( $\omega_0 C_c Z_0 \ll 1$  und  $\omega_0 L_c \ll Z_0$ ) wie folgt ausgedrückt werden:

$$f_{\rm r} = \frac{f_0}{1 + 4f_0 C_{\rm c} Z_0 + 4f_0 \frac{L_{\rm c}}{Z_0}}$$

(2.24)

Die minimale Transmission wird bei der Resonanzfrequenz erreicht und entspricht dem Quotient aus belastender und intrinsischer Güte des Resonators  $S_{21}^{\min} = Q_1/Q_i$ . Die intrinsische Güte  $Q_i$  im supraleitenden Resonator wird durch die Verlustmechanismen über Substrat, Quasiteilchen und Abstrahlung bestimmt [14]. Die belastete Gesamtgüte  $Q_l$  ergibt sich durch die Kopplungsgüte  $Q_c$  und die intrinsische Güte  $Q_i$  [12]:

$$\frac{1}{Q_{\rm l}} = \frac{1}{Q_{\rm i}} + \frac{1}{Q_{\rm c}} \tag{2.25}$$

Die Gesamtgüte ist somit ein Maß für den dissipativen Energieverlust im Resonator und die verlustfreie Abgabe der Energie zurück in die Leiterbahn. Die Kopplungüte ist über die Kopplungskapazität des Resonators gegeben:

$$Q_{\rm c} = \frac{\pi}{2Z_0^2(\omega_r C_c)} \tag{2.26}$$

Für große intrinsische Güten  $(Q_i \to \infty)$  kann sowohl die Bandbreite B als auch die Einschwingzeit  $\tau_{res}$  des Resonators allein über die Wahl der Koppelkapazität definiert werden [26]:

$$\tau_{\rm res} = \frac{1}{\pi B} \text{ mit } B = \frac{f_{\rm r}}{Q_{\rm l}} \approx \frac{f_{\rm r}}{Q_{\rm c}}$$

(2.27)

Beim Mikrowellen-SQUID-Multiplexer ermöglicht dies eine Angleichung der Bandbreite der Resonatoren in Abhängigkeit ihrer Resonanzfrequenz. Die typischen Bandbreiten der Resonanzen bei der Verwendung mit Kalorimetern liegen bei 1 MHz im Gigahertzbereich.

Um nun das Sensorsignal in die Veränderung der Resonanzfrequenz umzusetzen, wird ein ungeshuntetes, nicht-hysteretisches rf-SQUIDs mit der Induktivität  $L_{\rm S}$  an die Induktivität  $L_{\rm C}$  im Resonanzkreis mit der Gegeninduktivität  $M_{\rm C}$  magnetisch angekoppelt (vgl. Abbildung 2.9). Mit dieser Kopplung verändert die Abschlussinduktivität  $L_{\rm C}$  ihren Wert in Abhängigkeit zum magnetischen Fluss  $\Phi$  (vgl. Gleichungen 2.5 und 2.15):

$$L_{\rm c,eff}(\Phi) = L_{\rm c} - \frac{M_{\rm c}^2}{L_{\rm S}} \frac{\beta_{\rm L} \cos(2\pi\Phi/\Phi_0)}{1 + \beta_{\rm L} \cos(2\pi\Phi/\Phi_0)},$$

(2.28)

wobei zusätzliche resistive und kapazitive Anteile des Josephson-Kontakts vernachlässigt werden. Die Flussabhängigkeit der Resonanzfrequenz  $f_{\rm r}$  kann mittels Differenzierung und unter der Vereinfachung  $\omega_0 L_c \ll Z_0$  für geringe Ausleseleistung als

$$f_{\rm r}(\Phi) \approx f_0 - 4f_0^2 \left[ C_{\rm c} Z_0 + \frac{L_{\rm c}}{Z_0} - \frac{M_{\rm c}^2}{Z_0 L_{\rm S}} \frac{\beta_{\rm L} \cos(2\pi\Phi/\Phi_0)}{1 + \beta_{\rm L} \cos(2\pi\Phi/\Phi_0)} \right]$$

(2.29)

geschrieben werden [14, 12, 26]. Für eine höhere Ausleseleistung führen die im Resonator fließenden Ströme zu einer signifikanten magnetischen hochfrequenten Flussamplitude im rf-SQUID, sodass die hieraus resultierenden nicht-linearen Effekte berücksichtigt werden müssen [47].

**Abbildung 2.10:** Auslese von Kalorimetern mittels eines Mikrowellen-SQUID-Multiplexers: Jedem Resonator ordnet sich eine Auslesefrequenz zu; wird eines der MMCs von einem Teilchen getroffen, verschiebt sich je nach Polarität des jeweiligen Detektorpixels die Resonanzkurve entweder zu höheren oder niedrigeren Frequenzen. Dadurch wird die Amplitude des zugehörigen Auslesetons moduliert.

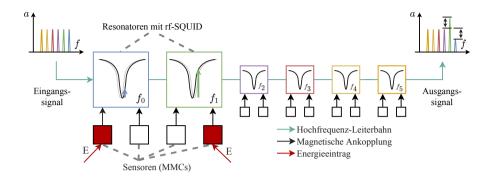

Für die Verwendung im Multiplexer werden mehrere  $\lambda/4$ -Resonatoren unterschiedlicher Länge  $l_{\rm n}$  und Kopplungkapazitäten  $C_{\rm c,n}$  an eine gemeinsame Leiterbahn gekoppelt. Der Frequenzgang der Leiterbahn weist dadurch für jeden Auslesekanal einen kerbenartige Transmissionsabfall an den Resonanzfrequenzen  $f_0, f_1, \ldots$  auf (vgl. Abbildung 2.10). Das Tieftemperatur-Kalorimeter-Signal verändert aufgrund der flussabhängigen SQUID-Induktivität die Resonanzfrequenz des Resonators und somit die Transmission und die Phase in einem lokalen Bereich des Frequenzgangs. Das Sensor-Array kann mittels eines Frequenzkamms, in dem sich je eine konstante Frequenz  $f_{\rm A,0}, f_{\rm A,1}, \ldots$  einem Resonator zuordnet, ausgelesen werden. Die Transmissionsänderung eines Kanals bewirkt eine Modulation des entsprechenden Auslesesignals. Die Auslesefrequenz liegt für die Auslese über die Amplitude nicht im Zentrum der Resonanz, sondern an den Flanken um einen größtmöglichen Übertragungskoeffizienten zu erhalten. Durch die Kopplung zweier Sensoren an ein rf-SQUID mit gegensätzlicher Polarität kann über einen Resonator die Auslese beider Sensoren erfolgen.

#### 2.3.4 Flussrampenmodulation

Das am Resonator angekoppelte rf-SQUID verschiebt die Resonanzfrequenz des Resonators durch die Änderung der SQUID-Induktivität periodisch über dem magnetischen Fluss. Der Arbeitspunkt auf der SQUID-Charakteristik liegt für eine Amplituden-Modulation idealerweise auf dem Punkt mit dem größten Gradienten, welcher allerdings nur einen kleinen quasilinearen Bereich aufweist. Der Arbeitspunkt des SQUIDs nach dem Übergang vom normal- in den supraleitenden Zustand ist durch Restmagnetfelder zufällig und erfordert eine individuelle Einstellung. Außerdem bewegt sich der Arbeitspunkt bei großen Flusssignalen aus dem linearen Bereich heraus. Der dadurch entstehende Fehler kontrastiert das sehr lineare Verhalten der

magnetischen Mikrokalorimeter und sollte daher vermieden werden. Der Arbeitspunkt wird bei der Einkanal-Auslese individuell für jedes SQUID mit einer Rückkopplungsschleife eingestellt und linearisiert (vgl. Abbildung 2.8). Diese Einstellung erfordert eine weitere elektrische Verbindung für jedes SQUID und ist daher insbesondere für das Frequenzmultiplexverfahren ungeeignet. Zur Linearisierung des SQUID-Signals und zur Vermeidung des individuellen Rückkopplungssignals kann die Flussrampenmodulation eingesetzt werden [48].

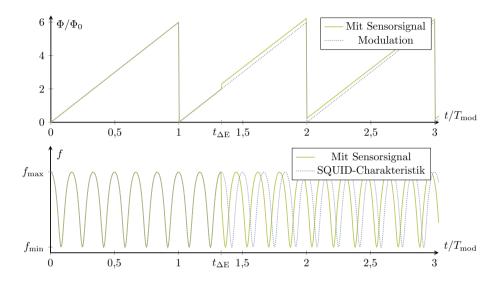

Abbildung 2.11: Flussrampenmodulation mit aus der SQUID-Charakteristik entstehender periodischer Resonanzverschiebung. An Zeitpunkt  $t_{\Delta E}$  ist ein Sensorereignis angedeutet, welches zu einem Phasenversatz führt.

Bei dieser Methode wird mittels einer zusätzlichen Spule  $L_{\rm mod}$  in das rf-SQUID ein Magnetfeld  $\Phi_{\rm mod}$  eingebracht (vgl. Abbildung 2.9). An der Spule wird ein sägezahnförmiges Modulationssignal  $I_{\rm mod}$  angelegt, die sogenannte Flussrampe, welche die Resonanzfrequenz  $f_{\rm r}$  (vgl. Gleichung 2.29) linear über mehrere Perioden der Kennlinie steuert. Es entsteht ein sinus-ähnliches Signal als Resonanzverschiebung (siehe Grafik 2.11). Da um die Resonanzfrequenz des Resonators die Transmission auf der gemeinsamen Durchgangsleitung verringert ist, entsteht durch die Modulation eine periodische Transmissionsänderung in diesem Frequenzbereich. Im Kontext der Auslese resultiert aus der Transmissionsänderung eine periodische Amplituden-Modulation des Auslessesignals. Wird nun durch das magnetische Mikrokalorimeter ein zusätzlicher magnetischer Fluss  $\Phi_{\rm sens}$  erzeugt, ist dies äquivalent zu einem zeitlichen Versatz der Flussrampe und somit zu einem Phasenversatz des modulierten Signals (vgl. Abbildung 2.11). Der Phasenversatz folgt dem magnetischen Fluss des Sensors und ist damit linear abhängig zum Sensorsignal.

Der magnetische Fluss zur Modulation kann nicht beliebig weit rampenförmig erhöht werden, deshalb kann als Modulationssignal bzw. Flussrampe beispielsweise ein Sägezahn oder ein Dreieckssignal verwendet werden. Hiermit wird ein möglichst linearer Verlauf des Eingangssignals erreicht, es können jedoch zum Zeitpunkt der Stufe im Sägezahn oder an den Eckpunkten des Dreiecks aus dem Ausgangssignal keine Phaseninformationen extrahiert werden. Falls die Umschaltung anders als in der Grafik nicht genau in einem ganzen Vielfachen des Flussquantums stattfindet, wird an diesen Stellen ein Phasensprung auftreten. Das Sensorsignal kann über die Bildung des Fourier-Koeffizienten des SQUID-Signals und über die Berechnung der zugehörigen Phase extrahiert werden [48] (vgl. Abschnitt 5.5). Die Flussrampen-Modulation ist für die Anwendung des Mikrowellen-SQUID-Multiplexers in Experimenten unabdingbar.

## 2.4 Das ECHo-Experiment und dessen Anforderungen

Das Electron Capture in Holmium-163 (ECHo) Experiment wurde initiiert, um die Elektronen-Neutrino-Masse zu untersuchen. Durch die Analyse des kalorimetrisch gemessenen Elektroneneinfang (EC)-Spektrums des Isotops  $^{163}$ Ho soll in der finalen Ausbaustufe (ECHo-1M) eine Energieauflösung im Sub-eV-Bereich bei der Massenbestimmung erreicht werden [8]. Das radioaktive Isotop zerfällt unter Aussendung eines Elektron-Neutrinos zu Dysprosium im angeregten Zustand, welches dann unter Abgabe der Energie  $E_{\rm EC}$  in den Grundzustand gelangt:

$$^{163}\text{Ho} \to ^{163}\text{Dy}^* + \nu_e$$

(2.30)

$$^{163}\text{Dv}^* \to ^{163}\text{Dv} + E_{\text{EC}}$$

(2.31)

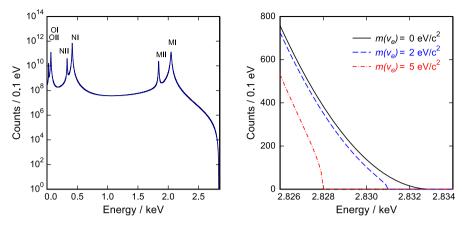

Die maximale Energie für diesen Zerfall wird aktuell mit  $Q_{\rm EC}$  = 2,833 keV [49] beziffert und soll mit hochpräziser Pennig-Fallen-Massenspektrometrie nachbestimmt werden [8, 50]. Die direkte Messung der Masse des beim Zerfall emittierten Neutrinos ist nicht möglich, da es nur selten mit anderer Materie interagiert. Allerdings spiegelt die messbare Energie  $E_{\rm EC}$ , die beim Zerfall frei wird, die Massendifferenz  $Q_{\rm EC}$  exklusive der Masse des Neutrinos wider. Die freigesetzte Energie  $E_{\rm EC}$  (siehe Abb. 2.12) bildet ein kontinuierliches Energiespektrum, welches zum Endpunktbereich nahe  $Q_{\rm EC}$  verschwindet. Eine nichtverschwindende Neutrinomasse beeinflusst die Form des Spektrums im Endpunktbereich, sodass ein Rückschluss auf die Neutrinomasse möglich ist. Das Energieintervall der freiwerdenden Energie  $E_{\rm EC}$  liegt im dynamischen Bereich von magnetischen Mikrokalorimetern. Das Holmium wird für die Messung in die Absorber der Kalorimeter implantiert.

**Abbildung 2.12:** Theoretisches Spektrum und Endpunkt der  $E_{\rm EC}$ -Energie [8, 34]

Ein verwandtes Experiment ist das Karlsruhe Tritium Neutrino Experiment (KATRIN), welches im Unterschied zu ECHo die Masse des Elektron-Antineutrinos misst. Bei dem Beta-Zerfall von Tritium wird etwa 18,6 keV Energie in Form eines Elektron und eines Antineutrinos frei. Das Elektron enthält anteilig die Energie des Zerfalls, maximal die Energie der Massendifferenz abzüglich der Energie des Antineutrinos. Die Messung der Energie des Elektrons erlaubt somit einen direkten Rückschluss zur Antineutrinomasse. Durch das sogenannte MAC-E-Filter<sup>1</sup> werden die entstehenden Elektronen fokussiert und vorgefiltert, sodass nur Teilchen hoher Energie auf das Spektrometer auftreffen [51]. Aus jüngsten Ergebnissen wurde eine Antineutrinomasse von 1,1 eV/c² (90 % C.L.) abgeleitet [52].

Anders als beim KATRIN-Experiment werden beim ECHo-Experiment alle Zerfallsereignisse aufgenommen, d.h es existiert kein Vorfilter. Die Messung erfordert die Verarbeitung und Analyse des gesamten Energiespektrums. In der Zwischenausbaustufe ECHo-100k wird angestrebt, die Neutrinomasse mit einer oberen Grenze von 1,5 eV/c² (90 % C.L.) zu bestimmen [53]. Auf das kalorimetrisch gemessene Spektrum kann eine Modellfunktion des theoretischen Spektrums angepasst werden, um die Auflösung im Endpunktbereich zu erhöhen. Die maximale Auflösung der Neutrinomasse wird dabei maßgeblich durch die Energieauflösung der Detektoren, die Anzahl der Ereignisse im Spektrum und das Hintergrundrauschen durch unauflösbare, koinzidente Detektorereignisse bestimmt [8]. Die genannten Parameter und die Rate, mit der die Ereignisse aufgezeichnet werden, bestimmen die erforderliche Messzeit des Experiments. Für die 100k-Phase des Experiments soll eine Gesamtzahl an Ereignissen von  $10^{13}$  mit einer Rate von 100 kBq aufgezeichnet werden, um eine ausreichend hohe Sensitivität zu erreichen [53]. Aufgrund des internen Hintergrunds, der durch eine unauflösbare Koinzidenz von Ereignissen in einem Detektor verursacht wird (sogenannter *unresolved Pile-Up*),

Magnetic Adiabatic Collimation combined with an Electrostatic Filter

wird die Aktivität auf 10 Bq pro Detektor beschränkt [8]. Daher sind große Detektorarrays mit bis zu 10<sup>4</sup> parallel arbeiteten Detektoren erforderlich, um die benötigte Gesamtaktivität zu erreichen und die Messung in einer Zeitskala von drei Jahren durchführen zu können [53].

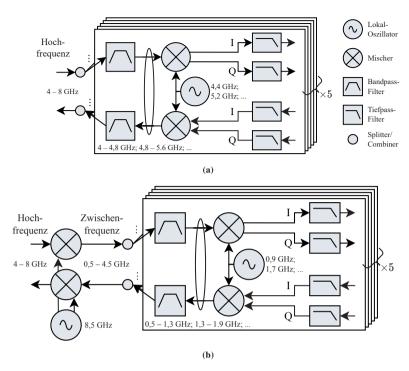

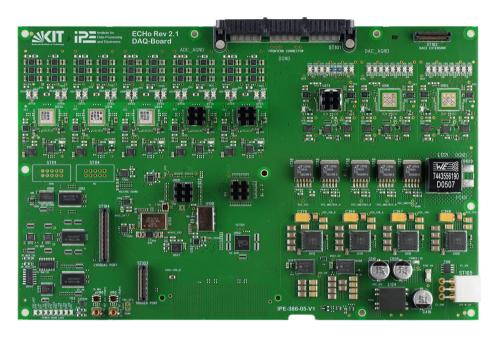

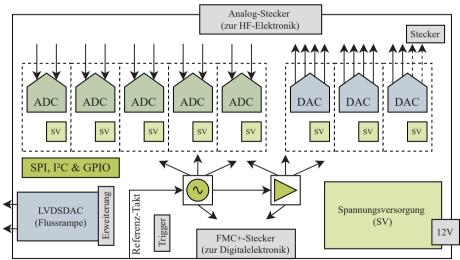

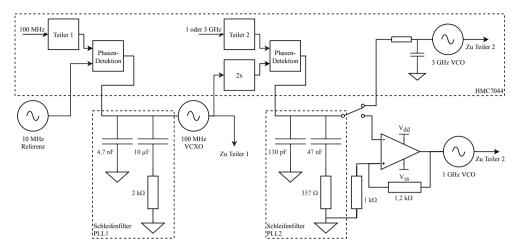

ECHo-100k ist das erste Experiment, welches zur Auslese einen Mikrowellen-SQUID-Multiplexer in Kombination mit MMCs einsetzt. Es ist eine Resonatorbandbreite im Bereich von 1 MHz und ein Frequenzabstand zwischen den Kanälen von 10 MHz geplant. Der Abstand von 10 MHz wird für die Isolation benachbarter Kanäle benötigt. Es wird jeweils ein MMC, welches aus zwei Pixeln mit Ausgangssignalen unterschiedlicher Polarität besteht, an ein rf-SQUID gekoppelt, sodass maximal 12 000 Sensoren über 6000 Resonatorkanäle ausgelesen werden können. Je 400 Resonatoren verteilen sich auf 4 GHz Systembandbreite zwischen 4 und 8 GHz, die zusammen durch ein Einzelsystem erfasst werden sollen. Das Auslesesystem umfasst somit fünfzehn Einzelsysteme, welche die Signale vom Hochfrequenzbereich herabmischen, aufzeichnen und verarbeiten. Durch die hohe Bandbreite des Multiplexes muss die Ausleseplattform die aufgenommenen Daten weitestgehend in Echtzeit verarbeiten. Dazu gehört der Demultiplex der Kanäle, die Verarbeitung der Flussrampenmodulation und die Erkennung von Sensorereignissen. So können die extrahierten Sensorereignisse an einen Server weitergeleitet werden, der die Daten auswertet und abspeichert [San19].

## 2.5 Zusammenfassung

Tieftemperatur-Mikrokalorimeter sind vielversprechend für Anwendungsfelder in der Physik wie hochsensitive Röntgenspektrographie und Astrophysik. Unter den verschiedenen Kalorimetertypen steht das besonders lineare magnetische Mikrokalorimeter im Fokus dieser Arbeit. Die Detektoren erreichen im Millikelvin-Bereich ihre höchste Auflösung und die Auslese erfolgt mittels rauscharmer SQUIDs. Zur Auslese einer großen Anzahl an Sensoren muss ein Multiplexverfahren eingesetzt werden, um die Anzahl der Verbindungen zwischen Raumtemperatur- und Tieftemperaturbereich zu minimieren. Der Mikrowellen-SQUID-Multiplexer in Kombination mit der Flussrampenmodulation ist ein Frequenzmultiplexverfahren, welches die Auslese hunderter MMCs mithilfe von Resonatoren und nicht-hysteretischen rf-SQUIDs ermöglicht. Der hohe Multiplexfaktor ist interessant für zukünftige Experimente wie das ECHo-Experiment, das die Elektron-Neutrino-Masse anhand des Röntgen-Spektrums des Holium-163-Isotops untersucht. Für die Auslese der Mikrokalorimeter mittels Frequenzmultiplex ist eine leistungsfähige Elektronik notwendig, die im Mikrowellenbereich Signale generieren und verarbeiten kann.

# 3 Technologische Grundlagen

Auslesesysteme für den Mikrowellen-SQUID-Multiplexer erfordern ein Spektrum an Technologien. So wird zur Umsetzung der Mikrowellen-Signale eine Mischerelektronik benötigt und im Anschluss eine Wandlungselektronik zur Übersetzung in den digitalen Bereich. Im Digitalen wird ein System-on-Chip (SoC) mit Field-Programmable-Gate-Array (FPGA) verwendet um die Algorithmen zur Extraktion der einzelnen Sensorsignale zu implementieren. Die Steuerung des Systems erfolgt mit Software auf dem Prozessor des SoCs. Dieses Kapitel beschreibt die technologischen Grundlagen zu den verwendeten Elektroniken sowie zur Signalverarbeitung im Kontext der Auslese.

## 3.1 Rauschleistung und Jitter

Die Auslesefrequenzen für die Mikrowellenresonatoren  $f_{\rm A,n}$  bilden zusammen ein Mehrtonsignal; im Frequenzspektrum ist dieses als Frequenzkamm charakterisiert. Durch die Überlagerung der Frequenzen im Zeitbereich kann es zu großen Spitzenwerten kommen, die einen hohen dynamischen Bereich bei der Quantisierung erfordern. Im folgenden Abschnitt werden die Eigenschaften des Signals bezüglich des Quantisierungsrauschens untersucht und im Anschluss der mit der Quantisierung zusammenhängende Abtastjitter.

## 3.1.1 Quantisierungsrauschen und Scheitelfaktor

Beim Übergang von kontinuierlichen, analogen Signalen zu zeit- und wertdiskreten, digitalen Signalen wird einer Spannung u(t) innerhalb des Wandlers ein digitaler Wert zugewiesen. Durch die endlich kleinen Quantisierungsschritte tritt ein Fehler im gemessenen Amplitudenwert auf, wenn dieser im Bereich zwischen zweier Quantisierungsschritte liegt. Dieser Fehler wird Quantisierungsfehler genannt. Vergleichbar mit dem Abtasttheorem der Zeitdiskretisierung muss bei der Wertdiskretisierung das Quantisierungstheorem erfüllt sein, um das Signal fehlerfrei zu rekonstruieren [54]. Das Quantisierungstheorem lässt sich in der Praxis nur schwer erfüllen, wird aber bei den meisten Anwendungen näherungsweise erfüllt, wenn

das Signal mehrere Quantisierungsstufen im beobachteten Zeitintervall erreicht [55]. Bei Erfüllung kann von einem linearen Quantisierungsmodel, das heißt von einem gleichverteilten, mittelwertfreien Quantisierungsfehler ausgegangen werden. Die Varianz, gleichbedeutend mit der Rauschleistung, kann mittels der gleichverteilten Wahrscheinlichkeitsdichte des Quantisierungsfehlers  $f_{e_0}$  über einen Quantisierungsschritt q berechnet werden [54]:

$$E\{e_{q}^{2}(t)\} = \int_{-\infty}^{\infty} e_{q}^{2} \cdot f_{e_{q}}(e_{q}) de_{q} = \frac{1}{q} \int_{-q/2}^{q/2} e_{q}^{2} de_{q} = \frac{q^{2}}{12}$$

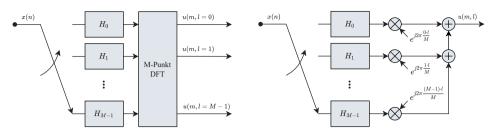

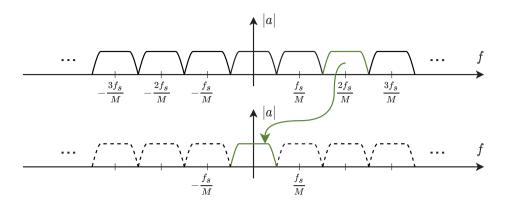

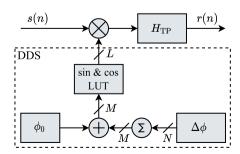

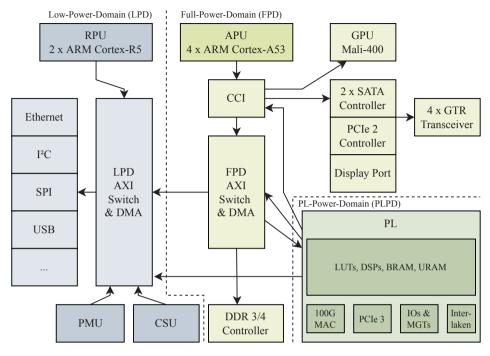

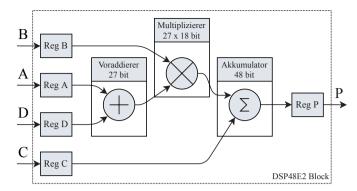

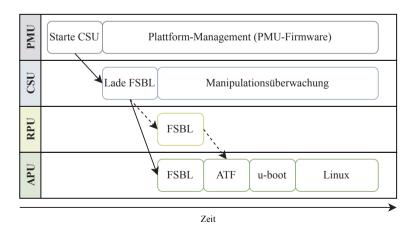

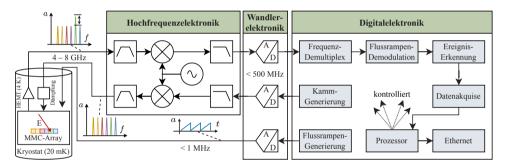

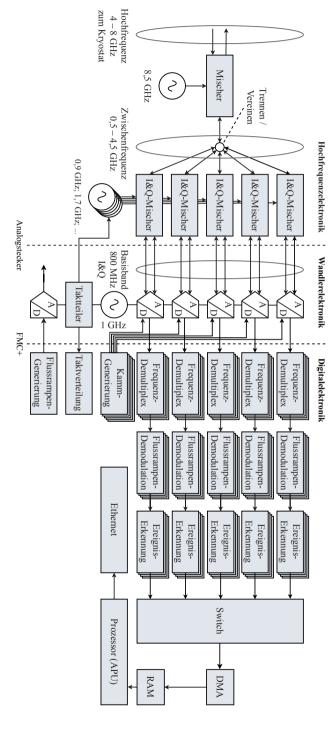

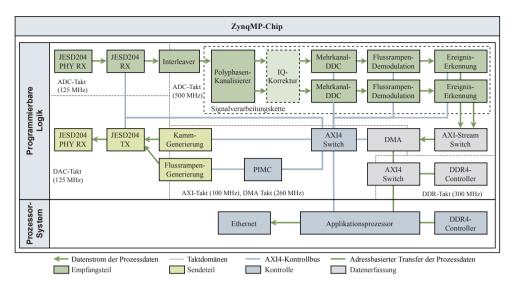

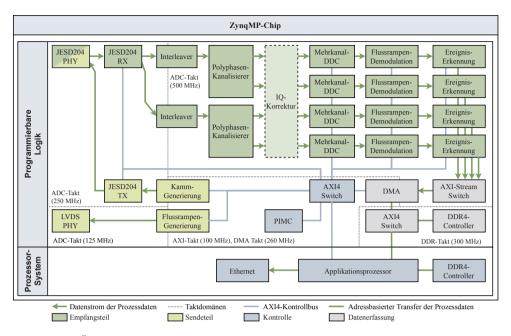

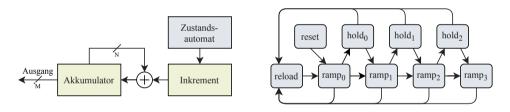

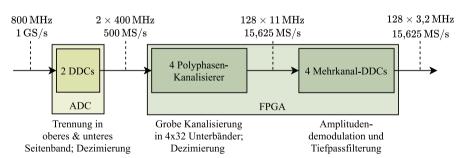

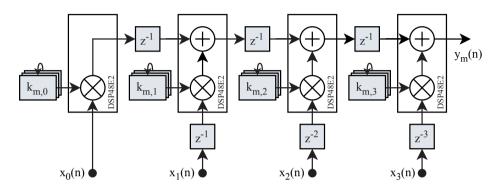

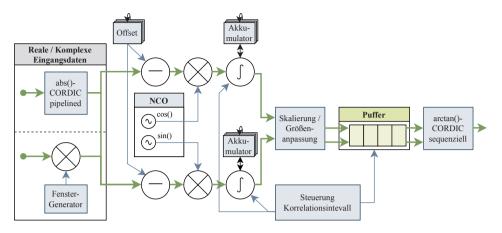

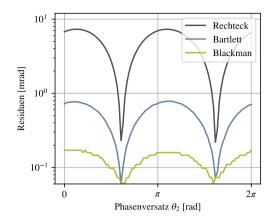

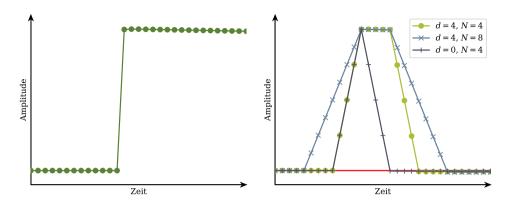

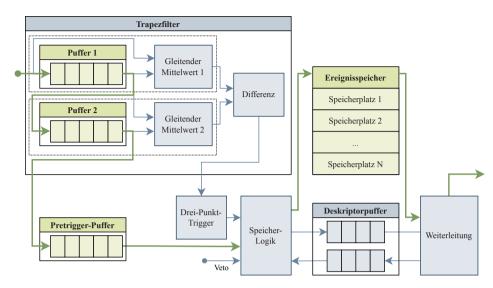

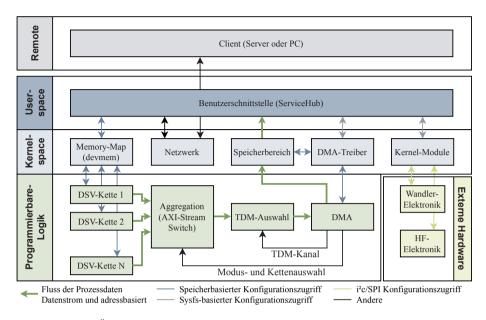

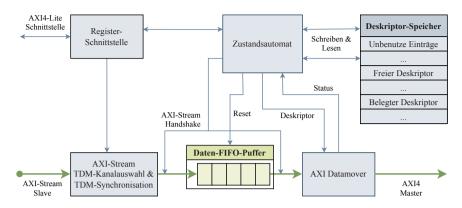

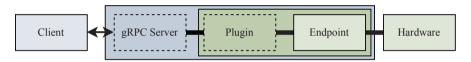

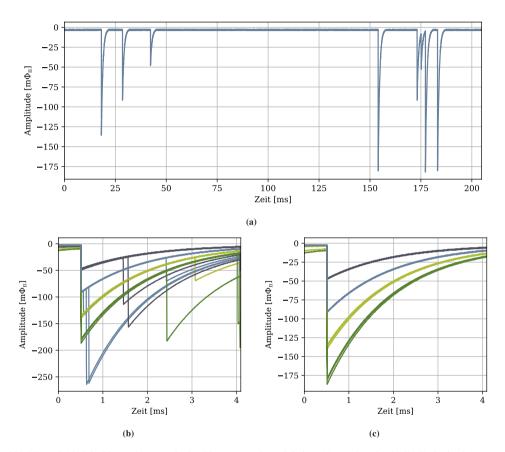

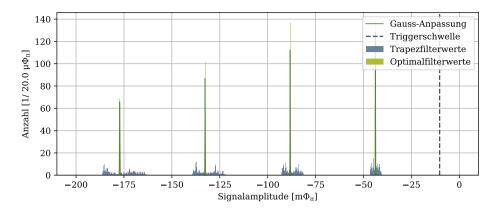

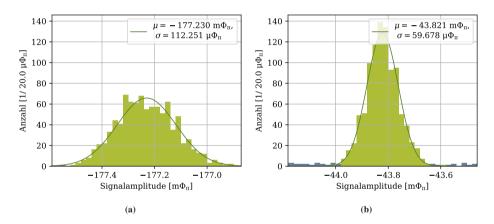

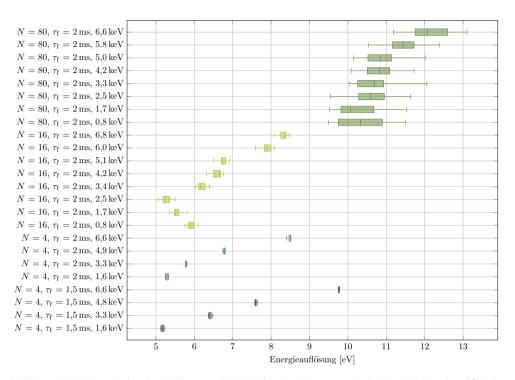

(3.1)