# Optimization of a 65 nm CMOS imaging process for monolithic CMOS sensors for high energy physics

G. Aglieri Rinella,<sup>*a*</sup> A. Andronic,<sup>*o*</sup> M. Antonelli,<sup>*i*</sup> R. Baccomi,<sup>*i*</sup> R. Ballabriga,<sup>*a*</sup> M. Barbero,<sup>k</sup> P. Barrillon,<sup>k</sup> J. Baudot,<sup>l</sup> P. Becht,<sup>n</sup> F. Benotto,<sup>h</sup> S. Beole,<sup>h</sup> G. Bertolone,<sup>1</sup> A. Besson,<sup>1</sup> W. Bialas,<sup>a</sup> G. Borghello,<sup>a</sup> J. Braach,<sup>a</sup> M. Buckland,<sup>i</sup> S. Bugiel,<sup>1</sup> E. Buschmann,<sup>a</sup> P. Camerini,<sup>i</sup> M. Campbell,<sup>a</sup> F. Carnesecchi,<sup>a</sup> L. Cecconi,<sup>*a*</sup> E. Charbon,<sup>*w*</sup> A. Chauhan,<sup>*q*</sup> C. Colledani,<sup>*l*</sup> G. Contin,<sup>*i*</sup> D. Dannheim,<sup>*a*</sup> K. Dort,<sup>a</sup> J. de Melo,<sup>a</sup> W. Deng,<sup>a,y</sup> G. De Robertis,<sup>e</sup> A. Di Mauro,<sup>a</sup> A. Dorda Martin,<sup>*a*,+</sup> A. Dorokhov,<sup>*l*</sup> P. Dorosz,<sup>*a*</sup> G. Eberwein,<sup>*u*</sup> Z. El Bitar,<sup>*l*</sup> X. Fang,<sup>*l*</sup> A. Fenigstein,<sup>c</sup> C. Ferrero,<sup>h</sup> D. Fougeron,<sup>k</sup> D. Gajanana,<sup>m</sup> M. Goffe,<sup>l</sup> L. Gonella,<sup>t</sup> A. Grelli,<sup>m</sup> V. Gromov,<sup>m</sup> A. Habib,<sup>k</sup> A. Haim,<sup>d</sup> K. Hansen,<sup>q</sup> J. Hasenbichler,<sup>a,v</sup> H. Hillemanns,<sup>a</sup> G.H. Hong,<sup>x</sup> C. Hu,<sup>l</sup> A. Isakov,<sup>r</sup> K. Jaaskelainen,<sup>l</sup> A. Junique,<sup>a</sup> A. Kotliarov,<sup>r</sup> I. Kremastiotis,<sup>a</sup> F. Krizek,<sup>r</sup> A. Kluge,<sup>a</sup> R. Kluit,<sup>m</sup> G. Kucharska,<sup>a</sup> T. Kugathasan,<sup>a</sup> Y. Kwon,<sup>x</sup> P. La Rocca,<sup>f</sup> L. Lautner,<sup>a,p</sup> P. Leitao,<sup>a</sup> B.-H. Lim,<sup>h</sup> F. Loddo,<sup>e</sup> M. Mager,<sup>a</sup> D. Marras,<sup>g</sup> P. Martinengo,<sup>a</sup> S. Masciocchi,<sup>n</sup> S. Mathew,<sup>s</sup> M.W. Menzel,<sup>n</sup> F. Morel,<sup>l</sup> B. Mulyanto,<sup>q</sup> M. Munker,<sup>a</sup> L. Musa,<sup>a</sup> M. Nakamura,<sup>b</sup> P. Pangaud,<sup>k</sup> S. Perciballi,<sup>h</sup> H. Pham,<sup>l</sup> F. Piro,<sup>a,w</sup> F. Prino,<sup>h</sup> S. Rachevski,<sup>i</sup> K. Rebane,<sup>a</sup> C. Reckleben,<sup>q</sup> F. Reidt,<sup>a</sup> R. Ricci,<sup>j</sup> R. Russo,<sup>m</sup> I. Sanna,<sup>a,p</sup> V. Sarritzu,<sup>g</sup> U. Savino,<sup>h</sup> D. Schledewitz,<sup>n</sup> I. Sedgwick,<sup>s</sup> S. Senyukov,<sup>l</sup> W. Snoeys,<sup>*a*,\*</sup> H.K. Soltveit,<sup>*n*</sup> J. Sonneveld,<sup>*m*</sup> J. Soudier,<sup>*l*</sup> J. Stachel,<sup>*n*</sup> M. Suzuki,<sup>*b*</sup> P. Svihra,<sup>a</sup> M. Suljic,<sup>a</sup> N. Takahashi,<sup>b</sup> G. Termo,<sup>a</sup> N. Tiltmann,<sup>o</sup> E. Toledano,<sup>d</sup> A. Triffiro,<sup>f</sup> A. Turcato,<sup>h</sup> G. Usai,<sup>g</sup> I. Valin,<sup>l</sup> A. Villani,<sup>i</sup> J.B. Van Beelen,<sup>a</sup> M.D. Vassilev,<sup>z</sup> C. Vernieri,<sup>z</sup> A. Vitkovskiy,<sup>m</sup> Y. Wu,<sup>#</sup> A. Yelkenci<sup>m</sup> and A. Yuncu<sup>n</sup> <sup>a</sup>CERN, Esplanade des Particules 1, CH-1211 Geneva 23, Switzerland <sup>b</sup>Tower Partners Semiconductor Co. Ltd., Uozu city, Toyama, Japan <sup>c</sup>Tower Semiconductor Ltd., Migdal Haemek, Israel <sup>d</sup>Etesian Semiconductor Ltd., Ramat Yishai, Israel <sup>e</sup> University and INFN Bari, Bari, Italy <sup>f</sup> University and INFN Catania, Catania, Italy <sup>g</sup> University and INFN Cagliari, Cagliari, Italy <sup>h</sup>University and INFN Torino, Torino, Italy <sup>*i*</sup>University and INFN Trieste, Trieste, Italy <sup>j</sup>University of Salerno and Bologna, Italy

<sup>\*</sup>Speaker and corresponding author: W. Snoeys, CERN, Geneva, Switzerland, walter.snoeys@cern.ch

<sup>©</sup> Copyright owned by the author(s) under the terms of the Creative Commons Attribution-NonCommercial-NoDerivatives 4.0 International License (CC BY-NC-ND 4.0).

<sup>k</sup>Aix Marseille Univ, CNRS/IN2P3, CPPM, Marseille, France <sup>1</sup>Institut Pluridisciplinaire Hubert Curien (IPHC), Strasbourg, France <sup>m</sup>Nationaal Koninklijk Instituut voor Hoge Energie Fysika (NIKHEF), the Netherlands <sup>n</sup>Heidelberg University, Heidelberg, Germany <sup>o</sup>Münster University, Münster, Germany <sup>p</sup>Technical University Munich, Germany <sup>q</sup>Deutsches Elektronen-Synchroton DESY, Hamburg, Germany <sup>r</sup>Prague University, Prague, Czech Republic <sup>s</sup>STFC (Rutherford Appleton Laboratory), Didcot, United Kingdom <sup>t</sup>Birmingham University, Birmingham, United Kingdom <sup>u</sup>Oxford University, Oxford, United Kingdom <sup>v</sup>Technical University Vienna, Vienna, Austria <sup>w</sup>Ecole Polytechnique Federale Lausanne, Ecublens, Switzerland <sup>x</sup>Yonsei University, Incheon, South Korea <sup>y</sup>Central China National University, Wuhan, Republic of China <sup>2</sup> Stanford Linear Accelerator (SLAC) and Stanford University, Stanford, CA, USA <sup>+</sup>Karlsruhe Institute of Technology, Karlsruhe, Germany

<sup>#</sup>University of Science and Technology of China (USTC), Hefei, Anhui, China

The long term goal of the CERN Experimental Physics Department R&D on monolithic sensors is the development of sub-100nm CMOS sensors for high energy physics. The first technology selected is the TPSCo 65nm CMOS imaging technology. A first submission MLR1 included several small test chips with sensor and circuit prototypes and transistor test structures. One of the main questions to be addressed was how to optimize the sensor in the presence of significant in-pixel circuitry. In this paper this optimization is described as well as the experimental results from the MLR1 run confirming its effectiveness. A second submission investigating wafer-scale stitching has just been completed. This work has been carried out in strong synergy with the ITS3 upgrade of the ALICE experiment.

10th International Workshop on Semiconductor Pixel Detectors for Particles and Imaging (Pixel2022) 12-16 December 2022 Santa Fe, New Mexico, USA

# 1. State of the art

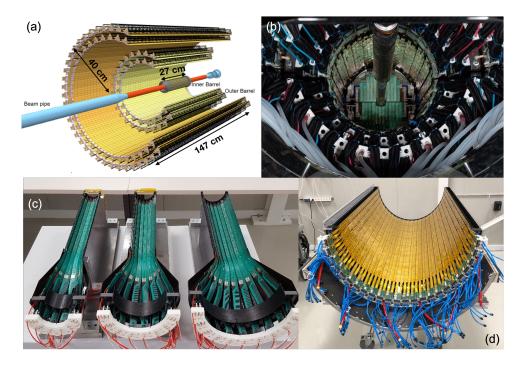

**Figure 1:** (a) A schematic view of the ITS2 detector [1, 2] with about 12.5 Gpixels over about 10 m<sup>2</sup>, (b) a picture during its installation in the ALICE experiment, and pictures of (c) inner and (d) outer half-barrels during construction, the latter covering about 2 m<sup>2</sup>.

Figure 2: Events taken by the ITS2 detector in the ALICE experiment. On the right all seven layers are clearly visible, the three inner layers are to be replaced for the ITS3 upgrade (see below).

CMOS monolithic active pixel sensors (MAPS) revolutionized visible imaging, and now they are making their way into high energy physics (HEP). Most detectors in HEP are still implemented in hybrid form with a readout chip and a silicon sensor chip, but monolithic sensors integrating readout and sensor in the same chip offer easier detector assembly, lower material budget, and lower cost. The largest system to date with monolithic CMOS sensors is the ALICE ITS2 detector covering a 10 m<sup>2</sup> area with 3 x 1.5 cm<sup>2</sup> ALPIDE CMOS sensor chips for about 12.5 billion pixels [1, 2]. The ALPIDE sensor [2, 3] contains full CMOS readout circuitry in the pixel, a pixel front end [4] with amplifier and discriminator and was the first monolithic sensor with a sparse readout

as in hybrid sensors. The sensor development was carried out from 2012 to 2016, the detector was installed in 2021 and is now taking data. Figure 1 shows pictures of the detector assembly, the ALPIDE chip, and the detector installed in the experiment. Figure 2 shows some events taken in the experiment.

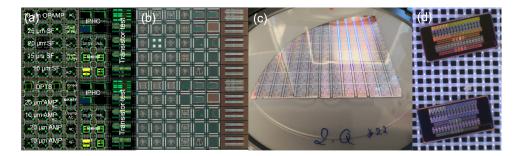

**Figure 3:** MLR1 submission in the TPSCo 65 nm ISC technology: (a) Layout and (b) picture of one reticle field on the wafer containing 70 test chips of 1.5 mm x 1.5 mm or 3 mm x 1.5 mm (55 different ones, 15 chips printed twice), (c) a diced quarter wafer on tape, and (d) transistor test chips in a gelpack.

The success of the ALPIDE and the ITS2 raised interest by several other HEP experiments. Also in ALICE a further upgrade is planned with the ITS3 [5–7], aimed to further reduce material budget by replacing the inner layers with wafer-scale stitched MAPS sensors, thinned to a few tens of microns to make them flexible and bend them around the beam pipe[8]. R&D work started at CERN in collaboration with several other institutes [9] to develop MAPS sensors in sub-100nm technologies, also with specific interest for the ALICE ITS3 upgrade, not only for better density and performance but also because 300 mm wafers give access to large stitched sensors. A first technology identified is the TPSCo 65 nm ISC imaging CMOS technology, and a first Multi Layer per Reticle run (MLR1) was completed (see Figure 3). It included sensor optimization based on general principles as already applied and summarized below in the 180 nm CMOS imaging technology before going into detail on the 65 nm technology.

## 2. Sensor optimization in the TowerJazz 180nm CMOS technology

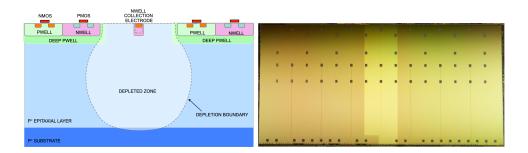

Figure 4: ALPIDE pixel cross-section (left), and die picture (right)[3].

Figure 4 shows a cross-section of the ALPIDE pixel and a die picture of the ALPIDE chip. The charge collection electrode in the center is formed by an nwell diffusion. The in-pixel circuitry is placed in a deep pwell, which shields nwells within the circuitry from the epitaxial layer preventing

them to collect charge. The depletion layer is 'balloon'-shaped, it extends from the junction at the collection electrode, and does not reach the pixel edges. Charge is still collected from outside the depletion layer by diffusion, but this collection is relatively slow and subject to charge trapping after non-ionizing radiation. The dependence of the extension of the depletion layer on the reverse bias is smaller for a spherical junction (as an approximation for the junction at the collectrode) than for a one-sided planar junction:

$$-V = \frac{qN_A}{2\mathcal{E}}\Delta^2 \qquad (a) \qquad \Delta = \sqrt{\frac{2\mathcal{E}|V|}{qN_A}} \qquad (b)$$

$$-V = \frac{qN_A}{3\varepsilon} \left[ -\frac{3R_2^2}{2} + \frac{R_2^3}{R_1} + \frac{R_1^2}{2} \right] (c) \qquad \qquad R_2 = \sqrt[3]{\frac{2\varepsilon|V|}{qN_A} \frac{3R_1}{2}} (d)$$

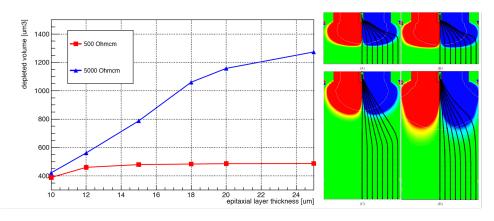

**Figure 5:** (left) Depleted volume versus epitaxial layer thickness for two different epitaxial resistivities. (right) Lateral electric field (red and blue for opposite sign) illustrating the extension of the depletion layer for the 10  $\mu$ m and 25  $\mu$ m points in the left plot. For the thin 10  $\mu$ m epitaxial layer (top) increasing the resistivity from 500 (a) to 5000  $\Omega$ cm (b) does not significantly increase the depletion volume, for the thicker 25  $\mu$ m epitaxial layer (bottom, c and d) it does.

Formulas (a) and (b) show that for an abrupt planar junction the depletion layer width  $\Delta$  is proportional to the square root of the reverse bias, or more precisely the sum of the externally applied reverse bias and the built-in voltage. Formula (c) shows reverse bias as a function of inner and outer radius R1 and R2 of the depletion layer for an abrupt spherical junction. R1 is approximately equal to the radius of the collection electrode, small for a small collection electrode. In case R2 is significantly larger than R1, the relation simplifies to formula (d), illustrating a much weaker dependence of the depletion on the reverse bias with a cubic root instead of a square root and a term equal to 1.5 times R1 under the root. After the depletion reaches the substrate or the deep pwells, further extension of the depletion is significantly reduced as both can provide significant depletion charge over a small volume to balance the additional reverse bias. This is further illustrated in Figure 5 (a), which shows the simulated depleted volume as a function of epitaxial layer thickness for two epitaxial resistivity values for an example pixel of 15  $\mu$ m pitch. For low thickness a higher resistivity does not provide an advantage, but for higher thicknesses it does. Figure 5 (right), shows

the simulated lateral electric field in a sensor, significantly different from zero only in the depletion layer (red and blue represent the opposite sign). This further illustrates that a higher resistivity results in a larger depleted volume only for a thicker epitaxial layer.

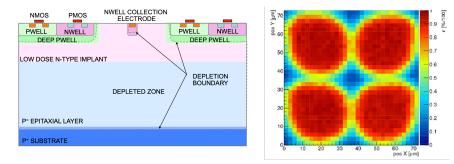

Figure 6: (a) Introduction of a blanket deep low dose n-type implant creating a planar junction to achieve full depletion of the epitaxial layer including the low dose implant [10](b) Detection efficiency degradation in the pixel corners after 5 x  $10^{14}$  1 MeV n<sub>eq</sub>/cm<sup>2</sup>[13].

As a first step in sensor optimization, the 180 nm TowerJazz process was modified in a side development of the ALPIDE sensor [10]: a deep blanket low dose n-type implant was introduced (Figure 6) to create a planar junction deep in the sensor separated from the collection electrode. This achieves full depletion of the epitaxial layer with some reverse bias, and signal charge collection by drift, without any layout changes in the sensor design except the definition of the region of the implant over the pixel matrix, hence allowing the same designs to be processed in the standard and the modified process for comparison. The process modification improved the tolerance to NIEL from  $10^{13}$  1 MeV  $n_{eq}/cm^2$  by an order of magnitude.

**Figure 7:** (a) Addition of an additional deep pwell or (b) a gap in the low dose n-type implant to increase the lateral field near the pixel edges. This strongly accelerates the signal charge towards the collection electrode [14] and fixed the detection efficiency loss in the corners [15].

This early result triggered a development in this modified process for the outer pixel layer of the ITk upgrade in ATLAS, also funded by the European Commission's Horizon 2020 Programme under contract number 675587, the STREAM project, with the design of two pixel sensors, the MALTA [11] and TJ MONOPIX [12], with very similar pixel sensor layout but different readout architectures. However, beam tests on irradiated devices from a first iteration showed significant detection efficiency degradation in the pixel corners after 5 x  $10^{14}$  1 MeV  $n_{eq}/cm^2$  due to a very low lateral field near the pixel edges allowing charge to be prone to trapping by radiation induced defects[13].

To improve the lateral field near the pixel edges, an additional deep pwell implant or a gap in the deep low dose n-type implant was introduced (Figure 7) [14]. This accelerates the charge collection for charges generated near the pixel edges and yielded the desired improvement for fluencies up to  $10^{15}$  1 MeV  $n_{eq}/cm^2[15]$  with an additional improvement from a higher gain and better uniformity of the pixel front end [16]. After this heavy irradiation the devices needed cooling to -20 °C to reduce the radiation-induced leakage and the noise.

## 3. Applying the same principles in 65 nm.

To optimize the sensor in the presence of significant in-pixel circuitry and also include standard digital gates in the pixel matrix, the same principles were applied to the 65 nm technology. As discussed before, without modifications the thinner epitaxial layer (10  $\mu$ m instead of 25  $\mu$ m in 180 nm) limits the extension of the depletion, and made these modifications more needed and more beneficial. A deep nwell was added to the pixel and its dose adjusted to form the low dose n-type implant. Also the deep pwell was modified to improve the isolation between the sensor and the circuitry, eliminate punch-through between the deep nwell implant and the circuitry, and prevent local potential wells retaining the signal charge. Four process splits were done, gradually moving from the standard process to the most optimized:

Split 1: Standard process without modifications.

Split 2: First modification of the deep pwell to improve isolation between circuitry and sensor and prevent punch-through between deep nwell and circuitry.

Split 3: Adding to split 2 the deep nwell adjustment in the pixel to allow full depletion.

Split 4: Adding to split 3 an additional deep pwell modification to prevent potential wells created by the additional in-pixel circuitry.

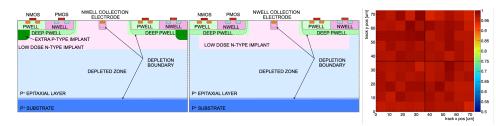

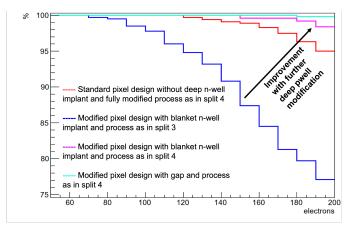

**Figure 8:** Simulated detection efficiency for minimum ionizing particles as a function of charge threshold for different process and pixel design variants for a pixel pitch of 15  $\mu$ m. The second deep pwell modification, the difference between split 3 and split 4, eliminates the efficiency loss by potential wells introduced by the additional in-pixel circuitry for the modified pixel design with blanket low dose n-type implant and brings its performance for the process of split 4 to what is expected.

Three different pixel designs were implemented for all splits: the standard pixel design without deep n-well implant, the modified with a blanket deep nwell implant, and the modified with a gap

in the deep nwell implant near the pixel border. No version with an additional deep pwell was implemented. Figure 8 shows the simulated detection efficiency for minimum ionizing particles as a function of the charge threshold for different process and pixel design variants. The most probable value for a MIP in 10  $\mu$ m is about 600 electrons with an onset of the Landau distribution well below. If charge sharing is more pronounced, the seed pixel collects less charge and detection efficiency degrades for lower charge thresholds. The figure shows that, contrary to the standard pixel design, the pixel variant with gap and all process modifications remains efficient for higher thresholds as it concentrates the charge much more on a single pixel. The pixel variant with a blanket low dose n-type implant exhibits a very low lateral field and is very sensitive to potential wells retaining signal charge. Figure 8 compares the detection efficiency for this pixel variant for process split 3 and split 4, and illustrates the effect of the second pwell modification to eliminate the impact of potential wells introduced by the additional in-pixel circuitry causing charge loss. After this split 4 gives the expected result that the detection efficiency is worst for higher thresholds in the standard pixel design without low dose n-type implant, intermediate for the modified pixel with blanket low dose n-type implant, and best for the modified pixel with gap in the implant due to the impact of the pixel design on the charge sharing.

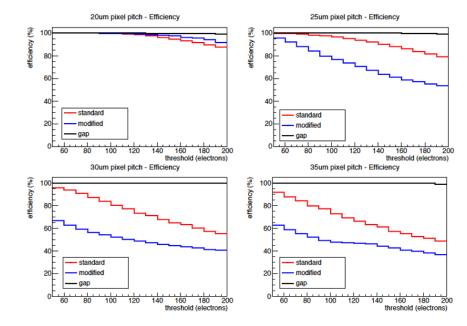

**Figure 9:** Simulated detection efficiency for minimum ionizing particles for the three different pixel designs, standard without low dose n-type implant, modified with blanket low dose n-type implant, and gap with a gap in the low-dose n-type implant, for several pixel pitches for the process with all modifications (as split 4). Only the pixel variant with gap maintains good efficiency at larger pixel pitches.

Figure 9 shows the simulated detection efficiency for minimum ionizing particles for the three different pixel variants and different pixel pitches for the process with all modifications (as split 4). Charge sharing reduces the amount of signal charge on a single pixel and reduces efficiency for larger thresholds and larger pixel pitches. The increased lateral field generated by the gap in the low dose n-type implant is essential to reduce the charge sharing and concentrate an amount of signal charge on a single pixel sufficient to remain efficient for larger pixel pitches.

# 4. Experimental results.

Figure 10: Different sensor test chips implemented on the first MLR1 run (a) the analog pixel test structure (APTS) [17] (b) the digital pixel test structure (DPTS) [18] and (c) the CE65[19, 20].

Figure 10 shows different pixel sensor test chips implemented in the first MLR1. All of them measure 1.5 mm by 1.5 mm. The analog pixel test structure or APTS [17] features a 6 by 6 pixel matrix, of which the central 4 by 4 pixels are connected via an analog buffer chain to the output. There are two variants, in the source follower version the readout chain consists of 4 source follower stages, in the opamp version the output stage is based on an operational amplifier. The digital pixel test structure or DPTS [18] contains a 32 by 32 pixel matrix at 15  $\mu$ m pitch with an amplifier and discriminator in each pixel and a time encoded digital readout. The CE65 contains a pixel matrix with analog readout in a rolling shutter configuration [19, 20].

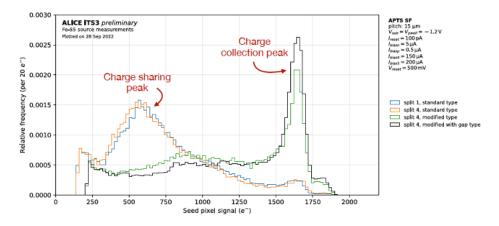

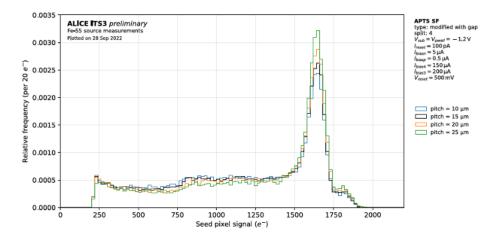

**Figure 11:** Spectrum of the charge collected on the seed pixel in different variants of the APTS with source follower under irradiation by a radioactive <sup>55</sup>Fe source[21].

Figure 11 shows the spectrum of the charge collected on the seed pixel from a <sup>55</sup>Fe radioactive source for different pixel variants and process splits. For the standard variant without low dose n-type implant and hence only a somewhat different deep pwell, the sensor behaves very similarly for the standard process (split 1) and for the process with all modifications (split 4): the iron peaks are still visible but rather low, and a very large charge sharing peak is visible at much lower signal amplitudes. The situation is very different for split 4 with the low dose n-type implant with and

**Figure 12:** Spectrum of the charge collected on the seed pixel under irradiation by a radioactive <sup>55</sup>Fe source for various pitches for the standard pixel variant without deep low dose n-type implant in the APTS with source follower. Charge sharing increases with pixel pitch resulting in a larger charge sharing peak and less pronounced iron peaks [21].

Figure 13: Spectrum of the charge collected on the seed pixel under irradiation by a radioactive  ${}^{55}$ Fe source for various pitches in the APTS with source follower for the pixel variant with low dose n-type implant with gap[21].

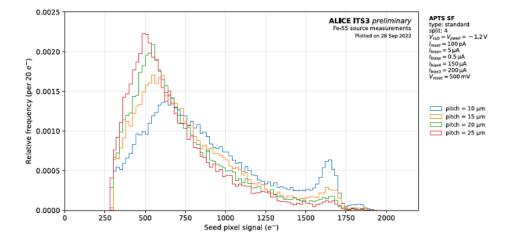

The impact of the process and pixel design optimization is further illustrated by measuring the spectrum of the charge collected by the seed pixel for different pixel pitches for the different variants under iron source exposure. Figure 12 shows this for the standard pixel variant without deep low dose n-type implant in the process of split 4. Charge sharing increases with increasing pixel pitch illustrated by the larger charge sharing peak and even less pronounced iron peaks. The contrast with the pixel variant with the deep low dose n-type implant with gap shown in Figure 13 is striking: charge sharing is suppressed with very pronounced <sup>55</sup>Fe peaks. For this pixel variant

the iron peaks are practically identical indicating that charge sharing is not significantly affected for the various pixel pitches.

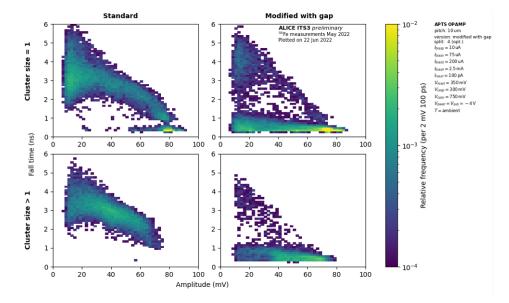

**Figure 14:** Signal fall time versus signal amplitude under <sup>55</sup>Fe irradiation measured on the APTS with opamp for different cluster sizes, comparing the standard pixel variant without deep low dose n-type implant (left) and the modified variant with gap in this n-type implant (right).

Figure 14 compares signal fall time versus signal amplitude for the standard pixel variant without low dose n-type implant and the modified variant with gap in this implant for various cluster sizes. For the standard variant fall time and amplitude are rather broadly distributed. For the variant with gap the amplitude is concentrated at the <sup>55</sup>Fe peak, and the fall time well below the ns. This also illustrates the impact of the process and pixel design modifications on the charge collection. For the variant with gap sensor timing studies are in progress. In 180 nm time resolutions better than 150 ps were achieved [22], there are first indications that this may be improved in 65 nm.

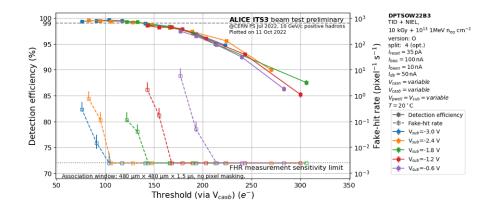

Figure 15 shows the detection efficiency and fake hit rate as a function of the charge threshold for the digital pixel test structure or DPTS with the pixel variant with low dose n-type implant with gap in the optimized process split (split 4). The efficiency is over 99 % and increasing the reverse bias brings the fake hit rate down to the detection limit, broadening the window of operation. The chip is irradiated up to 10 kGy and  $10^{13}$  1 MeV  $n_{eq}/cm^2$ , the requirement for the ITS3 upgrade. In fact, the same variant of the DPTS proved full detection efficiency in a test beam a few weeks after diced chips became available, validating the circuitry and the sensor with process modifications. In addition full efficiency was also reached after  $10^{15}$  1 MeV  $n_{eq}/cm^2$ , at room temperature[21]. Higher fluences are under investigation, but cooling will be necessary to reach full efficiency. Tolerance to ionizing radiation is in line with other deep submicron CMOS technologies[23, 24], and single event upset cross-sections are according to expectations.

MAPS do not necessarily require dedicated imaging technologies, but this section illustrates some flexibility on the foundry side has been very helpful to significantly influence the charge

Figure 15: Efficiency and fake hit measurement on the DPTS for various reverse bias on (deep) pwell and substrate. As reverse bias increases, the fake hit rate drops more rapidly under the detection limit giving more margin to operate at an efficiency above 99%[21].

collection in the sensor and enhance sensor performance. The modifications discussed here also improve sensor performance and operating margin before irradiation by concentrating more charge on a single pixel, this was experimentally confirmed also for the 180 nm in [25].

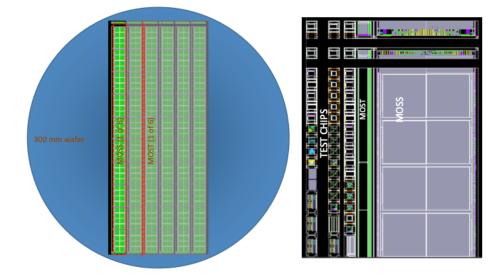

Figure 16: The ER1 submission contains two stitched sensors, MOSS and MOST, both about 26 cm long. The wafer (left) contains 6 of each, and also test chips. The reticle is shown on the right.

After these encouraging results, a new submission has just been completed with two stitched sensors, MOSS [26, 27] and MOST, and about 50 test chips, with as main goals to learn about stitching and continue to learn about the technology [28]. The two stitched chips have a different approach to powering and yield: the MOSS has fully separated powered sub-matrices [26, 27] to be powered down in case of defects, the MOST has a global power network, conservatively designed, to which small subcircuits are connected using switches. This allows a higher granularity in the powering, and subcircuits to be designed at full density. Figure 16 shows wafer and reticle.

#### 5. Conclusions

To develop sub-100 nm CMOS monolithic sensors, also towards the ALICE ITS3 upgrade, the TPSCo 65 nm ISC CMOS imaging technology was selected as a technology candidate. A first run, MLR1, was submitted with some splits on the process and various pixel sensor designs to optimize the sensor in the presence of complex readout circuitry including digital gates. The optimization is carried out following general principles already applied to the TowerJazz 180 nm imaging technology. Measurements now validate the effectiveness of this optimization with a fully efficient sensor, analog front end and digital readout chain in a 15  $\mu$ m by 15  $\mu$ m pixel in the DPTS, and measurements on other test chips clearly illustrate the impact of the optimization on the charge collection. All these results now help to qualify this technology for use in high energy physics. A stitched engineering run has been submitted to learn about stitching and to continue to learn about the technology.

# References

- [1] ALICE Collaboration, Journal of Physics G: Nuclear and Particle Physics 41 (8) (2014) 087002, https://doi.org/10.1088%2F0954-3899%2F41%2F8%2F087002.

- [2] F. Reidt, "The ALICE pixel detector upgrade", Pixel 2016, Sestri Levante, September 2016, 2016 JINST 11 C12038, https://doi.org/10.1088/1748-0221/11/12/C12038.

- [3] G. Aglieri Rinella, "The ALPIDE pixel sensor chip for the upgrade of the ALICE Inner Tracking System", Vienna Conference on Instrumentation 2016, Vienna, February 2016, NIM A 845 (2017) 583, https://doi.org/10.1016/j.nima.2016.05.016.

- [4] D. Kim, "Front end optimization for the monolithic active pixel sensor of the ALICE Inner Tracking System upgrade", 2016 JINST 11 C02042, https://doi.org/10.1088/ 1748-0221/11/02/c02042.

- [5] ALICE Collaboration, Tech. Rep. CERN-LHCC-2019-018. LHCC-I-034, CERN, Geneva (Dec 2019), https://cds.cern.ch/record/2703140.

- [6] A. Kluge, "ALICE ITS3 A bent, wafer-scale CMOS detector", Vienna Conference on Instrumentation, February 2022, NIM A 1041 (2022) 167315, https://doi.org/10.1016/ j.nima.2022.167315.

- [7] L. Lautner, "The ALICE Pixel Sensor Upgrade", this conference.

- [8] G. Aglieri Rinella et al., "First demonstration of in-beam performance of bent Monolithic Active Pixel Sensors", https://doi.org/10.48550/arXiv.2105.13000.

- [9] CERN Experimental Physics Department R&D, https://ep-dep.web.cern.ch/ rd-experimental-technologies.

- [10] W. Snoeys et al., "A process modification for CMOS monolithic active pixel sensors for enhanced depletion, timing performance and radiation tolerance", NIM A 871 (2017) 90, https://doi.org/10.1016/j.nima.2017.07.046.

- W. Snoeys

- [11] H. Pernegger et al., "First tests of a novel radiation hard CMOS sensor process for Depleted Monolithic Active Pixel Sensors", 2017 JINST 12 P06008, https://doi.org/10.1088/ 1748-0221/12/06/P06008.

- [12] C. Bespin et al., "DMAPS Monopix developments in large and small electrode designs" NIMA 978 (2020) 164460, https://doi.org/10.1016/j.nima.2020.164460.

- [13] E. J. Schioppa et al., "Measurement results of the MALTA monolithic pixel detector", NIM A 958 (2020) 162404, https://doi.org/10.1016/j.nima.2019.162404.

- [14] M. Munker et al., "Simulations of CMOS pixel sensors with a small collection electrode, improved for a faster charge collection and increased radiation tolerance", 2019 JINST 14 C05013, https://doi.org/10.1088/1748-0221/14/05/C05013.

- [15] E. M. Dyndal, et al., "Mini-MALTA: radiation hard pixel designs for small-electrode monolithic CMOS sensors for the High Luminosity LHC" 2020 JINST 15 P02005, https: //doi.org/10.1088/1748-0221/15/02/p02005.

- [16] F. Piro et al.,"A 1-μW Radiation-Hard Front-End in a 0.18-μm CMOS Process for the MALTA2 Monolithic Sensor", *IEEE Trans. Nucl. Sci.*, https://doi.org/10.1109/TNS. 2022.3170729.

- [17] W. Deng et al., "Design of an analog monolithic pixel sensor prototype in TPSCo 65 nm ISC CMOS imaging technology", *Topical Workshop on Electronics for Particle Physics TWEPP* 2022, Bergen, September 2022.

- [18] L. Cecconi et al., "Design and readout architecture of a monolithic binary active pixel sensor in TPSCo 65nm CMOS imaging technology", *Topical Workshop on Electronics for Particle Physics TWEPP 2022, Bergen, September 2022.*

- [19] S. Bugiel et al., "Charge sensing properties of monolithic CMOS pixel sensors fabricated in a 65 nm technology", Vienna Conference on Instrumentation, February 2022, NIM A 1040 (2022) 167213, https://doi.org/10.1016/j.nima.2022.167213.

- [20] J. Baudot, "From vertex detectors to applications in ion detection and spectrometry: a glimpse of MAPS R&D in Strasbourg", this conference.

- [21] I. Sanna et al., "Characterization of first prototypes fabricated in 65 nm CMOS technology for the ALICE Inner Tracking System upgrade", *IEEE Nuclear Science Symposium 2022, Milan October 2022.*

- [22] J. Braach et al.,"Performance of the FASTPIX Sub-Nanosecond CMOS Pixel Sensor Demonstrator", *Instruments 2022*, 6, 13, https://www.mdpi.com/2410-390X/6/1/13.

- [23] A. Dorda et al.,"Measurements of Total Ionizing Dose Effects in TPSCo65 nm and Influence of NMOS Bulk Bias", *Topical Workshop on Electronics for Particle Physics TWEPP 2022*, *Bergen, September 2022*.

- [24] P. Barrillon et al., "Digital cells radiation hardness study of TPSCo 65nm ISC technology by designing a Ring Oscillator", *Topical Workshop on Electronics for Particle Physics TWEPP* 2022, *Bergen, September 2022*.

- [25] K. Dort et al., "Comparison of different sensor thicknesses and substrate materials for the monolithic small collection-electrode technology demonstrator CLICTD", https://doi. org/10.1016/j.nima.2022.167413.

- [26] P. Leitao et al., "Development of a Stitched Monolithic Pixel Sensor prototype (MOSS chip) towards the ITS3 upgrade of the ALICE Inner Tracking System", *Topical Workshop on Electronics for Particle Physics TWEPP 2022, Bergen, September 2022.*

- [27] G.-H. Hong et al., "Monolithic Stitched Sensor (MOSS) Development for the ALICE ITS3 Upgrade", this conference.

- [28] V. Sarritzu et al., "The ALICE Pixel Readout Upgrade", this conference.