Stefan Christoph Mersche

---

## Der Quasi-n-Level Betrieb des Flying Capacitor Umrichters für Mittelspannungsanwendungen

---

# **Der Quasi-n-Level Betrieb des Flying Capacitor Umrichters für Mittelspannungsanwendungen**

Zur Erlangung des akademischen Grades eines

**DOKTORS DER INGENIEURWISSENSCHAFTEN**

**(Dr.Ing.)**

von der KIT-Fakultät für

Elektrotechnik und Informationstechnik

des Karlsruher Instituts für Technologie (KIT)

genehmigte

## **Dissertation**

von

M.Sc. Stefan Christoph Mersche

Tag der mündlichen Prüfung:

17. Mai 2023

Hauptreferent:

Prof. Dr.-Ing. Marc Hiller

Korreferent:

Prof. Dr.-Ing. Marco Liserre

(Christian-Albrechts-Universität)

**Karlsruher Institut für Technologie (KIT)

Elektrotechnisches Institut (ETI)**

Zur Erlangung des akademischen Grades eines Doktor-Ingenieurs

von der KIT-Fakultät für Elektrotechnik und Informationstechnik des

Karlsruher Instituts für Technologie (KIT) genehmigte Dissertation

von M.Sc. Stefan Christoph Mersche, geb. in Karlsruhe

Tag der mündlichen Prüfung: 17. Mai 2023

Hauptreferent: Prof. Dr.-Ing. Marc Hiller

Korreferent: Prof. Dr.-Ing. Marco Liserre

(Christian-Albrechts-Universität zu Kiel)

Dieses Dokument ist unter der Creative Commons Lizenz verfügbar

Attribution-ShareAlike 4.0 International License (CC BY-SA 4.0) soweit nicht

anders angegeben: <https://creativecommons.org/licenses/by-sa/4.0/deed.en>

DOI: 10.5445/IR/1000159689

# Vorwort

Diese Dissertation ist während meiner Tätigkeit als wissenschaftlicher Mitarbeiter am Elektrotechnischen Institut (ETI) des Karlsruher Instituts für Technologie (KIT) entstanden. Es war eine Zeit von wissenschaftlicher Freiheit in Forschung und Lehre mit vielen Höhen und Tiefen. In den Jahren am Institut gab es viele Möglichkeiten meine persönlichen Kompetenzen und Fähigkeiten weiterzuentwickeln. Dabei war das Aufgabenspektrum sehr vielseitig und in manchen Bereichen sehr umfangreich, sehr arbeitsintensiv und auch sehr nervenaufreibend. In dieser Zeit war ein ständiger Wandel am Institut und so durfte ich sehr viele Mitarbeitende und Studierende am KIT kennen lernen. Bei der Arbeit und meinen vielen verschiedenen Aufgaben am Institut war es mir nie langweilig und die Arbeit war nie einseitig.

Nach dieser Zeit möchte ich mich bei einigen Personen bedanken. Für die Möglichkeit der Promotion und die Funktion als Hauptreferent möchte ich mich bei Prof. Dr.-Ing. Marc Hiller bedanken. Bei Prof. Dr.-Ing. Marco Liserre möchte ich mich für die Übernahme des Korreferats bedanken.

Bei meinem Bürokollegium in den Jahren - M. Schnarrenberger, E. Specht, F. Sommer, D. Schultz und S. Knierim - möchte ich mich für die zahlreichen amüsanten Stunden und anregenden Diskussionen im Büro bedanken. Das Kollegium in den letzten Monaten möchte ich nicht vergessen - F. Hoffmann, R. Rehm und B. Jux.

Besonders möchte ich mich bei D. Bräckle, P. Himmelmann, F. Stamer, L. Stefanski, R. Schwendemann, M. Brodatzki und M. Schnarrenberger für die zahlreichen Hilfestellungen, die Unterstützung und sehr gute Zusammenarbeit, in den Jahren meiner Tätigkeit am Institut, bedanken.

Nicht zu vergessen, gilt mein Dank P. Kiehnle und B. Schmitz-Rode für die gute Zusammenarbeit in der Weiterentwicklung der Software des ETI-SOC-Systems am Institut.

Ebenso gilt mein besonderer Dank den Kollegen in der Werkstatt für die Unterstützung bei den Projekten in diesen Jahren. Auch bei sehr schwierigen und ambitionierten Vorhaben in unterschiedlichen Bereichen der Infrastruktur- oder Forschungsvorhaben wurde immer ein gemeinsamer Weg gefunden.

Bei R. Schreier und C. Laeske möchte ich mich für die langjährige Unterstützung durch ihre studentische Hiwi-Tätigkeit und ihre Mitarbeit durch ihre studentischen Abschlussarbeiten bei meiner Forschung bedanken.

Die freundschaftliche Umgangsform zwischen den Mitarbeitenden am Institut war sehr schön und die mehrheitlich gute Zusammenarbeit in den Jahren hat mich gefreut. Viele Erlebnisse mit vielen Mitarbeitenden aus dieser Zeit werden wohl länger bei mir in Erinnerung bleiben.

Die Exkursionen und Konferenzbesuche waren in der Zeit die schöneren Momente. Besonders der letzte Konferenzbesuch am anderen Ende der Welt zusammen mit J. Stoß und A. Liske war eine besondere Zeit.

Zuletzt und nicht zu vergessen, möchte ich mich bei meiner Familie bedanken für die Unterstützung und Geduld während meines Studiums und meiner Promotion. Bei meiner Mutter möchte ich mich im Besonderen für das Korrekturlesen meiner Dissertation bedanken.

Eine Promotion ist nicht nur eine Tätigkeit, sondern ein persönlicher Entwicklungsprozess, der nicht beim Verlassen der Arbeitsstätte endet, sondern zu Gedankenprozessen in allen Lebenslagen des beruflichen und privaten Lebens führt.

# Kurzfassung

In dieser Arbeit wird der Quasi-n-Level Betrieb des Flying Capacitor Umrichters (FICs) betrachtet. Dabei ist der Fokus auf dem Quasi-Zwei-Level-Betrieb (Q2LB) und der Quasi-Drei-Level-Betrieb (Q3LB) wird ebenfalls kurz betrachtet. Zur Einordnung der Arbeit wird eine kurze Übersicht an Multilevel-Umrichtern mit einer zugehörigen Gruppierung präsentiert.

Weiter wird allgemein der Quasi-n-Level Betrieb eines Multilevel-Umrichters mit Vor- und Nachteilen einschließlich einer Übersicht an bisher veröffentlichten Forschungsergebnissen vorgestellt. Beim Flying Capacitor Umrichter (FIC) mit dem Q2LB ist ein nicht unerheblicher Teil der Veröffentlichungen im Rahmen dieser Dissertation entstanden. Ein Vergleich des Q2LBs vom Modular Multilevel Converter (MMC) und FIC ist inbegriffen.

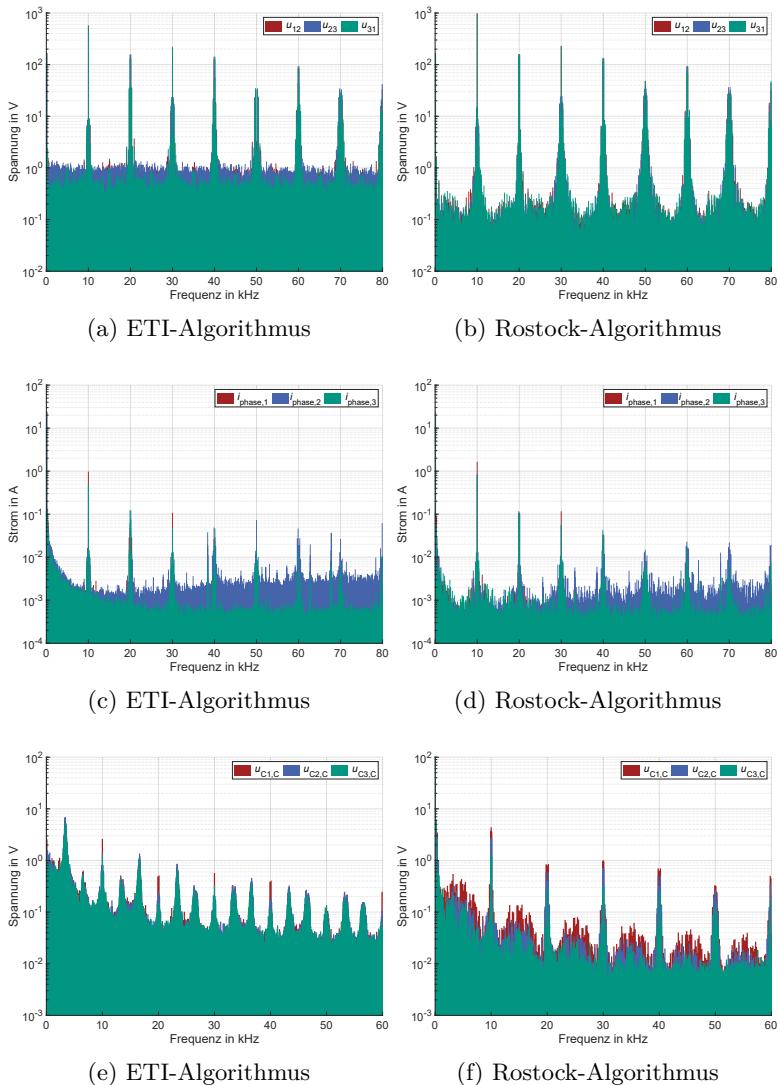

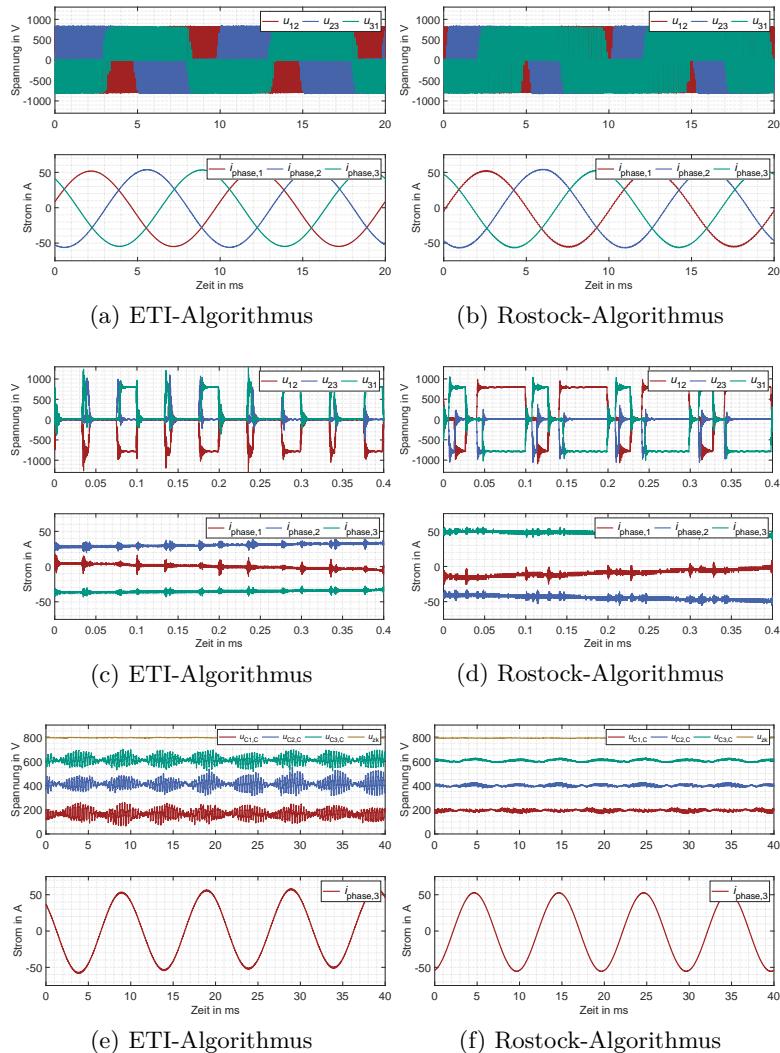

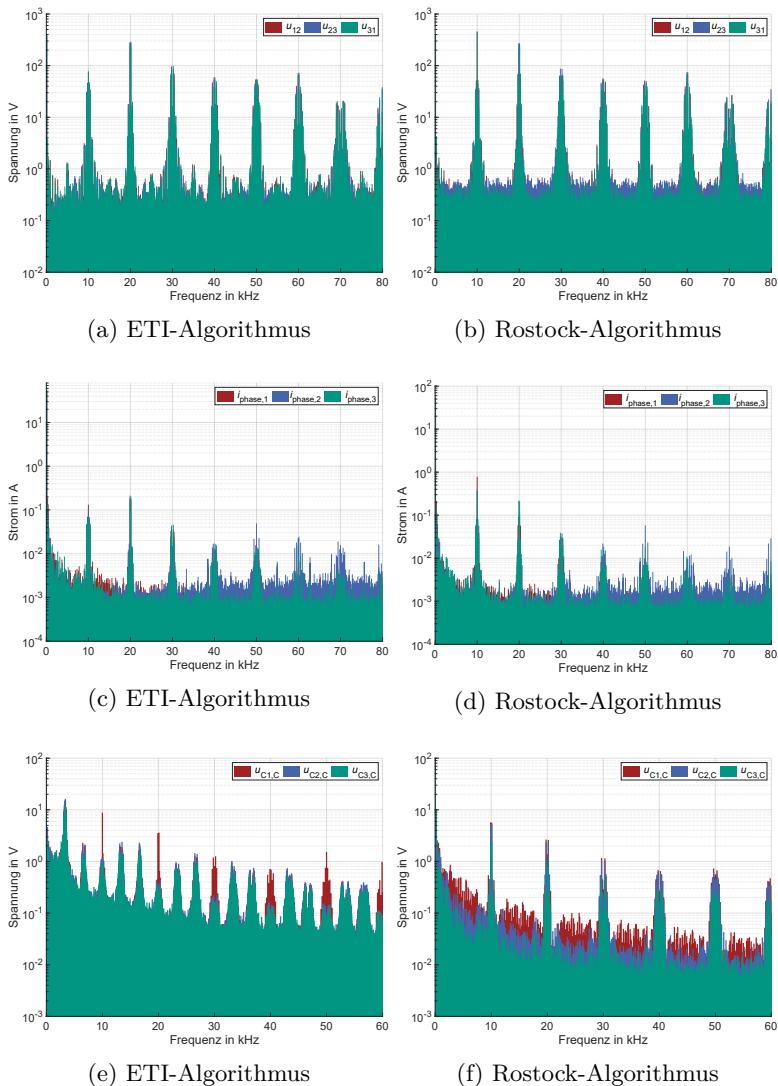

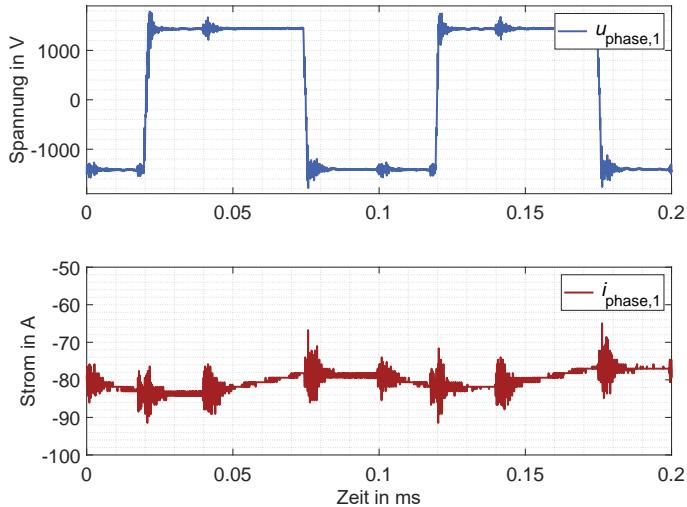

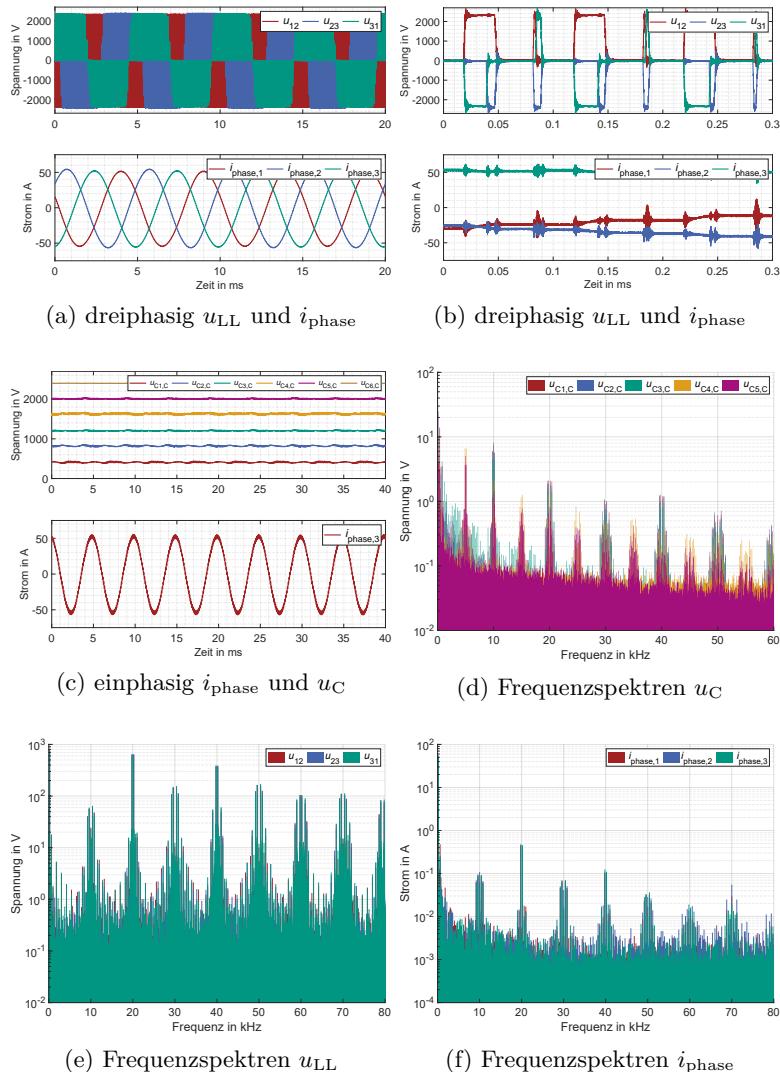

Im Hauptteil des Werks wird der Q2LB und Q3LB des FICs erläutert. Dazu wird die Theorie mit Auslegung der wichtigsten Leistungskomponenten präsentiert und anhand von Simulationsergebnissen verdeutlicht. Ebenso werden die Regelung, die Modulation und die Symmetrierungsalgorithmen für die Kondensatorspannungen erklärt. Bei den Symmetrierungsalgorithmen wird die Funktionsweise und die unterschiedlichen Auswirkungen der verschiedenen Algorithmen dargestellt.

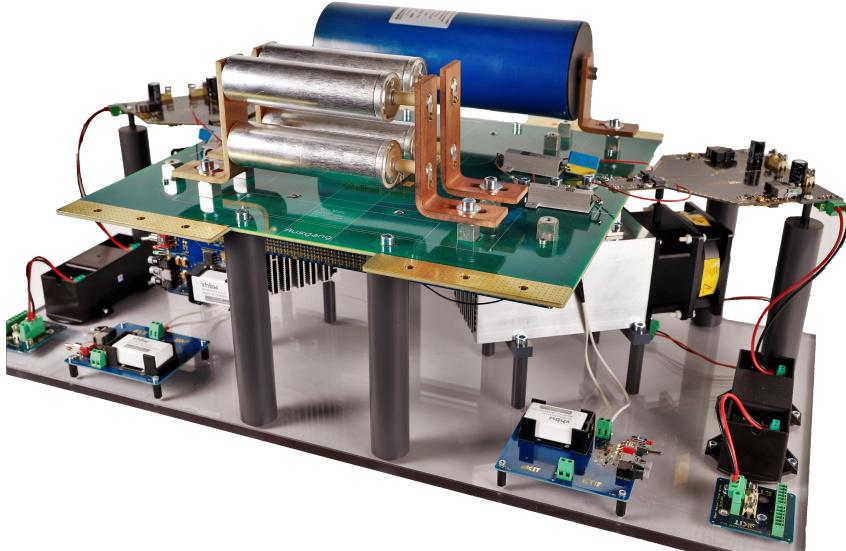

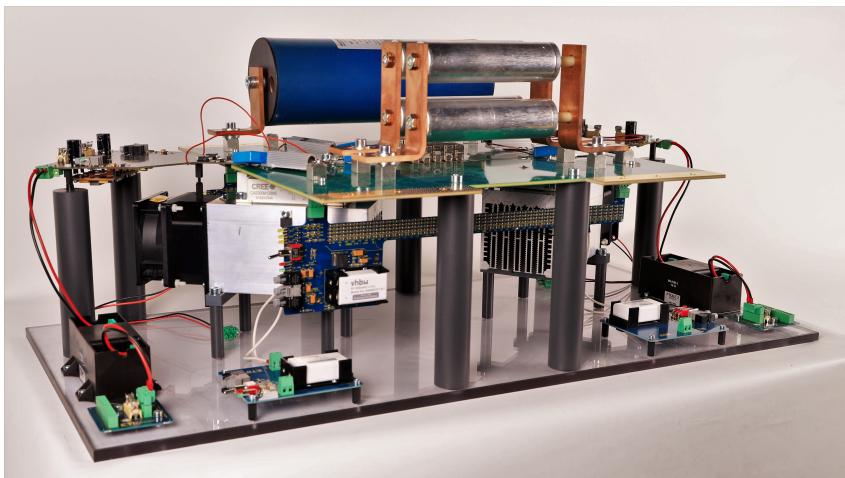

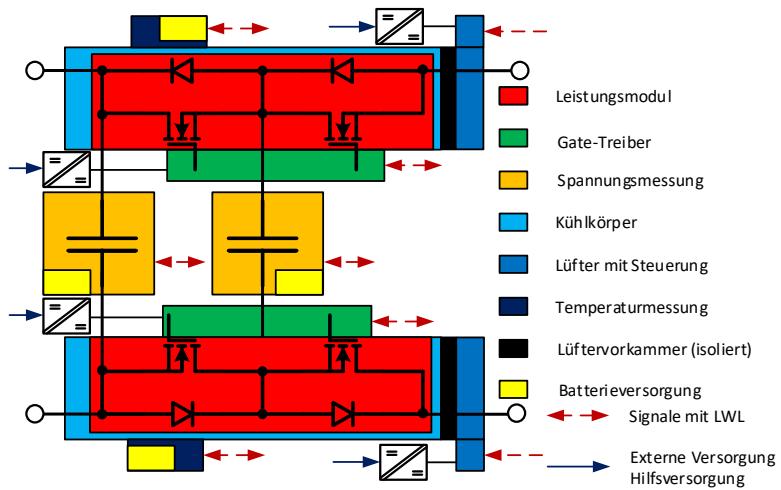

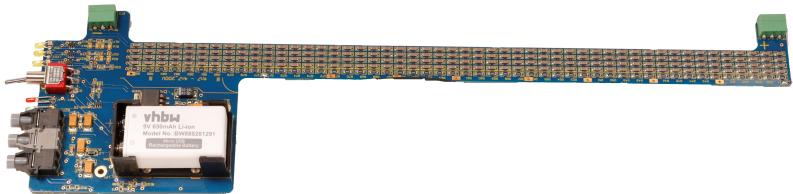

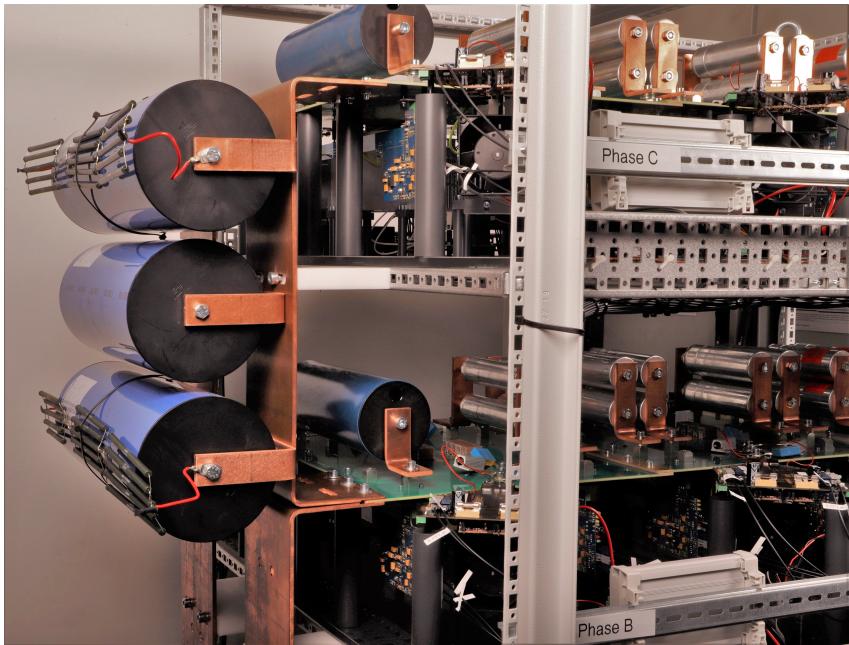

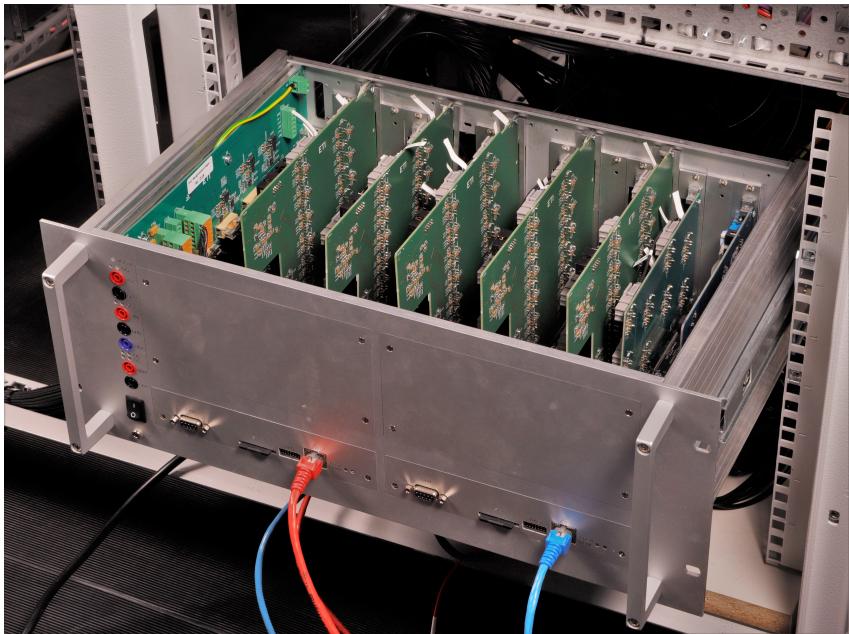

Zur Validierung der Theorie des Q2LBs des FICs wurde ein Prototyp aufgebaut und der entworfene Hardwareaufbau für Mittelspannung wird beschrieben. Das Konzept des PEBBs wird erläutert und mit allen wichtigen Komponenten und Funktionsgruppen vorgestellt. Das realisierte dreiphasige Umrichtersystem mit der zugehörige Signalverarbeitung wird ebenfalls erläutert. Ein wichtiger Teil des Prototyps ist die Struktur der Signalverarbeitung und die implementierten Funktionen an unterschiedlicher Stelle.

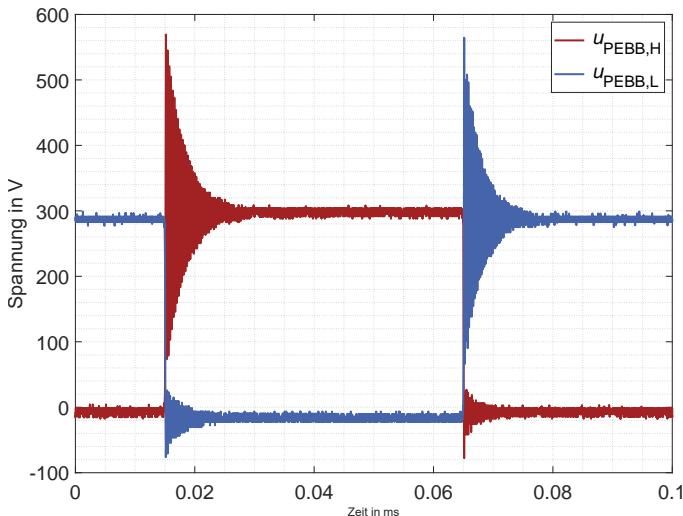

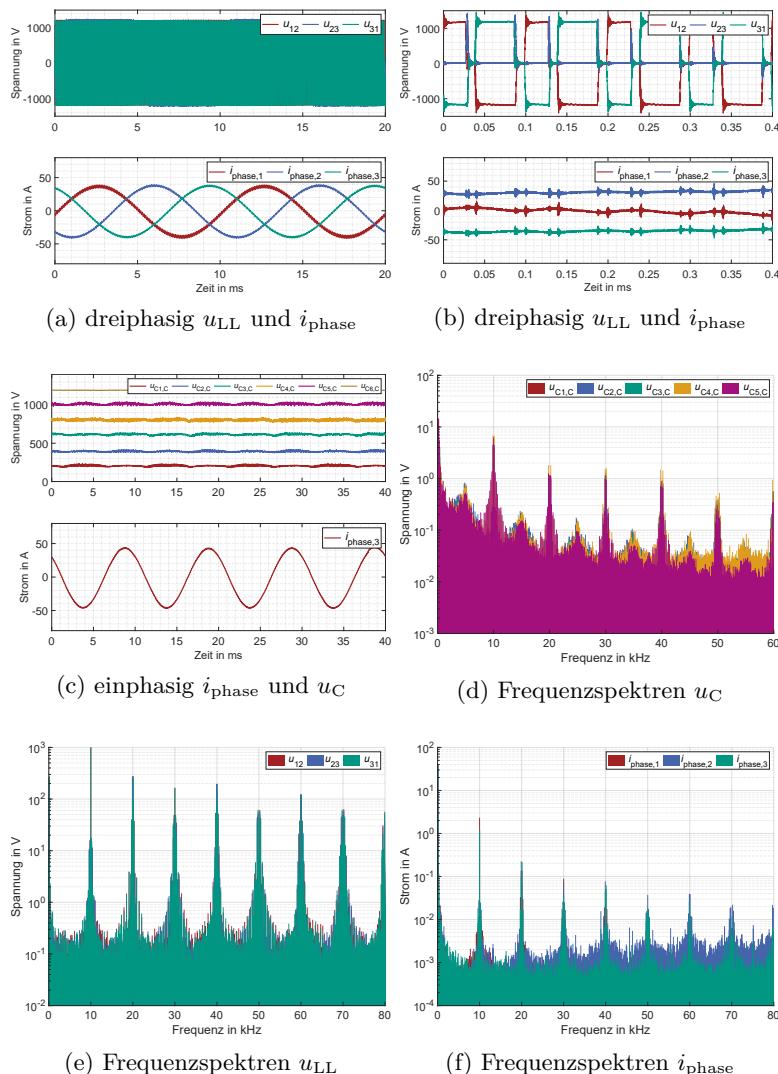

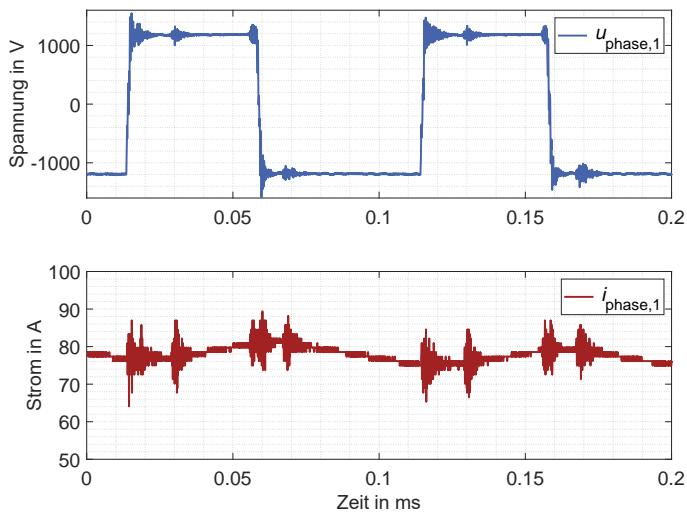

Da es bisher keine Mittelspannungsumrichter am ETI gab, wird der in den letzten Jahren geplante und aufgebaute Prüfplatz für hochdynamische Mittelspannungsumrichter beschrieben. Die mit dem realisierten Hardwareaufbau generierten Messergebnisse werden bei der Inbetriebnahme einphasig mit Niederspannung und dreiphasig mit Niederspannung gezeigt und erläutert. Im extra entworfenen Prüfplatz erzeugte Messergebnisse mit Mittelspannung wurden ebenfalls analysiert. Mit den Messergebnissen des Quasi-Zwei-Level-Betriebs (Q2LBs) wurde gezeigt, dass sich durch diese Betriebsweise das  $\frac{du}{dt}$  und die Überspannungen am Phasenausgang im Vergleich zu einem vergleichbaren Zwei-Level Umrichter verringern lässt.

# Inhaltsverzeichnis

|                                                                                      |            |

|--------------------------------------------------------------------------------------|------------|

| <b>Vorwort</b>                                                                       | <b>i</b>   |

| <b>Kurzfassung</b>                                                                   | <b>iii</b> |

| <b>1 Einleitung</b>                                                                  | <b>1</b>   |

| 1.1 Ziele der Arbeit . . . . .                                                       | 3          |

| 1.2 Gliederung der Arbeit . . . . .                                                  | 4          |

| 1.3 Wissenschaftliche Beiträge . . . . .                                             | 6          |

| <b>2 Stand der Technik</b>                                                           | <b>9</b>   |

| 2.1 Übersicht über Multilevel-Topologien . . . . .                                   | 10         |

| 2.1.1 Neutral Point Clamped (NPC) . . . . .                                          | 12         |

| 2.1.2 Flying Capacitor Umrichter (FlC) . . . . .                                     | 14         |

| 2.1.3 Cascaded H-Bridge (CHB) . . . . .                                              | 18         |

| 2.1.4 Modular Multilevel Converter (MMC) . . . . .                                   | 20         |

| 2.2 Betrieb des Flying Capacitor Umrichters . . . . .                                | 26         |

| 2.2.1 Funktionsweise der Topologie . . . . .                                         | 27         |

| 2.2.2 Konventionelle Symmetrierung und Modulation . . . . .                          | 32         |

| <b>3 Der Quasi-n-Level Betrieb eines Multilevel-Umrichters</b>                       | <b>39</b>  |

| 3.1 Idee des Quasi-Zwei-Level Betriebs . . . . .                                     | 40         |

| 3.2 Vorteile des Quasi-Zwei-Level Betriebs . . . . .                                 | 42         |

| 3.3 Übersicht bisheriger Forschung bei verschiedenen Multilevel-Umrichtern . . . . . | 47         |

| 3.3.1 Neutral Point Clamped (NPC) . . . . .                                          | 47         |

| 3.3.2 Flying Capacitor Umrichter (FlC) . . . . .                                     | 47         |

| 3.3.3 Modular Multilevel Converter (MMC) . . . . .                                   | 49         |

|          |                                                                                                   |            |

|----------|---------------------------------------------------------------------------------------------------|------------|

| 3.4      | Quasi-Zwei-Level Betrieb des Modularen Multilevel Umrichters . . . . .                            | 51         |

| 3.4.1    | Prinzip beim Quasi-Zwei-Level Betrieb des Modularen Multilevel Umrichters . . . . .               | 51         |

| 3.4.2    | Auslegung der Bauteile bei Quasi-Zwei-Level Betrieb des Modularen Multilevel Umrichters . . . . . | 53         |

| 3.5      | Vergleich Quasi-Zwei-Level-Betrieb bei FIC und MMC . . . . .                                      | 55         |

| 3.5.1    | Exemplarischer Vergleich Q2LB FIC mit Q2LB MMC                                                    | 55         |

| 3.5.2    | Resümee Q2LB des MMCs und FICs . . . . .                                                          | 58         |

| <b>4</b> | <b>Der Quasi-n-Level Betrieb des Flying Capacitor Umrichters</b>                                  | <b>61</b>  |

| 4.1      | Der Quasi-Zwei-Level Betrieb des Flying Capacitor Umrichters . . . . .                            | 61         |

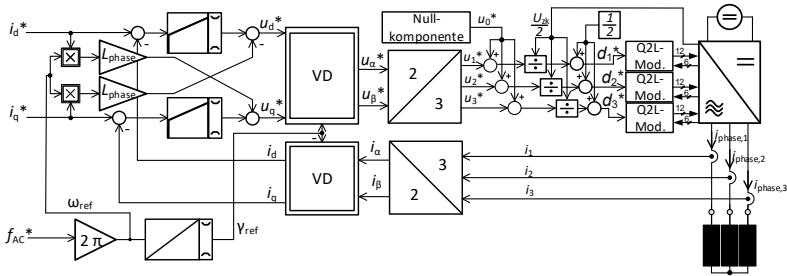

| 4.1.1    | Regelung des Umrichters im Quasi-Zwei-Level Betrieb                                               | 63         |

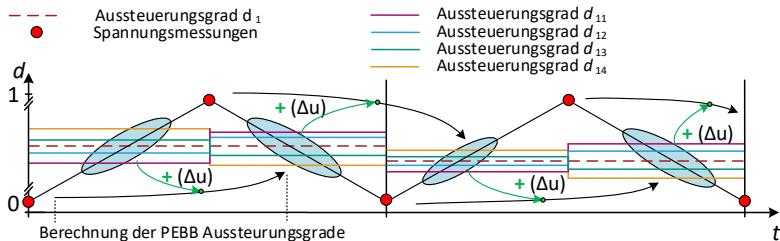

| 4.1.2    | Modulationsprinzip des Quasi-Zwei-Level Betriebs                                                  | 65         |

| 4.1.3    | Symmetrierungsalgorithmen der Kondensatorspannungen . . . . .                                     | 67         |

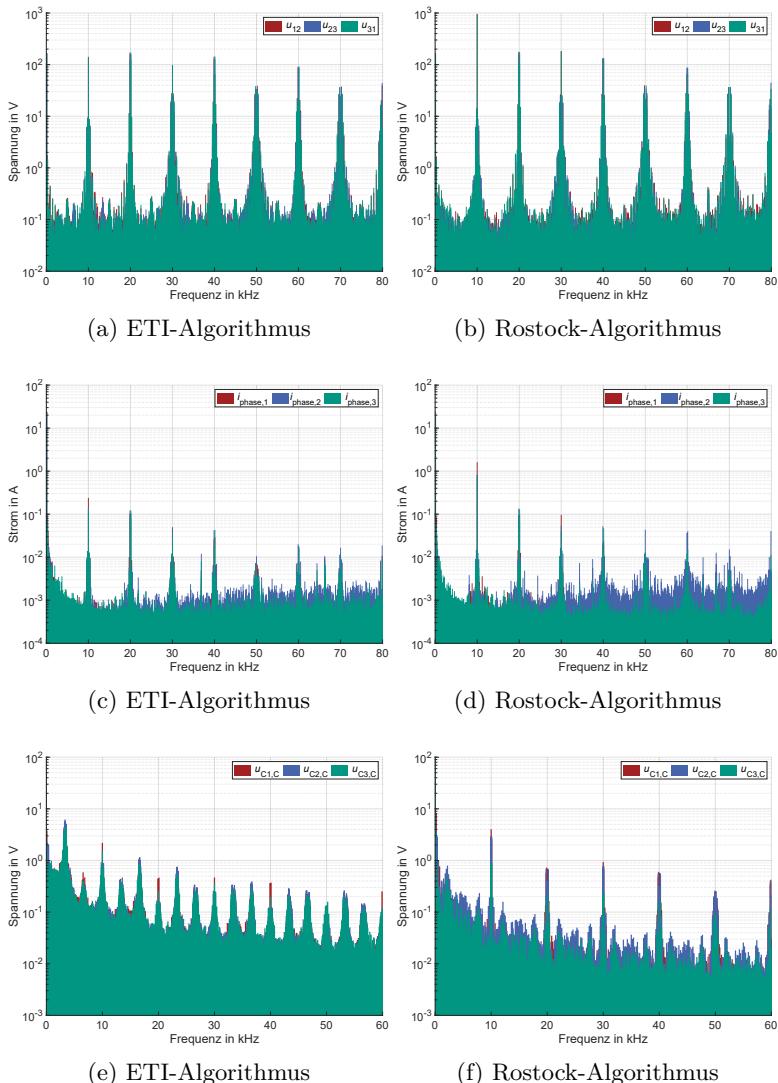

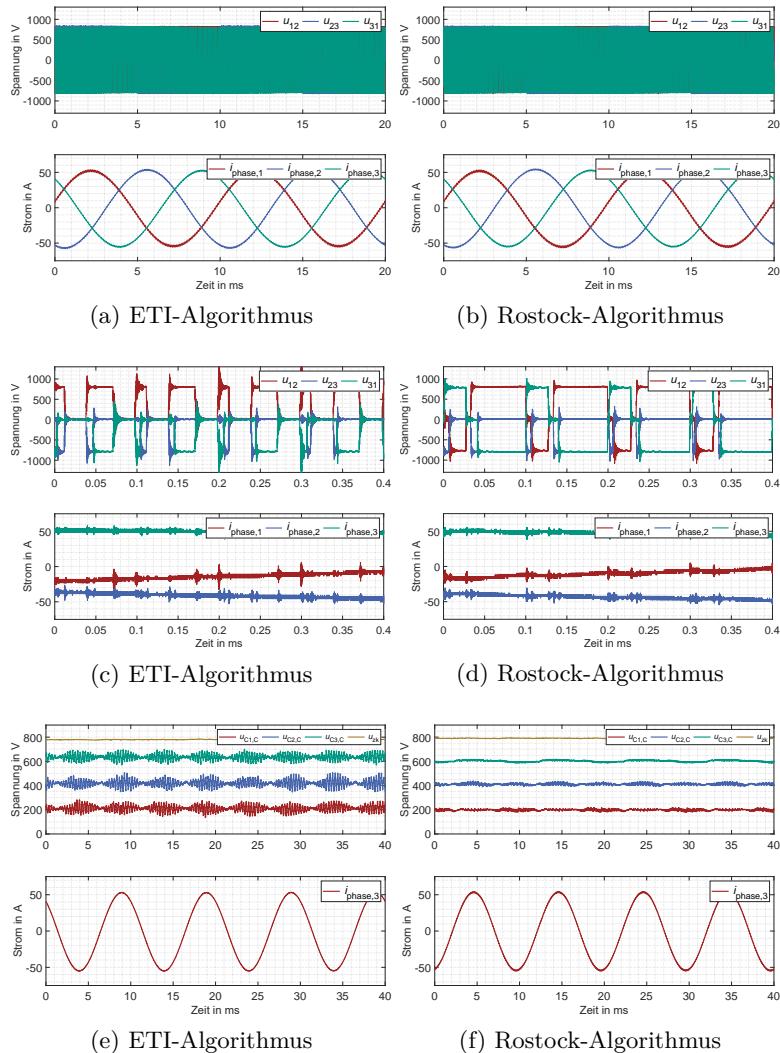

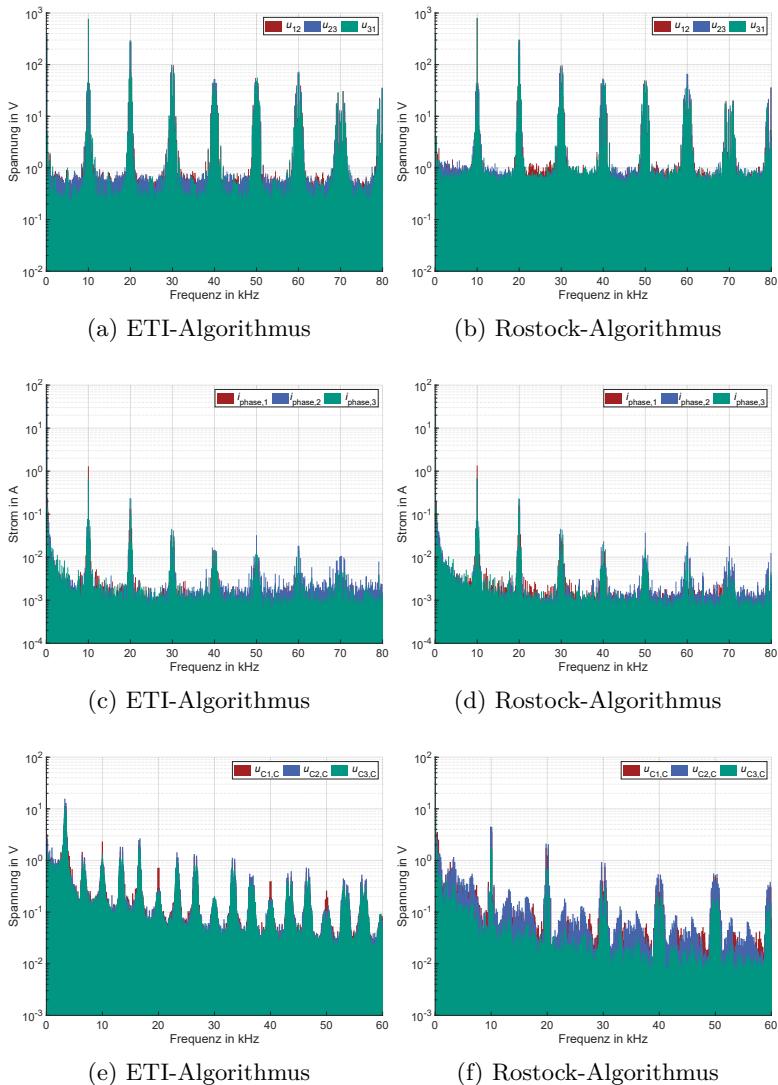

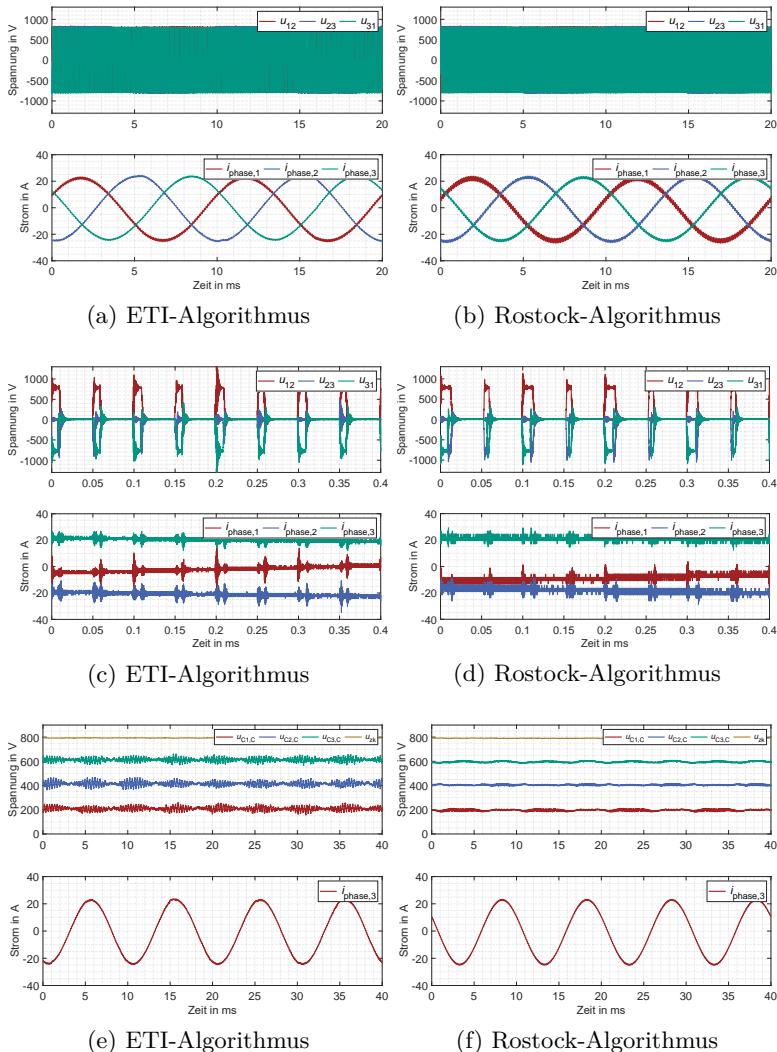

| 4.1.4    | Vergleich der Symmetrierungsalgorithmen mit Simulationsergebnissen . . . . .                      | 78         |

| 4.1.5    | Betriebspunkt Leerlauf . . . . .                                                                  | 83         |

| 4.1.6    | Vorladung der Kondensatoren . . . . .                                                             | 85         |

| 4.1.7    | Auslegung der Bauelemente . . . . .                                                               | 87         |

| 4.2      | Der Quasi-Drei-Level-Betrieb des Flying Capacitor Umrichters . . . . .                            | 92         |

| 4.2.1    | Modulationsprinzip des Quasi-Drei-Level Betriebs                                                  | 92         |

| 4.2.2    | Symmetrierungsalgorithmus der Kondensatorspannungen . . . . .                                     | 93         |

| 4.2.3    | Auslegung der Bauelemente . . . . .                                                               | 95         |

| 4.2.4    | Simulationsergebnisse des Quasi-Drei-Level Betriebs                                               | 98         |

| <b>5</b> | <b>Der Hardwareprototyp für den Q2LB des FICs</b>                                                 | <b>103</b> |

| 5.1      | Die Leistungszelle – der „PEBB“ . . . . .                                                         | 103        |

| 5.1.1    | Konzept . . . . .                                                                                 | 106        |

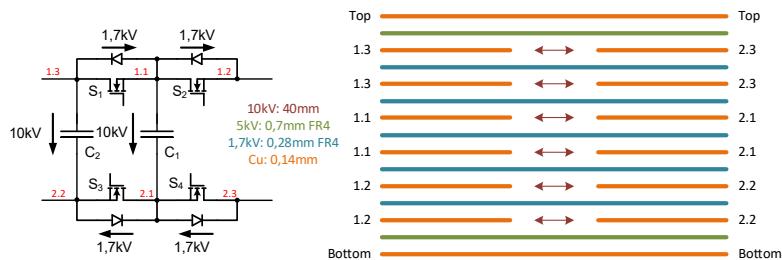

| 5.1.2    | Bauelemente . . . . .                                                                             | 106        |

| 5.1.3    | Mechanische Konstruktion . . . . .                                                                | 109        |

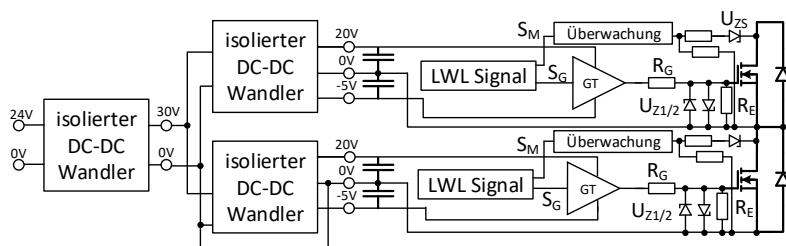

| 5.1.4    | Funktionsgruppen . . . . .                                                                        | 119        |

| 5.1.5    | Zusätzliche Beschaltung . . . . .                                                                 | 127        |

| 5.2      | Der dreiphasige 7-Level FIC . . . . .                                                             | 132        |

| 5.2.1    | DC-Zwischenkreis . . . . .                                                                        | 132        |

|                                               |                                                                                             |            |

|-----------------------------------------------|---------------------------------------------------------------------------------------------|------------|

| 5.2.2                                         | Ausgangstrommessung . . . . .                                                               | 137        |

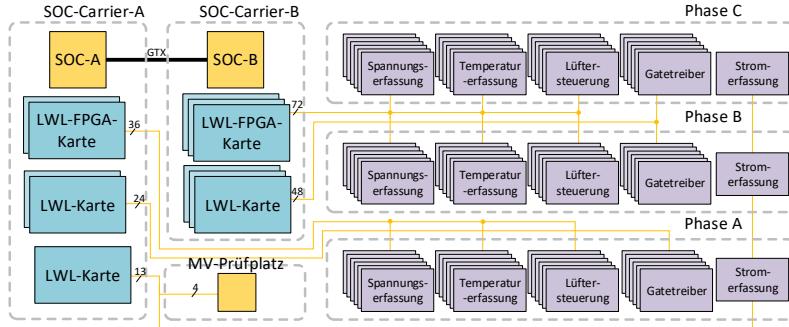

| 5.3                                           | Das Signalverarbeitungssystem . . . . .                                                     | 139        |

| 5.3.1                                         | Komponenten der Signalverarbeitung . . . . .                                                | 140        |

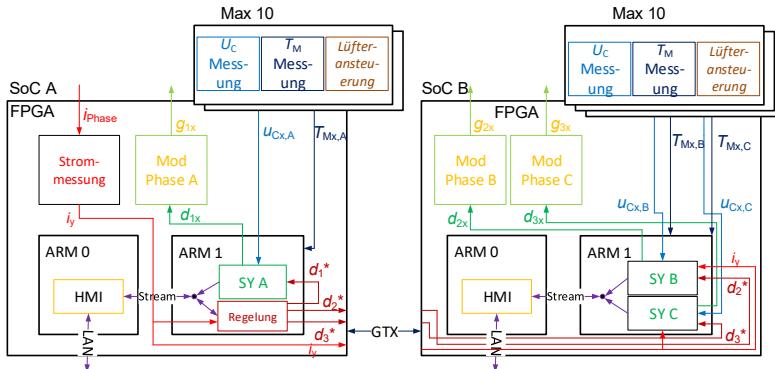

| 5.3.2                                         | Signalplan . . . . .                                                                        | 142        |

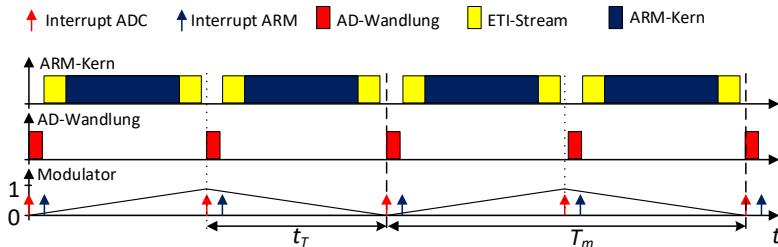

| 5.3.3                                         | Struktur der Implementierung . . . . .                                                      | 143        |

| 5.3.4                                         | Interrupt basierte Softwareimplementierung . . . .                                          | 145        |

| 5.3.5                                         | Kompensation der Totzeit bei Kondensatorspannungsmessung . . . . .                          | 147        |

| 5.3.6                                         | Ausgangstromregelung . . . . .                                                              | 149        |

| <b>6</b>                                      | <b>Der Prüfplatz für hochdynamische Mittelspannungsumrichter</b>                            | <b>151</b> |

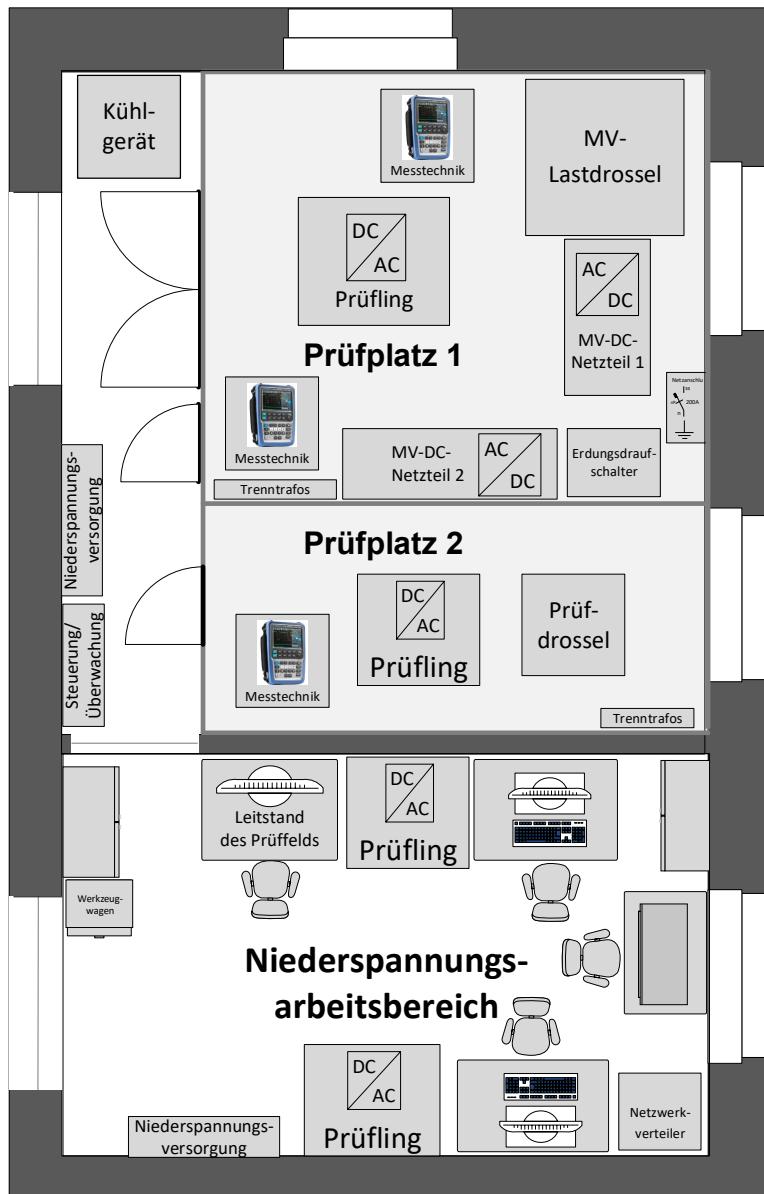

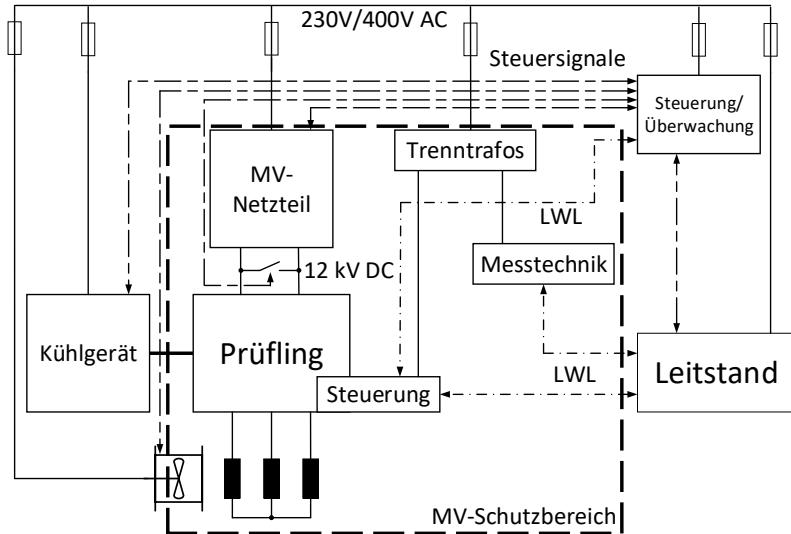

| 6.1                                           | Konzept des Prüfplatzes . . . . .                                                           | 153        |

| 6.2                                           | Komponenten des Prüfplatzes . . . . .                                                       | 155        |

| 6.2.1                                         | MV-Netzteil des Prüfplatzes . . . . .                                                       | 156        |

| 6.2.2                                         | MV-Lastdrossel des Prüfplatzes . . . . .                                                    | 156        |

| 6.2.3                                         | Trenntransformatoren des Prüffelds . . . . .                                                | 158        |

| 6.2.4                                         | Erdungsdraufschalter des Prüfplatzes . . . . .                                              | 158        |

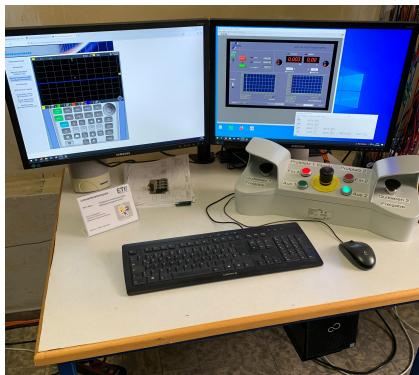

| 6.2.5                                         | Leitstand des Prüffelds . . . . .                                                           | 158        |

| <b>7</b>                                      | <b>Messergebnisse</b>                                                                       | <b>159</b> |

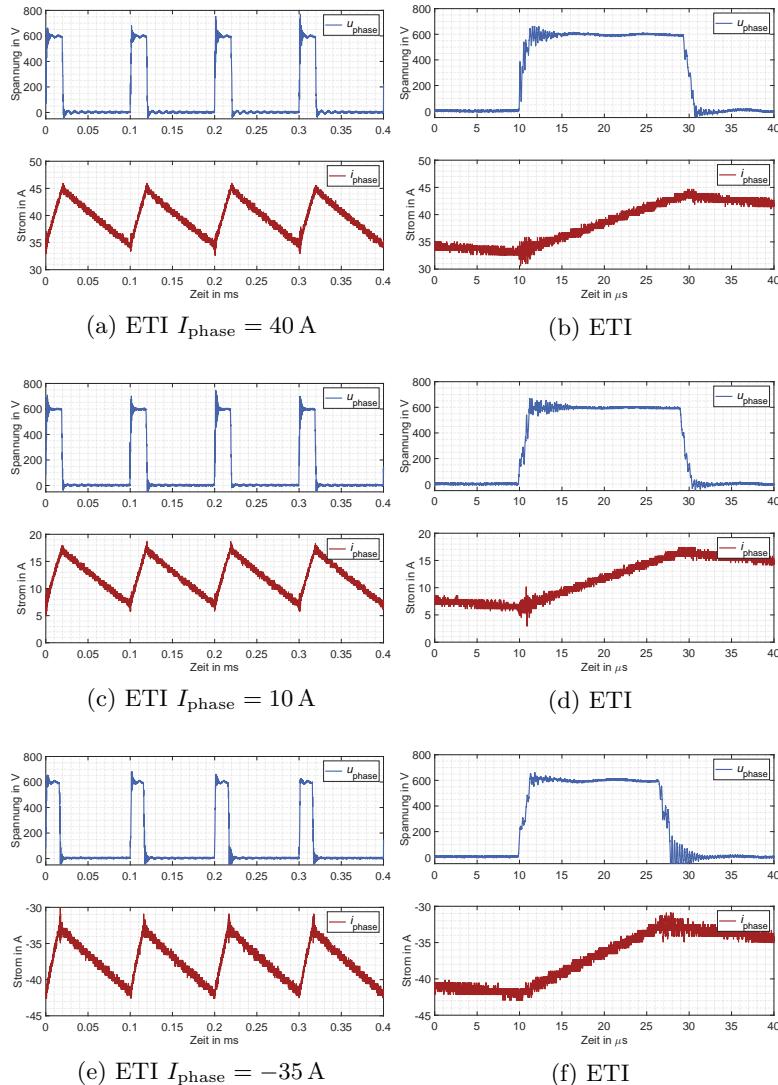

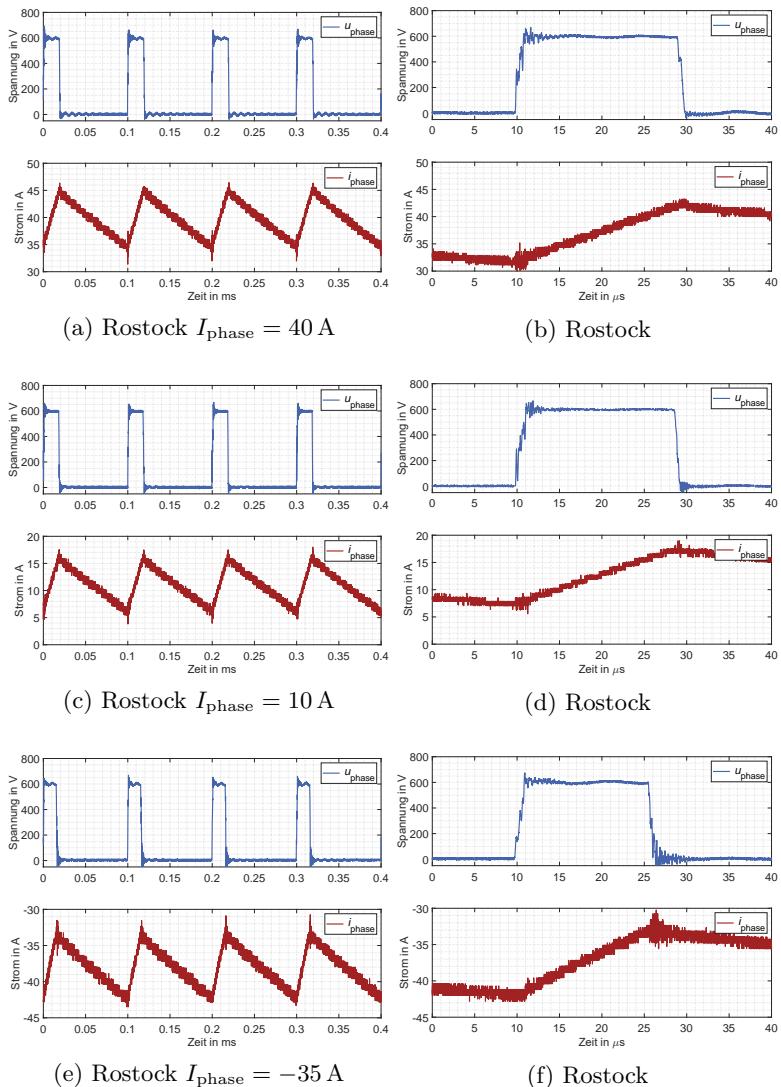

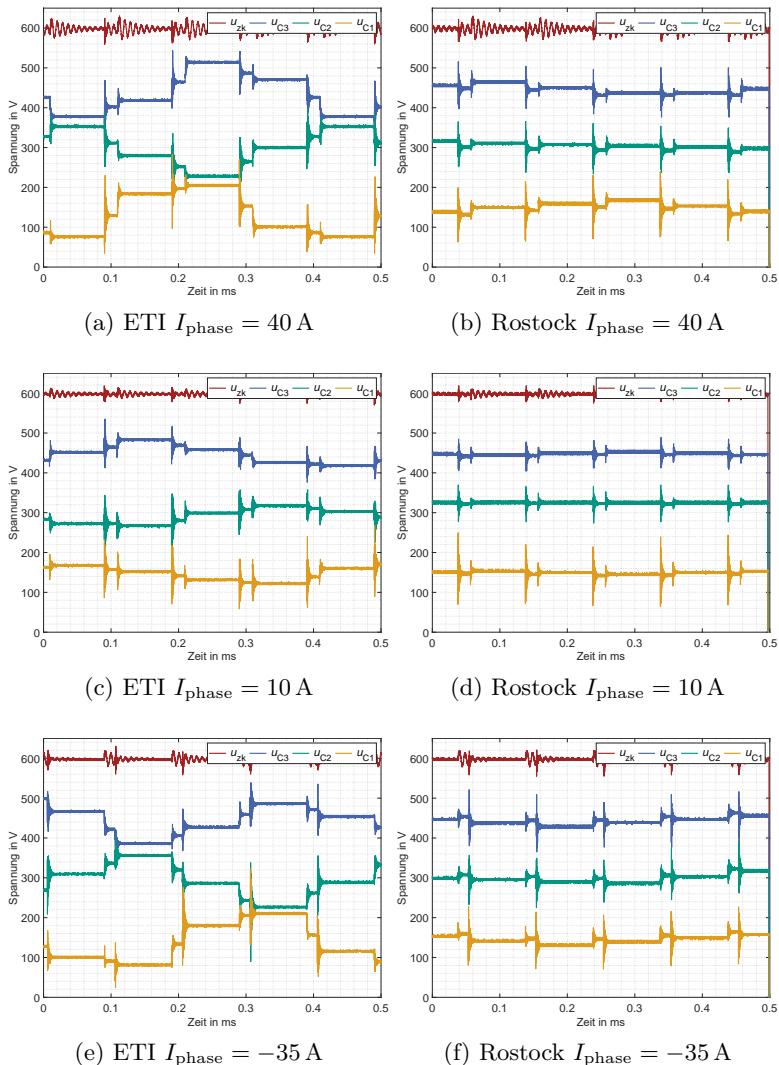

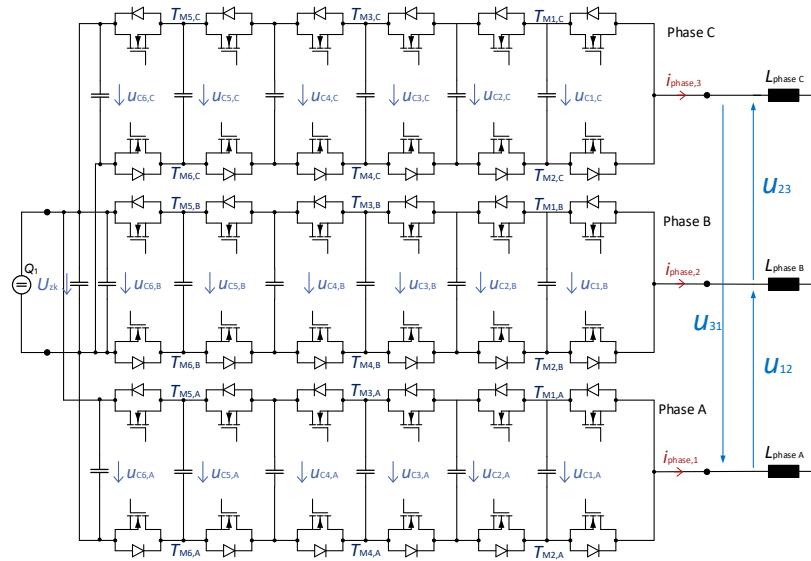

| 7.1                                           | Stationärer einphasiger Betrieb . . . . .                                                   | 159        |

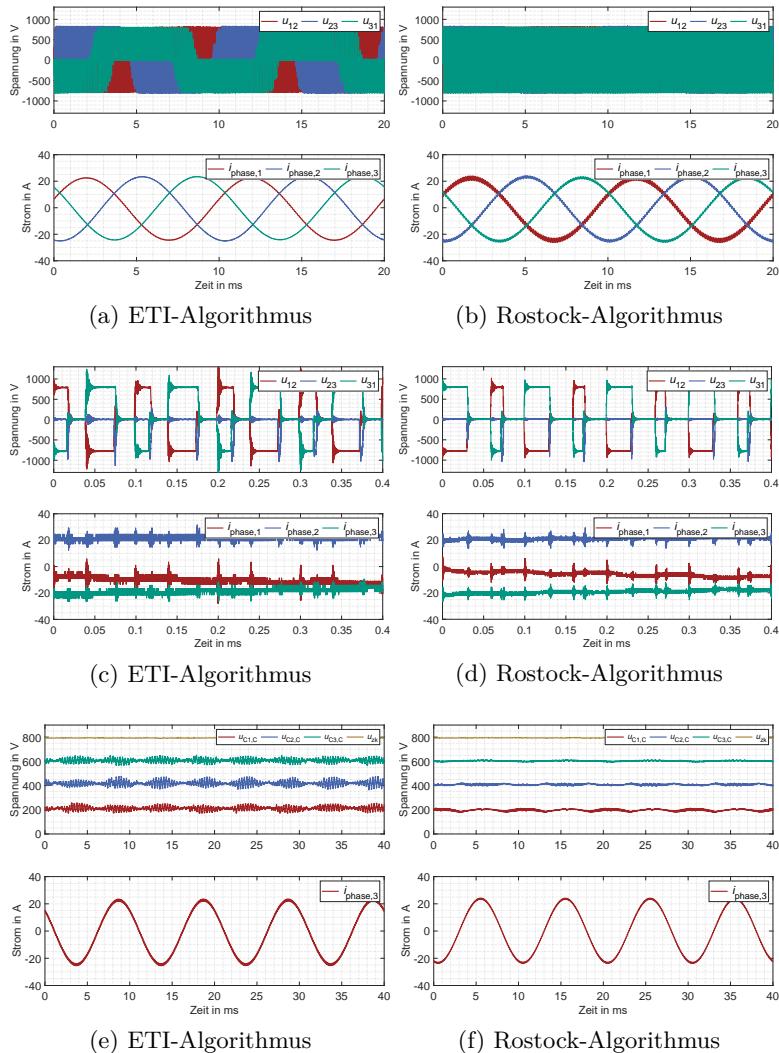

| 7.2                                           | Stationärer dreiphasiger Betrieb . . . . .                                                  | 166        |

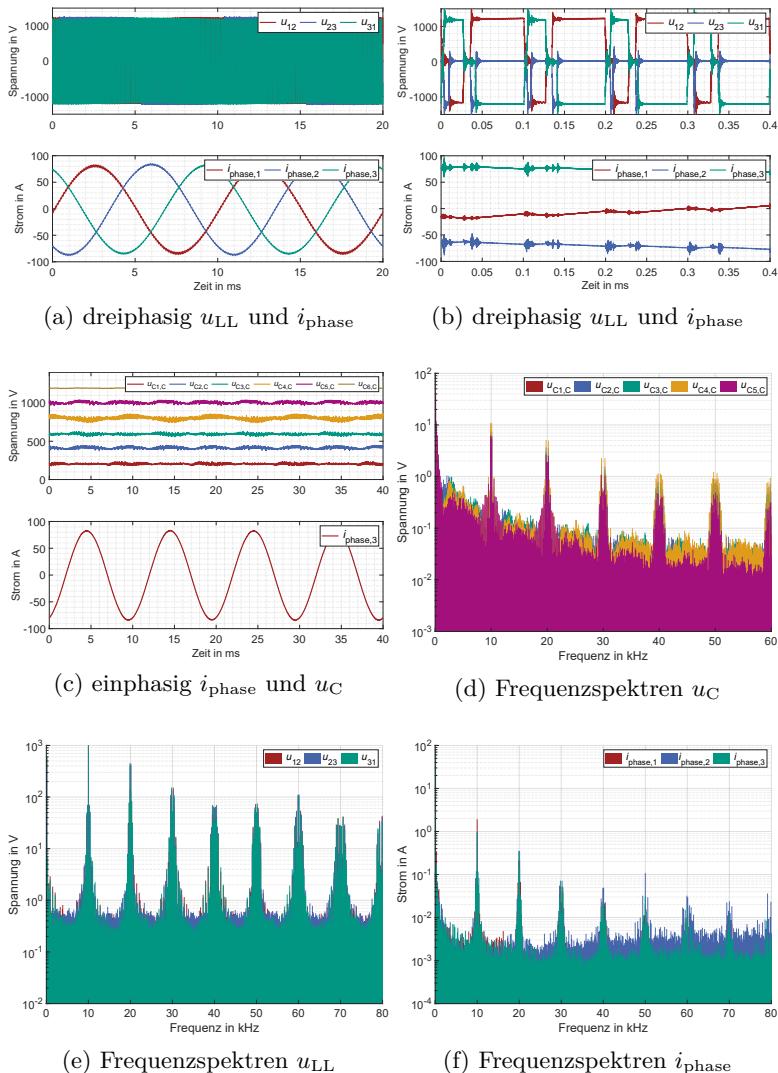

| 7.2.1                                         | Dreiphasiger Betrieb mit Niederspannung mit 5-Level                                         | 167        |

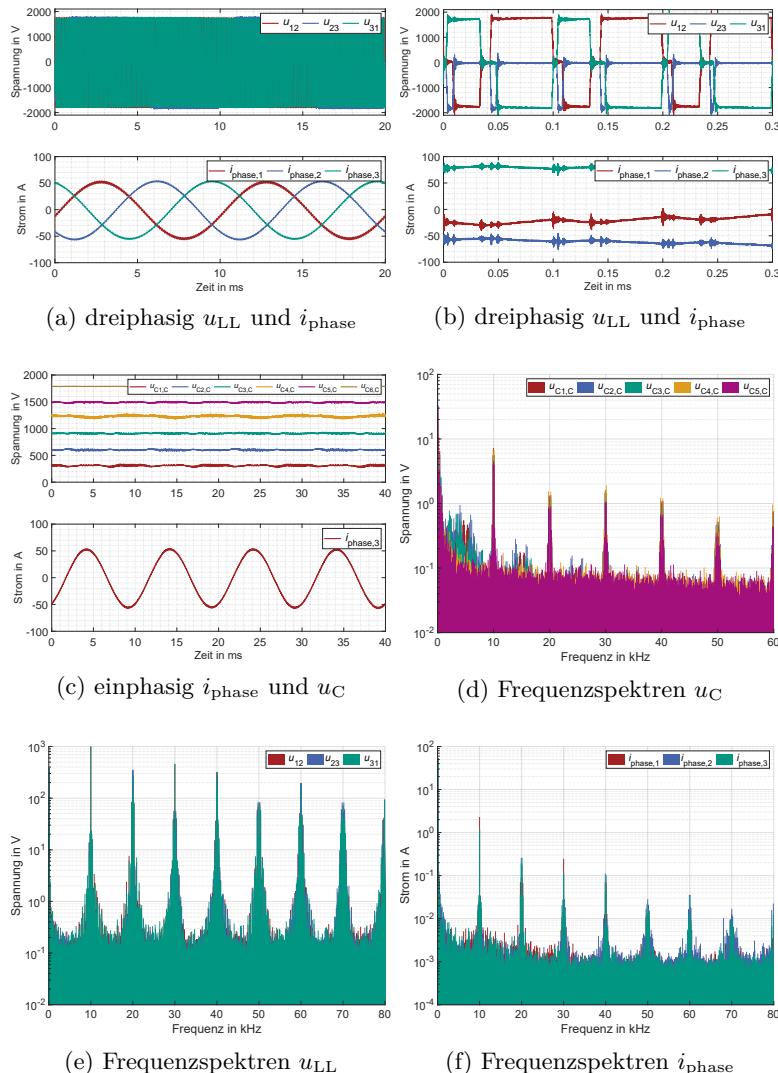

| 7.2.2                                         | Dreiphasiger Betrieb mit Niederspannung mit 7-Level                                         | 181        |

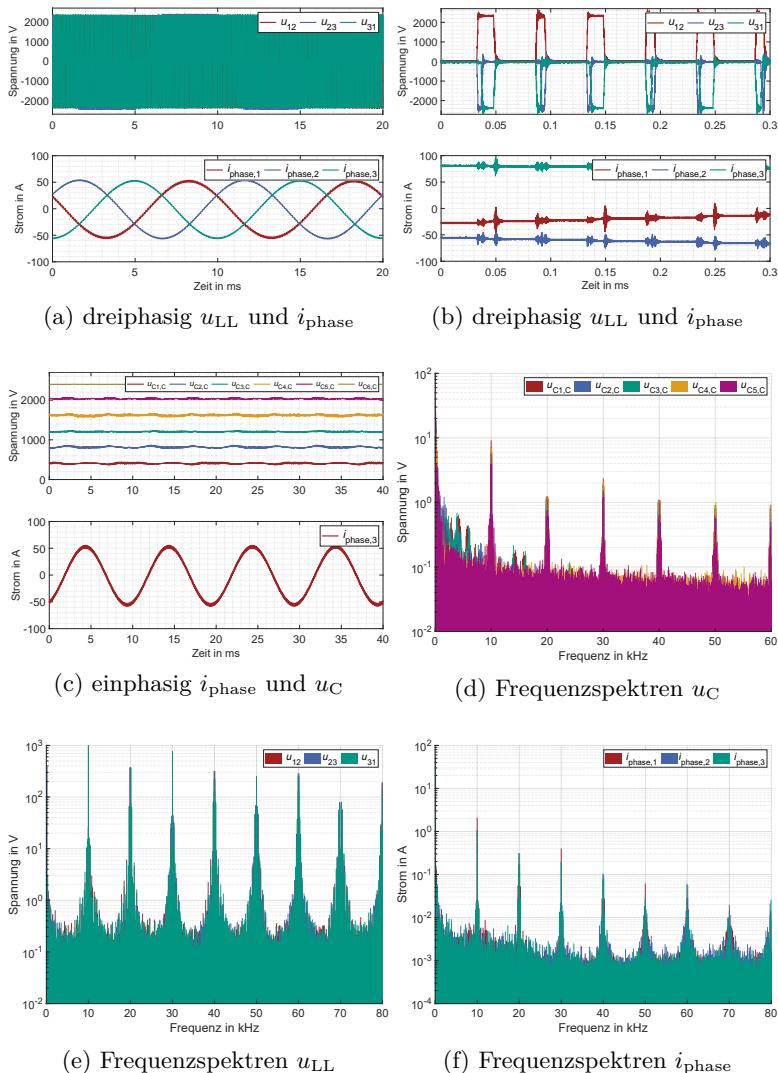

| 7.2.3                                         | Dreiphasiger Betrieb mit Mittelspannung mit 7-Level                                         | 184        |

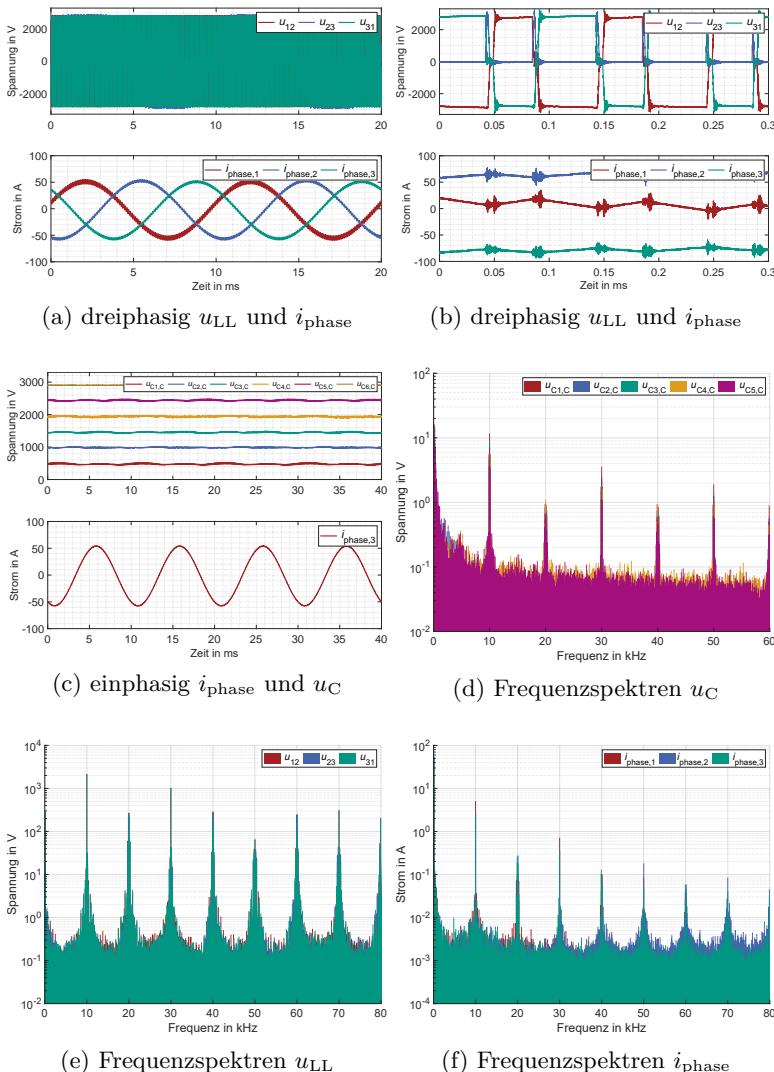

| 7.2.4                                         | Dreiphasiger Betrieb mit Mittelspannung mit 7-Level mit größerer Ausgangsfrequenz . . . . . | 193        |

| 7.2.5                                         | Verwendete Messtechnik bei den dreiphasigen Messungen . . . . .                             | 193        |

| 7.3                                           | Dynamischer dreiphasiger Betrieb mit Mittelspannung .                                       | 194        |

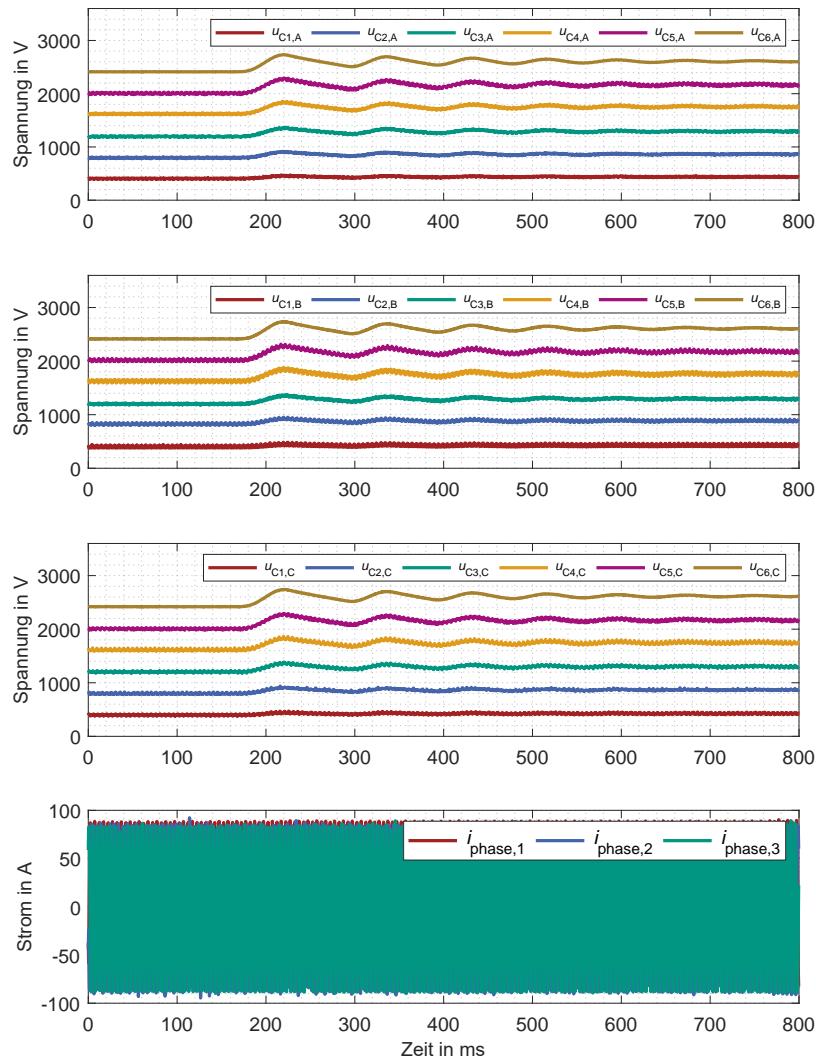

| 7.3.1                                         | Stationäres Verhalten . . . . .                                                             | 194        |

| 7.3.2                                         | Dynamische Ausgangstromveränderung . . . . .                                                | 197        |

| 7.3.3                                         | Dynamische Zwischenkreisspannungsveränderung .                                              | 200        |

| <b>8</b>                                      | <b>Zusammenfassung und Ausblick</b>                                                         | <b>203</b> |

| <b>Formelsymbol und Abkürzungsverzeichnis</b> |                                                                                             | <b>207</b> |

| <b>Abbildungsverzeichnis</b>                  |                                                                                             | <b>213</b> |

**Tabellenverzeichnis** **219**

**Literaturverzeichnis** **221**

# Kapitel 1

## Einleitung

In den letzten Jahrzehnten wurde die Leistungselektronik immer verbreiteter und wird auch in der Zukunft immer mehr an Bedeutung gewinnen. Dies liegt insbesondere am zunehmenden Umbau unserer Infrastruktur der Energieversorgung, also der Erzeugung elektrischer Energie aus regenerativen Energiequellen [1], sowie dem Elektrifizieren des Transportsektors [2]. Photovoltaik-Anlagen auf Gebäuden und Ladeinfrastruktur von Elektroautos sind Beispiele in der Niederspannung, welche die wachsende Anzahl an leistungselektronischen Betriebsmitteln im elektrischen Versorgungsnetz unter anderem repräsentieren. Weitere Anwendungen werden bei der Sektor Kopplung von Wärme, Transport und elektrischer Energie in der Zukunft folgen [3]. Die Speicherung elektrischer Energie in Heimspeichersystemen wird ebenfalls zunehmend ausgebaut werden. In all diesen Bereichen ist Leistungselektronik eine Schlüsseltechnologie. Zum Erreichen der energiepolitischen Ziele [4], welche von der Bundesregierung für den Klima- und Umweltschutz beschlossen wurden, ist eine Veränderung der derzeitigen Energieflüsse nötig. Das hat nicht nur Konsequenzen in den Niederspannungsverteilnetzen, sondern wird sich auch in den Mittelspannungsverteilnetzen auswirken. Der Energiefluss wird sich nicht mehr von wenigen großen Erzeugern bzw. Kraftwerken zu den dezentralen Verbrauchern einstellen. Die Erzeugung wird zukünftig zu wesentlichen Teilen dezentral im Versorgungsnetz integriert sein. Die Einspeisung der regenerativen Energien erfolgt im Wesentlichen in unterschiedlichen Netzebenen. In den Niederspannungsverteilnetzen werden

mehr Photovoltaikanlagen mit geringer Leistung integriert. Photovoltaikanlagen mit großer Leistung und einzelne Windkraftanlagen werden an die Mittelspannungsverteilnetze angeschlossen. Windkraftanlagenparks mit großer Leistung werden in die Hochspannungsübertragungsnetze angebunden. Bei Windkraftanlagenparks im Meer (offshore) wird diese Anbindung über Hochspannungsgleichstromübertragung (HGÜ) realisiert.

Vor allem bei Mittelspannungsumrichtern werden sich die installierte Leistung und die Anforderungen an das Netzverhalten erhöhen. Zudem wird sich deren Anzahl auf Grund von Netzkupplungen, Sektor Kopplungen, Anbindung von Wind- und Solarkraftwerken und die Integration von lokalen DC-Netzen u.a. deutlich erhöhen.

Auch Antriebe größerer Industrieanlagen mit einer Leistung von mehreren Megawatt, welche direkt an die Mittelspannung angeschlossen sind, werden sich verändern. Bisher sind solche leistungselektronischen Systeme meist mit Diodengleichrichtern als alleiniger Verbraucher an das Versorgungsnetz angeschlossen. Es gibt bereits Lösungen mit aktiven Leistungshalbleitern, welche einen bidirektionalen Leistungsfluss ermöglichen. Somit können diese Lösungen Netzdienstleistungen, wie Blindleistungsausgleich und Kurzschlussleistung, zur Verfügung stellen. Allerdings haben die bidirektionalen Lösungen einen geringeren Wirkungsgrad als die Diodengleichrichter und werden bisher wenig verwendet. Allerdings muss die Leistungselektronik zunehmend Netzdienstleistungen übernehmen und ihren Beitrag zur Netzstabilität leisten.

In diesem Zusammenhang werden unter Mittelspannung alle Systemspannungen größer 1000 VAC oder 1500 VDC und bis zu 35 kVAC verstanden [D1]. In dieser Spannungsebene kommen in der Regel Multilevel-Umrichter zum Einsatz, da die Sperrspannung von einzelnen Leistungshalbleitern derzeitig nicht ausreichend ist. Diese Umrichter besitzen bei einer Multilevel-Betriebsweise viele große passive Komponenten, welche kostenintensiv sind.

Allerdings bieten sich durch die kommerzielle Einführung von 1,2 kV-Leistungshalbleitern auf Basis von Siliziumkarbid (SiC) neue Möglichkeiten zum Verkleinern der passiven Komponenten für Mittelspannungsumrichter. Die 1,2 kV-Leistungshalbleiter auf SiC werden durch die steigende Elektrifizierung häufiger verwendet und sind somit zu einem verfügbaren Massenprodukt geworden. Dagegen sind Halbleiter mit sehr hohen Sperrspannungen ein weniger nachgefragtes Produkt und damit verhältnismäßig teurere Halbleiter. Daher wird untersucht, ob Umrichter mit

geringen Anzahlen an Ausgangsstufen und wenigen Halbleitern mit hohen Sperrspannungen durch Umrichter mit größerer Ausgangsspannungsstufenanzahl und geringerer Sperrspannung der einzelnen Leistungshalbleiter ersetzt werden können. Aus diesem Grund stehen Ansätze für neue Betriebsweisen zum Einsatz von Multilevel-Umrichtern mit mehr Halbleitern, welche sich als Umrichter mit geringen Ausgangsspannungsstufenanzahlen verhalten, im Fokus der Forschung.

## 1.1 Ziele der Arbeit

Bei der Optimierung der Mittelspannungsumrichter sind die Ziele kleinere passive Komponenten bei gleichbleibenden Netzrückwirkungen und gleicher Effizienz des Umrichtersystems. Im Rahmen dieser Dissertation wurde daher der Ansatz des Quasi-n-Level-Betriebs eines Multilevel-Umrichters betrachtet. Dieser Ansatz stellt einen möglichen Ersatz für einen Umrichter mit geringen Ausgangsspannungsstufenanzahlen mit wenigen Halbleitern mit hohen Sperrspannungen dar. Die untersuchte Topologie ist der Flying Capacitor Umrichter (FLC) und es wurden der Quasi-Zwei-Level-Betrieb (Q2LB) und Quasi-Drei-Level-Betrieb (Q3LB) betrachtet. Die Betriebsweise des Q2LBs des FLCs wurde simulativ und mit einem dafür entwickelten Hardwareprototyp untersucht.

Es wurde mit Messungen validiert, dass die Kapazität mit dem Q2LB signifikant reduziert werden kann. Weiter wurde demonstriert, dass das Konzept des Q2LBs in der Mittelspannung angewendet werden kann. Ein Nachweis sollte erfolgen, dass die Überspannung und die Spannungsänderung am Ausgang des Umrichtersystems entsprechend gering ist, trotz des Einsatzes von schnell schaltenden Leistungshalbleitern. Damit der Q2LB untersucht werden konnte, war es zuerst nötig, einen Symmetrierungsalgorithmus mit Modulation für den Betrieb zu entwickeln. Bisher waren nur für den Multilevel-Betrieb des FLCs Symmetrierungsalgorithmen und Modulationen bekannt. Bei den ersten simulativen Untersuchungen war die Bestimmung der mindestens notwendigen Kapazität der Kondensatoren im FLC eine Erweiterung des bisherigen Wissensstandes.

Die Demonstration des Konzepts sollte dreiphasig in der Mittelspannung durchgeführt werden. Daher wurde das erste dreiphasige Umrichtersystem für den Q2LB des FLCs mit einer DC-Spannung von größer 1500 V entwickelt und aufgebaut.

Bei den messtechnischen Untersuchungen hat sich gezeigt, dass die Überspannung der schnell schaltenden SiC-Halbleiter signifikant klein ist. Es ist mit dem Q2LB möglich, die notwendige Kapazität der Kondensatoren innerhalb der Topologie beim FIC zu reduzieren. Davon unabhängig kann die Schaltfrequenz der Halbleiter zur Minimierung der Ausgangsfilter oder der Optimierung des Wirkungsgrades des gesamten Umrichtersystems entsprechend gewählt werden. Eine Schaltfrequenz von 10 kHz ist mit den eingesetzten Halbleitern beim Hardwareprototypen realisiert worden, was im Vergleich zu bisherigen Mittelspannungsumrichtern um den Faktor fünf größer ist.

## 1.2 Gliederung der Arbeit

Die Dissertation besteht neben der Einleitung aus sieben weiteren Kapiteln. Zuerst wird in Kapitel 2 eine Übersicht an Multilevel-Topologien vorgestellt. Dabei werden die wichtigsten Multilevel-Topologien kurz beschrieben. Genauso wird der konventionelle Betrieb des FICs mit Funktionsweise, Modulation und Symmetrierung erläutert.

In Kapitel 3 wird beschrieben, was das Neuartige am Quasi-n-Level-Betrieb ist und warum dieser in den Fokus der Forschung gerückt ist. Ebenso wird ein Überblick über die bisherigen Untersuchungen bei den verschiedenen Multilevel-Topologien mit dieser Betriebsweise aufgezeigt. Der Quasi-n-Level-Betrieb kann mit jeder Multilevel-Topologie verwendet werden, allerdings gibt es Topologien, welche sich besser eignen. Es wurde ein Vergleich zwischen dem Q2LB des Modular Multilevel Converters (MMCs) und dem Q2LB des FICs beschrieben. Der Vergleich mit dem MMC wurde gemacht, da der MMC in unterschiedlichen Einsatzmöglichkeiten seit einigen Jahren Gegenstand vieler Forschungsarbeiten ist. Der FIC wurde bisher wenig verwendet, hat im Vergleich zum MMC beim Q2LB jedoch einige Vorteile.

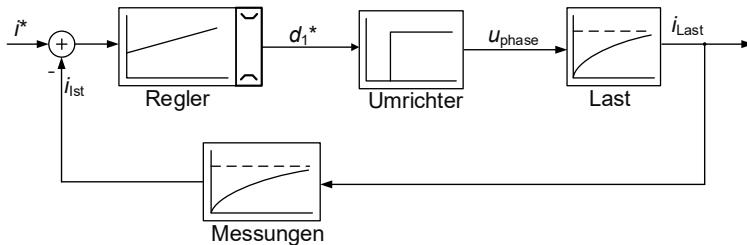

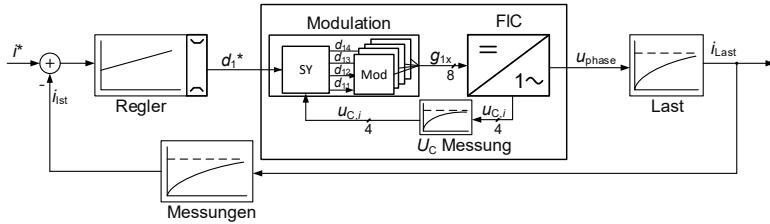

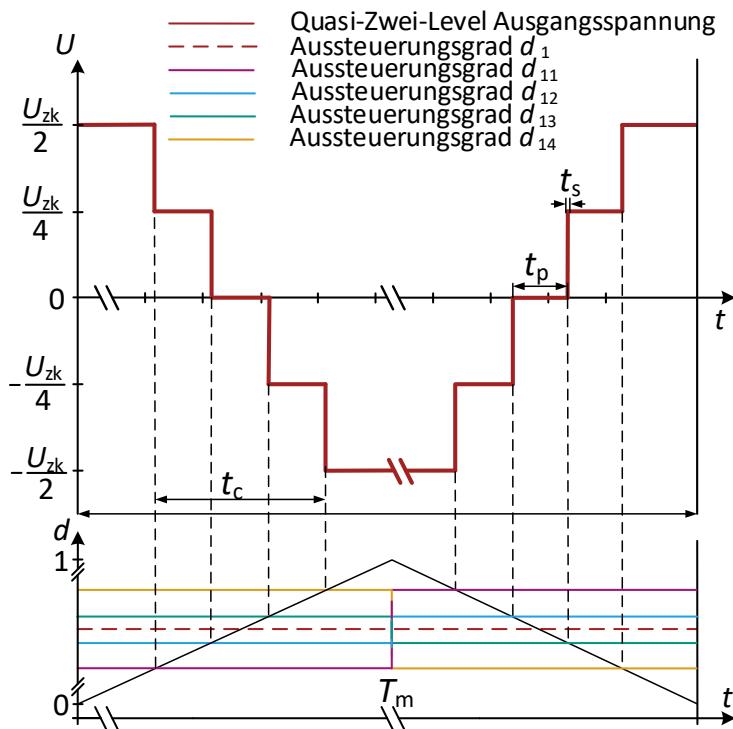

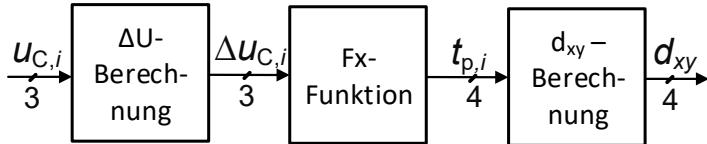

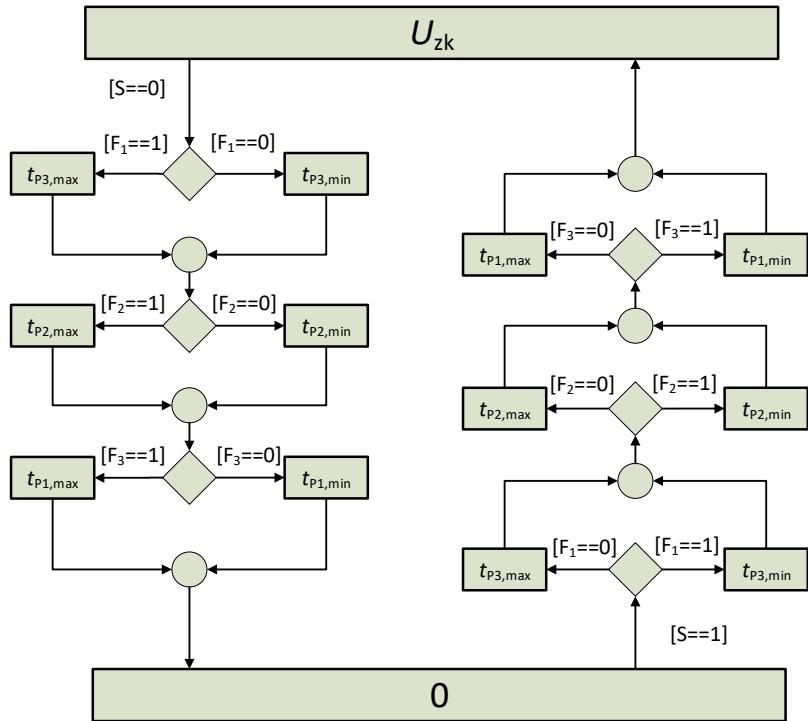

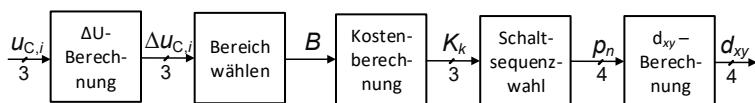

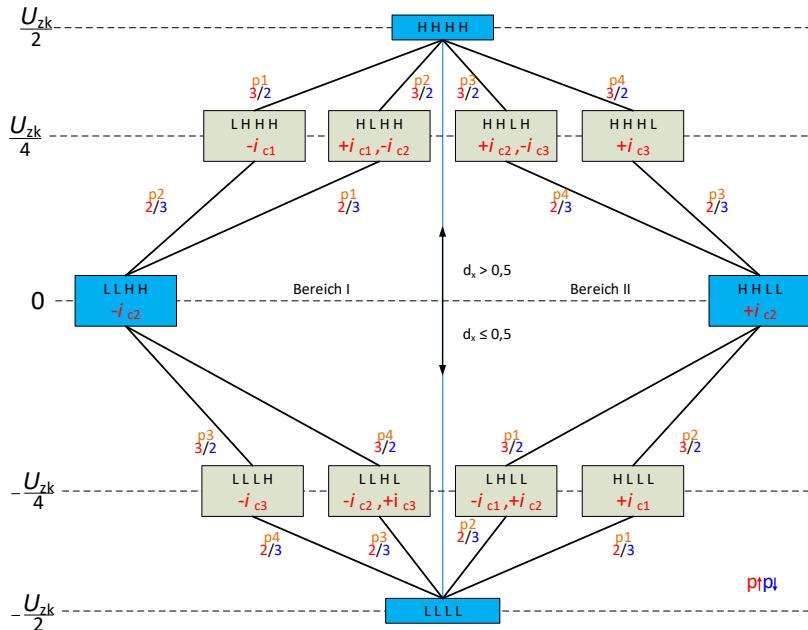

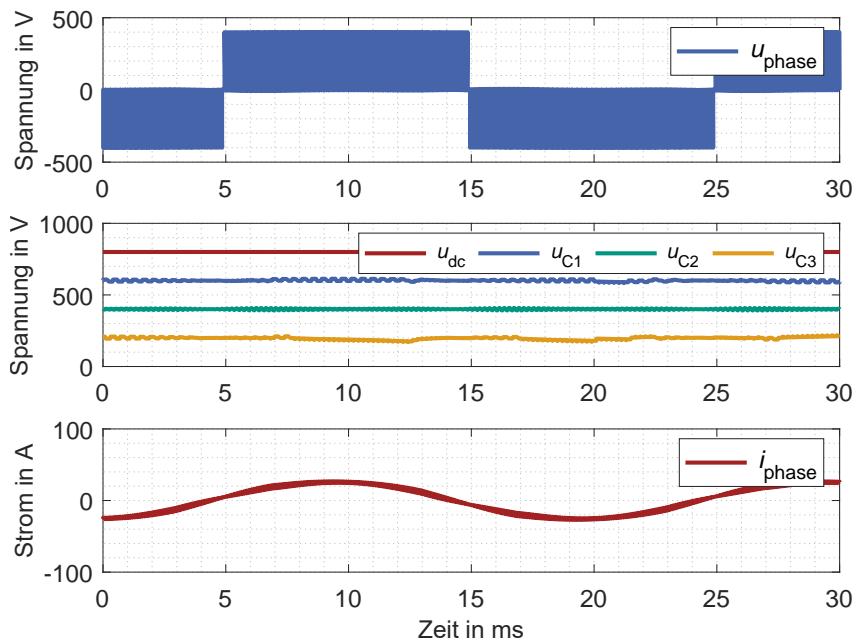

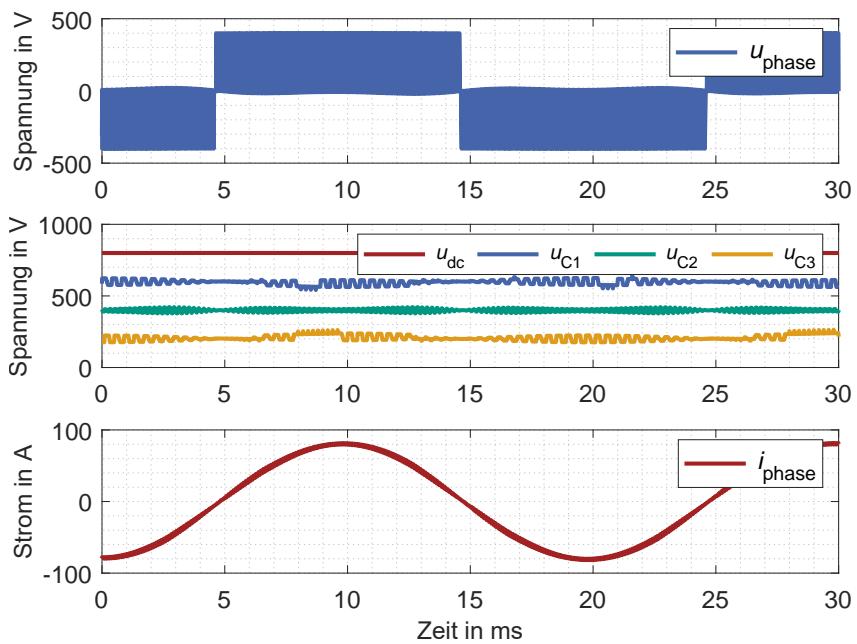

In Kapitel 4 wird die Regelung, das Modulationsprinzip mit Symmetrierung der Kondensatorspannungen und die Auslegung der Bauteile des Q2LBs und Q3LBs des FICs ausgeführt. Zuerst wird der Q2LB in Abschnitt 4.1 beschrieben. Dabei werden anhand der Struktur des regelungstechnischen Strukturbilds die einzelnen Teile des neuartigen Betriebs erläutert. Für den neuartigen Betrieb wurden neue Symmetrierungsalgorithmen benötigt, welche hier beschrieben werden. Ebenso wird ein

Vergleich der unterschiedlichen veröffentlichten Symmetrierungsalgorithmen der Kondensatorspannungen vorgestellt. Die größte Herausforderung bei dieser Betriebsweise ist die Integration der Symmetrierung in die Ansteuerung der Leistungshalbleiter bzw. der Modulation. Im folgenden Abschnitt 4.2 wird der Q3LB beschrieben, der nur eine Änderung in der Modulation des Symmetrierungsalgorithms und der Auslegung einzelner Komponenten zum Q2LB beinhaltet.

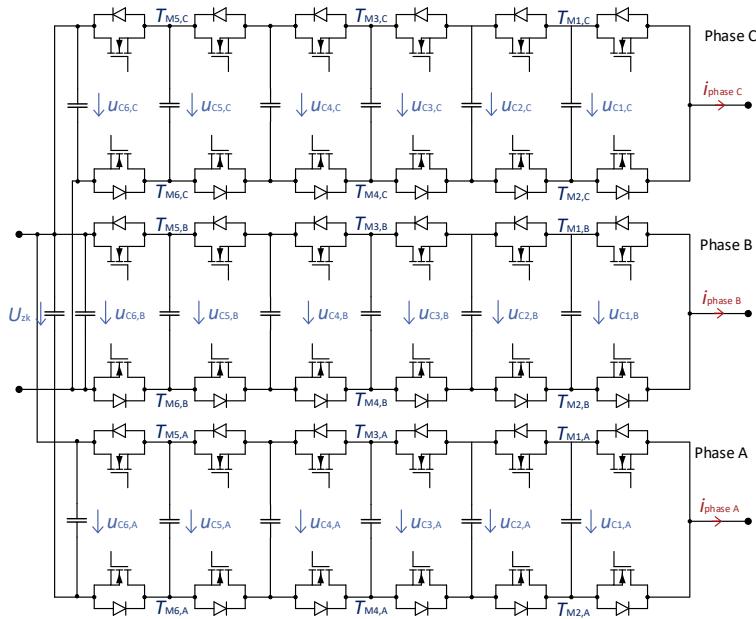

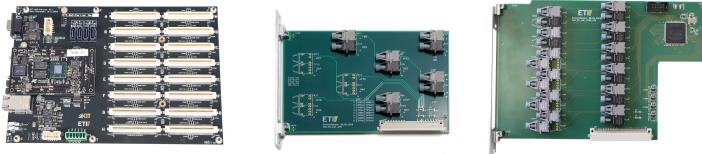

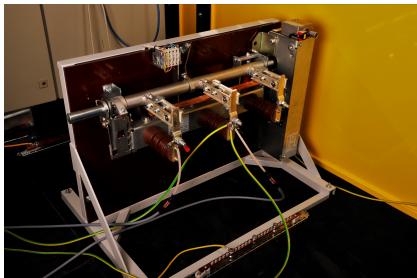

In Kapitel 5 wird die entwickelte Hardware von der Leistungszelle bis zum dreiphasigen 7-Level-Aufbau beschrieben. Es wird das Konzept, die Auslegung der einzelnen Komponenten, die integrierten Funktionsgruppen und die Validierungsmessungen der Leistungszelle vorgestellt. Aus den einzelnen Leistungszellen wurde der dreiphasige 7-Level-Aufbau realisiert. Die Anordnung der Komponenten im Gesamtsystem, die Auslegung des zentralen Zwischenkreises und die Systemintegration wird beschrieben. Die eingesetzte Hardware wird von der am Institut entwickelten Signalverarbeitung gesteuert und die dafür verwendete Signalverarbeitungsstruktur vorgestellt.

Für die Validierung des Umrichtersystems war ein entsprechender Prüfplatz notwendig. Am Institut existierten bisher ausschließlich Prototypen für Niederspannung. Daher wurde in der Zeit der wissenschaftlichen Tätigkeit für den Mittelpunktspannungsprototypen ein dafür notwendiger Prüfplatz für Mittelpunktspannung geplant und realisiert. Der im Rahmen dieser Dissertation entstandene Prüfplatz zum Vermessen des Hardwaredprototyps wird in Kapitel 6 vorgestellt. Das Konzept, die einzelnen Komponenten und die räumliche Struktur werden erläutert. Die wichtigsten Leistungsdaten für das Prüffeld sind die maximale Zwischenkreisspannung eines Prüflings von 12 kV und der dauerhafte maximale Ausgangstrom von 500 A.

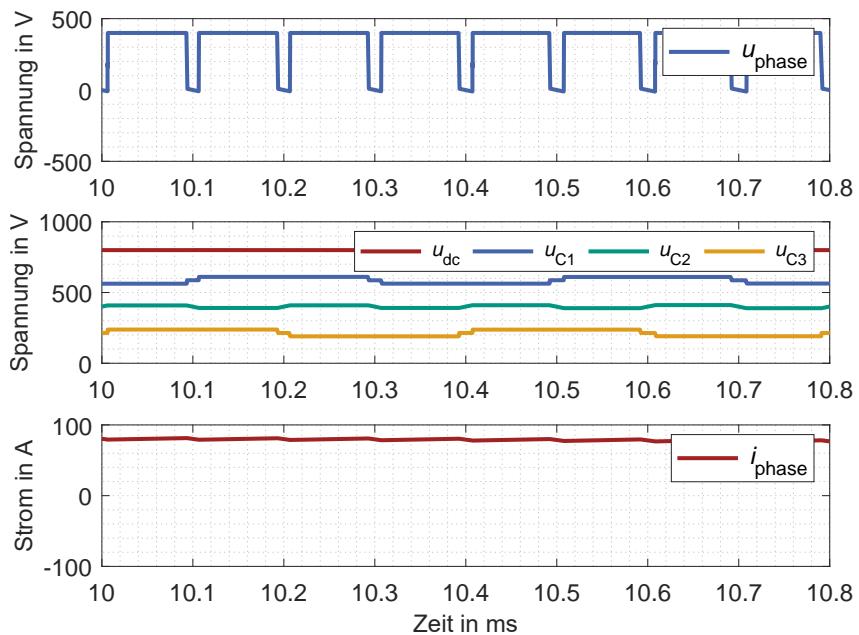

Die entstandenen Messergebnisse des Q2LBs werden zuerst mit Niederspannung und danach mit Mittelpunktspannung in Kapitel 7 präsentiert. Dabei sind der Quasi-Zwei-Level-Verlauf der Phasenspannung und die Verläufe der Kondensatorspannungen die wichtigsten Elemente. Eine Analyse der Symmetrierungsalgorithmen und die Validierung der geringen Überspannungen werden dabei vorgestellt. Die Dynamik der neuen Betriebsweise wurde ebenfalls mit Messungen validiert.

Den Abschluss bilden eine Zusammenfassung und ein Ausblick in Kapitel 8. Die Erkenntnisse dieser Dissertation sind darin zusammengefasst. Im Ausblick wird beschrieben, welche Forschungsthemen auf dieser Dissertation aufbauen könnten.

## 1.3 Wissenschaftliche Beiträge

Im Forschungsgebiet der Dissertation wurden in [E1] ein Symmetrierungsalgorithmus und das Einsparpotential der Kondensatoren im Umrichter beim FIC mit dem Q2LB präsentiert. Die entwickelte Leistungszelle (PEBB) wurde mit ersten Messergebnissen in [E2] veröffentlicht. Der selbst entwickelte Symmetrierungsalgorithmus wurde mit zeitgleich veröffentlichten Algorithmen verglichen und dieser Vergleich wurde in [E3] präsentiert. In dieser Veröffentlichung wurde auch ein Algorithmus zum Vorladen des FICs gezeigt. Der Hardwareprototyp in dreiphasiger Ausführung mit Signalverarbeitungsstruktur und Regelungsstruktur wurde in [E4] vorgestellt. Dieser Prototyp ist der erste FIC-Aufbau in der Mittelspannung, welcher für den Quasi-n-Level-Betrieb optimiert aufgebaut wurde. Neben dem FIC gibt es den Q2LB auch beim MMC. Diese beiden Topologien mit der Betriebsweise des Q2LBs wurden in [E5] verglichen. Abschließend wurde in [E6] eine Zusammenfassung bisheriger Veröffentlichungen und eine Auswahl der dreiphasigen Messungen des Q2LBs mit Mittelspannung präsentiert.

Neben der Forschung im Bereich der Dissertation sind Beiträge bei An-sätzen zum Einsatz eines Modular Multilevel Converters (MMCs) in Inselnetzen [E7] und dynamischer Regelung des MMCs in [E8] entstanden. Der MMC ist ein Multilevel-Umrichter mit großer Anzahl an Spannungsstufen und somit ideal geeignet für den Einsatz als netzbildenden Umrichter oder zur Kompensation von Netzharmonischen und Blindleistung.

Die Steuerung und Regelung von leistungselektronischen Systemen wird immer komplexer und erfordert daher höhere Dynamiken. Aus diesem Grund wurde am Institut eine neue Generation der Signalverarbeitung entwickelt. Die Verbesserung der Kommunikationsmöglichkeiten und Visualisierung waren dabei mein Hauptbeitrag. Das neue ETI-Signalverarbeitungssystem wurde in [E9] präsentiert.

Im Rahmen dieser Dissertation wurden in unterschiedlichen Bereichen, neben den Veröffentlichungen, noch studentische Arbeiten betreut. Im Forschungsbereich des Quasi-n-Level-Betriebs des FICs wurden mit den studentischen Arbeiten [S1], [S2], [S3], [S4] und [S5] unterschiedliche Aspekte betrachtet und realisiert. In [S1] wurde der konventionelle Multilevel-Betrieb betrachtet. Der erste Prototyp der Leistungszelle wurde in [S2] aufgebaut. Der einphasige Betrieb des FICs mit der

Leistungsquelle wurde in [S3] und [S4] untersucht. Die dreiphasige Betriebsweise des FlCs wurde in [S5] betrachtet.

Neben Abschlussarbeiten im Forschungsbereich der Dissertation wurden in den anderen Forschungsbereichen - Erforschung des MMCs am Versorgungsnetz und an Inselnetzen mit den Themenschwerpunkten Netzsynchroneisation, Netzkupplung und netzseitige Stromrichterregelung - die Abschlussarbeiten [S6], [S7], [S8], [S9] und [S10] angeleitet. Darüber hinaus wurden in dem Bereich der Signalverarbeitung und Weiterentwicklung des Monitor Control Tools des Instituts die Arbeiten [S11], [S12] und [S13] betreut, wobei es sich beim Monitor Control Tool um das selbst entwickelte Steuerungs- und Auslesetool für die ETI-Signalverarbeitungssysteme handelt.

Darüber hinaus ist die Lehre ein wichtiger Teil der Aufgaben am Institut. Bei der Abschlussarbeit [S14] wurde die Entwicklung eines Konzepts zur Demonstration eines leistungselektronischen Antriebssystems betrachtet. Ein Laborversuch zur Vermessung der Asynchronmaschine wurde mit der Abschlussarbeit [S15] realisiert.

# Kapitel 2

## Stand der Technik

In diesem Kapitel wird ein kurzer Überblick über den Stand der Technik bei Multilevel-Topologien gegeben, welche für die Mittelspannung geeignet sind. Unter Multilevel wird hier verstanden, dass mehr als zwei Spannungs niveaus pro Phase gestellt werden können. Allerdings ist die meistverwendete Topologie bei Spannung zwischenkreisumrichtern eine Zwei-Level-Topologie.

Bei einem dreiphasigen System ist die Drehstrombrücke der Standard-Zwei-Level-Umrichter. Dabei sind die Einsatzmöglichkeiten dieser Topologie begrenzt durch die möglichen Sperrspannungen der eingesetzten Leistungshalbleiter. Die höchste kommerziell erhältliche Spannungsklasse eines Insulated-Gate Bipolar Transistors (IGBTs) sind 6,5 kV. Diese Spannungsklasse wird von vielen Herstellern angeboten und hat sich als Standard etabliert. Bei anderen Halbleitermaterialien, wie Siliziumkarbid (SiC), gibt es Forschungsvorhaben für Leistungshalbleiter mit Sperrspannungen größer als 10 kV [5]. Allerdings sind solche Leistungshalbleiter bisher nicht kommerziell erhältlich. Bei der Drehstrombrücke mit 6,5 kV-Leistungshalbleitern sind maximal Zwischenkreisspannungen  $U_{\text{zk}}$  bis 4 kV möglich. Damit würden Netzspannungen  $U_{\text{Netz}}$  bis zu 3 kV erreicht werden. Im Bereich der Mittelspannung sind Spannungen  $U_{\text{Netz}}$  bis zu 20 kV und darüber hinaus üblich.

Um mit einer Zwei-Level-Topologie größere Spannungen als  $U_{\text{zk}} = 4 \text{ kV}$  zu erreichen, gibt es die Möglichkeit der Reihenschaltung von Leistungshalbleitern. Dabei ist ein grundlegendes Problem die Aufteilung der Spannung auf die einzelnen Halbleiter. Für IGBTs und SiC-Metal Oxide

Semiconductor Field-Effect Transistors (MOSFETs) gibt es unterschiedliche Ansätze in Veröffentlichungen. Grundlegend gibt es die Möglichkeit durch externe Beschaltungen oder einem aktiven Gate-Treiber die Spannungsverteilung zu beeinflussen. Veröffentlichte exemplarische Ansätze bei IGBTs sind in [6] und [7] beschrieben. Dabei werden beide Möglichkeiten der Beeinflussung der Spannungsverteilung verwendet. Bei SiC-MOSFETs gibt es Ansätze zu aktiven Gate-Treiber Regelungen wie in [8] und mit einer zusätzlichen Beschaltung der Halbleiter in [9]. Die Konzepte über die Reihenschaltung von Halbleitern mit größerer Anzahl haben sich nicht, bis auf eine Ausnahme, kommerziell durchgesetzt. Die Firma ABB hat unter dem Begriff HVDC-light eine Reihenschaltung von IGBTs im Presspack-Gehäuse angeboten [10]. Ein Umrichtersystem mit  $\pm 150\text{ kV}$  wurde entwickelt. Der erste Prototyp wurde ab 1997 zwischen Hellsjön und Grängesberg mit einer Leistung von 3 MW betrieben. Bei Multilevel Topologien wird die Aufteilung der Spannungen auf die einzelnen Halbleiter in der Topologie mit mehreren verteilten Energiespeichern realisiert. Dabei sind in den letzten Jahrzehnten verschiedenste Topologien entwickelt worden.

## 2.1 Übersicht über Multilevel-Topologien

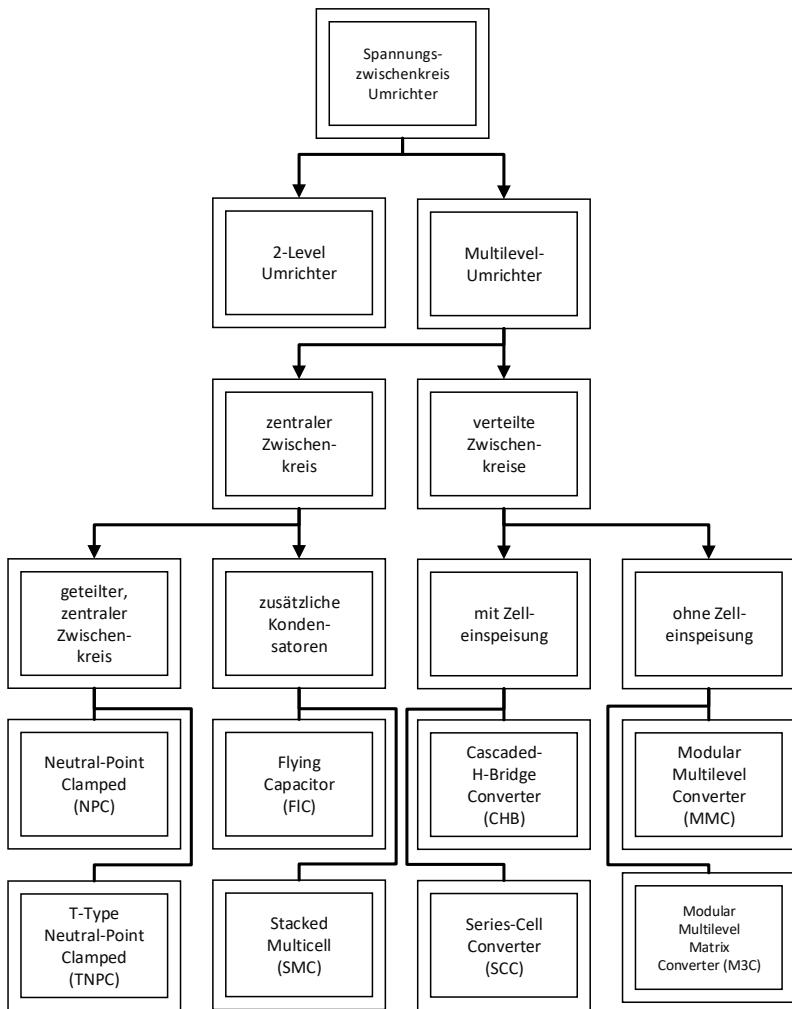

Im Folgenden wird eine kurze Übersicht der wichtigsten Arten von Multilevel-Topologien vorgestellt. Dabei werden die Multilevel-Topologien, wie sie in Abb. 2.1 gezeigt werden, in vier Hauptgruppen eingeteilt. Zuerst in die Gruppen mit zentralem Zwischenkreis und mit verteilten Zwischenkreisen. Danach wird die Gruppe der Topologien mit zentralem Zwischenkreis unterteilt in die Topologien mit geteiltem zentralen Zwischenkreis und die Topologien, welche zusätzliche Kondensatoren beinhalten. Die Gruppe mit verteilten Zwischenkreisen wird in die Topologien mit Einspeisung in die verteilten Zwischenkreise und Topologien ohne Einspeisung in die verteilten Zwischenkreise unterschieden. Es gibt in der Literatur auch andere Sortierungen. Die hier beschriebene wurde anhand üblicher Unterscheidungen am ETI zusammengestellt.

Abbildung 2.1: Eine Übersicht über die verschiedenen Multilevel-Topologien

### 2.1.1 Neutral Point Clamped (NPC)

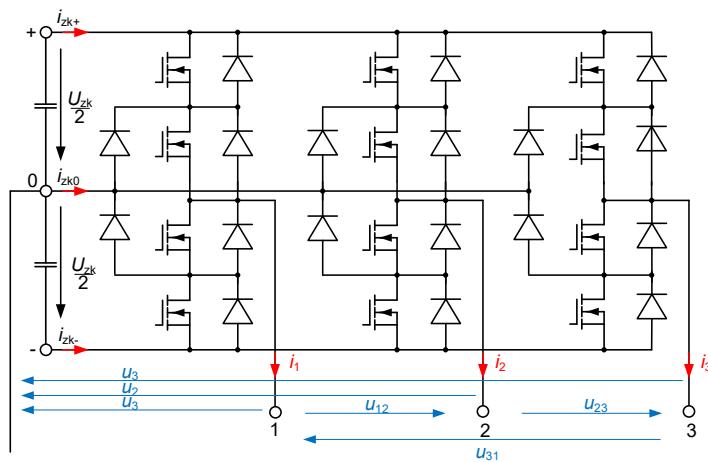

Der NPC wurde 1981 bereits in [11] vorgestellt. Diese Topologie ist eine weitverbreitete Drei-Level-Topologie mit einem zentralen, geteilten Zwischenkreis, die in Abb. 2.2 dargestellt ist. Dazu ist der zentrale Zwischenkreis in zwei Kondensatoren in Serie aufzuteilen. An diesen Mittelpunkt werden die Dioden für das dritte Ausgangsspannungslevel angeschlossen. Wegen dieses Anschlusses wird diese Art des Multilevel-Umrichters so bezeichnet. Der zentrale Zwischenkreis wird von allen Phasen gemeinsam genutzt und kann somit bei einer dreiphasigen Ausführung deutlich kleiner als im einphasigen Aufbau ausgelegt werden. Eine Phase besteht aus vier Leistungshalbleitern, wobei in der Mitte der Phasenausgang angeschlossen wird. Zusätzlich sind die Mittelpunkte der oberen und unteren Halbbrücken, mit jeweils einer Diode, mit dem Mittelpunkt des Zwischenkreises verbunden. Durch die Dioden und die zusätzlichen Leistungshalbleiter, im Vergleich zum Zwei-Level-Umrichter, kann das dritte Spannungsniveau generiert werden.

Letztendlich gibt es unterschiedlichste Varianten dieser Topologie, wie den T-Type Neutral Point Clamped (TNPC). Anstelle von Dioden wird hier ein aktiver Leistungshalbleiter zum Zuschalten der zusätzlichen Stufe verwendet. Innerhalb dieser Gruppe gibt es auch Topologien mit vier oder fünf Leveln und mehr Ausgangsspannungsniveaus pro Phase. Bei allen Topologievarianten teilen sich die Spannungsbelastungen gleichmäßig auf die Halbleiter auf. Die Verluste in den Halbleitern unterscheiden sich jedoch, da sie vom jeweiligen Modulationsgrad abhängen [12].

Wie bei allen Multilevel-Topologien müssen die Kondensatorspannungen auf einem bestimmten Sollwert gehalten werden. Bei dem NPC in Drei-Level-Ausführung ist das  $\frac{U_{zk}}{2}$ , damit sich die Spannung über die eingesetzten MOSFETs gleichmäßig aufteilt. Bei dieser Topologie wird die Symmetrierung durch Variation der Schaltkombinationen mit Beteiligung des dritten Spannungsniveaus erreicht. Wenn das Null-Spannungsniveau gestellt wird, fließt der Ausgangsstrom durch einen der zwei Teile des geteilten Zwischenkreises. Die Aufteilung des Ausgangsstroms auf die zwei Teile des Zwischenkreises muss gleichmäßig sein, damit die Spannungsaufteilung gleichmäßig ist.

In der Literatur verwendete Multilevel-Modulationen bei dieser Topologie sind Phase Disposition (PD), Alternated Phase Opposition Disposition (APOD) und Phase Opposition Disposition (POD) [12]. Keine dieser Modulationen hat gegenüber den anderen Modulationen klare Vorteile. Bei

Abbildung 2.2: Neutral Point Clamped (NPC) mit MOSFETs nach [11] in dreiphasiger Ausführung

jeder Anwendung muss anhand der Anforderungen entschieden werden, welche Modulation dafür besser geeignet ist. In aktueller Forschung wurde bei einem T-Type Neutral Point Clamped (TNPC) eine Optimierung der Symmetrierung am ETI betrachtet und die Erkenntnisse in [13] veröffentlicht. Ein neuartiges Verfahren zur Schaltzustandswahl, im Vergleich zu den bisher erwähnten trägerbasierten Modulationsverfahren, wurde dabei präsentiert. Es wurde ein virtueller Vector eingeführt, welcher sich aus zwei benachbarten Schaltzuständen ohne Fluss des Ausgangstroms durch den geteilten Zwischenkreis ergibt. Damit kann der Ausgangstrom durch den Mittelpunkt des geteilten Zwischenkreises reduziert werden. Weiter gibt es noch den Aktive Neutral Point Clamped (ANPC), in welchem, im Vergleich zum NPC, die Dioden durch aktive Halbleiter ersetzt werden. Für die Symmetrierung der geteilten Zwischenkreisspannung gibt es dadurch mehr Freiheitsgrade. Eine Besonderheit des ANPC ist die Möglichkeit, durch die aktiven Verbindungen zum geteilten Zwischenkreis, die Verluste der einzelnen Halbleiter aktiv zu beeinflussen [14]. Dabei wird ausgenutzt, dass es möglich ist, die gleiche Spannungsstufe mit unterschiedlichen Schaltkombinationen zu stellen. So ist es möglich, die Schaltfrequenz der einzelnen Halbleiter unterschiedlich zu wählen.

### 2.1.2 Flying Capacitor Umrichter (FIC)

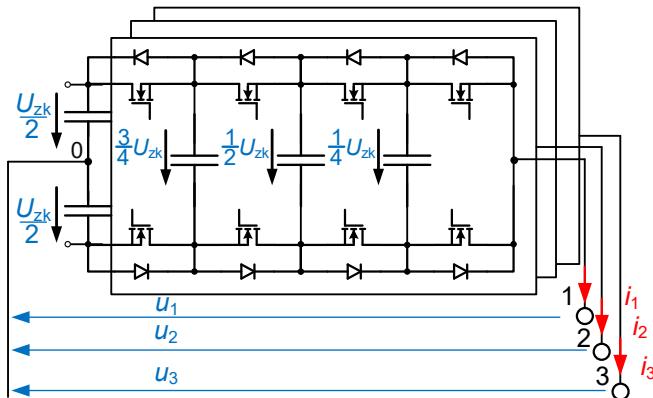

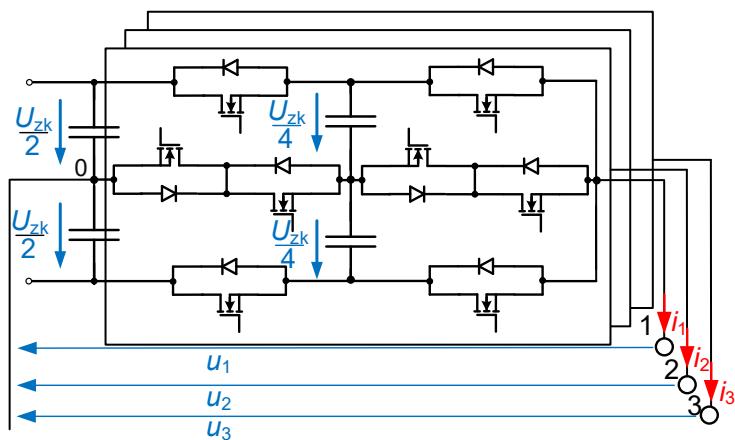

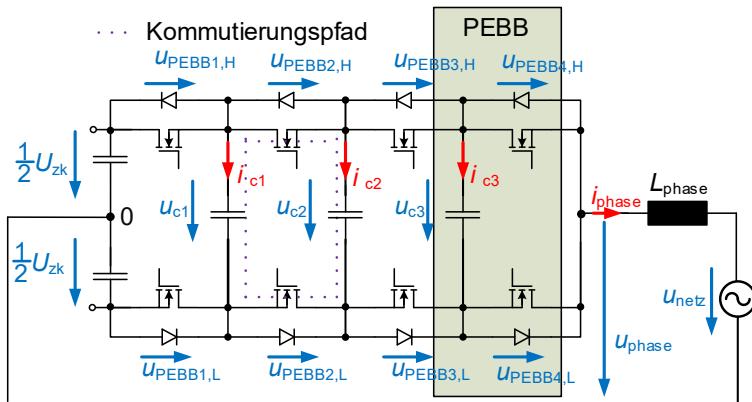

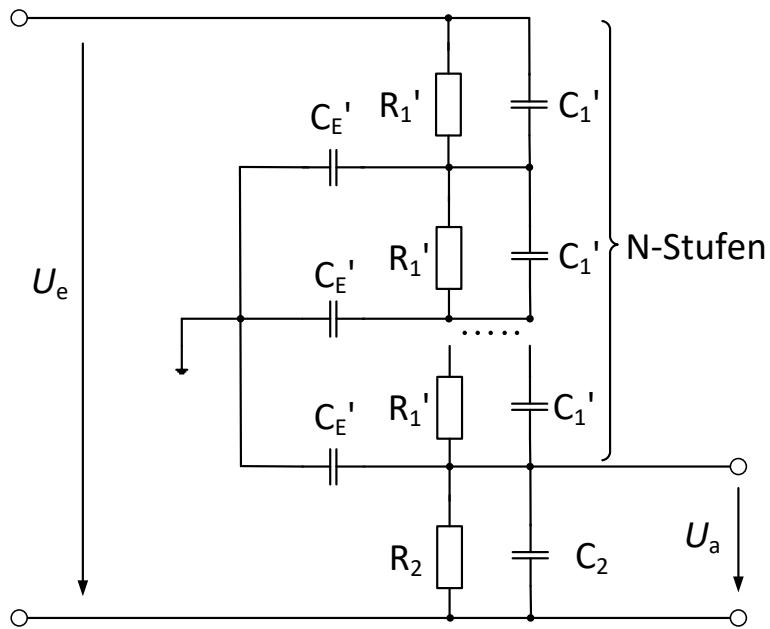

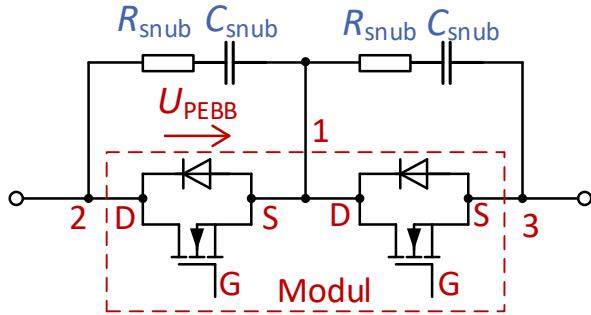

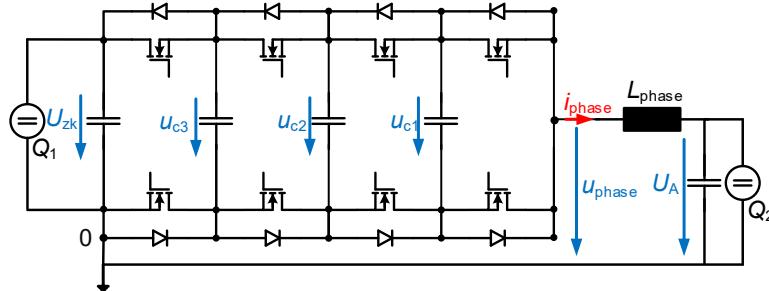

Der Flying Capacitor Umrichter (FIC) wurde 1992 in [15] zuerst präsentiert. Die einphasige Ausführung als 5-Level-FIC wird in Abb. 2.3 gezeigt. Wie beim NPC gibt es einen zentralen Zwischenkreis, der von allen Phasen genutzt werden kann. Zusätzlich zu dem Zwischenkreiskondensator existieren weitere Kondensatoren mit unterschiedlichen Sollspannungswerten pro Phase. Die Sollwerte der zusätzlichen Kondensatoren sind identisch in jeder Phase. Die zusätzlichen Kondensatoren verbinden immer zwei korrespondierende Anschlüsse der Leistungshalbleiter. Bei dieser Topologie ist ersichtlich, dass für ein zusätzliches Spannungsniveau immer die gleiche Anzahl an Bauelementen hinzugefügt werden muss. Allgemein gilt: Ein  $N$ -Level FIC ( $N \in \mathbb{N}$ ) besteht aus  $2 \cdot (N - 1)$  Leistungshalbleiterschaltern und  $(N - 2)$  Kondensatoren, zusätzlich zum Zwischenkreiskondensator. Durch die Struktur dieser Topologie lässt sich eine Modularisierung erreichen, da immer gleiche Baugruppen für eine größere Stufenanzahl hinzugefügt werden müssen. Diese identischen Baugruppen werden im Folgenden Power Electronic Building Block (PEBB) genannt.

Abbildung 2.3: einphasiger 5-Level-Flying Capacitor Umrichter (FLC) nach [15]

Die Kondensatorspannungssollwerte können nach Gleichung (2.1) berechnet werden.

$$U_{C,nom,i} = U_{zk} \cdot \frac{N - 1 - i}{N - 1} \quad i \in [1 \dots (N - 2)] \quad (2.1)$$

Durch die unterschiedlichen Kondensatorspannungssollwerte wird erreicht, dass sich die Spannungsbelastungen gleichmäßig auf die Leistungshalbleiter aufteilen. Zum Erreichen der unterschiedlichen Ausgangsspannungsniveaus werden unterschiedliche Kondensatoren in den stromführenden Pfad geschaltet. Diese Erzeugung der Multilevel-Spannungen ist grundlegend anders im Vergleich zum NPC.

Beim Betrieb des FLCs müssen die Kondensatorspannungen innerhalb eines Toleranzbandes um den jeweiligen Sollwert gehalten werden, um eine Zerstörung der Halbleiter durch eine unzulässige Spannungsverteilung zu vermeiden. Dies wird mit Hilfe eines Symmetrierungsalgorithmus erreicht, der Teil der Modulation des Umrichters ist. Aus der Literatur sind dabei für den konventionellen Betrieb die Phase Disposition (PD) und Alternated Phase Opposition Disposition (APOD) bekannt.

Die Symmetrierung erfolgt bei diesen Verfahren durch die feste Zuordnung von Halbleitern zu einzelnen Trägern bei einer sinusförmigen Ausgangsleistung. Ein neueres Symmetrierungsprinzip mit Raumzeigermodulation wurde in [16] präsentiert. Dabei werden in Abhängigkeit der Kondensatorspannungsabweichungen die jeweils verwendeten Raumzeiger variiert. Weiter gibt es einen direkten Symmetrierungsalgorithmus mit einer direkten Schaltzustandswahl vom ETI entwickelt und in [17] veröffentlicht. Dieses Prinzip gibt vor, dass in Abhängigkeit der Kondensatorspannungsabweichungen bei den jeweiligen Ausgangsspannungsstufen ein bestimmter Schaltzustand gewählt wird. Ein neuer Ansatz zur Integration der Symmetrierung in die Regelung wurde in [18] vorgestellt. Dabei wird die Ausgangsregelung und die Modulation mit Symmetrierung nicht mehr einzeln betrachtet.

Grundsätzlich hat diese Topologie den Nachteil, dass die Anzahl der Schaltkombinationen mit der Anzahl an Stufen mit  $2^{(N-1)}$  pro Phase steigt und sich dabei auch die mögliche Anzahl an Schaltkombinationen bei gleichem Ausgangsspannungsniveau erhöht. Der Aufwand für die Symmetrierung der Kondensatorspannungen und der Modulation steigt nicht linear mit der Anzahl an Ausgangsspannungsstufen. Ein weiterer Nachteil ist, dass die verschiedenen Kondensatoren alle auf verschiedene Sollwerte vorgeladen werden müssen. Diese Topologie wurde in Forschung und Industrie bisher nur mit bis zu neun Spannungsstufen betrachtet.

Auch bei dieser Topologie gibt es Varianten in der Literatur, wie den Cascaded-Flying-Capacitor (CFLC), welcher in [19] präsentiert wurde. Weitere Varianten sind der Full-Bridge-Flying-Capacitor (FBFLC) aus [20] oder der Symmetric-Flying-Capacitor (SFLC) aus [21] und [22]. Weitere Erklärungen zum FLC und dem konventionellen Multilevel-Betrieb sind in Abschnitt 2.2 gegeben.

### **Stacked-Multicell Converter (SMC)**

Der SMC ist eine direkte Weiterentwicklung des FLCs und wurde in [23] vorgestellt. Abbildung 2.4 stellt einen 5-Level-SMC dar. Bei gleicher Stufenanzahl werden weniger Kondensatoren benötigt als beim FLC [12]. Die geteilten Kondensatoren bei dieser Topologie müssen genauso auf ihren Spannungssollwerten gehalten werden. Dafür wird ein Symmetrierungsalgorithmus verwendet.

Dabei wird auf die gleichen Prinzipien, wie beim FLC, zurückgegriffen. Ein einfacher Ansatz ist es, den 5-Level-SMC als 3-Level-FLC mit

Abbildung 2.4: einphasiger 5-Level-Stacked-Multicell Converter (SMC) nach [23]

mehreren Trägerverfahren nach APOD oder PD Prinzip zu betreiben. Dabei wird jeder der zwei gleichen Baugruppen des 5-Level-SMCs die Trägersignale einer Drei-Level-Modulation des FICs zugeordnet. Bei den Symmetrierungen mit trägerbasierten Modulationen wird die Symmetrie der Schaltzustände und dem damit verbundenen Mittelwert der Kondensatorströme von Null bei den einzelnen Kondensatoren genutzt. Bei einer großen Modulationsfrequenz  $f_c$  im Vergleich zu einer kleinen Ausgangsfrequenz bildet sich trotzdem ein niederfrequenter Spannungsrippel bei sinusförmigen Ausgangsströmen aus. Der Ausgangstrom ändert sich innerhalb einer Modulationsperiode  $T_m$  gering, was zu dieser Schwebung führt.

Zur Lösung gibt es andere Ansätze zur Unterdrückung der niederfrequenten Spannungsrippel in den Kondensatorspannungen wie in [24] und [25]. Des Weiteren ist diese Topologie auch für nicht symmetrische Netzspannungen mit Netzfehlern in [26] betrachtet und eine dafür optimierte Regelung vorgestellt worden.

### 2.1.3 Cascaded H-Bridge (CHB)

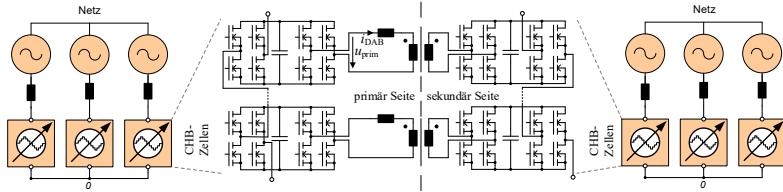

Bei der CHB werden Leistungszellen auf der AC-Seite in Serie geschaltet und jede dieser Leistungszellen verfügt über eine eigene Einspeisung. Letzteres ist der topologische Unterschied zu einem MMC. Bei dieser Struktur wird die Einspeisung in den Leistungszellen mit einem Mittelfrequenz-Transformator realisiert. Dabei hat sich der Begriff Cascaded H-Bridge (CHB) für diese Struktur in der Forschung durchgesetzt. Eine Struktur der CHB mit einer Dual Active Bridge (DAB) DC/DC-Wandler als Beispiel der Einspeisung wird in Abb. 2.5 gezeigt. Dabei wird für die Einspeisung jeder Zelle ein eigener Transformator genutzt. Die Realisierung der Einspeisung ist genauso mit anderen DC/DC-Wandler-Topologien mit Transformatoren möglich. Jedoch muss jeder der Transformatoren für die maximal auftretende Systemspannung isoliert werden.

Bei der CHB handelt es sich in der Regel um eine Serienschaltung von Vollbrücken, welche einen Zweig bzw. Phase bildet. Jede der Phasen unterliegt einer Leistungspulsation mit doppelter Ausgangsfrequenz, da kein zentraler Zwischenkreis zum Leistungsausgleich existiert. Da es sich um bidirektionale Verbindungen zwischen den einzelnen Leistungszellen der Zweige bzw. Phasen handelt, wird die Leistungspulsation mit der übertragenen Leistung der Transformatoren ausgeglichen. Somit müssen die Transformatoren für die maximale Übertragungsleistung ausgelegt

Abbildung 2.5: Netzkupplung mit CHB mit DAB DC/DC-Wandler als bidirektionale Einspeisung der Zellen

werden und werden nicht mit konstanter Leistung betrieben. Falls die DC/DC-Wandler mit konstanter Leistung betrieben werden, muss die Leistungspulsation mit den Kondensatoren in den Leistungszellen gepuffert werden. Zur Konsequenz hat dies, dass die Kommutierungsspannung der eingesetzten Halbleiter sehr stark schwankt.

Weiter gibt es bei sinusförmigen Ausgangsgrößen der CHB nicht eine gleichmäßige Ausnutzung der Leistungszellen. Bei maximaler Aussteuerung werden alle Leistungszellen verwendet, bei geringerer Aussteuerung werden weniger verwendet. Für eine gleichmäßige thermische Belastung der Zellen müssen die Zellen bei der Modulation durchgewechselt werden. Die Struktur CHB mit Dual Active Bridge (DAB) als DC/DC-Wandler wurde in [E10] für die Anbindung einer multi-phasen elektrischen Maschine an ein dreiphasiges Mittelwechselspannungsnetz oder an ein Mittelspannungsgleichspannungsnetz analysiert. Diese Topologie mit einer DAB wurde in [27] mit sekundärseitiger DC-Verbindung anstelle einer zweiten CHB betrachtet. Die Anwendung dieser Topologie ist die Kopplung von AC- und DC-Netzen sowie AC- und AC-Netzen.

Bei den aktuellen Forschungsvorhaben wird im Vergleich zum Series Cell Converter untersucht, wie die CHB und der zugehörige DC/DC-Wandler mit Transformator betrieben werden kann, sodass die Leistungsschwankungen in den einzelnen Komponenten verringert werden. Die Compensation der Leistungsschwankungen kann zu kleineren notwendigen Kapazitäten der Kondensatoren in den jeweiligen Komponenten und zu einem höheren Wirkungsgrad der Topologie führen. Bei einer Netzkopplung mit einer CHB gibt es viele Freiheitsgrade in der Betriebsführung.

Allerdings ist es nicht leicht, mit vielen Leistungshalbleitern und vielen hochfrequenten Transformatoren im Vergleich zu einem leistungsgrößeren niederfrequenten Transformator die gleiche Ausfallsicherheit zu erreichen. Jedenfalls ist diese aktuell Gegenstand der Forschung mit noch offenem Ergebnis.

### **Series Cell Converter (SCC)**

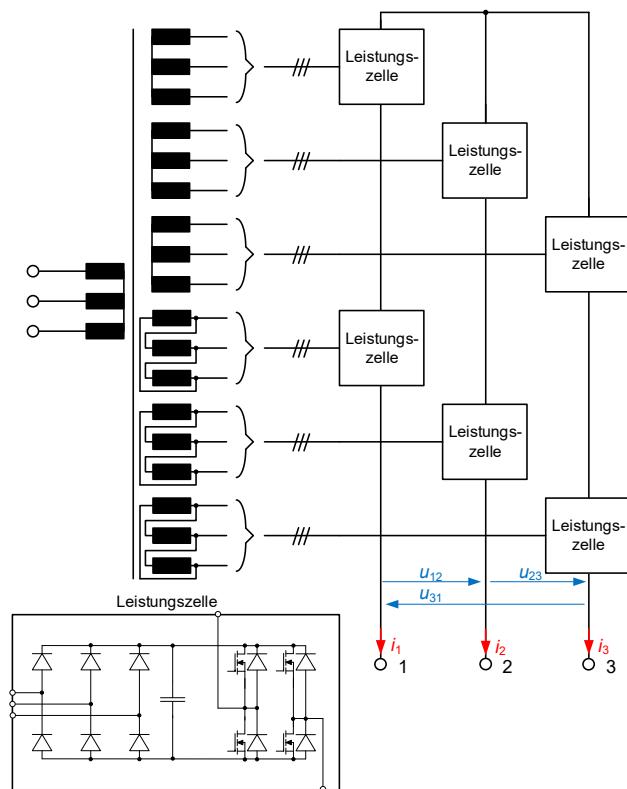

Die Bezeichnung Series Cell Converter (SCC) ist eine Bezeichnung, welche in der Literatur am ETI [28] verwendet wird. Bei Siemens wird diese Topologie als PERFECT HARMONY GH180 bezeichnet [D2]. Die klassische Struktur eines solchen Umrichters wird in Abb. 2.6 gezeigt. Dabei werden Leistungszellen auf der AC-Seite in Serie geschaltet und jede dieser Leistungszellen verfügt über eine eigene Einspeisung. In dieser Abbildung wird die Einspeisung der Zellen mit einem 50 Hz-Transformator mit vielen sekundärseitigen Wicklungssystemen und daran angeschlossenen Gleichrichtern realisiert. Die Leistungszellen bestehen aus Vollbrücken. Der Einsatz eines 50 Hz-Transformators ist der Unterschied zur CHB. Diese Gruppe der Multilevel-Umrichter verfügt immer über eine Potentialtrennung innerhalb der Topologie. Denn jede Leistungszelle arbeitet auf einem anderen Potentialniveau bzw. ändert dieses während des Schaltens der Halbleiter. In der gezeigten Leistungszelle ist nur ein passiver Gleichrichter dargestellt, eine Drehstrombrückenschaltung als bidirektionaler Umrichter auf der Netzseite ist jedoch genauso möglich. Bei dieser Topologie handelt es sich um einen einphasigen Umrichter in jeder Phase, weshalb eine Leistungsschwankung in den Leistungszellen auftritt. Diese Leistungsschwankung muss mit dem Kondensator in den Leistungszellen oder der Einspeiseleistung ausgeglichen werden.

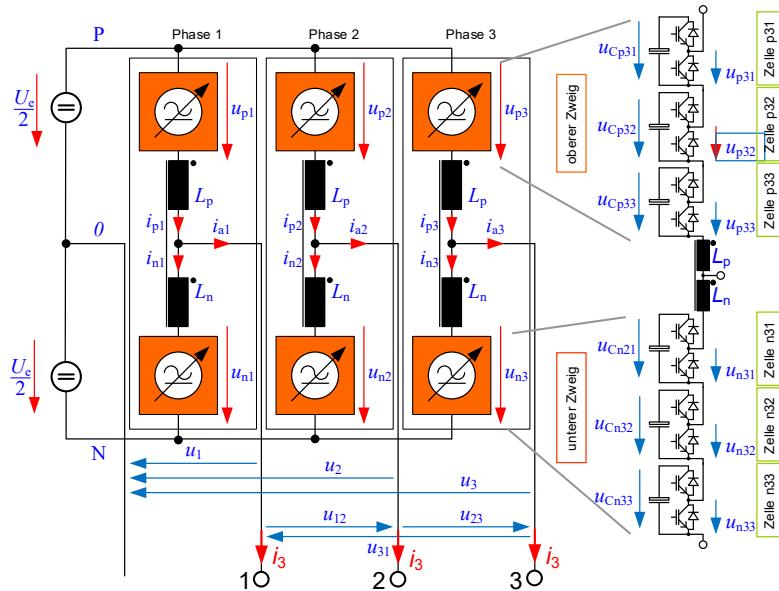

#### **2.1.4 Modular Multilevel Converter (MMC)**

Der Modular Multilevel Converter (MMC) wurde 2002 national in [30] bzw. 2003 international in [31] vorgestellt. Diese Topologie in der klassischen Form ist in Abb. 2.7 gezeigt. Der Umrichter besteht in dreiphasiger Ausführung aus sechs sogenannten Zweigen, die sich wiederum aus einer Serienschaltung von Zellen zusammensetzen. Die ursprünglichen Zellen bestanden aus einer Halbbrücke mit zugehörigem Kondensator. Eine Weiterentwicklung sind Zellen mit Vollbrücken mit zugehörigem Kondensator. Die Zweige mit Vollbrücken im Vergleich zu Zweigen mit Halbbrücken

Abbildung 2.6: 5-Level-Series Cell Converter aus [28]

Abbildung 2.7: MMC mit sechs Zweigen aus [29]

besitzen einen erweiterten Stellbereich der Zweigspannung. Dieser ermöglicht es, dass die DC-Spannung am Eingang kleiner als die AC-Spannung am Ausgang sein kann. Weiter kann anstelle einer DC-Spannung auch eine Wechselspannung an der Eingangsseite gestellt werden.

Diese Topologie wird mit sehr großen Zellanzahlen pro Zweig realisiert. Der große Vorteil dieser Topologie ist, dass jede Zelle im Umrichter identisch aufgebaut ist. Somit lässt sich ein großer Spannungs- und Leistungsbereich mit dieser Topologie mit identischen Leistungshalbleitern lediglich durch Änderung der Zellanzahl realisieren. Weiter lässt sich die Ausfallwahrscheinlichkeit dieser Topologie durch redundante Zellen im Umrichter bei integrierten Bypass-Schaltern am Zellausgang verringern. Abhängig von der Anzahl der Zellen ( $M_{\text{zweig}}$ ) pro Zweig kann eine  $N$ -stufige Spannung pro Phase bei Halbbrückenzellen gestellt werden. Dabei gilt  $N = 2 \cdot (M_{\text{ac}} - 1)$  - wobei es gilt  $M_{\text{zweig}} = M_{\text{ac}} + M_{\text{dc}}$ . In der Regel ist die Anzahl der für die Wechselspannung  $M_{\text{zweig}}$  und Gleichspannung  $M_{\text{dc}}$  verwendeten Zellen pro Zweig gleich groß. Dabei wird angenommen, dass die Gleichspannungsamplitude und Wechselspannungsamplitude gleich groß sind. Unter dieser Annahme kann die Formel Ausgangsspannungsstufenanzahl zu  $N = M_{\text{zweig}} - 1$  vereinfacht werden.

Auch bei dieser Topologie müssen die Kondensatorspannungen der einzelnen Zellen innerhalb eines Zweiges angeglichen werden. Mit der Sortierung der Zellen mit unterschiedlichen Algorithmen wird dies erreicht. Das Prinzip aller Algorithmen ist, dass die Zellen, welche die negative größte Abweichung zum Sollwert haben, am längsten bei positiver Zellleistung eingeschaltet werden. Die Zelle mit der nächstkleineren Abweichung am zweitlängsten usw. Es werden nur Zellen verwendet, wenn diese zum Stellen der Zweigspannung benötigt werden. Bei negativer Zellleistung wird zuerst die Zelle mit größter positiver Abweichung eingeschaltet und danach die Zelle mit der nächstkleineren Abweichung usw. Dabei sollen die zu großen Kondensatorspannungen bei negativer Zellleistung entladen werden. Die Zellleistung ist nach Gleichung (2.2) definiert und wird aus der jeweiligen Kondensatorspannung  $u_{c,p,x,y}$  und dem Zweigstrom  $i_{p,y}$  berechnet.

$$p_{\text{zell},x,y} = i_{p,y} \cdot u_{c,p,x,y} \quad x \in [1 \dots n], y \in [1 \dots 3] \quad (2.2)$$

Da bei dieser Topologie keine Einspeisung in den Zellen existiert und die Zweige untereinander keinen gemeinsamen Zwischenkreiskondensator zum Leistungsausgleich zwischen den Phasen besitzen, muss dieser

Leistungsausgleich durch die Zellkondensatoren ausgeglichen werden oder aktiv durch einen Leistungsfluss zwischen den Phasen. Die geringfügigen Abweichungen der einzelnen Zellen und Zweige sorgt für unterschiedliche Leistungsaufteilung zusätzlich zur Leistungsschwankung mit doppelter Ausgangsfrequenz. Beim MMC wird der Leistungsausgleich durch die Kondensatoren möglichst reduziert, damit die notwendige Kapazität reduziert werden kann. Der Leistungsausgleich zwischen den Zweigen wird durch Ströme zwischen den Phasen und Zweigen mit Spannungskomponenten der gestellten Zweigspannung, die weder am Eingang noch am Ausgang wirksam sind, erreicht. Die für den Betrieb notwendige Regelung des Leistungsausgleichs zwischen den Phasen und Zweigen wird beim MMC als Symmetrierungsregelung bezeichnet. Die Regelung der Zweig-energien und die Modulation mit Sortierung der Zellen innerhalb der Zweige, sind sehr komplex und es gibt mehrere Lösungen dafür.

In [29], [32] und [33] wurde der Betrieb des MMCs untersucht. Ein Ansatz für einen generischen N-Phasen MMC zur Analyse und Regelung wurde in [34] präsentiert. Die Dissertation [35] hat sich mit einem neuen Anwendungsgebiet der MV-DC Anwendungen des MMCs beschäftigt. Allerdings gibt es bei dieser Topologie unterschiedliche Ausführungen. Eine besondere Kopplung für dreiphasige Netze mit Potentialtrennung mit MMC ist in [36] beschrieben. Von zwei Phasen werden die vier Zweiginduktivitäten magnetisch gekoppelt und bilden einen Überträger für die Leistung zwischen den Netzen. Eine ältere Variante des MMCs mit Vollbrücken in Serie verschaltet ohne eigene Einspeisung wurde als dreiphasiger STATCOM in [37] vorgestellt.

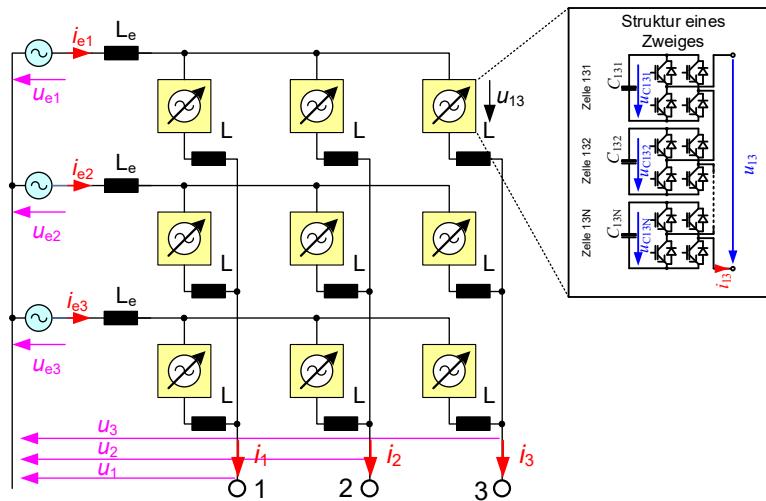

### **Modular Multilevel Matrix Converter (M3C)**

Der Modular Multilevel Matrix Converter (M3C) ist eine Abwandlung des klassischen MMCs. Es handelt sich um eine Kombination des Matrix-Direktumrichters mit MMC-Zweigen als Ausführung der Schaltelemente. Dabei handelt es sich um eine Topologie mit neun Zweigen. Diese Topologie koppelt eine dreiphasige Eingangsspannung mit einer dreiphasigen Ausgangsspannung ohne eine Wandlung zu einer Gleichspannung miteinander. Eine Abbildung ist in Abb. 2.8 gezeigt. In [38] wurde eine Systemanalyse und Regelung vorgestellt.

Abbildung 2.8: M3C mit neun Zweigen aus [38]

## 2.2 Betrieb des Flying Capacitor Umrichters

In Abschnitt 2.1.2 wurde bereits die Topologie vorgestellt. Im Folgenden werden die notwendigen Grundlagen zur Topologie und dem konventionellen Betrieb des FLCs zum Verständnis der späteren Kapitel erläutert. Eine wichtige Anforderung bei Multilevel-Umrichtern ist die gleichmäßige Spannungsaufteilung auf die einzelnen Halbleiter. Allgemein kann die Kommutierungsspannung beim FLC mit Gleichung (2.3) berechnet werden. Dabei werden die Kondensatorspannungen nach Gleichung (2.1) vorausgesetzt. Gleichzeitig ist diese Spannung die Differenz zwischen zwei Spannungsniveaus der Multilevel-Ausgangsspannung  $u_{\text{phase}}$ .

$$U_{\text{kom}} = \frac{U_{\text{zk}}}{(N - 1)} \quad (2.3)$$

Eine sehr wichtige Bedingung beim FLC ist, dass im Betrieb nicht die zwei Halbleiter, welche den Plus- und Minuspol zweier benachbarter Kondensatoren verbinden, zeitgleich eingeschaltet werden. Wenn diese korrespondierenden Halbleiter gleichzeitig eingeschaltet wären, dann würden die benachbarten Kondensatoren parallelgeschaltet und die unterschiedlichen Kondensatorspannungen gleichen sich instantan an. Dies kann zur Zerstörung der geschalteten Halbleiter durch den zu großen Ausgleichstrom zwischen den Kondensatoren bzw. einer zu hohen anliegenden Spannung an den anderen Halbleitern führen. Daher spricht man beim FLC bei den jeweiligen korrespondierenden Halbleitern, der sogenannten Kommutierzelle, immer nur von einem Zustand dieser zwei Halbleiter. Im normalen Betrieb kann der Zustand der Zelle nur zwei Werte annehmen. Der obere Halbleiter ist durchgeschaltet oder der untere Halbleiter ist durchgeschaltet. Im Übergang dieser Zustände werden beide ausgeschaltet und der Ausgangsstrom fließt durch die Freilaufdioden in Abhängigkeit des Vorzeichens des Ausgangstroms. Danach wird erst einer der zwei Halbleiter eingeschaltet. Weiteres dazu befindet sich in Abschnitt 2.2.1.

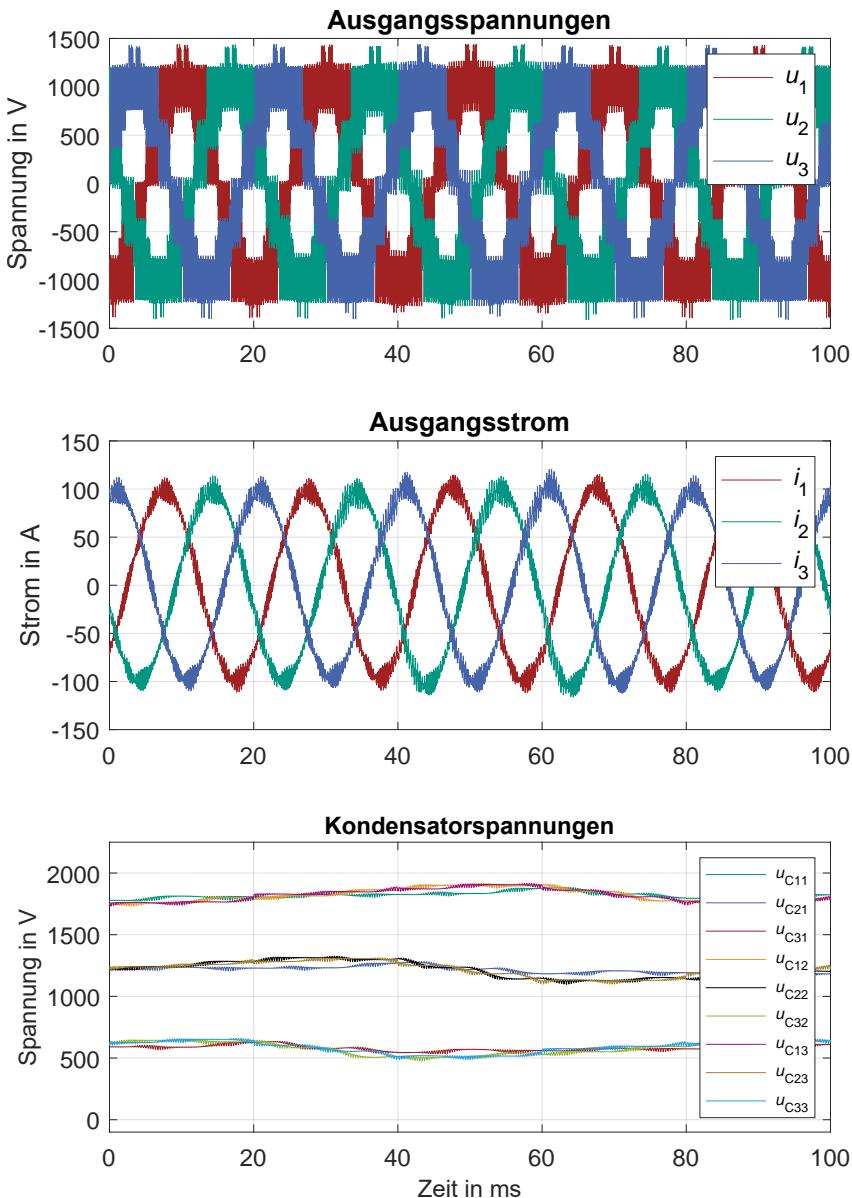

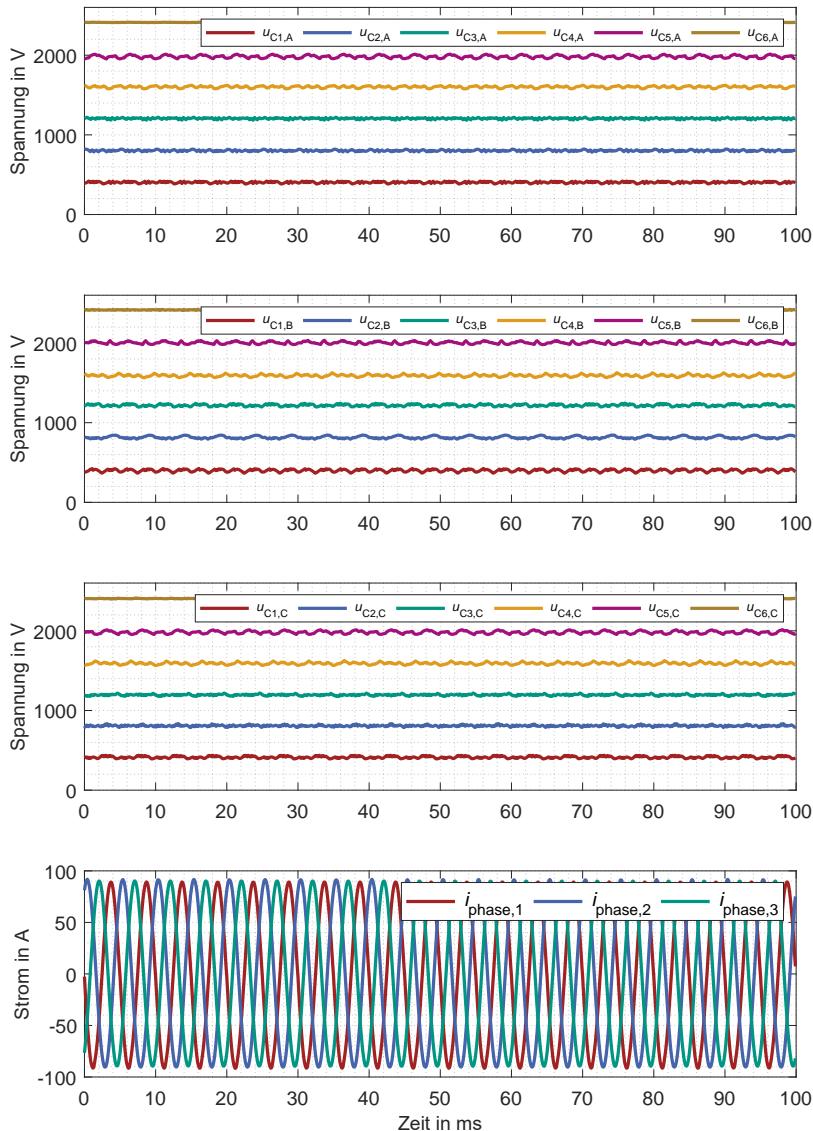

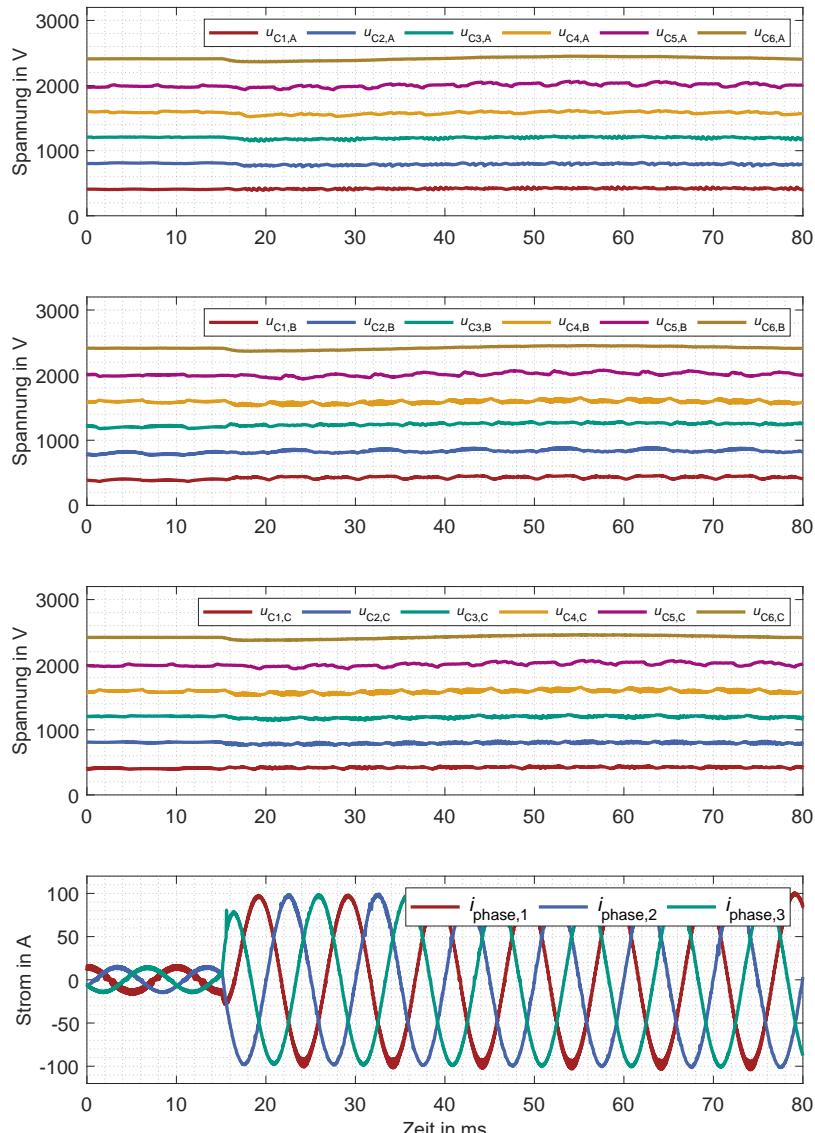

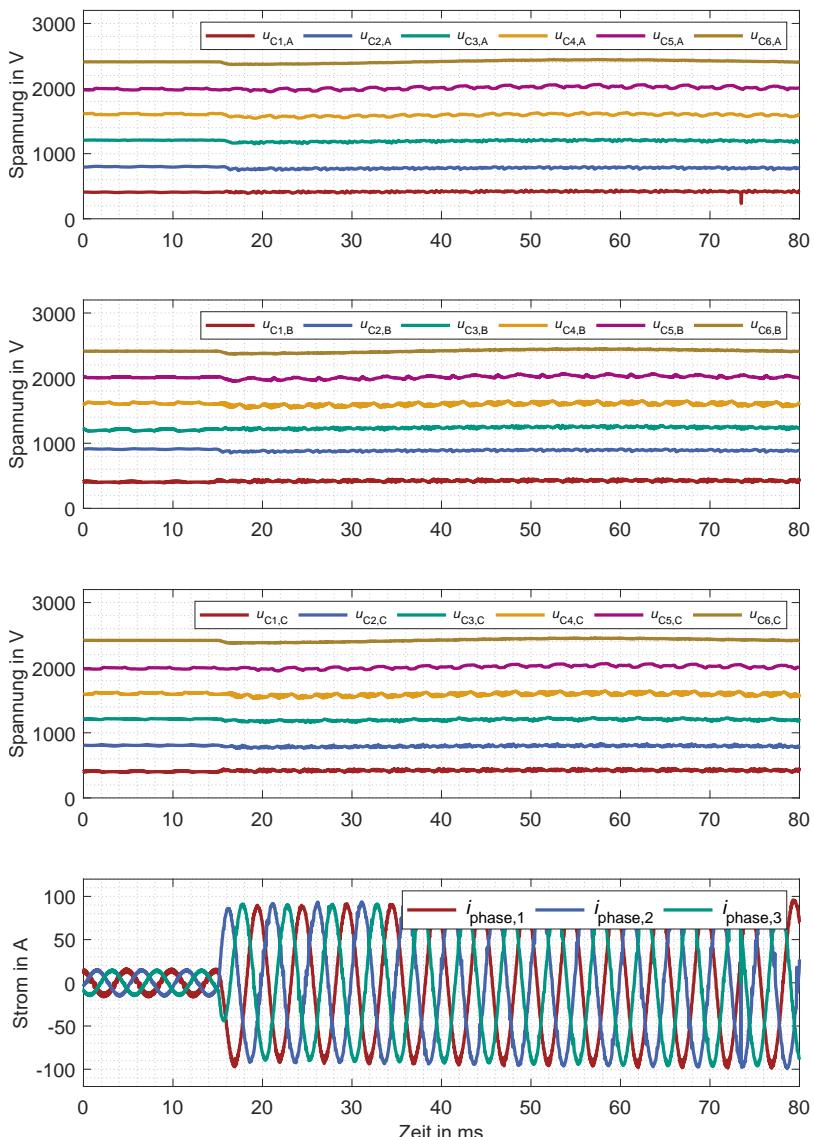

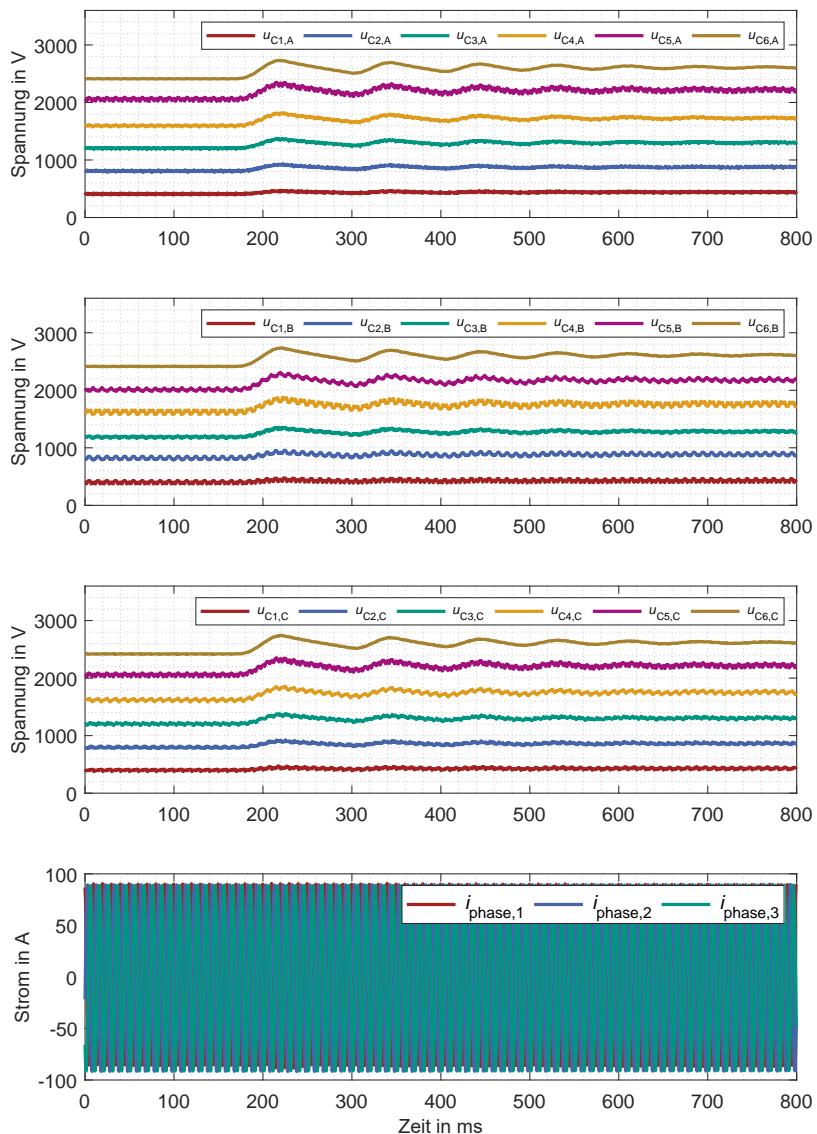

Im konventionellen Betrieb stellt der FLC eine Multilevel-Ausgangsspannung, wie auch bei allen anderen Multilevel-Umrichtern. In Abb. 2.9 wird die simulierte, dreiphasige Ausgangsspannung und der dreiphasige Ausgangsstrom eines 5-Level-FLCs gezeigt. Dabei sind die unterschiedlichen Spannungsniveaus der Multilevel-Spannung der jeweiligen Ausgangsspannung zu erkennen. Bei der Simulation wurde die

Zwischenkreisspannung  $U_{\text{zk}} = 2,4 \text{ kV}$  eingestellt. Damit sind die fünf Spannungsniveaus  $u_{\text{phase}} \in \{-1,2 \text{ kV}, -0,6 \text{ kV}, 0 \text{ kV}, 0,6 \text{ kV}, 1,2 \text{ kV}\}$  der Phasenspannung möglich. Weiter sind die sinusförmigen dreiphasigen Ausgangsströme mit  $I_{\text{phase}} = 70 \text{ A}$  gezeigt. Es wurde eine dreiphasige Drossel mit der Induktivität von  $6,25 \text{ mH}$  und eine Schaltfrequenz  $f_s = 3 \text{ kHz}$  verwendet. Die Netzspannung beträgt  $U_{\text{Netz}} = 1,4 \text{ kV}$ . Im dritten Diagramm sind die neun Kondensatorspannungsverläufe der dreiphasigen Ausführung mit  $u_{Cxy}$  gezeigt. Dabei bedeutet bei den Indices  $x$  der jeweilige Kondensator und  $y$  die jeweilige Phase. Die Kondensatoren besitzen jeweils ihre Kondensatorspannungssollwerte, welche mit Gleichung (2.1) berechnet werden. In den Simulationsergebnissen ist direkt ersichtlich, dass die Kondensatorspannungen im Betrieb eine veränderliche Abweichung zu ihren Sollwerten haben. Diese Abweichung sollte so gering wie möglich sein, allerdings ist dies eine Optimierungsfrage.

### 2.2.1 Funktionsweise der Topologie

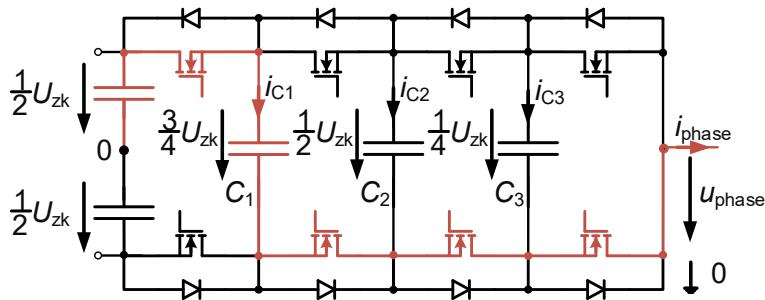

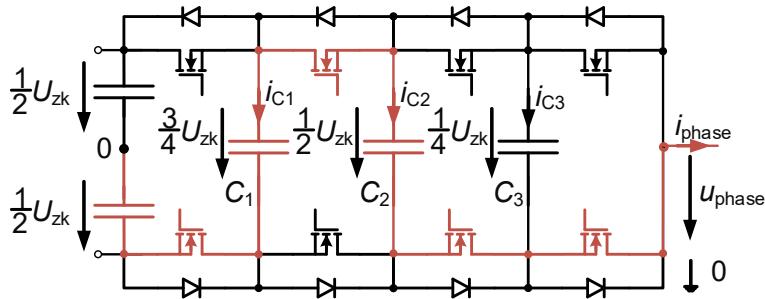

Beim FlC gibt es bezüglich der Erzeugung der Multilevel-Ausgangsspannung eine kombinatorische Vielfalt für die gleiche Ausgangsspannungsstufe. In Abb. 2.10 ist für den Schaltzustand *HLLL* der Stromflusspfad bei positivem Ausgangstrom gezeigt. Die Nomenklatur mit *H* und *L* bedeutet, dass bei *H* der obere Halbleiter durchgeschaltet ist und bei *L* der untere Halbleiter der korrespondierenden Halbleiterpaare eingeschaltet ist. Die Ausgangsspannung dieses Schaltzustands ist:  $u_{\text{phase}} = +0,5 \cdot U_{\text{zk}} - 0,75 \cdot U_{\text{zk}} = -0,25 \cdot U_{\text{zk}}$ . In Abb. 2.11 ist der Stromflusspfad bei positivem Ausgangstrom des Schaltzustands *LHLL* gezeigt. Dabei ist die Ausgangsspannung  $u_{\text{phase}} = -0,5 \cdot U_{\text{zk}} + 0,75 \cdot U_{\text{zk}} - 0,5 \cdot U_{\text{zk}} = -0,25 \cdot U_{\text{zk}}$ . Bei diesen zwei Schaltzuständen ergibt sich die identische Ausgangsspannung, allerdings ist der Stromfluss durch die Kondensatoren unterschiedlich. Im Schaltzustand *HLLL* fließt der Ausgangstrom in positiver Richtung alleinig durch den Kondensator  $C_1$ . Dagegen fließt der Ausgangstrom im Schaltzustand *LHLL* durch den Kondensator  $C_1$  in negativer Richtung und beim Kondensator  $C_2$  in positiver Richtung. Somit wird bei den unterschiedlichen Schaltzuständen einmal der Kondensator  $C_1$  aufgeladen und bei dem anderen Schaltzustand entladen. Diese verschiedenen Stromflüsse durch die Kondensatoren werden zur Symmetrierung der Kondensatorspannungen verwendet.

Abbildung 2.9: Simulationsergebnisse eines dreiphasigen 5-Level-FLCs mit Ausgangsspannung, Ausgangsstrom und den neun Kondensatorspannungsverläufen

Abbildung 2.10: Schaltbild mit Stromflusspfad bei positivem Ausgangsstrom für den Schaltzustand *HLLL*

Abbildung 2.11: Schaltbild mit Stromflusspfad bei positivem Ausgangsstrom für den Schaltzustand *LHLL*

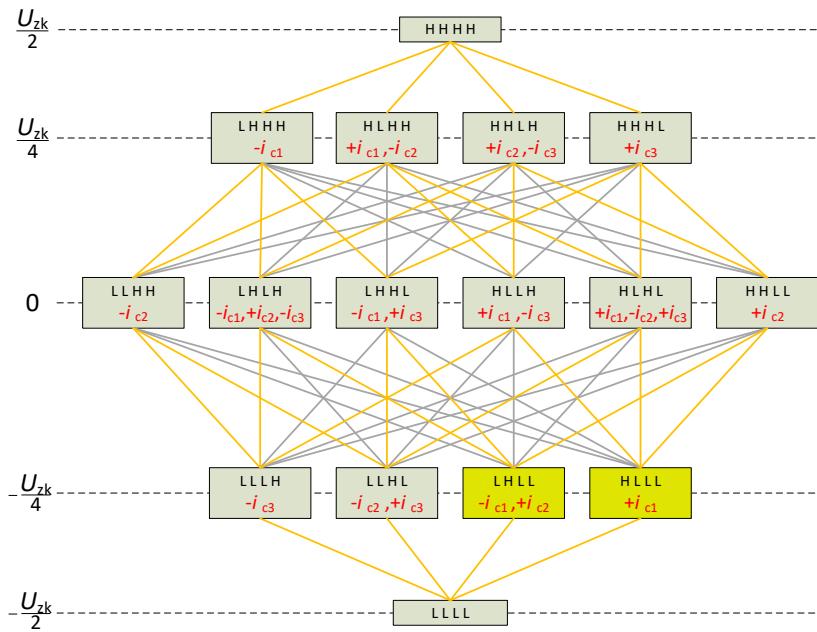

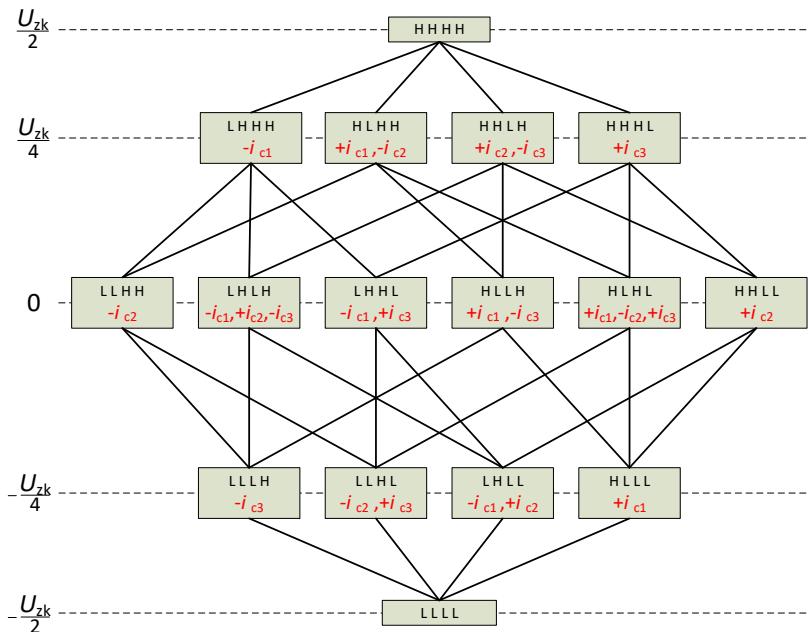

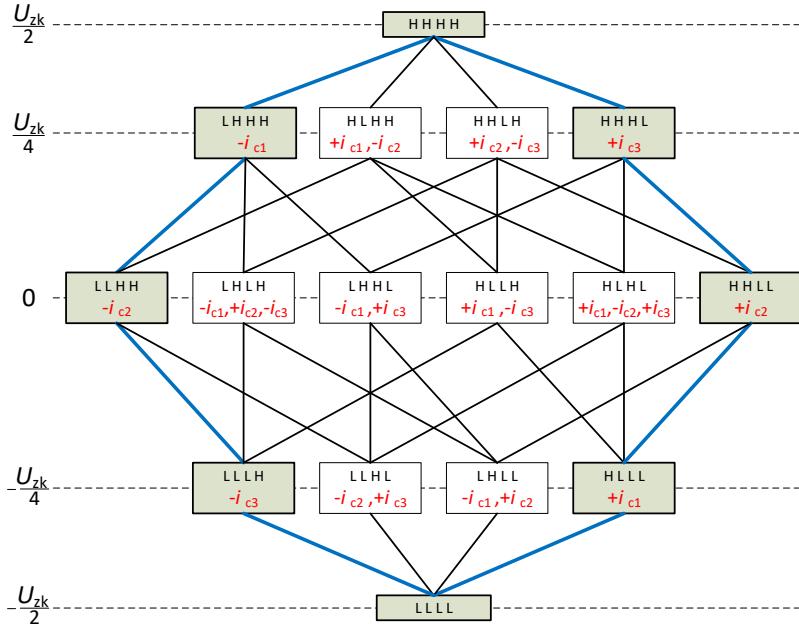

In Abb. 2.12 sind für einen 5-Level-FLC alle Schaltkombinationen für die jeweiligen Spannungsniveaus eingezeichnet. Die gelb markierten Schaltzustände sind die in Abb. 2.10 und Abb. 2.11 Dargestellten. Bei dieser Darstellung ist zu erkennen, wie viele Zellen im Zustand  $H$  oder  $L$  sein müssen, um die jeweilige Ausgangsspannungsstufe zu stellen. In diesem Diagramm sind mit den Verbindungslinien die möglichen Umschaltungen zwischen den einzelnen Spannungsstufen eingezeichnet. Wenn vom Zustand  $LLLL$  zu  $HLLL$  gewechselt wird, dann ändert nur eine Zelle zeitgleich ihren Zustand. Von jedem Zustand gibt es Übergänge mit dem Wechsel des Zustands nur einer Zelle, diese sind im Diagramm orange markiert. Wichtig dabei ist, dass die Kommutierung innerhalb einer Leistungszelle abläuft und der Kommutierungskreis dadurch möglichst klein ist. Dies ist vor allem beim Einsatz von schnell schaltenden Halbleitern wie SiC wichtig. In [39] wurde der Einsatz von SiC-Halbleitern in einem FLC präsentiert. Damit nur Kommutierungen mit möglichst kleinen Überspannungen an den Halbleitern verwendet werden, wurde die Modulation entsprechend abgeändert. Bei konventionellen Modulationsverfahren wird die Minimierung der gleichzeitigen Umschaltungen nicht beachtet. Wenn der Referenzwert genau einen Schnittpunkt von zwei Trägersignalen schneidet, dann schalten gleichzeitig mehrere Kommutierungszellen um. Bei der Veröffentlichung wurden die Trägersignale und das Referenzsignal so gewählt, dass solche Schnittpunkte nicht auftreten.

Abbildung 2.12: Schaltdiagramm eines 5-Level-FICs mit allen möglichen Schaltfolgen der verschiedenen Schaltzustände der jeweiligen Spannungslevels

## 2.2.2 Konventionelle Symmetrierung und Modulation

Bei Multilevel-Umrichtern müssen die verschiedenen Kondensatoren auf ihren Sollspannungswerten gehalten werden. Die Abweichungen entstehen durch den Ausgangsstrom, welcher zeitweise durch die Kondensatoren fließt. Genauso entsteht eine Abweichung durch die Toleranzen in den Kapazitäten und der Selbstentladung der Kondensatoren. Die Anforderung an die Symmetrierung kann mathematisch nach Gleichung (2.4) beschrieben werden. Dabei wird die Selbstentladung durch einen externen Entladewiderstand betrachtet. Die folgenden Formeln gelten für jeden Kondensator einzeln im FIC.

$$\bar{p}_C = \frac{1}{T} \cdot \int_0^T p_C \, dt = \frac{1}{T} \cdot \int_0^T u_C \cdot i_C \, dt = 0 \quad (2.4)$$

In Gleichung (2.4) gibt es nur eine Größe, welche direkt beeinflusst werden kann, das ist der Kondensatorstrom  $i_C$ . Die Kondensatorspannung  $u_C$  sollte möglichst konstant bleiben, damit die Annahmen für Gleichung (2.3) gelten. Bedingt durch die Selbstentladung muss ein entsprechender Ausgangsstrom  $I_{\text{phase}}$  mindestens fließen, damit die Kondensatoren symmetriert werden können. Dies hat bei den später erläuterten Modulationen zur Konsequenz, dass ein reiner Leerlauf also  $I_{\text{phase}} = 0 \text{ A}$  bei dieser Topologie nicht beim konventionellen Multilevel-Betrieb realisiert werden kann.

In Abb. 2.12 sind die möglichen Stromflusspfade durch die einzelnen Kondensatoren bei den Schaltzuständen eingezeichnet. Dabei bedeutet +, dass die Stromflussrichtung durch den jeweiligen Kondensator der Stromflussrichtung des Ausgangsstroms entspricht. Bei einem – bedeutet es, dass die Stromflussrichtung durch den Kondensator entgegengesetzt zur Stromflussrichtung des Ausgangsstroms ist. In jeder Spannungsstufe der Ausgangsspannung kann jeder Kondensatorstrom in den verschiedenen Kondensatoren sowohl positiv als auch negativ sein. Damit lässt sich bei entsprechend alternierender Wahl der Schaltzustände die Forderung nach Gleichung (2.4) realisieren. Für den konventionellen Multilevel-Betrieb wird ein Verfahren aus der Literatur APOD in Abschnitt 2.2.2 erläutert. Es gibt auch nicht trägerbasierte Verfahren, wie den einfachen Symmetrierungsalgorithmus von G. Clos [17]. Dieser Algorithmus wählt je nach Kondensatorspannungsabweichung direkt die Schaltzustände für die nächste Multilevel-Spannungsstufe. In Tabellen ist in

Abhangigkeit der Kondensatorspannungsabweichungen und dem Vorzeichen des Ausgangsstroms hinterlegt, welcher Schaltzustand bei einem entsprechenden Sollwert der Ausgangsspannung in der nachsten Modulationsperiode gestellt wird. Dieses Verfahren bildet die Grundlage fur den Symmetrierungsalgorithmus mit variabler Schaltsequenz beim Q2LB, wie in Abschnitt 4.1.3 beschrieben wird.

Je nach Symmetrierung variiert die Auslegung der Kapazitat der Kondensatoren. Dabei kann ganz allgemein die Gleichung (2.5) fur die Ladung  $Q_C$  des Kondensators aufgestellt werden.

$$Q_C = C_C \cdot U_C = \int_0^T i_C \, dt \quad (2.5)$$

Die Gleichung (2.5) kann mit der Annahme von konstantem Kondensatorstrom  $i_C$  in definierten Zeitabstanden  $\Delta t = T$  in Form der Gleichung (2.6) umgeschrieben werden.

$$\Delta Q_C = C_C \cdot \Delta U_C = \Delta t \cdot i_C \quad (2.6)$$

Die Gleichung (2.6) kann nach der Kapazitat des Kondensators  $C_C$  umgestellt werden.

$$C_C = \frac{\Delta t \cdot i_C}{\Delta U_C} \quad (2.7)$$

Bei der Auslegung muss das Zeit Intervall  $\Delta t$  und die Kondensatorspannungsabweichung  $\Delta U_C$  gewahlt werden. Der Kondensatorstrom  $i_C$  ist beim FLC eindeutig der maximale Ausgangsstrom  $\hat{i}_{\text{phase}}$ . Die Auslegung wurde bereits mehrmals in der Literatur betrachtet und wird daher aus [12] ubernommen. Beim konventionellen Multilevel-Betrieb kann die Kapazitat mit Gleichung (2.8) aus [12] bestimmt werden.

$$C_{\text{konv}} = \frac{\hat{i}_{\text{phase}}}{(N - 1) \cdot f_c \cdot \Delta U_{C,\text{max}}} \quad (2.8)$$

Fur  $\Delta U_{C,\text{max}}$  wird 10% bis 20% der Kommutierungsspannung  $U_{\text{kom}}$  gewahlt. Die Modulationsfrequenz  $f_c$  ergibt sich aus dem gewahlten Modulationsprinzip und der gewahlten Schaltfrequenz  $f_s$  der Halbleiter.

Damit ergibt sich mit den Parametern, welche fur den Hardwareprototypen gewahlt wurden – mit  $f_c = 10 \text{ kHz}$ ,  $\hat{i}_{\text{phase}} = 150 \text{ A}$  und  $\Delta U_{C,\text{max}} = 160 \text{ V}$  – eine notwendige Kapazitat von  $C_{\text{konv}} = 23,44 \mu\text{F}$  bei

5-Level-Betrieb für jeden Kondensator exklusiv des Zwischenkreises. Zum Vergleich, der Q2LB benötigt ungefähr eine Kapazität von  $1 \mu\text{F}$ . Dabei ist die Schaltfrequenz von  $f_s = 10 \text{ kHz}$  für einen heutigen Mittelspannungs-umrichter sehr hoch und diese verkleinert die notwendige Kapazität des konventionellen Betriebs des FLCs.

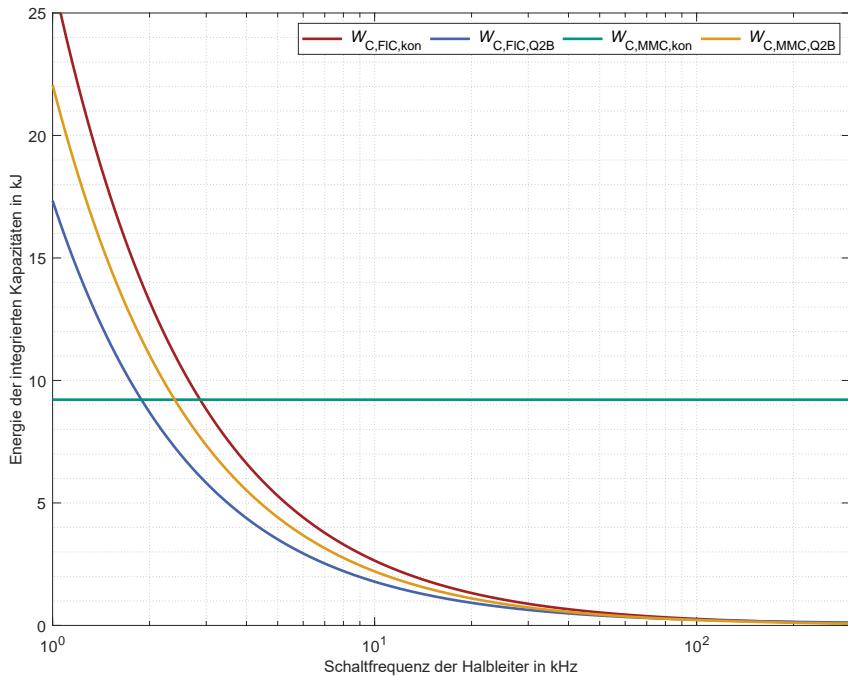

Damit es besser mit anderen Topologien verglichen werden kann, wird im Folgenden die integrierte Energiemenge sowie das Verhältnis aus  $\frac{W_C}{P_{AC}}$  bestimmt. Für die Berechnung wird die maximale Zwischenkreisspannung von  $U_{zk} = 3,2 \text{ kV}$  und die nominale Ausgangsleistung von  $P_{AC} = 240 \text{ kW}$  angenommen. Da für den konventionellen Multilevel-Betrieb und den Q2LB sich der Zwischenkreis bzw. deren Kapazität nicht unterscheidet, wird diese mit  $C_{zk} = 250 \mu\text{F}$  festgelegt. Bei diesem Vergleich wird von einem dreiphasigen 5-Level-FLC-Aufbau ausgegangen.

$$W_C = 3 \cdot \sum_{i=1}^3 \frac{1}{2} \cdot C_C \cdot {U_{C,nom,i}}^2 + \frac{1}{2} \cdot C_{zk} \cdot {U_{zk}}^2 \quad (2.9)$$

Mit Gleichung (2.9) ergibt sich für den konventionellen Betrieb  $W_{C,con} = 1,64 \text{ kJ}$ , was ein  $\frac{W_{C,con}}{P_{AC}} = 5,97 \text{ ms}$  ist. Beim Q2LB ist  $W_{C,q2b} = 1,29 \text{ kJ}$ , was ein  $\frac{W_{C,q2b}}{P_{AC}} = 4,69 \text{ ms}$  ist.

Für den folgenden Vergleich wird noch der dreiphasige 7-Level-FLC betrachtet. Eine maximale Zwischenkreisspannung von  $U_{zk} = 4,8 \text{ kV}$  und die nominale Ausgangsleistung von  $P_{AC} = 420 \text{ kW}$  ergeben sich bei 7-Level. Die Zwischenkreiskapazität  $C_{zk}$  und die Kapazitätswerte der anderen Kondensatoren bleiben unverändert. Die integrierte Energiemenge wird mit Gleichung (2.10) berechnet.

$$W_C = 3 \cdot \sum_{i=1}^5 \frac{1}{2} \cdot C_C \cdot {U_{C,nom,i}}^2 + \frac{1}{2} \cdot C_{zk} \cdot {U_{zk}}^2 \quad (2.10)$$

Beim 7-Level-FLC ergibt sich für den konventionellen Betrieb  $W_{C,con} = 4,34 \text{ kJ}$ , was ein  $\frac{W_{C,con}}{P_{AC}} = 8,54 \text{ ms}$  ist. Beim Q2LB ist  $W_{C,q2b} = 2,04 \text{ kJ}$ , was ein  $\frac{W_{C,q2b}}{P_{AC}} = 5,77 \text{ ms}$  ist.

Bei jedem der Vergleiche wird gezeigt, dass die kleineren Kapazitäten des Q2LBs sich bei der integrierten Energiemenge auswirken. Die Mehrheit der integrierten Energiemenge befindet sich allerdings im Zwischenkreis selbst, welcher der Q2LB nicht beeinflusst.

Abbildung 2.13: Struktur der Trägersignale bei der APOD Modulation

### Alternated Phase Opposition Disposition

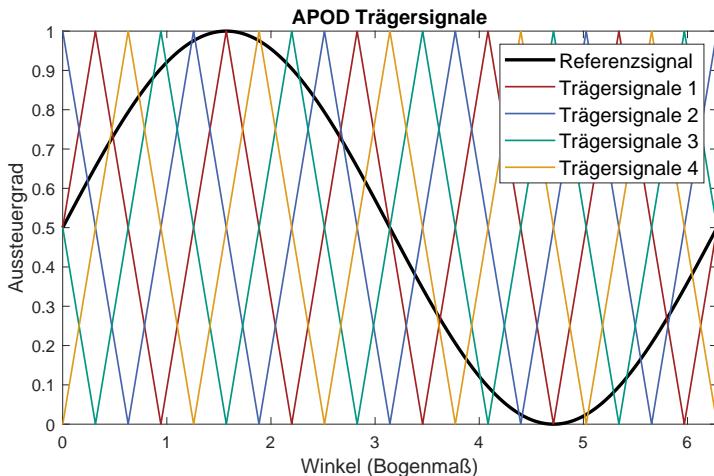

Das Verfahren Alternated Phase Opposition Disposition (APOD) ist ein exemplarisches Multi-Carrier-Verfahren, welches für viele Multilevel-Topologien angewendet werden kann. Die Bezeichnung wurde aus [12] übernommen. Es ist ein trägerbasiertes Modulationsverfahren und dabei wird beim FLC für jedes Halbleiterpaar ein separater Träger erzeugt. Bei einem 5-Level-FLC sind dies vier Trägersignale. Diese vier Trägersignale werden jeweils um die Phasenlage von  $\frac{1}{4} \cdot \frac{1}{f_c}$  verschoben. Die Zuordnung der Träger zur Kommutierungszelle wird konstant gewählt. In Abb. 2.13 wird das Muster der Trägersignale bei einem Verhältnis von  $\frac{f_c}{f_{ref}} = 5$  gezeigt.  $f_{ref}$  ist die Frequenz des Referenzsignals. In realen Anwendungen ist das Verhältnis bedeutend größer. Bei größerem Verhältnis wäre das Muster allerdings nicht gut erkennbar. Das Referenzsignal ist die Vorgabe der Aussteuerung des Umrichters von der überlagerten Regelung der Anwendung. In dieser Abbildung ist das Referenzsignal zeitlich sehr hoch aufgelöst. Bei real implementierten Systemen wäre das Referenzsignal deutlich gestufter.

Abbildung 2.14: simulierter Kondensatorspannungsverlauf einer Phase eines 5-Level-FICs mit  $f_c = 3\text{ kHz}$  bei APOD-Modulation

Abbildung 2.15: Frequenzspektrum der Ausgangsströme bei  $f_c = 3\text{ kHz}$  bei APOD-Modulation

Wenn das Referenzsignal einen der Träger schneidet, wird zu diesem Zeitpunkt ein Zustandswechsel einer Kommutierungszelle veranlasst. Bei einem höheren Wert des Referenzsignals als dem Trägersignal, wird der obere Halbleiter eingeschaltet und der untere Halbleiter ausgeschaltet. Bei einem niedrigeren Wert des Referenzsignals ist der Schaltzustand genau umgekehrt. Bei realen Halbleitern ist eine Verriegelung der Gate-Signale zwingend notwendig, welche durch eine Verzögerung der Gate-Signale zum Einschalten realisiert wird. Sonst würde im Betrieb eine kurzzeitige Parallelschaltung der benachbarten Kondensatoren erfolgen.

Die Idee der Symmetrierung ist, dass bei einem periodischen Ausgangstrom die Kondensatoren durch die verschiedenen Wechsel zwischen den Schaltzuständen gleichmäßig aufgeladen und entladen werden. Wenn die Ausgangsgröße bzw. das Referenzsignal sich nicht periodisch verändert, funktioniert das Prinzip von APOD nicht. Bei einem festen Aussteuergrad und konstantem Ausgangstrom wird nicht periodisch, durch das Wechseln der Schaltzustände, jeder Kondensator innerhalb der gleichen Zeit auf- und entladen.

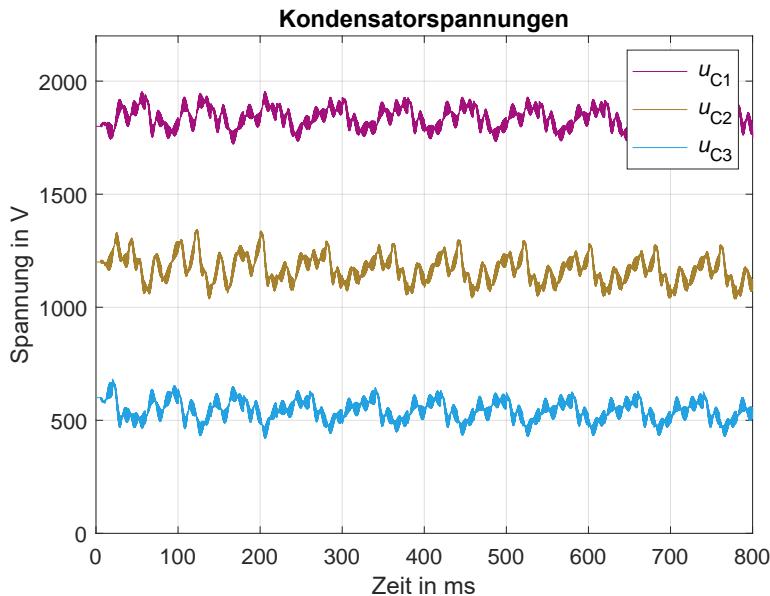

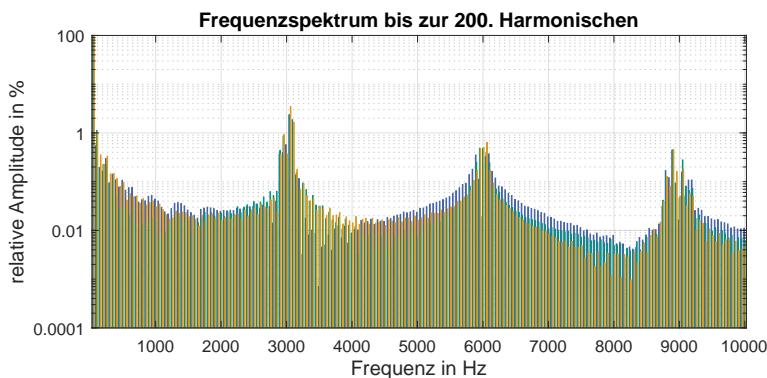

Für diese Modulation sind die Kondensatorspannungsverläufe einer Phase in Abb. 2.14 über 40 Netzperioden zu sehen. Bei der Simulation wurden die gleichen Parameter, wie sie in Abschnitt 2.2 beschrieben sind, verwendet. Die Halbleiter wurden mit Parametern des SiC-Halbleiters CAS300M12BM2 [D3] mit einer Verriegelungszeit  $t_{lock} = 200\text{ ns}$  simuliert. Dabei ist die schon angesprochene periodische Veränderung der Kondensatorspannungen zu erkennen. Die Konsequenz dabei ist, dass die gestellten Spannungszeitflächen der Ausgangsspannung ebenfalls einer periodischen Veränderung unterliegen. Diese Veränderung hat Einfluss auf das Frequenzspektrum des Ausgangsstroms, welche in Abb. 2.15 gezeigt ist. Bei ideal gleichmäßigen Multilevel-Ausgangsspannungsstufen würden sich nur Frequenzen ausprägen, die ein Vielfaches der Netzfrequenz bzw. Modulationsfrequenz  $f_c$  sind. Durch diese periodische Veränderung ergibt sich eine Verbreiterung der Spitzen im Spektrum. Das Phänomen der Verbreiterung lässt sich im Bereich von 6 kHz deutlich erkennen.

# Kapitel 3

## Der Quasi-n-Level Betrieb eines Multilevel-Umrichters

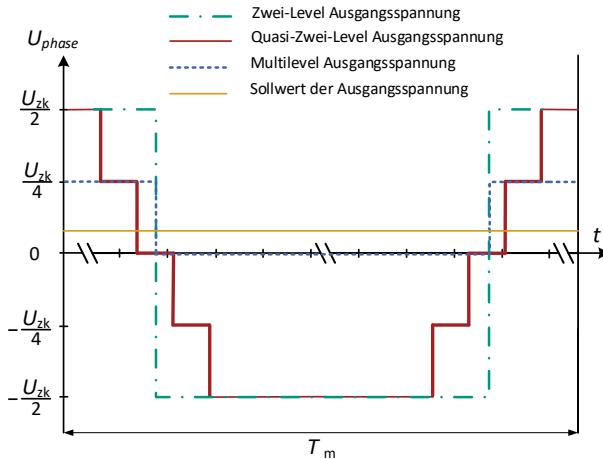

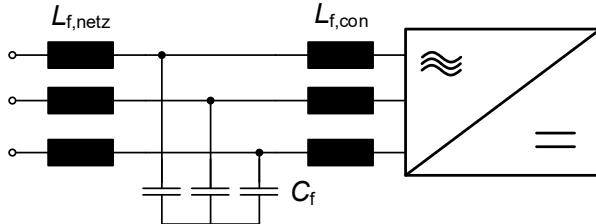

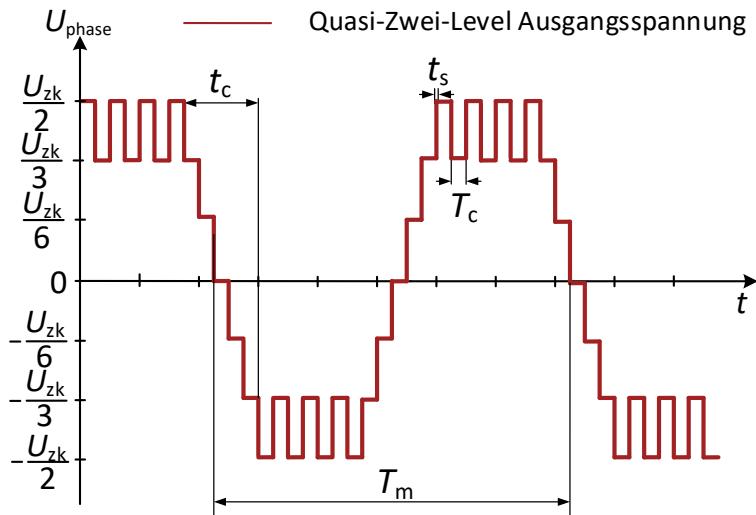

Der Quasi-n-Level Betrieb eines Multilevel-Umrichters ist eine andere Betriebsart als der konventionelle Multilevel Betrieb des jeweiligen Multilevel-Umrichters. Bisher am häufigsten verwendete Varianten davon sind der Quasi-Zwei-Level-Betrieb (Q2LB) und der Quasi-Drei-Level-Betrieb (Q3LB). Grundsätzlich wäre immer möglich, einen Quasi-n-Level Betrieb mit  $n$  kleiner als die Anzahl an möglichen Spannungsniveaus  $N$  der jeweiligen Multilevel Topologie zu betreiben. Dabei werden nur die  $n$ -Spannungsstufen mit signifikanten Anteilen innerhalb einer Modulationsperiode gestellt, so dass diese Spannungsstufen die Phasenausgangsspannung der Wechselspannung erzeugen. Der Begriff Quasi soll den Zusammenhang der geringeren Anzahl an möglichen Spannungsstufen verdeutlichen. In den letzten Jahren ist diese Betriebsart in den Fokus der Forschung gerückt, wobei diese Betriebsart allerdings nicht neu und seit einigen Jahren bereits veröffentlicht ist. Die kommerzielle Einführung von 1,2 kV-Leistungshalbleitern basierend auf SiC machte diese Betriebsweise interessant. Mit diesen verfügbaren Halbleitern bietet es sich an hochsperrende Halbleiter in der Mittelspannung durch viele Halbleiter mit geringerer Sperrspannung zu ersetzen.

Als älteste bekannte Quelle des Quasi-n-Level Betriebs aus dem Jahr 2007 sind die Veröffentlichungen [40] und [41] zu nennen. Dabei wurden bereits der Quasi-Zwei-Level und Quasi-Drei-Level Betrieb anhand eines NPCs vorgestellt. Bei vielen Multilevel Topologien folgten gleiche Ansätze und

in Abschnitt 3.3 wird eine Übersicht vorgestellt. Die grundlegende Idee ist gleichgeblieben und die angestrebten Vorteile dieses Betriebs sind ähnlich. Da sich die Mehrheit mit dem Quasi-Zwei-Level-Betrieb (Q2LB) der jeweiligen Topologie beschäftigt hat, wird im folgenden Kapitel primär nur dieser Betrieb beschrieben. Der Quasi-Drei-Level-Betrieb (Q3LB) ist in der Idee und den Vorteilen nicht anders als Q2LB und bringt lediglich die Vorteile eines Drei-Level Umrichters gegenüber eines Zwei-Level-Umrichters mit. Als allgemeine Vorteile eines Drei-Level Umrichters gegenüber eines Zwei-Level-Umrichters sind die mögliche gleichtaktfreie Ausgangsspannung, das geringere  $dU/dt$  der Ausgangsspannung bei gleicher Schaltgeschwindigkeit zu nennen.

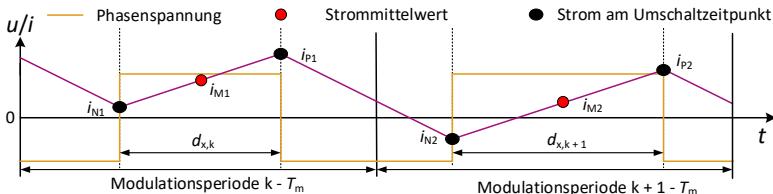

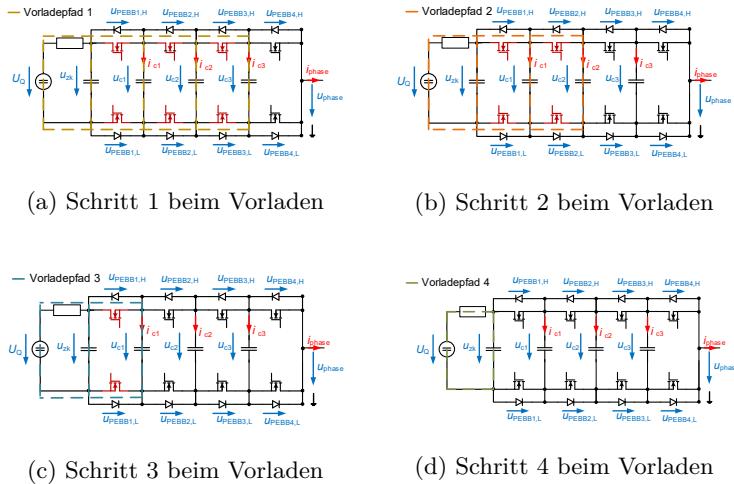

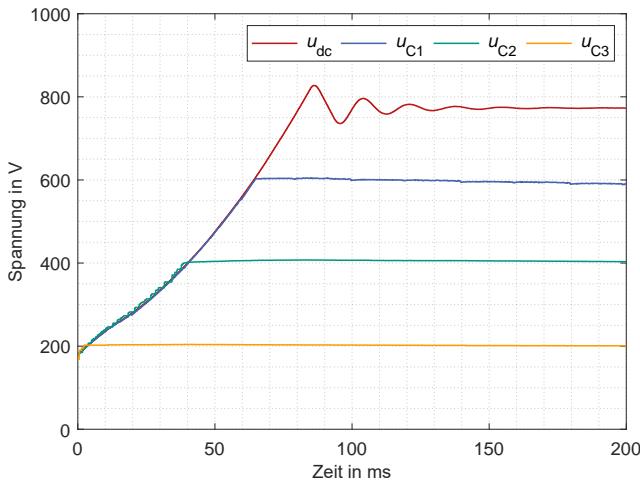

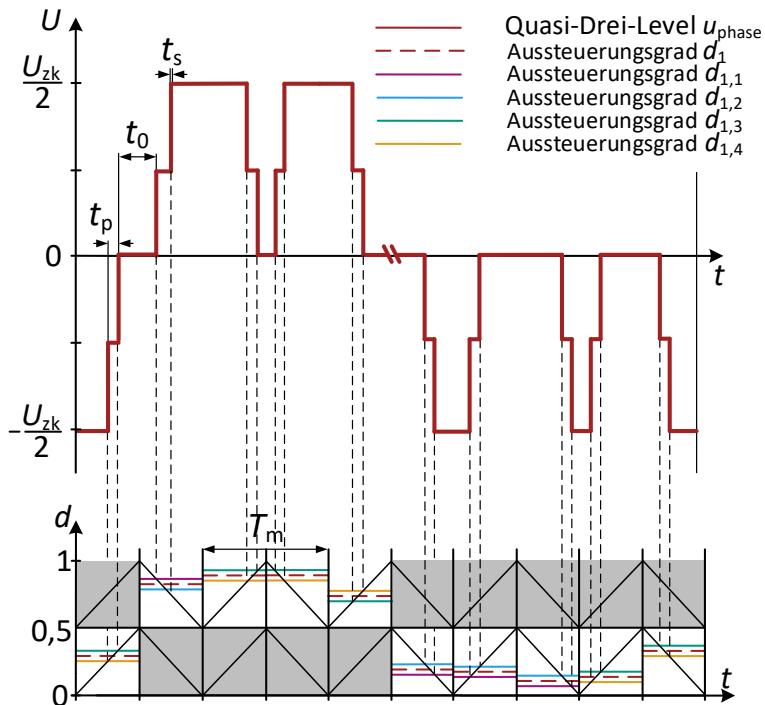

### 3.1 Idee des Quasi-Zwei-Level Betriebs