#### **PAPER • OPEN ACCESS**

# Measurements of total ionizing dose effects in TPSCo 65 nm and influence of NMOS bulk bias

To cite this article: A. Dorda Martin et al 2023 JINST 18 C02036

View the <u>article online</u> for updates and enhancements.

# You may also like

- Influence of Composition/Microstructure of Composite Cathode on Electrical Performance of Anode-Supported Solid Oxide Fuel Cells Young-Sung Yoo, Joon-Ho Koh, Jin-Woo Park et al.

- Long-Term Stability of SOFC Composite Cathode Activated by Electrocatalyst Infiltration Shiwoo Lee, Nicholas Miller and Kirk

- Gerdes

- Ammonium Ions Intercalated 1T-MoS<sub>2</sub> for Enhanced Electrochemical Hydrogen Production

- Elamathy Balamoorthy, Thangavel Srinivas, Kaushik Jayasayee et al.

# 244th ECS Meeting

Gothenburg, Sweden • Oct 8 – 12, 2023

Early registration pricing ends September 11

Register and join us in advancing science!

Learn More & Register Now!

RECEIVED: October 21, 2022 Accepted: December 12, 2022 Published: February 14, 2023

Topical Workshop on Electronics for Particle Physics Bergen, Norway 19–23 September 2022

# Measurements of total ionizing dose effects in TPSCo 65 nm and influence of NMOS bulk bias

A. Dorda Martin, $^{a,b,*}$  R. Ballabriga, $^a$  G. Borghello, $^a$  M. Campbell, $^a$  W. Deng, $^{a,c}$  G.H. Hong, $^{a,d}$  I. Kremastiotis, $^a$  W. Snoeys $^a$  and G. Termo $^e$

E-mail: ana.dorda.martin@cern.ch

ABSTRACT: The CERN EP R & D WP 1.2 aims to develop state-of-art monolithic pixel detectors using modern CMOS processes. The TPSCo 65 nm process is a suitable candidate and its radiation tolerance and sensor performance are therefore being studied. The impact of the back bias on the transistor behavior has also been measured to provide the designers with accurate models. This process shows sensitivity to radiation and degradation mechanisms similar to previously studied 65 nm CMOS technologies, strongly dependent on the geometry of the transistors. This paper presents preliminary characterization results of this technology that can serve as a guideline for designers.

Keywords: Radiation damage to detector materials (solid state); Analogue electronic circuits; Radiation-hard electronics; Particle tracking detectors (Solid-state detectors)

<sup>&</sup>lt;sup>a</sup>CERN, Espl. des Particules 1, 1211 Meyrin, Switzerland

<sup>&</sup>lt;sup>b</sup>KIT, Hermann-von-Helmholtz-Platz 1, 76344 Eggenstein-Leopoldshafen, Germany

<sup>&</sup>lt;sup>c</sup>CCNU, Hongshan, Wuhan, Hubei, China

<sup>&</sup>lt;sup>d</sup>Yonsei University, 50 Yonsei-ro, Seodaemun-gu, Seoul 03722, Republic of Korea

<sup>&</sup>lt;sup>e</sup>EPFL, Rte Cantonale, Lausanne 1015, Switzerland

<sup>\*</sup>Corresponding author.

| Co | ontents                                                  |               |

|----|----------------------------------------------------------|---------------|

| 1  | Introduction                                             | 1             |

| 2  | First measurements up to 1 Grad (SiO2) TID               | 2             |

| 3  | Transistor dimension related effects 3.1 Leakage current | <b>2</b><br>4 |

| 4  | Influence of nMOS bulk bias                              | 4             |

| 5  | Conclusion                                               | 5             |

## 1 Introduction

One of the main objectives of the EP R & D Work Package (WP) 1.2 is to develop monolithic active CMOS pixel sensors for vertex measurements at a high rate and hostile environments at the HL-LHC (High Luminosity-Large Hadron Collider). The higher luminosity leads to a maximum expected Total Ionizing Dose (TID) of up to 1 Grad (SiO<sub>2</sub>). The move to more advanced nodes with smaller feature sizes should allow for reducing power consumption and more sophisticated signal processing. Moreover, the thinner gate oxide which comes with the downscaling of the transistor size increases the tolerance to TID [1, 2]. During phase 1, WP1.2 intends to evaluate different nodes and their performance for radiation tolerance and sensor performance. At the moment TPSCo 65 nm process is the main candidate.

Several Transistor Test Structures (TTS) including both pMOS and nMOS have been designed and tested. Some of these TTS include core CMOS devices (rated at 1.2 V) distributed into two arrays of transistors, where either the width or the length varies, allowing to test the radiation response on different transistor dimensions. TID tests up to 1 Grad (SiO<sub>2</sub>) on core 1.2 V devices confirm the reliability of these transistors under irradiation, showing similar radiation response to other 65 nm technologies [3, 4]. Post-irradiation high-temperature annealing revealed the presence of two well-known radiation effects: RISCE (Radiation-Induced Short Channel Effects) and RINCE (Radiation-Induced Narrow Channel Effects) [5]. These are directly related to the radiation-induced charge trapped in the spacers and the Shallow Trench Isolation (STI) oxide.

Another topic of study was the effect of bulk bias on the transistor performance. This is relevant as there are certain pixel designs where the nMOS on the pixel matrix are biased with their bulk at voltages down to -6 V. This is done to fully deplete the sensor in order to improve the charge collection [6, 7]. However, significant reverse bulk bias might induce a considerable threshold voltage shift due to the body effect and therefore a decrease of the maximum drain current [8]. This study aims to analyze the behavior of nMOS transistors at an unusual operating point at which

the models provided by the foundry are not longer valid. Measurements at different negative bulk bias showed the impact of the body effect.

# 2 First measurements up to 1 Grad (SiO<sub>2</sub>) TID

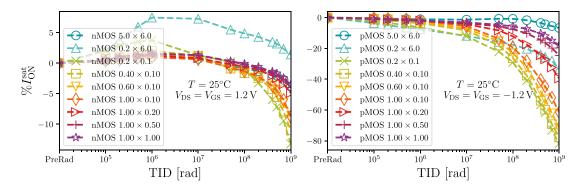

We performed a first measurement up to 1 Grad (SiO<sub>2</sub>) to test the performance of this technology at the maximum TID level expected at HL-LHC. Figure 1 shows the measured degradation of the maximum drain current ( $\%I_{ON}^{sat}$ ) for both nMOS (left) and pMOS (right). For nMOS transistors  $I_{ON}^{sat}$  drops ~15% while for the pMOS decreases by ~80%. The behaviour seen on both nMOS and pMOS matches with the results shown in [4], from the same technology node but different foundry. For both nMOS and pMOS, there is a correlation between the drain current drop and the size of the transistor (smaller sizes are less resilient to radiation). This points out the presence of both RISCE and RINCE [5], further discussed below.

**Figure 1.** Variation of  $I_{\rm ON}^{\rm sat}$  for nMOS (left) and pMOS (right) transistors with widths from 0.2  $\mu$ m to 5.0  $\mu$ m and lengths from 0.1  $\mu$ m to 6.0  $\mu$ m. The transistors were biased with  $|V_{\rm DS}| = |V_{\rm GS}| = 1.2 \,\rm V$ .

# 3 Transistor dimension related effects

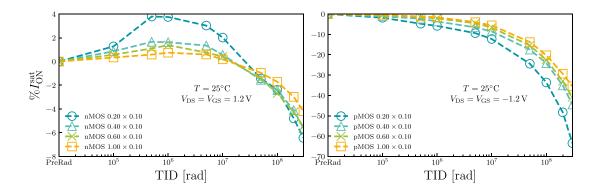

After these measurements up to 1 Grad (SiO<sub>2</sub>), we performed a second irradiation on a new TTS1 up to 300 Mrad (SiO<sub>2</sub>) followed by 85 h annealing at 100 °C. This allowed us to study in detail the effects of RINCE and RISCE on this 65 nm technology. RINCEs are related with the charges accumulated in the STI which generates an electric field, narrowing the effective channel. nMOS transistors and pMOS transistors are affected differently by TID. In nMOS devices, at the beginning of irradiation, the positive charges accumulate in the STI lowering the threshold voltage and increasing the drain current. As we increase the TID level, the negative charges accumulate at the STI/Si and compensate for the field generated by the trapped holes [9]. These two compensating effects cause the non-monotonic behaviour visible in figure 2. On the other hand, the behaviour of pMOS shown in figure 2 is monotonic. This is due to the fact that both the charges at the STI and at the STI/Si interface have the same positive sign, increasing  $V_{\rm TH}$ , and causing the maximum drain current to decrease.

**Figure 2.** Variation of  $I_{\rm ON}^{\rm sat}$  during irradiation of nMOS (left) and pMOS (right) for transistors with width from 0.2 µm to 1.0 µm and length 0.1 µm. The transistors were biased with  $V_{\rm DS} = V_{\rm GS} = 1.2 \, \rm V$  for the nMOS and with opposite sign of the pMOS.

As expected from studies performed on other 65 nm technologies from different manufacturers [5], this node also shows the presence of RISCEs; making the short channel transistors less radiation hard. RISCE can be described as [10]: (i) an increase of resistivity on the sides of the transistor induced by the accumulation of positive charges in the spacers and (ii) temperature-induced transport of hydrogen ions H<sup>+</sup> from the spacers to the gate oxide. On pMOS transistors, these two processes are visible during irradiation and annealing respectively. In the case of the nMOS, both processes are visible already during irradiation, making its study more difficult. We will focus on the pMOS as it is possible to separate the effect due to irradiation from temperature.

In order to study RISCEs table 1 shows, for a short pMOS device, maximum drain current ( $|I_{\text{ON}}^{\text{sat}}|$ ), threshold voltage ( $|V_{\text{TH}}^{\text{sat}}|$ ) and the transconductance ( $K_{\text{U}}^{\text{sat}}$ ) together with their shift from their pre-irradiation value. Variations on the latter one are directly related with variations on the series resistance. The values are extracted before irradiation, at 300 Mrad (SiO<sub>2</sub>), and at 25 °C after annealing. As mentioned before, during irradiation, there is an increase on the series resistance due to the positive charges trapped in the spacers. This is visible at 300 Mrad (SiO<sub>2</sub>) where  $I_{\text{ON}}^{\text{sat}}$  drops 36% while  $K_{\text{U}}^{\text{sat}}$  decreases by ~20%. On the other hand, the temperature-activated transport of  $H^+$  in pMOS devices is visible at 25 °C after annealing. At this point, the  $V_{\text{TH}}$  increases ~175 mV from its value before irradiation while  $K_{\text{U}}^{\text{sat}}$  almost recovers its pre-irradiation value. This temperature-dependent behaviour matches with the results obtained from similar studies performed on other 65 nm technologies [3].

**Table 1.** Maximum drain current ( $|I_{\rm ON}^{\rm sat}|$ ), threshold voltage ( $|V_{\rm TH}^{\rm sat}|$ ) and the transconductance ( $K_{\rm U}^{\rm sat}$ ) before irradiation together with their shift from their pre-irradiation value, at 300 Mrad (SiO<sub>2</sub>), and at 25 °C after annealing for a 1.0  $\mu$ m  $\times$  0.1  $\mu$ m pMOS transistor.

|                                               | PreRad. | 300 Mrad (SiO <sub>2</sub> ) | After Ann.     |

|-----------------------------------------------|---------|------------------------------|----------------|

| $ I_{\mathrm{ON}}^{\mathrm{sat}} $ [ $\mu$ A] | 252.0   | 163.0 (-36.0%)               | 176.0 (-30.0%) |

| $K_{\rm U}^{\rm sat}~[{\rm mA/V}]$            | 40.9    | 32.8 (-19.9%)                | 38.11 (-6.85%) |

| $ \Delta V_{ m TH}^{ m sat} ~[{ m mV}]$       | 275.1   | 288.8 (13.8)                 | 450.9 (175.8)  |

#### 3.1 Leakage current

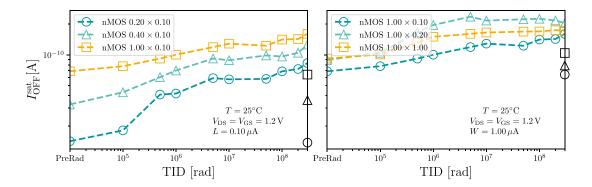

nMOS devices are known to suffer radiation-induced leakage current increase ( $I_{\rm OFF}^{\rm sat}$ ) [11, 12]. Figure 3 shows the evolution of  $I_{\rm OFF}^{\rm sat}$  during irradiation up to 300 Mrad (SiO<sub>2</sub>).  $I_{\rm OFF}^{\rm sat}$  increase less than an order of magnitude from its pre-radiation value. The minimum size device shows a lower pre-radiation leakage current and higher increase of  $I_{\rm OFF}^{\rm sat}$  during the exposure. This leads to assume that transistors with high nominal pre-radiation leakage current will see a lower increase in  $I_{\rm OFF}^{\rm sat}$  than transistors with a smaller initial leakage current. Nevertheless it is not possible to correlate the increase of  $I_{\rm OFF}^{\rm sat}$  with the length of the transistor, as it could be expected from previous studies [13]. Regarding the post-annealing values, there seems to be a good recovery of the leakage current values, almost going back to their pre-radiation nominal values before TID exposure.

**Figure 3.** Evolution of  $I_{\text{OFF}}^{\text{sat}}$  during irradiation up to 300 Mrad (SiO<sub>2</sub>). On the left, for nMOS transistors with lengths of 0.10  $\mu$ m and widths ranging from 0.20  $\mu$ m to 1.0  $\mu$ m. On the right, for nMOS transistors with widths fix to 1.00  $\mu$ m and lengths ranging from 0.10  $\mu$ m to 1.0  $\mu$ m. The black markers at the end of each plot corresponds to the values of  $I_{\text{OFF}}^{\text{sat}}$  measured after 85 h of annealing at 100 °C.

## 4 Influence of nMOS bulk bias

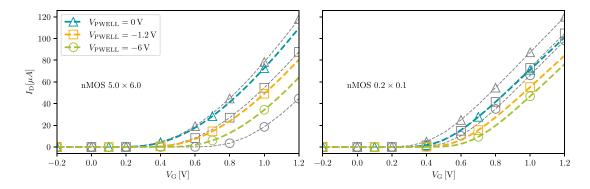

In order to study the influence of negative bulk biasing on nMOS devices, we measured the  $I_{\rm D}$  vs.  $V_{\rm G}$  curves for maximum and minimum size devices, with their bulks biased at 0, -1.2, and -6 V. The results are plotted in figure 4. The extracted values of  $V_{\rm TH}$  and its respective shift from the nominal value (at  $V_{\rm PWELL} = 0$  V) are shown in table 2. Measurements of nMOS transistors with a pwell biasing of -6 V show an increase of the nominal  $V_{\rm TH}$  of ~260 mV together with a ~40% drop of  $I_{\rm ON}^{\rm sat}$ .

In order to test the accuracy of the models, we compared the measurements with the simulations using typical (TYP) corner. The extracted values of  $V_{\rm TH}$  and  $I_{\rm ON}^{\rm sat}$ , together with their shift and percentage of variation from the nominal value (at  $V_{\rm PWELL}=0$ ,  $-1.2\,\rm V$ ,  $-6\,\rm V$ ), can be found on table 2. Figure 4 reports the simulated  $I_{\rm D}$  vs.  $V_{\rm G}$  characteristics in grey color to ease the comparison with the measurements. In the case of the maximum size device, at a bias of  $-6\,\rm V$ , the measured  $V_{\rm TH}$  error w.r.t. the simulation reaches  $\sim 160\,\rm mV$ . Regarding the minimum-size device, for both the  $V_{\rm TH}$  and  $I_{\rm ON}^{\rm sat}$  there is a significant error compared with the simulation, but on the same

order of magnitude for the three biases. However, the  $V_{\mathrm{TH}}$  shift is overestimated for maximum size devices and underestimated for minimum size devices, in both cases not accurate at large reverse biases.

Figure 4.  $I_{\rm D}$  vs.  $V_{\rm G}$  of a maximum size 5  $\mu$ m  $\times$  6  $\mu$ m device (left) and a minimum size 0.2  $\mu$ m  $\times$  0.1  $\mu$ m device (right) measured at  $V_{\rm PWELL} = 0 \, \rm V$  (blue triangles), at  $V_{\rm PWELL} = -1.2 \, \rm V$  (orange squares) and at  $V_{\rm PWELL} = -6 \, \rm V$  (green circles). Grey colored curves correspond to their equivalent simulations (TYP corner).

**Table 2.** Extracted values of  $V_{\rm TH}$  and  $I_{\rm ON}^{\rm sat}$  from the measurements and simulation (TYP corner) showed at figure 4 for  $V_{\rm PWELL} = 0$ ,  $-1.2\,\rm V$ ,  $-6\,\rm V$ . The respective  $V_{\rm TH}$  shift and percentage of variation of  $I_{\rm ON}^{\rm sat}$  from the nominal value ( $I_{\rm ON}^{\rm sat}$  and  $V_{\rm TH}^{\rm sat}$  measured at  $V_{\rm PWELL} = 0$ ,  $-1.2\,\rm V$ ,  $-6\,\rm V$ ) is shown in parenthesis with the same color coding as in figure 4.

| Size    | $V_{ m PWELL} \left[ { m V}  ight]$ | $ V_{\mathrm{TH}}^{\mathrm{sat}} $ [mV] | $ V_{\mathrm{TH,TYP}}^{\mathrm{sat}} $ [mV] | $I_{ m ON}^{ m sat} \left[ \mu { m A} \right]$ | $I_{ m ON,TYP}^{ m sat}$ [ $\mu$ A] |

|---------|-------------------------------------|-----------------------------------------|---------------------------------------------|------------------------------------------------|-------------------------------------|

|         | 0                                   | 223.4                                   | 223.1 (-0.4)                                | 109.5                                          | 118.4 (7.75%)                       |

| 5.0/6.0 | -1.2                                | 354.7                                   | 352.5 (-2.2)                                | 80.5                                           | 87.7 (8.93%)                        |

|         | -6                                  | 487.1                                   | 650.5 (+163.5)                              | 64.6                                           | 44.6 (-30.4%)                       |

|         | 0                                   | 315.2                                   | 241.1 (-74.1)                               | 101.2                                          | 120.0 (18.60%)                      |

| 0.2/0.1 | -1.2                                | 413.7                                   | 321.8 (-91.1)                               | 84.4                                           | 104.8 (24.12%)                      |

|         | -6                                  | 483.2                                   | 371.3 (-111.9)                              | 76.5                                           | 98.2 (28.35%)                       |

## 5 Conclusion

We presented the irradiation response of TPSCo 65 nm transistors together with the performance degradation study of nMOS transistors under negative bulk biases.

Irradiation results up to 1 Grad (SiO<sub>2</sub>) proof the resilience of nMOS transistors to irradiation (max. ~15%  $I_{\rm ON}^{\rm sat}$  drop) while pMOS transistors show similar degradation (max. ~80%  $I_{\rm ON}$  drop) to other 65 nm studies. Irradiation test up to 300 Mrad (SiO<sub>2</sub>) and subsequent annealing at 100 °C confirmed the presence of RISCE and RINCE. We measured  $V_{\rm TH}$  shifts up to -200 mV, followed by a fast recovery of  $K_{\rm U}$  and  $V_{\rm TH}$  after annealing. Small and monotonic radiation-induced leakage current increase on nMOS transistors of less than one order of magnitude. Minimum size devices show a higher increase of  $I_{\rm OFF}$  during irradiation.

Regarding bulk biasing, measurements of nMOS transistors with a pwell biasing of -6 V shows an increase of the nominal  $V_{\text{TH}}$  of  $\sim$ 260 mV. For bulk biases down to -1.2 V, the measured  $V_{\text{TH}}$  matches the simulation. But this is not the case for a bias of -6 V, where the error concerning the simulation reaches  $\sim$ 160 mV.

This paper offered a preliminary characterization of this technology, but this subject requires further studies. Increasing the number of measured transistors will allow to quantify the device-to-device variability. More irradiation tests will lead to reliable statistics and the understanding of radiation induced variability. Lastly, a more detailed study of performance degradation due to body effect and its correlation with transistor sizing would be beneficial for the designers, to provide an accurate model to assist on analog circuit design.

# Acknowledgments

These results are the product of the team-work. Geun Hee Hong and Wenjing Deng are the designers of the TTS and collaborated on the initial measurements. Giulio Borghello and Gennaro Termo took care of performing the irradiation and the annealing, as well as a first processing of the results. Ana Dorda performed pre-radiation measurements, analyzed the data and was the responsible of the measurement and characterization of the transistor performance under several bulk biases.

This work has been sponsored by the Wolfgang Gentner Programme of the German Federal Ministry of Education and Research (Grant No. 13E18CHA).

#### References

- [1] H. Barnaby et al., *Total-ionizing-dose effects in modern CMOS technologies*, *IEEE Trans. Nucl. Sci.* **53** (2006) 3103.

- [2] D.M. Fleetwood et al., Evolution of total ionizing dose effects in MOS devices with Moore's law scaling, IEEE Trans. Nucl. Sci. 65 (2018) 1465.

- [3] G. Borghello et al., *Ionizing radiation damage in 65 nm CMOS technology: influence of geometry, bias and temperature at ultra-high doses, Microelectron. Reliab.* **116** (2021) 114016.

- [4] M. Menouni et al., 1 Grad total dose evaluation of 65 nm CMOS technology for the HL-LHC upgrades, 2015 JINST 10 C05009.

- [5] F. Faccio et al., Radiation-Induced Short Channel (RISCE) and Narrow Channel (RINCE) effects in 65 and 130 nm Mosfets, IEEE Trans. Nucl. Sci. 62 (2015) 2933.

- [6] W. Snoeys et al., A process modification for CMOS monolithic active pixel sensors for enhanced depletion, timing performance and radiation tolerance, Nucl. Instrum. Meth. A 871 (2017) 90.

- [7] M. Munker et al., Simulations of CMOS pixel sensors with a small collection electrode, improved for a faster charge collection and increased radiation tolerance, 2019 JINST 14 C05013.

- [8] B. Razavi et al., Design of Analog CMOS Integrated Circuits, McGraw-Hill Education (2016).

- [9] F. Faccio et al., *Total ionizing dose effects in shallow trench isolation oxides, Microelectron. Reliab.* **48** (2008) 1000.

- [10] F. Faccio et al., Influence of LDD spacers and H+ transport on the total-ionizing-dose response of 65-nm MOSFETs irradiated to ultra high doses, IEEE Trans. Nucl. Sci. 65 (2017) 164.

- [11] U. Youk et al., Radiation-enhanced short channel effects due to multi-dimensional influence from charge at trench isolation oxides, IEEE Trans. Nucl. Sci. 46 (1999) 1830.

- [12] C. Zhang et al., Characterization and modeling of gigarad-TID-induced drain leakage current of 28-nm bulk MOSFETS, IEEE Trans. Nucl. Sci. 66 (2019) 38.

- [13] G. Borghello et al., Ionizing radiation effects on 28 nm CMOS technology, *CERN Technical Report*, (2020).