# AVX Overhead Mitigation: OS Support for Power-Limited Systems

Zur Erlangung des akademischen Grades eines

Doktors der Ingenieurwissenschaften

von der KIT-Fakultät für Informatik des Karlsruher Instituts für Technologie (KIT)

genehmigte Dissertation

Mathias Gottschlag, M.Sc.

aus Bad Driburg

Tag der mündlichen Prüfung: 23. Juni 2023 Erster Referent: Prof. Dr. Frank Bellosa Zweiter Referent: Prof. Dr. Timo Hönig

## Acknowledgements

I am immensely grateful to my supervisor, Prof. Dr. Frank Bellosa, for giving me full freedom when choosing my direction of research, yet always giving invaluable advice whenever needed. His thorough feedback on paper and thesis drafts proved to be very helpful, as did his focus on making sure that I always had the tools required for my experiments. I would also like to extend my gratitude to Prof. Dr. Timo Hönig for his valuable commentary on drafts of this thesis and for his invitation to present my work at the 2022 PEACHES workshop.

My heartfelt thanks go to the other members of the operating systems group for their continued support throughout my work. Thorsten Gröninger, Marius Hillenbrand, Jens Kehne, Marc Rittinghaus, and Lukas Werling all had a large impact on this thesis, be it via valuable insights during discussions or via thorough feedback on drafts and presentations. In many cases, you taught me the finer points of the scientific crafts, for which I am very grateful.

I am also deeply thankful for the assistance from Maximilian Heß and my brother Bernd Gottschlag, who dedicated many hours to proofreading this thesis. It is not only this direct support that makes a thesis such as this one possible, though. Especially during the more stressful phases of a PhD, emotional support is often equally valuable. In this sense, I would like to extend my gratitude to all the friends who lifted my spirits over countless rounds of board games and computer games.

I would also like to thank my parents, without whose continued guidance throughout life I would have hardly been in a position where I would be able to perform such research work. Finally, thank you Itzel for always being there and supporting me whenever I needed support.

## Abstract

In recent years, processors have become more and more power-limited. As a result, one of the main goals of CPU frequency selection of recent processors is to maximize performance under the given power constraints. On these processors, the choice of instructions has started to affect operating frequencies as different instructions require different amounts of energy. For example, current Intel server CPUs with support for the AVX2 and AVX-512 instruction set extensions reduce the frequency of individual cores that execute these power-intensive SIMD instructions. The resulting temporary frequency reduction reduces the throughput of the SIMD code itself, but also affect other, less power-intensive code that is, for example, executed on another hardware thread of the same physical CPU core at the same time.

This thesis focuses on the overhead that is caused by such situations where code consisting only of simple instructions with little energy consumption is executed at sub-optimal CPU frequencies. This *remote AVX overhead* has been reported to slow some workloads down by up to 30% and presents a major challenge in the use of AVX2 and AVX-512. As we show, remote AVX overhead is largely avoidable using OS-level techniques, though.

In this thesis, we perform a thorough analysis of the origins of remote AVX overhead and present a profiler that is able to accurately measure its performance impact. We then demonstrate that existing frequency selection policies implemented by the CPU provide little potential for improvement in most scenarios – instead, major performance gains are possible via techniques implemented in the operating system. We present two scheduler modifications to mitigate the impact of remote AVX overhead in different situations. First, we show how limiting the use of AVX-512 to few CPU cores and migrating individual tasks to appropriate cores can greatly reduce remote AVX overhead in heterogeneous workloads involving AVX-512 code. Second, we show how prioritizing tasks affected by remote AVX overhead can greatly improve performance isolation in the presence of remote AVX overhead caused by either AVX2 or AVX-512 code.

Our work demonstrates the need for increased involvement of the operating system with CPU frequency selection in current – and, potentially, future – power-limited systems. In addition, we uncover a range of potential improvements to existing CPU designs that would allow for even more effective mitigation of effects such as remote AVX overhead.

## Zusammenfassung

In den vergangenen Jahren haben sich Prozessoren dahingehend entwickelt, dass sie mehr und mehr durch ihre Leistungsabgabe begrenzt wurden. Aus diesem Grund ist eines der Hauptziele der Strategie zur Auswahl der Frequenz aktueller Prozessoren, die Performance innerhalb der gegebenen Leistungsgrenzen zu maximieren. Auf diesen Prozessoren beeinflusst deshalb die Wahl der Instruktionen mittlerweile oft die Betriebsfrequenz, da unterschiedliche Instruktionen unterschiedlich viel Energie benötigen. Ein Beispiel dafür findet sich in aktuellen Intel-Server-Prozessoren mit Unterstützung für AVX2- und AVX-512-Instruktionen. Diese Prozessoren reduzieren die Frequenz von CPU-Kernen, die leistungsintensiven Code mit solchen SIMD-Instruktionen ausführen. Die dadurch verursachte Frequenzreduktion reduziert den Durchsatz dieses SIMD-Codes, beeinflusst aber auch anderen weniger leistungsintensiven Code, der zum Beispiel gleichzeitig auf einem anderen Hardware-Thread des gleichen physischen CPU-Kerns ausgeführt wird.

Diese Arbeit konzentriert sich auf die Kosten, die in solchen Situationen dadurch entstehen, dass einfacher, wenig leistungsintensiver Code mit einer suboptimalen CPU-Frequenz ausgeführt wird. Diese Kosten – *Remote AVX Overhead* genannt – verlangsamen laut früherer Arbeiten manche Workloads um bis zu 30% und stellen eine große Herausforderung bei der Verwendung von AVX2 und AVX-512 dar. Remote AVX Overhead kann jedoch, wie wir zeigen, größtenteils durch im Betriebssystem umgesetzte Techniken vermieden werden.

In dieser Arbeit führen wir eine umfangreiche Analyse der Gründe für Remote AVX Overhead durch und beschreiben einen Profiler, der in der Lage ist, Remote AVX Overhead mit hoher Genauigkeit zu quantifizieren. Zudem zeigen wir, dass die Frequenzauswahlstrategie existierender Prozessoren in den meisten Fällen wenig Potential für Performance-Verbesserungen bietet – stattdessen sind wesentliche Verbesserungen durch Betriebssystemmodifikationen möglich. Wir beschreiben zwei Modifikationen des Schedulers, die in unterschiedlichen Situationen dem Einfluss von Remote AVX Overhead entgegenwirken. Zuerst zeigen wir, wie dadurch, dass AVX-512-Nutzung auf wenige Prozessorkerne beschränkt wird und Tasks auf passende Kerne migriert werden, Remote AVX Overhead stark reduziert wird, wenn Teile der ausgeführten Software AVX-512 verwenden. Danach zeigen wir, wie eine Priorisierung von Tasks, die durch Remote AVX Overhead verlangsamt werden, die Performance-Isolierung zwischen Tasks in Situationen verbessert, wenn das System teilweise entweder AVX2 oder AVX-512 ausführt.

Unsere Arbeit demonstriert, dass das Betriebssystem wesentlich stärker in der Wahl von Prozessorfrequenzen in aktuellen und zukünftigen leistungslimitierten Systemen involviert sein muss. Zudem zeigen wir eine Reihe von möglichen Verbesserungen existierender Prozessorarchitekturen auf, die eine noch effektivere Reduktion des Einflusses von Effekten wie Remote AVX Overhead ermöglichen würden.

## Contents

| Ab | stract | :       |                                         | iii |

|----|--------|---------|-----------------------------------------|-----|

| Zu | samm   | enfassi | ung                                     | v   |

| 1  | Intro  | ductio  | n                                       | 1   |

|    | 1.1    | Scope   |                                         | 3   |

|    | 1.2    | Contri  | ibutions                                | 4   |

|    | 1.3    | Studer  | nt Theses and Publications              | 4   |

|    | 1.4    | Docur   | nent Structure                          | 6   |

| 2  | Back   | ground  | I: Power-Limited Computing              | 9   |

|    | 2.1    | Transi  | istor Scaling and Processor Design      | 9   |

|    |        | 2.1.1   | Pipelining and Out-Of-Order Processors  | 10  |

|    |        | 2.1.2   |                                         | 15  |

|    | 2.2    | CMOS    | S Power Consumption                     | 16  |

|    |        | 2.2.1   | Dynamic Voltage and Frequency Scaling   | 17  |

|    |        | 2.2.2   |                                         | 18  |

|    |        | 2.2.3   |                                         | 21  |

|    | 2.3    | Denna   | ard Scaling and Leakage-Limited Scaling | 23  |

|    |        | 2.3.1   | Power-Limited DVFS                      | 25  |

|    |        | 2.3.2   | Energy-Efficient Accelerators           | 27  |

|    |        | 2.3.3   | Heterogeneous Systems                   | 29  |

| 3  | Perf   | ormanc  | e Implications of AVX2 and AVX-512      | 33  |

|    | 3.1    | Local   | Impact on Performance and Power         | 34  |

|    | 3.2    | Freque  | ency Management for AVX2 and AVX-512    | 36  |

|    |        | 3.2.1   | AVX2 and AVX-512 Frequency Levels       | 37  |

|    |        | 3.2.2   | Frequency Reduction                     | 38  |

|    |        | 3.2.3   | Delayed Frequency Increase              | 42  |

|    | 3.3    | AVX (   |                                         | 44  |

|    |        | 3.3.1   | Local AVX Overhead                      | 44  |

|    |        | 3.3.2   | Remote AVX Overhead                     | 46  |

|    |        | 3.3.3   | Implications of Frequency Change Delays | 47  |

|    |        | 3.3.4   |                                         | 48  |

|    |        | 3.3.5   |                                         | 48  |

|    |        | 3.3.6   |                                         | 52  |

|    | 3.4    | Inform  |                                         | 52  |

|    | 3.5    | Applic  | cability to Other Microarchitectures    | 55  |

| 4.1Existing Profilers584.2Detecting Unnecessary Frequency Reduction604.2.1Frequency Reduction Sampling614.3DVFS Performance Prediction Model644.3.1Existing Models654.3.2Stall Cycle Counting for Intel Skylake-SP684.4Source of Overhead704.5Evaluation714.5.1Profiler Accuracy724.5.2Impact of Instrumentation Perturbation734.5.3Profiler Overhead744.5.4Overhead Source Analysis764.6Discussion774.6.1Optimized Frequency Reduction Sampling784.6.2Proposed Hardware Changes795Viability of Improved DVFS Policies835.1Parallels to Dynamic Power Management845.2Characterization of AVX Frequency Changes875.2.3Break-Even Time of Frequency Changes915.3Simulating Improved Prequency Scaling925.4Discussion966Separating AVX-512 and Non-AVX-512 Code996.1Existing Mitigation Techniques1006.2.2Number of AVX-512 Code1066.3.3Detecting Non-AVX-512 Code1126.3.1Choice of Scheduler1126.3.2Tripled Run Queues1136.3.2Tripled Run Queues1136.3.3AVX-512 Phases1216.5.4Estimation of Effectiveness                                                                                                                                                                                                                                                                      | 4 | Run  | ime Profiling of AVX2 and AVX-512 Overhead        | 7 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------|---------------------------------------------------|---|

| 4.2.1       Frequency Reduction Sampling       61         4.3       DVFS Performance Prediction Model       64         4.3.1       Existing Models       65         4.3.2       Stall Cycle Counting for Intel Skylake-SP       68         4.4       Source of Overhead       70         4.5       Evaluation       71         4.5.1       Profiler Accuracy       72         4.5.2       Impact of Instrumentation Perturbation       73         4.5.3       Profiler Overhead       74         4.5.4       Overhead Source Analysis       76         4.6       Discussion       77         4.6.1       Optimized Frequency Reduction Sampling       78         4.6.2       Proposed Hardware Changes       83         5.1       Parallels to Dynamic Power Management       84         5.2       Characterization of AVX Frequency Changes       87         5.2.1       Frequency Reduction Overhead       87         5.2.2       Frequency Boost Overhead       89         5.3       Simulating Improved Frequency Changes       91         5.3       Simulating Improved Frequency Changes       91         5.3       Simulating Improved Frequency Changes       99 <t< td=""><td></td><td>4.1</td><td>Existing Profilers</td><td>8</td></t<>                           |   | 4.1  | Existing Profilers                                | 8 |

| 4.3       DVFS Performance Prediction Model       64         4.3.1       Existing Models       65         4.3.2       Stall Cycle Counting for Intel Skylake-SP       68         4.4       Source of Overhead       70         4.5       Evaluation       71         4.5.1       Profiler Accuracy       72         4.5.2       Impact of Instrumentation Perturbation       73         4.5.3       Profiler Overhead       74         4.5.4       Overhead Source Analysis       76         4.6       Discussion       77         4.6.1       Optimized Frequency Reduction Sampling       78         4.6.2       Proposed Hardware Changes       79         5       Viability of Improved DVFS Policies       83         5.1       Parallels to Dynamic Power Management       84         5.2       Characterization of AVX Frequency Changes       87         5.2.1       Frequency Boost Overhead       87         5.2.2       Frequency Boost Overhead       89         5.3       Simulating Improved Frequency Scaling       92         5.4       Discussion       96         6       Separating AVX-512 and Non-AVX-512 Applications       102         6.2 <t< td=""><td></td><td>4.2</td><td>Detecting Unnecessary Frequency Reduction</td><td>0</td></t<>           |   | 4.2  | Detecting Unnecessary Frequency Reduction         | 0 |

| 4.3.1       Existing Models       65         4.3.2       Stall Cycle Counting for Intel Skylake-SP       68         4.4       Source of Overhead       70         4.5       Evaluation       71         4.5.1       Profiler Accuracy       72         4.5.2       Impact of Instrumentation Perturbation       73         4.5.3       Profiler Overhead       74         4.5.4       Overhead Source Analysis       76         4.6       Discussion       77         4.6.1       Optimized Frequency Reduction Sampling       78         4.6.2       Proposed Hardware Changes       79         5       Viability of Improved DVFS Policies       83         5.1       Parallels to Dynamic Power Management       84         5.2       Characterization of AVX Frequency Changes       87         5.2.1       Frequency Reduction Overhead       89         5.2.3       Break-Even Time of Frequency Changes       91         5.3       Simulating Improved Frequency Scaling       92         5.4       Discussion       96         6       Separating AVX-512 and Non-AVX-512 Code       99         6.1       Existing Mitigation Techniques       100         6.2.1                                                                                                     |   |      | 4.2.1 Frequency Reduction Sampling                | 1 |

| 4.3.2Stall Cycle Counting for Intel Skylake-SP684.4Source of Overhead704.5Evaluation714.5.1Profiler Accuracy724.5.2Impact of Instrumentation Perturbation734.5.3Profiler Overhead744.5.4Overhead Source Analysis764.6Discussion774.6.1Optimized Frequency Reduction Sampling784.6.2Proposed Hardware Changes795Viability of Improved DVFS Policies835.1Parallels to Dynamic Power Management845.2Characterization of AVX Frequency Changes875.2.1Frequency Reduction Overhead875.2.2Frequency Boost Overhead895.2.3Break-Even Time of Frequency Changes915.4Discussion966Separating AVX-512 and Non-AVX-512 Code996.1Existing Mitigation Techniques1006.2Core Specialization for AVX-512 Applications1026.3.1Choice of Scheduler1126.3.2Directing NOn-AVX-512 Code1106.3AVX-512 Frequenes1136.3.3AVX-512 Reduce1106.5Evaluation1176.5.1Effectiveness1156.5Evaluation1176.5.1Effectiveness1156.5Evaluation of Effectiveness1216.5.3Short Non-AVX-512 Phases1216.5.4Estimation                                                                                                                                                                                                                                                                                                 |   | 4.3  | DVFS Performance Prediction Model    6            | 4 |

| 4.4       Source of Overhead       70         4.5       Evaluation       71         4.5.1       Profiler Accuracy       72         4.5.2       Impact of Instrumentation Perturbation       73         4.5.3       Profiler Overhead       74         4.5.4       Overhead Source Analysis       76         4.6       Discussion       77         4.6.1       Optimized Frequency Reduction Sampling       78         4.6.2       Proposed Hardware Changes       79         5       Viability of Improved DVFS Policies       83         5.1       Parallels to Dynamic Power Management       84         5.2       Frequency Reduction Overhead       87         5.2.1       Frequency Reduction Overhead       87         5.2.2       Frequency Robot Overhead       87         5.2.3       Break-Even Time of Frequency Changes       91         5.3       Simulating Improved Frequency Scaling       92         5.4       Discussion       96         6       Separating AVX-512 and Non-AVX-512 Code       99         6.1       Existing Mitigation Techniques       100         6.2.1       Scheduling Policy       104         6.2.2       Number of AVX-512                                                                                                        |   |      | 4.3.1 Existing Models                             | 5 |

| 4.5       Evaluation       71         4.5.1       Profiler Accuracy       72         4.5.2       Impact of Instrumentation Perturbation       73         4.5.3       Profiler Overhead       74         4.5.4       Overhead Source Analysis       76         4.6       Discussion       77         4.6.1       Optimized Frequency Reduction Sampling       78         4.6.2       Proposed Hardware Changes       79         5       Viability of Improved DVFS Policies       83         5.1       Parallels to Dynamic Power Management       84         5.2       Characterization of AVX Frequency Changes       87         5.2.1       Frequency Reduction Overhead       87         5.2.2       Frequency Robot Overhead       89         5.2.3       Break-Even Time of Frequency Changes       91         5.3       Simulating Improved Frequency Scaling       92         5.4       Discussion       96         6       Separating AVX-512 and Non-AVX-512 Code       99         6.1       Existing Mitigation Techniques       100         6.2       Core Specialization for AVX-512 Code       107         6.2.1       Scheduling Policy       104         6.2.2 </td <td></td> <td></td> <td>4.3.2 Stall Cycle Counting for Intel Skylake-SP 6</td> <td>8</td> |   |      | 4.3.2 Stall Cycle Counting for Intel Skylake-SP 6 | 8 |

| 4.5.1       Profiler Accuracy       72         4.5.2       Impact of Instrumentation Perturbation       73         4.5.3       Profiler Overhead       74         4.5.4       Overhead Source Analysis       76         4.6       Discussion       77         4.6.1       Optimized Frequency Reduction Sampling       78         4.6.2       Proposed Hardware Changes       79         5       Viability of Improved DVFS Policies       83         5.1       Parallels to Dynamic Power Management       84         5.2       Characterization of AVX Frequency Changes       87         5.2.1       Frequency Reduction Overhead       89         5.2.3       Break-Even Time of Frequency Changes       91         5.3       Simulating Improved Frequency Scaling       92         5.4       Discussion       96         6       Separating AVX-512 and Non-AVX-512 Code       99         6.1       Existing Mitigation Techniques       100         6.2       Core Specialization for AVX-512 Code       99         6.1       Existing Mitigation Techniques       100         6.2.1       Scheduling Policy       104         6.2.2       Number of AVX-512 Code       107 <t< td=""><td></td><td>4.4</td><td>Source of Overhead</td><td>0</td></t<>                 |   | 4.4  | Source of Overhead                                | 0 |

| 4.5.2       Impact of Instrumentation Perturbation       73         4.5.3       Profiler Overhead       74         4.5.4       Overhead Source Analysis       76         4.6       Discussion       77         4.6.1       Optimized Frequency Reduction Sampling       78         4.6.2       Proposed Hardware Changes       79         5       Viability of Improved DVFS Policies       83         5.1       Parallels to Dynamic Power Management       84         5.2       Characterization of AVX Frequency Changes       87         5.2.1       Frequency Reduction Overhead       87         5.2.2       Frequency Boost Overhead       89         5.2.3       Break-Even Time of Frequency Changes       91         5.3       Simulating Improved Frequency Scaling       92         5.4       Discussion       96         6       Separating AVX-512 and Non-AVX-512 Code       99         6.1       Existing Mitigation Techniques       100         6.2       Overber of AVX-512 Code       107         6.2.1       Scheduling Policy       104         6.2.2       Number of AVX-512 Code       107         6.3.1       Implementation       112         6.3.2 </td <td></td> <td>4.5</td> <td>Evaluation</td> <td>1</td>                                     |   | 4.5  | Evaluation                                        | 1 |

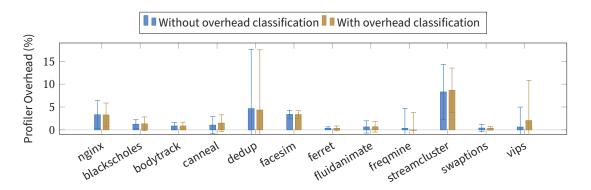

| 4.5.3       Profiler Overhead       74         4.5.4       Overhead Source Analysis       76         4.6       Discussion       77         4.6.1       Optimized Frequency Reduction Sampling       78         4.6.2       Proposed Hardware Changes       79         5       Viability of Improved DVFS Policies       83         5.1       Parallels to Dynamic Power Management       84         5.2       Characterization of AVX Frequency Changes       87         5.2.1       Frequency Reduction Overhead       87         5.2.2       Frequency Boost Overhead       89         5.2.3       Break-Even Time of Frequency Changes       91         5.3       Simulating Improved Frequency Scaling       92         5.4       Discussion       96         6       Separating AVX-512 and Non-AVX-512 Code       99         6.1       Existing Mitigation Techniques       100         6.2       Core Specialization for AVX-512 Code       99         6.1       Existing Mitigation Techniques       100         6.2.1       Scheduling Policy       104         6.2.2       Number of AVX-512 Code       107         6.2.4       Detecting Non-AVX-512 Code       107                                                                                               |   |      | 4.5.1 Profiler Accuracy                           | 2 |

| 4.5.4       Overhead Source Analysis       76         4.6       Discussion       77         4.6.1       Optimized Frequency Reduction Sampling       78         4.6.2       Proposed Hardware Changes       79         5       Viability of Improved DVFS Policies       83         5.1       Parallels to Dynamic Power Management       84         5.2       Characterization of AVX Frequency Changes       87         5.2.1       Frequency Reduction Overhead       87         5.2.2       Frequency Boost Overhead       89         5.2.3       Break-Even Time of Frequency Changes       91         5.3       Simulating Improved Frequency Scaling       92         5.4       Discussion       96         6       Separating AVX-512 and Non-AVX-512 Code       99         6.1       Existing Mitigation Techniques       100         6.2       Core Specialization for AVX-512 Code       99         6.1       Existing Mitigation Techniques       102         6.2.1       Scheduling Policy       104         6.2.2       Number of AVX-512 Code       107         6.2.4       Detecting Non-AVX-512 Code       101         6.3       Implementation       112                                                                                                   |   |      | 4.5.2 Impact of Instrumentation Perturbation      | 3 |

| 4.6Discussion774.6.1Optimized Frequency Reduction Sampling784.6.2Proposed Hardware Changes795Viability of Improved DVFS Policies835.1Parallels to Dynamic Power Management845.2Characterization of AVX Frequency Changes875.2.1Frequency Reduction Overhead875.2.2Frequency Boost Overhead895.2.3Break-Even Time of Frequency Changes915.3Simulating Improved Frequency Scaling925.4Discussion966Separating AVX-512 and Non-AVX-512 Code996.1Existing Mitigation Techniques1006.2Core Specialization for AVX-512 Applications1026.2.1Scheduling Policy1046.2.2Number of AVX-512 Code1076.2.4Detecting AVX-512 Code1076.3.1Choice of Scheduler1126.3.2Tripled Run Queues1136.3.3AVX-512 Feature Detection1146.4Estimation of Effectiveness1176.5.2Overhead1216.5.3Short Non-AVX-512 Phases1216.5.4Estimation of Effectiveness1226.6Discussion123                                                                                                                                                                                                                                                                                                                                                                                                                              |   |      | 4.5.3 Profiler Overhead                           | 4 |

| 4.6.1       Optimized Frequency Reduction Sampling       78         4.6.2       Proposed Hardware Changes       79         5       Viability of Improved DVFS Policies       83         5.1       Parallels to Dynamic Power Management       84         5.2       Characterization of AVX Frequency Changes       87         5.2.1       Frequency Reduction Overhead       87         5.2.2       Frequency Boost Overhead       89         5.2.3       Break-Even Time of Frequency Changes       91         5.3       Simulating Improved Frequency Scaling       92         5.4       Discussion       96         6       Separating AVX-512 and Non-AVX-512 Code       99         6.1       Existing Mitigation Techniques       100         6.2       Core Specialization for AVX-512 Applications       102         6.2.1       Scheduling Policy       104         6.2.2       Number of AVX-512 Code       107         6.2.3       Detecting AVX-512 Code       107         6.2.4       Detecting Non-AVX-512 Code       107         6.3.1       Choice of Scheduler       112         6.3.2       Tripled Run Queues       113         6.3.3       AVX-512 Feature Detection       114                                                                            |   |      | 4.5.4 Overhead Source Analysis                    | 6 |

| 4.6.2       Proposed Hardware Changes       79         5       Viability of Improved DVFS Policies       83         5.1       Parallels to Dynamic Power Management       84         5.2       Characterization of AVX Frequency Changes       87         5.2.1       Frequency Boost Overhead       87         5.2.2       Frequency Boost Overhead       89         5.2.3       Break-Even Time of Frequency Changes       91         5.3       Simulating Improved Frequency Scaling       92         5.4       Discussion       96         6       Separating AVX-512 and Non-AVX-512 Code       99         6.1       Existing Mitigation Techniques       100         6.2       Core Specialization for AVX-512 Applications       102         6.2.1       Scheduling Policy       104         6.2.2       Number of AVX-512 Code       107         6.2.3       Detecting Non-AVX-512 Code       101         6.3       Implementation       112         6.3.1       Choice of Scheduler       112         6.3.2       Tripled Run Queues       113         6.3.3       AVX-512 Feature Detection       114         6.4       Estimation of Effectiveness       117 <td< td=""><td></td><td>4.6</td><td>Discussion</td><td>7</td></td<>                                  |   | 4.6  | Discussion                                        | 7 |

| 5       Viability of Improved DVFS Policies       83         5.1       Parallels to Dynamic Power Management       84         5.2       Characterization of AVX Frequency Changes       87         5.2.1       Frequency Reduction Overhead       87         5.2.2       Frequency Boost Overhead       89         5.2.3       Break-Even Time of Frequency Changes       91         5.3       Simulating Improved Frequency Scaling       92         5.4       Discussion       96         6       Separating AVX-512 and Non-AVX-512 Code       99         6.1       Existing Mitigation Techniques       100         6.2       Core Specialization for AVX-512 Code       99         6.1.1       Scheduling Policy       104         6.2.2       Number of AVX-512 Cores       106         6.2.3       Detecting NOT-AVX-512 Code       107         6.2.4       Detecting NOT-AVX-512 Code       110         6.3       Implementation       112         6.3.1       Choice of Scheduler       112         6.3.2       Tripled Run Queues       113         6.3.3       AVX-512 Feature Detection       114         6.4       Estimation of Effectiveness       117         6                                                                                              |   |      | 4.6.1 Optimized Frequency Reduction Sampling      | 8 |

| 5.1       Parallels to Dynamic Power Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   |      | 4.6.2    Proposed Hardware Changes    7           | 9 |

| 5.1       Parallels to Dynamic Power Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5 | Viab | lity of Improved DVFS Policies                    | 3 |

| 5.2       Characterization of AVX Frequency Changes       87         5.2.1       Frequency Reduction Overhead       87         5.2.2       Frequency Boost Overhead       89         5.2.3       Break-Even Time of Frequency Changes       91         5.3       Simulating Improved Frequency Scaling       92         5.4       Discussion       96         6       Separating AVX-512 and Non-AVX-512 Code       99         6.1       Existing Mitigation Techniques       100         6.2       Core Specialization for AVX-512 Code       99         6.1       Existing Mitigation Techniques       102         6.2.1       Scheduling Policy       104         6.2.2       Number of AVX-512 Cores       106         6.2.3       Detecting Non-AVX-512 Code       107         6.2.4       Detecting Non-AVX-512 Code       101         6.3       Inplementation       112         6.3.1       Choice of Scheduler       112         6.3.2       Tripled Run Queues       113         6.3.3       AVX-512 Feature Detection       114         6.4       Estimation of Effectiveness       117         6.5.1       Effectiveness       117         6.5.2       Ove                                                                                                       | Ŭ |      |                                                   |   |

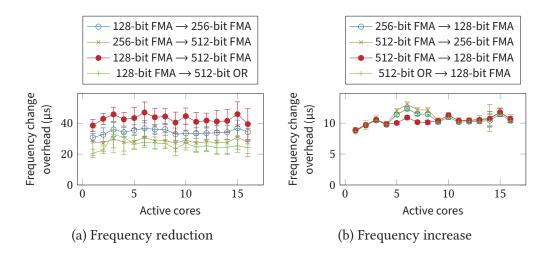

| 5.2.1       Frequency Reduction Overhead       87         5.2.2       Frequency Boost Overhead       89         5.2.3       Break-Even Time of Frequency Changes       91         5.3       Simulating Improved Frequency Scaling       92         5.4       Discussion       96         6       Separating AVX-512 and Non-AVX-512 Code       99         6.1       Existing Mitigation Techniques       100         6.2       Core Specialization for AVX-512 Applications       102         6.2.1       Scheduling Policy       104         6.2.2       Number of AVX-512 Cores       106         6.2.3       Detecting AVX-512 Code       107         6.2.4       Detecting Non-AVX-512 Code       110         6.3       Implementation       112         6.3.1       Choice of Scheduler       112         6.3.2       Tripled Run Queues       113         6.3.3       AVX-512 Feature Detection       114         6.4       Estimation of Effectiveness       117         6.5.1       Effectiveness       117         6.5.2       Overhead       121         6.5.3       Short Non-AVX-512 Phases       121         6.5.4       Estimation of Effectiveness                                                                                                            |   |      |                                                   |   |

| 5.2.2       Frequency Boost Overhead       89         5.2.3       Break-Even Time of Frequency Changes       91         5.3       Simulating Improved Frequency Scaling       92         5.4       Discussion       96         6       Separating AVX-512 and Non-AVX-512 Code       99         6.1       Existing Mitigation Techniques       100         6.2       Core Specialization for AVX-512 Applications       102         6.2.1       Scheduling Policy       104         6.2.2       Number of AVX-512 Cores       106         6.2.3       Detecting Non-AVX-512 Code       107         6.2.4       Detecting Non-AVX-512 Code       107         6.3.1       Choice of Scheduler       112         6.3.2       Tripled Run Queues       113         6.3.3       AVX-512 Feature Detection       114         6.4       Estimation of Effectiveness       117         6.5.1       Effectiveness       117         6.5.2       Overhead       121         6.5.3       Short Non-AVX-512 Phases       121         6.5.4       Estimation of Effectiveness       122         6.6       Discussion       123                                                                                                                                                            |   | 5.2  |                                                   |   |

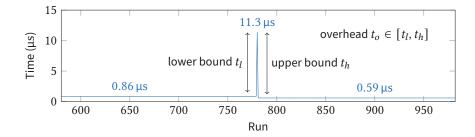

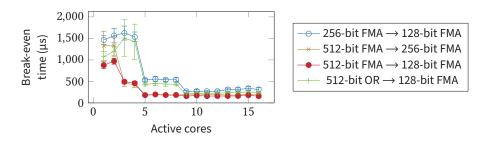

| 5.2.3       Break-Even Time of Frequency Changes       91         5.3       Simulating Improved Frequency Scaling       92         5.4       Discussion       96         6       Separating AVX-512 and Non-AVX-512 Code       99         6.1       Existing Mitigation Techniques       100         6.2       Core Specialization for AVX-512 Applications       102         6.2.1       Scheduling Policy       104         6.2.2       Number of AVX-512 Cores       106         6.2.3       Detecting AVX-512 Code       107         6.2.4       Detecting Non-AVX-512 Code       107         6.3.3       Detecting Non-AVX-512 Code       110         6.3       Implementation       112         6.3.1       Choice of Scheduler       112         6.3.2       Tripled Run Queues       113         6.3.3       AVX-512 Feature Detection       114         6.4       Estimation of Effectiveness       117         6.5.1       Effectiveness       117         6.5.2       Overhead       121         6.5.3       Short Non-AVX-512 Phases       121         6.5.4       Estimation of Effectiveness       122         6.6       Discussion       123 </td <td></td> <td></td> <td></td> <td></td>                                                                     |   |      |                                                   |   |

| 5.3       Simulating Improved Frequency Scaling       92         5.4       Discussion       96         6       Separating AVX-512 and Non-AVX-512 Code       99         6.1       Existing Mitigation Techniques       100         6.2       Core Specialization for AVX-512 Applications       102         6.2.1       Scheduling Policy       104         6.2.2       Number of AVX-512 Cores       106         6.2.3       Detecting AVX-512 Code       107         6.2.4       Detecting Non-AVX-512 Code       107         6.3.1       Choice of Scheduler       112         6.3.1       Choice of Scheduler       112         6.3.2       Tripled Run Queues       113         6.3.3       AVX-512 Feature Detection       114         6.4       Estimation of Effectiveness       117         6.5.1       Effectiveness       117         6.5.2       Overhead       121         6.5.3       Short Non-AVX-512 Phases       121         6.5.4       Estimation of Effectiveness       122         6.6       Discussion       123                                                                                                                                                                                                                                      |   |      |                                                   |   |

| 5.4       Discussion       96         6       Separating AVX-512 and Non-AVX-512 Code       99         6.1       Existing Mitigation Techniques       100         6.2       Core Specialization for AVX-512 Applications       102         6.2.1       Scheduling Policy       104         6.2.2       Number of AVX-512 Cores       106         6.2.3       Detecting AVX-512 Code       107         6.2.4       Detecting Non-AVX-512 Code       107         6.2.4       Detecting Non-AVX-512 Code       110         6.3       Implementation       112         6.3.1       Choice of Scheduler       112         6.3.2       Tripled Run Queues       113         6.3.3       AVX-512 Feature Detection       114         6.4       Estimation of Effectiveness       115         6.5       Evaluation       117         6.5.1       Effectiveness       117         6.5.2       Overhead       121         6.5.3       Short Non-AVX-512 Phases       121         6.5.4       Estimation of Effectiveness       122         6.6       Discussion       123                                                                                                                                                                                                              |   | 53   |                                                   |   |

| 6.1       Existing Mitigation Techniques       100         6.2       Core Specialization for AVX-512 Applications       102         6.2.1       Scheduling Policy       104         6.2.2       Number of AVX-512 Cores       106         6.2.3       Detecting AVX-512 Code       107         6.2.4       Detecting Non-AVX-512 Code       107         6.3       Implementation       112         6.3.1       Choice of Scheduler       112         6.3.2       Tripled Run Queues       113         6.3.3       AVX-512 Feature Detection       114         6.4       Estimation of Effectiveness       115         6.5       Evaluation       117         6.5.1       Effectiveness       117         6.5.2       Overhead       121         6.5.3       Short Non-AVX-512 Phases       121         6.5.4       Estimation of Effectiveness       121         6.5.4       Estimation of Effectiveness       122         6.6       Discussion       123                                                                                                                                                                                                                                                                                                                    |   |      |                                                   |   |

| 6.1       Existing Mitigation Techniques       100         6.2       Core Specialization for AVX-512 Applications       102         6.2.1       Scheduling Policy       104         6.2.2       Number of AVX-512 Cores       106         6.2.3       Detecting AVX-512 Code       107         6.2.4       Detecting Non-AVX-512 Code       107         6.3       Implementation       112         6.3.1       Choice of Scheduler       112         6.3.2       Tripled Run Queues       113         6.3.3       AVX-512 Feature Detection       114         6.4       Estimation of Effectiveness       115         6.5       Evaluation       117         6.5.1       Effectiveness       117         6.5.2       Overhead       121         6.5.3       Short Non-AVX-512 Phases       121         6.5.4       Estimation of Effectiveness       121         6.5.4       Estimation of Effectiveness       122         6.6       Discussion       123                                                                                                                                                                                                                                                                                                                    |   | -    |                                                   | • |

| 6.2       Core Specialization for AVX-512 Applications       102         6.2.1       Scheduling Policy       104         6.2.2       Number of AVX-512 Cores       106         6.2.3       Detecting AVX-512 Code       107         6.2.4       Detecting Non-AVX-512 Code       107         6.3       Implementation       112         6.3.1       Choice of Scheduler       112         6.3.2       Tripled Run Queues       113         6.3.3       AVX-512 Feature Detection       114         6.4       Estimation of Effectiveness       115         6.5       Evaluation       117         6.5.1       Effectiveness       117         6.5.2       Overhead       121         6.5.3       Short Non-AVX-512 Phases       121         6.5.4       Estimation of Effectiveness       122         6.6       Discussion       123                                                                                                                                                                                                                                                                                                                                                                                                                                         | 6 | -    | -                                                 |   |

| 6.2.1       Scheduling Policy       104         6.2.2       Number of AVX-512 Cores       106         6.2.3       Detecting AVX-512 Code       107         6.2.4       Detecting Non-AVX-512 Code       107         6.3       Implementation       112         6.3.1       Choice of Scheduler       112         6.3.2       Tripled Run Queues       113         6.3.3       AVX-512 Feature Detection       114         6.4       Estimation of Effectiveness       115         6.5       Evaluation       117         6.5.1       Effectiveness       117         6.5.2       Overhead       121         6.5.3       Short Non-AVX-512 Phases       121         6.5.4       Estimation of Effectiveness       122         6.6       Discussion       123                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |      |                                                   |   |

| 6.2.2       Number of AVX-512 Cores       106         6.2.3       Detecting AVX-512 Code       107         6.2.4       Detecting Non-AVX-512 Code       110         6.3       Implementation       112         6.3.1       Choice of Scheduler       112         6.3.2       Tripled Run Queues       113         6.3.3       AVX-512 Feature Detection       114         6.4       Estimation of Effectiveness       115         6.5       Evaluation       117         6.5.1       Effectiveness       117         6.5.2       Overhead       121         6.5.3       Short Non-AVX-512 Phases       121         6.5.4       Estimation of Effectiveness       122         6.6       Discussion       123                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   | 0.2  |                                                   |   |

| 6.2.3       Detecting AVX-512 Code       107         6.2.4       Detecting Non-AVX-512 Code       110         6.3       Implementation       112         6.3.1       Choice of Scheduler       112         6.3.2       Tripled Run Queues       113         6.3.3       AVX-512 Feature Detection       114         6.4       Estimation of Effectiveness       115         6.5       Evaluation       117         6.5.1       Effectiveness       117         6.5.2       Overhead       121         6.5.3       Short Non-AVX-512 Phases       121         6.5.4       Estimation of Effectiveness       121         6.5.4       Estimation of Effectiveness       121         6.6       Discussion       122                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   |      |                                                   |   |

| 6.2.4       Detecting Non-AVX-512 Code       110         6.3       Implementation       112         6.3.1       Choice of Scheduler       112         6.3.2       Tripled Run Queues       113         6.3.3       AVX-512 Feature Detection       114         6.4       Estimation of Effectiveness       115         6.5       Evaluation       117         6.5.1       Effectiveness       117         6.5.2       Overhead       121         6.5.3       Short Non-AVX-512 Phases       121         6.5.4       Estimation of Effectiveness       121         6.5.4       Estimation of Effectiveness       121         6.6       Discussion       122                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |      |                                                   |   |

| 6.3Implementation1126.3.1Choice of Scheduler1126.3.2Tripled Run Queues1136.3.3AVX-512 Feature Detection1146.4Estimation of Effectiveness1156.5Evaluation1176.5.1Effectiveness1176.5.2Overhead1216.5.3Short Non-AVX-512 Phases1216.5.4Estimation of Effectiveness1226.6Discussion123                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |      |                                                   |   |

| 6.3.1Choice of Scheduler1126.3.2Tripled Run Queues1136.3.3AVX-512 Feature Detection1146.4Estimation of Effectiveness1156.5Evaluation1176.5.1Effectiveness1176.5.2Overhead1216.5.3Short Non-AVX-512 Phases1216.5.4Estimation of Effectiveness1226.6Discussion123                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   | 62   |                                                   |   |

| 6.3.2       Tripled Run Queues       113         6.3.3       AVX-512 Feature Detection       114         6.4       Estimation of Effectiveness       115         6.5       Evaluation       117         6.5.1       Effectiveness       117         6.5.2       Overhead       121         6.5.3       Short Non-AVX-512 Phases       121         6.5.4       Estimation of Effectiveness       122         6.6       Discussion       123                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   | 0.5  | 1                                                 |   |

| 6.3.3 AVX-512 Feature Detection1146.4 Estimation of Effectiveness1156.5 Evaluation1176.5.1 Effectiveness1176.5.2 Overhead1216.5.3 Short Non-AVX-512 Phases1216.5.4 Estimation of Effectiveness1226.6 Discussion123                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |      |                                                   |   |

| 6.4       Estimation of Effectiveness       115         6.5       Evaluation       117         6.5.1       Effectiveness       117         6.5.2       Overhead       121         6.5.3       Short Non-AVX-512 Phases       121         6.5.4       Estimation of Effectiveness       122         6.6       Discussion       123                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |      | 1                                                 |   |

| 6.5       Evaluation       117         6.5.1       Effectiveness       117         6.5.2       Overhead       121         6.5.3       Short Non-AVX-512 Phases       121         6.5.4       Estimation of Effectiveness       122         6.6       Discussion       123                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   | 6.4  |                                                   |   |

| 6.5.1       Effectiveness       117         6.5.2       Overhead       121         6.5.3       Short Non-AVX-512 Phases       121         6.5.4       Estimation of Effectiveness       122         6.6       Discussion       123                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |      |                                                   |   |

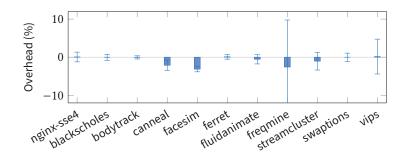

| 6.5.2       Overhead       121         6.5.3       Short Non-AVX-512 Phases       121         6.5.4       Estimation of Effectiveness       122         6.6       Discussion       123                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   | 0.5  |                                                   |   |

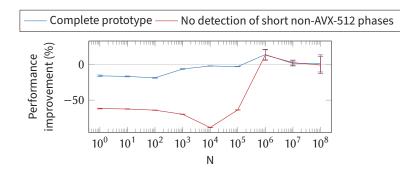

| 6.5.3       Short Non-AVX-512 Phases       121         6.5.4       Estimation of Effectiveness       122         6.6       Discussion       123                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   |      |                                                   |   |

| 6.5.4       Estimation of Effectiveness       122         6.6       Discussion       123                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |      |                                                   |   |

| 6.6 Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |      |                                                   |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   | 6.6  |                                                   |   |

| 6.6.1 Reducing Migration Overnead                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   | 0.0  | 6.6.1    Reducing Migration Overhead    12        |   |

|     |         | 6.6.2     | NUMA Support                                           | 124 |

|-----|---------|-----------|--------------------------------------------------------|-----|

|     |         | 6.6.3     | Imprecise Detection of Power-Intensive Code            | 124 |

|     |         | 6.6.4     | Proposed Hardware Changes                              | 125 |

| 7   | Sche    | eduling f | for Improved Performance Isolation                     | 127 |

|     | 7.1     | Fairnes   | ss and Performance Isolation                           | 128 |

|     | 7.2     |           | ifying AVX2 and AVX-512 Performance Isolation Problems | 130 |

|     | 7.3     | Metric    | s for Performance Isolation                            | 131 |

|     | 7.4     | Modifi    | ed CPU Time Accounting                                 | 134 |

|     |         | 7.4.1     | Attribution of Frequency Changes                       | 134 |

|     |         | 7.4.2     | Estimating Remote AVX Overhead                         | 135 |

|     |         | 7.4.3     | Frequency Reduction Compensation                       | 138 |

|     | 7.5     | Thread    | d Mobility                                             | 139 |

|     | 7.6     |           | tion                                                   | 141 |

|     |         | 7.6.1     | Setup                                                  | 142 |

|     |         | 7.6.2     | Performance Isolation                                  | 142 |

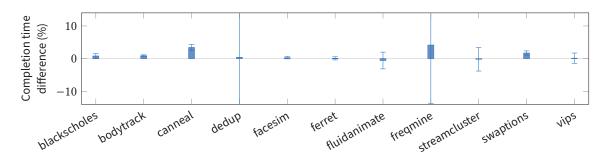

|     |         | 7.6.3     | Overhead                                               | 144 |

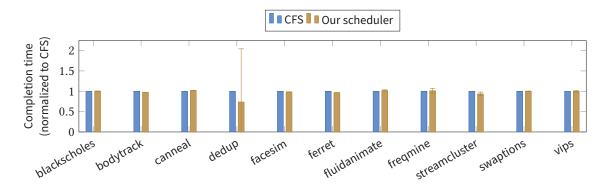

|     |         | 7.6.4     | Comparison with CFS                                    | 145 |

|     | 7.7     | Discus    | sion                                                   | 146 |

|     |         | 7.7.1     | Attribution of Remote AVX Overhead                     | 146 |

|     |         | 7.7.2     | Throttle Cycles                                        | 147 |

|     |         | 7.7.3     | Compatibility with Profiling Tools                     | 147 |

|     |         | 7.7.4     | NUMA-Support                                           | 148 |

| 8   | Con     | clusion   |                                                        | 149 |

|     | 8.1     | Future    | Work                                                   | 150 |

| Bil | bliogr  | aphy .    |                                                        | 151 |

| Lis | st of F | igures .  |                                                        | 169 |

| Lis | st of T | ables .   |                                                        | 171 |

| Lis | stings  |           |                                                        | 173 |

## **1** Introduction

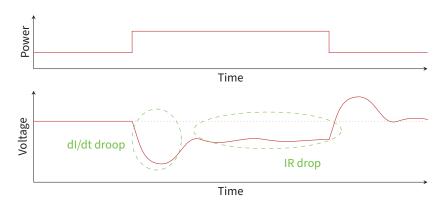

For a long time, technical progress in the area of semiconductor manufacturing meant that the power density of processors at full load remained constant despite rising CPU frequencies and exponentially increasing transistor density [64]. In recent years, this trend stopped as CPU manufacturers were unable to further reduce operating voltages – such voltage reduction had been central to the required continuous improvements to power efficiency [243]. Increasing power densities soon reached the limits of economically viable cooling solutions, requiring CPU manufacturers to reduce operating frequencies or to leave parts of the chip inactive. In this scenario, the desire of CPU manufacturers to maximize performance has led to the introduction of a range of techniques to fully exploit the available power budget. For example, overall power dissipation is reduced when CPU cores are disabled. Techniques such as Intel Turbo Boost [117] use the resulting thermal headroom to increase CPU frequencies whenever some CPU cores are inactive.

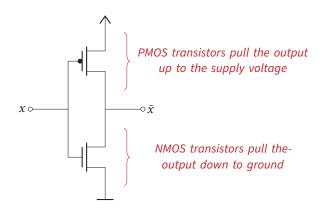

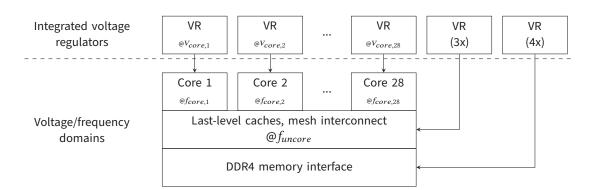

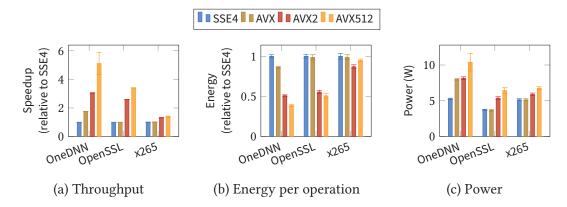

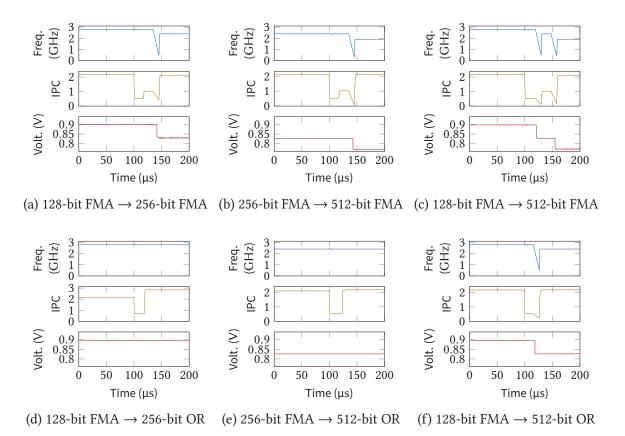

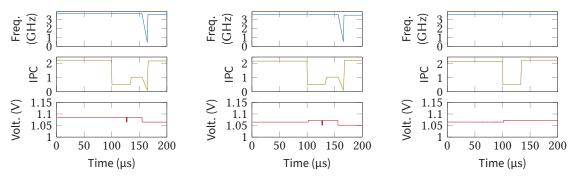

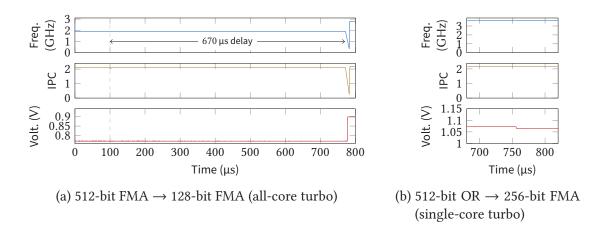

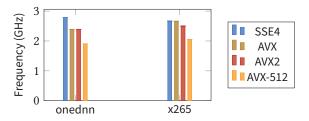

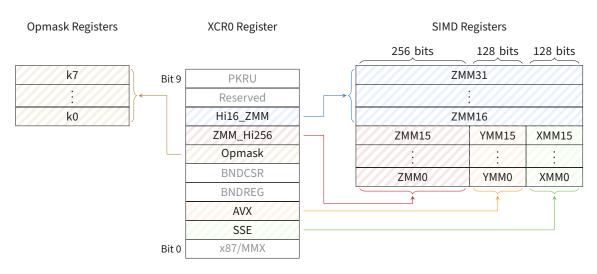

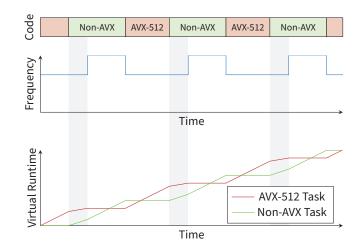

Similarly, power dissipation depends on the energy consumption of individual instructions. To maximize performance for all types of code, a processor can execute code consisting of only simple instructions at a higher frequency than code involving energy-intensive complex instructions. The first widely available processors showing such behavior were those using the Intel Haswell, Broadwell, and Skylake microarchitecture which reduced their operating frequencies when executing code using AVX2 and AVX-512 instructions [76, 77, 213]. AVX2 and AVX-512 are single-instruction multiple-data (SIMD) instruction set extensions operating on large 256-bit and 512-bit vector registers supporting, for example, up to 16 32-bit multiplications in a single instruction. Due to the complexity of these instructions, the Skylake-SP CPUs targeted by this thesis provide three discrete sets of operating frequencies – a low "AVX-512" frequency level, an intermediate "AVX2" frequency level, and a high non-AVX frequency level [113, p. 2-14]. Upon execution of 512-bit or 256-bit SIMD instructions, individual CPU cores switch to the appropriate level and revert the change after a period where no such power-intensive instructions are executed.

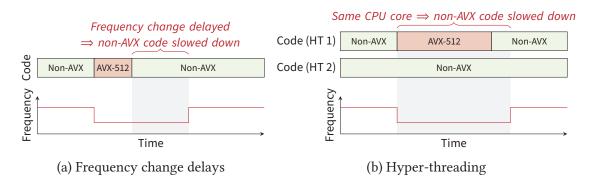

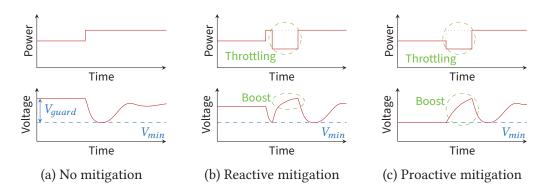

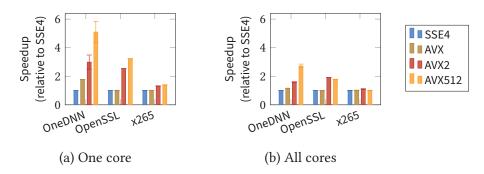

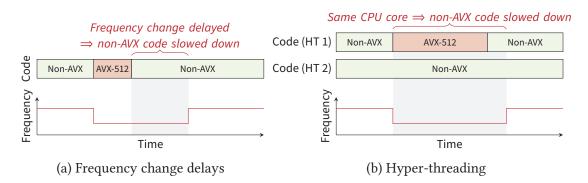

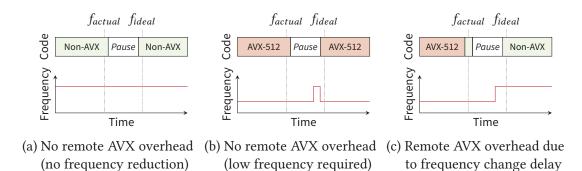

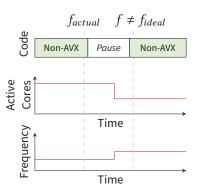

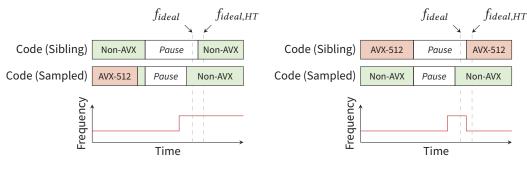

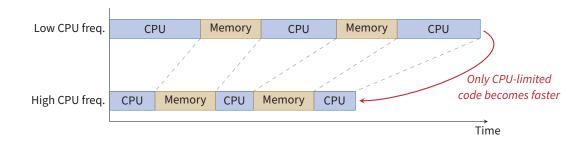

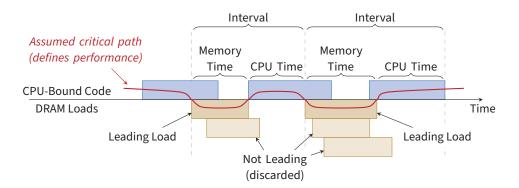

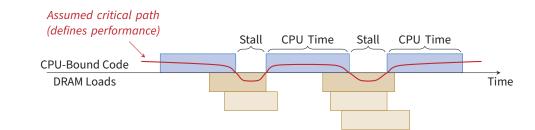

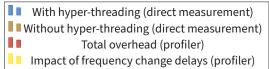

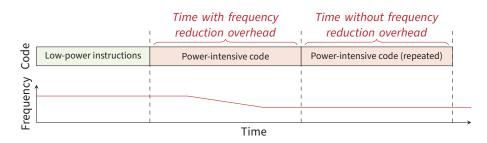

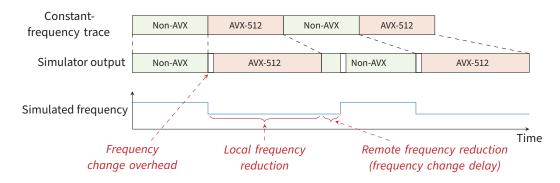

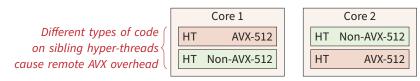

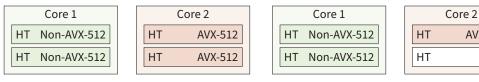

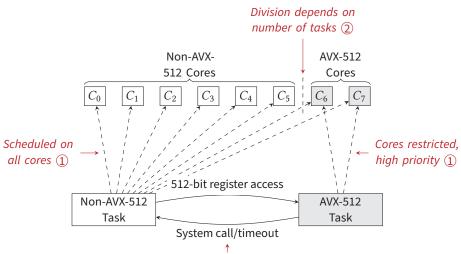

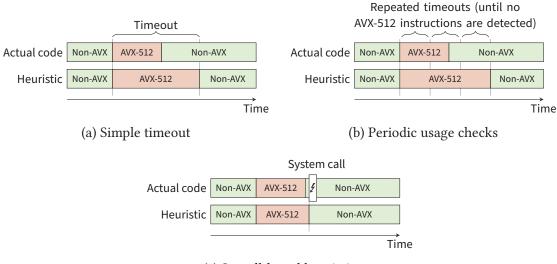

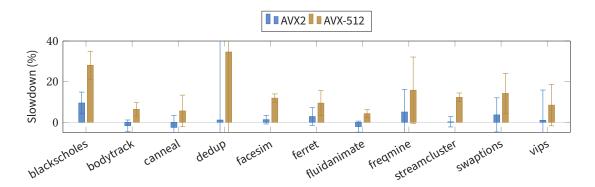

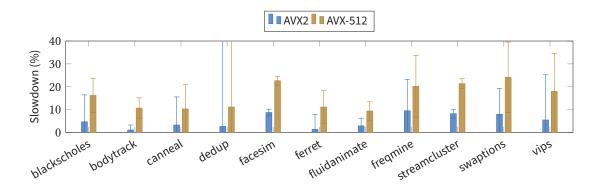

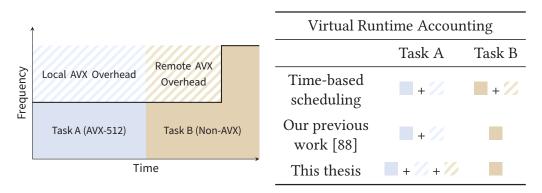

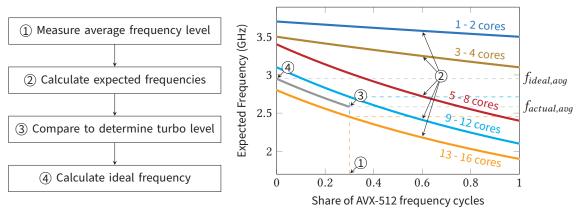

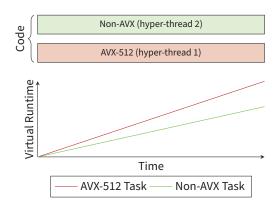

This frequency management scheme results in increased performance for many workloads, in particular those only consisting of simple instructions with low energy consumption. Such workloads would otherwise have to be executed at unnecessarily low frequency levels. In other workloads, the frequency reduction triggered by AVX2 and AVX-512 – or, in future CPUs, other similarly power-intensive instructions – has a substantial performance impact. This performance impact is most pronounced when, as shown in Figure 1.1, power-intensive code causes other, less power-intensive code to be executed at lower frequencies, which we term *remote frequency reduction*. This remote frequency reduction causes what we, in the case of AVX2 and AVX-512, call *remote AVX overhead* – code which uses power-intensive instructions slows other code down. Remote AVX overhead has been observed by related work in web server scenarios where AVX-512 in cryptography routines caused the whole web server to be slowed down by 10% [141]. Remote AVX

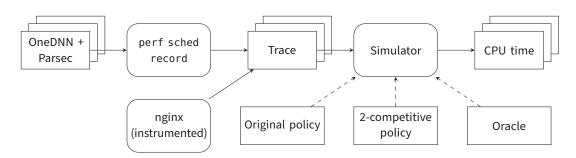

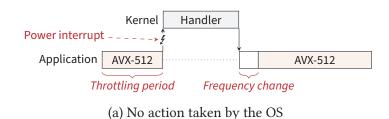

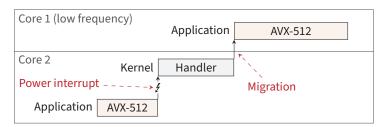

Figure 1.1: Power-intensive instructions such as AVX2 and AVX-512 cause the CPU frequency to be temporarily reduced. This frequency reduction also affects less power-intensive code that directly follows on the same hyper-thread (a) or that is executed in parallel on the sibling hyper-thread (b) The resulting slowdown is called remote AVX overhead.

overhead was also demonstrated in a multi-application scenario where a latency-critical was slowed down by up to 30% by a concurrently running machine learning workload using AVX-512 [55]. Apart from an obvious impact on overall system throughput, the multi-application scenario also shows how remote AVX overhead impacts performance isolation. Concurrently executed processes could easily cause the latency-critical application to fail to meet real-time requirements.

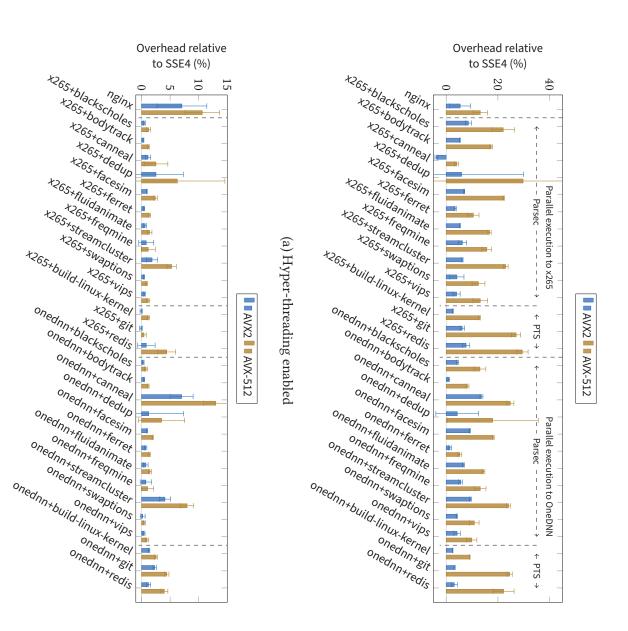

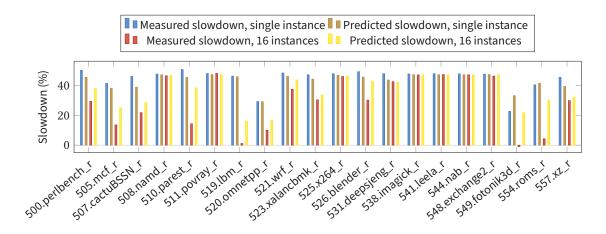

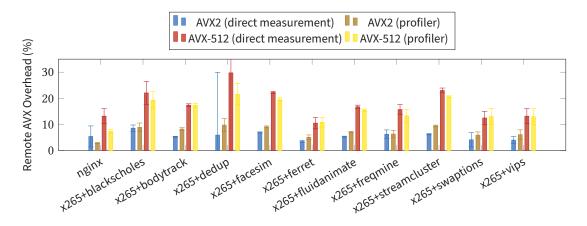

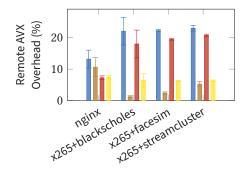

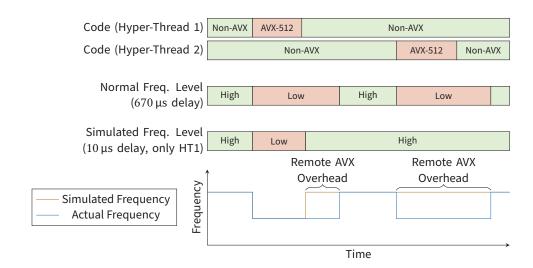

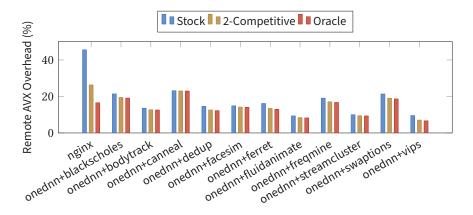

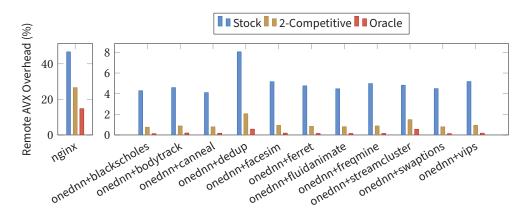

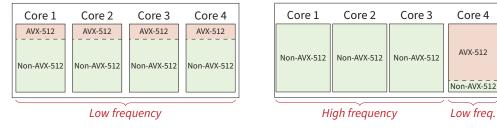

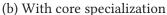

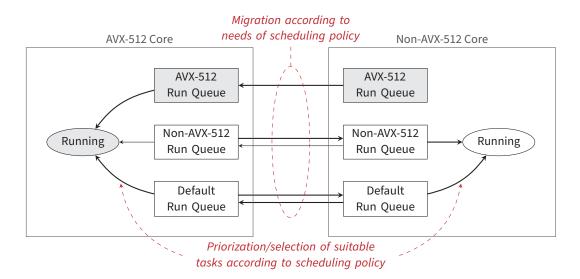

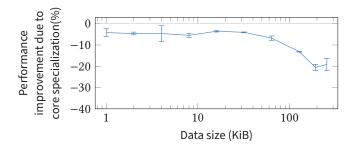

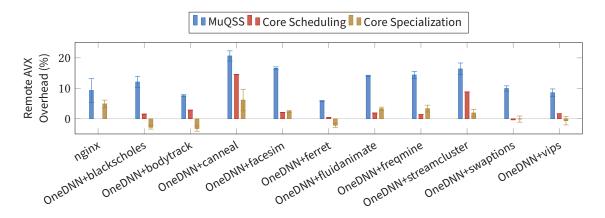

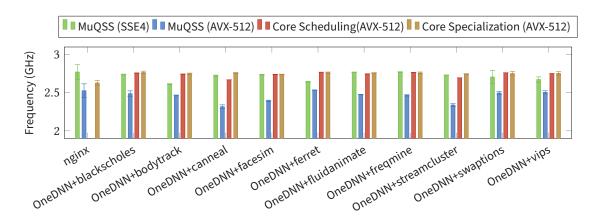

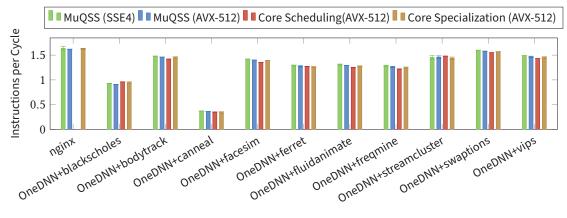

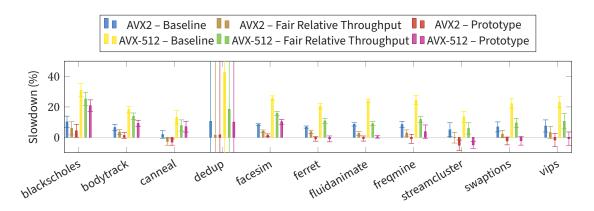

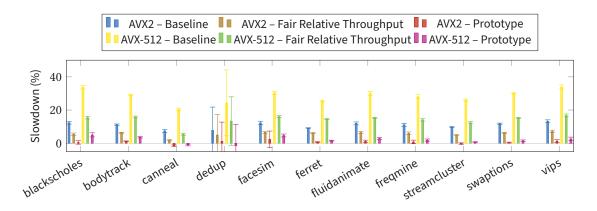

In this thesis, we provide a detailed analysis of remote AVX overhead. We show how it effects a wide range of workloads and why it is hard to predict as it is caused by the interaction of multiple software components. Most importantly, though, we show that the impact of remote AVX overhead can often be mitigated. To this end, we describe a set of tools to quantify and prevent remote AVX overhead. First, we describe a profiler that creates accurate estimates of the amount of remote AVX overhead by periodically pausing individual CPU cores and analyzing the resulting frequency changes. This profiler is able to measure remote AVX overhead with an average error of only 2.2 percentage points and is able to determine the reason for remote AVX overhead. We also show how information from the OS such as predictions of the time of the next AVX2 or AVX-512 phase can help the CPU to deploy better frequency scaling policies. While such improved frequency scaling policies are very effective for systems without hyper-threading as they remove frequency change delays, all server CPUs with support for AVX-512 also support hyper-threading. For these systems, we therefore show how the scheduler can be modified to reduce the co-scheduling of power-intensive and less power-intensive code that leads to remote AVX overhead. Limiting AVX-512 code to a subset of the available CPU cores results in an average reduction of remote AVX overhead by 90.4% over a wide range of workloads. Due to limitations of existing CPUs, our prototype is ineffective for workloads with AVX2 code, though. To mitigate the remaining performance isolation problems - in particular those in workloads with AVX2 - caused by remote AVX overhead, we finally describe how existing fair schedulers can be modified to prioritize tasks affected by remote AVX overhead to counteract the slowdown. This approach is, for example, able to reduce the average slowdown of non-AVX applications caused by AVX2 applications by 70.8%.

Our work leads to mainly two conclusions: First, the performance and performance isolation improvements achieved by our prototypes show how important it is for the OS to be designed with remote AVX overhead or similar effects in power-limited systems in mind. We expect techniques such as those described in this thesis to become even more important in the future as CPU manufacturers will likely integrate more accelerators similar to AVX-512 into CPUs in an effort to improve performance and power efficiency [234]. Second, our prototypes demonstrate the requirement for improved interfaces between the OS and the CPU. For example, while our prototypes are functional, they often suffer from limited effectiveness due to a lack of information provided by the CPU. We propose that future CPUs should provide more fine-grained information about power requirements of currently executed code and should give the OS more control about how and when frequency changes occur.

#### 1.1 Scope

This thesis focuses on the effects of AVX2 and AVX-512 instructions on the performance of applications running on Skylake-SP server CPUs. Power-intensive instructions cause similar effects on many other CPUs. Generally, these CPUs lie outside of the scope of this thesis. For example, the predecessors to Skylake CPUs – Haswell and Broadwell CPUs – also feature frequency reduction during execution of AVX2 code [76]. Also, later server CPUs using the Cascade Lake or Ice Lake microarchitecture feature similar frequency management as Skylake-SP CPUs [188], as do many recent desktop CPUs [58]. We expect most of the techniques described in this thesis to be applicable to microarchitectures similar to Skylake-SP.