## Karlsruhe Reports in Informatics 2024,2

Edited by Karlsruhe Institute of Technology, Faculty of Informatics ISSN 2190-4782

## Proseminar Mobile Computing WS 2023/24

## Mobile und Verteilte Systeme Ubiquitous Computing Teil XXI

Herausgeber: Alexander Studt, Paul Tremper Chaofan Li, Haibin Zhao, Michael Beigl

2024

KIT - The Research University in the Helmholtz Association

## Please note:

This Report has been published on the Internet under the following Creative Commons License: http://creativecommons.org/licenses/by-nc-nd/4.0/de.

# Proseminar Mobile Computing WS 2023/24

# Mobile und Verteilte Systeme Ubiquitous Computing

# Teil XXI

## Herausgeber

Alexander Studt, Paul Tremper Chaofan Li, Haibin Zhao Michael Beigl

Karlsruhe Institute of Technology (KIT) Fakultät für Informatik Lehrstuhl für Pervasive Computing Systems (PCS) und TECO

> Interner Bericht 2024,2 ISSN 2190-4782

## Vorwort

Die Seminarreihe Mobile Computing und Ubiquitäre Systeme existiert seit dem Wintersemester 2013/2014. Seit diesem Semester findet das Proseminar Mobile Computing am Lehrstuhl für Pervasive Computing System statt.

Das Proseminar Mobile Computing wird seit dem Wintersemester 2013/2014 in jedem Semester durchgeführt. Seit dem Wintersemester 2003/2004 werden die Seminararbeiten als KIT-Berichte veröffentlicht. Ziel der Seminarreihe ist die Aufarbeitung und Diskussion aktueller Forschungsfragen.

Dieser Seminarband fasst die Arbeiten der Seminare des Wintersemesters 2023-2024 zusammen. Die Themen der hier zusammengefassten Aufsätze umfasst die Themen "Solving the Long-Tail Problem", "Parallelization in Python", "Active Mobile Exoskeletons", und "Quantum Computing". Wir danken den Studierenden für ihren besonderen Einsatz, sowohl während des Seminars als auch bei der Fertigstellung dieses Bandes.

Karlsruhe, den 05. August 2024

Alexander Studt Paul Tremper Chaofan Li Haibin Zhao Michael Beigl

# Inhaltsverzeichnis

| Ton That Hoai An<br>Improving DRAM with Regards to Performance,<br>Energy-Efficiency and Reliability |

|------------------------------------------------------------------------------------------------------|

| Cornelius Niklas Breitschwerdt<br>Mobile Aktive Exoskelette in der Industrie                         |

| Quoc Anh Dang<br>NRAM as a Potential DRAM Replacement                                                |

| Beyza Keskin<br>Quantum Annealing                                                                    |

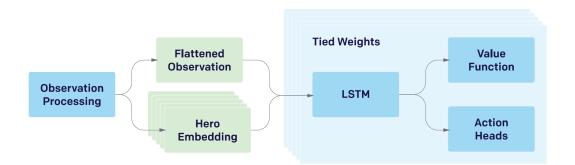

| Annemarie Schaub<br>Recent Development in AI in Video Games                                          |

| Peter Bohner<br>Memory Considered Harmful:<br>The Rowhammer Vulnerability in DRAM74                  |

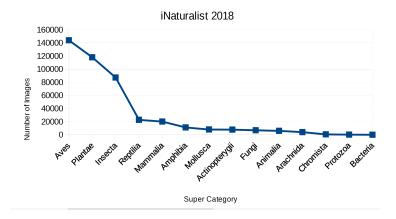

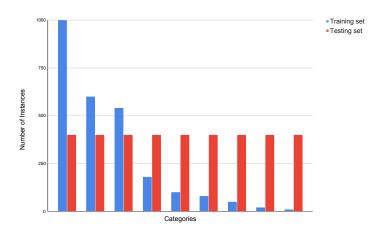

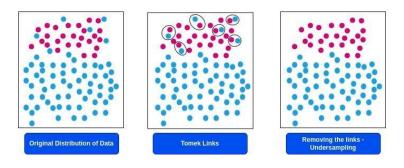

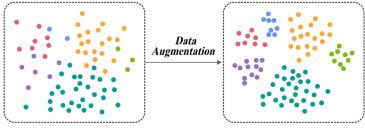

| Nathan Ridinger<br>Solving the Long Tail Problem with Sampling Stratgies                             |

## Improving DRAM with regards to performance, energy-efficiency and reliablity

Ton That, Hoai An

Karlsruher Institut für Technologie, Fakultät für Informatik, 76128 Karlsruhe, Germany

Abstract. Many fields of computer science are dependent upon data. Much of this data needs to be stored in devices capable of retaining the stored data for a prolonged duration. These devices need to be reliable, safe, fast, cheap and simple to produce. Such devices are Random Access Memory types like Dynamic Random Access Memory, Static Random Access Memory or Resistive Random Access Memory. In this seminar paper we will look at a technology called Copy-ROW Dynamic Random Access Memory to improve upon the aforementioned properties while being flexible and cheap to produce. The evaluation results show a significant improvement in performance, energy-efficiency as well as reliability.

Keywords: memory  $\cdot$  performance  $\cdot$  energy-efficiency  $\cdot$  reliability

## 1 Introduction

Random Access Memory (RAM) is an elementary component in each computation system on the market. The consumer-based evaluation nowadays is mostly based on the memory capacity the RAM module provides. This metric does not represent the entire capabilities of a RAM module. Other factors that need to be accounted for are performance (e.g., refresh latency, access-time), security, reliability and durability. Many new explored RAM types try to mitigate the weaknesses of previous RAM type generations. Nonetheless the common types of RAM on the market are still Dynamic Random Access Memory (DRAM) and Static Random Access Memory (SRAM). Both RAM types are well explored till date. The important difference between those is that, DRAM can be easily replaced by the consumer while on the other side SRAM is integrated into the hardware making it a less important concern for the consumer. The goal of this seminar paper is to delve into different techniques and structures to improve DRAM and enable new possibilities regarding performance, energy-efficiency and reliability.

## 2 Background

This section describes the DRAM organization and its operations that are necessary to understand the inner workings of DRAM.

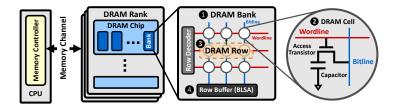

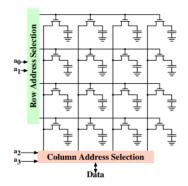

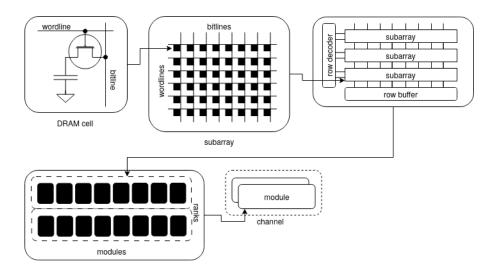

## 2.1 DRAM - Organization

A typical DRAM based system is shown in Fig. 1. In those systems the bits flow through separate Input/Output (I/O) buses from DRAM to Central Processing Unit (CPU). This flow is controlled by several memory controllers of the CPU that are connected through a DRAM channel. A DRAM channel can be connected to several modules. The DRAM module itself is ordered hierarchical, starting from DRAM rank down to DRAM subarray. The DRAM module consists of billions of DRAM cells ordered in the aforementioned hierarchy. The DRAM module itself contains several DRAM ranks which are ordered again into DRAM chips. Those DRAM chips contain several DRAM banks where the actual DRAM subarray containing the DRAM cells is present. The subarray is structured like a matrix (e.g., 128x128) [11,2,5,6]. A row of cells in the matrix is connected by a wordline which is selected by a row decoder. The columns are connected with bitlines. At the end of the bitlines, a row buffer sits to buffer the data from the activated line. The row buffer also contains the bitline sense amplifiers (BLSA) to amplify the signal [2,5]. This structure enables the DRAM to continuously access and update the stored data.

Fig. 1. DRAM module hierarchy [5]

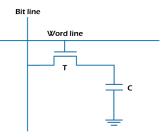

## 2.2 DRAM - Internal cell functionality

A DRAM cell consists of a transistor and a capacitor as seen in Fig. 1. The DRAM cell contains a bit depending on the current charge level. Due to the nature of a capacitor and the size of the cell, the charge leaks with time and needs to be refreshed [11,2,5,4]. Periodically each row is activated, allowing the charges to travel through the bitlines towards the row buffer. For the periodic refresh, the bitlines need to be precharged to a certain level. Generally the required charge level is  $V_{dd}/2$ . The BLSA in the row buffer then amplifies the charge back into the cells. Each operation on a cell requires a specific amount of time until a stable state is reached, these times are called timing parameters [4].

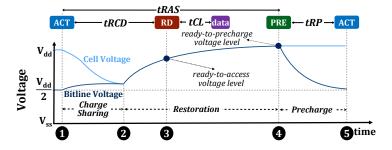

## 2.3 DRAM - Operations

To communicate with the outside world, the memory controller provides the Precharge, Activate, Read, Write and Refresh operations. All these operations

are restricted by timing parameters to guarantee a correct execution. Within these operations the Refresh operation takes a special position as it is periodically called to prevent data loss due to charge leakage [2].

Fig. 2. DRAM operations, operation timings and current voltage during a Read [2]

**2.3.1** Activate The Activate (ACT) operation applies an electrical current to the specified row address sent alongside the operation if the row was not already activated. The row decoder decodes the row address and determines the selected row. After the activation, the data contained in the cells are send to the row buffer. This operation is constrained by the timing parameter *Row* Address to Column Address Delay (tRCD) which is the required time until the data has stabilized in the row buffer. [2,5]. The operation requires the bitline to be precharged as opening the row allows the transistor charge to flow towards the bitlines. After stabilizing the charge, the BLSA detects the change in charge and restores the charge inside the transistor depending on the read change. The charge restoration is necessary as the capacitor does not contain the correct charge after the row opening [2].

**2.3.2** Read The Read (RD) operation can be started after a row was activated. The column address is sent alongside this operation to specify the part inside the matrix to be retrieved. This data is then read and stored in the global row buffer. From the buffer the data then moves through a connected bus to the memory controller. The timing parameter for this operation is called *CAS latency* (tCL) and decides the required time until the data appears on the bus [2,4].

**2.3.3** Write The Write (WR) operation operates similar to the ACT operation. The Write operation requires a charge restoration. Instead of just restoring the previous charge, the BLSA sends the to be written data into the capacitors. The timing parameter *Write Recovery Time* (tWR) defines the required passing time till the next operation [2,4].

**2.3.4 Refresh** As previously mentioned, a DRAM cell can not retain its state for a prolonged time due to the charge leakage. To ensure the correct retrieval of the data at any point in time, this refresh (REF) operation is periodically called in a specified interval. Each row is typically refreshed in a standardized time frame (e.g., 64ms) [2,5,4].

**2.3.5 Precharge** The Precharge (PRE) operation is necessary to close a row and prepare the bitlines for the next ACT. The timing parameters tRAS decides the time until the next PRE can be called. The time itself the PRE operations need is called *Row Precharge Time* (tRP). It allows the bitlines enough time to be charged to the required charge level [2,4].

## 3 Copy-Row DRAM

The Copy-Row DRAM (CROW) is a new technology proposed in the paper [2]. It tries to mitigate the bottleneck, which the regular DRAM causes, by using new mechanisms for faster, more energy-efficient and more reliable use of DRAM.

## 3.1 Copy-Row DRAM - Overview

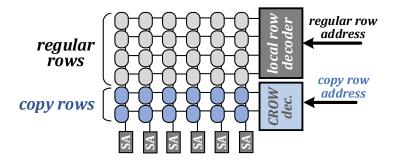

CROW introduces two new components to achieve the desired properties.

The first component are *copy rows* that are, additionally to the regular rows, located in each subarray. Those can be used to copy or remap data stored in the regular rows [2].

The second component is the CROW-table located inside the memory controller. It tracks the occupied copy rows and its corresponding regular row [2].

As CROW uses two different types of rows, both need to be addressed separately thus resulting in another row decoder for the copy rows. This allows a new action called *multiple-row activation* (MRA) which activates copy rows and regular rows simultaneously. Two new DRAM primitives are possible due to this new action.

First, CROW can perform bulk data movement, it can copy content from a regular row to a copy row. This is achieved by activating the regular row first. After the ACT operation, the data is stored inside the buffers. The copy row is activated additionally to the regular row. The sense amplifers now redirect the charge towards the open regular row as well as the open copy row [2].

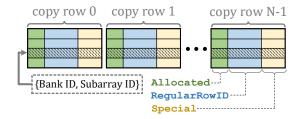

Second, CROW can perform reduced-latency DRAM access under certain conditions. If a regular row got copied beforehand into a copy row, the memory controller can activate both simultaneously [2]. Two charges are spreading inside the bitlines which results into faster charge time for the sense amplifiers. The sense amplifier can redirect the charge faster as a result thus decreasing the activation time. **3.1.1 Copy Row** As mentioned previously, CROW contains two different types of rows as shown in Fig. 3. On one side the usual rows in every DRAM, denoted here as regular rows, on the other side the copy rows. These copy rows can be accessed independently as a second row decoder is used to address these rows. The occupied area of the second row decoder is much smaller than the one for the regular rows as the amount of copy rows will be kept small. Additionally to the regular row, now another address needs to be send from the memory controller. Due to the amount of copy rows, not many extra bits are necessary for the address.

Fig. 3. CROW DRAM structure [2]

**3.1.2 CROW-table** The CROW-table is located in the memory controller. A rough organization of the data structure can be seen in Fig. 4. It stores data regarding the copied regular rows inside the copy rows. The CROW-table itself is n-way set associative, n is the amount of copy rows that are located in each subarray. The table is accessed by the memory controller by using the bank-and subarray-address to retrieve. The current design requires three fields for each entry. First, a valid field to check whether the copy row is valid. Second, a pointer towards the copied regular row. Third, additional information for CROW operations.

Fig. 4. CROW-table [2]

## 3.2 CROW - New operations

CROW introduces two new operations that exploit the new subarray structure. These operations aim to improve upon performance, energy-efficiency and reliability.

**3.2.1** Activate-and-copy The Activate-and-copy operation (ACT-c) executes a copy operation from a regular row to a copy row. The operation first performs a regular row activation. After the sense amplifier is charged, the copy row is then activated as well. Due to there being two opens rows now, both will be charged with the corresponding data. For this operation the regular row address and copy row address are required. The addresses will then be supplied to the corresponding row decoder.

**3.2.2** Activate-two The Activate-two operation (ACT-t) executes two activate primitives at once. Assuming the to be activated row is also existent in another copy row, the ACT-t operation activates both rows simultaneously. As this operation activates two rows at once, it requires the regular row and copy row address. A lookup into the CROW-table before ACT-c is required as the copy row might be invalid.

## 3.3 CROW - Improvement mechanisms

Three mechanisms are proposed in the paper [2] to improve upon the properties performance, energy-efficiency and reliability. The first strategy is called CROWcache, it takes advantage of the MRA operation to achieve faster access time as well as less energy consumption. The second strategy is called CROW-ref and reduces refresh overhead by taking advantage of the copy rows for faster REF operations. The third strategy relies on remapping regular rows onto copy rows to counteract against rowhammer attacks.

**3.3.1 CROW-cache** The key idea behind the CROW-cache is to exploit the MRA operation to charge the bitlines from two locations. This results in an faster restoration of the sense amplifier, by using this fact the access towards specific rows can be increased.

Assuming N copy rows, N regular rows can be copied. The N copy rows will act as an cache and will store the most frequently accessed rows like a regular cache. The cache can be filled by using any operation systems cachereplacement-policy like First-In-First-Out. In case the cache-replacement-policy requires more bits, more bits need to be allocated for the CROW-table. The memory controller can now check on every access whether a row got copied. In case the CROW-table retrieves a miss, the regular row is getting copied to a copy row by using the newly introduced ACT-c operation. After the execution of the operation both rows contain the same data. Due to restoring the data to two different rows, we gain a slight overhead in restoration latency. The effect on the entire is system is little as the cache-replacement-policy should provide a high hit-rate.

The second introduced operation ACT-t exploits the fact, that two rows containing the same data are existent in the DRAM. The key idea is to activate a copy row and regular row simultaneously to allow faster access. Assuming the to be access regular row already has an entry inside the CROW-table, we can execute and ACT-t. This results into faster charging of the bitlines and faster general activation time. By using this combination of operations the buffer retrieves the data faster and access-time can be speed up.

We gain another positive side-effect from activating two rows at once, an increased capacitance on the bitline. By exploiting this fact, we can relax the tRAS timing parameter by using a technique called partial restoration [10]. The key idea is to stop the row activation earlier than usual resulting into partially restored cells. The increased capacitance results into slower charge leak thus keeping the data until the next refresh. By combining the partial restoration technique with the previously mentioned techniques, we can achieve an even faster access time. Due to the partial charge state, those cells can only be accessed with ACT-t. The next section will touch upon this drawback. As previously mentioned, the access time can be decreased by using partially charged cells. There are two cases, where the the cells are not necessarily in that state.

First, the operations in between the PRE operation and the ACT operation surpass the time needed for full recharge.

Second, no further requests are made to the memory controller resulting in time to delay the PRE operation. In any other case, we need to store the information of the partial restoration state to prevent faulty accesses. This is accomplished by using the additional information bits inside the CROW-table. We use one bit to store the partial restoration state and call it is FullyRestored. This field is only false, if the time between ACT and PRE is below the the tRAS timing parameter. Due to the already existing timing information, the calculation of this field does not result into a significant overhead.

As already mentioned in previous sections, the copy rows act similar to a cache. The introduction of the partially charged states provides a new challenge regarding the eviction policy that needs to be addressed. Assume a copy row is evicted for a copy of another regular row, yet the copy row is not fully restored. The memory controller can access this information inside the CROW-table. To circumvent this issue, the memory controller issues an ACT-t operation and awaits the the regular tRAS timing parameter. After the passing of the regular timing parameter, the cell is fully restored. This trick results into a negligible overhead with the assumption of a high hit-rate.

**3.3.2 CROW-ref** CROW-ref is a mechanism to increase the refresh window by remapping weak regular rows to strong copy rows. This mechanism allows us to extend the worst-case timing parameter and reduce energy consumption. For the CROW-ref mechanism, a row retention profiler is necessary for identification of weak rows. The row retention profiler is run at start-up or during runtime

to analyze the weak and strong rows. The profiler tests all rows with specified procedures upon certain specifications to rate all rows. Works in the papers [1,7] find that most rows do not necessarily need worst-case refresh interval. This indicates, that using strong rows results into more efficient usage of refresh intervals. By using these results, we can calculate how many copy rows are neccessary to ensure a efficient usage of rows. The calculation for the probability of a weak row results from the counter probability for no weak cells.

$$P_{weak\_row} = 1 - (1 - P_{weak\_cell})^{N_{cells\_row}}$$

(1)

Using (1) and the binomial distribution, we determine the probability for more than n weak rows in a subarray.

$$P_{subarray\_n\_rows} = 1 - \sum_{k=0}^{n} \binom{N_{row}}{k} P_{weak\_row}^{k} * (1 - P_{weak\_row})^{N_{row}-k}$$

(2)

Under the assumption of  $P_{weak\_cell} = 4 \cdot 10^{-9}$  and 512 rows per subarray with 8192 cells, we arrive at a probability of  $P_{subarray\_8\_rows} = 3.3 \cdot 10^{-11}$ . This means, 8 copy rows will suffice for most objectives to cover most of the weak rows. By using the knowledge about weak and strong rows, we can remap all weak regular rows onto strong copy rows. The tracking of the copies happens with the CROW-table. After each remapping the CROW-table stores the regular row id in its corresponding field. At each memory access, the memory controller checks the CROW-table for a remapping. If the check is positive, the corresponding row is activated instead. By using the above-mentioned strategy, the worst-case timing parameter is extended due to strong rows having a longer lifetime. This results in less refresh periods as well as better energy usage. The profiling during runtime is necessary due to variable retention time (VRT) [9,8]. The VRT results into sporadic changes of retention time. To act against this behaviour, runtime profiling is necessary. The remapping strategy remains the same.

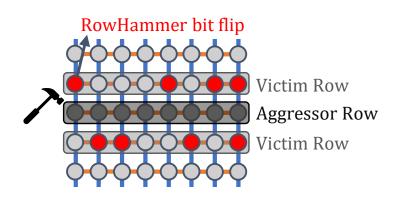

## 3.4 Row-hammer mitigation

The scaling nowadays result in many issues as bitlines and cells are positioned in close proximity. The electromagnetic fields surrounding each component may affect one another due to the distance leading to corrupted data. Such an attack is the rowhammer attack, the concept behind it is to consecutively activate a row to peturb nearby victim rows. Aside from reliability issues stemming from corrupted data, previous work also have shown that privileged access can be gained through this attack. CROW has the ability to mitigate this kind of attack by exploiting the copy mechanism. Several papers [3,11] already delved into the topic of row-hammer detection. By using CROW we can prevent a row from being corrupted. After detection, several ACT-c operations are executed to copy the adjacent victim rows to copy rows. By doing that, the content of the rows are saved, therefore negating the attack on the victim rows. For any following ACT operation, the corresponding copy row can be retrieved from the CROW-table inside the memory controller.

Fig. 5. Rowhammer attack [3]

## 4 Evaluation

Evaluation results on performance and energy-efficiency are presented in the paper [2] and will be discussed here.

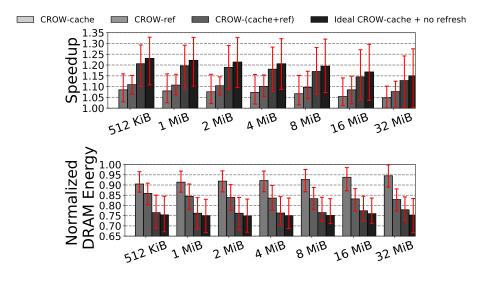

## 4.1 CROW-cache

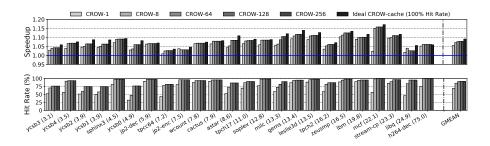

The evaluation for CROW-cache will be made on configurations with differing amount of copy rows. The CROW configuration will be denoted by CROW-N where N is the amount of copy rows. For the evaluation, CROW was run on several benchmark applications e.g., cactus. The quantity mentioned alongside the application refers to the misses per kilobyte instruction.

**4.1.1 Single-core performance** As discussed earlier, ACT-t provides an speedup due to faster access which can be seen in Fig. 6. CROW-1 already shows an average speedup compared to traditional DRAM of 5.5%, CROW-8 and CROW-256 respectively 7.1% and 7.8%. This improvement is also coupled with an more efficient energy-usage as more operations can be executed as result from the speedup. These numbers are based under the assumption of the Most Recently Used eviction policy. By just using this eviction policy, we can already see a high hit rate. This is proportional to the speedup as can be seen.

Fig. 6. Single-core performance [2]

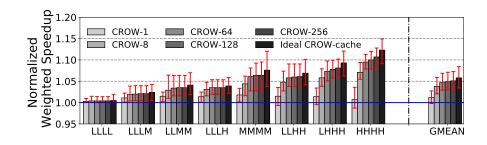

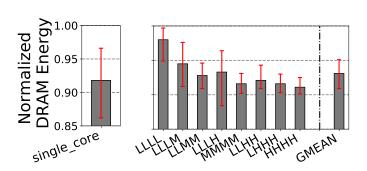

**4.1.2** Multi-core performance In Fig. 7 we can see the evaluations results for a four-core system. The red bars show the performance fluctuation between each core. The workload of each core is denoted by High (H), Medium (M) and Low (L). As can be seen, CROW-1 provides, on average, a 1.1% speedup, while CROW-8 and CROW-256 provide a 3.7% and 4.9% speedup, respectively. We can see, CROW-1 does not provide a great speedup boost in case of a multi-core performance system. Due to multiple cores accessing the same subarray, the copy row gets frequently replaced resulting into an inefficient usage of the CROW. In contrast to single-core performance, multi-core performance still achieves a significant speedup compared to the regular performance.

Fig. 7. Four-core performance [2]

## 4.2 Energy-efficiency

ACT-t and ACT-c are elementary operations for the CROW improvement strategies. Even though compared to ACT, both operations consume more energy on average, CROW-cache amortizes the energy-usage in general. This lies in more efficient usage of energy by executing operations faster. On average, the energy usage lies around 8.2% and 6.9% for single-core systems and multi-core systems respectively. It should be noted, the more operations are used, the more the energy-efficiency rises due to amortization over all operations

Fig. 8. CROW-cache energy consumption [2]

## 4.3 CROW-ref

For the CROW-ref evaluation, the refresh interval was extended to 128ms instead of the usual 64ms. CROW-ref provides benefits in the aspects performance and energy-efficiency. The interval extension results into less refreshes per cycle thus less energy used up for refreshes. As a result of less refreshes per cycle, other operations can be executed instead. Therefore a speedup in performance can be seen as well. It has to be noted, less rows are available for regular CROW-cache in case of using both strategies at once. The observation results for average energy consumption can be seen in Fig. 9.

Fig. 9. CROW-ref energy consumption [2]

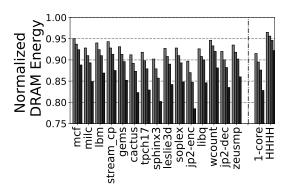

## 4.4 CROW-cache and CROW-ref

Furthermore, observations made in the paper [2] indicate a synergy in combining both mechanisms. CROW-ref does not necessarily use all copy rows and thus can be used for CROW-cache instead. This is due to the low probability of weak rows, resulting in free copy rows that can be used by CROW-cache instead. Only one extra bit is necessary to store which mechanisms is used for the copy row inside the CROW-table. Fig. 10 shows the comparisons of the two mechanisms separately as well as combined together with regard to the DRAM capacity for a single-core. We can identify, the benefits of the combination of both mechanisms is bigger than the sum of both mechanisms separately. Regarding the performance improvement, they are a result of the improved REF operations per cycle. Due to less REF operations, more operations can be executed in between, increasing the throughput of work-related operations. By decreasing the amount of REF operations, we can also see the increase that we would have gotten from CROW-ref independently. In total, we can mitigate the bottleneck by combining both mechanisms.

Fig. 10. CROW comparisons [2]

## 5 Conclusion

The paper [2] proposes a new structure called CROW that partitions the rows inside a DRAM into two types of rows which can be activated independently. By exploiting this fact, CROW introduced three strategies to improve upon performance, energy-efficiency as well as reliability. CROW-cache uses the copy rows as a kind of cache to achieve faster activation-time. CROW-ref profiles the rows of the DRAM to remap weak regular rows to strong copy rows. This achieved a reduction of refresh operation per cycle. CROW is also able to prevent rowhammer attacks by copying the victim rows into copy rows. By deploying all three mechanism improvement can be made on all respective fields.

## References

- Choi, H., Hong, D., Lee, J., Yoo, S.: Reducing dram refresh power consumption by runtime profiling of retention time and dual-row activation. Microprocessors and Microsystems 72, 102942 (2020). https://doi.org/https://doi.org/10.1016/j.micpro.2019.102942

- 2. Hassan, H.: Improving dram performance, reliability, and security by rigorously understanding intrinsic dram operation (2023)

- Hassan, H., Tugrul, Y.C., Kim, J.S., van der Veen, V., Razavi, K., Mutlu, O.: Uncovering in-dram rowhammer protection mechanisms: A new methodology, custom rowhammer patterns, and implications (2022)

- 4. Kim, J.S.: Improving dram performance, security, and reliability by understanding and exploiting dram timing parameter margins (2021)

- Luo, H., Olgun, A., Yağlıkçı, A.G., Tuğrul, Y.C., Rhyner, S., Cavlak, M.B., Lindegger, J., Sadrosadati, M., Mutlu, O.: Rowpress: Amplifying read disturbance in modern dram chips (2023)

- Olgun, A., Bostanci, F.N., Oliveira, G.F., Tugrul, Y.C., Bera, R., Yaglikci, A.G., Hassan, H., Ergin, O., Mutlu, O.: Sectored dram: An energy-efficient highthroughput and practical fine-grained dram architecture (2022)

- Patel, M., Kim, J.S., Mutlu, O.: The reach profiler (reaper): Enabling the mitigation of dram retention failures via profiling at aggressive conditions. In: 2017 ACM/IEEE 44th Annual International Symposium on Computer Architecture (ISCA). pp. 255–268 (2017). https://doi.org/10.1145/3079856.3080242

- Qureshi, M.K., Kim, D.H., Khan, S., Nair, P.J., Mutlu, O.: Avatar: A variableretention-time (vrt) aware refresh for dram systems. In: 2015 45th Annual IEEE/IFIP International Conference on Dependable Systems and Networks. pp. 427–437 (2015). https://doi.org/10.1109/DSN.2015.58

- Restle, Park, Lloyd: Dram variable retention time. In: 1992 International Technical Digest on Electron Devices Meeting. pp. 807–810 (1992). https://doi.org/10.1109/IEDM.1992.307481

- Wang, Y., Tavakkol, A., Orosa, L., Ghose, S., Mansouri Ghiasi, N., Patel, M., Kim, J.S., Hassan, H., Sadrosadati, M., Mutlu, O.: Reducing dram latency via chargelevel-aware look-ahead partial restoration. In: 2018 51st Annual IEEE/ACM International Symposium on Microarchitecture (MICRO). pp. 298–311 (2018). https://doi.org/10.1109/MICRO.2018.00032

- Zhou, R., Liu, J., Ahmed, S., Kochar, N., Rakin, A.S., Angizi, S.: Threshold breaker: Can counter-based rowhammer prevention mechanisms truly safeguard dram? (2023)

## Mobile aktive Exoskelette in der Industrie

Cornelius Niklas Breitschwerdt

Karlsruher Institut für Technologie, 76131 Karlsruhe, Germany cornelius.breitschwerdt@student.kit.edu

**Zusammenfassung.** Es werden Motivation hinter der Nutzung von Exoskeletten behandelt und ihre Anwendungsbereiche klassifiziert. Eine Reihe an Systemen wird vorgestellt und stellvertretend für ihre Klassen verglichen.

Schlüsselwörter: Mobil  $\cdot$  Aktiv  $\cdot$  Industrie  $\cdot$  Exsokelett

## 1 Einführung

Exoskelette sollen Arbeitsabläufe beschleunigen und menschliches Versagen verhindern [24]. Sie ermöglichen es ihren Trägern, Lasten von bis zu 90 kg mit weniger Kraftaufwand und geringerer Anstrengung zu heben [33]. Ununterbrochene Produktion und weniger Ausfälle werden aufgrund von geringerer Erschöpfung und erhöhter Sicherheit erreichbar.

In dieser Arbeit wird vorgestellt, was ein Exoskelett bewirken kann, welche Arten von Exoskeletten es gibt und wie sie in der Industrie eingesetzt werden. Zudem werden mehrere Exoskelette vorgestellt und anschließend einige ihrer Eigenschaften, unter anderem Kraft, Gewicht und Aktivität, verglichen.

Es wird eine Einschränkung auf aktive, also durch z. B. Elektrizität oder Luftdruck betriebene, Exoskelette gemacht.

## 2 Motivation

Dieses Kapitel wird einen kurzen Überblick über die verschiedenen Gründe für die Nutzung von Exoskeletten in der Industrie geben.

#### 2.1 Muskel- und Skeletterkrankungen – MSE

Muskel- und Skeletterkrankungen (MSE) umfassen Schädigungen und Störungen der Gelenke und des Gewebes. Am häufigsten betroffen sind der oberere Rücken und Nacken, andere Bereiche wie untere Gliedmaßen sind jedoch nicht ausgeschlossen [11]. MSE entstehen über einen längeren Zeitraum durch wiederholte Bewegungen und Vibrationen, schlechte Haltung und schwere körperliche Arbeit [12].

MSE können zu intensiven Schmerzen und Bewegungseinschränkungen führen. Dies kann tägliche Aufgaben erschweren oder unmöglich machen [23] und somit zu einem Fernbleiben von der Arbeit führen. Für Firmen bedeutet dies einen finanziellen Rückfall. In Deutschland tragen Unternehmen Kosten von bis zu 28.7 Milliarden Euro pro Jahr für Krankheitstage, die mit MSE verknüpft sind [28].

Besonders betroffene Industrien sind die Land- und Forstwirtschaft, Bauund Abbruchindustrie, das Gesundheitswesen und die Transportindustrie [6].

Die Nutzung von Exoskeletten kann die Verletzungsrate stark reduzieren und die Lasten auf den Körper minimieren. Dies führt zu besseren Arbeitsbedingungen und ermöglicht ein längeres und erfüllteres Berufsleben [6].

## 2.2 Muskelermüdung

Bei längeren Arbeiten ist Muskelermüdung ein wichtiger und gefährlicher Faktor. Sowohl Präzision als auch Kraft können hiervon reduziert werden und somit ein Unfallrisiko erzeugen.

Exoskelette können hier, vor allem bei Lastentransport, Werkzeugnutzung, Überkopfarbeit, gebückten und hockenden Arbeiten, dem Träger helfen über einen längeren Zeitraum seine Arbeit zu verrichten und zusätzlich die Verletzungsgefahr zu reduzieren [7]. Zudem kann sich der Komfort des Trägers durch die Nutzung eines Exoskeletts während dem Arbeiten steigern, indem es eine gewisse Menge an Gewicht trägt oder eine bequemere Arbeitsposition ermöglicht.

## 2.3 Leistungssteigerung

Exoskelette sind darauf ausgelegt, die körperlichen Fähigkeiten von Nutzern und damit auch ihre Arbeitskapazität zu erweitern. Dies hilft Firmen in der Balance zwischen Arbeitsaufträgen und Arbeiterkapazität [4].

Effizientere Bearbeitung von Aufgaben Diese Erweiterung der Fähigkeiten kann sich in Form von längerer Arbeitszeit ohne Pause, qualitativ besserer Arbeitsleistung [7] oder in weniger krankheitsbedingten Fehltagen zeigen. Letzteres ist Resultat von weniger biomechanischer Last auf den Körper [7]. Ein weiterer Punkt, der im Angesicht einer alternden Arbeiterschaft immer wichtiger wird, ist die technische Unterstützung, um die Fähigkeiten älterer Arbeiter zu erhalten [22].

**Erweiterung der menschlichen Fähigkeiten** Eine andere Sicht auf die Produktivitätssteigerung ist die Erweiterung von Fähigkeiten um Eigenschaften, die ohne Exoskelette für einen Menschen nicht möglich sind.

Eine dieser Möglichkeiten ist die Kraftsteigerung, welche besonders in der Logistik Anwendung findet. Hier wird das Exoskelett genutzt, um dem Träger mehr Kraft zu verleihen [10], wenn möglich ohne die Präzision zu beeinträchtigen. Sicherheitssteigerung Obwohl Exoskelette nicht als traditionelle persönliche Schutzausrüstung bezeichnet werden, ist einer ihrer größten Motivationspunkte an industriellen Arbeitsplätzen die Verletzungsvorbeugung [7] und Unfallrisikominimierung, sowie die Minimierung der damit verbundenen Kosten [6].

## 3 Anwendungsbereiche in der Industrie

In diesem Kapitel geht es speziell um die Bereiche der Industrie, in welchen Arbeiter besonders von Exoskeletten profitieren können. Diese werden im Folgenden klassifiziert und mit Beispielen versehen.

Es wird in drei Klassen unterteilt [38]. Die Kriterien, anhand welchen unterschieden wird, sind Stärke und Art der physikalischen Unterstützung. Diese Klassen werden später zur besseren Einordnung von Exoskeletten genutzt.

K1 Ungewöhnliche Arbeitspositionen und Bewegungen Diese Klasse beinhaltet Arbeiten, bei denen ungewöhnliche und unbequeme Positionen oder Bewegungen gehalten bzw. wiederholt werden. Hierzu zählen Überkopfarbeiten, welche das Halten der Arme über den Schultern bzw. dem Kopf verlangen, aber auch gebückte oder hockende Arbeiten. Beispiele hierfür sind Montage, Schweißen oder Fließbandarbeit in der Automobilindustrie [38].

**K2** Manipulation schwerer Lasten Diese Klasse beinhaltet Lastenarbeit. Speziell Manipulationen von Massen über 4 kg, welche nur gegen die Gravitation gehoben bzw. gehalten werden. Beispiele hierfür sind die Logistik, in welcher Arbeiter Pakete verschiedenster Massen über variierende Distanzen bewegen, oder die Automobilindustrie, mit der Montage von z. B. einem Kabelbaum [38].

K3 Unterstützung beim Montageaufwand Diese Klasse beinhaltet die Manipulation von Massen in alle Richtungen. Statt dem Kraftaufwand gegen die Gravitation spielen hier Kräfte in z. B. horizontale Richtung die Hauptrolle. Beispiele hierfür sind Fließbandarbeiten oder das Installieren von hermetischen Dichtungen in der Automobilindustrie.

Aufgrund von zunehmender Komplexität im Design und Einschränkungen in der Masse, gibt es nur eine kleine Menge an Exoskeletten, die multidirektional Kraft aufwenden können und somit für diesen Anwendungsfall gebaut sind [38].

**Grenzen dieser Klassifizierung** Kfz-Mechatroniker/innen [31] sind eindeutig **K1** zuzuordnen, Logistik, Bau und Montage gehören **K2** an. Die Automobilindustrie oder Metallindustrie, so wie auch viele andere Berufe, gehören jedoch mehreren Klassen an.

Die Grenzen in der Klassifizierung stehen also nicht endgültig fest und sind nur als Hilfestellung zur besseren Einordnung und zu einem besseren Vergleich von Exoskeletten gedacht.

## 4 Definitionen

### 4.1 Exoskelett

Ein Exoskelett ist ein Mensch-Roboter-System, welches Muskelkraft- und Ausdauersteigerungen in verschiedensten Umgebungen für den Nutzer bringt, während dieser die Aufgaben der Position, Steuerung und Wahrnehmung übernimmt. Die mechanischen Teile sind hierbei am Nutzer angebracht [21].

### 4.2 Mobilität

Das Gewicht eines Exoskeletts ist ein wichtiger Faktor der Mobilität. Ist es zu schwer, schränkt es den Nutzer in seinen Bewegungen, seiner Geschwindigkeit und seiner Reaktionszeit ein. Es ist zudem wichtig, wie das Gewicht gelagert ist, also ob es vom Exoskelett selbst getragen wird oder auf z. B. den Hüften des Nutzers lastet. Dies kann Auswirkungen auf die Ausdauer des Nutzers haben und somit die Reichweite und Tragedauer beeinträchtigen.

### 4.3 Aktivitätsgrad

Der Aktivitätsgrad eines Exoskeletts wird durch die Art von Energie, die es nutzt, klassifiziert [13]. Hierbei wird zwischen externer und selbst generierter Energie unterschieden.

**Aktiv** Aktive Exoskelette nutzen einen oder mehrere Antriebsmechanismen, bzw. Aktuatoren, welche externe Energiequellen benötigen. Beispiele hierfür sind hydraulische und pneumatische Zylinder oder elektrische Motoren [4].

Aktive Exoskelette sind z. B. dazu geeignet schwere Massen, manche bis zu 100 kg, zu manipulieren. Sie sind jedoch durch die zusätzliche Hardware, wie z. B. Motoren, Kabel und Batterie, meist schwerer und teurer als ihre passiven Gegenstücke [4].

**Passiv** Passive Exoskelette nutzen Mechanismen, welche Energie vom Nutzer speichern und diese zu einem späteren Zeitpunkt effektiv freigeben [4]. Beispiele hierfür sind elastische Elemente wie z. B. Federn [13], [4]. Gelenke ohne eine Antriebsmethode zählen auch hierzu. Diese haben meist eine stabilisierende Aufgabe und dienen zum Schutz des Nutzers.

Passive Exoskelette sind z. B. gut geeignet, um Werkzeuge über einen längeren Zeitraum auf einer Höhe zu halten [13] und sind aufgrund ihrer Unabhängigkeit von aktiven Energiequellen flexibel einsetzbar. Quasi-Aktiv Quasi-aktive Exoskelette nutzen eine Mischung aus aktiven und passiven Antriebsmechanismen, hier sind vor allem einzelne Gelenke bzw. Aktuatoren gemeint. Diese quasi-aktiven Gelenke bestehen aus einem aktiven Teil, welcher für eine gewisse Anzahl von Freiheitsgraden zuständig ist. Zum anderen bestehen sie aus einem passiven Teil, welcher für die restlichen spezifizierten Freiheitsgrade zuständig ist.

Quasi-aktive Exoskelette sind weniger komplex und leichter als aktive Exoskelette, was sie weniger fehleranfällig und komfortabler macht. Dennoch haben sie die Vorteile von aktiver Krafterzeugung auf den relevanten Freiheitsgraden. Sie werden z. B. für Hebe- und Laufaufgaben mit Gewicht verwenden [19].

## 4.4 Energieversorgung

Aktive und quasi-aktive Exoskelette benötigen einen Energiespeicher. Es ist auch möglich, dass mehrere Energiearten und damit mehrere Energiespeicher zugleich verwendet werden. Dies ist jedoch seltener, da hierdurch die Komplexität steigt. Ein solcher Speicher kann ein Akkumulator oder Drucklufttank [13] sein. Je nach Anwendungsort und -fall kann auch eine kabel- oder schlauchgebundene Energiequelle, z. B. Stromnetz oder Hallendruckluftsystem, verwendet werden [13]. Dies schränkt jedoch die Mobilität ein.

## 4.5 Kontrolle

Aktive Kontrolle Der Nutzer des Exoskeletts kann das Level an Unterstützung oder den Funktionsmodus während der Ausführung von Aktivitäten anpassen. Er hat also direkten Einfluss auf die Abläufe des Exoskeletts.

**Passive Kontrolle** Die Bewegungen des Nutzers werden von Sensoren erfasst und durch Algorithmen in Bewegungen des Exoskeletts umgewandelt. Der Nutzer hat keine Möglichkeit, während des Betriebs in diesen Ablauf einzugreifen.

#### 4.6 Körperabdeckungsbereich

Exoskelette können anhand der Bereiche des Körpers, welche sie unterstützen, kategorisiert werden. Am häufigsten wird zwischen Oberkörper, Unterkörper und Ganzkörper unterschieden [4], es kann jedoch auch ein speziellerer Körperteil angesprochen werden.

Oberkörperbezogene Exoskelette werden in diesen wissenschaftlichen Arbeiten behandelt: [15], [36], [26]. Einige in der Industrie verwendete Exoskelette sind hier zu finden: [5], [17], [35].

Unterkörperbezogene Exoskelette werden in diesen wissenschaftlichen Arbeiten behandelt: [20], [40], [3]. Einige in der Industrie verwendete Exoskelette sind hier zu finden: [30], [37].

Ganzkörperbezogene Exoskelette werden in diesen wissenschaftlichen Arbeiten behandelt: [8], [25]. Ein in der Industrie verwendetes Exoskelett ist hier zu finden: [33].

## 5 Konkrete Anwendungsbeispiele

Hier werden einige Beispiele als Stellvertreter für größere Gruppen und Charakteristiken vorgestellt. Diese werden im anschließenden Kapitel verglichen.

### 5.1 Lucy

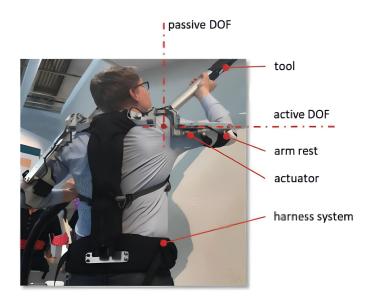

Dieses Exoskelett ist der wissenschaftlichen Arbeit [29] entnommen. Es wurde für diese Arbeit ausgewählt, da es die Kategorien der oberkörperbezogenen, druckluftbetriebenen und aktiv kontrollierten Exoskelette vertritt.

Motivation dieses Exoskeletts Die Hauptmotivation für Lucy ist Forschung. Ziel ist hierbei verschiedenen Ansätzen zur Industriellen Assistenz zu testen und evaluieren. Hierbei haben Effizienz, Komfort und Nutzerakzeptanz Vorrang.

Aufbau Lucy ist ein Exoskelett, welches sowohl aktive als auch passive Aktuatoren nutzt. Der aktive Teil wird durch Druckluftzylinder betrieben([39], [16], [27]). Diese sind an einen Drucklufttank oder, über eine Schlauchverbindung, an ein Druckluftsystem angeschlossen. Zweiteres führt zu einer Einschränkung der Mobilität, sowohl räumlich als auch hinsichtlich der Rotation um die eigene Achse.

Die Kraftübertragung geschicht entlang der Oberarme, des Rückens und der Hüfte. Hierbei sind die mechanischen Teile so nah wie möglich am Körper des Nutzers befestigt (Abb. 1). Die Körperabdeckung ist somit der Oberkörper.

Zudem wird Lucy aktiv gesteuert. Das bedeutet, dass der Nutzer, während er arbeitet, die Stärke der Unterstützung anpassen kann. Diese wird über Knöpfe am Griff des genutzten Werkzeugs eingestellt.

**Anwendungsbereich** Lucy ist der Klasse K1 (siehe K1 Ungewöhnliche Arbeitspositionen und Bewegungen) zuzuordnen. Es ist darauf ausgelegt, das Arbeiten mit Werkzeug, insbesondere das Überkopfschrauben oder -schleifen, zu erleichtern.

Industrien, in denen es verwendet werden kann, sind Automobilindustrie und Baugewerbe.

Es ist anzumerken, dass Lucy nicht kommerziell verwendet wurde. Es wurde lediglich in Studien, die einer Anwendung in der Industrie gleichen, getestet.

**Fähigkeiten und Limitierungen** Lucy ist in der Lage, eine beträchtliche Menge an Unterstützung zu bieten.

Eine erhöhte Geschwindigkeit im Arm, und damit ein Potenzial zur Produktivitätssteigerung, wurde gemessen. Dies bezieht sich jedoch nur auf einige Testfälle und müsste daher weiter untersucht werden.

Die aktive Kontrolle wurde von einigen Nutzern als ihr Kontrollgefühl steigernd beschrieben. Dies kann sich positiv auf die Nutzerakzeptanz auswirken.

**Abb. 1.** Aufbau des Exoskeletts Lucy. Beschriftung der aktiven und passiven Freiheitsgrade (hochskaliert aus [29]).

Zudem wurde erfolgreich gezeigt, dass gerade für Aufgaben mit variablem Gewicht eine aktive Steuerung von Vorteil ist und dass hierfür Knöpfe am Werkzeuggriff ausreichen.

Weitere Forschung an diesem Exoskelett wird benötigt, um Auswirkungen auf Muskeln und Bewegungen des ganzen Körpers zu beurteilen.

## 5.2 UMExoLEA

Dieses Exoskelett ist der wissenschaftlichen Arbeit [32] entnommen. Es wurde für diese Arbeit ausgewählt, da es die Kategorien der unterkörperbezogenen und durch Elektrizität betriebenen Exoskelette vertritt.

Motivation dieses Exoskeletts Dieses Exoskelett ist dafür gedacht, manuell arbeitenden Arbeitern in ihrer Mobilität zu assistieren, indem es bei Hebe- und Trageaufgaben das Gewicht vom Unterkörper und Rücken des Nutzers übernimmt.

Zudem wird es aktuell in der Forschung genutzt, um Designauswirkungen und Steuerungselemente für Unterkörper-Exoskelette zu erforschen [32].

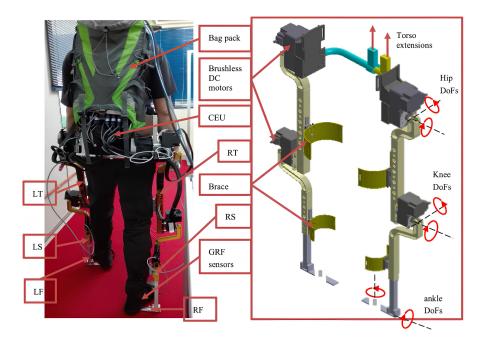

**Aufbau** UMExoLEA nutzt sowohl aktive als auch passive Aktuatoren. Es handelt sich um ein Unterkörper-abdeckendes Exoskelett. Jedes Bein besitzt 6 Freiheitsgrade: Einen aktiven und einen passiven Freiheitsgrad im Hüftgelenk, einen aktiven und einen passiven Freiheitsgrad im Kniegelenk und 2 passive Freiheitsgrade im Knöchel. Die aktiven Aktuatoren sind durch elektrische Motoren angetrieben. Dies hat zur Folge, dass ein Rucksack, in dem sich eine Batterie befindet, getragen werden muss. Die Abb. 2 verdeutlicht den Aufbau von UMExoLEA.

Das Exoskelett wird durch jeweils 2 Gurte an den Beinen, einem Gürtel und dem Rucksack mit dem Körper des Nutzers verbunden.

Die Steuerung des Exoskeletts findet mithilfe von Winkelpotentiometern, Grenzfrequenzsensoren und einem Algorithmus, welcher die benötigte Kraft abschätzt, statt. Der Nutzer hat keinen direkten Einfluss. Somit wird UMExoLEA passiv gesteuert.

Das Gewicht liegt ohne Rucksack bei ungefähr 11 kg. Hierbei wurde auf die Wahl der Aktuatoren, des Materials, der Energieeffizienz und der Komplexität geachtet, z. B. wurde auf aktive Knöchelgelenke verzichtet.

**Abb. 2.** Aufbau des Exoskeletts UMExoLEA. Beschriftung der 12 Freiheitsgrade (hochskaliert aus [32]).

**Anwendungsbereich** UMExoLEA ist der Klasse K2 (siehe K2 Manipulation schwerer Lasten) zuzuordnen. Seine Aufgaben sind Assistenz bei Hebe- und Trageaufgaben.

Die vorgesehenen Anwendungsbereiche sind Logistik und Be-/Entladen. Einige Beispielindustrien sind Produktion, Bau und Pflege.

Es ist anzumerken, dass es sich bei UMExoLEA bisher nur um einen Prototyp handelt, welcher in der Praxis nicht verwendet wurde.

**Fähigkeiten und Limitierungen** Das Exoskelett ist in der Lage bis zu 36% der Muskelaktivität sowohl beim Laufen als auch beim Knien zu reduzieren. Weitere Tests sind für eine Ganzkörperevaluation und genauere Messwerte nötig.

Es wird aktuell ein PC außerhalb des tragbaren Systems verwendet. Der Rucksack beinhaltet, abgesehen von der Batterie, ein Kommunikationsmodul. Somit besteht eine räumliche Abhängigkeit zu einem externen System.

Die Kraftkontrolle beruht auf einem Linearen-Quadratischen-Gaus-Drehmoment-Kontroller (linear-quadratic-gaussian-regulator), der möglichst genaue Gelenkwinkel benötigt. Diese werden allerdings nur vom Steuerungssystem abgeschätzt und sind somit nicht zuverlässig exakt. Zukünftige Arbeiten müssten die Drehmoment- und Gleichgewichtskontrolle durch einen neuen Ansatz, mit Rücksicht auf das gesamte dynamische System, ersetzen.

#### 5.3 Body Extender

Dieses Exoskelett wurde der wissenschaftlichen Arbeit [14] entnommen. Es wurde für diese Arbeit ausgewählt, da es die Kategorien der ganzkörperbezogenen und vollständig-aktuierten Exoskelette vertritt.

**Motivation dieses Exoskeletts** Der Body Extender ist in erster Linie als Forschungsplattform gedacht. Es sollen der Transport und die Handhabung von Lasten bis zu 50 kg unter schlechten Bedingungen, sowie die Interaktion zwischen Mensch und Exoskelett untersucht werden.

Der praktische Hintergedanke ist das Assistieren beim Heben und Manipulieren, indem es das volle Gewicht vom Körper des Nutzers nimmt.

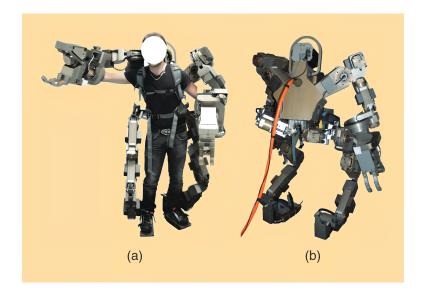

**Aufbau** Der Body Extender ist ein Ganzkörper-Exoskelett. Es besteht aus 2 Beinen mit jeweils 6 Freiheitsgraden, 2 Armen mit jeweils 4 Freiheitsgraden und 2 Parallelbackengreifern mit jeweils einem Freiheitsgrad. Alle 22 Freiheitsgrade sind aktiv und sind durch Elektromotoren angetrieben. Aus Wartungs-, Komplexitäts- und Kostengründen wurde hier für alle Gelenke der gleiche Motortyp verwendet.

Die Elektronik, Steuerung und Sensorik ist an Bord des Exoskeletts. Als Energiequelle wird ein Batteriesystem verwendet, welches sich aktuell noch getrennt auf dem Boden befindet (Abb. 3 b). Das System ermöglicht ca. 20 Stunden Betriebszeit bei einem durchschnittlichen Leistungsverbrauch von 900 Watt.

Der Nutzer ist an den Händen, Schultern, Füßen und der Hüfte mit dem Exoskelett verbunden (Abb. 3 a). Das Exoskelett trägt die 160 kg Eigengewicht selbst.

Die Steuerbefehle werden von 5 Sensoren an den Kontaktpunkten mit dem Körper des Nutzers und mithilfe von 2 Griffen für die Hände aufgenommen. Hierbei sind alle Eingaben, bis auf die Hände, passiv.

Abb. 3. Aufbau des Body Extender Exoskeletts (hochskaliert aus [14]).

**Anwendungsbereich** Der Body Extender ist der Klasse K2 (siehe K2 Manipulation schwerer Lasten) zuzuordnen. Er ist für die Manipulation und den Transport von schweren Massen in unbekannten Umgebungen gemacht.

Einige Beispielindustrien, in denen er verwendet werden kann, sind Logistik, Konstruktion und Flugzeug- bzw. Bootsbau. Zudem ist er für Notfall- und Bergungsarbeiten geeignet.

**Fähigkeiten und Limitierungen** Forschungsergebnisse haben gezeigt, dass der Body Extender bei Aufgaben wie Laufen oder Hocken bis zu 500 N Kraft aufwenden kann. Dies entspricht 50 kg pro Arm. Dabei ist eine Laufgeschwindigkeit von 0,5 m/s erreichbar. An dieser Geschwindigkeit ist zu erkennen, dass das System aktuell nicht auf Geschwindigkeit, sondern Kraft und das Heben von schweren Lasten ausgelegt ist.

Aktuell ist keine automatische Balancierung des Exoskeletts implementiert, der Nutzer muss diese selbst übernehmen. Das liegt an der vorläufigen Kontroller-Implementation. Diese setzt nur die Basisfunktionen wie Körperteilbewegungen, Gewichtsmanipulation und Laufen. Sie verfügt jedoch über keine hohe Genauigkeit. Dies hat zu Folge, dass Nutzer eine gewisse Trainingszeit benötigen und dass alle Tests und Studien mit entsprechenden Sicherheitsmaßnahmen durchgeführt wurden. Durch zukünftige Entwicklung von angemessenen Kontrollmechanismen und Algorithmen kann dieser Mangel ausgebessert werden [14]. Für stabile Manipulation und Zusammenarbeit beider Hände ist weitere Entwicklung und Forschung an Kontrollmechanismen notwendig.

An den meisten dieser Limitierungen wird laut den Schlussfolgerungen aus [14] gearbeitet, jedoch sind noch keine Veröffentlichungen zu finden.

## 5.4 AGADEXO Shoulder

Dieses Exoskelett wurde von Agade (Italien) entwickelt [2]. Es wurde für diese Arbeit ausgewählt, da es die Kategorien der schulterbezogenen und kommerziell erwerblichen Exoskelette vertritt.

Motivation dieses Exoskeletts Das Exoskelett ist auf die Assistenz bei Manipulation und Transport ausgelegt. Hierdurch sollen Unterbrechungen während Arbeitsschichten vermieden und kontinuierliche Produktion erreicht werden.

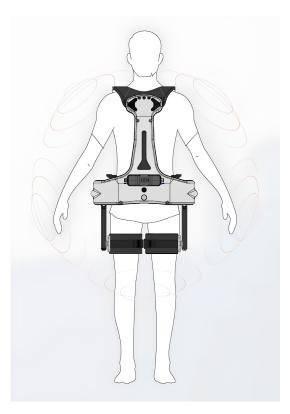

**Aufbau** Das AGADEXO Shoulder ist ein Oberkörper-Exoskelett, das speziell für die Entlastung von Schultern gemacht ist. Agadexo steht für "Anti-Gravity Active Device for Exoskelettons" [9].

Das Exoskelett hat 2 aktive Freiheitsgrade, welche das Heben der Arme über den Kopf unterstützen. Es werden quasi-aktive Aktuatoren benutzt, die zum Teil aus elastischen Mechanismen und zum anderen aus elektrischen Motoren bestehen. Durch diese Aktuatoren-Wahl wird weniger Strom benötigt und damit die Größe der Batterie reduziert, was das Gesamtgewicht auf 4 kg bringt.

Das Exoskelett ist aus Carbonfasern gefertigt, was zusätzlich zu dem geringen Gewicht den Tragekomfort erhöht. Es ist an der Hüfte, den Schultern und den Oberarmen mittels Gurten befestigt (Abb. 4).

Das Exoskelett ist mit kabellosen Armbändern verbunden, welche während Hebeaufgaben zur Erkennung von Lasten genutzt werden. Dies geschieht über einen Algorithmus, welcher anhand der Sensordaten der Armbänder und der Aktuatoren bestimmt, in welchem Modus sich das Exoskelett befinden soll. Somit ist das Exoskelett passiv kontrolliert. Der Modus, wenn keine Last erkannt wurde, ist Transparenz. Hier minimiert das Exoskelett seine Aktivität und spart dadurch Energie. Der Modus wechselt, sobald Lasten erkannt werden. Hier unterstützt das Exoskelett mit durchschnittlich 36 Nm Drehmoment, was ungefähr 25 kg Hebe- bzw. Haltekraft entspricht.

**Anwendungsbereich** Es handelt sich bei AGADEXO Shoulder um ein Exoskelett der Klasse K2 (siehe K2 Manipulation schwerer Lasten). Es ist auf Hebe-

**Abb. 4.** Aufbau des AGADEXO Shoulder Exoskeletts (Ausschnitt aus animierter 360° Ansicht [2]).

und Transportaufgaben ausgelegt. Einige Beispielindustrien sind Automobil, Logistik und Einzelhandel.

**Fähigkeiten und Limitierungen** Das Lastenerkennungssystem ermöglicht es, die Batterielaufzeit zu erhöhen, was wiederum zu einer kleineren Batterie, geringeren Kosten und höherem Tragekomfort führt. Die Batterielaufzeit beträgt bis zu 20 Stunden.

Während Materialmanipulationsaufgaben ist das Exoskelett in der Lage, automatisch das Level an Unterstützung anzupassen und damit den Nutzer optimal zu entlasten. Es kann bis zu 25 kg gegen die Schwerkraft heben und dabei bis zu 40% der Schultermuskelbeanspruchung übernehmen.

#### 5.5 Bes-hv

Dieses Exoskelett wurde von ULS Robotics Co. (China) entwickelt [37]. Es wurde für diese Arbeit ausgewählt, da es die Kategorien der unterkörperbezogenen, kommerziell erwerblichen und aktiv kontrollierten Exoskelette vertritt.

Motivation dieses Exoskeletts Bes-HV wurde entwickelt, um die Produktivität und Effizienz zu steigern, sowie die Arbeitsintensität zu verringern.

**Aufbau** Das Bes-HV ist ein Unterkörper-Exoskelett, welches speziell für die Unterstützung der Hüfte und des Rückens gebaut ist. Es ist in 2 Freiheitsgraden an der Hüfte aktiv angetrieben, einem für jedes Bein. Hier werden elektrische Motoren genutzt. Das Exoskelett ist an den Beinen, den Schultern (Abb. 5) und der Hüfte mittels Gurten befestigt, der Nutzer trägt hierbei das Gewicht hauptsächlich am Hüftgurt. Das Exoskelett wiegt 5,6 kg.

Es handelt sich um aktive Kontrolle, der Nutzer hat eine kleine Kontrolleinheit am rechten Schultergurt. Über diese lässt sich der Modus umstellen, es gibt "Gleichgewicht halten", "Helfen/Heben" und "Gehen". Zudem kann die Stärke der Assistenz eingestellt werden.

Es gibt eine 4G/5G-Schnittstelle, über welche drahtlos Echtzeit<br/>informationen ausgelesen werden können.

**Abb. 5.** Abbild des BES-HV Exoskeletts aus der Perspektive von Hinten (hochskalierter Ausschnitt aus [37]).

**Anwendungsbereich** Es ist der Klasse K2 (siehe K2 Manipulation schwerer Lasten) zuzuordnen. Es wird für das Heben und den Transport von Lasten verwendet. Einige Beispielindustrien sind Logistik, Montage und Handwerk.

**Fähigkeiten und Limitierungen** Bes-HV ist in der Lage, seinen Nutzer zu unterstützen, sodass dieser bis zu 30 kg mehr heben kann. Es reduziert dabei bis zu 60% der Last auf den unteren Rücken. Der Laufmodus ermöglicht eine Geschwindigkeit von 7,5 km/h. Die Akkulaufzeit beträgt 5-8 Stunden, je nach Betriebsmodus und Verwendung.

## 5.6 Guardian XO

Dieses Exoskelett wurde von der Sarcos Technology and Robotics Corporation (USA) entwickelt [33]. Es wurde für diese Arbeit ausgewählt, da es die Kategorien der ganzkörperbezogenen, kommerziell erwerblichen und vollständig-aktuierten Exoskelette vertritt.

Motivation dieses Exoskeletts Der Guardian verstärkt die Kraft des Nutzers, ohne seine Mobilität einzuschränken. Hierdurch sollen die Produktivität und die Sicherheit gesteigert werden.

**Aufbau** Der Guardian XO ist ein aktives Ganzkörper-Exoskelett. Es besitzt 24 Freiheitsgrade, alle sind durch elektrische Motoren angetrieben und somit aktiv. Hierzu wird ein schnell austauschbares Batteriesystem verwendet, was eine nahezu durchgängige Laufzeit ermöglicht. Die Steuerung wird durch 6 Sensoren an den Händen, Füßen, Rücken und Becken ermöglicht [18]. Zusätzlich kann das Level der Unterstützung durch einen kleinen Bildschirm beeinflusst werden [1]. Es handelt sich jedoch um passive Kontrolle, da das Kontrollsystem auf Bewegungen des Nutzers reagiert und das Exoskelett entsprechen bewegt.

Die Greifer bzw. Endeffektoren sind austauschbar und dadurch vom Nutzer für den gewünschten Anwendungsfall auswählbar. Zudem können die Arme in einer Position festgestellt werden, sodass der Nutzer seine Hände für Feinarbeiten verwenden kann. Dies ist in Abb. 6 zu sehen.

Das Exoskelett wiegt in etwa 70 kg, trägt sein Gewicht aber selbst [1]. Der Nutzer ist an Händen, Füßen, Hüfte und Oberkörper mit der Struktur verbunden.

Der Preis liegt bei ungefähr 100.000\$ pro Jahr. Dies beinhaltet einen von Sarcos gestellten Techniker, der die Exoskelette betreut [1].

Anwendungsbereich Es handelt sich um den Anwendungsfall der Klasse K2 (siehe K2 Manipulation schwerer Lasten), wobei auch, mit dem richtigen Greifer, die Klasse K3 (siehe K3 Unterstützung beim Montageaufwand) argumentiert

**Abb. 6.** Abbildung des Guardian XO aus 4 Perspektiven (Ausschnitt aus Werbebroschüre [34]).

werden kann. Aufgaben können dabei von Manufaktur, über Außendienst bis zu Logistik reichen.

Einige Beispielindustrien sind Fertigung, Automobil, See- und Luftfahrt. Zudem kann dieses Exoskelett auch in militärischen Anwendungen genutzt werden.

Fähigkeiten und Limitierungen Der Guardian ermöglicht es einer einzelnen Person, bis zu 90 kg ohne die entsprechende Müdigkeit oder Anstrengung zu heben und damit die Sicherheit und Produktivität zu steigern. Dies entspricht einer Kraftsteigerung von bis zu 2000%, wobei 100% der Last auf die Exoskelettstruktur übertragen werden.

Der Freihand-Modus ermöglicht es dem Nutzer, die Exoskelettarme unabhängig von deren Belastung festzustellen und seine eigenen Arme frei zu nutzen.

Sollte der Guardian unerwartet einen Energieversorgungsausfall erfahren, so ist die Hardware auf passives Bremsen und einen sicheren Stopp ausgelegt.

Die Reaktionsgeschwindigkeit des Kontrollsystems ist hoch genug, dass der Nutzer sein Gleichgewicht selber halten kann und kein Gleichgewicht-Kontrollalgorithmus benötigt wird [1].

Guardian ermöglicht die Nutzung von zusätzlicher Schutzausrüstung.

In Tests wurde festgestellt, dass Nutzer bis zu 50 kg Gewicht tragen konnten, es sich jedoch nur wie ungefähr 6 kg anfühlt [18].

# 6 Vergleich/Gegenüberstellung

Im vorigen Kapitel wurde sechs Exoskelette, welche verschiedene Kriterien und Gruppen vertreten, vorgestellt. Hier werden diese Exoskelette stellvertretend für ihre Gruppen verglichen.

Die Tabelle 1 zeigt einige wichtige Kriterien der Exoskelette in direktem Vergleich.

| Exo Lucy UMExoLEA Body Agadexo BES-1                                                            | HV Guardian          |

|-------------------------------------------------------------------------------------------------|----------------------|

| Kriterium Budy Chillion Body Right Body Right Body                                              | XO                   |

| Preis                                                                                           | 100.000\$            |

|                                                                                                 | pro Jahr             |

| Energieart Pneumatisch Elektrisch Elektrisch Elektrisch Elektrisch                              |                      |

| Körper- Oberkörper Unterkörper Ganzkörper Schulter Hüfte                                        | e/ Ganzkörper        |

| abdeckung                                                                                       | en                   |

| Mobilitätslevel Schlauch- Batterie- Externe integrierte integr                                  | rierte schnell aus-  |

| gebunden Rucksack Batterie Batterie Batte                                                       | erie tauschbare      |

|                                                                                                 | Batterie             |

| Aktivitätslevel 2 aktiv, 4 aktiv, 22 aktiv 2 quasi-2 akti                                       | iv 24 aktiv          |

| in 2 Passiv 8 passiv aktiv,                                                                     |                      |

| Freiheitsgraden 2 passiv                                                                        |                      |

| Anwendungs- K1 K2 K2 K2 K2                                                                      | K2 mit Ten-          |

| bereich                                                                                         | denz zu K3           |

| Motivation Forschung Hebe- und Forschung Manipula- Produ                                        | ukti- Kraft-         |

| an indus- Trageaufga- an Mensch- tion und vität,                                                | steigerung,          |

| trieller ben, Exoskelett Transport Effizie                                                      | enz, Produkti-       |

| Assistenz Unterkörper Interaktion, von Lasten, Arbei                                            | its- vität,          |

| und Rücken Transport kontinuier- intens                                                         | sität Sicherheit     |

| entlasten und Hand-liche Pro-verrin                                                             | ngern                |

| habung von duktion                                                                              |                      |

| Lasten                                                                                          |                      |

| Kraftaufwand         -         36%         der         -         40%         Schul-         60% | der 100% der         |

| Reduktion (des Muskelakti- Last                                                                 | aufLasst             |

| Nutzers) vität beanspru- unter                                                                  | en                   |

| chung Rücke                                                                                     |                      |

|                                                                                                 | g mehr 90 kg         |

| Exoskeletts Arm heben                                                                           | n                    |

| Gewicht - 11 kg (ohne 160 kg 4 kg 5,6 kg                                                        | g 70 kg              |

| Batterie)                                                                                       |                      |

|                                                                                                 | merziell Kommerziell |

| keine Praxis mit Praxis- Prototyp                                                               |                      |

| Bezug                                                                                           |                      |

Tabelle 1. Vergleich der vorgestellten sechs Exoskelette.

"-" bedeutet, dass keine Informationen vorliegen.

#### 6.1 Vergleich der Energiearten

Die Energieart und die daraus folgende Energieversorgung sind wichtige Faktoren in der Planung und im Aufbau eines aktiven Exoskeletts.

Besonders ist hierbei die Effizienz relevant. Energie muss möglichst effizient transportiert und am Ziel in meist kinetische Energie umgewandelt werden. Darum haben sich bei aktiven Systemen vor allem Elektrizität (UMExoLEA, Body Extender, AGADEXO Shoulder, Bes-hv, Guardian XO) und Druckluft (Lucy) durchgesetzt.

Zudem ist Zugänglichkeit ein wichtiges Kriterium der Energiewahl, hiermit ist die Speicherung der Energie gemeint. Der Energiespeicher muss immer mit dem Exoskelett verbunden und somit in dessen Nähe sein. Eine Batterie eignet sich hierfür, da sie relativ kompakt eine große Menge an Energie speichern kann. Ein Drucklufttank hingegen kann Energie nicht so kompakt speichern, was zu einem größeren Tank oder einer geringeren Laufzeit führt.

Schlauch-gebundene Systeme (Lucy, Body Extender) sind hiervon ausgenommen. Hier ist relevant, welche Energieart in der näheren Umgebung vertreten ist. Elektrizität ist dabei häufiger zu finden, Druckluft Infrastruktur muss meist extra gebaut werden oder ist nur an bestimmten Orten wie Fabrikgebäuden zu finden. Zudem haben schlauchgebundene Systeme eine eingeschränkte Mobilität, sowohl was Distanz zum Anschluss, als auch Rotationsfreiheit um die eigene Achse angeht.

Wird ein quasi-aktiver Krafterzeuger genutzt (AGADEXO Shoulder), so ist die Energieart des aktiven Teils noch immer relevant, es wird durch den passiven Teil lediglich eine Teillast übernommen und umverteilt.

#### 6.2 Kraft des Exoskeletts in Relation zur Körperabdeckung

Die Körperabdeckung ist für ein Exoskelett ausschlaggebend. Sie bestimmt den Betrag an Kraft, welche das Exoskelett aufbringen und damit seinem Nutzer abnehmen kann. Hierbei lassen sich Exoskelette in 2 Gruppen aufteilen:

Zum einen Exoskelette, die am Nutzer befestigt sind und von ihm getragen werden (Lucy, AGADEXO Shoulder, Bes-hv). Diese assistieren dem Nutzer, indem sie das Gewicht, welches zu tragen ist, umverteilen. Die Limitierung ist meist, wie viel der Nutzer komfortabel mit den Beinen heben kann. Ein Beispiel für ein solches System ist AGADEXO Shoulder, welches das Gewicht von den Armen auf den Rücken umverteilt und somit die Oberarme und Teile des oberen Rückens entlastet.

Dem gegenüber stehen Exoskelette, welche ihr Gewicht selbst tragen und in welche der Nutzer meist hinein geschnallt wird (UMExoLEA, Body Extender, Guardian XO). Diese ermöglichen es, größere Lasten zu heben, da der Nutzer nicht mehr das Limit festsetzt. Er steuert lediglich das Exoskelett, trägt aber selbst kaum Gewicht. Die neue Limitierung ist die Kraft, welche durch die Aktuatoren erzeugt werden kann. Diese kann theoretisch errechnet werden und dient somit als Sicherheitsrichtlinie und meist auch als softwarelimitierter Maximalwert.

### 6.3 Aktivitätslevel in Relation zum Gewicht

Eine interessante Gegenüberstellung ist das Aktivitätslevel, welches hier über die Anzahl von aktiven Freiheitsgraden gemessen wird, und das Gewicht eines Exoskeletts. Das Gewicht steigt, je mehr Freiheitsgrade das Exoskelett implementiert und vor allem je mehr Freiheitsgrade es aktiv unterstützt. Dies lässt sich wie folgt erklären: Jeder Freiheitsgrad benötigt Hardware und jeder aktive Freiheitsgrad zusätzlich einen Krafterzeuger. Dies sieht man im Vergleich von Bes-hv, mit 2 Freiheitsgraden und 5,6 kg, zu UMExoLEA, mit 4 aktiven Freiheitsgraden und 11 kg. Die passiven Freiheitsgrade sind hier vernachlässigbar, da sie nicht viel mehr als die umliegende Struktur wiegen.

Speziell zu betrachten sind quasi-aktive Krafterzeuger. Diese ermöglichen einen geringeren aktiven Erzeugeranteil und somit eine Gewichtsreduktion, da weniger Hardware benötigt wird. Dies ist im Vergleich zwischen Bes-hv, welches 2 Freiheitsgrade aktiv unterstützt und 5,6 kg wiegt, und AGADEXO Shoulder, welches 2 Freiheitsgrade quasi-aktiv unterstützt und 4 kg wiegt, gut zu erkennen.

Implementationsdetails, Energieart und Körperabdeckungsbereich beeinflussen diese Gegenüberstellung, somit sind diese Erkenntnisse nicht universell anwendbar, können aber unter Vorsicht als Richtlinie verwendet werden.

### 6.4 Anwendungsbereich

Ein Exoskelett kann nach seinem Anwendungsbereich kategorisiert werden. Hierzu wurden im Kapitel 3 speziell drei Klassen definiert. Anhand dieser kann man Exoskelette ebenfalls vergleichen. Der Vergleich ist jedoch nicht ausreichend genau, da die Menge an Anwendungsbereichen so groß ist, dass eine Einteilung in drei Klassen nicht ausreicht. Für einen genaueren Vergleich müsste man diese 3 Klassen weiter auftrennen, z. B. die Klasse K2 (siehe K2 Manipulation schwerer Lasten) nochmals anhand des Betrags der erzeugten Kraft oder der Körperabdeckung spalten. Dies führt jedoch zu einer höheren Komplexität, welche in dieser Arbeit durch die getrennte Betrachtung dieser zusätzlichen Aspekte umgangen wurde. Von der Klassenzuordnung zweier Exoskelette kann man nicht auf Ähnlichkeiten in deren Aufbauten oder Industriezweigen schließen. Ein Beispiel hierfür sind AGADEXO Shoulder und Guardian XO, diese unterscheiden sich in ihrem Aufbau sehr. Dennoch hilft diese Klassenzuordnung beim groben Einordnen und Unterscheiden.

#### 6.5 Kosten vs. Nutzen

Für Unternehmen und Firmen besonders relevant ist die Kosten-Nutzen-Abschätzung.

Der Nutzen von Exoskeletten wurde bereits in Kapitel 2 behandelt.

Die Kosten haben eine große Spanne zwischen verschiedenen Exoskeletten. Faktoren in der Preisrechnung sind Körperabdeckung, Energieversorgung, Kraft des Exoskeletts, Aktivitätslevel und noch viele weitere. Ein Teil der hier behandelten Exoskelette werden in der Forschung entwickelt und genutzt (Lucy, UMExoLEA, Body Extender), diesen kann man keinen Preis zuordnen.

# 7 Fazit

Diese Arbeit zeigt eine Vielzahl an Anwendungsbereichen und Industrien auf, welche von Exoskeletten profitieren können.

Es wurden verschiedene Arten von aktiven Exoskeletten vorgestellt und anhand einiger Beispiele verglichen.

Exoskelette wurden überwiegend positiv dargestellt. Es gibt jedoch auch einige Herausforderungen, die noch zu überwinden sind.

Die Akzeptanz des Nutzers ist wichtig. Diese hängt vom Tragekomfort, der Einfachheit der Nutzung, physiologischen Auswirkungen auf den Körper und noch einigen weiteren Faktoren ab. Die Akzeptanz der Gesellschaft ist ebenfalls relevant. Diese hängt wiederum von der Akzeptanz vieler Nutzer, aber auch von der Akzeptanz der Firmenvorstände und dem Meinungsbild der Gesellschaft, ab. Ein Exoskelett kann noch so viele Vorteile haben, wird es nicht akzeptiert, so wird es nicht effektiv genutzt und führt zu einer schlechten Arbeitsmoral und geringerer Produktivität.

Ein weiterer Punkt ist die bereits angesprochene Kosten-Nutzen-Abschätzung. Fällt diese für Firmen nicht profitabel aus, werden Exoskelette und ihre Vorteile für Arbeiter nicht zur Verwendung kommen.

Die Energieversorgung hat in den letzten Jahren große Fortschritte gemacht, dennoch muss ein Exoskelett in regelmäßigen Intervallen an eine Energiequelle, z. B. ein Stromnetz, angeschlossen werden. Dies schränkt die Mobilität und Betriebsdauer ein.

Dies sind Punkte, die bei der Investition und Nutzung von Exoskeletten in Betracht gezogen werden müssen.

# Literatur

- 1. Ackerman, E.: Sarcos demonstrates powered exosuit that gives workers super strength. https://spectrum.ieee.org/sarcos-guardian-xo-powered-exoskeleton (2024), accessed: 31.1.2024

- Agade: Human-tailored robotics agadexo shoulder. https://agade-exoskeletons. com/en/product/ (2024), accessed: 29.1.2024

- Aguirre-Ollinger, G., Colgate, J.E., Peshkin, M.A., Goswami, A.: Active-impedance control of a lower-limb assistive exoskeleton. In: 2007 IEEE 10th International Conference on Rehabilitation Robotics. pp. 188–195 (2007). https://doi.org/10. 1109/ICORR.2007.4428426

- Alabdulkarim, S., Nussbaum, M.A.: Influences of different exoskeleton designs and tool mass on physical demands and performance in a simulated overhead drilling task. Applied Ergonomics 74, 55–66 (2019). https://doi.org/https://doi.org/ 10.1016/j.apergo.2018.08.004, https://www.sciencedirect.com/science/article/pii/ S0003687018302618

- Auxivo AG: Deltasuit das Überkopf-exoskelett für erweiterte schulterunterstützung. https://www.auxivo.com/de/deltasuit (2024), accessed: 3.2.2024

- Bogue, R.: Exoskeletons a review of industrial applications. Industrial Robot: An International Journal 45(5), 585–590 (Jan 2019). https://doi.org/10.1108/ IR-05-2018-0109, https://doi.org/10.1108/IR-05-2018-0109

- Brian D. Lowe, W.G.B., Peterson, D.R.: Astm f48 formation and standards for industrial exoskeletons and exosuits. IISE Transactions on Occupational Ergonomics and Human Factors 7(3-4), 230–236 (2019). https://doi.org/10.1080/24725838. 2019.1579769, https://doi.org/10.1080/24725838.2019.1579769

- Christensen, S., Bai, S., Rafique, S., Isaksson, M., O'Sullivan, L., Power, V., Virk, G.S.: Axo-suit-a modular full-body exoskeleton for physical assistance. In: Mechanism Design for Robotics: Proceedings of the 4th IFToMM Symposium on Mechanism Design for Robotics. pp. 443–450. Springer (2019)

- 9. Christensen, S.S.: User-centered modelling and design of assistive exoskeletons (2023)

- Deng, M.J., Wang, Z., He, H.H., Xue, Y.: Design and weight lifting analysis of a strengthen upper limb exoskeleton robot. In: Industrial Design and Mechanics Power II. Applied Mechanics and Materials, vol. 437, pp. 695–699. Trans Tech Publications Ltd (12 2013). https://doi.org/10.4028/www.scientific.net/AMM.437. 695

- EU-OSHA: Muskel- und skeletterkrankungen. https://osha.europa.eu/de/themes/ musculoskeletal-disorders (2023), accessed: 14.12.2023

- European Agency for Safety and Health at Work and Podniece, Z and Pinder, A and Yeomans, L: Work-related musculoskeletal disorders – Back to work report. Publications Office (2007)

- 13. exoIQ GmbH: Passive vs. aktive exoskelette funktionsweisen und charakteristika. https://www.exoiq.com/wissen/ passive-vs-aktive-exoskelette-funktionsweisen-und-charakteristika (2024), accessed: 8.1.2024

- Fontana, M., Vertechy, R., Marcheschi, S., Salsedo, F., Bergamasco, M.: The body extender: A full-body exoskeleton for the transport and handling of heavy loads. IEEE Robotics Automation Magazine 21(4), 34–44 (2014). https://doi.org/10. 1109/MRA.2014.2360287

- Gopura, R.A.R.C., Kiguchi, K.: Mechanical designs of active upper-limb exoskeleton robots: State-of-the-art and design difficulties. In: 2009 IEEE International Conference on Rehabilitation Robotics. pp. 178–187 (2009). https://doi.org/10. 1109/ICORR.2009.5209630

- Heo, U., Kim, S.J., Kim, J.: Backdrivable and fully-portable pneumatic back support exoskeleton for lifting assistance. IEEE Robotics and Automation Letters 5(2), 2047–2053 (2020). https://doi.org/10.1109/LRA.2020.2969169

- 17. Hyundai Motor Deutschland GmbH: Hyundai erleichtert Überkopfarbeit mit tragbarer roboterweste. https://www.hyundai.news/de/articles/press-releases/ hyundai-erleichtert-ueberkopfarbeit-mit-tragbarer-roboterweste.html (2024), accessed: 3.2.2024

- Kim, S., Srinivasan, D., Nussbaum, M.A., Leonessa, A.: Human gait during level walking with an occupational whole-body powered exoskeleton: Not yet a walk in the park. IEEE Access 9, 47901–47911 (2021). https://doi.org/10.1109/ACCESS. 2021.3068836

- soo Kim, W., hoon Lee, S., don Lee, H., nam Yu, S., soo Han, J., soo Han, C.: Development of the heavy load transferring task oriented exoskeleton adapted by lower extremity using qausi - active joints. In: 2009 ICCAS-SICE. pp. 1353–1358 (2009)

- Lee, H., Ferguson, P.W., Rosen, J.: Chapter 11 lower limb exoskeleton systems—overview. In: Rosen, J., Ferguson, P.W. (eds.) Wearable Robotics, pp. 207–229. Academic Press (2020). https://doi.org/https://doi.org/10.1016/ B978-0-12-814659-0.00011-4, https://www.sciencedirect.com/science/article/pii/ B9780128146590000114

- Lee, H., Kim, W., Han, J., Han, C.: The technical trend of the exoskeleton robot system for human power assistance. International Journal of Precision Engineering and Manufacturing 13(8), 1491–1497 (Aug 2012). https://doi.org/10.1007/ s12541-012-0197-x, https://doi.org/10.1007/s12541-012-0197-x

- 22. de Looze, M.P., Krause, F., O'Sullivan, L.W.: The potential and acceptance of exoskeletons in industry. In: González-Vargas, J., Ibáñez, J., Contreras-Vidal, J.L., van der Kooij, H., Pons, J.L. (eds.) Wearable Robotics: Challenges and Trends. pp. 195–199. Springer International Publishing, Cham (2017)

- Martinez, F., Retolaza, I., Pujana-Arrese, A., Cenitagoya, A., Basurko, J., Landaluze, J.: Design of a five actuated dof upper limb exoskeleton oriented to workplace help. In: 2008 2nd IEEE RAS EMBS International Conference on Biomedical Robotics and Biomechatronics. pp. 169–174 (2008). https://doi.org/10.1109/ BIOROB.2008.4762788

- Martini, M., Botta, J.: Iron man am arbeitsplatz?–exoskelette zwischen effizienzstreben, daten-und gesundheitsschutz. Neue Zeitschrift für Arbeitsrecht pp. 625– 637 (2018)

- Matsubara, T., Uchikata, A., Morimoto, J.: Full-body exoskeleton robot control for walking assistance by style-phase adaptive pattern generation. In: 2012 IEEE/RSJ International Conference on Intelligent Robots and Systems. pp. 3914–3920 (2012). https://doi.org/10.1109/IROS.2012.6385528

- McFarland, T., Fischer, S.: Considerations for industrial use: A systematic review of the impact of active and passive upper limb exoskeletons on physical exposures. IISE Transactions on Occupational Ergonomics and Human Factors 7(3-4), 322–347 (2019). https://doi.org/10.1080/24725838.2019.1684399, https://doi.org/ 10.1080/24725838.2019.1684399

- Nassour, J., Zhao, G., Grimmer, M.: Soft pneumatic elbow exoskeleton reduces the muscle activity, metabolic cost and fatigue during holding and carrying of loads. Scientific Reports 11(1), 12556 (Jun 2021). https://doi.org/10.1038/s41598-021-91702-5, https://doi.org/10.1038/s41598-021-91702-5

- 28. Orthexo.de Ratgeber für Neuroorthopädie und Exoskelette UG: Industrielle exoskelette: Die 77+ besten exoskelette für die industrie, logistik, handwerk und pflege (2023). https://orthexo.de/exoskelette/industrielle-exoskelette/ ?phaina-interviewID=49IA7hgXIr423ekDyGXcz (2023), accessed: 14.12.2023

- Otten, B.M., Weidner, R., Argubi-Wollesen, A.: Evaluation of a novel active exoskeleton for tasks at or above head level. IEEE Robotics and Automation Letters 3(3), 2408–2415 (2018). https://doi.org/10.1109/LRA.2018.2812905

- RB3D: exo back by rb3d. https://www.rb3d.com/en/exosquelettes/exoback (2024), accessed: 3.2.2024

- Redaktion Automotive-Aktuell.de: Wissenswertes über das exoskelett in der automobilindustrie. https://www.automotive-aktuell.de/ wie-kommen-exoskelette-in-der-automobilindustrie-zum-einsatz-34483.html (2023), accessed: 14.12.2023