# **Broadband BPSK Transmitter Systems with Beam Steering at mm-Wave Frequencies**

Zur Erlangung des akademischen Grades eines

**Doktors der Ingenieurwissenschaften (Dipl.-Ing.)**

von der KIT-Fakultät für

Elektrotechnik und Informationstechnik

des Karlsruher Instituts für Technologie (KIT)

angenommene

## **DISSERTATION**

von

**M. Sc. Joachim Nikolaus Hebeler**

geb. am 18.05.1994 in Homberg (Efze)

Tag der mündlichen Prüfung:

02.12.2024

Hauptreferent:

Korreferent:

Prof. Dr.-Ing. Dr. h.c. Thomas Zwick

Prof. Dr. sc. techn. habil. Frank Ellinger

# Abstract

This thesis explores the uncharted territory of circuits, packaging solutions, and antenna systems for broadband high-datarate systems operating in the sub-THz spectrum. The thesis first presents the necessary theoretic basics and investigations to fully contextualize the design task. Further, the circuit design of the crucial power amplifier is unveiled and discussed. Next, the antenna choices are evaluated and the chosen designs are meticulously investigated. Based on this, the packaging of the whole transmitter is analyzed and detailed. The work concludes with the measurements of the implemented transmitters, revealing the groundbreaking performance of the realized systems.

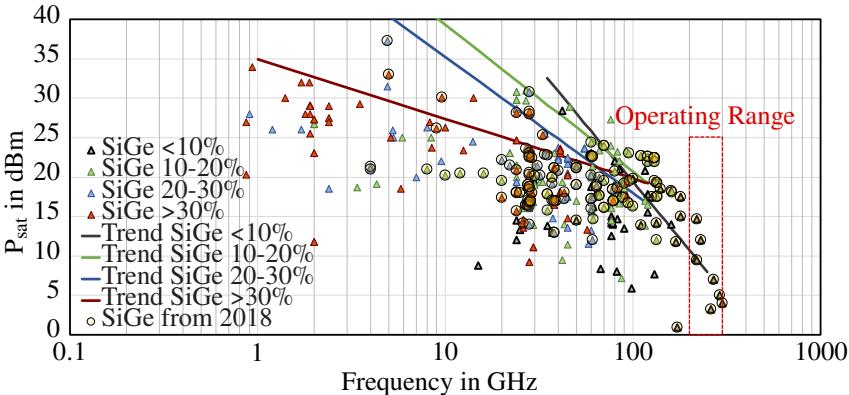

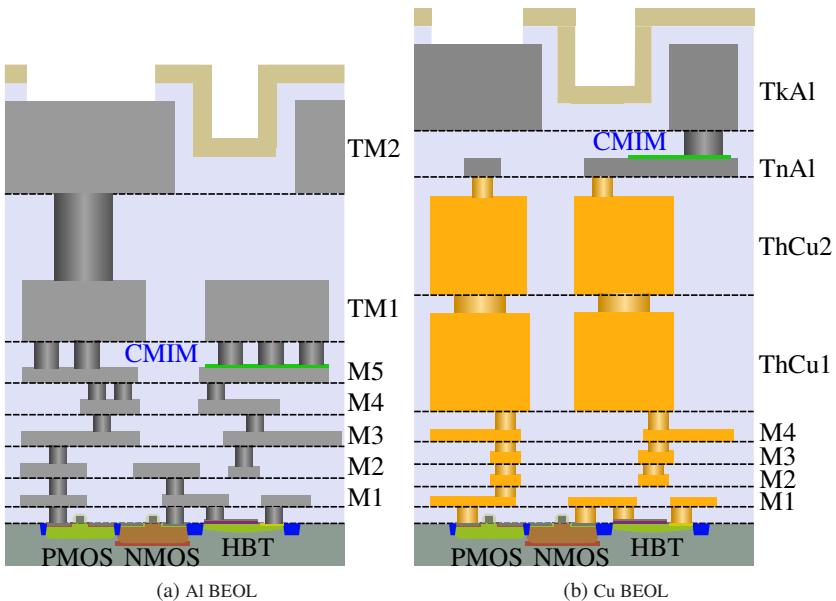

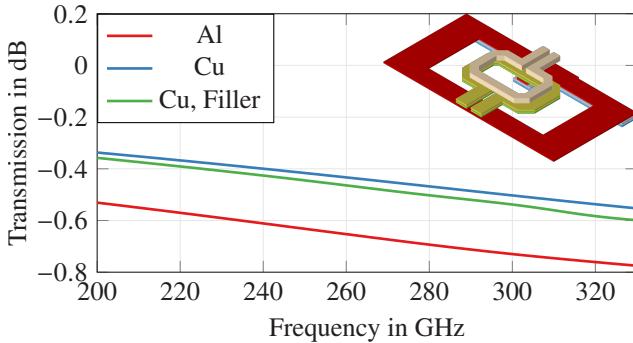

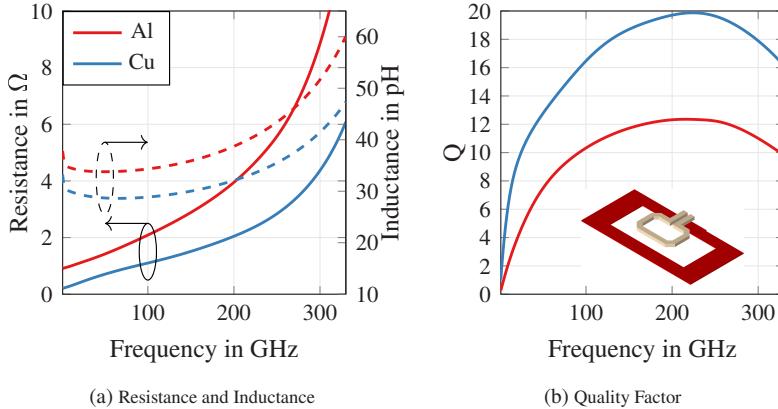

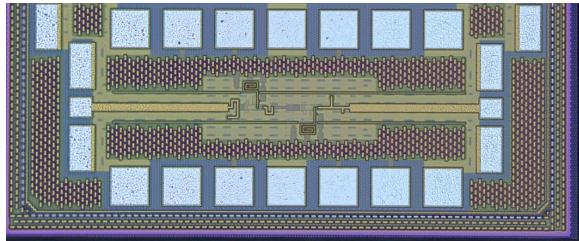

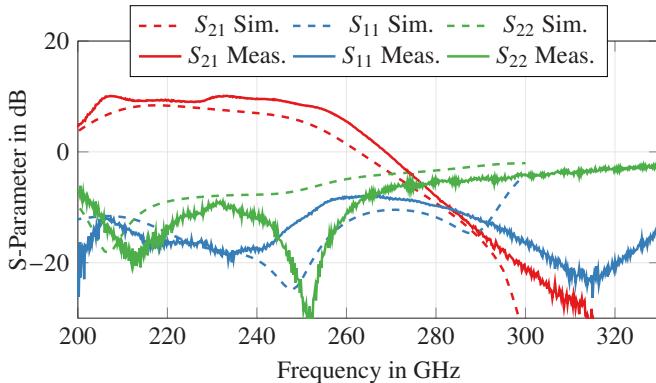

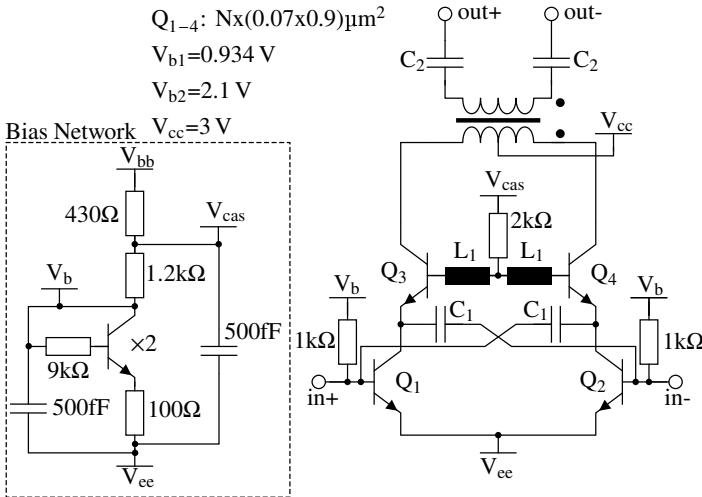

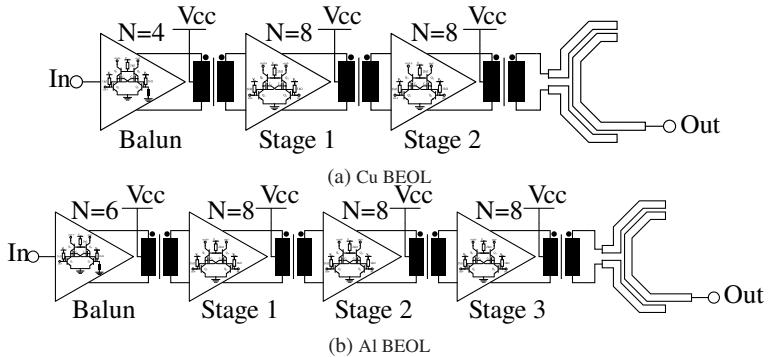

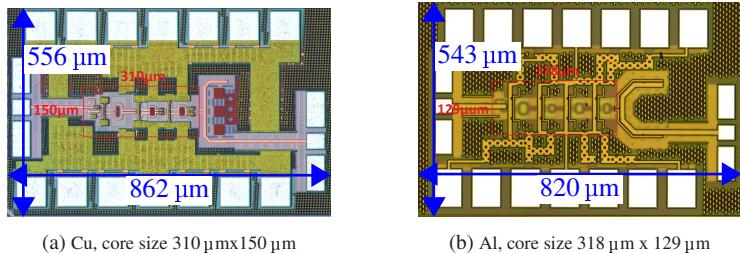

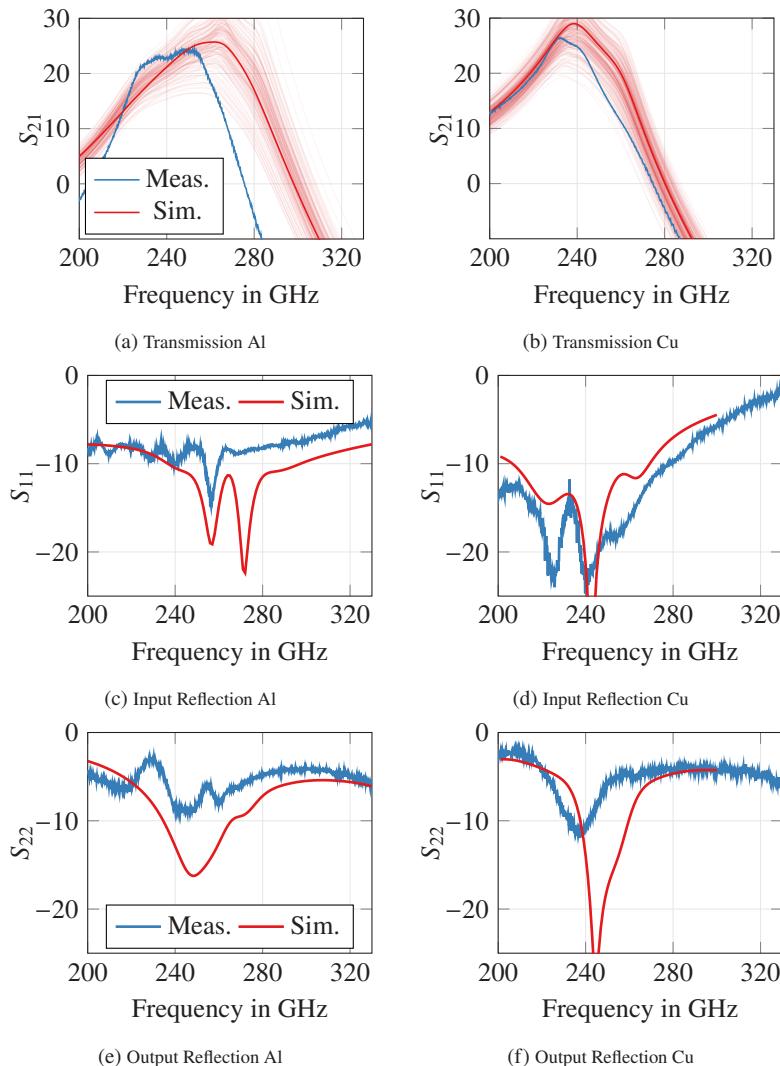

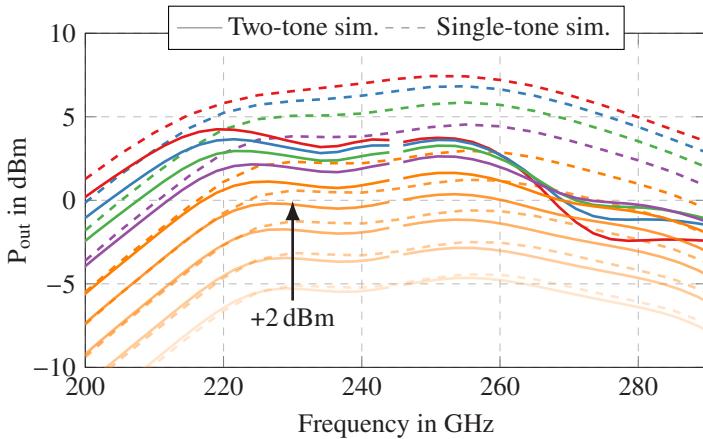

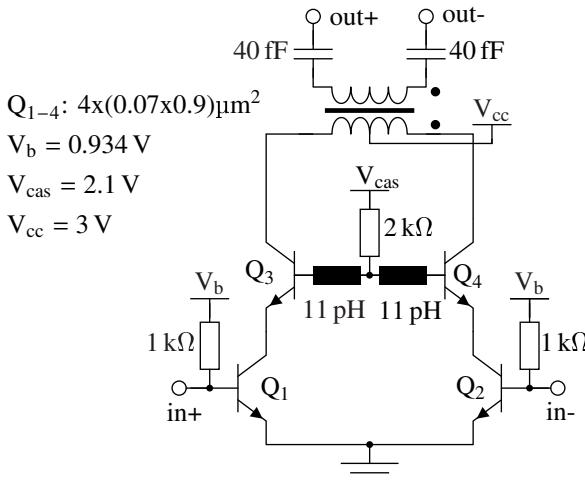

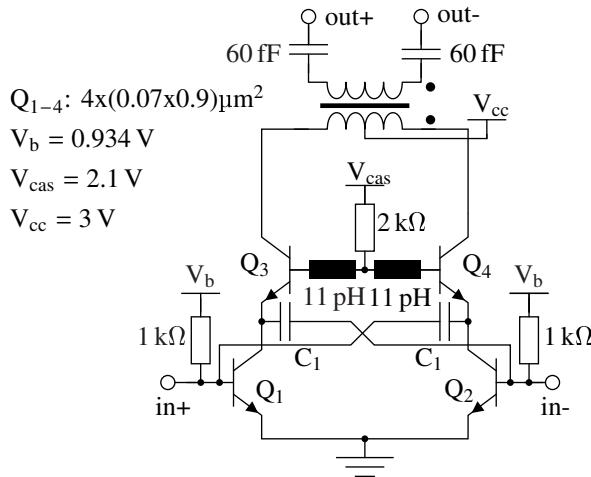

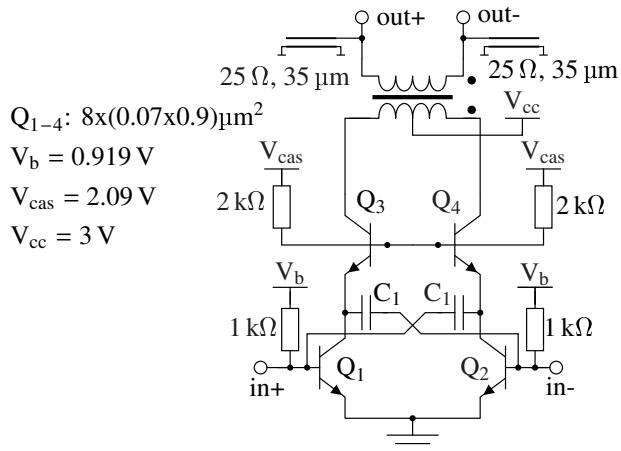

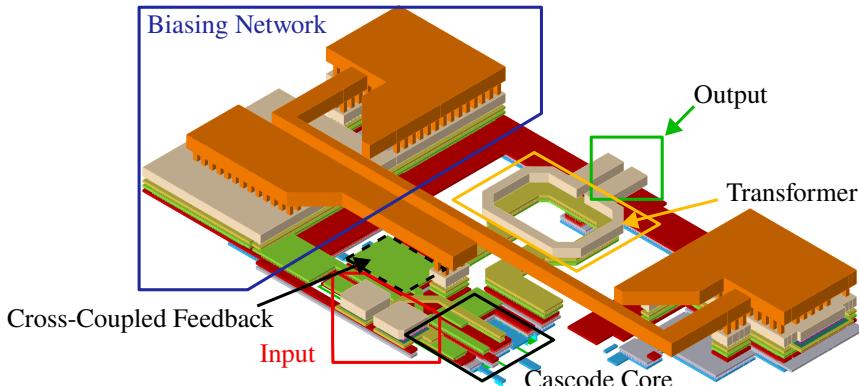

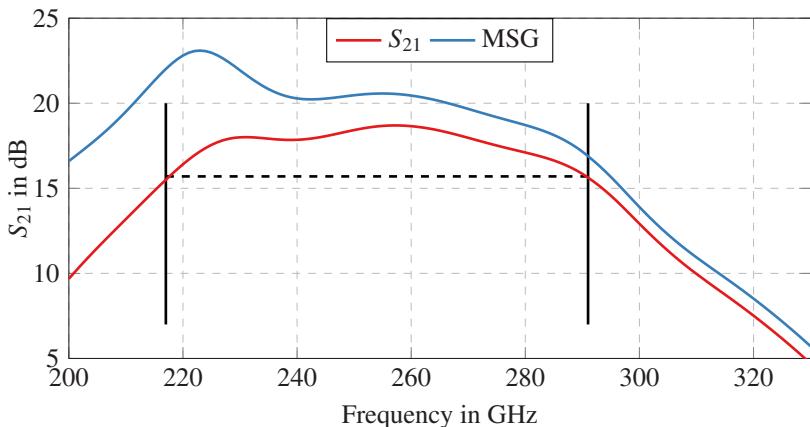

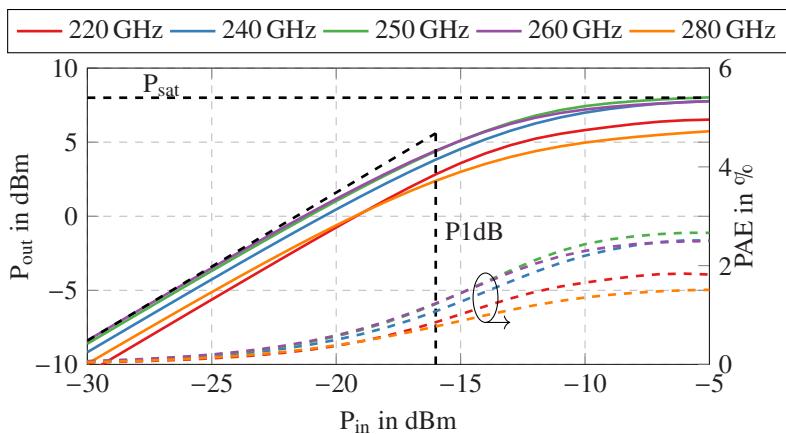

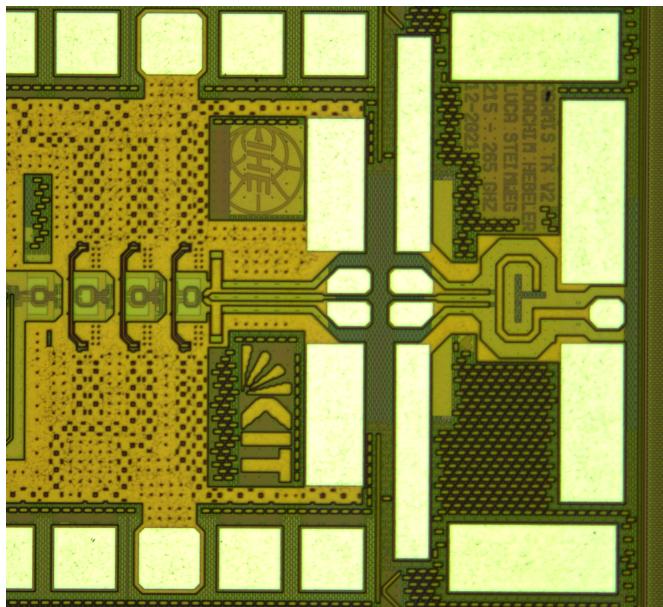

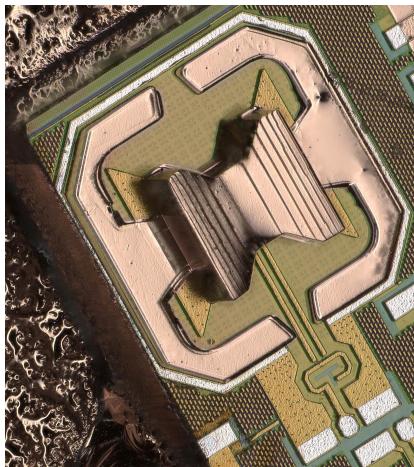

The sub-THz frequency range between 100 GHz to 300 GHz offers a vast spectrum with currently little regulation. Firstly, principle investigation of the physical constraints is done to evaluate influences such as signal to noise ratio (**SNR**) and harmonic spurs. Further, limitations in the available measurement equipment are investigated to highlight issues in performance evaluation. A compact and efficient power amplifier (**PA**) is designed by carefully analyzing the state of the art of published **PAs** in the employed frequency range. Concluding this analysis, the decision is made to implement a pseudo-differential cascode topology in silicon-germanium (**SiGe**) as it offers the best trade-off between radio frequency (**RF**) performance, system integration and integration density. Based on this decision, two available metal stack-ups are analyzed and compared against each other to guide the choice of the best possible technology. With the technology choice fixed, the multi-stage design is investigated. The design is frequency-staggered and optimized for the necessary bandwidth and output power by employing transformer-coupled stages and carefully implemented feedback paths. Analysis of the whole system shows the excellent performance of the **PA**, which exceeds the state of the art in bandwidth, non combined output power, and compactness. Simulation and physical verification show a bandwidth of 74 GHz and an output power of 8 dBm in at a very small chip core area of 0.045 mm<sup>2</sup>.

A novel approach within this thesis is the usage of a differential **RF** inter-

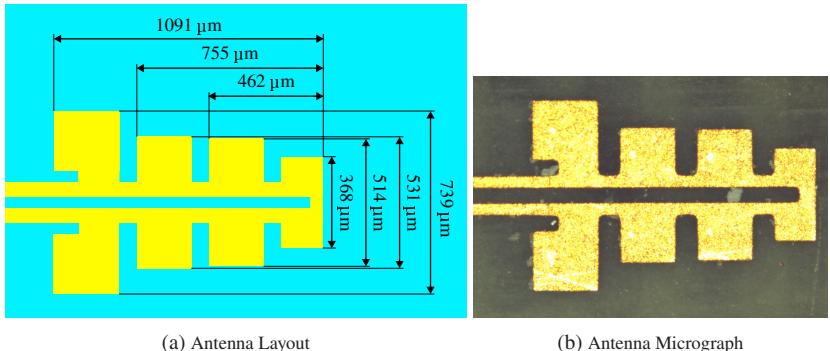

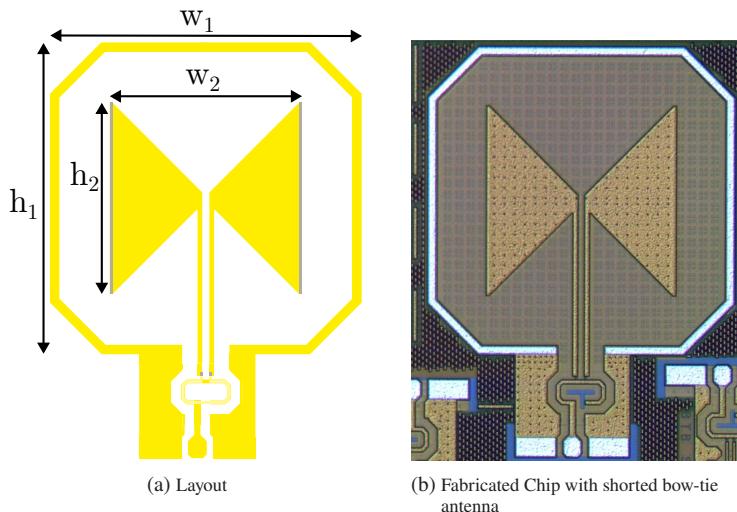

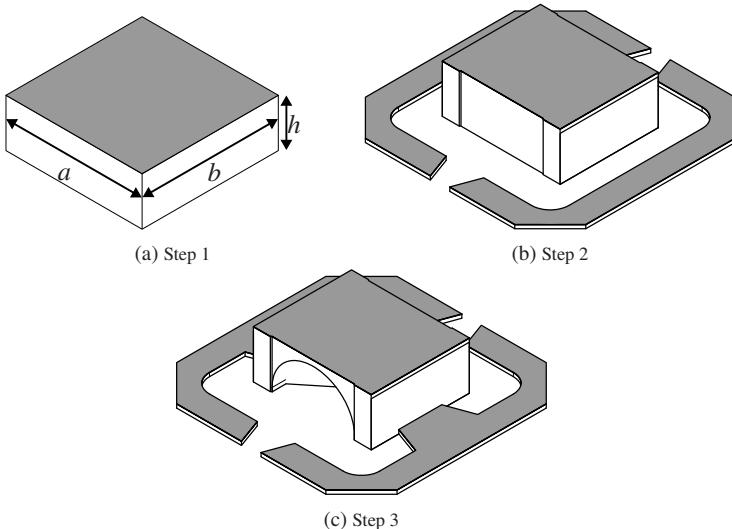

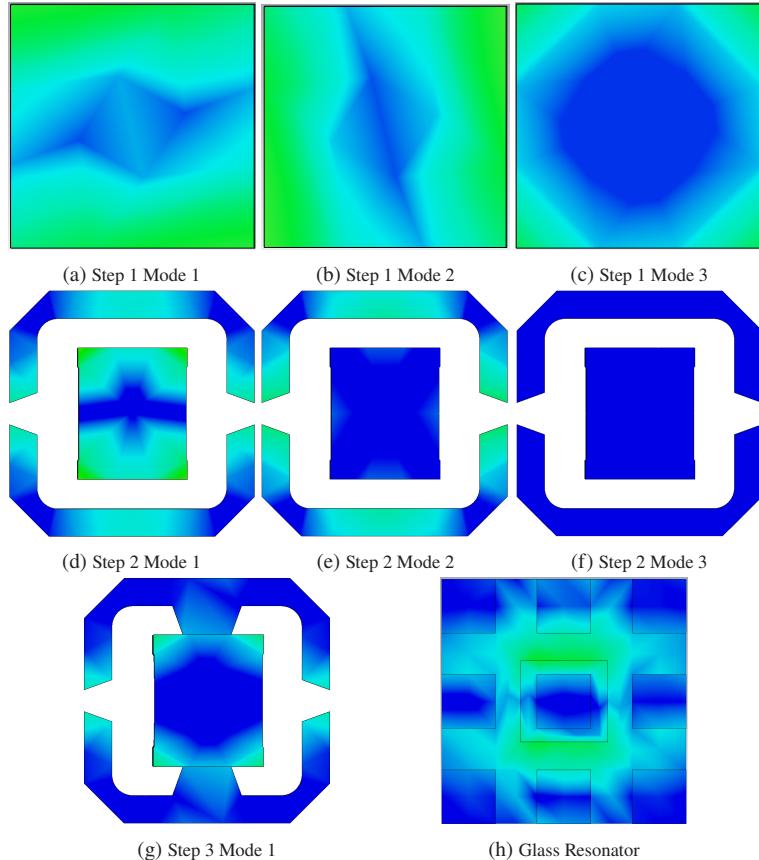

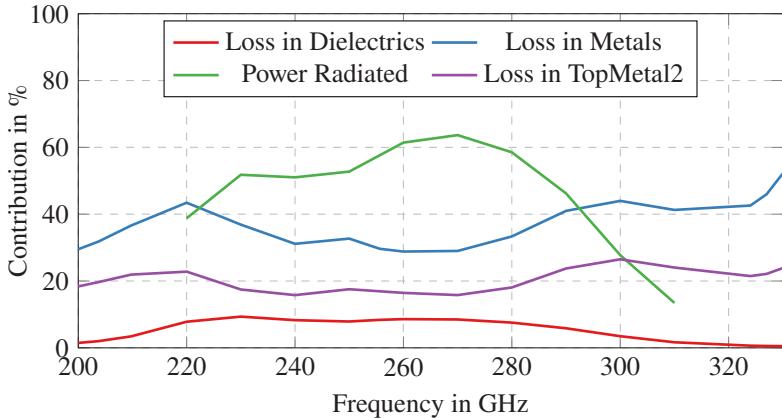

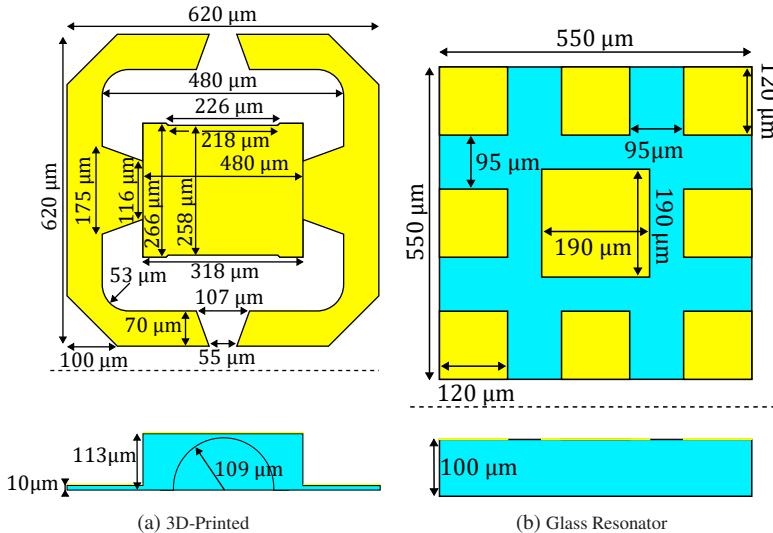

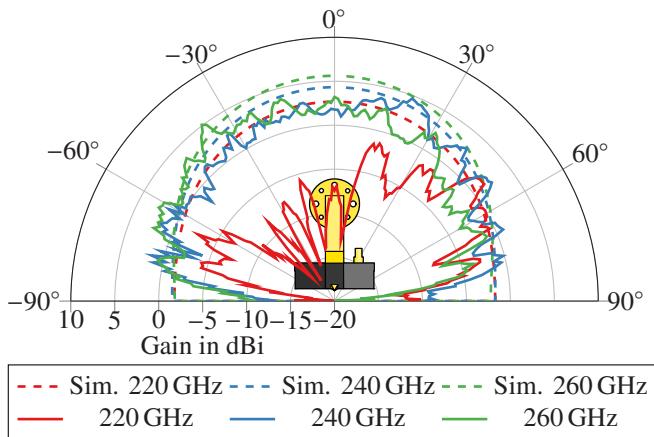

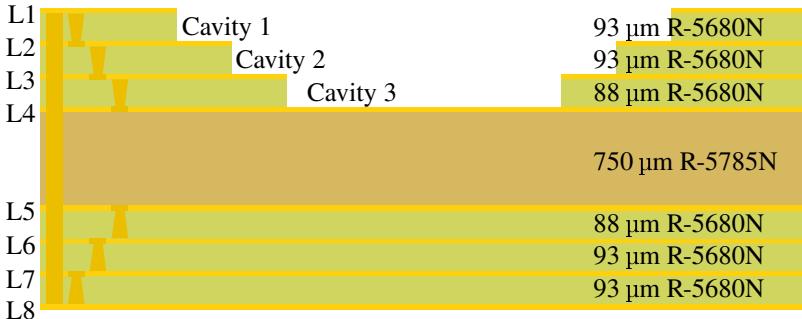

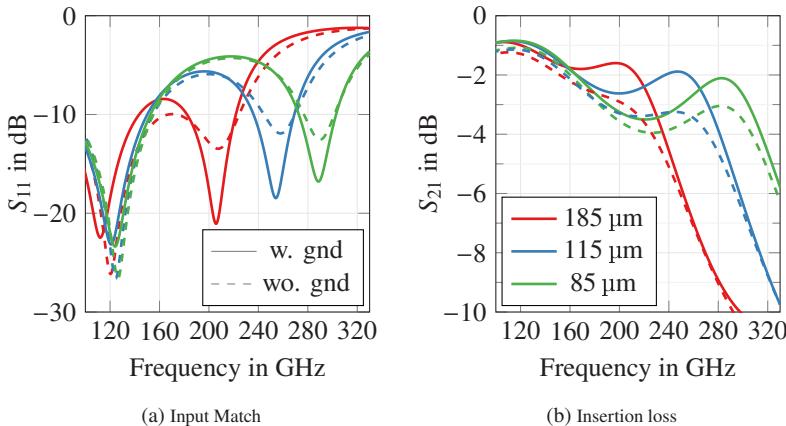

connect. Hence, differential antennas are investigated to exploit the system performance fully. For this, two different approaches are investigated. The first approach are printed circuit board (**PCB**) based antennas, successfully implemented and evaluated for the first time at this frequency range. The second approach uses a shorted bow-tie feeding element to achieve a compact and wideband on-chip antenna without using localized backside-etching (**LBE**) or through-substrate radiation. This design is novel and pushes the state of the art in on-chip antennas significantly in terms of integration, efficiency, and bandwidth. Reaching above 20 % relative bandwidth pushes the state of the art. The on-chip design employs either a 3D-printed resonator or a thin-film processed glass sheet as a parasitic resonator to enhance the bandwidth and efficiency. The **PCB** based design uses series-fed frequency staggered patches to achieve wideband operation on substrates with a solid ground plane and is a first of its kind at the tested frequencies.

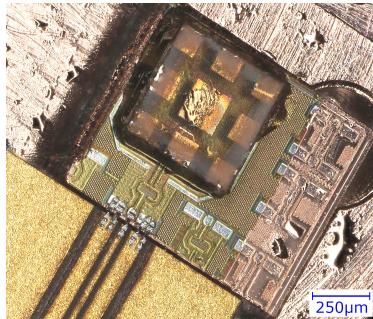

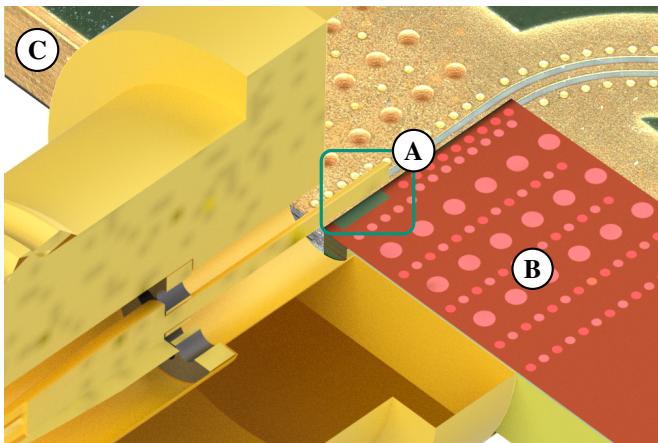

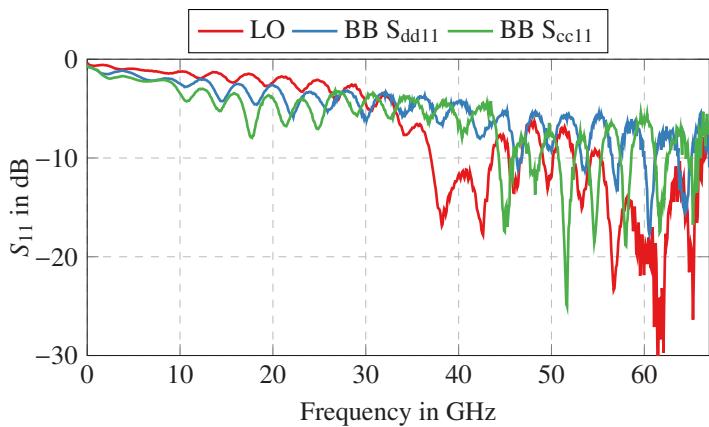

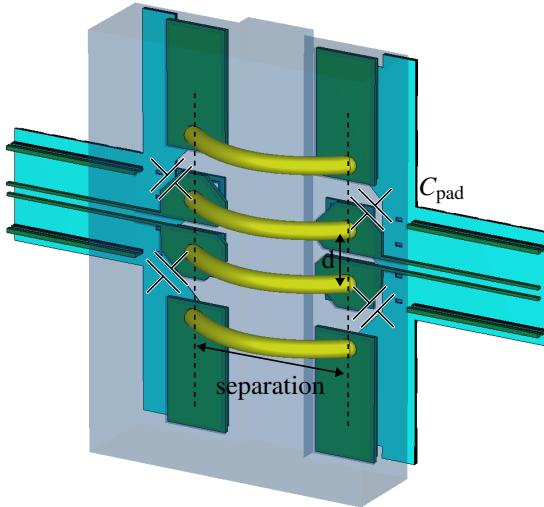

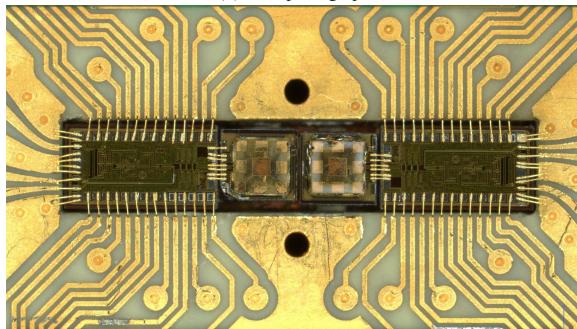

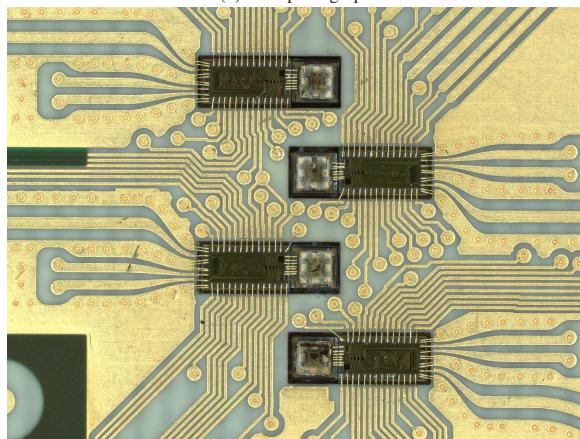

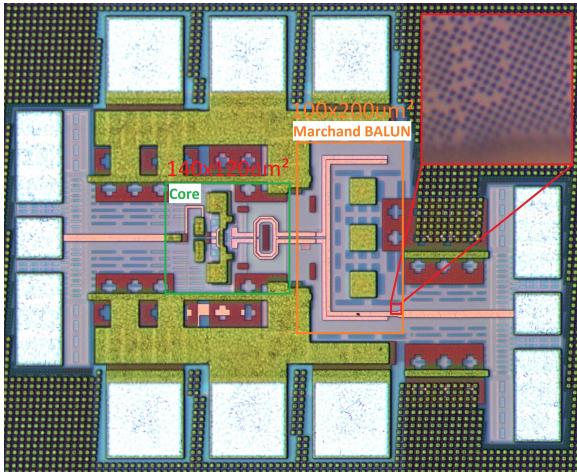

Everything is tied together with a novel packaging approach using impedance-tailored differential bond wires connecting the monolithic microwave integrated circuit (**MMIC**) to the antennas. The **RF**-transition is analyzed in detail, and the design methodology is explained. Further, the packaging solutions for the 64 GHz local oscillator (**LO**) signal and the wideband baseband (**BB**) signal with frequencies up to 50 GHz are explained.

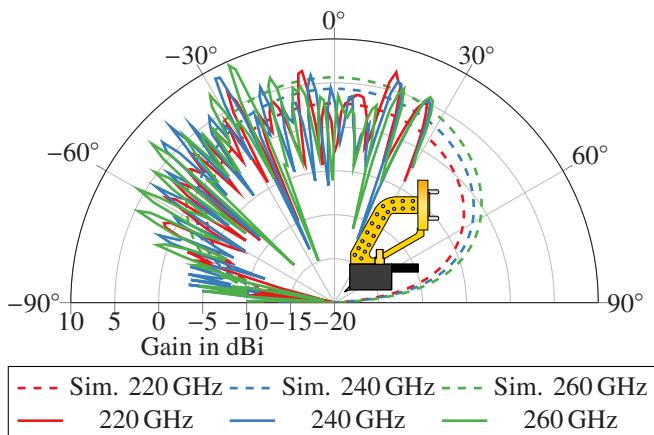

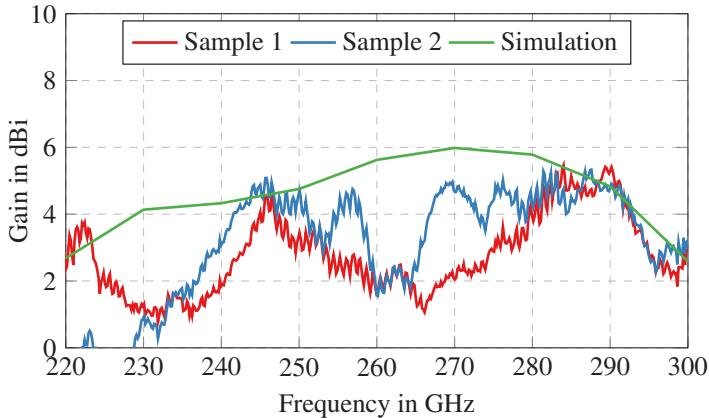

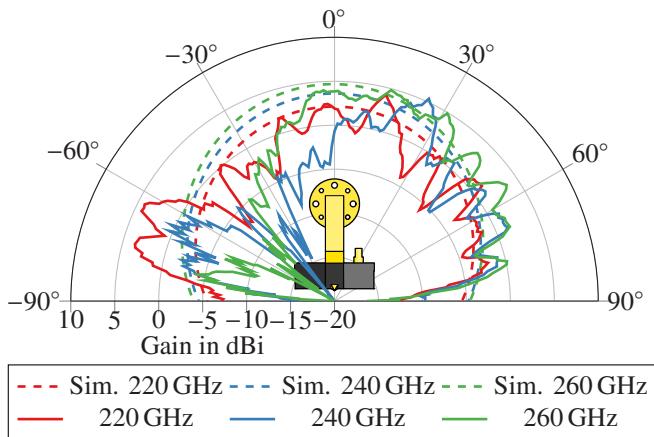

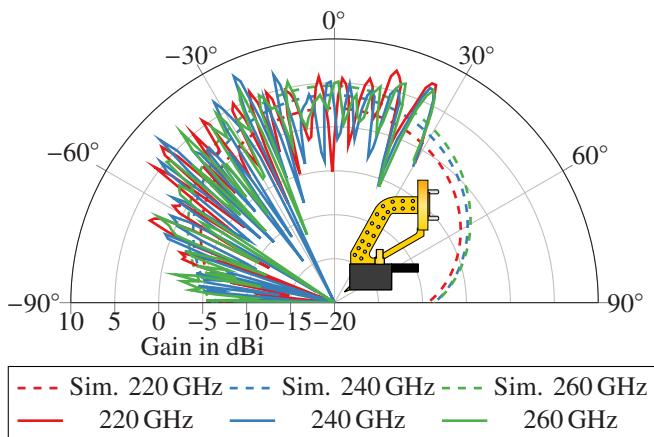

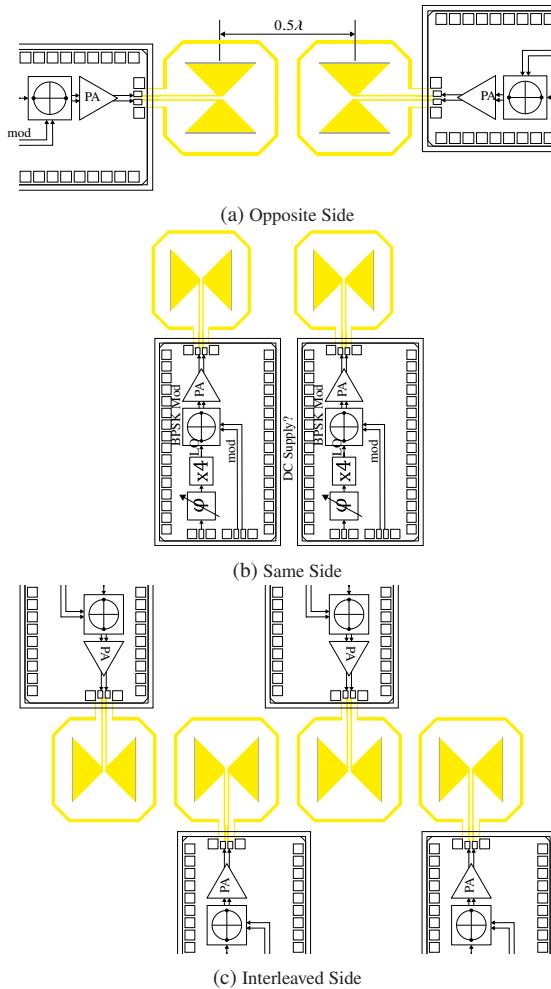

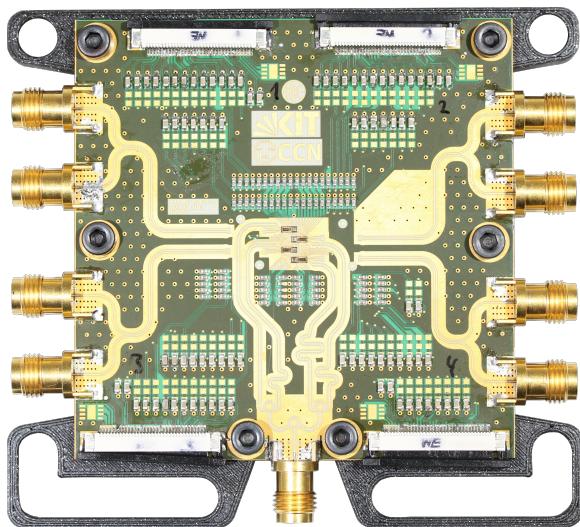

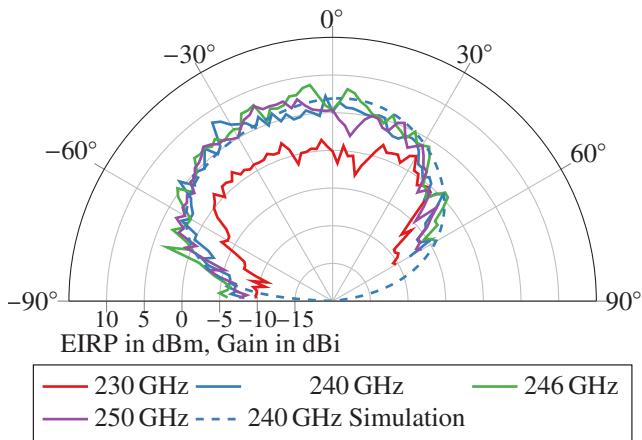

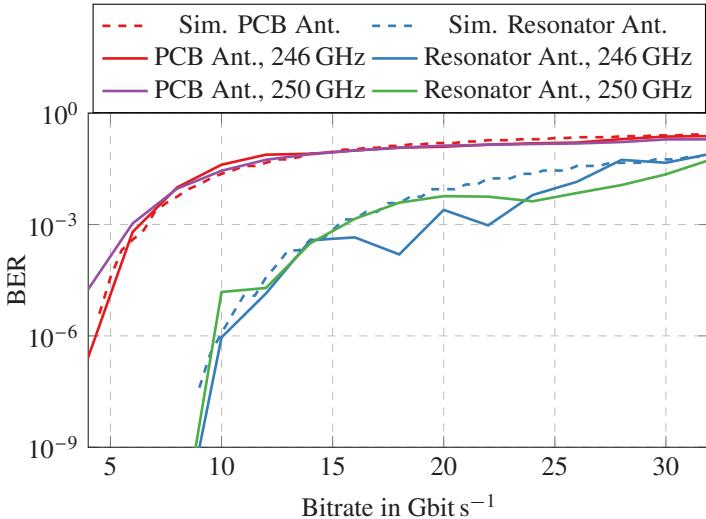

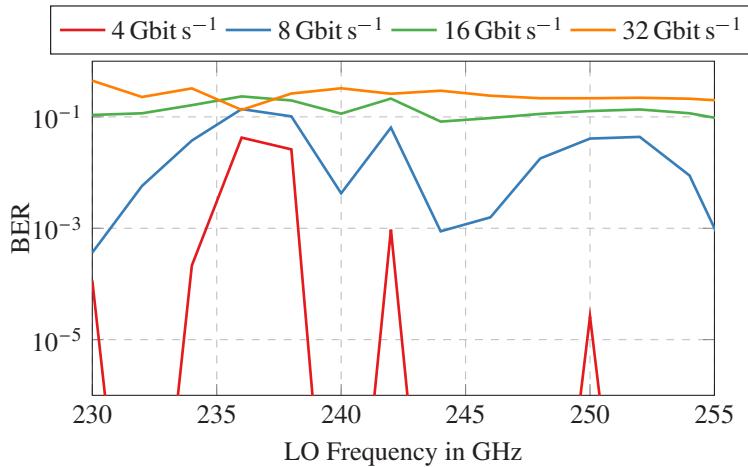

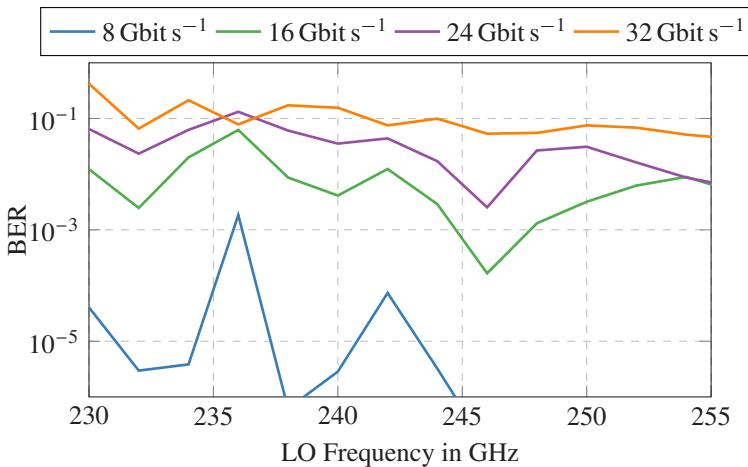

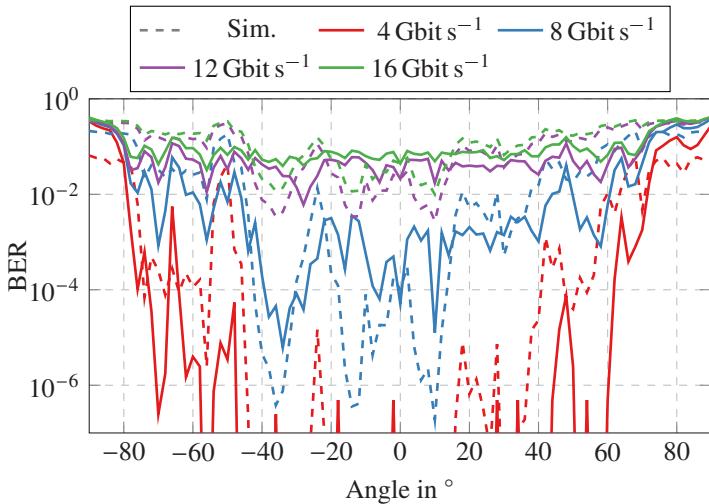

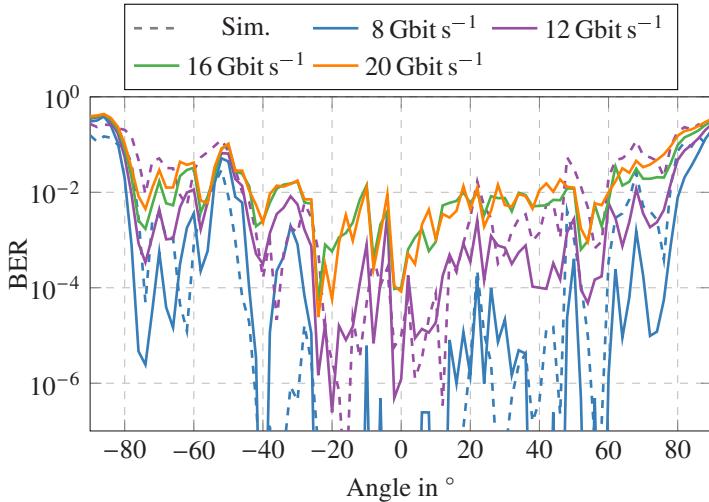

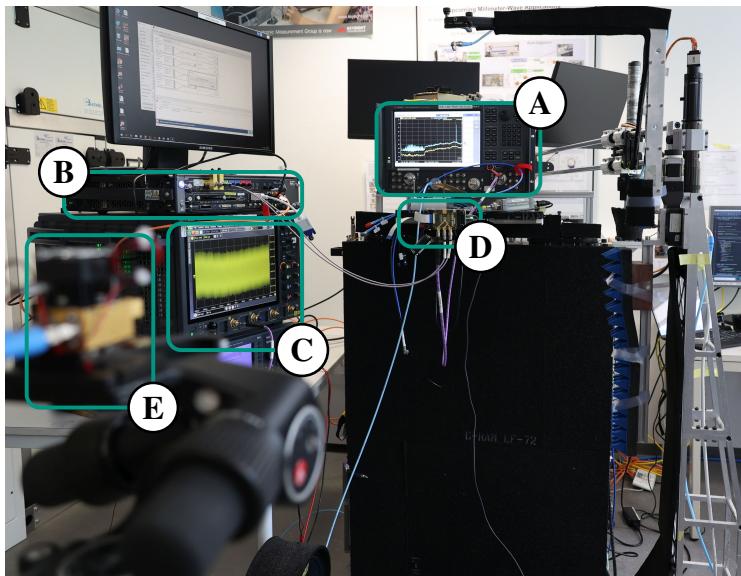

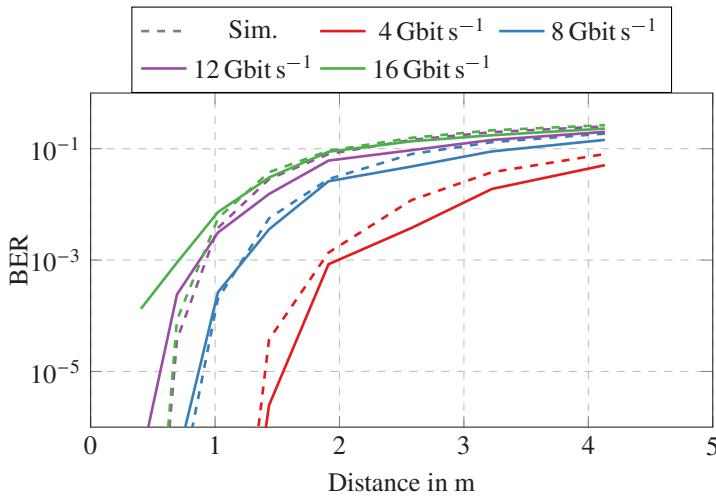

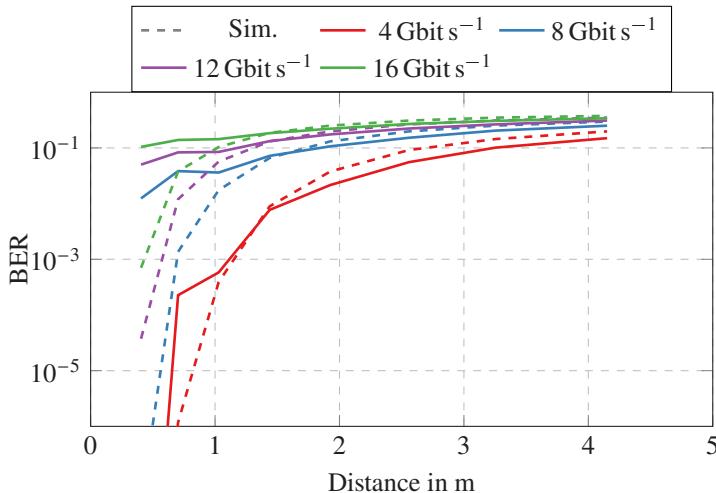

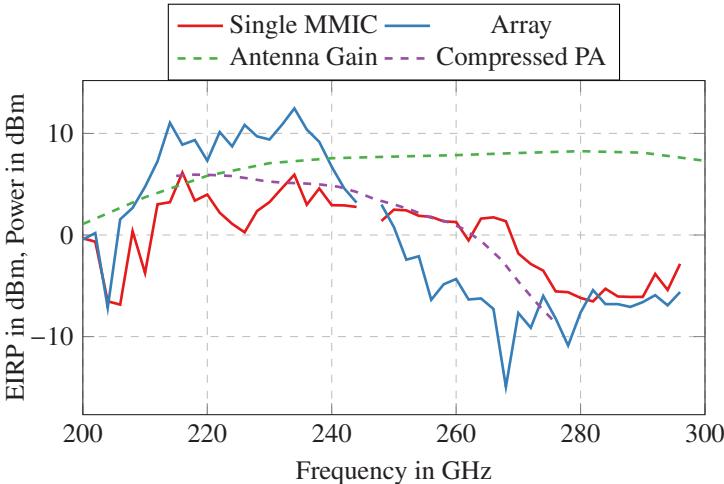

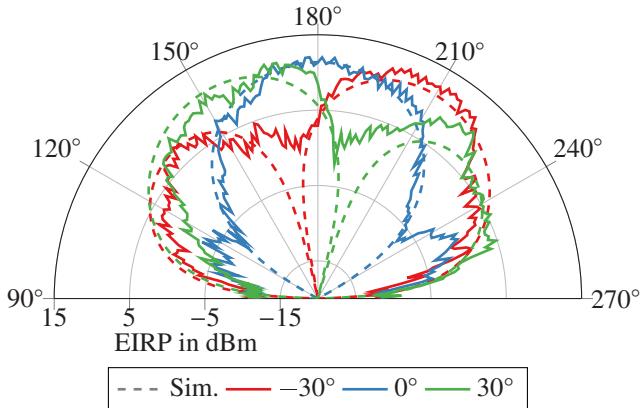

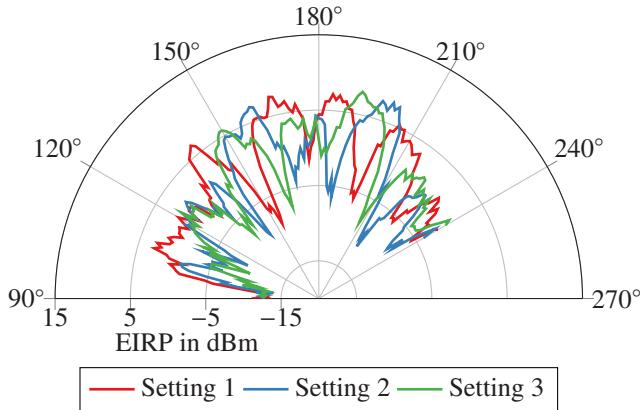

Lastly, the implemented transmitter systems are investigated. In total, four different systems are built. Two transmitters with a single chip, each using either a **PCB**-antenna or the resonator-loaded antenna, and two phased arrays with a 1x2 and 1x4 configuration using the resonator-loaded antennas are investigated. All systems are measured for their **RF**-performance and the antenna pattern. Further, a novel investigation of bit error rate (**BER**) over angle, bit-rate, distance, and beam-steering is done to analyze the static behavior and the truly achievable data rates over real-world conditions. The presented results and the demonstrated system exceed the state-of-the-art regarding the tested data-rate with rates up to  $32 \text{ Gbit s}^{-1}$  and array steering evaluations. In comparison to the state of the art the system shows an excellent efficiency of  $41.4 \text{ pJ bit}^{-1}$  while being smaller than any other reported system.

Together, the results of this thesis not only contribute to the academic understanding of the technologies for the sub-THz band but also pave the way for its future commercial exploitation. The novel RF transition and the ability to shrink system size while increasing design flexibility are the stepping stones for future high data-rate systems, inspiring a new era of possibilities in the field.

# Zusammenfassung

Diese Arbeit erforscht neue und innovative Lösungen im Bereich der Integrierten Schaltkreise, Aufbautechniken und Antennen für hoch-integrierte Sendesysteme im sub-THz Frequenzbereich. Die Arbeit stellt zunächst die notwendigen theoretischen Grundlagen und Untersuchungen vor, um die Entwurfsaufgabe vollständig zu kontextualisieren. Darauf aufbauend wird der Schaltungsentwurf der Schlüsselkomponente Leistungsverstärker vorgestellt und diskutiert. Anschließend werden die möglichen Antennenlösungen identifiziert, gegeneinander Bewertet und anhand von Messungen qualifiziert. Darauf aufbauend wird die Aufbautechnik des gesamten Senders analysiert und detailliert beschrieben. Die Arbeit wird konkludiert durch die Messungen der implementierten Sender, die die ausgezeichnete Leistung der Sende unterstreicht.

Der Sub-THz-Frequenzbereich zwischen 100 GHz und 300 GHz bietet ein breites verfügbares Frequenzspektrum mit derzeit wenig rechtlichen Einschränkungen. Daraus ergibt sich eine Vielzahl an möglichen Realisierungen. Um die Auswahl einzuzgrenzen und zu Begründen wird eine grundlegende Untersuchung der physikalischen Beschränkungen durchgeführt. Dabei werden Einflüsse wie [SNR](#) und harmonische Spur im Gesamtkontext bewertet. Weiterhin werden die Limitationen der derzeitig verfügbaren Messgeräte untersucht, um Probleme bei der Leistungsbewertung aufzuzeigen.

Aufbauend auf dem Stand der Technik werden die Realisierungsmöglichkeiten des Leistungsverstärkers eingegrenzt. Als Resultat dieser Analyse wird die pseudo-Differentielle Kaskodentopologie ausgewählt. Diese bietet die beste Abwägung zwischen Funktionalen Aspekten und der Integrationsdichte. Auf der Grundlage dieser Entscheidung werden zwei verfügbare Metall-Stack-ups analysiert und miteinander verglichen, um die Technologiewahl detailliert zu begründen. Basierend darauf wird ein mehrstufiger Verstärkeransatz untersucht. Das Design ist Frequenzgestaffelt und für die erforderliche Bandbreite und Ausgangsleistung optimiert. Dies wird durch den Einsatz von Transformatoren zwischen den Stufen und sorgfältig gewählten Rückkopplungspfaden

ermöglicht. Die anschließende Analyse des Gesamtsystems und die Diskussion der gewonnenen Erkenntnisse zeigen die hervorragende Leistung des Verstärkers, der den Stand der Technik in Bezug auf Bandbreite, nicht kombinierte Ausgangsleitung und Kompaktheit übertrifft. Simulationen und Messungen zeigen eine Bandbreite von 74 GHz und eine Ausgangsleistung von 8 dBm in einer Fläche von gerade einmal 0.045 mm<sup>2</sup>.

Ein neuer Ansatz in dieser Arbeit ist die Verwendung einer differentiellen **RF**-Verbindung. Diese erfordert auch differentielle Antennen, wofür zwei verschiedene Ansätze untersucht werden. Der erste Ansatz betrachtet **PCB**-basierte Antennen, die in dieser Arbeit zum ersten Mal in diesem Frequenzbereich erfolgreich implementiert wurden. Der zweite Ansatz nutzt ein kurzgeschlossenes Bow-Tie-Speiseelement, um eine kompakte und breitbandige On-Chip-Antenne ohne Verwendung von **LBE** oder Strahlung durch das Substrat zu realisieren. Dieses Design ist neuartig und bringt den Stand der Technik bei On-Chip-Antennen in Bezug auf Integration, Effizienz und Bandbreite erheblich voran. Mit relativen Bandbreiten über 20 % wird der Stand der Technik deutlich übertroffen. Das On-Chip-Design verwendet wahlweise einen 3D-gedruckten Resonator oder Metallische Resonatoren auf einem Glasplättchen, um die Bandbreite und Effizienz zu erhöhen. Das **PCB**-basierte Design verwendet seriengespeiste, frequenzversetzte Patches, um die Breitbandigkeit auf Substraten mit durchgehender Massefläche zu erreichen. Dieser Ansatz ist der erste dieser Art in dem gewählten Frequenzbereich.

Die Aufbautechnik basiert auf einem innovativen Konzept, bei dem impedanzangepasste differentielle Bonddrähte den **MMIC** mit den Antennen verbindet. Der **RF**-Übergang wird im Detail analysiert, und die Entwurfsmethodik wird erläutert. Außerdem werden die Packaging-Lösungen für das 64 GHz **LO**-Signal und das breitbandige **BB**-Signal mit Frequenzen bis zu 50 GHz erläutert.

Abschließend werden die implementierten Sendersysteme untersucht. Insgesamt wurden vier verschiedene Systeme gebaut. Zwei Sender mit je einem Chip, die jeweils entweder eine **PCB**-Antenne oder die resonatorgeladene Antenne verwenden. Dazu werden zwei Phased-Arrays mit einer 1x2 und 1x4 Konfiguration unter Verwendung der resonatorgeladenen Antennen untersucht. Alle Systeme werden hinsichtlich ihrer **RF**-Performance und des Antennen-diagramms gemessen. Außerdem wird eine Analyse des **BER** über Winkel, Bitrate, Entfernung und Strahlsteuerung durchgeführt, um das statische Verhalten und die tatsächlich erreichbaren Datenraten unter realen Bedingungen zu analysieren. Die vorgestellten Ergebnisse und das demonstrierte System übertreffen den Stand der Technik hinsichtlich der getesteten Datenratenraten

bis hin zu  $32 \text{ Gbit s}^{-1}$  und dem Detailgrad der Untersuchung im Bezug auf **BER** über Winkel und Distanz. Dabei zeigt sich im Vergleich die hohe Effizienz von  $41.4 \text{ pJ bit}^{-1}$  bei gleichzeitig kompakten Aufbau des binary phase shift keying (**BPSK**)-Transmitters als besonders positiv.

Zusammenfassend tragen die Ergebnisse dieser Arbeit nicht nur zum akademischen Verständnis der Technologien für das Sub-THz-Band bei, sondern ebnen auch den Weg für dessen zukünftige kommerzielle Nutzung. Der neuartige RF-Übergang und die Fähigkeit, die Systemgröße zu verringern und gleichzeitig die Design-Flexibilität zu erhöhen, sind ein Sprungbrett für künftige Systeme mit hoher Datenrate.

# Preface

This thesis was written during my time as a research associate at the Institute of Radio Frequency Engineering and Electronics (IHE) at the Karlsruhe Institute of Technology (KIT).

First of all, I would like to thank Prof. Dr.-Ing. Dr. h.c. Thomas Zwick for enabling me to pursue this scientific journey and giving me the freedom to explore many different aspects. I want to extend my sincere thanks to Prof. Dr. sc. techn. habil. Dipl. Betriebswissenschaften Frank Ellinger for his interest in my work and for willingly accepting the co-lecture. I would also like to thank Prof. Dr.-Ing. Cagri Ulusoy for the discussions about integrated circuits and the possibilities of being part of the circuit design team of IHE. Lastly, many thanks go out to Luca Steinweg for the good time on our shared journey tackling our project.

I also want to express my appreciation for those who have been with me through the ups and downs of my scientific journey. Christian Bohn, in particular, has been a valuable discussion partner, providing support and insights during the many hours we spent navigating our scientific challenges. I am also grateful to Alexander Quint and Elizabeth Bekker, who have been both roommates and friends, offering companionship and support over the years. I also want to acknowledge the contributions of Luca Valenziano, Marius Kretschmann, and Georg Gramlich, who provided valuable scientific input and offered a much-needed distraction from our academic pursuits. Lastly, a heartfelt thank you to all the people within the IHE and around the campus who supported me with valuable discussions their help.

I want to express my heartfelt thanks to my parents, brother, and friends, who have been unwavering in their support over the past three decades. Their unconditional support has been a constant source of strength and encouragement. I also want to extend my gratitude to Anja Pohlemann for her unwavering support and for simply being the amazing person she is.

Berlin, September 2024

# Table of Contents

|                                                          |      |

|----------------------------------------------------------|------|

| <b>Abstract</b> . . . . .                                | i    |

| <b>Preface</b> . . . . .                                 | vii  |

| <b>Symbols and Abbreviations</b> . . . . .               | xiii |

| <b>1 Introduction</b> . . . . .                          | 1    |

| 1.1 Objective of this Thesis . . . . .                   | 3    |

| 1.2 Structure of this Thesis . . . . .                   | 5    |

| <b>2 Physical Background</b> . . . . .                   | 7    |

| 2.1 Differential S-Parameters . . . . .                  | 7    |

| 2.2 Differential Planar Transmission Lines . . . . .     | 12   |

| 2.3 Wideband Planar Antennas . . . . .                   | 14   |

| 2.4 Planar Phased Arrays . . . . .                       | 17   |

| 2.5 Digital Modulation . . . . .                         | 20   |

| 2.6 Power Amplifiers . . . . .                           | 21   |

| 2.7 Frequency Staggering . . . . .                       | 24   |

| <b>3 System and Implementation Constraints</b> . . . . . | 27   |

| 3.1 Choice of Modulation Type . . . . .                  | 27   |

| 3.2 Physical Antenna Array Implementation . . . . .      | 29   |

| 3.3 MMIC Antenna Co-Design . . . . .                     | 29   |

| 3.4 Harmonic Content in the Multiplier Chains . . . . .  | 31   |

| 3.5 Measurement Uncertainty . . . . .                    | 32   |

| 3.5.1 On Wafer Measurement Repeatability . . . . .       | 33   |

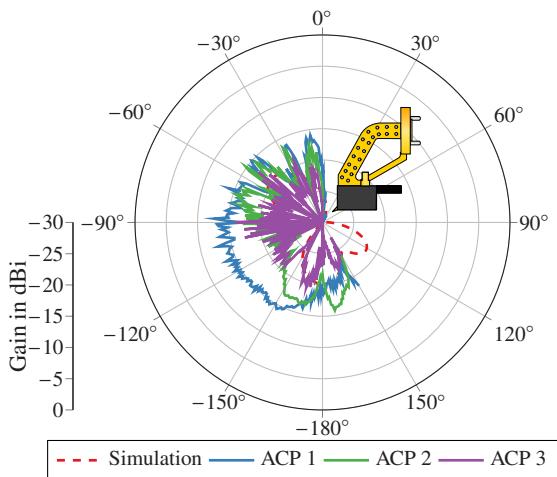

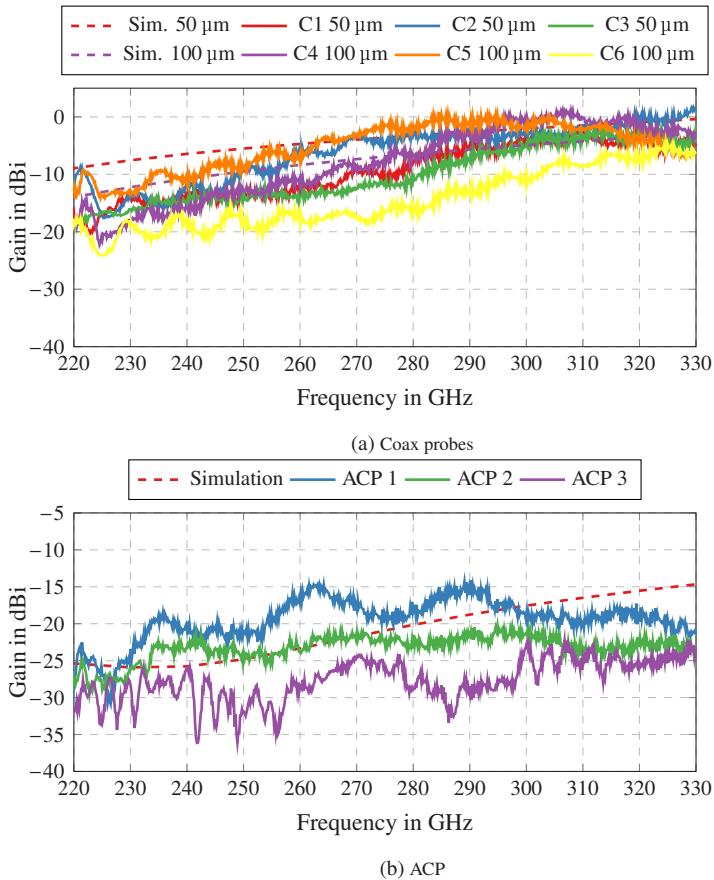

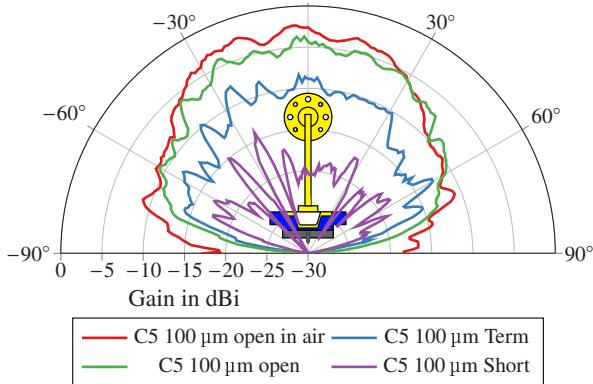

| 3.5.2 mmWave Probe Radiation Behaviour . . . . .         | 35   |

|                                                                                     |            |

|-------------------------------------------------------------------------------------|------------|

| <b>4 Power Amplifier Design and Evaluation . . . . .</b>                            | <b>41</b>  |

| 4.1 State of the art in PA MMICs . . . . .                                          | 41         |

| 4.2 Technology Overview . . . . .                                                   | 43         |

| 4.2.1 Transmission Lines . . . . .                                                  | 45         |

| 4.2.2 Transformers . . . . .                                                        | 46         |

| 4.2.3 Capacitors . . . . .                                                          | 48         |

| 4.2.4 Technology Selection . . . . .                                                | 50         |

| 4.3 Single Ended Amplifier Evaluation . . . . .                                     | 50         |

| 4.4 Differential Amplifier Design . . . . .                                         | 52         |

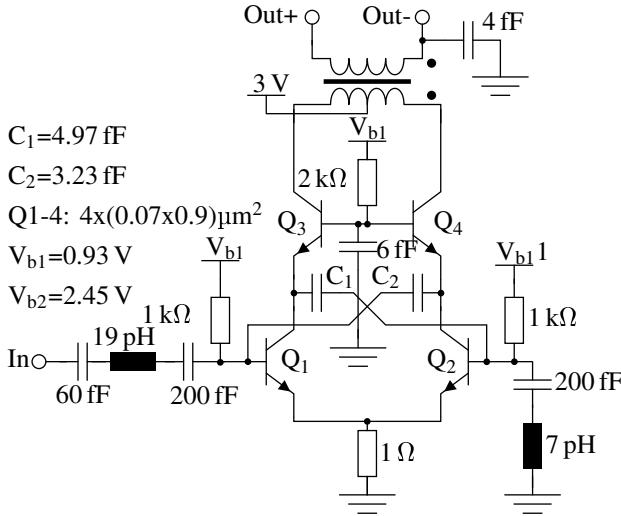

| 4.4.1 Core Design . . . . .                                                         | 53         |

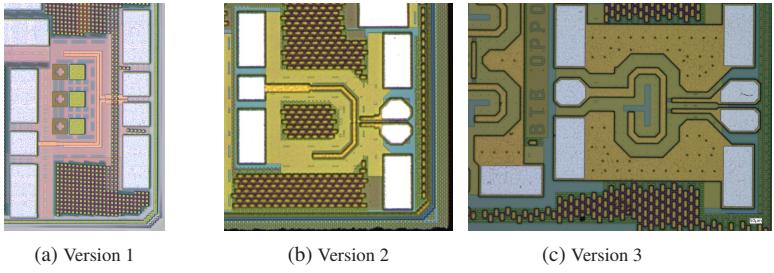

| 4.4.2 Comparison PA in Copper and Aluminium Back-end                                | 54         |

| 4.4.3 Model Dissection for Stability and Linearity Analysis                         | 57         |

| 4.4.4 Final Design . . . . .                                                        | 60         |

| <b>5 Wideband Phased Array Antenna Designs . . . . .</b>                            | <b>67</b>  |

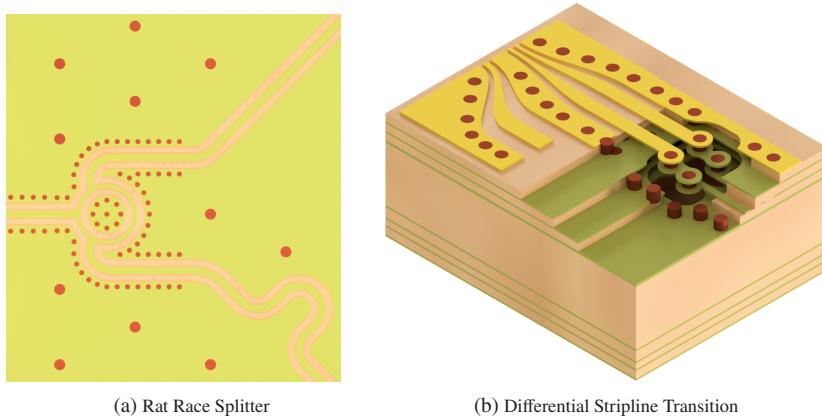

| 5.1 PCB Antennas . . . . .                                                          | 69         |

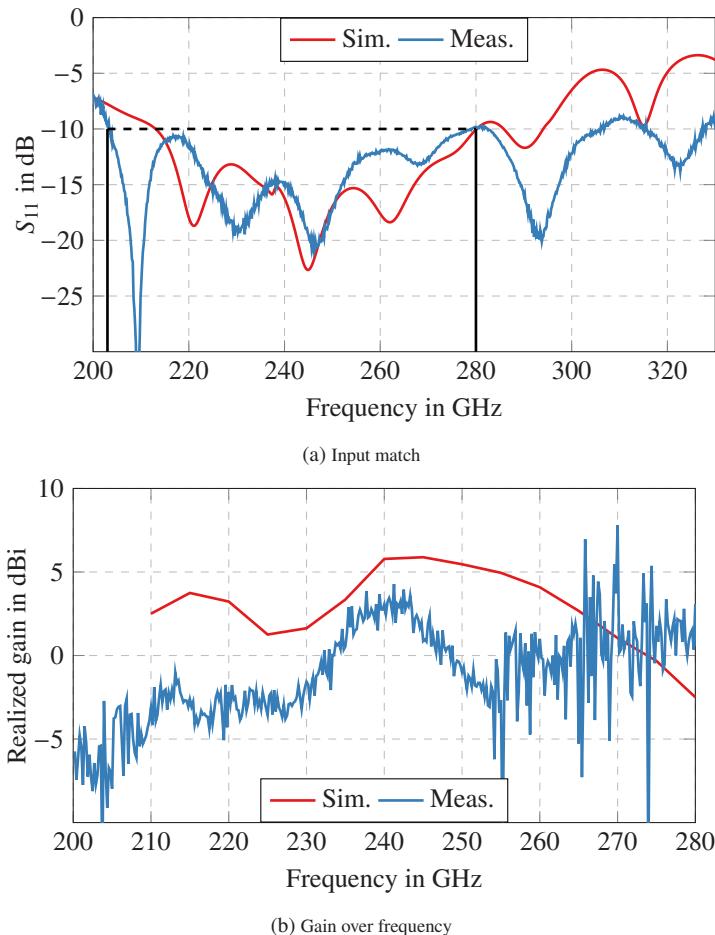

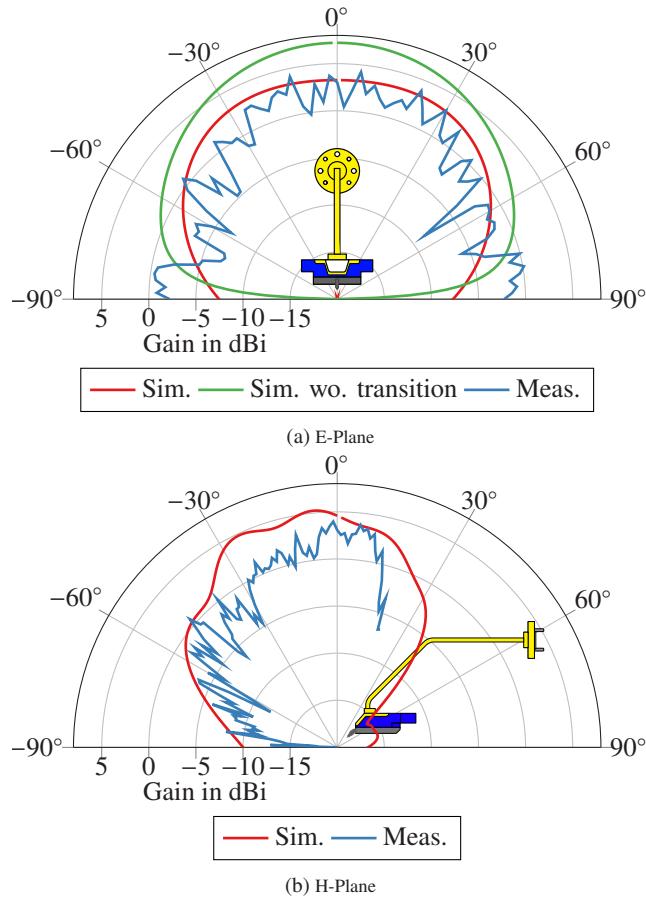

| 5.1.1 PCB Antenna Version 1 . . . . .                                               | 71         |

| 5.1.2 PCB Antenna Version 2 . . . . .                                               | 72         |

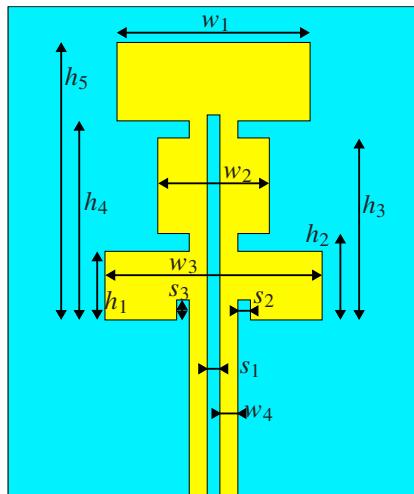

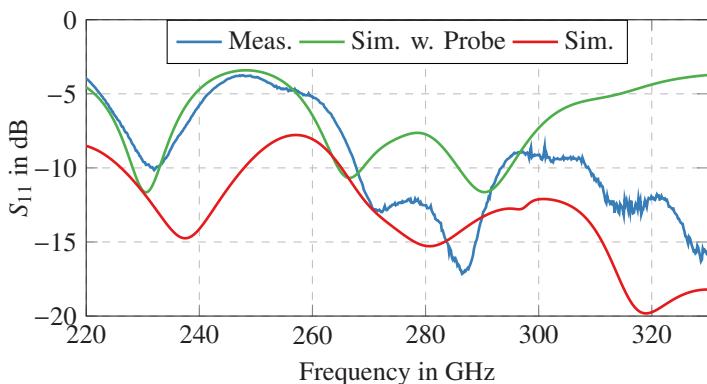

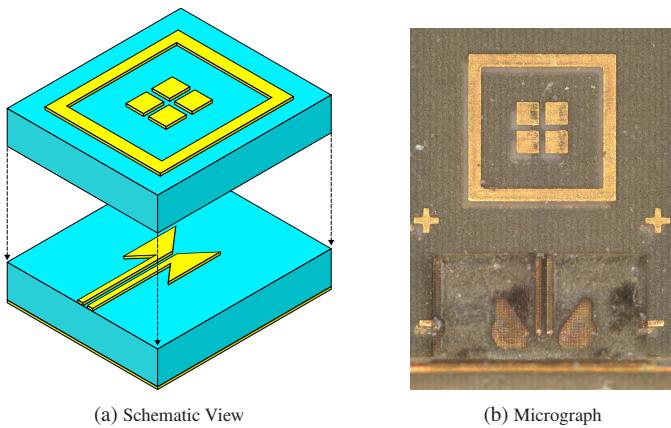

| 5.2 On-Chip Antennas . . . . .                                                      | 79         |

| 5.2.1 On-Chip Resonator Design . . . . .                                            | 82         |

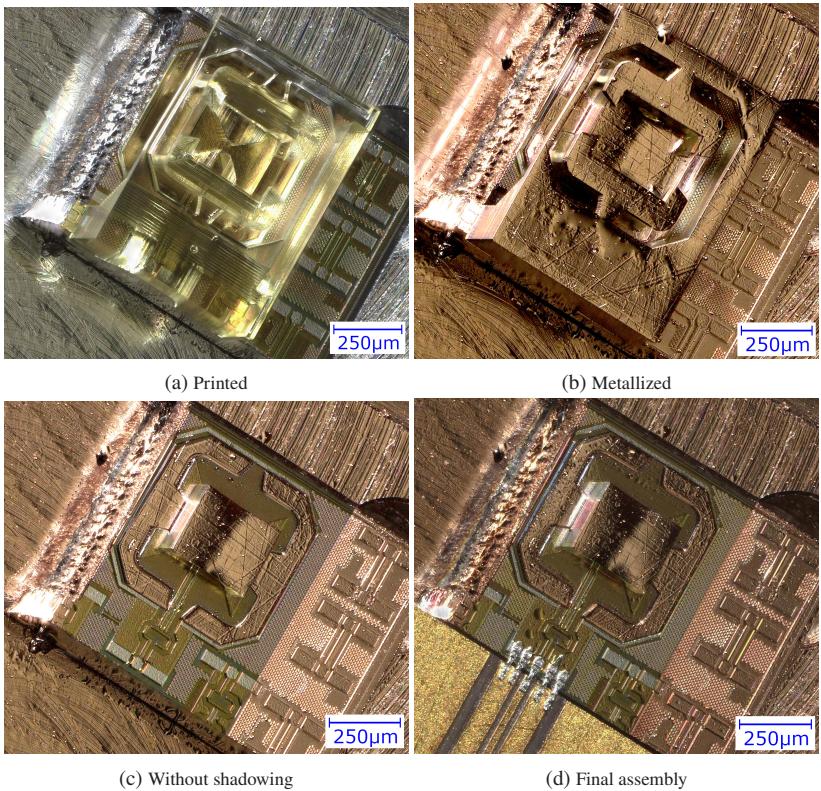

| 5.2.2 Resonator Sample Manufacturing . . . . .                                      | 85         |

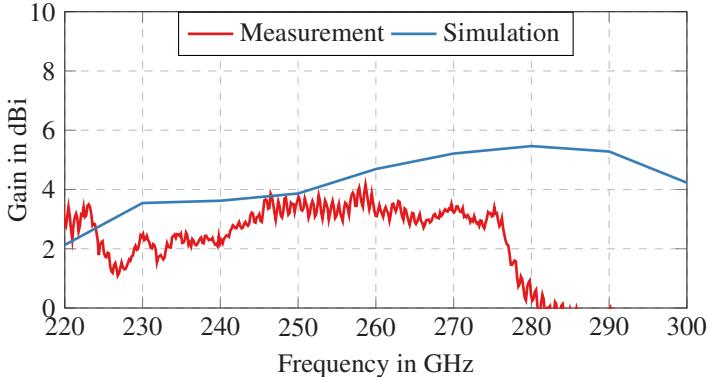

| 5.2.3 3D-Printed Resonator Measurement . . . . .                                    | 88         |

| 5.2.4 Glass Resonator Measurement . . . . .                                         | 90         |

| 5.3 mmWave Phased Arrays . . . . .                                                  | 92         |

| <b>6 RF Interconnects for Chip to PCB and Chip to Antenna Connections . . . . .</b> | <b>95</b>  |

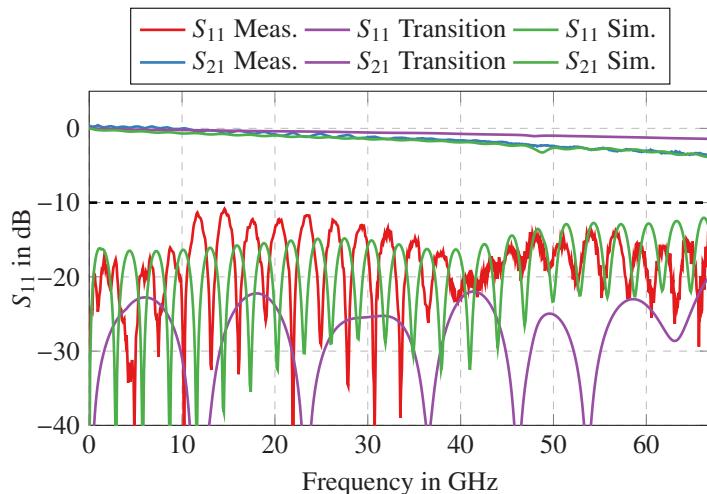

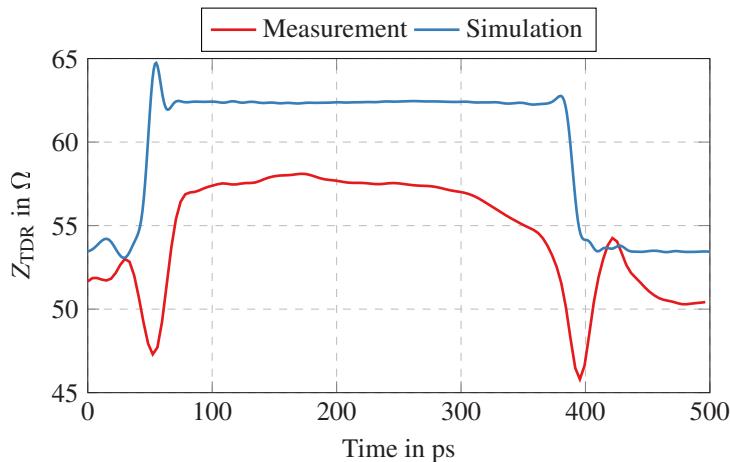

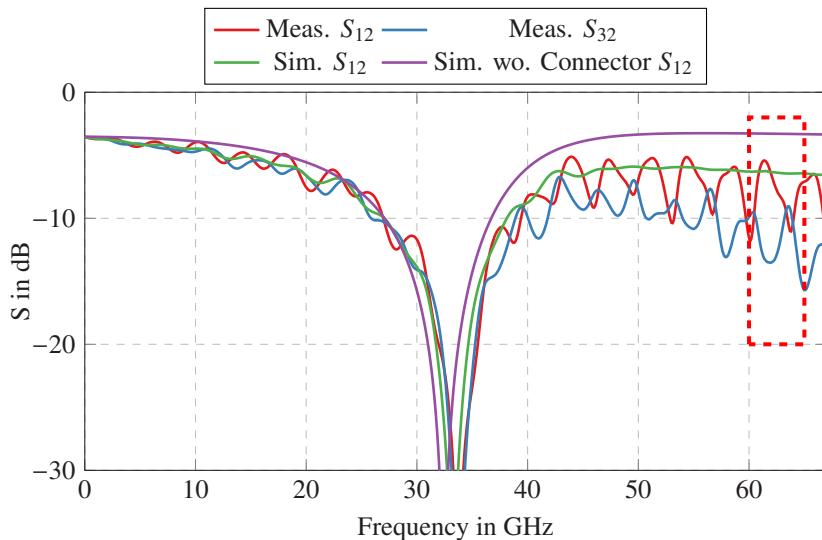

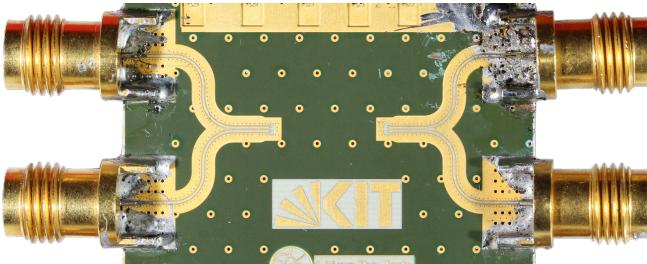

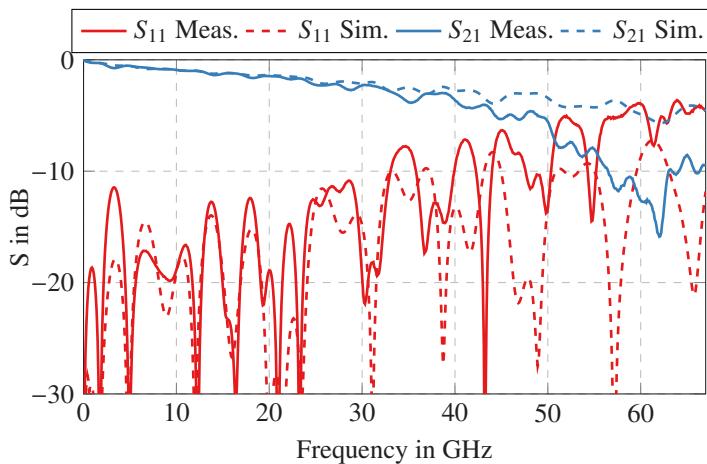

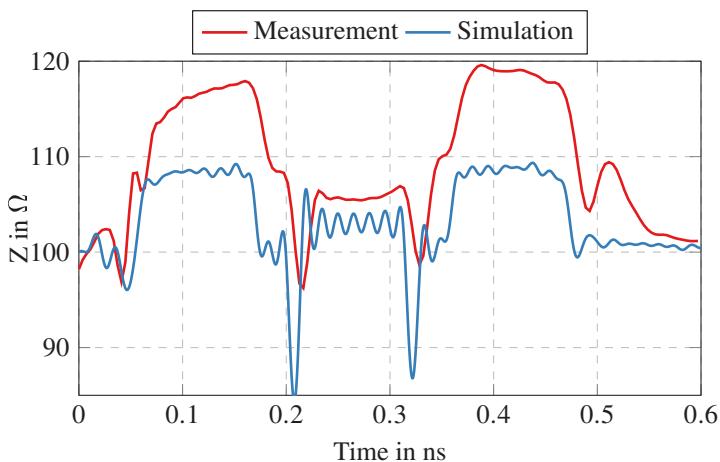

| 6.1 Wideband Coax to PCB Transitions . . . . .                                      | 96         |

| 6.2 On-PCB RF Signal Routing . . . . .                                              | 97         |

| 6.3 Bondwire MMIC to PCB Connection . . . . .                                       | 101        |

| 6.4 Differential RF bond-wire Transition . . . . .                                  | 105        |

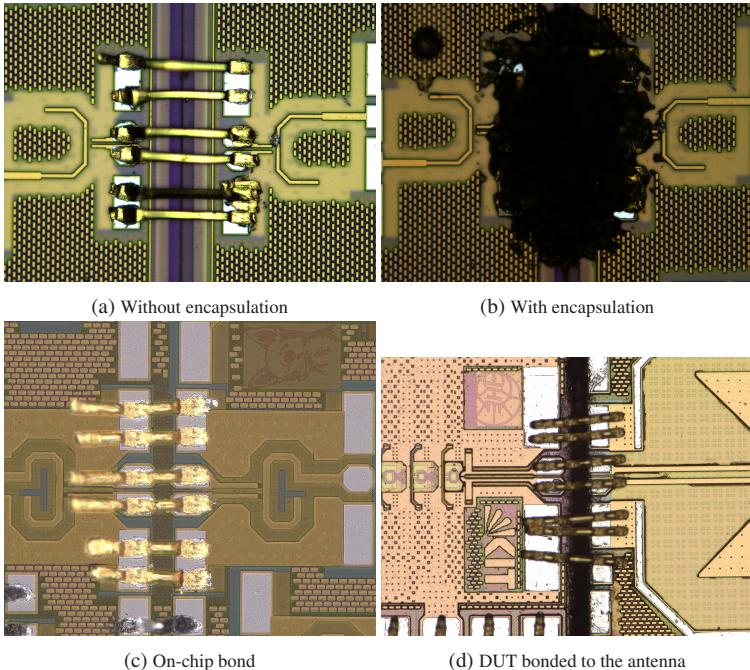

| 6.4.1 Fabrication . . . . .                                                         | 108        |

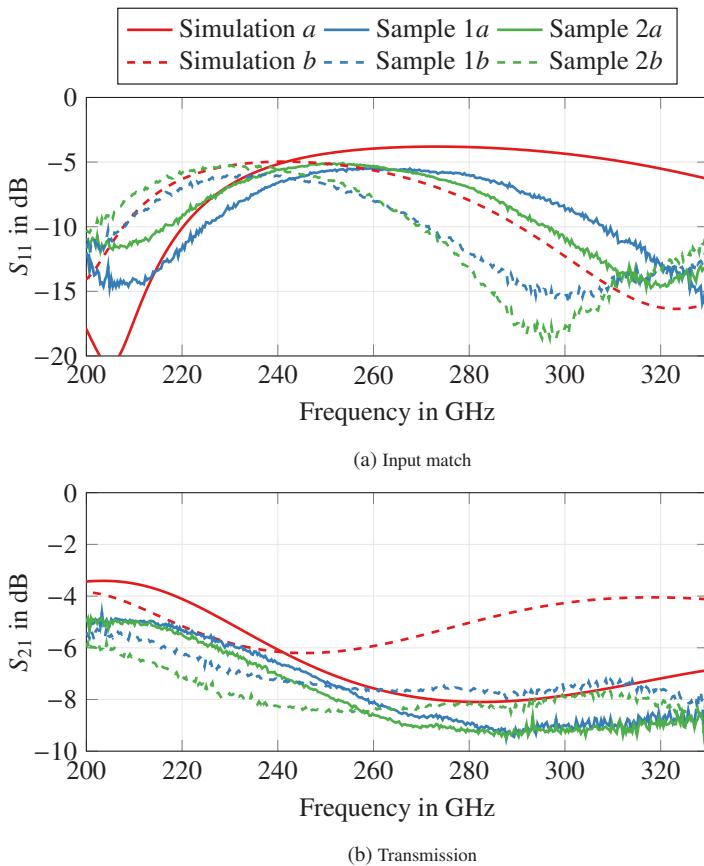

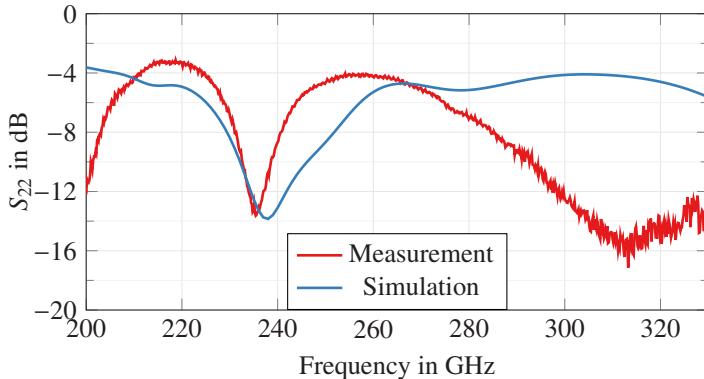

| 6.4.2 Measurement . . . . .                                                         | 109        |

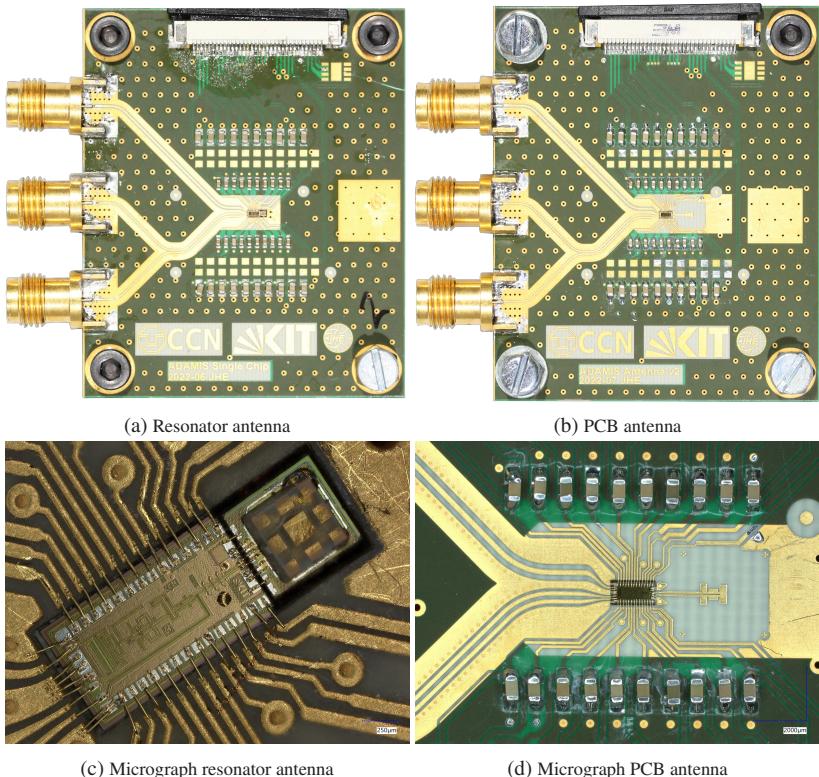

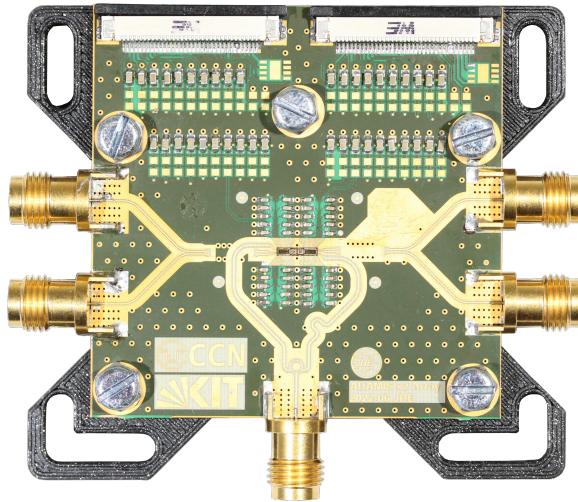

| 6.5 Realized Transmitters . . . . .                                                 | 112        |

| <b>7 Full Transmitter Evaluation . . . . .</b>                                      | <b>117</b> |

|                                   |                                              |            |

|-----------------------------------|----------------------------------------------|------------|

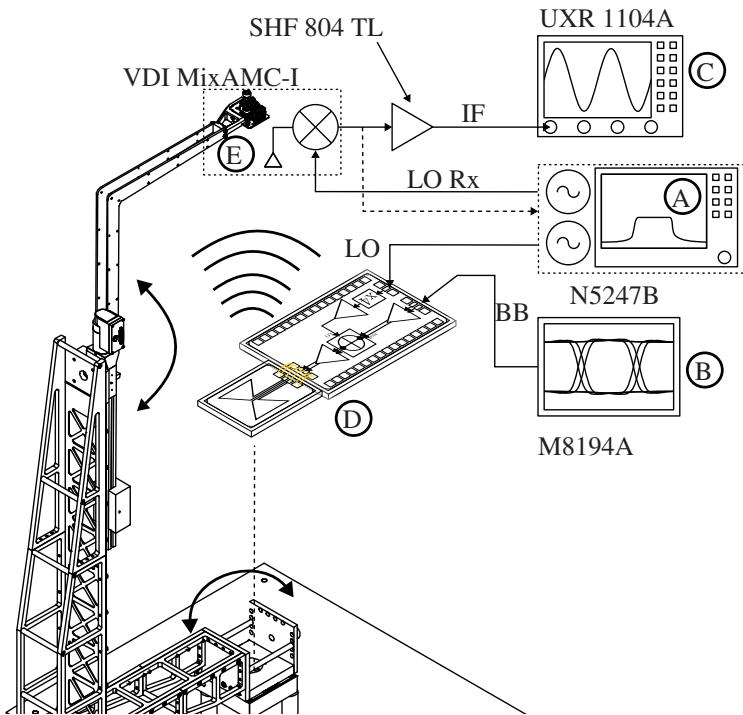

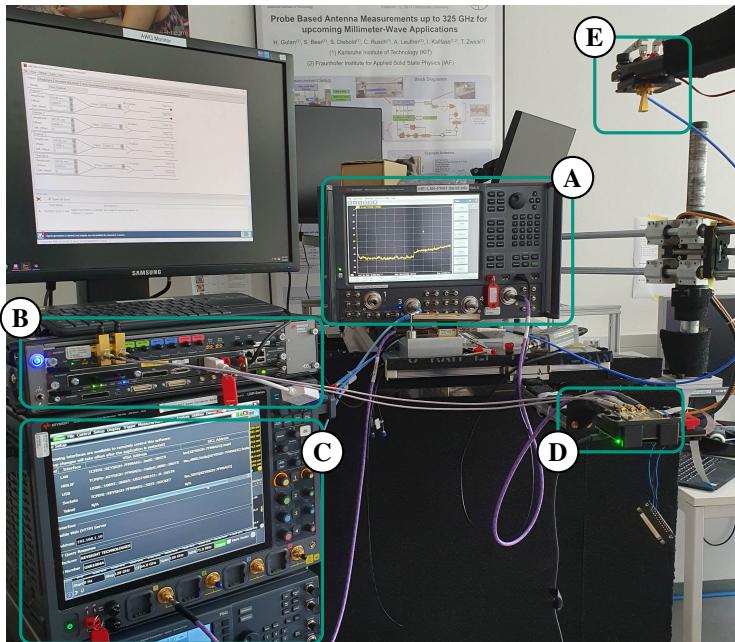

| 7.1                               | Measurement Setup . . . . .                  | 117        |

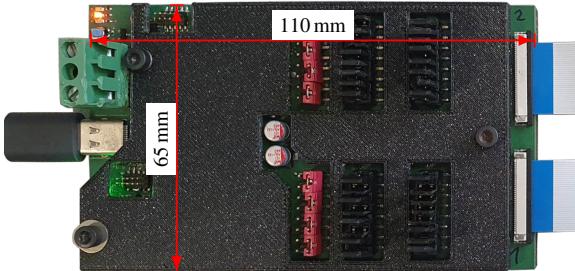

| 7.1.1                             | DC Supply . . . . .                          | 120        |

| 7.2                               | Single Chip Measurements . . . . .           | 122        |

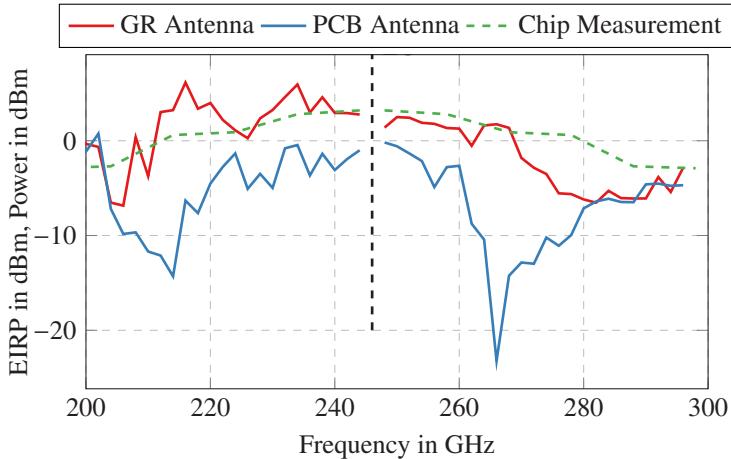

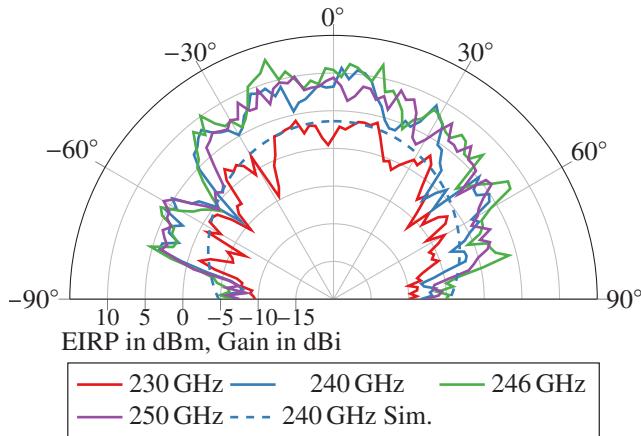

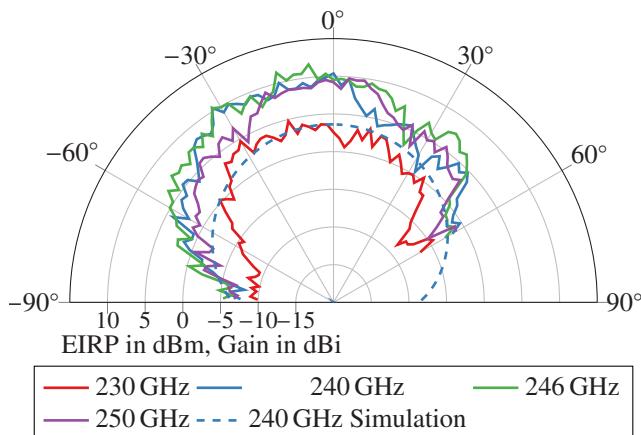

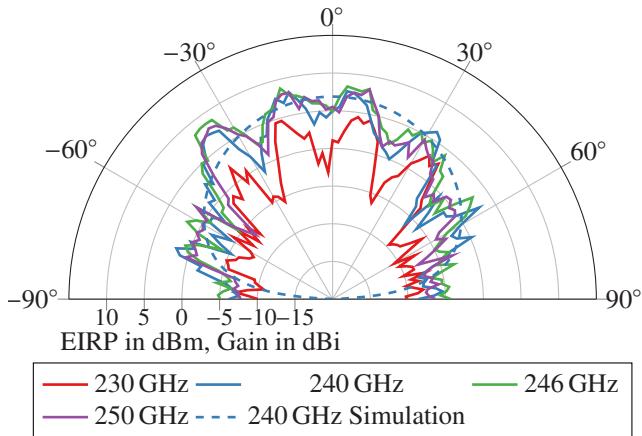

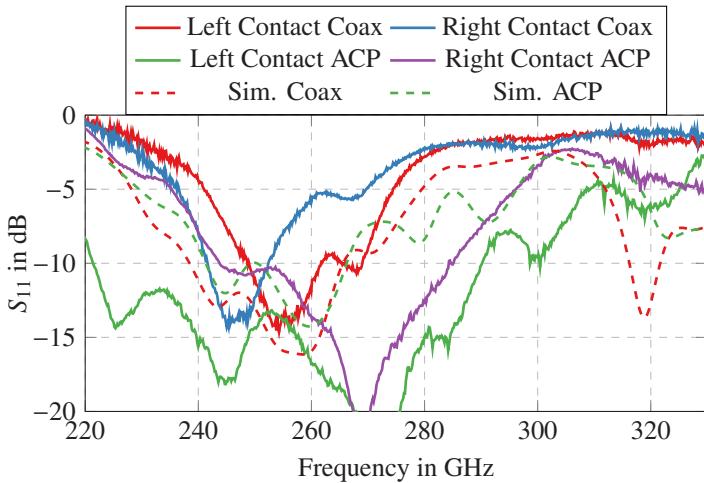

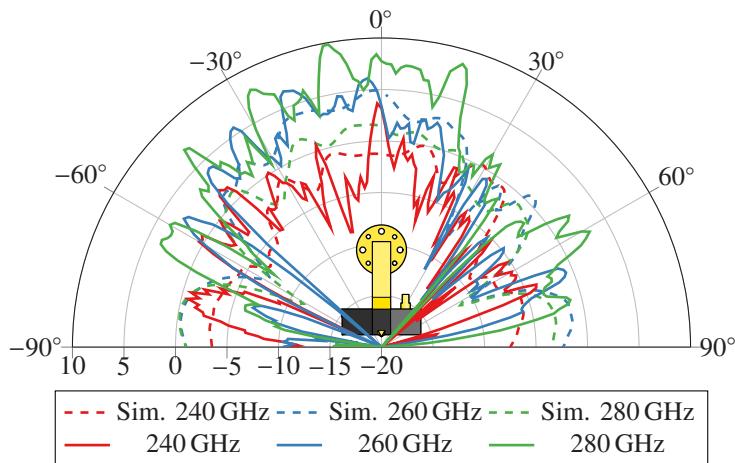

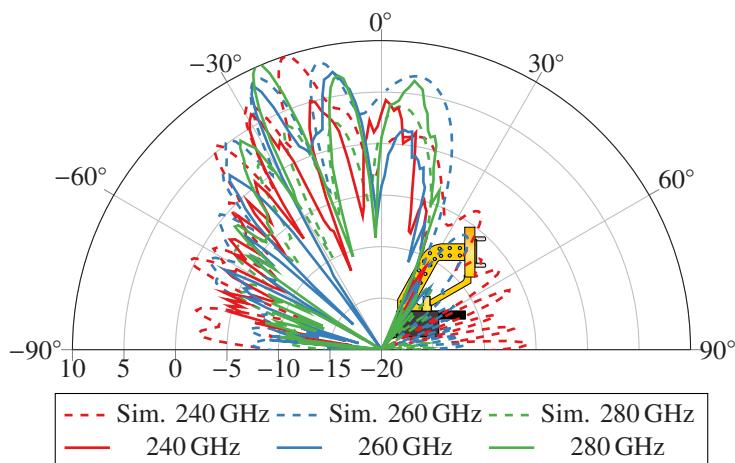

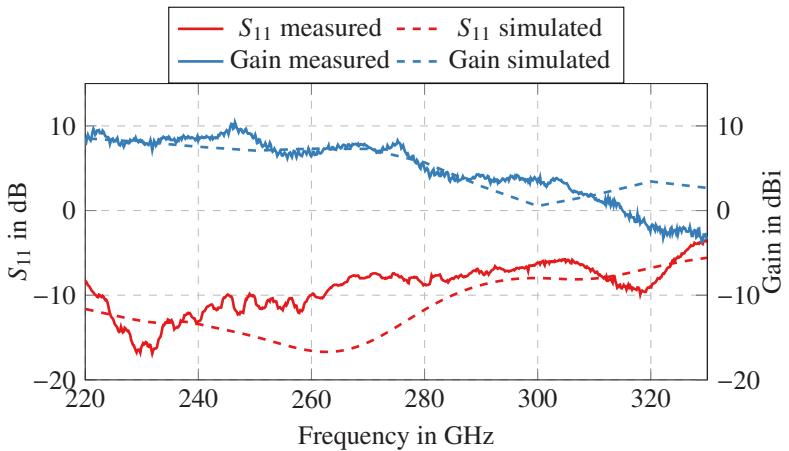

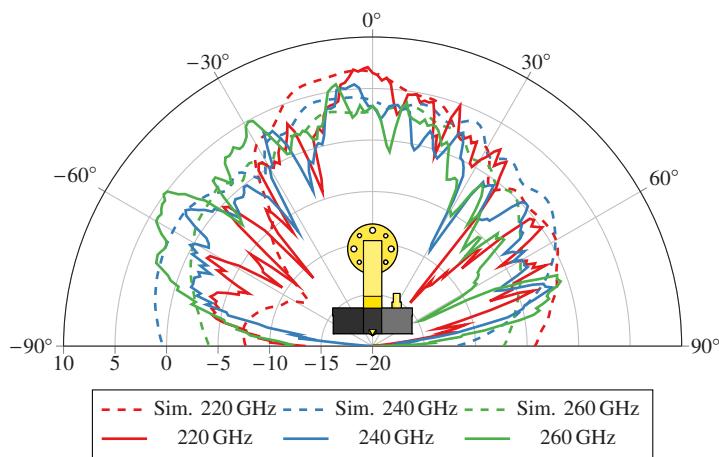

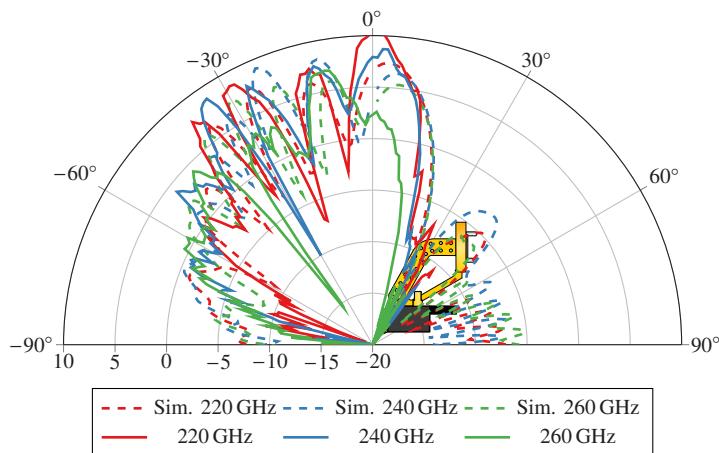

| 7.2.1                             | RF Evaluation . . . . .                      | 123        |

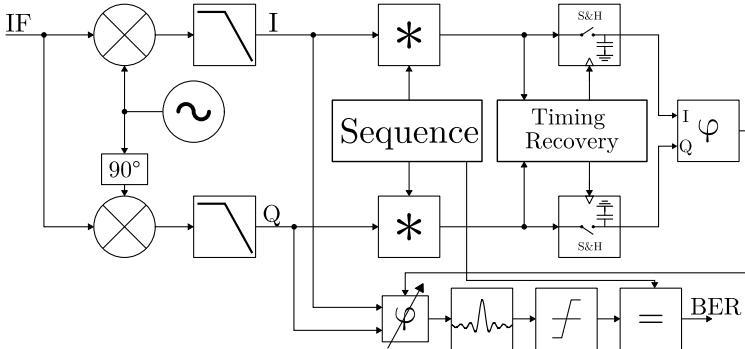

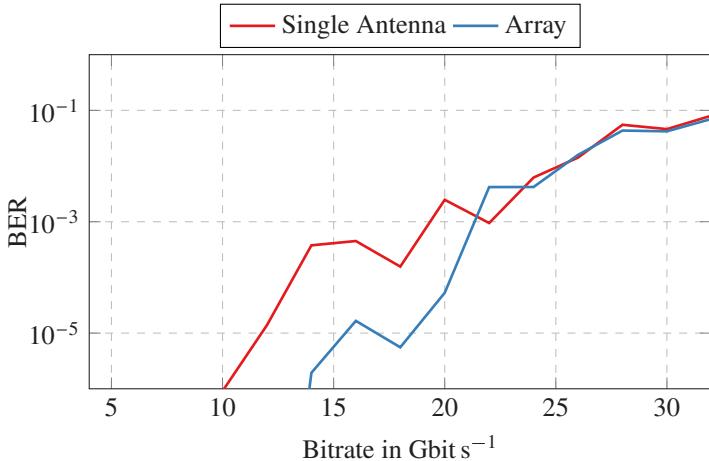

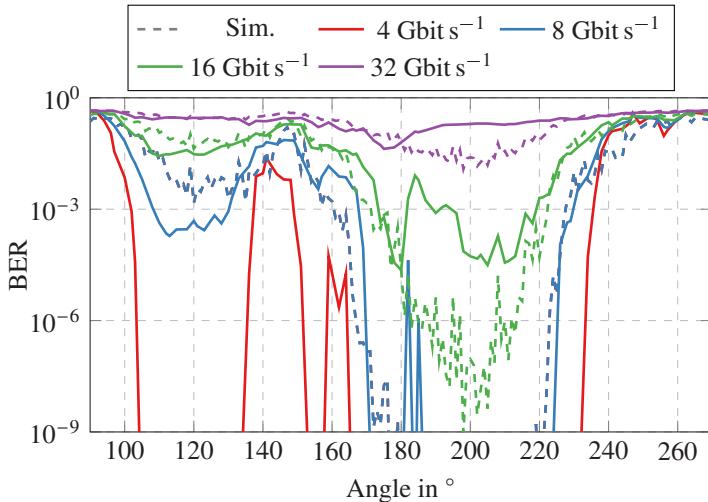

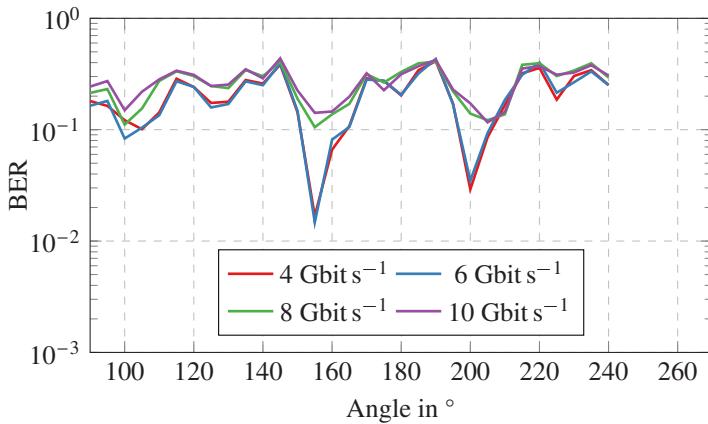

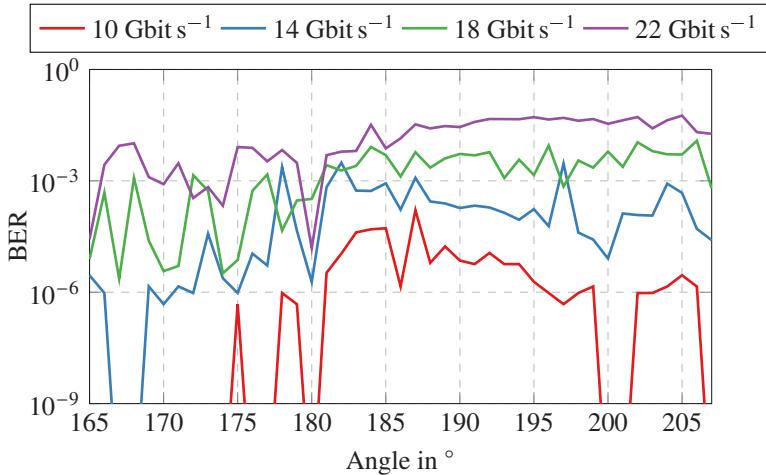

| 7.2.2                             | Bit Error Rate . . . . .                     | 124        |

| 7.3                               | Phased Array Measurements . . . . .          | 134        |

| 7.3.1                             | RF Performance . . . . .                     | 134        |

| 7.3.2                             | Bit Error Rate . . . . .                     | 136        |

| 7.4                               | Comparison to the State of the Art . . . . . | 140        |

| <b>8</b>                          | <b>Conclusion and Outlook . . . . .</b>      | <b>145</b> |

| <b>A</b>                          | <b>Appendix . . . . .</b>                    | <b>149</b> |

| A.1                               | Series Fed Patch Antenna . . . . .           | 149        |

| A.2                               | Buried Feed Resonator Antenna . . . . .      | 152        |

| A.3                               | 3D-Printed Curved Antenna . . . . .          | 155        |

| A.4                               | Differential Test and Measurement . . . . .  | 156        |

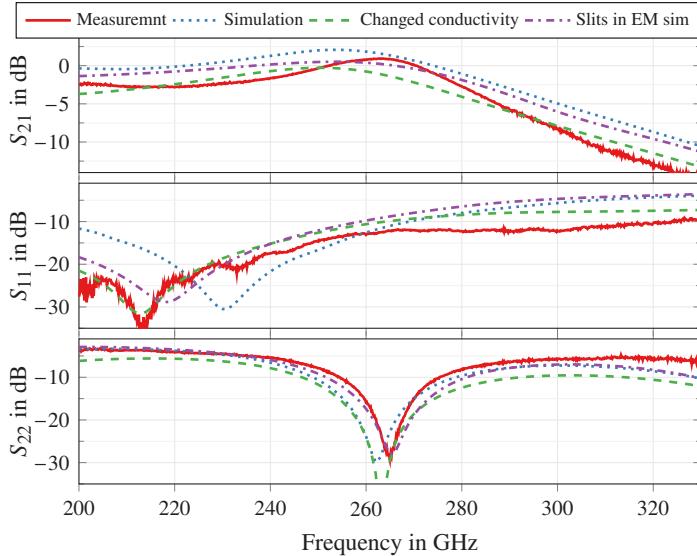

| A.4.1                             | Passive Baluns . . . . .                     | 156        |

| A.4.2                             | Active vs Passive Baluns . . . . .           | 157        |

| <b>References . . . . .</b>       |                                              | <b>161</b> |

| <b>Own Publications . . . . .</b> |                                              | <b>177</b> |

| Journal Publications . . . . .    |                                              | 177        |

| Conference Papers . . . . .       |                                              | 178        |

# Symbols and Abbreviations

## Abbreviations

**AC** alternating current

**ACP** air co-planar

**ASK** amplitude shift keying

**AWG** arbitrary waveform generator

**AWGN** additive white gaussian noise

**BB** baseband

**BEOL** back-end of line

**BER** bit error rate

**BPG** bit pattern generator

**BPSK** binary phase shift keying

**CMA** characteristic mode analysis

**CMIM** capacitor with metal isolation metal layer

**CMOM** capacitor with metal oxide metal layer

**CMOS** complementary metal-oxide-metal

**CPW** coplanar waveguide

**DAC** digital to analog converter

**DC** direct current

**DFG** Deutsche Forschungsgemeinschaft

**DRC** design rule check

**DSP** digital signal processor

**DUT** device under test

**EIRP** equivalent isotropic radiated power

**EM** electro-magnetic

**EVM** error vector magnitude

**FEC** forward error correction

**FFC** flat-flex connector

**FSK** frequency shift keying

**FSPL** free space path loss

**GCPW** grounded coplanar waveguide

**GSG** ground signal ground

**GSSG** ground signal signal ground

**HBT** heterojunction bipolar transistor

**IC** integrated circuit

**IF** intermeditate frequency

**ILA** integrated lens antenna

**ISS** impedance standard substrate

**LBE** localized backside-etching

**LCP** liquid crystalline polymer

**LDO** low dropout regulator

**LO** local oscillator

**MMIC** monolithic microwave integrated circuit

**MOS** metal oxide semiconductor

**MSG** maximum stable gain

**OP1DB** output referred 1 dB compression point

**PA** power amplifier

**PAE** power added efficiency

**PAPR** peak-to-average power ratio

**PBO** power amplifier back-off

**PC** personal computer

**PCB** printed circuit board

**PLL** phase locked loop

**PSK** phase shift keying

**QAM** quadrature amplitude modulation

**QPSK** quadrature phase shift keying

**RF** radio frequency

**SAP** semi additive processing

**SiGe** silicon-germanium

**SLA** stereolithography

**SMD** surface mounted device

**SMU** source measurement unit

**SNR** signal to noise ratio

**TDR** time domain reflectometry

**T/R** combined transmit and receive

**UE** user equipment

**USB** universal serial bus

**VIA** vertical interconnect access

**VNA** vector network analyzer

**WiFi** set of standard relating to wireless LAN

## List of Symbols

|             |                                                                 |

|-------------|-----------------------------------------------------------------|

| $\alpha$    | Attenuation constant                                            |

| $a_i$       | Complex power-wave flowing into port $i$ in $\sqrt{\text{W}}$   |

| $A_i$       | Amplitude                                                       |

| $A(\omega)$ | Transfer function                                               |

| $\beta$     | Phase constant                                                  |

| $b_i$       | Complex power-wave flowing out of port $i$ in $\sqrt{\text{W}}$ |

| <b>BW</b>   | Bandwidth in Hz                                                 |

| $C$         | Capacitance in F                                                |

| <b>C</b>    | Channel capacity in $\text{bit s}^{-1}$                         |

| $\gamma$    | Complex propagation constant                                    |

| $\Delta z$  | Infinitesimal length in m                                       |

| $D$         | Antenna directivity                                             |

| $d$         | Distance in m                                                   |

|                 |                                     |

|-----------------|-------------------------------------|

| $\eta$          | Efficiency                          |

| $\epsilon_r$    | Relative permittivity               |

| $f$             | Frequency in Hz                     |

| $f_0$           | Center frequency in Hz              |

| $f_t$           | Transit frequency in Hz             |

| $f_{\max}$      | Maximum oscillation frequency in Hz |

| $G$             | Conductance in S                    |

| $G_{\text{re}}$ | Realized gain                       |

| $g_n$           | Size identifier in m                |

| $h_n$           | Height in m                         |

| $k$             | Wavenumber in $\text{m}^{-1}$       |

| $L$             | Inductance in H                     |

| $l$             | Length in m                         |

| $\lambda$       | Wavelength in m                     |

| <b>M</b>        | Transforming matrix                 |

| $N$             | Multiplication factor               |

| $\omega$        | Angular frequency in rad            |

| $P$             | Power in W                          |

| $\phi$          | Phase in rad                        |

| $Q$             | Quality factor                      |

| $Q_n$           | Transistor identifier               |

| $R$             | Resistance in $\Omega$              |

| $r_n$           | Radius in m                         |

| $S$             | Radiation intensity in W            |

|                      |                                                                 |

|----------------------|-----------------------------------------------------------------|

| $S_0$                | Radiation intensity of an isotropic source in W                 |

| <b>S</b>             | S-parameter matrix                                              |

| $S_{ij}$             | S-parameter with wave impeding on port $j$ and exiting port $i$ |

| <b>S<sub>M</sub></b> | Mixed-mode S-parameter matrix                                   |

| $s_n$                | Separation in m                                                 |

| <b>SNR</b>           | Signal-to-noise ratio                                           |

| $t$                  | Time in s                                                       |

| $\tan \delta$        | Dielectric loss tangent                                         |

| $V$                  | Voltage in V                                                    |

| $v^+$                | Voltage on the positive node of a differential node in V        |

| $v^-$                | Voltage on the negative node of a differential node in V        |

| $w_n$                | Width in m                                                      |

| $Z_0$                | Complex Impedance in $\Omega$                                   |

| $z_n$                | Height in z-direction in m                                      |

# 1 Introduction

Since its inception three decades ago, the internet has seen unprecedented growth in not only the usage of computers, digital services, and data transmission but also due to the desire of humans to connect and communicate. Where in the past time, phone lines were realized as physical cables and were always bound to a physical location, the introduction of the wireless phone and associated standards marked a shift in how we communicate. The advent of smartphones marked another significant change. With fully featured computers portable and accessible to many, connected wirelessly to a seamless network of computers, servers, and overall, people, the desire for more and better data links is more pressing than ever.

The underlying technology is often underrepresented in its role of advancing the internet and enabling the digital world as we know it. New developments in complementary metal-oxide-metal ([CMOS](#)), [SiGe](#), and III-V semiconductor technology pushed the technically possible. Especially fiber optics saw a significant improvement over the years, achieving over  $1 \text{ Pbit s}^{-1}$  per fiber [[RLP<sup>+</sup>22](#)] building the backbone of the internet. But not only optical communication has proliferated. Wireless technologies profited massively from better analog circuits, higher efficiencies, and more computational power. Higher modulation schemes and more compensation for non-ideal [RF](#) behavior continuously push the achievable data rate even in congested urban environments and adverse conditions. However, these staggering speeds are often brought with bulky and power-hungry equipment unsuitable for direct consumer interaction or implementation in user equipment ([UE](#)).

Even though technology is advancing fast, wireless links are also limited by the available bandwidth and government regulations. The frequency range below 6 GHz is limited in the available bandwidth and shared between many different services. Hence, industry and research are looking into higher operating frequencies offering more bandwidth. This incentive created new frequency bands at 28 GHz and 60 GHz. However, predictions show that these new bands

will not suffice, so even higher frequencies are targeted. The largest window currently planned ranges from 64 GHz to 71 GHz but even higher frequencies are considered [Fed22].

Operating frequency alone is not the only factor limiting data-rate. Congestion on shared channels and regulations force a lot more overhead on the protocol layer, further decreasing the data-rate. To make the most of the available channel bandwidths and transmission windows higher order modulations are used. These necessitate power hungry IQ-Systems and pre-distortion to exploit the analog hardware and channel to the fullest. The set of standard relating to wireless LAN (WiFi) chipset in a smartphone needs between  $1.3 \text{ nJ bit}^{-1}$  to  $5 \text{ nJ bit}^{-1}$  to achieve a speed of  $400 \text{ Mbit s}^{-1}$  [AGB<sup>21</sup>]. Even worse is 5G with an energy per bit of  $500 \text{ nJ bit}^{-1}$  depending on traffic [XZZ<sup>20</sup>].

Considering the mentioned points, seeking higher operating frequencies to bridge the gap between backbone infrastructure and UE becomes detrimental. Increasing the frequency also reduces antenna sizes to the point where high-gain antennas or larger antenna arrays can fit comfortably, even in smartphones. In contrast, larger absolute bandwidth availability in the frequency spectrum allows simpler modulation schemes to reduce power consumption and circuit complexity. A possible downside is the higher atmospheric attenuation coupled with free space path loss limiting the range. However, this can also be seen as a benefit in crowded scenarios as spatial multiplexing becomes more manageable. Even simple physical objects like thin walls can serve as effective shielding between multiple transmission channels, reducing the necessary protocol layer.

Choosing a new, significantly higher frequency band is constrained by certain physical limitations. Water absorption windows in the atmosphere drive the choice of suitable channels outside of applications in space. One such window is around 140 GHz and is currently under investigation for the upcoming 6G standard [AAKG23]. Nevertheless, as advancements in the silicon-based transistor technology offer us transistors exceeding an  $f_{\max}$  of 500 GHz, even higher frequencies can be investigated. This is mainly driven by advancements in SiGe-based transistors, where the base region of a vertical NPN-transistor is doped with germanium to enhance the drift velocity and increase the operating frequency. IHP was the first to offer transistors with an  $f_{\max}$  over 500 GHz (DotFIVE) in 2015 [CCL<sup>10</sup>] and recently offered the next gener-

ation of technology with an  $f_{\max}$  of over 700 GHz (DotSEVEN) [SBd<sup>+</sup>16]. However, the latter technology was introduced too late to be used in this work.

Concerning the transmission medium and frequency the absorption window around 254 GHz offering up to 100 GHz of bandwidth [PAB<sup>21</sup>] is quite interesting. Which, if utilized with a quadrature amplitude modulation (QAM) 1024 signal, could lead to  $1 \text{ Tbit s}^{-1}$  data transmission. As work in this range is under investigation, no real spectrum assignment by governing bodies is present. First attempts in standardization are done with IEEE 802.15.3d, describing a channel from 252 GHz to 325 GHz for point to point communication with up to  $100 \text{ Gbit s}^{-1}$  [IEE17]. However, neither the American Federal Communication Commission (FCC) [Fed22] nor the European Electronic Communications Committee (ECC) [Ele23] have allocated this standard or anything else above 275 GHz and only rudimentary satellite bands between 100 GHz to 275 GHz, making it still a free space to explore different concepts and frequencies.

## 1.1 Objective of this Thesis

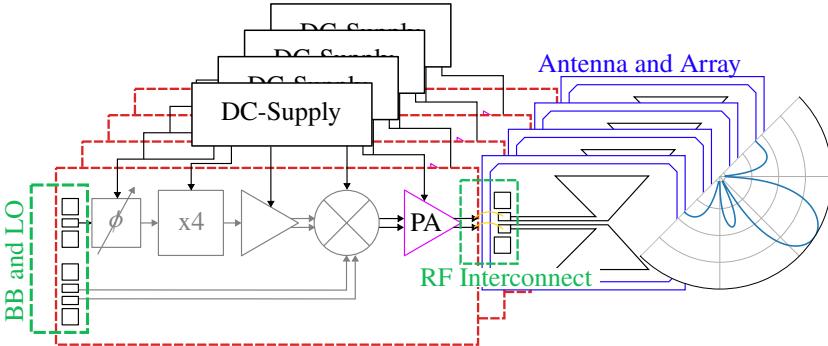

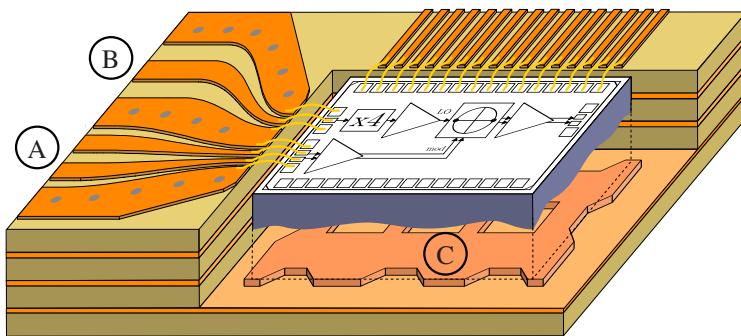

In the Deutsche Forschungsgemeinschaft (DFG) funded project "ADAMIS" (Adaptive Millimeter Wave Transmitters), the aim is to develop a power-efficient and compact BPSK transmitter with beam steering capability. Fig. 1.1 illustrates the system's general concept. The LO and BB signals are externally generated and fed into the MMIC to be designed. The LO signal is fed into a phase shifter ranging from  $0^\circ$  to  $90^\circ$ . It precedes the times four multiplier chain to achieve a continuous  $0^\circ$  to  $360^\circ$  phase shift in the RF domain. An amplifier buffers the multiplied LO-signal before it drives the modulator. The modulator is a modified gilbert cell which uses the BB signal to switch the LO signal between  $0^\circ$  and  $180^\circ$ , creating the BPSK modulation. The output signal is fed into the PA, which is connected to the antenna. A phased array system is realized by combining multiple MMICs.

A low-order modulation scheme like BPSK reduces the spectral efficiency but also the circuit complexity. BPSK modulation can directly be created by the use of a modulator. Not needing a digital to analog converter (DAC) and a digital signal processor (DSP) chain to calculate high bit-rate modulation waveforms decreases overall system complexity severly and reduces power consumption. Baseband circuits with a binary output are currently available

Figure 1.1: Overview of the system architecture with designated tasks and array configuration.

up to  $28 \text{ Gbit s}^{-1}$  [HCY<sup>+</sup>13], hence a **BPSK** system can directly feed the binary bitstream into the modulator bypassing a large portion of traditional transmitter circuitry.

The components shaded in gray in Fig. 1.1 are developed by the *Chair of Circuit Design and Network Theory* at *Technische Universität Dresden*, as described in the dissertation of *Luca Steinweg* [Ste23]. This work investigates besides the wideband **PA** also wideband antennas, packaging for wideband signals, and adaptivity at both **MMIC** and system levels. Previous efforts in this frequency range have been limited by fixed setups, hindering their versatility across usage scenarios, a limitation this work aims to overcome.

Considering these factors, the decision was made to operate around 246 GHz, providing ample bandwidth of at least 50 GHz. This avoids equipment limitations and offers more headroom for transistors. This choice of frequency center allows for technological and practical benefits without current regulation constraints.

Furthermore, this dissertation focuses on developing a system suitable for future applications within the last-meter domain, distinct from high-gain antenna-based systems designed for long-range communication. The emphasis is on creating a flexible chip and packaging concept that can adapt to various applications within the last meter domain or **UE** scenarios. Hence a phased array solution is sought that adapts dynamically to the presented scenario.

The thesis covers three main areas of work: designing a power amplifier that meets bandwidth, output power, and efficiency requirements while being co-designed with system interconnect solutions and antenna concepts; developing **RF** interconnect solutions, including packaging that balance performance with flexibility and adaptability; and designing an antenna concept suitable for phased array applications with targeted data rates, ensuring seamless integration with the overall system design. Finally all three parts are tied together to realize a phased array transmitter system.

## 1.2 Structure of this Thesis

The first chapter describes the work's motivation and the objectives and framework wherein this work is done.

Chapter 2 provides an introduction into the necessary theoretical concepts to contextualize the work of this theses. First the mathematical representation of differential **RF** circuits are presented. Next the conductor based transmission of such signals is investigated. This is concluded by a short overview of antennas theory. Further, digital modulation schemes are explained and lastly the circuit design aspects of **PA** design is detailed.

Chapter 3 introduces system aspects and considerations, presenting mathematical and physical groundwork for the used target metrics and goals. Physical limitations and trade-offs are also described to contextualize the results.

Chapter 4 introduces the power amplifier design and the measurement results of the amplifier itself. After presenting a thorough state of the art analysis the proposed design is introduced and explained. Different possible technologies are compared against each other and the best option chosen. The design details are highlighted and the final design characterized.

Chapter 5 introduces the antenna concept, and chapter 6 presents the packaging of the whole system.

Finally, chapter 7 presents the measurement of the realized transmitter samples over many measured metrics. For this, the measurement setup is introduced and described. Then, two different concepts of a single **MMIC** with antenna is measured and compared against each other. Using **BER** measurements

as a direct transmission quality metric, the transmitters are evaluated over transmission angle, distance, and data rate. Based on these measurements, two phased-array systems are measured and compared against each other.

Lastly, chapter 8 concludes and gives an outlook for future research.

## 2 Physical Background

Pushing the state of the art in mmWave and THz transceivers means pushing the boundaries of the technologically possible. This necessitates a deeply rooted understanding of many of the underlying physical concepts and their implication for the design, analysis and measurement. In the following, certain key aspects will be presented and the intricate details explained.

### 2.1 Differential S-Parameters

S-Parameters are a highly effective metric to analyze and characterize **RF** systems and components and found widespread use in the realm of **RF** system design [Poz05]. One main advantage over time domain voltages and currents is the possibility to measure them at high frequencies and on wave guiding structures, that have no definition for voltage nodes and currents. Further, they are mathematically cascadable allowing to calculate the overall performance based on component wise measurements. Hence they play a vital role in analyzing circuits, transitions and antennas designed within this work.

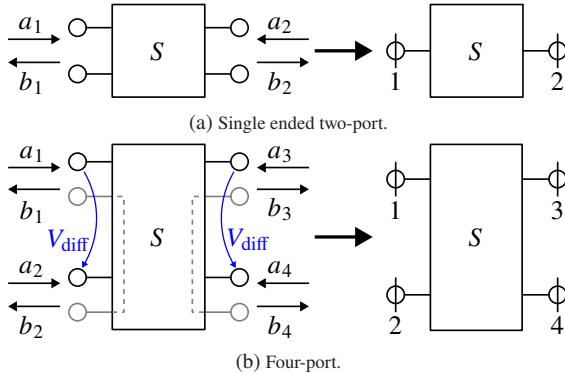

The definition of S-parameters is based on single ended circuits as shown in Fig. 2.1(a). Each port of the exemplary 2-port device is constituted of two pins to complete a current loop in circuit analysis. Conceptually, a power wave  $a_1$  is impinging on port 1 of the device, which results in a partly reflected wave  $b_1$  and a transmission on port 2 with  $b_2$ . The power waves are defined as

$$a_i = \frac{1}{2} k_i (V_i + Z_i I_i), \quad (2.1)$$

$$b_i = \frac{1}{2} k_i (V_i + Z_i^* I_i), \quad (2.2)$$

Figure 2.1: Schematic S-parameter definitions.

with  $k_i$  being

$$k_i = \left( \sqrt{\mathbb{R}\{Z_i\}} \right)^{-1}. \quad (2.3)$$

They relate the voltage  $V_i$  on port  $i$  to the current  $I_i$  with the characteristic impedance on the respective port  $Z_i$ . Hence, they have the unit  $\sqrt{\text{W}}$  as the represent a quasi power wave [Kur65].

The S-parameters for the two-port shown in Fig. 2.1(a) are then calculated as

$$\begin{aligned} S_{11} &= \left. \frac{b_1}{a_1} \right|_{a_2=0}, & S_{22} &= \left. \frac{b_2}{a_2} \right|_{a_1=0}, \\ S_{21} &= \left. \frac{b_2}{a_1} \right|_{a_2=0}, & S_{12} &= \left. \frac{b_1}{a_2} \right|_{a_1=0}. \end{aligned}$$

Expanding this formulation for differential systems is not directly possible. Differential signaling is based on two signal conductors that are  $180^\circ$  out of phase. The signal is the difference between both signal conductors, resulting in a cancellation of common mode currents and voltages. Based on this, the voltages and currents used for the definition of  $a_i$  and  $b_i$  are not clearly defined. One approach to overcome this limit is the extension of the differential port into two independent single ended ports as indicated in Fig. 2.1(b) by using an additional reference pin on each port [Poz05]. This extension is however only

Figure 2.2: Possible stimuli for a differential port.

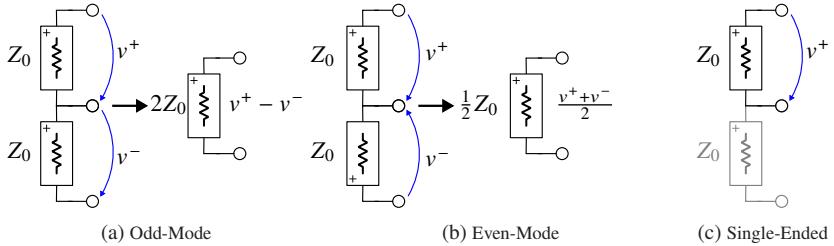

applicable in very specific circumstances. Investigating the electrical behavior on a differential port, three distinct cases can be identified as shown in Fig. 2.2. The ideal case, also called odd-mode, is the differential feed with the electrical signals on both pins  $180^\circ$  apart as shown in Fig. 2.2(a). Fed from two single ended sources with impedance  $Z_0$ , this yields a virtual feeding impedance of  $2Z_0$ . The opposing case is the even-mode, where both signals are in-phase, yielding the stimulus shown in Fig. 2.2(b). Here both sources are in parallel yielding a virtual impedance of  $0.5Z_0$ . A third extreme case is the feed with only a single signal on one of the differential pins [Poz05].

Concerning the voltages  $v^+$  and  $v^-$  we can write them as

$$v^+ = A_1 e^{j(\omega t + \phi_1)}, \quad (2.4)$$

$$v^- = A_2 e^{j(\omega t + \phi_2)}. \quad (2.5)$$

The differential voltage across the two pins of the terminal is then

$$V_{\text{diff}} = v^+ - v^-, \quad (2.6)$$

$$V_{\text{diff}} = A_1 e^{j(\omega t + \phi_1)} - A_2 e^{j(\omega t + \phi_2)}. \quad (2.7)$$

The three cases in Fig. 2.2 can now be described by the relation of amplitude and phase of each signal. For the symmetric stimulus the amplitudes are the same  $A_1 = A_2$  but the phase difference either  $\phi_1 - \phi_2 = 0$  or  $\phi_1 - \phi_2 = 180$  for even and odd-mode respectively. The single ended case sees one amplitude to be zero. However, any combination of phase and amplitude is possible which is described as the superposition of the three distinct cases.

Lastly, if the device under test (DUT) can be assumed to be a linear network the superposition of the input signals has to be possible. This allows to measure or simulate a differential two-port as a single-ended four port device. The resulting single-ended 4x4 S-parameter matrix  $\mathbf{S}$  then can be used to calculate the odd- and even-mode response. This can be handily achieved by a matrix multiplication

$$\mathbf{M} = \frac{1}{\sqrt{2}} \begin{bmatrix} 1 & -1 & 0 & 0 \\ 0 & 0 & 1 & -1 \\ 1 & 1 & 0 & 0 \\ 0 & 0 & 1 & 1 \end{bmatrix}, \quad (2.8)$$

$$(2.9)$$

resulting in the mixed mode S-parameter matrix

$$\mathbf{S}_M = \mathbf{M} \cdot \mathbf{S} \cdot \mathbf{M}^{-1}. \quad (2.10)$$

The matrix  $\mathbf{M}$  is used to calculate the two cases of odd- and even mode stimulus. The resulting mixed mode matrix

$$\mathbf{S}_M = \begin{bmatrix} S_{dd11} & S_{dd12} & S_{dc11} & S_{dc12} \\ S_{dd21} & S_{dd22} & S_{dc21} & S_{dc22} \\ S_{cc11} & S_{cc12} & S_{cc11} & S_{cc12} \\ S_{cc21} & S_{cc22} & S_{cc21} & S_{cc22} \end{bmatrix} \quad (2.11)$$

consists out of the differential and common-mode S-parameters as well as the common-to-differential and differential-to-common mode parameters [Zhu10]. That is the common-mode response to a differential-mode stimulus and vice versa. This analysis approach can also be used for three port devices such as

baluns, that convert a single ended input to a differential output. Assuming the single ended port to be port three, the matrix is

$$\mathbf{M}_{\text{mixed}} = \frac{1}{\sqrt{2}} \begin{bmatrix} 1 & -1 & 0 \\ 1 & 1 & 0 \\ 0 & 0 & \sqrt{2} \end{bmatrix}, \quad (2.12)$$

$$\mathbf{S}_M = \begin{bmatrix} S_{cc11} & S_{dc11} & S_{sc12} \\ S_{cd11} & S_{dd11} & S_{sd12} \\ S_{cs21} & S_{ds21} & S_{33} \end{bmatrix}. \quad (2.13)$$

With these new formed two-port matrices, established analysis tools like rollett-k factor or maximum stable gain ([MSG](#)) can be applied to study the linear differential circuit. While these calculations are fairly easy and yield accurate results, they are only applicable to linear systems such as passive circuits and small-signal analysis of active circuits. Non-linear systems necessitate a true to real world stimulus, which is however not necessarily defined. As evident from Eq. 2.7 any combination of amplitude and phase might be present at the input of a device, which theoretically needs to be evaluated to check for instability or other issues. This is impractical and has to be reduced to the stimulus expected within the application.

One last issue with differential circuit analysis is the presented impedance for the different stimulus cases shown in Fig. 2.2. The simple approach to model the feed as two independent sources with impedance  $Z_0$  is only valid in some applications. There are however antennas, transmission lines or transformers that do not present themselves as two sources but present rather different impedances for the different cases. A transformer should present itself as an open circuit to a common-mode signal as the current through the coil is zero, while the differential signal will couple through. Practically this can cause common-mode voltage swing issues with the common-mode wave being reflected back into the [DUT](#) if not properly designed [[WRE06](#)].

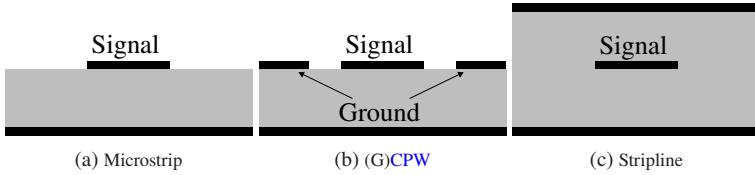

Figure 2.3: Cross section through different planar transmission lines.

Figure 2.4: Different Model Views.

## 2.2 Differential Planar Transmission Lines

Transmission lines are conductor based waveguides essential in almost all RF systems. Some of the most common planar types are the microstrip line, the coplanar waveguide (CPW) and the strip line as shown in Fig. 2.3. Within planar circuits and especially MMICs the microstrip and grounded coplanar waveguide (GCPW) lines are favored [Raz98].

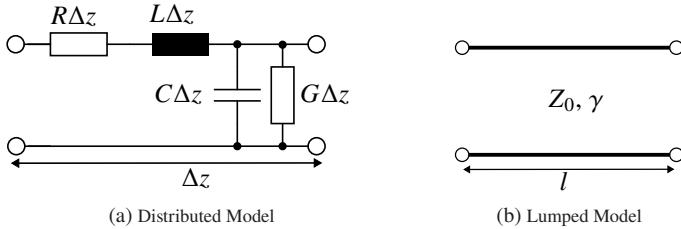

From [Poz05], a transmission line can be approximated by a series inductor and resistor as well as a parallel capacitor and conductance as shown in Fig. 2.4(a). This network has to be distributed along the length  $z$  of the conductor in steps  $\Delta z$  significantly smaller than the wavelength  $\Delta z \ll \lambda/10$ . As calculating the response of a large network of small elements is time consuming, a lumped element model of a transmission line is developed. It is based on the apparent line impedance  $Z_0$ , a complex propagation constant  $\gamma$  and the physical length  $l$ .

The characteristic impedance relates to the elements of the distributed model with

$$Z_0 = \sqrt{\frac{R + j\omega L}{G + j\omega C}} \quad (2.14)$$

as shown in [Poz05]. If the losses in the transmission line are negligible small, which is the desired state in most transmission lines Eq. 2.14 simplifies to

$$Z_0 \simeq \sqrt{\frac{L}{C}}. \quad (2.15)$$

The complex propagation constant is

$$\gamma = \sqrt{(R + j\omega L)(G + j\omega C)}. \quad (2.16)$$

With the assumption that the lines are low loss, which is expected in most applications, it can be expanded to

$$\gamma = \alpha + \beta, \quad (2.17)$$

$$\alpha \simeq \frac{1}{2} \left( \frac{R}{Z_0} + GZ_0 \right), \quad (2.18)$$

$$\beta \simeq \omega \sqrt{LC}, \quad (2.19)$$

as shown in [Poz05].

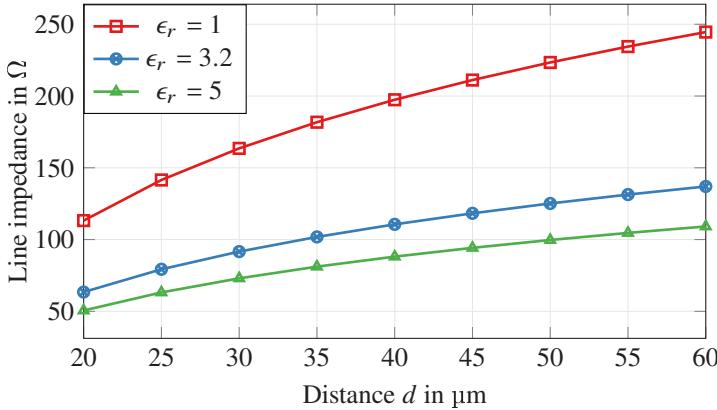

To extend the single-ended microstrip line to a differential line, an additional signal conductor is placed in parallel to the first one as shown in Fig. 2.5. From the plotted field lines a significant difference between the single ended and differential case is visible. The coupling between the lines significantly influences the characteristic impedance of the even and odd modes. Close spacing of the conductors or a far away ground plane create the case of a two-wire line with strong coupling between the two conductors. Wide separation of the lines or a close ground plane will remove any coupling and two independent microstrip-lines are present. In the later case tuning the impedance of each line to  $50\Omega$  will create a  $100\Omega$  odd mode impedance and a  $25\Omega$  common impedance. However, the lines are independent and can have significant phase shift between each other, increasing mode conversion. Spacing the lines

Figure 2.5: Differential microstrip line.

closer together the even-mode impedance can change significantly and phase-deviations between the two lines are minimized.

## 2.3 Wideband Planar Antennas

The targeted application necessitates wideband antennas with efficient radiation. To qualify the achieved results first the theoretical limits have to be introduced. Antennas are described in terms of their physical size, efficiency, directivity and the bandwidth.

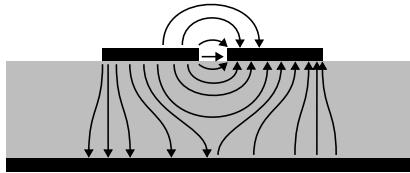

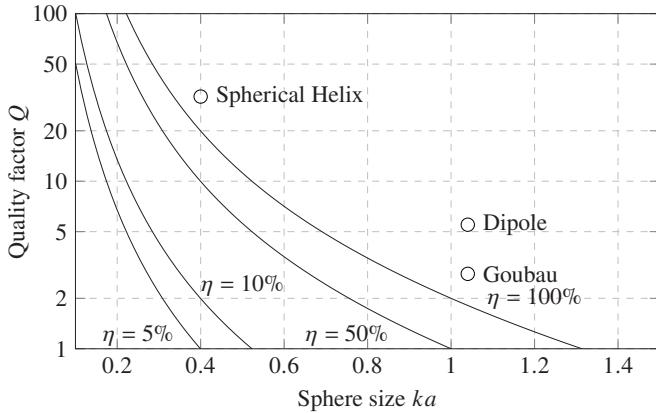

The physical size of an antenna is often non-trivial to determine as all physical elements that significantly interact with the antenna have to be considered. While theoretical assumptions can ignore the physical environment, this simplification cannot be done in modern day complex scenarios such as on-chip or highly integrated on-substrate antennas. Hence, careful analysis of the antenna and interactions in the near field have to be done to accurately estimate the antennas performance. Related to this is the boundary between the near-field, radiating near-field and the far-field as depicted in Fig. 2.6. The near-field describes the reactive region of the fields where interactions directly influence an antennas radiation pattern and hence have to be included in the physical size. The far-field region describes the region where the transmitted energy behaves optically and no influence on the antenna is present. The region in between is the radiating near-field, which for some antennas might not be present at all [Bal16].

The efficiency relates the radiated power  $P_{\text{rad}}$  to the accepted incident power  $P_{\text{in}}$  by

$$\eta = \frac{P_{\text{rad}}}{P_{\text{in}}}. \quad (2.20)$$

Figure 2.6: Radiating field definitions on an arbitrary antenna with  $a$  as the radius of the smallest sphere encompassing the antenna.

Hence, the efficiency quantifies ohmic and dielectric losses in the designed antenna. The directivity describes the relative radiation in a specific direction to the average radiation intensity of the antenna or an equivalent isotropic antenna

$$D = \frac{S}{S_0} = \frac{4\pi S}{P_{\text{rad}}}. \quad (2.21)$$

$S$  is the radiation intensity at a specific point and  $U_0$  the radiation intensity of an isotropic source. The directivity does not include the efficiency of an antenna. Hence practical antennas are quantified by their realized gain which is related to the directivity by

$$G_{\text{re}}(\theta, \phi) = \eta \cdot D(\theta, \phi). \quad (2.22)$$

It includes all the losses of the antenna and represents the gain observable in a measurement setup.

Figure 2.7: Chu-Harrington limit of single-mode antenna radiation [Han81].

The bandwidth of an antenna can be related to either the input return loss or the frequency range where its intended radiation behavior stays nearly the same. With the assumption of high efficiency and consequently low loss the input return loss should indicate radiation and hence offers itself as a valid metric. However, with low efficiency it indicates ohmic losses rather than radiation. Hence, other metrics such as the realized gain are used. This is also true in scenarios where the input match cannot be accurately measured such as directly connected antennas.

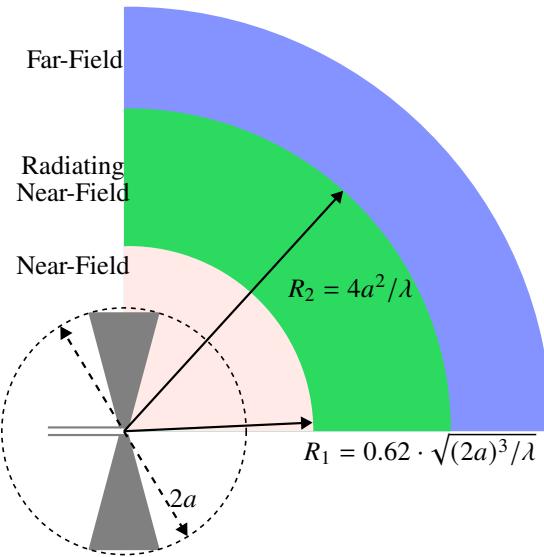

Based on these definitions fundamental limits of antennas can be deducted. A first theoretical limit was introduced by the works of Chu [Chu48] and Harrington [Har60] and reviewed by Hansen [Han81] and relates the physical size of an antenna to the achievable quality factors concerning different efficiencies as plotted in Fig. 2.7. The quality factor relates to the bandwidth with

$$BW = \frac{1}{Q}. \quad (2.23)$$

The size of an antenna is measured as the smallest sphere with radius  $a$  that encompasses the antenna itself [Han81].  $k$  is the wavenumber. The curves plotted in Fig. 2.7 represent the theoretical lower limit. Further some points

Figure 2.8: Directivity limit over antenna size [Bal16].

for ideal antennas are plotted as reference. The main observation of this plot is that bandwidth of an antenna necessitates a larger structure.

Another fundamental limit is the achievable directivity for a given aperture size plotted in Fig. 2.8. Again it is observable that higher directivity necessitates a larger aperture and hence a larger antenna.

For planar antennas these two limits pose some interesting challenges. Due to inherent limitation of a planar antenna the volumetric efficiency of the engulfing sphere is poor. Any increase in antenna size causes the sphere to increase as well. Hence, concepts have to be followed that utilize the 3D volume better to enhance the performance of the antenna. The second implication of Fig. 2.8 is the maximum gain achievable.

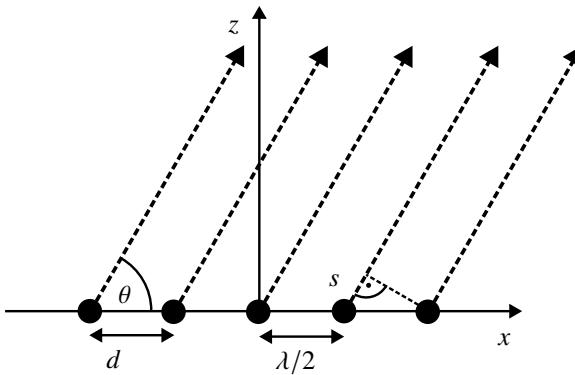

## 2.4 Planar Phased Arrays

In the previous section, single antenna elements that should provide a large radiation bandwidth with a small physical size were investigated. However, due to the free space path loss (FSPL) at sub-THz frequencies, high gain is necessary to establish robust transmission links over distances above a few meters of range. As Fig. 2.8 shows, the directivity is directly linked to the

Figure 2.9: Schematic of a phased array.

antenna's physical size. This yields a conflict where, on one hand, a small antenna element is desired, and simultaneously, a large aperture is required. Another solution to increase an antenna configuration's aperture is placing multiple radiators in a geometrical arrangement called an array. The overall antenna pattern is the vector sum of each element, with the constraint that the elements have to be placed within the near-field regions of each other. Feeding all antennas a correlated signal creates constructive and destructive interference in the near-field zone, shaping the radiation pattern.

Investigating the most straightforward case, a 1D-array of isotropic radiators, a configuration shown in Fig. 2.9 is present. The elements are spaced  $\lambda/2$  apart, which is the best case for an antenna array. If each element is fed with the same sinusoid and zero phase shift between each other, the field should be added constructively in  $z$ -direction. Introducing a phase-shift between each element, the constructive interference happens at an angle  $\theta$ . This is a very interesting use case for phased arrays, as it allows us to change the beam direction of such an array electrically. Evidently, from Fig. 2.9, tilting the beam creates a time delay between the individual elements that, for a pure sinus signal, translates to a phase shift. The physical additional length of the individual signals depends on the steering angle  $\theta$  by  $s = d \cdot \cos(\theta)$ . The overall radiated field can be

calculated by the field of a single radiating element and a function called the *array factor*

$$AF(\hat{r}) = \sum_{n=1}^N a_n e^{jk\hat{r} \cdot \vec{r}_n}, \quad (2.24)$$

which is a function of the physical location of all radiators  $\vec{r}_n$ , their complex excitation  $a_n$  and the direction unit vector  $\hat{r}$  [Bal16]. The array factor is calculated assuming isotropic radiators and is applied to an arbitrary radiator by multiplication

$$\mathbf{E}_{\text{array}} = \mathbf{E} \times AF. \quad (2.25)$$

The AF for the linear uniform five-element array shown in Fig. 2.9 is

$$AF = \sum_{n=1}^5 e^{j(n-1)(kd \cos \theta + \beta)}, \quad (2.26)$$

with  $\beta$  the phase difference between two adjacent elements.

The increase in directivity of the array depends on the array factor. For the linear array with isotropic radiators with broad-side radiation, the directivity is

$$D_0 \simeq \frac{Nkd}{\pi} = 2N \left( \frac{d}{\lambda} \right). \quad (2.27)$$

While this equation suggests a larger spacing of the elements will increase the directivity, this does not mathematically hold. First, the assumptions to derive the equation assume a spacing well below  $\lambda$  [Bal16]. Next, increasing the spacing also increases the aperture, so an antenna array with more elements spanning the same physical area should be considered for a fair comparison. Effectively, one can assume an  $N$ -times increase in directivity for an  $N$ -element array.

As evident so far, the spacing of the elements plays a crucial role in the correct operation of the phased array. Spacing above  $\lambda/2$  causes increased phase shift between elements and causes additional zeros and maxima. This increases secondary radiation peaks called side lobes, especially for steering. This is often unwanted as it reduces the directivity of the main beam and radiates energy in unwanted directions. Spacings below  $\lambda/2$  increase the coupling between antenna elements. This either necessitates much larger currents in the antennas to achieve the desired pattern or creates radiation in the

$x$ -direction, called end-fire. Contrary, as explained in Sec. 2.3, some antennas cannot be physically smaller than  $\lambda/2$  to suffice the spacing requirement. The concepts of the 1D array can be extended to a planar 2D or even a 3D array. All investigations so far assume a narrow-band signal that a sinusoid can approximate to simplify the mathematical modeling. However, investigating Fig. 2.9, one can deduce that the distance  $s$  is the physical distance a signal has to travel. This means that the phase shift has to change with frequency for correct operation over a wider bandwidth. Keeping a constant phase shift, as this is physically easier to implement, an effect called beam-squint happens. This is a change in beam angle over frequency, causing a loss of signal power. To avoid beam-squinting, the signals have to be time-delayed to be able to be overlaid correctly [Bal16].

## 2.5 Digital Modulation

Digital modulation is a process where a digital data stream is encoded onto a carrier signal for transmission over a communication channel. It involves mapping the digital data bits onto variations in one or more characteristics of the carrier signal, such as amplitude, frequency, or phase. The three fundamental digital modulation techniques per [Poz05] are:

1. amplitude shift keying (**ASK**): In **ASK**, the amplitude of the carrier signal is varied to represent the binary data. For example, a high amplitude can represent a binary one, while a low amplitude represents a binary zero.

2. frequency shift keying (**FSK**): In **FSK**, the frequency of the carrier signal is shifted between discrete values to represent the binary data.

3. phase shift keying (**PSK**): In **PSK**, the phase of the carrier signal is varied to represent the binary data. Different phase shifts correspond to different binary values. Common examples include **BPSK** and quadrature phase shift keying (**QPSK**).

More advanced digital modulation techniques, such as **QAM**, combine amplitude and phase modulation to increase the data rate and spectral efficiency.

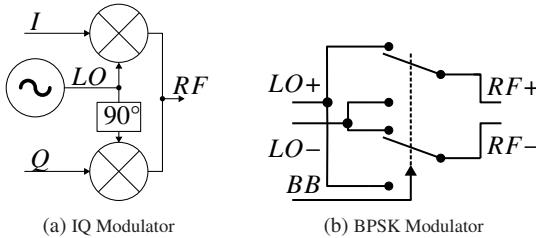

Figure 2.10: RF up-conversion circuits.

A differentiation between symbols and bits is done to distinguish the different operating principle of digital modulation compared to binary data representation. Within one time frame one symbol is transmitted, which can encode more than one bit of information. In case of a **QPSK** this is two bits, a **QAM-1024** would encode 10-bit. Hence a mapping of bits to symbols is necessary as a first step in the digital modulation scheme. Next is the modulation of the analog **LO** signal. This can be done in different ways depending on the targeted modulation and system constraints.

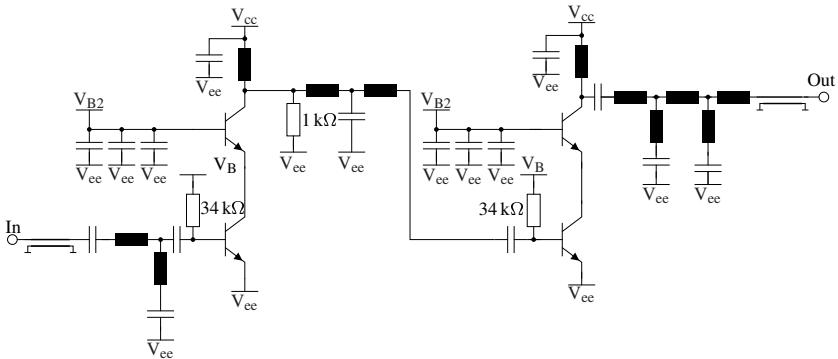

The universal mathematical approach to modulation is the superposition of scaled in-phase(I) and quadrature(Q) components. This is achieved by splitting the **LO** signal into a direct branch and one  $90^\circ$  shifted signal. Those two components are then multiplied by individual weighting factors and the result summed together. A circuit implementation is shown in Fig. 2.10(a). This approach can generate any form of digital modulation by feeding in the correct amplitudes to the **I** and **Q** component. A simpler approach for lower order modulations is the **BPSK** modulator shown in Fig. 2.10(b). Here the data-signal, called **BB**, is driving two synchronous switches, which in turn change the polarity of the **LO** signal. This generates the modulated RF output with a dual-sideband characteristic.

## 2.6 Power Amplifiers

Amplification is a common task in **RF** systems, so amplifiers are ubiquitous. Amplifier topologies and approaches are classified by output power, noise

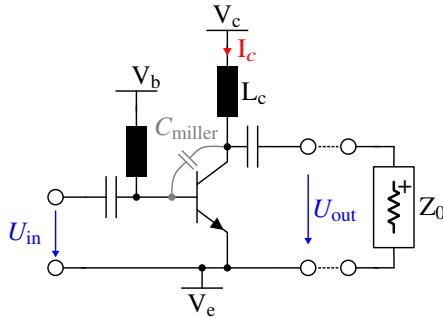

Figure 2.11: Schematic of a SiGe power amplifier.

contribution, bandwidth, or linearity metrics. Power amplifiers, in particular, differentiate themselves by providing the highest output power possible given the operational and technological constraints. In this context, efficiency is also a crucial aspect optimized for **PA**s as cooling and overall power consumption are important factors. Other constraints limiting the design are bandwidth and linearity constraints [Raz98].

A simple amplifier circuit realized with SiGe heterojunction bipolar transistors (HBTs) is shown in Fig. 2.11. The circuit consists of a common-emitter amplifier circuit with reactive collector loading through the inductor  $L_c$ . The input and output are capacitively coupled. A power amplifier aims to provide the largest output voltage swing  $U_{out}$  into a load with impedance  $Z_0$ . However, it is evident that the transistor output voltage swing is limited by the collector supply voltage  $V_c$  and can, with reactive loading, only ever rise to  $2 \cdot V_c$ . The maximum collector voltage is limited by the breakdown voltage of the transistors, which is a technology-dependent parameter. The current through the transistor can be controlled by the number of transistors in parallel and, hence, can be increased to a certain degree. Consequently, power amplifiers tend to have a very low output impedance as it is easier to increase the collector current to get more power than to increase the collector voltage through stacking. This then necessitates some form of reactive impedance transformer to change the near-short impedance of the **PA** back to typically  $50\Omega$  system impedance [Raz98].

The increased power of more transistors in parallel is limited by the input  $RC$  constant formed by the base-emitter capacitance and the base resistance.

Hence, as frequency increases, the number of parallel transistors decreases for a given technology. Another limiting factor is the matching bandwidth of an input and output matching network. The closer the output tends to a short circuit, that is, very high currents with minimal voltage swing, the more narrowband and lossy a matching network becomes. Hence, proper design has to trade-off losses in the matching networks, transistor sizing and surface area for the matching networks. Another limiting factor is the miller capacitance denoted  $C_{miller}$  in Fig. 2.11. It is the intrinsic and parasitic collector-base capacitance and presents a feedback path, causing stability issues. A common approach to reducing the miller-effect is using a cascode, which has another common-base amplifier on top of the common-emitter amplifier, which keeps the voltage on the collector node close to the input signal and limits the coupling effect [Raz98].

To characterize a **PA** the following metrics are used within this work:

#### 1. Saturated Output Power

The highest output power achieved under single tone stimulus.

#### 2. Small Signal Bandwidth

Defined as the 3 dB bandwidth of  $S_{21}$ .

#### 3. Large Signal Bandwidth

Defined as the 3 dB bandwidth of the output power over frequency.

#### 4. Power Consumption

Consumed direct current (**DC**) power over all circuit parts that are part of the **PA**.

#### 5. Efficiency, power added efficiency (**PAE**)

The efficiency relates the delivered **RF** output power to the consumed **DC** power. However, low gain amplifier stages tend to also translate a significant amount of input **RF** power, hence the **PAE** is used as a metric to include that. **PAE** is defined as  $PAE = \frac{P_L - P_{in}}{P_{DC}}$ .

#### 6. output referred 1 dB compression point (**OP1DB**)

1 dB compression point of the single-tone output power, referred to the achieved output power.

## 7. Size

The physical size of the PA as a metric of spatial efficiency.

## 8. Stability

Not a direct metric per se, but analyzed to ensure stable operation over all conditions.

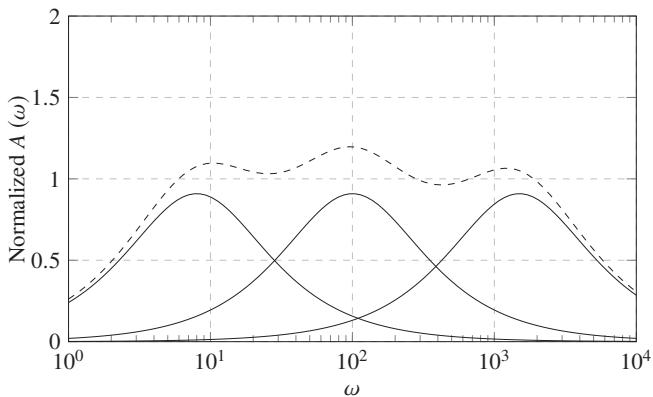

## 2.7 Frequency Staggering

A common issue with increasing data rates is the necessary bandwidth in all components. Improving an amplifier's operating bandwidth is not as straightforward as modifying a matching network, as the Bode-Fano limit puts mathematical bounds to reactive matching and bandwidth [Poz05]. One approach to overcome this limit is the traveling wave approach, which tries to compensate the transistor's input capacitance by cascading multiple transistors with inductive line segments that form a pseudo transmission line. While this approach can achieve extreme bandwidths, it also consumes a large surface area and increases power consumption [Raz98].

Hence, another solution is used in the form of frequency staggering. The basic idea is the superposition of detuned bandpass filter responses of cascaded amplifiers, resulting in a broadband gain. This concept is plotted in Fig. 2.12. The basic bandpass response is assumed as

$$A(\omega) = \frac{A_0}{1 + Q \cdot \left( \frac{\omega_0}{\omega} + \frac{\omega}{\omega_0} \right)}. \quad (2.28)$$

The superposition of correctly tuned responses results in the dashed line in Fig. 2.12 and yields a bandwidth enhancement. It should be noted that the transfer function of a real amplifier is more complicated than assumed in Eq. 2.28. Hence, a realistic design requires more effort to correctly tune the amplitude and phase response to get a correct overlay response. Another limitation comes with non-linearity. While the additivity and homogeneity

Figure 2.12: Superposition of stagger tuned bandpass filter responses.

under small-signal stimulus are valid, large signal conditions will drastically influence the overall response.

## 3 System and Implementation Constraints

Figure 1.1 presents an abstract representation of the targeted system architecture. The selected operating frequency range presents both advantages and challenges. The absence of regulatory constraints and frequency allocation allows for flexibility in bandwidth occupation, signal strength and center frequency. However, this lack of external limitations also requires the careful determination of system design parameters.

Tying directly into these considerations is the choice of modulation scheme. Hence in the following section the benefits and downsides of different modulation schemes is discussed and analyzed. Going further, the physical constraints for the phased array antenna are discussed based on a study of the state of the art. Following the interaction between the **MMIC** and antenna is analyzed. Finally some measurement constraints are presented that are considered for the system conception.

### 3.1 Choice of Modulation Type

The achievable data rate in an additive white gaussian noise (**AWGN**) channel is given by the Shannon-Hartley theorem:

$$C = BW \log_2 (1 + SNR) . \quad (3.1)$$

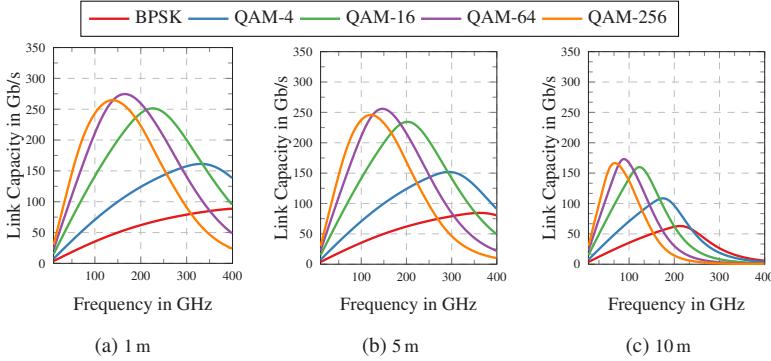

Hence, to increase the data rate either the channel bandwidth or the **SNR** ratio have to be increased. However, the capacity increase of the **SNR** is due to using spectrally more efficient modulations, hence has to be seen as a trip point. The overall interaction between these factors is analyzed in [DR24]. Fig. 3.1 shows the theoretical link capacity for a communication link using **SiGe** transceivers over distance, center frequency  $f_0$ , and different modulation schemes. The

Figure 3.1: Theoretical link capacity for a realistic SiGe link for different modulation schemes over (a) 1 m, (b) 5 m and (c) 10 m, modified from [DR24] © IEEE 2024.

plots are calculated based on [DR24]. One immediate observation is a peak in the link capacity that shifts down in frequency with increasing distance. This results from the frequency-dependent **FSPL** and shrinking antenna aperture, causing the SNR to decrease while available bandwidth increases.

Another interesting result from this simulation is that lower-order modulation schemes help maximize the available link budget as SNR degrades. This is due to the lower necessary back-off for a **PA** and better peak-to-average power ratio (**PAPR**) for the lower order modulation schemes. However, the difference between **QAM-4** and **BPSK** is not as significant as between the higher-order modulation schemes. It also shows the lower spectral efficiency of **BPSK**, a trade-off for simplicity in the system design. Similar to this is that **QAM-256** has a lower peak link capacity than **QAM-64**. This is again due to the higher linearity requirements of the higher order modulation, which are disadvantageous as frequency and bandwidth increase.

The last observation is that for the system values assumed within the simulation, no  $100 \text{ Gbit s}^{-1}$  is possible for **BPSK**. This is, however, an artifact of the assumed relative bandwidth. The used value of 20 % relative bandwidth can be increased in practice [DR24].

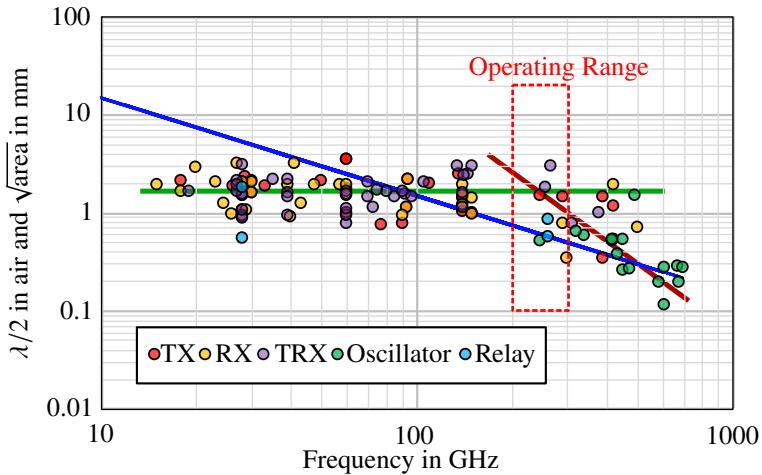

## 3.2 Physical Antenna Array Implementation

Concerning the physical construction of the phased array, we can investigate the survey reported in [WLM24]. Fig. 3.2 shows the reported physical size of the antenna elements within phased arrays in the sub-THz spectrum. The blue line represents  $\lambda/2$ . One can observe that the physical size of antenna elements stays somewhat constant over frequency, as shown by the green line. This causes a turning point at 100 GHz, where the elements are no longer below the half-wavelength. Another turning point is observable around 300 GHz, shown in the red curve, where antenna elements shrink again. The behavior below 300 GHz can be explained by two factors. Firstly, the available channel bandwidth increases with frequency, and hence, necessary aperture size increases, while the physical size decreases. Secondly, due to fabrication limits of well established technologies a gap in realizable physical sizes is present. Below 100 GHz or 3 mm free space wavelength **PCB** based structures are viable to create  $\lambda/2$  spacing and electrically small elements. Above this frequency structure sizes fall below the currently manufacturable dimensions of standard **PCB** processes and necessitate special processes and substrates. Simultaneously, the dimensions are to large for monolithic integration within thin-film processes or on-chip structures. Starting at around 300 GHz or 1 mm free space wavelength on-chip antennas can be economically integrated within the same **MMIC** to achieve  $\lambda/2$  spacing.

For the system, this indicates that an antenna element size below  $\lambda/2$  is a challenge and should not be aimed at. Especially considering the bandwidth target. The target realized gain should be below 10 dBi to stay within antenna size targets and allow broader beam steering.

## 3.3 MMIC Antenna Co-Design

One part of the system is achieving good performance on the **MMIC**. An equally crucial aspect is the antenna, especially the integration with the power amplifier. The antenna does not only need to match the bandwidth of the amplifier. It also needs to be placed within an array. For the phased array, antenna spacing and antenna count are critical. This leaves the question of the general approach to the antenna and interconnect to the **MMIC** and

Figure 3.2: Survey of phased array antennas element size and surface area versus frequency as presented in [WLM24].

general structure of the phased array. Based on previously published work, the following potential antenna concepts are possible:

1. On-chip Antenna [LZRR22]

2. Off-chip antenna on thick film substrate [AdGW<sup>+</sup>22]

3. Waveguide feed [HMK<sup>+</sup>24]

4. On-chip launcher with reflectarray [WLZ<sup>+</sup>18]

Evaluating the presented options and the state-of-the-art monolithically integrated on-chip antennas were ruled out. A significant limitation with monolithically integrated on-chip antennas is the lack of measurement opportunities of the underlying **MMIC**. There is no direct way of evaluating the RF performance of the **MMIC** and the antenna separately, leaving many aspects unclear. Manufacturing a separate chip to test the antenna and **MMIC** alone adds costs and does not solve the in-situ test issue.

A waveguide feed is a straightforward way of implementing systems at terahertz frequencies. However, waveguides are only useful in test and measurement scenarios as they lack adaptivity, are costly, and are bulky.

This leaves the decision for off-chip structures connected to the amplifier. Due to the lack of differential measurement equipment, single-ended circuits are preferred. However, employing single-ended connections removes the benefit of the differential amplifier and poses a significant challenge in the interconnect between **MMIC** and antenna. An alternative that is chosen is a differential wire-bond interface to connect the **MMIC** and antenna.

## 3.4 Harmonic Content in the Multiplier Chains

Generating the necessary **LO** signals at the targeted **RF** frequencies is still an active field of research. Systems generating the **RF** tone directly by the use of a fundamental oscillator and stabilized through a phase locked loop (**PLL**) circuit or injecting locking are rare and have issues with tuning range, output power, and stability [NH20]. Another disadvantage of integrated **LO** generation is the synchronization for phased array applications. Using a low frequency signal to synchronize **PLLs** together faces significant challenges for coherence.

Hence, many systems utilize frequency multiplier circuits, which ease these requirements significantly. Based from a strong lower frequency source harmonics are generated in a non-linear device. By tuning and filtering the desired multiple of the input frequency a strong and stable **LO** tone can be generated.

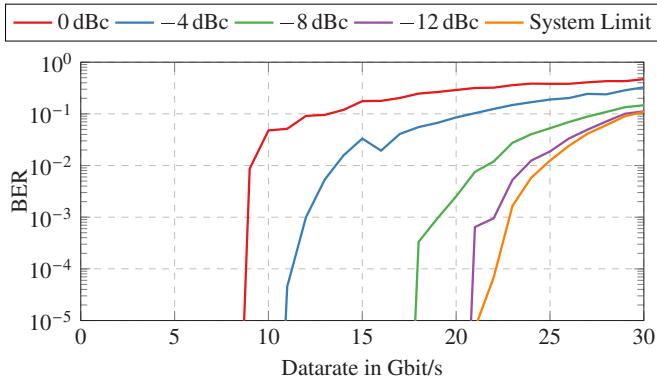

One issue emerging from the fundamental principle is harmonic suppression. Due to the strong non-linearity of the multiplier, all harmonics are generated with varying strength and will find their way to the output. While the system designed here works around this by choosing a low multiplication factor and a large harmonic spacing, not all parts of the measurement setup have this liberty. The receiving mixer in the measurement setup uses a multiplication of 24 times, causing harmonics to land within the bandwidth of the usable signal. This limits the maximum data rate measurable with this receiver.

Fig. 3.3 shows the result of simulations quantifying this effect. The simulation creates an **RF** waveform, including the next harmonics of the **LO** for the upconversion. The downconversion process assumes a mixer converting to an intermediate frequency (**IF**) with the **LO** spaced 30 GHz apart from the **RF**

Figure 3.3: Calculated theoretical **BER** limit due to **LO** harmonic content from the multiplier chain [5] © IEEE 2024.

signal. A software receiver then demodulates the **IF** signal and evaluates the **BER**. Due to the 30 GHz offset and the chosen demodulation algorithm, a system **BER** limit is present approaching a modulation bandwidth of 15 GHz, corresponding to a data rate of  $30 \text{ Gbit s}^{-1}$ , half the **IF** center frequency. The simulation shows that an average carrier offset of 12 dBc increases the **BER** over the system limit. Even less suppression leads to significant system limitations with the extreme case of 0 dBc limiting the maximum datarate to be lower than the **LO** tone spacing. This is also true for the receiving side, limiting the measurement setup used in this work as presented in [2].

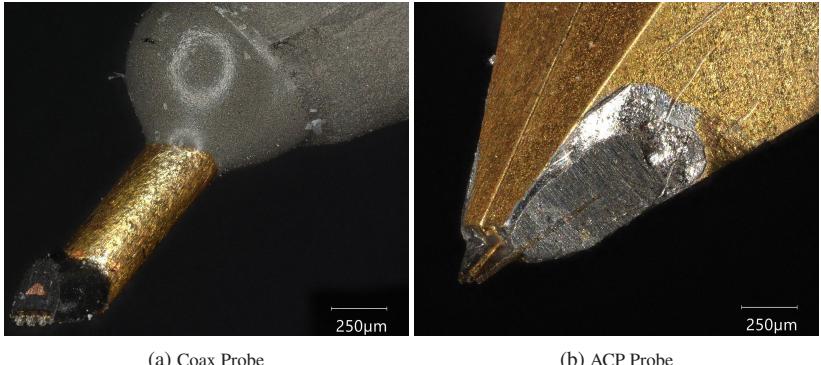

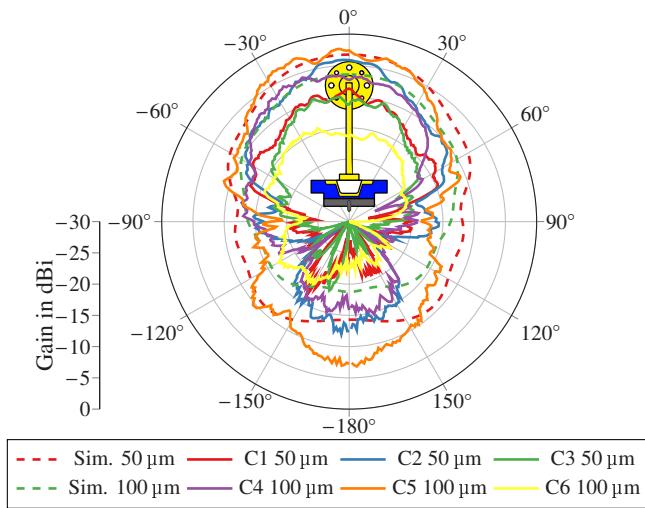

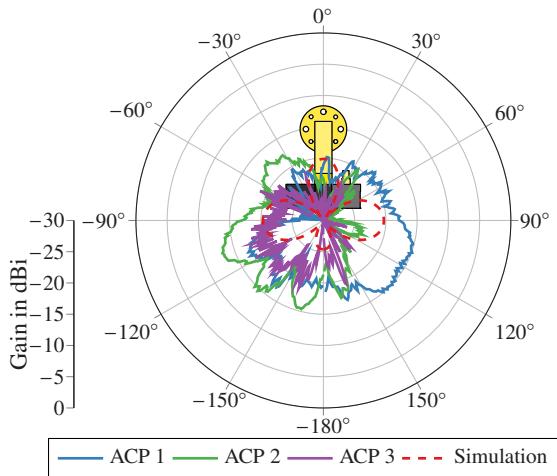

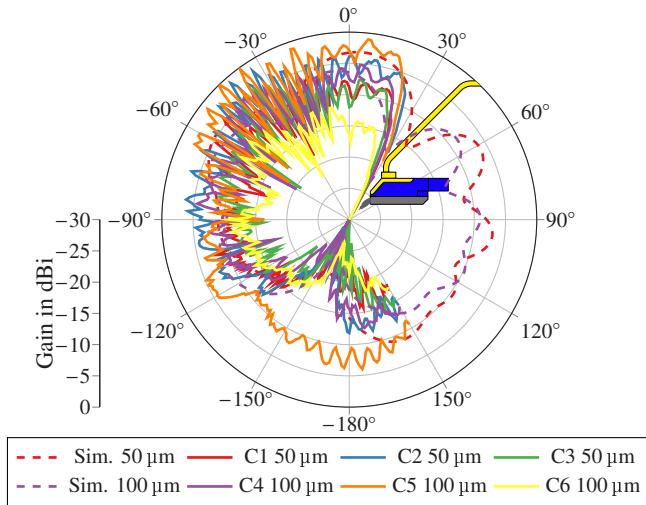

## 3.5 Measurement Uncertainty