# Resistive Switching Devices Based on Solution Processable Metal Oxides

Zur Erlangung des akademischen Grades eines

# Doktors der Ingenieurwissenschaften (Dr.-Ing.)

von der KIT-Fakultät für Elektrotechnik und Informationstechnik des Karlsruher Instituts für Technologie (KIT)

genehmigte

#### DISSERTATION

von

M.Sc. Hongrong Hu

geb. in Chongqing, China

Tag der mündlichen Prüfung: 30.07.2024

Hauptreferent: Prof. Dr. rer. nat. Jasmin Aghassi-Hagmann

Korreferent: Prof. Dr. rer. nat. Regina Dittmann

## **Publication List**

### **Journal Article**

- H. Hu, A. Scholz, C. Dolle, A. Zintler, A. Quintilla, Y. Liu, Y. Tang, B. Breitung, G. C. Marques, Y. M. Eggeler, and J. Aghassi-Hagmann, "Inkjet-printed tungsten oxide memristor displaying non-volatile memory and neuromorphic properties", *Advanced Functional Materials*, vol. 34, no. 20, pp. 2302290, 2024.

- **H. Hu**, A. Scholz, Y. Liu, Y. Tang, G. C. Marques, and J. Aghassi-Hagmann, "A fully inkjet-printed unipolar metal oxide memristor for nonvolatile memory in printed electronics", *IEEE Transactions on Electron Devices*, vol. 70, no. 6, pp. 3051-3056, 2023.

- L. Yang, H. Hu, A. Scholz, F. Feist, G. C. Marques, S. Kraus, N. M.Bojanowski, E. Blasco, C. Barner-Kowollik, J. Aghassi-Hagmann, and M. Wegener, "Laser printed microelectronics", *Nature Communications*, vol. 14, no. 1, pp. 1103, 2023.

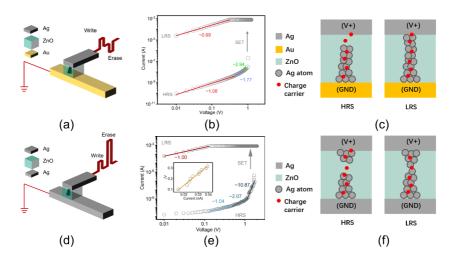

- H. Hu, A. Scholz, S. A. Singaraju, Y. Tang, G. C. Marques, and J. Aghassi-Hagmann, "Inkjet-printed bipolar resistive switching device based on ag/zno/au structure", *Applied Physics Letters*, vol. 119, no. 11, pp. 112103, 2021.

- X. Feng, S. A. Singaraju, H. Hu, G. C. Marques, T. Fu, P. Baumgartner, D. Secker, M. B. Tahoori, and J. Aghassi-Hagmann, "Low-frequency Noise

Characteristics of Inkjet-Printed Electrolytegated Thin-Film Transistors", *IEEE Electron Device Letters*, vol. 42, no. 6, pp. 843-846, 2021.

### **Under Preparation**

- H. Hu, W. Wang, A. Ahmadian, B. Breitung, M. Ibrahim, G. C. Marques, C. Kübel, and J. Aghassi-Hagmann, "Polyoxometalate (POM) Enables Low-power and Uniform Inkjet-printed Metal-oxide Memristor", 2024.

- Y. Liu, F. Fischer, H. Hu, H. Gliemann, C. Natzeck, C. Wöll, B. Breitung, J. Aghassi-Hagmann, "Inkjet Printed Metal-Organic Frameworks for Non-volatile Memory Application", 2024.

- Y. He, Y. Ting, H. Hu, T. Diemant, Y. Dai, J. Lin, G. C. Marques, H. Hahn,

Y. Ma, T. Brzezinski, P. M. Kowalski, J. Aghassi-Hagmann, B. Breitung,

"Emerging Sodium ion-modulated Non-Volatile Printed Memory based on

Multicomponent Prussian Blue Material", 2024.

## **Conference Contributions**

### **Oral Presentation**

- 2023 Material Research Society (MRS) Spring meeting, San Francisco, California, USA

- "2D/3D Printed Metal Oxide Transistor"

- 2022 Materials Systems Engineering (MSE) Day, Karlsruhe, Germany "Printed Electronic Devices and Circuits"

### **Poster**

- 2023 Material Research Society (MRS) Spring meeting, San Francisco, California, USA

- "Printed Memristors for Memory, Computing and Hardware Security"

- 2022 3D Matters Made to Orders Conference, Schöntal Monastery, Germany

- "Inkjet-printed Resistive Switching Devices Based on Metal Oxides"

# Kurzfassung

Die gedruckte Elektronik ist eine aufstrebende Technologie, die im Vergleich zur klassischen CMOS (komplementären Metall-Oxid-Halbleiter) Technologie noch in den Kinderschuhen steckt. Sie bietet jedoch einzigartige Vorteile wie Transparenz, Dehnbarkeit, Skalierbarkeit in der Fläche, kostengünstige Herstellung und mechanische Flexibilität. Diese Eigenschaften erweitern das Anwendungsspektrum der Elektronik auf großflächige, leichte, flexible, nachhaltige und allgegenwärtige Szenarien. Allerdings bleiben die Komplexität, Integrationsdichte und Intelligenz der modernsten gedruckten Elektronik nach wie vor rudimentär, was ihre Fähigkeit zur Durchführung komplexer Aufgaben einschränkt. Dieses Phänomen ist hauptsächlich auf den Mangel an gedruckten Speicher- und Rechenkomponenten zurückzuführen. Das bloße Nachbilden konventioneller CMOS-Speicher- und Rechensysteme mit zeitgenössischer gedruckten elektronischen Bauelemente hat sich als unpraktikabel erwiesen, da die Leistung der gedruckten Transistoren moderat ist und die Drucktechniken und ihre Auflösung bei der Realisierung von großflächigen integrierten Schaltungen begrenzt sind. In diesem Zusammenhang dienen neuartige Arten von elektronischen Bauelemente zusammen mit ihren zugehörigen Speicher- und Rechenparadigmen als entscheidende Ermöglicher für ein intelligentes, vollständig gedrucktes elektronisches System. Gleichzeitig müssen diese neuartigen Bauelemente die technischen Beschränkungen der gedruckten Elektronik berücksichtigen.

Memristoren, auch als resistive Schaltbauelemente bezeichnet, sind eine Klasse neuartiger zweipoliger elektronischer Bauelemente, deren interner Widerstand von der Historie der angelegten Spannung und des Stroms abhängt. Die veränderten internen Widerstandszustände können für eine bestimmte Zeit ohne Energieversorgung aufrechterhalten werden und sind daher als Widerstände mit

Gedächtniseffekten angesehen. Die resistiven Schalteigenschaften von Memristoren bieten enormes Potenzial für die Implementierung speicherbasierter Anwendungen, einschließlich, aber nicht beschränkt auf nichtflüchtigen Speicher, neuromorphes Rechnen und Hardwaresicherheit.

Bis heute sind die Fortschritte in der Memristor-Forschung hauptsächlich auf vakuumverarbeitete Metalloxide zurückzuführen. Memristoren, die aus flüssigprozessierbaren Metalloxiden hergestellt werden, gewinnen aufgrund ihres kostengünstigen Herstellungsprozesses und ihrer Leistung, die mit der ihrer vakuumbasierten Gegenstücke vergleichbar ist, zunehmend an Interesse. Die Forschung zur Anpassung der flüssigprozessierbaren Metalloxide für gedruckte Memristoren, die Untersuchung der zugrunde liegenden Schaltmechanismen und der Schlüsselparameter für die entsprechenden Schaltungsarchitekturen sind jedoch noch kaum erforscht. Unter diesen Umständen zielt diese Arbeit darauf ab, resistive Schaltbauelemente zu entwickeln und charakterisieren, die mit flüssigprozessierbaren Metalloxiden gedruckt werden, und ihre Schlüsseleigenschaften für vielfältige Anwendungen in der gedruckten Elektronik zu bewerten, einschließlich nichtflüchtiger Speicher, neuromorphes Rechnen und Hardwaresicherheit.

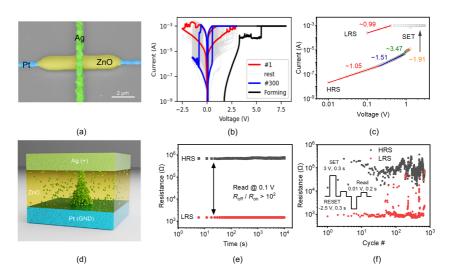

Für die nichtflüchtige Datenspeicherung wurden Metalloxid-basierte Memristoren durch Tintenstrahldruck entwickelt. Das digitale resistive Schaltverhalten der gedruckten Memristoren wurde vollständig elektrisch charakterisiert und zeigte hervorragende Eigenschaften, die für nichtflüchtige Speicher eingesetzt werden können, einschließlich niedriger Betriebsspannung (< 1 V), gute Haltbarkeit (über  $10^4\,\mathrm{s}$ ), großem Speicherfenster ( $R_\mathrm{off}/R_\mathrm{on}$ -Verhältnis über  $10^7$ ) und hohe Betriebszyklen (12672).

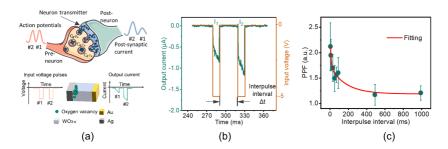

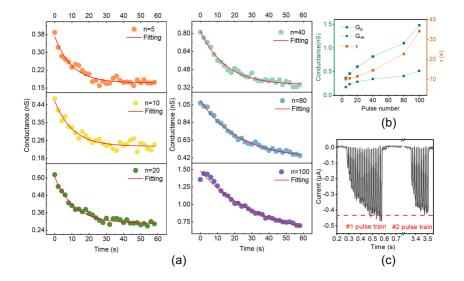

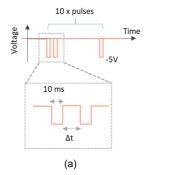

Um das Potenzial für neuromorphes Rechnen zu erforschen, wurden die flüchtigen und analogen resistiven Schalteigenschaften der mit Tintenstrahldruck gedruckten Memristoren untersucht. Die gedruckten Memristoren wurden als künstliche Synapsen eingesetzt und imitierten mehrere synaptische Funktionen. Diese umfassen die Paired-Pulse Facilitation (PPF), frequenzabhängige Integration und Filterung von Eingangssignalen, mehrere Formen der Kurzzeitplastizität einschließlich Fazilitation (10-177 ms), Augmentation (10 s) und Potenzierung

$(35\,\mathrm{s}).$  Außerdem wurde eine höhere Ordnung der Kurzzeitplastizität, d.h. Metaplastizität, ebenfalls mit dem gedruckten Memristor emuliert.

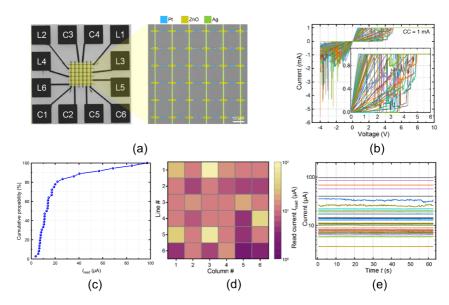

Eine andere digitale Drucktechnik, der direkte Laserdruck mit noch kleineren möglichen Merkmalgrößen (bis zu 500 nm anstatt 10 µm wie beim Tintenstrahldruck) sowie einem überlegenen Konzept für metallische Verbindungen, wurde zur Herstellung von Dioden, Memristoren und integrierten Arrays von Memristoren verwendet. Der Laserdruck basiert auf Mehrphotonenabsorption in den Tinten und wurde in dieser Arbeit erstmals als überlegenes additives Fertigungsverfahren für Mikroelektronik nachgewiesen. Ein metalloxid-basierter Memristor mit der kleinsten Gerätefläche von  $0.43\,\mu\text{m}^2$  unter allen gemeldeten gedruckten Memristoren wurde durch Laserdruck erreicht. Zudem wurde ein memristives Kreuzschienen-Schaltung bestehend aus  $6\times 6$  Memristoren vollständig lasergedruckt. Diese Schaltung wurde später verwendet, um die physikalisch unklonbarer Funktionen (PUFs) zu implementieren, die ein hardwarebasiertes Sicherheitsprimitive ist. Der lasergedruckte memristive PUF erzeugte 36 binäre Zufallszahlen, die über 300 Iterationen ausgezeichnete Stabilität zeigten und keinen Bitfehler aufwiesen (Bitfehler = 0%).

## **Abstract**

Printed electronics is an emerging technology still in its infancy when compared to classical CMOS (complementary metal-oxide semiconductors) technology. However, it offers unique advantages such as transparency, stretchability, scalability in area, low-cost manufacturing, and mechanical flexibility. These features broaden the application spectrum of electronics to large-area, lightweight, flexible-shape, sustainable, and ubiquitous scenarios. However, the complexity, integration density, and intelligence of state-of-the-art printed electronics still remain rudimentary, limiting their capacity for performing complex tasks. This phenomenon is mainly attributed to the scarcity of printed information storage and computing components. Simply replicating conventional CMOS memory and computing systems by employing contemporary printed electronics has been proven impracticable due to the moderate performance of the printed transistors and the constraint of printing techniques and their resolution in the realization of large-scale integrated circuits. In this context, novel types of electronic devices, along with their associated memory and computing paradigms, serve as pivotal enablers for an intelligent, fully-printed electronic system. At the same time, these novel devices must accommodate the technical constraints of printed electronics. Memristors, also referred to as resistive switching devices, are a class of novel two-terminal electronic components, of which the internal resistance depends on the history of the applied voltage and current. The changed internal resistive states can be maintained for a particular time without an energy supply and, thus, are regarded as resistors with memory effects. The resistive switching characteristics of memristors hold enormous potential to be exploited in implementing memory-based applications, including but not limited to non-volatile memory, neuromorphic computing, and hardware security.

To date, the remarkable advancements in memristor research are mainly attributed to vacuum-processed metal oxides. Memristors derived from solution-processed metal oxides are gaining more and more interest recently owing to their cost-effective fabrication process and performance that is on par with their vacuum-based counterparts. However, research on tailoring the solution-processed metal oxide for printed memristors, the investigation of the underlying switching mechanisms, and the key performance parameters for working in corresponding circuit architectures are still scarcely explored. Under this circumstance, this thesis aims to develop and characterize resistive switching devices printed with solution-processable metal oxides and to assess their key performance metrics for manifold applications in printed electronics, including non-volatile memory, neuromorphic computing, and hardware security.

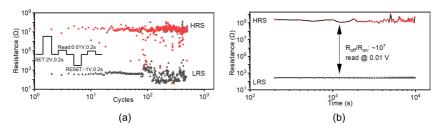

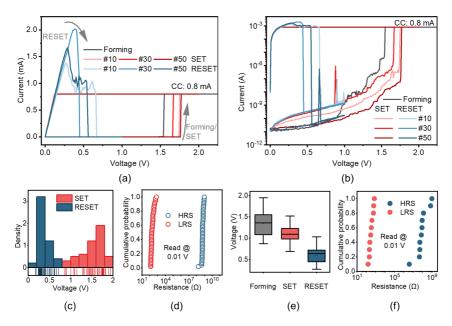

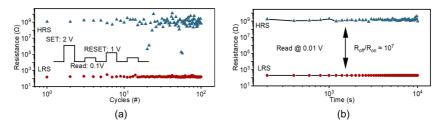

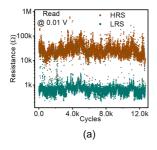

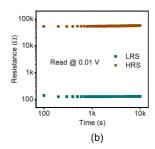

For non-volatile data storage, metal-oxide-based memristors were developed by inkjet printing. The digital resistive switching behavior of printed memristors was fully electrically evaluated, exhibiting excellent figures of merit for non-volatile memory, including low-operation voltage (< 1 V), good retention performance (over  $10^4$  s), large memory window ( $R_{\rm off}/R_{\rm on}$  ratio over  $10^7$ ), and the highest endurance cycles amongst reported printed memristor (12672).

To explore the potential for neuromorphic computing, the inkjet-printed memristors' volatile and analog resistive switching properties were investigated. The printed memristors were deployed as artificial synapses, remarkably mimicking multiple synaptic functions. These involve paired-pulse facilitation (PPF), frequency-dependent input signal integration and filtering, multiple forms of short-plasticity including facilitation (10-177 ms), augmentation (10 s), and potentiation (35 s). Besides, a higher order of short-term plasticity, i.e., metaplasticity, was also emulated with the printed memristor.

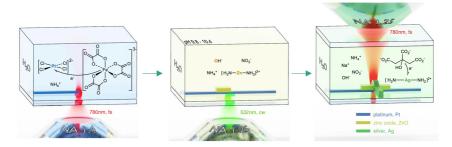

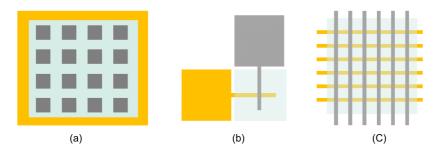

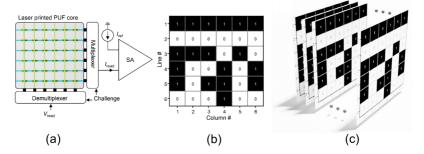

Another digital printing technique, direct laser printing with even lower possible feature sizes (down to  $500\,\mathrm{nm}$  instead of  $10\,\mathrm{\mu m}$  as in the case of inkjet printing) as well as with a superior concept for metallic interconnects was used to fabricate diodes, memristors and integrated arrays of memristors. Laser printing is based on multi-photon absorption in the inks and was proven as a superior additive manufacturing method for microelectronics for the first time in this thesis. A metal-oxide-based memristor with the smallest device area of  $0.43\,\mathrm{\mu m}^2$  among

all reported printed memristors was achieved with laser printing. Moreover, a memristive crossbar circuit consisting of  $6\times 6$  memristors was fully laser-printed. This circuit was later used to implement the physical unclonable function (PUF), which is a hardware-based security primitive. The laser-printed memristive PUF generated 36 binary random numbers, which possess excellent stability over 300 iterations, showing no bit error (bit error = 0%).

# Acknowledgements

First and foremost, I would like to express my deepest gratitude to my main supervisor, Prof. Jasmin Aghassi-Hagmann, for providing me with the opportunity to conduct research on printed electronics, which sparked my interest and enthusiasm for a career in research. Prof. Aghassi-Hagmann has been a great mentor, guiding me through both my master's thesis and dissertation. She is always generous in teaching me all scientific skills and consistently helping me improve in thinking, writing, presenting, and communicating. The knowledge and guidance I received from Prof. Aghassi-Hagmann have greatly contributed to my success today and will continue to benefit my future research endeavors.

I am also grateful to Prof. Regina Dittmann for agreeing to be the co-examiner of my thesis. The scientific discussions with Prof. Dittmann in Jülich and San Fransisco were very inspiring, and her great work in memristive devices has been a constant reference for me.

I would like to acknowledge my Ph.D. committee members, Prof. Jürgen Becker, Prof. Ivan Peric, and Prof. Gerardo Hernandez Sosa, for their valuable suggestions and advice on my work.

Special thanks go to Dr. Alexander Scholz and Dr. Gabriel Cadilha Marques. Alex always supported me in my scientific thinking and writing and helped me during challenging times at work. Gabriel is a great group leader who provided ample guidance and assistance with my research work and created a joyful working atmosphere. I am deeply grateful for his time and efforts in improving my dissertation.

I would also like to sincerely thank my colleagues at the Institute of Nanotechnology, KIT, for their support and suggestions during my work: Dr. Ben Breitung, Dr. Xiaowei Feng, Dr. Surya Singaraju, Dr. Yushu Tang, Yan Liu, Franz Fischer,

Palak Gupta, Sophie Sauva, Haoran Duan, Merve Nur Ekmekci, Shawon Alam, and George Mathew. A special thanks to Secretary Siri Weiße for her help with administrative matters.

I am grateful to Prof. Martin Wegener and his group, particularly his former postdoctoral researcher, Dr. Liang Yang, for the excellent collaboration on laser-printed electronics. Additionally, I appreciate the contributions from Prof. Yolita Eggeler and her group members, Dr. Aina Quintilla, Dr. Christian Dolle, and Dr. Alexander Zintler, for their outstanding work in material characterization.

I would like to acknowledge the Carl Zeiss Foundation and Germany's Excellent Strategy: Cluster of Excellence "3D Matter Made to Order" for their financial support of my work.

Last, I would like to thank my family for the unconditional love and support they have given me: my parents, Ruiyou Hu and Xingying Zhong, and my sisters, Hongmei, Hongling, and Hongjuan. My deepest love goes to my wife, Wenjing.

# **Contents**

| Pι | ıblic | ation List                                              |

|----|-------|---------------------------------------------------------|

| Co | onfei | rence Contributions iii                                 |

| Κι | ırzfa | ssung v                                                 |

| ΑI | ostra | ct ix                                                   |

| A  | kno   | wledgements xiii                                        |

| 1  | Intr  | oduction                                                |

|    | 1.1   | Overview of Printed Electronics                         |

|    | 1.2   | Motivation                                              |

|    | 1.3   | Structure of the Thesis                                 |

| 2  | Bac   | ckground                                                |

|    | 2.1   | Technological Evolution of Information Storage Medium 9 |

|    | 2.2   | Charge-based Memory                                     |

|    | 2.3   | Fundamentals of Memristors                              |

|    |       | 2.3.1 Evolution of Memristive Devices                   |

|    |       | 2.3.2 Basic Working Concepts of Memristive Devices 16   |

|    | 2.4   | Categories of Working Mechanisms                        |

|    |       | 2.4.1 Filamentary                                       |

|    |       | 2.4.2 Non-filamentary                                   |

|    | 2.5   | Printing Technologies                                   |

|    |       | 2.5.1 Inkjet Printing                                   |

|    |       | 2.5.2 Laser Printing 37                                 |

| 3 | Me  | thods                                                          | 39 |

|---|-----|----------------------------------------------------------------|----|

|   | 3.1 | Fabrication                                                    | 39 |

|   |     | 3.1.1 Inkjet Printing                                          | 39 |

|   |     | 3.1.2 Laser Printing                                           | 41 |

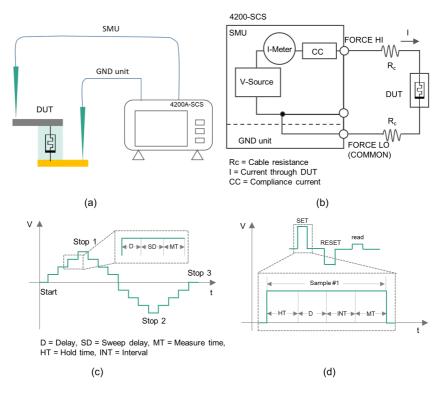

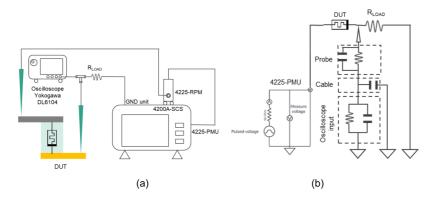

|   | 3.2 | Electrical Characterization                                    | 42 |

|   |     | 3.2.1 Quasi-static Measurements                                | 42 |

|   |     | 3.2.2 Dynamic Pulsed Measurements                              |    |

| 4 | Pri | nted Memristors for Non-volatile Memory                        | 47 |

|   | 4.1 | Introduction to Printed Non-volatile Memory                    | 47 |

|   | 4.2 | Inkjet-printed Memristors Based on Metal Oxide Precursor Inks  | 51 |

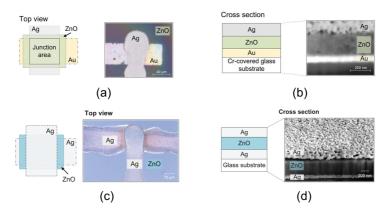

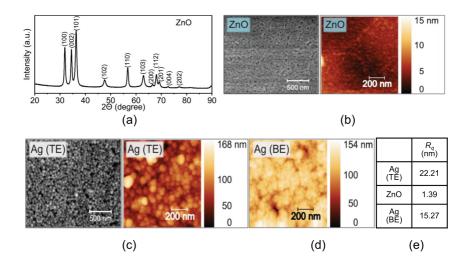

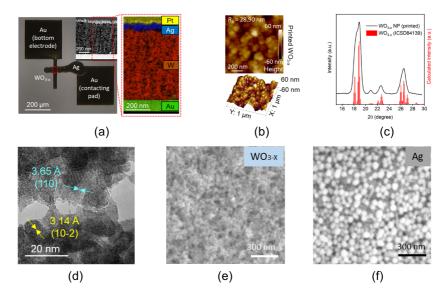

|   |     | 4.2.1 Device Structure                                         | 52 |

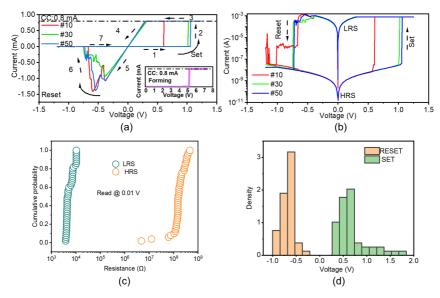

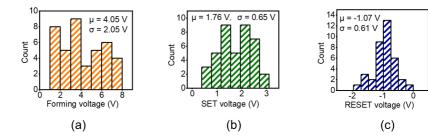

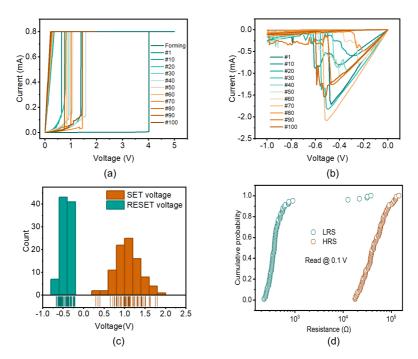

|   |     | 4.2.2 Device Performance                                       | 54 |

|   |     | 4.2.3 Mechanism Analysis                                       | 62 |

|   | 4.3 | Inkjet-printed Memristors Based on Metal Oxide                 |    |

|   |     | Nanoparticle Inks                                              | 67 |

|   |     | 4.3.1 Device Structure                                         | 67 |

|   |     | 4.3.2 Device Performance                                       | 68 |

|   | 4.4 | Conclusion                                                     | 72 |

| 5 | Pri | nted Memristors for Neuromorphic Computing                     | 77 |

|   | 5.1 | Introduction to Neuromorphic Computing in Printed Electronics  | 77 |

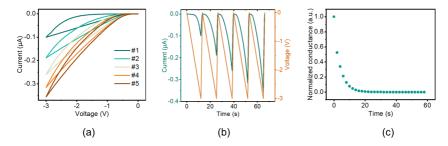

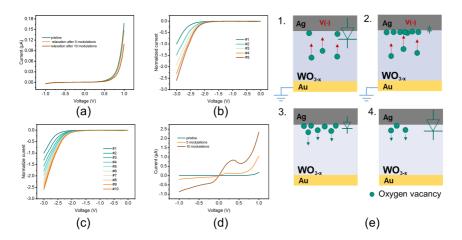

|   | 5.2 | Analog Resistive Switching Devices and Their Characteristics   | 80 |

|   | 5.3 | Analysis of Working Mechanism                                  |    |

|   | 5.4 | Emulation of Synaptic Functions                                | 85 |

|   |     | 5.4.1 Artificial Memristive Synapse: Paired-pulse Facilitation | 85 |

|   |     | 5.4.2 Artificial Memristive Synapse: Short-term Plasticity     |    |

|   |     | with Enhanced Relaxation Time for Memory Formation             | 87 |

|   |     | 5.4.3 Artificial Memristive Synapse:                           |    |

|   |     | Frequency-dependent Input Signal Filtering and Integration .   |    |

|   | 5.5 | Conclusions                                                    | 93 |

| 6 |     | nted memristor for Hardware Security                           |    |

|   |     | Introduction of Hardware Security Based on Memristors          |    |

|   | 6.2 | Device Characteristics of Laser-printed Memristor              | 97 |

|     | 6.3 Laser-printed Memristive Crossbar as Physical Unclonable |                                      |  |

|-----|--------------------------------------------------------------|--------------------------------------|--|

|     |                                                              | Function (PUF)                       |  |

|     | 6.4                                                          | Conclusions                          |  |

| 7   | Sur                                                          | mmary and Outlook                    |  |

|     | 7.1                                                          | Summary                              |  |

|     | 7.2                                                          | Outlook                              |  |

| Α   | Apı                                                          | pendix                               |  |

|     | A.1                                                          | Ink Preparation for Inkjet Printing  |  |

|     | A.2                                                          | Preparation of Non-printed Electrode |  |

|     | A.3                                                          | Ink Preparation for Laser Printing   |  |

|     | A.4                                                          | Material Characterization Methods    |  |

|     | A.5                                                          | PUF Calculation                      |  |

| Lis | st of                                                        | Figures                              |  |

| Lis | st of                                                        | Tables                               |  |

| Αc  | ron                                                          | yms and symbols                      |  |

| Cι  | ırric                                                        | ulum Vitae                           |  |

| Bil | bliod                                                        | graphy                               |  |

### 1 Introduction

### 1.1 Overview of Printed Electronics

Printing, an ancient technology, transfers patterns such as text or graphics from ink onto a carrier like paper or cloth. Electronics is a discipline where components that can manipulate electrons or other electrically charged particles are designed or fabricated. Printed electronics (PE) denotes the emerging technology that revolutionizes the fabrication of electronic devices and circuits with printing techniques in an additive, low-cost, and large-scale manner [1].

Nowadays, complementary metal oxide semiconductor (CMOS), as well as Sibased technology, has fostered the development of modern electronic engineering, which is fundamental to the boom in information technology. CMOS-based electronics are regarded as a technology of high performance, reliability, and high integration density. Printed electronics have never been targeted to replace conventional Si-based technology since its advent due to the inherent limitation of this technology. Compared to Si-based electronics, PE has a larger feature size (above micrometers), low performance, and low reliability. However, the research on PE has been booming in the past decades [2, 3, 4] because it is regarded as a complementary technology to CMOS and enables emerging applications where CMOS has limitations, such as disposable electronics, flexible electronics, and large-area applications [4, 5].

The fabrication of PE is an additive manufacturing process where devices are fabricated using a bottom-up drop-on-demand approach. The general process of printing an electronic component is to deposit inks such that the patterns of different functional material types (e.g., conductors, isolators, or semiconductors) are formed at the expected location on the substrate, followed by the formation of a

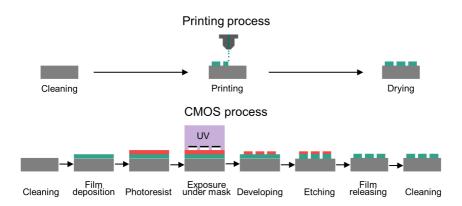

Figure 1.1: Schematics of comparison between printed electronics and conventional CMOS process.

thin film after an annealing step. This has significantly shortened the manufacturing process compared to conventional CMOS, which generally requires material deposition in vacuum, photolithography, and etching. Modern chip manufacturing requires over 300 sequenced processing steps [1, 6]. Figure 1.1 compares the fabrication processes of PE with conventional CMOS technology. Moreover, CMOS manufacturing is a subtractive process in which materials are deposited entirely on the substrate, creating areas where the material is unnecessarily deposited and needs to be removed in a subsequent etching step. This results in a tremendous amount of material waste. On the contrary, in PE, the materials are deposited on demand onto the substrate, significantly reducing the waste [1, 6].

In addition, although CMOS is advanced in achieving ultra-large-scale integrated circuits, the substrate is restricted to the rigid Si wafer of a limited size. On the contrary, PE is independent of the properties of the substrate, regardless of physical size or mechanical properties. The substrate can be as large as meters of rigid or flexible and stretchable materials, spanning from glass, over plastic, to even papers [1, 2, 6, 8]. Thanks to the aforementioned advantages, including cost-effective fabrication and independence of substrate property, PE emerges in future applications where cost and flexibility are more important than performance. These promising application scenarios include large-scale displays, large-scale sensing

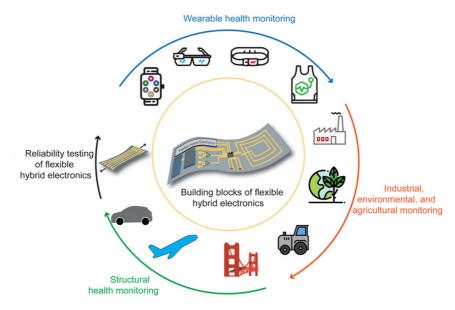

Figure 1.2: Spectrum of application with PE. Flexible hybrid electronics as an example to show possible application scenarios spanning from wearable health monitoring over industrial, environmental, and agricultural monitoring to structural health monitoring. © 2019 WILEY-VCH Verlag GmbH & CO. KGaA, Weinheim. Reproduced with permission from [7].

for monitoring (e.g., monitoring in transport tools and infrastructure, or industrial, environmental, and agricultural-related scenes), smart packaging in logistics, the Internet of Things (IoT), and wearable electronics for health monitoring, to name a few [4, 7, 9]. Figure 1.2 shows part of PE's promising applications.

### 1.2 Motivation

As introduced earlier, PE will play a complementary role to CMOS and will show advantages in specific application scenarios, including but not limited to wearable electronics, IoT, smart packages, large-scale displays and sensing, and so on. However, the main achievements in PE are still limited to discrete electronic

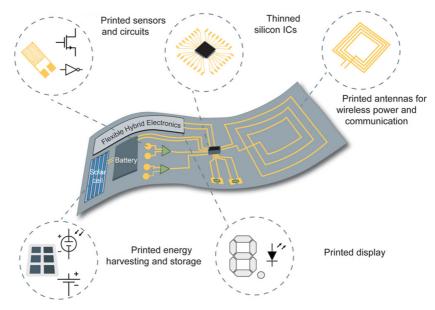

components, including field-effect transistor (FET) [10], various sensors [9], solar cells [11], diodes [12], light-emitting diodes (LED) [13], capacitors [14], and antennas [15]. Simple circuit based on printed transistors are also reported [3], such as inverters [16], ring oscillators [17], logic gates [18], decoders [19], latches [20], and so on. In a complex printed electronics system where data processing is required, a thinned Si-based microcontroller is needed for information storage and processing [5, 7], as illustrated in Figure 1.3. This hybrid system leverages the high performance of Si-based ICs while at the same time exploiting the low cost, conformability, and scalability of printed components [5, 7]. The incorporation of Si-based ICs largely enhances the intelligence of printed electronics systems, albeit the thinned Si microcontroller largely elevates the cost, which significantly weakens the advantage of printed electronics in low-cost manufacturing. Printed microcontrollers are highly sought after in this context, but their research confronts remarkable challenges [5, 21]. Two major challenges are the lack of appropriate printed information storage and computing components.

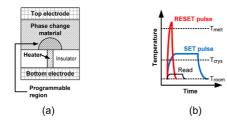

In the case of information storage, the performance parameters and manufacturing complexity of the existing memory technologies may not align with PE. For instance, transistor-based static random access memory (SRAM) and dynamic random access memory (DRAM) are two mainstream memory technologies in conventional Si-based ICs, but they are volatile memories requiring a consistent power supply to maintain the stored data [22], which imposes high requirements on the power-supply system and concurrently increases the complexity of related circuits. This presents considerable technical challenges in realizing complex circuits in printed electronics. Although printed transistor-derivative memory devices, including Flash memory and ferroelectric FETs (FeFETs), are non-volatile, but high operation voltage (over tens of volts) [23, 24, 25, 26] makes powering the memory through batteries not feasible. Other novel non-volatile memory technologies, such as magnetic random access memory (MRAM) and phase change memory (PCM) [22], have stringent material property requirements and thus present a challenge to be printed. In this context, a novel memory device that accommodates the constraints of printed electronics is highly demanded.

In the case of computing, the realization of the conventional von Neumann computing architecture with printed electronics presents significant challenges. First,

Figure 1.3: Schematics of a flexible embedded PE system. Display, antennas, sensors, and energy supply units (such as energy harvesting devices and batteries) are printed, while the information processing and storage units still rely on thinned silicon ICs. © 2019 WILEY-VCH Verlag GmbH & CO. KGaA, Weinheim. Reproduced with permission from [7].

the features of von Neumann architecture [27], including separation between computation and memory, binary data-based programming and communication, and clock-driven timing, require a large number of building blocks and sophisticated peripheral circuits. This imposes enormous challenges to current printing technologies due to low resolution and high variability in fabrication. Second, printed transistors, as the cornerstone of implementing computation, are still confronting low yield rates and high variability, which hinder the development of complex circuits from the technical perspective [10]. In addition, state-of-the-art printed transistors are still demanding significant improvements. The trade-off between high threshold voltage (up to tens of volts) and low switching speed (down to several hertz) is always met due to the lack of gating materials that confine well with the channel [10]. The moderate performance of the printed transistors

will exacerbate the inherent bottleneck of the von Neumann computing architecture, which eventually renders the printed computing units inadequate to perform signal processing tasks within the scope of printed electronics applications. Alternatively, neuromorphic computing, a new computing paradigm inspired by the human brain, aims to process data directly in the memory in a rather parallel manner [27]. Moreover, this event-driven computing paradigm performs computation only when data is available [27]. These features of neuromorphic computing will largely simplify the circuitry, thus mitigating the technical limitations of current PE. As shown in recent research, neuromorphic computing is an energy-efficient computing paradigm that is superior in dealing with specific tasks such as classification of unordered data, parallel signal processing, and self-learning [28, 29, 30]. Therefore, neuromorphic computing emerges as a promising enabler for intelligent printed electronics systems as the computing solution [31, 32, 33]. Implementing neuromorphic computing relies on memory devices, necessitating the advancement of novel memory devices tailored for printed electronics.

Memristors, also referred to as resistive switching devices, are novel two-terminal electronic devices, of which the internal resistance depends on the history of applied voltage and current [34, 35]. The changed internal resistive states can be maintained for a particular time without an energy supply and thus are regarded as resistors with memory effects. Compared to other memory devices, memristors show unparalleled advantages, such as: (a) Simple device structure, which promises to reduce fabrication complexity. (b) High device performance, including low operation voltage (down to hundreds mV), fast switching speed (down to ps), excellent retention and endurance properties. (c) Good mechanical flexibility. All these advantages render this class of two-terminal electronic devices promising in advancing the development of fully printed electronic systems. The current advancements in memristor research are mainly attributed to vacuum-processed metal oxides [36, 37, 38, 39, 40]. Memristors derived from solution-processed metal oxides [41, 42] are incrementally garnering interest, owing to cost-effective fabrication process and performance that is on par with their vacuum-based counterparts. However, the research on tailoring solution-processed metal oxide to be printable and investigating the performance of printed memristors is still in its infancy.

The primary objective of this thesis is to develop printed memristors derived from solution-processable metal oxides and systematically characterize and evaluate their performance to be used for non-volatile memory and neuromorphic computing within the domain of printed electronics. In addition to inkjet printing, one of the predominant printing techniques utilized in printed electronics, multi-material laser printing based on multi-photon absorption, will be exploited to fabricate sub-micrometer printed memristors for the first time. The successful implementation of hardware security with a laser-printed memristive crossbar circuit provides a proof-of-concept of employing printed memristors based on solution-processed metal oxides in circuit-level applications.

### 1.3 Structure of the Thesis

The remaining parts of this thesis are structured as follows:

- Chapter 2 introduces the fundamental concepts of current memory technologies, including resistive switching devices. Next, the basic concepts and working mechanisms of resistive switching devices corresponding to the device categories are systematically introduced. At the end of this chapter, the basic concepts of two printing technologies used in this thesis, inkjet printing and laser printing, are discussed.

- Chapter 3 describes the fabrication process of printed memristors, including

inkjet printing and laser printing. The ink formulation and annealing steps

are described in more detail. Moreover, the setup and test protocol for the

electrical measurements are shown.

- Chapter 4 presents the results of inkjet-printed memristors for non-volatile memory. First, a brief review of current research progress on printed non-volatile memory is given. Next, three types of inkjet-printed memristors based on solution-processable metal oxide, i.e., Ag/ZnO/Au, Ag/ZnO/Ag, and Au/WO<sub>3-x</sub>/Au are presented, including the properties of the materials, the resistive switching characteristics, the variability analysis in terms of

device-to-device and cycle-to-cycle, as well as the critical device performance metrics for non-volatile memory. Finally, the underlying mechanisms of resistive switching are discussed.

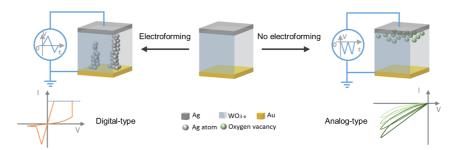

- Chapter 5 presents the results of exploiting the analog resistive switching characteristics of inkjet-printed Au/WO<sub>3-X</sub>/Au in neuromorphic computing. First, a brief introduction to neuromorphic computing in printed electronics is given. The basic concepts in the field of neuromorphic computing are discussed. Next, volatile and analog resistive switching characteristics and underlying mechanisms are presented. Finally, the results of emulating synaptic behavior with printed Ag/WO<sub>3-x</sub>/Au memristor are shown.

- Chapter 6 exploits the results of laser-printed Ag/ZnO/Pt memristors for the hardware security application. First, a brief introduction to hardware security based on memristors is given. Next, the device properties of laserprinted memristors are presented. Finally, the implementation of a physical unclonable function (PUF) with a fully laser-printed memristive crossbar is demonstrated.

- Chapter 7 summarizes the thesis and gives an outlook on future research topics.

## 2 Background

# 2.1 Technological Evolution of Information Storage Medium

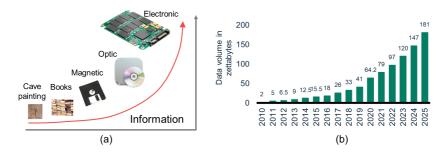

The information contains knowledge or data that can be processed, stored, or transmitted [43]. The representation of information relies on its retrieval and storage in a reliable medium. For instance, biological information is encoded in DNA, knowledge is written in books, an event can be recorded on a magnetic tape, and so forth. In regards to representing information, the storage mediums in human society evolved from paintings and carvings to scribing and digitization [44], as shown in Figure 2.1(a). Digitalization is the most significant revolution in the development of storage technology and enables the storage of sounds, images, and words in a binary form. Thereafter, human society entered the information age, and the generated data expanded drastically within the last decade. According to a forecast from the International Data Corporation (IDC) [45], the global generated data volume will leap to 181 zettabytes (1 zettabyte =  $10^{21}$  bytes) in 2025 (Figure 2.1(b)). To store such a huge amount of data, modern memory technologies are employed. In general, memory technologies are categorized into three groups according to the underlying mechanism, e.g., magnetic memories (such as magnetic tapes and hard discs), optical memories (such as CD, DVD, and Blu-ray), as well as electronic memories (such as SRAM, DRAM, EPROM, EEPROM, Flash, etc.). However, the focus of this thesis will be on electronic memories.

In recent years [22, 46], memory devices have attracted huge attention from both industry and academia for computing purposes. The popularity stems from the

Figure 2.1: (a) Historical evolution of information storage medium. (b) Growth of the data volume generated in human society. Source: IDC, & Statistica.

bottleneck inherited from the conventional von Neumann Computing paradigm, mainly due to the memory wall [22, 47, 48]. Advanced central processing units (CPUs) operate within the GHz regime. However, the performance of the current computing system is severely limited by data transport between the memory unit and the CPU [4]. Under these circumstances, researchers seek new paradigms that allow faster and more energy-efficient computing. Two mainstream strategies are executing computation in memory (In-memory computing) and mimicking the brain (neuromorphic computing). These two new computing paradigms rely strongly on memory technologies and foster research in electronic memory devices.

Conventional electronic memory devices store information through the presence or absence of charges, as in DRAM, SRAM, and Flash memory [49]. Charge-based memories are mature technologies that dominate the memory unit in various applications. In addition, there is an emerging class of memory devices that store information through different resistance states, thus termed resistive memory. Resistive memories are mainly classified into two groups following the working mechanisms. The first type changes its resistance by altering the atomic arrangement within the active layer, while the second type relies on the change of the electron transport properties [22]. The working mechanism of the resistive memories will be systematically introduced in Section 2.4. In the following, a general introduction to charge-based memory technologies will be given.

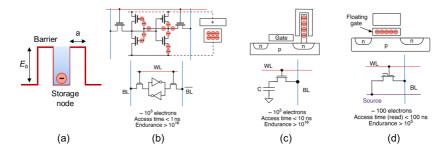

Figure 2.2: Basic concept and schematics of charge-based memory technologies. (a) Schematic of an electron that is trapped in a storage node, which is defined by the height and width of the energy barrier. (b) A SRAM cell consists of 6 CMOS transistors, which are configured as a pair of back-to-back inverters. The stored charge is confined between the FET channels and gate insulators. (c) A DRAM cell in a structure of 1-transistor-1-capacitor. The stored charge is blocked between the channels of the transistor and the dielectric layer of the capacitor. (d) A Flash memory cell incorporates a floating gate in a FET as the storage node, where the charge is stored. (b), (c), and (d) with © 2020 Springer Nature Limited. Reproduced with permission from [7].

## 2.2 Charge-based Memory

Charge-based memory technologies represent state-of-the-art memory in modern information and communication technologies. The essential idea of storing information in charge-based memory devices is to maintain the electrons within the storage node. In other words, the presence or absence of electrons in the storage node represents the states 0 and 1, respectively. In a storage node, energy barriers are exploited to preserve electrons, as demonstrated in Figure 2.2(a). The barrier height  $(E_b)$  and width (a) determine the retention time of memory cells [49]. Three different electronic devices are used to maintain electrons in charge-based memory cells. According to storage mechanisms, they are categorized into SRAM, DRAM, and Flash memory.

The common configuration of an SRAM cell consists of 6 transistors (Figure 2.2(b)), of which two transistors serve as selectors and two pairs of CMOS inverters are connected back to back. The output potential of one inverter is connected to the input of the other. Therefore, a feedback loop is formed to freeze the cell in a logic state [22, 49]. In this configuration, electrons are viewed

as being confined within the barriers formed by the field-effect transistor (FET) channel and gate insulator. The SRAM cell is known to be the fastest charge-based memory device with access times lower than 1 ns. Due to the low barrier height between the channel and the gate insulator of FET (0.5 eV), electrons can tunnel through the barrier; thus, the SRAM cell needs to be always connected to the power supply to replenish the electrons constantly within the storage node [22]. A DRAM cell consists of a capacitor (storage node) and a FET (selector) in series (Figure 2.2(c)). The electrons are maintained between the capacitor and the FET. The barrier height at the FET side is lower and depends on the band-gap of the channel material (ca. 1.1 eV in silicon), which determines the retention time of a DRAM cell and is typically in the ms range [49]. It is worth mentioning that the DRAM cells require periodic refresh operations. A Flash memory cell is a special FET type that involves a floating gate sandwiched between the gate insulator (Figure 2.2(d)). During the write operation, the electrons from the channel are injected into the floating gate by tunneling. The floating gate serves as the storage node where the electrons are trapped by the high energy barrier of the gate insulator. The Flash memory cell is non-volatile since the barrier height (ca. 3.1 eV) of the storage node is sufficient to guarantee long-term retention (ca. 10 years) [49]. Due to the barrier height, the access time of the Flash memory cell is about hundreds of μs, which is the longest among the charge-based memory technologies [49].

### 2.3 Fundamentals of Memristors

#### 2.3.1 Evolution of Memristive Devices

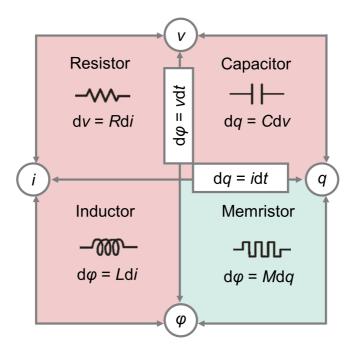

In 2008 [50], the Williams group at Hewlett-Packard Labs announced that "The missing memristor found". The term "memristor" was first proposed by Leon Chua in 1971 [51] that there should be a fourth fundamental element in addition to the three fundamental passive circuit elements, e.g., the resistor, the capacitor, and the inductor. Chua postulated the existence of the fourth fundamental element based on a discussion of symmetrical mathematical relations connecting pairs of

Figure 2.3: Theoretical prediction of the existence of memristor based on a discussion of symmetrical mathematical relations, each of which links a pair of the four fundamental circuit variables. Four fundamental circuit variables are: current i, voltage v, charge q, and magnetic flux  $\varphi$ . Existed and predicted passive fundamental circuits elements and related characteristic properties: resistor and resistance (R), capacitor and capacitance (C), inductor and inductance (L), and memristor and memristance (M).

the four fundamental circuit variables: electric current i, voltage v, charge q, and magnetic flux  $\varphi$  (Figure 2.3). Taking two of these variables randomly to build up a mathematical relation, there should be six different combinations. It is known: (a) charge and flux are time integral respectively of current and voltage (horizontal and vertical formula in Figure 2.3), and (b) three passive electrical elements related physical quantities can link two variables (I, II, and III quadrants in Figure 2.3). One mathematical relation is still missing at the bottom right corner, which can link the magnetic flux  $(\varphi)$  and the charge (q). Therefore, Chua supposed that,

theoretically, there is a missing element that can functionally link charge and flux. He named this missing element memristor (a contraction of memory resistor), and its characteristic property memristance "M" is derived from the differential equation:

$$M = \frac{\mathrm{d}\varphi}{\mathrm{d}q}.\tag{2.1}$$

If M is a constant, the memristor behaves more like a resistor. But if M itself is a function of q, this equation will indicate nonlinear characteristics of the memristor and thus is more interesting. In 1976 [52], Chua and Kang generalized the concept of the memristor to a much broader class of nonlinear dynamical systems that is referred to as the memristive system. According to the broader definition, a memristive system can be defined as current- or voltage-controlled. The current-controlled memristive system is represented by a differential form (the voltage-controlled form is in a bracket for comparison):

$$v = R(w, i)i \qquad [i = G(w, v)v)] \tag{2.2}$$

$$\frac{\mathrm{d}w}{\mathrm{d}t} = f(w, i) \qquad \left[\frac{\mathrm{d}w}{\mathrm{d}t} = f(w, v)\right],\tag{2.3}$$

in which v and i are the voltage and the current, w is a set of state variables. f, R, and G are in general explicit functions of time. Equation 2.2 indicates the unique property of a memristive system differing from an arbitrary dynamical device: no current will flow through the system when the applied voltage is zero, regardless of the state w. The above memristive equation was proven to model the i-v characteristics of some devices and systems, such as thermistors, Josephson junctions, and even the Hodgkin-Huxley model of the neuron in Chua's work [52]. Although the theory of memristor was established in the 70s, the first physical model and experimental demonstration of a "real" memristor were announced by Hewlett-Packard labs in 2008 [50]. They showed that the memristance arises naturally in a two-terminal nanoscale system consisting of a stack of Pt/TiO $_2$ /Pt. Solid-state electronic and ionic transport in this system are coupled under an external bias voltage. Some researchers [53] disagree with the claim of "Found of memristor" since they hold the opinion that the devices reported in 2008 were

not new. The hypothesized memristor requires magnetism but has no material memory in Chua's conceptual proposition, while in Hewlett-Packard's work, the reported devices constitute analog memory that can work without magnetism. Although the existence of a "real" memristor is still controversial, the special resistive switching phenomenon with memory effect is promising in many applications, such as novel non-volatile memory, new paradigms of computing, encryption, and radio-frequency communication [35]. Terms like "resistive switching" and "memristive" are more accepted when referring to this class of devices in the literature.

When discussing resistive switching, these phenomena have been studied since the early 1960s in various solid-state materials. A representative case is the anomalous negative differential resistance observed in metal oxides of a metal-insulator-metal (MIM) structure. The insulator material "I" spans from binary and multinary oxides, chalcogenides, and to group-IV, III-V, and II-IV semiconductors[49]. Due to the lack of sufficient analytic tools to understand the microscopic mechanism of the resistive switching overserved in metal oxides at that time and the significant advantages of Si semiconductor-based memories (such as DRAM, SRAM, and Flash), the research momentum of resistive switching devices was quenched. In the new informative era, the explosive growth of the generated data and the high cost of increasing the density of classical charge-based memory appeal to the research on novel memory devices. Resistive switching devices, as one group of novel memory elements, have again gained attention from both industry and academia. Nowadays, the papers published per year in the field of memristive devices contribute to a significant part in solid-state physics and nanoelectronic engineering [38]. In the past two decades, all major semiconductor research institutes and manufacturers have launched large research and development projects on resistive switching devices and systems. Samsung successfully demonstrated a ReRAM chip using  $180 \,\mathrm{nm}$  in 2004, Sandisk and Toshiba released  $32 \,\mathrm{GB}$  ReRAM chips in 2013, and Micron and Sony presented 16 GB ReRAM chips in 2014, to name a few [38].

### 2.3.2 Basic Working Concepts of Memristive Devices

Memristive devices are one class of emerging memory technologies and hold promise for various applications spanning from information storage, computation, hardware security, and radio-frequency communication [35]. A set of terminologies is defined to facilitate communication within the field.

Memristor is the most well-known name representing this class of two-terminal electronic devices. Due to the aforementioned debate about the memristor definition among the researchers, resistive switching or memristive elements, devices, memories, or cells are more mitigating ways to refer to these devices. These terms are also preferred and will be intensively used in later discussions. Resistive switching devices are initiated to serve as random-access memory (RAM). Therefore, upon the application, they are also known as resistive RAM (ReRAM or RRAM). It is worth noting here that ReRAM is also used to refer to redox-based resistive switching random access memory to emphasize the mechanisms in some literature [38, 54, 55].

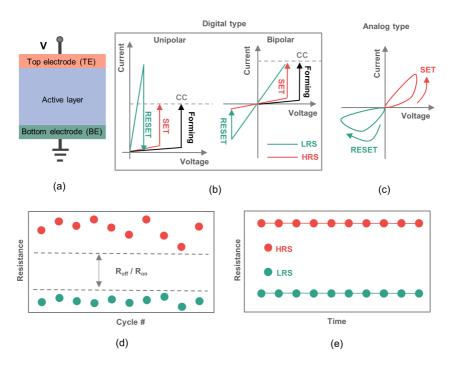

In general, a memristive device consists of a top electrode (TE), a bottom electrode (BE), and an active layer sandwiched between TE and BE (Figure 2.4(a)). From the perspective of a circuit designer, a memristive device serves as a twoterminal "switch", which determines the quantity of the current flow through the two-terminal element with distinct resistance levels when subjected to an electric field. The most reported memristive devices work in a binary form. That is to say, the devices are switched between their low resistive state (LRS) and high resistive state (HRS). LRS and HRS are called On and Off states, respectively, to associate with the tree terminal transistor. Researchers who target applications for information storage, encryption, radio-frequency communication, and logic operations prefer devices with binary resistive switching. Other groups of researchers endeavor to explore multiple intermediate resistive states (IRS) between LRS and HRS, which is referred to as *multilevel storage*. These types of devices are promising for increasing memory density by storing more than one bit within one cell. Moreover, the devices with multilevel are intensively studied for in-memory computing (IMC).

Figure 2.4: Basic concepts of memristive devices. (a) Schematics of a memristor in a cross-sectinal view. A common structure of memristors consists of a top electrode (TE), an active layer, and a bottom electrode (BE). TE is generally biased while the BE is grounded during the electrical measurements. (b) Schematic of typical *I - V* characteristic curves of digital-type memristors: unipolar (left-hand side) and bipolar (right-hand side) resistive switching modes. (c) Schematic of typical *I - V* characteristic curves of analog-type memristors. (d) and (e) Schematics of a typical results plot of endurance and retention.

Almost all of the reported memristive devices are in HRS as fabricated. The operation to initiate the first resistive switching, e.g., to bring the device from initial HRS to LRS, is called *Forming* process (Figure 2.4(b)). Accordingly, the voltage that is required to trigger Forming is termed as Forming voltage. The process to switch the device back to HRS is called *RESET* (also called *erase* when used as a memory device), while the reversed operation is termed as SET (also named write corresponding to RESET in information storage application). Although Forming and SET identically tend to bring devices from HRS to LRS, Forming generally requires a higher voltage than SET. Some researchers [56, 57, 58] claimed they developed a "Forming-free" device since the Forming cannot differentiate from the SET clearly. In the Forming and SET processes, the resistive switching from HRS to LRS results in a drastic increase in current, and a *compliance current (CC)* is commonly used to prevent the device from hard breakdown, as the gray dash lines shown in Figure 2.4(b). The operation to determine the resistance of the device after each SET and RESET is called read, which is achieved by applying a small voltage to the device. In reviews [36, 38, 59], it is suggested the read voltage should not exceed 1/10 of the SET voltage to avoid an unwanted resistance disturbance.

Depending on the polarity of the SET and RESET voltage, the memristive cells are classified into bipolar and unipolar resistive switching devices. Bipolar denotes that the SET and RESET operations are realized under opposite voltage polarities, while unipolar refers to the manner in which resistive switching always occurs under the same voltage polarity. In addition to the voltage polarity, memristive devices are categorized into two types. One is known as digital type, whose SET and RESET processes experience an abrupt change in current. The other one is termed as analog type, which, on the contrary, undergoes a gradual resistance change. The I-V characteristics of bipolar, unipolar, digital, and analog-type memristive devices are represented by sketched curves in Figure 2.4(b) and (c). A couple of parameters are commonly considered when evaluating the performance of a memristive cell. As a reversible electronic switch, the maximum number of resistance change cycles between two or multiple levels is of primary interest. This figure of merit is termed endurance, which is presented by plotting the value of LRS and HRS against the cycle numbers (Figure 2.4(d)). One needs

to consider the resistance ratio between HRS and LRS,  $R_{\rm Off}/R_{\rm On}$ , in the endurance plot. The endurance counts upon the  $R_{\rm Off}/R_{\rm On}$  are still acceptable. One advantage of ReRAM over SRAM and DRAM is its non-volatility. Therefore, researchers will consider the time of each resistive state that can be maintained without a voltage supply. This critical parameter is called *retention* (Figure 2.4(e)). Other parameters need consideration, but it depends on the application scenarios. Endurance, retention, and  $R_{\rm Off}/R_{\rm On}$  ratio are the essential figures of merit and thus will given especially attention throughout this thesis.

## 2.4 Categories of Working Mechanisms

Memristors, or memristive devices, are referred to as a family of electronic elements, of which resistive switching is the common characteristic. Nevertheless, the underlying physical mechanisms are manifold. From the natural perspective, resistive switching can be attributed to stoichiometric change induced by ions within the active layer, phase change of the active layer between high- and low-conductive states, magnetoresistive effects, electron trapping/de-trapping effect of the active layer, ferroelectric effect, and nano ionic redox phenomena [60, 61]. In an intuitional way, memristive devices are categorized into "filamentary" and "non-filamentary" types depending on whether the resistive switching occurs within a few localized conduction channels or uniformly across the entire area [60]. These two tags are widely used to indicate the resistive mechanisms. In the following, the abovementioned physical mechanisms will be introduced in detail under the filamentary and non-filamentary groups. Since the main work underlying the thesis involves filamentary and ion migration of non-filamentary types, they will be the focus of this section.

## 2.4.1 Filamentary

The filament type is the absolute dominating device category in the field of memristive devices. This type of memristive cell relies on the formation and rupture of conductive channels within the active layer to realize resistive switching. Depending on the ion species that participate in the formation of the conductive filaments, this vast family of devices is further divided into three subgroups. The first subgroup is termed electrochemical mechanism (ECM), which relies on the cation-based redox reaction. The second subgroup is referred to as the valence change mechanism (VCM), which is based on the migration of anions in the active layer. A variation of ECM and VCM is called thermochemical mechanism (TCM), in which the filaments can be formed by cations or anions. The distinction between TCM and the other two types is the RESET process. For TCM, Joul heating induced by the high current flowing through the filaments plays a crucial role. In the following sections, the working mechanism of the microscopic aspects and the device characteristics of these three types of filamentary memristive devices will be elucidated and compared.

#### **Electrochemical Metallization Mechanism (ECM)**

As the term implies, electrochemical metallization (ECM) memristive devices rely on the electrochemical process of metal ions. In general, ECM is more frequently used in the literature when referring to the underlying mechanism of this class of devices. In fact, they were called programmable metallization cells (PMC) originally, which now refers to the technology platform that spans a variety of applications beyond memory. In the semiconductor industry, the term conductive bridging random access memory (CBRAM) was coined to refer to this memristive technology in a memory array [61].

ECM memristive cells are generally in a configuration of so-called "MIM", which refers to a metal-ion conductor-metal system. One metal layer is called an active electrode (AE), made from electrochemically active metals such as Ag, Cu, and Ni. This class of metals tends to lose electrons when subjected to a positive bias and migrate within the ion conductor layer and the electrical field. In addition, Ag<sup>+</sup> and Cu<sup>2+</sup> are highly movable in solid electrolytes [62], which benefits the fast resistive switching process in ECM devices. On the contrary, the counter electrode in the MIM system consists of an electrochemically inert metal, such as

| AE | Active layer       | CE | $R_{\rm off}/R_{\rm on}$ | Retention (s) | Endurance  | Reference | Year |

|----|--------------------|----|--------------------------|---------------|------------|-----------|------|

| Cu | TiO <sub>2</sub>   | Pt | $2 \times 10^{4}$        | $10^{6}$      | $10^{5}$   | [63]      | 2018 |

| Ag | ZnO                | Pt | $> 10^{2}$               | 300           | $> 10^{3}$ | [64]      | 2018 |

| Cu | GeSe               | W  | $> 10^{2}$               | $10^{5}$      | $10^{5}$   | [65]      | 2010 |

| Ag | FAPbI <sub>3</sub> | Pt | $10^{5}$                 | 3000          | 1200       | [66]      | 2018 |

| Ag | $V_2C$             | W  | $10^{4}$                 | 2000          | 100        | [67]      | 2021 |

| Ag | PVP-PEDOT:PSS      | Pt | $10^{4}$                 | $10^{5}$      | 1300       | [68]      | 2020 |

| Ag | h-BN               | Pt | $10^{5}$                 | $10^{4}$      | 850        | [69]      | 2023 |

**Table 2.1:** List of typical reported ECM cells of different material stacks.

Pt, Au, W, or metal nitride. These metal materials serve as the counter electrode (CE), where the metal cations stem from AE harvest electrons and then are reduced to their electrically neutral form. The middle layer between AE and CE works as a matrix supporting cation migration. The utilized material for this ion conductor layer covers a vast family of functional materials, including transition metal oxides, chalcogenides, perovskite, MXene, organic materials, 2D materials, and their related derivatives, and so forth. The typical materials for AE, CE, and ion conductors are summarized in Table 2.1, together with the reported ECM devices.

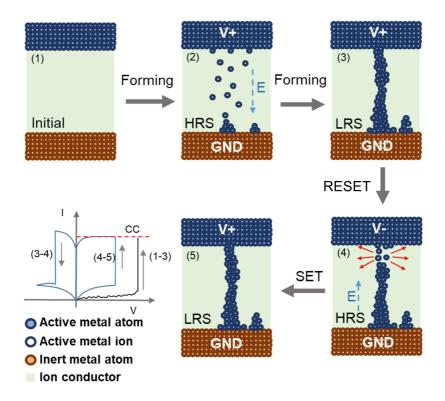

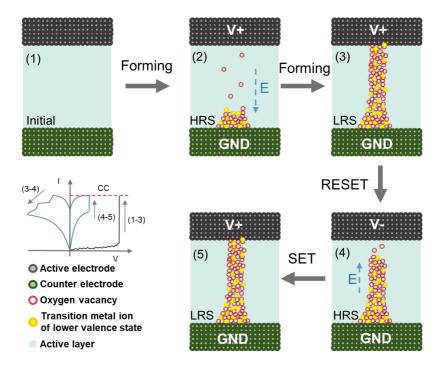

The underlying mechanism of resistive switching in ECM cells is attributed to the highly conductive metallic filaments formed within the active layer. The filaments can connect and disconnect the AE and CE reversibly, resulting in a switch from LRS to HRS and vice versa. The formation, rupture, and closing of the metal filament connection in the ECM cell involve a series of redox and electrical field-induced cation migrating processes. These physical and chemical processes account for the Forming, SET, and RESET operations over an ECM cell. Figure 2.5 is a schematic that elucidates the resistive switching processes of an ECM cell with respect to its redox and cation migration in a cross-sectional view. The sketched I-V curves of ECM cells on a logarithmic scale capture the characteristics of each operation process.

In general, the CE is grounded (GND) while only the polarity of the voltage applied to the AE is changed between positive and negative (V+ and V-) during

Figure 2.5: Mechanisms of ECM type memristors: A series of cross-sectional schematics illustrate the dynamic processes of the filament evolution behind Forming, SET, and RESET. The numbered processes relate to the sections involved in the typical I-V curves on a semi-logarithmic scale.

the operations. For the Forming process (processes 1 to 3), the AE is positively biased, and a pair of redox reactions will be triggered respectively at the AE and CE. At the side of AE, the half-cell reaction occurs as follows:

$$Me \to Me^{z+} + ze^{-}. \tag{2.4}$$

The atoms Me of AE will lose z electrons ( $e^-$ ) and be oxidized into cations Me<sup> $z^+$ </sup>. The dissolved cations will migrate along the electrical field in the middle solid

electrolyte and harvest electrons as long as they arrive at the CE, where another half-cell reaction occurs:

$$Me^{z+} + ze^{-} \rightarrow Me.$$

(2.5)

These two half-cell reactions lead to the growth of active metal filaments from CE towards AE (processes 1 to 2 in Figure 2.5), and eventually, the filaments will bridge both electrodes (process 3 in Figure 2.5), resulting in a low resistive state of the ECM cell. This process is termed Forming, as introduced previously. Since the movement of the cations within the electrolyte layer is a stochastic process, the reduction and growth of the filament will happen simultaneously at several locations on the CE of an actual ECM cell. One of these filaments grows at the fastest speed and will "short" the cell first, and the growth of the other filaments will terminate. This winner filament will dominate the resistive switching phenomena later on. This is similar to the rule "winner takes all." For the RESET process, the AE is negatively biased. A high current flowing through the bridging filament generates local Joule heating. Firstly, the local heating will promote ion diffusion from the filament towards the surrounding ion conductor and lead to a rupture of the filaments at the thinnest location (near the AE). Secondly, as long as a gap induced by the rupture exists within the filament, the residual filaments connecting the CE serve as a cation supplier while the AE works as a cation receiver since the electrical field is opposite to the Forming process. Consequently, the active metal from the filaments will dissolve into the electrolyte and migrate towards the AE, switching the ECM cell back to HRS (process 3 to 4 in Figure 2.5). The SET process happens when the AE is again applied with a positive voltage. Thereby, a similar process as Forming will revert the cell to LRS by closing the filament at the gap (process 4 to 5 in Figure 2.5). Since the growth of filaments in the Forming process covers the entire length of the ion conductor layer, while in the SET process, a shorter gap needs to be closed, the SET voltage is lower than the Forming voltage. By manipulating the polarity of the applying voltage, the ECM can be reversibly switched between HRS and LRS. Due to the high mobility of the metal ions in the electrolyte, the resistive switching phenomena of ECM cells are drastic, which can be seen

from the abrupt fall/drop of current in the I-V curves. The real dynamic process of forming and breaking filament in an ECM cell has been visualized through in- and ex-situ electron microscope technology during the past decades, including scanning electron microscope (SEM) [70, 71] and transmission electron microscope (TEM) [72, 73]. Thanks to the scalpel Atomic Force Microscope (AFM) technology, the CFs in ECM cells were visualized in 3D view [74, 75].

## Valence Change Mechanism (VCM)

Valence change mechanism (VCM) based memristive cells are the other major filamentary devices. In comparison with ECM cells, this type of device relies on the migration of anions, mostly oxygen ions, in the transition metal oxidesbased active layers [38]. In most of the transition metal oxide, oxygen ions are easier to move upon applying the external electrical field than the transition metal ions [76]. The migration of the oxygen ions away from its lattice leaves defects that are known as oxygen vacancy (V<sub>0</sub>). V<sub>0</sub> is regarded as positively charged and serves as a donor in n-type transition metal oxide semiconductors [77]. The enrichment or depletion of V<sub>o</sub> results in a valence state change of the transition metal cations and consequently changes the conductivity of the transition metal oxide [76]. Many transition metal oxides have been reported as the active layer for VCM cells, including TaO<sub>x</sub> [78, 79], TiO<sub>x</sub> [50, 80], HfO<sub>x</sub> [81, 82], WO<sub>x</sub> [83, 84], YO<sub>x</sub> [85, 86], and ZnO<sub>x</sub> [87, 88], to name a few. Like ECM cells, VCM cells are also composed of two electrodes: active electrode (AE) and counter electrode (CE). For the AE, electrochemical stable metals such as Pt, Au, W, etc., with high work functions are required. AE is also termed Schottky electrode (SE) when discussing VCM cells. In an ECM cell, Ag and Cu are commonly used due to their electrochemical dissolution in the active layer, while for a VCM cell, the metal cation injection is unwanted. Instead, metals with high oxygen affinity are preferred for CE, such as Al, Ti, Ta, etc. The CE and the active layer generally form an Ohmic contact. Thus, CE is also called an Ohmic electrode (OE) in the discussion of VCM cells. Table 2.2 lists some reported VCM devices of different material stacks and their respective performances. To elaborate on the working

| SE  | Active layer     | OE  | $R_{\rm off}/R_{\rm on}$ | Retention (s) | Endurance | Reference | Year |

|-----|------------------|-----|--------------------------|---------------|-----------|-----------|------|

| Pt  | TaO <sub>x</sub> | Ta  | 10                       | -             | $10^{10}$ | [78]      | 2010 |

| Pt  | $TiO_x$          | Ti  | 10                       | $10^{4}$      | 2000      | [89]      | 2020 |

| TiN | $HfO_x$          | Hf  | 10                       | -             | $10^{10}$ | [82]      | 2012 |

| Pt  | $WO_x$           | Al  | 10                       | $> 10^4$      | 200       | [90]      | 2016 |

| Pt  | $YO_x$           | TiN | $10^{3}$                 | $10^{5}$      | 300       | [90]      | 2016 |

| Pt  | $ZO_x$           | Al  | $10^{3}$                 | $10^{4}$      | 50        | [91]      | 2013 |

Table 2.2: List of typical VCM cells of different materials stack. Absence of parameter = "-".

mechanism of VCM cells from a microscopic point of view, a schematic in Figure 2.6 illustrates the processes of resistive switching in a generic VCM device model. The VCM memristive cells also rely on redox reactions between the electrode and the active layer. Differing from the ECM cells, the electrochemical reactions accounting for the resistive switching in VCM devices are generalized in the following three equations:

$$O_{o}^{x} \to V_{o}^{"} + 2e^{'} + \frac{1}{2}O_{2}$$

(2.6)

$$2Me^{z^{+}} + 2e^{'} \rightarrow 2Me^{(z-1)^{+}}$$

(2.7)

$$V_{o}^{"} + 2e^{'} + \frac{1}{2}O_{2} \rightarrow O_{o}^{x}.$$

(2.8)

In the above equations,  $O_0^x$  denotes the lattice oxygen ion,  $V_0^{"}$  is the oxygen vacancy,  $O_2$  is oxygen oxidized from oxygen ions, and  $Me^{z^+}$  represents lattice transition metal ion. In the Forming process, the positive voltage is applied to the SE, and while the OE is grounded, oxygen ions migrate towards the SE. The oxygen ions will be oxidized at the SE and released as gas, which is represented by Equation 2.6. The extraction of oxygen ions leaves oxygen vacancies behind [38]. As an equivalent view, this process can be described as the migration of positively charged Vo towards OE, resulting in the growth of the conductive path towards SE (processes (1) - (3) shown in Figure 2.6). Simultaneously, the sublattice metal ions along the filaments in the active layer are reduced to a lower valence state

**Figure 2.6:** Mechanisms of VCM type memristors: A series of cross-sectional schematics illustrate the dynamic process of the filament evolution behind Forming, SET, and RESET. The numbered processes relate to the sections involved in the typical I-V curves on a semi-logarithmic scale.

by combining with one free electron to complete the redox reaction pair, which is represented by Equation 2.7. For the RESET process, the SE is negatively biased. Thus, the oxygen vacancies are forced to be pushed away from the filaments and are filled again with oxygen ions, which are generated by reducing the oxygen at the SE (Equation 2.8 and processes (3) - (4) in Figure 2.6). Therefore, the cell is switched to HRS. The SET process is similar to Forming but is completed at a lower voltage since the conductive filaments are partially dissolved during the RESET. The introduced VCM mechanism here is only one typical model accepted by the community. The oxidation reaction can also happen at the OE by oxidizing the metals of high oxygen affinity, and the direction of the filament's growth can also be in the opposite manner. For a full spectrum of VCM cells, a comprehensive review [38] is recommended.

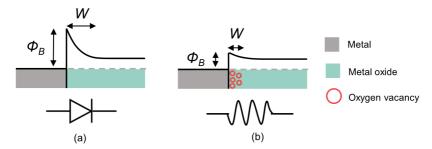

#### Thermochemical Mechanism (TCM)

Thermochemical mechanism (TCM) refers to the third class of filaments-based memristive devices that are derived from ECM and VCM but show unique resistive switching behavior. VCM and ECM cells show resistive switching in a bipolar manner, which implies the opposite polarity of SET and RESET voltages. On the contrary, the TCM cells work in unipolar form. For a TCM cell, the resistive switching between LRS and HRS can be triggered by a voltage of identical signs. Figure 2.7(a) demonstrates the typical I-V curves of a VCM device. Similar to ECM and VCM devices, a Forming process is generally required for a TCM cell to initiate resistive switching. After the Forming, the SET and RESET can be achieved either under positive or negative bias. In general, the threshold voltage value of SET is higher than that of RESET. For the SET process, a CC is also needed to prevent a "hard breakdown" while for the RESET process, the CC is not required.

Both anion- and cation-based devices are reported to be categorized as TCM type. Therefore, the material selections of TCM devices overlap with ECM and VCM cells. The electrode materials include Pt, Au, Ag, and Cu. Almost all oxides reported in ECM and VCM also show TCM mechanism, including TiO<sub>2</sub> [92],

**Figure 2.7:** Schematics illustrates the resistive switching characteristics of TCM cells. (a) TCM cells show a unipolar resistive switching mode as the I-V curves exhibit. (b) Rupture at the thinnest part in the middle of the filaments during the RESET.

HfO<sub>2</sub> [93], ZnO [94], Al<sub>2</sub>O<sub>3</sub> [95], and NiO [96, 97]. Among them, the NiO system is the most well-known model to investigate the TCM mechanism since both metallic (Ni-based) and oxygen vacancy filaments are feasible to be formed within the NiO layer [61]. The Forming and SET mechanism of ECM and VCM cells can be applied to explain cation and anion-based TCM cells, while the RESET process of a TCM device, as the name implies, relies more on thermal effects that accelerate the ion migration between the filaments and surrounded metal oxide matrix. Compared to the ECM and VCM devices, the filaments in the TCM devices rupture in the middle instead of in the vicinity of either electrode (as Figure 2.7(b) shows). The ion diffusion process of RESET differs between anion and cation-based TCM cells. In an anion-based cell, the filaments are composed of highly conductive oxygen vacancies. The current flowing through the filaments leads to a local temperature increase, which promotes the movement of oxygen ions towards the oxygen ion depletion region. This leads to the oxidization of the filaments and breaks the conductive bridge at the weakest point. In a cation-based cell, the heating effect promotes the diffusion of the metal ion from the filaments radially toward the surrounding metal oxide matrix, resulting in a rupture at the thinnest part of the filament.

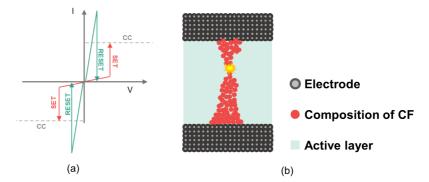

## 2.4.2 Non-filamentary

In addition to the filamentary-type memristive devices, there is another class of devices that function without the conductive path between the electrodes. For this type of device, the resistive switching occurs either at the interface between the electrode and active layer or within the whole active layer. Accordingly, this class of memristive devices is categorized as "non-filamentary". Compared to the filamentary type, the resistance values (two or multiple resistive states) of non-filamentary cells are dependent on the effective device area. In other words, the on- and off-currents will be scaled with the size of the device. In the case of filamentary devices, the on-current is independent of the device size until it shrinks to the dimension of the filaments [60]. In general, compared to the filament-type counterparts, non-filamentary devices show unique properties such as relatively slower resistive switching speed, shorter retention time, smaller range of resistive states, good uniformity, high device yield, forming-free, and low working current. There are no absolute advantages or disadvantages with respect to the device figure of merit. The discussion of the pros and cons needs to be drawn based on the applications. The filamentary devices are advantageous for non-volatile memory and logic-related applications, whereas the non-filamentary cells are powerful in implementing neuromorphic computing. The underlying mechanisms accounting for the non-filamentary resistive switching are manifold. They include but are not limited to "ion migration", "electron trapping/de-trapping", "ferroelectric effect", and "phase transition". In the following sections, the different types of nonfilamentary devices will be briefly introduced.

## **Ion Migration**

Metal oxides are the main family of materials that compose the MIM structure of memristive devices as the "I" layer. "I" stands not only for isolators but also can be semiconductors. With regard to memristive devices, transition metal oxides including TaOx [98], TiOx [99], and WOx [100] are reported to be used for resistive switching devices. In addition, some ternary and complex oxides (e.g.,

Figure 2.8: Oxygen vacancy concentration dependent band structure at the metal/metal oxide interface. (a) Schottky barrier height  $(\phi_B)$  and the width (W) results in a current rectifying characteristic. (b) An Increase in the oxygen vacancy concentration at the metal/metal oxide interface can reduce both the barrier height and width, which elevates the conductance of the junction and changes the junction to a resistor-like characteristic.

LSMO [101], PCMO [77], and Nb-doped SrTiO<sub>3</sub> [102]) are also investigated as the active layer of the memristive cell. Within the MIM structure, the selected metal oxide semiconductor layer will form a Schottky contact with one of the metal electrodes, which possesses a high work function (such as Pt). The difference between the work function of the metal electrode ( $\phi_M$ ) and the electron affinity of the metal oxide semiconductor layer ( $\chi_S$ ) is expressed as Schottky barrier height ( $\phi_B$ ) [103], and the relation is written as:

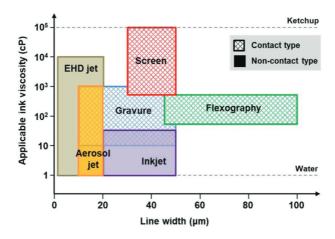

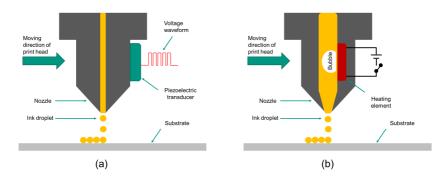

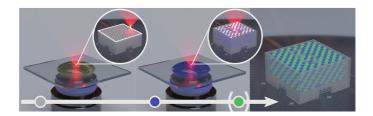

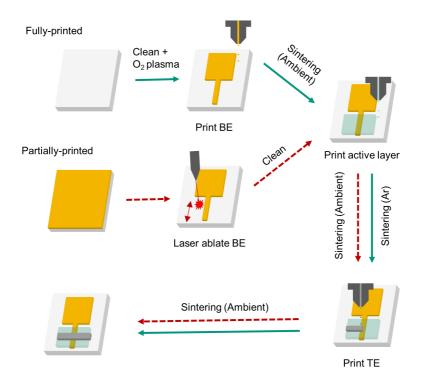

$$\phi_B = \phi_M - \chi_S. \tag{2.9}$$