# Compact and Power-Efficient RF Front-End Components for Beamforming Networks

Zur Erlangung des akademischen Grades eines

# DOKTORS DER INGENIEURWISSENSCHAFTEN (Dr.-Ing.)

von der KIT-Fakultät für Elektrotechnik und Informationstechnik des Karlsruher Instituts für Technologie (KIT)

angenommene

#### DISSERTATION

von

#### M.Sc. Kateryna Smirnova

geb. in Enerhodar (Ukraine)

Tag der mündlichen Prüfung: 29.01.2025

Hauptreferent: Prof. Dr.-Ing. Ahmet Çağrı Ulusoy Korreferent: Prof. Dr. Ir. Domine M.W. Leenaerts

# Zusammenfassung

Die neuesten Forschungsanstrengungen zur Gewährleistung der globalen Konnektivität sehen die Integration von terrestrischen, luftgestützten und satellitengestützten Kommunikationssystemen mit nahtloser Interoperabilität auf allen Ebenen vor. Phased Arrays, eine Schlüsseltechnologie für die elektronische Strahlsteuerung, kommen in jedem dieser Systeme zum Einsatz. Moderne Anforderungen treiben die Standards der nächsten Generation von Kommunikationssystemen zu höheren Betriebsfrequenzen. Der begrenzte verfügbare Abstand zwischen den Antennenelementen in einem Array führt zu strengen Flächenbeschränkungen für die elektronischen Komponenten des Strahlformungsnetzwerks. Zusätzlich wird bei Phased Arrays mit einer großen Anzahl von Elementen der hohe Stromverbrauch der IC-Komponenten aufgrund der damit verbundenen thermischen Herausforderungen zu einer weiteren kritischen Einschränkung. In dieser Arbeit werden Designtechniken zur Reduzierung des Flächen- und Stromverbrauchs untersucht, um eine kostengünstige und leichte industrielle Implementierung in hochintegrierten mm-Wellen-Systemen zu ermöglichen.

Es werden Miniaturisierungsstrategien diskutiert, beginnend mit passiven Strukturen, da diese in der Regel am meisten zum Gesamtflächenverbrauch der Schaltung beitragen. Es werden mehrere kompakte Geometrien für I/Q-Splitter vorgeschlagen, darunter ein differentieller 3D-Lange-Koppler und ein differentieller Spiralkoppler. Letzterer veranschaulicht auch die Performanzkompromisse, die mit einer engeren miniaturisierten Geometrie verbunden sind. Darüber hinaus werden gute Layout-Praktiken für andere Komponenten, wie z. B. mehrschichtige Induktivitäten und transformatorbasierte Impedanzanpassungsnetzwerke, erforscht und eingesetzt.

Als nächster Schritt wird in dieser Forschungsarbeit der Miniaturisierungsaufwand auf der Topologieebene des kompletten Phasenschiebers erweitert und vorgestellt. Es werden drei Designs im W-Band vorgestellt, die auf industrielle Spezifikationen für zukünftige terrestrische 6G-Systeme abzielen.

Alle Phasenschieber nutzen die Vektorsummierung als Phasenkontrollmechanismus, der eine hohe Phasenauflösung bei kompakter Bauweise bietet. Das erste Design basiert auf einer konventionellen Gilbert-Zelle, enthält aber einen zuvor vorgestellten kompakten differentiellen Lange-Koppler als I/Q-Splitter, ein LC-basiertes Ausgangsanpassungsnetzwerk und zwei Marchand-Baluns für die Single-Ended-Version. Die Integration dieser kompakten passiven Strukturen führt zu einer Chipfläche von 0,053 mm<sup>2</sup>, die im Vergleich zu früheren akademischen Forschungspublikationen für dieselbe Betriebsfrequenz und Phasenauflösung deutlich kleiner ist. Die nächste Design-Iteration führt eine grundlegende änderung der Topologie der Gilbert-Zelle ein, die von der Blixer-Schaltung inspiriert ist. Bei diesem Ansatz wird die klassische Transkonduktanzstufe der Emitterschaltung g<sub>m</sub> modifiziert, um einen integrierten aktiven Balun auf der Eingangsseite zu bilden. Gleichzeitig werden das Ausgangsanpassungsnetzwerk und die Balun-Funktionalität in einem Transformator kombiniert. Durch diese Modifikationen und die zuvor angewandten kompakten Layout-Strategien wird die belegte Fläche weiter auf 0,026 mm<sup>2</sup> reduziert. Der dritte Entwurf schließt das Kapitel ab, indem er verschiedene Ansätze für den bidirektionalen Betrieb erweitert und einige der besten Eigenschaften von aktiven und passiven Phasenschiebern in einem einzigen schalterlosen Block kombiniert. Dies wird erreicht, indem der Koppler und die Transformatoren für beide Signalrichtungen wiederverwendet werden und nur der Transistorkern verdoppelt wird. Alle Entwürfe wurden auf dem Wafer charakterisiert, und ihre Funktionalität wurde erfolgreich bestätigt.

Das nächste Kapitel befasst sich mit der Satellitenkommunikation als einem der Elemente der zukünftigen Beyond-5G-Infrastruktur. Die Spezifikationen und Entwurfsziele spiegeln die globalen Forschungstrends in diesem Bereich wider, einschließlich der Q- und V-Band Frequenzbereiche. Es wurde ein Subsystem für selbstkalibrierende Satellitenkommunikationssysteme entwickelt, wobei der Schwerpunkt auf einer großen Bandbreite und einem großen Dynamikbereich liegt. Da die belegte Fläche in der Raumfahrtanwendung ein noch größeres Problem darstellt, wurden die Miniaturisierungsbemühungen auf der Kettenebene durch Überdenken der Rollen und zusätzlichen Funktionen der Bausteine fortgesetzt. Als Ergebnis wird ein Blixer-basierter Phasenschieber für eine quasi-unabhängige Phasen- und Verstärkungsteuerung verwendet, der einen Übergang vom single-ended zum differentiellen Signal zwischen dem LNA und den folgenden VGA-Stufen bereitstellt. Darüber hinaus ermöglicht eine VGA-Stufe mit einem Resonator zwischen dem positiven und dem ne-

gativen Pfad sowohl die Verstärkungsteuerung als auch die Anpassung der Verstärkungssteigung. Durch die Integration mehrerer Funktionen kann daher die Gesamtzahl der erforderlichen Komponenten minimiert werden.

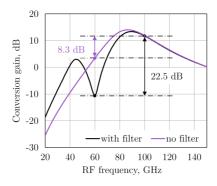

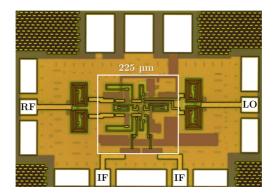

Das letzte Kapitel befasst sich mit Low-Power-Designs und den damit verbundenen Performanzkompromissen. Zur Beurteilung der akzeptablen Leistungsreduzierung werden zwei zweistufige W-Band-LNAs – ein Design mit optimaler Leistung und ein Design mit geringem Stromverbrauch – vorgestellt und quantitativ verglichen. Eine weitere Komponente des W-Band-Empfängers, die in diesem Kapitel vorgestellt wird, ist ein Mischer mit integriertem Spiegelfrequenzunterdrückungsfilter. Abhängig von den Anforderungen an die Spiegelfrequenzunterdrückung und dem Strahlformungsschema kann dieses Design als stromsparende, kompaktere Alternative zu den üblicherweise verwendeten Quadraturmischern dienen. Alle drei Schaltungen wurden charakterisiert, und die erzielten experimentellen Ergebnisse bestätigen die Gültigkeit der vorgestellten Ideen und Überlegungen.

## **Abstract**

The latest research efforts to ensure global connectivity envision the integration of terrestrial, airborne, and satellite communication systems, with seamless interoperability across all layers. Phased arrays, a key technology for electronic beam steering, are utilized in each of these systems. Modern demands push the standards of next-generation communication systems to higher operational frequencies. Consequently, the limited available spacing between antenna elements in an array imposes strict area constraints on the electronic components of the beamforming network. Additionally, in phased arrays with a large number of elements, high power dissipation of IC components becomes another critical limitation due to the associated thermal challenges. This thesis investigates design techniques for area and power reduction to enable potential low-cost and lightweight industrial implementation and feasibility in highly integrated mm-wave systems.

Miniaturization strategies are discussed, beginning with passive structures since they typically contribute the most to overall circuit area consumption. Several compact geometries for I/Q splitters are proposed, including a 3D differential Lange coupler and a differential spiral coupler. The latter also exemplifies performance trade-offs associated with tighter miniaturized geometry. Additionally, good layout practices for other components, such as multi-layer inductors and transformer-based impedance matching networks, are explored and employed.

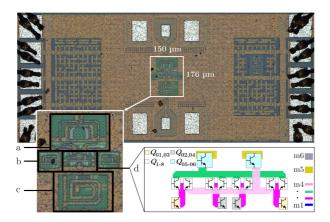

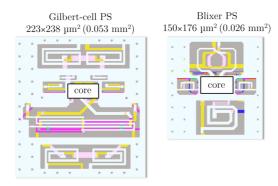

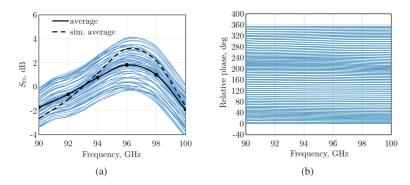

As the next step, this research work expands and presents the miniaturization effort on the topology level of the complete phase shifter. Three designs are presented in the *W*-band, targeting industrial specifications for future terrestrial 6G systems. All phase shifters utilize vector summation as the phase control mechanism, which offers high phase resolution within a compact footprint. The first design is based on a conventional Gilbert cell but incorporates a previously presented compact differential Lange coupler as an I/Q splitter, an LC-based output matching network, and two Marchand baluns for the single-ended versi-

on. The integration of these compact passive structures results in a die area of 0.053 mm², significantly smaller compared to prior academic research publications for the same operating frequency and phase resolution. The next design iteration introduces a fundamental modification to the Gilbert cell topology, inspired by the Blixer circuit. In this approach, the conventional CE  $g_m$ -stage is modified to form an integrated active balun on the input side. Simultaneously, the output matching network and the differential-to-single-ended conversion are combined in one transformer. These modifications, along with previously employed compact layout strategies, further reduce the occupied area to 0.026 mm². The third design concludes the chapter by expanding various approaches to bidirectional operation, combining some of the best properties of active and passive phase shifters into a single switchless block. This is achieved by re-using the coupler and transformers for both signal directions and only doubling the transistor core. All designs have been characterized on-wafer, and their functionality has been successfully confirmed.

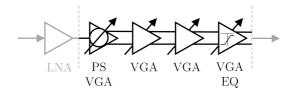

The next chapter focuses on satellite communication as one of the elements in future beyond-5G infrastructure. Specifications and design goals reflect global research trends in this field, including frequency range of interest in the Q- and V- band. A subsystem for self-calibrating satellite communication systems has been developed with the focus on broad bandwidth and large dynamic range. As occupied area imposes even larger concern in space application, miniaturization efforts on the chain level, have been made by reconsidering the roles and additional functions of the building blocks. As a result, a Blixer-based phase shifter is used for quasi-independent phase and gain control, providing a single-ended to differential transition between the LNA and the following VGA stages. Additionally, a VGA stage with a resonator between the positive and negative branches enables both gain control and gain slope adjustment. Integrating multiple functions, therefore, allows for minimizing the total number of required components.

The final chapter explores low-power designs and the associated performance compromises. To assess acceptable levels of power reduction, two two-stage W-band LNAs – an optimum-performance design and a low-power design – are presented and quantitatively compared. Another W-band receiver component discussed in this chapter is a down-conversion mixer with an integrated image-reject filter. Depending on image rejection requirements and the beamforming scheme, this design can serve as a low-power, more compact alternative to

commonly-used quadrature mixers. All three circuits have been characterized, and the experimental results obtained confirm the validity of the presented ideas and considerations.

# Acknowledgement

Looking back on the last five years, I realize how lucky I have been to be surrounded by so many incredible people and to have had the opportunity to learn and develop both professionally and personally. I am sincerely grateful to my supervisor, Prof. Dr.-Ing. Ahmet Çağrı Ulusoy, for giving me this opportunity and for his guidance. His encouragement, especially in my moments of drowning in self-criticism, inspired me to move forward with my ideas without hesitation.

I had the honor of having Prof. Dr. Ir. Domine M.W. Leenaerts as my cosupervisor, who significantly contributed to my PhD with his broad expertise, attention to my ideas, and incredible support, which I deeply appreciate.

I would like to thank all the colleagues from IHE for the great time I had there, for keeping traditions alive, for being open to various discussions, and for being ready to help. In addition, it was a pleasure to share the office first with Lucas, Basim, and Benjamin, and later with Tsung-Ching, Kaan, and Christian. The walls of our offices have witnessed it all: discussions, helping and motivating each other, endless coffee breaks, long evenings, struggles, and successes. It would not have been the same without all those moments – different but uniting. I also sincerely appreciate Selina, Matthias, Elizabeth, and Adriana being in my life. Their support and empathy healed my soul every time.

Thanks to the MyWave consortium, I had the chance to experience an industrial stay at NXP Semiconductors in Eindhoven. I would like to thank the entire Advanced Design Team (back in 2021) for always making me feel included, welcomed, and encouraged. I was also lucky to share this experience with Roger and Dmitrii, who brought so much joy and wonderful memories to my time in Eindhoven.

I am forever grateful to my close friends, Yelyzaveta and Daria, for their unconditional support throughout so many years, despite the distance, the pandemic, the war – literally anything that could happen.

Lastly, I thank my dear family for believing in me, respecting my freedom, and staying strong.

Karlsruhe, December 2024

Kateryna Smirnova

# **Contents**

| Zι | ısam  | menfassung                                              | İ  |

|----|-------|---------------------------------------------------------|----|

| Αl | ostra | ct                                                      | v  |

| Αd | cknov | vledgement                                              | ix |

| Ad | crony | ms and Symbols                                          | χv |

| 1  | Intro | oduction                                                | 1  |

|    | 1.1   | Phased Arrays in Advanced Wireless Communication        | 1  |

|    |       | 1.1.1 Principle of Operation                            | 1  |

|    |       | 1.1.2 Beamforming Architectures                         | 3  |

|    |       | 1.1.3 Analog Phase Shifting Configurations              | 6  |

|    | 1.2   | Satellite Communication in Beyond-5G Infrastructure     | 8  |

|    | 1.3   | SiGe BiCMOS Technologies in Next-Generation Communi-    |    |

|    |       | cation Systems                                          | 10 |

|    | 1.4   | Structure and Goals of the Thesis                       | 11 |

| 2  | Min   | iaturization of Passive Components                      | 13 |

|    | 2.1   | I/Q Splitters Overview                                  | 13 |

|    | 2.2   | Proposed Quadrature Couplers                            | 16 |

|    |       | 2.2.1 Differential Lange Coupler                        | 16 |

|    |       | 2.2.2 Differential Coupler Based on Spiral Edge-Coupled |    |

|    |       | Lines                                                   | 19 |

|    | 2.3   | Inductors and Baluns                                    | 21 |

|    | 2.4   | Conclusion                                              | 23 |

| 3  | W-F   | and Vector-Sum Phase Shifters for Phased Arrays         | 25 |

|   | 3.1  | Archit  | tectures and Definitions                              | 25 |

|---|------|---------|-------------------------------------------------------|----|

|   |      | 3.1.1   | Beam Squint in Phase-Based Beam Steering              | 25 |

|   |      | 3.1.2   | Phase Shifter Topologies                              | 28 |

|   |      | 3.1.3   | Performance Metrics                                   | 31 |

|   | 3.2  | Gilber  | rt-Cell Based Phase Shifter                           | 33 |

|   |      | 3.2.1   | Circuit Description                                   | 34 |

|   |      | 3.2.2   | Experimental Results                                  | 40 |

|   | 3.3  | Blixer  | -Based Phase Shifter                                  | 43 |

|   |      | 3.3.1   | Circuit Description                                   | 43 |

|   |      | 3.3.2   | Experimental Results                                  | 46 |

|   | 3.4  | Bidire  | ectional Active Phase Shifter                         | 49 |

|   |      | 3.4.1   | Circuit Description                                   | 49 |

|   |      | 3.4.2   | Experimental Results                                  | 53 |

|   | 3.5  | Conclu  | usion                                                 | 56 |

| 4 | Q- a | ınd V-E | Band Building Blocks for Space Electronics            | 59 |

|   | 4.1  |         | d V-Band Frequencies in Satellite Communication       | 59 |

|   | 4.2  | _       | tions and Specifications                              | 60 |

|   | 4.3  |         | e Phase Shifter for Broadband Phase and Gain Control. | 61 |

|   |      | 4.3.1   | Circuit Description                                   | 61 |

|   |      | 4.3.2   | *                                                     | 64 |

|   |      | 4.3.3   |                                                       | 66 |

|   | 4.4  | Broad   | band Variable Gain Amplifier with Gain Equalization.  | 68 |

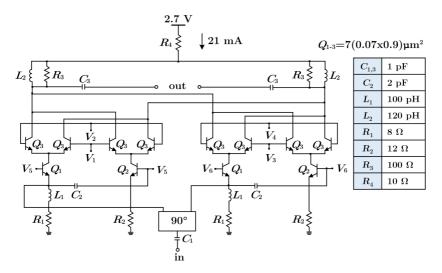

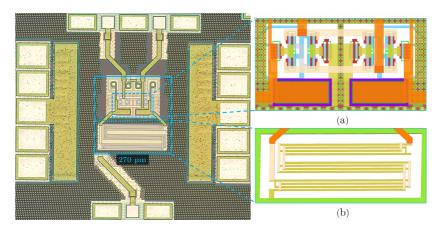

|   |      | 4.4.1   | Circuit Description                                   | 68 |

|   |      | 4.4.2   | Simulation Results                                    | 69 |

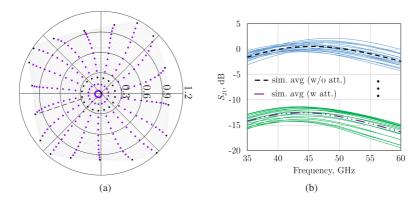

|   | 4.5  | Chann   | nel RFIC Simulation Results                           | 72 |

|   | 4.6  |         | usion                                                 | 75 |

| 5 | W-F  | Rand I  | ow-Power Components                                   | 77 |

| • | 5.1  |         | s Caused by High Power Dissipation                    | 77 |

|   | 5.2  |         | Power Low-Noise Amplifier                             | 78 |

|   | ٠.2  | 5.2.1   | Performance Metrics                                   | 78 |

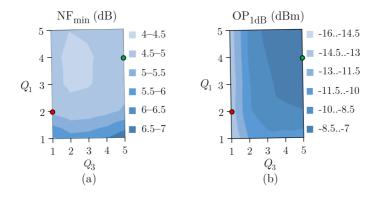

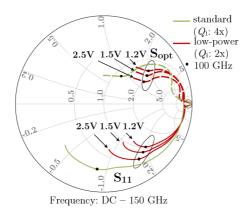

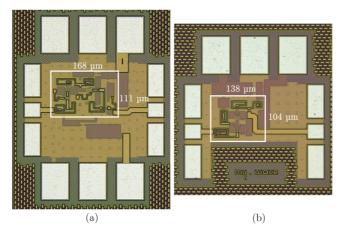

|   |      | 5.2.2   | Optimal-Performance Design Description                | 79 |

|   |      | 5.2.3   | Low-Power Design Description                          | 80 |

|   |      | 5.2.4   | Experimental Results                                  | 83 |

|   |      |         |                                                       |    |

|    | 5.3   | Down-     | -C   | onv  | ers  | ior | ı N | /liz | xe | r v | vit | h   | In | na | ge | R | lej | ec | tio | on |  |  |  |  | 87  |

|----|-------|-----------|------|------|------|-----|-----|------|----|-----|-----|-----|----|----|----|---|-----|----|-----|----|--|--|--|--|-----|

|    |       | 5.3.1     | F    | Perf | orn  | naı | 100 | e N  | Λe | etr | ics | 3   |    |    |    |   |     |    |     |    |  |  |  |  | 87  |

|    |       | 5.3.2     | Ι    | ma   | ge ] | Re  | jec | cti  | on | Α   | p   | orc | oa | ch | es |   |     |    |     |    |  |  |  |  | 89  |

|    |       | 5.3.3     | (    | Circ | uit  | D   | esc | cri  | pt | io  | n   |     |    |    |    |   |     |    |     |    |  |  |  |  | 90  |

|    |       | 5.3.4     | F    | Exp  | eri  | me  | nt  | al   | Re | esi | ult | S   |    |    |    |   |     |    |     |    |  |  |  |  | 93  |

|    | 5.4   | Conclu    | usi  | on   |      |     |     |      |    |     |     |     |    |    |    |   |     |    |     |    |  |  |  |  | 95  |

| 6  | Cor   | clusio    | ns   | ar   | nd   | Οι  | ıtl | 00   | ok | Ĭ.  |     |     |    |    |    |   |     |    |     |    |  |  |  |  | 99  |

| Re | efere | nces .    |      |      |      |     |     |      |    |     |     |     |    |    |    |   |     |    |     |    |  |  |  |  | 103 |

| O۱ | wn P  | ublicat   | tio  | ns   |      |     |     |      |    |     |     |     |    |    |    |   |     |    |     |    |  |  |  |  | 115 |

|    | Jour  | nal Pape  | ers  |      |      |     |     |      |    |     |     |     |    |    |    |   |     |    |     |    |  |  |  |  | 115 |

|    | Con   | ference ! | Pa   | per  | s.   |     |     |      |    |     |     |     |    |    |    |   |     |    |     |    |  |  |  |  | 115 |

|    | Othe  | er Contr  | rihi | ıtio | ns   |     |     |      |    |     |     |     |    |    |    |   |     |    |     |    |  |  |  |  | 115 |

# **Acronyms and Symbols**

### **Acronyms**

**BEOL** back end of line

**BiCMOS** bipolar CMOS

**CB** common-base

CE common-emitter

**EM** electromagnetic

**FoM** figure of merit

**HBT** heterojunction bipolar transistor

**IHE** Institute of Radio Frequency Engineering and Electronics

**IHP** Leibniz Institute for High Performance Microelectronics

**IRR** image rejection ratio

**KIT** Karlsruhe Institute of Technology

LNA low-noise amplifier

**NF** noise figure

**PA** power amplifier

**PS** phase shifter

Rx receiver

**SiGe** silicon germanium

Tx transmitter

VGA variable gain amplifier

#### **Constants**

$\pi = 3.14159..$  Pi

c = 299792458 m/s Speed of light in vacuum

## **Latin Symbols**

*f* Frequency

IP3 Third-order intercept point

IMD3 Third-order intermodulation distortion

$P_{1\text{dB}}$  1 dB compression point

$P_{\rm DC}$  Power consumption

## **Greek Symbols**

$\lambda$  Wavelength

$\varphi$  Phase

$\theta$  Phase control setting; beam direction

$\omega$  Angular frequency

## 1 Introduction

# 1.1 Phased Arrays in Advanced Wireless Communication

The fifth generation (5G) and future beyond-5G mobile communication networks in contrast to previous generations move higher in operating frequencies utilizing mm-wave bands. The large number of unlicensed and therefore less crowded bands as well as their larger absolute available bandwidth leading to higher achievable data rates are some of the most attractive features. Whereas 5G bands assigned in some countries include  $K_a$  (27–40 GHz), Q (33–50 GHz), and E-band (60–90 GHz) frequencies [HJY+21], the ongoing research in 6G systems development foresees the use of higher frequencies, such as W-band (75–110 GHz) and even reaching the sub-THz frequency range. Some of the foreseen 6G applications include autonomous unmanned vehicles, smart cities and massive Internet of Things.

Phased arrays are integral to modern communication systems, driving critical advancements in high-frequency wireless technologies. By enabling electronic beam steering, phased array technology provides precise and efficient directional communication. This capability is particularly valuable in environments with high user density and complex signal propagation, such as urban areas and satellite networks. The ability to dynamically form and steer beams, combined with techniques such as spatial diversity and spatial multiplexing [Mas17], is a key enabler of 5G and likely future generations of communication systems.

### 1.1.1 Principle of Operation

The use of phased arrays in mm-wave communication systems offers significant advantages compared to single antenna systems. Increasing with frequency

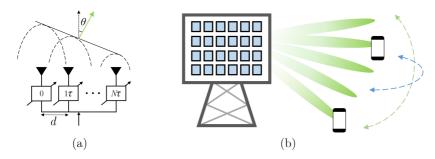

Figure 1.1: Uniform linear phased array (a) and 2D beam steering example (b).

propagation loss requires higher transmitter output power. Instead of a single high-power power amplifier (PA), a set of relatively low-power PAs in an array configuration exhibits improved energy efficiency by distributing the power requirements across the system [CA20]. The power usage is further optimized by focusing the radiated energy in narrower beams. For example, for a uniform N-element linear array (Fig. 1.1a) with a distance d between the elements, the 3-dB beamwidth  $\theta_B$  vs. the beam steering angle  $\theta$  is approximated as  $\theta_B = \frac{0.886 \lambda}{N d \cos \theta}$  [Mai94]. Hence, more elements will narrow the radiated beam.

At the receiver side, the use of phased arrays leads to improved signal-tonoise ratio, due to coherent signal combining and the uncorrelated nature of noise [GHH04] [Ma16].

One key property of phased arrays is their beam steering capability. In essence, it means the ability to adjust the radiation pattern of an array, in other words, to electronically steer the beam. Variable time-delay control compensates for path length differences between each antenna element and the target direction and thus ensures a coherent signal combining at the desired angle. Additional amplitude control (tapering) can be applied to further adjust the radiation pattern shape, e.g. to reduce the side lobes. Therefore, phased arrays are capable of forming the main beam in the direction of the desired signal with reduced side lobes and providing eventually the null-steering (zero-forcing) in other directions, especially the direction of a known interferer.

For a single signal frequency, the required time delay difference  $\tau = \frac{d\sin\theta}{c}$  translates into a phase shift difference of  $\varphi = \omega \tau = \frac{2\pi d\sin\theta}{\lambda}$  (hence "phased"

array). For narrow-band systems the phase shift over the band can be assumed to be the same as for the center frequency of the band. For wide-band systems, an error occurs resulting in beam squint. To overcome this effect, one must use a true-time-delay functionality. This thesis focuses on phase-controlled phased arrays. More details on this choice are discussed in Chapter 3.

A beam steering example is schematically shown in Fig. 1.1b. Applying the same approach to a 2D array (e.g., on a base station) enables the beam steering in both vertical and horizontal planes.

#### 1.1.2 Beamforming Architectures

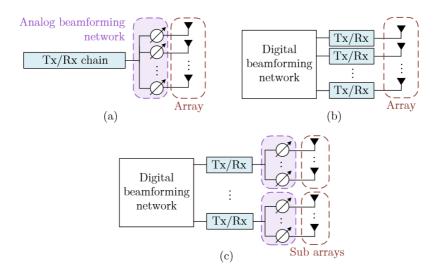

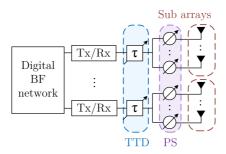

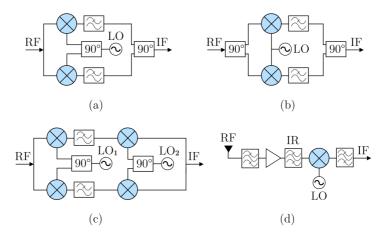

Depending on the implementation, the beamforming can be categorized into three types: analog, digital, and hybrid (Fig. 1.2).

Figure 1.2: Analog (a), digital (b), and hybrid (c) beamforming.

#### **Analog Beamforming**

In systems using analog beamforming, the weighting and delay functionality is added to the signal in the analog domain. In most cases, this is done per antenna element to obtain maximum flexibility. However, column and/or row driven antenna panels are also in use, the weighting and delay functionality is then implemented for a group of antennas. Analog beamforming is a low-cost solution with low power consumption and lower complexity because after the signal summation operation or before the signal-split operation is completed, the remaining hardware is shared for all antenna elements (Tx/Rx chain in Fig. 1.2a). At the same time, this architecture suffers from several disadvantages. Signal combining in the analog domain excludes any additional data manipulations in the digital domain and thus limits the beamforming flexibility compared to the fully digital alternative. Limited bandwidth of analog phase shifters as key components for beam steering, in this case, results in reduced system's operational bandwidth. In addition, a conventional single array cannot generate multiple beams without employing complex techniques, such as splitting the array into sub-arrays based on the desired number of beams, which significantly increases overall hardware complexity. Moreover, mitigating the effects of undesired interaction between the beams may pose more challenges compared to digital beamforming, which can employ advanced algorithms for this purpose. However, analog beamforming is still the leading technique in communication systems, being cellular infrastructure or mobile handheld. A recent example is a joint concept for a sub-THz 6G system developed by Ericsson and Intel in 2023, where analog beamforming is anticipated to be the most likely scheme for a final implementation [PBE<sup>+</sup>23].

#### **Digital Beamforming**

In digital beamforming, each antenna has an individual dedicated RF chain, whereas the phase control is performed by digital baseband processing. In this case, mathematical algorithms can be used with maximum flexibility. This architecture can be used in both single- and multi-user scenarios, due to the ability to not only create multiple spatial streams simultaneously but also to reconfigure their number immediately if needed. However, such an attractive performance comes at the expense of increased cost and power consumption because of an increased number of components. Moreover, in receive mode, there is no early spatial filtering since the null-steering is performed in the digital domain. This means that all front-end components and ADCs are exposed

Table 1.1: Analog vs. Digital Beamforming

to potentially strong interferers from different directions [Sah]. This implies stricter linearity requirements to prevent signal distortion and therefore results in even higher power consumption. Required computational resources contribute to it as well, since the data that needs to be processed is proportional to the number of elements, number of beams, and instantaneous bandwidth of the signal. Digital beamforming has been used in conventional MIMO systems but may become too complex and expensive for both manufacturing and operation in massive MIMO systems, especially those using hundreds or more antenna elements.

Table 1.1 schematically summarizes the above-mentioned advantages and disagvantages of analog and digital beamforming.

#### **Hybrid Beamforming**

In essence, hybrid beamforming is an extension of the analog architecture to the multi-stream scenario. The main idea is to use a two-step procedure: analog signal processing within smaller sub-arrays (Fig. 1.2c) and digital signal processing with reduced dimensions (due to the reduced number of RF chains). Alternatively, analog and digital beamforming schemes can be applied to different scanning planes of an array – analog in the azimuth plane and digital for a coarser scan in the elevation plane. By combining the best features of analog and digital architectures, hybrid beamforming can be considered a promising trade-off solution. Some of the related research activities can be found in [MRH+17] and [IE19].

#### 1.1.3 Analog Phase Shifting Configurations

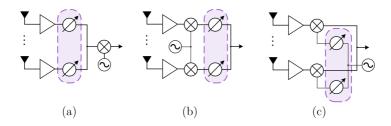

Phase shifters are used in both analog and hybrid beamforming schemes and their position in a chain determines the corresponding phase shifting configuration. Fig. 1.3 explains three configurations, namely RF (a), IF (b), and LO (c) phase shifting. Such naming corresponds to the phase shifter location relative to a frequency conversion stage (mixer). In the following discussion, a receiver array is used as an example.

#### **RF Phase Shifting**

In the RF configuration, the phase shifting takes normally place after the received signal is amplified by a low-noise amplifier (LNA), but not down-converted in frequency yet. The phase shifting operation takes place on RF signals. This approach has multiple advantages, such as simplified LO distribution, overall reduced complexity and therefore the lowest area and power consumption. This is due to the phase-shifted signal combining implemented before the down-conversion, therefore, only one mixer and a corresponding LO source are required for the entire array. Disadvantages of this architecture include challenging phase shifter design at higher frequencies and a strong influence of its performance on the array functionality.

#### **IF Phase Shifting**

The use of a phase shifter after down-conversion at the intermediate frequency (IF) simplifies its design process in general but requires a separate mixer per antenna element and a complex LO distribution. In addition, another mixer is needed after such phase shifting for frequency conversion from IF to baseband, thus increasing the die area and power dissipation. The large footprint of passive

Figure 1.3: RF (a), IF (b) and LO (c) phase shifting as categories of analog beamforming.

| Phase shifting | Area/Cost | $P_{\mathrm{DC}}$ | Phase shifter design | LO distri-<br>bution |

|----------------|-----------|-------------------|----------------------|----------------------|

| RF             |           |                   |                      |                      |

| IF             |           |                   |                      |                      |

| LO             |           |                   |                      |                      |

Table 1.2: Phase Shifting Schemes Comparison

power combiners (e.g., the Wilkinson combiner) at lower frequencies further increases the total area.

#### **LO Phase Shifting**

LO phase shifting architecture also suffers from a complex LO distribution network, especially challenging because of certain phase coherency that it has to guarantee. On the other hand, some of the requirements for the phase shifter performance are relatively relaxed, since the loss, non-linearity, and noise performance do not directly translate to the receiver performance [Fak].

Table 1.2 compares the RF, IF and LO phase shifting schemes by illustrating some of the above-mentioned aspects. In the available literature, rather few examples of mm-wave phased arrays utilizing IF phase shifting can be found, such as a D-band 8Tx-8Rx phased array [LR22] and a V-band 4-element receiver [KP15]. On the other hand, LO phase shifting implementations are more frequently reported in recent studies, including a 94-GHz 4Tx-4Rx phased array IC [TST+17], a 94-GHz 16Tx-1Rx chip [ZXL+24], and an E-band 16-TRx module [ESB20]. In most cases, enhanced SNR is highlighted as the primary motivation for adopting LO phase shifting, as the phase shifter's insertion loss does not affect the signal propagation path. However, due to its numerous advantages, RF phase shifting remains the most widely used scheme for high-frequency phased arrays. Several examples in W-band include [LPO+18], [LCH+22], [NVGS+15], [MMM+24] and many others. As shown in Table 1.2, the primary limitation of the RF phase shifting scheme is the challenging design of high-frequency phase shifters. Addressing this challenge is one of the key motivations of this thesis.

# 1.2 Satellite Communication in Beyond-5G Infrastructure

Nowadays, the latest technological advancements still have not resulted in meeting the demanded ubiquity, i.e., availability in remote areas. Ensuring a full coverage for various scenarios, including mobility use cases on land, sea, or air, requires a more complex multi-dimensional network with heterogeneous elements. Satellite constellations will complement 5G/6G terrestrial coverage and provide connectivity across the globe. European Space Agency (ESA) is actively carrying out various activities to integrate satellite technologies into communication networks as part of the "Space for 5G/6G" program. More details can be found in [Age].

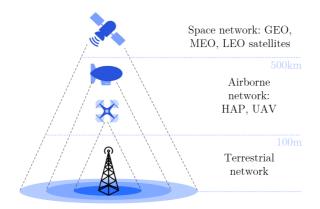

These activities include the design and implementation of a three-layer network architecture, comprised of the terrestrial, airborne, and space layers, schematically illustrated in Fig. 1.4.

Multi-beam phased arrays using analog beamforming scheme are widely used in modern satellite communication. The most recent examples include:

• **Starlink**, launched in 2018 by SpaceX into LEO (low Earth orbit). The constellation of thousands of satellites operates at the  $K_u$ -band

Figure 1.4: Multi-layer network architecture for 5G/6G.

Figure 1.5: Beam hopping technology.

(12–18 GHz) and uses beam hopping (illustrated in Fig. 1.5) as the beam coverage method. The phase shifters are one of the main components of the 8-channel beamforming chip [MKAY<sup>+</sup>21].

• Eutelsat Quantum, developed by ESA, Eutelsat, and Airbus, and launched in 2021 into GEO (geostationary orbit). The satellite uses the same coverage method and frequency in receive mode as Starlink. Further details and more examples can be found in work [YWZ<sup>+</sup>23].

The increasing number of launched  $K_u$ - and  $K_a$ -band satellites seemingly pushes the research focus to Q- (33–50 GHz) and V- (50–75 GHz) frequency bands, which promise extensive spectrum resources. Companies like Boeing, SpaceX, and Telesat plan to explore these bands for the next generation of LEO Internet constellation systems [YWZ<sup>+</sup>23].

According to the overview [YWZ<sup>+</sup>23], analog beamforming plays a dominant role in modern satellite communication systems when a limited number of beams is sufficient. In such systems, the phase shifter remains a key component of the beamforming network, efficiently enabling the beam hopping technique for flexible coverage.

# 1.3 SiGe BiCMOS Technologies in Next-Generation Communication Systems

SiGe BiCMOS technologies made a new turn in the history of IC manufacturing and nowadays are continuously under development. This mixed-device semiconductor process offers simultaneously a superior high-frequency performance of SiGe HBT devices with  $f_t$  and  $f_{\rm max}$  exceeding 300 GHz, as well as integration of a CMOS-based digital logic on a single substrate. The back end of line (BEOL) with large number of available metal layers additionally contributes to highly integrated compact electronic components by allowing a denser routing. Some SiGe BiCMOS technologies provide an option to use slower bipolar transistors with higher breakdown voltage, enhancing power amplifiers' performance. These properties enable a scalable phased array implementation on a single chip. Fully integrated SiGe BiCMOS W-band phased arrays were presented for instance in [LPO+18] and [SHSB19] from IBM and Nokia Bell Labs, respectively, and in [MMM+24] from NXP Semiconductors.

As an alternative, an array performance can be additionally optimized by combining the main advantages of several technologies in one multi-chip system. The main idea is explained in work [RP17]. The SiGe-based beamformer IC is combined with GaAs PA and LNA. Due to the higher breakdown voltage and low-loss substrate, such use of GaAs results in higher output power and lower noise figure (NF), respectively. The authors also present several examples of  $K_u$  and  $K_a$  phased arrays for satellite communication manufactured by Rockwell Collins and Boeing. If the advantages of such multi-chip implementations remain prominent enough at W-band and higher frequencies in the future, considering related packaging challenges, cost, mass volume production and continuous technological developments, is difficult to foresee.

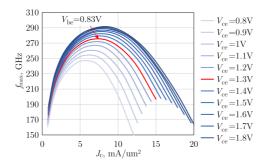

The circuits presented in this thesis are implemented in:

- NXP's high volume 140-nm SiGe BiCMOS process with 6-layer BEOL and  $f_t/f_{\rm max}$  of 280 GHz for high-speed devices (Chapter 2, 3);

- IHP's 130-nm SiGe BiCMOS SG13G2 process with 7-layer aluminum BEOL and  $f_t/f_{\rm max}$  of 300/500 GHz (Chapter 5);

- IHP's 130-nm SiGe BiCMOS SG13G3Cu process with 6 copper and 2 aluminum BEOL layers and  $f_t/f_{max}$  of 470/650 GHz (Chapter 4).

#### 1.4 Structure and Goals of the Thesis

In essence, many weak points in analog beamforming architecture come from the degrading performance of analog circuits at higher frequencies and their challenging design. This is especially relevant for phase shifters, as they are responsible for the complete beamforming functionality of analog and partially of hybrid schemes. Die area consumption is another critical point, as its reduction not only enables a higher level of integration but also directly influences the manufacturing costs, especially noticeable in volume production.

In addition, the antenna elements are normally placed proportionally closer to each other when the operating frequency increases. The spacing of  $\lambda/2$  is often preferred to minimize grating lobes, which at 100 GHz would mean a grid of 1.5 mm. In this space, a full Tx and Rx RF chain (between the power combiner and the antenna), including digital control circuits, memory, etc., should be placed. Therefore, moving forward to sub-THz frequencies, the area consumption of a component becomes a defining factor, since a larger chain might simply not fit between the antenna elements.

This thesis investigates area- and power-reduction strategies for building blocks of phased arrays potentially used in beyond-5G systems both on land and in space.

In Chapter 2, various passive structures are presented with a focus on area reduction. Different implementations of quadrature signal splitters are discussed in detail and several designs are presented. The structures from this chapter are later used as building blocks for the circuits presented in the remaining chapters.

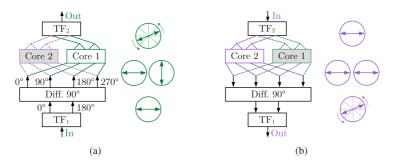

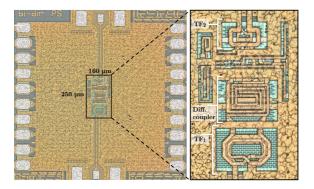

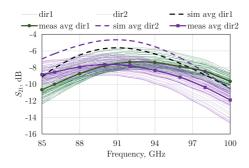

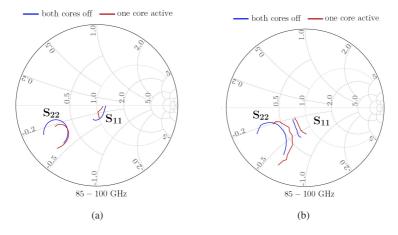

Chapter 3 presents three *W*-band active phase shifters designs. The first design is based on a conventional Gilbert cell and uses a compact vertical differential Lange coupler as an I/Q splitter. The second circuit uses one topology modification to integrate a balun-functionality directly to the core without additional components, thus further contributing to the circuit's miniaturization. The third design concludes the chapter by considering the use of phase shifters in a transceiver, i.e. operating in two directions. This circuit still uses a compact active topology and in addition, adapts one of the main advantages of passive phase shifters, namely their bidirectional operation.

Q- and V-band broadband components for space electronics are demonstrated in Chapter 4. This chapter discusses considerations for an efficient chain design with a focus on high dynamic range. In addition, an effort has been made to reduce the number of circuits in the chain by integrating several functions into one component. Presented designs include a phase shifter that can be simultaneously used as a variable gain amplifier (VGA) and a VGA with an additional equalization function.

Chapter 5 discusses design aspects for low-power operation, especially important for large phased arrays. Two *W*-band LNAs with standard and reduced power consumption are presented to investigate related compromise between performance metrics. A down-converting mixer design with additional image signal suppression is discussed as a low-power and compact alternative to conventional I/Q mixers.

# 2 Miniaturization of Passive Components

The size and number of passive components in a circuit directly impact the overall area consumption. This makes them the first candidate and the lowest hierarchical design level to develop miniaturization strategies. Inductors, couplers, transformers, baluns, power combiners, and other components are typically implemented using conventional geometries based on established design guidelines. However, the availability of multiple metal layers in modern technologies provides flexibility, enabling experimenting with different shapes and orientations.

## 2.1 I/Q Splitters Overview

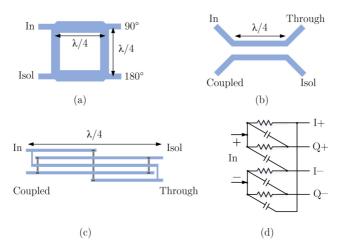

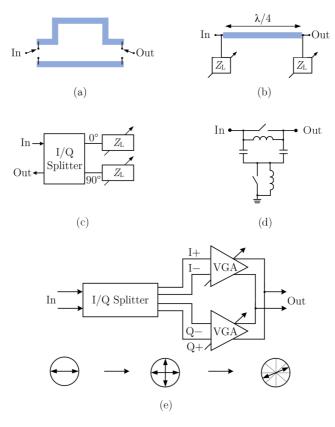

One of the key steps in the phase shifter design is an in-phase and quadrature phase (I/Q) signal generation, required for many topologies. Some conventional passive I/Q splitter implementations are shown in Fig. 2.1.

Branch-line coupler shown in Fig. 2.1a achieves very low insertion loss and is easy to implement. The main disadvantages are the narrow-band response and its physically large geometry. Improved bandwidth and smaller footprint are possible to achieve using a coupled-line coupler, schematically shown in Fig. 2.1b. In this case, to obtain the power splitting with a 90° degrees phase difference two quadrature-wave lines are placed close to each other horizontally thus achieving an edge coupling. Vertical placement of the two lines provides a broadside coupling. By changing the distance between the two lines, one can control the proportion of the power splitting over the two output ports "through" and "coupled". It is common to target a slight over-coupling instead of an ideal 3-dB splitting to enhance the frequency bandwidth. The concept is illustrated in Fig. 2.2.

Figure 2.1: Quadrature signal generation: branch-line coupler (a), coupled-lines coupler (b), Lange coupler (c), polyphase filter (d).

Figure 2.2: Simplified demonstration of an ideal 3-dB splitting (a) and over-coupling (b).

One common difficulty in coupled-line couplers is when for a desired coupling coefficient the lines have to be placed closer than allowed by the design rules of the technology used. This is especially true at mm-wave frequencies. To overcome this limitation, Julius Lange invented in 1969 a coupler as shown in Fig. 2.1c and by now known as the Lange coupler. In essence, the used interdigitated geometry is an evolution of a coupled-line coupler.

The simplified mathematical derivations to describe the Lange coupler function can be found in [KPP78]. They are based on the analysis of the even- and odd-

mode capacitances of the 4-conductor line, starting from a 2-conductor line (or 2-coupled lines). The analysis can be further expanded to an N-conductor line configuration, resulting in the change of the odd-mode capacitance:

$$C_{oN} \approx \frac{C_1}{2} + (N-1)(C_{0o} - C_{0e}),$$

(2.1)

where  $C_{0o}$  and  $C_{0e}$  are odd- and even-mode capacitances of a 2-conductor line, respectively, and  $C_1$  is a total capacitance to ground of an equivalent single microstrip line. For simplicity, the rest of the analysis is left out here. The results show that for the same coupling coefficient in the Lange coupler the lines have to be placed wider apart than in the conventional coupled-line coupler, which solves the forementioned problem with design rules. The Lange coupler exhibits an additional advantage of a wideband frequency performance.

Another passive technique to provide an I/Q signal is to use an RC polyphase filter (PPF). The simplest schematic, namely a one-stage PPF is shown in Fig. 2.1d. One advantage of this topology is its very compact implementation form in silicon. When using multiple stages, it is possible to minimize the gain and phase errors over a large bandwidth, otherwise the performance can only be optimized at a single frequency point. At mm-wave frequencies, the PPFs are not frequently used as an I/Q splitter. Their main disadvantage is the significantly higher insertion loss in comparison with quadrature couplers. In most cases, an additional amplifying stage is required to compensate these losses at the drawback of increased power dissipation and area consumption. Some PPF examples include a wideband ring-shaped two-stage PPF proposed in [MHHP16] operating at 20–50 GHz and a type II two-stage PPF as an I/Q splitter at the input of a 26-GHz vector modulator from [KBKG19]. The abovementioned designs exhibit an insertion loss of 19 dB and 12 dB, respectively. Moving towards higher operating frequencies, the advantage of reduced die area consumption becomes less and less pronounced, since the couplers also become proportionally smaller with increasing frequency while having much smaller insertion loss than PPF.

Other types of I/Q splitters, such as a 90° delay line and a rat-race coupler, were not considered in this overview.

### 2.2 Proposed Quadrature Couplers

Parts of this section include material previously published in [2] and [3].

From the previous overview, both Lange and coupled-line couplers were chosen as the most promising implementations of the I/Q splitter for a W-band phase shifter, as they demonstrate a compromise between the area consumption and insertion loss.

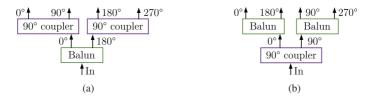

Figure 2.3: Differential I/Q signal generation using quadrature couplers.

Differential vector-sum phase shifters require differential I/Q splitters. To build one using quadrature couplers, two conventional approaches can be employed: using a balun for single-ended to differential conversion followed by two quadrature couplers (see Fig. 2.3a) or using one coupler followed by two baluns (see Fig. 2.3b). Both approaches result in the same set of output phases. However, the first approach allows flexible adjustment from single-ended to differential input by removing the balun. For this reason, this option was ultimately chosen for the proposed designs.

## 2.2.1 Differential Lange Coupler

For many topologies, an I/Q splitter, in any form, is essential for analog phase-shifting functionality and cannot be omitted. In many cases, the coupler occupies more than half of the IC area of an active phase shifter. Therefore, exploring more compact solutions remains crucial. From the discussion above, the first candidate chosen for our compact I/Q splitter is the Lange coupler due to its good compromise between insertion loss, chip area, and bandwidth. To build the complete differential I/Q splitter from Fig. 2.3a, the straightforward implementation would include two couplers placed next to each other, meaning

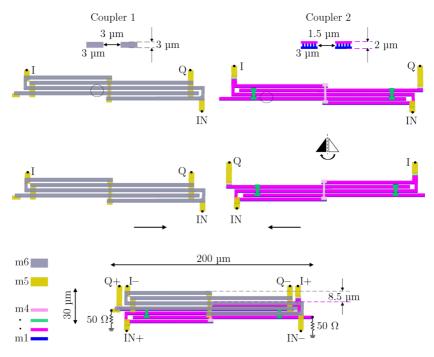

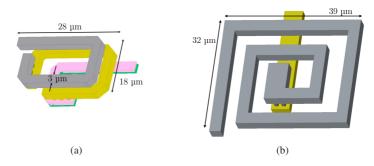

double area and a complicated connection with the succeeding hardware, due to the long shape of the Lange coupler in one direction. However, this thesis explores another approach, shown in Fig. 2.4.

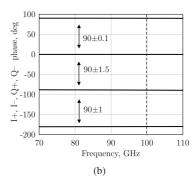

The proposed differential coupler is built in essence by placing the first coupler vertically under the second one, obtaining differential operation for the same footprint. As a first step, couplers 1 and 2 were designed and optimized separately in a 6-metal layer technology. The line width and spacing in coupler 1 is 3  $\mu$ m, following design rules for the upper thick metal layer. Since the thickness of metal layers m1 and m6 is unequal, two stacked thin metal layers (m1 and m2) are used for coupler 2 to partially compensate for the imbalance in ohmic losses and to achieve comparable performance.

Figure 2.4: Differential Lange coupler.

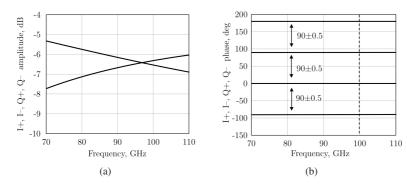

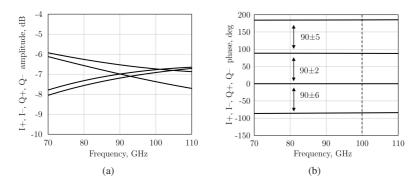

Figure 2.5: Simulated performance of two identical couplers placed next to each other: amplitude (a) and phase (b) response.

As the next design step, the two couplers were placed together and optimized as one differential structure. The main challenge in the layout optimization of such a combined structure is an unwanted broadside coupling between the two couplers. To reduce this interaction, coupler 2 was horizontally flipped relative to coupler 1. For the same reason, only two layers are used for coupler 2. Additionally, a horizontal offset of 8.5  $\mu m$  was introduced to further increase the separation and reduce capacitive coupling between the two couplers. The offset was selected so that most of the lines in coupler 2 were positioned horizontally between the lines of coupler 1, rather than directly aligned underneath them.

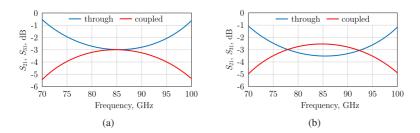

Fig. 2.5 shows the simulated performance of a differential coupler formed by two identical Lange couplers (coupler 1), conventionally placed next to each other. This simulation uses an ideal balun, therefore, in Fig. 2.5a, 6 dB is the splitting loss, and an additional 0.4 dB (at 97 GHz) is the actual added (resistive) loss from the coupler layout. The ideal balun and a separate EM simulation of the identical couplers are also the reasons for four curves overlapping and appearing as two in the plot. Fig. 2.5b shows the relative phase response of the obtained phase states, as well as the maximum phase error between them within 70–100 GHz.

Fig. 2.6, in turn, presents the simulated performance of the proposed differential Lange coupler in its compact vertical implementation. Compared to the results of the conventional implementation, one can observe only 0.1 dB higher

Figure 2.6: Simulated performance of the proposed vertical differential Lange coupler: amplitude (a) and phase (b) response.

insertion loss and a  $0.5-1^{\circ}$  larger phase error. However, this is an expected and acceptable sacrifice for such a significant area reduction of almost 50%.

# 2.2.2 Differential Coupler Based on Spiral Edge-Coupled Lines

If broadband operation is not required and the design rules allow placing metal lines on the chosen layer close enough to each other, the use of a conventional coupled-line can offer more flexibility in terms of chosen geometry than the Lange coupler. Practically speaking, two coupled lines are easier to bend into various shapes to reduce the overall footprint than several interdigitated conductors with multiple connections.

In the next design iteration of a compact differential I/Q splitter, two single-ended couplers based on edge-coupled lines are used and turned into spiral geometries. They are implemented on different metal layers following the above-presented approach, i.e. placed vertically under each another. Coupler 2 is flipped relative to coupler 1 and uses the m1 and m2 layers, as in the previous design. The final geometry is presented in Fig. 2.7. The resulting structure, similar to the previous case, occupies only half the area normally required for two couplers placed side by side. Additionally, the square geometry

Figure 2.7: Differential spiral coupler.

is another beneficial property, as it often enables more convenient integration with other parts of the layout.

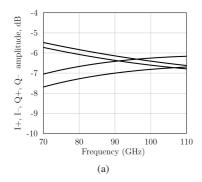

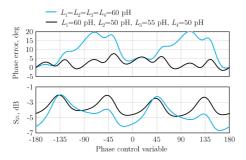

Fig. 2.8 shows the simulated performance of the differential spiral coupler. The structure exhibits 0.5 dB higher insertion loss compared to the differential Lange coupler, presumably caused by folding the lines several times to form a spiral. In addition, amplitude and phase imbalances deteriorate more within the same frequency range. However, such a narrow-band response was expected from the coupled-line coupler.

This example also demonstrates the difficult optimization process with increasing geometry complexity and related performance sacrifices. Nevertheless, these geometrical experiments can lead to effective miniaturization benefits.

Figure 2.8: Simulated performance of the proposed vertical differential spiral coupler: amplitude (a) and phase (b) response.

# 2.3 Inductors and Baluns

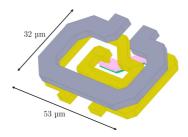

Miniaturization techniques can be applied to other passive components as well. If a high Q-factor of an inductor is not critical, a multi-layer solution was used to reduce area consumption, as in [TIK+22] and [HTAH08]. An example of such an inductor is shown in Fig. 2.9a and was designed for the phase shifter which will be presented in Section 3.3.

The inductor uses two top layers and two thin layers stacked together to reduce the resistive loss of the final turn. An EM-simulated inductance of 130 pH is

Figure 2.9: Multi-layer inductor (a) and conventional inductor (b).

Figure 2.10: Transformer

achieved, with a Q-factor of 9.8 at 100 GHz. Adding more turns using lower thin metal layers is possible, allowing for a more compact design. However, increased resistive losses and reduced distance to the substrate lead to a Q-factor drop from nearly 10 to 8. Additionally, since the smallest turn on the highest metal layers is constrained by design rules, the area reduction achieved with a fourth turn would be minimal and not justify the trade-offs. Consequently, the final design uses three turns. An essential design consideration is maintaining the same signal propagation direction for each turn when transitioning between layers to enhance the structure's inductive behavior. Introducing a horizontal offset between turns can further improve performance by reducing undesired parasitic capacitance.

Fig. 2.9b illustrates an example of a conventional inductor geometry for size comparison. This structure achieves the same inductance of 130 pH with a Q-factor of 12 at 100 GHz. To summarize, the Q-factor drop from 12 to 9.8 corresponds to approximately a 40% reduction in area. It is important to note that this example provides a rough comparison and does not cover all possible geometries, implementations, or technological advancements available in various BEOL processes.

The use of transformers frequently contributes to the area efficiency of a circuit by combining impedance matching and a single-ended to differential conversion in one component. Fig. 2.10 shows one of the transformers used for the circuit to be discussed in Section 3.4. Two turns were used on one of the coils to further reduce the transformer size.

Normally the coupling coefficient degrades with increasing frequency. The coupling can be slightly improved for higher frequencies by, e.g., using sandwich-

Figure 2.11: Marchand balun.

coupled transformers [HMM22], whereas the bandwidth remains rather limited. A broadband alternative for the single-ended to differential conversion among passive structures is a Marchand balun. The balun in Fig. 2.11 was designed for the single-ended version of the phase shifter presented in Section 3.2. It uses the broadside coupling between the lines turned into spirals for a more compact footprint than a conventional straight geometry of the Marchand balun

# 2.4 Conclusion

This chapter presents miniaturization approaches applied to the layout design of I/Q splitters, a critical building block commonly used in phase shifters. Several conventional topologies are discussed in the context of mm-wave operation. The Lange coupler and coupled-line coupler are selected as baseline designs, as at W-band frequencies, they offer a smaller footprint than the branch-line coupler and lower insertion loss than polyphase filters. The objective of this chapter is to reduce the required area for these couplers by utilizing multiple metal layers and the available vertical volume. As a result, the proposed 3D differential Lange coupler achieves a 50% reduction in area with negligible performance degradation compared to two separate single-ended Lange couplers. An alternative design, the 3D spiral-shaped coupled-line coupler, occupies slightly less than 50% of the area of the previous design but at the expense of more significant phase and amplitude imbalances. The chapter also briefly discusses other passive structures, such as inductors, transformers, and baluns, and their role in area reduction.

# 3 W-Band Vector-Sum Phase Shifters for Phased Arrays

W-band phased arrays employing RF beamforming are in focus for the future terrestrial 6G systems development, as discussed in Chapter 1. The beam steering functionality of such arrays is critically dependent on the phase shifter design, which is the primary focus of this chapter.

## 3.1 Architectures and Definitions

# 3.1.1 Beam Squint in Phase-Based Beam Steering

To better understand the necessary hardware for a beam steering functionality, it is important to consider a more general principle of operation of phased arrays in terms of the instantaneous (or signal) bandwidth. Using the same example of the uniform linear array from Section 1.1.1, its array factor can be expressed as [Hau19]:

$$AF = \sum_{n=1}^{N} e^{j2\pi(n-1)\frac{d}{c}(f\sin\theta - f_c\sin\theta_s)},$$

(3.1)

where  $f_c$  denotes the center frequency, d – the distance between two antenna elements, N – total number of antenna elements,  $\theta$  – the angle of the wavefront and  $\theta_s$  – desired beam direction.

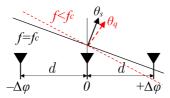

In case  $f = f_c$ , the phase difference of  $\Delta \varphi = \frac{2\pi f_c}{c} d\sin\theta_s$  applied to the neighboring elements will make the beam point to  $\theta_s$ . If  $f \neq f_c$ , then with the same phase settings, the beam will deviate or squint from the target direction  $\theta_s$  to  $\theta_q(f) = \sin^{-1}(\frac{f_c}{f}\sin\theta_s)$ . This mechanism is illustrated in Fig. 3.1 [Mai94].

Figure 3.1: Beam squint during the phased array operation not at the central frequency  $f_c$ .

The acceptable level of beam squint for a system defines what signal bandwidth can be approximated as "narrow" or quasi-monochromatic. One commonly used criterion is derived from the concept of an array "fill time" [Mai94] at its largest scan angle. The array is minimally "filled", if a leading edge of a short pulse  $\tau_{\min}$  arrives at the last antenna element, while a trailing edge hits the first antenna element. Therefore,

$$B_s = \frac{1}{\tau} \le \frac{c}{Nd\sin\theta_s},\tag{3.2}$$

where  $B_s$  is the signal bandwidth,  $\tau$  is the corresponding pulse duration and other variables are the same as in (3.1).

If the condition above is not satisfied, a pulse dispersion occurs leading to an increased bit error rate of digitally modulated signals.

Apart from the instantaneous signal bandwidth, the system or operational bandwidth is influenced by many other factors, such as mutual coupling between the elements, the bandwidth of each antenna and the remaining hardware [Hau17].

To mitigate the beam squint and ensure the broadband operation of a phased array without losing its beamsteering precision, a general solution is the use of true-time delay units (TTD). The phase shift is exactly proportional to the frequency and translates to a perfectly flat frequency response of the group delay.

One of the conventional implementations of a TTD includes time delay elements, e.g., multiple transmission lines of different lengths, with switches in between and additional equalizers to compensate for increasing insertion loss over frequency. High complexity and significant area consumption are the main drawbacks fundamentally inherent to TTD. In the literature, no publicly

available examples of W-band TTDs were found. The only available design in the D-band with sufficient maximum delay is presented in [KEKM20]. The circuit covers the 3-dB bandwidth of 60 GHz and provides 16 delay settings, which is equivalent to a phase shifter with a 4-bit phase resolution. Let us consider the work [RGB+21] for a very approximate size comparison. It presents a D-band active phase shifter design with a 5-bit phase resolution and 20 GHz of bandwidth. The first and latter circuits occupy 1.16 mm<sup>2</sup> and 0.05 mm<sup>2</sup>, respectively. This example demonstrates a very high price for wideband operation, namely in this case, about a 23 times area penalty. On the other hand, the discussed TTD is based on the conventional topology with a separate delay stage per bit. An alternative approach was presented for a lower operating frequency range but resulted in a more compact footprint. Work [MLM14] demonstrated continuous delay control by separating stages for coarse switching and analog fine-tuning, resulting in an area of only 0.22 mm<sup>2</sup>. Although significant miniaturization is achieved, the area of 0.22 mm<sup>2</sup> does not include a potentially required amplification stage to compensate for the 15-dB insertion loss of this circuit, as reported at 30 GHz.

For many integrated systems the use of such a bulky component at every antenna element is not an option. The use of the phase shifters is therefore frequently a preferred solution for the majority of narrow-band phased arrays with analog or hybrid beamforming schemes. An alternative solution to reach a compromise between wider bandwidth and a relatively compact system is shown in Fig. 3.2. Such hybrid phased array uses TTD only for the coarse delay control at the common legs of the sub-arrays, whereas a finer phase tuning is

Figure 3.2: An example of a hybrid phased array as a compromise between time-delay-based and phase-shift-based arrays.

done by the phase shifters within each sub-array. The beam squint is also less critical for the individual sub-arrays due to their wider beamwidth. However, the final architecture choice and the feasibility of such trade-offs are defined by the application requirements.

This research work focuses on phase-shifter-based beamforming networks, whereas more information on TTD can be found in [Ma16].

# 3.1.2 Phase Shifter Topologies

Phase shifter as a building block allows for a large variety of possible implementations that exhibit different limitations depending on e.g. operating frequency, phase control range and resolution, area and linearity requirements. Several examples are presented in Fig. 3.3.

Switched-line and loaded-line topologies (shown in Fig. 3.3a,b) belong to well-known passive switchable solutions. They are easy to implement and use a straightforward principle of operation. However, in a single stage implementation, these topologies cannot provide the entire 360° phase shift range. Multiple stages combined could potentially do this, but achieving high phase resolution requires a large number of various passive structures and switches in between. Such solutions present therefore the highest area consumption and insertion loss.

Reflection-type phase shifters (RTPS) (shown in Fig. 3.3c) use a different principle of operation and provide continuous phase control by using two tunable loads connected to the conventional output ports of a  $90^{\circ}$  coupler. The output signal in this case is taken from the isolated port of the coupler. The main challenge of an RTPS is achieving the wide phase shift range which requires a more complex reflective load, such as in [GN17] or the use of additional phase shifting stages. This topology is especially popular in K and  $K_a$  frequency bands, where passive structures are more compact than at lower frequencies. At higher frequencies the RTPS exhibits higher insertion loss than other implementation forms, however, a few examples can be found for V-band, e.g., [LW18].

As a 1-bit phase-shifting stage, various switched-filter networks can be employed. One of the many possible implementations is illustrated in Fig. 3.3d.

Figure 3.3: Phase shifter architectures: switched-line (a), loaded-line (b), reflection-type (c), switched-filter, and vector-sum (e) topologies.

This type of phase shifters, similar to switched-line and loaded-line topologies, suffers from an increased insertion loss when aiming for a high phase resolution but offers a larger bandwidth.

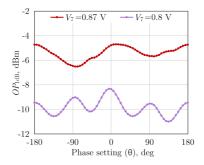

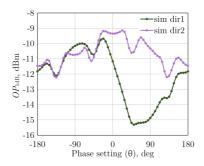

Finally, the vector-sum architecture is an active topology, which is frequently used in beamforming networks of phased arrays. The block-diagram as shown in Fig. 3.3e explains the principle of operation. After providing the differential input signal to the I/Q splitter, a differential I/Q signal is obtained, achieving four critical phase points, namely  $0^{\circ}$ ,  $90^{\circ}$ ,  $180^{\circ}$  and  $270^{\circ}$ . These points are

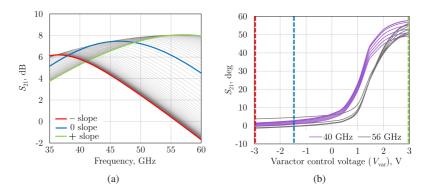

necessary to potentially reach a  $360^\circ$  phase range through the vector summation in all four quadrants. The VGAs in the I- and Q-path ensure the required amplitude weights for the desired signal at the output. The implementation of the VGAs, especially their gain control circuitry and its tunability, defines the maximum achievable phase resolution. The vector-sum architecture can also be adapted as a passive phase shifter by replacing the VGAs with attenuators, as proposed in [ZYG+23].

When moving to W-band frequencies, the implementation of a phase shifter becomes considerably challenging. Both passive and active solutions exhibit various limitations thus making the choice between them not obvious. Active implementations introduce either some gain or significantly lower loss compared to passive alternatives while having the most compact layouts ([LCHH20], [ZWL+23]). Passive phase shifters become smaller as the frequency increases and provide inherently high linearity, but their losses also increase, especially for high resolution, and require additional amplification. This in turn limits the linearity compared to a fully passive implementation, increases the overall die size and eliminates the attractive feature of reduced power consumption. As an example, the passive phase shifter in [WYW<sup>+</sup>22], based on switched networks, has an 18-dB average loss for a 6 bits phase resolution. Another recent work [GYA+24], proposes a W-band passive phase shifter with a combined architecture that incorporates two filter-based phase shift stages, an RTPS and a delay line. This implementation achieves an average insertion loss of 14.61 dB at 96 GHz and occupies an area of 0.22 mm<sup>2</sup>. Another alternative could be a hybrid approach as a trade-off between linearity, phase-shift range, and phase-shifter loss. An example is demonstrated in [NVGS+15] and named a "cascaded active-passive phase-shift approach".

Apart from the overall fabrication costs increasing with the IC area consumption, limited spacing between antenna elements in arrays makes the area constraint non-negotiable in many cases. Because of the above-mentioned reasons, various hybrid implementations as well as fully active phase shifters become dominant in *W*-band. Instead of diving into a wide variety of component combinations and building a complex multi-stage phase shifting system, in this thesis, the preference is to explore the full potential of a single active phase shifter.

#### 3.1.3 Performance Metrics

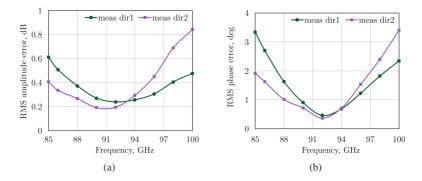

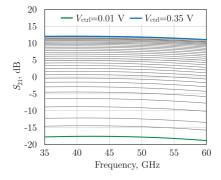

In this thesis, a phase shifter with a phase resolution of 6 bits in the  $90-100\,\mathrm{GHz}$  frequency range was specified as design goal. These requirements were derived from a 6G mm-wave infrastructure communication system. The most critical performance metrics for this particular phase shifter include:

• Discreet phase control with a finite **resolution** *N* is a simpler and cheaper approximation of a desired continuous linear phase gradient. Reducing the phase shifter resolution leads to an increased pointing error

$$\frac{\Delta\theta}{\theta_{3dB}} = \frac{\pi}{4} \frac{1}{2^N} \tag{3.3}$$

and causes quantization sidelobes with  $P_{QL} = -6N$  dB [Mai94]. Various research activities aim to reduce these effects, e.g. using a two-dimensional quantization algorithm proposed by [HMB14]. As stated, 6 bit resolution is the requirement leading to  $5.625^{\circ}$  phase resolution.

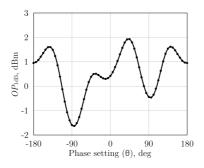

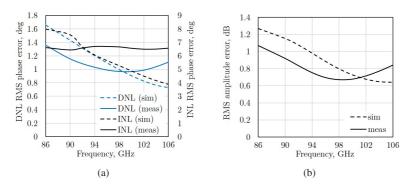

- Amplitude RMS error represents the undesired amplitude variation across different phase states. The metric is calculated as a root-meansquare of the amplitude deviation for each state from the average amplitude.

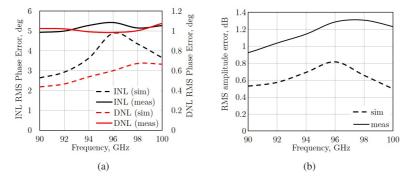

- Phase RMS error has two definitions commonly used as the industrial standards in the field of mm-wave 6G systems. An integral nonlinearity (INL) definition defines the error in comparison to an ideal set of phase values. INL RMS phase error eventually represents full accumulated phase error across all states and is conventionally used as the phase RMS error definition in the literature. Another definition namely differential nonlinearity (DNL) RMS phase error is calculated as an average error between each state and the previous one and describes the phase shifting monotonicity.

Derived from the 6G system, the target amplitude RMS error and phase INL RMS error are in the range of 1 dB and 2°, respectively, across the frequency band.

The importance of amplitude and phase error assessment is caused by the overall performance degradation of the full array in the presence of such errors. Several examples include angle estimation degradation [Esc22], array gain reduction, as well as a negative impact for the null-steering of adaptive arrays leading to the worse interference rejection [BJ09] independent of the number of antenna elements.

The next performance characteristics are not specific to the phase shifters but are rather standard for most of the IC components. In this work, the aim was to generally optimize the designs to achieve a trade-off between the belowmentioned metrics.

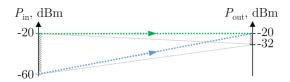

- Power consumption of the individual phase shifter is less critical, compared to a PA that dominates in the chain in this regard. However, in an array, it is multiplied by the number of elements and thus every milliwatt can grow into a significant power dissipation if this number is very large. The most obvious practical disadvantages from the user perspective are stricter requirements for a power supply and increased operating expenses [MOM+20]. From a system design point of view, high power consumption creates significant challenges for heat dissipation components. An overheating affects the performance of electronic components and thus the entire system. Mechanical damage, i.e. bending the antenna plane due to thermal issues, will negatively influence the array beam steering capabilities [CHFX09].

- Noise figure (NF) of the vector-sum phase shifters is inherently increased by the splitting loss at the input and the insertion loss of the I/Q splitter. This is less problematic for an RF-beamforming receiver, as the phase shifter is located directly after the LNA and therefore presents a reduced noise contribution to the chain, if the preceding gain is high enough. The NF specifications on the transmitter side, in turn, imply stricter requirements for the phase shifter, even though the acceptable Tx NF is higher. The signal amplification by the PA occurs at the output, therefore the preceding components do not suppress the phase shifter noise presented to the chain. This is especially evident if the phase shifter or the remaining components additionally provide a gain control (attenuation), which is mostly the case in practice. This aspect is further discussed in Chapter 4.

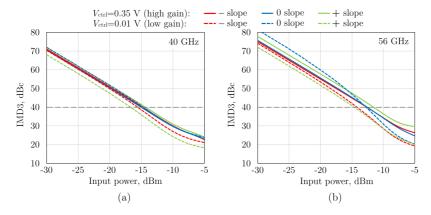

• Linearity of a system defines the upper limit of its dynamic range and is often expressed in terms of the third-order intermodulation distortion (IMD3) or third-order intercept point (IP3) that eventually translates into an error vector magnitude (EVM) constraint. Considering linearity from a compression point of view, described by the 1-dB compression point (IP<sub>1dB</sub> or OP<sub>1dB</sub>), helps to understand the fundamentally different requirements for the phase shifter operating in Rx and Tx direction. The input signal amplified by the LNA can compress the phase shifter as the next component in the Rx chain. In the Tx chain, the signal amplification occurs after the phase shifter, therefore, the IP<sub>1dB</sub> requirements can be more relaxed. In this chapter, the target OIP3 is set to 7 dBm.

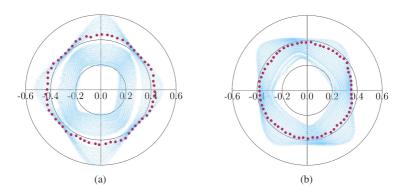

# 3.2 Gilbert-Cell Based Phase Shifter

Parts of this section include material previously published in [3].

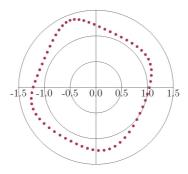

Based on the previously presented topology overview, the the vector-sum architecture is selected as the most suitable candidate for a compact implementation of a 6-bit phase shifter in one stage. In this topology, the gain of the VGAs in I- and Q-branches is set proportionally to  $\cos\theta$  and  $\sin\theta$ , respectively, where  $\theta$  is the desired phase of the output signal. Theoretically, this ensures a constant amplitude across all settings as the resulting amplitude after the vector summation is proportional to  $\sqrt{\cos^2\theta + \sin^2\theta} = 1$ , i.e. independent of the phase, whereas the resulting phase is equal to the desired phase:  $\varphi = \tan^{-1}\left(\frac{\sin\theta}{\cos\theta}\right) = \tan^{-1}(\tan\theta) = \theta$ .

The VGAs needed in the vector-sum phase shifter architecture can use various topologies, such as the Gilbert cell topology [GKR13a], [ZGKR+16], and a current-steering cascode topology [PZ17], [WGMKB18]. In this thesis, the Gilbert cell topology has been used as baseline. Several promising modifications will be introduced, starting from the miniaturization of passive structures and moving to more pronounced topology adjustments. The corresponding designs are presented in detail in the following sections.

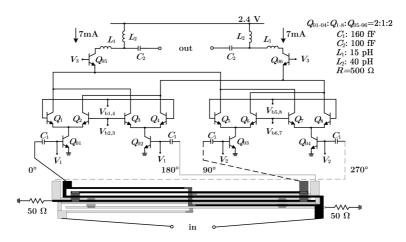

# 3.2.1 Circuit Description

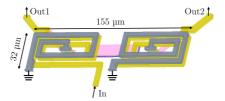

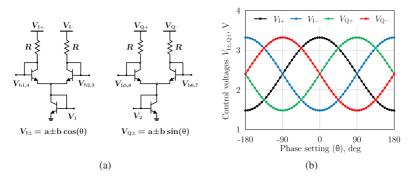

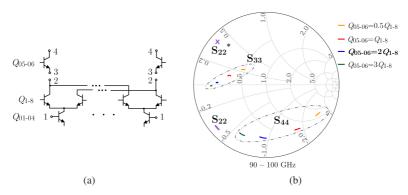

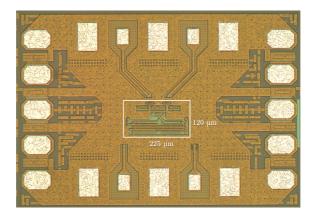

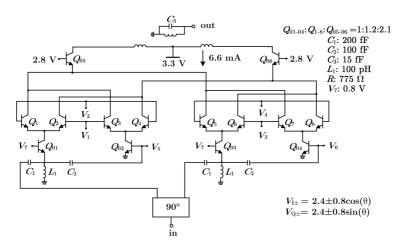

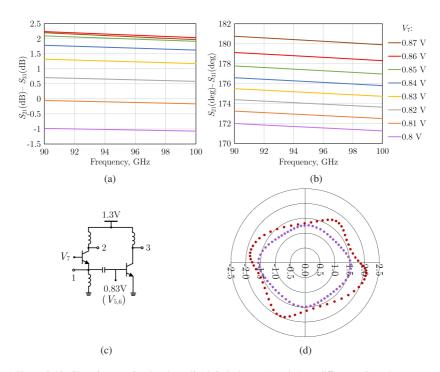

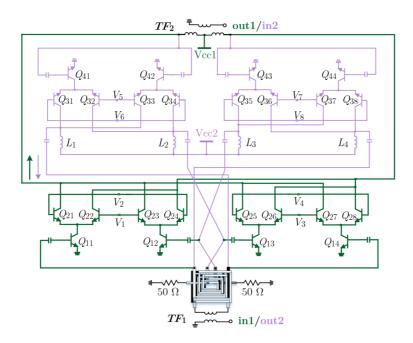

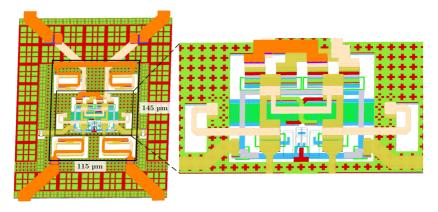

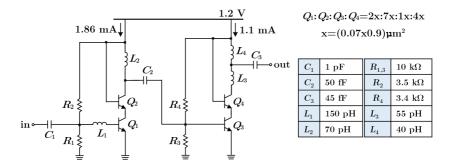

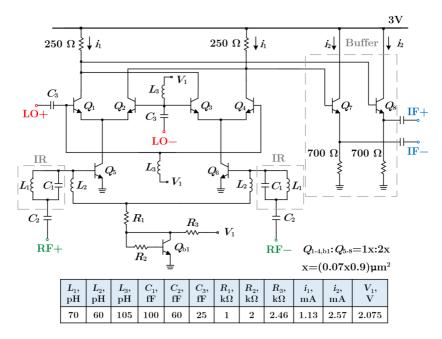

In the first vector modulator implementation, two Gilbert cells are formed by transistors  $Q_{01-04}$  and  $Q_{1-8}$ , as shown in Fig. 3.4. Decoupling capacitors are not shown in the schematic for simplicity but are included at the supply voltage Vcc and bias voltage  $V_3$ . Besides, available spacing on the die between DC pads is used for extra decoupling.

Figure 3.4: Simplified schematic. [3] ©IEEE

#### **Phase Control**

The circuit operation is based on a current-steering architecture. By varying  $V_{\rm b1-8}$ , one can control current steering between all  $Q_{\rm 1-8}$  transistors and thus ensure that the required portions of each input signal (for vector summation) reach the output.

The phase shifter uses the differential Lange coupler discussed in Chapter 2 (Fig. 2.4) as an I/Q splitter. This leads to an overall area reduction compared to conventionally used two single-ended couplers placed next to each other.

Currents flowing through the  $Q_{1-8}$  transistors must satisfy cos- and sin- functions in a differential way as discussed previously. The design goal is achieving

Figure 3.5: Bias networks (a) and phase control voltages (b).

a perfect 360° circle in the I-Q plane with constant amplitude for all phase states in an ideal case. The final implementation involves an integration of digital-to-analog converters (DAC) for the phase control, leading to the 6 bit resolution as discussed in section 3.1.3. As the digital part of the design is rather straightforward, this was not the objective of this work and therefore not implemented. In addition, certain measurement flexibility was needed for the prototype testing and potential troubleshooting.

As a temporary solution, the bias networks shown in Fig. 3.5a have been used for the analog control. The networks use a current mirror topology to copy the control currents to transistors  $Q_{1-8}$ . At a later stage, the ideal current sources on the schematic level were replaced by a combination of control voltages  $V_{\rm I,Q\pm}$  and resistors R. Such transition from current to voltage control helps to simplify chip characterization by allowing the use of a programmable source measure unit (SMU) for automated measurements. Fig. 3.5b shows the abovementioned control voltages for every phase setting in the  $360^{\circ}$  range assuming the 6-bit resolution.

Figure 3.6: Quad transistors  $Q_{1-8}$  from Fig. 3.4 and the used notations for the current steering simulation.

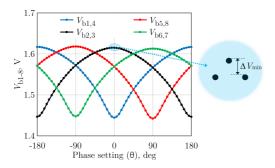

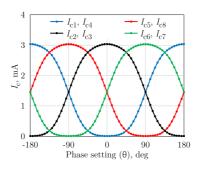

Fig. 3.6 explains the used notations in the current steering simulation. The temporary bias networks translate voltages to the  $Q_{1-8}$  base voltages  $V_{b1-8}$  (Fig. 3.7) to obtain the collector currents  $I_{c1-8}$  as shown in Fig. 3.8.

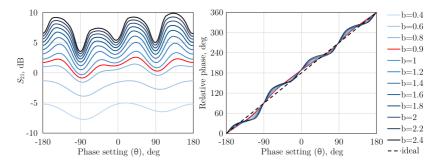

As mentioned above, in a practical scenario, the currently used bias network will be replaced by DACs, therefore the DAC has to be able to supply bias voltages directly at  $V_{b1-8}$ , according to Fig. 3.7. The phase resolution limitation, in this case, comes from the regions where the points are located more densely, e.g., as shown in the same figure.  $\Delta V_{min}$  sets thus the resolution requirement on the DAC. From this simulation, for the 6-bit phase shifter, the required range of voltages is from 1.44 V to 1.62 V with the smallest step of 1 mV. This can be achieved for example by a DAC supplying from 0 to 2.5 V with 12-bit resolution, being a common specification for a static DAC.

Figure 3.7: Base voltages of  $Q_{1-8}$  and phase resolution limitation.

Figure 3.8: Collector currents of  $Q_{1-8}$ .

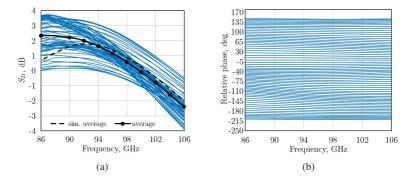

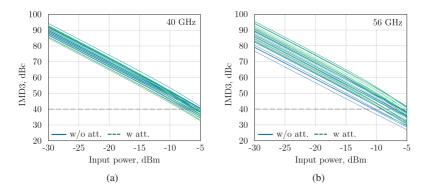

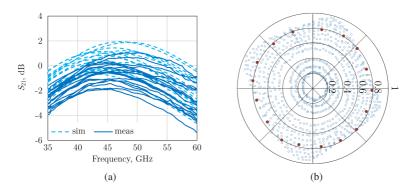

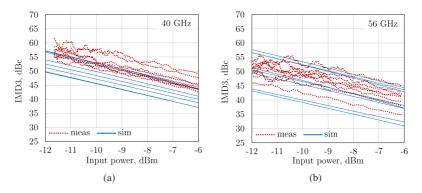

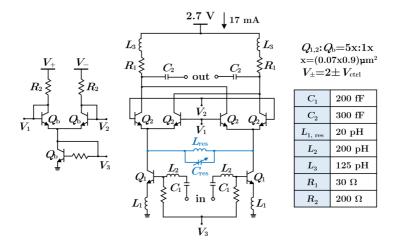

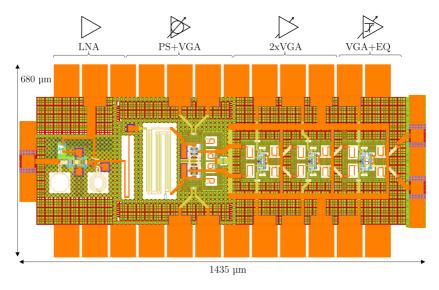

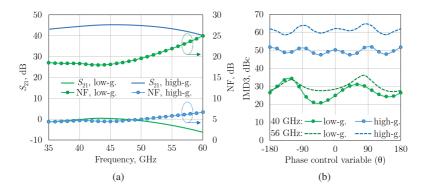

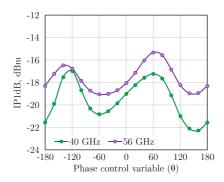

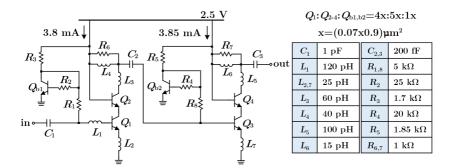

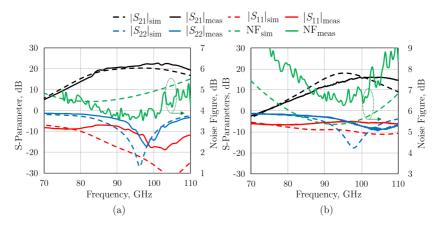

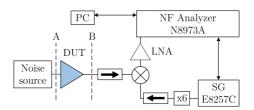

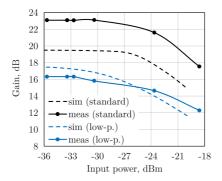

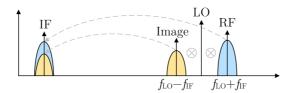

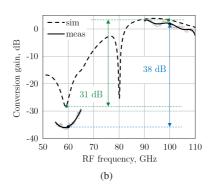

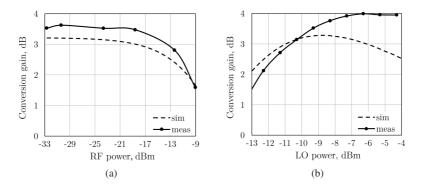

Figure 3.9: Choosing *b* coefficient in phase control equations.