# A Compact 238–278-GHz Frequency Sextupler Based on a Single Bootstrapped Gilbert Cell

Matthias Möck<sup>®</sup>, Graduate Student Member, IEEE, Kaan Balaban<sup>®</sup>, Graduate Student Member, IEEE, and Ahmet Cağrı Ulusoy<sup>®</sup>, Senior Member, IEEE

Abstract—We present an integrated frequency multiplier-bysix (sextupler) for signal generation at J-band (220–325 GHz) frequencies. Typically, multiplication-by-six in state-of-the-art designs is achieved by cascading frequency tripler and doubler circuits. In contrast, we propose to accomplish the multiplicationby-six in a single bootstrapped Gilbert cell (BGC) by leveraging odd-harmonic generation in the transconductance stage and self-mixing in the switching quad. A circuit analysis of the harmonic generation and mixing mechanisms is presented and verified through simulations. The sextupler is combined with a balance-compensated transformer (TF) balun at the input and a cascode amplification stage to increase the output power. As proof-of-concept, a prototype is fabricated in an advanced 130-nm SiGe BiCMOS technology with a core area of only 0.06 mm<sup>2</sup>. The circuit demonstrates a measured peak conversion gain (CG) of 7 dB and output power of up to 4.3 dBm at 257 GHz with a dc power consumption of 119 mW, resulting in a leadingedge dc-to-RF efficiency of 2.2%. All undesired harmonics are suppressed by more than 20 dBc over the entire 3-dB bandwidth, ranging from 238-278 GHz. Compared to recently published silicon-based frequency sextuplers operating at similar frequencies, our proposed single-stage approach results in a significant reduction of dc power and silicon area, while maintaining a superior dc-to-RF efficiency and competitive output power.

*Index Terms*— Efficiency, frequency multiplier, harmonic suppression, *J*-band, millimeter-wave (mm-wave), multichannel, self-mixing, SiGe BICMOS, signal generation.

#### I. INTRODUCTION

SILICON technologies offer low cost, high-level integration, and have become the dominant choice to exploit the large bandwidth and small wavelength available at millimeterwave (mm-wave) frequencies. Recent technological advances have pushed the transit frequency ( $f_T$ ) and maximum oscillation frequency ( $f_{MAX}$ ) of silicon-based transistors beyond 500 and 700 GHz, respectively [1], driving research toward higher frequency bands such as J-band (220–325 GHz). Single-channel J-band transceivers have already been demonstrated for various radar applications using silicon [2], [3], [4].

Received 17 September 2024; revised 16 November 2024 and 11 December 2024; accepted 17 December 2024. This work was supported by the Deutsche Forschungsgemeinschaft (DFG, German Research Foundation) – SFB 1527/1 – Project-ID 454252029. (Corresponding author: Matthias Möck.)

The authors are with the Institute of Radio Frequency Engineering and Electronics (IHE), Karlsruhe Institute of Technology (KIT), 76131 Karlsruhe, Germany (e-mail: matthias.moeck@kit.edu).

Color versions of one or more figures in this article are available at https://doi.org/10.1109/TMTT.2024.3520824.

Digital Object Identifier 10.1109/TMTT.2024.3520824

Current research focuses on multichannel systems, such as phased array [5] and multiple-input-multiple-output (MIMO) architectures [6], which offer improved angular resolution, beamforming, and spatial diversity. A multichannel architecture is also advantageous for high-power signal generation, where combining transmit (TX) channels increases effective isotropic radiated power (EIRP) [7]. In the project underlying this work, the goal is to develop a transmitter operating at 260 GHz, employing at least 2 × 2 parallel TX channels for use in a nuclear magnetic resonance experiment.

A major challenge in *J*-band systems is to provide a signal source with low phase noise and a wide tuning range. Fundamental operation of voltage-controlled oscillators (VCOs) or phase-locked loops (PLLs) at *J*-band is difficult due to low quality factors, increasing impact of parasitics [8], and limited operating speed of silicon-based dividers [9]. As a result, VCOs or PLLs are often operated at lower frequencies, with frequency multipliers used to generate the *J*-band signal [2], [3], [4], [5], [6], [7]. The planned transmitter foresees a multiplication factor (MF) of six, leading to an operating frequency of the signal source below 50 GHz, allowing either on-chip realization or the use of a laboratory signal generator.

Another obstacle in multichannel chips is that they usually feature a central local oscillator (LO) distribution network. LO distribution after the multiplier and operating directly at *J*-band is not feasible due to multiple reasons. First, transmission line lengths become comparable to the wavelength, thus exhibiting excessive loss and sensitivity to impedance transformation. Second, additional amplification to compensate for the passive loss is inefficient at *J*-band due to limited device gain at these frequencies. Therefore, the preferred approach is to distribute signals at lower frequencies and use a frequency multiplier in each channel [3], [4], [5], [6], [7]. However, this increases the importance of a compact form factor and high efficiency of the multiplier to minimize footprint, power consumption, and heat generation in solid-state implementations.

We introduce a J-band frequency multiplier-by-six (sextupler) aiming to address the stringent requirements in multichannel systems. In Section II, we present a comprehensive state-of-the-art review of mm-wave multipliers, highlighting that frequency sextuplers mainly rely on the robust but area- and power-inefficient approach of cascading triplers and doublers. In this work, we propose to replace the cascaded approach by a single-stage solution to perform the

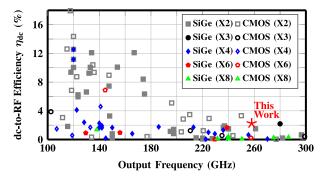

Fig. 1. State-of-the-art summary of silicon-based millimeter-wave frequency multipliers above 100 GHz.

multiplication-by-six on a significantly smaller form factor and with a superior efficiency than prior art. A detailed circuit analysis of our proposed single-stage sextupler follows in Section III, and the experimental results of our fabricated prototype are discussed in Section IV of this work.

#### II. REVIEW: MILLIMETER-WAVE MULTIPLIERS

In general, frequency multipliers generate higher order harmonics  $n \cdot f_0$  ( $n = 2, 3, \ldots$ ) of input frequency  $f_0$  by leveraging device nonlinearity or waveform clipping, with a filter or injection-locked oscillator selecting the target harmonic. Injection-locked multipliers require only low power of the injected signal near the oscillator's self-oscillation frequency, but they usually suffer from a narrow locking range [10], [11], [12] and are not considered in this work, which focuses on non-injection-locked approaches. Key performance metrics of mm-wave multipliers are output power, conversion gain (CG), harmonic rejection ratio (HRR), and dc-to-RF efficiency

$$\eta_{\rm dc} = P_{\rm out}/P_{\rm dc} \tag{1}$$

where  $P_{\text{out}}$  is the output power at the desired harmonic and  $P_{\text{dc}}$  the applied dc power. Fig. 1 summarizes state-of-the-art silicon-based multipliers above 100 GHz, showing a clear trend of decreasing  $\eta_{\text{dc}}$  with rising frequency. We next review common circuit topologies and recent strategies for miniaturization and efficiency enhancement.

# A. Frequency Doublers and Triplers

There are two main categories of doublers. The first is pushpush (PP) doublers, including a pair of transistors combining even-order harmonics, while odd-order harmonics ideally cancel each other out. PP doublers are widely used at mm-wave frequencies [13], [14], [15], [16], [17], [18], [19], [20], [21], but provide only single-ended output. The second group leverages the Gilbert cell (GC) as a four-quadrant multiplier to generate the second harmonic by self-mixing of the input frequency. In [22], a modified version, the so-called bootstrapped Gilbert cell (BGC), has been proposed. Unlike the standard GC, where the input signal directly drives the switching quad, the BGC's quad is fed from the transconductance  $(g_m)$  stage's output. This bootstrapping technique enhances input impedance, CG, and output signal balance [22], [23].

Frequency triplers are commonly implemented as over-driven differential amplifiers [24], [25], [26], or they leverage the enhanced second-order nonlinearity by using a doubler followed by a mixer [27], [28] to produce a  $3 f_0$  output signal by mixing the input signal with the output signal of the doubler.

# B. Higher Order Multipliers

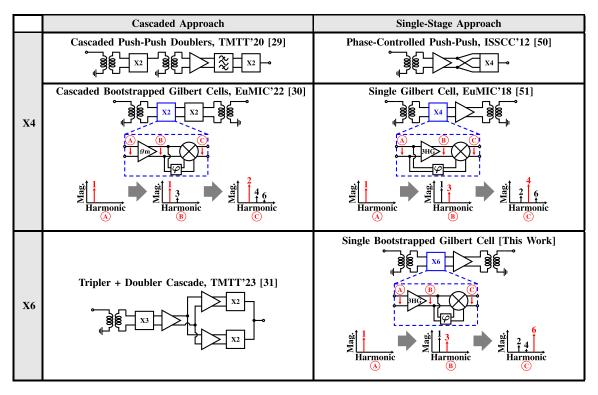

Higher MFs > 3 are usually achieved by cascading doublers (X2) and triplers (X3). Fig. 2 shows popular cascaded approaches for quadruplers (X4) and sextuplers (X6) in the left column. The X4 in [29] employs two cascaded PP doublers with interstage balun and bandpass filter for enhanced HRR, but needs an amplifier to compensate for interstage loss. In [30], the interstage balun is eliminated by using BGC-based doublers with differential output. The  $f_0$  input signal is applied to the  $g_{\rm m}$  stage, and its output current feeds the quad stage generating the second harmonic through self-mixing. However, each BGC requires long transmission lines to shift the phase  $(\varphi)$  between RF and LO inputs to optimize CG and suppress dc self-mixing components [23]. Similar limitations are seen in prior-art sextuplers. The X6 in [31] combines a tripler with multiple amplifiers to feed a final doubler stage, using two-way power combining to counter the single-ended PP output, though at the expense of increased power and silicon area. Comparable architectures are used in [32], [33], [34], [35], [36], [37], and [38]. Higher factors (MF = 8 [39], [40], [41], MF = 9 [42], [43], [44], and beyond [27], [45], [46], [47], [48], [49]) are achieved using similar cascaded methods but typically at the cost of power and area efficiency, limiting their use in multichannel systems.

To address this issue, several studies have proposed higher order multiplication in a single stage, as shown in the right column of Fig. 2. Wang et al. [50] suggest replacing the PP doubler cascade with a phase-controlled PP cascode to extract the fourth harmonic, reducing form factor and improving  $\eta_{\rm dc}$  but retaining single-ended output. In [51], X4 multiplication is demonstrated in a single GC by using the  $g_{\rm m}$  stage as third harmonic generator (3HG), which mix with the  $f_0$  input signal in the quad (see concept in Fig. 2). While the available single-stage studies are mostly limited to MF = 4, only few examples are available for higher MF. In [52], waveform clipping in a cascode amplifier is proposed to achieve X4, X6, or X8 multiplication, but output power and efficiency remain low at 180 GHz ( $P_{\rm out} = -6$  dBm,  $\eta_{\rm dc} = 0.32\%$ ).

In summary, prior art mainly relies on robust but inefficient cascaded approaches for higher order multipliers, while no promising single-stage solutions are yet available for the target MF = 6. This work proposes to combine the advantages of the bootstrapping technique with the self-mixing concept to demonstrate a highly compact and power-efficient X6 multiplication in a single BGC. As illustrated in Fig. 2 (bottom right), the  $g_{\rm m}$  stage is used as 3HG stage, and the bootstrapped topology enables efficient self-mixing of the third harmonic in the quad, producing the sixth harmonic without extra cascaded multiplication stages. Compared to a PP doubler, which typically requires an additional driver stage at these

Fig. 2. Evolution from conventional cascaded to single-stage approach for prior-art frequency quadruplers and proposed frequency sextupler.

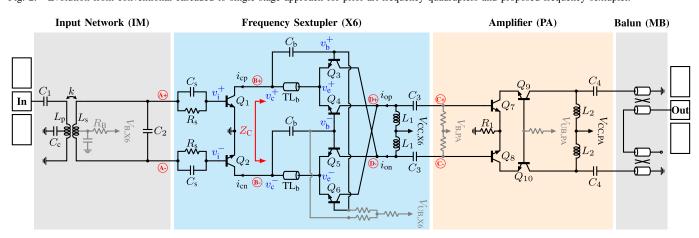

Fig. 3. Circuit schematic of the frequency sextupler.

frequencies [17], [18], [19], [20], [21], the BGC quad benefits from enhanced CG and can be driven directly by the output current of the 3HG stage. To our knowledge, this is the first use of a single bootstrapped GC for higher order multiplication. Our design achieves a measured output power of 4.3 dBm at 257 GHz with the smallest core area of 0.06 mm<sup>2</sup> and highest reported dc-to-RF efficiency of 2.2% for silicon-based sextuplers at J-Band frequencies up to date.

#### III. CIRCUIT DESIGN

The prototype circuit is designed in IHP's advanced 130-nm SiGe BiCMOS technology SG13G3. This technology features heterojunction bipolar transistors (HBTs) with  $f_{\rm T}/f_{\rm MAX} = 470/650$  GHz, which are scalable in discrete values via the finger count  $N_x$ , each having a size of  $70 \times 900$  nm. The collector–emitter (BV<sub>CEO</sub>) and collector–base (BV<sub>CBO</sub>)

breakdown voltages are specified with BV<sub>CEO</sub> = 1.5 V and BV<sub>CBO</sub> = 3.8 V, respectively. The process offers an eight-layer metal stack from X-FAB including four thin (M1–M4) and two 3.2  $\mu$ m-thick (ThCu1, ThCu2) copper layers, as well as one thin (ThinAl) and one 2.8  $\mu$ m-thick (ThickAl) aluminum top layer. Metal–insulator–metal (MIM) capacitors with 2 fF/ $\mu$ m<sup>2</sup> are available between both aluminum layers. Further, salicided and unsalicided polysilicon resistors as well as MOS varactors can be used. The complete circuit diagram of our proposed frequency sextupler is given in Fig. 3. The circuit is divided into four main parts (IM, X6, PA, MB), which are analyzed in detail in the sections below.

#### A. Single-Stage Bootstrapped Frequency Sextupler

The following circuit analysis of our proposed frequency sextupler concept refers to Fig. 3. The sextupler topology is

a BGC. Transistors  $Q_{1-2}$  form a transconductance  $(g_m)$  stage and their collector currents  $(i_{cp}, i_{cn})$  become emitter currents of the quad devices  $Q_{3-6}$ . The  $R_s$ - $C_s$  high-pass network at the input is added to reduce gain at low frequencies, while a cut-off frequency well below the desired input frequency range avoids undesired performance degradation. To explain the working principle of the proposed sextupler, we begin to analyze the  $g_m$  stage separately first.

In prior-art BGC-based doublers, the main purpose of the  $g_{\rm m}$  stage is to present a relatively high input impedance and to convert the differential input voltage ( $v_{\rm i}=v_{\rm i}^+-v_{\rm i}^-$ ) at frequency  $f_0$  into a collector current ( $i_{\rm c}=i_{\rm cp}-i_{\rm cn}$ ) of the same frequency. Since higher harmonic generation is undesired, a small-signal analysis is often carried out [23]. However, unlike prior art, we wish to use the  $g_{\rm m}$  stage as 3HG (from now on referred to as the 3HG stage) and leverage a strong third-harmonic component at nodes (B) for self-mixing in the switching quad. We therefore have to rely on a nonlinear analysis to assess the 3HG stage operation. In general, higher order harmonics are generated by the inherently exponential I-V characteristics of the HBTs or by waveform clipping. To analyze the nonlinearities caused by the device I-V characteristics, let us assume a monotone input signal

$$v_{\rm i}^+ = V_{\rm i} \cdot \cos(\omega_0 t) \tag{2}$$

being applied at the base of  $Q_1$ . When  $V_i$  reaches a level sufficient to forward-bias the base–emitter diode, a collector current  $i_{\rm cp}$  is flowing through the device, and its maximum value is controlled by  $V_i$ . As  $V_i$  decreases and the base–emitter diode is turned off,  $i_{\rm cp}$  is truncated. We can therefore model  $i_{\rm cp}$  as a clipped cosine pulse [53] and the interval  $t_0$  of nonzero current divided by the period T of the input signal is referred to as conduction angle. Since the cosine pulses are periodic, we can express  $i_{\rm cp}$  (and similarly  $i_{\rm cn}$ ) as a Fourier series with the amplitude of the nth harmonic given by [53]

$$I_n = I_{\text{max}} \frac{2}{\pi} \frac{\sin(n\delta)\cos(\delta) - n\sin(\delta)\cos(n\delta)}{n(n^2 - 1)}$$

(3)

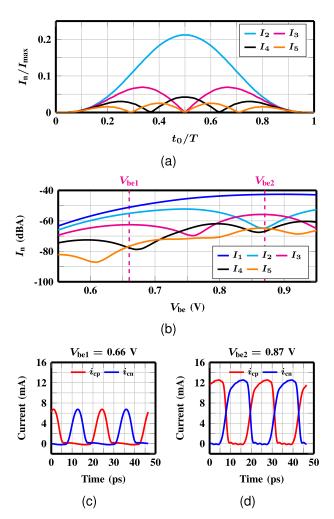

where  $I_{\rm max}$  is the peak collector current and  $\delta = \pi t_0/T$ . Fig. 4(a) shows the harmonic content calculated from (3) and normalized to  $I_{\rm max}$ . It can be seen that the third harmonic features two maxima at  $t_0/T \approx 0.33$  and  $t_0/T \approx 0.67$ . However, since (3) does not account for device parasitics and the effect of waveform clipping, precise large-signal models of the HBTs are required to predict the actual nonlinear behavior.

We therefore rely on the simulated harmonic amplitudes of the collector current, which are given in Fig. 4(b) as a function of the base–emitter voltage  $V_{\rm be}$  for a fixed collector–emitter voltage of  $V_{\rm ce}=1.1~{\rm V}$  and a 43-GHz input signal with amplitude of  $V_{\rm i}\approx 300~{\rm mV}$  ( $\approx 0~{\rm dBm}$  in a 50  $\Omega$  system), which is a realistic value for oscillators at this frequency and can be generated by a signal generator without any problems. As predicted by (3), the simulated third harmonic also exhibits two maxima, the first at  $V_{\rm be1}\approx 0.66~{\rm V}$  and the second at  $V_{\rm be2}\approx 0.87~{\rm V}$ . A closer look at the simulated waveforms of  $i_{\rm cp}$  and  $i_{\rm cn}$  at  $V_{\rm be1}=0.66~{\rm V}$  in Fig. 4(c) justifies our previous modeling as truncated cosine pulses for small  $V_{\rm be}$ . However, the second maximum at  $V_{\rm be2}=0.87~{\rm V}$  features

Fig. 4. Analysis of 3HG stage current harmonics at nodes B. (a) Calculated harmonics based on clipped cosine model. (b) Simulated harmonics of collector current  $i_{cp}$  versus  $V_{be}$ . Simulated time-domain waveforms of  $i_{cp}$  and  $i_{cn}$  for (c)  $V_{be1} = 0.66 \, \text{V}$  and (d)  $V_{be2} = 0.87 \, \text{V}$ .

a larger third harmonic than the first maximum. As shown in Fig. 4(d), this is because the upper half-waves of the collector currents are clipped as well. As a result, the current waveforms have a square-wave shape and are therefore rich in odd harmonics. Also, the third harmonic component in Fig. 4(b) is larger than the second harmonic, as even harmonics exhibit a local minimum at  $V_{\rm be2} \approx 0.87$  V. Even though we expect the even harmonics to cancel out due to differential operation, this reduces undesired mixing products that may arise from a common-mode excitation at the input, for example caused by amplitude and phase imbalance of the transformer (TF) balun. It should be noted that the optimum bias point depends on the conduction angle and thus varies with the applied input power and the size of the HBTs. A larger device size  $(N_x)$  increases the current amplitudes, but larger input power is required to clip the upper half-wave of  $i_c$  due to a reduced input impedance. We therefore choose a moderate device size of  $N_x = 3$  and bias the 3HG stage devices at  $V_{\rm be} = 0.87 \text{ V}$  and  $V_{\rm ce} = 1.1 \text{ V}$ . The 3HG stage devices are voltage-biased over series resistor  $R_{\rm B}=1~{\rm k}\Omega$  at the center tap of the input TF's secondary winding to inherently reduce  $V_{be}$  when the input power (and thus the base current over the biasing resistor) increases. This ensures the efficient generation of higher harmonics even for larger input power levels [29]. Alternatively, a current-biasing scheme with a tail current source at the virtual ground node between  $Q_{1-2}$  emitters is also an effective way to generate square-wave current waveforms, but was omitted here due to an increased voltage headroom and its parasitic output capacitance, which gives rise to common-mode excitation at high frequencies.

We now turn back to Fig. 3 and continue our analysis with the switching quad. If  $Z_c$  denotes the impedance seen at the collectors of  $Q_{1-2}$ , further assuming  $v_b = v_c$  are ideally ac-shorted over  $C_b$ , we notice that

$$v_{\rm b} = v_{\rm b}^+ - v_{\rm b}^- = \underbrace{v_{\rm c}^+ - v_{\rm c}^-}_{v_{\rm c}} = \underbrace{\left(i_{\rm cp} - i_{\rm cn}\right)}_{i_{\rm c}} \cdot Z_{\rm c}.$$

(4)

From Fig. 4, we know that  $i_c$  in our design has strong first and third harmonic components and can be expressed as

$$i_c = I_0 + I_1 \cdot \cos(\omega_0 t) + I_3 \cdot \cos(3\omega_0 t) \tag{5}$$

assuming that the fifth and higher odd-order harmonics can be neglected for facilitated derivations and using the fact that even harmonics are inherently suppressed under ideal differential excitation. As analyzed in [23], the impedance

$$Z_{c} = f(\omega, Z_{0}, \theta, C_{b}, g_{m}) \tag{6}$$

is a frequency-dependent function, mainly depending on the impedance presented by  $Q_{3-6}$  emitters and bases, capacitance  $C_b$ , as well as characteristic impedance  $Z_0$  and electrical length  $\theta$  of the transmission line TL<sub>b</sub>. Using (5) and (6), we can write the first and third harmonic components of  $v_b$  separately

$$v_{b1} = v_{c1} = V_{b1} \cdot \cos(\omega_0 t) \tag{7}$$

$$v_{b3} = v_{c3} = V_{b3} \cdot \cos(3\omega_0 t)$$

(8)

where  $V_{b1} = I_1 \cdot Z_c(\omega_0)$  and  $V_{b3} = I_3 \cdot Z_c(3\omega_0)$ . Similarly, we can express the harmonic components of  $v_e$  as

$$v_{\rm e1} = V_{\rm e1} \cdot \cos(\omega_0 t + \varphi_1) \tag{9}$$

$$v_{\rm e3} = V_{\rm e3} \cdot \cos(3\omega_0 t + \varphi_3) \tag{10}$$

noting that the network formed by  $C_b$  and  $TL_b$  introduces a frequency-dependent phase shift  $\varphi(\omega)$  between base and emitter. Using (7)–(10) and assuming ideal four-quadrant multiplication in the switching quad [54], we are now able to formulate the mixing processes in the quad

$$v_{b1} \cdot v_{e1} = \frac{V_{b1}V_{e1}}{2} [\cos(\varphi_1) + \cos(2\omega_0 t + \varphi_1)]$$

(11)

$$v_{b1} \cdot v_{e3} = \frac{V_{b1}V_{e3}}{2} [\cos(2\omega_0 t + \varphi_3) + \cos(4\omega_0 t + \varphi_3)] \quad (12)$$

$$v_{\rm b3} \cdot v_{\rm e1} = \frac{V_{\rm b3} V_{\rm e1}}{2} \left[ \cos(2\omega_0 t - \varphi_1) + \cos(4\omega_0 t + \varphi_1) \right] \quad (13)$$

$$v_{b3} \cdot v_{e3} = \frac{V_{b3}V_{e3}}{2} [\cos(\varphi_3) + \cos(6\omega_0 t + \varphi_3)]. \tag{14}$$

Equations (11)–(14) present important results. First, we note that (14) is the desired self-mixing process, which is why we wish to maximize the third harmonic voltage amplitudes

$(v_{b3}, v_{e3})$  to generate a strong sixth harmonic component at the output. Second, from (11)–(13), we see other mixing products at  $2f_0$  and  $4f_0$ , which need to be suppressed. At last, we see from (11) and (14) that the dc components from the self-mixing processes can be eliminated for  $\varphi_1, \varphi_3 = m \cdot 90^\circ$   $(m = \pm 1, \pm 3, ...)$ . If we assume an ideal linear frequency dependence of  $\varphi(\omega)$ , this condition is fulfilled by

$$\varphi_1 = \frac{\varphi_3}{3} = \pm 90^\circ. \tag{15}$$

Inserting (15) into (12) and (13), we realize that in this case the  $4f_0$  terms possess opposite phases and (given that the amplitudes of both mixing products are equal) cancel each other out. This is a remarkable result because it means that an optimized phase shift between  $Q_{3-6}$  base and emitter ideally eliminates both the dc and  $4f_0$  terms simultaneously. We conclude from our derivations that the network formed by  $C_b$  and  $TL_b$  needs to be optimized carefully since it controls the amplitude and phase relations of the switching quad and thus the harmonic components at the output of the BGC.

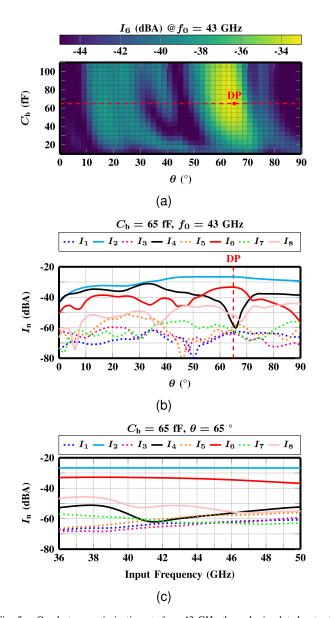

We first analyze the harmonics at the quad output nodes (D) without any filtering network included. Fig. 5(a) shows the sixth harmonic component of the output current ( $i_{out}$  =  $i_{\rm op}-i_{\rm on}$ ) versus  $C_{\rm b}$  and the electrical length  $\theta$  (specified at  $f_0 = 43$  GHz) of transmission line TL<sub>b</sub>. Since device and layout parasitics affect the optimum  $\theta$  [23], the quad layout is simulated until the metals connecting to  $C_b$  and  $TL_b$  to consider the parasitic effects in the simulation. We see that the influence of  $C_b$  is minor above  $\approx$ 40 fF, which allows us to choose our design point (DP) at  $C_b = 65$  fF for easy implementation as a MIM capacitor. When moving along the (red dashed) line of constant  $C_{\rm b}=65$  fF, the current contour shows its global maximum at  $\theta \approx 65^{\circ}$ . Simulations confirm that  $V_{\rm b3}$  exhibits a maximum at the same  $\theta$  value, as expected from (14). To continue our analysis, we inspect the first eight simulated harmonics of  $i_{out}$  versus  $\theta$  at constant  $C_b = 65$  fF in Fig. 5(b). In accordance with our derivations, the even-order harmonics dominate over the odd-order ones. Also, the global maxima of the  $2f_0$  and  $6f_0$  components are both located around  $\theta \approx 65^{\circ}$ . At the same value of  $\theta$ , the  $4f_0$  component exhibits its global minimum and is suppressed by more than 20 dB compared to the desired  $6f_0$  component. Time-domain simulations show that  $v_b$  is ahead of  $v_e$  by 90°, which confirms that (15) holds and  $\theta \approx 65^{\circ}$  is the optimum electrical length of TL<sub>b</sub> for our sextupler. TL<sub>b</sub> is realized as a microstrip line with  $Z_0 = 70 \Omega$  using the top-most thick copper layer (ThCu2) for lowest loss and M3 ground layer to allow shielded supply routing below M3. Fig. 5(c) shows the simulated harmonics of  $i_{\text{out}}$  over different input frequencies, indicating that the inherent suppression of the fourth harmonic is maintained over a wide frequency range.

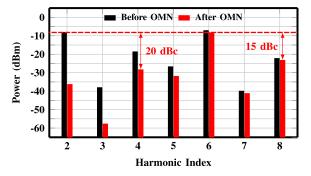

At last, the output matching network (OMN) is analyzed for high sixth harmonic output power and suppression of undesired harmonics. The simulations from Fig. 5(b) and (c) indicate that the closest even-order harmonics  $(4f_0, 8f_0)$  are

<sup>1</sup>Note that we have neglected the  $5\omega_0$  and higher terms in (5) and have assumed ideal four-quadrant multiplication in our derivation. In reality, there exist mixing terms at all harmonics of  $f_0$ , from which the ones close to  $6f_0$  are most critical, while the others can be filtered out effectively.

Fig. 5. Quad stage optimization at  $f_0 = 43$  GHz through simulated output current ( $i_{\text{out}} = i_{\text{op}} - i_{\text{on}}$ ) into nodes ①. (a) Sixth harmonic current versus  $C_{\text{b}}$  and electrical length  $\theta$  of TL<sub>b</sub>. (b) First–eighth harmonic versus  $\theta$  at  $C_{\text{b}} = 65$  fF. (c) Harmonic performance over input frequency at  $C_{\text{b}} = 65$  fF,  $\theta = 65$ °.

suppressed below  $6f_0$  thanks to the phase optimization in the quad. Since  $2f_0$  remains the most critical undesired harmonic, a simple two-element high-pass network composed of  $L_1$  and  $C_3$  is chosen to filter out  $2f_0$  components effectively while providing optimal load impedance at  $6f_0$ . Inductance  $L_1$  is realized with a short metal line and  $C_3$  is a metal-oxide-metal (MOM) capacitor formed between M3 and M4 due to their close proximity. The OMN is optimized through electromagnetic (EM) simulations, and its filtering effectiveness is assessed in Fig. 6. This is done by simulating the harmonic power levels at nodes  $\mathbb O$  (before OMN) and  $\mathbb C$  (after OMN) at the sextupler's output, with an input frequency of  $f_0 = 43$  GHz and input power  $P_{\rm in} = 0$  dBm. The results confirm that the OMN's high-pass characteristics significantly enhance suppression of all harmonics below  $6f_0$ . At the design

Fig. 6. Simulated harmonic power levels at sextupler output before OMN (at nodes ①) and after OMN (at nodes ②) for input frequency/power of 43 GHz/0 dBm.

frequency of  $6f_0 = 258$  GHz, the OMN's insertion loss is 1.2 dB. The minimum HRR after the OMN is 15 dBc for the eighth harmonic, with all other harmonics being suppressed by at least 20 dBc with respect to the desired sixth harmonic. Given that the resonant amplification in the PA stage further improves the suppression of undesired harmonics, we have refrained from implementing higher order bandpass [29] or bandstop filters [55] in this work. For applications with more stringent HRR requirements than in our case, the harmonic suppression can be further improved by choosing a network with enhanced frequency selectivity around  $6f_0$  at the expense of increased passive loss and silicon area.

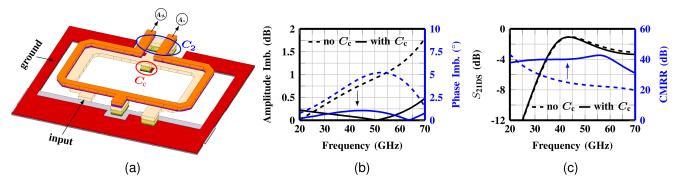

## B. Balance-Compensated Input TF

The input network (IM) in Fig. 3 is used to convert the single-ended input signal into a balanced signal at nodes (A), and for impedance matching. Both tasks can be combined effectively by using a TF-based balun, featuring a smaller form factor compared to Marchand baluns (MBs) with LC-based matching network. Our optimized input TF layout is shown in Fig. 7(a). We use the top-most thick copper layer (ThCu2) for the TF's primary coil and the secondary coil is formed by stacking both aluminum layers for reduced ohmic loss. The TF exhibits simulated primary inductance  $L_p = 144$  pH with quality factor  $Q_p = 22$ , secondary inductance  $L_s = 189 \text{ pH}$ with  $Q_s = 14$ , and coupling factor k = 0.61 (see Fig. 3) at the design frequency of 43 GHz. MOM capacitor  $C_2$  = 28 fF between the balanced outputs and series MIM capacitor  $C_1 = 75$  fF [not shown in Fig. 7(a)] at the input are added for matching purposes.

Even though primary and secondary coils do not fully overlap in our design, mutual parasitic capacitance between TF windings poses a challenge at mm-wave frequencies, since it results in undesired common-mode excitation [56]. The common-mode portion in turn causes amplitude and phase imbalance between nodes (A), which need to be minimized to avoid unwanted even-harmonic generation in the 3HG stage of our proposed sextupler. It has been shown that the common-mode excitation can be reduced by grounding the center tap of the TF's secondary coil and connecting an additional susceptance to the center tap of the primary winding [56] or vice versa [34]. In our design, the center tap of the secondary coil is ac-grounded through MIM capacitors

Fig. 7. Input TF design. (a) Layout view with balance-compensation capacitance  $C_c$  and matching capacitance  $C_2$ , (b) simulated amplitude/phase imbalance of the output signals, and (c) simulated single-ended-to-differential transmission  $S_{21DS}$  and CMRR.

[not shown in Fig. 7(a)] in close proximity to the TF area. Also, we have added a small balance-compensation capacitance  $C_c = 11$  fF at the primary coil's center tap, which is realized as a MOM capacitor between metal layers M4 and ThCu1. The optimum value of  $C_c$  is found through EM simulations to also account for the parasitic on-chip ground plane inductance. To assess the effect of  $C_c$  on the balun performance, the TF is simulated with (solid lines) and without (dashed lines) the balance-compensation capacitance. Fig. 7(b) shows the amplitude and phase imbalance over a wide range of input frequencies. It can be seen that inserting  $C_c$  minimizes the imbalance at the design frequency of 43 GHz by 0.7 dB and 3.4°, respectively. Without balancecompensation, imbalances of up to 1.8 dB/5.2° are observed in the displayed frequency range. After adding  $C_c$ , the imbalance can be reduced to values below 0.5 dB/1.1°, indicating that the balance-compensation works effectively over a wide frequency range. As shown in Fig. 7(c), the reduced imbalance also reflects in an improved common-mode rejection ratio (CMRR), while the single-ended to differential transmission  $(S_{21DS})$  is not affected by  $C_c$ .

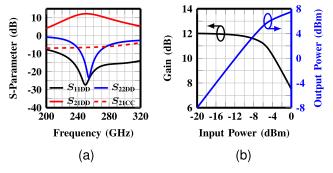

# C. J-Band Cascode Amplifier and Output Balun

As shown in Fig. 3, the sextupler is followed by a fully differential cascode amplifier (PA) optimized around  $6f_0$  to further enhance output power and harmonic suppression. A fully differential topology with  $R_1 = 8.3 \Omega$  is opted to achieve high CMRR and hence robustness against any imbalance at the PA input. A conservative device size of  $N_x = 4$  is selected for  $Q_{7-10}$  based on the available input power from the sextupler. Transistors  $Q_{7-10}$  are biased at peak  $f_T/f_{MAX}$ current density and draw 24 mA from a 2.6 V supply. The output network formed by  $L_2 = 11 \text{ pH}$  and  $C_4 = 20 \text{ fF}$  is optimized to transform a balanced impedance of 100  $\Omega$  into the PA's optimum load impedance. The simulated small-signal performance of the PA is summarized in Fig. 8(a), indicating a peak differential gain  $(S_{21DD})$  of 12.2 dB with a 3-dB bandwidth of 226-282 GHz (22.1%). At the design frequency of 258 GHz, a CMRR of 19 dB is achieved. The large-signal simulations in Fig. 8(b) are carried out at 258 GHz, showing an input-referred 1-dB compression point around −6 dBm, which coincides with the maximum power delivered from the sextupler.

Fig. 8. Simulated performance of the *J*-band amplifier. (a) S-parameters versus frequency. (b) Gain and output power versus input power at 258 GHz.

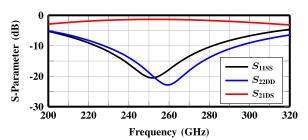

Fig. 9. Simulated mixed-mode S-parameters of the J-band MB including the output pad's parasitic capacitance.

The PA's balanced output signal is converted into a single-ended signal through a MB, which is added solely for measurement purposes. The simulated S-parameters of the MB including the effect of the output pad's parasitic capacitance are given in Fig. 9, demonstrating an insertion loss of  $S_{21DS} = 1.35$  dB at 258 GHz. Both single-ended ( $S_{11SS}$ ) and balanced ( $S_{22DD}$ ) ports are well matched over a wide frequency range centered around 258 GHz.

#### IV. EXPERIMENTAL RESULTS

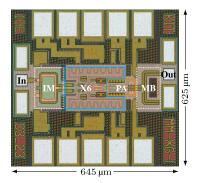

The chip micrograph of the proposed frequency sextupler is given in Fig. 10. The total chip area including pads is 0.4 mm<sup>2</sup>. The core area, which comprises the complete RF path except the output MB, measures only 0.06 mm<sup>2</sup>.

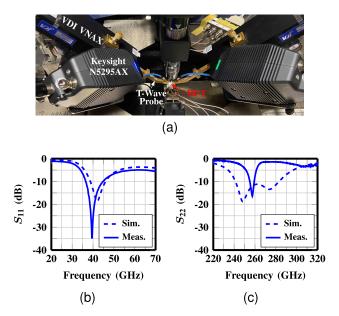

Small-signal measurements covering the complete frequency range from 10 MHz up to 330 GHz are performed using a Keysight N5291A vector network analyzer (VNA) in two different setups. The frequency range below 220 GHz is covered in a single measurement with the broadband

Fig. 10. Chip micrograph of the fabricated frequency sextupler.

Fig. 11. Small-signal characterization. (a) 220 GHz broadband measurement setup. (b) Input reflection coefficient. (c) Output reflection coefficient.

measurement setup shown in Fig. 11(a) including a Form-Factor dual-band T-wave probe with integrated diplexer and two parallel VNA extenders at each port for the 0.01–130 GHz (Keysight N5295AX) and 130–220 GHz frequency range (VDI WR5.1-VNAX), respectively. The input reflection coefficient in Fig. 11(b) shows a good agreement between measurement and simulation and remains below –10 dB between 36–45 GHz (22.2%). For the frequency range from 220–330 GHz (WR3.4), VNA extenders from OML are used. Measured and simulated output reflection coefficients are given in Fig. 11(c).

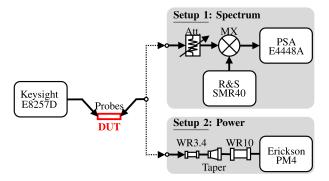

The on-wafer measurement setup used for large-signal characterization of the frequency multiplier is shown in Fig. 12. The first harmonic input signal is generated by a Keysight E8257D signal generator. At the output side, spectrum measurements including the third to eighth harmonic power levels are performed by using an Agilent E4448A spectrum analyzer and different down-conversion mixers (MX) for the frequency ranges of 220–330 GHz (VDI WR3.4MixAMC-I) as well as 110–170 GHz (VDI WR6.5MixAMC-I). A variable waveguide attenuator precedes the mixer to avoid gain compression during down-conversion. An additional power measurement in the

Fig. 12. Large-signal measurement setup.

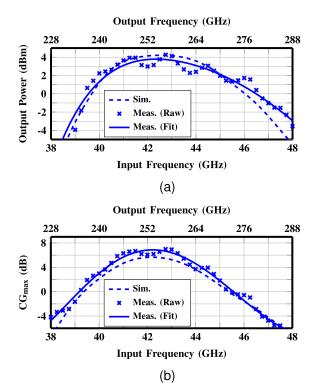

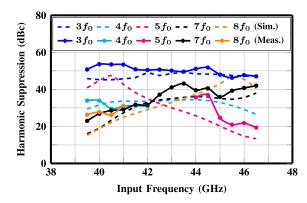

Fig. 13. Measured and simulated large-signal performance. (a) Sixth harmonic output power at fixed input power level of  $P_{\rm in}=5$  dBm. (b) CG<sub>max</sub> versus frequency.

Fig. 14. Measured and simulated harmonic suppression within the 3-dB bandwidth at fixed input power level of  $P_{\text{in}} = 5 \text{ dBm}$ .

WR3.4 frequency range is conducted with an Erickson PM4 calorimetric power meter to verify the sixth harmonic output power. The measured and simulated sixth harmonic output

| TABLE I                                                                                 |

|-----------------------------------------------------------------------------------------|

| STATE-OF-THE-ART SILICON-BASED HIGHER ORDER FREQUENCY MULTIPLIERS AT J-BAND FREQUENCIES |

| Ref.  | Technology $(f_{ m T}/f_{ m MAX})$ | MF | Topology      | f <sub>c</sub> (GHz) | BW <sub>3dB</sub> (%) | Pout (dBm) | Ways | $P_{ m in}^{\dagger}$ (dBm) | CG <sub>max</sub> (dB) | $P_{ m dc}^{\dagger}$ (mW) | $\eta_{ m dc} \ (\%)$ | HRR<br>(dBc)     | Area§ (mm²)       |

|-------|------------------------------------|----|---------------|----------------------|-----------------------|------------|------|-----------------------------|------------------------|----------------------------|-----------------------|------------------|-------------------|

| [57]  | $ 45 \text{ nm SOI} \\ (-/-) $     | 4  | PPX2–PPX2     | 280                  | 3.6                   | -7         | 1    | 12                          | -19                    | 93.5                       | 0.21 <sup>a</sup>     | 17 <sup>b</sup>  | 0.13°             |

| [58]  | 130 nm SiGe<br>(300/450)           | 4  | PPX4          | 255.5                | 5.0                   | -8.4       | 1    | 3.5                         | -10.4                  | 22.4                       | 0.65ª                 | 10               | 0.24              |

| [59]  | 130 nm SiGe<br>(300/500)           | 4  | PPX2–PA–PPX2  | 236                  | 20.3                  | 5.5        | 2    | 0                           | 7°                     | 270                        | 1.4                   | >20 <sup>b</sup> | 0.19 <sup>c</sup> |

| [32]  | 40 nm CMOS<br>(-/-)                | 6  | PA-X3-PA-PPX2 | 257.5                | 6.6                   | 3          | 4    | -10                         | 13ª                    | 890                        | 0.22ª                 | _                | 6.11°             |

| [33]  | 130 nm SiGe<br>(300/500)           | 6  | X3–GCX2       | 229.5                | 6.5                   | -4         | 2    | 0                           | -1°                    | 900                        | 0.04 <sup>a</sup>     | >14              | 0.19 <sup>c</sup> |

| [31]  | 130 nm SiGe<br>(300/500)           | 6  | X3–PA–PPX2    | 239                  | 28.5                  | 9          | 2    | 2                           | 16                     | 480                        | 1.92                  | >15              | 0.2               |

| This  | 130 nm SiGe<br>(470/650)           | 6  | BGCX6–PA      | 258                  | 15.5                  | 4.3        | 2    | 5                           | 7                      | 119                        | 2.2                   | >20              | 0.06              |

| This* | 130 nm SiGe<br>(470/650)           | 6  | BGCX6–PA      | 258                  | 15.5                  | 5.6        | 2    | 5                           | 8.3                    | 119                        | 3.1                   | >20              | 0.06              |

<sup>\*</sup> excluding output balun

b simulated

c estimated

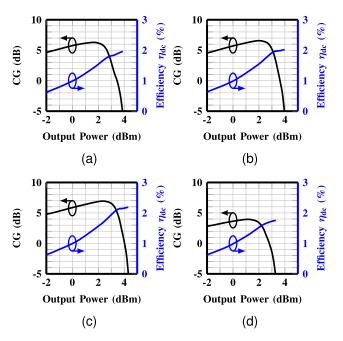

Fig. 15. Measured CG and dc-to-RF efficiency at input/output frequency of (a) 41/246 GHz, (b) 42.5/255 GHz, (c) 43/258 GHz, and (d) 44.5/267 GHz.

power and the maximum conversion gain ( $CG_{max}$ ) are plotted in Fig. 13. The results show excellent agreement between measurement and simulation, with peak measured values of 4.3 dBm for output power and 7 dB for  $CG_{max}$  at 256.5 GHz. The measured results also indicate a 40 GHz wide output power 3-dB bandwidth ( $BW_{3dB}$ ) ranging from 238–278 GHz (15.5%). Within this bandwidth, all other harmonics are suppressed by more than 20 dBc, as shown in Fig. 14. Around the center frequency, a minimum harmonic suppression of more than 30 dBc is achieved. At the peak output power of 4.3 dBm, the sextupler and output amplifier draw 23.5 mA / 24 mA from their 2.4 V / 2.6 V supplies, respectively. This results in

a total dc power consumption of 118.8 mW. The measurement results of CG and dc-to-RF efficiency are plotted in Fig. 15 versus output power at various frequencies. A peak efficiency of  $\eta_{\rm dc} = 2.2\%$  is demonstrated at 258 GHz. Consistent results are achieved by repeating measurements on different samples.

## V. CONCLUSION

We have introduced a single-stage sextupler based on a BGC, implemented in a 130-nm SiGe BiCMOS technology with  $f_T/f_{MAX} = 470 \text{ GHz}/650 \text{ GHz}$ . Our analysis of the harmonic generation and mixing mechanisms in the BGC has revealed that it is possible to simultaneously maximize the desired sixth harmonic and inherently suppress the most critical mixing products at the fourth and eighth harmonic frequencies by carefully optimizing the phase relations in the switching quad. Thanks to this inherent suppression mechanism, the requirements on the filter network are greatly relaxed. A single cascode amplification stage is included, helping us to achieve a peak output power of 4.3 dBm and a minimum harmonic suppression of > 30 dBc at 257 GHz. Further, we have shown the effectiveness of adding a small balance-compensation capacitance at the primary coil's center tap in a TF-based balun to improve amplitude and phase imbalance over a wide frequency range.

In Table I, we provide a comparison of silicon-based higher order frequency multipliers at *J*-band frequencies. Among the listed studies, our design stands out by achieving the highest dc-to-RF efficiency and by occupying the smallest silicon core area. By replacing the traditional tripler-doubler cascade used in prior-art sextuplers with our proposed single-stage approach, approximately 70% of core area and more than 75% of dc power can be saved when compared to state-of-the-art sextuplers at similar frequencies and output power levels. The compilation in Table I also indicates that our proposed design is favored by an enhanced suppression of undesired harmonics and a competitive 3-dB bandwidth. Given these results, the

$<sup>^{\</sup>dagger}$  at peak  $P_{\mathrm{out}}$

<sup>§</sup> core area

a calculated from table data

presented single-stage frequency sextupler is highly attractive for realizing compact and power-efficient LO paths in phased arrays or any other multichannel systems.

#### REFERENCES

- [1] B. Heinemann et., "SiGe HBT with  $f_T/f_{max}$  of 505 GHz/720 GHz," in *IEDM Tech. Dig.*, Dec. 2016, pp. 3.1.1–3.1.4.

- [2] S. Thomas, C. Bredendiek, and N. Pohl, "A SiGe-based 240-GHz FMCW radar system for high-resolution measurements," *IEEE Trans. Microw. Theory Techn.*, vol. 67, no. 11, pp. 4599–4609, Nov. 2019.

- [3] R. Hasan, M. H. Eissa, W. A. Ahmad, H. J. Ng, and D. Kissinger, "Wideband and efficient 256-GHz subharmonic- based FMCW radar transceiver in 130-nm SiGe BiCMOS technology," *IEEE Trans. Microw. Theory Techn.*, vol. 71, no. 1, pp. 59–70, Jan. 2023.

- [4] E. Turkmen et al., "A 223–276-GHz cascadable FMCW transceiver in 130-nm SiGe BiCMOS for scalable MIMO radar arrays," *IEEE Trans. Microw. Theory Techn.*, vol. 71, no. 12, pp. 5393–5412, Dec. 2023.

- [5] I. Abdo et al., "A bi-directional 300-GHz-band phased-array transceiver in 65-nm CMOS with outphasing transmitting mode and LO emission cancellation," *IEEE J. Solid-State Circuits*, vol. 57, no. 8, pp. 2292–2308, Aug. 2022.

- [6] C. Mangiavillano, A. Kaineder, T. Wagner, and A. Stelzer, "A 240-GHz 4-TX 4-RX 2-D-MIMO FMCW Radar transceiver in 130-nm SiGe BiCMOS," *IEEE Microw. Wireless Technol. Lett.*, vol. 33, no. 8, pp. 1239–1242, Aug. 2023.

- [7] C. Wang et al., "24.3 a 236-to-266GHz 4-element amplifier-last phased-array transmitter in 65nm CMOS," in *Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC)*, Feb. 2024, pp. 415–417.

- [8] M. Möck, I. K. Aksoyak, and A. Ç. Ulusoy, "A K<sub>a</sub>-band colpitts-clapp VCO With 30% tuning range and high output power," *IEEE Microw. Wireless Technol. Lett.*, vol. 33, no. 4, pp. 439–442, Apr. 2023.

- [9] F. Vogelsang, C. Bredendiek, J. Schöpfel, H. Rücker, and N. Pohl, "A static frequency divider up to 163 GHz in SiGe-BiCMOS technology," in Proc. IEEE BiCMOS Compound Semiconductor Integr. Circuits Technol. Symp. (BCICTS), Oct. 2022, pp. 49–52.

- [10] Z. Peng, J. Chen, H. Wang, L. Zhang, W. Hong, and X. Liu, "A 208-GHz injection locking doubler chain with 3.2% PAE and 2.9-mW output power in CMOS technology," *IEEE Microw. Wireless Compon. Lett.*, vol. 32, no. 4, pp. 351–354, Apr. 2022.

- [11] S. Kim, D. Yoon, J. Kim, J. Yoo, K. Song, and J.-S. Rieh, "A CMOS 300-GHz injection-locked frequency tripler with a tri-layer dual coupled line for improved locking range," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 69, no. 2, pp. 309–313, Feb. 2022.

- [12] A. Siligaris et al., "A 278 GHz heterodyne receiver with on-chip antenna for THz imaging in 65 nm CMOS process," in *Proc. Conf. 41st Eur. Solid-State Circuits Conf. (ESSCIRC)*, Sep. 2015, pp. 307–310.

- [13] M. Möck, İ. K. Aksoyak, and A. Ç. Ulusoy, "A high-efficiency D-band frequency doubler in 22-nm FDSOI CMOS," in *Proc. 17th Eur. Microw. Integr. Circuits Conf. (EuMIC)*, Sep. 2022, pp. 272–275.

- [14] Z. Yang, K. Ma, F. Meng, and B. Liu, "A 120-GHz class-F frequency doubler with 7.8-dBm P<sub>out</sub> in 55-nm bulk CMOS," *IEEE J. Solid-State Circuits*, vol. 58, no. 8, pp. 2173–2188, Aug. 2023.

- [15] M. Abbasi, T. Thapliyal, S. M. A. Uddin, and W. Lee, "A 114–126-GHz frequency doubler with >10 dBm output power and >12% efficiency in 45 nm RFSOI," *IEEE Microw. Wireless Technol. Lett.*, vol. 34, no. 9, pp. 1107–1110, 2024.

- [16] M. Möck, İ. K. Aksoyak, and A. Ç. Ulusoy, "A 4.5 dBm SiGe doubler-amplifier chain covering the entire D-band," in *Proc. IEEE 24th Topical Meeting Silicon Monolithic Integr. Circuits RF Syst. (SiRF)*, Jan. 2024, pp. 29–32.

- [17] F. Ahmed, M. Furqan, and A. Stelzer, "A 0.3-THz SiGe-based frequency doubler chip with 3-dB 50 GHz bandwidth and 17 dB peak conversion gain," in *Proc. 12th Eur. Microw. Integr. Circuits Conf. (EuMIC)*, Oct. 2017, pp. 134–137.

- [18] S. Li, X. Li, H. Wu, and W. Chen, "A 200-to-350GHz SiGe BiCMOS frequency doubler with slotline-based mode-decoupling harmonic-tuning technique achieving 1.1-to-4.7dBm output power," in *Proc. IEEE Int. Solid- State Circuits Conf. (ISSCC)*, Feb. 2023, pp. 23–25.

- [19] H.-C. Lin and G. M. Rebeiz, "A SiGe multiplier array with output power of 5–8 dBm at 200–230 GHz," *IEEE Trans. Microw. Theory Techn.*, vol. 64, no. 7, pp. 2050–2058, Jul. 2016.

- [20] S. Breun, A. -M. Schrotz, M. Dietz, V. Issakov, and R. Weigel, "A 314–344 GHz frequency doubler with driving stage and 1 dBm Psat in SiGe BiCMOS technology," in *Proc. IEEE 21st Top. Meeting Silicon Monolithic Integr. Circuits RF Syst.*, 2021, pp. 11–14.

- [21] S. Muralidharan, K. Wu, and M. Hella, "A 165–230GHz SiGe amplifier-doubler chain with 5dBm peak output power," in *Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC)*, May 2016, pp. 302–305.

- [22] S. Yuan and H. Schumacher, "90–140 GHz frequency octupler in Si/SiGe BiCMOS using a novel bootstrapped doubler topology," in *Proc.* 9th Eur. Microw. Integr. Circuit Conf. (EuMIC), Oct. 2014, pp. 158–161.

- [23] M. Kucharski, M. H. Eissa, A. Malignaggi, D. Wang, H. J. Ng, and D. Kissinger, "D-band frequency quadruplers in BiCMOS technology," *IEEE J. Solid-State Circuits*, vol. 53, no. 9, pp. 2465–2478, Sep. 2018.

- [24] H. Fudem and E. C. Niehenke, "Novel millimeter wave active MMIC triplers," in *IEEE MTT-S Int. Microw. Symp. Dig.*, Jun. 1998, pp. 387–390.

- [25] K. Katayama, K. Takano, S. Amakawa, T. Yoshida, and M. Fujishima, "2.37-dBm-output 288–310 GHz frequency multiplier in 40 nm CMOS," in *Proc. IEEE Int. Symp. Radio-Frequency Integr. Technol. (RFIT)*, Aug. 2017, pp. 28–30.

- [26] A. Chandra-Prabhu, J. Grzyb, P. Hillger, B. Heinemann, H. Rücker, and U. Pfeiffer, "A wideband W-band frequency tripler with a novel modeselective filter for high harmonic rejection," in *Proc. 18th Eur. Microw. Integr. Circuits Conf. (EuMIC)*, Sep. 2023, pp. 197–200.

- [27] J. Romstadt et al., "A 117.5–155-GHz SiGe ×12 frequency multiplier chain with push-push doublers and a Gilbert cell-based tripler," IEEE J. Solid-State Circuits, vol. 58, no. 9, pp. 2430–2440, Sep. 2023.

- [28] X. Huang, H. Jia, W. Deng, Z. Wang, and B. Chi, "A 91.9–113.2 GHz compact frequency tripler with 44.6 dBc peak fundamental harmonic-rejection-ratio using embedded notch-filters and area-efficient matching network in 65 nm CMOS," in *Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC)*, Jun. 2023, pp. 165–168.

- [29] B.-H. Ku, H. Chung, and G. M. Rebeiz, "A milliwatt-level 70–110 GHz frequency quadrupler with >30 dBc harmonic rejection," *IEEE Trans. Microw. Theory Techn.*, vol. 68, no. 5, pp. 1697–1705, May 2020.

- [30] M. K. Ali, G. Panic, and D. Kissinger, "A broadband 110–170 GHz frequency quadrupler with 29 dBc harmonic rejection in a 130-nm SiGe BiCMOS technology," in *Proc. 17th Eur. Microw. Integr. Circuits Conf.* (EuMIC), Sep. 2022, pp. 44–47.

- [31] Z. Li, J. Chen, D. Tang, R. Zhou, and W. Hong, "A 205–273-GHz frequency multiplier chain ×6 with 9-dBm output power and 1.92% DC-to-RF efficiency in 0.13μm SiGe BiCMOS," *IEEE Trans. Microw. Theory Techn.*, vol. 71, no. 7, pp. 2909–2919, 2023.

- [32] R. Dong et al., "A 260-GHz four-way phase compensated CMOS frequency multiplier chain," *IEEE Trans. THz Sci. Technol.*, vol. 13, no. 1, pp. 20–27, Jan. 2023.

- [33] A. Ergintav, F. Herzel, J. Borngräber, D. Kissinger, and H. J. Ng, "An integrated 240 GHz differential frequency sixtupler in SiGe BiCMOS technology," in *Proc. IEEE 17th Topical Meeting Silicon Monolithic Integr. Circuits RF Syst.*, Phoenix, AZ, USA, Jan. 2017, pp. 43–46.

- [34] S. Li, W. Chen, X. Li, and Y. Wang, "A 5.1 dBm 127–162 GHz frequency sextupler with broadband compensated transformer-based baluns in 22nm FD-SOI CMOS," in *Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC)*, Jun. 2022, pp. 315–318.

- [35] M. Bao, Z. He, T. N. Do, and H. Zirath, "A 110-to-147 GHz frequency sixtupler in a 130 nm SiGe BiCMOS technology," in *Proc. 13th Eur. Microw. Integr. Circuits Conf. (EuMIC)*, Sep. 2018, pp. 105–108.

- [36] P. Zhou, J. Chen, D. Hou, and W. Hong, "Analysis and design of D-band high output power signal sources in 130-nm SiGe BiCMOS process," in *IEEE MTT-S Int. Microw. Symp. Dig.*, May 2021, pp. 1–3.

- [37] M. M. Pirbazari and A. Mazzanti, "E-band frequency sextupler with >35 dB harmonics rejection over 20 GHz bandwidth in 55 nm BiC-MOS," *IEEE J. Solid-State Circuits*, vol. 57, no. 7, pp. 2155–2166, Jul. 2022.

- [38] D.-J. Shin, U.-G. Choi, and J.-R. Yang, "A compact D-band CMOS frequency sixtupler using a mode analysis of the harmonics," *IEEE Trans. Microw. Theory Techn.*, vol. 71, no. 4, pp. 1501–1508, Apr. 2023.

- [39] T. Buecher, S. Malz, K. Aufinger, and U. R. Pfeiffer, "A 210–291-GHz 8× frequency multiplier chain with low power consumption in 0.13-μm SiGe," *IEEE Microw. Wireless Compon. Lett.*, vol. 30, no. 5, pp. 512–515, 2020.

- [40] J.-H. Park, D.-Y. Yang, K.-J. Choi, and B.-S. Kim, "D-band ×8 frequency multiplier using complementary differential frequency doubler," *IEEE Microw. Wireless Technol. Lett.*, vol. 33, no. 3, pp. 311–314, 2023.

- [41] V.-S. Trinh and J.-D. Park, "An E-band transformer-based ×8 frequency multiplier with enhanced harmonic rejection," *IEEE Trans. Microw. Theory Techn.*, vol. 71, no. 3, pp. 1019–1030, 2023.

- [42] S. Park et al., "A D-band low-power and high-efficiency frequency multiply-by-9 FMCW radar transmitter in 28-nm CMOS," *IEEE J. Solid-State Circuits*, vol. 57, no. 7, pp. 2114–2129, Jul. 2022.

- [43] A. C. Prabhu, J. Grzyb, P. Hillger, T. Bücher, H. Rücker, and U. Pfeiffer, "A 300 GHz ×9 multiplier chain with 9.6 dBm output power in 0.13μm SiGe technology," in *Proc. IEEE 24th Topical Meeting Silicon Monolithic Integr. Circuits RF Syst. (SiRF)*, Jan. 2024, pp. 37–40.

- [44] R. Chen, H.-Y. Chien, and M.-C.-F. Chang, "A compact D-band multiply-by-9 frequency multiplier with inductor-less active balun in 16nm p-FinFET technology," in *Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC)*, Jun. 2024, pp. 147–150.

- [45] W. Wu, "A 276–312-GHz ×12 frequency multiplier chain with milliwatt level output power in 65-nm CMOS technology," *IEEE Microw. Wireless Technol. Lett.*, vol. 33, no. 11, pp. 1556–1559, Nov. 2023.

- [46] Y. Zhang, W. Liang, C. Esposito, X. Jin, P. Sakalas, and M. Schroter, "LO chain ×12 integrated 190-GHz low-power sige receiver with 49-db conversion gain and 171-mW DC power consumption," *IEEE Trans. Microw. Theory Techn.*, vol. 69, no. 3, pp. 1943–1954, Mar. 2021.

- [47] N. Sarmah et al., "235–275 GHz (x16) frequency multiplier chains with up to 0 dBm peak output power and low DC power consumption," in *Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC)*, May 2014, pp. 181–184.

- [48] E. Öjefors, B. Heinemann, and U. R. Pfeiffer, "Active 220- and 325-GHz frequency multiplier chains in an SiGe HBT technology," *IEEE Trans. Microw. Theory Techn.*, vol. 59, no. 5, pp. 1311–1318, May 2011.

- [49] E. Turkmen, I. K. Aksoyak, W. Debski, W. Winkler, and A. Ç. Ulusoy, "A 220–261 GHz frequency multiplier chain (x18) with 8-dBm peak output power in 130-nm SiGe," *IEEE Microw. Wireless Compon. Lett.*, vol. 32, no. 7, pp. 895–898, Jul. 2022.

- [50] Y. Wang, W. L. Goh, and Y.-Z. Xiong, "A 9% power efficiency 121-to-137GHz phase-controlled push-push frequency quadrupler in 0.13μm SiGe BiCMOS," in *Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC)*, Feb. 2012, pp. 262–264.

- [51] M. Ko, M. H. Eissa, J. Borngräber, A. Cagri Ulusoy, and D. Kissinger, "110–135 GHz SiGe BiCMOS frequency quadrupler based on a single Gilbert cell," in *Proc. 13th Eur. Microw. Integr. Circuits Conf. (EuMIC)*, Sep. 2018, pp. 101–104.

- [52] V. Rieß, C. Carta, and F. Ellinger, "Frequency multiplication with adjustable waveform shaping demonstrated at 200 GHz," *IEEE Trans. Microw. Theory Techn.*, vol. 67, no. 4, pp. 1544–1555, Apr. 2019.

- [53] S. A. Maas, Nonlinear Microwave and RF Circuits, 2nd ed., Boston, London: Artech House, 2003.

- [54] H. Schumacher, S. Yuan, and V. Valenta, "Design of wideband frequency multipliers for high chirp bandwidth mm-wave FMCW sensors," in Proc. Integr. Nonlinear Microw. Millimetre-wave Circuits Workshop (INMMiC), Oct. 2015, pp. 1–6.

- [55] A. Karakuzulu, M. H. Eissa, D. Kissinger, and A. Malignaggi, "A broadband 110–170 GHz frequency multiplier by 4 chain with 8 dBm output power in 130 nm BiCMOS," in *Proc. IEEE 47th Eur. Solid State Circuits Conf. (ESSCIRC)*, Sep. 2021, pp. 451–454.

- [56] K. Wu, S. Muralidharan, and M. M. Hella, "A wideband SiGe BiCMOS frequency doubler with 6.5-dBm peak output power for millimeter-wave signal sources," *IEEE Trans. Microw. Theory Techn.*, vol. 66, no. 1, pp. 187–200, Jan. 2018.

- [57] M. Abbasi and D. S. Ricketts, "275–285 GHz balanced frequency quadrupler chain in 45 nm SOI CMOS," *Electron. Lett.*, vol. 51, no. 18, pp. 1424–1426, Sep. 2015.

- [58] L. Steinweg, V. Rieß, P. Stärke, P. V. Testa, C. Carta, and F. Ellinger, "A low-power 255-GHz single-stage frequency quadrupler in 130-nm SiGe BiCMOS," *IEEE Microw. Wireless Compon. Lett.*, vol. 30, no. 11, pp. 1101–1104, Nov. 2020.

- [59] J. Yu, J. Chen, Z. Li, D. Hou, Z. Chen, and W. Hong, "A 212–260 GHz broadband frequency multiplier chain ×4 in 130-nm BiCMOS technology," in *IEEE MTT-S Int. Microw. Symp. Dig.*, 2021, pp. 454–457.

Matthias Möck (Graduate Student Member, IEEE) received the B.Eng. degree in mechatronics/microelectronics from Reutlingen University, Reutlingen, Germany, in 2018, and the M.Sc. degree in electrical engineering from Karlsruhe Institute of Technology (KIT), Karlsruhe, Germany, in 2020, where he is currently pursuing the Ph.D. degree at the Institute of Radio Frequency Engineering and Electronics.

His research interests include silicon-based signal generation circuits for millimeter-wave systems,

including voltage-controlled oscillators, frequency multiplication circuits, and phase-locked loops.

Mr. Möck was a recipient of the Best Student Paper Award (second place) at the IEEE Radio and Wireless Week in 2024.

Kaan Balaban (Graduate Student Member, IEEE) received the B.Sc. degree in electrical and electronics engineering from Bogazici University, Istanbul, Turkey, in 2017, and the M.Sc. degree in electronics engineering from Politecnico di Milano, Milan, Italy, in 2019. He is currently pursuing the Ph.D. degree with the Institute of Radio Frequency Engineering and Electronics, Karlsruhe Institute of Technology, Karlsruhe, Germany.

His research interests include silicon-based transceivers, components for millimeter-wave systems, and high-power SiGe amplifiers.

Ahmet Çağrı Ulusoy (Senior Member, IEEE) received the B.Sc. degree in electrical engineering from Istanbul Technical University, Istanbul, Turkey, in 2006, and the M.Sc. and Ph.D. degrees in electrical engineering from Ulm University, Ulm, Germany, in 2008 and 2012, respectively.

From 2012 to 2015, he was with Georgia Institute of Technology, Atlanta, GA, USA, as a Research Engineer. From 2015 to 2016, he was the Team Leader of the Broadband Mixed-Signal ICs Group, IHP, Frankfurt (Oder), Germany. From 2016 to 2019,

he was an Assistant Professor with Michigan State University, East Lansing, MI, USA. In January 2019, he became a Full Professor with Karlsruhe Institute of Technology, Karlsruhe, Germany, and the Director of the Institute of Radio Frequency Engineering and Electronics. He has authored or co-authored more than 150 publications in this field. His research interests include the broad area of high-frequency integrated circuits and systems.

Dr. Ulusoy was a recipient and a co-recipient of several Best Paper Awards. His dissertation received the Südwestmetall Young Scientist Award. He is a member of the Microwave Theory and Techniques Society and the Chair of Technical Committee 14. He served as the Chair for the IEEE Topical Meeting on Silicon Monolithic Integrated Circuits in RF Systems and as the TPC Chair for the IEEE International Conference on Microwaves for Intelligent Mobility. He served as an Associate Editor for IEEE MICROWAVE WIRELESS COMPONENT LETTERS.