# A Cryogenic Gallium Nitride Full Bridge for Use in a Thermally Insulating Dual Active Bridge

1<sup>st</sup> Frank, S.R.

2<sup>nd</sup> Stroebele, T.

3<sup>rd</sup> Swoboda, P.

Institute of Electrical Engineering (ETI) Institute of Electrical Engineering (ETI) Institute of Electrical Engineering (ETI)

Karlsruhe Institute of Technology (KIT), Karlsruhe Institute of Technology (KIT), Karlsruhe Institute of Technology (KIT),

Karlsruhe, Germany

S.frank@kit.edu thomas.stroebele@student.kit.edu philipp.swoboda@kit.edu

4th Schwendemann, R.

Institute of Electrical Engineering (ETI)

Karlsruhe Institute of Technology (KIT),

Karlsruhe, Germany

ruediger.schwendemann@kit.edu

5<sup>th</sup> Hiller, M.

Institute of Electrical Engineering (ETI)

Karlsruhe Institute of Technology (KIT),

Karlsruhe, Germany

marc.hiller@kit.edu

Abstract—In this paper, a Liquid Nitrogen ( $LN_2$ ) cooled Gallium Nitride (GaN) Cryogenic Full Bridge (CFB) is presented as part of a Dual Active Bridge (DAB) for use in a hybrid Liquid Hydrogen ( $LH_2$ ) High Temperature Superconductor (HTS) transmission line. The concept of a 20 kW DAB with cryogenic parts is outlined and the design of the CFB as one of the cryogenic parts is presented. Furthermore, the construction of a cryogenic test bench is described which is used to validate the functionality of the CFB and to characterize it. Finally, the first measurements of the prototype down to 82 Kelvin are presented, which confirm the increased efficiency of the GaN semiconductors at cryogenic temperatures.

Index Terms—Wide-Bandgap, GaN, Cryogenic, Dual Active Bridge (DAB), Measurements

#### I. MOTIVATION

Due to the increasing number of superconducting applications, such as superconducting drives for electric aviation [1], [2], generators for energy production [3], [4] or cables for energy transmission [5], [6], the operation of power electronics in combination with superconducting applications is becoming an increasingly important research topic.

Nowadays, power electronics work at much higher ambient temperatures than the cryogenic system and the connection between these two parts is made with copper-based current supplies, which leads to a high heat input into the cryogenic area. This in turn increases the necessary cooling power and thus reduces the overall efficiency of the system. One way of reducing the heat input is to replace the copper-based current supplies with a galvanically isolated converter, whereby the galvanic isolation also serves as a thermal barrier to separate the cryogenic area from the environment.

Therefore, one part of the power electronics operates in the cryogenic temperature range which, depending on the used semiconductor material and component technology, leads to lower conduction and switching losses and thus even further increases the system efficiency [7]. This paper will investigate the opportunity to improve efficiency by using semi-cryogenic

converters instead of copper feeders. For this purpose, a widely used galvanically isolated converter topology, the DAB, is examined.

This work is motivated by an  $LH_2$  project, in which a hybrid  $LH_2$ -HTS transmission line, similar to the idea pointed out in [8], is developed and constructed. Due to the cryogenic boiling temperature of the hydrogen of  $21.15\,\mathrm{K}$  [9] the system intrinsically provides the low temperatures necessary for superconductor operation, which additionally can be used for cooling the power electronics as well.

The paper is structured into six sections. In the following section II, the concept of a DAB with cryogenic converter parts is outlined. One of the cryogenic parts, the CFB is described in detail in section III. The construction of a cryogenic test bench, with which the functionality of the CFB is validated, is pointed out in section IV. First measurements are presented in section V. Finally, in section VI a summary and an outlook is given.

# II. CRYOGENIC GALLIUM NITRIDE BASED DUAL ACTIVE BRIDGE

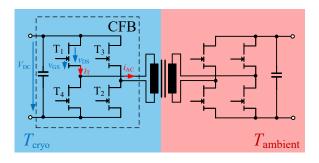

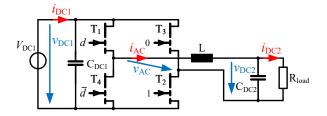

A possible topology with an intrinsic galvanic isolation is the DAB [10]. This circuit basically consists of two full bridge circuits, connected to a Medium Frequency (MF) or High Frequency (HF) transformer, allowing a magnetically coupled energy transmission. Both, the input and output port are DC ports, making this topology suitable for the interface connection of an HTS. In the following, the design of such a DAB operating at the transition between the cryogenic and the ambient temperature system parts is described. The topology is depicted in Fig. 1.

One of the two full bridges, the CFB, and one of the transformer windings work at cryogenic temperatures. The second full bridge, second winding and the transformer core operate at ambient temperature. Hence, the thermal insulation is between both transformer windings which is challenging

Fig. 1: DAB with CFB and thermally insulating transformer

for the transformer design. The idea is similar to the setup published in [11], but instead of silicon semiconductors GaN-HEMTs are used, allowing higher switching frequencies and therefore a more compact transformer design.

Due to the promising cryogenic behavior of GaN-HEMTs [12]–[15], the GS66516T transistors [16] from Infineon/GaN Systems are used in this work. These are  $650\,\mathrm{V}$ ,  $60\,\mathrm{A}$  rated devices resulting in a DC link voltage  $V_\mathrm{DC}$  of  $400\,\mathrm{V}$  and a desired rated power  $P_\mathrm{N}$  of  $20\,\mathrm{kW}$ . When operating the DAB in Single Phase Shift (SPS) mode, the transmitted power is controlled by the phase shift  $\varphi$  between the voltages of the two full bridges. With the equations given in [10] the transmitted power can be calculated for a 1:1 transformer ratio to

$$P = \frac{V_{\rm DC1} \cdot V_{\rm DC2} \cdot \varphi}{2 \cdot \pi \cdot L_{\sigma} \cdot f_{\rm sw}} \cdot \left(1 - \frac{|\varphi|}{\pi}\right). \tag{1}$$

The maximum power is transmitted for  $\varphi=\frac{\pi}{2}$ . It is proportional to the DC voltages  $V_{\rm DC1}$ ,  $V_{\rm DC2}$  and inversely proportional to the stray inductance  $L_{\sigma}$  of the transformer and the switching frequency  $f_{\rm sw}$ . To keep the design simple, the two DC link voltages are chosen  $V_{\rm DC1}=V_{\rm DC2}=V_{\rm DC}$  equal. To reach the desired power of  $P_{\rm N}=20\,{\rm kW}$  with the given DC link voltage  $V_{\rm DC}$ , the product of  $L_{\sigma}\cdot f_{\rm s}$  must not exceed  $1\,{\rm H\,s^{-1}}$ . Hence, the maximum switching frequency is limited by the stray inductance of the transformer.

The detailed transformer design will be published in a subsequent paper. However, first analytic calculations and Finite Element Method (FEM) simulations showed an expected value of the stray inductance  $L_{\sigma}$  in the range of 2.5..7 µH, highly dependent on the gap between the ambient primary and cryogenic secondary winding. Here, an optimum is to be found to ensure thermal insulation on the one hand and to reduce the stray inductance of the transformer for reaching the rated power of  $20\,\mathrm{kW}$  on the other hand. With the simulated values for the stray inductance, the rated switching frequency was set to  $f_{\mathrm{sw}}=100\,\mathrm{kHz}$ . The design characteristics of the DAB are summarized in Tab. I.

To increase the transmitted power, several GaN-DAB cells can be connected in series and parallel. Furthermore, due to the positive temperature coefficient of the on-resistance  $R_{\rm DS,on}$  and the negative temperature coefficient of the transconduc-

TABLE I: Design characteristics of the proposed cryogenic DAB

| Semiconductors                            | GaN Systems GS66516T |

|-------------------------------------------|----------------------|

| Rated power $P_{\rm N}$                   | $20\mathrm{kW}$      |

| DC link voltage $V_{\mathrm{DC}}$         | $400\mathrm{V}$      |

| Switching frequency $f_{\rm sw}$          | $100\mathrm{kHz}$    |

| Stray inductance transformer $L_{\sigma}$ | $2.57\mathrm{\mu H}$ |

|                                           |                      |

tance  $g_{\rm m}$  over the full temperature range down to 93 K, as shown in [12], [14], a direct parallelization of GaN-HEMTs even at cryogenic temperatures is suitable and promising.

The power electronics design of both full bridges, the cryogenic and the conventional one, is identical, offering a direct comparison of the circuits. The difference only lies in the cooling. While the "warm" full bridge is cooled using conventional water cooling, the cryogenic one is  $LN_2$  cooled.  $LN_2$  is used because of its low boiling point at  $77.15 \, K$  [9], its good availability and for safety reasons. The detailed design of the full bridge is outlined in the next section.

# III. DESIGN OF THE CRYOGENIC FULL BRIDGE

The challenge in designing the CFB is to ensure a safe operation of all components at cryogenic temperatures. While the GaN-HEMTs itself are suitable for temperatures down to 77 K, care must be taken into a proper selection of the other necessary components such as the DC link capacitors, the gate-drivers and their power supplies.

A split DC link is used, consisting of six 100 nF NPO ceramic capacitors as primary link and a single 210 µF Polypropylene (PP) secondary capacitor. According to [7] both capacitor types are suitable for cryogenic temperatures. As gate driver two SI8275AB-IS1 isolated half-bridge ICs from Skyworks are used. Several cryogenic measurements with this driver family are reported in [17] and [18], showing a successful operation at temperatures down to 77 K. The isolated power supply of the drivers at cryogenic temperatures is challenging. An overview of several DC/DC converters exposed to 77 K is given in [18], showing that none of the investigated devices performs well at cryogenic temperatures. For that reason, the proposed design positions the power supplies spatially separated from the gate drivers and the GaN-HEMTs, offering a thermal insulation. The thermal conductivity between the cold power section and the "warm" signal processing section on the Printed Circuit Board (PCB) is further reduced by board cut-outs. Note that the complete gate loop itself, consisting of the GaN-HEMT, the gate driver, the gate resistors and buffer capacitors is located in the cold section and therefore stays as small as possible. Furthermore, the power supplies can be heated by optional heating resistors if necessary. To measure the on-resistance of the GaN devices, the clamping circuit presented in [19] is used. The measurement principle is described in detail in section V.

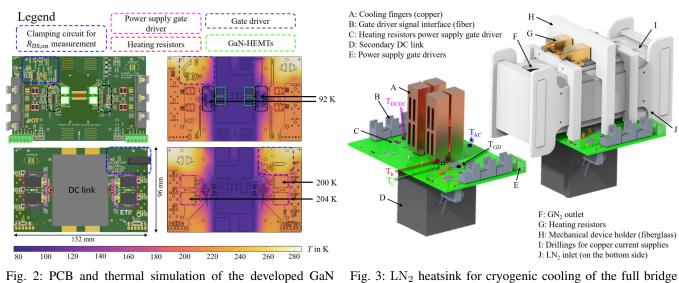

The PCB design and the results of a thermal steady state simulation are shown in Fig. 2. The simulation was performed

Fig. 2: PCB and thermal simulation of the developed GaN

with COMSOL Multiphysics, using the heat transfer and thermal radiation module. As the entire PCB is later located in a vacuum, no convection is considered. Several simplifications are made. All electronic components are defined as solid copper bodies, the case temperature of the GaN-HEMTs is set to constant 77 K and the ambient temperature, which is relevant for the thermal radiation calculation, is set to 300 K. The aim of the simulation is to validate the thermal insulation between the power part in the middle of the PCB and the signal processing part on the left and right side. This separation is clearly visible in Fig. 2. While the temperatures of the GaN-HEMTs, DC capacitors and gate drivers remain below 100 K, the power supply for the gate drivers, consisting of four MGN1D050603MC-R13 DC/DC converters, reaches temperatures equal or greater than 200 K.

### IV. DESIGN OF THE CRYOGENIC POWER ELECTRONICS TEST BENCH

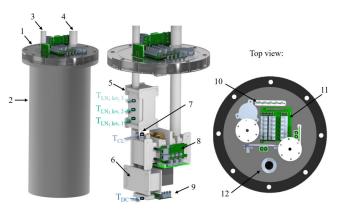

Instead of putting the whole setup into  $LN_2$ , an indirect cooling with finger-shaped copper heat sinks is used to ensure that only the GaN-HEMTs are cooled. This concept is pictured in Fig. 3. One end of the cooling fingers is placed on the top-side cooled transistors. As Thermal Interface Material (TIM) indium foil is used since indium has a high thermal conductivity of  $\lambda_{\rm Indium} = 81.6\,{\rm W\,K^{-1}\,m^{-1}}$  and shows good formability [9], leading to smaller thermal contact resistances. The thermal resistance of the TIM layer is calculated using

$$R_{\rm th,TIM} = \frac{1}{\lambda_{\rm Indium}} \cdot \frac{d_{\rm TIM}}{A_{\rm HEMT}}.$$

(2)

With a thickness  $d_{\text{TIM}}$  of 200 µm and a cooling pad area  $A_{\rm HEMT}$  of  $8.27\,{\rm mm}\cdot 5.64\,{\rm mm}$  [16] the thermal resistance  $R_{\rm th,TIM}$  of the TIM layer is about  $\approx 0.05\,\rm K\,W^{-1}$ . Similarly, the thermal resistance of one copper finger can be estimated to  $R_{\rm th,h} \approx 0.26\,{\rm K\,W^{-1}}$ . The fingers are glued into a rectangular

fiberglass pipe, using Stycast1266. Before operation, LN<sub>2</sub> is fed into the pipe. During operation, the heat dissipating into the  $LN_2$  causes it to evaporate at the cooling fingers. Assuming maximum semiconductor losses  $P_{\rm loss, HEMT}$  of 25 W for a single transistor leads to a maximum case temperature  $T_{\rm c}$  of

$$T_{\rm c} = P_{\rm loss, HEMT} \cdot (R_{\rm th, TIM} + R_{\rm th, h}) + T_{\rm LN2} \approx 85 \,\mathrm{K}$$

(3)

For simplification, the thermal contact resistance from copper to LN2 is neglected and the constant LN2 boiling temperature is assumed at the contact surface of the copper fingers with the liquid. To keep the thermal contact resistance as small as possible, several cut-outs increase the surface area.

A siphon design as shown in Fig. 4 lets the emerging Gaseous Nitrogen (GN<sub>2</sub>) only escape via an outlet pipe. By measuring the evaporation rate, the heat flow into LN<sub>2</sub> and hence the occurring losses of the power converter can be determined. For dimensioning the whole LN<sub>2</sub> piping, the evaporation rate for a continuous CFB operation is taken. As the worst-case scenario semiconductor losses  $P_{loss,tot}$  of 100 W are considered. These can be converted into the evaporation rate of the nitrogen using

$$\dot{V}_{\rm LN2} = 2 \cdot M_{\rm N} \cdot P_{\rm loss,tot} \cdot \frac{1}{\rho_{\rm LN2} \cdot \Delta H_{\rm vap,N}}.$$

(4)

With the molar mass  $M_{\rm N} \approx 14.007\,{\rm g\,mol}^{-1}$ , the mass density  $\rho_{\rm LN2} \approx 0.81\,{\rm kg}\,{\rm L}^{-1}$  and the evaporation enthalpy of  $\Delta H_{\rm vap,N} \approx 5.58\,{\rm kJ\,mol}^{-1}$  of  ${\rm LN_2}$  as given in [9], follows a volume flow rate of  $\dot{V}_{\rm LN2} \approx 0.62\,{\rm mL\,s}^{-1}$  for the liquid. With its much lower mass density  $\rho_{\rm GN2} \approx 1.25\,{\rm g\,L^{-1}}$  the volume flow rate of the vaporizing nitrogen is  $V_{\rm GN2} \approx 402\,{\rm mL\,s^{-1}}$ . For the GN<sub>2</sub>, pipes with 26 mm inner diameter are taken, resulting in flow rates smaller than  $v_{\text{max,GN2}} = 0.757 \,\text{m}\,\text{s}^{-1}$ . The pipes for  $LN_2$  have an inner diameter of  $17 \, \mathrm{mm}$  which is chosen to simplify and accelerate the LN2 filling. Smaller diameters make filling more difficult due to evaporation through contact with the warm pipe wall.

To enable measurements at a defined temperature above the boiling temperature of nitrogen, heating resistors are mounted on the other side of the cooling fingers (cf. Fig. 3). The temperatures at different locations (cf. Fig. 3 and Fig. 4) are measured and supervised using PT1000 temperature sensors. For galvanic isolation, the AMC3336 Analog Digital Converter (ADC) is used, enabling e.g. a measurement directly between the cooling fingers and the case of the GaN-HEMT. The same sensor type is used to measure the LN<sub>2</sub> level inside the LN<sub>2</sub> tank.

- 1: Vacuum cover

- 2: Vacuum chamber

- 4: LN<sub>2</sub> outlet

- 5: LN<sub>2</sub> tank 6: LN<sub>2</sub> siphon

- 8: Temperature measurement

- 9: Voltage and current meas. 10: Measurement feedthrough

- 11: Signal feedthrough

- 12: Vacuum pump connection

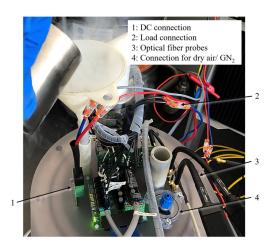

Fig. 4: Cryogenic test bench for CFB characterization

To prevent icing of the CFB, the whole setup operates in a hermetic chamber, that can be either flooded with GN2 or dry compressed air. Alternatively, it can be evacuated. In the intended DAB operation, an evacuated chamber is desired to prevent any convective flow of heat. To monitor the pressure, a PVC4100 vacuum transducer based on a Pirani sensor is used. However, the results presented in this paper are measured with dry air at ambient pressure, due to microcracks at several adhesive joints detected after the first cryogenic measurements, caused by different expansion coefficients of various fiberglass materials and copper. However, further cryogenic measurements are still possible since the leakage rates through the microcracks are small enough.

The DC port, AC port, the gate signals and all measurement signals are routed outside using in-house developed vacuum feedthroughs, consisting of several PCBs that are glued into the vacuum chambers cover.

#### V. MEASUREMENTS

This section presents cryogenic measurements of the developed CFB. First, the correct function of the circuit is validated at cryogenic temperatures by applying single pulses to the circuit. The recorded traces are used to determine the onresistance  $R_{\mathrm{DS,on}}$  over the full temperature range of the case

temperature  $T_{\rm c}$  from Room Temperature (RT) down to 82 K. Furthermore, the temperature distribution in the test setup and on the power PCB is examined in more detail. Eventually, the continuous operation of the circuit is investigated.

## A. Functional Testing at Cryogenic Temperatures

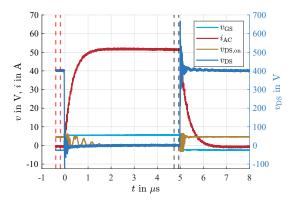

For the functional test, an ohmic load with a parasitic inductive component is connected to the AC terminals of the CFB and single pulses are applied at different DC link voltages. The waveforms of  $v_{\rm GS}$ ,  $v_{\rm DS}$  and  $v_{\rm DS,on}$  of transistor T1 (cf. Fig. 1) as well as of the load current  $i_{AC}$  are recorded. The voltage  $v_{\rm DS,on}$  is measured using the clamping circuit shown in Fig. 8 and corresponds to the drain-to-source voltage of T1 during on-state.

For all voltage measurements, optically isolated probes are deployed, Tab. II shows a list of the measuring devices used. The constructed test bench during the cooling phase is shown in Fig. 5. Before every cryogenic measurement, the chamber is flooded with dry air. A Sensirion SHT21 humidity sensor monitors the humidity inside to prevent icing. After ensuring a relative humidity smaller than 10 %, the cooling starts by pouring LN<sub>2</sub> into the fiberglass pipe. The case temperature can be adjusted via the filling rate. To reduce the mechanical stress on the cooled parts, the rate should be moderate, resulting in a test duration of  $\approx 3 \,\mathrm{h}$  for the entire series of measurements.

TABLE II: Measurement setup on-resistance measurements

Oscilloscope Probe for  $v_{\mathrm{GS}}$  measurement Probe for  $v_{\mathrm{DS}}$  measurement Probe for  $v_{\mathrm{DS,on}}$  measurement Probe for  $i_{AC}$  measurement

LeCroy Wavesurfer 4104HD, 12 bit, 1 GHz PMK Firefly FF-1500 with FF-MMCX-25V tip Micsig MOIP02P with OP500-2 tip Micsig MOIP02P with OP10-2 tip CWT CWTUM/1/B Rogowski coil 300 A, 9 Hz - 30 MHz

Fig. 5: Test bench for cryogenic measurements

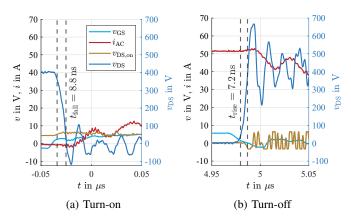

The results for a DC link voltage  $V_{\rm DC}$  of  $400\,{\rm V}$  and a load resistor  $R_{\rm load}$  of  $7.5\,\Omega$  at case temperature  $T_{\rm c}$  of  $99\,{\rm K}$  are shown in Fig. 6 for a complete switching period, Fig. 7 focuses on the turn-on and turn-off event. In the latter, the fall time  $t_{\rm fall,cryo}=8.8\,{\rm ns}$  and rise time  $t_{\rm rise,cryo}=7.2\,{\rm ns}$  of the drainto-source voltage  $v_{\rm DS}$  are marked. The values  $t_{\rm fall,rt}=9.6\,{\rm ns}$  and  $t_{\rm rise,rt}=6\,{\rm ns}$  at RT are similar.

At the turn-off event a high overvoltage resulting in a maximum drain-to-source voltage  $v_{\rm DS,max}$  of  $\approx 667\,{\rm V}$  occurs (cf. Fig. 7b). However, it could be proven that this overvoltage is caused by the developed feedthrough PCB of the measurement signals and does not correspond to the real voltage across the semiconductor. Measurements at RT with and without the feedthrough show that the voltage directly at the GaN HEMT is only  $\approx 513\,{\rm V}$ . Hence, the transients measured at cryogenic temperatures with the feedthrough are not reliable. Nevertheless, the stationary end values used e.g. for the  $R_{\rm DS,on}$  calculation are not significantly influenced.

Fig. 6: Waveforms for one switching period at  $T_{\rm c}=99\,{\rm K},$   $V_{\rm DC}=400\,{\rm V}$  and  $R_{\rm load}=7.5\,\Omega$

When looking at the gate voltage  $v_{\rm GS}$ , a reduction of the absolute values of the positive and negative driver voltage supplied by the MGN1D050603MC-R13 DC/DC converter is observed. During operation at RT, the positive and negative voltages  $v_{\rm GS,pos}$  and  $v_{\rm GS,neg}$  are  $5.85\,\mathrm{V}$  and  $-2.81\,\mathrm{V}$ , respectively. These voltages drop to  $5.6\,\mathrm{V}$  or  $-2.56\,\mathrm{V}$  during the cooling process down to the DC/DC converter temperature  $T_{\rm DCDC}$  of  $\approx 150\,\mathrm{K}$ . To compensate for this drop, the inte-

Fig. 7: (a) Turn-on and (b) turn-off events at  $T_{\rm c}=99\,{\rm K},$   $V_{\rm DC}$  =  $400\,{\rm V}$  and  $R_{\rm load}=7.5\,\Omega$

grated heating resistors can be used to increase the temperature  $T_{\rm DCDC}$  up to  $\approx 180\,\rm K$  and thus the voltages to  $5.68\,\rm V$  and  $-2.72\,\rm V$ .

In total, the functionality of the CFB is validated over the complete investigated temperature range down to  $T_{\rm c}\approx 82\,{\rm K}$ . Even at the minimum measured temperature  $T_{\rm DCDC}\approx 150\,{\rm K}$  that corresponds to  $T_{\rm c}=82\,{\rm K}$  (cf. Fig. 12a) and without using the optional heating resistors, the DC/DC converter voltages are high enough to ensure safe switching.

#### B. Wide Temperature Range On-Resistance Measurement

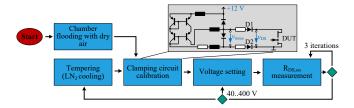

The traces shown in Fig. 6 are used for determining the onresistance  $R_{\rm DS,on}.$  In the interval between the two red dotted lines, the offset of  $i_{\rm AC}$  is measured and between the two black dotted lines, the values of  $i_{\rm AC}$  and  $v_{\rm DS,on}$  are averaged for the  $R_{\rm DS,on}$  calculation. Hence, these traces are recorded for each operation temperature. The temperature range of the case temperature  $T_{\rm c}$  for the measurement is from RT down to  $\approx 82\,{\rm K}$  in  $\approx 25\,{\rm K}$  steps. At each temperature, calibration of the clamping circuit and variation of different DC link voltages  $V_{\rm DC}$  from  $40\,{\rm V}$  to  $400\,{\rm V}$  are performed. Three measurements with a constant ohmic load are recorded for all operating points. The procedure is shown in Fig. 8.

Fig. 8: Procedure of the cryogenic  $R_{\rm DS,on}$  measurement

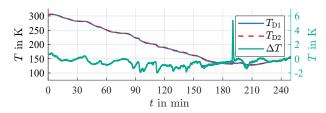

As mentioned in section III, the clamping circuit described in [19] is used for measuring the voltage  $V_{\rm DS}$  during on-state. The circuit is pictured in Fig. 8. It is based on a current mirror and several clamping diodes. The diodes  ${\rm D_1}$  and  ${\rm D_2}$  are within the measurement path. Hence, both diodes must show identical behavior to ensure that the forward voltage across both diodes during the on-state of the transistor is identical. Further, they must operate at the same temperature. Temperature sensors are attached to both diodes to monitor their temperatures  $T_{\rm D1}$  and  $T_{\rm D2}$  during the measurement series.

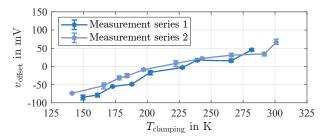

Fig. 9: Temperatures of the clamping diodes during the entire cryogenic experiment

The results are depicted in Fig. 9. As shown, the difference between both temperatures  $\Delta T$  stays smaller than  $2\,\mathrm{K}$  for

the whole measurement series until  $t=180\,\mathrm{min}$ . However, when measuring the voltage  $v_{\mathrm{meas}}$  (cf. Fig. 8) without any load, but turned on transistor at different temperatures, the temperature-dependent offset-voltage  $v_{\mathrm{offset}}$  depicted in Fig. 10  $(T_{\mathrm{clamping}}=(T_{\mathrm{D1}}+T_{\mathrm{D2}})/2)$  can be observed. For this reason, the aforementioned calibration of the clamping circuit is carried out for every operation temperature.

Fig. 10: Offset voltage of the clamping circuit

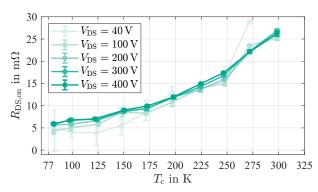

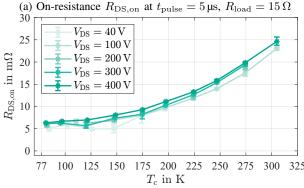

In Fig. 10 and the following graphs, the asterisks mark the measured mean values and the bars are the minimum and maximum values. The measured on-resistance values  $R_{\rm DS,on}$  for a constant ohmic load  $R_{\rm load}$  of  $15\,\Omega$  or  $7.5\,\Omega$  and various DC link voltages  $V_{\rm DC}$  are depicted over the entire temperature range in Fig.11a and Fig. 11b. Note, that the CFB is rated for a DC link voltage  $V_{\rm DC}$  of  $400\,\rm V$ .

(b) On-resistance  $R_{\rm DS,on}$  at  $t_{\rm pulse}=5\,\mu {\rm s},~R_{\rm load}=7.5\,\Omega$

Fig. 11: On-resistance  $R_{\rm DS,on}$  measurements

Compared to RT, a reduction in resistance by a factor of  $\approx 5$  can be achieved for a case temperature  $T_c$  of  $\approx 82\,\mathrm{K}$ .

Particularly at low voltages and  $R_{\rm load}=15\,\Omega$ , a large fluctuation in the measured values is observed. This can be explained by the low voltages  $v_{\rm DS,on}$  in the order of a few  $10\,{\rm mV}$  for these operation points.

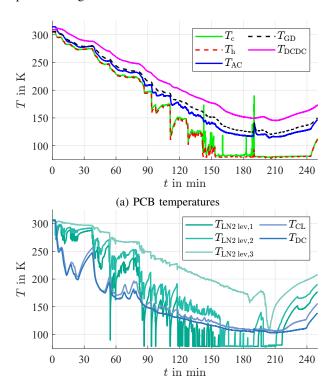

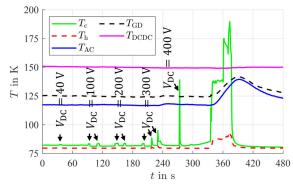

#### C. Cryogenic Temperature Distribution

To monitor the temperature at various points of the CFB during a complete cryogenic measurement, the temperature sensors shown in Fig. 3 and Fig. 4 are used. Their results are depicted in Fig. 12.

(b) Temperatures of the test bench

Fig. 12: Temperatures during the entire cryogenic experiment

Over the first  $\approx 160\,\mathrm{min}$  the  $R_\mathrm{DS,on}$  measurement is carried out. The plateaus with constant  $T_\mathrm{c}$  are recognizable. Further, it is visible, that until  $\approx 140\,\mathrm{min}$  the temperatures of the cooling finger  $T_\mathrm{h}$  and directly above the case  $T_\mathrm{c}$  are almost identical. Afterwards, there are deviations for around  $20\,\mathrm{min}$ , until they are almost identical again. It can be assumed that the proper thermal contact between the cooling finger and the transistor is no longer present at the beginning of this interval. This leads to a significantly increased thermal resistance which in turn limits the maximum coolable power dissipation of the transistor. During the time range from  $\approx 180\,\mathrm{min}$  to  $\approx 195\,\mathrm{min}$  measurements with continuous switching are conducted. From  $t\approx 210\,\mathrm{min}$ , the system heats up again.

The sensors  $T_{\rm LN2lev,1}$ ,  $T_{\rm LN2lev,2}$  and  $T_{\rm LN2lev,3}$  are for monitoring the LN<sub>2</sub> level. Immersed in LN<sub>2</sub>, they show 77 K, otherwise the value is significantly higher. Their measured values can be used to determine the evaporation rate during the warm-up process of the setup. The sensors are each  $4~\rm cm$  apart

which corresponds to a volume of  $\approx 120\,\mathrm{mL}$  enclosed by the sensors in this setup. When comparing  $T_{\mathrm{LN2lev},1}$  and  $T_{\mathrm{LN2lev},2}$  after  $t=210\,\mathrm{min}$ , the time between  $T_{\mathrm{LN2lev},1}$  leaving  $\mathrm{LN_2}$  and  $T_{\mathrm{LN2lev},2}$  leaving  $\mathrm{LN_2}$  is determined to  $\approx 5.5\,\mathrm{min}$ , resulting in an evaporation rate  $\dot{V}_{\mathrm{LN2}}$  of  $\approx 0.36\,\mathrm{mL\,s^{-1}}$ . With (4) this can be translated into a heat input of  $\approx 58\,\mathrm{W}$  with the power electronics turned off. Note, that this is only a rough estimation for the heat input without any load. In the final setup, this heat input offset is expected to be much less, due to the convection prevented by the vacuum. In addition to the method described below with the power meter, the calorimetric approach described here using the evaporation rate of the  $\mathrm{LN_2}$  can also be used to measure the efficiency.

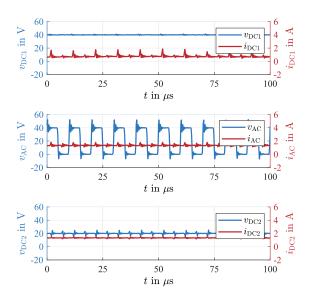

#### D. Continuous Operation

In this section the continuous operation of the CFB at cryogenic temperatures is analyzed. The circuit operates in buck mode as shown in Fig. 13. A constant ohmic load  $R_{\rm load}$  of  $15\,\Omega$  and an open loop control with a switching frequency  $f_{\rm sw}$  of  $100\,{\rm kHz}$  and a duty cycle d of 0.5 are applied. The choke has an inductance L of  $1\,{\rm mH}$ .

Fig. 13: Continuous operation of the CFB in buck mode

During operation the input voltage  $v_{\rm DC1}$ , the input current  $i_{\rm DC1}$ , the output voltage  $v_{\rm DC2}$ , the output current  $i_{\rm DC2}$  and the AC voltage  $v_{\rm AC}$  and current  $i_{\rm AC}$  are measured with a DEWETRON DEWE3-PA8-RM power meter. For current measurement, Signaltec CT100 current transducers are used. The voltages are measured directly with DEWETRON's TRION3 1810M-PA module.

The continuous operation is performed after the  $R_{\rm DS,on}$  measurement described in subsection V-B, when the CFB is cooled down to case temperature Tc of  $82\,\rm K$ . The first measurement is performed for around  $5\,\rm s$  with a DC link voltage  $V_{\rm DC}$  of  $40\,\rm V$ . Figure 14 shows the recorded traces for a time interval of  $100\,\rm \mu s$ .

The efficiency calculated from the measured traces in this operation point  $\eta_{\rm meas,cryo}$  is  $\approx 97.65\,\%$ . A *PLECS* simulation with the circuit parameters and the semiconductor model from *GaN Systems* with extrapolated losses for the cryogenic region gives for RT an efficiency  $\eta_{\rm sim,rt}$  of  $\approx 97.13\,\%$ . For a case temperature Tc of  $82\,\rm K$  an efficiency  $\eta_{\rm sim,cryo}$  of  $\approx 98.02\,\%$  is simulated. Therefore, the measured efficiency at cryogenic temperature is higher than the simulated efficiency at RT.

The efficiency values pointed out are quite low, due to the low DC link voltage  $V_{\rm DC}$  of 40 V, which is only one-tenth of the rated voltage. Further, the limited accuracy of

Fig. 14: Voltage and current traces for buck-mode continuous operation (cf. Fig. 13 for the current and voltage definitions)

the power meter, especially for low current and voltage values has to be considered. However, it is not possible with the current test bench to reach stable continuous operation for higher voltages, due to the loss of the proper thermal connection between the semiconductor and the cooling finger, as assumed in subsection V-C. This is investigated further in detail. Figure 15 therefore shows the zoomed time interval from Fig. 12a for the period of the continuous measurement. At  $t \approx 35 \,\mathrm{s}$ , the measurement with the DC link voltage  $V_{\mathrm{DC}}$  of  $40\,\mathrm{V}$  is performed. When evaluating the case temperature  $T_{\mathrm{c}}$ , an increase  $\Delta T_{\rm meas}$  of about 0.6 K during switching can be detected. Comparing this measured value with the simulated temperature increase  $\Delta T_{\rm sim}$  of only 20 mK, it can be assumed that the theoretically calculated thermal resistance  $R_{\rm th,TIM}$ from section IV is significantly lower than the real effective resistance.

Fig. 15: Temperatures for buck-mode continuous operation

Further tests with higher DC voltages are shown in Fig. 15. A power limitation of the power supply unit was activated for these measurements, which limits the output power  $P_{\rm DC1}$  to

$100\,\mathrm{W}$  after a few milliseconds. The peaks in the case temperature  $T_\mathrm{c}$ , visible from the  $300\,\mathrm{V}$  measurements onwards, result from this limitation and the insufficient thermal connection of the semiconductors. With the  $400\,\mathrm{V}$  measurement, the increased thermal resistance leads to a temperature increase in the case temperature  $T_\mathrm{c}$  of more than  $100\,\mathrm{K}$  which ultimately leads to the destruction of the semiconductor at around  $335\,\mathrm{s}$ .

For that reason, in a future design care must be taken to a better thermal connection between the heatsink and the case of the transistor. This can be realized, for example, by increasing the contact pressure with spring screws. With those, the thermal contraction of the copper finger, which is around 250 µm in the current design, can be compensated.

#### VI. SUMMARY AND OUTLOOK

This paper introduces a LN2 cooled full bridge circuit, based on GaN-HEMTs for the use within a thermally insulating DAB, rated with  $P_{\rm N}=20\,{\rm kW},\ V_{\rm DC}=400\,{\rm V}.$  The dimensioning and design of the power PCB and the whole cryogenic test bench are outlined. First measurements show a successful single pulse operation over the complete currentvoltage-temperature operation range up to  $V_{\rm DC} = 400 \, {\rm V}$ ,  $I_{\rm T} \approx 50\,{\rm A}$  and down to  $T_{\rm c} = 82\,{\rm K}$ . The on-resistance is reduced by a factor of five at  $T_{\rm c}\,=\,82\,{\rm K}$  compared to operation at RT. The cryogenic behavior of the gate driver and measurement circuit are described in detail. All circuits operate successfully over the whole temperature range. In addition, various temperature sensors allow the temperature distribution throughout the converter to be monitored. This information can be used e.g. to monitor the thermal connection of the semiconductors or to calculate the heat input into the system. The continuous operation of the circuit in buck mode at cryogenic temperatures was demonstrated for a DC link voltage of 40 V. An improved efficiency was measured for this operation point compared to operation at RT, which still has to be proven for higher DC link voltages and currents.

Therefore, future work includes appropriate improvements in the thermal connection of the semiconductors, which will allow continuous operation at rated power and rated voltage. To solve the problem of microcracks described in section IV, the fiberglass/copper combination will be replaced by all-metal heat sinks. This will allow the operation under a vacuum. Moreover, the development and construction of the thermally insulated transformer will be finished. Finally, the complete system, consisting of two back-to-back connected DABs, will be realized and characterized.

#### ACKNOWLEDGMENT

This work was carried out within the hydrogen flagship project TransHyDE and was funded by the Federal Ministry of Education and Research under the funding grant number 03HY204A. The responsibility for the content of this publication lies with the authors.

#### REFERENCES

- P. Alvarez, M. Satrústegui, S. G. Scheifler, J. Bastarrarena, L. G. López, and M. Martinez-Iturralde, "Design of a HTS 2 MW Electric Motor for Single-Aisle Regional Aircraft," *IEEE Access*, vol. 11, pp. 144 325– 144 336, 2023.

- [2] Y. Wang, L. Zhou, Q. Yuan, and X. Song, "Feasibility Study of High Temperature Superconducting Machines for Electric Aircraft," in 2024 IEEE 7th International Electrical and Energy Conference (CIEEC), 2024, pp. 1082–1087.

- [3] S. Miura, M. Iwakuma, and T. Izumi, "Lightweight Design of Tens-MW Fully-Superconducting Wind Turbine Generators With High-Performance REBa2Cu3Oy Wires," *IEEE Transactions on Applied Superconductivity*, vol. 30, no. 4, pp. 1–6, 2020.

- [4] S. Lengsfeld, J. Grundmann, M. Oomen, C. Vargas-Llanos, B. Ponick, and M. Jung, "Comparing Armature Windings for a 10 MW Fully Superconducting Synchronous Wind Turbine Generator," in 2022 12th International Conference on Power, Energy and Electrical Engineering (CPEEE), 2022, pp. 49–53.

- [5] M. Stemmle, F. Merschel, M. Noe, L. Hofmann, and A. Hobl, "Super-conducting MV cables to replace HV cables in urban area distribution grids," in *PES T&D 2012*, 2012, pp. 1–5.

- [6] A. Allais, J.-M. Saugrain, B. West, N. Lallouet, H. Caron, D. Ferandelle, L. Terrien, G. Bouvier, G. Hajiri, K. Berger, and L. Quéval, "SuperRail-World-First HTS Cable to be Installed on a Railway Network in France," *IEEE Transactions on Applied Superconductivity*, vol. 34, no. 3, pp. 1–7, 2024.

- [7] H. Gui et al., "Review of Power Electronics Components at Cryogenic Temperatures," *IEEE Transactions on Power Electronics*, vol. 35, no. 5, pp. 5144–5156, 2020.

- [8] V. Vysotsky, I. Antyukhov, V. Firsov, E. Blagov, V. Kostyuk, A. Nosov, S. Fetisov, S. Zanegin, V. Rachuk, and B. Katorgin, "Energy Transfer with Hydrogen and Superconductivity The Review of the First Experimental Results," *Physics Procedia*, vol. 65, pp. 299–302, 2015, proceedings of the 27th International Symposium on Superconductivity (ISS 2014) November 25-27, 2014, Tokyo, Japan. [Online]. Available: https://www.sciencedirect.com/science/article/pii/S1875389215003119

- [9] H. Sicius, Handbook of the Chemical Elements. Springer, 2024.

- [10] R. De Doncker et al., "A three-phase soft-switched high-power-density DC/DC converter for high-power applications," *IEEE Transactions on Industry Applications*, vol. 27, no. 1, pp. 63–73, 1991.

- [11] P. C. Saha, Y. Shi, M. Steurer, P. Cheetham, C. Kim, S. Pamidi, J. Goldman, B. German, Z. Jin, L. Graber, and C. Park, "CLEAN: Cryogenic Link for Electric Aircraft Propulsion," *IEEE Transactions on Applied Superconductivity*, vol. 33, no. 5, pp. 1–6, 2023.

- [12] R. Chen and F. F. Wang, "SiC and GaN Devices with Cryogenic Cooling," *IEEE Open Journal of Power Electronics*, vol. 2, pp. 315– 326, 2021.

- [13] A. Deriszadeh, X. Zeng, Z. Wang, R. K. Surapaneni, G. Galla, L. Ybanez, and X. Pei, "Cryogenic Operation of Enhancement-Mode GaN HEMTs," PEASA 2023, pp. 1–6, 2023.

- [14] R. Ren et al., "Characterization and Failure Analysis of 650-V Enhancement-Mode GaN HEMT for Cryogenically Cooled Power Electronics," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 8, no. 1, pp. 66–76, 2020.

- [15] A. Wadsworth et al., "GaN-based cryogenic temperature power electronics for superconducting motors in cryo-electric aircraft," Superconductor Science and Technology, vol. 36, no. 9, 2023.

- [16] Top-side cooled 650 V E-mode GaN transistor, GaN Systems, 2021, rev. 210727. [Online]. Available: https://www.infineon.com

- [17] Mustafeez-Ul-Hassan et al., "Investigation about Operation and Performance of Gate Drivers for Power Electronics Converters for Cryogenic Temperatures," EPE 2022 ECCE Europe, pp. 1–9, 2022.

- [18] M. u. Hassan, Y. Wu, F. Luo, and V. Solovyov, "Development of Gate Drive Configuration for GaN Based Cryogenic Power Electronics Converters," *IEEE Transactions on Industry Applications*, vol. 59, no. 6, pp. 7039–7051, 2023.

- [19] R. Gelagaev, P. Jacqmaer, and J. Driesen, "A Fast Voltage Clamp Circuit for the Accurate Measurement of the Dynamic ON-Resistance of Power Transistors," *IEEE Transactions on Industrial Electronics*, vol. 62, no. 2, pp. 1241–1250, 2015.