# **Ressourcenbasierte Inferenz- Partitionierung von Deep Neural Networks in eingebetteten Systemen**

Zur Erlangung des akademischen Grades eines

**DOKTORS DER INGENIEURWISSENSCHAFTEN (Dr.-Ing.)**

von der KIT-Fakultät für Elektrotechnik und Informationstechnik

des Karlsruher Instituts für Technologie (KIT)

angenommene

## **DISSERTATION**

von

**M.Sc. Fabian Frederic Kreß**

geboren am 12.07.1995 in Karlsruhe

Tag der mündlichen Prüfung:

19.12.2024

Hauptreferent:

Korreferent:

Prof. Dr.-Ing. Dr. h. c. Jürgen Becker

Prof. Dr.-Ing. Mladen Berekovic

# Kurzfassung

In vielen Anwendungsbereichen, wie der Robotik oder im Automobilbereich, in denen eine große Anzahl von Sensoren integriert ist, sind eingebettete Systeme zu finden. Diese erzeugen oft große Datenmengen, die in möglichst kurzer Zeit von den sensornahen Plattformen an die zentrale Steuereinheit übertragen werden müssen. Folglich benötigen solche Plattformen hohe Linkbandbreiten für die Verbindungen zwischen den eingesetzten Komponenten. Der zunehmende Einsatz von Künstlicher Intelligenz (KI) in vielen dieser Anwendungen stellt darüber hinaus weitere Anforderungen an das Gesamtsystem. So erfordern insbesondere sicherheitskritische Anwendungen, wie das autonome Fahren, zur Verarbeitung von rechenintensiven Deep Neural Networks (DNNs) einen hohen Datendurchsatz bei gleichzeitig geringer Latenz. Aus diesem Grund wurden im Laufe des vergangenen Jahrzehnts verschiedene analoge Processing-In-Memory-Architekturen (PIM) sowie rein digitale Hardwarebeschleuniger entwickelt, welche auf den Datenfluss von DNNs optimiert sind und damit eine bessere Performance und Energieeffizienz bieten als handelsübliche CPUs und GPUs. Modernste DNN-Architekturen bestehen jedoch mitunter aus mehreren Millionen Parametern, die für eine energie- und zeiteffiziente Inferenz möglichst nahe am Prozessor oder dem dedizierten Beschleuniger gespeichert werden müssen. Die verfügbare Fläche, insbesondere von sensornahen Mikroprozessoren, ist allerdings in der Regel stark begrenzt, sodass die internen Speicher dieser Plattformen den Anforderungen ganzer DNNs oft nicht vollständig genügen.

Ein Ansatz zur Lösung dieser Herausforderungen in eingebetteten Systemen mit mehreren zum Teil verteilten Hardwarebeschleunigern ist die Inferenz-Partitionierung von DNNs. Dabei wird die Arbeitslast über verschiedene Beschleuniger im System verteilt, um eine höhere Performance sowie Energieeffizienz zu erzielen und gleichzeitig die benötigte Fläche für die Hardwareressourcen über mehrere Plattformen aufzuteilen. Die Partitionierung von DNNs in eingebetteten Systemen ist allerdings eine komplexe Aufgabe, da hierbei verschiedene Optimierungsziele, wie die benötigte Bandbreite zur Übertragung von Zwischenergebnissen, beachtet werden müssen. Der aktuelle Stand der Technik umfasst unterschiedliche Ansätze, welche allerdings relevante

Metriken vernachlässigen oder lediglich auf bestimmte Rechnerarchitekturen zugeschnitten sind.

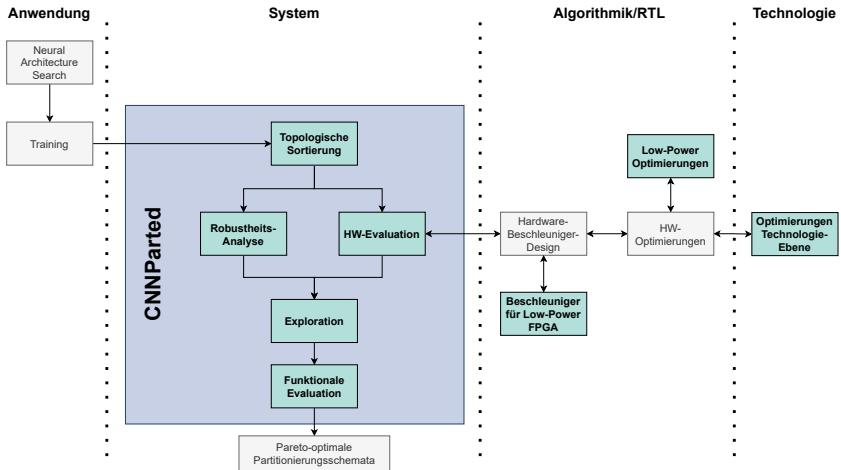

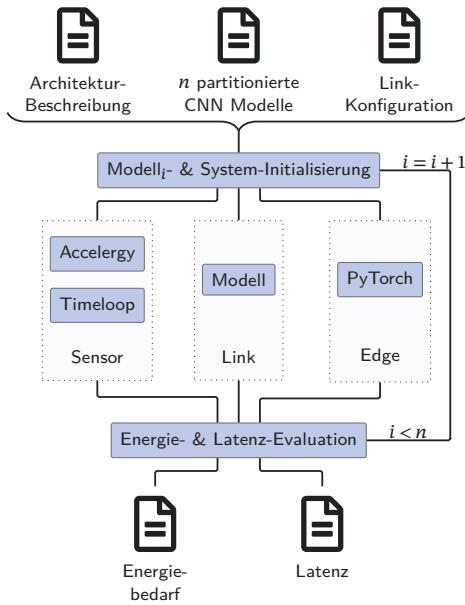

Die vorliegende Arbeit präsentiert daher mehrere neuartige Methoden zur Optimierung solcher Systeme auf unterschiedlichen Entwurfsebenen. Dazu zählt unter anderem ein generischer Ansatz auf Systemebene für die Inferenz-Partitionierung von DNNs mit dem Fokus auf Convolutional Neural Networks (CNNs), welcher eine Vielzahl an nicht-funktionalen Metriken sowie die Genauigkeit des CNNs als funktionale Metrik für die Optimierung verwendet. Letzteres ist notwendig, da Hardwarebeschleuniger in der Regel keine Fließkommazahlen, sondern meist Festkomma- oder gar Ganzzahlen verarbeiten. Die Quantisierung von Gewichten und Aktivierungen führt dabei üblicherweise zu einer Verschlechterung der Genauigkeit, weshalb auch diese Metrik bei der Suche nach einem optimierten Partitionierungsschema berücksichtigt werden muss. Das Framework CNNParted, das diese Methodik implementiert, exploriert automatisiert den Entwurfsraum der Inferenz-Partitionierung in Systemen mit mehreren Beschleunigern unter Beachtung der verfügbaren Hardwareressourcen. Dabei verwendet es Modellierungen der integrierten analogen PIM- und digitalen Hardwarebeschleuniger sowie der Links zwischen den Plattformen im System, um valide Partitionierungsschemata zu bewerten. Aus den Ergebnissen der Untersuchungen generiert CNNParted schließlich eine Pareto-Front hinsichtlich der Optimierungsziele. Die durchgeführten Experimente belegen, dass eine ressourcenbasierte Inferenz-Partitionierung vorteilhaft gegenüber Methoden des aktuellen Stands der Technik ist. So wurden zum Teil deutliche Verbesserungen verschiedener Metriken für heterogene Systeme, bestehend aus analogen PIM- und digitalen Hardwarebeschleunigern, erzielt. Folglich erreicht die entsprechende Wahl eines Pareto-optimalen Partitionierungsschemas unter anderem eine deutlich höhere Energieeffizienz als für die Ausführung der Inferenz auf einer einzigen Beschleunigerplattform.

Anschließend legt die vorliegende Arbeit aber auch dar, dass eine Inferenz-Partitionierung nicht in jedem Fall ohne zusätzliche Optimierungen sinnvoll ist. So ist die Einhaltung von Systemanforderungen meist nicht gewährleistet, wenn zur Übertragung von Zwischenergebnissen Links mit geringer Bandbreite zum Einsatz kommen. Folglich ist eine Optimierung der Software notwendig, um dennoch eine Inferenz-Partitionierung zu ermöglichen. Gleichzeitig muss aufgrund des begrenzten Energiebudgets in Anwendungsfällen wie dem Internet-of-Things (IoT) jedoch auch die Hardware optimiert werden, um DNNs zu integrieren. Handelsübliche Mikrocontroller verfügen meist nicht über die notwendige Performance und Energieeffizienz für die Ausführung der Inferenz. Da nach aktuellem Stand der Technik nur wenige Metho-

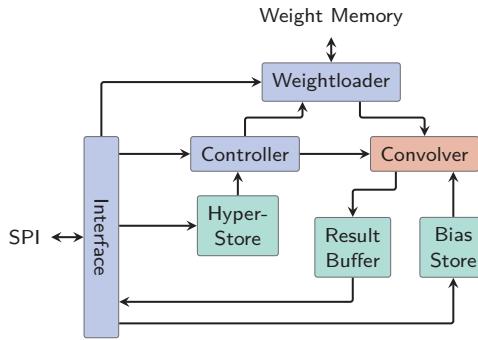

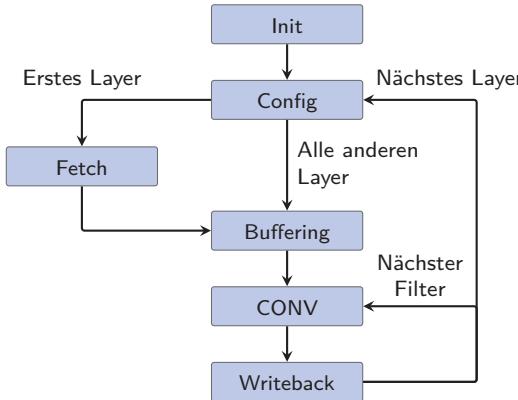

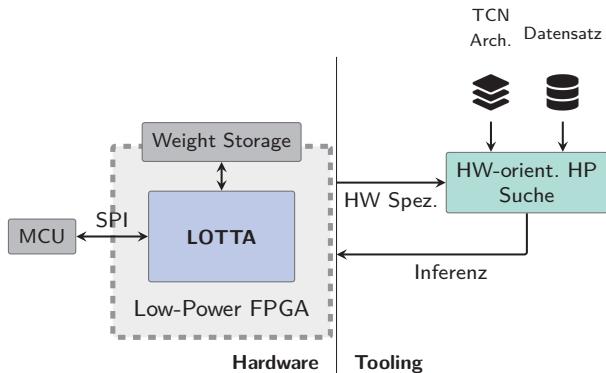

den existieren, welche ein entsprechendes Hardware/Software Co-Design durchführen, zeigt die vorliegende Arbeit weitere Ansätze zur Lösung dieser Probleme auf. So kann unter anderem durch Implementierung von approximierten Multiplizierern und einer approximierten Aktivierungsfunktion ein sehr kleiner Hardwarebeschleuniger realisiert werden, dessen Architektur bei Anwendung von Quantization-Aware Training (QAT) nur zu einem geringen Verlust der Genauigkeit des DNNs führt. Des Weiteren stellt die vorliegende Arbeit die Beschleunigerarchitektur LOTTA für Temporal Convolutional Networks (TCNs) vor, mit der nachgewiesen wurde, dass auch der Einsatz von Low-Power Field Programmable Gate Arrays (FPGAs) im IoT für die Ausführung von DNNs möglich ist. Dabei ergaben Messungen von LOTTA auf einem Low-Power FPGA mit externen, nicht-flüchtigen Speichern für die Gewichte eines exemplarischen TCNs eine Leistungsaufnahme von lediglich 27,81 mW, womit das System zum Teil deutlich unter dem Energiebedarf handelsüblicher Low-Power Mikrocontroller liegt.

# Abstract

Embedded systems can be found in many application areas, such as robotics or the automotive industry, in which a large number of sensors are integrated. These systems often generate large amounts of data, which must be transferred from the near-sensor platforms to the central control unit in the shortest possible time. Consequently, such platforms require high link bandwidths for the connections between the components used. The increasing use of artificial intelligence (AI) in many of these applications also places further demands on the overall system. In particular, safety-critical applications such as autonomous driving require high data throughput and low latency to process computationally intensive deep neural networks (DNNs). As a result, various analog processing-in-memory (PIM) architectures and purely digital hardware accelerators have been developed over the past decade, which are optimized for the data flow of DNNs and therefore offer better performance and energy efficiency than standard CPUs and GPUs. However, state-of-the-art DNN architectures might consist of several million parameters, which have to be stored as close as possible to the processing unit or the dedicated accelerator for energy- and time-efficient inference. However, the available area, especially of microprocessors close to the sensor, is usually very limited, which is why the internal memory of these platforms often does not meet the requirements of entire DNNs.

One approach to solving these challenges in embedded systems with several hardware accelerators, some of which are distributed, is the inference partitioning of DNNs. This involves distributing the workload across different accelerators in the system in order to achieve higher performance and energy efficiency while simultaneously distributing the area required for the hardware resources across multiple platforms. However, the partitioning of DNNs in embedded systems is a complex task, as various metrics, such as the bandwidth required to transfer intermediate results, must be taken into account. Different approaches exist in the current state of the art, but these often neglect relevant metrics or are only tailored to specific computer architectures.

This thesis therefore presents several novel methods for optimizing such systems at different design levels. These include a generic system-level approach for the inter-layer inference partitioning of DNNs with a focus on Convolutional Neural Networks (CNNs), which uses a variety of non-functional metrics as well as the accuracy of the CNN as a functional metric for optimization. The latter is necessary because hardware accelerators usually do not process floating point data, but mostly fixed point or even integers. The quantization of weights and activations usually leads to a deterioration in accuracy, which is why this metric must also be considered when searching for an optimized partitioning scheme. The CNNParted framework, which implements this methodology, automatically explores the design space of inference partitioning in systems with multiple accelerators, taking into account the available hardware resources. It uses models of the integrated analog PIM and digital hardware accelerators as well as of the links between the platforms in the system to evaluate valid partitioning schemes. Finally, CNNParted generates a Pareto front regarding the relevant metrics from the results of the explorations. The experiments carried out proved that resource-based inference partitioning is advantageous compared to state-of-the-art methods. In some cases, significant improvements in various metrics were achieved for heterogeneous systems consisting of analog PIM and digital hardware accelerators. Consequently, by choosing a Pareto-optimal partitioning scheme, for example, significantly higher energy efficiency is achieved than for running inference on a single accelerator platform.

However, this work also shows that inference partitioning does not always provide benefits without additional optimizations. For example, fulfilling system requirements is usually not guaranteed if low-bandwidth links are used to transfer intermediate results. Consequently, the software must be optimized to enable inference partitioning. At the same time, however, due to the limited energy budget in applications such as the Internet of Things (IoT), the hardware must also be optimized in order to infer DNNs. Commercially available microcontrollers usually do not have the necessary performance and energy efficiency to perform inference. As there are only a few methods in the current state of the art that carry out a corresponding hardware/software co-design, this thesis shows further approaches to solving these problems. For example, by implementing approximated multipliers and an approximated activation function, a very small hardware accelerator can be realized whose architecture leads to only a small loss in the accuracy of the DNN when using Quantization-Aware Training (QAT). Furthermore, this paper presents the LOTTA accelerator architecture for Temporal Convolutional Networks (TCNs), which proves that the use of low-power FPGAs in the IoT is also possible for

the execution of DNNs. Measurements of LOTTA on a low-power FPGA with external non-volatile memories for the weights of an exemplary TCN resulted in a power consumption of only 27,81 mW, which means that the system is significantly below the energy requirements of commercially available low-power microcontrollers.

# Vorwort

Die vorliegende Dissertation entstand während meiner Zeit als wissenschaftlicher Mitarbeiter am Institut für Technik der Informationsverarbeitung (ITIV) des Karlsruher Instituts für Technologie (KIT). An dieser Stelle möchte ich all jenen meinen herzlichen Dank aussprechen, die mich auf diesem Weg begleitet und unterstützt haben.

Mein besonderer Dank gilt Prof. Jürgen Becker für die Betreuung meines Promotionsvorhabens, sein Vertrauen und die Freiheiten, die er mir im Rahmen meiner Arbeit am Institut gewährt hat. Ebenso danke ich Prof. Mladen Berekovic für die Übernahme des Korreferats und sein Feedback zur inhaltlichen Vervollständigung der Arbeit. Nicht vergessen möchte ich auch die Prüfungskommission, bestehend aus Prof. Mike Barth, Prof. Cornelius Neumann und Prof. Ivan Peric, welchen ich für Ihre Zeit danken möchte.

Darüber hinaus bedanke ich mich herzlich bei meinen ehemaligen Kolleginnen und Kollegen des ITIV, mit denen ich spannende Diskussionen führen und eine gute Zusammenarbeit in Projekten und der Lehre erleben durfte. Sie haben mir eine bereichernde Zeit am Institut ermöglicht und immer wieder neue Wege für meine Forschung aufgezeigt, wovon ich in vielerlei Hinsicht profitieren konnte. Ebenso danke ich allen Studierenden, die ich im Rahmen von Abschlussarbeiten und HiWi-Tätigkeiten betreuen durfte und die zum Gelingen dieser Arbeit beitrugen. Nicht zu vergessen sind die Mitarbeiterinnen und Mitarbeiter aus der Verwaltung und insbesondere dem Sekretariat des ITIV, die mich auf meinem Weg stets unterstützt haben. Ohne all diese Menschen wäre die vorliegende Arbeit nicht möglich gewesen.

Zu guter Letzt möchte ich meinen Freunden und meiner Familie, meinen Eltern, meinem Bruder und meiner Freundin meinen tiefsten Dank aussprechen. Ihre ständige Unterstützung und Motivation haben mich während dieser Zeit stets vorangebracht und mir auch in schwierigen Phasen Halt gegeben.

Karlsruhe, im Februar 2025

Fabian Kreß

# Inhaltsverzeichnis

|                                                             |    |

|-------------------------------------------------------------|----|

| <b>1 Einleitung</b>                                         | 1  |

| 1.1 Motivation                                              | 1  |

| 1.2 Zielsetzung und Beitrag der Arbeit                      | 3  |

| <b>2 Grundlagen</b>                                         | 7  |

| 2.1 Deep Neural Network (DNN)                               | 7  |

| 2.1.1 Convolutional Neural Network (CNN)                    | 8  |

| 2.1.2 Long Short-Term Memory (LSTM)                         | 9  |

| 2.1.3 Temporal Convolutional Network (TCN)                  | 11 |

| 2.1.4 Quantisierung                                         | 12 |

| 2.2 DNN Hardwarebeschleuniger                               | 13 |

| 2.2.1 Vektorprozessoren                                     | 14 |

| 2.2.2 Systolische Arrays                                    | 14 |

| 2.2.3 Processing-In-Memory                                  | 16 |

| 2.2.4 Hardware-Mapping                                      | 17 |

| 2.3 Mehrzieloptimierung                                     | 18 |

| <b>3 Stand der Technik</b>                                  | 23 |

| 3.1 Intra-Layer-Inferenz-Partitionierung                    | 23 |

| 3.2 Inter-Layer-Inferenz-Partitionierung                    | 28 |

| 3.3 Ableitung der Anforderungen                             | 35 |

| <b>4 Gesamtkonzept</b>                                      | 41 |

| 4.1 Rahmenbedingungen                                       | 41 |

| 4.2 Entwurfsebenen                                          | 42 |

| 4.2.1 Systemebene                                           | 43 |

| 4.2.2 Algorithmische Ebene                                  | 44 |

| 4.2.3 Technologieebene                                      | 45 |

| <b>5 Inferenz-Partitionierung von DNNs</b>                  | 47 |

| 5.1 Vorstudie I: Partitionierung in ASIC-basierten Systemen | 47 |

| 5.1.1 Übersicht                                             | 48 |

| 5.1.2 Systemmodellierung                                    | 50 |

| 5.1.3 Testaufbau                                            | 54 |

|          |                                                                                  |            |

|----------|----------------------------------------------------------------------------------|------------|

| 5.1.4    | Evaluation . . . . .                                                             | 57         |

| 5.2      | Vorstudie II: Partitionierung in FPGA-basierten Systemen . . . . .               | 63         |

| 5.2.1    | Toolchain . . . . .                                                              | 63         |

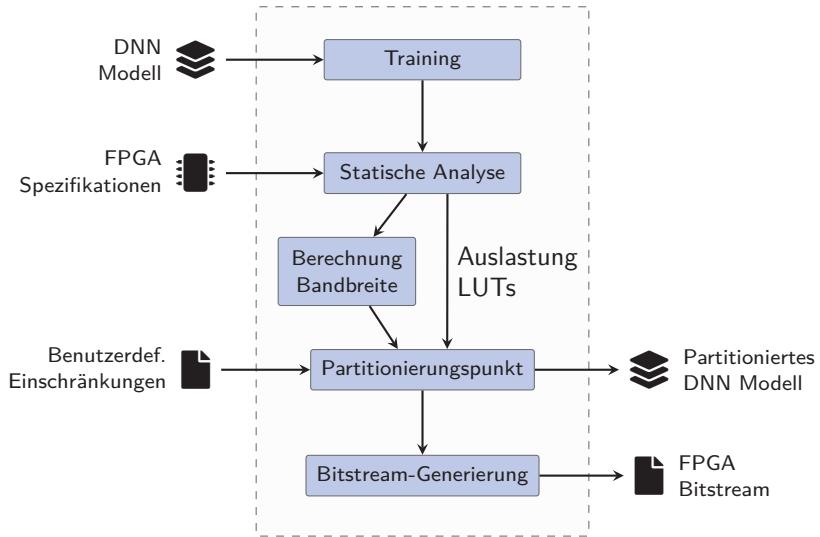

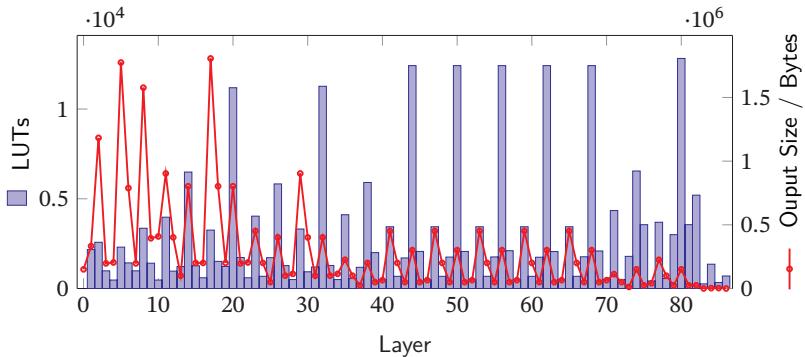

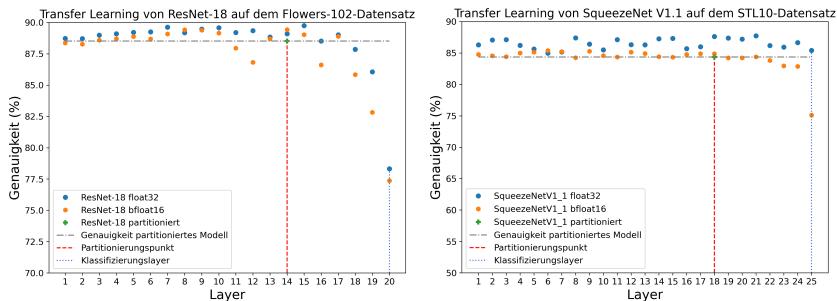

| 5.2.2    | Training und statische Analyse . . . . .                                         | 65         |

| 5.2.3    | Methodik . . . . .                                                               | 66         |

| 5.2.4    | Evaluation . . . . .                                                             | 68         |

| 5.3      | Allgemeine Problemdefinition . . . . .                                           | 71         |

| 5.4      | CNNParted Framework . . . . .                                                    | 75         |

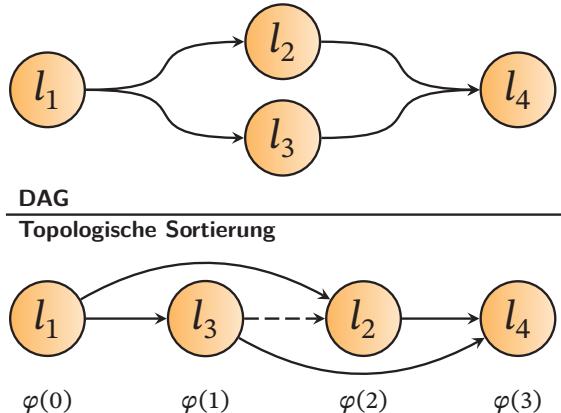

| 5.4.1    | Graphinitialisierung . . . . .                                                   | 78         |

| 5.4.2    | Topologische Sortierung . . . . .                                                | 78         |

| 5.4.3    | Robustheitsanalyse . . . . .                                                     | 79         |

| 5.4.4    | Beschleuniger-Modellierung . . . . .                                             | 82         |

| 5.4.5    | Link-Modellierung . . . . .                                                      | 85         |

| 5.4.6    | Explorationsalgorithmus . . . . .                                                | 87         |

| 5.4.7    | Funktionale Evaluation . . . . .                                                 | 92         |

| 5.5      | Anwendungsstudien . . . . .                                                      | 93         |

| 5.5.1    | Verteilte eingebettete Systeme . . . . .                                         | 94         |

| 5.5.2    | Chiplet-basierte Systeme . . . . .                                               | 97         |

| <b>6</b> | <b>Hardware/Software Optimierungen . . . . .</b>                                 | <b>111</b> |

| 6.1      | Motivation . . . . .                                                             | 111        |

| 6.2      | DNN Optimierungen . . . . .                                                      | 114        |

| 6.2.1    | Bandbreiten-Optimierung . . . . .                                                | 115        |

| 6.2.2    | Modell-Quantisierung . . . . .                                                   | 116        |

| 6.2.3    | Hardware-Anforderungen . . . . .                                                 | 117        |

| 6.3      | Approximate Computing . . . . .                                                  | 119        |

| 6.3.1    | Hintergrund . . . . .                                                            | 119        |

| 6.3.2    | Hardwarekonzept . . . . .                                                        | 121        |

| 6.3.3    | Systemintegration . . . . .                                                      | 126        |

| 6.3.4    | Evaluation . . . . .                                                             | 128        |

| 6.4      | Low-Power FPGA Beschleuniger . . . . .                                           | 134        |

| 6.4.1    | Verwandte Arbeiten . . . . .                                                     | 134        |

| 6.4.2    | Hardwarearchitektur . . . . .                                                    | 135        |

| 6.4.3    | Evaluation . . . . .                                                             | 140        |

| 6.4.4    | Hardware-orientierte Modell-Optimierung . . . . .                                | 145        |

| 6.4.5    | Fallstudien . . . . .                                                            | 146        |

| <b>7</b> | <b>Technologische Optimierung für sicherheitskritische Anwendungen . . . . .</b> | <b>151</b> |

| 7.1      | Motivation . . . . .                                                             | 151        |

|                                        |                                               |            |

|----------------------------------------|-----------------------------------------------|------------|

| 7.2                                    | Hintergrund . . . . .                         | 153        |

| 7.2.1                                  | Magnetischer Tunnelkontakt . . . . .          | 153        |

| 7.2.2                                  | Register Checkpointing . . . . .              | 155        |

| 7.2.3                                  | Verwandte Arbeiten . . . . .                  | 157        |

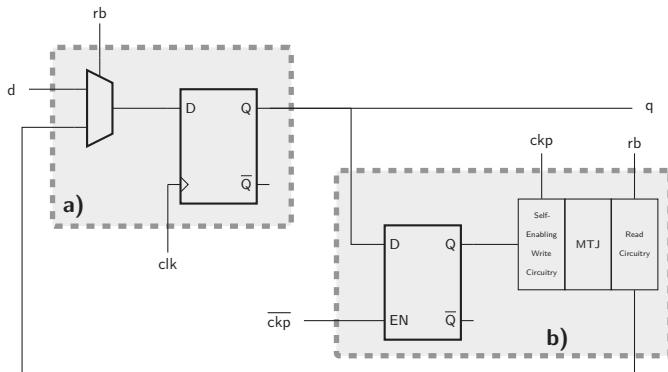

| 7.3                                    | Hybrider Magnetischer Flip-Flop . . . . .     | 158        |

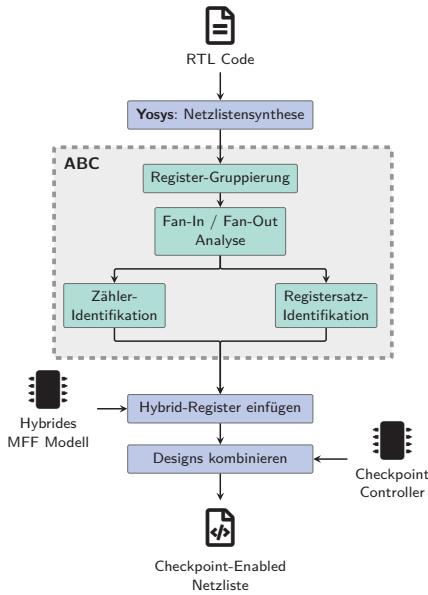

| 7.4                                    | Toolchain . . . . .                           | 160        |

| 7.4.1                                  | Register-Gruppierung . . . . .                | 162        |

| 7.4.2                                  | Fan-In- und Fan-Out-Analyse . . . . .         | 163        |

| 7.4.3                                  | Zähler-Identifikation . . . . .               | 163        |

| 7.4.4                                  | Registersatz-Identifikation . . . . .         | 164        |

| 7.5                                    | Evaluation . . . . .                          | 164        |

| 7.5.1                                  | Verifikation . . . . .                        | 165        |

| 7.5.2                                  | Ergebnisse . . . . .                          | 165        |

| <b>8</b>                               | <b>Zusammenfassung und Ausblick</b> . . . . . | <b>169</b> |

| <b>Literatur</b> . . . . .             | <b>177</b>                                    |            |

| <b>Publikationen</b> . . . . .         | <b>205</b>                                    |            |

| <b>Studentische Arbeiten</b> . . . . . | <b>211</b>                                    |            |

| <b>Abbildungen</b> . . . . .           | <b>215</b>                                    |            |

| <b>Tabellen</b> . . . . .              | <b>219</b>                                    |            |

| <b>Abkürzungsverzeichnis</b> . . . . . | <b>221</b>                                    |            |

# Kapitel 1

## Einleitung

Innerhalb der letzten Dekade hat das Interesse an der Entwicklung neuer Algorithmen für Künstliche Intelligenz (KI) in vielen Fachgebieten und Forschungsbereichen stark zugenommen. Dies ist insbesondere auf die Fortschritte im Bereich der künstlichen neuronalen Netze, sogenannte Deep Neural Networks (DNNs), zurückzuführen, welche unter anderem die Basis für das inzwischen weltweit bekannte Tool ChatGPT bilden. In diesem Fall handelt es sich um ein Large Language Model (LLM), welches insbesondere auf große Datenmengen angewiesen ist, um durch langwieriges Training gute Ergebnisse zu liefern [1]. Ähnliche Anforderungen ergeben sich in anderen Bereichen, wie der Bilderkennung, welche beispielsweise in der Medizintechnik zum Einsatz kommt [2]. Für die Inferenz, also die Ausführung dieser KI-Algorithmen, bedarf es hoher Rechenkapazitäten, weshalb hierfür in der Regel leistungsstarke Server genutzt werden.

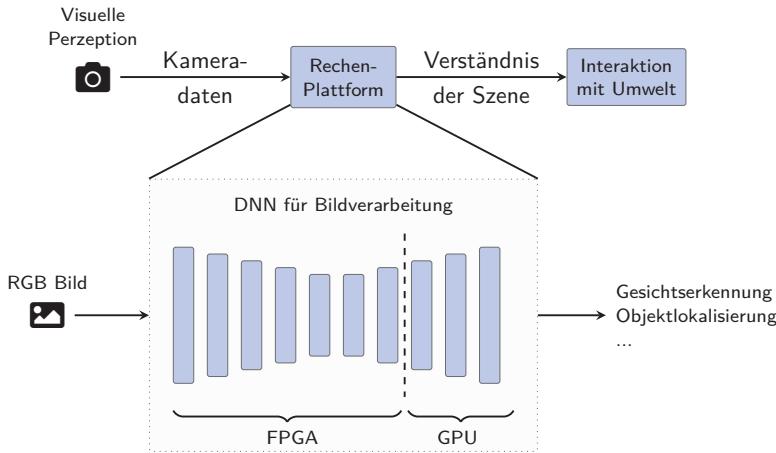

Abseits dieser Entwicklung existieren jedoch auch DNNs für eingebettete Systeme, welche beispielsweise die Objekterkennung anhand von Kamera-daten mit hoher Genauigkeit durchführen. So finden sich DNNs inzwischen nicht nur in Anwendungen im Bereich der Fahrassistentensysteme [3] wieder, sondern auch im Bereich der Assistenzrobotik [4], zur intelligenten Überwachung von Maschinen [5] oder der Gesundheitsvorsorge [6]. Auf dieser Grundlage erschließen sich viele neue Möglichkeiten zur Automatisierung von Aufgaben [7].

### 1.1 Motivation

Über die vergangenen Jahre ist dabei ein klarer Trend hin zu immer aufwendiger werdenden Algorithmen zu beobachten [8]. Dabei nimmt nicht nur die Komplexität der Netze zu, sondern insbesondere auch die Anzahl

der Parameter und damit das dafür benötigte Speichervolumen. Dies stellt besonders eingebettete Systeme vor eine enorme Herausforderung, da diese in der Regel limitiert in der Fläche und dem maximalen Energiebedarf sind [9].

Aus diesem Grund wurden in den letzten Jahren verschiedene Hardwareplattformen vorgestellt, welche für unterschiedliche Aufgabenfelder optimiert sind. Dies reicht dabei von kleinen Mikrocontrollern wie dem GAP8 von GreenWaves Technologies [10], über spezialisierte Hardware-Beschleuniger Architekturen wie der Google Edge TPU [11] bis hin zu eingebetteten Plattformen wie der NVIDIA Jetson Architektur, bestehend aus einer Graphics Processing Unit (GPU) und einem zusätzlichen Beschleuniger, dem sogenannten Deep Learning Accelerator (DLA), für KI-Anwendungen [12]. Der GAP8 eignet sich dabei aufgrund der hohen Energieeffizienz sehr gut für den Einsatz nah am Sensor, verfügt dagegen allerdings nicht über genügend Performance für die schnelle Ausführung größerer Netze. Plattformen wie NVIDIA Jetson erzielen sehr geringe Latenzen für die Inferenz, haben jedoch einen deutlich höheren Energiebedarf und eignen sich daher nicht für den Einsatz in jedem Anwendungsfäll.

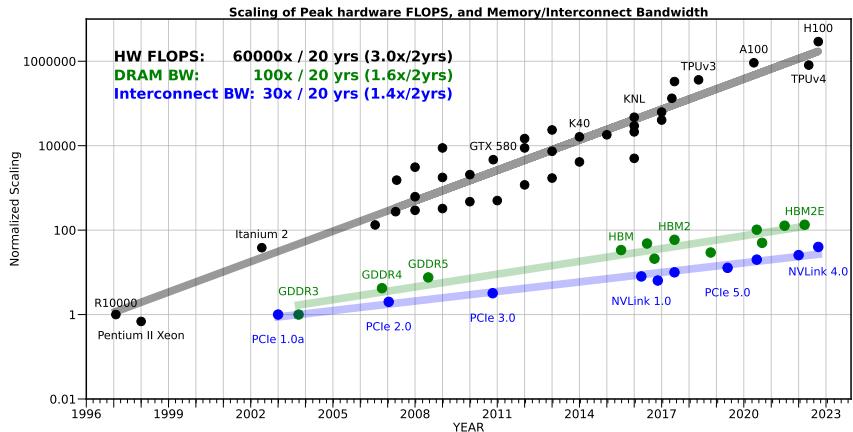

Neben solchen digitalen Plattformen ist in der Forschung zunehmend ein Trend hin zu In-Memory Beschleunigern zu beobachten, welche in situ Rechenoperationen im Speicher ausführen [13, 14]. Die Motivation für diese Entwicklung ist in Abbildung 1.1 dargestellt. Im Vergleich zur Verbesserung der Hardwareperformance von Prozessoren und anwendungsspezifischen Beschleunigern entwickelt sich die verfügbare Speicherbandbreite langsamer, sodass an dieser Stelle ein Flaschenhals entsteht. Diese sogenannte Memory Wall resultiert in einer Begrenzung der Berechnungsdauer datengetriebener Anwendungen nicht durch den Prozessor selbst, sondern insbesondere durch den Speicher. Durch Ausführung von Berechnungen im Speicher steht eine wesentlich höhere Speicherbandbreite zur Verfügung, was in der Regel zu einer deutlichen Erhöhung der Performance führt, unter anderem für Anwendungen wie die Inferenz von DNNs. Allerdings geht dies meist auf Kosten eines höheren Flächenbedarfs, weshalb der Einsatz solcher Hardwarebeschleuniger nicht in jedem Anwendungsfall sinnvoll ist. Aus diesem Grund bieten heterogene Architekturen, wie in [15, 16] vorgeschlagen, die Möglichkeit, zwei unterschiedliche Hardwarebeschleuniger für die Inferenz von DNNs zu nutzen.

Ähnlich hierzu arbeiten Forschungsgruppen weltweit an Chiplet-basierten Systemen für den Einsatz in leistungsfähigen Systemen [17, 18]. Der Vorteil der Chiplet-Technologie ist eine erhöhte Ausbeute korrekt funktionierender

**Abbildung 1.1:** Zeitliche Entwicklung von Hardware-Performance und Interconnect-/Speicherbandbreite aus [19]

Chips in der Produktion, da das gesamte System nicht auf einem einzigen Die realisiert werden muss. Die hohe Performance des Systems basiert auf der Kombination von leistungsstarken Recheneinheiten auf den Chiplets mit einem effizienten Interconnect, der die verschiedenen Komponenten miteinander verbindet. Im Gegensatz zu den in Abbildung 1.1 betrachteten Links weist eine solche interne Verbindung der Chiplets über einen sogenannten Interposer eine deutlich höhere Bandbreite auf, wodurch der Datenaustausch zwischen verschiedenen Prozessoren und Hardwarebeschleunigern wesentlich schneller erfolgt. Allerdings ist zu berücksichtigen, dass dieser Ansatz eine Verringerung der Flexibilität des Systems zur Folge hat, da bereits zur Entwurfszeit die einzelnen Komponenten festgelegt werden müssen. Dies bedingt gleichzeitig eine Erhöhung der Komplexität durch einen deutlich vergrößerten Entwurfsraum.

## 1.2 Zielsetzung und Beitrag der Arbeit

In den letzten zehn Jahren haben viele Untersuchungen nachgewiesen, dass die Aufteilung der Inferenz über mehrere Hardwarebeschleuniger vorteilhaft hinsichtlich verschiedener Metriken sein kann (siehe Kapitel 3). Dies gilt neben heterogenen und Chiplet-basierten Plattformen auch für verteilte eingebettete Systeme, bestehend aus mehreren, über einen entsprechenden Link

miteinander verbundenen Recheneinheiten. Die vorliegende Arbeit hat zum Ziel, eine solche Partitionierung für unterschiedliche Systemarchitekturen unter Beachtung unterschiedlicher Anforderungen durchzuführen und dabei eine optimierte Aufteilung der DNN-Inferenz zu erzielen. Hierfür notwendig ist ein Hardware/Software Co-Design, ausgehend von vortrainierten DNNs, welches Anpassungen auf beiden Seiten vornimmt, um den Systemanforderungen gerecht zu werden (siehe [Kapitel 4](#)).

Als wesentlicher Bestandteil der Methodik dient dabei das im Rahmen der Arbeit entwickelte Open-Source Framework CNNParted, welches in [Kapitel 5](#) detailliert vorgestellt wird. Für die Suche nach einem optimierten Partitionierungsschema bezieht es dabei die Hardwarearchitektur der einzelnen Systemkomponenten in Form analytischer Modelle ein, um bereits zur Entwurfszeit eine Aufteilung möglicher Anwendungen zu untersuchen. In diese Exploration des Entwurfsraums fließen dabei funktionale und nicht-funktionale Metriken ein, um unterschiedlichen Systemanforderungen zu genügen. Die abschließende Diskussion der Methodik erfolgt im Kontext eines verteilten eingebetteten Systems sowie einer Chiplet-basierten Plattform, um die Flexibilität des CNNParted-Frameworks hinsichtlich unterschiedlicher Systemarchitekturen zu demonstrieren.

Gleichzeitig legt die vorliegende Arbeit aber auch dar, dass eine Aufteilung der DNN-Inferenz nicht in jedem Fall sinnvoll ist und es weiterer Optimierungen der Hard- und Software bedarf, um den Einsatz von KI in eingebetteten Systemen zu ermöglichen. Aus diesem Grund stellt [Kapitel 6](#) unterschiedliche Optimierungen vor, welche von der Quantisierung der Gewichte zur Reduktion des Speicherbedarfs bis zum Entwurf von spezialisierten Hardwarebeschleunigern reichen. Letztere Architekturen nutzen dabei entweder approximative Rechenoperationen, um die benötigten Hardwareressourcen signifikant zu reduzieren, oder zielen auf eine energieeffiziente Nutzung der vorhandenen Logikblöcke auf einem Low-Power Field Programmable Gate Array (FPGA) ab. Abschließend behandelt [Kapitel 7](#) eine Optimierung auf technologischer Ebene, um zusätzliche funktionale Anforderungen an Systeme in sicherheitskritischen Anwendungen zu erfüllen.

# Kapitel 2

## Grundlagen

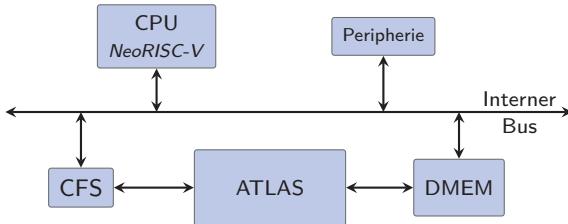

Die vorliegende Arbeit behandelt die ressourcenbasierte Inferenz-Partitionierung von DNNs in eingebetteten Systemen, wie diese beispielsweise in Fahrzeugen für Advanced Driver-Assistance System (ADAS) oder auch im Internet-of-Things (IoT) zum Einsatz kommen. Nach Bringmann et al. handelt es sich bei eingebetteten Systemen um „*Rechensysteme, die in einen technischen Kontext, bzw. in ein übergeordnetes System eingebunden sind und vordefinierte Aufgaben erfüllen*“ [20]. Sie setzen sich üblicherweise aus Prozessor(en), Speicher, Schnittstellen nach außen und ggf. Rechenbeschleuniger zusammen, in heterogenen Plattformen werden unter anderem auch FPGAs integriert. Dabei vernetzt ein interner Systembus die einzelnen Komponenten, um einen Datenaustausch zu ermöglichen. Aufgrund der geringen verfügbaren Fläche in den genannten Anwendungsfällen kommen dort in der Regel System-on-Chips (SoCs) bzw. Multiprozessor-System-on-Chips (MPSoCs) zum Einsatz, wobei das komplette System auf einem Chip realisiert ist. Im Folgenden werden die zum Verständnis der vorliegenden Arbeit benötigten Konzepte und Begriffe näher erläutert.

### 2.1 Deep Neural Network (DNN)

KI gilt als Grundlage vieler Anwendungen der Zukunft wie dem autonomen Fahren oder auch der Robotik. Insbesondere das Feld des Machine Learning (ML), welches zum Ziel hat, Algorithmen zu entwerfen, die es einem Computer erlauben, aus Daten zu lernen und entsprechend zu handeln, ist dabei ein zentrales Element der Forschung. Nach Kelleher umfasst ML „*die Entwicklung und Evaluation von Algorithmen die es einem Computer ermöglichen, Funktionen aus einem Datensatz zu extrahieren*“ [21]. Dabei entspricht ein Datensatz einer Menge an Beispielen, deren Lösung bekannt ist. Anhand dessen können im Laufe des Trainingsprozesses vom Algorithmus Muster erkannt werden

und diese in eine Funktion eingehen. Innerhalb des Teilgebiets des ML, welches als Deep Learning bezeichnet wird, erfolgt die Darstellung der zuvor genannten Funktionen mittels sogenannter DNNs.

DNNs bestehen aus mehreren unterschiedlichen Schichten (Layern), welche zur Aufgabe haben, jeweils sich wiederholende Merkmale (Features) in den Eingangsdaten zu erlernen und diese entsprechend während der Inferenz zu erkennen. Je nach Komplexität der Aufgabe sind daher unterschiedliche Arten und Strukturen von DNNs erforderlich, um möglichst präzise Ergebnisse und damit eine hohe Genauigkeit der Erkennung eines Musters in den Daten zu erzielen. Die Suche nach solchen Netzen wird dabei als Neural Architecture Search (NAS) bezeichnet. Die nachfolgenden Unterabschnitte stellen die für das Verständnis der vorliegenden Arbeit notwendigen Arten von DNNs und deren Funktionsprinzip vor.

### 2.1.1 Convolutional Neural Network (CNN)

Für die Verarbeitung strukturierter Daten in gitterförmiger Anordnung wie beispielsweise Bilder, haben bislang besonders Convolutional Neural Networks (CNNs) [22] sehr gute Ergebnisse geliefert. Aus diesem Grund bilden diese bis heute die Grundlage vieler Bildverarbeitungsaufgaben wie z.B. der Objekterkennung, -klassifizierung oder semantischen Segmentierung. Innerhalb der ersten Schichten eines CNNs werden in der Regel Bildmerkmale (Features) mittels Faltungsoperation extrahiert. Am Ende des Netzes erfolgt eine Zusammensetzung dieser Features und schließlich die Ausgabe abhängig vom Anwendungsfall.

#### Convolutional Layer

Die namensgebende Faltung sorgt in den Convolutional Layer (CONV) dafür, dass ein Bild schrittweise mittels zweidimensionaler Filter auf diese Merkmale abgesucht wird [21]. Dadurch erzielen CNNs recht präzise Ergebnisse mit verhältnismäßig wenigen Gewichten und sind somit gleichzeitig besser skalierbar. Sie ist in der diskreten eindimensionalen Form zu Verarbeitung in der Hardware wie folgt definiert [23].

$$s(t) = (i * w)(t) = \sum_{m=-\infty}^{\infty} i(m) \cdot w(t-m) \quad (2.1)$$

Auf dieser Grundlage leitet sich die Implementierung der Faltungsoperation für die zweidimensionalen Bilddaten im CNN wie folgt ab [24].

$$S(i, j) = (K * I)(i, j) = \sum_m \sum_n I(i + m, j + n) \cdot K(m, n), \quad (2.2)$$

wobei  $I$  den Eingangsdaten bzw. den sogenannten Aktivierungen, und  $K$  dem zweidimensionalen Filter, bestehend aus Gewichtungsfaktoren, kurz Gewichten, entspricht. Üblicherweise werden mehrere Filter innerhalb einer Schicht verwendet, wodurch diese Operation entsprechend der Anzahl wiederholt wird. Diesem CONV-Layer folgt häufig eine Pooling-Schicht, um die Aktivierungen zu komprimieren.

## Fully-Connected Layer

CNNs können aus lediglich diesen Layern zusammengesetzt werden, um beispielsweise eine semantische Segmentierung vorzunehmen [25]. In diesem Fall werden sie als Fully-Convolutional Networks (FCNs) bezeichnet. Allerdings ist dies in vielen Anwendungen nicht sinnvoll, um eine hohe Genauigkeit zu erzielen. Stattdessen werden wie zuvor beschrieben Fully-Connected Layer am Ende der CNNs verwendet, um beispielsweise eine Klassifizierung vorzunehmen. Dabei ist intern jedes Eingangs- mit jedem Ausgangsneuron über eine gewichtete Kante verbunden. Die Ausgangsaktivierungen  $S$  lassen sich folglich, wie in Gleichung (2.3) beschrieben, über eine Matrixmultiplikation der Eingangsdaten  $I$  mit der Gewichtsmatrix  $W$  und anschließender Addition des Bias berechnen [26].

$$S = I \cdot W = \sum_{j=1}^m i_{ij} \cdot w_{jk} \quad (2.3)$$

### 2.1.2 Long Short-Term Memory (LSTM)

CNNs verwenden nur die aktuellen Eingabedaten für die Inferenz und speichern nicht die Ergebnisse früherer Durchläufe. Es gibt jedoch Anwendungen, bei denen genau dies von Vorteil ist. Aufgrund dieser Anforderungen wurden Recurrent Neural Networks (RNNs) für die Verarbeitung von sequenziellen Daten entwickelt. Frühe Versionen solcher DNNs litten jedoch erheblich unter verschwindenden Gradienten in der Lernphase, was zu sehr langsamem oder gar unbrauchbarem Training führte. Um dieses Problem zu lösen, schlugen

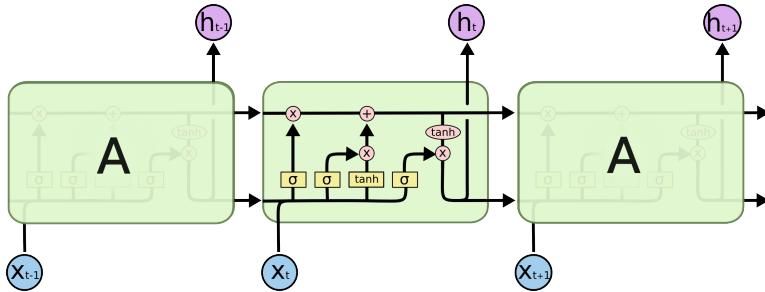

**Abbildung 2.1:** Schematische Darstellung eines LSTMs aus [28]

Hochreiter und Schmidhuber die sogenannten Long Short-Term Memorys (LSTMs) vor [27].

LSTMs finden sich heute in unterschiedlichen Anwendungen wieder, beispielsweise in der prädiktiven Instandhaltung [29] oder der Spracherkennung [30]. Wie in Abbildung 2.1 dargestellt, besteht ein LSTM aus mehreren Zellen, welche miteinander verbunden sind. Diese speichern jeweils ihren eigenen Zustand, wodurch Informationen über frühere Ereignisse in die Inferenz einfließen. Der Zustand wird dabei durch mehrere Layer (Gates) bestimmt, nämlich das Forget- ( $f_t$ ), Input- ( $i_t$ ) und Output-Gate ( $o_t$ ) sowie der Candidate-Speicher ( $\tilde{c}_t$ ). Mathematisch lässt sich eine solche Zelle mit ihren Gates wie folgt beschreiben:

$$i_t = \sigma(W_x^i x_t + W_h^i h_{t-1} + b^i) \quad (2.4)$$

$$f_t = \sigma(W_x^f x_t + W_h^f h_{t-1} + b^f) \quad (2.5)$$

$$o_t = \sigma(W_x^o x_t + W_h^o h_{t-1} + b^o) \quad (2.6)$$

$$\tilde{c}_t = \tanh(W_x^c x_t + W_h^c h_{t-1} + b^c) \quad (2.7)$$

$$c_t = f_t \odot c_{t-1} + i_t \odot \tilde{c}_t \quad (2.8)$$

$$h_t = o_t \odot \tanh(c_t) \quad (2.9)$$

wobei  $\sigma(x)$  (Sigmoid-Funktion) und  $\tanh(x)$  die Aktivierungsfunktionen darstellen, die Eingabe zum Zeitpunkt  $t$  als  $x_t$  und der Hidden-State als  $h_t$  bezeichnet wird. Unter Verwendung der Gewichtsmatrix  $W$  sowie der Biases  $b$  berechnet die Zelle den neuen Zellzustand  $c_t$ . Somit ergibt sich aus der Eingabe  $x_t$  eine Ausgabe der Zelle in Form des Hidden-States  $h_t$ , welche auch an die nächste Zelle im LSTM weitergegeben wird.

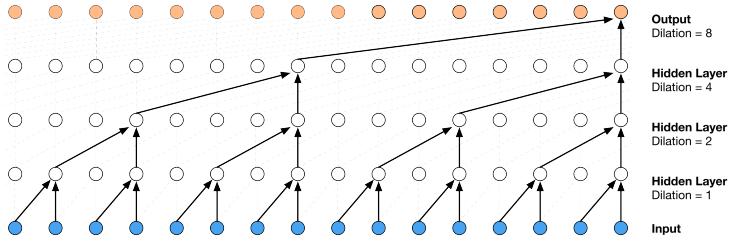

**Abbildung 2.2:** Schematische Darstellung eines TCN-Stapels aus [31]

### 2.1.3 Temporal Convolutional Network (TCN)

Eine etwas neuere Form der Verarbeitung von sequenziellen Daten stellen Temporal Convolutional Networks (TCNs) dar, vorgestellt von van den Oord et al. in [31]. Sie sind eine spezielle Art von CNNs und basieren auf gedehnten (dilated) Faltungen mit residualen Blöcken, die in der zeitlichen Dimension angewendet werden. Aufgrund dieser Struktur sind TCNs schneller und einfacher zu trainieren. Zudem weisen sie eine geringere Anfälligkeit für verschwindende Gradienten im Training auf als RNNs, insbesondere im Falle langer Sequenzen [32]. Abbildung 2.2 zeigt beispielhaft den Aufbau eines solchen TCNs.

Gedehnte Faltungen in Kombination mit der Stapelung mehrerer Schichten ermöglichen ein breites rezeptives Feld, das wiederum das Lernen von lang anhaltenden zeitlichen Verbindungen in den Eingabedaten ermöglicht. Dieses rezeptive Feld definiert, wie viele Werte der Eingabe berücksichtigt werden, um eine neue Ausgabe zu erzeugen und lässt sich mathematisch wie folgt formulieren [33]:

$$r = 1 + (k - 1) \cdot n_{stack} \cdot \sum_i d_i, \quad (2.10)$$

wobei  $k$  der Kernelgröße,  $n_{stack}$  der Anzahl der Stapel und  $d$  einem Vektor bestehend aus Dehnungsfaktoren (Dilations) innerhalb des Stapels entsprechen. Ist die Länge der Eingabesequenz kleiner als das rezeptive Feld, füllt das TCN die fehlenden Stellen mit Nullen auf. Dies hat im Training allerdings einen negativen Einfluss und beeinflusst damit die Genauigkeit des Netzes. Daher ist bei der Wahl der Hyperparameter zu berücksichtigen, dass das rezeptive Feld eine Größe aufweist, die nicht wesentlich größer ist als die minimale Länge einer Sequenz.

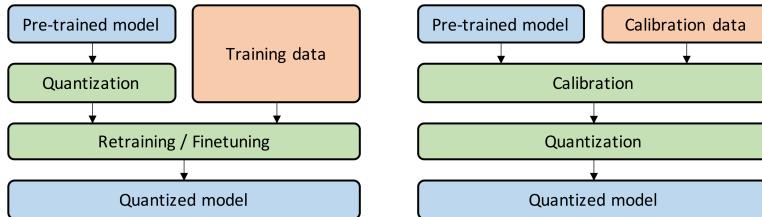

**Abbildung 2.3:** Vergleich QAT und PTQ aus [35]

## 2.1.4 Quantisierung

Das Training und die Inferenz von DNNs erfolgt im Rahmen der DNN-Frameworks wie Caffe, Keras oder PyTorch basierend auf Gleitkommazahlen. Im Vergleich zu Festkomma- oder Ganzzahlen sind Rechenoperationen mit Daten in diesem Format aufwendiger und benötigen daher mehr Zeit oder Energie [34]. Um die Inferenz in Hardware zu optimieren, erfolgt in der Regel eine Quantisierung der Gewichte und Aktivierungen. Ist der Trainingsdatensatz bekannt, kann dies auf zwei Arten erfolgen [35], wie in Abbildung 2.3 gezeigt.

Einerseits kann Quantization-aware Training (QAT) angewandt werden, wobei die Quantisierung bereits im Training Berücksichtigung findet. Problematisch ist dabei allerdings, dass die Anpassung der Gewichte auf Gradienten basiert (Backpropagation), welche durch die nicht-differenzierbare Quantisierung meist dem Wert null entsprächen. Daher kommt hierfür häufig der Straight-Through-Estimator (STE) zum Einsatz [36], sodass das Training weiterhin auf Gleitkommazahlen basiert. Im Gegensatz dazu beinhaltet Post Training Quantization (PTQ) kein Retraining des DNNs, wodurch dieses Vorgehen deutlich schneller ist. Lediglich eine Kalibrierung ist notwendig, um die Clipping Range für die Abbildung der Gleitkommazahlen in den entsprechenden Zahlenraum festzulegen. Dafür werden mehrere Inferenzen mit Testdaten durchgeführt und der Bereich zwischen minimalem und maximalem Wert einer Aktivierung ermittelt. Im Vergleich zur symmetrischen Quantisierung führt die asymmetrische Quantisierung in der Regel zu einer deutlich kleineren Clipping Range, was eine geringe Schritthöhe zwischen den Quantisierungsstufen zur Folge hat. [35]. Die Anwendung von PTQ ohne zusätzliche Optimierung führt jedoch üblicherweise zu einer signifikanten Verringerung der Genauigkeit des Netzes [37].

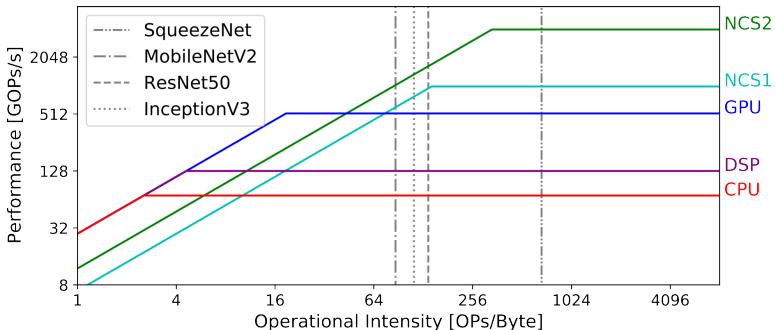

Abbildung 2.4: Roofline Model für verschiedene Prozessoren und CNNs aus [38]

## 2.2 DNN Hardwarebeschleuniger

Um DNNs effizient in eingebetteten Systemen hinsichtlich Latenz und Energiebedarf zu integrieren, bedarf es leistungsfähiger Hardwareplattformen. Insbesondere für sicherheitskritische Anwendungen müssen diese Systeme Garantien erbringen, die nicht mit einer herkömmlichen Central Processing Unit (CPU) zu erzielen sind. Dies zeigt auch Abbildung 2.4, welches verschiedene Plattformen hinsichtlich der Performance untersucht. Die Darstellung mittels *Roofline Model* ermöglicht einen grafischen Vergleich der jeweiligen maximalen Rechenleistung (horizontale Linien) und maximalen Speicherbandbreite (diagonale Linien) der Systeme. In Bezug auf die vier untersuchten CNN-Anwendungen lässt sich feststellen, dass die maximalen Rechenleistungen der Plattformen eine limitierende Wirkung auf die Leistungsfähigkeit dieser Anwendungen haben. Dies trifft gleichermaßen auf CPU, GPU und Digitaler Signal-Prozessor (DSP) zu. Dagegen ergibt sich für die beiden Varianten des Intel Neural Compute Sticks (NCS) eine Limitierung durch die begrenzte Speicherbandbreite. Mit anderen Worten bedeutet dies, dass die CNNs nicht in der Lage sind, die volle Rechenleistung des Systems zu nutzen, da die Speicheranbindung zu langsam ist. Diese Beobachtung von Cao et al. [38] zeigt ähnlich wie die Arbeit von Zhang et al. [39] auf, dass DNNs während der Inferenz viele Daten laden und speichern müssen. Daher sind optimierte Hardwarearchitekturen erforderlich, die eine hohe Rechenleistung und Speicherbandbreite zur Verfügung stellen. Eine Übersicht des aktuellen Stands der Technik ist beispielsweise in [Guo] gegeben. Nachfolgend wird jedoch nur auf die für die vorliegende Arbeit relevanten Architekturen kurz eingegangen.

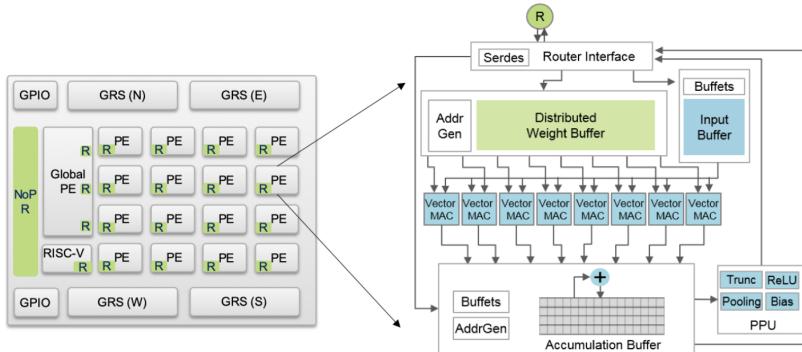

**Abbildung 2.5:** Simba-Chiplet Architektur aus [40]

## 2.2.1 Vektorprozessoren

Eine den herkömmlichen CPUs und GPUs ähnliche Architektur ist die Integration parallel Vektoreinheiten zur Berechnung von Multiply-Accumulate (MAC)-Operationen. Wie im Beispiel der Simba-Architektur [40] zu sehen (s. Abbildung 2.5), werden dafür zunächst die Gewichte aus dem Speicher geladen und anschließend mathematische Operationen zusammen mit verschiedenen Eingangsdaten durchgeführt. Die Vektoreinheiten berechnen dabei parallel das Skalarprodukt und geben das Ergebnis weiter. Durch die Integration eines lokalen Puffers für die Gewichte und einer direkten Anbindung an die MAC-Einheiten wird einerseits die Speicherbandbreite erhöht und andererseits werden durch die Wiederverwendung der Gewichte über mehrere Takte die Anforderungen an diese verringert. Diese Architektur erlaubt insgesamt eine hohe Flexibilität hinsichtlich des Datenflusses und ist damit auch für große DNNs gut geeignet [40].

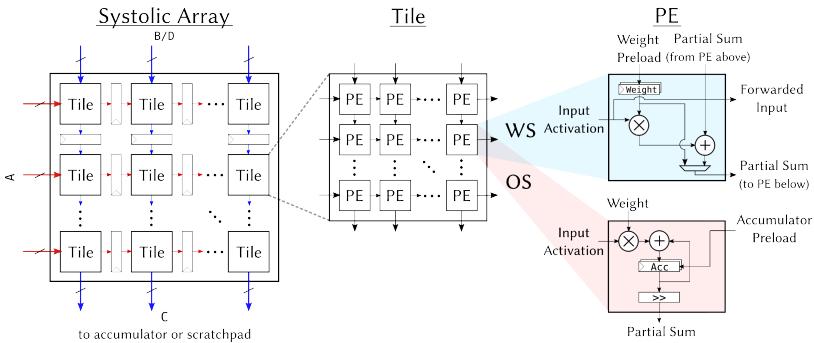

## 2.2.2 Systolische Arrays

Bei der Untersuchung von Hardware-Beschleunigern für DNNs ist festzustellen, dass der Aufbau eines systolischen Arrays eine häufig anzutreffende Architektur darstellt. Dies ist insbesondere in eingebetteten Systemen der Fall, bei denen sowohl ein geringer Stromverbrauch als auch eine hohe Performance gefordert sind. Eine solche Architektur ist in Abbildung 2.6 beispielhaft anhand von Gemmini [41] dargestellt. Die zweidimensionale

Abbildung 2.6: Gemmini Architektur aus [41]

Struktur ermöglicht die Weitergabe von (Zwischen-)Ergebnissen in zwei Richtungen innerhalb eines Takts, sodass Daten schnell weiterverarbeitet werden. Durch eine solch stark datenflussgetriebene Architektur erzielen derartige Hardwarebeschleuniger einen hohen Grad an Datenwiederverwendung und kommen daher gut mit einer geringeren Speicherbandbreite aus. Nachteilig an dieser Architektur ist die teilweise geringe Auslastung der Recheneinheiten im Array, da ein Layer nicht immer exakt passend auf die Hardware abgebildet werden kann. Dies ist besonders für in der Fläche beschränkte Systeme von Bedeutung.

Grundsätzlich ergeben sich für solche Architekturen mehrere mögliche Varianten des Datenflusses [42]. Im Falle von Weight-Stationary werden die Gewichte im lokalen Register der MAC-Einheit gespeichert und für mehrere Eingangsdaten wiederverwendet [41, 43]. Folglich wandern Eingangsaktivierungen und Zwischenergebnisse durch das systolische Array. Dagegen übertragen Output-Stationary Architekturen die Aktivierungen und Gewichte innerhalb des Arrays und speichern die Zwischenergebnisse im internen Speicher, bis die Berechnung abgeschlossen ist [44, 45]. Der Row-Stationary-Datenfluss basiert auf der Berechnung einer Reihe der Faltung in einer MAC-Einheit, wobei die Gewichte in einem internen Registersatz gespeichert werden [46, 47]. Dadurch müssen weder Zwischenergebnisse noch Gewichte innerhalb des systolischen Arrays weitergegeben werden. Abschließend ist auch eine Realisierung ohne Register in den MAC-Einheiten möglich (No Local Reuse). Diese Architekturen zielen auf einen minimierten Flächenbedarf ab und nehmen den dadurch den gestiegenen Bedarf an eine hohe Bandbreite hin [48]. Je nach Systemanforderungen wird somit ein entsprechender Aufbau des systolischen Arrays ausgewählt.

(a) Multiply-Accumulate operation

(b) Vector-Matrix Multiplier

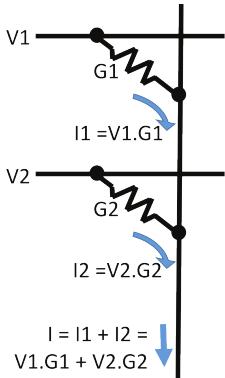

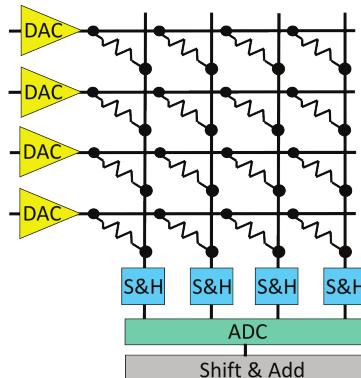

Abbildung 2.7: RRAM-Crossbar für die Ausführung von MAC-Operationen aus [49]

### 2.2.3 Processing-In-Memory

Für die Beschleunigung von DNNs in der Hardware gewinnen analoge Processing-In-Memory (PIM)-Architekturen zunehmend an Bedeutung. Basierend auf neuartigen Speichertechnologien wie Magnetoresistive Random Access Memory (MRAM), Resistive Random Access Memory (RRAM), oder Phase Change Random Access Memory (PCM) für diese eine Matrix-Vector-Multiplikation (MVM) direkt im Speicher aus, wodurch die Notwendigkeit der Übertragung von Gewichten entfällt. Im Vergleich zu anderen Speichertechnologien bieten sie eine hohe Dichte, inhärente Nichtflüchtigkeit und einstellbare Widerstandseigenschaften. Durch die zweidimensionale Speichermatrix aus solchen Bausteinen, die sogenannte Crossbar, werden die Berechnungen direkt analog ausgeführt, wie in Abbildung 2.7 schematisch dargestellt. Anhand des Stroms oder der Spannung auf den Bitleitungen lassen sich schließlich mittels Analog-to-Digital Converters (ADCs) die Ergebnisse der MVM auslesen. Da diese Operation die Grundlage für CONV- und Fully-Connected-Layer bilden, erlaubt die Verwendung von analogen PIM-Komponenten im System eine deutliche Steigerung der Leistungsfähigkeit und der Energieeffizienz im Vergleich zu Complementary Metal Oxide Semiconductor (CMOS)-basierten Beschleunigern [50]. Ein Nachteil ist allerdings die hohe Fehleranfälligkeit durch Überlagerung von Rauschen auf den Leitungen und Ungenauigkeiten im ADC bzw. den Bitzellen in der Crossbar. Folglich existieren verschiedene Techniken, die eine Fehlerkompensation in PIM-basierten Beschleunigern ermöglichen,

wie beispielsweise von Eldebiky et al. [51] vorgeschlagen durch das Einfügen entsprechender lernfähiger Layer in das DNN.

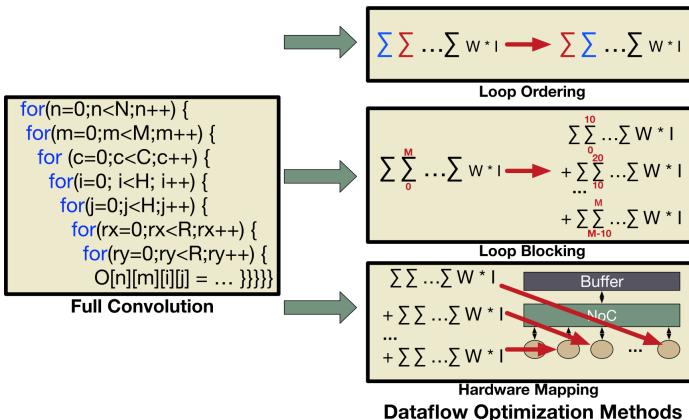

## 2.2.4 Hardware-Mapping

Die zeit- und energieeffiziente Inferenz eines DNNs in einem Hardwarebeschleuniger hängt maßgeblich von der Abbildung des Datenflusses auf die Architektur ab. Ein schlechtes Mapping führt demnach zu einer schlechten Auslastung der vorhandenen Ressourcen und folglich zu einer verringerten Performance und Energieeffizienz. Zusätzlich ist das Ziel eines guten Mappings ein hoher Grad an Wiederverwendung von geladenen Daten, um die Anzahl der zeit- und energieintensiven Speicherzugriffe zu reduzieren [52]. Dies kann zum einen auf räumliche Art geschehen, wobei Daten zwischen Recheneinheiten ausgetauscht werden. Eine solche Form der Datenwiederverwendung nutzen unter anderem systolische Arrays explizit aus. Alternativ kann eine Wiederverwendung von Daten auch in der zeitlichen Dimension erfolgen, wie es PIM-Architekturen inhärent implementieren. In diesem Fall werden die Daten, wie unter anderem die Gewichte, bereits vor der Inferenz vollständig lokal in den Beschleuniger geladen.

Wie in Abbildung 2.8 dargestellt, können jedoch schon zuvor Optimierungen des Datenflusses in Abhängigkeit von der Hardwarearchitektur vorgenommen werden. Zum Beispiel führt die Neuordnung der Schleifen eines Layers oder die Aufteilung einer Schleife in mehrere Blöcke zu einem Datenfluss, der sich besser auf die Architektur des Hardwarebeschleunigers abbilden lässt. Diese Optimierung kann dabei auch über Layergrenzen hinweg durchgeführt werden, um eine Datenwiederverwendung zwischen mehreren aufeinanderfolgenden CONVs zu ermöglichen [53].

Sind darüber hinaus die Gewichte bekannt, ist eine weitere Optimierung des Datenflusses möglich. Im Falle von Nullgewichten ist das Ergebnis der Multiplikationsoperation, die häufig in DNNs verwendet wird, bereits bekannt und die Berechnung kann daher entfallen. Darüber hinaus haben viele Gewichte einen Wert nahe Null, sodass die Multiplikation mit der Eingangsaktivierung keinen relevanten Einfluss auf die Inferenz hat. An dieser Stelle kann das sogenannte Pruning eingesetzt werden, welches alle Werte der Gewichte unterhalb einer definierten Schwelle auf Null setzt und somit eine Ausführung der mathematischen Operation überflüssig macht [54]. Daher ist auch dieser Einfluss auf den Datenfluss und damit auf das Mapping des Layers auf den Hardwarebeschleuniger zu berücksichtigen.

Abbildung 2.8: Optimierung des DNN-Datenflusses für das HW-Mapping aus [53]

## 2.3 Mehrzieloptimierung

Die Realisierung einer ressourcenbasierten Inferenz-Partitionierung in eingebetteten Systemen setzt die Betrachtung mehrere Metriken im Hardware-/Software Co-Design voraus. Aus diesem Grund handelt es sich hierbei um ein Mehrzieloptimierungsproblem, zu dessen Lösung sich in der Literatur verschiedene Verfahren finden lassen [55]. Beispielsweise sortiert die lexicographische Optimierung die Ziele nach abnehmender Wichtigkeit und optimiert anschließend schrittweise das Problem ausgehend vom wichtigsten Ziel. Für die in der vorliegenden Arbeit durchgeführte Optimierung des Systems ist dies allerdings von Nachteil. Ergibt sich bereits im ersten Schritt des Verfahrens eine einzelne optimale Lösung, werden nachfolgende Ziel nicht mehr betrachtet. Findet der Algorithmus beispielsweise zunächst eine einzige minimale Konfiguration hinsichtlich der Latenz, endet die Suche sofort ohne Analyse anderer relevanter Metriken.

Eine weitere Option ist die Gewichtung der einzelnen Zielfunktionen und eine Zusammenführung dieser in Form einer Summe. Auf diese Weise lässt sich das Problem als ganzzahliges lineares Optimierungsproblem darstellen und damit unter anderem durch den Simplex-Algorithmus lösen [56]. Dies ist für die in der vorliegenden Arbeit betrachtete Problemstellung aus zwei Gründen von Nachteil. Einerseits ist die gefundene Lösung stets ein Eckpunkt des zulässigen Bereichs und stellt damit nicht unbedingt die optimale Lösung dar. Wesentlich problematischer ist allerdings die Wahl passender Zielgewichte,

welche in komplexen Systemen unter Beachtung der verschiedenen funktionalen und nicht-funktionalen Metriken nur sehr schwer oder gar nicht in allgemeiner Form zu bestimmen sind. Dies liegt an den zum Teil konkurrierenden Zielen, wodurch eine vorteilhafte Abwägung zwischen den Metriken gefunden werden muss. So führt ein hoher Datendurchsatz durch parallele Verarbeitung von Daten in der Regel zu einem höheren Flächenbedarf im SoC im Vergleich zur sequentiellen Prozessierung der Daten.

Aus diesem Grund verfolgt die vorliegende Arbeit im weiteren Verlauf die Bestimmung möglichst vieler effizienter bzw. Pareto-optimaler Punkte im Suchraum. Solche Punkte sind wie folgt definiert [57].

**Definition 1** (Pareto-optimal). *Ein Element  $x \in X$  heißt Pareto-optimal bezüglich der Zielfunktionen  $c_i, i = 1, \dots, k$ , wenn es kein anderes Element  $x' \in X$  gibt, das die folgenden beiden Bedingungen erfüllt:*

$$\forall i, 1 \leq i \leq k : \quad f_i(x') \geq f_i(x), \quad (2.11)$$

$$\exists i, 1 \leq i \leq k : \quad f_i(x') > f_i(x). \quad (2.12)$$

Sind Gleichung (2.11) und Gleichung (2.12) erfüllt, dominiert  $x'$  das Element  $x$  streng und heißt Pareto-optimal. Die Bestimmung der Pareto-Front und damit von entsprechenden Lösungen solcher Mehrzieloptimierungsproblemen ist eine  $\mathcal{NP}$ -schwere Aufgabe [56] und folglich mit exponentiellem Rechenaufwand verbunden. Daher werden üblicherweise Heuristiken angewandt. Diese können zwar nicht gewährleisten, der Pareto-Front nahe zu kommen, liefern jedoch gute Ergebnisse in annehmbarer Zeit. Viele Metaheuristiken wie Simulated Annealing oder Tabu Search nutzen eine Zielfunktion, welche entsprechend zu optimieren ist.

Für die in dieser Arbeit betrachteten Problemstellungen stellt der genetische Algorithmus mit nicht-dominiertter Sortierung (NSGA) [58] und insbesondere dessen optimierte Variante NSGA-II nach Deb et al. [59] ein vorteilhaftes Suchverfahren dar. Allgemein basieren genetischen Algorithmen neben der Evaluation der potenziellen Lösungen auf mehreren Operationen, welche für jede neue Generation durchlaufen werden. Aus einer initial erzeugten Population, also einer Menge an Lösungen, werden zunächst durch Kreuzung der Individuen neue Lösungen generiert. Im Anschluss erfolgt eine zufällige Veränderung des Lösungsvektors durch die Mutation sowie eine Aussortierung einiger weniger geeigneter und nach Gleichung (2.11) dominierter Lösungen, welche durch die Selektion identifiziert werden. Auf diese Weise erkundet der Algorithmus den Suchraum parallel in verschiedene Richtungen hin zur

Pareto-Front. Da es sich bei diesen Verfahren um eine Verbesserungsheuristik [56] handelt, ist der Erfolg der Suche jedoch abhängig von der initialen Population. Bei Generierung einer schlechten initialen Population, findet der Algorithmus keine oder nur schlechte Lösungen. Folglich ist es bei der Verwendung solcher Verfahren notwendig, über Konstruktionsheuristiken wie dem Greedy-Verfahren [56] erste gute Lösungen als Ausgangspunkt der weiteren Exploration zu finden.

# Kapitel 3

## Stand der Technik

Die Inferenz-Partitionierung von DNNs ist ein Forschungsgebiet, das in den letzten Jahren zunehmend an Bedeutung gewonnen hat. Folglich wurden seit-her verschiedenste Methoden präsentiert, welche die Aufteilung des DNNs ab-hängig vom Anwendungsfall optimieren. Im Gegensatz zu klassischen Ansätz-en, welche die Arbeitslast über das System verteilen indem Funktionen innerhalb der Firmware ausgelagert werden, basiert die Inferenz-Partitionierung insbesondere auf dem Datenfluss. Allgemein lassen sich die Ansätze in Intra-Layer-Partitionierung, also einer parallelen Ausführung von Teilen eines Lay-ers auf verschiedenen Plattformen, sowie Inter-Layer-Partitionierung, einer sequentiellen Verarbeitung der DNN-Schichten, kategorisieren. Dieses Kapitel gewährt einen Einblick in den aktuellen Stand der Technik und zeigt schließlich auf, warum ein neuartiger Ansatz notwendig ist, um eine optimierte Inferenz-Partitionierung unter Beachtung relevanter Systemanforderungen zu erzielen.

### 3.1 Intra-Layer-Inferenz-Partitionierung

Verteilte eingebettete Systeme können besonders im IoT-Bereich stark von der Aufteilung der Arbeitslast über mehrere Plattformen profitieren. Die Intra-Layer-Inferenz-Partitionierung bietet sich dabei für Systeme an, welche aus vielen kleinen Recheneinheiten bestehen, welche parallel identische Rechen-operationen ausführen. Verfügen diese Plattformen über eine unzureichende Speicherkapazität oder Performance, so ist die vollständige Ausführung eines DNNs oder sogar einzelner Layer nicht möglich. In diesem Fall schafft die Partitionierung eines Layers Abhilfe.

Der aktuelle Stand der Technik umfasst verschiedene Verfahren, welche sich mit diesem Problem auseinandersetzen. Es existieren Ansätze, welche auf

eine Verteilung der Eingangsdaten über verschiedene Clients im Systeme zurückgreifen [60, 61, 62]. Dadurch übernimmt jedes Gerät im System einen kleinen Teil der Berechnung, deren Teilergebnisse anschließend an einem Punkt zusammengeführt werden. Gleichzeitig kann eine explizite Aufteilung der Rohdaten vom Sensor zu den Hardwareeinheiten zusätzlich für einen erhöhten Datenschutz sorgen [63].

Allgemein können die Eingangsdaten der Layer auf unterschiedliche Weise aufgeteilt werden. So schlagen Dey et al. [64] eine Aufteilung der Aktivierungen und der Filter entlang der Tiefe vor. Im Gegensatz zur ebenfalls häufig verwendeten zeilen- oder spaltenbasierten Partitionierung der Daten entsteht dadurch eine geringe Anzahl zusätzlich zu übertragender Informationen, verursacht durch den Stride-Parameter eines Layers. All diese Verfahren haben jeweils verschiedene Vor- und Nachteile und werden daher entsprechend der Anwendungsanforderungen eingesetzt [65, 66]. Die genannten Ansätze zeigen jedoch in ihrer Ausführung über das gesamte DNN betrachtet eine geringe Energieeffizienz sowie Performance. Grund hierfür ist die Notwendigkeit, Zwischenergebnisse zwischen den Recheneinheiten auszutauschen und die Aktivierungen des letzten partitionierten Layers zusammenzuführen. Eine Alternative hierzu ist die Betrachtung der statischen Aufteilung der Schichten bereits während des Trainings. So zeigen unter anderem die Untersuchungen [67, 68], dass dies zu einer signifikanten Reduktion des Datenaustauschs zwischen den Recheneinheiten im System führt. Allerdings bedeutet dies einen zusätzlichen Entwicklungsschritt, welcher den Prozess der NAS deutlich verlangsamt.

Um die Problematik der Datenabhängigkeiten zwischen den Schichten für die Intra-Layer-Inferenz-Partitionierung zu umgehen, wurde das Konzept der sogenannten Layer Fusion entwickelt. Bei diesem Verfahren erfolgt die Aufteilung der Berechnungen derart, dass die Ergebnisse direkt als Eingabe des nächsten Layers verwendet werden. Somit entfällt der Datenaustausch zwischen den Recheneinheiten im System. Hierfür werden die Eingangsaktivierungen je nach Methodik entweder entlang einer [69, 70, 71, 72] oder zweier Achsen [73, 74] aufgeteilt.

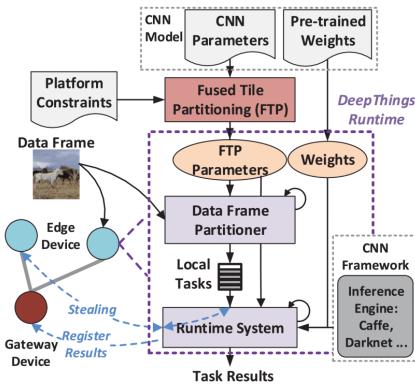

Letzteres nutzt auch das Open-Source Framework DeepThings [75], welches als eines der Vorreiter in diesem Forschungsfeld gilt. Eine Übersicht des Aufbaus ist in Abbildung 3.1 dargestellt. Im Zentrum der Arbeit steht das Fused Tile Partitioning (FTP), welches CONV-Layer in unabhängige Segmente partitioniert, die anschließend dynamisch zur Laufzeit über die im System verfügbaren Geräte verteilt werden. Dabei betrachtet das Framework insbesondere frühe CONV-Schichten des CNNs mit geringeren Speicheranforde-

**Abbildung 3.1:** Übersicht des DeepThings Frameworks aus [75]

rungen, um auch kleine Recheneinheiten einzubinden. Diese Verteilung der Aufgaben an die Plattformen erfolgt in DeepThings unter Beachtung der Leistungsfähigkeit sowie der zuletzt verarbeiteten Segmente, um eine möglichst hohe Datenwiederverwendung und damit einen geringen Kommunikationsaufwand zu erzielen. Auf diese Weise erlaubt die Interaktion zwischen den IoT-Plattformen die Ausführung komplexer CNNs im System mit geringerer Latenz und höherem Datendurchsatz als dies bei der Verwendung eines einzelnen Geräts für die Inferenz der Fall wäre. Abgesehen davon vernachlässigt das Framework jedoch wichtige Metriken wie beispielsweise die Energieeffizienz. Die Optimierung hat demnach ausschließlich das Ziel, eine möglichst hohe Performance zu erreichen.

Bei diesen Verfahren ist es jedoch unvermeidlich, die gleiche Berechnung mehrmals durchzuführen, wenn der Kommunikationsaufwand reduziert werden soll. Je mehr sequenzielle Layer eine Plattform ausführen soll, desto mehr Redundanz ergibt sich im Gesamtsystem. Im aktuellen Stand der Technik existieren Ansätze, welche sich ähnlich zu DeepThings auf die ersten Layer eines Netzes fokussieren und dort einen Austausch von Zwischenergebnissen unterbinden [76, 77]. Diese wenden stattdessen Zero-Padding an, wobei die fehlenden Datenblöcke durch Nullen aufgefüllt werden. Ohne zusätzliches Training führt ein solches Verfahren allerdings zu einer Verringerung der Genauigkeit des CNNs.

Des Weiteren ist bei der Intra-Layer-Inferenz-Partitionierung die Leistungsfähigkeit der verfügbaren Hardware zu berücksichtigen, wodurch die Suche nach einer optimalen Aufteilung an Komplexität zunimmt. Findet diese Me-

**Abbildung 3.2:** Übersicht des Map-and-Conquer Frameworks aus [82]

trik keine Beachtung, führt es wahrscheinlich dazu, dass performante Plattformen viel Zeit im untätigen Zustand verbringen. Auch für dieses Problem existieren geeignete Verfahren, die diese Randbedingung in die Verteilung der Aufgaben einbeziehen und folglich die Größe der Partition derart bestimmen, dass diese proportional zur Rechenleistung ist [77, 78, 79]. Folglich erhöht sich die durchschnittliche Auslastung der Plattformen und damit auch die Performance des Gesamtsystems. Auf FPGAs basierende Systeme, welche inzwischen in zahlreichen Anwendungsbereichen des High-Performance Computing (HPC) zum Einsatz kommen, erhöhen die Komplexität der Inferenz-Partitionierung aufgrund der erhöhten Flexibilität durch die Möglichkeit der Rekonfiguration der Hardware. Hierbei besteht die Herausforderung zusätzlich in der Verringerung des Kommunikationsaufwands zwischen den Plattformen bei Beachtung der limitierten Hardwareressourcen der verwendeten FPGAs [80, 81].

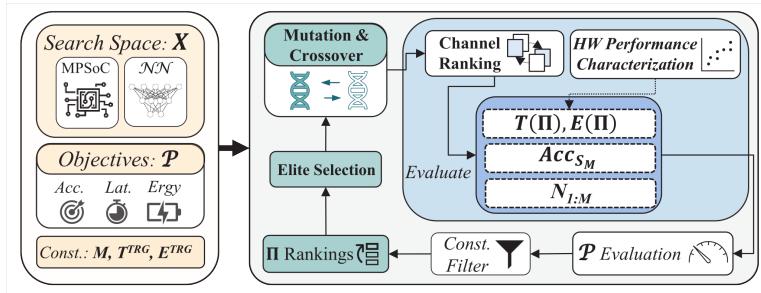

Die Inferenz-Partitionierung innerhalb eines heterogenen MPSoCs betrachtet beispielsweise das Framework Map-and-Conquer [82], welches in Abbildung 3.2 dargestellt ist. Das Verfahren analysiert dabei auch den Einfluss der verschiedenen Quantisierungen in den Hardwareeinheiten und zieht dies in die Bewertung der Partitionierungsschemata ein. Um das Mapping-Problem zu lösen, nutzen Bouzidi et al. einen Genetischen Algorithmus (GA), welcher als Ziel die Minimierung des Genauigkeitsverlusts, der Latenz und des Energiebedarfs hat. Auf diese Weise sucht das Framework nach einer optimalen Aufteilung des DNNs. Für die Ermittlung der Systemperformance eines möglichen Partitionierungsschemas setzt das Framework auf ein Gradient-Boosting-Verfahren. Die ML-basierte Methode durchläuft zunächst ein Training mit einem Datensatz, der verschiedene Layerkonfigurationen umfasst. Im Anschluss wird sie als Teil von Map-and-Conquer zur Abschätzung der

Abbildung 3.3: Übersicht des HybridAC Frameworks aus [84]

Latenz sowie des Energiebedarfs eingesetzt. Basierend auf den Evaluationsergebnissen ermöglicht dieses Verfahren eine signifikante Verbesserung von Energieeffizienz und Latenz der DNN-Inferenz in MPSoCs. Ähnlich diesem Ansatz sucht das ODiMO Framework [83] nach einer vorteilhaften Aufteilung des Netzes auf einen MPSoC bestehend aus analogem und digitalem Hardwarebeschleuniger. Im Gegensatz zum zuvor genannten Verfahren nutzt ODiMO analytische Modelle basierend auf Messergebnissen realer Hardware, um Latenz und Energiebedarf abzuschätzen. Für die Suche nach einem optimalen Partitionierungsschema findet zusätzlich auch der Einfluss der Aufteilung auf die Genauigkeit Berücksichtigung. Dies ist im Falle analoger Beschleuniger von entscheidender Bedeutung, da aufgrund des schlechten Signal-Rausch-Verhältnisses im Vergleich zu digitalen Architekturen eine höhere Anfälligkeit für Störungen besteht.

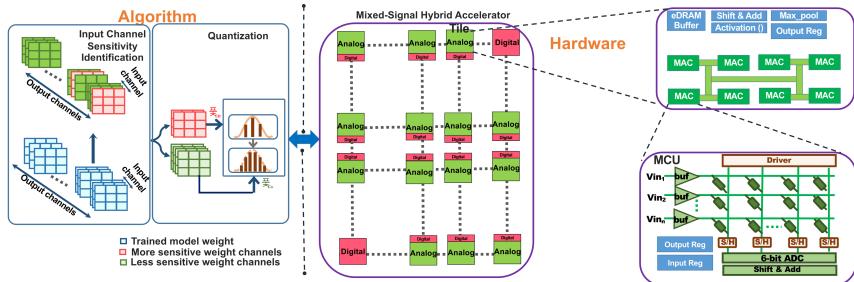

HybridAC [84] ermöglicht die Exploration zur Entwurfszeit für hybride Systeme bestehend aus einem analogen und einem digitalen Beschleuniger. Beispielhaft entwickelten die Autoren im Rahmen ihrer Arbeit ein SoC bestehend aus einem großen analogen und einem kleinen digitalen Beschleuniger, wobei letzterer für die Inferenz weniger robuster Kanäle der Layer zuständig ist. Eine Übersicht der Implementierung ist in Abbildung 3.3 dargestellt. Die Auswahl dieser Kanäle erfolgt, indem Gewichte extrahiert werden, die eine geringe Robustheit gegenüber Hardwarefehlern aufweisen. Dafür nutzt HybridAC einen Ansatz basierend auf [85], welcher für die Abschätzung auf die Hesse-Matrix zurückgreift. Durch dieses Hardware/Software Co-Design erreicht HybridAC eine optimierte Partitionierung verschiedener DNNs hinsichtlich relevanter Metriken wie Genauigkeit, Leistungsaufnahme, Fläche und Latenz. Dennoch zielt dieses Framework auf ein System mit dem analogen Beschleuniger im Zentrum ab und erlaubt dadurch keine automatisierte Exploration für Systeme aus mehreren Plattformen.

Aufgrund der hohen Komplexität der Intra-Layer-Inferenz-Partitionierung ist häufig eine umfassende Exploration möglicher Partitionierungsschemata notwendig, um eine optimierte Aufteilung der DNN-Inferenz zu finden. Für leistungsschwache Plattformen, welche über keinen anwendungsspezifischen Hardwarebeschleuniger verfügen, ermöglichen die genannten Verfahren jedoch generell die Ausführung der Inferenz im Gesamtsystem. Daher sind diese Methoden insbesondere für verschiedene eingebettete Systeme im Kontext von IoT relevant.

## 3.2 Inter-Layer-Inferenz-Partitionierung

Im Gegensatz zu IoT-Anwendungen stehen eingebetteten Plattformen im Automobilbereich oder einem ähnlichen Umfeld wesentlich mehr Ressourcen zur Verfügung. Damit einher geht eine sinkende Bedeutung der Intra-Layer-Inferenz-Partitionierung, da diese in der Regel ineffizient hinsichtlich Performance, Energie- und Speicherbedarf ist. Folglich fokussieren sich im aktuellen Stand der Technik wesentlich mehr Ansätze auf Formen der Inter-Layer-Inferenz-Partitionierung. Die nachfolgenden Ausführungen widmen sich einer vertiefenden Betrachtung der relevanten Aspekte dieser Thematik. Für die genaue Analyse werden dabei zunächst Methoden zur Inter-Layer-Inferenz-Partitionierung für FPGA-basierte und anschließend für eingebettete Systeme vorgestellt.

### FPGA-basierte Systeme

Wie zuvor erwähnt, nutzen viele Systeme neben klassischen GPUs, wie unter anderem die von Lane et al. entwickelte Software DeepX [86], inzwischen auch FPGAs für die Inferenz-Partitionierung von DNNs. Dabei kommt der Inter-Layer-Inferenz-Partitionierung ebenfalls eine wichtige Rolle zu, wie verschiedene Studien in den vergangenen Jahren demonstriert haben [87, 88, 89, 90]. Beispielsweise präsentieren Zhang et al. [91] einen Ansatz für das Mapping großer DNNs auf asymmetrische Multi-FPGA-Plattformen unter Beachtung der benötigten Bandbreite zwischen den Partitionen sowie der Ressourcenallokation der jeweiligen FPGAs. Für letzteres werden neben Flip-Flops (FFs) und Look-Up Tables (LUTs) auch DSPs und Block RAMs (BRAMs) betrachtet. Da das Verfahren auf Datencenter zugeschnitten ist, versucht der verwendete Optimierungsalgorismus ein Partitionierungsschema mit maximalem Datendurchsatz zu finden.

**Abbildung 3.4:** Übersicht des Elastic-DF Frameworks aus [92]

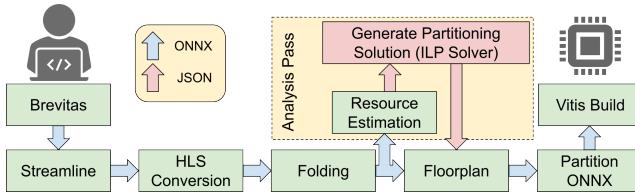

Ein ähnliches Ziel verfolgt Elastic-DF [92], welches in Abbildung 3.4 dargestellt ist. Das Framework generiert dafür zunächst eine Hardwarerepräsentation des DNNs auf dem FPGA, um daraus eine Abschätzung der benötigten Ressourcen abzuleiten. Unter Beachtung der vorhandenen Blöcke in den jeweiligen FPGAs sowie der Übertragungslatenz zwischen den Partitionen ermittelt das Framework automatisiert eine Aufteilung zwischen den verfügbaren Plattformen. Durch dieses Verfahren erzielt das Framework eine Verringerung der Latenz um bis zu 44 % und einen Anstieg des Durchsatzes um bis zu 78 %.

Kamath et al. [93] schlagen dagegen mit M5 ein Framework für die Inferenz-Partitionierung in FPGA-basierten Systemen vor, welches einen besonderen Schwerpunkt auf die Reduzierung der notwendigen Anzahl an FPGAs im System legt. Zu diesem Zweck nutzt M5 unter anderem einen eigens dafür konzipierten Explorationsalgorithmus, welcher mehr potenzielle Partitionierungsschemata in DNNs mit parallelen Pfaden findet als klassische Scheduling-Algorithmen. Für eine möglichst geringe Latenz und möglichst hohe Auslastung der verwendeten Hardwareressourcen analysiert M5 zusätzlich die Datenabhängigkeiten zwischen den Layern. Basierend auf den Evaluationsergebnissen erreicht die Anwendung des Verfahrens für verschiedene DNNs eine deutliche Reduzierung der benötigten FPGAs.

## Eingebettete Systeme

In Bezug auf eingebettete Systeme existiert eine Vielzahl von Verfahren zur Inter-Layer-Inferenz-Partitionierung. Allerdings wurden diese Verfahren bislang vorwiegend zur Untersuchung von im Handel erhältlicher Hardwareplattformen eingesetzt. Einige Methoden betrachten dabei lediglich ein oder zwei Metriken wie Latenz und Energieverbrauch [94, 95, 96, 97]. Beispielsweise evaluiert das von Huang et al. in [98] entwickelte Framework DeePar die Partitionierung zwischen einem mobilen Endgerät, einer Edge-Plattform

**Abbildung 3.5:** Übersicht von Neurosurgeon aus [99]

und der Cloud hinsichtlich der Berechnungsdauer. Deren Anwendungsstudie ergibt, dass eine Partitionierung zu einer Reduzierung der Gesamtlatenz von bis zu 80 % führt. Es sei jedoch darauf verwiesen, dass das Framework auf den hier betrachteten Anwendungsfällen beschränkt ist und wesentliche Metriken wie den Energiebedarf nicht berücksichtigt.

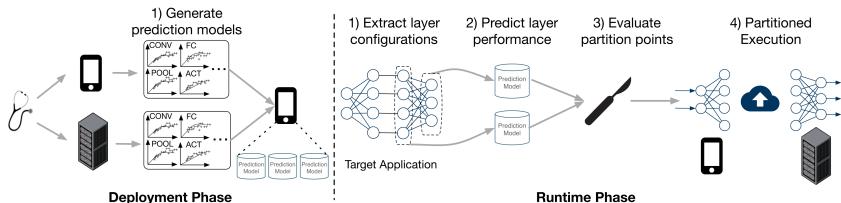

Als ein Vorreiter der Inter-Layer-Inferenz-Partitionierung von DNNs gilt der Scheduler Neurosurgeon [99], welcher nach einer optimierten Aufteilung der Arbeitslast zwischen mobilem Endgerät und der Cloud sucht. Wie in Abbildung 3.5 gezeigt, teilt sich das Verfahren in zwei Phasen auf. In der Deployment-Phase werden Vorhersagen für verschiedene Layer-Typen für die verwendeten Hardwareplattformen generiert. Diese Informationen werden in der zweiten Phase (Runtime-Phase) genutzt, um dynamisch den besten Partitionierungspunkt zu ermitteln. Dabei werden neben der Latenz auch die Auslastung des Datencenters sowie die geschätzte Leistungsaufnahme für die Inferenz im mobilen Endgerät zur Entscheidungsfindung herangezogen. Daneben zählt auch das Dynamic Adaptive DNN Surgery (DADS) Verfahren nach Hu et al. [100] zu den relevanten Methoden im aktuellen Stand der Technik. Im Vergleich zu Neurosurgeon erlaubt der Graph-basierte Ansatz auch die Partitionierung innerhalb paralleler Pfade, wodurch sich eine deutlich höhere Systemperformance erzielen lässt. Außerdem berücksichtigt DADS den Fall, dass aufgrund anderer Nutzer im Netzwerk nicht die gesamte Bandbreite zur Verfügung steht. Dies beeinflusst die Entscheidung der Partitionierung stark, da ein stark ausgelastetes Netzwerk zu einem deutlichen Anstieg der Latenz für die Übertragung der Daten führt. Gleiches gilt auch für das Framework RoaD-RuNNer [101], welches eine weitere Optimierung im Verfahren verwendet, um eine bessere Skalierbarkeit für große DNNs zu erreichen. So werden nicht alle Layer des DNNs im Profiling untersucht, sondern eine zufällige Auswahl an Schichten. Basierend auf den Messergebnissen bezüglich Latenz und Energiebedarf werden so die Metriken für alle anderen Layer abgeschätzt. Mit dem Framework PArtNNer [102] schlagen Ghosh et al. ein Verfahren ohne

**Abbildung 3.6:** Übersicht des SPINN Frameworks aus [108]

offline Profiling vor. In diesem Fall werden zur Laufzeit Messungen durchgeführt und basierend auf den Ergebnissen nimmt der Algorithmus schließlich die Inferenz-Partitionierung vor.

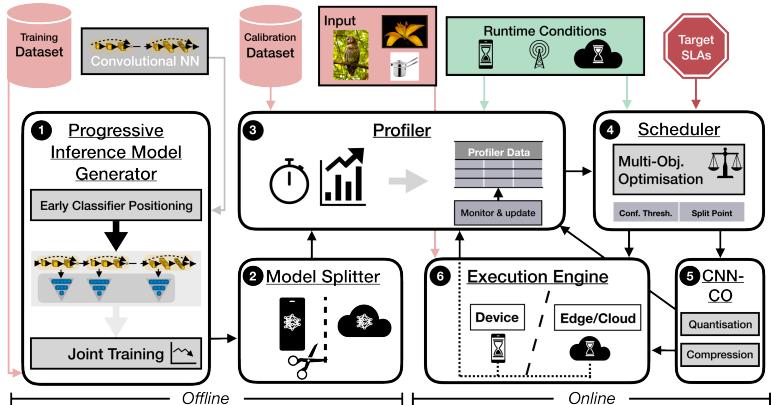

Ähnlich der zuvor vorgestellten Ansätze fokussieren sich mehrere Verfahren [103, 104, 105] ausschließlich auf die Latenz des Systems und nutzen für die weitere Optimierung der Inferenz-Partitionierung zusätzlich Early Exits im DNN. Dabei handelt es sich um eine von Teerapittayanon et al. [106] vorgeschlagene Anpassung der DNN-Architektur. In ein bestehendes Netz werden dabei Exit Points eingeführt, an denen ein neuer Pfad hin zu einer Ausgabe angehängt ist. Am Ende dieses Pfads – bestehend aus verschiedenen Layern – ermittelt das Netzwerk einen Parameter, der angibt, mit welcher Wahrscheinlichkeit die Vorhersage des Netzes korrekt ist. Liegt diese über einem definierten Schwellwert, wird die Inferenz beendet und das Ergebnis ausgegeben. Andernfalls führt das System die nachfolgenden Layer des DNNs auf dem ursprünglichen Pfad aus. Im Vergleich zur Inter-Layer-Inferenz-Partitionierung unveränderter DNNs führt dies zu einer erhöhten Komplexität des Optimierungsproblems, da die Wahl eines frühen Exit Points signifikante Auswirkungen auf relevante Metriken hat [107]. Die Integration von Early Exits nutzt auch SPINN [108], welches dynamisch zur Laufzeit des Systems entscheidet, welcher Exit Point für die laufende Inferenz ausgewählt wird. Wie in Abbildung 3.6 dargestellt, ermittelt das Framework in der Offline-Phase zunächst Early Exits sowie alle potenziellen Partitionierungspunkte des trainierten DNNs. Zur Laufzeit ermittelt der Scheduler basierend auf den Runtime Conditions einen Partitionierungspunkt und gibt diese Information

an den Communication Optimizer (CO) zur Reduktion der Datenübertragung. Das Framework Boomerang [109] optimiert diese Wahl weiter mittels Deep Reinforcement Learning nach Wang et al. [110], indem es zusätzlich nach einem optimalen Partitionierungspunkt auf dem Early Exit Pfad sucht und somit eine Verringerung der Datenübertragung erzielt. Problematisch hierbei ist, dass die Verwendung von Early Exits abhängig von der DNN-Architektur einen Einfluss auf die Genauigkeit hat und damit auch ein entsprechendes Training der neu hinzugefügten Layer benötigt. Auswirkungen auf die Genauigkeit hat ebenfalls das von [111] vorgeschlagene Verfahren, welches in ihrem Framework Auto-Split Anwendung für Edge-Cloud-Systeme findet. Das Ziel besteht in der Reduzierung der Latenz durch Partitionierung und individueller Quantisierung der in der Edge-Plattform ausgeführten Layer unter Beachtung der Speicherbeschränkungen sowie der zulässigen minimalen Genauigkeit des DNNs.

Neben der Latenz bewerten einige Ansätze auch den Energiebedarf der vorhandenen Plattformen für verschiedene Partitionierungsschemata. Beispielsweise schlagen Ghasemi et al. [112] ein Framework vor, welches auf eine energieeffiziente Inferenz-Partitionierung abzielt. Dabei soll insbesondere ein geringer Energiebedarf im mobilen Endgerät für die Berechnungen und Datenübertragung erreicht werden. Sie formulieren das Problem in Form eines gewichteten Graphen und nutzen das Min-Cut-Verfahren, um einen optimierten Partitionierungspunkt zu ermitteln. Für die Gewichtung der Kanten ist dabei ein Profiling der Leistungsaufnahme des Geräts notwendig. Zusätzlich dazu bezieht das Framework JointDNN [113] die Limitierung durch den aktuellen Ladestand des Akkus mit ein. Je nach Anforderungen und Systemzustand wird somit dynamisch zwischen verschiedenen Partitionierungspunkten gewechselt, die entweder auf Performance oder Energieeffizienz optimiert sind.

Das Open-Source Framework DEFER [114] ermittelt die Partitionierungspunkte anhand der Anzahl von im System verfügbaren Plattformen und der zu erwartenden Latenz pro Layer und optimiert anschließend die Übertragung durch verlustlose Komprimierung der Daten. Ein ähnliches Verfahren nutzen Li et al. [115] in ihrem JALAD-Framework, welches auf Huffman-Codierung zur Verringerung der benötigten Bandbreite bei der Partitionierung der DNNs zurückgreift. Die Entwickler von DynO [116] eliminieren den aufwendigen Schritt der Codierung durch unabhängige Quantisierung der zu übertragenen Aktivierungen zwischen den Partitionen in Kombination mit Bit Shuffling. Dies ermöglicht nach Einschätzung der Autoren eine deutlich höhere Komprimierung im nachfolgenden Schritt. Neben klassischen Algorithmen zur Komprimierung existieren im aktuellen Stand der Technik auch Verfahren,

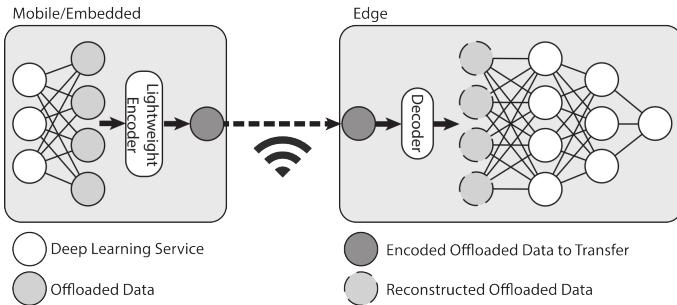

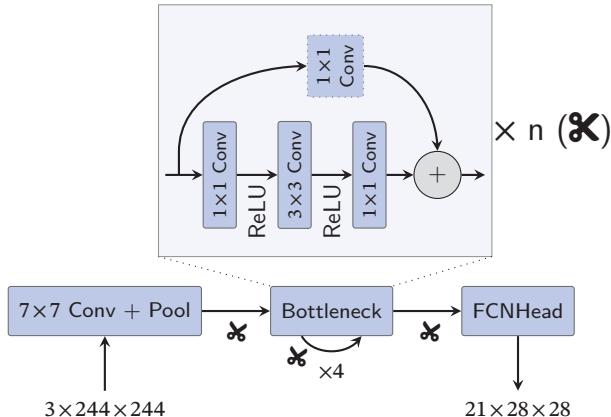

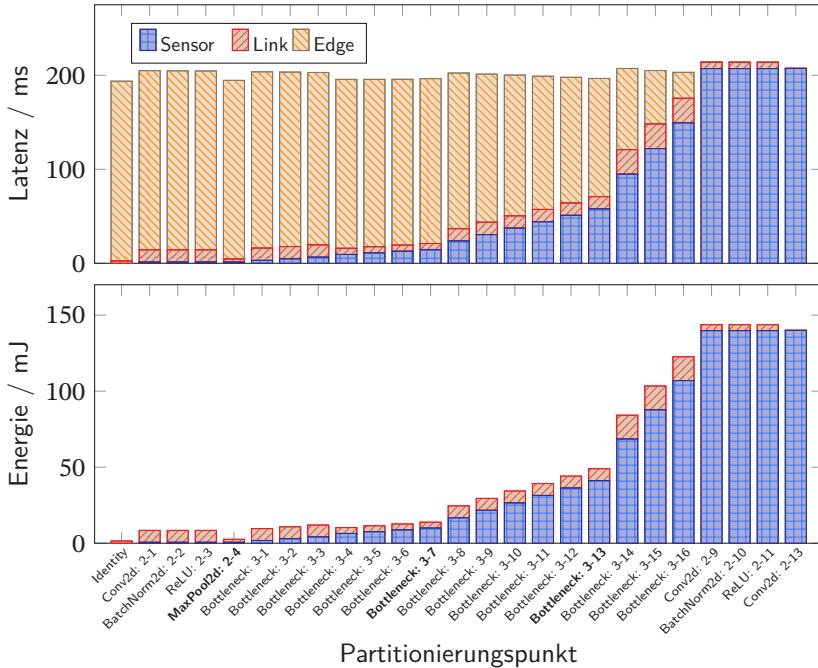

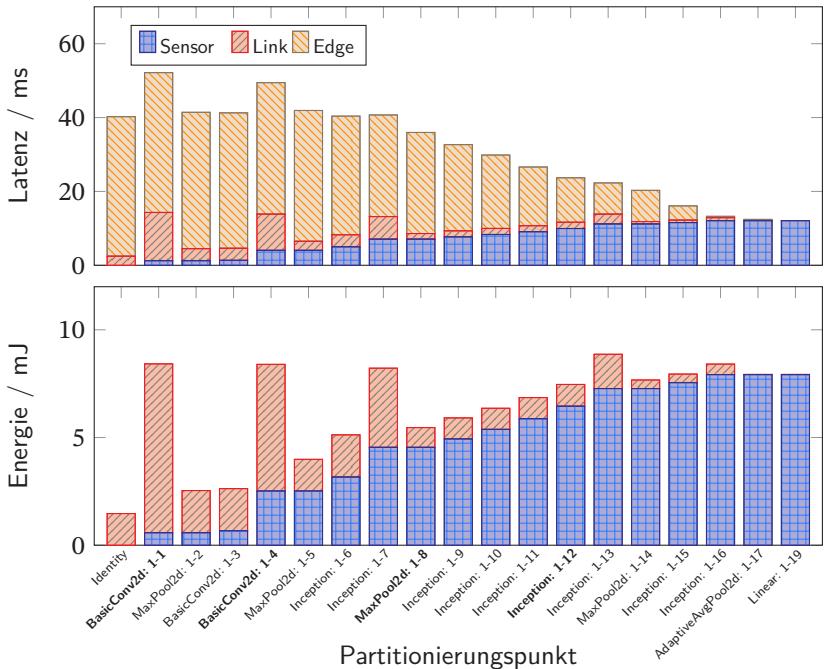

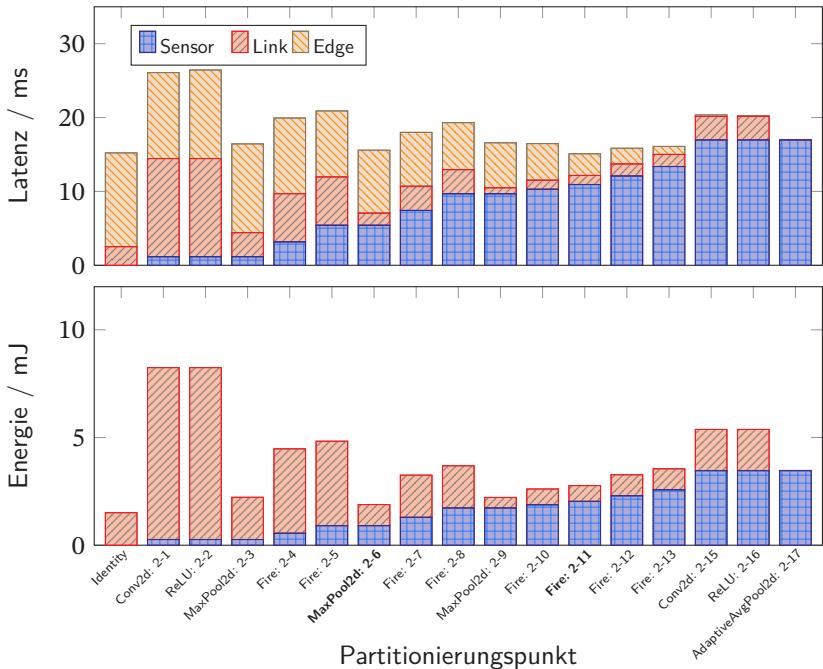

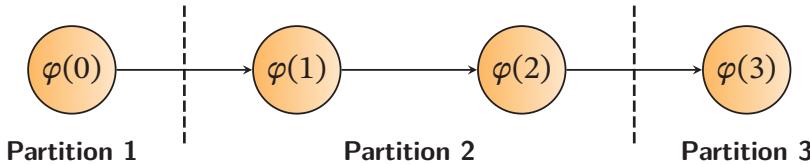

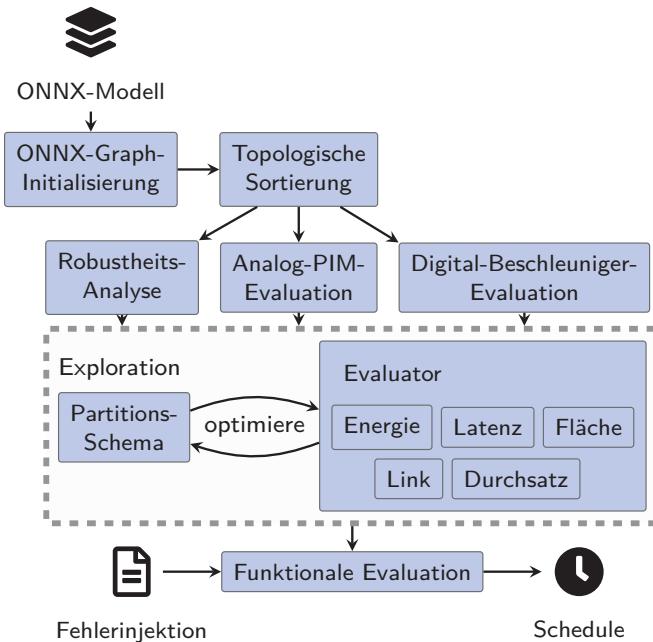

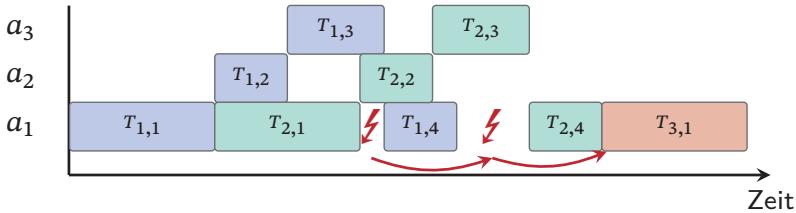

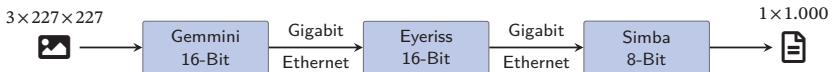

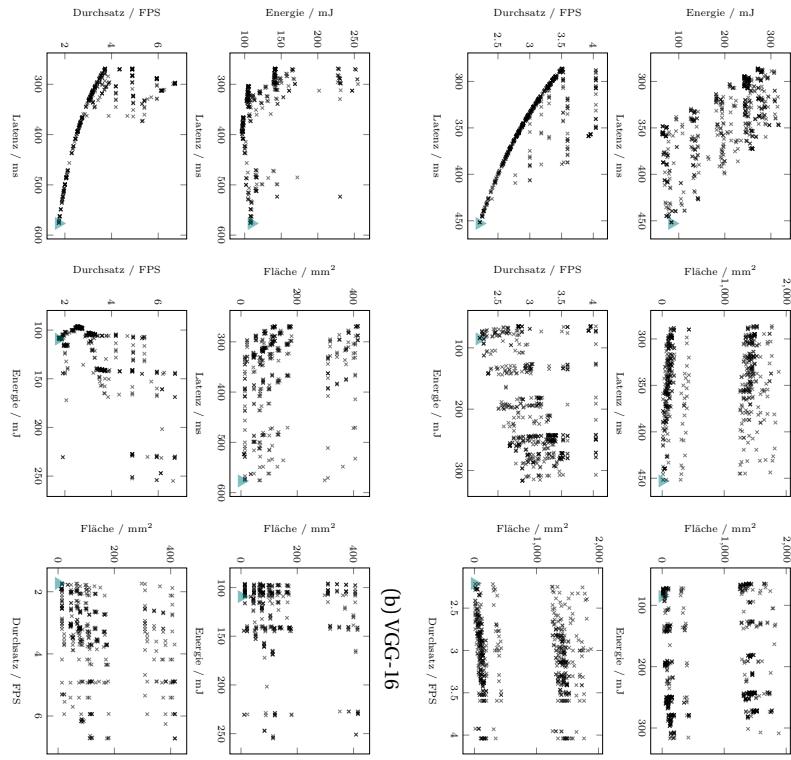

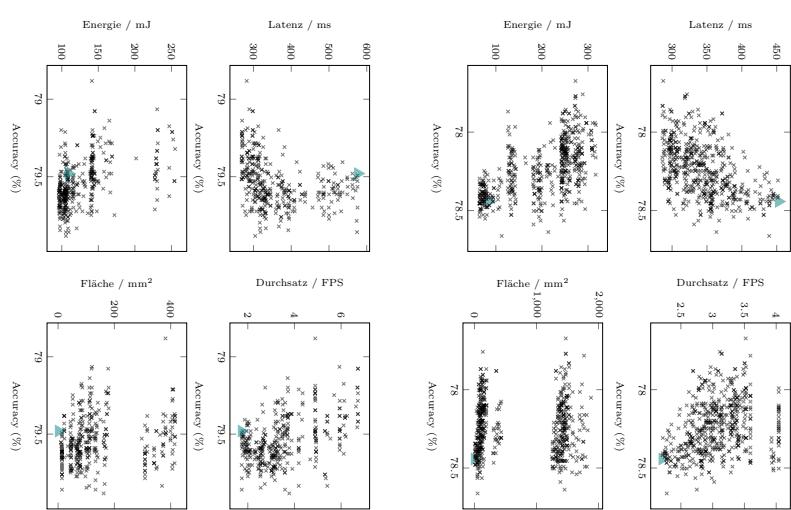

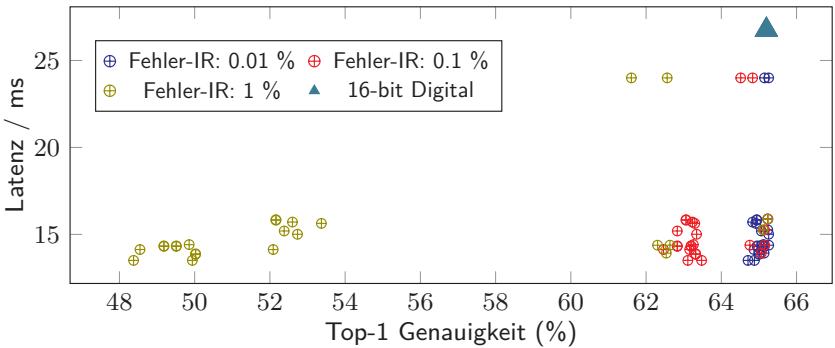

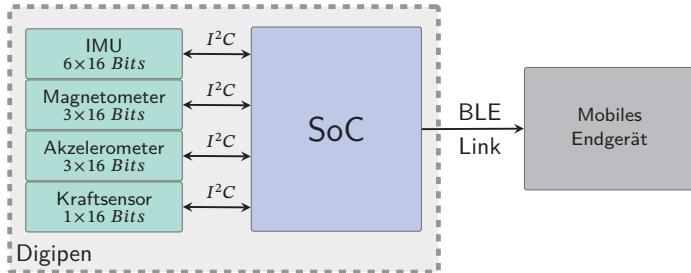

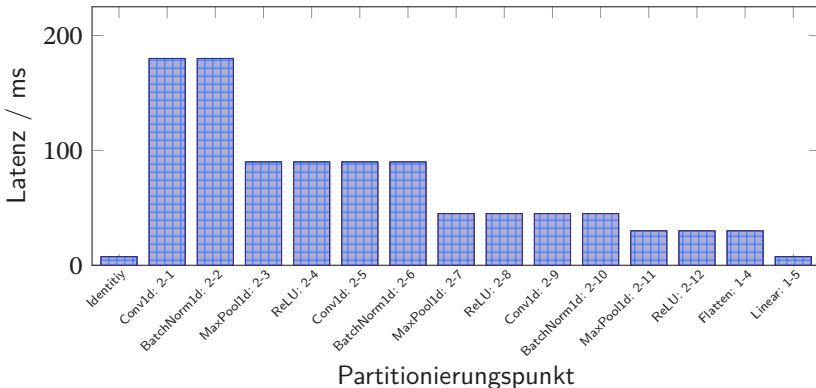

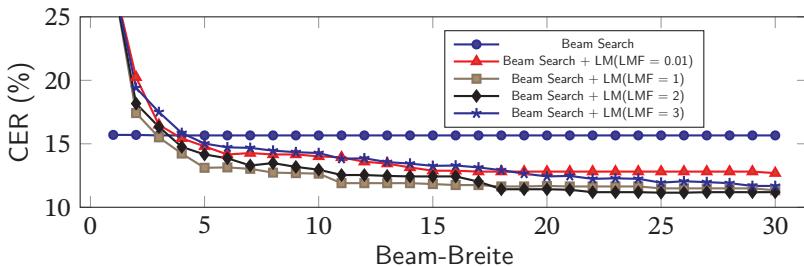

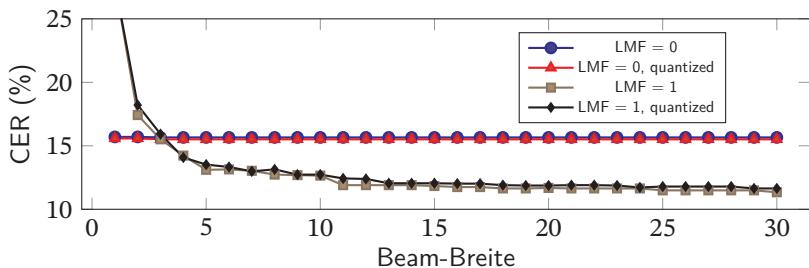

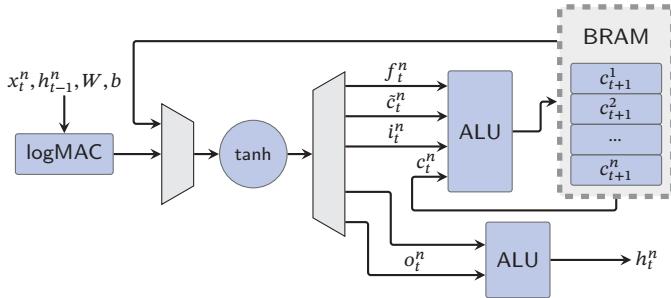

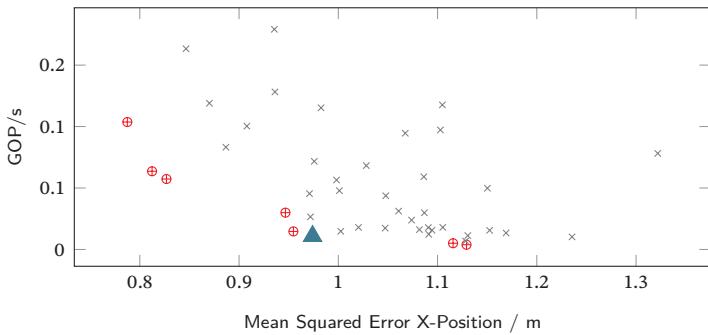

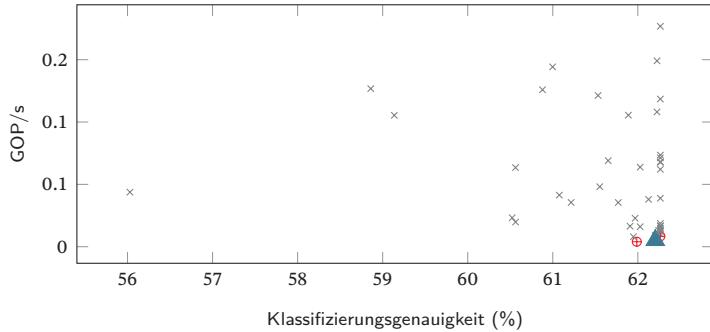

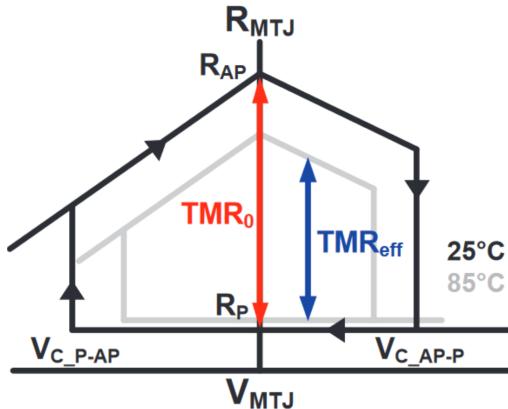

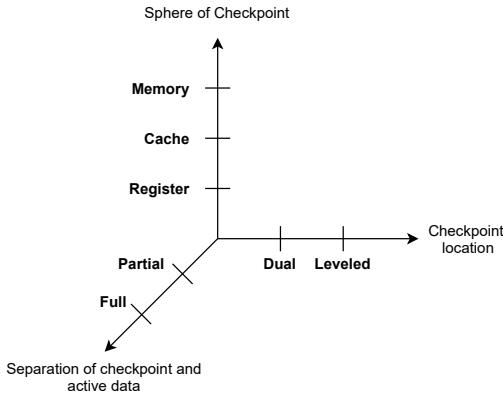

**Abbildung 3.7:** Übersicht des Deep Compressive Offloading Framework aus [118]