# Real-time reinforcement learning with online training for large-scale facilities

Zur Erlangung des akademischen Grades eines

Doktors der Ingenieurwissenschaften (Dr.-Ing.)

von der KIT-Fakultät für Elektrotechnik und Informationstechnik des Karlsruher Instituts für Technologie (KIT)

angenommene DISSERTATION

von

M.Sc. Luca Scomparin

geboren in Treviso (Italien)

Tag der mündlichen Prüfung: Hauptreferent: Korreferent: 28. March 2025 Prof. Dr.-Ing. Dr. h. c. Jürgen Becker Prof. Dr. rer. nat. Frank Simon

## **Abstract**

Modern advancements in machine learning (ML) offer solutions to complex problems, ranging from image classification, predicting the folding structure of proteins, providing agents with high-level conversational skills, or controllers capable of besting the current human champion in almost any conceivable game. Reinforcement learning (RL) is the perfect candidate for applying ML techniques to control problems, as it trains an agent to optimize outcomes through interaction with its environment, theoretically creating adaptable, turn-key controllers. The required large amounts of data for training, however, are impractical to gather in most real-world environments. Usually, the agent is thus trained on a simulated copy of the environment and then deployed to the real-world. This approach suffers from the so-called *sim2real* gap: a mismatch between simulation and reality can strongly reduce the performance of the agent. High-interaction-rate environments, like those in large-scale facilities, could quickly generate enough training data.

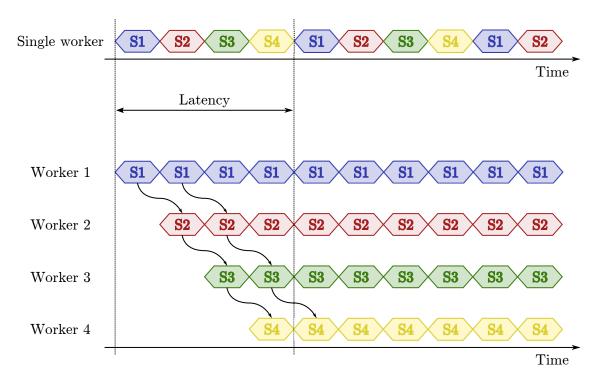

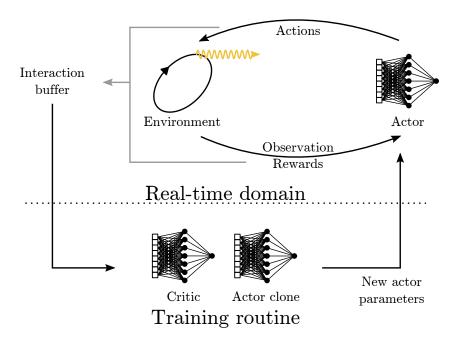

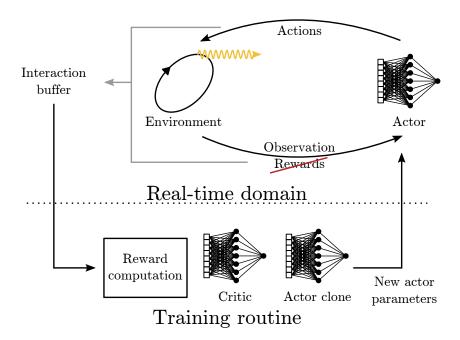

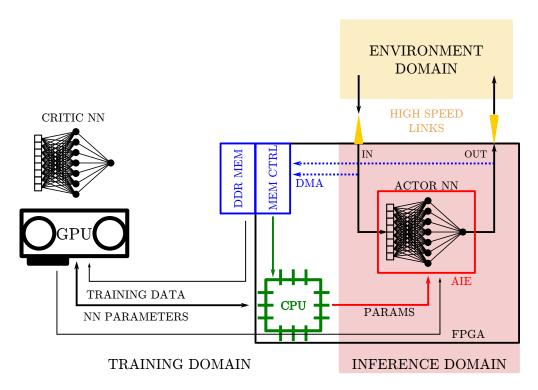

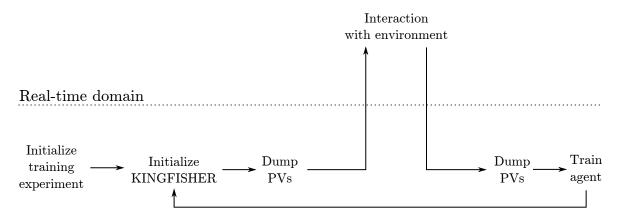

Online training on data gathered from a real-world environment entirely solves the issue of the *sim2real* gap. Adaptation of established RL algorithms to environments with real-time constraints requires extensive expertise, which is not commonly available to many experiments. In order to simplify the deployment of RL algorithms in these situations, the experience accumulator architecture was developed. This design pattern relies on a real-time agent, interacting with an environment, while its interactions are recorded. In this way the real-time constraints for the agent inference are automatically satisfied. These data is then transferred to another computation unit, where training can be performed with less stringent real-time constraints. A scheme was devised for computing the agent's reward at training time, in this way reducing the amount of components with real-time constraints and increasing the flexibility of the system by allowing exploration of different reward functions during an experiment.

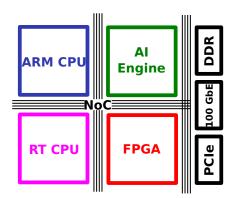

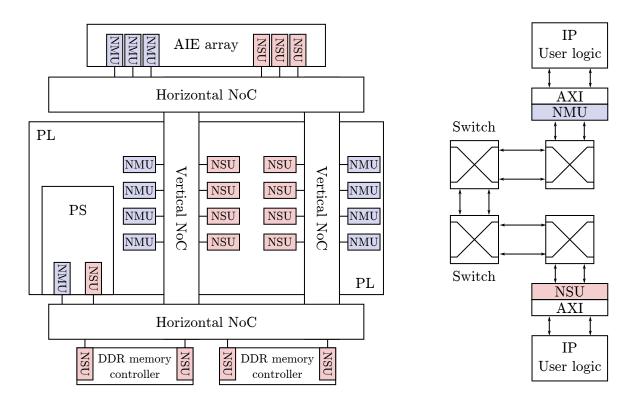

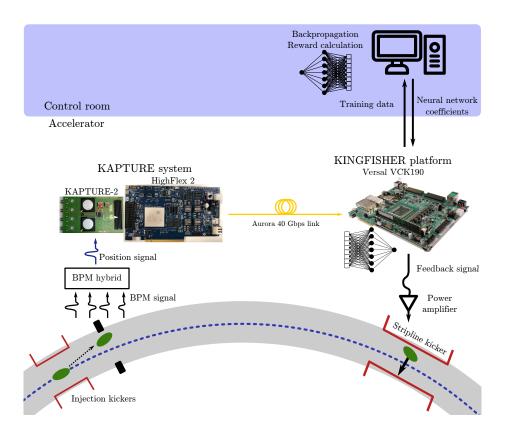

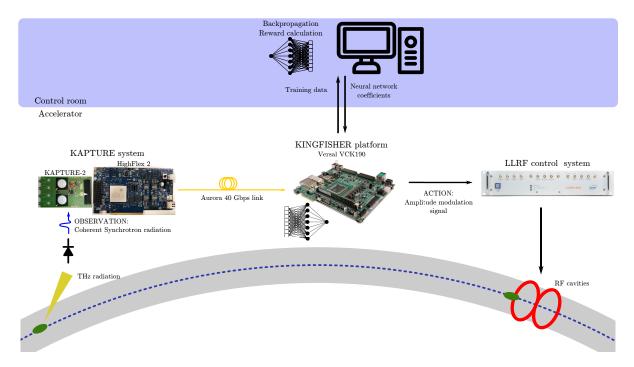

The implementation of RL policies with real-time constraints demands specialized hardware, enabling these ML solutions to operate on the edge by processing data directly on the devices interacting with the environment to minimize overall latency. To implement this architecture and simplify control experiments, the KINGFISHER platform based on the AMD/Xilinx Versal family of devices was designed and implemented. The main underlying idea is to create a library of the interfaces to large-scale facilities and common components necessary when implementing experience accumulator systems. In this way, the data processing path responsible for the low-latency inference of the RL policies becomes more modular and facility-independent, reducing the deployment effort.

A synchrotron light source and accelerator test platform such as the Karlsruhe research accelerator (KARA) is an ideal place to test a technology such as KINGFISHER and experience

accumulator systems. This large-scale facility provides several possible control problems that require actions within the microsecond timescale, thus being an interesting candidate for the application of an edge RL controller. The betatron oscillations offer a control problem that is well understood, for which a classical controller exists, allowing a proof-of-principle demonstration of the functionality of the system. On the other hand, a more challenging problem is needed to showcase the capabilities of these techniques. A good candidate is the microbunching instability, characterized by highly nonlinear self-interaction phenomena between an electron bunch and its own emitted coherent synchrotron radiation.

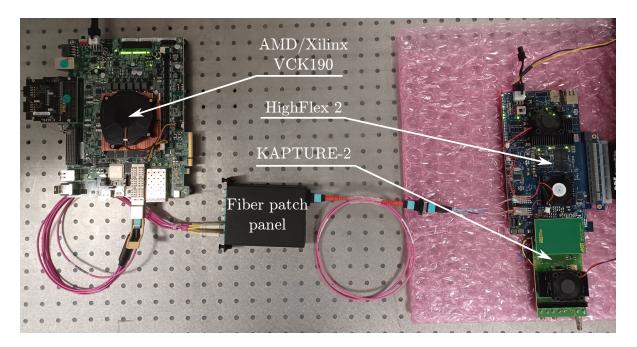

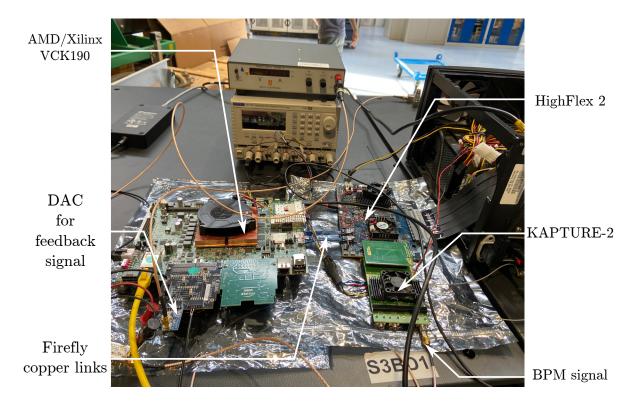

Furthermore, KARA offers cutting edge beam diagnostic infrastructure such as Karlsruhe pulse taking ultra-fast readout electronics (KAPTURE) and Karlsruhe linear array detector for MHz repetition rate spectroscopy (KALYPSO), providing continuous turn-by-turn information on the bunch position, synchrotron light emission, and charge density, that can be employed as the input of a controller. As part of this work, the KAPTURE system was integrated with the KINGFISHER platform, together with a transversal stripline kicker and the main radiofrequency (RF) system of the accelerator. These two systems are capable of acting with low-latency on the dynamics of interest for the control problem.

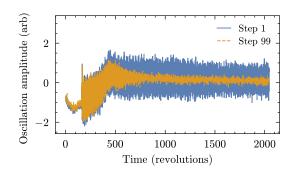

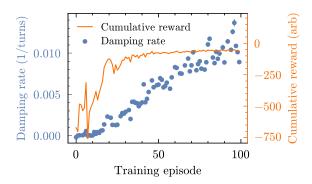

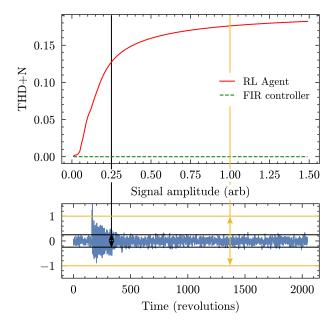

The system just described allowed performing experiments of the control of the horizontal betatron oscillations. KINGFISHER was first employed to test the conventional controller based on a finite impulse response filter feedback, as a further verification step that proved successful. Several RL-based controllers were then trained and tested. The system could reliably produce a functional controller every time. Often this achieved better performance than the conventional system. Furthermore, the amount of interaction time necessary to obtain enough training data by interacting with the machine is only 0.076 s, compared to the 17.6 s necessary on simulation. This result proves the effectiveness of the experience accumulator approach.

The more challenging problem of the control of the microbunching instability was then tackled. This kind of dynamics exhibits oscillations in two main frequency ranges: a bursting around a few tens of kHz, and a low-bursting around a few hundreds of Hz. These two phenomena represent very different control problems. Nonetheless, a classical controller developed in collaboration with the University of Lille, tackling the low-bursting was tested. This system was proven to be effective only in a specific range of beam currents. The RL controller also showed similar behavior, hinting to a fundamental characteristic of the instability. A few attempts were also carried out targeting the bursting oscillations.

In conclusion, the experience accumulator architecture with training time reward definition was conceived in order to deploy real-time RL agents. Albeit with a reduced flexibility compared to the libraries conventionally employed, the system was shown to be easily transferable to different control problems. Furthermore, the KINGFISHER system on the AMD/Xilinx Versal™ computing platform was designed and produced, leading to a first online learning edge system at a particle accelerator. Finally, two control problems at a large-scale facility were tackled with the system, showcasing its versatility and functionality.

## Zusammenfassung

Moderne Fortschritte im Bereich des maschinellen Lernens (ML) bieten Lösungen für komplexe Probleme, wie z. B. die Bildklassifikation, die Vorhersage der Faltstruktur von Proteinen, die Ausstattung von Agenten mit fortschrittlichen Konversationsfähigkeiten oder die Entwicklung von Steuerungssystemen, die menschliche Champions in nahezu jedem erdenklichen Spiel übertreffen können. Verstärkungslernen (RL) ist ein idealer Ansatz, um ML-Techniken auf Steuerungsprobleme anzuwenden, da es Agenten durch Interaktion mit ihrer Umgebung dazu trainiert, Ergebnisse zu optimieren, und somit theoretisch anpassungsfähige und einsatzbereite Steuerungssysteme ermöglicht. Allerdings erfordert das Training große Mengen an Daten, die in den meisten realen Umgebungen schwer zu beschaffen sind. Üblicherweise wird der Agent daher in einer simulierten Umgebung trainiert und anschließend in der realen Welt eingesetzt. Dieser Ansatz leidet unter der sogenannten "Sim2Real"-Lücke: Eine Diskrepanz zwischen Simulation und Realität kann die Leistung des Agenten erheblich beeinträchtigen. Hochinteraktive Umgebungen, wie sie in großtechnischen Anlagen vorkommen, könnten jedoch schnell ausreichend Trainingsdaten generieren.

Das Online-Training mit Daten aus einer realen Umgebung löst das Problem der *Sim2Real*-Lücke vollständig. Die Anpassung etablierter RL-Algorithmen an Umgebungen mit Echtzeitbeschränkungen erfordert umfangreiches Fachwissen, das in vielen Experimenten nicht allgemein verfügbar ist. Um den Einsatz von RL-Algorithmen in solchen Situationen zu vereinfachen, wurde die Experience-Accumulator-Architektur entwickelt. Dieses Designmuster basiert auf einem Echtzeit-Agenten, der mit einer Umgebung interagiert, während seine Interaktionen aufgezeichnet werden. Auf diese Weise werden die Echtzeit-Anforderungen für die Agenten-Inferenz automatisch erfüllt. Diese Daten werden dann an eine andere Recheneinheit übertragen, auf der das Training mit weniger strengen Echtzeit-Anforderungen durchgeführt werden kann. Ein Schema zur Berechnung der Belohnung des Agenten während der Trainingszeit wurde entwickelt, wodurch die Anzahl der Komponenten mit Echtzeit-Anforderungen reduziert und die Flexibilität des Systems erhöht wird, indem die Erkundung verschiedener Belohnungsfunktionen während eines Experiments ermöglicht wird.

Die Implementierung von RL-Strategien mit Echtzeit-Computing erfordert spezialisierte Hardware, sodass diese ML-Lösungen direkt an der Quelle, also auf den Geräten, die mit der Umgebung interagieren, betrieben werden können, um die Gesamtlatenz zu minimieren. Zur Umsetzung dieser Architektur und zur Vereinfachung von Steuerungsexperimenten wurde die KINGFISHER-Plattform auf Basis der AMD/Xilinx Versal-Gerätefamilie entworfen und implementiert. Die zugrunde liegende Idee ist der Aufbau einer Bibliothek von Schnittstellen zu großtechnischen Anlagen sowie häufig verwendeten Komponenten, die für die Implementierung von Experience-Accumulator-Systemen erforderlich sind. Dadurch wird der

Datenverarbeitungspfad, der für die latenzarme Inferenz der RL-Strategien verantwortlich ist, modularer und anlagenunabhängiger, was den Implementierungsaufwand reduziert.

Eine Synchrotronstrahlungsquelle und Plattform für Beschleunigertests wie Karlsruhe research accelerator (KARA) bietet einen idealen Rahmen, um eine Technologie wie KINGFISHER und Experience-Accumulator-Systeme zu testen. Diese großtechnische Anlage stellt mehrere Steuerungsprobleme bereit, die Aktionen im Mikrosekundenbereich erfordern, und ist somit ein interessanter Kandidat für den Einsatz eines Edge-RL-Steuerungssystems. Die Betatron-Oszillationen bieten ein gut verstandenes Steuerungsproblem, für das ein klassischer Regler existiert, was eine Machbarkeitsstudie der Systemfunktionalität ermöglicht. Andererseits ist ein anspruchsvolleres Problem erforderlich, um die Leistungsfähigkeit dieser Techniken zu demonstrieren. Ein guter Kandidat ist die Mikrobunchinginstabilität, die durch hochgradig nichtlineare Selbstwechselwirkungen zwischen einem Elektronenbündel und seiner emittierten kohärenten Synchrotronstrahlung gekennzeichnet ist.

Darüber hinaus bietet KARA eine hochmoderne Strahldiagnose-Infrastruktur wie KAPTURE und KALYPSO, die kontinuierlich turn-by-turn-Informationen über die Bündelposition, die Synchrotronstrahlung und die Ladungsdichte liefern können, die als Eingabe für einen Regler verwendet werden können. Im Rahmen dieser Arbeit wurde das KAPTURE-System mit der KINGFISHER-Plattform integriert, zusammen mit einem transversalen Stripline-Kicker und dem Haupt-RF-System des Beschleunigers. Diese beiden Systeme können mit niedriger Latenz auf die für das Steuerungsproblem relevanten Dynamiken einwirken.

Das beschriebene System ermöglichte Experimente zur Steuerung der horizontalen Betatron-Oszillationen. KINGFISHER wurde zunächst eingesetzt, um den herkömmlichen Regler basierend auf einem FIR-Filter-Feedback zu testen, was als erfolgreicher Verifizierungsschritt diente. Anschließend wurden mehrere RL-basierte Regler trainiert und getestet. Das System konnte zuverlässig jedes Mal einen funktionierenden Regler erzeugen, der oft eine bessere Leistung als das herkömmliche System zeigte. Darüber hinaus betrug die für die Datensammlung durch Interaktion mit der Maschine benötigte Zeit nur 0.076 s, verglichen mit 17.6 s in der Simulation. Dieses Ergebnis belegt die Effektivität des Experience-Accumulator-Ansatzes.

Das anspruchsvollere Problem der Kontrolle der Mikrobunchinginstabilität wurde ebenfalls angegangen. Diese Dynamik zeigt Oszillationen in zwei Hauptfrequenzbereichen: ein Bursting im Bereich von einigen zehn kHz und einem Low-Bursting im Bereich von einigen hundert Hz. Diese beiden Phänomene stellen sehr unterschiedliche Steuerungsprobleme dar. Dennoch wurde ein in Zusammenarbeit mit der Universität Lille entwickelter klassischer Regler getestet, der das Low-Bursting adressierte. Dieses System erwies sich als effektiv nur in einem spezifischen Bereich von Strahlströmen. Der RL-Regler zeigte ein ähnliches Verhalten, was auf eine grundlegende Eigenschaft der Instabilität hindeutet. Einige Versuche wurden auch durchgeführt, um die Bursting-Oszillationen zu adressieren.

Zusammenfassend wurde die Experience-Accumulator-Architektur mit der Belohnungsdefinition während der Trainingszeit entwickelt, um Echtzeit-RL-Agenten einzusetzen. Obwohl das System im Vergleich zu herkömmlichen Bibliotheken eine reduzierte Flexibilität aufweist, konnte es leicht auf unterschiedliche Steuerungsprobleme übertragen werden. Darüber hinaus wurde das KINGFISHER-System auf der AMD/Xilinx Versal-Computing-Plattform entwickelt

und implementiert, was zu einem ersten Online-Lernsystem an einem Teilchenbeschleuniger führte. Schließlich wurden zwei Steuerungsprobleme an einer großtechnischen Anlage mit dem System angegangen, was seine Vielseitigkeit und Funktionalität unter Beweis stellte.

# **Contents**

| Ab | stract | :       |                                                                     |

|----|--------|---------|---------------------------------------------------------------------|

| Zu | samm   | enfassı | ung                                                                 |

| 1. | Intro  | duction | 1                                                                   |

|    | 1.1.   | Motiva  | ation                                                               |

|    | 1.2.   | Resear  | ch questions                                                        |

|    | 1.3.   | Object  | rives and contributions                                             |

|    | 1.4.   | Outlin  | e                                                                   |

| 2. | Func   | lamenta | als and state of the art                                            |

|    | 2.1.   | Particl | e accelerators                                                      |

|    |        | 2.1.1.  | Synchrotron motion                                                  |

|    |        | 2.1.2.  | Betatron motion                                                     |

|    |        | 2.1.3.  | Synchrotron radiation                                               |

|    |        | 2.1.4.  | Microbunching instability                                           |

|    |        | 2.1.5.  | The Karlsruhe research accelerator                                  |

|    |        | 2.1.6.  | The KAPTURE system                                                  |

|    |        | 2.1.7.  | The KALYPSO system                                                  |

|    |        | 2.1.8.  | Summary                                                             |

|    | 2.2.   | Reinfo  | rcement learning                                                    |

|    |        | 2.2.1.  | Brief introduction to machine learning                              |

|    |        | 2.2.2.  | Neural networks                                                     |

|    |        | 2.2.3.  | Introduction to reinforcement learning                              |

|    |        | 2.2.4.  | Modern reinforcement learning                                       |

|    |        | 2.2.5.  | The current library landscape                                       |

|    |        | 2.2.6.  | Applications of reinforcement learning to large-scale facilities 32 |

|    |        | 2.2.7.  | Summary                                                             |

|    | 2.3.   | Comp    | uting devices                                                       |

|    |        | 2.3.1.  | Processing units                                                    |

|    |        | 2.3.2.  | Data transfer techniques                                            |

|    |        | 2.3.3.  | Real time computing                                                 |

|    |        | 2.3.4.  | Specialized ML coprocessors                                         |

|    |        | 2.3.5.  | Summary                                                             |

| 3. | Plati  | form de | velopment for real-time RL                                          |

|    | 3.1.   |         | ime reinforcement learning                                          |

|    | 3.2. | Experience accumulator architecture                                                   | . 61  |

|----|------|---------------------------------------------------------------------------------------|-------|

|    | 3.3. | Training-time reward definition                                                       | . 63  |

|    | 3.4. | High-level policy structure                                                           | . 64  |

|    |      | 3.4.1. Observation vector                                                             | . 65  |

|    |      | 3.4.2. Activation functions                                                           |       |

|    | 3.5. | Summary                                                                               |       |

| 4. | The  | KINGFISHER hardware platform                                                          | . 71  |

|    | 4.1. | Integration of KAPTURE                                                                |       |

|    |      | 4.1.1. Ethernet based connection                                                      |       |

|    |      | 4.1.2. Aurora based connection                                                        |       |

|    |      | 4.1.3. Comparison                                                                     |       |

|    | 4.2. | Data management system                                                                |       |

|    | 4.3. | Policy design                                                                         |       |

|    |      | 4.3.1. Intrinsics                                                                     |       |

|    |      | 4.3.2. Matrix-vector product                                                          |       |

|    |      | 4.3.3. Activation functions                                                           |       |

|    |      | 4.3.4. Observation vector                                                             |       |

|    |      | 4.3.5. Reconfiguration control                                                        |       |

|    |      | 4.3.6. Random number generation                                                       |       |

|    | 4.4. | Benchmarks                                                                            |       |

|    |      | 4.4.1. Feed-forward neural network benchmarks                                         |       |

|    |      | 4.4.2. Policy benchmarking platform                                                   | . 96  |

|    | 4.5. | Control system integration                                                            |       |

|    | 4.6. | Online training and reconfiguration                                                   |       |

|    | 4.7. | Summary                                                                               |       |

|    |      | ·                                                                                     |       |

| 5. |      | forcement learning control of the horizontal betatron oscillations $oldsymbol{\cdot}$ |       |

|    | 5.1. | Problem description                                                                   |       |

|    | 5.2. | Closing the feedback loop                                                             |       |

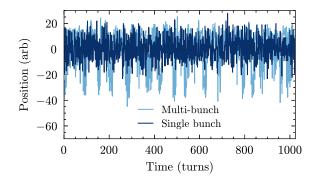

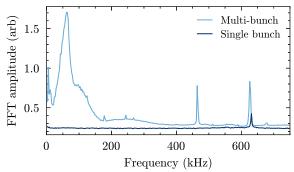

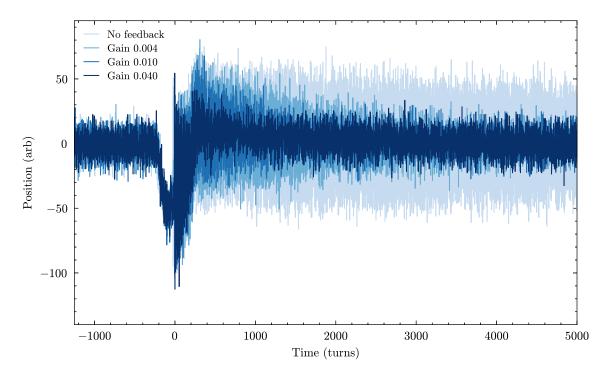

|    |      | 5.2.1. Effects of coupled bunch instabilities                                         |       |

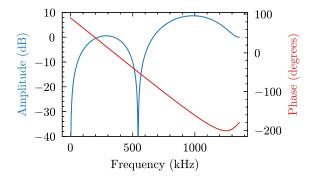

|    | 5.3. | FIR-based control                                                                     |       |

|    | 5.4. | Formulation as an RL task                                                             |       |

|    |      | 5.4.1. Simulation study                                                               |       |

|    | 5.5. | PPO policy implementation on KINGFISHER                                               |       |

|    | 5.6. | Reinforcement learning based control                                                  | . 112 |

|    |      | 5.6.1. Training-time reward definition                                                |       |

|    |      | 5.6.2. Online neural network reconfiguration                                          |       |

|    |      | 5.6.3. Training stability and robustness                                              |       |

|    |      | 5.6.4. Improvement during cumulative reward plateau                                   |       |

|    | 5.7. | Performance of the controller                                                         | . 117 |

|    | 5.8  | Summary                                                                               | 120   |

| 6.    | Rein    | orcement   | learning co | ontrol  | of th | e mi  | crob  | uncł  | ning | g ins | stab | ilit | у . | <br> |  |  | <br>121 |

|-------|---------|------------|-------------|---------|-------|-------|-------|-------|------|-------|------|------|-----|------|--|--|---------|

|       | 6.1.    | Task descr | ription     |         |       |       |       |       |      |       |      |      |     | <br> |  |  | <br>121 |

|       |         | 6.1.1. Po  | ssible obs  | ervabl  | es .  |       |       |       |      |       |      |      |     | <br> |  |  | <br>122 |

|       |         | 6.1.2. Se  | election of | action  |       |       |       |       |      |       |      |      |     | <br> |  |  | <br>122 |

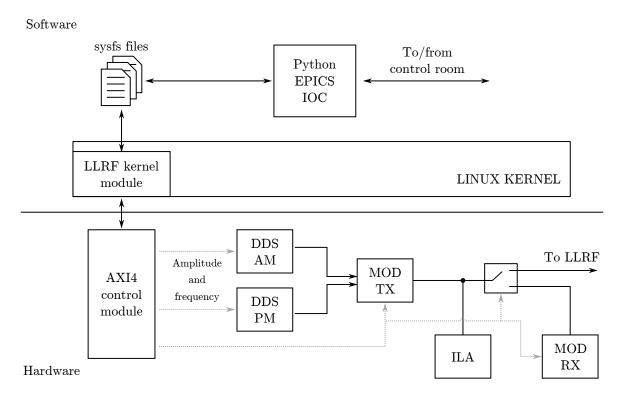

|       |         | 6.1.3. Lo  | w-level ra  | diofre  | quer  | ıcy s | yste  | m in  | teg  | rati  | on   |      |     | <br> |  |  | <br>124 |

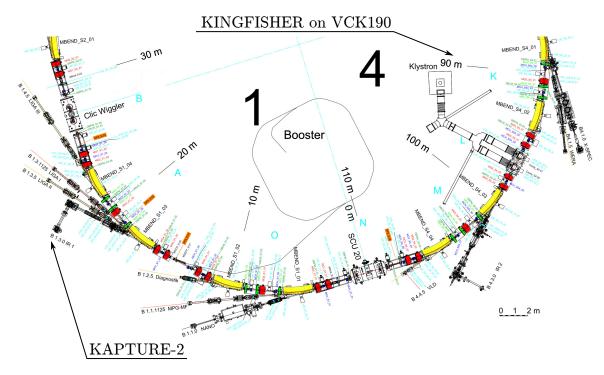

|       |         | 6.1.4. Fi  | nal KINGF   | ISHEF   | R ins | talla | tion  |       |      |       |      |      |     | <br> |  |  | <br>129 |

|       | 6.2.    | Feedback-  | based con   | trol .  |       |       |       |       |      |       |      |      |     | <br> |  |  | <br>131 |

|       | 6.3.    | Study with | h proporti  | onal c  | ontro | oller |       |       |      |       |      |      |     | <br> |  |  | <br>133 |

|       | 6.4.    | Formulati  | on as a rei | nforce  | men   | t lea | rnin  | g tas | k.   |       |      |      |     | <br> |  |  | <br>140 |

|       | 6.5.    | Reinforce  | ment learr  | ning ba | ised  | cont  | rol . |       |      |       |      |      |     | <br> |  |  | <br>142 |

|       | 6.6.    | Studies of | reinforce   | ment l  | earn  | ing c | ontr  | ol.   |      |       |      |      |     | <br> |  |  | <br>144 |

|       | 6.7.    | Discussion | n and outl  | ook .   |       |       |       |       |      |       |      |      |     | <br> |  |  | <br>145 |

|       | 6.8.    | Summary    |             |         |       |       |       |       |      |       |      |      |     | <br> |  |  | <br>148 |

| 7.    | Conc    | lusions    |             |         |       |       |       |       |      |       |      |      |     | <br> |  |  | <br>149 |

| A.    | Low-    | latency Fo | urier trans | form    |       |       |       |       |      |       |      |      |     | <br> |  |  | <br>153 |

| Acı   | ronym   | ıs         |             |         |       |       |       |       |      |       |      |      |     | <br> |  |  | <br>157 |

| Bik   | oliogra | phy        |             |         |       |       |       |       |      |       |      |      |     | <br> |  |  | <br>159 |

| ۵، دا | cnowl   | adamants   |             |         |       |       |       |       |      |       |      |      |     |      |  |  | 171     |

## 1. Introduction

#### 1.1. Motivation

Machine learning techniques have been proven successful in a wide variety of tasks that were before considered only approachable by a human. Driven by the availability of embarrassingly parallel computing platforms such as GPU, ever-larger models allowed to vastly extend the complexity of tasks that can be approached by these techniques. For example, unprecedented image classification was achieved in 2012 by AlexNet [1], paving the way to the usage of large convolutional neural network-based models. In 2022, a mere ten years afterwards, the large language model revolution occurred with OpenAI releasing ChatGPT. This large language model was the first widespread commercially available tool capable of carrying out conversations with a user through a chat-like interaction [2] while exhibiting human-level conversational skill. Furthermore, the 2024 Nobel Prize for Chemistry was shared by the AlphaFold [3] team. Their model was capable of predicting the folding structure of proteins, a previously unsolved problem in biochemistry. The difference in complexity that occurred in a span of only ten years is striking: AlexNet had 60 million parameters, while some versions of ChatGPT exceeded the 175 billion [4]. Recent versions of ChatGPT are estimated to have an even greater number of parameters. The possibility for ever greater computational power and machine learning models allows to approach problems that were previously impossible.

In the case of control problems, techniques such as reinforcement learning (RL) allow training an agent to optimize a reward signal by using information from interaction with an environment. These kind of techniques were employed in a wide variety of complex problems, such as playing Atari games surpassing expert human level [5]. The AlphaGo [6] model was capable of beating the Go world champion. Due to the sheer number of possible game states, it was considered much more complex than chess. For more scientific applications, RL algorithms were also capable of controlling the plasma in a fusion reactor [7].

One of the major benefits of RL techniques is their adaptability to varying conditions: the training procedure can be used, in case of drifts or variation of the control problem, to retune the agent. This capability is analogous to the one achievable with adaptive control techniques [8], were the parameters of a classical controller can be tuned based on the reconstructed state of the system under control. The key difference is the trade-off between problem complexity and stability guarantees. RL can solve extremely complex and non-linear problems, usually unattainable with the adaptive control approach. Its main drawback is that safety and stability guarantees are lacking, as safe-RL is still an open field of study [9], while the behavior of adaptive control techniques can be designed in a more deterministic manner.

Currently, the range of applicability of RL techniques to real-world problems is hindered by the large amount of data necessary for their training. Albeit some novel algorithms are mitigating this behavior [10], this usually makes training on a simulated version of the environment the only feasible option. Such a technique, although functional, encounters the so-called *sim2real* gap: subtle differences between the real-world environment and its simulation could lead to an under-performing, or non-functional agent.

The interaction rate with some real-world environments can be very high, in the order of several millions of interactions per second. This is often the case in large-scale facilities, which are specially designed installations equipped for specific purposes, requiring significant resources to operate, e.g. research, manufacturing, and commercial, such as experimental fusion reactors, particle accelerators, datacenters, etc.

In this case, obtaining enough data for training an agent would require only of a few seconds, opening the possibility of training an RL agent online by interaction with the real-world environment. The drawback of this approach is that these environments are challenging from a computational perspective, as they require an action to be chosen within a time frame dictated by the dynamics targeted by the control problem. This kind of requirement is known as a real-time constraint.

Performing computations and inference at such an high rate is challenging and requires specialized hardware and design techniques [11]. In order to minimize the inference latency of an agent, a common approach is for such systems to be deployed at-the-edge. Compared to cloud deployment, where computing resources are in a different physical location from where data is gathered, edge system process data were it is acquired. The reduction of data transfer times translates into a latency reduction. Furthermore, computing devices such as FPGAs allow to precisely define the timing of the data processing pipeline, making it possible to ensure that a given latency constraint is satisfied.

## 1.2. Research questions

This work uses a set of research questions to guide its investigation. These questions arise from the introduction, but their contextualization and answer will be carried out in the rest of this dissertation.

First of all, in order to approach these high repetition rate environments, one needs to investigate how RL algorithms can successfully be implemented in such a setting. The current implementations available cannot reach the required level of determinism and latency, and some new architectural ideas need to be conceived. Ideally, this new architecture should impact the flexibility of the system only marginally. Thus one could ask:

**Question 1** How can reinforcement learning algorithms be adapted so training on high-repetition rate environments can be performed?

Similarly to the RL algorithm implementations, the computing platforms where they are usually deployed on, such as central processing units (CPUs) and graphics processing units (GPUs), are not intended to operate with real-time in mind. Employing the platforms such as the ones intended for edge computing could greatly improve the performance of the system. As such:

**Question 2** How can reinforcement learning be deployed to an edge computing platform?

Such a RL platform should be verified to be functional, possibly by testing it at a large-scale facility or other high-repetition rate environments to ensure it operates as expected. Moreover, the fact that it is also capable of learning from the interaction with the environment and achieve control needs to be demonstrated. So:

**Question 3** *Is the edge-computing platform capable of learning online from interaction with an environment?*

Finally, it is interesting to compare the performance of these self-learning RL algorithms with more traditional control approaches, in order to determine their range of implementation and adaptability. Specifically, the training capability of RL allows to obtain an adaptive controller, but adds a further layer of complexity to the system. Understanding the difference of this approach with respect to a more conventional one is thus fundamental to guide future applications of the results described in this work. Thus:

**Question 4** How does online edge reinforcement learning compare to more traditional control approaches?

## 1.3. Objectives and contributions

In order to address question 1, a critical discussion of the timing constraints dictated by modern RL algorithms will be carried out. The main contribution of this work is a training scheme allowing to reuse current RL implementations as much as possible, so that the deployment and experimental effort is minimal, while trying to still maintain the microsecond latency performance needed during inference [12].

Additionally, the design of high-performance neural networks (NNs) for use as RL policies targeting the novel AMD/Xilinx Versal<sup>™</sup> platform, together with the necessary logic required for gathering training data, will be discussed in order to answer question 2. The necessary interfaces to communicate with a large-scale facility, together with the training data logic, have been packaged into the KINGFISHER framework [13].

Finally, question 3 and question 4 will involve the application of the aforementioned platform to two real-world problems [12, 14]. This represents the first application of low-latency online-learning RL at a particle accelerator. The performance of the approach will then be compared with the current state of the art controller. The stability of the RL controller is beyond the scope of this work.

#### 1.4. Outline

The work presented in this thesis is multidisciplinary by nature, as it requires an understanding of RL algorithms, how the electronics they will be deployed on operates, and what are the challenges encountered when working with particle accelerators. For the first deployment at a large-scale facility, before any intended hardware inter-operability standard is in place, one needs deep understanding of the functional aspect of the facility, together with the ones of the hardware trying to control it. As such, chapter 2 introduces in its three section these main background topics.

In section 2.1, an introduction to particle accelerators and the dynamics of particle beams will be carried out, together with a description of the Karlsruhe research accelerator (KARA) employed as a testing large-scale facility and its cutting edge diagnostic infrastructure.

To better understand the challenges of implementing RL algorithms, section 2.2 provides an introduction to machine learning, neural networks, and modern RL algorithms. Furthermore, the current state of the art implementations are described, together with some deployments to large-scale facilities that do not require strong real-time constraints.

Section 2.3 gives an introduction to the some available computing platforms, some of which will be employed in the later parts of this work. The challenging of real-time programming will be also discussed. Finally, the AMD/Xilinx Versal<sup>TM</sup> platform chosen as an edge platform will be described, together with its programming model.

After this introductory chapter, chapter 3 discusses the architecture of an RL edge system. Its implementation, together with a discussion of how neural network policies can be deployed to the AMD/Xilinx Versal™ platform, is carried out in chapter 4. Chapters 5 and 6 describe the application of the platform to two different kind of dynamics encountered at the Karlsruhe research accelerator. In chapter 5, the system is applied to the control of the horizontal betatron oscillations, for which a reliable classical controller is available, allowing to perform extensive comparisons, specifically regarding the adaptive nature of RL. Finally chapter 6 applies the system to the control of the microbunching instability, a problem for which a general solution has not yet been found.

## 2. Fundamentals and state of the art

The topic described in this work is multidisciplinary, combining elements from several different field. In order to fully contextualize the results, three subtopics will be introduced: particle accelerators in section 2.1, reinforcement learning in section 2.2, and computing platforms in section 2.3. Accelerators are a fundamental of this work, as their non-linear dynamics with timescales in the order of  $\mu$ s are the perfect candidate to apply the RL algorithms. This feat would be impossible without deep knowledge of computing platforms, specifically their timing characteristics.

#### 2.1. Particle accelerators

As discussed in the Introduction, one example of a large-scale facility where extreme conditions might be encountered are particle accelerators, such as synchrotron light sources. In this chapter, a brief introduction to the physics governing synchrotron light sources is provided, with a special focus on the longitudinal and transversal dynamics. Furthermore, the effect of coherent and incoherent synchrotron radiation emissions will be discussed, with a particular focus on the microbunching instability. Finally, Karlsruhe research accelerator (KARA) at KIT is then described, together with some challenging phenomena that might benefit from high-speed controllers. Finally, the high-performance diagnostic system available at the facility will be described.

KARA will serve as the test facility for the control system presented in this work, as it is readily available and provides challenging conditions that are difficult to capture in a simulation.

#### 2.1.1. Synchrotron motion

A charged particle can be guided along a circular path by means of an external magnetic field  $\vec{B}$  thanks to Lorentz force

$$\vec{F} = q\vec{v} \times \vec{B},\tag{2.1}$$

where  $\vec{v}$  is the velocity of the particle and  $\vec{F}$  is the force being applied to it<sup>1</sup>. In practice, the magnetic field is usually applied to a small volume called *beam pipe*, where the reference orbit

<sup>&</sup>lt;sup>1</sup> The path is not actually circular due to synchrotron radiation emission, more fully described in sections 2.1.1 and 2.1.3

of a particle resides in. The pipe is kept under ultra-high vacuum conditions to avoid particle losses.

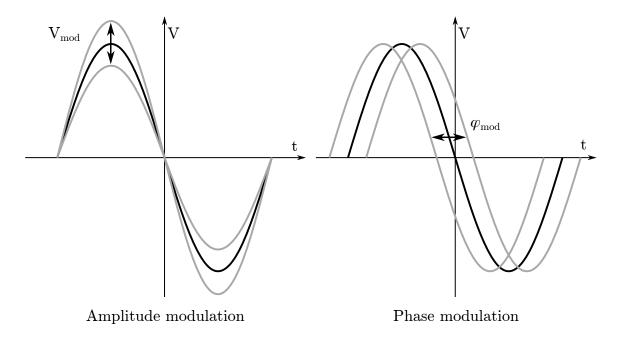

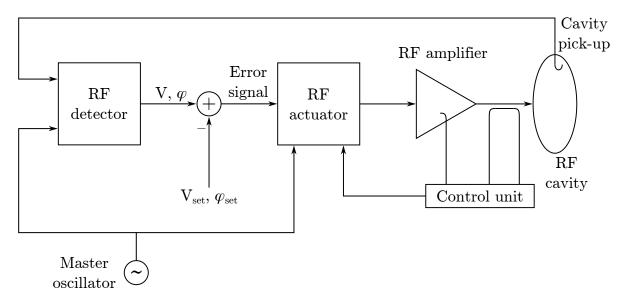

To balance the energy losses of the stored particles and to accelerate them, an alternating radiofrequency (RF) field is employed in order to produce a longitudinal electric field. In practice this is done by applying an high power RF signal to a *cavity*, where the standing wave mode produces the desired potential. This field usually oscillates at a frequency  $f_{RF}$  which is a multiple of the revolution frequency  $f_{rev}$ . Inside of the cavity, the RF potential encountered will have the form

$$V_{\rm acc} = V_0 \sin \left(2\pi f_{\rm RF} t\right),\tag{2.2}$$

where  $V_0$  is the amplitude of the RF field, and  $V_{\rm acc}$  the potential observed by a particle arriving at time t.

A particle accelerator can have several operation modes, defined by the combination of electromagnetic fields used for confinement and acceleration. Each of these modes has a reference orbit and energy defined during its design. A particle in such an orbit will remain on it if no perturbations are present. The revolution period along the machine is usually a multiple of the RF period. This allows to define the harmonic number,  $h \stackrel{\text{def}}{=} f_{\text{RF}}/f_{\text{rev}}$ . If the path length and velocity are constant over the reference orbit, given the period matches a multiple of the RF period, its arrival phase on the RF sinusoid will be constant. This phase is called the synchronous phase,  $\varphi_0$ .

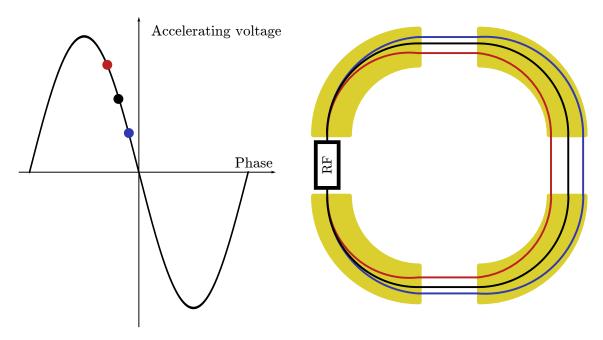

The set of magnetic fields of an accelerator, usually denoted as *lattice*, can be designed such that particles with an energy above the reference energy take a longer time to travel around the accelerator (figure 2.1). The opposite is true for particles with lower energy, as they will arrive earlier. For the correct slope of the RF voltage sinusoid, a lower energy particle, arriving late, encounters a stronger accelerating voltage, thus compensating its lower energy. Conversely, a higher energy particle will arrive late, obtaining a lower energy gain.

In the approximation of ultra-relativistic particles, for which  $\beta \stackrel{\text{def}}{=} v/c \approx 1$ , it is possible to construct a toy model of the longitudinal dynamics of the accelerator as follows. The path-length difference of an off-energy particle is usually described with the longitudinal momentum compaction factor  $\alpha_c$ , that is defined as<sup>2</sup>

$$\alpha_c \stackrel{\text{def}}{=} \frac{dL/L}{dp/p_0} \approx \frac{\Delta t_{\text{arr}}/dt}{dp/p_0},$$

(2.3)

where  $p_0$  is the reference momentum, L is the path length, and  $\Delta t_{\rm arr}$  is the arrival time difference compared to the reference particle over a time interval dt. This allows to compute the phase difference of an off-momentum particle as

$$\Delta t_{\rm arr} = \alpha_c \frac{\delta}{p_0} dt. \tag{2.4}$$

For non-ultrarelativistic particles, or in cases where  $\alpha_c$  is in the same order of magnitude as  $1/\gamma^2$ , the so-called *phase-slip factor*,  $\eta \stackrel{\text{def}}{=} \alpha_c - 1/\gamma^2$ , needs to be used, as it contains a part accounting for the mass of the particles.

**Figure 2.1.:** Schematic of the working principle of phase focusing. Particles with higher energy (blue), will have a longer trajectory than the reference particle (black), arriving late and thus experiencing a smaller energy gain. The converse is true for the lower energy particles (red).

where  $\delta \stackrel{\text{def}}{=} p - p_0$  is the momentum difference from the reference momentum.

By using the expression for the accelerating voltage of equation (2.2), one can linearize the problem and obtain the rate of energy gain for an off-energy particle with a given arrival time difference

$$d\frac{d\delta}{dt} \approx q \frac{dV_{\rm acc}}{dt} \bigg|_{\varphi_0} \Delta t_{\rm arr} f_{\rm rev} = qV_0 \cos(\varphi_0) 2\pi f_{\rm RF} \alpha_c \frac{\delta}{p_0} dt f_{\rm rev}, \tag{2.5}$$

where the  $f_{rev}$  is used because the increase of energy from the acceleration potential happens at a rate of once per revolution.

By rearranging the terms, one obtains

$$\frac{d^2\delta}{dt^2} = \frac{2\pi q V_0 \cos \varphi_0 f_{\text{rev}}^2 h \alpha_c}{p_0} \delta, \tag{2.6}$$

corresponding to the equation of an harmonic oscillator with frequency

$$f_{\rm s} = f_{\rm rev} \sqrt{\frac{qV_0 \cos \varphi_0 h \alpha_c}{2\pi p_0}},\tag{2.7}$$

known as the synchrotron frequency.

This acts as a reaction force leading to time-of-arrival, momentum, and longitudinal oscillations known as synchrotron oscillations. It is worth noticing how this has the effect of stabilizing the machine (figure 2.1): off-energy particles will not be lost, as they will start to oscillate around the reference particle. This phenomenon is called *phase-focusing* and is fundamental

**Figure 2.2.:** Magnetic field lines of a quadropole magnet. An electron (yellow) traveling in the direction entering the page, experiences a force (green) due to the local magnetic field (red).

to the operation of these machines. Moreover, it gives insight on the name of the machine: to increase the energy of the stored beam it is sufficient to *ramp* the magnetic field. This will change the synchronous phase making the bunch oscillate around it. The RF voltage needs then to be varied *synchronously* with the magnetic field. A particle accelerator using these principles is called a *synchrotron*. The mechanism responsible for the damping of these oscillations is described in section 2.1.3.

#### 2.1.2. Betatron motion

Similarly to how phase-focusing stabilizes the beam in a synchrotron along the longitudinal degree-of-freedom, it is possible to design the magnetic fields of the accelerator in a way where also horizontal and vertical stability is guaranteed. This is usually achieved with quadrupole magnets, albeit properly designed dipole magnets can nonetheless produce focusing.

As shown in figure 2.2, quadrupole magnets have four magnetic poles, arranged 90° from each other, with opposing polarities. A particle displaced by a distance d will experience a magnetic field B = Gd, where G is called the quadrupole gradient. Notably,  $\vec{B}$  had direction perpendicular to d. As such, due to Lorentz law (equation (2.1)), a particle would experience a force proportional to the displacement and directed along it

$$F = qvGd. (2.8)$$

Gauss's law for the magnetic field states that

$$\nabla \cdot \vec{B} = \frac{\partial B_x}{\partial x} + \frac{\partial B_y}{\partial y} + \frac{\partial B_z}{\partial z} = 0.$$

(2.9)

The partial derivative along z vanishes within the magnet, because it is symmetric along that direction. Along x the gradient is G by construction, so this fundamentally fixes the gradient along y to -G. Thus a quadrupole magnet is capable of focusing particles in one axis, while having a defocusing action in the other. This behavior can be fixed by combining several quadrupole magnets in doublets and triplets.

While traveling along the accelerator, a particle will experience a force according to equation (2.8), by substituting the expression of the momentum,

$$m\gamma \frac{d^2y}{dt^2} = qvG(t)y, \tag{2.10}$$

where  $\gamma = \sqrt{1 - \beta^2}^{-1}$ . It is worth noticing that the gradient will vary along the accelerator, thus it has a time dependence. The direction y was chosen because for motions in the accelerator plane x, and additional component is present due to the circular motion of the particles around the ring. It is possible to rewrite equation equation (2.10) as

$$\frac{d^2y}{dt^2} + K_y(t)y = 0, (2.11)$$

where K are called *focusing functions*. The equation for the x direction is identical, with the exception of containing an additional term within the K function.

An important characteristic of the function K is that it is periodic: every revolution the beam will return to a region with the same gradient. In the specific case where K is periodic, equation (2.11) is called Hill's differential equation. For accelerators an additional simplification can be performed: due to the fact that the gradient within a magnet is approximately constant, K is piecewise constant. As such it can be studied as the chaining of several harmonic oscillators that periodically change harmonic constant. The study of the stability of this function is beyond the scope of this work, but it is possible to design a lattice that has a stable solution. In that case, the solution to Hill's equation is

$$y(t) = y_0 \sqrt{\beta_y(t)} \cos(\psi_y(t) + \psi_{y,0})$$

$$\psi_y(t) = \int_0^t \frac{d\tau}{\beta_y(\tau)},$$

(2.12)

where  $\beta_y$  is the *beta-function*, a periodic function behaving like the local oscillation period.

An observer measuring the beam position at a fixed point in the accelerator will sample y(t) at each revolution. Specifically,

$$y_r = y(rT_{\text{rev}}),\tag{2.13}$$

where r is now the revolution index,  $T_{rev}$  is the revolution period. The number of oscillation periods at each revolution is constant, due to the periodicity of the beta-function, as such, one can define the *betatron tune* as

$$Q_y \stackrel{\text{def}}{=} \frac{1}{2\pi} \int_0^{T_{\text{rev}}} \frac{d\tau}{\beta_u(\tau)}.$$

(2.14)

From  $y_r$ , only the measurement of the fractional part of Q can be performed, as we might be under-sampling the betatron oscillation.

It is worth noticing though, that this introduction is primarily meant as a way of understanding the control problem that will be at hand. The topic, in fact, is vast and there are effects like chromatic aberrations, where higher energy particles are less bent by magnetic fields, i.e. are less focused, or the fact that a properly designed dipole magnet could in theory serve as an additional horizontal focusing element, that are beyond the scope of this introduction.

#### 2.1.3. Synchrotron radiation

Accelerated charged particles emit electromagnetic radiation. A particle on a circular orbit, even if its speed is constant, experiences a non-zero acceleration created by the change of direction of its velocity vector. The emitted power can be computed with Larmor's formula [15, 16]

$$P_{\parallel} = \frac{q^2}{6\pi\epsilon_0 c^3 m^2} \left(\frac{d\vec{p}}{dt}\right)^2 \tag{2.15}$$

$$P_{\perp} = \frac{q^2 \gamma^2}{6\pi\epsilon_0 c^3 m^2} \left(\frac{d\vec{p}}{dt}\right)^2 \tag{2.16}$$

For a particle in a circular accelerator, the perpendicular component is dominant. By using the fact that, for a particle moving on a circle

$$|d\vec{p}| \approx p \, d\theta = \frac{\beta c dt}{R} p,$$

(2.17)

where  $d\theta$  is an infinitesimal curvature angle, R is the curvature radius and  $\beta = v/c$ . If this expression is substituted into equation (2.16), one obtains the power emitted by synchrotron radiation, that in the ultrarelativistic regime when  $\beta \approx 1$  becomes

$$P_s = \frac{q^2 c}{6\pi\epsilon_0} \frac{1}{(mc^2)^4} \frac{E^4}{R^2}.$$

(2.18)

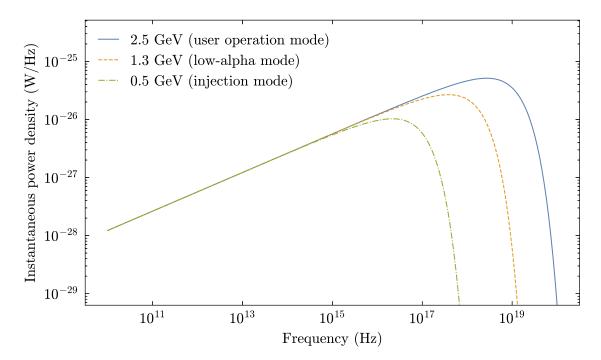

Noticeably,  $P_s \propto m^{-4}$  meaning lighter particles will radiate more power. This explains why this effect is extremely pronounced in electron accelerators. Additionally, the dependence  $P_s \propto E^4$  makes it increase very sharply with the energy of the particle. The power spectrum of the synchrotron radiation, in this case for KARA that will be better described in section 2.1.5, is shown in figure 2.3.

For control problems, synchrotron radiation plays an extremely important role. In the case of synchrotron radiation, for instance, the emitted power is greater for higher energy particles, and lower for lower energy ones. This in turn damps the synchrotron oscillations described in section 2.1.1. In the case of the betatron oscillations, on the other hand, the recoil resulting from the emission of radiation provides a very similar damping phenomena. A rule of thumb is that the damping time is in the order of  $\tau \approx E/P_s$ , i.e. roughly the time it would take the synchronous particle to loose all its energy via synchrotron radiation.

**Figure 2.3.:** Instantaneous radiated power per unit frequency for a single electron at three energies, which are typically set at KARA during operation.

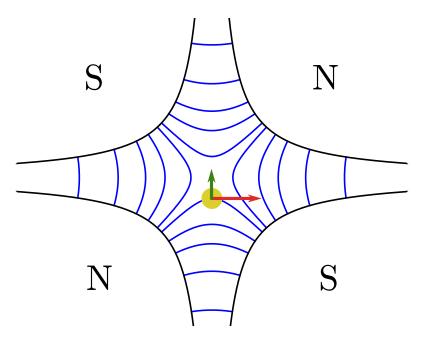

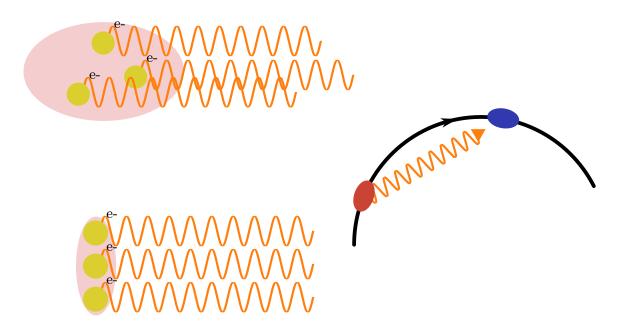

Depending on the charge distribution of the bunch, synchrotron radiation can be emitted incoherently or coherently (left side of figure 2.4). Incoherent synchrotron radiation (ISR) originates when the wavelength of the emitted radiation is smaller than the size of the bunch. In this case, the phases of the electromagnetic field of each particle are not correlated, and thus the fields are summed randomly, leading to an intensity of radiation  $I \propto N$ , with N the number of particles. If the wavelength is greater or comparable to the size of the bunch, the radiation from the particles is summed coherently, in this case leading to coherent synchrotron radiation (CSR) with the characteristic behavior that  $I \propto N^2$ .

This strong enhancement in radiation emission is considerable intensity gain for accelerator-based light sources, allowing the production of light with unprecedented brilliance. In the next section, one of the mechanisms responsible for the emission of CSR at synchrotron light sources will be described.

### 2.1.4. Microbunching instability

The electromagnetic fields from the magnets and RF cavities are not the only one experienced by the particles in a synchrotron. A given bunch can interact with its own emitted electromagnetic fields, or with the field of the other bunches. This can be modelled as an additional potential,  $V_{\text{wake}}(t)$  the wake potential, that is summed to the one of the accelerating structures. This can be computed by defining a wake function W(t), the potential that would be produced by a

**Figure 2.4.:** On the left, this drawing compares incoherent (top-left) and coherent (bottom-left) synchrotron radiation emissions. The right side illustrates an exaggerated representation of the radiation emitted by the bunch (red) catching up with the bunch itself (blue).

single charged particle. The total wake potential can be computed as the convolution of the wake function with the charge density  $\rho(t)$ , i.e.

$$V_{\text{wake}}(t) = \int_{-\infty}^{+\infty} d\tau \ W(t - \tau) \, \rho(\tau). \tag{2.19}$$

In synchrotron light sources, when the charge density increases above a certain threshold, microstructures in the longitudinal phase space start forming. These structures have a characteristic size such that they usually emit coherently in the terahertz frequency range. This emitted CSR is moving on a straight path, while the beam is curved on a closed path inside a dipole magnet (figure 2.4). As such the CSR creates wakefields, that in turn interacts with the microstructures that formed it. The effect of this self-interaction is that the emitted CSR power fluctuates sharply, in a phenomenon known as microbunching instability (MBI).

Systematic studies of this instability have been performed, highlighting its strong dependence on several parameters as the longitudinal momentum compaction factor  $\alpha_c$ , the accelerating voltage, the energy of the beam, the bunch current (or charge) and the longitudinal damping time [17].

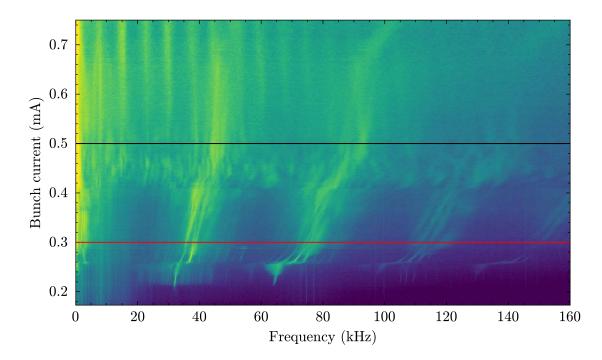

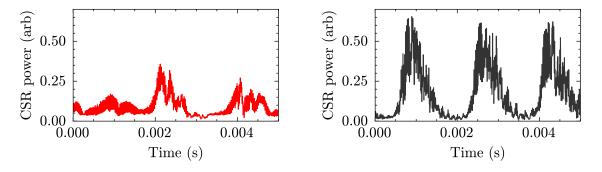

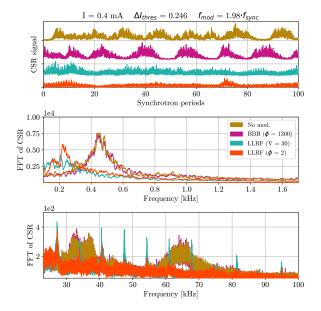

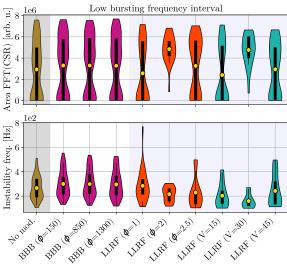

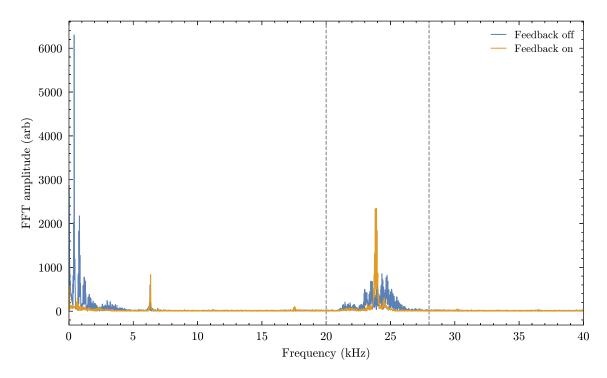

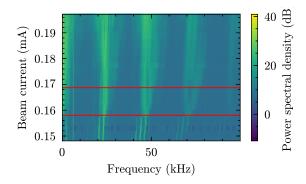

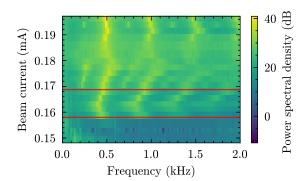

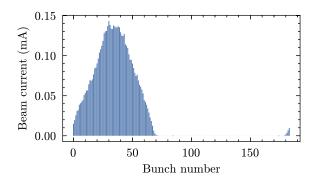

In figure 2.5, the fast Fourier transform (FFT) of the CSR signal amplitude (shown in figure 2.6) is shown as a function of the bunch current, for one specific machine setting. The instability starts above a threshold, where a roughly sinusoidal oscillation starts. Due to the shape of this feature in the plot, this is usually referred as *finger* or bursting frequency, and usually originates from the rotation of the microstructures in the phase space. As such, it is usually a multiple of the synchrotron frequency. When the current increases more, a second threshold is reached. Here the interaction of the CSR with the bunch is strong enough that the microstructures are

**Figure 2.5.:** Waterfall plot showing the FFT of the CSR power signal as a function of the current. The instability starts above 0.2 mA, with structures that strongly depend on the current. The horizontal lines indicate the current of the signal shown in figure 2.6. Data courtesy of Johannes L. Steinmann.

**Figure 2.6.:** Example CSR power signals corresponding to the currents of 0.3 mA (left) and 0.5 mA (right), also indicated by the horizontal lines in figure 2.5. Data courtesy of Johannes L. Steinmann.

washed out and the bunch length is usually increased. This stops the emission of CSR until the synchrotron radiation damping reduces the bunch size to a level where the microstructures can form and the process starts again. In this regime, the a slower, sawtooth shaped oscillation is superimposed to the bursting, and is called *low-bursting*.

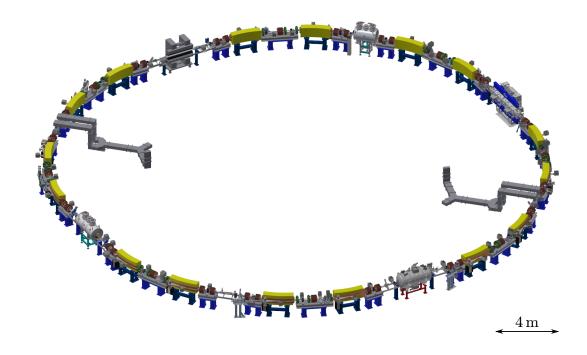

#### 2.1.5. The Karlsruhe research accelerator

The Karlsruhe research accelerator (KARA) is located at the Karlsruhe Institute of Technology, in Germany. It is a ramping electron storage ring, meaning that particles are injected at a lower energy, in this case 500 MeV, and then accelerated up to a maximum energy of

**Figure 2.7.:** Schematic of KARA. The beamlines are not shown. The dipole, quadropole and sextupole magnets are colored yellow, red, and green, respectively. Inside of the ring, the waveguides of the two RF stations are visible. Courtesy of Till Borkowski.

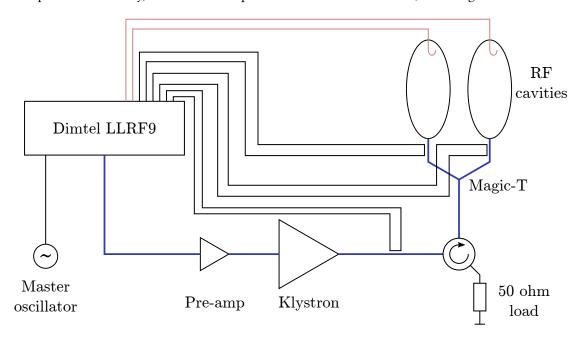

2.5 GeV. Its main RF system frequency is 500 MHz, with the accelerating voltage being applied in two station in opposing sectors of the machine. The ring is 110 m long, leading to a revolution frequency of 2.7 MHz and an harmonic number of 184. One of the peculiarities of this machine is the possibility of finely controlling the double-bend achromat lattice by tuning the five quadrupole and two sextupole families, in this way creating custom operation modes. Additionally, controlling the dipole, or *bend*, magnets, allows to control the energy of the specific operational mode [18].

The conventional operation mode for the synchrotron radiation users is at an energy of 2.5 GeV. Additionally, special modes with low, or negative, momentum compaction factor  $\alpha_c$  are available at several different energies [19]. The low-alpha mode, used to study the microbunching instability described in the previous sections, is usually at an energy of 1.3 GeV, and allows the selection of a custom value of  $\alpha_c$  from  $10^{-2}$  (user mode) to  $10^{-4}$ .

The beam is produced by an electron gun, at an energy of 90 keV [18]. It is then injected into a racetrack microtron that accelerates it to an energy of 53 MeV. Once a second, this system injects electron into the booster synchrotron that accelerates them to 500 MeV in roughly 500 ms. A system of three kickers and a septum merges the beam already being present in the KARA storage ring with the one coming from the booster.

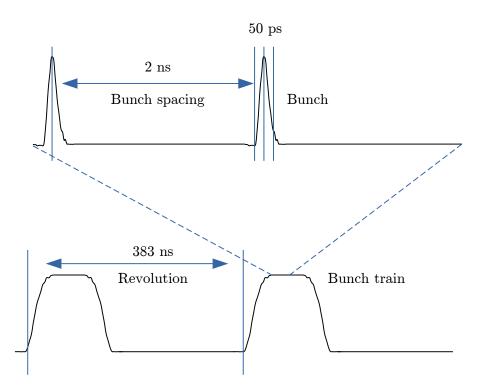

**Figure 2.8.:** Schematic representation of the signal produced by a synchrotron, highlighting the different timescales present. The pulse from a single bunch can have widths in the order of a few tens of picoseconds. Two consecutive bunches are separated by 2 ns, corresponding to the employed RF frequency of 500 MHz. The bunch filling pattern repeats at every revolution.

#### 2.1.6. The KAPTURE system

The signals produced by the circulating electrons in a synchrotron, such as the ones from synchrotron radiation or a beam position monitor (BPM), have a peculiar time structure (figure 2.8). For example, an ideal generic signal from KARA would exhibit the following characteristics. At long timescales, in the order of a few tens to a few hundred of microseconds, the synchrotron oscillations will be apparent. At smaller timescales, in the order of the revolution time ( $\approx 368\,\mathrm{ns}$ ), the charge distribution of the bunches in the machine, also known as *filling pattern*, will repeat at the revolution frequency. Furthermore, bunches will pass in front of a fixed observer at the main RF frequency, leading to a repetition with a  $\approx 2\,\mathrm{ns}$  period. The length of these bunches varies with operation mode, but is usually around a few tens of picoseconds. The response time of the detector used to produce the signal has a strong influence on the length and shape of the produced pulses.

In order to capture these fast peaked signals properly, one would need to sample the signal at very high rates in the order of hundreds of GS/s. Albeit technically possible, sampling at such high rates produces a challenging amount of data that needs to be saved and processed. This challenge is further compounded by the need to monitor the dynamics of these signals over several seconds, which significantly increases the amount of data generated and complicates both storage and analysis. This is unnecessary, though, given the pulse repeats at a much smaller rate compared to its width, most of the acquired signal will be empty.

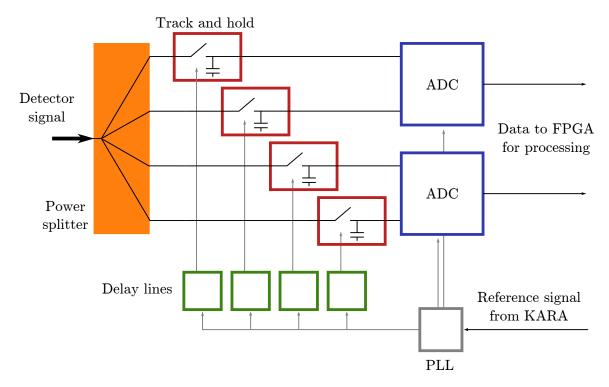

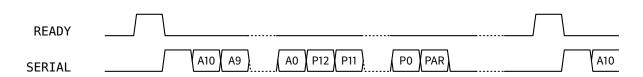

**Figure 2.9.:** Schematic of the working principle of the KAPTURE system. The signal to be acquired is split in four identical copies that are then sampled with a track and hold. The sampling time is finely tunable through delay lines. A PLL produces the reference clocks for the delay lines and the ADCs. The ADCs finally digitize the signal that is then processed by the FPGA.

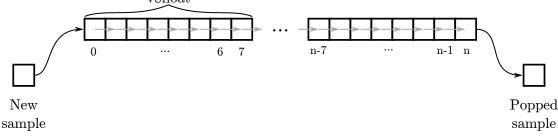

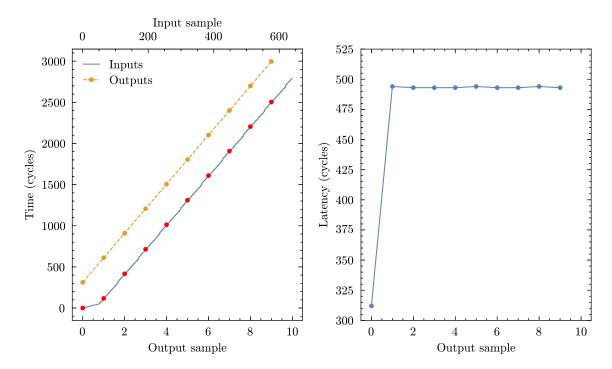

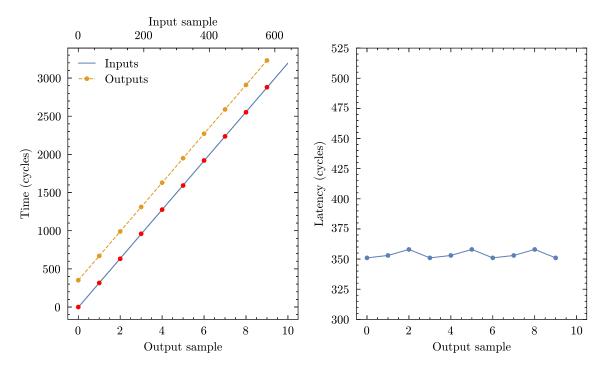

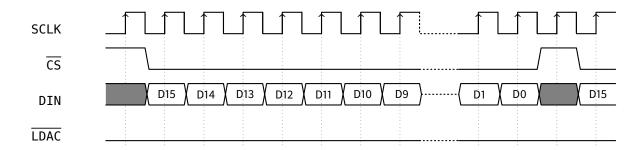

Based on this observation, the Karlsruhe pulse taking ultra-fast readout electronics (KAPTURE) system [20] was designed and developed. As shown in figure 2.9, the signal to be sampled is split into identical copies, either by means of an active or passive power splitter. Each of these copies is then sampled by a high-bandwidth track-and-hold circuit. These devices have two modes, selected by an external signal: track and hold. In track mode, the input signal is repeated to the output, and is then held constant at the arrival of the hold signal. The hold signal arrival time is individually delayed for each channel by a finely controllable amount of 3 ps. In this way the sampling points can be distributed along the pulse. The held signal can then be digitized by a much slower, and less expensive, analog-to-digital converter (ADC). In a KAPTURE board four channels are digitized by two ADCs, each with two channels.

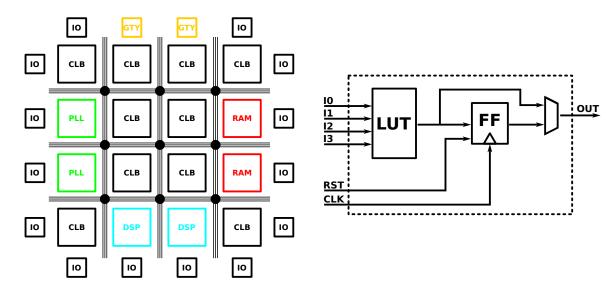

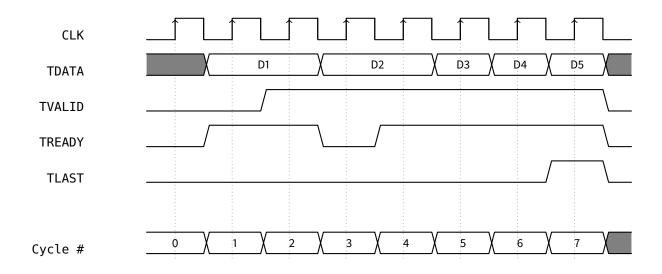

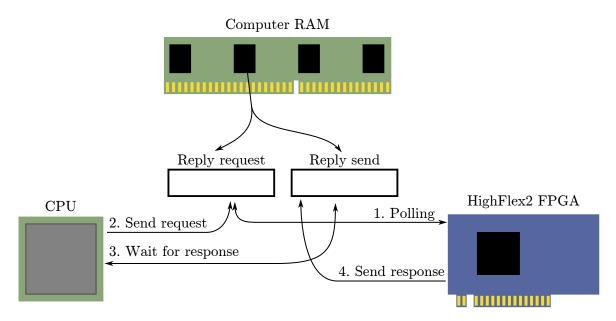

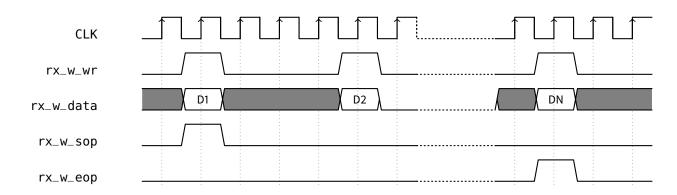

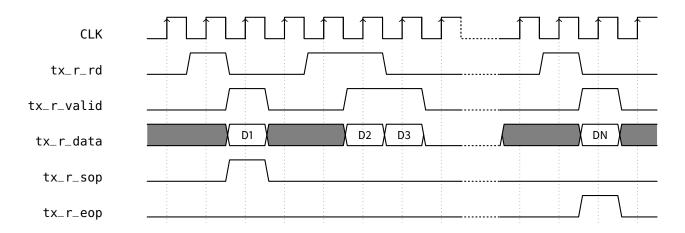

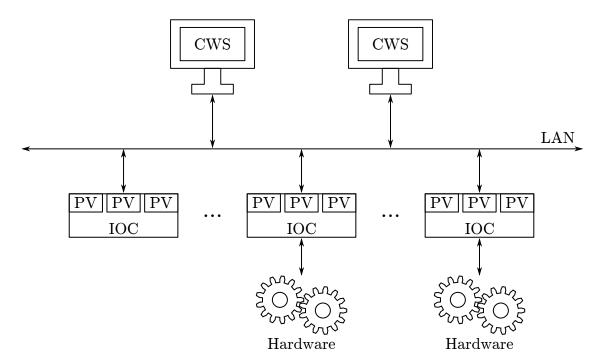

The delays lines and ADCs are all controlled by a field programmable gate array (FPGA). This device, that will be more thoroughly introduced in section 2.3, is fundamentally a lattice of logic gates interconnected by programmable switches. This allows the development of custom digital electronics. One HighFlex board can control two KAPTURE boards, for a data rate of 6.5 GB/s. This is usually transferred via a peripheral component interconnect express (PCIe) interface to the random access memory (RAM) of a host computer, where it can be later saved to persistent storage. It is worth noticing how with this system it is possible to sample the signal of a synchrotron with bunch-by-bunch and turn-by-turn repetition rate for several seconds.

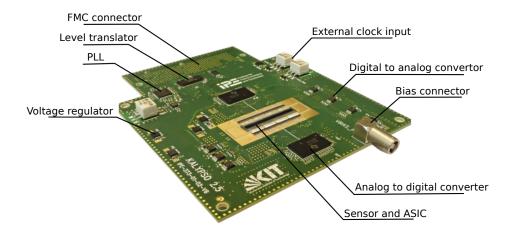

**Figure 2.10.:** Front-end PCB of a KALYPSO system, highlighting the main components. The external clock input and PLL allow to synchronize the sampling to the accelerator timing system. The sensor and ASIC are connected to ADCs that are then controlled by an FPGA that is connected to the FMC connector. Courtesy of M. M. Patil.

#### 2.1.7. The KALYPSO system

Several beam diagnostic instrumentation used at KARA and other synchrotron light sources encode information into light. The KAPTURE system described in the previous section allows monitoring the amplitude and shape of pulsed light signal, provided they are converted into a suitable electrical signal first. Oftentimes, the spatial dependence of this amplitude provides a great deal detail. This definition is fundamentally describing a camera. In order to produce turn-by-turn information, the frame rate would need to be in the MHz range. Due to the absence of systems capable of achieving this rates for several seconds to hours, the Karlsruhe linear array detector for MHz repetition rate spectroscopy (KALYPSO) system was developed at KIT [21–23].

A KALYPSO system is composed of a front-end printed circuit board (PCB), shown in figure 2.10, mounting a sensor, an analog signal processing ASIC, and an ADC, and a HighFlex based back-end card. The latter uses the same principles described for the KAPTURE system. Several sensors can be employed, depending on the wavelengths of interest. Silicon microstrip sensors can be employed up to 1050 nm, while indium-gallium-arsenide sensors can be used in the range from 1050 nm to 1.7  $\mu$ m. Each ASIC [24] has 128 input channels connected to the detector. Each channel has a charge-sensitive amplifier and shaping stage. A buffer holds the analog value until it is multiplexed to one of the sixteen output channels, where it is digitized by the ADC. The digital data is then transferred by an FPGA to the random access memory (RAM) of a computer, where it can be stored, visualized, and analyzed.

The KALYPSO system can be used to directly acquire the synchrotron light signal produced by an accelerator such as KARA. Furthermore, electro-optical (EO) systems can be employed to encode the temporal evolution of electric field strength into the polarization of the light signal [25]. More details on how this scheme can be employed for beam diagnostic are discussed in section 6.1.1.

#### **2.1.8. Summary**

A brief overview of the synchrotron and betatron dynamics was carried out, describing the fundamental phenomena that can be observed in an accelerator such as KARA. The synchrotron radiation emission characteristic of these machines was discussed, together with its impact on the beam stability. The betatron oscillations were shown to have the underlying dynamics of a harmonic oscillator. Its control could thus represent an interesting tool for testing novel control algorithms.

A more complex dynamics, the microbunching instability, appearing in special short bunch operation modes at synchrotron light source was described. Its usage for the production of strong terahertz radiation bursts makes it a useful tool for other scientific fields. Compared to the betatron oscillations, this dynamics exhibits strong non-linearity and threshold effects giving rise to abrupt changes in dynamics, leading to an extremely challenging problem for a controller.

Finally, the KARA synchrotron light source at KIT was described. This machine offers a wide variety of operation modes, allowing to experiment with the control of both the betatron oscillations and of the microbunching instability. Additionally, the cutting edge beam diagnostic infrastructure such as KAPTURE and KALYPSO offer powerful information that can be employed as the input of a controller.

## 2.2. Reinforcement learning

In this chapter the mathematical basis necessary for understanding both machine learning and reinforcement learning will be introduced. Special attention is given to neural networks, both to their inference and training. A short review of the modern algorithms and the underlying ideas used to perform efficient reinforcement learning training will follow, together with a discussion of the current state-of-the-art machine learning and reinforcement learning frameworks and a few of their applications to large-scale facilities.

## 2.2.1. Brief introduction to machine learning

Machine learning (ML) is comprised by a set of algorithms capable of learning from a dataset provided during a *training* phase, and then extrapolate this behavior to cases not covered in the training data. The following introduction on ML is based on reference [26]. A common use case for these algorithms are supervised categorization tasks. The problem can be stated as follows. A set of features  $f \in F$ , where the feature space F is usually  $\mathbb{R}^n$ , is the set of all possible objects. A label set L, is the set of possible labels that are applied to an element in F. A training set  $T \subset F \times L$ , is a labelled categorization example. Usually one can assume the correct set of labels are produced by a "correct" predictor  $h^*: F \to L$ . The goal of the algorithm is to learn a *predictor*  $h: F \to L$  that is capable of labeling elements. In order to

measure how well a given predictor behaves, it is useful to define a *loss function*, that in the case of binary classification, i.e.  $L = \{-1, 1\}$  is

$$\ell_F(h) = \underset{f \sim p(F)}{\mathbb{P}} \left[ h(f) \neq h^*(f) \right]. \tag{2.20}$$

Here  $f \sim p(F)$  denotes that the samples f are sampled with a probability density function p over the set F. This expression denotes the probability that the tested predictor h is wrong on a given sample. It is worth noticing how such a figure of merit depends on the chosen probability distribution.

Another common use-case of ML is function approximation, i.e. regression. Specifically, the goal of the training algorithm could be to output a function  $h: F \to \mathbb{R}$  approximating an unknown target function  $h^*: F \to \mathbb{R}$ . Again, a training set  $T \in F \times \mathbb{R}$  is provided. Several possible loss functions exist, for example

$$\ell_F(h) = \underset{f \sim p(F)}{\mathbb{E}} \left( h(f) - h^{\star}(f) \right)^2, \tag{2.21}$$

$$\ell_F(h) = \underset{f \sim p(F)}{\mathbb{E}} \left| h(f) - h^{\star}(f) \right|, \tag{2.22}$$

respectively called the mean-square error and mean absolute Z-score. The choice of function dictates how errors are weighted. For instance, equation (2.21) tends to penalize large errors compared to equation (2.22). The choice of loss function has a strong effect on the algorithm. Specific, problem-based tuning is sometimes necessary in order for the ML algorithms to work properly.

#### 2.2.2. Neural networks

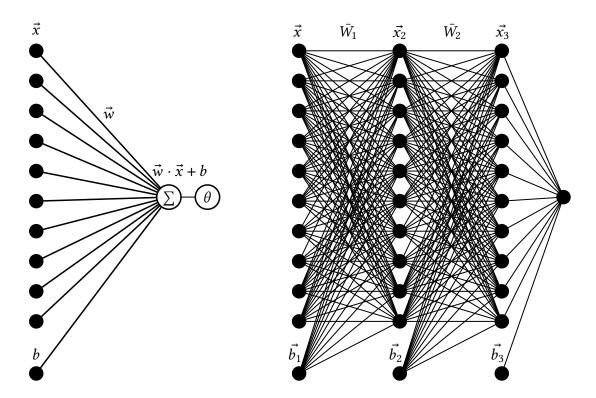

In ML, a common choice of predictor or of approximation function are neural networks (NNs). An artificial NN is constituted by a set of interconnected neurons, usually implemented with a *perceptron* (figure 2.11), defined as follows

$$y = \theta(\vec{w} \cdot \vec{x} + b). \tag{2.23}$$

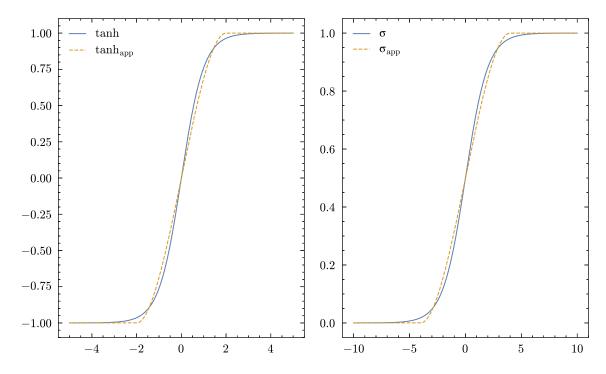

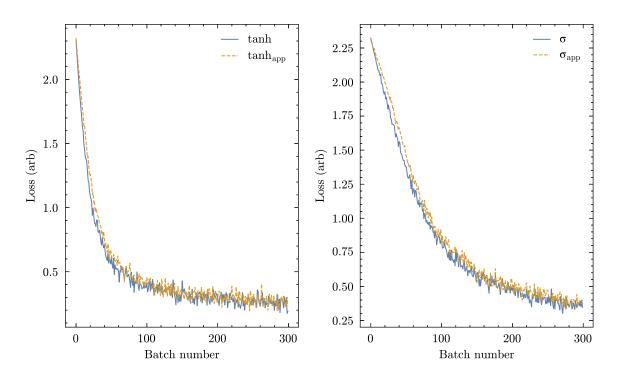

Here  $\vec{x} \in \mathbb{R}^n$  are the input features, while  $\vec{w}$  and b are respectively called the weights and bias of the perceptron, and  $\theta$  is a non-linear activation function. Common activation functions include the rectifying linear unit (ReLU), the sigmoid function  $\sigma$  and the hyperbolic tangent (tanh):

$$ReLU(x) = \begin{cases} x, & \text{if } x \ge 0\\ 0, & \text{otherwise} \end{cases}$$

(2.24)

$$\sigma(x) = \frac{1}{1 + e^{-x}},\tag{2.25}$$

$$\tanh(x) = \frac{e^x - e^{-x}}{e^x + e^{-x}} = \frac{e^{2x} - 1}{e^{2x} + 1}.$$

(2.26)

**Figure 2.11.:** On the left, drawing of a perceptron showing the sum used to perform the dot product, the activation function, and the weights and biases. On the right, a multilayer perceptron with two hidden layers and a single output neuron. The sum and activation functions have been coalesced into the neuron node for ease of representation.

Usually several perceptrons are grouped into a *layer*. The number of neurons in a layer is called its *width*. The perceptron definition of equation (2.23) can be expanded to a layer function  $h: \mathbb{R}^n \to \mathbb{R}^m$  by promoting the weights and bias respectively to a matrix and a vector,

$$\vec{y} = h(\vec{x}) = \theta(\vec{W}\vec{x} + \vec{b}), \tag{2.27}$$

where  $\theta$  is now performed element-wise,  $\bar{W} \in \mathbb{R}^{m \times n}$  is the weight matrix and  $\vec{b} \in \mathbb{R}^m$  is the bias vector, as shown in figure 2.11.

Several layers are composed together to form a NN known as multi-layer perceptron (MLP). Denoting the input layer  $\vec{x}$ , the output layer  $\vec{y}$  is computed by chaining l hidden layers  $\{h_i\}_{i=1...l}$ , each one denoted by a specific set  $\{\bar{W}_i, \bar{b}_i, \theta_i\}_{i=1...l}$ . In this way, the MLP is

$$\vec{y} = H(\vec{x}) = h_l(h_{l-1}(...h_2(h_1(\vec{x}))...)) = (h_l \circ h_{l-1} \circ ... \circ h_2 \circ h_1)(\vec{x})$$

(2.28)

In order to train a NN, one would need to find a set of weight and biases that minimize the loss function. If the  $L^2$ -loss of equation (2.21) is taken as an example, an estimator can be obtained by the substituting the expectation value with an average over the training set  $T = \{\vec{x_i}, y_i\}_{i=1...N_t}$ , thus giving

$$\ell_T(H) = \frac{1}{N_t} \sum_{i=1}^{N_t} (H(\vec{x}_i) - y_i)^2.$$

(2.29)

If one considers that H is defined by the combination of all its weights and biases  $\tilde{W}$ , one could consider the loss as

$$\ell_T(\tilde{W}) \stackrel{\text{def}}{=} \ell_T(H_{\tilde{W}}).$$

(2.30)

One could attempt minimizing this function via gradient descent methods. The idea behind this class of methods is analogous to trying to reach the top of a mountain by following the increase of the slope. This approach is in some cases guaranteed to reach the global minimum, but strong requirements are necessary, for example the convexity of  $\ell_T(\tilde{W})$ . This kind of strong constraints are not generally true, nonetheless a local minima is usually reached. A basic gradient descent method iteratively computes the gradient of the loss, and updates the weights accordingly according to a rule as

$$\tilde{W} \leftarrow \tilde{W} - \eta \nabla \ell_T(\tilde{W}),$$

(2.31)

where  $\eta$  is a training parameter known as the *learning rate*.

In practice, directly minimizing the loss function is computationally intensive. This issue is usually solved by means of stochastic or mini-batch gradient descent methods, where the loss is computed respectively on single sample of the training set or on a mini-batch of samples  $B = \{\vec{x_i}, y_i\}_{i=1...N_b}$ , where  $N_b$  is called the batch size and  $\{\vec{x_i}, y_i\} \in T$ . This has the additional benefit of leading to a noisier update that can make the optimizer "jump-out" of local minimum, in this way increasing the chance of reaching the global minimum.

If one tries to calculate the gradient of the loss, a fundamental for gradient descent, leads to

$$\nabla_W l_B(\tilde{W}) = \frac{1}{N_b} \sum_{i=1}^{N_b} \nabla_W \left( H_{\tilde{W}}(\vec{x}_i) - y_i \right)^2 = \frac{1}{N_b} \sum_{i=1}^{N_b} 2 \left( H_{\tilde{W}}(\vec{x}_i) - y_i \right) \nabla_W H_{\tilde{W}}(\vec{x}_i). \tag{2.32}$$

Efficiently computing the gradient of the NN,  $\nabla_W H_{\tilde{W}}(\vec{x}_i)$ , is thus fundamental in order to effectively perform training.

The chain rule for the jacobian matrix  $\nabla_{\vec{x}}(g \circ f)(\vec{x})$  with  $f : \mathbb{R}^n \to \mathbb{R}^m$  and  $g : \mathbb{R}^m \to \mathbb{R}^k$  is

$$\nabla_{\vec{x}}(q \circ f)(\vec{x}) = \nabla_f(q(f))\nabla_{\vec{x}}(f(\vec{x})) \tag{2.33}$$

In the case of MLP, the gradient has a peculiar property. Specifically, thanks to the chain rule of differentiation leads to

$$\nabla_{W_i}(h_l \circ h_{l-1} \circ \dots \circ h_2 \circ h_1) = (\nabla_{\vec{x_i}} h_l(\vec{x_l})) \nabla_{W_i}(h_{l-1} \circ \dots \circ h_2 \circ h_1). \tag{2.34}$$

This expression can be chained iteratively until the *i*-th layer is reached

$$\nabla_{W_i}(h_l \circ h_{l-1} \circ \dots \circ h_2 \circ h_1) = (\nabla_{\vec{x}_l} h_l(\vec{x}_l))(\nabla_{\vec{x}_{l-1}} h_{l-1}(\vec{x}_{l-1})) \dots \nabla_{W_i} h_i(\vec{x}_i). \tag{2.35}$$

At this point, using equation (2.27), one can directly calculate the jacobian matrices as being

$$\nabla_{x_i} h_i(\vec{x}_i) = (\nabla_{\vec{m}} \theta(\vec{m})) \cdot W_i \tag{2.36}$$

$$\nabla_{W_i} h_i(\vec{x}_i) = (\nabla_{\vec{m}} \theta(\vec{m})) \cdot \vec{x}_i \tag{2.37}$$

One important property of equation (2.35) is how, except in the i-th jacobian, all previous derivatives are the same independently of the layer i we are differentiating. As such, based on equations (2.35) to (2.37) a procedure, known as *backpropagation* can be devised, were the gradient with respect to the weights and biases is computed iteratively from the output layer to the input.

Modern ML frameworks as PyTorch [27], Tensorflow [28], Keras [29] and Caffe [30] make heavy use of this technique to efficiently compute the gradients. Specifically, a key concept of these tools is *automatic differentiation* [31, 32], where the computation graph to obtain a given value is used to reconstruct the gradients in a way that is totally transparent to the user.

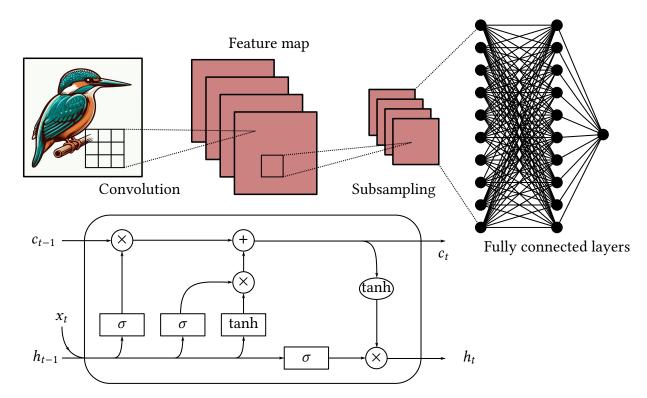

The MLP described in this section is widely employed and works well for some problems, but it is fundamentally not aware of the underlying structure of the input data. In the last decades several more advanced NN topologies have been developed, specifically to address this drawback. For instance, if the input to the network is an image, the position of the pixels and the scale is an important information that needs to be preserved. This is addressed with convolutional neural networks (CNNs) (figure 2.12), where a smaller convolution kernel is scanned over the image, creating a new representation called a feature map. This dramatically reduces the number of parameters required for the operation: if a  $256 \times 256$  pixel image is provided, a simple MLP will require 65356 input neurons to process it. A CNN, on the other hand, can use a first convolutional layer with size of  $8 \times 8$ , for example, that would lead to a much smaller number of input neurons and thus of parameters. In addition, pooling layers are usually applied, that are capable of further reducing the intermediate representation combining clusters in the feature map. This method has the advantage of being able to perceive local features, thanks to the convolutional layers, while it is still capable of having a comprehensive large-scale perspective thanks to the summarizing effect of the pooling layers.

An additional kind of structured data is time-series data, for which recurren neural networks (RNNs) can be employed. This kind of networks can encode an history by storing an internal state that is updated during inference. Common implementations are the long-short term memory (LSTM) (figure 2.12) and gated recurrent unit (GRU).

#### 2.2.3. Introduction to reinforcement learning

This introduction is based on [33, 34].

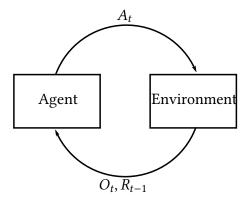

Reinforcement learning (RL) is a subset of ML algorithms that treat the learning of an agent from the interaction with an external environment (figure 2.13). Specifically, the agent receives a set of observation from the environment and tries to choose the best action to increase a cumulative reward signal.

In more mathematical terms, it is possible to model an environment as a Markov decision process (MDP), a tuple comprised of  $(S, A, P, R, \gamma)$ , where S is the set of states, A is the set of

**Figure 2.12.:** A schematic representation of a CNN is shown on the top part of this figure. An LSTM is represented in the bottom part. Here  $x_t$  are the inputs,  $h_t$  and  $c_t$  are respectively the hidden and cell state vectors. In this notation, the rounded bubbles represent element-wise operations, while the square bubbles represent linear layers followed by the depicted activation function.

**Figure 2.13.:** Interaction of an agent with the environment. The agent receives an observation and provides an action to the environment. Together with the observation, the reward of the last step is provided.

all actions. P denotes the transition probability from a state s to a state s', provided the action a was taken in state s

$$P_{s,s'}^{a} = \mathbb{P}\left[S_{t+1} = s' | S_t = s, A_t = a\right]. \tag{2.38}$$

In the special case where the state space is discrete, P can be described as a transition matrix. The reward function  $R_s^a$  is defined as the expected reward obtained in the next time step given the agent is in step s and took action a, i.e.

$$R_s^a = \mathbb{E}\left[R_{t+1}|S_t = s, A_t = a\right].$$

(2.39)

In order to consider long-term goals, the cumulative reward is defined as

$$G_t = R_{t+1} + \gamma R_{t+2} + \gamma^2 R_{t+3} + \dots = \sum_{i=0}^{\infty} \gamma^i R_{t+1+i},$$

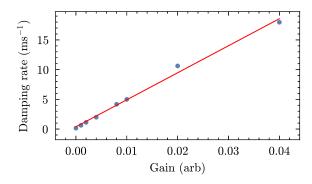

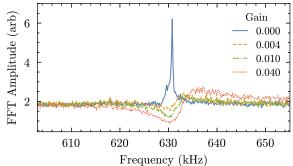

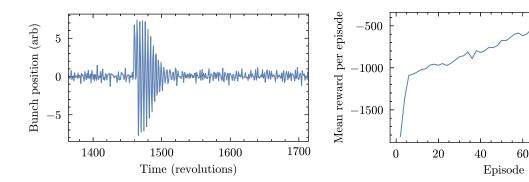

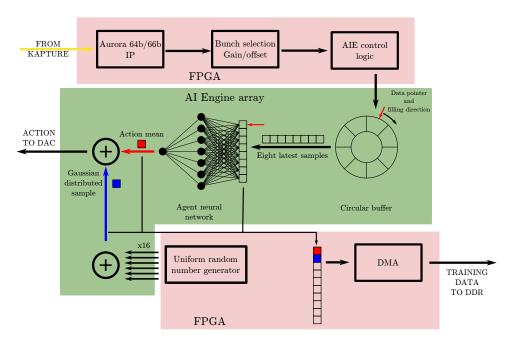

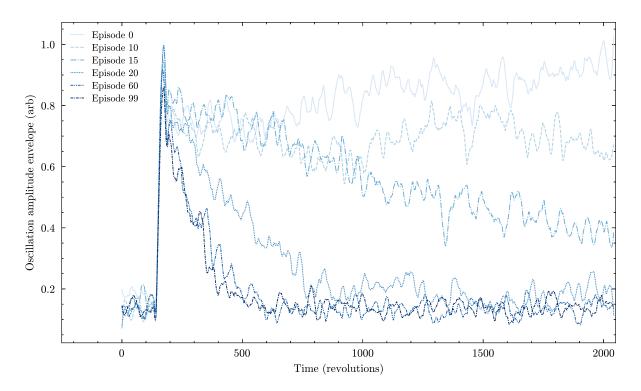

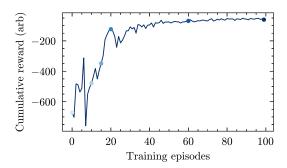

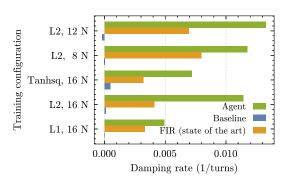

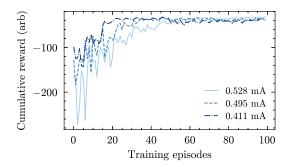

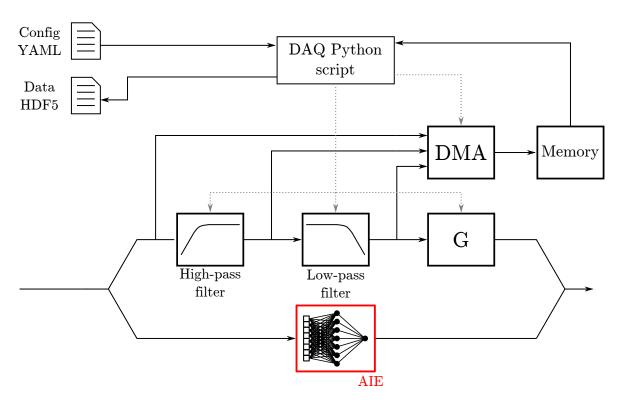

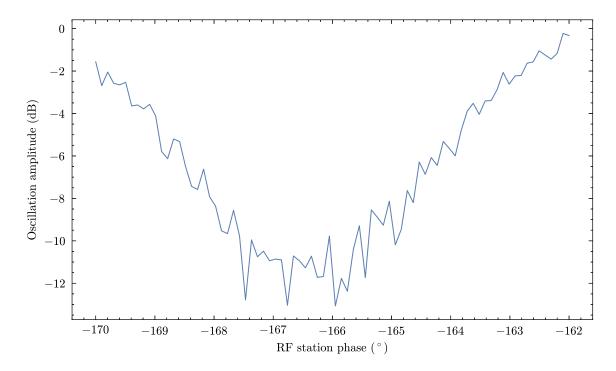

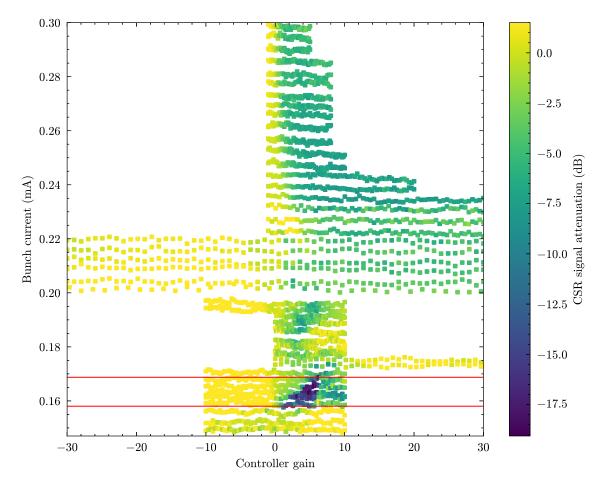

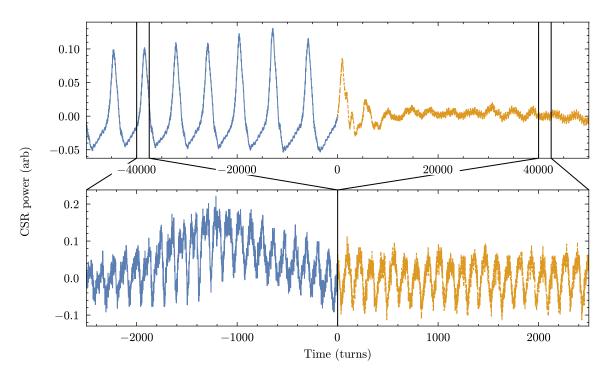

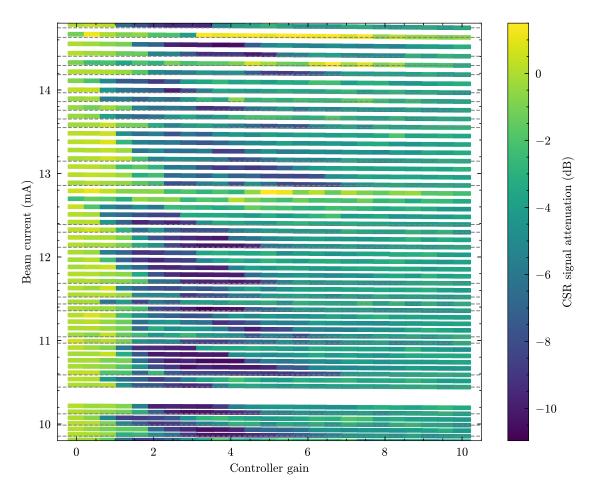

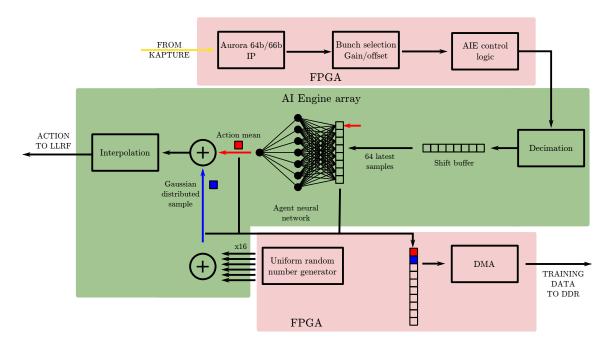

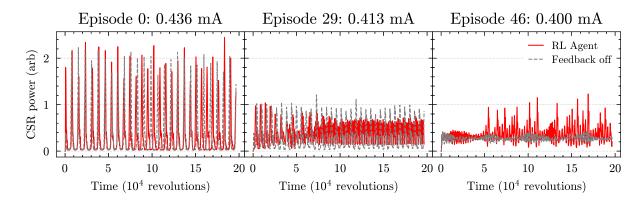

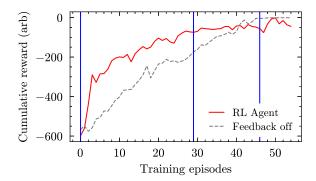

(2.40)