## Implementation and Characterization of Monolithic Pixel Detectors in 65 nm CMOS Imaging Sensor Technology

Zur Erlangung des akademischen Grades einer DOKTORIN DER INGENIEURWISSENSCHAFTEN (Dr.-Ing.)

von der KIT-Fakultät für Elektrotechnik und Informationstechnik des Karlsruher Instituts für Technologie (KIT)

$\begin{array}{c} \text{angenommene} \\ \text{DISSERTATION} \end{array}$

von

M.Sc. Ana Dorda Martin

Tag der mündlichen Prüfung: 30. September 2024

Hauptreferent: Prof. Dr. Ivan Peric

Korreferenten: Prof. Dr. Jasmin Aghassi-Hagmann

### Thesis External Supervisor

CERN Supervisor: Dr. Rafael Ballabriga Sune

Day of submission: 16 August 2024 Day of defense: 30 September 2024

The work leading to this thesis has been sponsored by the Wolfgang Gentner Programme of the German Federal Ministry of Education and Research (grant number 05E15CHA).

This work is licensed under a Creative Commons "Attribution 4.0 International" license. To view a copy of this license, visit https://creativecommons.org/licenses/by/4.0/deed.en.

In the midst of winter, I found there was, within me, an invincible summer.

Albert Camus, Return to Tipasa

## Acknowledgments

During these three years of doctoral studies, there have been people by my side who have helped and supported me both professionally and personally. I would like to dedicate a few lines of thanks to them, which only express a small part of how much they have contributed to my work and performance.

First, I would like to thank my supervisor at CERN, Rafael Ballabriga Sune, for accepting me as a PhD student and for giving me the opportunity and trust to dive into the topic of analog design. I would also like to thank Ivan Peric for accepting me as a PhD student under his supervision and for his help with the administrative work to finalize and submit the thesis.

I am grateful to H. Pommerenke, F. N. Bandi, and T. Hofmann for their comments on the thesis draft and the excellent translation of the German abstract. I could not have asked for better editors.

Among some of my colleagues over these years I would like to highlight and thank Walter Snoeys, for such fruitful discussions about this monolithic technology and its peculiarities. I would also like to thank Giulio Borghello, for making "easy" the effects of radiation on transistors. Finally, my sincere thanks to Iraklis Kremastiotis for welcoming me to the H2M project and helping me in my first steps as a PhD student and with Cadence.

During these three years, much of my work has been carried out under the wing of the Medipix team, with whom I have shared numerous team meetings. Among the more "veterans" members of the team, I would like to thank Michael Campbell, team leader, for his support with the H2M project and for allowing me to contribute to the Timepix EDU project. Jerome Alozy, my office partner: tu as été un collègue de bureau magnifique, merci pour ton soutien technique, mais aussi émotionnel. Xavier Llopart, for helping me with GitLab and the H2M manual and for his help closing the first H2M prototype for submission (moltes gràcies per les Catànies). At last, Lukas Tlustos, to whom I just have to say fantastisch!

Among the "youngsters" of the team, I want to thank my office neighbors: Tobias, with whom I started off on the wrong foot and is now more than appreciated, Franco, who has been feeding me these three years with alfajores and advice, and Andrea, my constant

reminder of my *Espanish* accent. Thanks for your support and involving me in the technical discussions (and in the not so technical ones too).

At last, also part of the Medipix team, I would like to thank Pinelopi. Thank you amica for all that we have shared these three years. And thank you also for introducing me to Yiota. To both of you, ευχαριστώ for lighting up my mood, being my source of female energy during these years and for showing me how passion for physics looks like.

Apart from the people I have met during my doctoral studies, there are others who were already there and have contributed in their own way. Among them, I would like to thank to my friends from Madrid. My childhood friend Iris, for always being on the other side of the phone. And my university friends, Javier and Carolina, it has been an honor to have shared my bachelor years with both of you.

Gracias a mi familia por su apoyo, especialmente a mi madre, por su paciencia, dedicación y burruños. Gracias a mi hermano, por descrubirme canciones y grupos que me han acompañado en la escritura de la tesis. Y gracias a mi padre, quien siempre me dejaba robarle las pilas AA para mis experimentos.

And finally, many thanks to my partner Hermann. Seeing your dedication and passion for engineering and science inspired me to start my PhD studies. I hope to share many more years with you, but I do not promise it will be watching Star Trek.

These years will be unforgettable. I wish you all the best both personally and professionally. Thank you all.

Silz, Mecklenburg-Vorpommern, Germany 6th August 2024

### Abstract

This thesis presents the design of a low-power, low-noise front-end based on a transconductance amplifier, conceived for monolithic applications with an emphasis on detecting and amplifying minimum ionizing particle signals.

TPSCo 65 nm transistor technology is currently the leading candidate for developing new monolithic active-pixel detectors for the European Organization for Nuclear Research (CERN) experiments. Prior to the design phase, a comprehensive characterization of this technology node was conducted, focusing on two primary concerns for analog designers in the high-energy physics community: characterization under irradiation, and the study of its analog performance using the Enz-Krummenacher-Vittoz (EKV) model. In the irradiation characterization, several transistor test structures were fabricated and subjected to Total Ionizing Dose (TID) tests up to 1 Grad (SiO<sub>2</sub>), followed by annealing at temperatures up to 100 °C. The resulting data were analyzed not only using traditional figures of merit but also employing a custom EKV extractor routine, enabling an indepth investigation into how irradiation and variations in bulk bias affect the analog performance of transistors of this technology. Both studies confirmed radiation-induced degradation in this node, comparable to other 65 nm technologies. However, the EKV model demonstrated that normalization can mitigate these impacts on transconductance efficiency, making it a powerful tool for analog designers.

Leveraging the insights gathered from the characterization and employing a structured analog design approach, all the various front-end sub-blocks (Charge Sensitive Amplifier (CSA), discriminator, tuning digital-to-analog converter, and feedback) are modeled and implemented. Simulations at schematic and layout levels, successfully demonstrate the feasibility of a low-power, low-noise front-end design using TPSCo 65 nm technology, which can be applied to future applications such as the ALICE ITS3 upgrade.

## Zusammenfassung

Diese Dissertation stellt den Entwurf eines stromsparenden, rauscharmen analogen Front-Ends für monolithische Anwendungen auf Basis eines Transkonduktanzverstärkers vor. Der Schwerpunkt liegt auf der Detektion und Verstärkung minimal-ionisierender Teilchensignale sowie geringem Energieverbrauch.

Die TPSCo 65 nm Transistortechnologie ist der derzeit führende Kandidat für die Entwicklung neuer monolithischer aktiver Pixeldetektoren für die Experimente der Europäischen Organisation für Kernforschung (CERN). Vor der Entwurfsphase wurde eine umfassende Charakterisierung dieses Technologieknotens durchgeführt, wobei der Fokus auf zwei primären Anliegen im Kontext der Hochenergiephysik lag: Charakterisierung unter radioaktiver Bestrahlung und Untersuchung der analogen Performanz mit dem Enz-Krummenacher-Vittoz (EKV) Modell. In der Bestrahlungscharakterisierung wurden mehrere Transistor-Teststrukturen gefertigt und Tests der Gesamtionisierungsdosis [engl. Total Ionizing Dose (TID)] bis zu 1 Grad (SiO<sub>2</sub>) unterzogen, gefolgt von Wärmebehandlung bei bis zu 100 °C. Die resultierenden Daten wurden nicht nur mit Hilfe traditioneller Kennzahlen analysiert, sondern auch mit einer benutzerdefinierten EKV-Extraktionsroutine. Diese erlaubt eine eingehende Untersuchung, inwieweit Bestrahlung und Variationen in der Substratvorspannung die Performanz der Transistoren dieser Technologie beeinflussen. Beide Studien bestätigten eine strahlungsinduzierte Verschlechterung in diesem Knoten, vergleichbar mit anderen 65 nm Technologien. Das EKV-Modell zeigte jedoch, dass durch Normalisierung diese Auswirkungen auf die Transkonduktanzeffizienz gemindert werden können, was es zu einem mächtigen Entwurfswerkzeug macht.

Die Dissertation schließt mit dem Entwurf eines stromsparenden, rauscharmen Front-Ends basierend auf einem ladungsempfindlichen Verstärker (engl. Charge Sensitive Amplifier, CSA). Unter Nutzung der aus der Charakterisierung gewonnenen Erkenntnisse und eines strukturierten Ansatzes für den Entwurf analoger Schaltungen werden verschiedene Blöcke (CSA, Diskriminator, Digital-Analog-Wandler zur Abstimmung, sowie Rückkopplung) modelliert und implementiert. Simulationen des Front-Ends auf Schaltbild- und Layout-Ebene demonstrieren erfolgreich die Machbarkeit eines stromsparenden, rauscharmen Entwurfs unter Verwendung der TPSCo 65 nm Technologie, das in zukünftigen energiesparenden Anwendungen wie dem ALICE ITS3-Upgrade eingesetzt werden kann.

## Contents

| A          | cknow  | ledgme   | ents                                                              | j    |

|------------|--------|----------|-------------------------------------------------------------------|------|

| <b>A</b> l | bstrac | ct       |                                                                   | ii   |

| Zι         | ısamı  | nenfass  | ung                                                               | v    |

| Li         | st of  | Figures  |                                                                   | x    |

| Li         | st of  | Tables   |                                                                   | xix  |

| Li         | st of  | Abbrev   | iations                                                           | xx   |

| Li         | st of  | Symbol   | s                                                                 | xxv  |

| 1          | Intr   | oductio  | on.                                                               | 1    |

|            | 1.1    | Struct   | ture of the Thesis                                                | . 3  |

|            | 1.2    | Thesis   | S Contributions                                                   | . 4  |

| 2          | Mor    | nolithic | Active Pixel Detectors                                            | 5    |

|            | 2.1    | Found    | lations on Pixel Detectors                                        | . 6  |

|            |        | 2.1.1    | The PN Junction (Drifting and Diffusion)                          | . 6  |

|            |        | 2.1.2    | The Sensor and Charge Generation (Bethe-Bloch Formula) $\ \ldots$ | . 7  |

|            |        | 2.1.3    | Signal Formation (Ramo Theorem)                                   | . 8  |

|            |        | 2.1.4    | Processing Chain                                                  | . 9  |

|            | 2.2    | Radia    | tion Detectors                                                    |      |

|            |        | 2.2.1    | Hybrid Pixel Sensors                                              | . 11 |

|            |        | 2.2.2    | Monolithic Active Pixel Sensors                                   | . 12 |

|            | 2.3    |          | of-the-Art: Recent Front-End Developments for MAPS on TPS-        |      |

|            |        | Co 65    |                                                                   |      |

|            |        | 2.3.1    | Monolithic Stitched Sensor (MOSS)                                 |      |

|            |        | 2.3.2    | Hybrid-to-Monolithic (H2M)                                        |      |

|            | 2.4    | Aspec    | ts to Consider on the Design of a CSA                             |      |

|            |        | 2.4.1    | Transfer Function of CSA                                          |      |

|            |        | 2.4.2    | Output Pulse Amplitude vs. CSA Gain                               | . 22 |

|            |        | 2.4.3    | Transfer Function of CSA with Feedback Network                    | . 23 |

|   | 2.5  | 2.4.4<br>Summ | Noise Sources on the Processing Chain                   | 23<br>27 |

|---|------|---------------|---------------------------------------------------------|----------|

| 3 | Cha  | racteriz      | ation of TID Effects: Experimental Details and Results  | 29       |

|   | 3.1  | Radiat        | ion-Induced Effects                                     | 30       |

|   |      | 3.1.1         | Gate Oxide Effects                                      | 30       |

|   |      | 3.1.2         | Spacer-Related Effects                                  | 31       |

|   |      | 3.1.3         | Shallow Trench Isolation Effects                        | 32       |

|   |      | 3.1.4         | Leakage Current                                         | 33       |

|   | 3.2  | Measu         | rements Set-up and Transistor Test Structures           | 33       |

|   | 3.3  | First N       | Measurements at 1 Grad TID                              | 36       |

|   | 3.4  | Gate (        | Oxide-Related Effects                                   | 38       |

|   | 3.5  | Chann         | el Length-Related Effects                               | 38       |

|   |      | 3.5.1         | Radiation-Induced Short Channel Effects (RISCE)         | 38       |

|   |      | 3.5.2         | Leakage Current                                         | 39       |

|   | 3.6  | Chann         | el Width-Dependent Effects                              | 41       |

|   |      | 3.6.1         | Radiation-Induced Narrow Channel Effects (RINCE)        | 41       |

|   | 3.7  | Proces        | s Comparison                                            | 42       |

|   |      | 3.7.1         | Pre-Radiation Measurements                              | 42       |

|   |      | 3.7.2         | 300 Mrad TID Measurements                               | 43       |

|   | 3.8  | Measu         | rements at 200 Mrad TID of Thick Oxide Devices          | 45       |

|   | 3.9  | Summ          | ary                                                     | 47       |

| 4 | Stud | ly of TI      | D and Back Bias Effects on the Analog Design Parameters | 49       |

|   | 4.1  | Model         | ling of MOS Devices Using the EKV Model                 | 50       |

|   |      | 4.1.1         | The Simplified EKV Model                                | 50       |

|   |      | 4.1.2         | Modeling of Gate Capacitances                           | 51       |

|   | 4.2  | Propos        | sal of EKV Parameters Extractor using Python            | 52       |

|   | 4.3  | TID E         | ffects on Large-Signal Characteristics                  | 57       |

|   |      | 4.3.1         | TID Effects on $I_{\rm D}(V_{\rm GS})$ Characteristics  | 57       |

|   |      | 4.3.2         | TID Effects on EKV Model Parameters                     | 57       |

|   | 4.4  | TID E         | ffects on Small-Signal Characteristics                  | 62       |

|   |      | 4.4.1         | TID Effects on Output Conductance                       | 62       |

|   |      | 4.4.2         | TID Effects on Transconductance Efficiency              | 63       |

|   | 4.5  | Influer       | nce of Back Bias on the Analog Performance              | 63       |

|   |      | 4.5.1         | Body Effect                                             | 63       |

|   |      | 4.5.2         | Back Bias Measurements and Simulations                  | 64       |

|   |      | 4.5.3         | EKV Back Bias Fitting                                   | 66       |

|   | 4.6  | Summ          | arv                                                     | 68       |

### Contents

| 5  | Imp    | lementa  | ation of a Novel Low-Power and Low-Noise Front-End             | 69   |

|----|--------|----------|----------------------------------------------------------------|------|

|    | 5.1    | Specif   | ications and Objectives                                        | . 70 |

|    | 5.2    | Study    | of Fundamental Limits on the Design of Low-Power and Low-Noise |      |

|    |        | Front-   | Ends                                                           | . 70 |

|    | 5.3    | Design   | n Procedure                                                    | . 74 |

|    |        | 5.3.1    | Charge Sensitive Amplifier                                     | . 74 |

|    |        | 5.3.2    | Feedback Network                                               | . 76 |

|    |        | 5.3.3    | Discriminator                                                  | . 79 |

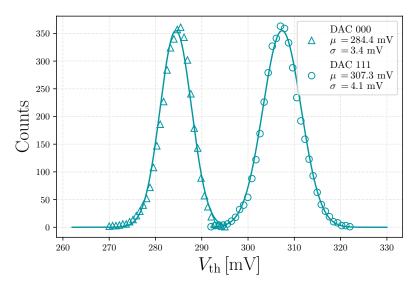

|    |        | 5.3.4    | 3-bit Threshold DAC                                            | . 80 |

|    |        | 5.3.5    | Feedback Capacitance                                           | . 83 |

|    | 5.4    | Schem    | natic Simulations                                              | . 84 |

|    | 5.5    | Post-I   | Layout Extraction Simulations                                  | . 87 |

|    |        | 5.5.1    | Layout Considerations                                          | . 87 |

|    |        | 5.5.2    | Influence of Parasitic Capacitances on the FE Performance      | . 89 |

|    |        | 5.5.3    | ToA and ToT Measurements                                       | . 91 |

|    |        | 5.5.4    | Voltage Drop                                                   | . 91 |

|    |        | 5.5.5    | High-Power Mode                                                | . 94 |

|    | 5.6    | Comp     | arison with the H2M and MOSS Front-Ends                        | . 95 |

|    | 5.7    | Summ     | nary                                                           | . 97 |

| 6  | Con    | clusions | s and Outlook                                                  | 99   |

| A  | H2N    | I Analo  | og Periphery: Design and Testing                               | 103  |

| Bi | bliogi | raphy    |                                                                | 119  |

# List of Figures

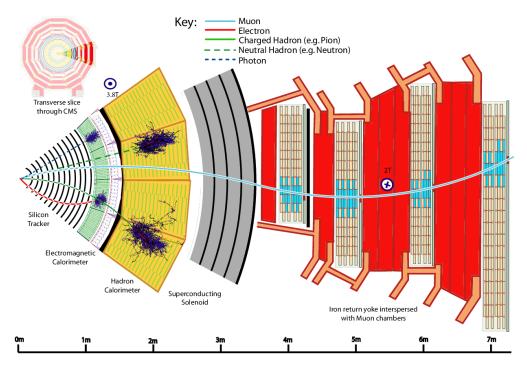

| 1.1 | Transverse slice through CMS. The vertex detector, positioned closest to the beam pipe, is immersed in a magnetic field. This magnetic field bends the tracks of charged particles, enabling the measurement of their momenta [3] | 2  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1 | The PN junction: a) structure b) space charge density c) electric field                                                                                                                                                           |    |

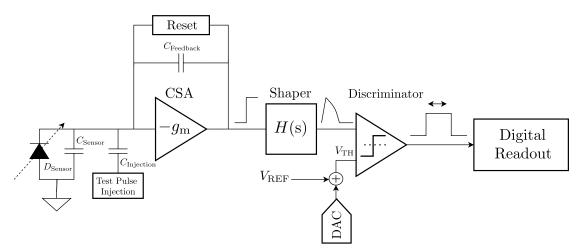

| 2.2 | distribution and d) potential distribution. Adapted from [20] Block diagram of a common processing chain. The signal is generated at the sensor, which is modelled as a diode in parallel to a capacitance. This                  | 6  |

|     | signal is integrated by the CSA, filtered by the shaper and compared to a                                                                                                                                                         | _  |

| 2.3 | threshold at the discriminator                                                                                                                                                                                                    | 10 |

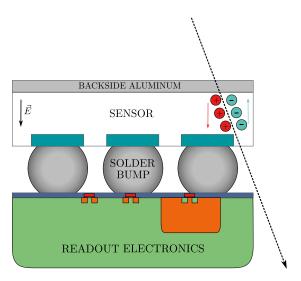

| 2.3 | Simplistic representation of a hybrid sensor. The backside aluminum is                                                                                                                                                            | 10 |

| 2.1 | connected to a positive potential (attracting electrons) while the other                                                                                                                                                          |    |

|     | side is connected to a negative potential. Once there is ionization on the                                                                                                                                                        |    |

|     | sensor, the holes while be attracted by the negative bias and detected by                                                                                                                                                         |    |

|     | the readout electronics                                                                                                                                                                                                           | 11 |

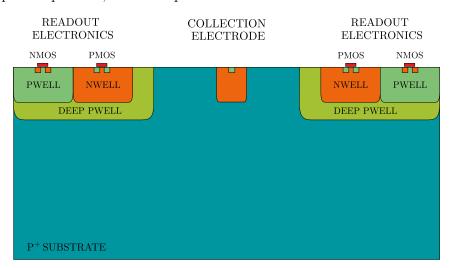

| 2.5 | Cross section of a MAPS with a small collection electrode                                                                                                                                                                         | 12 |

| 2.6 | Simplistic representation of the effect of reverse biasing in a cross-section                                                                                                                                                     |    |

|     | of a monolithic sensor. The nMOS are located at the pWELL (dark green).                                                                                                                                                           |    |

|     | Black arrow lines represent the field lines of the depleted sensor, and the                                                                                                                                                       |    |

|     | gradient is the magnitude of the electric field. The collection electrode                                                                                                                                                         |    |

|     | would be biased at a positive voltage while both the P <sup>+</sup> substrate and the                                                                                                                                             |    |

|     | pWELL would be biased at the same negative voltage, creating the field                                                                                                                                                            | 16 |

| 0.7 | lines depicted                                                                                                                                                                                                                    | 13 |

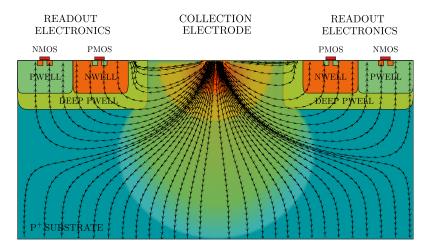

| 2.7 | Cross section of the sensor in the TPSCo 65 nm imaging technology: a) standard process, b) modified process with low-dose n- implant, c) with                                                                                     |    |

|     | gap in the low-dose n- implant                                                                                                                                                                                                    | 14 |

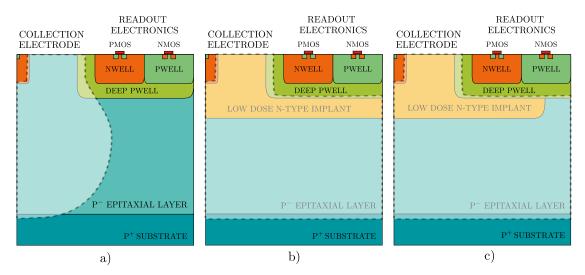

| 2.8 | ITS2 (left) and its proposed upgrade ITS3 (right). The ITS3 upgrade aims                                                                                                                                                          | 15 |

| 2.0 | to replace the inner tracker by a fully cylindrical one where the silicon                                                                                                                                                         |    |

|     | detectors are flexible [46]                                                                                                                                                                                                       | 15 |

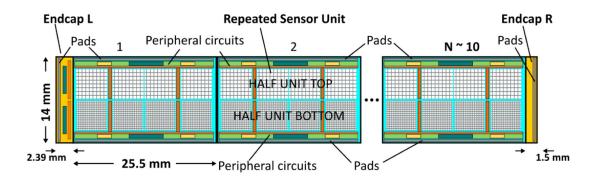

| 2.9 | Concept diagram of the MOSS chip [49]                                                                                                                                                                                             | 16 |

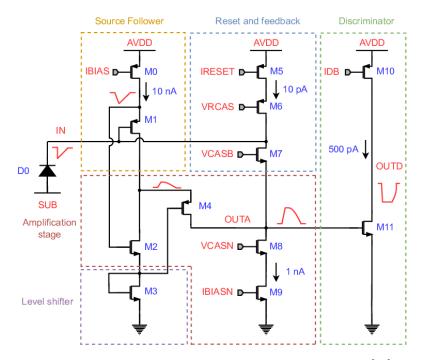

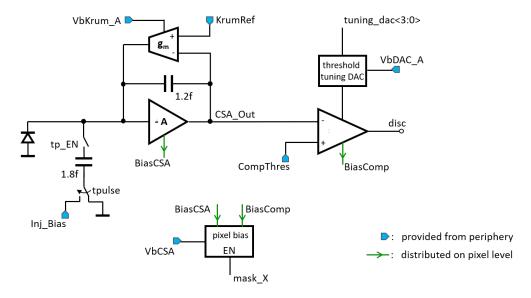

|     | Schematic of the front-end in the DPTS chip [50]                                                                                                                                                                                  | 17 |

|     |                                                                                                                                                                                                                                   |    |

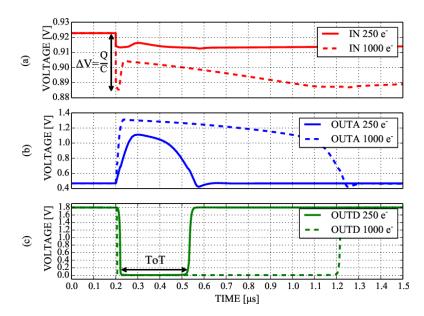

| 2.11 | Performance of the DPTS front-end. Red lines correspond to input signals, blue to output signals of the amplification stage, and green to the |                 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

|      | discriminator output. The gain of the amplifier is intrinsically nonlinear                                                                    |                 |

|      | and decreases with the input charge. However, the ToT is linear with the                                                                      |                 |

|      | charge as it is proportional to the discharge time of the collection electrode                                                                |                 |

|      |                                                                                                                                               | 18              |

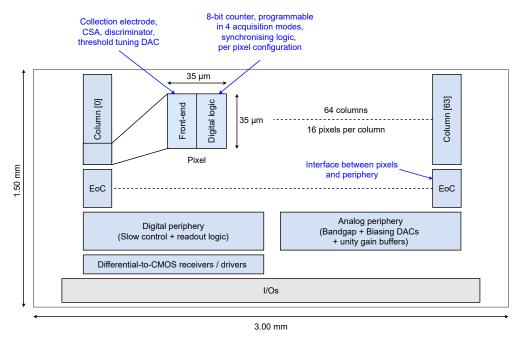

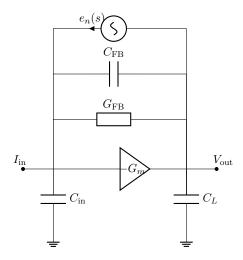

| 2.12 |                                                                                                                                               | 19              |

|      |                                                                                                                                               | 19              |

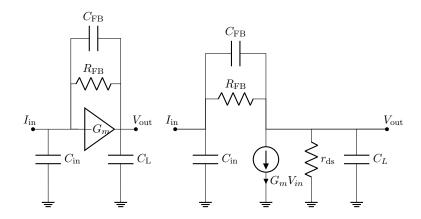

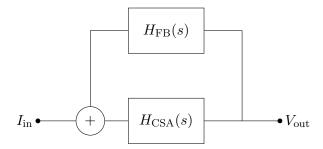

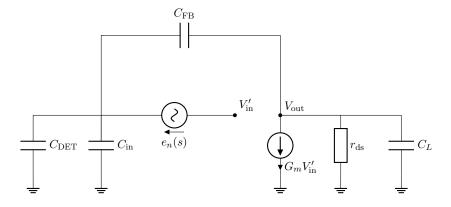

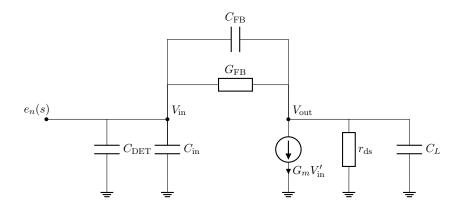

|      |                                                                                                                                               | $\frac{10}{22}$ |

|      |                                                                                                                                               | <br>23          |

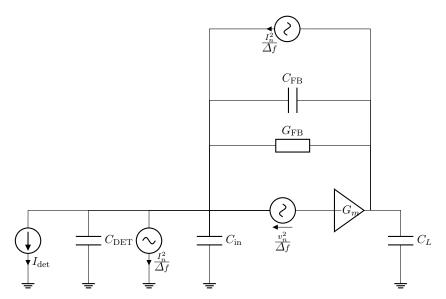

|      | Small signal model with the two thermal noise sources and the shot noise                                                                      |                 |

|      | _                                                                                                                                             | 24              |

| 2.17 | Small signal model with the thermal noise source from the input transistor.                                                                   |                 |

|      |                                                                                                                                               | $\frac{26}{26}$ |

|      | Small signal model with the thermal noise contribution from the feedback                                                                      |                 |

| 0    | _                                                                                                                                             | 27              |

|      |                                                                                                                                               |                 |

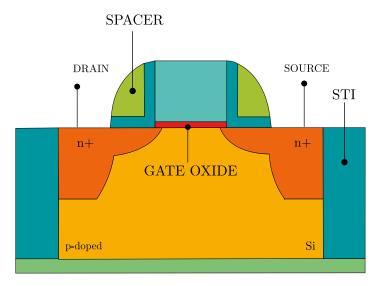

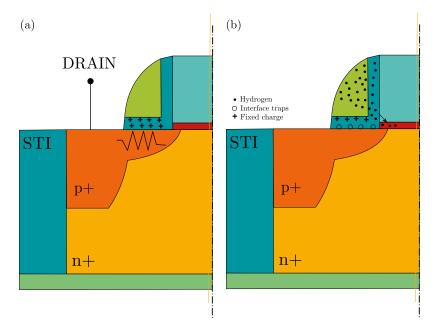

| 3.1  | Representation of an nMOS transistor section with gate oxide, STI, and                                                                        |                 |

|      | spacers, being the last two thicker and richer in defects making them more                                                                    |                 |

|      | sensitive to TID effects                                                                                                                      | 31              |

| 3.2  | Profile of a pMOS transistor showing (a) increase of the series resistance                                                                    |                 |

|      | at the sides of the transistor due to the accumulation of positive charges                                                                    |                 |

|      | at the spacers and (b) the temperature-induced activated transport of $H^+$                                                                   |                 |

|      | into the gate oxide. Under proper electric field direction and temperature,                                                                   |                 |

|      | $H^+$ ions can drift into the gate oxide. They depassivate the Si-H bonds at                                                                  |                 |

|      | the interface, generating interface traps                                                                                                     | 32              |

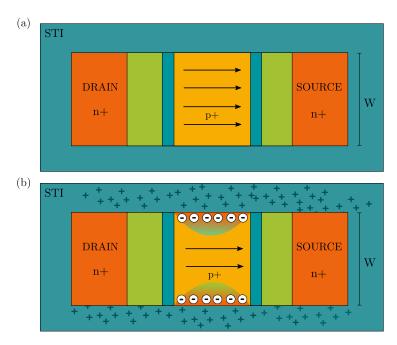

| 3.3  | Top view of an nMOS transistor where: (a) before irradiation and with                                                                         |                 |

|      | an inversion layer formed, the current flows from drain to source and                                                                         |                 |

|      | (b) during irradiation the positive charge gets accumulated at the STI                                                                        |                 |

|      | oxide whereas the negative charge gets accumulated at the interface traps                                                                     |                 |

|      | between STI and Si. This narrows the nominal channel decreasing the                                                                           |                 |

|      |                                                                                                                                               | 33              |

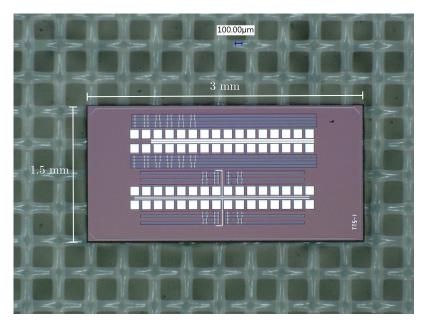

| 3.4  | TTS1 chip containing both nMOS and pMOS (i) wide and long transistors                                                                         |                 |

|      | $(6\mu\mathrm{m} \times 5\mu\mathrm{m})$ (ii) narrow and long transistors $(0.2\mu\mathrm{m} \times 6\mu\mathrm{m})$ (iii) narrow             |                 |

|      | and short transistors (0.2 $\mu$ m x 0.1 $\mu$ m). It also includes several nMOS                                                              |                 |

|      | and pMOS transistors with width fixed at 1.0 µm and length ranging from                                                                       |                 |

|      | $0.1\mu\mathrm{m}$ to $1.0\mu\mathrm{m}$ , and on the contrary, nMOS and pMOS transistors with                                                |                 |

|      | length fixed at 0.1 $\mu m$ and length ranging from 0.2 $\mu m$ to 1.0 $\mu m.$                                                               | 34              |

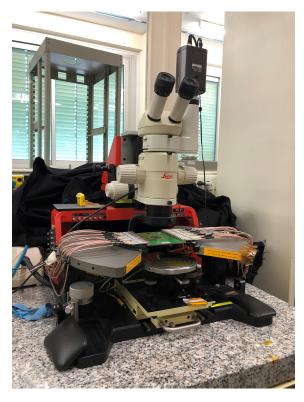

| 3.5  | Wafer probe station with a probe card and a thermal chuck used to perform                                                                     |                 |

|      |                                                                                                                                               | 35              |

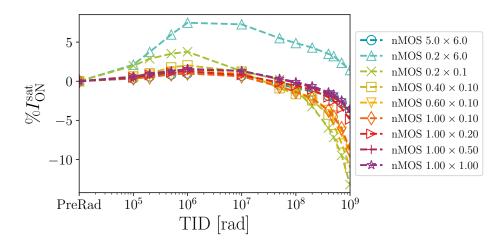

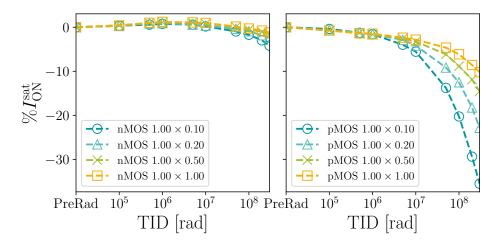

| 3.6  | Percentage variation of $I_{\text{ON}}^{\text{sat}}$ for nMOS transistors with widths ranging                                                 |                 |

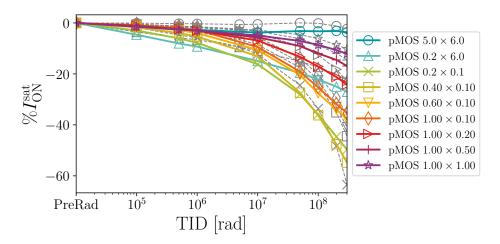

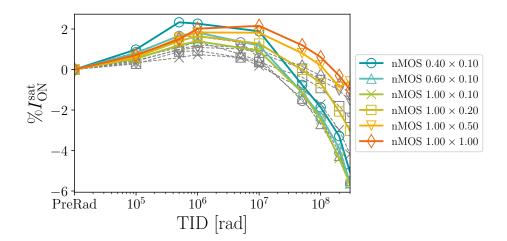

|      | from $0.2\mu\mathrm{m}$ to $5.0\mu\mathrm{m}$ and lengths from $0.1\mu\mathrm{m}$ to $6.0\mu\mathrm{m}$                                       | 36              |

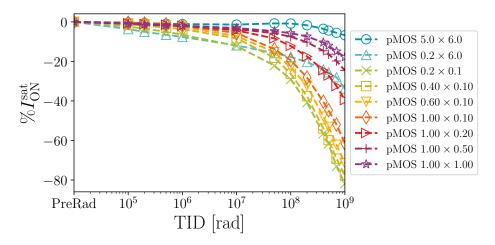

| 3.7  | Percentage variation of $I_{\text{ON}}^{\text{sat}}$ for pMOS transistors with widths ranging                                                                                                                  | 25 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

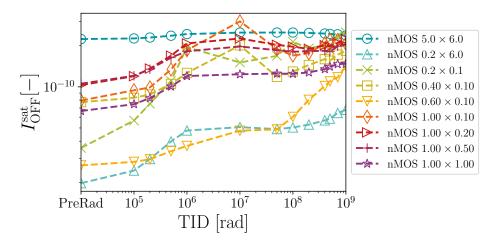

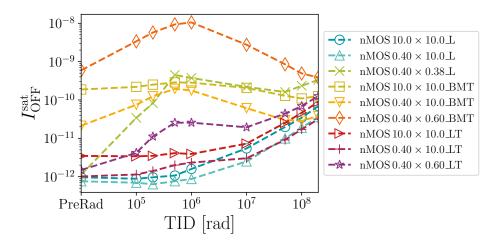

| 3.8  | from $0.2 \mu\text{m}$ to $5.0 \mu\text{m}$ and lengths from $0.1 \mu\text{m}$ to $6.0 \mu\text{m}$ Variation of $I_{\text{OFF}}^{\text{sat}}$ for nMOS transistors with widths ranging from $0.2 \mu\text{m}$ | 37 |

| 3.0  |                                                                                                                                                                                                                | 37 |

| 3.9  | to $5.0 \mu\text{m}$ and lengths from $0.1 \mu\text{m}$ to $6.0 \mu\text{m}$                                                                                                                                   | 31 |

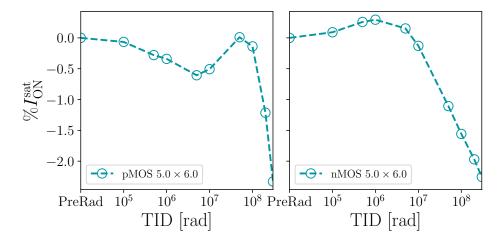

| 3.3  | (right) transistor. In this case the variations are dominated by the gate                                                                                                                                      |    |

|      | oxide effects. However, both nMOS and pMOS show a similar response                                                                                                                                             |    |

|      | with a low variation up to $\approx 2.5\%$                                                                                                                                                                     | 38 |

| 3 10 |                                                                                                                                                                                                                | 90 |

| 3.10 | Percentage variation of $I_{\text{ON}}^{\text{sat}}$ during irradiation of nMOS (left) and pMOS (right) for transistors with width 1.0 um and length from 0.1 um to 1.0 um                                     | 39 |

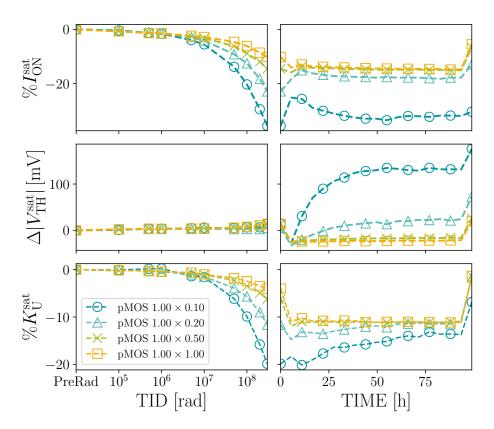

| 3 11 | (right) for transistors with width 1.0 µm and length from 0.1 µm to 1.0 µm.                                                                                                                                    | Jö |

| 0.11 | Percentage of variation of the maximum drain current ( $\%I_{\text{ON}}^{\text{sat}}$ ) (up), threshold voltage shift ( $\Delta V_{\text{TH}}^{\text{sat}} $ ) (middle) and the percentage of variation of     |    |

|      | the transconductance (% $K_{\rm U}^{\rm sat}$ ) (bottom). The values are plotted during                                                                                                                        |    |

|      | irradiation up to 300 Mrad (SiO <sub>2</sub> ) (left) and during 85 h annealing at                                                                                                                             |    |

|      | 100 °C (right). The last point was measured at the end of the annealing at                                                                                                                                     |    |

|      | 25 °C. The width of the transistors is fixed to 1.00 μm and lengths range                                                                                                                                      |    |

|      | from $0.1\mu\mathrm{m}$ to $1.0\mu\mathrm{m}$                                                                                                                                                                  | 40 |

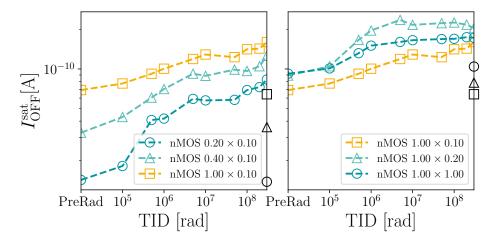

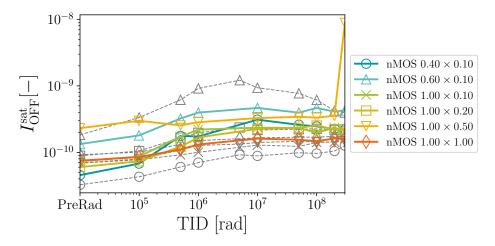

| 3.12 | Evolution of $I_{\text{OFF}}^{\text{sat}}$ during irradiation up to 300 Mrad (SiO <sub>2</sub> ). On the left,                                                                                                 |    |

| 9    | for nMOS transistors with lengths of 0.10 µm and widths ranging from                                                                                                                                           |    |

|      | 0.20 μm to 1.0 μm. On the right, for nMOS transistors with widths fixed to                                                                                                                                     |    |

|      | 1.00 μm and lengths ranging from 0.10 μm to 1.0 μm. The black markers                                                                                                                                          |    |

|      | at the end of each plot correspond to the values of $I_{ m OFF}^{ m sat}$ measured after                                                                                                                       |    |

|      | 85 h of annealing at 100 °C                                                                                                                                                                                    | 41 |

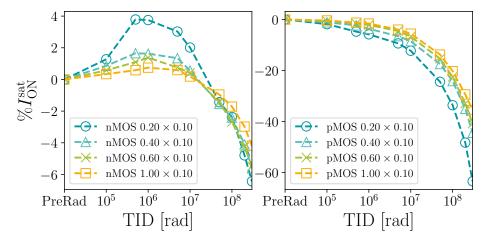

| 3.13 | Variation of $I_{\text{ON}}^{\text{sat}}$ during irradiation of nMOS for transistors (left) and                                                                                                                |    |

|      | pMOS transistors (right) with width from 0.2 μm to 1.0 μm and length                                                                                                                                           |    |

|      | $0.1\mathrm{\mu m}$ . The transistors were biased with $V_\mathrm{DS} = V_\mathrm{GS} = 1.2\mathrm{V}$                                                                                                         | 41 |

| 3.14 | Percentage variation of $I_{\rm ON}^{\rm sat}$ for pMOS transistors from WAF22 (modified                                                                                                                       |    |

|      | process) with widths ranging from $0.2\mu\mathrm{m}$ to $5.0\mu\mathrm{m}$ and lengths from                                                                                                                    |    |

|      | $0.1\mathrm{\mu m}$ to $6.0\mathrm{\mu m}$ . The transistors were diode biased with $V_\mathrm{DS} = V_\mathrm{GS} =$                                                                                          |    |

|      | -1.2 V                                                                                                                                                                                                         | 44 |

| 3.15 | Percentage variation of $I_{\rm ON}^{\rm sat}$ for nMOS transistors from WAF22 (modified                                                                                                                       |    |

|      | process) with widths ranging from 0.2 μm to 1.0 μm and lengths from                                                                                                                                            |    |

|      | $0.1\mu\mathrm{m}$ to $1.0\mu\mathrm{m}$ . The transistors were diode biased with $V_{\mathrm{DS}} = V_{\mathrm{GS}} =$                                                                                        |    |

|      | 1.2 V                                                                                                                                                                                                          | 44 |

| 3.16 | Variation of $I_{ m OFF}^{ m sat}$ for nMOS transistors with widths ranging from 0.2 $\mu$ m                                                                                                                   |    |

|      | to $1.0\mu m$ and lengths from $0.1\mu m$ to $1.0\mu m$ . The transistors were diode                                                                                                                           |    |

|      | biased with $V_{\rm DS} = V_{\rm GS} = 1.2\mathrm{V}.$                                                                                                                                                         | 45 |

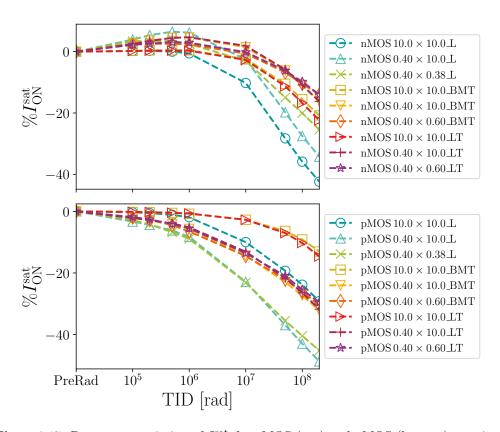

| 3.17 | Percentage variation of $I_{\text{ON}}^{\text{sat}}$ for nMOS (top) and pMOS (bottom) transi-                                                                                                                  |    |

|      | stors with different gate oxide thicknesses (L: 9.5 nm, LT: 6.5 nm, BMT:                                                                                                                                       | 40 |

| 0.10 | Bulk)                                                                                                                                                                                                          | 46 |

| J.18 | Variation of $I_{\text{OFF}}^{\text{sat}}$ for nMOS transistors with different gate oxide thicknesses                                                                                                          | 40 |

|      | (L: 9.5 nm, LT: 6.5 nm, BMT: Bulk)                                                                                                                                                                             | 46 |

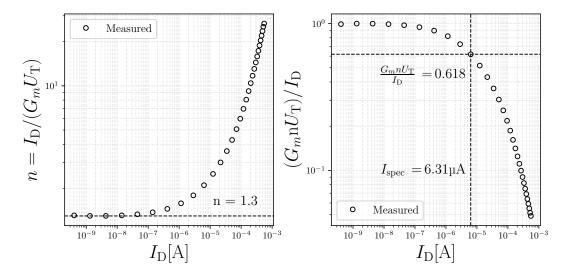

| 4.1  | First step (left): $n$ as a function of $I_D$ . The slope factor can be extracted from the plateau and its value will be fixed for the rest of the extraction as                                         |     |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | from the plateau and its value will be fixed for the rest of the extraction as it is free from velocity of saturation effects. Second step (right): $G_m n U_T / I_D$                                    |     |

|      | as a function of $I_D$ . $I_{\text{spec}}$ is the value of $I_D$ where $G_m n U_T / I_D$ becomes 0.618.                                                                                                  |     |

|      | The extracted value of $I_{\text{spec}}$ must be adjusted later on the optimization                                                                                                                      |     |

|      | process, as it is dependent on velocity of saturation effects                                                                                                                                            | 54  |

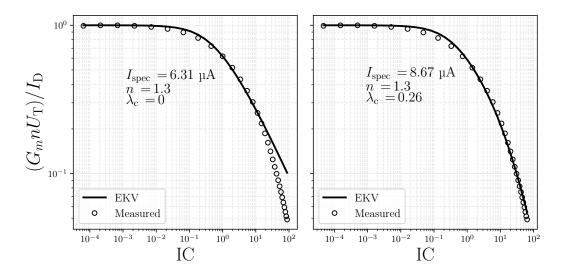

| 4.2  | Plot of $G_m n U_T / I_D$ using the simulation data and Equation (4.5) before optimization (left) and after optimization (right). To avoid over-fitting on                                               |     |

|      | the strong inversion region due to denser sampling, we weighted the cost function using the square root of the differences between the drain current                                                     |     |

|      | samples                                                                                                                                                                                                  | 55  |

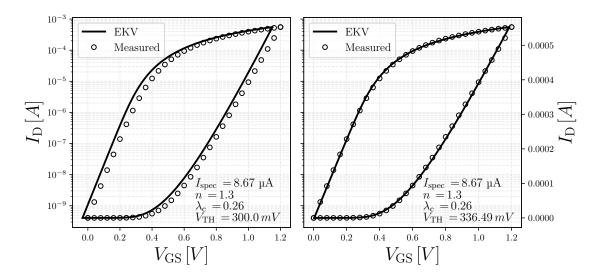

| 4.3  | $I_{\rm D}(V_{\rm GS})$ curves before (left) and after optimizing (right) in both linear and logarithmic scale. The four main parameters ( $I_{\rm spec}$ , $n$ , $\lambda_{\rm c}$ , $V_{\rm TH}$ ) are |     |

|      | also reported                                                                                                                                                                                            | 56  |

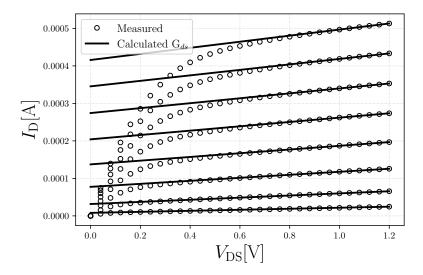

| 4.4  | $I_{\rm D}(V_{\rm DS})$ curves before irradiation and calculated $G_{\rm DS}$ for different gate voltages ranging from $0.2{\rm V}$ to $1.2{\rm V}$                                                      | 56  |

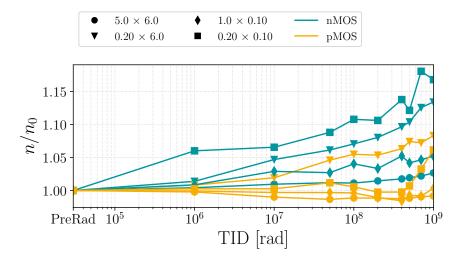

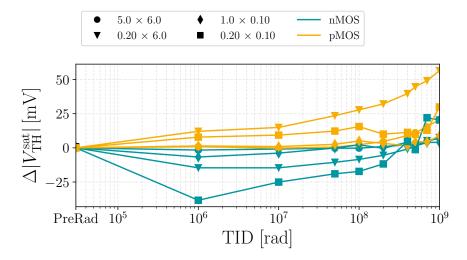

| 4.5  | Evolution of the slope factor $n$ with TID for four different extreme sizes of                                                                                                                           | 90  |

| 1.0  | nMOS (blue) and pMOS (orange) transistors. Narrow nMOS transistors exhibit a more significant increase, while pMOS devices, especially in                                                                |     |

|      | narrow configurations, show a slight upward trend, influenced by charge                                                                                                                                  |     |

|      | trapping effects on the STI interface                                                                                                                                                                    | 58  |

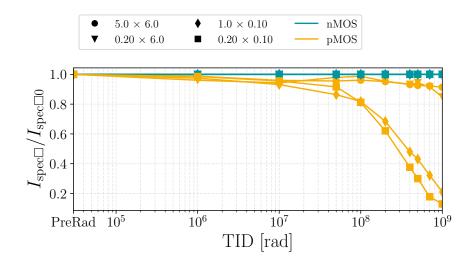

| 4.6  | Evolution of the specific current ( $I_{\text{spec}}$ ) with TID for four different extreme sizes of nMOS (blue) and pMOS (orange) transistors. In nMOS transistors,                                     |     |

|      | the variation of the specific current is negligible; however, there is a                                                                                                                                 |     |

|      | considerable degradation in pMOS devices                                                                                                                                                                 | 59  |

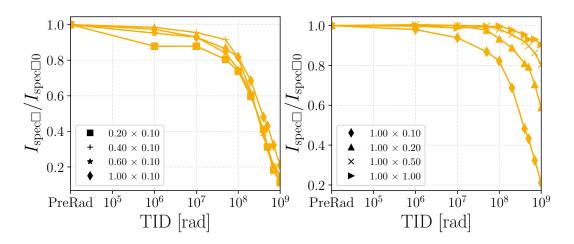

| 4.7  | Variation of $I_{\text{spec}}$ for pMOS transistors with a fixed length and different widths (left) and pMOS transistors with fixed width and different lengths                                          |     |

|      | widths (left), and pMOS transistors with fixed width and different lengths (left)                                                                                                                        | 59  |

| 4.8  | Evolution of the threshold voltage $(V_{\text{TH}})$ with TID for four different                                                                                                                         | 93  |

| 1.0  | extreme sizes of nMOS (blue) and pMOS (orange) transistors                                                                                                                                               | 60  |

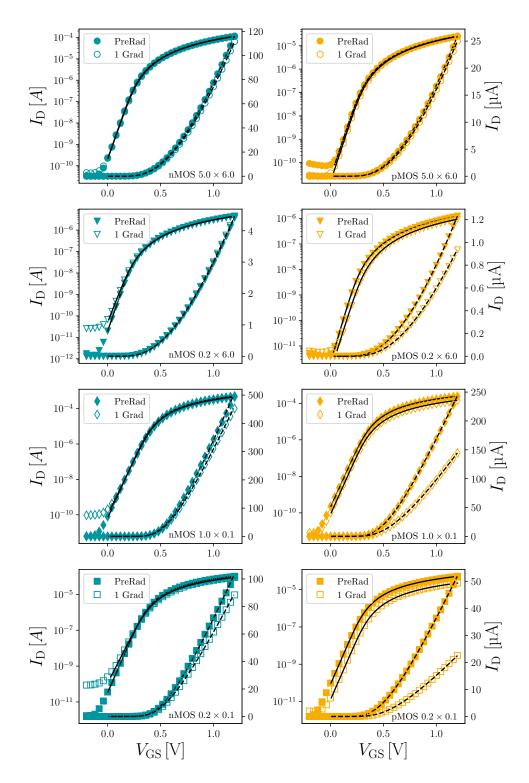

| 4.9  | Large-signal transfer characteristic extraction for four different sizes of                                                                                                                              | 0.0 |

|      | nMOS (blue) and pMOS (orange): wide and long, narrow and long, wide                                                                                                                                      |     |

|      | and short, and minimum size. Filled symbols represent the transfer charac-                                                                                                                               |     |

|      | teristics before irradiation, and the empty ones represent measurements at                                                                                                                               |     |

|      | 1 Grad. Black lines correspond to the EKV extraction                                                                                                                                                     | 61  |

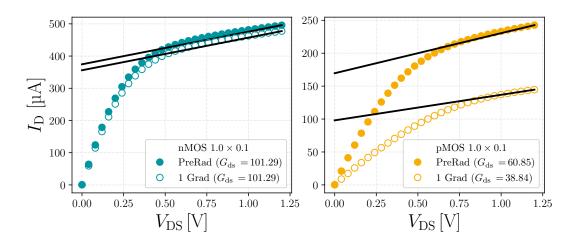

| 4.10 | Output characteristic of a wide and short nMOS transistor (left) and a                                                                                                                                   |     |

|      | pMOS transistor (right) before (filled symbols) and after (empty symbols)                                                                                                                                |     |

|      | irradiation. These values of $G_{\rm DS}$ were extracted from the measurements                                                                                                                           |     |

|      | and not from the model                                                                                                                                                                                   | 62  |

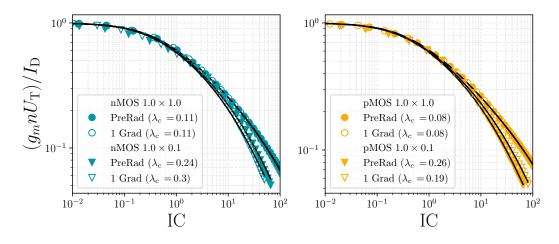

| 4.11 | Normalized transconductance efficiency of wide and long, as well as wide                                                                       |    |

|------|------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | and short, nMOS transistors (blue) and pMOS transistors (orange) before                                                                        |    |

|      | and after irradiation in relation to the inversion coefficient. The respective                                                                 |    |

|      | values of $\lambda_c$ are also provided                                                                                                        | 63 |

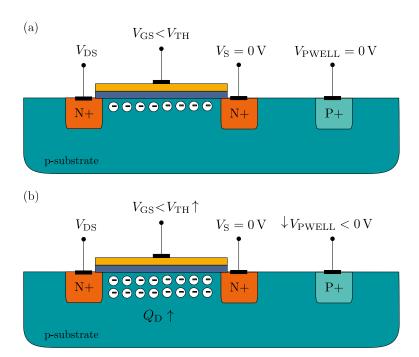

| 4.12 | Representation of the "body effect". In a) the nMOS device is biased with                                                                      |    |

|      | a $V_{\rm GS}$ not over $V_{\rm TH}$ but enough to create a depletion layer. In b) the                                                         |    |

|      | $V_{\mathrm{PWELL}}$ drops, the charge at the depletion layer $(Q_{\mathrm{d}})$ increases forcing the                                         |    |

|      | $V_{\mathrm{TH}}$ to increase. Therefore we will need a higher $V_{\mathrm{GS}}$ to invert the channel.                                        | 65 |

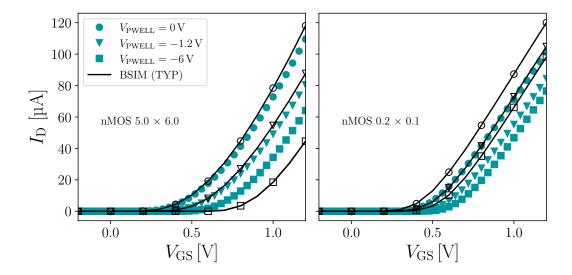

| 4.13 | $I_{\rm D}(V_{\rm GS})$ of a maximum size 5 $\mu$ m x 6 $\mu$ m device (left) and a minimum                                                    |    |

|      | size $0.2\mu\mathrm{m} \times 0.1\mu\mathrm{m}$ device (right) measured at $V_{\mathrm{PWELL}} = 0\mathrm{V}$ (circles),                       |    |

|      | at $V_{\rm PWELL} = -1.2{ m V}$ (triangles) and at $V_{\rm PWELL} = -6{ m V}$ (squares). Black                                                 |    |

|      | colored curves correspond to their equivalent simulations (TYP corner). $$ .                                                                   | 66 |

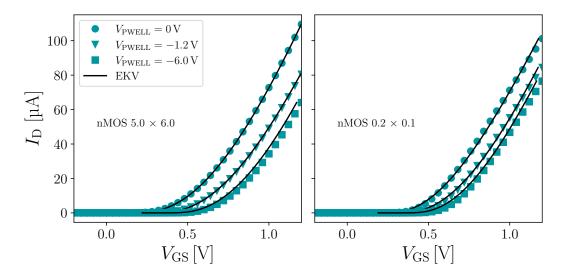

| 4.14 | $I_{\rm D}(V_{\rm GS})$ of a maximum size $5\mu{\rm m}$ x $6\mu{\rm m}$ device (left) and a minimum                                            |    |

|      | size $0.2\mu\mathrm{m} \times 0.1\mu\mathrm{m}$ device (right) measured at $V_{\mathrm{PWELL}} = 0\mathrm{V}$ (circles),                       |    |

|      | at $V_{\rm PWELL} = -1.2{ m V}$ (triangles) and at $V_{\rm PWELL} = -6{ m V}$ (squares). Black                                                 |    |

|      | curves correspond to the EKV fitting                                                                                                           | 67 |

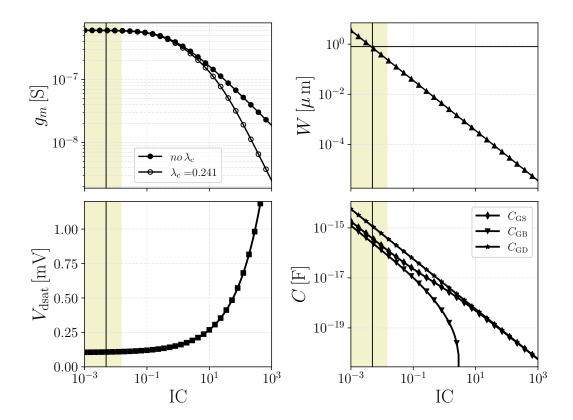

| E 1  | Then goes ductones (c.) width (III) setumetion welters (IV.) on the meta-                                                                      |    |

| 5.1  | Transconductance $(g_{\rm m})$ , width $(W)$ , saturation voltage $(V_{\rm dsat})$ , or the gate                                               |    |

|      | capacitance values $(C_{GS}, C_{GB}, C_{GD})$ versus the IC. The yellow shaded                                                                 |    |

|      | part is the area of interest as this is the range of widths available in the                                                                   |    |

|      | technology. The horizontal and vertical black lines mark the operating                                                                         | 71 |

| F 9  | points of the selected width of 800 nm                                                                                                         | 71 |

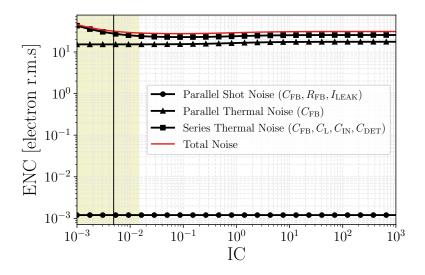

| 5.2  | Parallel shot noise, parallel thermal noise and series thermal noise, together with the total noise contribution versus IC                     | 79 |

| 5.3  | with the total noise contribution versus IC.                                                                                                   | 72 |

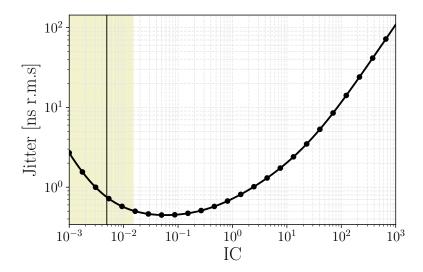

| 5.5  | Jitter versus the inversion coefficient. In the area of interest, the jitter                                                                   |    |

|      | reads below 10 ns. The jitter will be limited by the noise and the feedback capacitance value, and will decrease as the input charge increases | 73 |

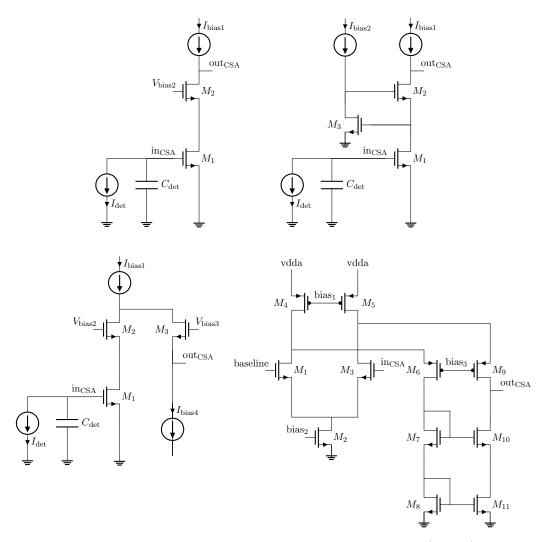

| 5.4  | Single-Ended CSA Topologies: cascoded common source (up left), common                                                                          | 10 |

| 0.4  | source with regulated cascode (up right), common source with folded cas-                                                                       |    |

|      | code (bottom left), and differential amplifier with folded cascode (bottom                                                                     |    |

|      | right)                                                                                                                                         | 75 |

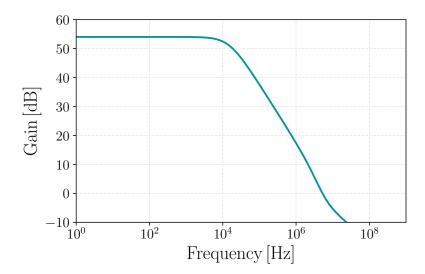

| 5.5  | Gain of the differential CSA                                                                                                                   | 77 |

| 5.6  | Explored feedback topologies [25]: Krummenacher feedback (left), current                                                                       | •  |

| 0.0  | mirror feedback (middle), and continuous reset (right). The red colored                                                                        |    |

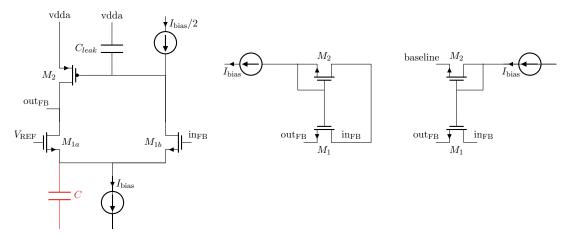

|      | component is the parasitic capacitance created by the differential pair                                                                        | 78 |

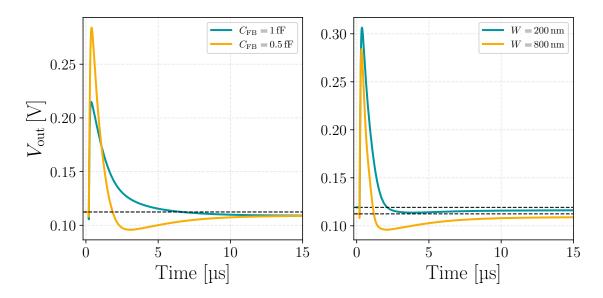

| 5.7  | Result of the two possible solutions to reduce the undershoot introduced                                                                       |    |

|      | by the Krummenacher feedback, applied when the CSA biasing current                                                                             |    |

|      | is 20 nA, the Krummenacher biasing current is 20 pA and the feedback                                                                           |    |

|      | capacitance is 0.5 fF. On the left, keeping the width fixed and changing                                                                       |    |

|      | the feedback capacitance. On the right, fixing $C_{\rm FB}$ and varying the width.                                                             | 79 |

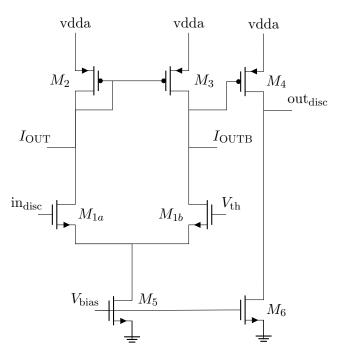

| 5.8  | Discriminator, based on a two-stage CMOS OTA                                                                                                   | 80 |

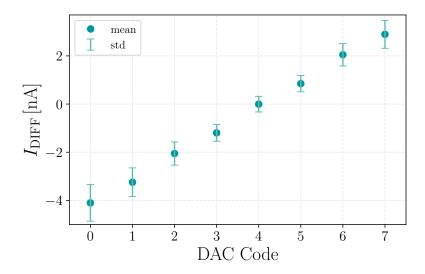

| 5.9  | Mean and standard deviation of the difference $(I_{\mathrm{DIFF}})$ between the positive           |    |

|------|----------------------------------------------------------------------------------------------------|----|

|      | output current $(I_{OUT})$ and the negative output current $(I_{OUTB})$ , obtained                 |    |

|      | after 400 Monte Carlo runs                                                                         | 81 |

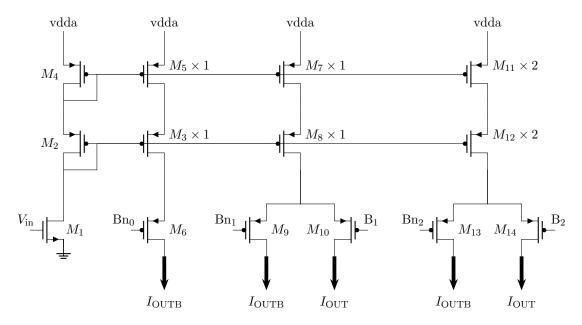

| 5.10 | Schematic 3-bit DAC                                                                                | 82 |

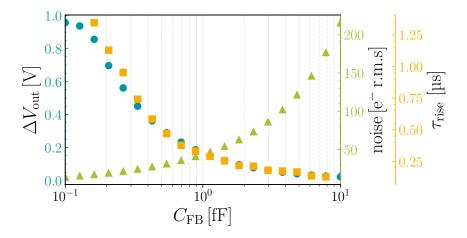

| 5.11 | Influence of feedback capacitance on the amplitude and rise time of the                            |    |

|      | CSA's output pulse, and on its baseline noise. In order to boost the                               |    |

|      | detection of small input charges and reduce noise, the feedback capacitance                        |    |

|      | will be set to 0.5 fF. $\dots$                                                                     | 83 |

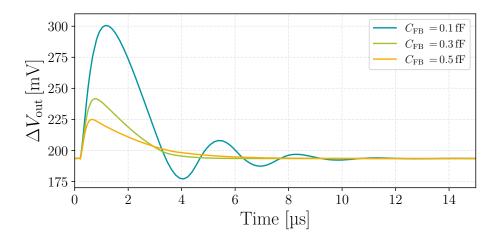

| 5.12 | Different CSA outputs for different $C_{\rm FB}$ values and the same input charge.                 |    |

|      | The value $C_{\rm FB}$ plays an important role on the stability of the FE                          | 84 |

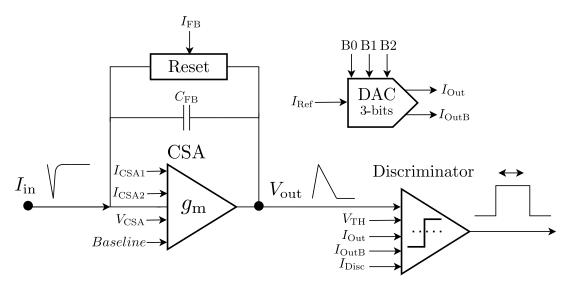

| 5.13 | Block digram of the implemented FE and the biasing lines of each designed                          |    |

|      | sub-block                                                                                          | 84 |

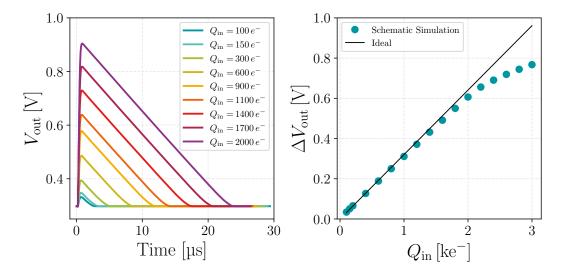

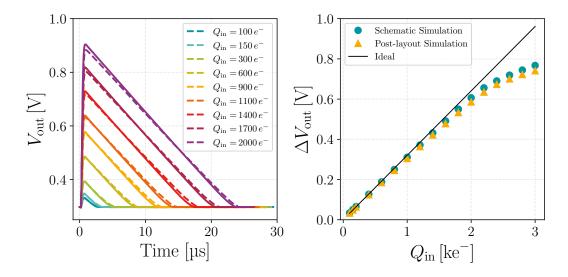

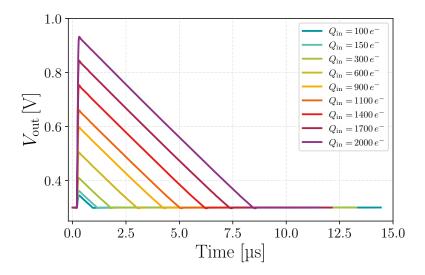

| 5.14 | Output of a transient simulation of the CSA with input pulses ranging                              |    |

|      | from $100\mathrm{e^-}$ to $3000\mathrm{e^-}$ . On the left, the output voltage versus time is      |    |

|      | presented for input charges ranging from 100 e <sup>-</sup> to 2000 e <sup>-</sup> . On the right, |    |

|      | the maximum amplitude of the output pulse against the input charge                                 | 85 |

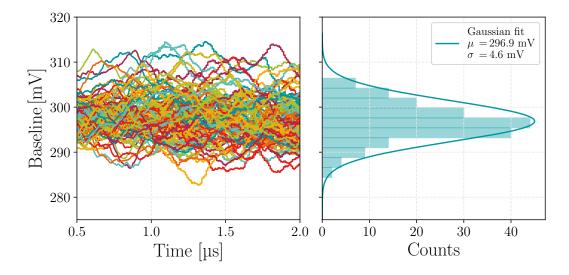

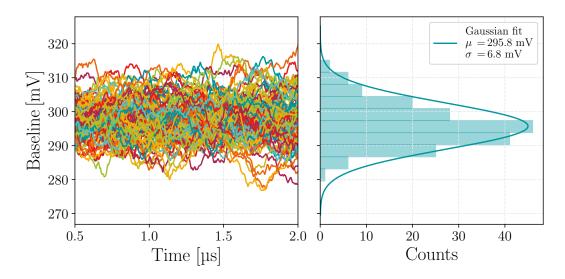

| 5.15 | Noise measurement of the FE. Blue bars correspond to measured counts                               |    |

|      | while scaning the baseline and the blue line to the Gaussian fit. The                              |    |

|      | standard deviation is the noise of the system which is 5 mV or 17 e <sup>-</sup>                   | 85 |

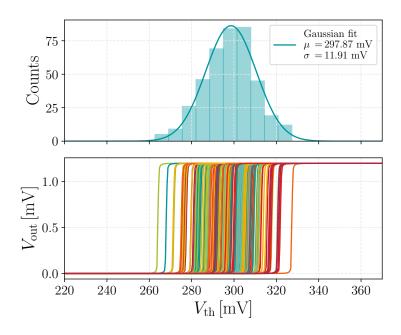

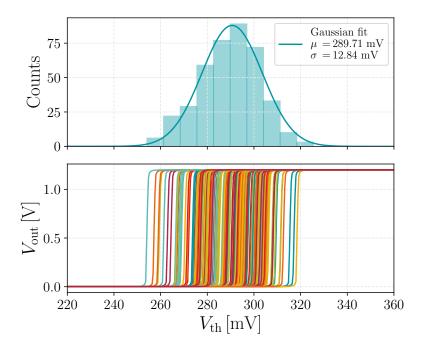

| 5.16 | Result of a Monte Carlo simulation with 200 runs. At the top, the simulated                        |    |

|      | number of counts versus the threshold voltage together with the Gaussian                           |    |

|      | fit. At the bottom, the discriminator output voltage versus the threshold                          |    |

|      | voltage. The unequalized threshold, which is the standard deviation, is                            |    |

|      | 12 mV or 40 e <sup>-</sup>                                                                         | 86 |

| 5.17 | Number of events counted while scanning the threshold voltage for a single                         |    |

|      | pixel. To extract these results we used the noise edge detection method                            | 87 |

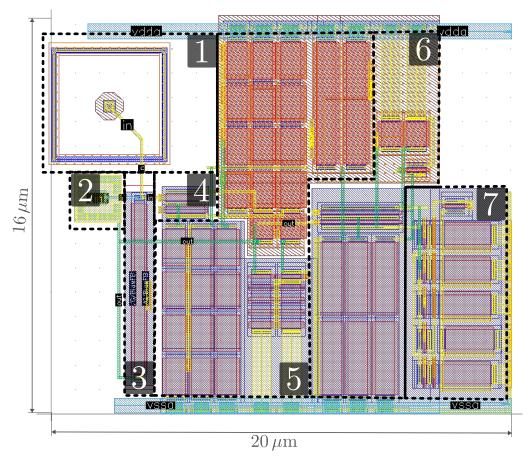

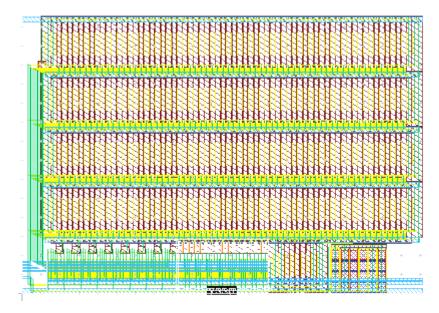

| 5.18 | Layout of the low-power, low-noise front-end. The FE includes: (1) collec-                         |    |

|      | tion electrode, (2) feedback capacitance, (3) feedback transistor, (4) input                       |    |

|      | transistor, (5) CSA, (6) discriminator, and (7) 3-bit DAC. This results in                         |    |

|      | a total size of $320  \mu \text{m}^2$                                                              | 88 |

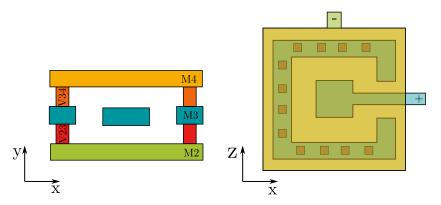

| 5.19 | Schematic view of feedback capacitance based on interconecting metals.                             |    |

|      | The inner terminal of the capacitance (in Metal 3) is surrounded by Metal                          |    |

|      | 2 and Metal 4                                                                                      | 89 |

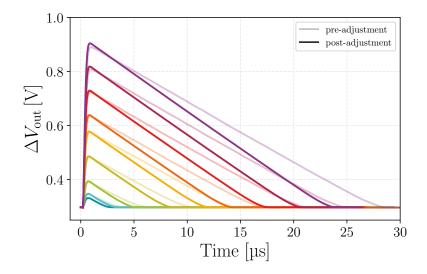

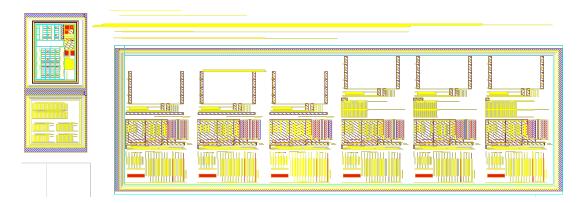

| 5.20 | Transient simulation output of CSA with increased bias current: layout                             |    |

|      | results. This plot shows the output voltage versus time but with a feedback                        |    |

|      | biasing current of 1.25 nA. After adjustments, the transient performance                           |    |

|      | becomes comparable to the schematic                                                                | 89 |

| 5.21       | Transient simulation output of the CSA: comparison between schematic and layout. On the left, output voltage versus time for input charges ranging from $100\mathrm{e^-}$ to $2000\mathrm{e^-}$ . The solid lines represent the schematic, while the dashed lines represent the layout. On the right, the maximum amplitude of the output pulse against the input charge. Blue dots correspond to |          |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|            | schematic, orange dots to layout, and the black line represents the ideal. To achieve similar performance, the feedback current was increased from 1 nA to 1.25 nA                                                                                                                                                                                                                                | 90       |

| 5.22       | Noise measurement of extracted layout for CSA. The plot displays the noise measurement with a standard deviation of $7\mathrm{mV}$ or $20\mathrm{e}^-$ . The increase in noise can be attributed to the rise in parasitic capacitances, leading to an                                                                                                                                             |          |

| 5.23       | increase in series thermal noise                                                                                                                                                                                                                                                                                                                                                                  | 91       |

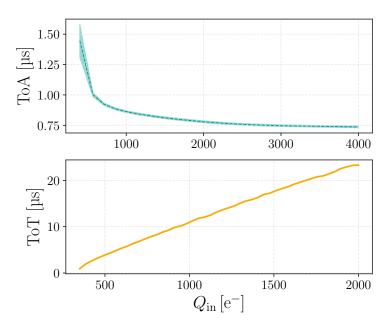

| 5.24       | $136\mathrm{e^-}$                                                                                                                                                                                                                                                                                                                                                                                 | 92<br>93 |

|            | Worst-case power supply voltage drop for a pixel at the top                                                                                                                                                                                                                                                                                                                                       | 93       |

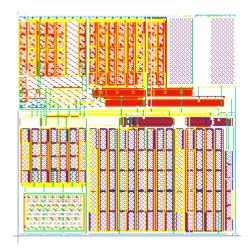

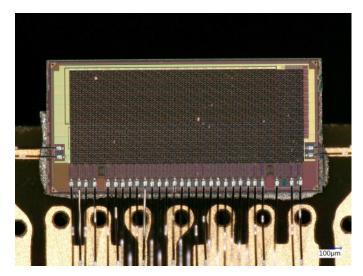

| A.1        | Layout of the 8-bit DAC. The main block is a matrix of transistors distributed in centroid configuration for better mismatch                                                                                                                                                                                                                                                                      | 104      |

| A.2        | Layout of the R2R block                                                                                                                                                                                                                                                                                                                                                                           |          |

| A.3        | Layout of the analog periphery. Inside the main rectangle (which is the guard ring), on the right, we can find three voltage DACs, and on the left, the three current DACs. The circuitry at the bottom of these blocks is the set of current mirrors used to adapt the range delivered by each DAC to                                                                                            |          |

| A.4<br>A.5 | the specifications of the FE                                                                                                                                                                                                                                                                                                                                                                      |          |

|            | transistors on the FE                                                                                                                                                                                                                                                                                                                                                                             | 106      |

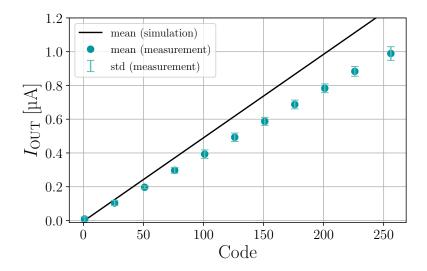

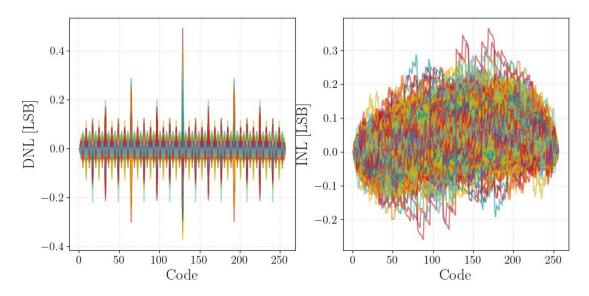

| A.6 | Measured DNL and INL. The DNL is below 1 LSB and the INL below 0.5 |

|-----|--------------------------------------------------------------------|

|     | LSB, ensuring non missing codes                                    |

## List of Tables

| 2.1  | Nominal settings of the H2M and MOSS front-ends                                                                                                                                                                                                                                                                                                                                                                 | 21 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.1  | Maximum drain current $I_{\rm ON}$ and leakage current $I_{\rm OFF}$ measured in linear and saturation region for narrow and short, large and short and narrow and long nMOS devices from WAF13 and WAF22                                                                                                                                                                                                       | 43 |

| 3.2  | Maximum drain current $I_{\rm ON}$ and leakage current $I_{\rm OFF}$ measured in linear and saturation region for narrow and short, large and short and narrow and long pMOS devices from WAF13 and WAF22                                                                                                                                                                                                       | 43 |

| 4.1  | Extracted values of $V_{\rm TH}$ from the measurements and simulation (TYP corner) showed at Figure 4.13 for $V_{\rm PWELL} = 0, -1.2  \rm V, -6  \rm V$ . The respective $V_{\rm TH}$ shift from the nominal value ( $V_{\rm TH}^{\rm sat}$ measured at $V_{\rm PWELL} = 0, -1.2  \rm V, -6  \rm V$ ) is shown in parenthesis                                                                                  | 65 |

| 4.2  | Extracted values of $I_{\text{ON}}^{\text{sat}}$ from the measurements and simulation (TYP corner) showed at Figure 4.13 for $V_{\text{PWELL}} = 0$ , $-1.2\text{V}$ , $-6\text{V}$ . The respective percentage of variation of $I_{\text{ON}}^{\text{sat}}$ from the nominal value ( $I_{\text{ON}}^{\text{sat}}$ measured at $V_{\text{PWELL}} = 0$ , $-1.2\text{V}$ , $-6\text{V}$ ) is shown in parenthesis | 66 |

| 4.3  | Extracted values of $V_{\text{TH}}$ , $\lambda_{\text{c}}$ , $I_{\text{spec}}$ , $n$ from the measurements and EKV fitting showed at Figure 4.14 for $V_{\text{PWELL}} = 0$ , $-1.2\text{V}$ , $-6\text{V}$                                                                                                                                                                                                     | 67 |

| 5.1  | MOSS front-end specifications at the time of the ER1 submission for an input capacitance of 5 fF [50]                                                                                                                                                                                                                                                                                                           | 70 |

| 5.2  | Prefixed parameters used during the modelling                                                                                                                                                                                                                                                                                                                                                                   | 71 |

| 5.3  | Topology comparison of three single-ended charge sensitive amplifier topologies: cascoded CS (A), CS with regulated cascode (B), CS with folded                                                                                                                                                                                                                                                                 |    |

|      | cascode (C), and (D) differential amplifier with folded cascode. The simulation of the control of the cascode (C) and (D) differential amplifier with folded cascode.                                                                                                                                                                                                                                           |    |

|      | lated parameters are: gain, Power Supply Rejection Ratio (PSRR), phase                                                                                                                                                                                                                                                                                                                                          |    |

|      | margin $(\phi_{\rm m})$ , the 3 dB frequency $(f_{\rm 3dB})$ , unity gain bandwidth $(f_{\rm T})$ and number of biasing lines                                                                                                                                                                                                                                                                                   | 76 |

| 5.4  | Complementary output currents of the DAC, $I_{OUT}$ and $I_{OUTB}$ , with its                                                                                                                                                                                                                                                                                                                                   | 10 |

| J. I | difference $I_{\text{DIFF}}$ and corresponding DAC code                                                                                                                                                                                                                                                                                                                                                         | 82 |

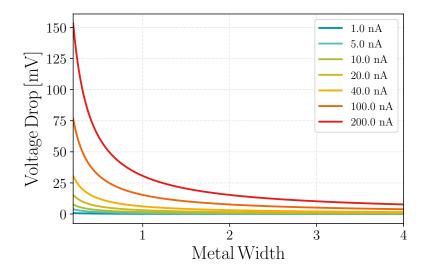

| 5.5 | Power lines (vdda and vssa), nominal currents, voltage drops, and metal    |    |

|-----|----------------------------------------------------------------------------|----|

|     | widths for each block in the pixel front-end. The CSA and discriminator    |    |

|     | power lines experience significant voltage drops due to high currents, but |    |

|     | simulations show negligible impact on the FE performance                   | 94 |

| 5.6 | Simulation extracted specifications for the MOSS and H2M front-ends and    |    |

|     | comparison with the proposed design (low-power and high-power modes).      |    |

|     | The threshold for the H2M and proposed FEs is equalized                    | 95 |

| 5.7 | Nominal settings of the H2M, MOSS, and the proposed FEs (for both          |    |

|     | low-power and high-power modes)                                            | 95 |

| 5.8 | Corner simulations (FS, SF, FF, SS, TYP) of the presented front-end        |    |

|     | working in low-power mode with an input charge of $1000\mathrm{e^-}$       | 97 |

| 5.9 | Final specifications of our design for high-power and low-power modes for  |    |

|     | a 35 $\mu$ m $\times$ 35 $\mu$ m pixel size                                | 98 |

### List of Abbreviations

**ALICE** A Large Ion Collider Experiment

ASIC Application-Specific Integrated Circuit

ATLAS A Toroidal LHC ApparatuS

BSIM Berkeley Short-channel IGFET Model

**CERN** European Organization for Nuclear Research

CMOS Complementary Metal-Oxide-Semiconductor

CMS Compact Muon Solenoid

**CSA** Charge Sensitive Amplifier

CS Common Source

**DAC** Digital-to-Analog Converter

**DNL** Differential NonLinearity Error

**DPTS** Digital Pixel Test Structure

**DRC** Design Rule Check

EKV Enz-Krummenacher-Vittoz

**ENC** Equivalent Noise Charge

EPFL Swiss Federal Institute of Technology Lausanne

**ER1** Engineering Run 1

FB Feedback

FE Front-End

FoMs Figures of Merit

**GUI** Graphic User Interface

**H2M** Hybrid-to-Monolithic

**HEP** High-Energy Physics

$\ensuremath{\mathbf{HL\text{-}LHC}}$  High Luminosity-Large Hadron Collider

IC Inversion Coefficient

I/O Input/Output

INL Integral NonLinearity Error

ITS Inner Tracking System

LHCb LHC beauty

LHC Large Hadron Collider

LSB Least Significant Bit

MALTA2 Monolithic from ALice To Atlas 2

MAPS Monolithic Active Pixel Sensor

MDC Minimum Detectable Charge

MIPs Minimum Ionizing Particles

MOSFET Metal-Oxide-Semiconductor Field-Effect Transistor

MOSS Monolithic Stitched Sensor

MOST MOnolithic Stitched sensor with Timing

MOS Metal-Oxide-Semiconductor

NDA Non-Disclosure Agreement

**OTA** Operational Transconductance Amplifier

PDK Process Design Kit

**PSD** Power Spectral Density

PSRR Power Supply Rejection Ratio

R2R Rail-to-Rail

RINCEs Radiation-Induced Narrow Channel Effects

xxii

### List of Abbreviations

RISCEs Radiation-Induced Short Channel Effects

$\mathbf{sEKV}$  simplified charge-based EKV

**SLVS** Scalable Low Voltage Signaling

STI Shallow Trench Isolation

${\bf TDC}\,$  Time to Digital Converter

**TID** Total Ionizing Dose

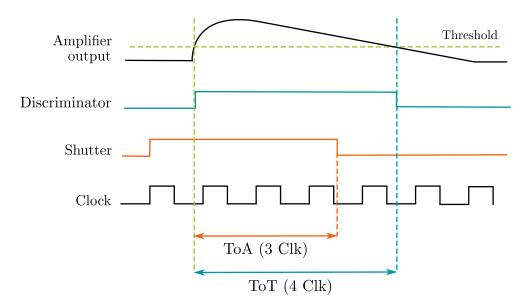

ToA Time-of-Arrival

**ToT** Time-over-Threshold

TTS Transistor Test Structure

# List of Symbols

| Voltages                   |                                                               |              |

|----------------------------|---------------------------------------------------------------|--------------|

| $V_{ m in}$                | Input voltage                                                 | V            |

| $V_{ m out}(s)$            | Output voltage in the Laplace domain                          | V            |

| $V_{ m GS}$                | Gate-to-source voltage                                        | V            |

| $V_{ m TH}$                | Threshold voltage                                             | V            |

| $V_{ m DS}$                | Drain-to-source voltage                                       | V            |

| $V_{ m dsat}$              | Saturation voltage                                            | V            |

| $V_{ m OV}$                | Overdrive voltage                                             | V            |

| $\Delta V_{ m out}$        | Amplitude of the output pulse                                 | V            |

| $V_{ m Drop}$              | Voltage drop across the pixel resistance                      | V            |

| Currents                   |                                                               |              |

| $i_{\rm k}(t)$             | Instantaneous current generated on the $k$ detector electrode | A            |

| $I_{\mathrm{in}}(s)$       | Input current in the Laplace domain                           | A            |

| $I_{ m leak}$              | Leakage current at the detector                               | A            |

| $I_{ m D}$                 | Drain current                                                 | A            |

| $I_{\rm ON}({ m TID})$     | Maximum drain current at irradiation step                     | A            |

| $I_{ m ON}^{ m lin}$       | Maximum drain current in linear region                        | A            |

| $I_{ m ON}^{ m sat}$       | Maximum drain current in saturation region                    | A            |

| $I_{ m OFF}^{ m sat}$      | Saturation leakage current                                    | A            |

| $I_{\mathrm{D,\ max}}$     | Maximum drain current in saturation                           | A            |

| $I_{ m SPEC}$              | Specific current                                              | A            |

| $I_{\mathrm{spec}\square}$ | Specific current per square                                   | A            |

| $I_n^2$                    | Noise power spectral density (PSD)                            | $A^2/Hz$     |

| $I_{ m LSB}$               | Least Significant Bit (LSB) current of the DAC                | A            |

| $\%I_{\mathrm{ON}}$        | Percentage of variation of the maximum drain current          | 1            |

| Capacitanc                 | res                                                           |              |

| $C_{\mathrm{FB}}$          | Feedback capacitance                                          | F            |