Rüdiger Schwendemann

## Hochdynamischer Netzemulator auf Basis eines Serien-Hybrid-Umrichters

# **Hochdynamischer Netzemulator auf Basis eines Serien-Hybrid-Umrichters**

Zur Erlangung des akademischen Grades eines

**DOKTORS DER INGENIEURWISSENSCHAFTEN (Dr.-Ing.)**

von der KIT-Fakultät für

Elektrotechnik und Informationstechnik

des Karlsruher Instituts für Technologie (KIT)

angenommene

**DISSERTATION**

von

M.Sc. Rüdiger Schwendemann

geb. in: Lahr/Schwarzwald

Tag der mündlichen Prüfung:

04. Februar 2025

Hauptreferent:

Prof. Dr.-Ing. Marc Hiller

Korreferent:

Prof. Dr.-Ing. Jörg Roth-Stielow

(Universität Stuttgart)

**Karlsruher Institut für Technologie (KIT)

Elektrotechnisches Institut (ETI)**

Zur Erlangung des akademischen Grades eines Doktors der Ingenieurwissenschaften von der KIT-Fakultät für Elektrotechnik und Informationstechnik des Karlsruher Instituts für Technologie (KIT) angenommene Dissertation

von M.Sc. Rüdiger Schwendemann, geb. in Lahr/Schwarzwald

Tag der mündlichen Prüfung: 04. Februar 2025

Hauptreferent: Prof. Dr.-Ing. Marc Hiller

Korreferent: Prof. Dr.-Ing. Jörg Roth-Stielow

(Universität Stuttgart)

This document is licensed under a Creative Commons

Attribution-ShareAlike 4.0 International License (CC BY-SA 4.0):

<https://creativecommons.org/licenses/by-sa/4.0/deed.en>

DOI: 10.5445/IR/1000181239

# **Vorwort**

Die Idee zur Untersuchung eines Serien-Hybrid-Umrichter als hochdynamischen Netzemulator entstand im Jahr 2017 während meiner Tätigkeit als wissenschaftlicher Mitarbeiter am Elektrotechnischen Institut (ETI) des Karlsruher Instituts für Technologie (KIT). Aus der Idee entwickelte sich in mehrjähriger Tätigkeit ein neues Konzept für einen hochdynamischen Netzemulator mit niedrigem Oberschwingungsgehalt und der Fähigkeit das frequenzabhängige Verhalten eines Prüflings bis zu einer Frequenz von 100 kHz analysieren zu können. Die Funktionsfähigkeit des Konzepts wurde mit Hilfe eines aufgebauten Prototyps mit einer Leistung von 50 kVA demonstriert.

Die erfolgreiche Vollendung meiner Forschungsarbeit wäre ohne die umfassende Unterstützung aus meinem beruflichen und privaten Umfeld nicht realisierbar gewesen. Dafür möchte ich allen Beteiligten meinen herzlichsten Dank aussprechen.

Mein besonderer Dank gilt meinem Doktorvater, Prof. Dr.-Ing. Marc Hiller, für das Vertrauen, das er mir entgegengebracht hat, sowie für die Möglichkeit, in diesem spannenden und vielseitigen Themenbereich zu promovieren. Besonders schätze ich die kontinuierliche Unterstützung und die große Freiheit, die mir bei der Durchführung dieser Forschungsarbeit gewährt wurden, sowie die wertvollen fachlichen Diskussionen, von denen ich erheblich profitiert habe.

Zudem möchte ich mich bei Herrn Prof. Dr.-Ing. Jörg Roth-Stielow für sein Interesse an meiner Arbeit und die Übernahme des Korreferats bedanken.

Mein Dank gilt selbstverständlich all meinen Kolleginnen und Kollegen am ETI. Der offene und freundschaftliche Umgang hat nicht nur zu einem

## Vorwort

---

angenehmen Arbeitsklima beigetragen, sondern auch durch zahlreiche Anregungen und Diskussionen die fachliche Grundlage für diese Arbeit geschaffen.

Ein besonderer Dank gilt in diesem Zusammenhang meinen Bürokollegen Fabian, Lukas und Daniel für die zahlreichen bereichernden Diskussionen und Anregungen, die hervorragende Arbeitsatmosphäre sowie die Unterstützung beim Aufbau des Teststands.

Mein Dank gilt auch den Studierenden, die durch ihre tatkräftige Unterstützung an diesem Projekt mitgewirkt haben. Zudem möchte ich der Werkstatt des ETIs für die angenehme Zusammenarbeit und die Unterstützung beim Aufbau des Teststands danken.

Nicht zuletzt möchte ich meiner Familie und Janina ganz besonders für die wertvolle Unterstützung während meiner Promotion danken, insbesondere für die unzähligen Stunden des Korrekturlesens und die Organisation einer großartigen Doktorfeier.

# Kurzfassung

Die gegenwärtige Transformation der elektrischen Energieversorgung führt zu einer verstärkten Integration leistungselektronischer Systeme in das Energienetz. Diese Entwicklung führt zu vermehrten Interaktionen zwischen diesen Systemen. Um diese Interaktionen präzise vorhersagen zu können, ist es entscheidend, sowohl das frequenzabhängige Klemmenverhalten der Systeme für verschiedene Arbeitspunkte als auch ihr Verhalten in dynamischen Szenarien, wie beispielsweise bei Netzfehlern, zu kennen. Diese Analyse erfolgt mithilfe von Power Hardware-in-the-loop-Netzemulatoren. Aufgrund funktionaler Einschränkungen ist es mit den bestehenden Systemen jedoch nicht möglich, das Verhalten neuer, auf schnellschaltenden Halbleitern basierender Systeme bis in den benötigten Frequenzbereich zu analysieren. An dieser Stelle knüpft die vorliegende Arbeit an, indem ein neuartiges Konzept für einen Netzemulator entwickelt wird. Hierzu werden zunächst mögliche Systemarchitekturen betrachtet und die Vorteile der verwendeten Serien-Hybrid-Architektur herausgearbeitet. Im nächsten Schritt erfolgt die Konzeptionierung, Dimensionierung, Konstruktion und Charakterisierung eines auf der Serien-Hybrid-Architektur basierenden Netzemulators. Daraufhin erfolgt eine analytische Betrachtung einer closed-loop-Emulation eines Netzanschlusspunktes und der impedanzbasierte Stabilitätsanalyse des frequenzabhängigen Klemmenverhaltens mithilfe der harmonischen Impedanz. Zudem wird die Messmethodik zur Vermessung der harmonischen Impedanz beschrieben. Messungen, bei denen verschiedene Netzszenarien nachgebildet und die Ergebnisse der Vermessung der harmonischen Impedanz eines Umrichters ermittelt werden, quantifizieren schließlich die Qualität des entwickelten Netzemulators.

# Inhaltsverzeichnis

|          |                                                                         |           |

|----------|-------------------------------------------------------------------------|-----------|

| <b>1</b> | <b>Einleitung.....</b>                                                  | <b>1</b>  |

| 1.1      | Stand der Technik .....                                                 | 4         |

| 1.1.1    | PHIL-Umrichter für Netzemulation .....                                  | 5         |

| 1.1.2    | Hybride Umrichterkonzepte .....                                         | 11        |

| 1.2      | Zielsetzung der Arbeit.....                                             | 17        |

| 1.3      | Gliederung der Arbeit .....                                             | 18        |

| <b>2</b> | <b>Konzeptionierung und Dimensionierung des PHIL-Systems .....</b>      | <b>21</b> |

| 2.1      | PHIL-Systemkonzept.....                                                 | 21        |

| 2.1.1    | Leistungselektronikkonzept.....                                         | 22        |

| 2.1.2    | Signalverarbeitungs- und Softwarestruktur des<br>PHIL-Systems.....      | 28        |

| 2.1.3    | Steuerung des SHCHB-Umrichters als Emulator .....                       | 30        |

| 2.2      | Analyse der CHB-Zelle.....                                              | 35        |

| 2.2.1    | Grundlagen des LLC-DC/DC-Wandlers .....                                 | 36        |

| 2.2.2    | Analyse des LLC-DC/DC-Wandlers.....                                     | 38        |

| 2.2.3    | Dimensionierung der CHB-Zelle inklusive des<br>LLC-DC/DC-Wandlers ..... | 43        |

|          |                                                                        |            |

|----------|------------------------------------------------------------------------|------------|

| 2.2.4    | Betriebsführung des LLC-DC/DC-Wandlers und der CHB-Zelle.....          | 52         |

| 2.3      | Analyse des Linearverstärkers .....                                    | 59         |

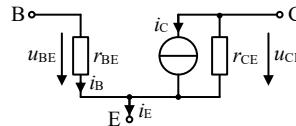

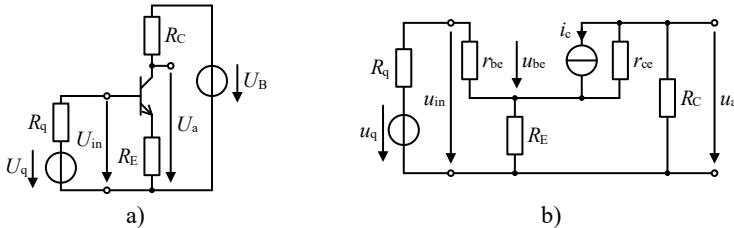

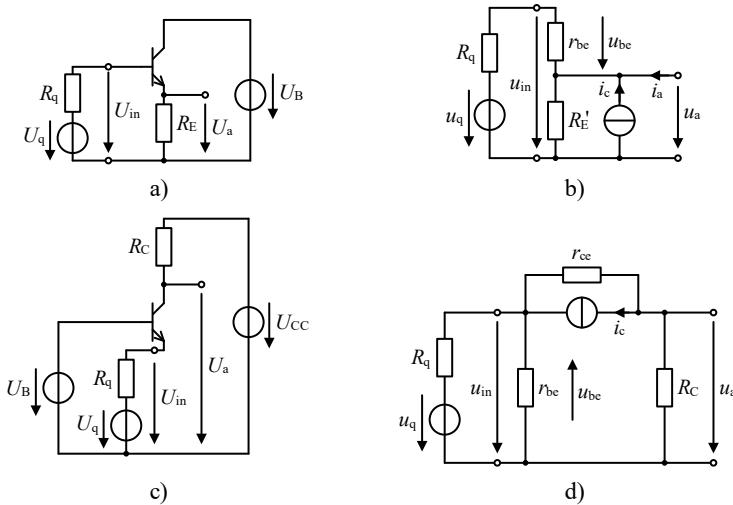

| 2.3.1    | Grundlagen der analogen Schaltungstechnik .....                        | 59         |

| 2.3.2    | Konzeptionierung des Linearverstärkers .....                           | 75         |

| 2.3.3    | Dimensionierung des Linearverstärkers .....                            | 86         |

| 2.3.4    | Ansteuerung des Linearverstärkers .....                                | 92         |

| 2.4      | Dimensionierung des Spannungssteilheitsfilters.....                    | 95         |

| <b>3</b> | <b>Versuchsaufbau und Charakterisierung des SHCHB-Umrichters .....</b> | <b>101</b> |

| 3.1      | Messequipment .....                                                    | 102        |

| 3.2      | Signalverarbeitungssystem .....                                        | 102        |

| 3.2.1    | Zentrales Signalverarbeitungssystem (CCU) .....                        | 102        |

| 3.2.2    | Dezentrale Kontrolleinheit (LCU).....                                  | 104        |

| 3.2.3    | LPA-Sollwertgenerator und Temperaturregelungseinheit .....             | 104        |

| 3.3      | PHIL-Leistungsteil.....                                                | 106        |

| 3.3.1    | CHB-Zellen .....                                                       | 106        |

| 3.3.2    | Linearverstärker .....                                                 | 110        |

| 3.3.3    | $du/dt$ -Filter.....                                                   | 117        |

| 3.4      | PHIL-System .....                                                      | 118        |

| 3.5      | Prüfling.....                                                          | 128        |

| <b>4</b> | <b>Analytische Beschreibung der closed-loop-Emulation .....</b>        | <b>131</b> |

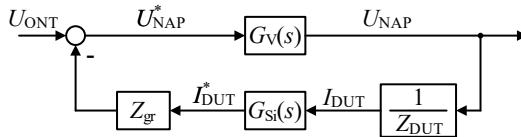

| 4.1      | Übertragungsfunktionen des PHIL-Prüfstands .....                       | 133        |

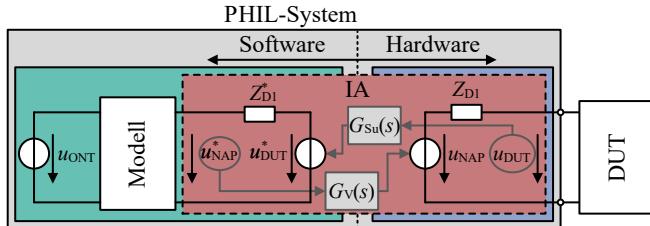

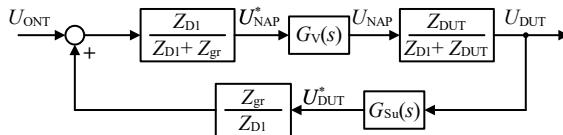

| 4.2      | Schnittstellenalgorithmus .....                                        | 135        |

| 4.2.1    | ITM-Algorithmus.....                                                   | 137        |

| 4.2.2    | PCD-Algorithmus .....                                                  | 137        |

|          |                                                                                                                 |            |

|----------|-----------------------------------------------------------------------------------------------------------------|------------|

| 4.2.3    | TLM-Algorithmus.....                                                                                            | 139        |

| 4.2.4    | TFA-Algorithmus .....                                                                                           | 140        |

| 4.2.5    | DIM-Algorithmus .....                                                                                           | 143        |

| 4.2.6    | FSF-Algorithmus und DITM-Algorithmus.....                                                                       | 144        |

| 4.3      | Bewertungskriterien für die verschiedenen<br>Schnittstellenalgorithmen.....                                     | 146        |

| <b>5</b> | <b>Harmonische Impedanz und impedanzbasierte<br/>Stabilitätsanalyse .....</b>                                   | <b>149</b> |

| 5.1      | Grundlagen der impedanzbasierten Stabilitätsuntersuchung ....                                                   | 150        |

| 5.2      | Messverfahren zur Ermittlung des frequenzabhängigen<br>Verhaltens .....                                         | 152        |

| 5.3      | Modellierung eines 2L-Umrichters mit LCL-Filter .....                                                           | 156        |

| <b>6</b> | <b>Analyse der verschiedenen Prüfszenarien.....</b>                                                             | <b>163</b> |

| 6.1      | Emulation eines schwachen Netzanschlusspunkts .....                                                             | 163        |

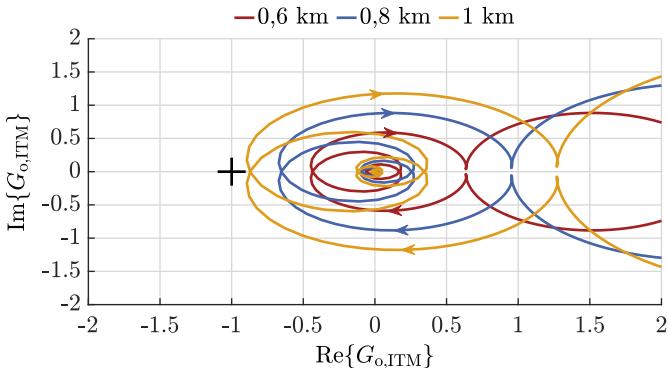

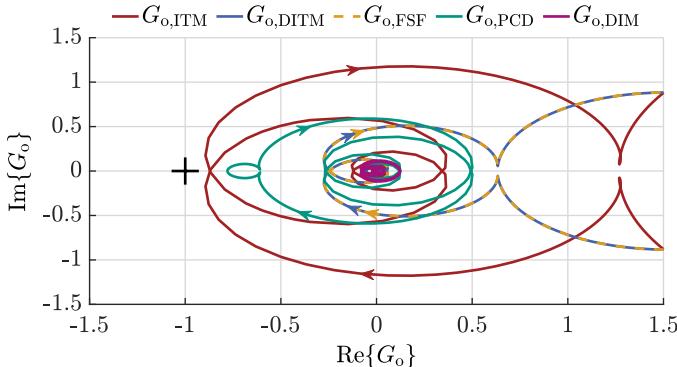

| 6.1.1    | Stabilitätsbetrachtung der Netzemulation für<br>verschiedene Schnittstellenalgorithmen .....                    | 165        |

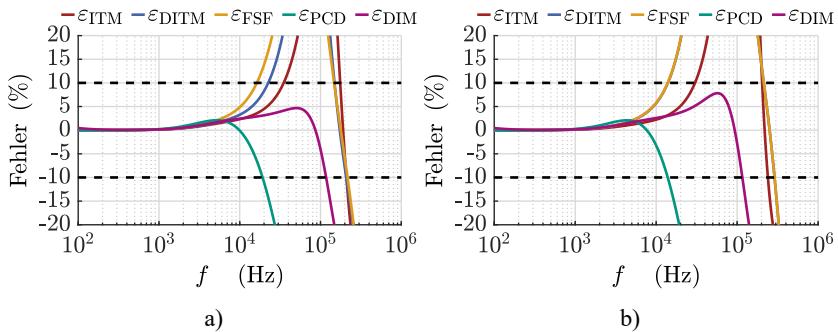

| 6.1.2    | Analyse der Genauigkeit und Bandbreite der<br>Netzemulation für verschiedene<br>Schnittstellenalgorithmen ..... | 168        |

| 6.1.3    | Umsetzung des Netzmodells auf dem SoC-System ....                                                               | 169        |

| 6.1.4    | Messtechnische Validierung des Netzmodells.....                                                                 | 174        |

| 6.2      | Nachbildung von Netzfehlern.....                                                                                | 176        |

| 6.2.1    | Spannungsfehlerfall .....                                                                                       | 176        |

| 6.2.2    | Harmonisch verzerrtes Netz und Frequenzfehler .....                                                             | 181        |

| 6.3      | Vermessung des frequenzabhängigen Verhaltens.....                                                               | 183        |

| 6.3.1    | Vermessung eines passiven DUTs .....                                                                            | 183        |

| 6.3.2    | Vermessung eines 2L-Umrichters mit LCL-<br>Netzfilter .....                                                     | 187        |

|                                                                                  |            |

|----------------------------------------------------------------------------------|------------|

| <b>7 Zusammenfassung .....</b>                                                   | <b>191</b> |

| <b>A Anhang.....</b>                                                             | <b>195</b> |

| A.1 Herleitung der Kenngrößen der drei Grundschaltungen .....                    | 195        |

| A.1.1 Emitterschaltung .....                                                     | 195        |

| A.1.2 Kollektorschaltung .....                                                   | 199        |

| A.1.3 Basisschaltung .....                                                       | 200        |

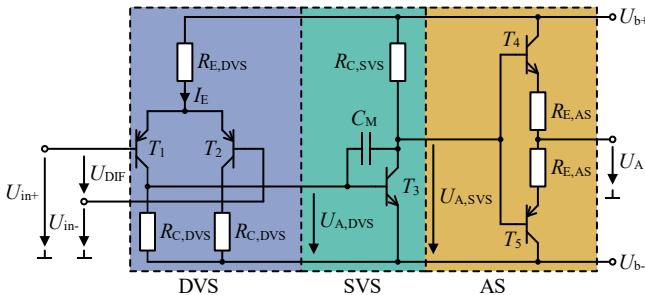

| A.2 Herleitung der Differenzverstärkerstufenkenngrößen .....                     | 203        |

| A.3 Herleitung der Ausgangsstufenkenngrößen .....                                | 206        |

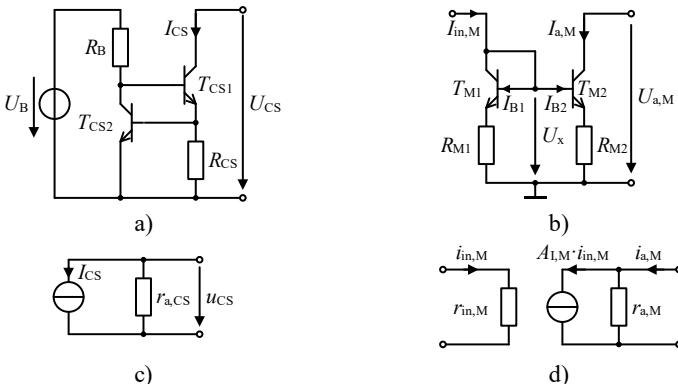

| A.4 Herleitung des Ausgangswiderstands der Stromquelle.....                      | 207        |

| A.5 Stromspiegel als Active Load .....                                           | 209        |

| A.6 Analyse der Kaskodenschaltung .....                                          | 216        |

| A.7 Analyse der Darlington-Schaltung.....                                        | 219        |

| A.8 Analyse der Triple Emitterfolger Ausgangsstufe .....                         | 222        |

| A.9 Herleitung der Umrichterimpedanz mittels Forward Return<br>Loop Methode..... | 227        |

| A.10 Beschreibung der verwendeten ETI-SoC-<br>Erweiterungskarten .....           | 230        |

| A.10.1 ADC-Karte.....                                                            | 230        |

| A.10.2 IO-Karte.....                                                             | 230        |

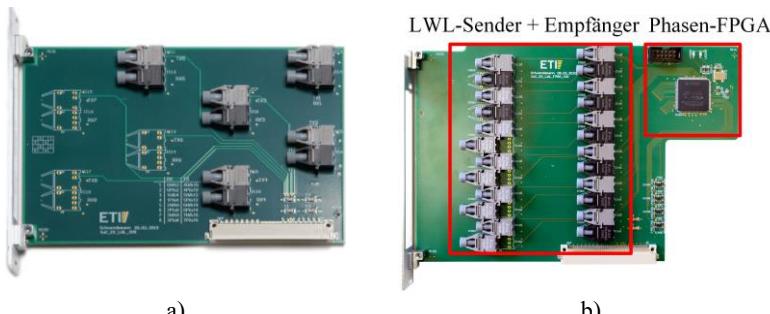

| A.10.3 LWL-Karte und Phasen-FPGA-Karte .....                                     | 231        |

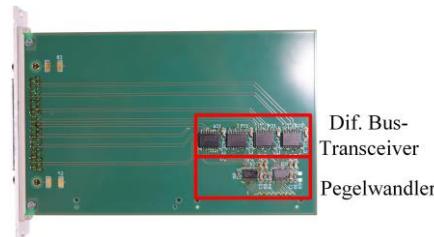

| A.10.4 Dig2Diff-Karte.....                                                       | 232        |

| <b>Symbolverzeichnis.....</b>                                                    | <b>233</b> |

| Abkürzungen.....                                                                 | 233        |

| Formelzeichen .....                                                              | 236        |

| <b>Abbildungsverzeichnis .....</b>                                               | <b>257</b> |

| <b>Tabellenverzeichnis .....</b>                                                 | <b>267</b> |

| <b>Literaturverzeichnis .....</b>                                                | <b>269</b> |

# 1

## Einleitung

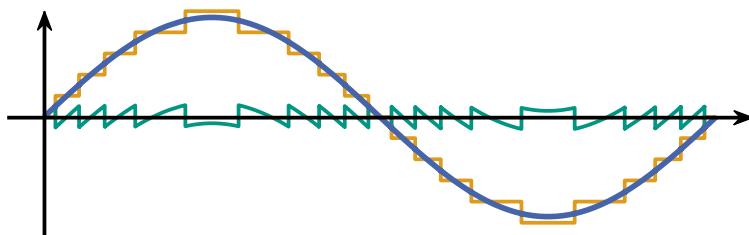

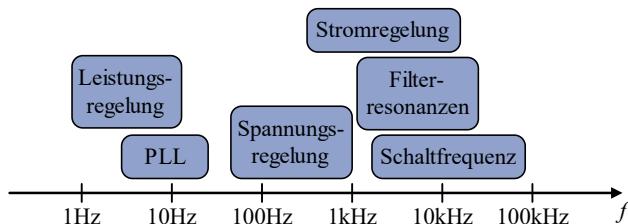

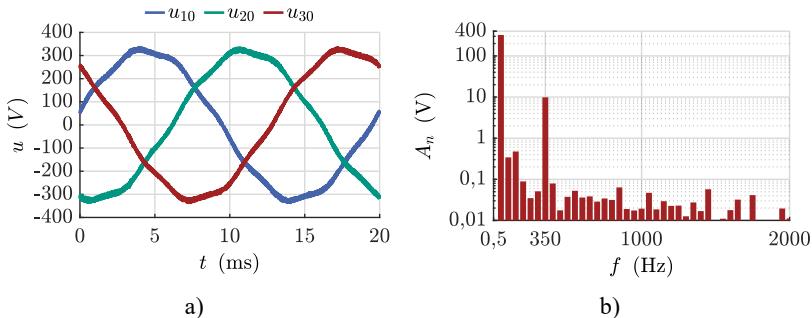

Aufgrund der zunehmenden dezentralen Energieerzeugung durch erneuerbare Energien und des Anstiegs von umrichtergespeisten Lasten nimmt die Durchdringung des Stromnetzes durch leistungselektronische (LE) Systeme stetig zu [1, 2]. Als Folge dieses Strukturwandels kommt es vermehrt zu Interaktionen zwischen den LE-Systemen in verschiedenen Anwendungen. Dazu gehören beispielsweise Oberschwingungen in Offshore-Windanlagen [3], Wechselwirkungen zwischen einzelnen Reglern paralleler Umrichtern untereinander oder mit ihren Netzfiltern [4], durch Schalthandlungen angeregte Resonanzen [5] bis hin zu instabilem Verhalten von Umrichtern in großen Photovoltaikanlagen [6]. Der jeweils wirksame Frequenzbereich dieser Phänomene hängt von den beteiligten Komponenten innerhalb der LE-Systeme ab. In Abbildung 1.1 sind die typischerweise in LE-Systemen auftretenden charakteristischen Frequenzbereiche dargestellt [7].

Abbildung 1.1: Charakteristische Frequenzbereiche der verschiedenen physikalischen Komponenten sowie Regelkreise eines LE-Systems

Es ist zu erkennen, dass die Frequenzbereiche der Phänomene, die durch die Stromregelung, Filterresonanzstellen oder Schalthandlungen hervorgerufen werden, bis in den hohen zweistelligen Kilohertzbereich reichen können.

Um das Auftreten dieser Phänomene zu vermeiden, sollten elektrische Betriebsmittel, insbesondere LE-Systeme, vor der Installation im Feld auf mögliche Interaktionen und instabiles Verhalten überprüft werden. Dafür ist ein leistungsfähiges Prüfsystem erforderlich, das in der Lage ist, die verschiedenen Netzsituationen zu emulieren und gleichzeitig das Verhalten der elektrischen Betriebsmittel in diesen Netzsituationen zu analysieren. Dabei stehen insbesondere Netzfehler im Fokus, ebenso wie transiente Spannungsschwankungen und -unterbrechungen, Netzunsymmetrien, harmonisch verzerrte Netzspannungen sowie instabile bzw. schwache Netze.

Des Weiteren muss das Prüfsystem auch in der Lage sein, das frequenzabhängige Klemmenverhalten des elektrischen Betriebsmittels, im Folgenden als Prüfling (DUT, engl.: *Device Under Test*) bezeichnet, zu analysieren. Dieses frequenzabhängige Klemmenverhalten wird auch als harmonische Impedanz bezeichnet. Die Kenntnis der harmonischen Impedanz des DUTs und des Netzausschlusspunkts NAPs, an dem der DUT später betrieben wird, ermöglicht es, mithilfe einer impedanzbasierten Stabilitätsanalyse zu überprüfen, ob ein stabiler Betrieb des DUTs in Verbindung mit dem NAP möglich ist [8]. Darüber ermöglicht die harmonische Impedanz die Vorhersage von Interaktionen des DUTs mit anderen elektrischen Betriebsmitteln.

Um die harmonische Impedanz zu bestimmen, muss das Prüfsystem Testsignale generieren. Diese Signale werden auf die gewünschte Ausgangsspannung, beispielsweise ein dreiphasiges 400 V-System, aufmoduliert. Anschließend wird die Reaktion des DUTs auf die Testsignale gemessen. Die höchste Genauigkeit wird dabei durch die Verwendung eines sinusförmigen Testsignals erzielt [9, 10].

Zur Nachbildung der unterschiedlichen Netzsituationen gibt es verschiedene Prüfsysteme basierend auf Transformatoren, Generatoren oder in Reihe geschaltete Impedanzen [11–13]. Diese Prüfsysteme weisen jedoch nicht die notwendige Flexibilität auf, um alle genannten Netzsituationen für verschiedene Parameter nachzubilden zu können. Des Weiteren sind sie auch nicht fähig, die benötigten sinusförmigen Testsignale auf die nachzubildende Netzspannung aufzumodulieren. Um alle geforderten Netzsituationen nachzubilden und die benötigten sinusförmigen Testsignale zu erzeugen, wird ein auf Leistungselektronik basierendes Prüfsystem benötigt, welches eine höhere Flexibilität

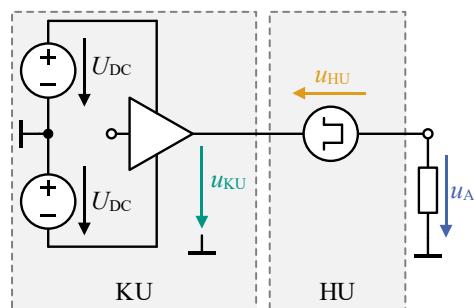

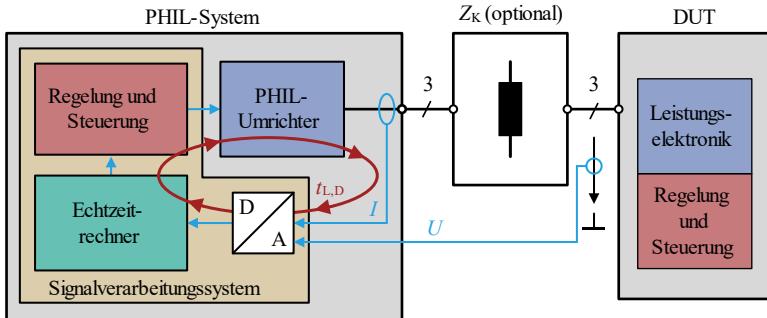

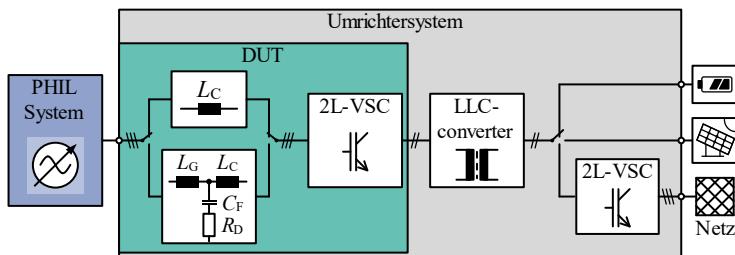

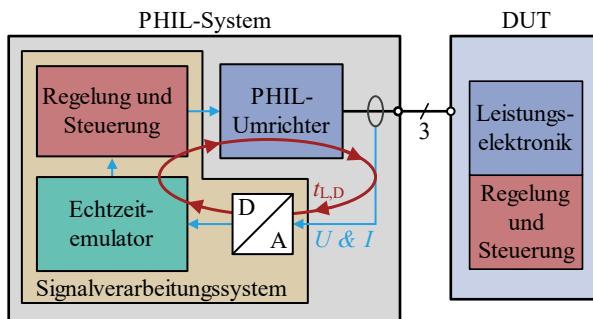

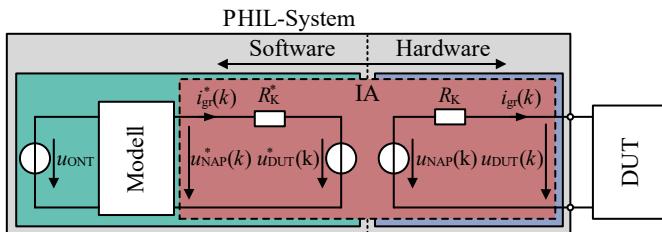

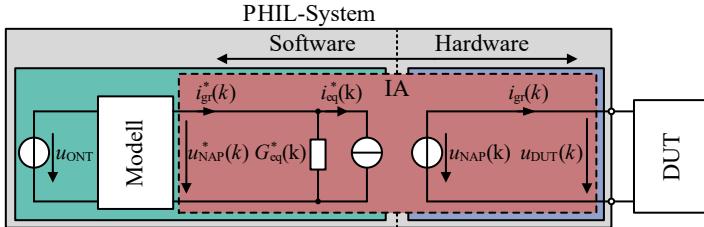

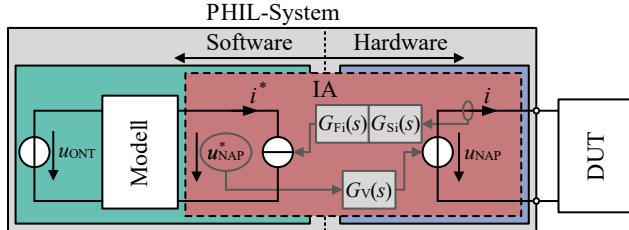

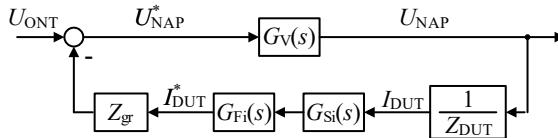

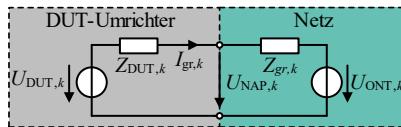

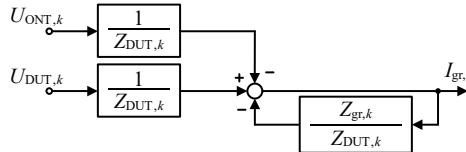

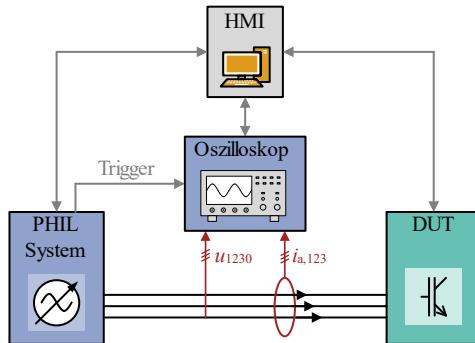

und einen höheren Funktionsumfang als die oben erwähnten Prüfsysteme aufweist [11, 13]. Das benötigte Verhalten wird dabei nicht durch die Veränderung der Hardware des Prüfsystems erreicht, sondern durch Änderung eines softwareseitigen Modells. Ein solches Prüfsystem wird als *Power Hardware-in-the-Loop* (PHIL)-System bezeichnet. Abbildung 1.2 zeigt die schematische Darstellung eines PHIL-Prüfstands.

Abbildung 1.2: Schematische Darstellung eines PHIL-Prüfstands

Im Echtzeitrechner des PHIL-Systems wird ein Modell mit dem nachzubildenden Verhalten berechnet. Hierzu werden abhängig von dem nachzubildenden Verhalten der Strom  $I$ , die Spannung  $U$  oder beide Werte des elektrischen DUTs gemessen. Die gemessenen Werte werden dem Echtzeitrechner für die Berechnung des Modells übergeben. Mithilfe des Modells werden Sollwerte für den PHIL-Umrichter generiert, die an die Regelung und Steuerung des PHIL-Umrichters übermittelt werden. Diese verarbeiten die Sollwerte entsprechend, sodass der PHIL-Umrichter die gewünschten Spannungs- oder Stromwerte an seinen Klemmen zur Verfügung stellt. Die eingezeichnete Koppelimpedanz  $Z_K$  zwischen PHIL-System und DUT wird nur benötigt, wenn das PHIL-System einen Ausgang mit Stromquellencharakteristik zur Verfügung stellen soll. Diese Art der Nachbildung der verschiedenen Netzsituationen wird als closed-loop-Emulation bezeichnet, da für die Berechnung des Klemmenverhaltens des PHIL-Systems im Echtzeitrechner das Verhalten des DUTs berücksichtigt wird. Mit einem solchen PHIL-Prüfstand können somit alle genannten Netzsituationen nachgebildet bzw. emuliert werden.

Aus den beschriebenen Prüfszenarien lassen sich mehrere Eigenschaften ableiten, die das PHIL-System aufweisen muss.

Für eine exakte Nachbildung von Netzfehlern bis in zweistelligen Kilohertz-

bereich wird ein hochdynamisches PHIL-System mit einer möglichst kurzen

Latenz  $t_{L,D}$  sowie einer möglichst hohen Bandbreite  $B_{PHIL}$  und Spannungsflan-

kensteilheit SR benötigt.

Das PHIL-System sollte in der Lage sein, die verschiedenen länderspezi-

fischen Niederspannungsnetze nachbilden zu können. Aufgrund der Varianz

erer Nennspannungen und Nennfrequenzen müssen sowohl Ausgangsspan-

nung als auch Ausgangsfrequenz des PHIL-Systems frei einstellbar sein.

Des Weiteren ist eine galvanische Trennung innerhalb des PHIL-Systems not-

wendig, sodass ein Betrieb auch für den Fall eines Potentialbezugs des DUTs

möglich ist. Eine exakte Nachbildung setzt zudem eine möglichst kleine Aus-

gangsimpedanz des PHIL-Systems voraus, damit der DUT keinen ungewollten

Einfluss auf die Ausgangsspannung des PHIL-Systems hat.

Aufgrund der zunehmenden Bedeutung von Gleichspannungsnetzen, die z.B.

bei größeren Ladeparks für E-Fahrzeuge verwendet werden, soll die Vermes-

sung eines DUTs sowohl für Wechselspannung (AC-Spannung) als auch für

Gleichspannung (DC-Spannung) möglich sein. Somit ist es erforderlich, dass

das PHIL-System neben der Erzeugung eines dreiphasiges Wechselspan-

nungssystems auch eine Gleichspannung am Ausgang zur Verfügung stellen

kann.

Bei der Bestimmung des frequenzabhängigen Klemmenverhaltens des DUTs

muss die Ausgangsspannung des PHIL-Systems zudem einen geringen Ober-

schwingungsgehalt (THD, engl.: Total Harmonic Distortion) aufweisen, um

das gemessene Klemmenverhalten nicht zu verfälschen.

Zur Erfüllung aller beschriebenen Eigenschaften und Anforderungen wird im

Rahmen dieser Arbeit ein neuartiges Konzept eines PHIL-Systems auf Basis

eines Serien-Hybrid-Umrichters entwickelt.

## 1.1 Stand der Technik

Zum besseren Verständnis der Arbeit wird nachfolgend der aktuelle Stand der

Technik von bereits existierenden PHIL-Systemen unter Betrachtung ihrer

Vor- und Nachteile diskutiert. Darauf aufbauend wird das Konzept der Hybrid-

Umrichter vorgestellt und mögliche Vorteile dieses Konzepts für die Anwen-

dung in einem PHIL-Prüfstand werden erläutert.

### 1.1.1 PHIL-Umrichter für Netzemulation

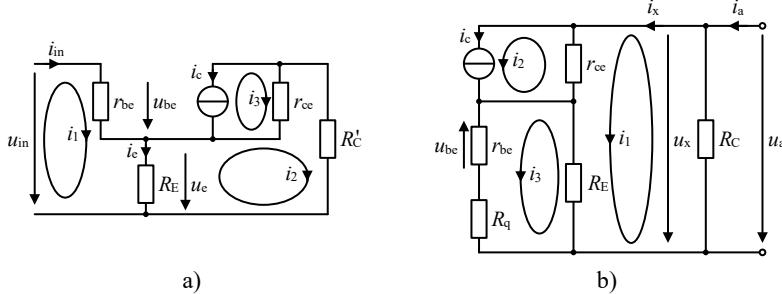

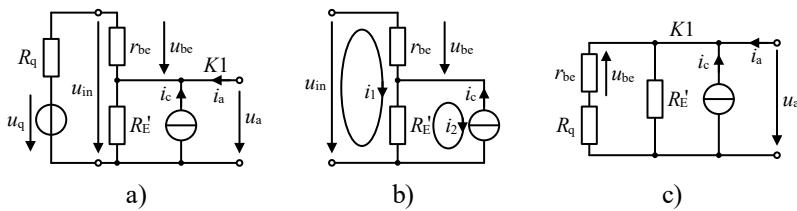

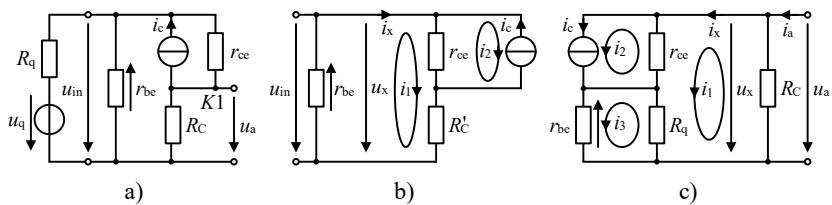

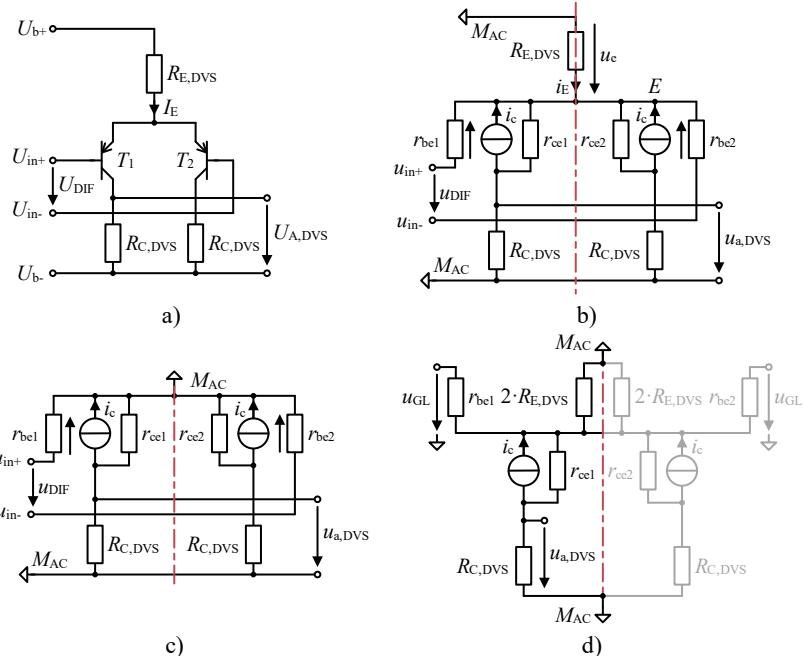

Existierende PHIL-Umrichter können in zwei Hauptkategorien unterteilt werden: taktende Umrichter und lineare Umrichter. Die jeweiligen spezifischen Eigenschaften dieser beiden Arten von Umrichtern führen bei deren Verwendung als Netzemulatoren zu unterschiedlichen Vor- und Nachteilen, die nachfolgend beleuchtet werden.

#### Taktende PHIL-Umrichter

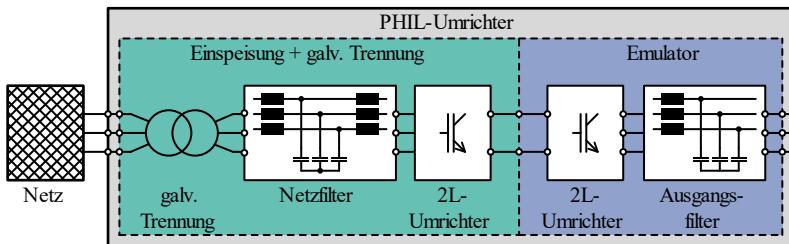

Bei den taktenden PHIL-Umrichtern existieren verschiedene Topologien. Im einfachsten Fall kann, wie in Abbildung 1.3 dargestellt, ein 2-Level (2L) Spannungswischenkreisumrichter (VSC, engl.: Voltage Source Converter) verwendet werden. Der PHIL-Umrichter lässt sich dabei in zwei Funktionsgruppen unterteilen: die Einspeisung inkl. galvanischer Trennung und der eigentliche Emulator, der die gewünschte Ausgangsspannung erzeugt. Die galvanische Trennung erfolgt meist mit einem 50 Hz Transformator auf der Einspeisungsseite.

In [14–17] werden auf 2L-VSC basierende PHIL-Umrichter als Netzemulatoren verwendet, um unsymmetrische Netze, Spannungseinbrüche oder Spannungsharmonische niedriger Ordnung nachzubilden.

Abbildung 1.3: PHIL-Umrichter auf Basis eines 2L-Umrichters

Der primäre Nachteil dieser PHIL-Umrichter besteht darin, dass das Ausgangsfilter aufgrund des hohen harmonischen Anteils in der Ausgangsspannung des 2L-VSC eine deutlich niedrigere Grenzfrequenz aufweisen muss, als die verwendete Schaltfrequenz  $f_{s,PHIL}$ , um eine Ausgangsspannung mit einem geringen Oberschwingungsgehalt zu erzeugen. Die in [14–17] verwendeten 2L-VSCs nutzen Si-basierte Bipolartransistoren mit isolierter Gate-Elektrode (IGBT, engl.: Insulated-Gate Bipolar Transistor) und weisen eine Schaltfrequenz  $f_{s,PHIL}$  von circa 10 kHz auf. Die dazugehörigen Ausgangsfilter haben

lediglich eine Grenzfrequenz von 260 Hz bis 900 Hz. Aufgrund dieser niedrigen Bandbreite und der damit verbundenen niedrigen Spannungssteilheit des Emulators sind weder eine hochdynamische Nachbildung eines Netzfehlers noch die Erzeugung von sinusförmigen Testsignalen im zweistelligen kHz-Bereich möglich. Selbst durch die Erhöhung der Schaltfrequenz auf 200 kHz durch die Verwendung von Siliziumcarbid-Metall-Oxid-Halbleiter-Feldeffekttransistoren (SiC-MOSFET, engl.: Metal Oxide Semiconductor Field-Effect Transistor), wie in [18, 19] dargestellt, liegt die erreichbare Klein-signalbandbreite maximal bei 2 kHz und ist somit ebenfalls unzureichend.

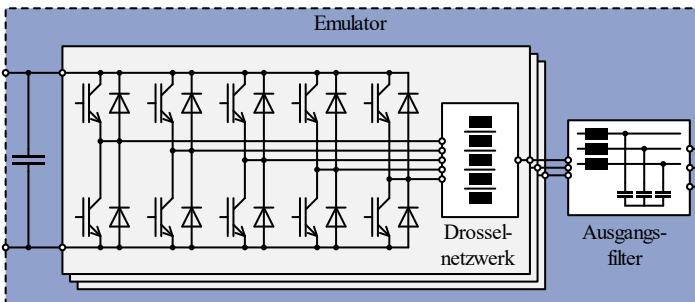

Eine Verbesserung der Bandbreite, der Spannungssteilheit und der Spannungsqualität wird durch die Verwendung von Multilevelumrichtern erreicht. Hierbei werden hauptsächlich die Modularen Multilevel Umrichter (MMC), die Kaskadierten H-Brücken (CHB) Umrichter sowie die sogenannten Modularen-Multiphasen-Multilevel Umrichter (MMPMC) verwendet. Letztere basieren auf parallelen Halbbrücken. In Abbildung 1.4 ist der Emulatorteil eines PHIL-Umrichters basierend auf einem MMPMC dargestellt.

Abbildung 1.4: Emulator basierend auf einem Multilevelumrichter aus mehreren parallelen Halbbrücken (MMPMC)

Mit Hilfe des Drosselnetzwerks, welches einen induktiven Spannungsteiler darstellt, können bei  $N$  parallelen Zweigen  $N + 1$  Ausgangsniveaus generiert werden. Um ein möglichst ideales Spannungsquellenverhalten zu erreichen, wird das Drosselnetzwerk mit gekoppelten Induktivitäten aufgebaut [20, 21]. Dadurch ist nur die Streuinduktivität als Ausgangsinduktivität wirksam. Die Topologie wird sowohl für die Emulation von Maschinen [21–23], als auch für die Emulation von Netzen verwendet [D1, 20]. Der Unterschied besteht darin, dass ein zusätzliches Ausgangsfilter nach dem Drosselnetzwerk für die Emulation von Netzen eingesetzt wird, um den Oberschwingungsgehalt der Ausgangsspannung zu reduzieren.

Dieses Konzept ermöglicht eine einfache Skalierung des Ausgangsstroms und somit auch der Ausgangsleistung des Systems durch die Parallelschaltung mehrerer Halbbrücken. Des Weiteren beträgt die Modulationsfrequenz der Ausgangsspannung im Idealfall das  $N$ -Fache der Schaltfrequenz einer Halbbrücke. Das in [D1] vorgestellte System erreicht dabei eine Modulationsfrequenz von circa 125 kHz mit einer maximalen Spannungsflankensteilheit von 12,6 V/ $\mu$ s und einer Kleinsignalbandbreite von 15 kHz. Die Latenz bei einer Sollwertänderung beträgt 28  $\mu$ s.

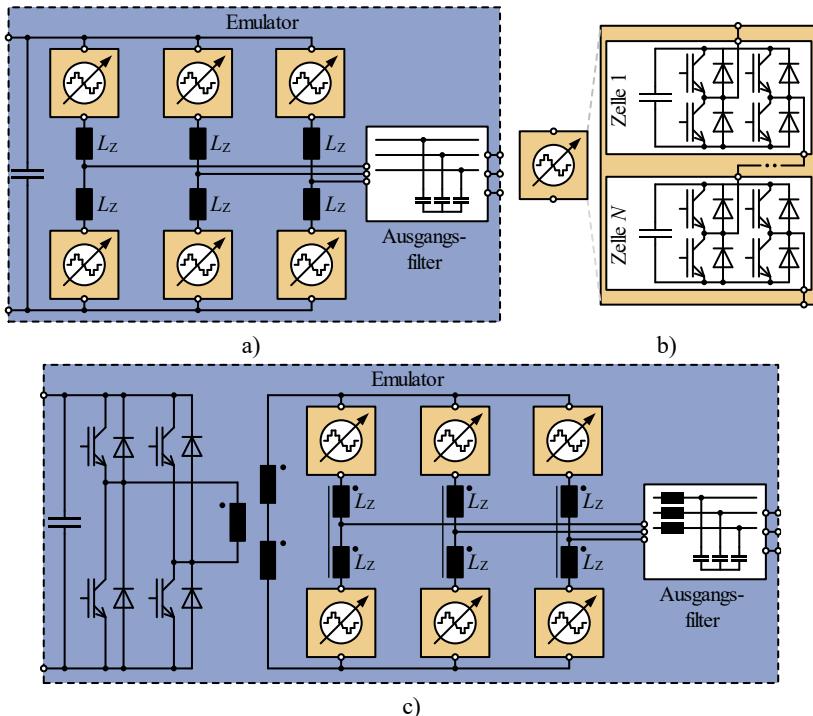

Abbildung 1.5 a) zeigt das Konzept eines Emulators basierend auf einem MMC. Im Gegensatz zum vorherigen System kann der MMC durch Hinzufügen zusätzlicher Zellen in der Spannung und somit in der Leistung skaliert werden. Er eignet sich daher auch als Emulator für höhere Spannungen. Es können  $2 \cdot N + 1$  Ausgangsspannungs niveaus generiert werden und die Modulationsfrequenz der Ausgangsspannung beträgt näherungsweise das  $N$ -Fache der Schaltfrequenz der Halbleiter. Dadurch ist wie beim MMPMC eine hohe Bandbreite und Dynamik am Ausgang erreichbar.

In [24, 25] wird ein Netzemulator auf Basis eines MMCs verwendet, um unsymmetrische Netzsituationen sowie Netzfehler zu emulieren. Dabei werden die in Abbildung 1.5 a) gezeigten Zweiginduktivitäten  $L_Z$  gleichzeitig als Filterinduktivität benutzt, weshalb das Ausgangsfilter nur noch aus einer Kapazität besteht.

In [26] wird ein MMC mit rechteckförmiger Einspeisung beschrieben, der so genannte SPMC (siehe Abbildung 1.5 c). Hier werden gekoppelte Induktivitäten als Zweiginduktivitäten  $L_Z$  verwendet, wodurch die Ausgangsimpedanz des MMCs klein ist. Des Weiteren erfolgt die Einspeisung über einen Mittelfrequenz-Transformator bei einer Frequenz von 1,25 kHz mit einer rechteckförmigen Spannung [27]. Dies bietet den Vorteil, dass kein 50 Hz Transformator zur galvanischen Trennung benötigt wird und der MMC ebenfalls zur Erzeugung von Gleichspannungen verwendet werden kann. Bei dem klassischen MMC wäre das aufgrund sehr großer Symmetrierungsströme nicht sinnvoll möglich [28]. Die Modulationsfrequenz der Ausgangsspannung dieses MMCs beträgt circa 120 kHz. Die erreichbare Dynamik und Bandbreite sind somit vergleichbar mit der des MMPMC.

Abbildung 1.5: a ) Emulator basierend auf einem Modularen Multilevel Umrichter (MMC); b) Zweig eines MMC; c) Emulator basierend auf einem Modularen Multilevel Umrichter mit rechteckförmiger Einspeisung (SPMMC)

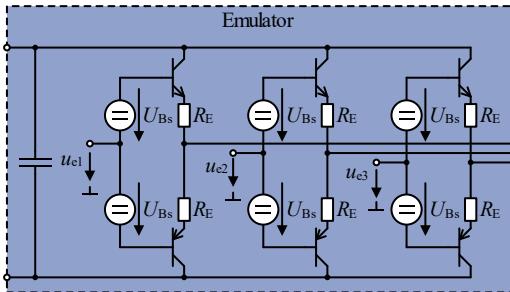

Neben dem MMC und MMPMC gibt es auch PHIL-Systeme, die auf einem CHB-Umrichter basieren. In Abbildung 1.6 ist die schematische Darstellung eines 1-phasigen CHB-Umrichters zu sehen, der z.B. in [29] beschrieben wird. Beim CHB-Umrichter erfolgt die galvanische Trennung entweder, wie in der Abbildung 1.6 dargestellt, durch einen 50 Hz Mehrwicklungstransformator oder in jeder Zelle separat durch einen galvanisch trennenden Gleichspannungswandler (DC/DC-Wandler), wie z.B. in [E1, 30].

Abbildung 1.6: PHIL-Umrichter basierend auf einem CHB-Umrichter

Der in [29] vorgestellte 1-phasige Prototyp besteht aus sechs Zellen und hat eine Leistung von 10 kW. Die erzielte Bandbreite und Spannungsflankensteilheit liegen mit 100 kHz bzw.  $50 \text{ V}/\mu\text{s}$  deutlich höher als die der bisherigen schaltenden PHIL-Systeme. Diese hohe Dynamik wird mit Hilfe einer sehr hohen Schaltfrequenz von 300 kHz pro Halbleiter bzw. einer effektiven Modulationsfrequenz von 3,6 MHz am Ausgang erreicht.

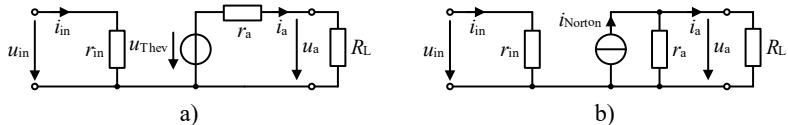

### Lineare PHIL-Umrichter

Neben den vorgestellten schaltenden PHIL-Umrichtern existieren auch lineare PHIL-Umrichter. Eine schematische Darstellung eines linearen Emulators, basierend auf einem Klasse AB-Verstärker, ist in Abbildung 1.7 dargestellt. Abhängig von der Polarität des Ausgangstroms leiten bei diesem linearen Emulator entweder die oberen oder die unteren Transistoren. Die Differenz zwischen der gewünschten Ausgangsspannung und der Zwischenkreisspannung fällt dabei über den Transistoren ab. Dies führt insbesondere für eine kapazitive oder induktive Last aufgrund des Phasenversatzes der Ausgangsspannung zum Ausgangsstrom zu sehr hohen Verlusten. Die höchste Verlustleistung tritt jedoch bei einem rückspeisenden DUT auf, da der Linearverstärker (LPA, engl.: Linear Power Amplifier) nicht rückspeisefähig ist und somit die gesamte rückzuspeisende Energie in Form von Verlusten innerhalb des LPAs abgeführt wird. Da dies ein wichtiger Betriebsmodus für einen Netzemulator darstellt, ist

die maximale Leistung eines linearen PHIL-Umrichters begrenzt [13]. Des Weiteren führen die hohen Verluste zu sehr großen Systemen mit geringer Leistungsdichte und den höchsten Kosten pro Watt [13].

Die Vorteile von linearen PHIL-Umrichtern sind ihre hohe Bandbreite und Spannungssteilheit sowie der geringe Oberschwingungsgehalt ihrer Ausgangsspannung und ihre geringe Latenz [31]. So erreicht der in [D2] vorgestellte lineare Umrichter eine Bandbreite von 50 kHz und eine Flankensteilheit von 52 V/ $\mu$ s bei einem maximalen Klirrfaktor von 0,2 % für eine Ausgangsspannung von 240 V. Des Weiteren benötigen lineare PHIL-Umrichter keinen Ausgangsfilter, wodurch die Rückwirkung der Last auf die Ausgangsspannung des PHIL-Umrichters geringer ausfällt als bei schaltenden PHIL-Umrichtern.

Abbildung 1.7: Schematische Darstellung eines Emulators basierend auf einem Linearverstärker

### Vergleich von schaltenden und linearen PHIL-Umrichtern

Die schaltenden PHIL-Umrichter auf Basis von Multilevelumrichtern zeichnen sich durch ihre einfache Skalierbarkeit aus. Hierdurch können Systeme bis in den Megawattbereich sowie bis in einen zweistelligen Kilovoltbereich konstruiert werden [32, 33]. Des Weiteren weisen sie einen deutlich höheren Wirkungsgrad sowie eine höhere Leistungsdichte verglichen mit linearen PHIL-Umrichtern auf. Ein weiterer großer Vorteil, insbesondere für Netzemulatoren, gegenüber linearen Systemen besteht in der Rückspeisefähigkeit von schaltenden PHIL-Umrichtern.

Lineare Systeme bieten den Vorteil, dass sie deutlich höhere Bandbreiten, größere Spannungsflankensteilheiten sowie geringere Latenzen und einen niedrigeren Oberschwingungsgehalt erreichen [31]. Es ist jedoch zu beachten, dass durch immer höhere Schaltfrequenzen bei schaltenden PHIL-Systemen sich der Ausgangsfilter reduziert. Dadurch nähern sich die Bandbreite und

Spannungsflankensteilheit dieser Systeme zunehmend denen linearer Systeme an. So weist der in [29] vorgestellte schaltende PHIL-Umrichter eine ähnliche Bandbreite und Spannungsflankensteilheit wie bereits vorhandene lineare Systeme auf. Der inhärente Nachteil von schaltenden PHIL-Systemen eines notwendigen Ausgangsfilters besteht jedoch auch bei diesem System. Dadurch besitzt der PHIL-Umrichter eine große Ausgangsimpedanz bei der Eigenfrequenz des Ausgangsfilters und es entsteht eine ungewollte Rückwirkung des DUTs auf die Ausgangsspannung des PHIL-Umrichters [30]. Dies ist vor allem bei der Emulation von Netzfehlern von Nachteil, da in diesem Fall dynamische Spannungssprünge generiert werden, die durch die Rückwirkung des DUTs auf die Ausgangsspannung des PHIL-Umrichters verfälscht werden.

Im Allgemeinen lässt sich festhalten, dass ein linearer PHIL-Umrichter zwar eine dynamischere und geringer verzerrte Ausgangsspannung als ein schaltender PHIL-Umrichter erzeugen kann, gleichzeitig aber teurer ist, eine geringere Leistungsdichte aufweist und in seiner Ausgangsleistung begrenzt ist.

### 1.1.2 Hybride Umrichterkonzepte

Ein Hybridumrichter besteht aus zwei Teilumrichtern: einem Hauptumrichter (HU), der den größten Teil der Ausgangsleistung bereitstellt, und einem Korrekturmrichter (KU), der die Verzerrungen des Hauptumrichters kompensiert [34: S. 162ff]. Abhängig von der Wahl der verwendeten Teilumrichter kann zwischen einem rein schaltenden Hybridumrichter, bei dem zwei schaltende Umrichter kombiniert werden, und dem klassischen Hybridumrichter, bei dem ein schaltender Umrichter mit einem LPA kombiniert wird, unterschieden werden. Neben dieser Unterscheidung existiert zudem eine Klassifizierung hinsichtlich der Verschaltungart der beiden Teilumrichter. Hierbei kann zwischen drei hybriden Schaltungskonzepten unterschieden werden: der Parallel Hybrid Converter (PHC), der Series Hybrid Converter (SHC) und der Envelope Hybrid Converter (EHC) [35: S. 20ff].

#### Parallel Hybrid Converter (PHC)

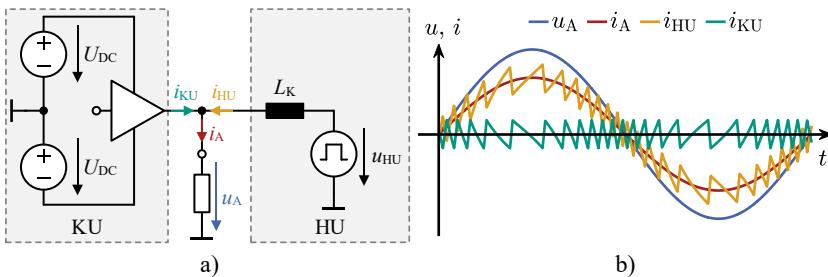

Das Konzept des PHCs ist in Abbildung 1.8 a) und die dazugehörigen Strom- und Spannungsverläufe sind in Abbildung 1.8 b) dargestellt. Der Korrekturmrichter ist parallel zum HU angeordnet. Der Ausgangstrom  $i_A$  entspricht der Summe des Ausgangstroms des KUs  $i_{KU}$  und des HUs  $i_{HU}$ . Beide Umrichter müssen für die gesamte Ausgangsspannung  $u_A$  ausgelegt sein. Der KU arbeitet beim PHC als Spannungsquelle und definiert die Ausgangsspannung

des gesamten Hybridumrichters  $u_A$ . Dadurch wird der HU von der Last entkoppelt. Dies führt zu zwei Vorteilen von Hybridumrichtern, die unabhängig davon gelten, ob ein PHC, EHC oder SHC betrachtet wird. Zum einen kann für die Auslegung der Regelung des HUs die Last vernachlässigt werden. Zum anderen definiert der KU die Ausgangsimpedanz des Hybridumrichters, weshalb für das Kleinsignalverhalten lediglich die Charakteristik des KUs betrachtet werden muss.

Abbildung 1.8: Parallel Hybrid Converter (PHC): a) Ersatzschaltbild, b) Strom- und Spannungsverläufe

Der HU ist stromgeregt und sieht die vom KU erzeugte Spannung als Gegenspannung. Der HU übernimmt den größten Teil des Ausgangsstroms  $i_A$ , sodass der KU nur den Verzerrungsblindstrom des HUs zur Verfügung stellen muss [E2, E3, 36]. Dies gilt jedoch nicht in allen Betriebsfällen, sodass eine Fallunterscheidung zwischen Groß- und Kleinsignalfall sowie zwischen Strom- und Spannungsverhalten durchgeführt werden muss. Für das Ausgangsspannungsverhalten definiert der KU sowohl im Klein- als auch im Großsignalfall das Verhalten des PHIL-Umrichterausgangs. Da der KU jedoch nicht für den gesamten Ausgangsstrom ausgelegt ist, muss beachtet werden, dass die Dynamik des HUs für den Großsignalfall des Ausgangsstroms entscheidend ist [E4]. Die Dynamik des HUs ist beim PHC geringer, da dieser möglichst effizient und mit einer hohen Leistungsdichte aufgebaut wird. Dies kann bei einem dynamischen Lastwechsel dazu führen, dass der KU im Extremfall bis zum doppelten Nennstrom führen muss [36, 37] bzw. in einem Fehlerfall der gesamte Fehlerstrom über den KU fließt, was zur Zerstörung des KUs führen kann.

In [37] wird der erste Aufbau eines parallelen Hybridumrichters mit einer Leistung von 100 W, einer Ausgangsspannung von 20 V und einer Grenzfrequenz von etwa 100 kHz vorgestellt. Weitere Systeme mit geringerer Leistung werden in [38, 39] erwähnt. Zudem wird in [40] ein System mit 1 kW und einer

Bandbreite von 10 kHz beschrieben. Alle Aufbauten sind dabei als 1-phasiger Prototyp konzipiert.

In [E4, E5, 41] wird der Aufbau des ersten 3-phasigen, schaltenden PHC beschrieben. Dabei werden ein 2L-VSC als HU und ein CHB-Umrichter mit 17 Ausgangsspannungsniveaus als KU verwendet. Das System wird als Maschinenemulator mit einer Ausgangsleistung von 50 kVA und einer Schaltfrequenz des KUs von circa 500 kHz und des HUs von circa 10 kHz eingesetzt.

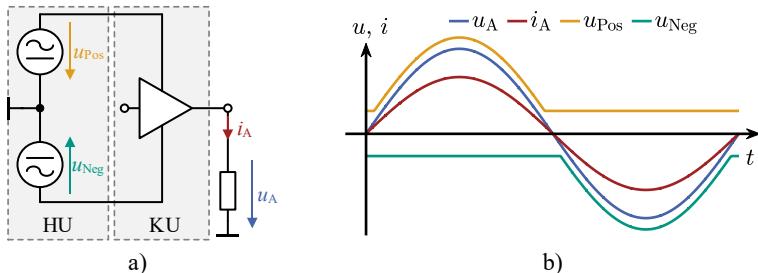

### **Envelope Hybrid Converter (EHC)**

Beim EHC stellt der HU eine variable Versorgungsspannung, bestehend aus  $u_{\text{Neg}}$  und  $u_{\text{Pos}}$ , für den KU zur Verfügung. Wie in Abbildung 1.9 zu sehen ist, wird die Versorgungsspannung so geregelt, dass sie die gewünschte Ausgangsspannung umhüllt. Hierdurch werden der Spannungsabfall über dem KU minimiert und die Verluste reduziert. Da die Versorgungsspannung der Ausgangsspannung  $u_A$  folgen muss, muss neben dem KU auch der HU eine sehr hohe Dynamik besitzen. Entsprechend wird der HU mit einer sehr hohen Schaltfrequenz betrieben [36]. Der KU liefert beim EHC den gesamten Ausgangstrom  $i_A$ . Des Weiteren wird bei der Auslegung des KUs vorausgesetzt, dass dieser die gesamte Ausgangsspannung  $u_A$  sperren muss [30].

Der EHC wird für Systeme kleinerer Leistung eingesetzt, beispielsweise im Bereich von batteriebetriebenen Anwendungen, um deren Laufzeit zu verlängern oder als Verstärker für piezoelektrische Sensoren [29, 36]. Die Leistung liegt im Bereich von 0,2 bis 50 W [42–45]. Neben diesen Anwendungen gibt es auch Untersuchungen mit höheren Leistungen. So wird in [46, 47] ein 500 W EHC mit einer Ausgangsspannung von 60 V und einer maximal getesteten Ausgangsfrequenz von 2,5 kHz bei einer Schaltfrequenz des HU von 200 kHz vorgestellt. [35, 48, 49] beschreiben einen 1 kW EHC mit einer Ausgangsspannung von 115 V und einer maximal getesteten Ausgangsfrequenz von 1 kHz bei einer Schaltfrequenz des HUs von 100 kHz. Alle Systeme sind als 1-phasiger Prototyp aufgebaut.

Abbildung 1.9: Envelope Hybrid Converter (EHC): a) Ersatzschaltbild, b) Strom- und Spannungsverläufe

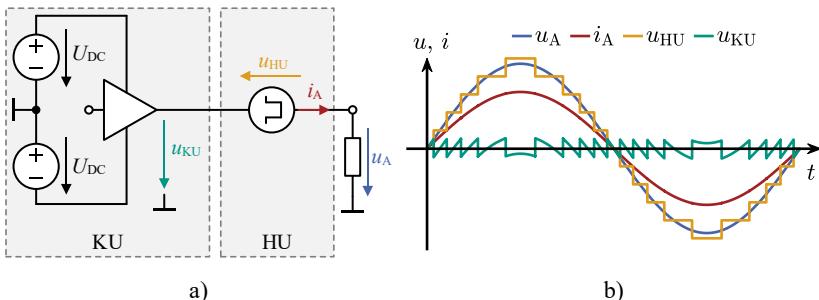

### Series Hybrid Converter (SHC)

Das grundlegende Schaltungskonzept des SHCs ist in Abbildung 1.10 a) dargestellt. Beim SHC ist der KU in Serie zum Hauptumrichter geschaltet. Beide Umrichter müssen in der Lage sein, den gesamten Ausgangstrom  $i_A$  zu führen. Die Ausgangsspannung  $u_A$  entspricht der Summe beider Teilspannungen  $u_{HU}$  und  $u_{KU}$ , wie in Abbildung 1.10 b) zu sehen ist. Der größte Teil der Ausgangsspannung wird dabei vom HU gestellt. Der KU muss die Differenz zwischen der gewünschten Ausgangsspannung  $u_A$  und der Spannung des HU  $u_{HU}$  zur Verfügung stellen und kann deshalb für eine kleinere Spannung als die Ausgangsspannung  $u_A$  ausgelegt werden. Hinsichtlich der erreichbaren Dynamik muss eine Fallunterscheidung durchgeführt werden. So wird das Kleinsignalverhalten des SHCs durch den KU bestimmt. Für das Großsignalverhalten ist hingegen die Charakteristik des HUs entscheidend, da der KU nur für einen kleinen Teil der gesamten Ausgangsspannung  $u_A$  ausgelegt wird.

Abbildung 1.10: Series Hybrid Converter (SHC): a) Ersatzschaltbild, b) Strom- und Spannungsverläufe

Die häufigste Anwendung für das Konzept des SHCs sind DC-Laborversorgungen. Dabei besteht das Ziel darin den Spannungsripple des schaltenden HUs zu kompensieren, um eine möglichst glatte DC-Spannung zu erzeugen [34: S. 273].

Neben dieser Anwendung wurden mehrere einphasige Prototypen zur Erzeugung einer dynamischen Wechselspannung mit geringem Oberschwingungsgehalt entwickelt. Eine Übersicht der entwickelten einphasigen SHC ist in Tabelle 1.1 zu finden.

Tabelle 1.1: Übersicht der entwickelten einphasigen SHCs

| Referenz | Leistung | Spannung | Bandbreite |

|----------|----------|----------|------------|

| [36, 50] | 500 W    | 155 V    | 1,2 kHz    |

| [30, 35] | 1000 W   | 270 V    | 10 kHz     |

| [51, 52] | 1000 W   | 311 V    | 400 Hz     |

| [53]     | 5000 W   | 180 V    | 1,5 kHz    |

Neben diesen klassischen SHCs wurden auch rein schaltende SHCs aufgebaut. Dabei gibt es zwei verschiedenen Topologien. Bei der ersten Topologie wird ein schnell taktender KU, typischerweise eine H-Brücke, direkt in Serie zum HU eingefügt. Neben einer theoretischen Analyse dieses Konzepts in [20, 54–56] erfolgt in [35, 57] auch eine experimentelle Validierung.

Bei der zweiten Topologie des rein schaltenden SHCs wird der KU über einen Transformator zwischen HU und Ausgang eingefügt. Dieses Prinzip wird verwendet, um ein 2 MW-System zur Emulation eines Niederspannungsnetzes mit einer Ausgangsspannung von 325 V aufzubauen [58]. Die Schaltfrequenz des HUs beträgt 2,5 kHz und die des KUs 8 kHz.

### Gegenüberstellung der hybriden Umrichterkonzepte hinsichtlich der Eignung als Netzemulator

Der EHC hat den Vorteil, dass ausschließlich der LPA die Ausgangsspannung definiert. Hierdurch kann theoretisch eine hochdynamische Ausgangsspannung mit einem geringen Oberschwingungsgehalt erzeugt werden, was für die Emulation von Netzen und Netzfehlern notwendig ist. Dabei ist zu berücksichtigen, dass hierzu die Dynamik der Versorgungsspannung ähnlich der des LPAs sein muss. Dafür sind hohe Schaltfrequenzen notwendig [36], was dem hybriden Konzept widerspricht, einen langsameren HU mit hoher

Leistungsdichte und hohem Wirkungsgrad mit einem hochdynamischen KU zu kombinieren. Problematisch an der Verwendung eines EHCs als PHIL-System ist zudem, dass die Bauteile des LPAs für die gesamte Ausgangsspannung sowie für den gesamten Ausgangstrom ausgelegt sein müssen. Dies erschwert eine Dimensionierung des LPAs für einen Netzemulator mit hoher Leistung und Spannung aufgrund der Bauteilauswahl [35: S. 74, 36, 59].

Beim klassischen PHC sowie beim rein schaltenden PHC wird der Ausgang, genau wie beim EHC, durch den KU bestimmt. Dadurch kann ebenfalls eine hochdynamische Spannungsquelle mit geringen Oberschwingungsgehalt generiert werden [36]. Aufgrund der parallelen Struktur ist es allerdings möglich, dass Störimpulse des HUs nicht vom KU kompensiert werden können und folglich die Ausgangsspannung gestört wird [30]. Ein weiteres Problem des klassischen PHCs besteht wie beim EHC darin, dass der LPA für die gesamte Ausgangsspannung ausgelegt werden muss. Das ist aufgrund der vorhandenen Bauteilauswahl bei den benötigten Spannungen problematisch [36].

Zusätzlich muss der KU beim PHC bei dynamischen Sollwertänderungen, wie z.B. bei den zu emulierenden Netzfehlern, die gesamte Leistung des System zur Verfügung stellen [36, 37]. Dies führt zu einer Überdimensionierung des KUs und widerspricht damit der Nutzung eines PHCs für die vorhandene Anwendung. Des Weiteren müssen für mögliche Überstromszenarien, die z.B. durch den DUT in einem dynamischen Netzfehlerfall erzeugt werden, zusätzliche Schutzorgane installiert werden. Diese Schutzorgane müssen den KU vor der Zerstörung schützen, da der PHC in seiner Grundstruktur dazu nicht in der Lage ist. Aus diesen genannten Gründen wird die Verwendung eines PHCs (klassisch und rein schaltend) für die angestrebte Anwendung nicht in Betracht gezogen.

Beim SHC ist der Schutz vor einem Überstromszenario durch die Verschaltung des HUs in Serie zum KU gewährleistet, da der HU den KU vom DUT trennen kann. Durch die Verwendung eines Multilevelumrichters als HU kann die Versorgungsspannung des LPAs beim klassischen SHC entsprechend reduziert werden, wodurch die Verluste des LPAs den Systemwirkungsgrad nur noch geringfügig beeinflussen [29]. Des Weiteren ist eine Überdimensionierung des LPAs wie beim PHC nicht notwendig, da die Versorgungsspannung des LPAs beim SHC festgelegt wird und auch in dynamischen Betriebsfällen eine Überlastung des LPAs ausgeschlossen wird. Dies führt jedoch dazu, dass die Dynamik des HUs beim SHC für einen Großsignalsprung der Ausgangsspannung bestimmend ist, da der LPA nur einen kleinen Teil der Großsignaländerung

beisteuern kann. Aufgrund dieser Einschränkung muss der SHC die entsprechende Dynamik bereitstellen, um die nachzubildenden dynamischen Netzfehlerfälle zu erzeugen.

Die weitaus größere Bandbreite wird jedoch für die Erzeugung der sinusförmigen Spannungstestsignale zur Analyse des frequenzabhängigen Klemmenverhaltens des DUTs benötigt. Da diese Testsignale jedoch Kleinsignale sind [60, 61] und somit im einstelligen Prozentbereich der Gesamtausgangsspannung liegen, muss bei der Dimensionierung des LPAs nur garantiert werden, dass er diesen Spannungsbereich abdeckt. Somit können seine hohe Bandbreite und Dynamik für die Messung genutzt werden.

Im Vergleich zum schaltenden SHC weist der klassische SHC eine höhere Bandbreite und Dynamik sowie eine geringere Ausgangsimpedanz und einen niedrigeren Oberschwingungsgehalt auf [30, 35: S. 199ff]. Aus diesen Gründen wird das Konzept des klassischen SHCs für das zu entwickelnde PHIL-System weiterverfolgt.

## 1.2 Zielsetzung der Arbeit

Im Rahmen dieser Arbeit soll ein hochdynamischer PHIL-Prüfstand entwickelt, aufgebaut und betrieben werden, der als Netzemulator fungiert, um das Verhalten eines DUTs unter verschiedenen Netzsituationen zu analysieren. Besonderes Augenmerk liegt hierbei auf der Analyse des Verhaltens bei möglichen Netzanomalien, wie z.B. harmonisch verzerrte oder unsymmetrische Netzspannungen, Spannungseinbrüche oder -erhöhungen sowie schwache bzw. instabile Netzanschlusspunkte. Zur Analyse des DUTs soll der entwickelte PHIL-Prüfstand zudem in der Lage sein, sinusförmige Spannungstestsignale zu generieren. Die Analyse soll dabei sowohl für DUTs mit Wechselspannungs- als auch mit Gleichspannungsanschluss möglich sein. Folglich muss der PHIL-Prüfstand sowohl ein Wechsel- als auch ein Gleichspannungssystem generieren können. Aufgrund der zunehmenden Schaltfrequenz der DUTs und der damit auch höheren Bandbreite, muss das PHIL-System auch eine höhere Dynamik und Bandbreite bei einer geringeren Latenz erzielen, als dies mit bereits vorhandenen PHIL-Systemen möglich ist.

Als Basistopologie für dieses PHIL-System wird ein SHC verwendet, da mit diesem, wie in Kapitel 1.1 beschrieben, gute Resultate mit einphasigen Prototypen kleiner Leistungen erzielt wurden und die inhärenten Eigenschaften des

SHCs vorteilhaft für die vorhandene Anwendung sind, insbesondere für die Erzeugung sinusförmiger Testsignale.

Das zu entwickelnde PHIL-System soll eine Analyse von Netzumrichtern, die am europäischen Niederspannungsnetz angeschlossen werden, sowohl auf der AC- als auch DC-Seite ermöglichen. Hierzu muss das PHIL-System in der Lage sein, das dreiphasige, europäische Niederspannungssystem mit einer Nennspannung von  $400\text{ V} \pm 10\%$  bereitzustellen. Des Weiteren sollen Netzteilnehmer mit einer Leistung von bis zu 50 kVA getestet werden. Das für die Analyse des frequenzabhängigen Verhaltens eines DUTs verwendete sinusförmige Testsignal soll eine Amplitude von mindestens 10 % der Nennspannung von 400 V bei einer Frequenz von bis zu 100 kHz besitzen. Die Latenz des PHIL-Systems bei einer closed-loop-Emulation soll kleiner als 1  $\mu\text{s}$  sein.

Bei der Verwendung des SHCs für diese Leistung liegt ein besonderes Augenmerk auf den verwendeten LPA, da sie eine hohe Verlustleistung generieren und sie für die Leistungsfähigkeit des SHCs maßgeblich sind [30]. Folglich muss für den LPA ebenfalls ein neuartiges Konzept entwickelt werden, da kommerziell verfügbare LPA die geforderten Eigenschaften nicht erfüllen, um einen Serien-Hybrid-Umrichter mit den genannten Leistungsdaten aufbauen zu können.

## 1.3 Gliederung der Arbeit

In der vorliegenden Dissertation wird in Kapitel 2 die Topologie und das Konzept des verwendeten Serien-Hybrid-Umrichters vorgestellt, dem Series Hybrid Cascaded H-Bridge (SHCHB) Umrichter. Daran anschließend werden die Signalverarbeitungs- und Softwarestruktur sowie die Betriebsführung des SHCHB-Umrichters als PHIL-Umrichter beschrieben. Es folgt eine detaillierte Untersuchung der drei Hauptkomponenten des Leistungspfads. Die Hauptkomponenten sind die CHB-Zellen, die Spannungssteilheitsfilter ( $du/dt$ -Filter) und die LPAs. Um die Anforderungen, die an den LPA als Teil des SHCHB-Umrichters gestellt werden, bestmöglichst zu erfüllen, wird für den LPA ein neues Linearverstärkerkonzept entwickelt.

In Kapitel 3 folgt die Beschreibung der praktischen Umsetzung des SHCHB-Umrichters sowie die Verifizierung der in Kapitel 2 hergeleiteten analytischen Beschreibungsformen. Des Weiteren erfolgt eine Charakterisierung der entwickelten Hardware. Hierbei werden sowohl quasistationäre als auch dynamische Messungen durchgeführt. Anhand dieser Messungen kann die

Leistungsfähigkeit des PHIL-Systems basierend auf dem SHCHB-Umrichter validiert werden.

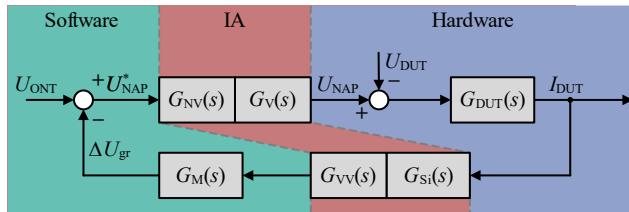

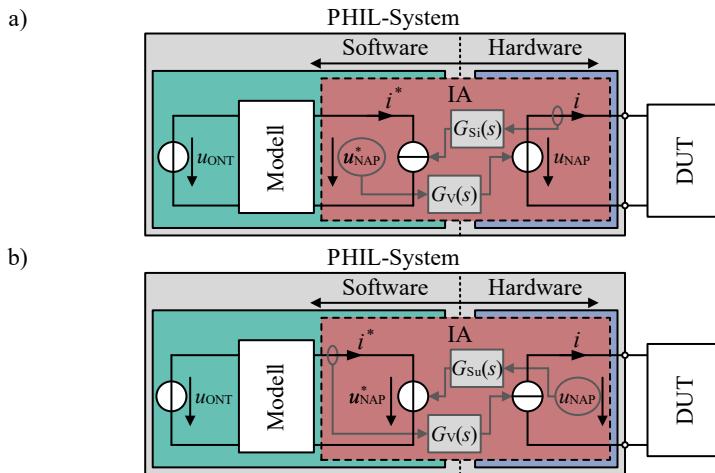

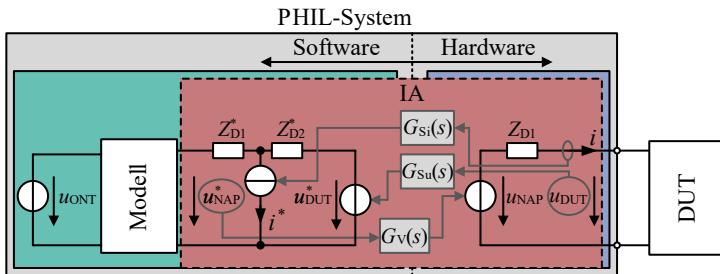

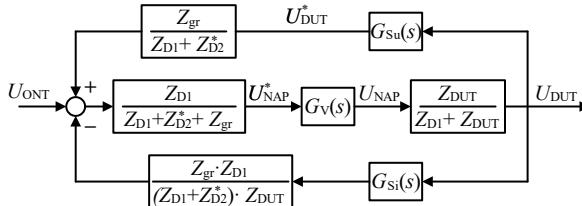

In Kapitel 4 erfolgt die analytische Betrachtung der closed-loop-Emulation unter Verwendung des SHCHB-Umrichters. Hierzu werden die korrespondierenden Übertragungsfunktionen der entwickelten Hardware hergeleitet. Des Weiteren wird der Einfluss von verschiedenen Schnittstellenalgorithmen (IA, engl.: Interface Algorithm) auf Stabilität und Genauigkeit der closed-loop-Emulation betrachtet. Abschließend werden mögliche Bewertungskriterien vorgestellt, anhand derer eine Gegenüberstellung der verschiedenen IAs erfolgt.

Neben der closed-loop-Emulation wird das entwickelte PHIL-System auch zur Analyse des frequenzabhängigen Verhaltens eines DUTs verwendet. Dieses Verhalten wird auch als harmonische Impedanz des DUTs bezeichnet. In Kapitel 5 werden die Grundlagen der impedanzbasierten Stabilitätsuntersuchung erläutert und das entwickelte Messverfahren zur Bestimmung der harmonischen Impedanz eines DUTs beschrieben. Zusätzlich wird ein analytisches Modell eines DUT-Umrichters hergeleitet, um dessen harmonische Impedanz zu berechnen.

Daran anschließend werden in Kapitel 6 die verschiedenen Prüfszenarien betrachtet, für die der SHCHB-Umrichter konzeptioniert ist. Hierzu zählen die closed-loop-Emulation eines Netzanschlusspunktes und die Nachbildung verschiedener Netzfehlerfälle. Des Weiteren wird das entwickelte Messverfahren zur Bestimmung der harmonischen Impedanz anhand von Messungen validiert.

Abschließend fasst das Kapitel 7 die Ergebnisse der vorliegenden Arbeit über den SHCHB-Umrichter als Vermessungs- und PHIL-System zusammen. Zudem wird anhand der gewonnenen Erkenntnisse ein Ausblick auf zukünftige Forschungs- und Anwendungsmöglichkeiten gegeben.

# 2

## Konzeptionierung und Dimensionierung des PHIL-Systems

Im folgenden Kapitel wird das Konzept des entwickelten PHIL-Systems zur Netzemulation auf Basis eines Serien-Hybrid-Umrichters (SHC) erläutert. Zunächst erfolgt eine Analyse der Leistungselektronikstruktur und die Auswahl der Topologie des schaltenden HUs. Anschließend werden die Signalverarbeitungs- und Softwarestruktur sowie die Betriebsführung des Serien-Hybrid-Umrichters als Emulator erörtert. Eine detaillierte Untersuchung der einzelnen Teilkomponenten, bestehend aus dem HU, dem Spannungssteilheitsfilter und dem KU, schließt sich an. Dabei wird ein neues Konzept eines Linearverstärkers für den KU entwickelt.

### 2.1 PHIL-Systemkonzept

PHIL-Systeme bestehen grundsätzlich aus drei Hauptkomponenten: der Leistungselektronik, der Signalverarbeitung und der Software [E6]. Für eine performante closed-loop-Emulation ist ein PHIL-System mit niedriger Latenz  $t_{L,D}$  und hoher Bandbreite  $B_{PHIL}$  erforderlich. Um dies zu erreichen, sind alle drei Komponenten von Bedeutung. Aus diesem Grund werden nachfolgend die Leistungselektronik-, die Signalverarbeitungs- sowie die Softwarestruktur näher analysiert.

## 2.1.1 Leistungselektronikkonzept

Im Folgenden wird das Leistungselektronikkonzept des entwickelten PHIL-Umrichters vorgestellt, der auf einem SHC basiert, und es werden mögliche Topologien für den Hauptumrichter des SHCs hinsichtlich ihrer Eignung für die vorhandene Anwendung erörtert.

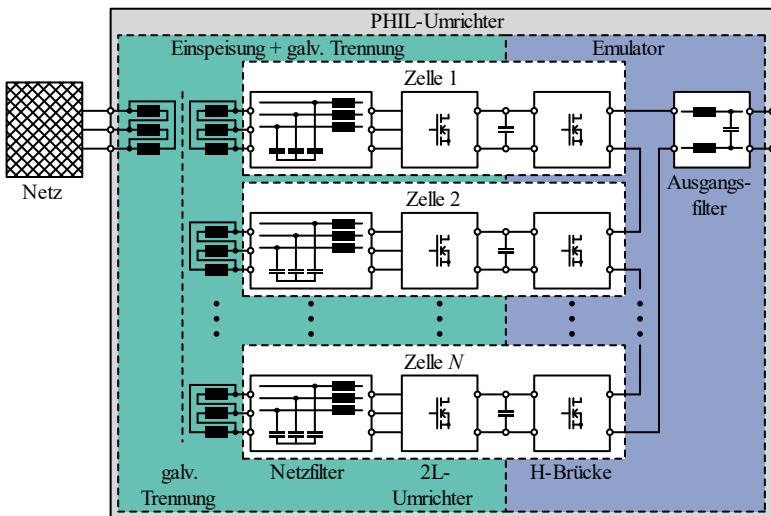

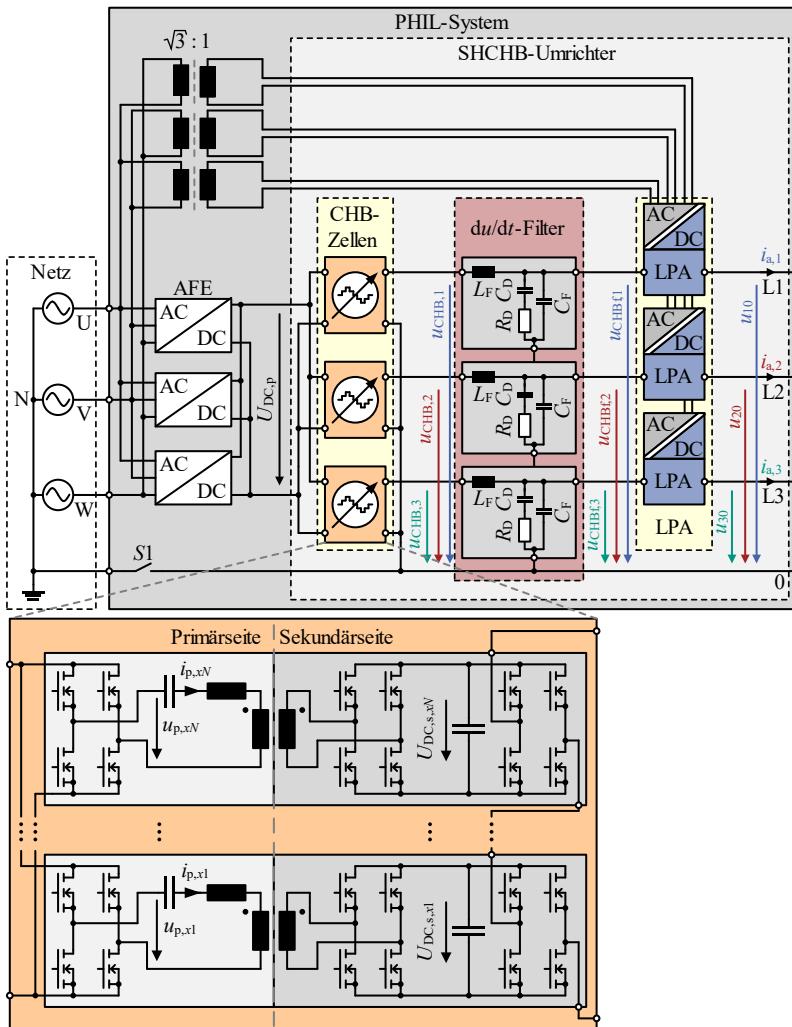

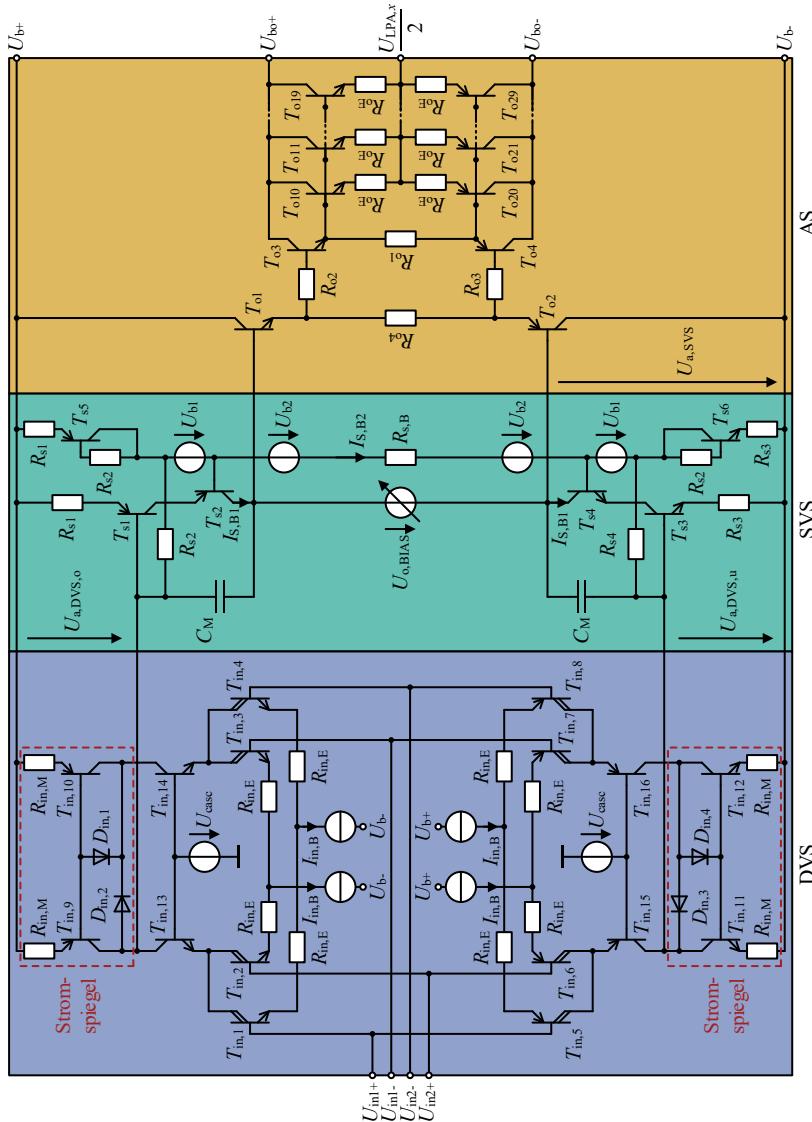

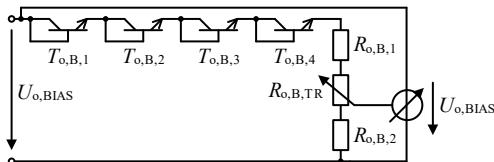

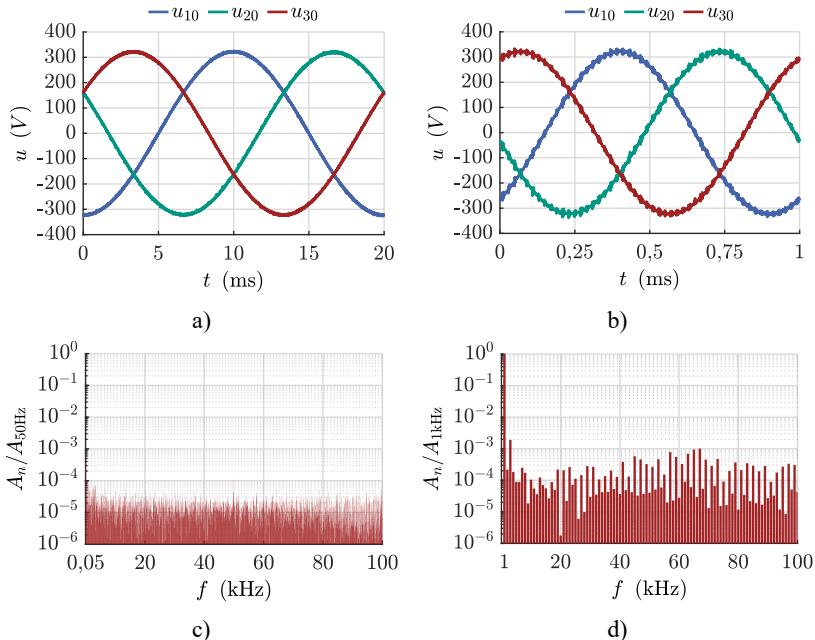

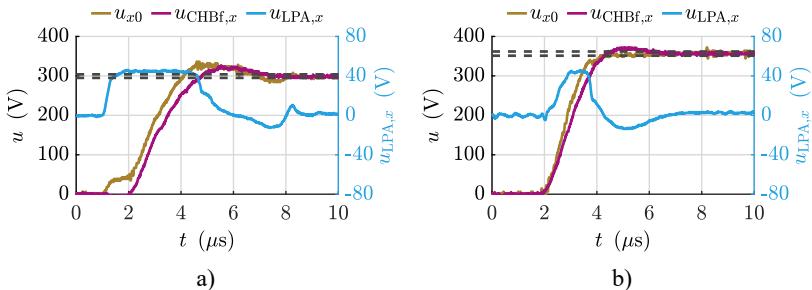

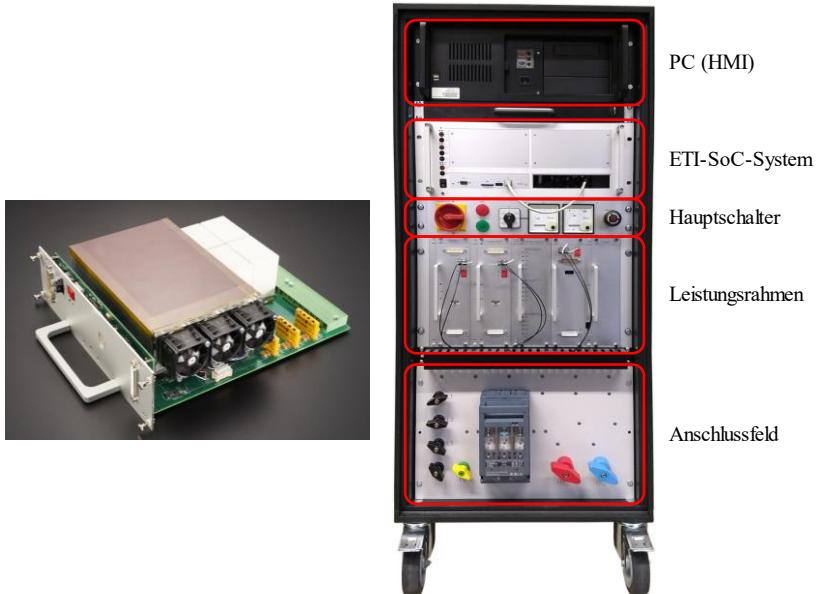

Der Hauptumrichter des SHCs sollte als Multilevelumrichter ausgelegt sein, damit der LPA, wie in Kapitel 1.1.2 beschrieben, lediglich einen geringen Anteil der Ausgangsspannung bereitstellen muss. Aufgrund der Anforderung neben eines Wechselspannungssystems auch ein Gleichspannungssystem erzeugen zu können, ist die Verwendung eines MMCs aufgrund der hohen Symmetrierungsströme nicht zielführend [28]. Der MMPMC kann grundsätzlich eine Gleichspannung stellen. Es muss jedoch berücksichtigt werden, dass aufgrund des verwendeten Drosselnetzwerks nach Abbildung 1.4 die Verschaltung der Drosseln durchgehend variiert werden muss, um eine Sättigung zu verhindern. Dies führt bei der Erzeugung einer Gleichspannung zu zahlreichen Umschaltungen des Drosselnetzwerks, was Spannungssprünge am Ausgang des MMPMC verursacht. Diese müssen vom LPA kompensiert werden, was wiederum höhere Verluste und einen erhöhten Oberschwingungsgehalt in der Ausgangsspannung zur Folge hat [S1]. Für den entwickelten SHC wird daher ein CHB-Umrichter verwendet, da die notwendigen Umschaltungen durch die vorhandene Einspeisung der Zellen auf ein Minimum reduziert werden. Der resultierende Emulationsumrichter bestehend aus CHB-Umrichter, Spannungsflankensteilheitsfilter ( $du/dt$ -Filter) und LPA wird nachfolgend als *Series Hybrid Cascaded H-Bridge* (SHCHB) Umrichter bezeichnet. Das Blockschaltbild des entwickelten PHIL-Systems inklusive des SHCHB-Umrichters ist in Abbildung 2.1 dargestellt.

Die CHB-Zellen werden jeweils über einen galvanisch trennenden LLC-DC/DC-Wandler versorgt. Die primärseitige Eingangsspannung von 660 V des LLC-DC/DC-Wandlers  $U_{DC,p}$  wird wiederum von drei parallel geschalteten 2L-VSCs, die als aktiver Netzgleichrichter (Active-Front-End: AFE) fungieren, zur Verfügung gestellt.

Zur Erzeugung der Ausgangsspannung werden pro Phase  $N$  CHB-Zellen zu einem Strang in Serie geschaltet. Die drei Stränge bilden die Spannungen  $\mathbf{u}_{CHB} = [u_{CHB,1} \ u_{CHB,2} \ u_{CHB,3}]^T$ . Dabei werden die drei unteren Ausgangsklemmen der drei Stränge zu einem Sternpunkt 0 zusammengefasst, der als Klemme zur Verfügung steht.

Abbildung 2.1: Blockschaltbild des PHIL-Systems bestehend aus Netzeinspeisung (AFE) und SHCHB-Umrichter

Der Sternpunkt 0 kann mit dem entwickelten Konzept, abhängig von der gewünschten Anwendung, mit dem Schalter  $S1$  geerdet oder potentialfrei ausgeführt werden.

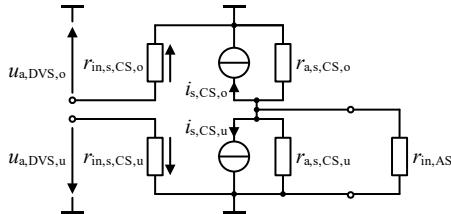

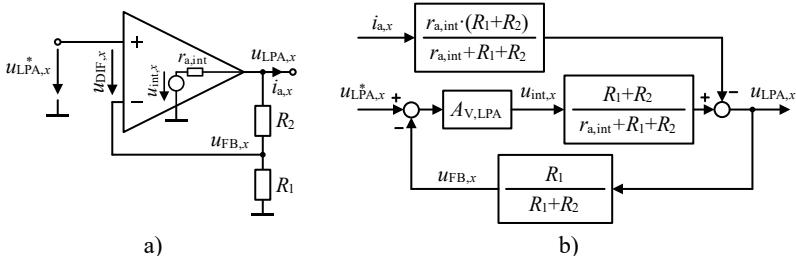

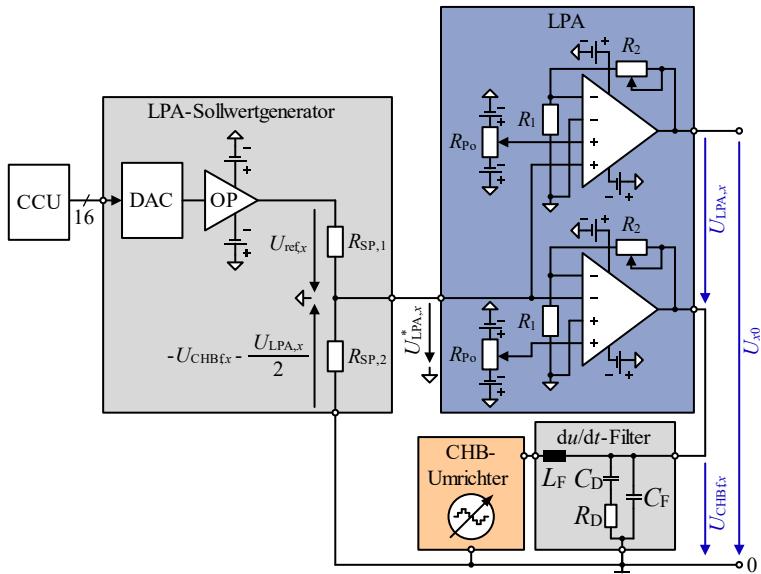

An den oberen Ausgangsklemmen der drei Stränge wird jeweils ein  $du/dt$ -Filter eingebaut, an deren Ausgängen wiederum die gefilterten Spannungen  $\mathbf{u}_{\text{CHBF}} = [u_{\text{CHBF},1} \ u_{\text{CHBF},2} \ u_{\text{CHBF},3}]^T$  anliegen. Die Flankensteilheit dieser Spannungen ist so weit reduziert, dass die LPAs in der Lage sind, die Sprungantworten der  $du/dt$ -Filter zu kompensieren. Dadurch sind am dreiphasigen Ausgang des PHIL-Umrichters  $u_{x0}$  ( $x = \{1,2,3\}$ ) idealerweise keine Spannungssprünge mehr sichtbar, die durch die Taktung der CHB-Zellen verursacht werden. Die LPAs erzeugen die Spannungen  $u_{\text{LPA},x}$  und werden zwischen den  $du/dt$ -Filtern und dem dreiphasigen Ausgang des PHIL-Umrichters eingefügt (siehe Abbildung 2.1). Jeder der drei LPAs wird von einem einphasigen, galvanisch trennenden AC/DC-Umrichter versorgt. Diese Umrichter sind über einphasige 400 V-zu-230 V-Transformatoren mit dem Anschlusspunkt des PHIL-Systems verbunden.

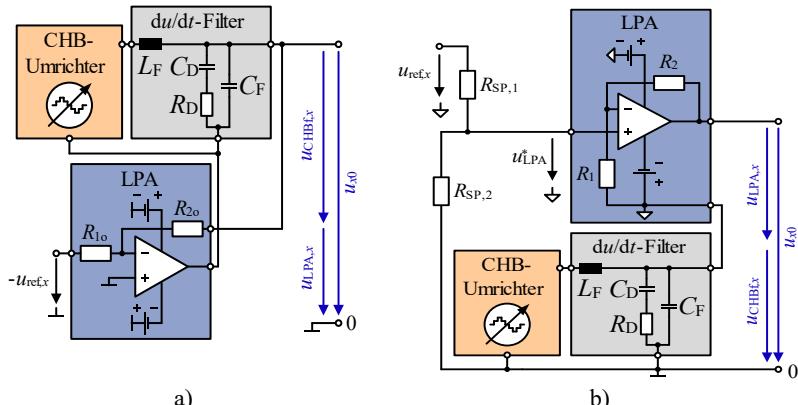

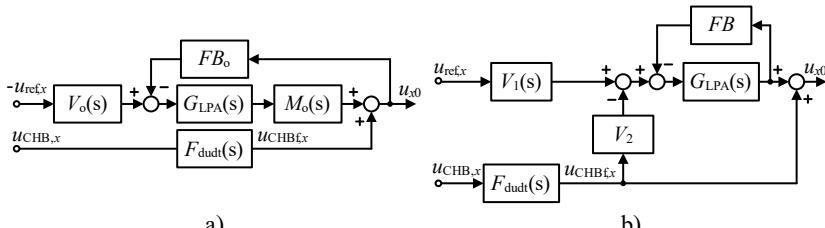

Diese Verschaltung der CHB-Zellen, der  $du/dt$ -Filter und der LPAs unterscheidet sich von den bisherigen Aufbauten, bei denen die LPAs am Sternpunkt 0 angeschlossen werden [35, 50–52, 59]. Die einphasigen Blockschaltbilder der beiden möglichen Verschaltungskonzepte sind in Abbildung 2.2 dargestellt. Das bisher genutzte Konzept hat den Vorteil, dass die LPAs keinen Spannungssprüngen ausgesetzt werden und ein definiertes Bezugspotential besitzen. Hierdurch ist der Aufwand für die Spannungsversorgung der LPAs sowie für das Isolationsmanagement innerhalb der LPAs geringer. Diese Verschaltung wirkt sich jedoch negativ auf die Stabilität und erreichbare Dynamik aus. Dies lässt sich mit Hilfe der Regelungstechnischen Signalflussdiagramme der beiden Verschaltungarten erklären, die in Abbildung 2.3 illustriert sind. Die Übertragungsfunktion des LPAs  $G_{\text{LPA}}$  kann dabei aufgrund der deutlich höheren Bandbreite des LPAs auf seine Leerlaufverstärkung  $A_{V0,\text{LPA}}$  reduziert werden. Es gilt:

$$G_{\text{LPA}}(s) = A_{V0,\text{LPA}} \quad (2.1)$$

Abbildung 2.2: Einphasige Darstellung der Verschaltungskonzepte des SHCHB-Umrichters: a) bisher genutztes SHC-Konzept, b) in dieser Arbeit verwendete SHC-Konzept

Abbildung 2.3: Regelungstechnisches Signalflussdiagramm: a) des bisher genutzten SHC-Konzepts, b) des in dieser Arbeit verwendeten SHC-Konzepts

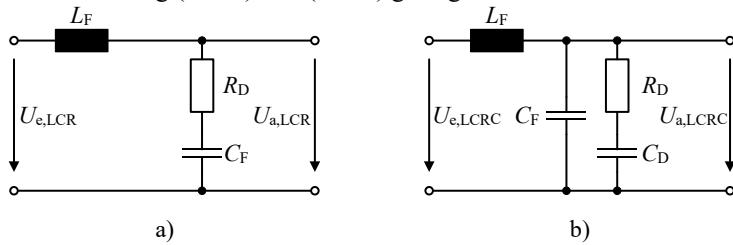

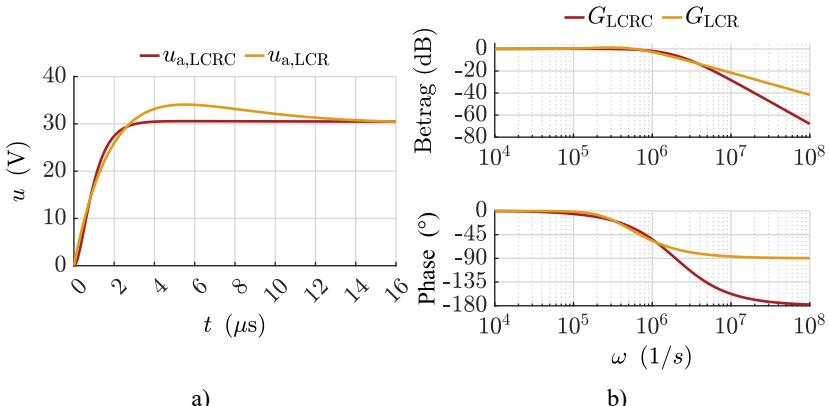

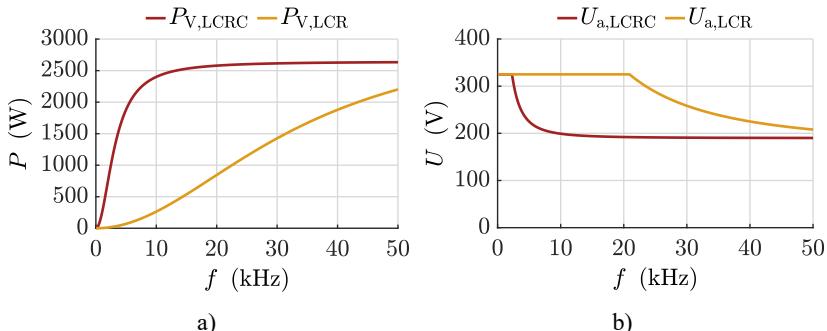

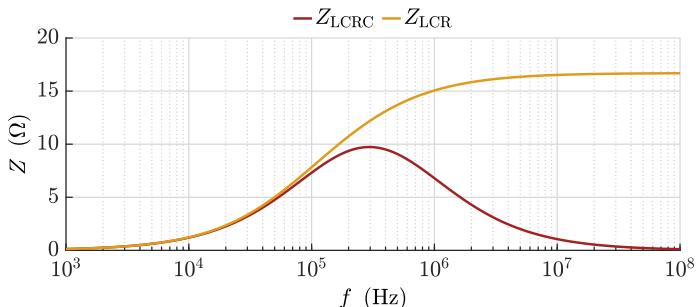

Die Übertragungsfunktion  $F_{\text{dudt}}$  beschreibt die Filterwirkung des  $du/dt$ -Filters.  $V_0$ ,  $V_1$  und  $V_2$  sind die Übertragungsfunktionen der einzelnen Spannungsteiler. Die Rückkoppelpfade werden durch die Übertragungsfunktionen  $FB$  und  $FB_0$  beschrieben. Beim bisher verwendeten Konzept existiert zusätzlich noch eine Übertragungsfunktion  $M_o$ . Für die genannten Übertragungsfunktionen gelten folgende Zusammenhänge:

$$F_{\text{dudt}}(s) = \frac{\frac{1}{C_F \cdot s} \left( R_D + \frac{1}{C_D \cdot s} \right)}{\frac{1}{C_F \cdot s} \left( R_D + \frac{1}{C_D \cdot s} \right) + (L_F \cdot s) \cdot \left( R_D + \frac{1}{C_D \cdot s} + \frac{1}{C_F \cdot s} \right)} \quad (2.2)$$

$$V_0(s) = \frac{R_{2o} + Z_{\text{CHB}}(s)}{R_{1o} + R_{2o} + Z_{\text{CHB}}(s)} \quad (2.3)$$

$$V_1(s) = \frac{R_{SP,2} + Z_{CHB}(s)}{R_{SP,1} + R_{SP,2} + Z_{CHB}(s)} \quad (2.4)$$

$$V_2 = \frac{R_{SP,1}}{R_{SP,1} + R_{SP,2}} \quad (2.5)$$

$$FB_o = \frac{R_{1o}}{R_{1o} + R_{2o}} \quad (2.6)$$

$$FB = \frac{R_1}{R_1 + R_2} \quad (2.7)$$

$$M_o(s) = \frac{R_{1o} + R_{2o}}{R_{1o} + R_{2o} + Z_{CHB}(s)} \quad (2.8)$$

wobei  $Z_{CHB}$  der Ausgangsimpedanz der CHB-Zellen einschließlich des  $du/dt$ -Filters entspricht und wie folgt berechnet wird:

$$Z_{CHB}(s) = \frac{(R_{CHB,x} + s \cdot L_F) \cdot \left(1 + \frac{1}{s \cdot R_D \cdot C_D}\right)}{s^2 \cdot C_F \cdot L_F + s \cdot \frac{L_F}{R_D} \left(1 + \frac{C_F}{C_D}\right) + s \cdot R_{CHB,x} \cdot C_F + \frac{R_{CHB,x}}{R_D} \left(1 + \frac{C_F}{C_D}\right) + \left(1 + \frac{1}{s \cdot R_D \cdot C_D}\right)} \quad (2.9)$$

Der Widerstand  $R_{CHB,x}$  kann nach Gleichung (2.16) berechnet werden und entspricht dem wirksamen Widerstand aller CHB-Zellen einer Phase. Mit Hilfe der ermittelten Übertragungsfunktionen können die offenen Übertragungsfunktionen der LPA-Regelkreise für das bisherige Konzept  $G_{O,LPA,o}$  sowie für das hier verwendete Konzept  $G_{O,LPA}$  abgeleitet werden. Ebenso lassen sich die entsprechenden geschlossenen Sollwertübertragungsfunktionen  $G_{IO,LPA,o}$  und  $G_{IO,LPA}$  ableiten.

$$G_{O,LPA,o}(s) = A_{LPA} \cdot FB_o \cdot M_o(s) = A_{V0,LPA} \cdot \frac{R_{1o}}{R_{1o} + R_{2o} + Z_{CHB}(s)} \quad (2.10)$$

$$G_{O,LPA}(s) = A_{LPA} \cdot FB = A_{V0,LPA} \cdot \frac{R_1}{R_1 + R_2} \quad (2.11)$$

$$G_{IO,LPA,o}(s) = \frac{u_{x0}}{-u_{ref,x}} = \frac{V_o(s) \cdot M_o(s)}{1/A_{V0,LPA} + M_o(s) \cdot FB_o} \quad (2.12)$$

$$G_{IO,LPA}(s) = \frac{u_{x0}}{u_{ref,x}} = \frac{V_1(s)}{1/A_{V0,LPA} + FB} \quad (2.13)$$

Unter der Annahme, dass der Kehrwert der Leerlaufverstärkung des LPAs  $1/A_{V,LPA}$  sehr klein ist, können die Sollwertübertragungsfunktionen vereinfacht werden zu:

$$G_{IO,LPA,0}(s) \cong V_o(s) \cdot \frac{1}{FB_0} = \frac{R_{20} + Z_{CHB}(s)}{R_{10} + R_{20} + Z_{CHB}(s)} \cdot \frac{R_{10} + R_{20}}{R_{10}} \quad (2.14)$$

$$G_{IO,LPA}(s) \cong V_1(s) \cdot \frac{1}{FB} = \frac{R_{SP,2} + Z_{CHB}(s)}{R_{SP,1} + R_{SP,2} + Z_{CHB}(s)} \cdot \frac{R_1 + R_2}{R_1} \quad (2.15)$$

Nach Gleichung (2.14) und (2.15) führt die Ausgangsimpedanz der CHB-Zellen unabhängig von der Verschaltungsart zu einer Verfälschung der gewünschten Sollwertübertragungsfunktion. Da  $Z_{CHB}$  für den verwendeten Frequenzbereich deutlich kleiner als  $R_{SP,2}$  ist (siehe Kapitel 2.3.4), kann der Fehler aber vernachlässigt werden.

Der Unterschied der beiden Verschaltungsarten wird in den offenen Übertragungsfunktionen der LPAs nach den Gleichungen (2.10) und (2.11) sichtbar. Beim bisher umgesetzten Konzept umfasst die Regelschleife des LPAs den gesamten Umrichter einschließlich der CHB-Zellen und des  $dU/dt$ -Filters. Beim hier verwendeten Konzept schließt sich die Regelschleife innerhalb des LPAs, wie in Abbildung 2.2 und Abbildung 2.3 zu sehen ist. Durch die kleinere Regelschleife wird die Empfindlichkeit der LPAs gegenüber Störungen reduziert, weshalb die Bandbreite und Flankensteilheit der LPAs erhöht werden kann. Darüber hinaus wird dadurch ein deterministischeres Verhalten des LPAs und somit des gesamten SHCHB-Umrichters erreicht. Aus diesen Gründen wird der entwickelte SHCHB-Umrichter gemäß dem in Abbildung 2.2 b) gezeigten Verschaltungskonzept aufgebaut.

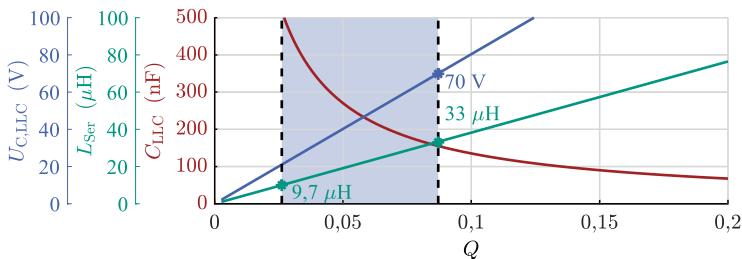

Die für das Konzept benötigte CHB-Zellenanzahl  $N_{CHB}$  pro Phase kann anhand der Anforderungen, die an das PHIL-System gestellt werden, bestimmt werden. Mit dem PHIL-System soll die frequenzabhängige Impedanz des Prüflings mit einem sinusförmigen Testsignal ermittelt werden. Die Höhe dieses Testsignal liegt typischerweise im einstelligen Prozentbereich der Netzspannung [62]. Um sämtliche Testsignale mit genügend Reserve erzeugen zu können, wird deshalb die maximale Amplitude auf 10 % Netzspannung und somit 32,5 V festgelegt. Dieses Signal soll ausschließlich von den LPAs erzeugt werden, um die hohe Bandbreite und Signalgüte der LPAs zu nutzen. Damit die LPAs in der Lage sind, die internen Spannungsabfälle sowie Störimpulse zu kompensieren, wird die maximale Amplitude ihrer Ausgangsspannungen  $\hat{U}_{LPA}$

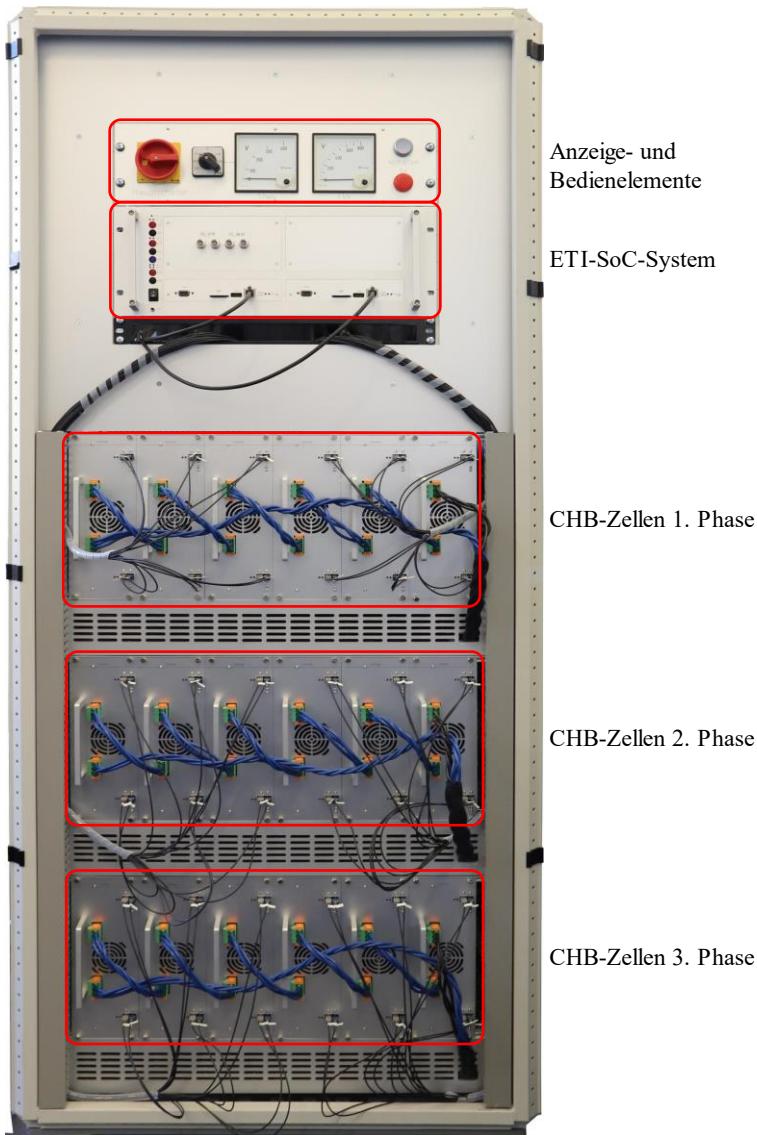

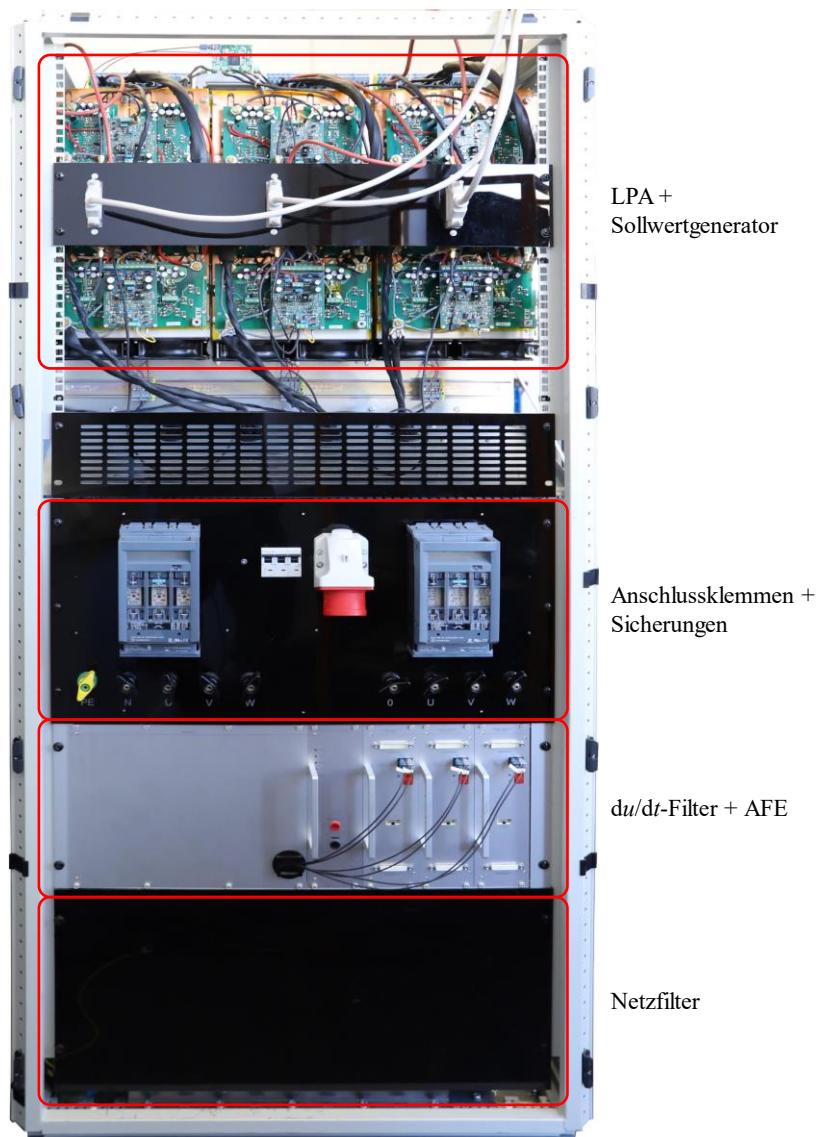

auf 40 V und die sekundären CHB-Zellspannungen  $U_{DC,s,xy}$  ( $y = \{1, 2, \dots, N_{CHB}\}$ ) auf 30 V festgelegt. Somit ergibt sich eine notwendige Zellenanzahl  $N_{CHB}$  von 12, um das europäische Niederspannungsnetz mit einer Nennspannung von  $400 \text{ V} \pm 10\%$  nachbilden zu können. Der SHCHB-Umrichter besteht folglich aus 36 CHB-Zellen, drei  $dU/dt$ -Filtern sowie drei LPAs.

## 2.1.2 Signalverarbeitungs- und Softwarestruktur des PHIL-Systems

Ein leistungsfähiges PHIL-System erfordert nicht nur eine performante Leistungselektronik, sondern auch eine leistungsfähige Signalverarbeitungsstruktur sowie die darauf aufgebaute Softwarestruktur, um die benötigten Modelle sowie Regler mit möglichst geringer Latenz und kleiner Regelperiode in Echtzeit berechnen zu können.

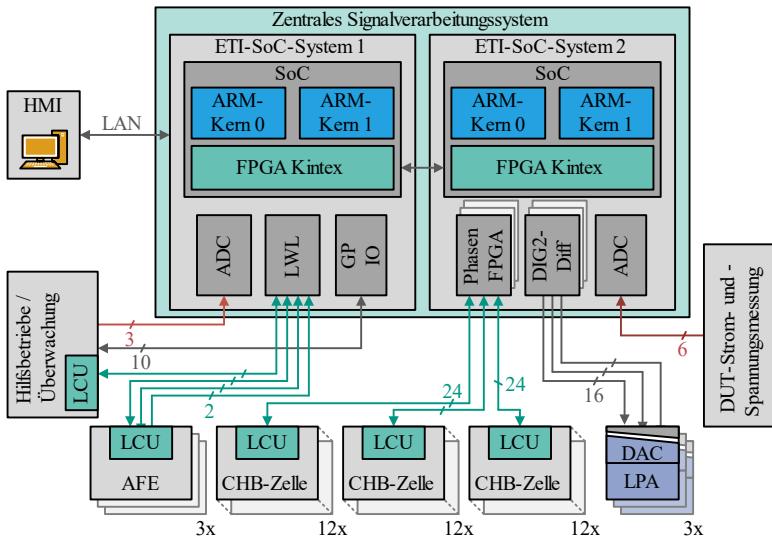

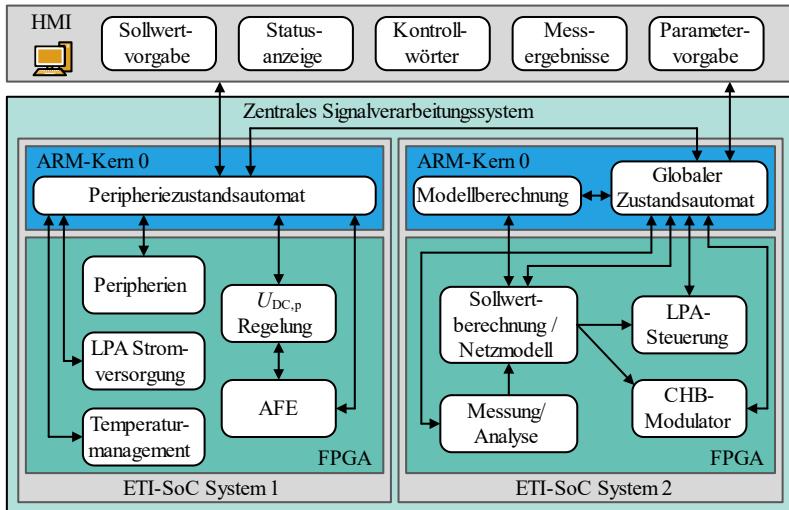

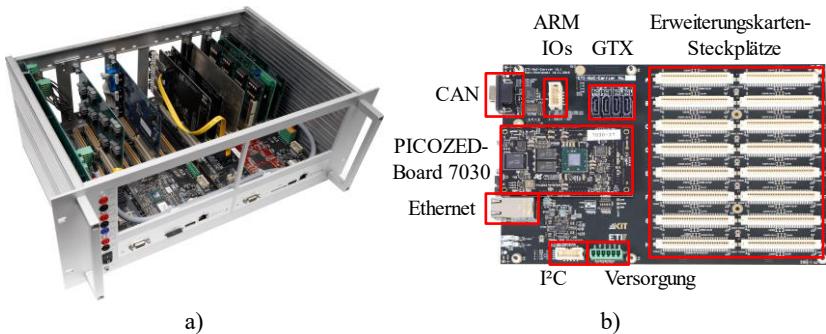

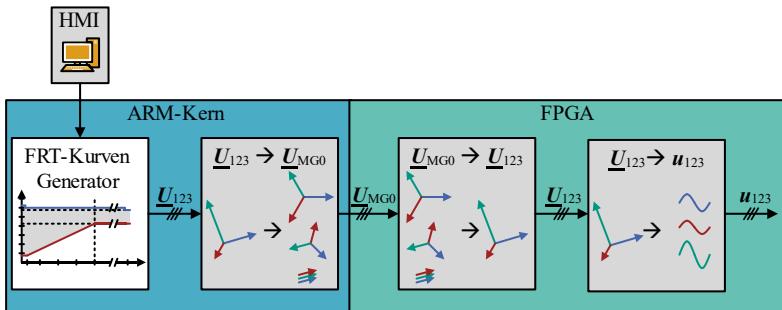

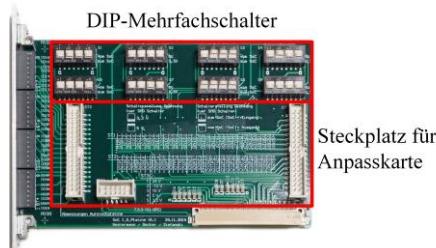

Bei der entwickelten Signalverarbeitungsstruktur wird dabei ein zentrales Signalverarbeitungssystem eingesetzt, das aus zwei ETI-System-on-Chip- (SoC) Systemen besteht, wie in Abbildung 2.4 dargestellt ist. Die zwei ETI-SoC-Systeme basieren dabei auf einem SoC, das einen *Field-Programmable-Gate-Array* (FPGA) und zwei *Advanced RISC Machines* (ARM) Prozessorkerne beinhaltet. Eine nähere Beschreibung der Hardware findet im Kapitel 3.2 statt. Der Prozessorkern 1 jedes Systems übernimmt die Kommunikation zum Prüfstandsrechner. Auf dem Prüfstandsrechner wird ein auf *LabVIEW* basierendes Monitorprogramm ausgeführt, welches, gemäß Abbildung 2.5, sowohl zur Steuerung und Überwachung des Prüfstands, als auch zur Parametervorgabe für Modelle und zur Auswertung der Messergebnisse verwendet wird [E7].

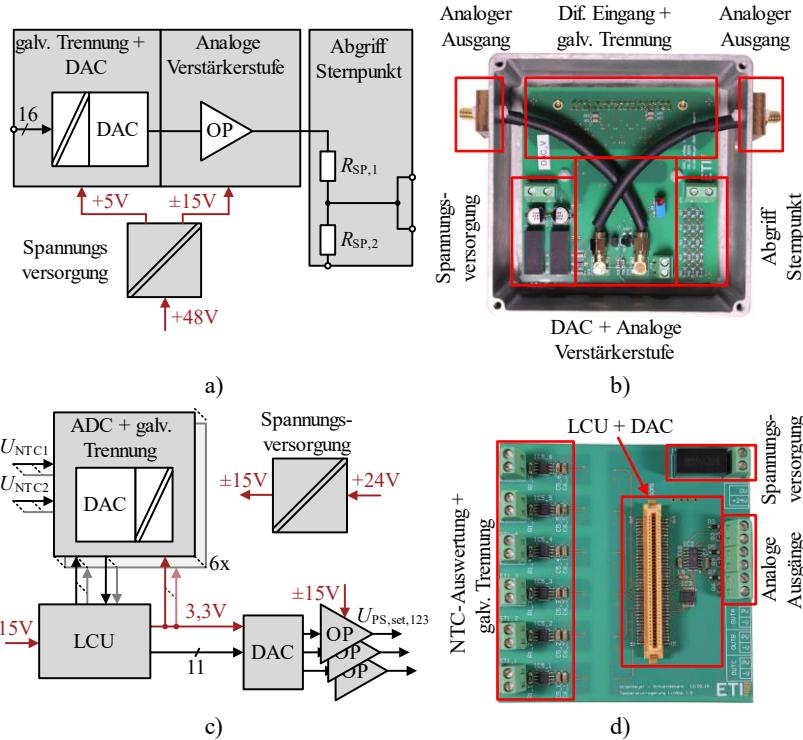

Das ETI-SoC-System 1 wird für die Steuerung der Leistungs- und Hilfsversorgung sowie für die Steuerung der Peripherien des PHIL-Systems, wie z.B. das Temperaturmanagement, eingesetzt. Das ETI-SoC-System 2 steuert den SHCHB-Emulationsumrichter und ist verantwortlich für die Berechnung von Netzmodellen. Das Netzmodell wird dabei abhängig von der Komplexität und der benötigten Latenz auf dem ARM-Kern 0 bzw. auf einem Echtzeitrechner und/oder auf dem FPGA berechnet, wie in Abbildung 2.5 dargestellt. Zusätzlich sind die zentralen Zustandsautomaten beider ETI-SoC-Systeme auf dem ARM-Kern 0 implementiert.

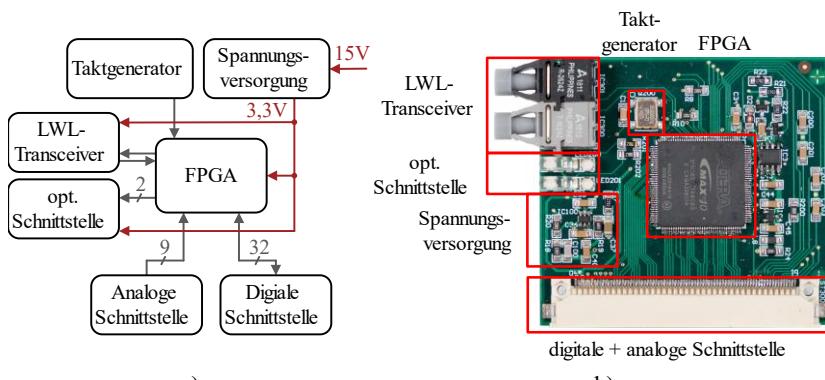

Abbildung 2.4: Signalverarbeitungsstruktur des PHIL-Systems mit Lichtwellenleitern (grün), analogen Messgrößen (rot) und digitalen Schnittstellen (grau)

Neben dem zentralen Signalverarbeitungssystem werden ebenfalls dezentrale Kontrolleinheiten (Local Control Unit: LCU) verwendet. Diese besitzen eine geringere Rechenleistung als das zentrale Signalverarbeitungssystem (siehe Kapitel 3.2.2) und werden zur Steuerung der einzelnen Komponenten des PHIL-Systems verwendet. Die LCUs der drei AFEs übernehmen die Stromregelung sowie Überwachungsaufgaben. Die überlagerte Spannungsregelung erfolgt, gemäß Abbildung 2.5, auf dem FPGA des ETI-SoC-Systems 1. Die LCU der Hilfsbetriebe überwacht die verschiedenen Temperaturen des PHIL-Systems und übermittelt diese an das ETI-SoC-System 1, welches das Temperaturmanagement übernimmt. Des Weiteren ist auf jeder CHB-Zelle eine LCU installiert, die sowohl die CHB-Zelle als auch den LLC-DC/DC-Wandler überwacht und deren H-Brücken steuert. Zusätzlich sind die drei in Kapitel 2.2.4 vorgestellten Betriebsmodi auf den LCUs der CHB-Zellen inklusive der entsprechenden Regelungen implementiert. Die LCUs kommunizieren mittels eines speziell entwickelten UART-Protokolls (vgl. Kapitel 2.2.4) mit dem ETI-SoC-System bzw. die LCUs der CHB-Zellen kommunizieren mit einem Phasen-FPGA. Das Phasen-FPGA ist auf einer Erweiterungskarte im SoC-System eingebettet (vgl. Anhang A.10) und ist für den Sortieralgorithmus sowie die Auswertung aller 12 LCUs einer Phase zuständig.

Abbildung 2.5: Softwarestruktur des PHIL-Systems

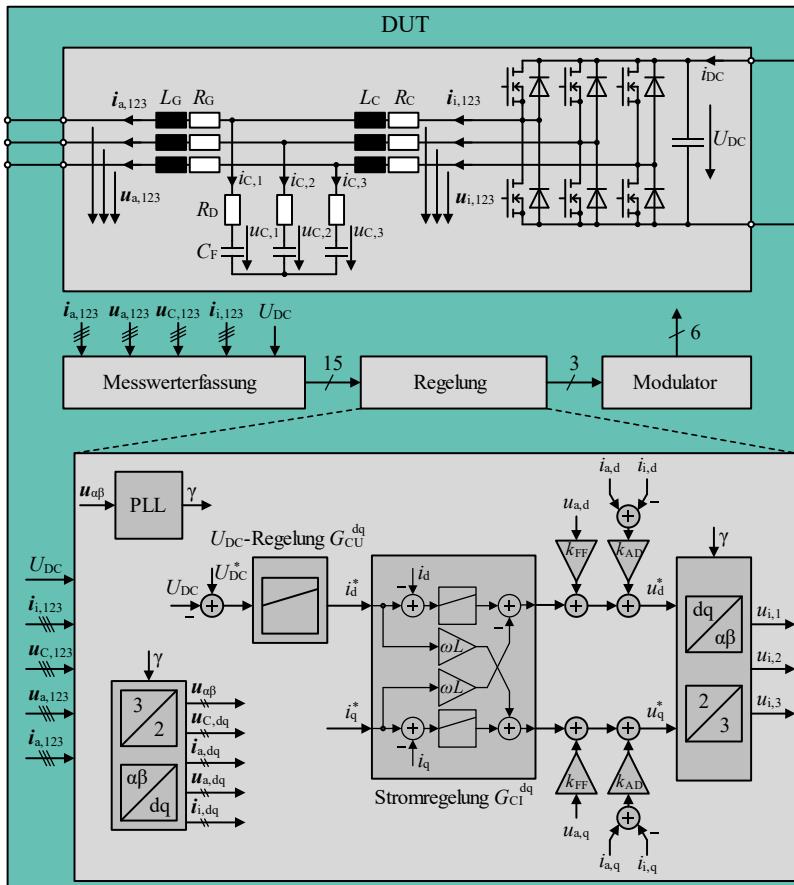

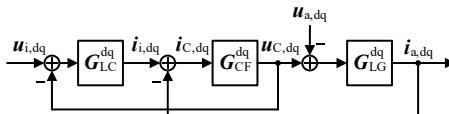

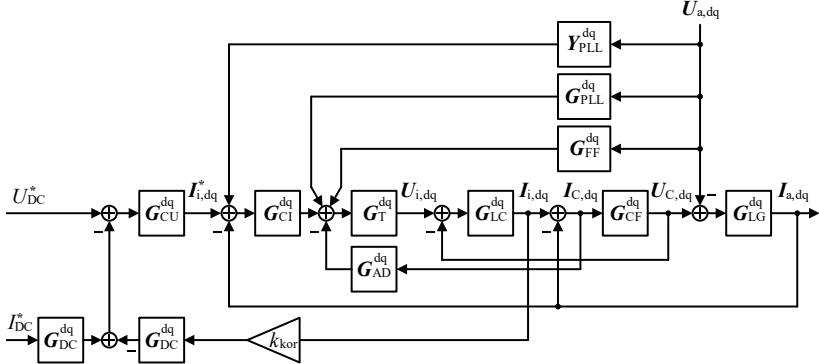

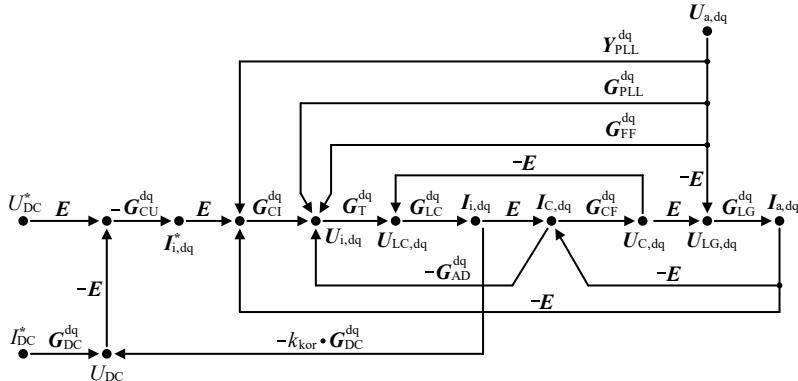

### 2.1.3 Steuerung des SHCHB-Umrichters als Emulator

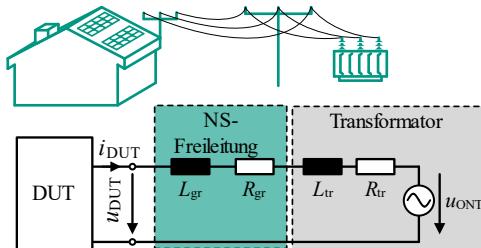

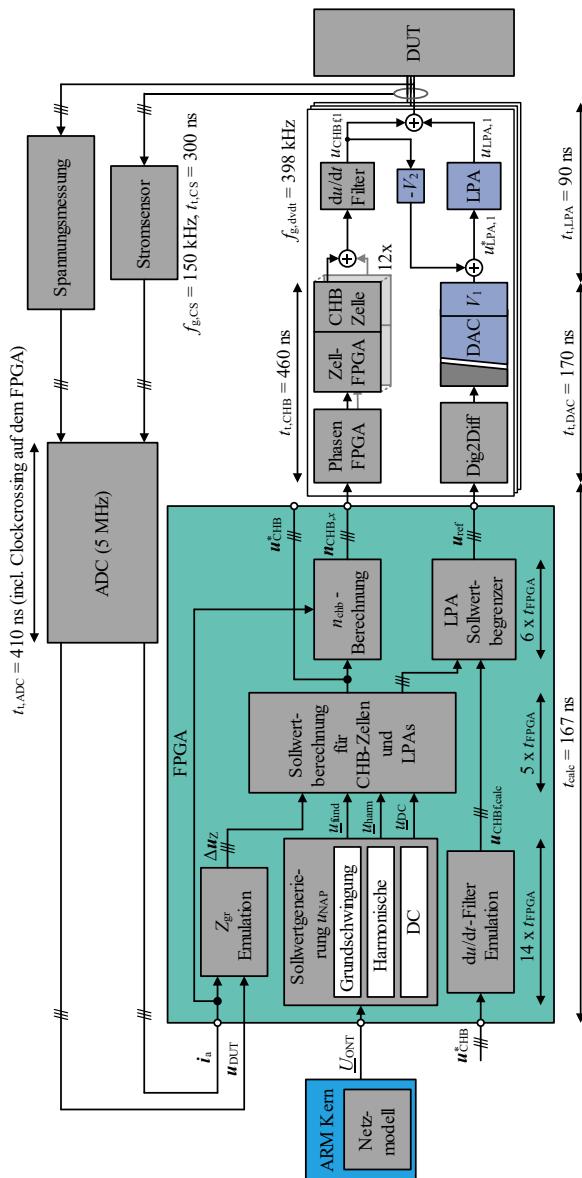

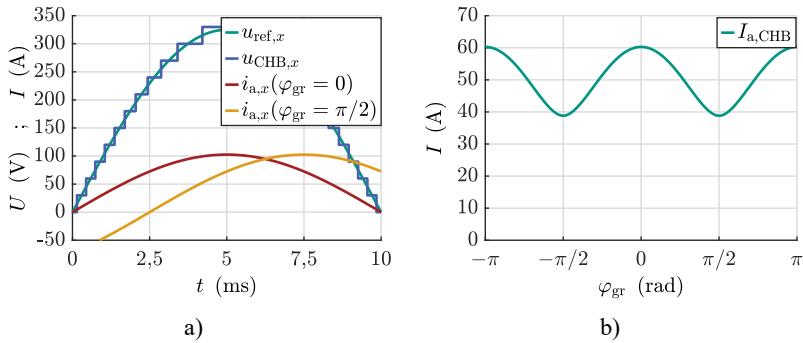

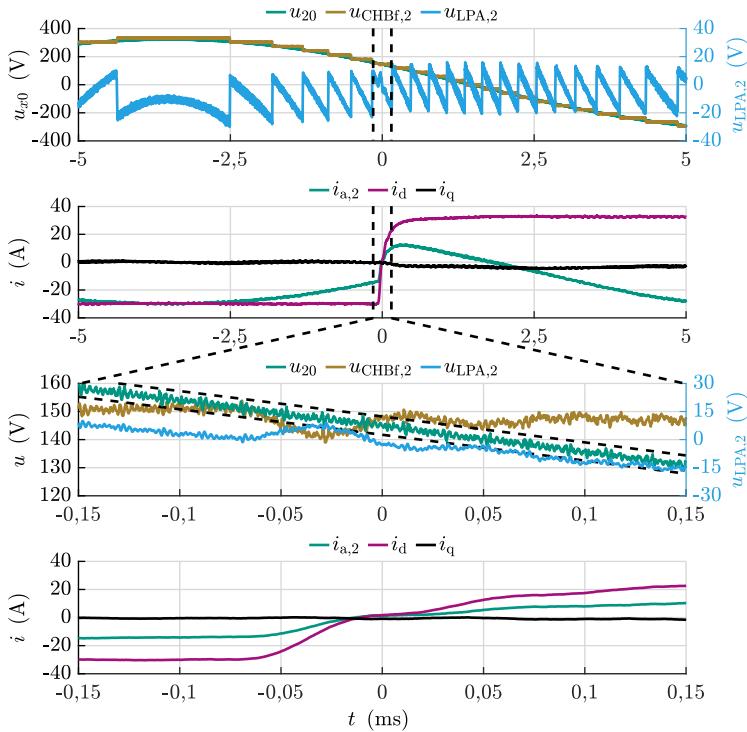

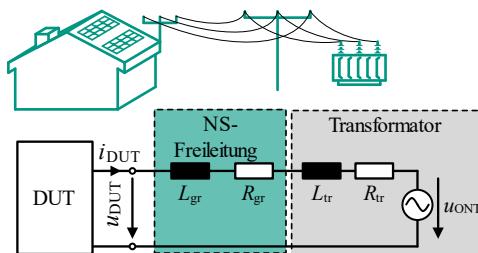

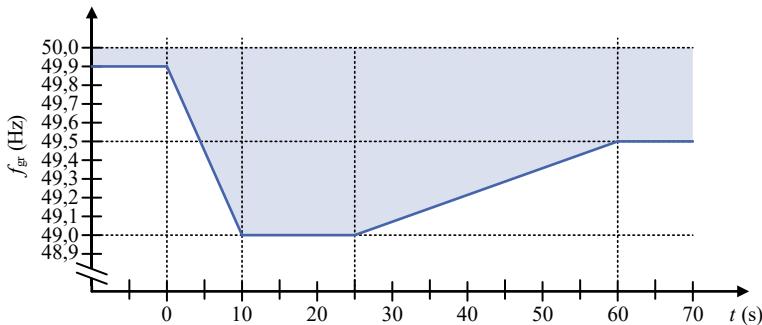

Nachfolgend wird die Steuerung und Betriebsführung des SHCHB-Umrichters für den Betrieb als Emulator beschrieben. Hierbei werden sämtliche Funktionsblöcke analysiert, die sich innerhalb der Emulationsschleife einer closed-loop-Emulation befinden. In Abbildung 2.7 ist der Signallaufplan für eine closed-loop-Emulation eines Netzanschlusspunktes unter Verwendung des SHCHB-Umrichters dargestellt. Ein mögliches Szenario, das mit dem PHIL-System emuliert werden soll, ist in Abbildung 2.6 abgebildet.

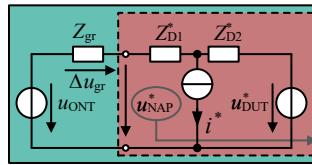

Die Messung der Ausgangsströme des PHIL-Systems  $i_a$  sowie der DUT-Spannungen  $u_{DUT}$  erfolgt über einen Analog-Digital-Wandler (ADC, engl.: Analog-Digital-Converter) auf einer Erweiterungskarte (siehe Anhang A.10). Die Messergebnisse werden direkt auf dem FPGA ausgewertet, um eine möglichst geringe Latenz zu verursachen. Mit den zur Verfügung stehenden Messwerten erfolgt die Emulation eines Teilmodells.

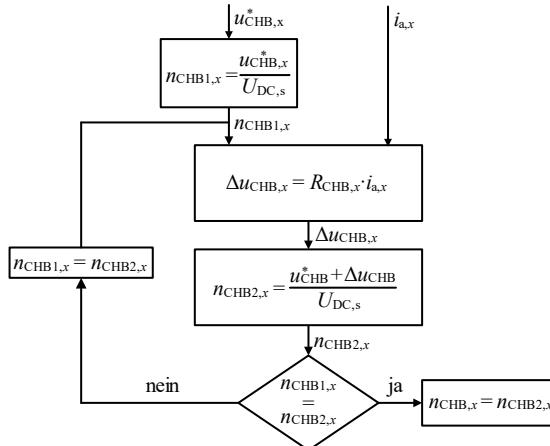

Abbildung 2.6: Beispielhafte Netzsituation, die mithilfe des PHIL-Systems nachgebildet wird

Die Emulation kann in zwei Teile unterteilt werden. Dabei wird die Impedanz vom DUT bis einschließlich des Ortsnetztransformators (ONT) ( $Z_{\text{gr}} + Z_{\text{Tr}}$ ) auf dem FPGA emuliert. Hierdurch wird eine minimale Latenz  $t_{\text{L,D}}$  des Emulators gewährleistet. Die Berechnung der Spannung des ONT  $U_{\text{ONT}}$  kann gemäß Abbildung 2.7 auf den ARM-Kern bzw. auf einen angeschlossenen Echtzeitrechner ausgelagert werden. Unter Berücksichtigung der Spannung  $U_{\text{ONT}}$  und dem Spannungsabfall  $\Delta u_z$  über der Impedanz  $Z_{\text{gr}}$  werden der Sollwert für die CHB-Zellen  $u_{\text{CHB}}^*$  und der Ausgangsspannung des SHCHB-Umrichters  $u_{\text{ref}}$  bestimmt. Anhand der Sollspannung der CHB-Zellen  $u_{\text{CHB}}^*$  wird anschließend die benötigte Anzahl an aktiven CHB-Zellen  $n_{\text{CHB},x}$  mit Hilfe des in Abbildung 2.8 dargestellten Algorithmus ermittelt [E8]. Dabei entspricht  $R_{\text{CHB},x}$  dem wirksamen Widerstand aller CHB-Zellen einer Phase und kann wie folgt bestimmt werden:

$$R_{\text{CHB},x} = n_{\text{CHB},x} \cdot R_{\text{CHB,eq}} + 2(N_{\text{CHB}} - n_{\text{CHB},x}) \cdot R_{\text{DS,(on),Si}} \quad (2.16)$$

Hierbei muss zwischen aktiver CHB-Zelle ( $U_{\text{a,CHB}} = \pm 30 \text{ V}$ ) und inaktiver CHB-Zelle ( $U_{\text{a,CHB}} = 0 \text{ V}$ ) unterschieden werden. Bei einer aktiven CHB-Zelle ist der äquivalente Ersatzwiderstand  $R_{\text{CHB,eq}}$  wirksam, der den internen Spannungsabfall der CHB-Zelle inklusive des LLC-DC/DC-Wandlers berücksichtigt (siehe Kapitel 3.3.1). Bei einer inaktiven CHB-Zelle ist nur der Einschaltwiderstand von zwei in Reihe geschalteten Si-MOSFETs der ausgangsseitigen H-Brücke  $R_{\text{DS,(on),Si}}$  wirksam.

Abbildung 2.7: Signallaufplan des SHCHB-Umrichters für eine closed-loop-Emulation sowie Sollwertgenerierung der CHB-Zellen und des LPAs

Abbildung 2.8: Algorithmus zur Bestimmung der aktiven Zellen

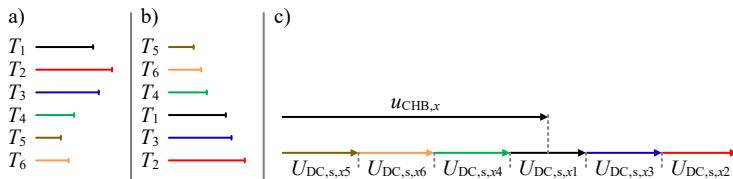

Die benötigte Zellenanzahl  $n_{\text{CHB},x}$  wird anschließend an die drei Phasen-FPGAs gesendet. Auf diesen wird der Sortieralgorithmus ausgeführt und die benötigten Zellen werden ausgewählt. Aufgrund der vorhandenen Einspeisung aller Zellen erfolgt die Sortierung beim SHCHB-Umrichter nicht anhand der Zellspannungen, wie z.B. bei MMCs, sondern anhand der Kühlkörpertemperaturen, wie in Abbildung 2.9 exemplarisch für sechs CHB-Zellen dargestellt [E8]. Hierbei werden vor jedem Umschaltzeitpunkt die momentanen Temperaturen gemessen (Abbildung 2.9 a)) und aufsteigend sortiert (Abbildung 2.9 b)). Die benötigte Ausgangsspannung  $u_{\text{CHB},x}$  wird anschließend mit den kältesten CHB-Zellen gebildet (Abbildung 2.9 c)). Durch diese Sortierung wird eine gleichmäßige Belastung aller CHB-Zellen gewährleistet.

Abbildung 2.9: Sortieralgorithmus der CHB-Zellen

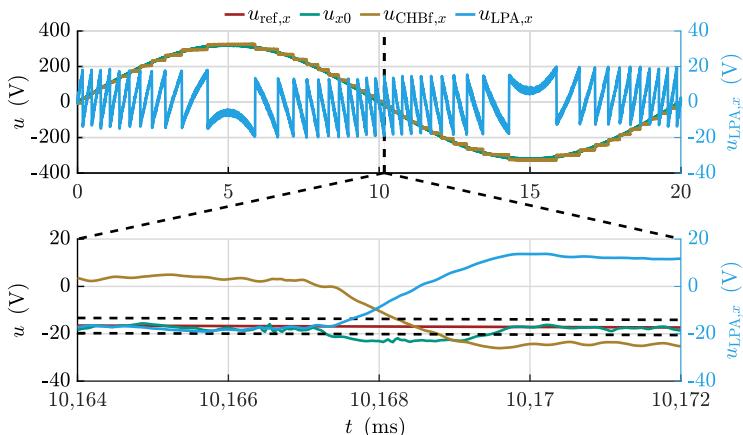

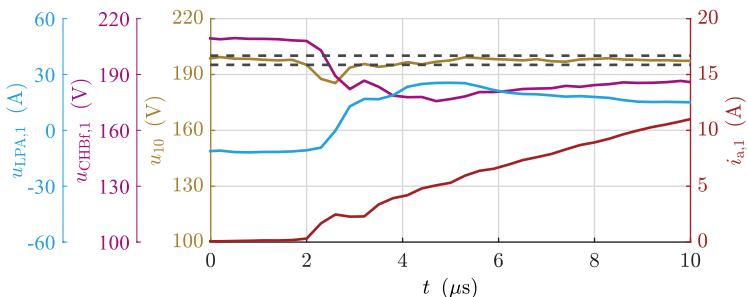

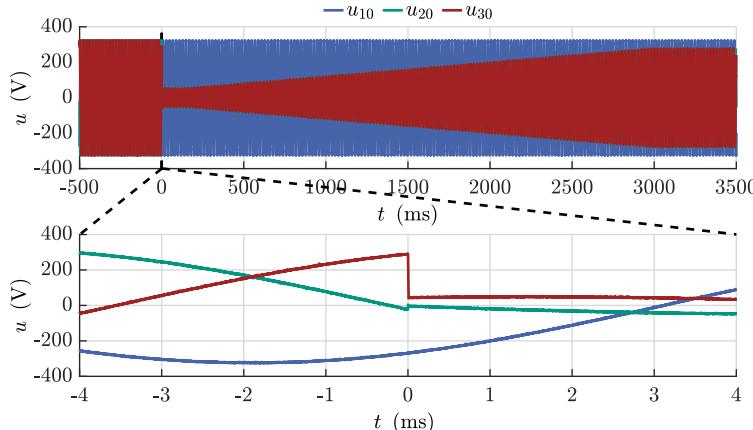

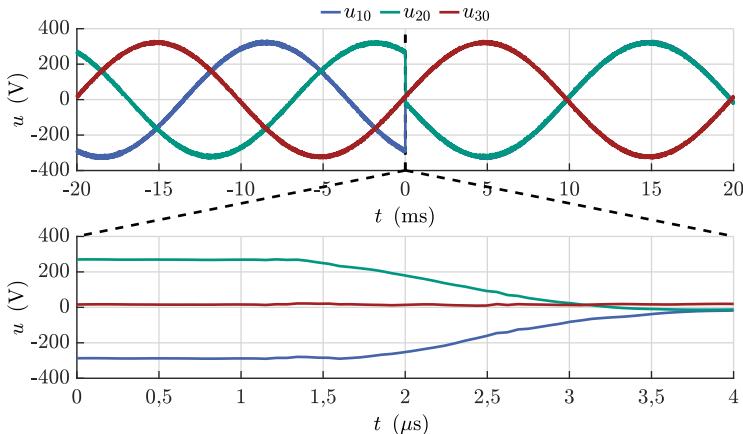

Bei der Erzeugung der Sollwertspannung  $\mathbf{u}_{\text{ref}}$  muss berücksichtigt werden, dass aus dieser die Sollwertspannungen der LPAs  $\mathbf{u}_{\text{LPA}}^*$  über einen Digital-Analog-Wandler (DAC) und über den Spannungsteiler  $V_1$  (bestehend aus  $R_{\text{SP},1}$  und  $R_{\text{SP},2}$ ) mit einer Verzögerung  $t_{\text{t,DAC}}$  von 170 ns (siehe

Abbildung 2.7) erzeugt werden. Die Latenz der CHB-Zellen  $t_{t,CHB}$  beträgt 460 ns. Zusätzlich wird deren Ausgangsspannung  $\mathbf{u}_{CHB}$  durch das  $du/dt$ -Filter gefiltert. Die wirksame, gefilterte Ausgangsspannung  $\mathbf{u}_{CHBf}$  folgt der gewünschten Sollwertspannung  $\mathbf{u}_{ref}$  somit verzögert und mit einer begrenzten Flankensteilheit. Dies würde bei einem Sollwertsprung größer als  $\hat{U}_{LPA}$  zu einem Sollwert der LPAs führen, der die Aussteuergrenze der LPAs überschreitet. Hierdurch würden die LPAs in Sättigung geraten und eine korrekte Funktion der Schaltung wäre nicht mehr gewährleistet (siehe Kapitel 3.4). Aus diesem Grund wird die erzeugte Referenzspannung  $\mathbf{u}_{ref}$  in einem Band von  $\hat{U}_{LPA}$  um die gefilterte Ausgangsspannung  $\mathbf{u}_{CHBf}$  herum begrenzt. Hierzu wird gemäß Abbildung 2.7 die Ausgangsspannung des  $du/dt$ -Filters mithilfe eines Modells auf dem FPGA des ETI-SoC-Systems 2 berechnet. Die berechnete Spannung  $\mathbf{u}_{CHBf,calc}$  wird anschließend für eine Sollwertbegrenzung der Referenzspannung genutzt, um eine Sättigung der LPAs zu verhindern.

Durch die vorgestellte Struktur nach Abbildung 2.7 zur Sollwertgenerierung wird eine sehr kurze Latenz bei der closed-loop-Emulation der Netzimpedanz  $Z_{gr}$  erreicht. Diese Latenz kann gemäß Gleichung (2.17) berechnet werden und beträgt lediglich 1,14  $\mu s$ .

$$t_{L,D} = t_{t,CS} + t_{t,ADC} + t_{calc} + t_{t,DAC} + t_{t,LPA} \quad (2.17)$$

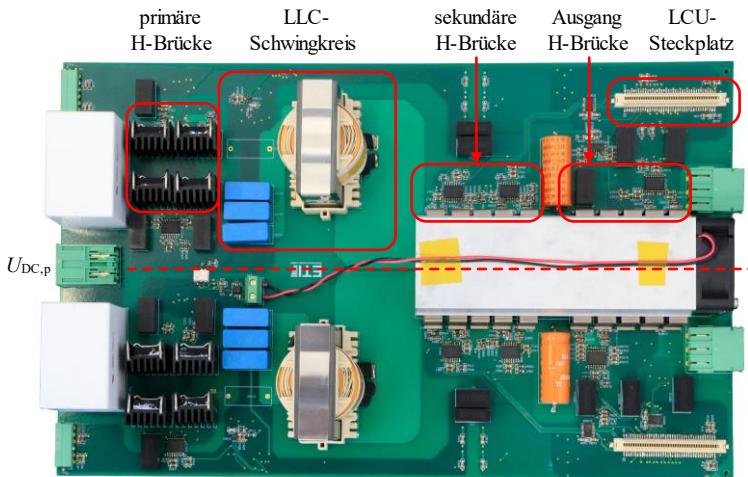

## 2.2 Analyse der CHB-Zelle

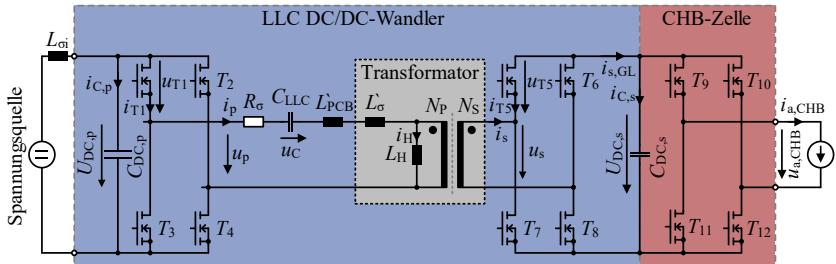

In diesem Abschnitt werden die entwickelte CHB-Zelle sowie deren galvanisch trennende DC-Versorgung erläutert. Die galvanische Trennung kann beim CHB-Umrichter durch einen 50 Hz Mehrfachwickeltransformator mit mehreren sekundären Wicklungen, wie in Abbildung 1.6 dargestellt, oder auf Zellenebene durch dezentrale galvanisch trennende DC/DC-Wandler erfolgen. Um ein möglichst modulares System zu erhalten, wird nachfolgend das Konzept mit dezentralen DC/DC-Wandlern verfolgt. Als galvanisch trennender DC/DC-Wandler wird ein resonanter LLC-Wandler verwendet, wie in der Abbildung 2.10 zu sehen ist.

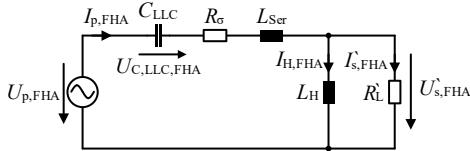

Abbildung 2.10: Prinzipschaltbild einer CHB-Zelle mit galvanisch trennendem LLC-DC/DC-Wandler

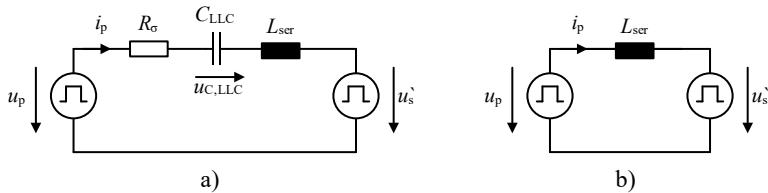

Der verwendete LLC-DC/DC-Wandler besteht aus einer primären H-Brücke mit den MOSFETs  $T_1$  bis  $T_4$  und einer sekundären H-Brücke mit den MOSFETs  $T_5$  bis  $T_8$  sowie aus einem Serienschwingkreis. Der Schwingkreis ist wiederum aus der Kapazität  $C_{LLC}$ , der Ersatzserieninduktivität  $L_{ser}$  und der Hauptinduktivität  $L_H$  aufgebaut. Für die Ersatzserieninduktivität  $L_{ser}$  gilt:

$$L_{ser} = L'_{\sigma T} + L'_{PCB} = L_{\sigma 1} + L_{PCB1} + a_T^2 \cdot (L_{\sigma 2} + L_{PCB2}) \quad (2.18)$$

$$a_T = \frac{N_p}{N_s} \quad (2.19)$$

wobei  $L'_{\sigma T}$  die wirksame Streuinduktivität des Transformators und  $L'_{PCB}$  die wirksame parasitäre Induktivität der Platine sind. Diese setzten sich jeweils aus einem primären Anteil und einem sekundären Anteil zusammen. Die sekundären Anteile dieser beiden Induktivitäten können mit dem Übersetzungsverhältnis des Transformators  $a_T$  auf die Primärseite transformiert werden.

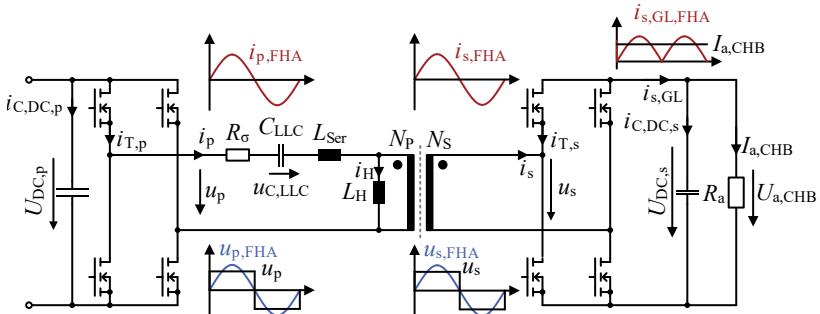

Nachfolgend werden zunächst die grundlegende Funktionsweise des LLC-DC/DC-Wandlers erläutert sowie dessen Übertragungsfunktion hergeleitet. Anschließend werden die daraus resultierenden Strom- bzw. Spannungsbelastungen der einzelnen Komponenten berechnet, die im Kapitel 2.2.3 zur Auswahl der entsprechenden Komponenten genutzt werden.

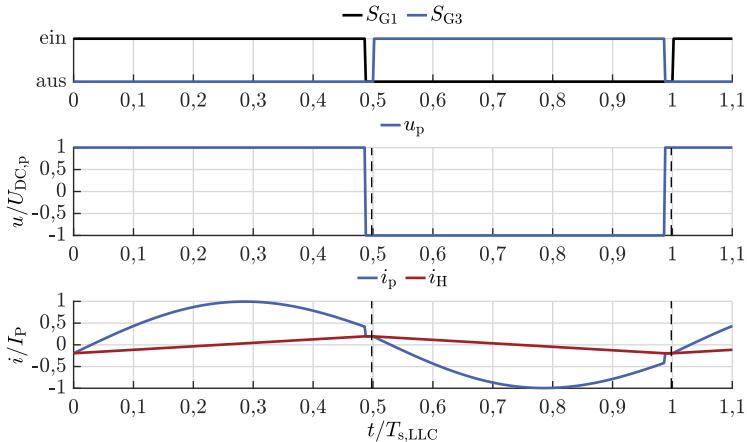

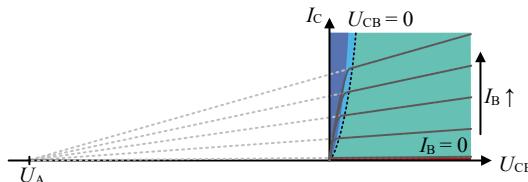

## 2.2.1 Grundlagen des LLC-DC/DC-Wandlers

Der LLC-DC/DC-Wandler besteht, wie bereits erwähnt, aus drei Teilen. Die primäre H-Brücke dient als Wechselrichter und erzeugt die rechteckförmige Primärspannung  $u_p$ . Der Serienschwingkreis dient zur Energieübertragung von der Primär- zur Sekundärseite. Aufgrund seiner Filterwirkung ist der im Schwingkreis fließende Strom  $i_p$  nahezu sinusförmig [63–65], wodurch ein entlastetes Schalten der MOSFETs ermöglicht und die Schaltverluste der MOSFETs sowie die Störaussendung reduziert werden [63, 66: S. 249ff, 67: S. 3]. Die sekundäre H-Brücke fungiert als Gleichrichter und stellt zusammen mit der sekundären Zwischenkreiskapazität  $C_{DC,S}$  die Ausgangsgleichspannung  $U_{DC,S}$  zur Verfügung.

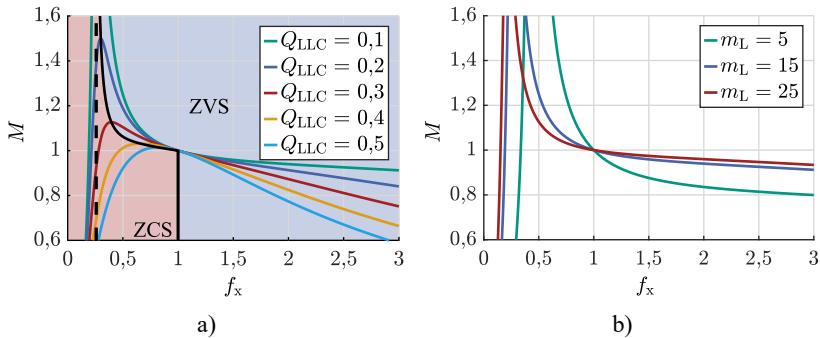

Abhängig von der gewählten Schaltfrequenz  $f_{s,LLC}$  werden die Halbleiter des LLC-DC/DC-Wandlers entweder stromlos ausgeschaltet (ZCS, engl.: Zero Current Switching) oder spannungslos eingeschaltet (ZVS, engl.: Zero Voltage Switching). Die Grenze zwischen diesen beiden Modi wird durch die zwei Resonanzfrequenzen des LLC-Schwingkreises  $f_{res}$  und  $f_{res,l}$  bestimmt.

$$f_{res} = \frac{1}{2\pi\sqrt{c_{LLC} \cdot L_{ser}}} \quad (2.20)$$

$$f_{res,l} = \frac{1}{2\pi\sqrt{c_{LLC} \cdot (L_{ser} + L_H)}} \quad (2.21)$$

Für Schaltfrequenzen, die kleiner als die untere Resonanzfrequenz  $f_{res,l}$  sind, wird der LLC-DC/DC-Wandler im ZCS-Modus betrieben. Für Schaltfrequenzen, die größer als die obere Resonanzfrequenz  $f_{res}$  sind, erfolgt ein Betrieb im ZVS-Modus. Zwischen den beiden Resonanzfrequenzen findet der Übergang vom ZCS-Modus hin zum ZVS-Modus statt. Der Übergang hängt dabei vom Laststrom  $i_{a,CHB}$  ab.

Je nach eingesetztem Halbleiter wird einer der beiden Modi verwendet. Für IGBTs, die hohe Ausschaltverluste aufgrund ihres Tailstroms aufweisen, ist die Verwendung des ZCS-Modus sinnvoll, da hierdurch die Ausschaltverluste

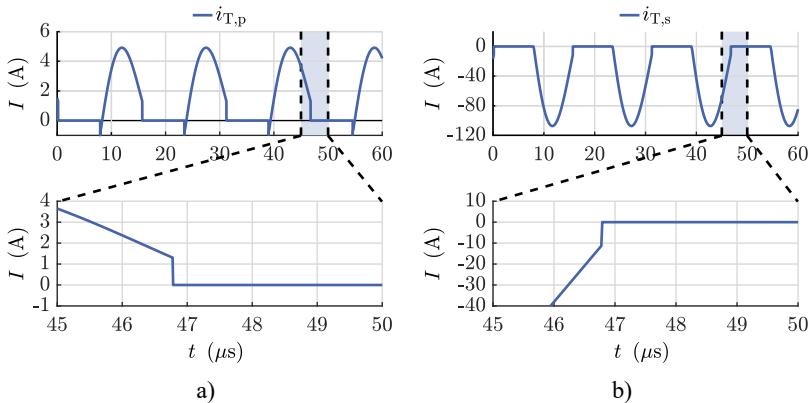

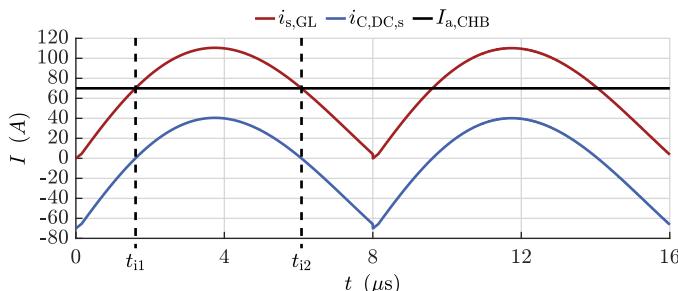

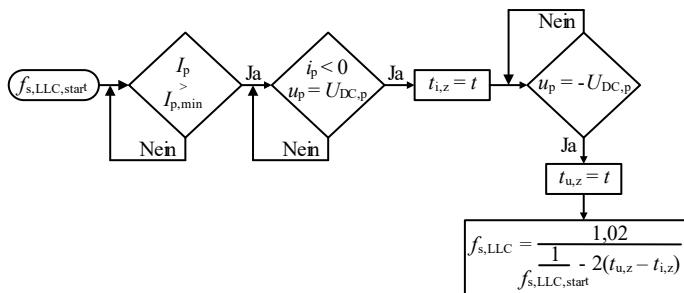

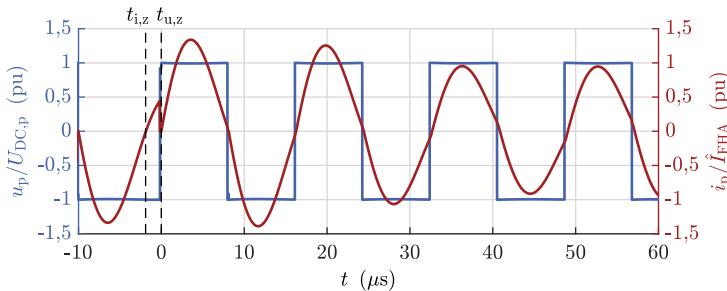

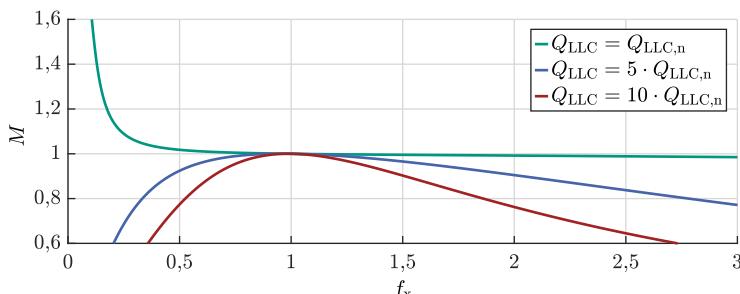

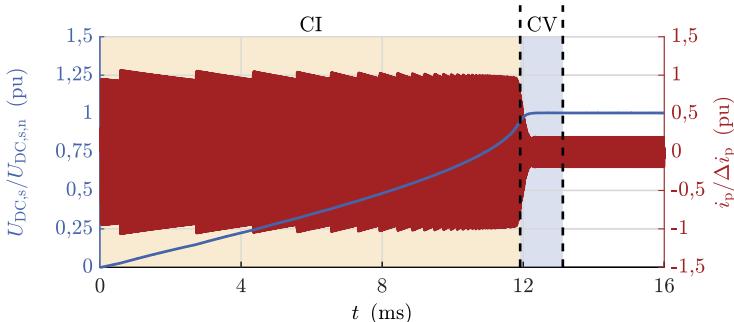

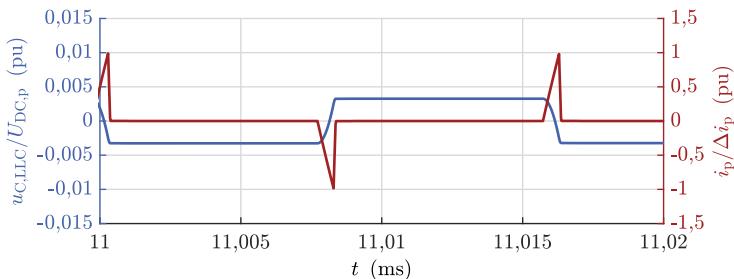

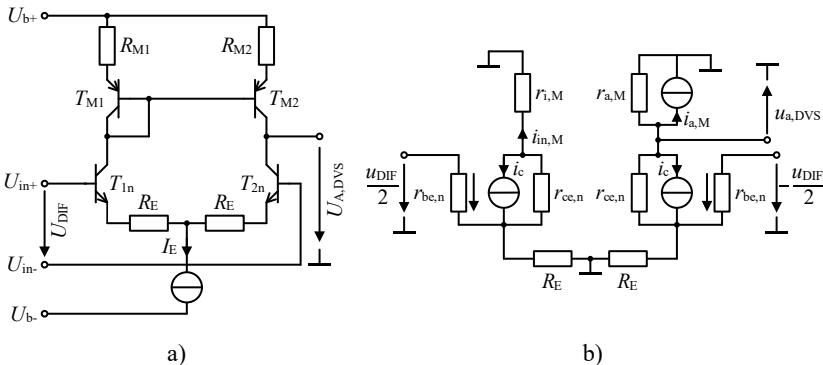

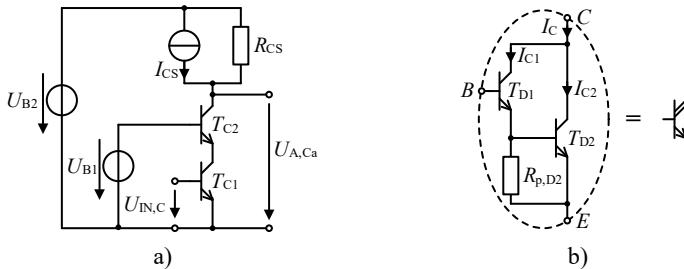

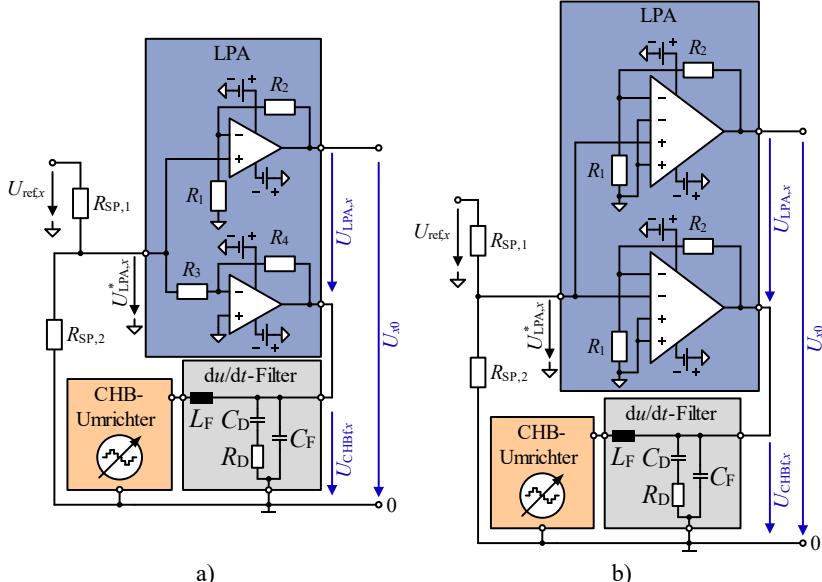

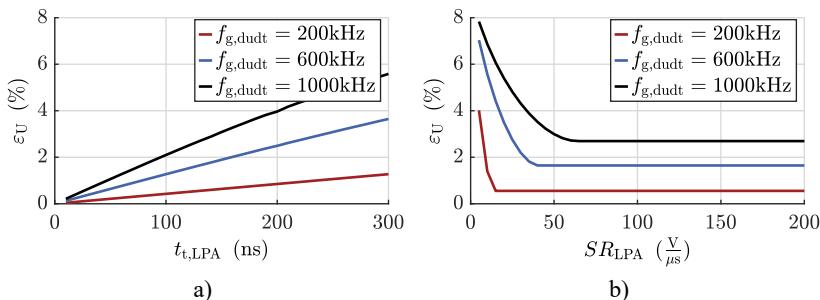

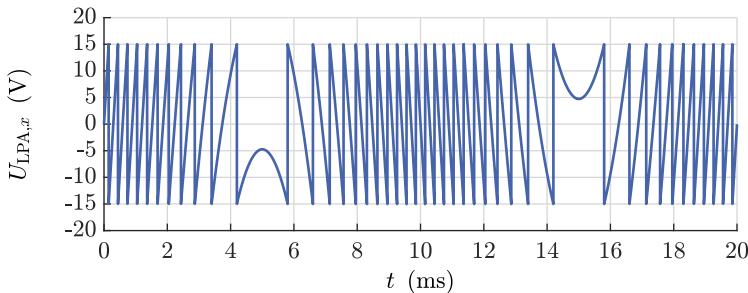

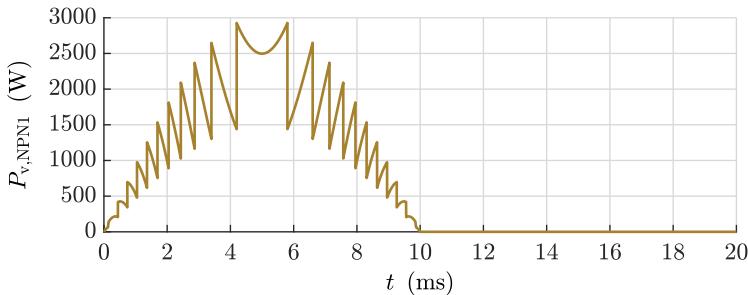

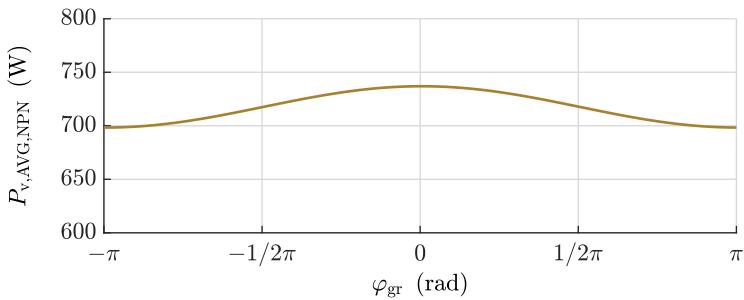

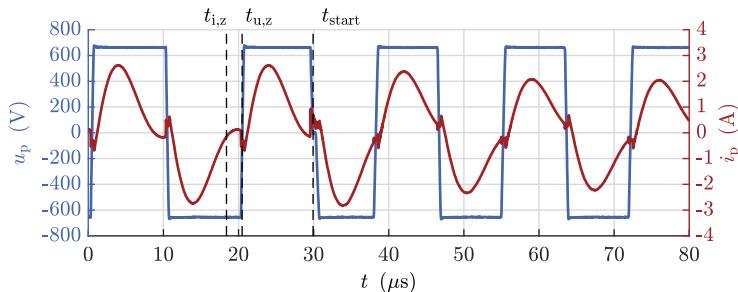

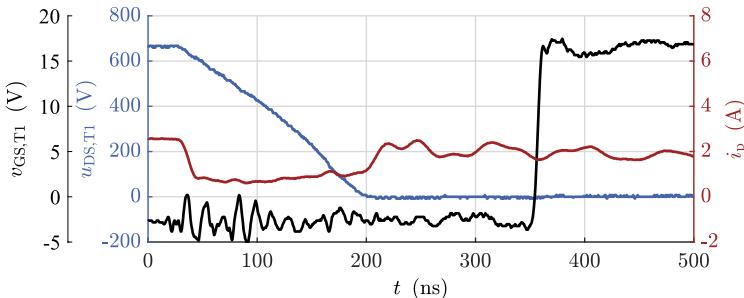

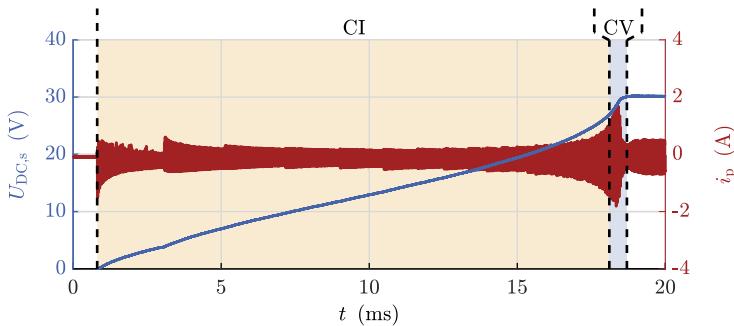

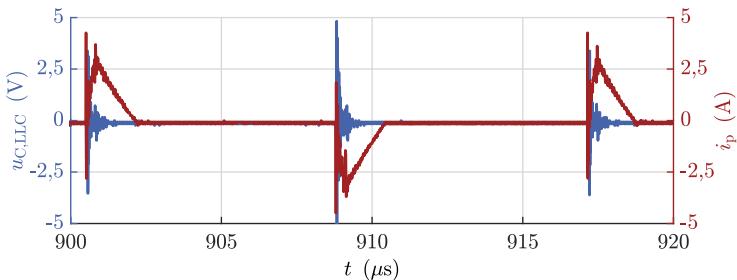

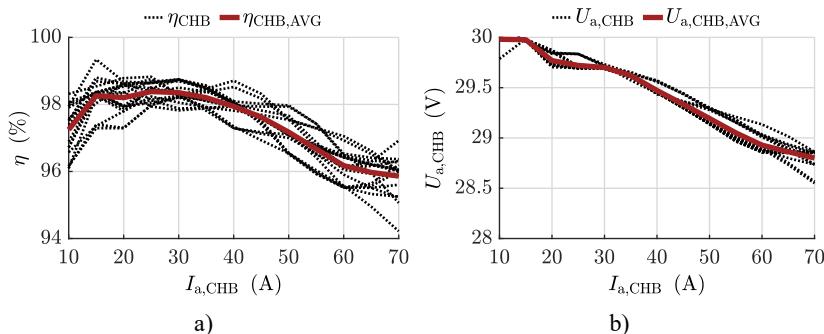

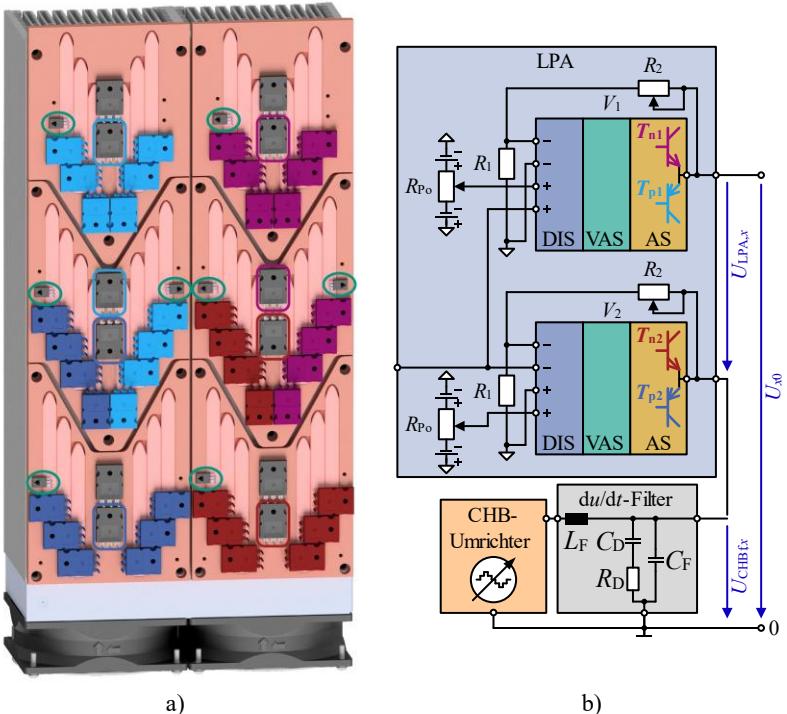

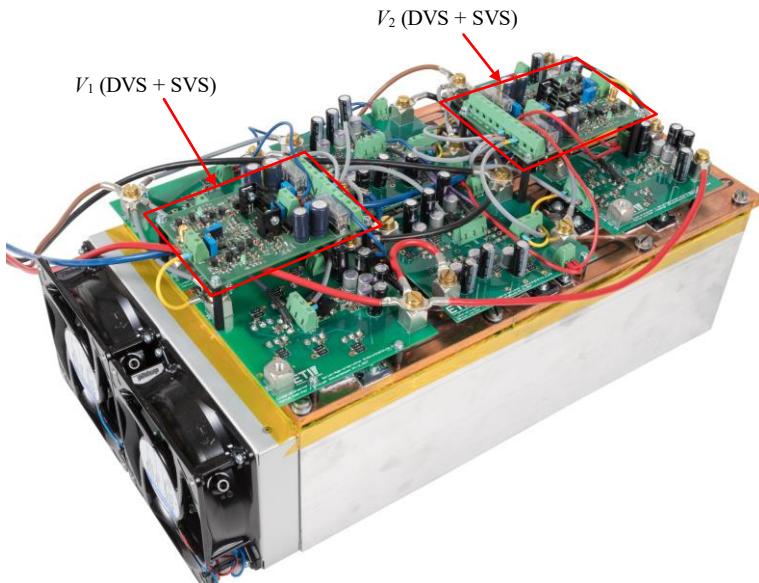

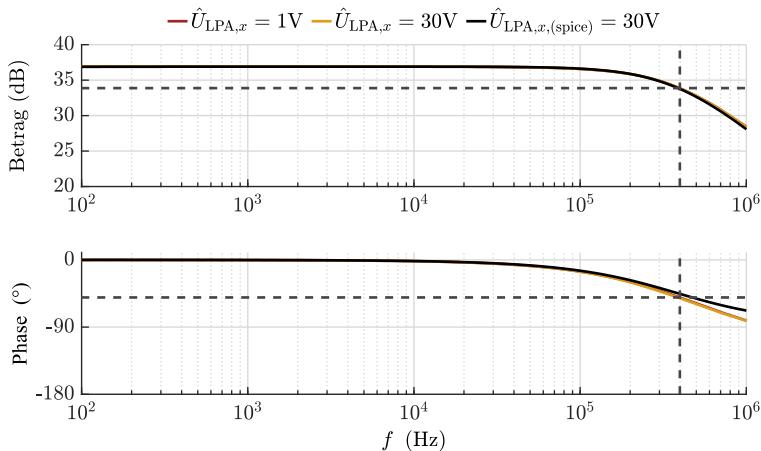

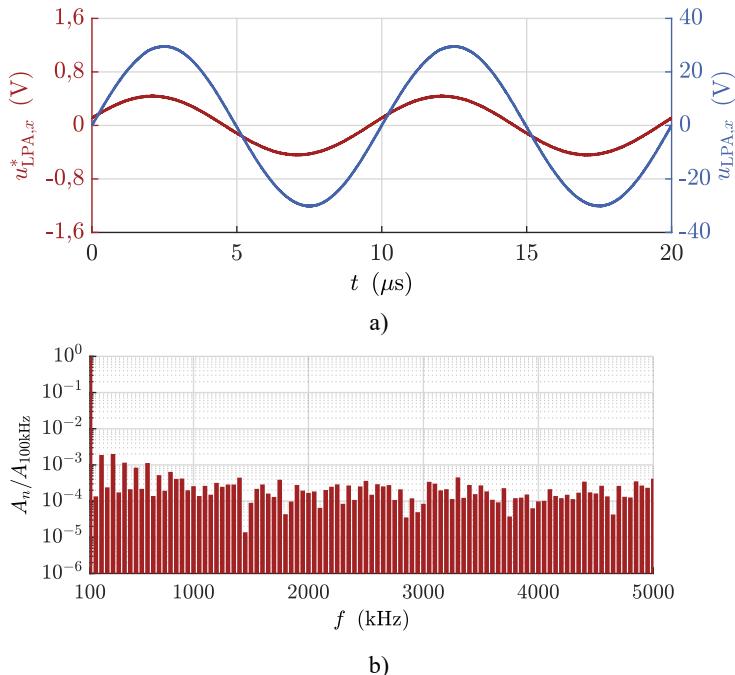

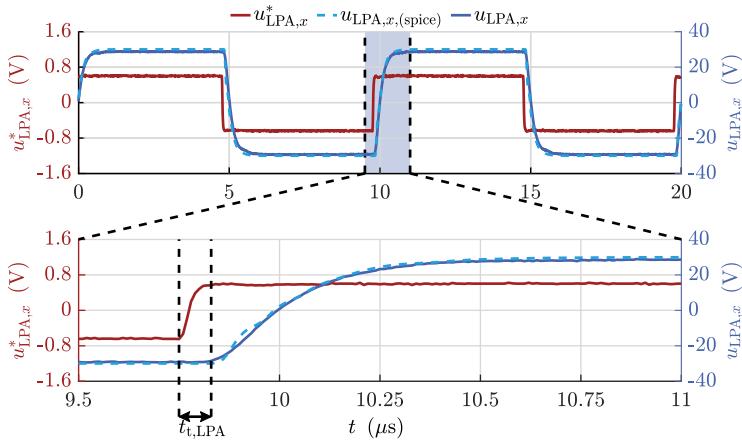

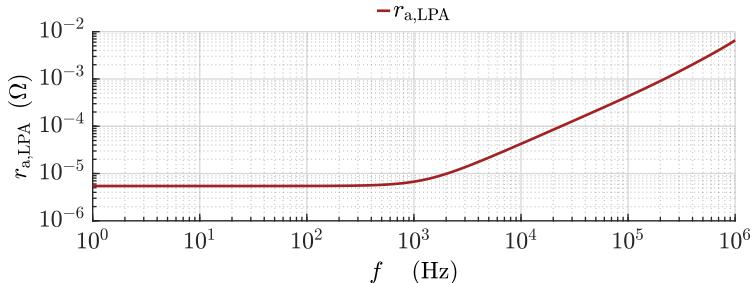

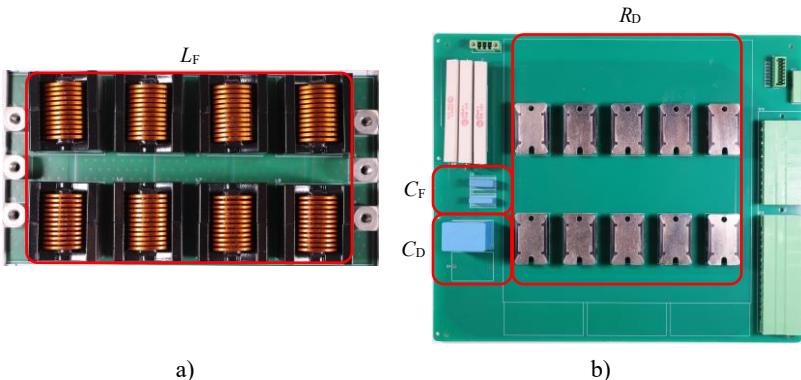

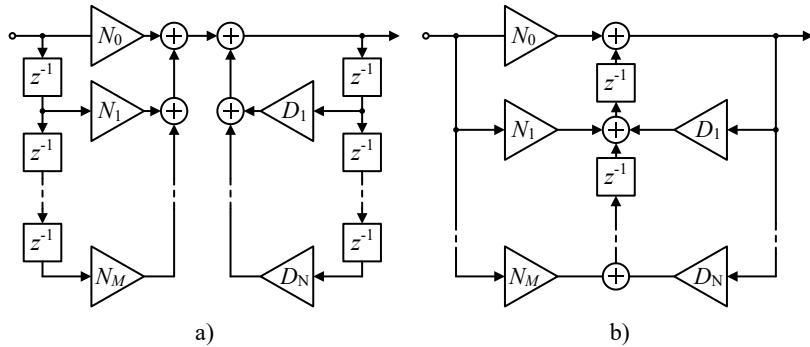

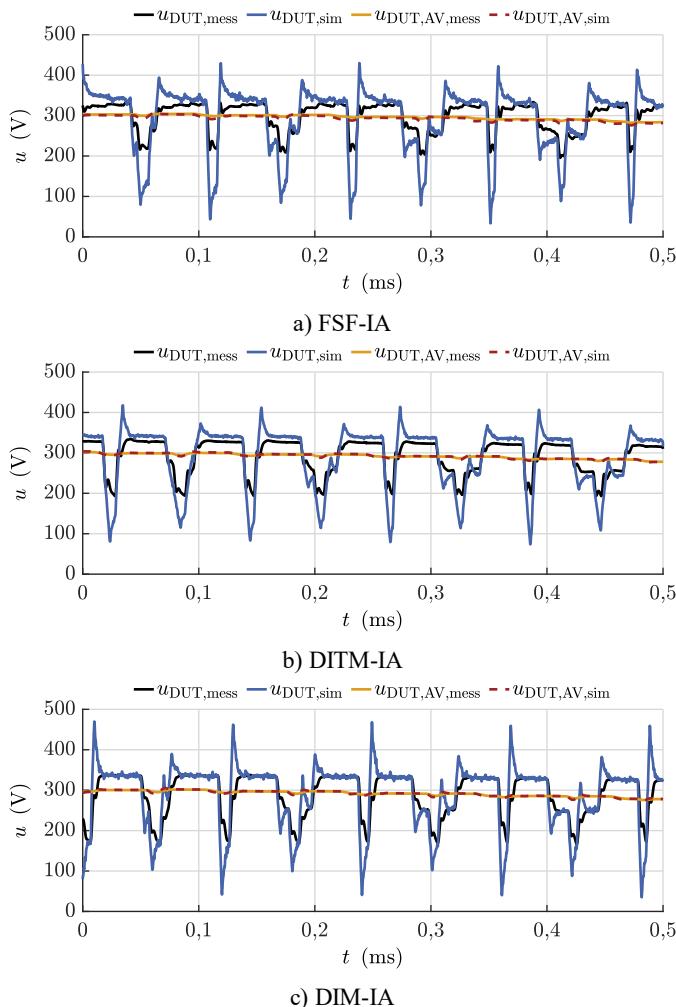

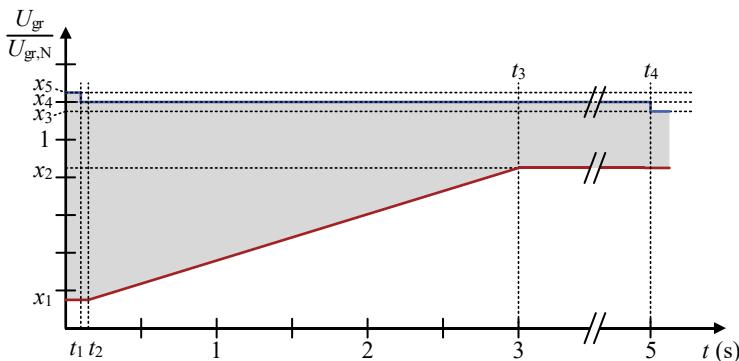

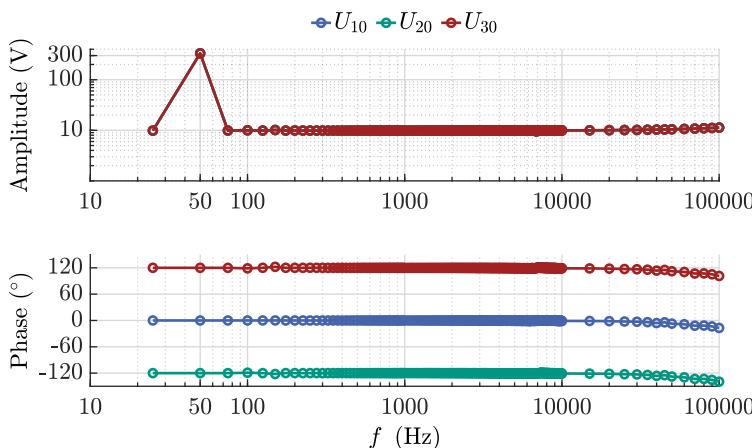

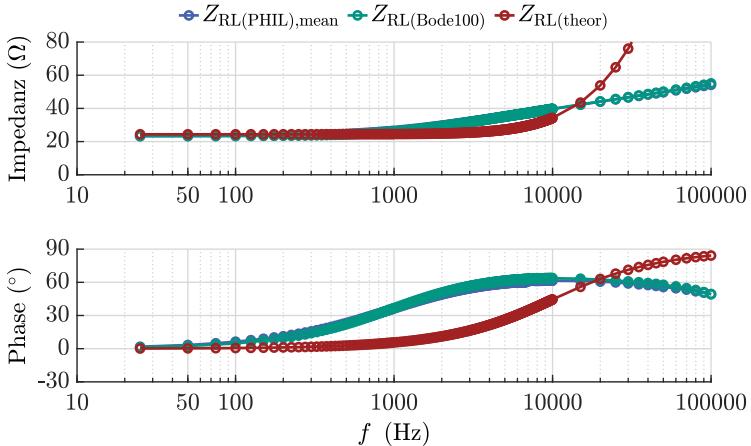

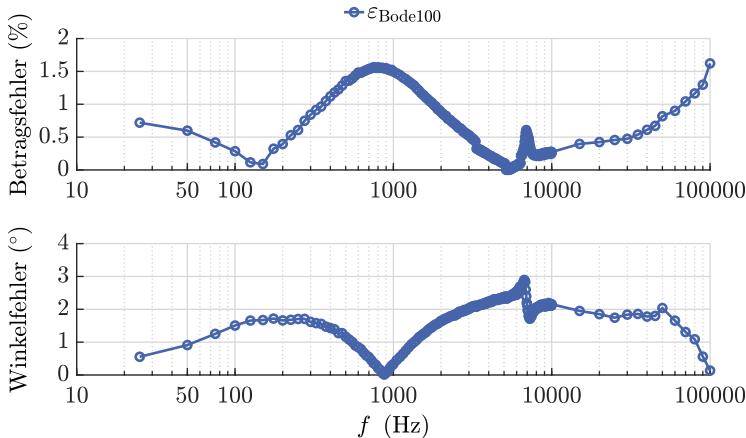

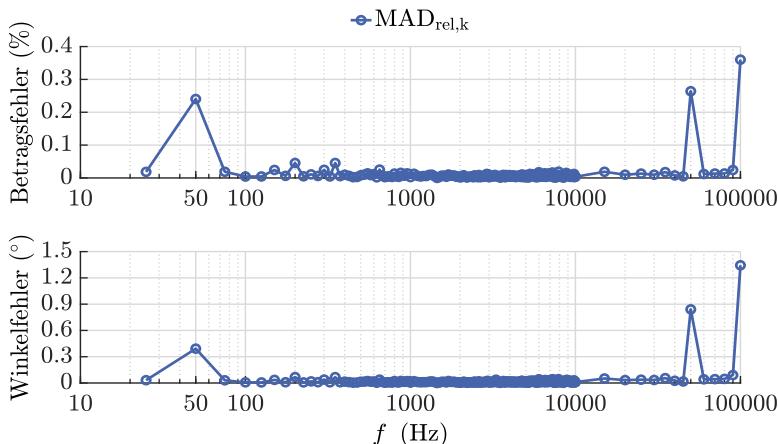

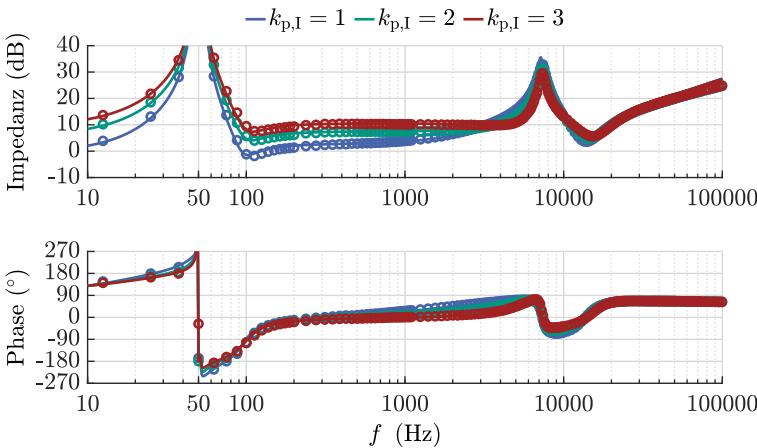

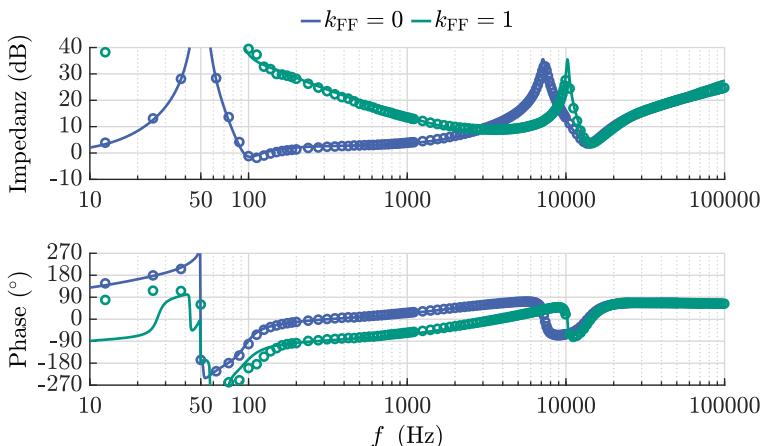

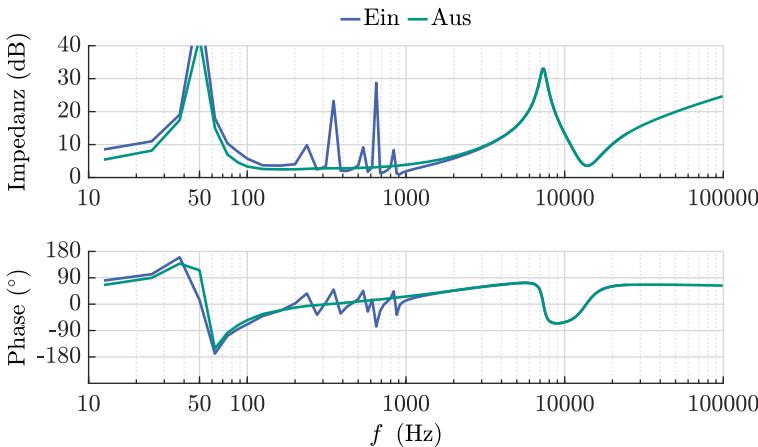

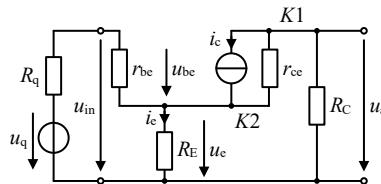

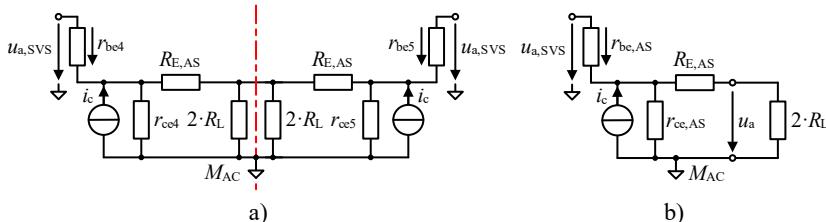

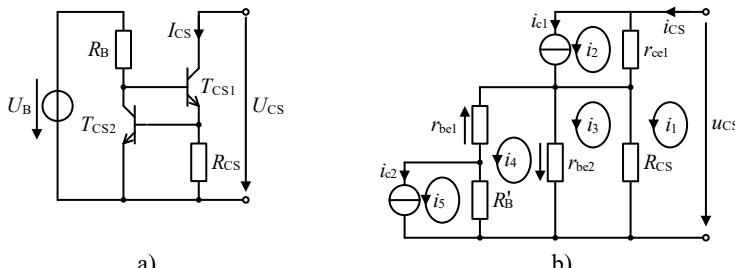

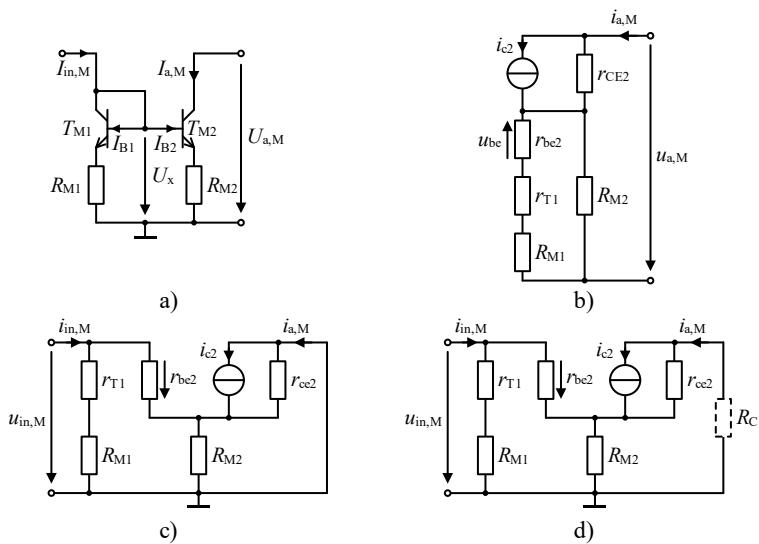

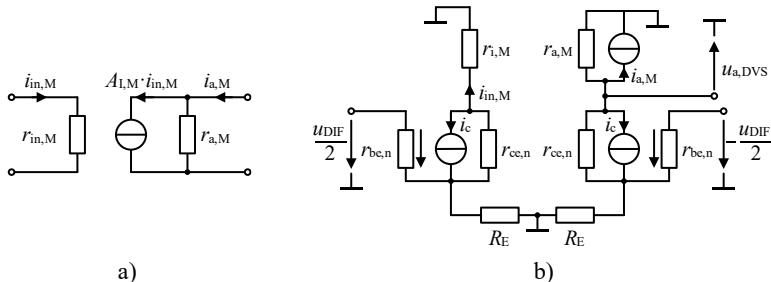

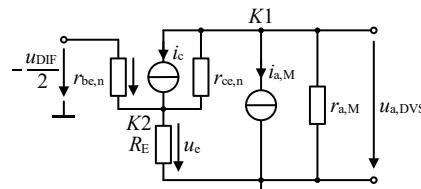

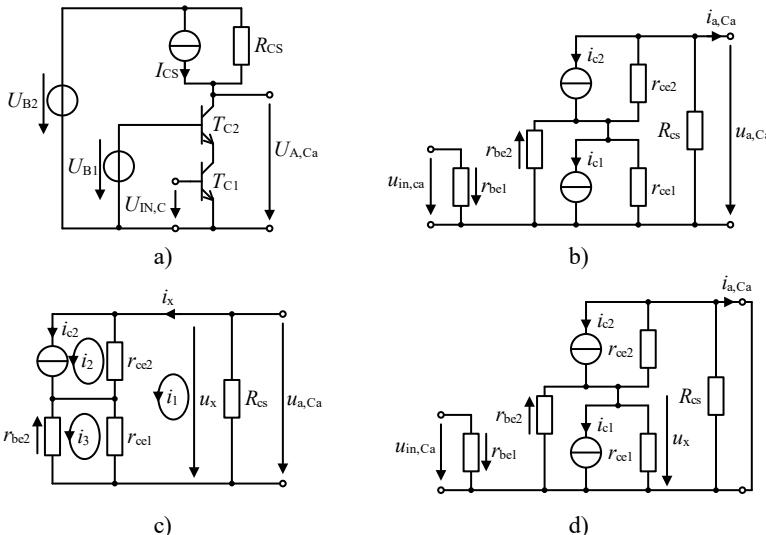

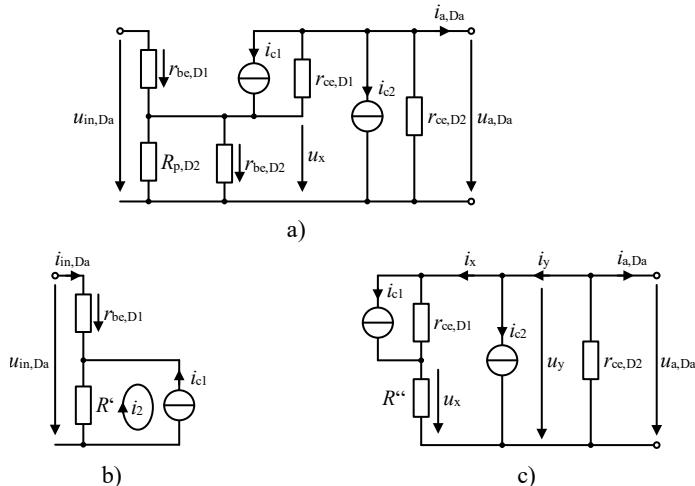

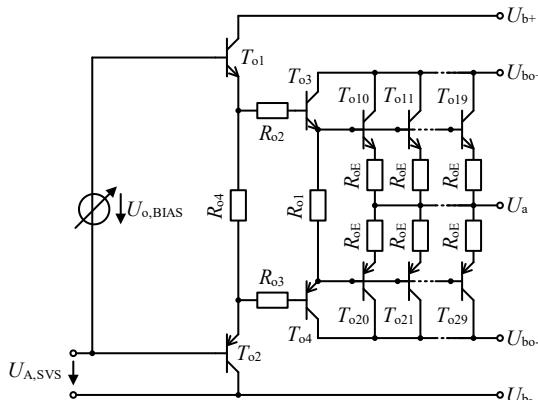

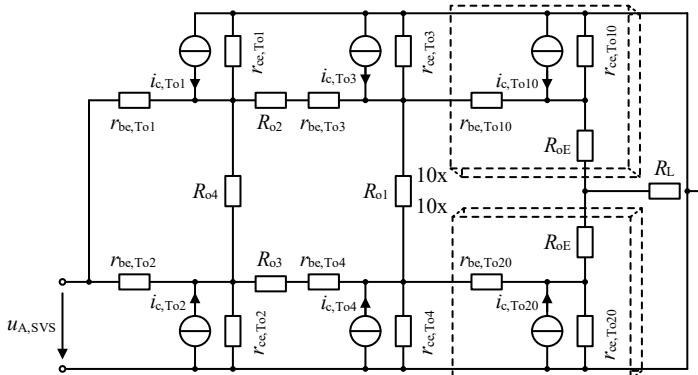

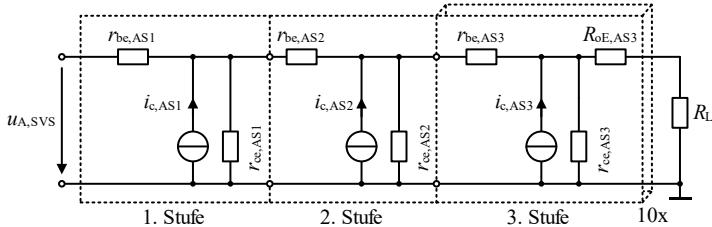

fast vollständig vermieden werden [67: S. 3, 68, 69: S. 951]. Beim Einsatz von MOSFETs ist der Betrieb im ZCS-Modus nicht zielführend, da eine Reduktion der Schaltverluste nur bedingt möglich ist [70: S. 11]. Der MOSFET ermöglicht einen bidirektionalen Stromfluss, wodurch der Strom bei einem Polariätswechsel weiter durch den MOSFET fließt und kein stromloses Ausschalten erreicht wird. Aus diesem Grund wird bei auf MOSFETs basierenden LLC-DC/DC-Wandlern, wie beispielsweise dem entwickelten DC/DC-Wandler, der ZVS-Modus verwendet.