# Application-Oriented Test Setup for Measuring Dynamic Output and Transfer Characteristics of GaN-HEMTs

1st Philipp Swoboda

2<sup>nd</sup> Martin Fein

3<sup>rd</sup> Simon Frank

Elektrotechnisches Institut (ETI) Karlsruhe Institute of Technology (KIT) Karlsruhe Institute of Technology (KIT) Karlsruhe Institute of Technology (KIT) Karlsruhe, Germany philipp.swoboda@kit.edu

Elektrotechnisches Institut (ETI) Karlsruhe, Germany martin.fein@kit.edu

Elektrotechnisches Institut (ETI) Karlsruhe, Germany s.frank@kit.edu

4<sup>th</sup> Andreas Liske

Elektrotechnisches Institut (ETI) Karlsruhe Institute of Technology (KIT) Karlsruhe, Germany andreas.liske@kit.edu

5<sup>th</sup> Marc Hiller Elektrotechnisches Institut (ETI) Karlsruhe Institute of Technology (KIT) Karlsruhe, Germany marc.hiller@kit.edu

Abstract-Apart from the excellent switching and conduction properties of power GaN-HEMTs, trapping effects are still an issue degrading the device's performance. As conventional methods have been proven inadequate for device characterization with respect to trapping, new application-oriented characterization methods have been developed in recent years. In this paper, an application-oriented test setup for measuring output and transfer characteristics is presented, which extends an existing setup for the measurement of the dynamic on-resistance. Initial results indicate that there is a significant change in characteristics dependent on the applied off-state drain voltage bias. Additionally, several typical trapping phenomena such as the dynamic on-resistance, threshold voltage shift and current collapse were observed.

Index Terms-Dynamic on-state resistance, gallium nitride high-electron-mobility transistors (GaN-HEMT), power semiconductor device characterization, conduction-losses, double pulse test (DPT), threshold voltage shift, transfer and output characteristics

#### I. INTRODUCTION

Trapping effects such as threshold voltage shift or  $V_{

m gs,th}$ shift, the dynamic on-resistance  $dR_{\rm ds,on}$  and current collapse are still present in today's power GaN-HEMTs. Those effects are mainly stimulated by applying a gate or a drain voltage bias to the device, when it is blocking. Previous investigations have shown that the impact of those effects on the device's performance depends on the magnitude and duration of the applied voltage bias [1]-[4]. In many cases, those effects are reversible, if a relaxation interval is inserted in which the biases are removed.

This work was carried out within the GaNius-programme for "Energy Efficient Power Electronics" funded by DFG (Deutsche Forschungsgemeinschaft). Name of the partial project: "Modelling and characterization of GaN-HEMT devices with respect to effects of charge carrier trapping"

Conventional methods for device characterization, as used for Si-based devices, are often inadequate, as the device is operated under idealistic conditions and not in an application-oriented scenario. The influence of trapping is neglected, since no preconditioning with drain or gate bias is applied to the device under test (DUT) prior to the measurement. To tackle that issue, several application-oriented characterization methods have been developed in recent years. In the majority of publications, the dynamic on-resistance  $dR_{\rm ds,on}$  was investigated, mostly in a modified double pulse test (DPT) setup, which is close to an actual power electronic converter [1], [5]–[7].

Further, the  $V_{

m gs,th}$ -shift phenomenon gained academic attention in recent years [2], [3]. In [2], the standardized method according to IEC60747-8-4 [8] for evaluation of the threshold voltage  $V_{

m gs,th}$  was expanded by additional circuitry to allow investigations on the  $V_{\rm gs,th}$ -shift phenomenon under consideration of drain- and gate-bias. The applied drain-bias  $V_{\rm ds}$  during the  $V_{\rm gs,th}$ -measurement was kept at a constant low voltage of 2.4 V, which is much lower than a typical  $V_{\rm ds}$  in a real hard-switching application. This, however, allows a more isolated investigation of the  $V_{\rm gs,th}$ -shift, as  $V_{\rm ds}$ -dependent effects, such as Drain-Induced Barrier Lowering (DIBL), do not occur. Strong  $V_{\mathrm{gs,th}}$ -shifts of up to  $500\,\mathrm{mV}$  were observed both under applied drain and gate bias in [2], with time constants of up to the hour range.

The test circuit presented in [3] allows  $V_{\mathrm{gs,th}}$ -measurements, whilst a  $V_{\rm ds}$ -bias of up to  $400\,{\rm V}$  is applied. Thereby, the DUT was switched under zero load current, which is more close to a real application and includes  $V_{\rm ds}$ -dependent effects like DIBL. The results show a significant time-dependent  $V_{\rm gs,th}$ -shift.

Further, the output characteristics was measured using a device analyzer. Thereby, a  $V_{\rm ds}$ -bias of 400 V was applied prior to the measurement. The result was a poorer performance of the device, indicated by an increased  $R_{ds,on}$ , a knee-point that was shifted downwards and a decreased saturation current. However, no previous work has been found that investigates those "dynamic" output and transfer characteristics in a converter-like setup, as it was done especially in the  $dR_{\rm ds~on}$ investigations [1], [4].

In this paper, a test setup is presented, which is capable of measuring both transfer and output characteristics with respect to trapping, which includes the evaluation of the threshold voltage  $V_{\rm gs,th}$ . It extends an existing test setup to investigate the dynamic on-resistance  $dR_{\rm ds,on}$  [4]. The measurement is carried out in a converter-like setup, whereby the DUT is switched under an inductive load, as often the case in a real power electronics application. Similar to [3], the threshold voltage  $V_{\rm gs,th}$  can be measured as a part of the transfer characteristics under fully applied blocking voltage  $V_{\rm ds}$  of up to  $400\,{\rm V}.$  This makes the characterization very close to the application.

The paper is structured as follows: First, the test circuit with its auxiliary circuitry around the DUT is described. This is followed by a description of the proposed measurement procedures for transfer and output characteristics. Subsequently, a short description of the practical test setup is provided. Finally, first measurements are shown and their results discussed.

#### II. DESCRIPTION OF THE TEST CIRCUITS

## A. Overview

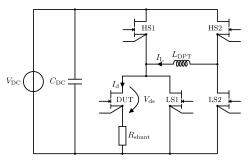

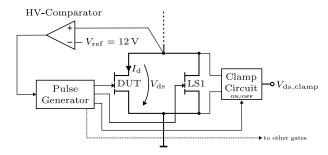

The main part of the test setup is an advanced DPT-circuit, consisting of a full bridge with one additional device LS1 connected in parallel to the DUT (Fig. 1). As with most power electronic circuits, an inductive load  $L_{\rm DPT}$  is used, which is connected between the two switching nodes. The additional

Fig. 1: Modified Double Pulse Circuit

device LS1 is required for the test procedures, to i.a. reduce the self-heating of the DUT. Its further purposes are described in the following sections.

In contrast to a conventional DPT setup, the given setup allows to control the applied drain-bias  $V_{\rm ds,IDLE}$  on the DUT,

when no measurement is performed. By switching HS1 and HS2 on,  $V_{\rm ds,IDLE}$  becomes the DC-link voltage  $V_{\rm DC}$ , whereas when LS1 and LS2 are turned on,  $V_{\rm ds,IDLE}$  becomes zero. This ability is crucial to control the trapping effects of GaN-HEMTs. The test circuit was first introduced in [4], where it

Fig. 2: Idle states for drain-bias preconditioning

was used for  $dR_{ds.on}$ -measurements. In this paper, the circuit is expanded by additional circuitry, which enables output and transfer characteristics measurements.

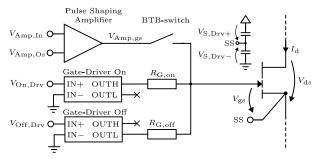

## B. Adaptive Gate Driver

As the procedure for transfer characteristics requires a slowed-down hard-switching event, the rise time at the gate needs to be adjustable down to several hundreds of nanoseconds. Further, for measuring the output characteristics at different magnitudes of the gate voltage  $V_{gs}$ , the gate driver must be capable of adjusting its output voltage. At the same time, parasitic turn-on of the DUT must be prevented, which requires a low-impedance path from the gate to the source in the off-state.

Fig. 3: Adaptive Gate Driver

To meet those requirements, an adaptive gate driver is required which is depicted in Fig. 3. It consists of a pulse shaping amplifier (PSA) and two commercially available gate-drivers [9], which are supplied by two adjustable bipolar power supply rails  $V_{S,Drv+}$  and  $V_{S,Drv-}$ . The gate-drivers feature two outputs each, one for turn-on (OUTH) and another one for turn-off (OUTL). By combining their logic inputs  $V_{\rm On,Drv}$ and  $V_{\rm Off,Drv}$  and by tieing their outputs together via the gate resistors  $R_{G,on}$  and  $R_{G,off}$ , a gate-driver with tristate-output is formed. The gate can either be left floating or be tied to  $V_{S,Drv+}$  or  $V_{S,Drv-}$  via the gate resistors (see TABLE I). Although the two gate-drivers can provide a low-impedance

path from the gate to the supply rails, they cannot adjust

TABLE I: Truth Table of the formed Tristate Gate-Driver

| $V_{ m On,Drv}$ | $V_{ m Off,Drv}$ | $V_{ m gs}$           |

|-----------------|------------------|-----------------------|

| Н               | Н                | $V_{\mathrm{S,Drv+}}$ |

| L               | L                | $V_{ m S,Drv-}$       |

| L               | Н                | Floating              |

| Н               | L                | Forbidden             |

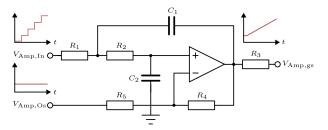

$V_{\rm gs}$  in magnitude and speed. This feature is provided by a PSA (Fig. 4), which can be connected to the gate-node of the DUT using two back-to-back (BTB)-connected transistors. Its output voltage  $V_{\rm Amp,gs}$  is controlled by the two inputs  $V_{\rm Amp,In}$  and  $V_{\rm Amp,Os}$ . Both of them are generated by a digital-to-analog converter (DAC). To filter out the stairs of

Fig. 4: Pulse Shaping Amplifier

the DAC-signal,  $V_{\rm Amp,In}$  is smoothed by a Sallen-Key low-pass filter [10], which is composed of  $R_1$ ,  $R_2$ ,  $C_1$  and  $C_2$ . Due to its low magnitude,  $V_{\rm Amp,In}$  does not fit the required range of  $V_{\rm gs}$ , which can be for instance from  $-6\,\rm V$  to  $6\,\rm V$ . Thus, amplification and offset shift is required. This feature is provided by the non-inverting amplifier part of the PSA, formed by  $R_4$  and  $R_5$ . The offset is thereby controlled by  $V_{\rm Amp,Os}$ . As  $V_{\rm Amp,Os}$  is a DC-signal, there is no need for filtering. The DC transfer function of the PSA is

$$V_{\rm Amp,gs} = V_{\rm Amp,In} \cdot \left(1 + \frac{R_4}{R_5}\right) - V_{\rm Amp,Os} \cdot \frac{R_4}{R_5}$$

(1)

Note that it is not possible that both the PSA and the gate-drivers are active at the same time. If the gate of the DUT needs to be charged with a reduced and adjustable speed to a certain magnitude, the two gate-driver outputs OUTH and OUTL need to be left floating and the BTB-switch needs to be turned on, which connects the PSA to the gate. Outside the measurement phase or when the inductor is charging, the gate potential is pulled against the  $V_{\rm S,Drv}$ -potential, providing a low-impedance path, whilst the BTB-switch is turned off.

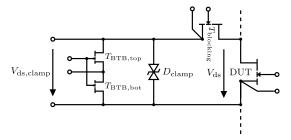

## C. Clamp Circuit

As the DUT can see blocking voltages of up to  $400\,\mathrm{V}$  while the on-state voltages are no higher than  $15\,\mathrm{V}$ , a clamp circuit is required. This enables measurements of the on-state drain voltage  $V_\mathrm{ds}$  with high accuracy, which is required for the output characteristics. The actively controlled clamp circuit is depicted in Fig. 5 and was already described in [4]. The

Fig. 5: Clamp Circuit with High Accuracy

only difference is the choice of the TVS-diode  $D_{\rm clamp}$ , which has now a higher clamp voltage  $V_{\rm clamp}$  of  $19\,\rm V$ , extending the measurement range to about  $\pm 15\,\rm V$ . With the higher measurement range, the output characteristics can be acquired for  $V_{\rm ds}$  of up to  $15\,\rm V$ .

## D. High-Voltage Comparator

A high-voltage comparator is crucial for the operation of the actively controlled clamp circuit and the measurement procedure for the output characteristics. The simplified circuitry is depicted in Fig. 6. The task of the comparator is to check whether  $V_{\rm ds}$  has fallen below a certain threshold  $V_{\rm Comp,th}$ , such as  $12\,\rm V$ . If that is not the case, the clamp circuit must

Fig. 6: Simplified Circuitry of the High-Voltage Comparator

not turn-on, to prevent damage to the clamp circuit or to the measurement equipment. This situation can be caused, for instance, when  $V_{\rm gs}$  is below  $V_{\rm gs,th}$ . In this case,  $V_{\rm ds}$  will not drop. Further, during an output characteristics measurement, the comparator has to check whether  $V_{\rm ds}$  exceeded the threshold, to turn-off the clamp circuit and to turn-on the bypass switch LS1. More details about that are given in the following section.

## III. MEASUREMENT PROCEDURES

## A. Transfer Characteristics

The procedure for measuring transfer characteristics is depicted in Fig. 7. The individual steps of the procedure are separated in time by the vertical grey bars and numbered as follows:

- (1) Inductor charging phase

- 2 Freewheeling phase

- 3 Measurement phase

- 4 Idle state

First the inductor  $L_{\mathrm{DPT}}$  is charged by switching on HS2 and LS1 ①. The duration of this phase defines the maximum drain current  $I_{\mathrm{d}}$  of interest in the transfer characteristics curve. Second, a freewheeling phase ② is inserted by only turning HS2 on, while HS1 is left in the off-state. As the current  $I_{\mathrm{L}}$  is positive, the current will flow through HS1 in reverse. Finally, the measurement phase ③ is initiated by applying a  $V_{\mathrm{gs}}$ -ramp with adjustable ramp-time  $t_{\mathrm{ramp}}$  and adjustable final value  $V_{\mathrm{gs,max}}$  to the DUT. The current slowly commutates from HS1 to the DUT as depicted in Fig. 7, while  $V_{\mathrm{gs}}$  is increasing to its final value  $V_{\mathrm{gs,max}}$ .

Fig. 7: Procedure for Transfer Characteristics Measurement

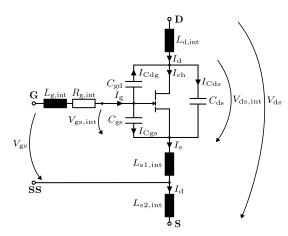

The choice of the ramp-time  $t_{\rm ramp}$  is crucial for the accuracy of the measurement. For an ideal measurement, the channel current  $I_{\rm ch}$  equals the measurable drain current  $I_{\rm d}$  and the internal gate voltage  $V_{

m gs,int}$  equals the measurable gate voltage at the terminals  $V_{\rm gs}$ . Due to the parasitic capacitances, inductances and resistances of the transistor (see Fig. 8), this can never be the exact case, as their currents and voltage drops affect the measurable quantities  $I_{\rm d}$  and  $V_{\rm gs}$ . Those parasitic effects, however, can be weakened significantly by slowing down the switching speed. Slower switching speeds also allow to filter the signals, which reduces the noise of the measurement. In contrast, when the switching speed is set too slow, the self-heating of the DUT can become excessive, as the switching energy heavily increases due to larger overlap in time of  $V_{\rm ds}$  and  $I_{\rm d}$ . Therefore, the optimal  $t_{\rm ramp}$  has to be examined by performing circuit simulations including the thermal model of the DUT.

From Fig. 7 another effect can be seen: The drain voltage  $V_{\rm ds}$  is smaller than  $V_{\rm DC}$  while the current  $I_{\rm d}$  is increasing. This voltage drop is mainly caused by the resistive elements

in the loop, such as the current shunt, the Equivalent Series Resistance (ESR) of the DC-link capacitor and the tracks on the PCB. As soon as the drain current  $I_{\rm d}$  has reached the inductor current  $I_{\rm L}$ , the main drop of  $V_{\rm ds}$  is initiated, at which  $V_{\rm DC}$  is gradually taken over by HS1.

Fig. 8: Equivalent Circuit of a GaN-HEMT with parasitics

It is apparent that the procedure is very close to a real hard-switching turn-on event. The only difference is that the switching speed of an actual application is much higher. By plotting the drain current  $I_{\rm d}$  against the gate-source voltage  $V_{\rm gs}$ , the transfer characteristics at  $V_{\rm ds}\approx V_{\rm DC}$  is obtained. After the measurement phase with the duration  $t_{\rm meas}$  is finished, either HS1 and HS2 or LS1 and LS2 will be switched on 4, to define  $V_{\rm ds,IDLE}$  to be  $V_{\rm DC}$  or  $0~\rm V$ , until the next measurement is conducted.

#### B. Output Characteristics

The procedure for the output characteristics is depicted in Fig. 9. In short, it consists of the following steps:

- (1) Charge the gate of the DUT to the desired  $V_{\rm gs}$

- 2 Measurement interval

- ③ Optional: Turn on LS1, if  $V_{\rm ds}$  exceeds 12 V

- (4) Idle state (Upper freewheeling state in the given case)

The idle state 4 is left by applying a gate-source voltage  $V_{\rm gs}$  to the DUT ①. If  $V_{\rm gs}$  is above  $V_{\rm gs,th}$ , the drain-source voltage  $V_{\rm ds}$  of the DUT will drop. Subsequently, HS2 is turned on, which causes the inductor current  $I_{\rm L}$  to rise. The maximum possible drain current  $I_d$  and on-time of the DUT is defined by the duration of the measurement interval  $t_{\text{meas}}$ , when the DUT and HS2 is turned on at the same time 2. While  $I_{\rm d}$  is increasing, the drain-source voltage  $V_{\rm ds}$  of the DUT increases as well due to the  $R_{\rm ds,on}$ . If the current  $I_{\rm d}$ is high enough for a certain  $V_{gs}$ , the saturation region is reached, which leads to a faster increase of  $V_{\rm ds}$ . In case  $V_{\rm ds}$  exceeds the comparator threshold  $V_{\rm Comp,th}$  of 12 V, the inductor current  $I_L$  will be bypassed through switch LS1, which prevents  $V_{\rm ds}$  to increase further and terminates the measurement phase. This optional step (3) is necessary to avoid destruction of the DUT due to excessive self-heating. Fig. 9 shows both cases, with and without the optional step.

Fig. 9: Raw Data of Output Characteristics Measurement at  $V_{\rm ds,IDLE}$  =  $300\,{\rm V}$

In the lower graph for  $V_{\rm gs}=3.5\,{\rm V}$ , the drain current  $I_{\rm d}$  becomes high enough to reach the saturation region and exceeds  $V_{\rm Comp,th}$ . The sudden drop of  $I_{\rm d}$  close to  $V_{\rm Comp,th}$  indicates that LS1 was switched on. Both switches are operating in parallel in this case. In the upper graph with  $V_{\rm gs}=6.0\,{\rm V}$ , the DUT remains in the linear region and the measurement is terminated, when the interval  $t_{\rm meas}$  has elapsed.

By plotting  $I_{\rm d}$  against  $V_{\rm ds}$  within the measurement interval  $\bigcirc$ , the output characteristics at the desired gate-source voltage  $V_{\rm gs}$  is obtained. After the measurement has finished,  $V_{\rm ds,IDLE}$  is applied at the DUT  $\bigcirc$ . In contrast to the procedure for the transfer characteristics, the parasitic influence on the measurement, except self-heating, is negligibly small. This arises from the fact, that the slopes of  $I_{\rm d}$  and  $V_{\rm ds}$ , that cause parasitic voltage drops and currents, are several magnitudes slower than it is the case with the transfer characteristics measurement. Nevertheless, it is reasonable to perform circuit simulations, to assess self-heating.

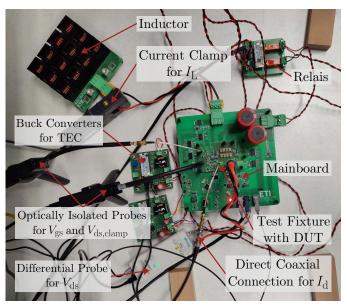

# IV. PRACTICAL REALIZATION OF THE TEST SETUP

As already mentioned, the given test setup depicted in Fig. 10 is an expansion of the one introduced in [4]. The major part is the mainboard, on which the exchangeable test fixture is mounted. Further, it contains the control circuit, which includes the circuits introduced in section II. On the test fixture, the DUT is mounted together with the test circuit depicted in Fig. 1. It further employs coaxial connectors for

Fig. 10: Picture of the Test Setup

the connection of the measurement equipment to measure the signals of interest  $I_{\rm d}$ ,  $V_{\rm gs}$ ,  $V_{\rm ds,clamp}$  and  $V_{\rm ds}$ . Both  $V_{\rm gs}$  and  $V_{\rm ds,clamp}$  are measured using two optically isolated differential probes of the type SigOFIT MOIP02P from Miscsig [11]. The current is measured using shunt-resistors with a total resistance of  $40\,\mathrm{m}\Omega$ , which are mounted on the test fixture. As the voltage drop on the shunt resistors can be very small, the voltage is measured directly with the oscilloscope via a series termination and a coaxial cable to achieve a good measurement accuracy. For additional monitoring of the applied drain-bias, the drain source voltage  $V_{\rm ds}$  is measured using a conventional differential probe. Not shown in Fig. 10 is the oscilloscope, which is a WavePro 404HD with  $4\,\mathrm{GHz}$  bandwidth, 12-bit resolution and  $0.5\,\%$  full-scale gain accuracy from LeCroy [12].

Due to the strong temperature coefficient of GaN-HEMTs, it is important to conduct the measurements at a defined temperature. This is achieved by using a thermoelectric cooler (TEC), which allows a temperature control with high dynamic [4]. The TEC is powered by two back-to-back connected buck converters, which are also shown in Fig. 10. The controlled variable is the case temperature  $T_{\rm c}$  of the DUT, which is measured with a thermally well-connected NTC-resistor.

The voltage  $V_{\rm DC}$  is provided by a high voltage power supply, whose poles are disconnected during a measurement using two relais, to reduce common-mode disturbances.

#### V. MEASUREMENTS AND DISCUSSION

## A. Measurement Conditions

The following measurements are carried out using the GS66508B GaN-HEMT with a Schottky p-GaN gate from GaN-Systems. It has a current rating of 30 A and a voltage

rating of  $650\,\mathrm{V}$ . In the off-state of the DUT, the gate-source voltage  $V_\mathrm{gs}$  is set to  $0\,\mathrm{V}$ . The charging time of the inductor  $L_\mathrm{DPT}$ , which is  $t_\mathrm{charge}$  for the transfer characteristics and  $t_\mathrm{meas}$  for the output characteristics, is always set such that the desired current  $I_\mathrm{d}$  is reached. The inductance  $L_\mathrm{DPT}$  has a nominal value of  $90\,\mathrm{\mu H}$ . Further, the case temperature  $T_\mathrm{c}$  is kept constant at  $25\,\mathrm{^{\circ}C}$  using the TEC-based temperature control. These conditions apply to all measurements.

Whenever the drain-bias  $V_{\rm ds,IDLE}$  is changed, a relaxation time of  $20\,\rm min$  is introduced to ensure that the traps are in a steady state. However, since trapping effects are also caused by any gate stress  $V_{\rm gs}$ , the influence of this on the treshold voltage  $V_{\rm gs,th}$  is the first part of the investigation. The threshold voltage  $V_{\rm gs,th}$  is defined at the threshold, when the drain current  $I_{\rm d}$  exceeds  $100\,\rm mA$ . For all transfer characteristics measurements or  $V_{\rm gs,th}$ -measurements, the ramp time  $t_{\rm ramp}$  is set to  $1\,\rm \mu s$ .

The transient junction temperature rise  $\Delta T_{\rm j}$  due to self-heating was simulated with the thermal model from the datasheet [13]. It was shown, that  $\Delta T_{\rm j}$  completely decayed within one second after a measurement. Thus, if the interval between two consecutive measurements  $t_{\rm IDLE}$  is chosen larger than one second,  $T_{\rm j}$  is not expected to accumulate. For the output characteristics,  $\Delta T_{\rm j}$  was always below  $10\,{\rm K}$  for currents  $I_{\rm d}$  of up to  $60\,{\rm A}$ . For the transfer characteristics,  $\Delta T_{\rm j}$  was  $0.5\,{\rm K}$  at  $5\,{\rm A}$ ,  $10\,{\rm K}$  at  $30\,{\rm A}$  and  $30\,{\rm K}$  at  $60\,{\rm A}$ . Consequently, except for the  $V_{\rm gs,th}$ -measurements at  $5\,{\rm A}$ , self-heating can not be neglected. However, as the pulse pattern applied to the DUT is identical with and without applied drain-bias  $V_{\rm ds,IDLE}$ , this is not expected to affect the

# B. Consideration of the Threshold Voltage Shift

general outcome of the result.

Any voltage  $V_{\rm gs}$  applied to the gate results in a  $V_{\rm gs,th}$ -shift. To acquire the characteristics, charging of the gate is essential, which in turn means that trapping at the gate or  $V_{\rm gs,th}$ -shift always occurs.

For reproducible measurements, these influences must be taken into account and by an appropriate timing of the measurements, the  $V_{\rm gs,th}$ -shift can be kept at an almost constant level. The measurements need to be conducted periodically, with a constant measurement time  $t_{\rm meas}$ , when a voltage is applied to gate and a constant resting time  $t_{\rm IDLE}$ , when  $V_{\rm gs}$  is zero.

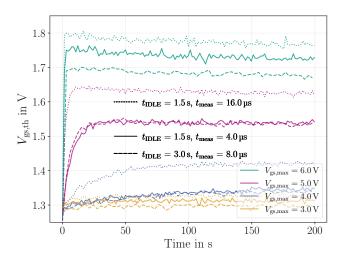

Fig. 11 shows measurements of the time dependency of  $V_{\rm gs,th}$  at different  $V_{\rm gs,max}$ ,  $t_{\rm IDLE}$  and  $t_{\rm meas}$ . The measurements were conducted at a very low  $V_{\rm DC}$  of 5 V with zero drain bias  $V_{\rm ds,IDLE}$ , to minimize the impact of drain-induced trapping and DIBL. In addition, the current  $I_{\rm d}$  was limited to 5 A, to minimize self-heating and to allow a reduced full-scale range of the oscilloscope, resulting in a more accurate determination of  $V_{\rm gs,th}$ . Between every measurement curve, the DUT rests for  $10\,{\rm min}$ , to restore the initial state of  $V_{\rm gs,th}$ . This can be

Fig. 11: Time dependency of  $V_{\rm gs,th}$ -shift

recognized by the fact that all curves start at  $V_{\rm gs,th} \approx 1.27\,{\rm V}$ . It can be seen that the greatest change of  $V_{\rm gs,th}$  for all curves occurs within the first hundred seconds. After that,  $V_{\rm gs,th}$  changes only in low tens of mV-steps. Further, the higher  $V_{\rm gs,max}$ , the higher the  $V_{\rm gs,th}$ -shift and the smaller the trapping time constant. For  $V_{\rm gs,max}$  smaller than  $3.0\,{\rm V}$ , the  $V_{\rm gs,th}$ -shift becomes negligibly small and is therefore not depicted in Fig. 11. When comparing different combinations of  $t_{\rm IDLE}$  and  $t_{\rm meas}$ , a different steady state  $V_{\rm gs,th}$  was observed in most of the cases. Two measurements are therefore only comparable, if their  $t_{\rm IDLE}$  and  $t_{\rm meas}$  are identical.

In order to obtain reproducible measurements, it is crucial that  $V_{\rm gs,th}$  is in a steady state. For the transfer characteristics measurements this state can be achieved, by always setting  $V_{\rm gs,max}$  to 6 V. In this case,  $V_{\rm gs,th}$  reaches its steady state within a couple of measurements or seconds. By only considering the last of ten consecutive measurements, the transfer characteristics measurement becomes reproducible. The output characteristic measurement, on the other hand, is associated with greater effort, as the measurements have to be conducted at different on-state  $V_{\rm gs}$ . Between each output characteristics curve, defined at a certain  $V_{

m gs}$ , a resting time of 10 min has to be inserted. Further, much more consecutive measurements have to be conducted, until  $V_{

m gs,th}$  has reached its steady state. With  $t_{\rm IDLE} = 1.5\,\mathrm{s}$  and 60 consecutive measurements, reproducible results can be produced, by only considering the last measurement.

## C. Transfer Characteristics

Two major effects, that significantly affect the transfer characteristics, are part of the investigation: The DIBL-effect and trapping induced by applying a drain-bias  $V_{\rm ds,IDLE}$  in the off-state. All measurements are conducted periodically, consisting of ten consecutive measurements, as described earlier, with  $t_{\rm meas}=4.0\,\mu{\rm s}$  and  $t_{\rm IDLE}=1.5\,{\rm s}$ .

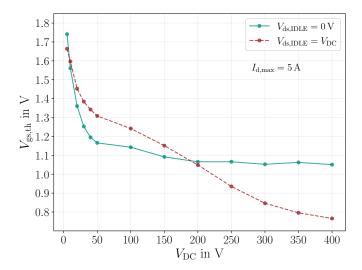

In Fig. 12 the influence of  $V_{\rm ds}$  on the steady state  $V_{\rm gs,th}$  at different  $V_{\rm ds,IDLE}$  is shown. As expected, the DIBL-effect occurs and significantly affects the threshold voltage  $V_{\rm gs,th}$ . Between  $100\,\rm V$  and  $400\,\rm V$ , this effect is noticeably stronger, if a drain-bias  $V_{\rm ds,IDLE}$  is applied in the pauses between the measurements, as the absolute sensitivity  $\|dV_{\rm gs,th}/dV_{\rm ds}\|$  is much higher. However, this is not the case within the first  $50\,\rm V$ . In this case, the curve for  $V_{\rm ds,IDLE}=0\,\rm V$  shows a stronger slope.

Fig. 12: Influence of  $V_{\rm ds}$  on  $V_{\rm gs,th}$  (DIBL-effect)

Important to mention is that  $V_{\rm gs,th}$  at zero drain bias  $V_{\rm ds,IDLE}$  and  $V_{\rm DC}=5\,\rm V$  is  $1.72\,\rm V$ , which is very close to the typical value of  $1.7\,\rm V$  from the datasheet of the DUT [13]. Here,  $V_{\rm gs,th}$  was defined at  $I_{\rm d}=7\,\rm mA$ , while the DUT was operated as diode-connected transistor.

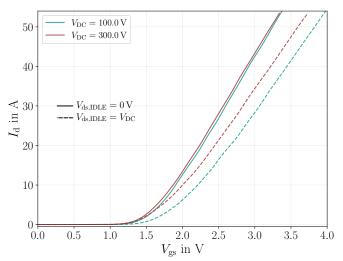

The actual transfer characteristics at chosen  $V_{\rm DC}$  and different  $V_{\rm ds,IDLE}$  is shown in Fig. 13. It can be clearly seen, that the curves for a  $V_{\rm DC}$  of 300 V increase earlier than the curves for 100 V. This indicates the DIBL-effect and coincides with the results shown in Fig. 12. As shown in Fig. 12, this effect appears to be stronger, if a drain-bias  $V_{\rm ds,IDLE}$  is applied in the off-state of the DUT. Further, the slope or transconductance  $g_{\rm m}$  of the curves differs dependent on  $V_{\rm ds,IDLE}$  and is lower, if a bias  $V_{\rm ds,IDLE}$  is applied. The transconductance  $g_{\rm m}$ , however, does not appear to be significantly affected by  $V_{\rm DC}$ .

If the average transconductance  $\hat{g}_{\rm m}$  is considered between  $10~{\rm A}$  and  $50~{\rm A}$ , the result for  $V_{\rm ds,IDLE}$  of  $V_{\rm DC}$  is about  $25~{\rm A~V^{-1}}$ . For a  $V_{\rm ds,IDLE}$  of  $0~{\rm V}$ , one obtains about  $30~{\rm A~V^{-1}}$ .

Consequently, a reduced transconductance leads to a lower current rise during switching, as it can also be seen in Fig. 7. In [3], switching transients are shown with and without applied drain-bias  $V_{\rm ds,IDLE}$ , that yield a slower current rise, after a  $V_{\rm ds,IDLE}$  was applied for  $30\,\rm min$ . Further, a turn-on loss increase of  $20\,\%$  was reported.

Fig. 13: Transfer Characteristics Comparison

#### D. Output Characteristics

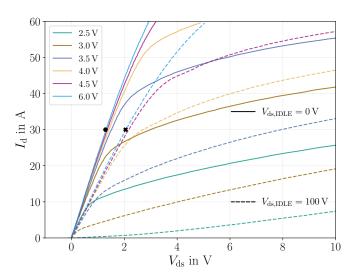

For the output characteristics measurements, a maximum drain-current  $I_{\rm d}$  of 60 A was chosen, while the resting-time  $t_{\rm IDLE}$  between two periodical measurements was set to  $1.5\,\rm s$ . As described earlier, the result was extracted only from the last measurement, after 60 measurements were performed. In Fig. 14 the output characteristics at  $V_{\rm DC}=100\,\rm V$  with

Fig. 14: Output Characteristics Comparison at  $V_{\rm DC}=100\,{\rm V}$

and without applied drain-bias  $V_{\rm ds,IDLE}$  are shown. It can be clearly seen, that the curves for an applied drain-bias  $V_{\rm ds,IDLE}$  indicate a poorer performance than the curves without bias. First, the slope of the linear region is reduced. From particular interest is the slope at  $V_{\rm gs}=6\,\rm V$ , as this refers to the on-resistance  $R_{\rm ds,on}$ . Without applied bias  $V_{\rm ds,IDLE}$ , the on-resistance  $R_{\rm ds,on}$  at the rated current  $I_{\rm d}=30\,\rm A$  is  $46.2\,\rm m\Omega$  (•), which comes close to the value of  $50\,\rm m\Omega$  from the datasheet [13]. With the bias  $V_{\rm ds,IDLE}$  applied, the on-resistance  $R_{\rm ds,on}$  is  $76.2\,\rm m\Omega$  (\*), which results in an increase

of 65 %.

Second, the knee point of the characteristics is shifted towards lower currents and the saturation current is decreased. For a  $V_{\rm gs}$  of  $2.5\,\rm V$ , the linear region seem to disappear completely and the curve looks similar to the characteristics of a diode. The decrease of the saturation current correlates with the transfer characteristics measurements, as  $g_{\rm m}$  is reduced with applied drain-bias  $V_{\rm ds,IDLE}$ . It can be assumed, that the shifted knee point, the disappearing linear region at low  $V_{\rm gs}$  and the reduced  $g_{\rm m}$  refers to the current collapse effect [14].

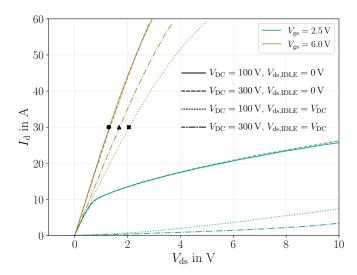

Fig. 15: Output Characteristics Comparison at different  $V_{\rm DC}$

In Fig. 15 the output characteristics at two different  $V_{\rm DC}$ ,  $100\,{\rm V}$  and  $300\,{\rm V}$ , is shown. As expected, the curves without drain-bias  $V_{\rm ds,IDLE}$  coincide. In this case, the DIBL-effect does not occur, as the DUT is switched under zero voltage. At an applied bias  $V_{\rm ds,IDLE}$  of  $300\,{\rm V}$ , the  $R_{\rm ds,on}$  is  $59.3\,{\rm m}\Omega$  (A), which is  $28\,\%$  more than the original value at  $V_{\rm ds,IDLE}=0\,{\rm V}$ . This voltage-dependency indicates the effect of the dynamic on-resistance  $dR_{\rm ds,on}$ , which is reported in earlier investigations [1], [4]. Both studies reported that the  $dR_{\rm ds,on}$  is reduced towards higher  $V_{\rm DC}$ . It should be also noted, that all three  $R_{\rm ds,on}$ -values are very close to the results from our previous  $dR_{\rm ds,on}$ -investigation [4]. In this case, the same DUT was used, but from a different batch.

## VI. CONCLUSIONS AND FUTURE WORK

Within this contribution, new methods are provided to measure the transfer and output characteristics of GaN-HEMTs in an environment that is close to an actual power converter. Those methods were already realized in a practical test setup and results were provided. The results show, that trapping stimulated by gate and drain bias significantly affects the device's characteristics. It could be shown that the effect of the dynamic on-resistance  $dR_{\rm ds,on}$  and the threshold voltage shift are present in the investigated DUT. Further, we assume that the current collapse effect still occurs, because of the i.a. reduced transconductance  $g_{\rm m}$  and the shifted knee

point, after a drain bias  $V_{\rm ds,IDLE}$  was applied for  $20\,\rm min$ .

Future studies could focus on the variation between different batches, different DUTs with different gate structures and the influence of the temperature on the characteristics. Thanks to the modular design of the test setup and the already existing temperature control using a TEC, the prerequisites for those investigations are given.

In addition, the switching losses and conduction-losses could also be investigated. An initial study already reported increased switching losses under the influence of trapping [3]. If the variation between the different batches is moderate, compact models can be developed using the obtained data, that include the influence of trapping.

#### REFERENCES

- [1] M. Goller, C. Schwabe, N. Thoenelt, G. Li, J. Lutz, and T. Basler, "Precise determination of dynamic RDSon in AlGaN/GaN power HEMTs under soft switching condition," in *PCIM Europe 2022; International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management*, 2022, pp. 1–8.

- [2] B. Kohlhepp, D. Breidenstein, and T. Dürbaum, "Test setup to study threshold voltage shift of GaN-HEMTs under short- and long-term gate and drain bias," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, pp. 1–1, 2024.

- [3] F. Yang, C. Xu, and B. Akin, "Characterization of threshold voltage instability under off-state drain stress and its impact on p-gan hemt performance," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 9, no. 4, pp. 4026–4035, 2021.

- [4] P. Swoboda, S. R. Frank, A. Liske, and M. Hiller, "Improved test circuit for characterization of the dynamic on-resistance of GaN-HEMTs over a wide operating range," in 2024 Energy Conversion Congress & Expo Europe (ECCE Europe), 2024, pp. 1–8.

- [5] E. A. Jones and A. Pozo, "Hard-switching dynamic Rds,on characterization of a GaN FET with an active GaN-based clamping circuit," in 2019 IEEE Applied Power Electronics Conference and Exposition (APEC), 2019, pp. 2757–2763.

- [6] R. Li, X. Wu, S. Yang, and K. Sheng, "Dynamic on-state resistance test and evaluation of GaN power devices under hard- and soft-switching conditions by double and multiple pulses," *IEEE Transactions on Power Electronics*, vol. 34, no. 2, pp. 1044–1053, 2019.

- [7] R. Hou, Y. Shen, H. Zhao, H. Hu, J. Lu, and T. Long, "Power loss characterization and modeling for GaN-based hard-switching halfbridges considering dynamic on-state resistance," *IEEE Transactions on Transportation Electrification*, vol. 6, no. 2, pp. 540–553, 2020.

- [8] "Discrete semiconductor devices metal-oxide semiconductor field-effect transistors (MOSFETs) for power switching applications," British Standards Institution, Standard, 2004, IEC 60747-8-4:2004.

- [9] UCC27511A Single-Channel High-Speed Low-Side Gate Driver With 4A Peak Source and 8A Peak Sink, Texas Instruments, 2024, SLUSD95A, available at: https://www.ti.com/lit/ds/symlink/ucc27511a.pdf (Oct 2024).

- [10] R. P. Sallen and E. L. Key, "A practical method of designing RC active filters," *IRE Transactions on Circuit Theory*, vol. 2, no. 1, pp. 74–85, 1955

- [11] SigOFIT Optical-fiber Isolated Probe Datasheet, Shenzhen Micsig Technology Co., Ltd., Shenzhen, Guangdong, March 2023, available at: https://www.micsig.com/SigOFIT (June 2024).

- [12] WavePro HD High Definition Oscilloscope, Teledyne LeCroy, Chestnut Ridge, NY, December 2018, available at: https://de.teledynelecroy.com/waveprohd (June 2024).

- [13] G\$66508B Bottom-side cooled 650 V E-mode GaN transistor Datasheet, GaN Systems, 2020, REV 200402, available at: https://gansystems.com/gan-transistors/gs66508b (Oct 2024).

- [14] G. Meneghesso, F. Rampazzo, P. Kordos, G. Verzellesi, and E. Zanoni, "Current collapse and high-electric-field reliability of unpassivated GaN/AlGaN/GaN HEMTs," *IEEE Transactions on Electron Devices*, vol. 53, no. 12, pp. 2932–2941, 2006.