# Virtualized Low Latency Data Acquisition Software Systems

Zur Erlangung des akademischen Grades eines

Doktors der Ingenieurwissenschaften (Dr.-Ing.)

von der KIT-Fakultät für Elektrotechnik und Informationstechnik des Karlsruher Instituts für Technologie (KIT)

angenommene

#### Dissertation

von

M.Sc. Mostafa, Jalal

geboren in Al Nakra, Libanon

Tag der mündlichen Prüfung: 28.07.2025

Hauptreferent: Prof. Dr.-Ing. Dr. h. c. Jürgen Becker

Korreferent: Prof. Dr. Marc Weber

I stand on the shoulders of the giants.

To my parents...

To my beloved Safaa...

To my siblings...

And to every person who contributed to the man I am today throughout history and in the present...

## **Abstract**

The breakthroughs in detector and computing technologies enabled researchers to observe and measure natural phenomena with higher spatial and temporal resolutions. These improvements yield scientific data at higher rates and in larger volumes. Consequently, the data acquisition systems that are responsible for collecting and reducing the data from high rates to only interesting events have grown in complexity. Despite the extensive data reduction on hardware-based functions of data acquisition systems, researchers employ software-based data reduction functions that run on a dedicated computer cluster located at the experiment's site.

This hybrid hardware-software structure of data acquisition systems imposes critical challenges on the data acquisition system's scalability and operability. As the computing cluster of software-based data acquisition functions is deployed on the experiment's site, scaling, operating, and maintaining the stability and performance of this cluster becomes a demanding responsibility that requires extensive time and manpower. Furthermore, such a computing cluster is used to measure or simulate the observed phenomena and is not shared with other studies in the same research institute. As a result, this data acquisition structure underutilizes the available computing resources and increases the costs to operate and scale the data acquisition system.

This work aims to prioritize the design and development of software-based data acquisition functions over the operational procedure to manage its local computing cluster. This thesis proposes to eliminate this cluster for all scientific experiments in a research institute, and, instead, to run their software-based data acquisition functions on widely available general-purpose campus computing facilities. Such

a shift in the execution environment minimizes the operational efforts to run a software-based data acquisition function and increases the computing resources' utilization as it shares the same resources with multiple scientific experiments while provisioning the required data transfer throughput between hardware-based and software-based functions.

To this end, this thesis proposes a new data acquisition paradigm called Data acquisition Functions Virtualization that leverages computer virtualization to isolate multiple software-based data acquisition functions running on the same host computer while sustaining their required input throughput. The thesis explores the key challenges in realizing Data acquisition Functions Virtualization within out-of-control virtualization environments like campus computing facilities and investigates which technologies are best suited for building high-throughput data transfer systems in these settings.

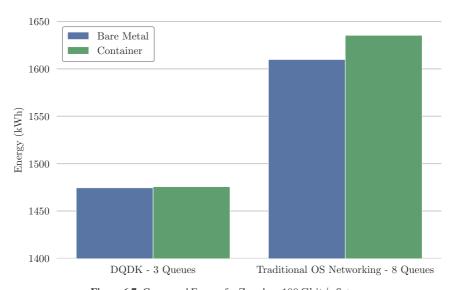

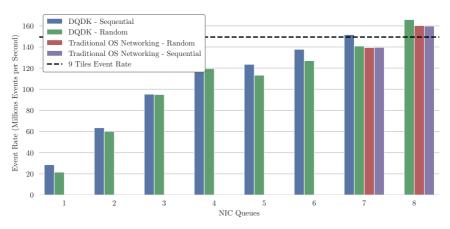

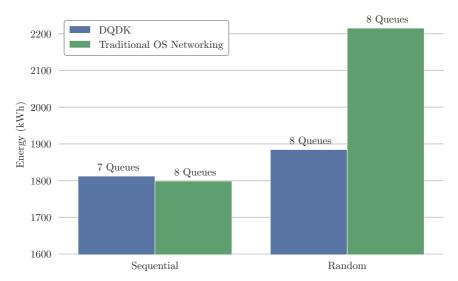

To realize Data acquisition Functions Virtualization, we propose, design, and implement the Data Acquisition Development Kit, a novel framework for software-based functions. The framework handles high-performance data transfer between detector electronics and campus computing facilities by exploiting an emerging networking technology called AF\_XDP and by adapting resource allocation to the shared execution environment of general-purpose computer systems used in campus computing facilities. We quantify the performance of the framework with and without computer virtualization, considering different computer virtualization setups. The new data acquisition paradigm is applied to the TRISTAN upgrade of the KATRIN experiment at the Karlsruhe Institute of Technology. The framework can reduce CPU resources by a factor of 2.67x and save up to 15% of the consumed energy.

# Kurzfassung

Dank fortschrittlicher Detektor- und Computertechnologien können Forscher natürliche Phänomene heute mit deutlich höherer räumlicher und zeitlicher Auflösung untersuchen. Dadurch entstehen wissenschaftliche Daten in bislang unerreichtem Umfang und mit hohen Erfassungsraten. Um aus dieser Datenflut nur die relevanten Ereignisse herauszufiltern, sind Datenerfassungssysteme zunehmend komplexer geworden. Neben der bereits umfangreichen hardwarebasierten Datenreduktion kommen zusätzlich softwaregestützte Funktionen zum Einsatz, die auf einem speziellen Rechnercluster direkt am Experimentstandort betrieben werden.

Diese hybride Struktur aus Hardware- und Softwarekomponenten stellt hohe Anforderungen an die Skalierbarkeit und Wartbarkeit von Datenerfassungssystemen. Da die softwarebasierten Funktionen auf einem lokalen Rechnercluster laufen, erfordert der Betrieb dieses Clusters erheblichen personellen und zeitlichen Aufwand – insbesondere, wenn es darum geht, Leistung und Stabilität dauerhaft sicherzustellen. Hinzu kommt, dass solche Cluster in der Regel ausschließlich für ein einzelnes Experiment genutzt werden und nicht mit anderen Forschungsprojekten innerhalb der Einrichtung geteilt werden. Das führt zu einer ineffizienten Nutzung der vorhandenen Rechenressourcen und erhöht sowohl die Betriebskosten als auch den Aufwand für eine spätere Skalierung.

Ziel dieser Arbeit ist es, den Fokus von der aufwendigen Verwaltung lokaler Rechnercluster hin zur Entwicklung und Ausführung softwarebasierter Datenerfassungsfunktionen zu verlagern. Anstatt für jedes Experiment eigene Cluster zu betreiben, wird vorgeschlagen, diese Funktionen auf allgemein verfügbaren, zentral betriebenen Rechensystemen innerhalb der Forschungseinrichtung auszuführen.

Ein solcher Paradigmenwechsel reduziert den betrieblichen Aufwand erheblich und verbessert gleichzeitig die Auslastung der vorhandenen Rechenressourcen, da mehrere Experimente dieselbe Infrastruktur gemeinsam nutzen können. Voraussetzung dafür ist allerdings, dass der erforderliche Datendurchsatz zwischen hardware- und softwarebasierten Komponenten zuverlässig gewährleistet wird.

Um dieses Ziel zu erreichen, wird in dieser Arbeit ein neues Paradigma vorgeschlagen: Virtualisierung softwarebasierter Funktionen der Datenerfassung. Dabei werden softwarebasierte Datenerfassungsfunktionen mithilfe von Virtualisierung voneinander isoliert, sodass mehrere dieser Funktionen gleichzeitig auf einem gemeinsamen Host-System betrieben werden können – ohne den erforderlichen Datendurchsatz zu beeinträchtigen. Die Arbeit untersucht die zentralen Herausforderungen bei der Umsetzung dieses Ansatzes in offenen, schwer kontrollierbaren Virtualisierungsumgebungen wie etwa campusweiten Rechenzentren. Zudem wird analysiert, welche Technologien sich am besten für eine leistungsfähige und zuverlässige Datenübertragung in solchen Szenarien eignen. Zur praktischen Umsetzung der Virtualisierung von Datenerfassungsfunktionen wird in dieser Arbeit das Data Acquisition Development Kit vorgestellt – ein neuartiges Framework für softwarebasierte Datenerfassungsfunktionen. Es ermöglicht eine performante Datenübertragung zwischen Detektorelektronik und zentralen Rechensystemen der Forschungseinrichtung, indem es auf die moderne Netzwerktechnologie AF XDP zurückgreift und die Ressourcenzuweisung dynamisch an die gemeinsam genutzte Ausführungsumgebung anpasst. Die Leistungsfähigkeit des Frameworks wird unter verschiedenen Virtualisierungsbedingungen sowohl mit als auch ohne Virtualisierung systematisch evaluiert. Anwendung findet das neue Paradigma im Rahmen des TRISTAN-Upgrades des KATRIN-Experiments am Karlsruher Institut für Technologie. Dabei zeigt sich, dass das Framework bis zu 2,67-mal weniger CPU-Ressourcen benötigt und den Energieverbrauch um bis zu 15% senken kann.

# Acknowledgements

This thesis would not have been possible with the support and guidance from many people at IPE and ITIV institutes at KIT. I want to thank my supervisors Prof. Jürgen Becker and Prof. Marc Weber for their guidance, feedback, and support throughout this journey. I am grateful to my KSETA mentor Prof. Guido Drexlin for supporting this thesis until the end. I also thank Prof. Frank Simon for his support and guidance during my time at IPE.

I thank Suren Chilingaryan and Andreas Kopmann for giving me the opportunity to be part of the IPE family. Their time they spent to support and guide this thesis and all the fruitful discussions are highly appreciated. Andreas, Suren, I am deeply grateful for your mentorship. You are the best! To my colleagues, Timo Dritschler and Nicholas Tan Jerome, thanks a bunch! Special thanks to Tanya Harbaum from ITIV for her support and time. I appreciate your assistance!

To my students: Sara Wehbe, Sandro Melissano, and the others, thank you for being part of this journey and the time we spent learning together.

I cannot but mention my family again whom I dedicate this thesis to. They are the real contributors to this thesis. For my father and my mother, I can't thank you enough. For my wife, Safaa, for her endless support during the PhD time and always, I'm truly grateful. For my eldest brother, Jaafar, for igniting the love of technology in me since I was a kid. For all of my brothers and sisters: Jaafar, Wael, Waed, and Israa, you have contributed to the person I am today and thus to this thesis, thank you! For you all, whether you know it or not, this thesis is *your* achievement.

# Contents

| A | bstra | ct                                                                   |

|---|-------|----------------------------------------------------------------------|

| K | urzfa | ssung                                                                |

| A | ckno  | wledgements                                                          |

| 1 | Inti  | oduction                                                             |

|   |       | Motivation                                                           |

|   |       | 1.1.1 The Operability Challenge                                      |

|   | 1.2   | Research Proposal and Questions                                      |

|   |       | Objectives and Contributions                                         |

|   |       | Outline                                                              |

| 2 | Bac   | kground and Related Work                                             |

|   | 2.1   | Introduction to Data Acquisition and Control Systems                 |

|   |       | 2.1.1 Anatomy of a Software-based Data Acquisition Function 14       |

|   |       | 2.1.2 Examples of Hybrid Hardware/Software Data                      |

|   |       | Acquisition in Research Infrastructure                               |

|   | 2.2   | Introduction to Data Transfer in General-Purpose Computer Systems 18 |

|   |       | 2.2.1 Key Performance Indicators                                     |

|   |       | 2.2.2 Peripheral Component Interconnect Express                      |

|   |       | 2.2.3 Networking Stacks                                              |

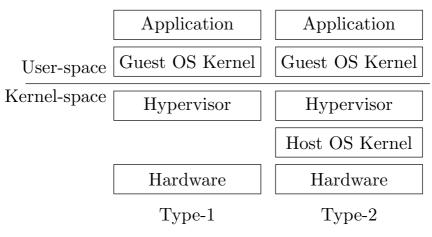

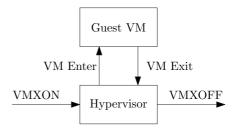

|   | 2.3   | Introduction to Computer Virtualization                              |

|   |       | 2.3.1 Virtual Machines                                               |

|   |       | 2.3.2 Containers                                                     |

|   | 2.4   |                                                                      |

|   |       | 2.4.1 Computer Virtualization in DAQ Systems                         |

|   |       | 2.4.2 High-Performance Software-based DAO                            |

| 3 | Hig | h-Pertormance Computer Networking Technologies                    |

|---|-----|-------------------------------------------------------------------|

|   |     | DFV                                                               |

|   | 3.1 | Criteria of Networking Technologies for DFV                       |

|   |     | 3.1.1 Suitability for Virtualization                              |

|   |     | 3.1.2 Resource Efficiency on Detectors' Electronics               |

|   |     | 3.1.3 High Performance                                            |

|   | 3.2 | High-Performance Networking Technologies                          |

|   |     | 3.2.1 Hardware-Assisted Technologies                              |

|   |     | 3.2.2 User-space Drivers                                          |

|   |     | 3.2.3 AF_XDP: The Express Data Path Sockets                       |

|   |     | 3.2.4 High-Performance Networking Technologies for DFV 54         |

|   | 3.3 | A Top-Down Analysis of AF_XDP Performance                         |

|   |     | 3.3.1 Experimental Setup                                          |

|   |     | 3.3.2 Results                                                     |

|   |     | 3.3.3 MPWQE Inlining Algorithm Analysis 60                        |

|   |     | 3.3.4 Inlined MPWQE in Mellanox DPDK User-space Driver 61         |

|   | 3.4 | Discussion                                                        |

|   |     | 3.4.1 Evolution of AF_XDP                                         |

|   | 3.5 | Conclusion                                                        |

| 4 | Cad | he-Aware Framework for High Performance Data                      |

|   |     | quisition Functions                                               |

|   |     | Sources of High Dispatching Latency in an AF_XDP Application . 70 |

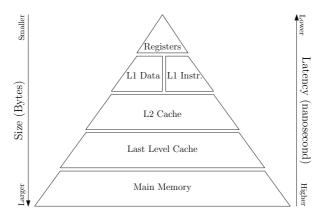

|   |     | 4.1.1 Memory Hierarchy & The Principle of Locality 70             |

|   |     | 4.1.2 The Memory Wall in Modern Computer Systems                  |

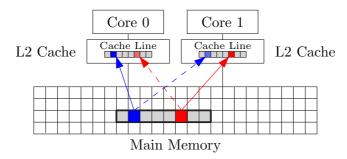

|   |     | 4.1.3 NUMA and the Principle of Locality                          |

|   |     | 4.1.4 SMP and the Principle of Locality                           |

|   |     | 4.1.5 DFV and Memory Wall                                         |

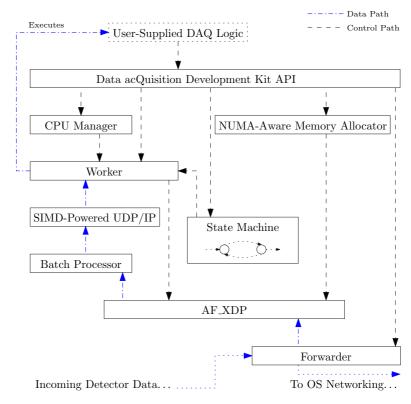

|   | 4.2 | The Data Acquisition Development Kit                              |

|   |     | 4.2.1 Design Principles                                           |

|   |     | 4.2.2 Architecture                                                |

|   |     | 4.2.3 DQDK Program Example                                        |

|   |     | 4.2.4 Design Limitations                                          |

|   | 4.3 | Performance Evaluation                                            |

|   |     | 4.3.1 Experimental Setup                                          |

|   |     |                                                                   |

|   |     | 4.3.2 Investigated Metrics                                 |

|---|-----|------------------------------------------------------------|

|   |     | 4.3.3 Benchmarking DQDK                                    |

|   |     | 4.3.4 Scaling DQDK                                         |

|   |     | 4.3.5 Performance Impact of Secure DMA 96                  |

|   | 4.4 | Conclusion                                                 |

| 5 | Vir | tualized Data Acquisition Functions                        |

|   | 5.1 | Computer Networks Virtualization                           |

|   |     | 5.1.1 Virtual Machines                                     |

|   |     | 5.1.2 Containers                                           |

|   | 5.2 | Porting DQDK to Virtual Environments                       |

|   | 5.3 | Performance Evaluation                                     |

|   |     | 5.3.1 Experimental Setup                                   |

|   |     | 5.3.2 Results                                              |

|   | 5.4 | Conclusion                                                 |

| 6 | Use | e-case: The TRISTAN Upgrade at KATRIN                      |

|   | 6.1 | The KATRIN Infrastructure                                  |

|   | 6.2 | The TRISTAN Experiment                                     |

|   |     | 6.2.1 Structure and Operational Modes                      |

|   |     | 6.2.2 The Hybrid Data Acquisition System                   |

|   | 6.3 | DFV for TRISTAN                                            |

|   | 6.4 | Implementation                                             |

|   | 6.5 | Evaluation                                                 |

|   | 6.6 | Conclusion                                                 |

| 7 | A S | calable Monitoring System in Scientific Infrastructure 127 |

|   |     | Introduction                                               |

|   |     | Process Data in Databases                                  |

|   |     | 7.2.1 ACID DBMS                                            |

|   |     | 7.2.2 Time-Series Databases                                |

|   | 7.3 | Related Work                                               |

|   |     | SciTS: Benchmarking Time-Series Databases in Scientific    |

|   |     | Infrastructure                                             |

|   |     | 7.4.1 Design Considerations                                |

|   |     | 7.4.2 Benchmark Workloads                                  |

|     |       | 7.4.3   | V        | Vo  | rk  | loa | ad  | De  | efi | ni  | tic        | n  | S   |     |    |    |    |   |  |   |   |   |   |   | <br> |  | 138 |

|-----|-------|---------|----------|-----|-----|-----|-----|-----|-----|-----|------------|----|-----|-----|----|----|----|---|--|---|---|---|---|---|------|--|-----|

|     |       | 7.4.4   | F        | er  | for | rm  | an  | ce  | N   | 1e  | tri        | cs | ;   |     |    |    |    |   |  |   |   |   |   |   | <br> |  | 139 |

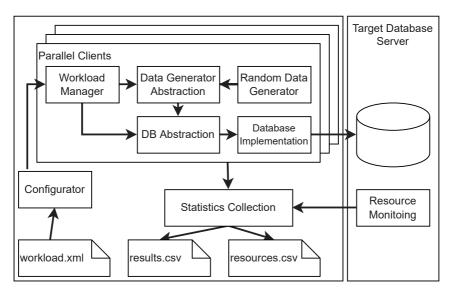

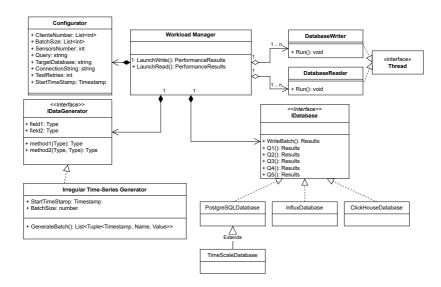

|     |       | 7.4.5   | Ί        | 'nε | e I | mŗ  | ole | me  | en  | tai | tio        | n  |     |     |    |    |    |   |  |   |   |   |   |   | <br> |  | 141 |

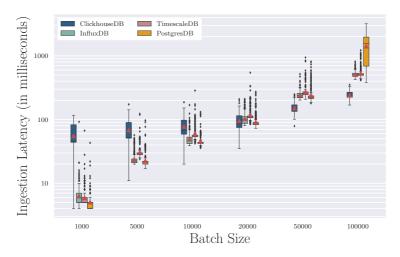

|     | 7.5   | Perfo   | rn       | ıar | 106 | e F | Eva | ılu | ati | ioı | n          |    |     |     |    |    |    |   |  |   |   |   |   |   | <br> |  | 142 |

|     |       | 7.5.1   | E        | Exp | oei | in  | nei | ıta | 1 5 | Se  | tu         | р  |     |     |    |    |    |   |  |   |   |   |   |   | <br> |  | 142 |

|     |       | 7.5.2   |          |     |     |     |     |     |     |     |            |    |     |     |    |    |    |   |  |   |   |   |   |   |      |  |     |

|     | 7.6   | Integr  | rat      | io  | n v | wi  | th  | Fie | elc | 1-1 | ev         | el | D   | ev  | ic | es |    |   |  |   |   |   |   |   | <br> |  | 155 |

|     |       | Conc    |          |     |     |     |     |     |     |     |            |    |     |     |    |    |    |   |  |   |   |   |   |   |      |  |     |

| 8   | Dis   | cussic  | on       | a   | nc  | 1 ( | Co  | nc  | lu  | ısi | <b>o</b> 1 | n  |     |     |    |    |    |   |  |   |   |   |   |   | <br> |  | 159 |

|     | 8.1   | Conc    | lu       | sic | n   | an  | d I | Res | sea | ar  | ch         | R  | les | ulı | S  |    |    |   |  |   |   |   |   |   | <br> |  | 159 |

|     |       | 8.1.1   |          |     |     |     |     |     |     |     |            |    |     |     |    |    |    |   |  |   |   |   |   |   |      |  |     |

|     |       | 8.1.2   |          |     |     |     |     |     |     |     |            |    |     |     |    |    |    |   |  |   |   |   |   |   |      |  |     |

|     | 8.2   | Futur   |          |     |     |     |     |     |     |     |            |    |     |     |    |    |    |   |  |   |   |   |   |   |      |  |     |

|     |       | 8.2.1   |          |     |     |     |     |     |     |     |            |    |     |     |    |    |    |   |  |   |   |   |   |   |      |  |     |

|     |       | 8.2.2   |          |     | _   |     |     |     |     |     |            |    |     |     |    |    |    |   |  |   |   |   |   |   |      |  |     |

|     |       |         |          |     |     |     |     |     |     |     |            |    |     |     |    |    |    |   |  |   |   |   |   |   |      |  |     |

| A   |       | _XDP    |          |     |     |     |     |     |     |     |            |    |     |     |    |    |    |   |  |   |   |   |   |   |      |  |     |

|     | A.1   | Drive   | ers      | In  | np  | leı | ne  | nta | ati | OI  | ıs         | fo | r   | 4F  |    | ΧI | )P | ) |  | • | • | • | • | • | <br> |  | 169 |

| Ac  | rony  | yms &   | s S      | yı  | ml  | bo  | ls  |     |     |     |            |    |     |     |    |    |    |   |  |   |   |   |   |   | <br> |  | 173 |

| Ri  | hline | graph   | <b>V</b> |     |     |     |     |     |     |     |            |    |     |     |    |    |    |   |  |   |   |   |   |   |      |  | 177 |

|     |       | t-Auth  | -        |     |     |     |     |     |     |     |            |    |     |     |    |    |    |   |  |   |   |   |   |   |      |  |     |

|     |       | ther Re |          |     |     |     |     |     |     |     |            |    |     |     |    |    |    |   |  |   |   |   |   |   |      |  |     |

|     |       |         |          |     |     |     |     |     |     |     |            |    |     |     |    |    |    |   |  |   |   |   |   |   |      |  |     |

| Lis | st of | Figur   | es       | ٠.  |     |     |     |     |     |     |            |    |     |     |    |    |    |   |  |   |   |   |   |   | <br> |  | 193 |

| Lis | st of | Table   | es       |     |     |     |     |     |     |     |            |    |     |     |    |    |    |   |  |   |   |   |   |   | <br> |  | 197 |

| Γiσ | stino | re      |          |     |     |     |     |     |     |     |            |    |     |     |    |    |    |   |  |   |   |   |   |   |      |  | 199 |

## 1 Introduction

### 1.1 Motivation

A scientific detector in a scientific research infrastructure consists of one or more electronic sensors that capture natural interactions with physical energy or particles in a scientific phenomenon to acquire data necessary for testing a scientific hypothesis. The data acquisition (DAQ) process is a complex online process that, during the detector operation, samples electronics signals from the scientific detector, reduces data volumes and rates by removing noise and extracting relevant data samples or regions of interest (RoI), and finally stores the data permanently for further later processing.

The breakthroughs in electronic technologies have endorsed scientists efforts to design novel scientific detectors capable of observing scientific phenomena in unprecedented details. These breakthroughs have allowed scientists to increase the measurement's spatial and the temporal resolutions leading to an increase in detectors' data volumes and rates. For example, the raw data rates of the Compact Muon Solenoid (CMS) experiment at the European Organization for Nuclear Research (known as CERN) have developed from  $100\,\mathrm{GB/s}$  by end of 2013 to  $200\,\mathrm{GB/s}$  by end of 2018 [5]. Doubling the data rates in 5 years only! Such detectors yield an everly growing data throughput that can reach several hundreds of gigabits per second [1], [6]. The data rate of the CMS experiment, for instance, is expected to grow to  $50\,\mathrm{Tbit/s}$  with the High Luminosity Large Hadron Collider (HL-LHC) [7].

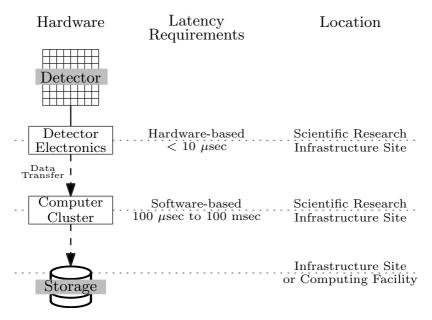

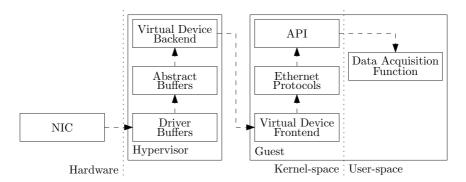

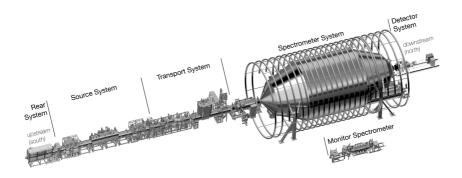

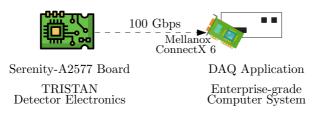

To handle the increasing data rates, scientists design hierarchical hybrid hardware-software data acquisition functions (DFs) for data reduction. Fig. 1.1 shows an

Figure 1.1: Overall Model of the Hybrid Hardware-Software DAQ

overall architecture of data reduction functions in DAQ systems. The hybrid hardware-software approach forms a compromise between performance and flexibility. Detector electronics are deployed close to the detector on the scientific research infrastructure's site and employ hardware technologies that can perform ultra-low-latency data reduction ( $<10\,\mu s$ ). Examples of such technologies are Field Programmable Gateway Arrays (FPGA) and Application–Specific Integrated Circuits (ASICs). Because of their long test and development cycles, these technologies consume scientists' efforts and time to design and test data reduction functions. After initial data reduction performed by hardware-based data reduction functions, scientists run software-based functions for further data reduction on computer clusters that are operated on the research infrastructure site. Contrary to hardware-based functions, software-based ones are easier to design and test complex reduction and feature extraction algorithms using high-level programming languages, e.g. C or Python, and parallel processing hardware and software frameworks, e.g. General Purpose Graphical Processing Units (GPGPU)

and Message Passing Interface (MPI). An example of software-based functions is High-Level Triggers (HLT) that are commonly used in several scientific research infrastructures like CMS [8] and ATLAS [9]. The transition from hardware-based to software-based functions includes data transfer of detector data from detector electronics to computer clusters. The data transfer is either performed over computer networks, e.g. Ethernet networks, or over computer buses, e.g. Peripheral Component Interconnect Express (PCIe).

### 1.1.1 The Operability Challenge

The hybrid hardware-software architecture imposes what we call the Operability Challenge. Since computer clusters of software-based data reduction functions are located at the scientific research infrastructure site, scientists have to put increasing efforts to manage and operate this computing infrastructure. The following attributes of computer clusters enforce the operability challenge:

Active System Maintenance Computer clusters of software-based data acquisition functions are composed of few to hundreds of computer systems which host and run diverse software middlewares and packages in addition to an operating system (OS). To remain fully operational and secure, these systems require active system maintenance that includes adequate system configuration and administration, troubleshooting software middleware problems, updating software packages, etc. Without such measures, the computer cluster may fail to run data acquisition functions impacting their availability, and it can get vulnerable to software security issues that may jeopardize the infrastructure of scientific instrumentation.

**Single-Purpose Under-utilized Clusters** Since these computer clusters are located at the research infrastructure site and protected by its security constraints, other research infrastructure cannot access them. They solely belong to one specific research infrastructure or scientific experiment and are sporadically utilized

when needed, e.g. a scientific measurement is being performed, or run some simulations. This may lead to under-utilization: each research infrastructure buys its own expensive hardware for the computer that is sitting idle for a considerable portion of time.

Every Research Infrastructure Operates Its Own Computer Cluster In a scientific or an academic institute, scientists usually host and operate more than one scientific research infrastructure. For example, Karlsruhe Institute of Technology simultaneously operates the Karlsruhe Tritium Neutrino (KATRIN) experiment, the Karlsruhe Research Accelerator (KARA), Far-infrared Linac and Test Experiment (FLUTE), etc., in one campus in Karlsruhe, Germany. However, every research infrastructure of them operates its dedicated computer cluster and dedicates manpower to maintain this cluster. This may lead to redundant efforts and increased costs. Contrarily, scientists should unite their computing power in shared computer clusters to minimize efforts and reduce costs.

**Low Scalability** A single unit in a computer cluster is a computer system. The performance of a computer cluster is limited by the number of its computer systems. Scaling the cluster for higher performance than its capabilities requires increasing the number of its computer systems – a complex lengthy process which involves procuring, installing, and administering of the additional computer systems.

## 1.2 Research Proposal and Questions

In this thesis, we target overcoming the operability challenge of DAQ systems by rebuilding the hybrid hardware-software architecture for better scalability and performance. We propose **D**ata acquisition **F**unctions **V**irtualization (DFV), a new DAQ paradigm that eliminates the need to operate a computer cluster in a research infrastructure. The DFV paradigm, instead, exploits computer

virtualization to run software-based DFs on campus computing facilities that are abundantly available for common use in most scientific and academic institutes. The main goal of this paradigm is to keep scientists' focus centered on the design of data acquisition functions and shift their efforts away from the operation of a local computer cluster by relying on the services provided by the shared computing facilities in an institute.

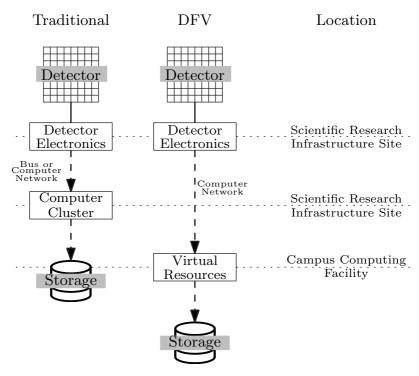

Figure 1.2: DFV vs Traditional Hybrid Hardware-Software DAQ

Fig. 1.2 shows the architecture of DFV in comparison to traditional hybrid hardware-software DAQ. In DFV, detector electronics located at the research infrastructure site still perform hardware-based DFs, but they transfer detectors' data to virtual computing resources located in campus computing facilities over

computer networks. DFV does not enforce major changes on hardware-based DFs but only requires an implementation of the used data transfer protocol to be interoperable with the software-based DFs. Since DFV can co-exist with diverse non-DAQ applications like web applications or file servers on the premises of campus computing facilities, it is important that they do not compromise each other's execution environments. DFV utilizes computer virtualization technologies for this purpose. They provide software-defined virtual execution environments that ensure peaceful coexistence of diverse applications by isolating each application in a sandbox that cannot access other sandboxes.

The shift to virtual computing resources on campus computing facilities have significant advantages in regard to the operability challenge compared to the traditional hybrid DAQ paradigm. Campus computing facilities are highly-scalable shared reusable computing resources. Therefore, using them instead of local computer clusters eliminates the efforts to operate a dedicated computing cluster in every research infrastructure and offloads system maintenance to the computing department of the owner institute. Multiple research infrastructures and scientific experiments can consequently use the computing resources of campus computing facilities at the same time which increases the utilization of computing resources in these facilities. Computer virtualization and their abundant computing resources provide easy means to scale DFs on demand without procuring additional hardware. Additionally, computer virtualization employ automatic software-defined mechanisms to support the DFs' availability which would reduce scientists efforts to monitor and track DFs' availability.

DFV runs on general-purpose computer systems in campus computing facilities. These systems can be black boxes of hidden hardware architectures, configurations, and software middlewares. Therefore, DFV should be resilient to adapt to diverse state-of-the-art technologies used on campus computing facilities.

The cornerstone and main challenge of DFV is zero-loss data transfer of detector's data from detector electronics to virtual computing resources in campus computing facilities over computer networks. This is important to ensure the integrity of scientific data in research infrastructure [10]. Without reliable data transfer

between DFs, scientific research infrastructure is exposed to probable data loss on the way from detector electronics to virtual computing resources in campus computing facilities rendering the whole infrastructure defective. A major reason for data loss is the *Slow Receiver* problem where the software-based DF, the receiver in our case, drops detector data because it cannot process the stream fast enough due to high data transfer latency [11]–[13]. While there exists some computer networking technologies of low data transfer latency to solve the *Slow Receiver* problem, not all of them might be suitable for campus computing facilities and DFV. Therefore, we raise the following question:

Question 1: What are the qualifications to choose a suitable networking technology for Campus Computing Facilities and DFV?

Based on these qualifications, we raise the second question in this thesis:

Question 2: What networking technology is a good compromise between performance and these qualifications to realize DFV?

Unlike traditional hybrid hardware-software DAQ, campus computing facilities share resources among diverse applications. It is probable and likely that these applications might interfere with each. In addition, general-purpose computer systems in campus computing facilities are not tuned and optimized for applications that demand low-latency like DFV. This brings us to raise to the following question in this thesis:

Question 3: What are the sources of higher data transfer latencies in general-purpose computer systems of campus computing facilities?

Scientists in research infrastructures usually lack the technological expertise to tackle such complex technical optimizations. Therefore:

Question 4: How can we autotune a general-purpose computer system for DFV without significant intervention from scientists?

Computer virtualization is an integral component of DFV. It protects DFs from unwanted malicious accesses from other applications. However, security comes in for a performance cost in computer systems. Therefore, we raise the question:

Question 5: What is a computer virtualization model that can handle hundreds of gigabits per second in throughput?

## 1.3 Objectives and Contributions

In this thesis, we argue that conventional data transfer technologies used in commodity computer networks are not reliable to realize DFV. An alternative reliable data transfer technology is required to realize DFV. Therefore, we will define the qualifications that would make a data transfer technology suitable for DFV as raised in Question 1. Based on these qualifications, we will survey available data transfer technologies, and we assess their performance to nominate one for DFV as discussed in Question 2. This thesis will also look at the challenges raised by deploying DFs on virtual computing resources on shared general-purpose computer systems like that of campus computing facilities in comparison to local computer clusters like that of the traditional hybrid architecture. We will study these challenges and propose the adequate tuning and mitigations as discussed in Questions 3 and 5. A framework will be proposed to provide easy-to-use DFV-based DFs without significant intervention from scientists to answer Question 4.

#### 1.4 Outline

The rest of the thesis is organized as follows:

**Chapter 2** will discuss the required preliminaries and background for a full understanding of this thesis. In the direction of DAQ systems, we will specifically discuss their overall hardware-software architecture, the anatomy and the reliability of a software-based DF, and finally we provide examples of traditional hybrid hardware-software DAQ architecture from real scientific infrastructures and experiments. The chapter also discusses the basics of conventional data transfer and how received data is processed in commodity networks from the point it reaches

the hardware of a computer system to the point is ready to be processed by the user application. We also compare DFV to state-of-the-art efforts to incubate computer virtualization and high-performance data processing in scientific research infrastructure and experiments.

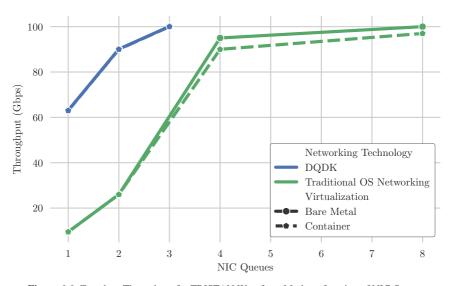

**Chapter 3** inducts a survey of computer networking technologies to perform reliable data transfer. The chapter discusses the criteria that qualify a computer networking technology for DFV from the perspectives of computer virtualization and the requirements of DAQ systems. Based on these criteria, we choose a computer networking technology called AF\_XDP. The rest of this chapter reasons why AF\_XDP is suitable for DFV in terms of performance and maturity and in comparison to other conventional and high-performance networking technologies.

**Chapter 4** studies the challenges of running a software-based DF on shared general-purpose computer systems. It discusses the problems that may rise due the computer and the memory architecture of these systems and measures their impact on performance. We will propose mitigations to tune and optimize the performance in these systems through a software framework called the Data Acquisition Development Kit in order to realize DFV.

**Chapter 5** quantifies the performance impact of computer virtualization setups on DFV. We study hardware-based and software-based network virtualization for both virtual machines and containers as computer virtualization technologies.

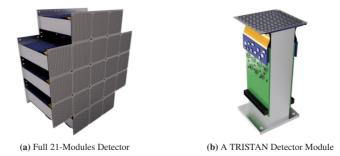

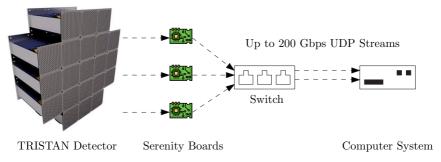

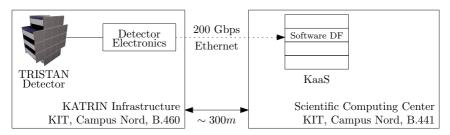

**Chapter 6** applies DFV on the TRISTAN detector as a use case of a hybrid hardware-software DAQ architecture. The chapter will introduce the TRISTAN detector, its operational modes, and its requirements. We will provide insights on DFV in real-life use cases through the TRISTAN detector.

**Chapter 7** proposes a new methodology for monitoring detector systems. It focuses on improving the performance of storing and accessing process data that usually monitors a detector DAQ system to ensure its robust operation. The chapter looks at time-series databases as an alternative to state-of-the-art ACID-based databases. We propose a benchmark named SciTS to evaluate different databases to manage process data and consequently propose a novel monitoring system for scientific infrastructure.

**Chapter 8** concludes this thesis with insights about DFV and its applicability to real-world scientific infrastructure and experiments. The chapter discusses the limitations of our contributions. It opens horizons for future works that can support DFV in particular those related to new computer and memory architectures like Smart Network Interface Cards and GPGPUs.

# 2 Background and Related Work

# 2.1 Introduction to Data Acquisition and Control Systems

A data acquisition and control system manages the data flow in research infrastructures and scientific experiments. It collects data from its sources, e.g. electronic components, makes it available to the scientists through computer storage, and preserves its integrity during the collection process.

For the successful operation of a research infrastructure, scientists install heterogeneous data sources, e.g. one or more detectors and other sensors of heterogeneous technologies. This produces different data forms and requirements inside a research infrastructure e.g. detector readout data, fast control data, and slow control data. All are important to the operation and experimental integrity of the scientific experiment and should be permanently stored to ensure the successful operation of a scientific experiment.

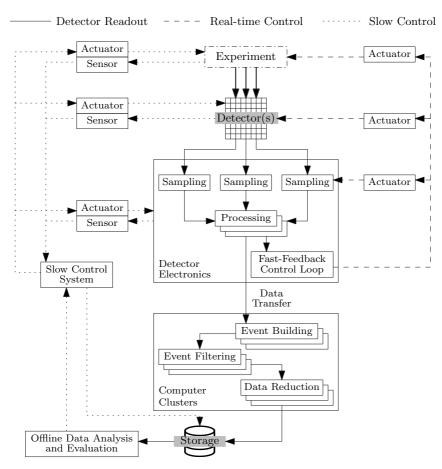

We can arrange a data acquisition and control system into 3 logical systems: the readout system, the fast-feedback control system, and the slow control system. We explain each logical system architecture and requirements by inspecting the data flow in a research infrastructure. Fig. 2.1 shows the data flow in a data acquisition and control system.

Detecting and measuring a natural phenomenon is performed by a system called the detector. A detector is a system of electronic sensors of physical properties that react to interactions with nature under certain circumstances by producing electromagnetic signals. These signals represent the interactions with nature in

Figure 2.1: Data Flow in Data Acquisition and Control Systems

addition to accumulated noise throughout the measurement procedure. Without collecting and processing these signals, we cannot derive meaningful scientific conclusions. Detector electronics are a group of electronic circuits systems that sample and convert the detector's electromagnetic signals from analog to digital signals. They also perform the required data processing to extract the needed information from the detector's signals. This type of data is called detector readout. Detector electronics are implemented using low-latency electronics e.g.

Field-Programmable Gate Array (FPGA), Application-Specific Integrated Circuit (ASIC), etc. Since these electronics implement complex data processing algorithms, their resources are considered scarce where efficient algorithms implementations are resource-efficient ones [14]–[17]. In addition, modern detector systems generate enormous amounts of data volumes and rates due to their high spatial and temporal resolution. For example, the data rates in the CMS experiment at CERN are expected to grow from 100 GB/s by end of 2013 to 200 GB/s by end of 2018 [5], and they are expected to grow up to 6.25 TB/s in the next few years [7]. Therefore, scientists employ a hybrid hardware-software DAQ architecture which provides high flexibility and extensible computing resources. Further data processing can be performed on a computer cluster to implement resourcedemanding algorithms like data compression and feature extraction algorithms. Examples of tasks performed in a computer cluster are: event building, event filtering, and data reduction. Event building is the process where one or more digital signals from detector electronics are constructing in an event that represent the natural phenomenon, e.g. particles' collision in a particle accelerator. Constructing events is followed by filtering interesting events using an algorithm that is specific to the goal of the research infrastructure. Data reduction helps reduce and compress the data even further if needed. Examples of such a computer cluster in research infrastructure are high-level triggers (HLT) and event filtering farms. This computer cluster use high-performance computing technologies like the Message Passing Interface (MPI) and General-Purpose Graphical Processing Units (GPGPU) programming. The data transfer between detector electronics and a computer cluster is performed over computer networks, e.g. Ethernet, computer buses, e.g. Peripheral Component Interconnect Express (PCIe), or serial links. The output data of this computer cluster is stored on persistent computer storage for the subsequent offline data analysis process.

Some research infrastructures require real-time feedback from detector electronics to the detector and other subsystems to control certain parameters of the experiment. An example is controlling micro-bunching instabilities in synchrotron light sources [17]. Due to their real-time constraints, such control systems are implemented on ultra-low latency detector electronics. A mechanism, known as

the Fast-feedback Control Loop, generates a control decision based on the processed data available from other detector electronics components. The generated decision is then implemented using actuators to change specific parameters in the detector electronics, the detector itself, or other subsystems of the research infrastructure.

The command center of a research infrastructure is the slow control system. It has 3 main tasks: (1) to control subsystems with *no* real-time constraints, e.g. power supplies, temperatures, high voltages, magnetic fields, etc. across the research infrastructure; (2) to collect data from sensors with slow data rates and volumes, e.g. temperature, magnetic fields, etc.; (3) to make the data available to scientists through visualization software and computer storage; (4) and to provide human-machine interfaces to initiate subsystems and start the operation of the research infrastructure.

This thesis focuses on improving the data flow of detector readout. It studies alternatives of using a computer cluster through employing campus computing facilities.

# 2.1.1 Anatomy of a Software-based Data Acquisition Function

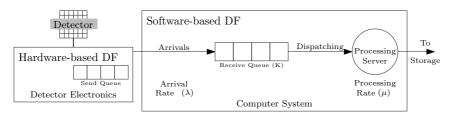

Figure 2.2: A Conceptual Model for Software-based Data Acquisition Functions

A software-based DF is a queuing-based system. Its conceptual model is shown in Fig. 2.2. After detector electronics complete the execution of hardware-based DF, processed detector data is transmitted to the software-based DF running on

a computer system. The transmission process involves submitting chunks of detector data to the Send Queue in the hardware-based DF that is responsible for managing transmission operations. Detector data exiting the Send Queue are dispatched to the data transfer medium, e.g. bus or computer network. The data transfer medium delays the arrival at the software-based DF to complete the transmission process, we denote this by  $\tau_{transfer}$ . The data arrival at the softwarebased DF is measured through the Arrival Rate denoted by  $\lambda$ . A software-based DF controls the *Receive Queue*, a queue of constant size K to buffer detector's data until it gets its turn for data processing. The end goal of a software-based DF is to execute its data reduction logic. Therefore, data is first dispatched from the Receive Queue by the processing server. The dispatching process also involves latency because the data passes through a medium from the Receive Queue to the processing server, e.g. copying from one memory buffer to another, we denote this latency by  $\tau_{dispatching}$  The processing server executes the data reduction algorithm, e.g. a feature extraction algorithm. Processing latency, denoted by  $\tau_{processing}$ , is defined by the time taken to finish the execution of a single algorithm run and therefore the processing rate is defined by:

$$\mu = \frac{1}{\tau_{processing} + \tau_{dispatching}} \tag{2.1}$$

The total latency from the moment detector's data exits the detector electronics to the moment it is ready for departure from the processing the server in the software-based DF can be calculated as follows:

$$\tau = \tau_{transfer} + \tau_{dispatching} + \tau_{processing} \tag{2.2}$$

According to queuing theory, to prevent data loss the following equation has to be satisfied:

$$\mu \ge \lambda$$

(2.3)

This property is defined as the stability of the queuing system. If the system gets unstable, i.e.  $\mu < \lambda$ , the software-based DF starts to lose data. The system's stability can then be achieved through scaling the system. There are

3 ways to scale the system: (1) increase queue size to provide a larger buffer that can accommodate more incoming received data while waiting their turn for processing; (2) increase the processing rate  $\mu$  through multiple processing servers that concurrently dispatch from the queue; (3) decrease dispatching latency from the queue which increases the processing rate.

# 2.1.2 Examples of Hybrid Hardware/Software Data Acquisition in Research Infrastructure

For better understanding of this thesis, we provide three examples of renown research infrastructures that employ a hybrid hardware-software DAQ architecture.

#### 2.1.2.1 **DUNE**

The Deep Underground Neutrino Experiment (DUNE) is an international experiment aiming to explain the origin of matter, the Grand Unification Theory, and formation of neutron stars and black holes by studying neutrinos, the most abundant particle in the universe [18]. DUNE runs 2 neutrino detectors in a beam of intense neutrino beam. The first detector (or the near detector) will record particle interactions near the neutrino beam source at the Fermi National Accelerator Laboratory in Batavia, Illinois, United States. A larger detector (or the far detector) will be deployed 1300 kilometers away from the neutrino beam and more than 1 kilometer underground at the Sanford Underground Research Laboratory in Lead, South Dakota, United States.

To simplify construction and operational efforts of the far detector DAQ, it will adopt a hybrid hardware-software DAQ architecture. The current far detector prototype at CERN divides the DAQ process into 2 components: hardware-based DAQ and software-based DAQ. Both components of the prototype will be interconnected through standard Ethernet protocols e.g. User Datagram Protocol (UDP) over a  $100~{\rm Gbit/s}$  link. The far detector electronics will reduce  $\approx 15~{\rm Tbit/s}$  to a  $200~{\rm Gbit/s}$  waveform. The software-based DAQ component

will take the 200 Gbit/s waveform as its input. It exploits Single Instruction Multiple Data (SIMD) parallel instructions on x86 computer systems to perform online reduction of electronic noise. The main component, however, is the high-performance data transfer that is performed through the Data Plane Development Kit, a third-party software library for high-performance networking technologies. Future work is scaling this software system to 400 Gbit/s detector readout [19].

#### 2.1.2.2 CMS at CERN

The CMS is a scientific experiment at CERN to look for evidence of physics beyond the Standard Model in physics by recording collisions of heavy ions at the Large hadron Collider (LHC) particle accelerator. Its notable achievement is the discovery of the Higgs-Boson particle. CMS adopts a hybrid hardware-software DAQ architecture: CMS's detector electronics perform a front data reduction system (better known as the Level-1 Trigger System) and pass its output to a computer cluster known as the High Level Trigger (HLT) and neighboring the detector at Point 5 in the LHC [20]. The HLT performs event reconstruction and filtering for particle identification and collisions [8].

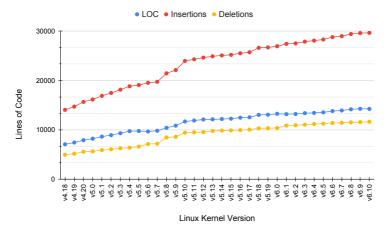

The CMS experiment has been performed in runs of 2-3 years with long shutdowns in between for major detector and hardware upgrades. Throughout the CMS's runs, its data rates and volumes has enormously increased. In Run 1 (2011-2012), the HLT at CMS was designed to accept  $100\,\mathrm{kHz}$  1 MB-events ( $100\,\mathrm{GB/s}$ ), its output rate to persistent storage was  $\approx 1.2\,\mathrm{GB/s}$  [8]. The HLT at Run 1 has  $13000\,\mathrm{CPU}$  cores and was interconnected to Level-1 Trigger system using serial links and a Myrinet network [5]. Run 2 (2015-2017) increased the input data rate to  $200\,\mathrm{GB/s}$  because the event size increased to  $2\,\mathrm{MB}$ , the output data rate of the HLT has also increased to  $\approx 3\,\mathrm{GB/s}$ . The number of CPU cores also increased to 16000 interconnected to the detector electronics using BSD Sockets over  $10\,\mathrm{GbE}$  and  $40\,\mathrm{GbE}$  Ethernet [5], [21]. The input rate of Run 3 (2022-2024) remained the same in total, however the HLT algorithm has changed requiring higher performance and so has the HLT itself. Its output rate increased to  $\approx 5.5\,\mathrm{GB/s}$ . The number of CPUs in the HLT increased to 25600 cores and

the HLT was augmented with 400 NVIDIA T4 GPGPUs for the first time [22], its interconnects to the detector electronics were also upgraded to 100 GbE Ethernet [23]. Run 3 ended in 2024 and scientists at CERN are preparing for the High-Luminosity LHC upgrade which will increase the data rates to unprecedented values. It is expected that CMS detector in Run 4 and Run 5 will reach up to  $750\,\mathrm{kHz}$  events of size up to  $6\,\mathrm{MB}$  yielding up to  $6.25\,\mathrm{TB/s}$  as input data rate to HLT, its output rate will reach up to  $\approx 31\,\mathrm{GB/s}$  [7].

#### 2.1.2.3 Belle II

The Belle II experiment is a particle physics experiment deployed at the SuperKEKB particle accelerator in Tsukuba, Ibaraki prefecture, Japan. Its goal is to study the properties of B mesons particles. The Belle II infrastructure is formed of mainly the pixel detector and 6 secondary detectors. The event rates of the secondary detectors can reach up to  $200\,\mathrm{MHz}$ . To overcome this high event rate, it employs a hybrid hardware-software DAQ architecture. The detector electronics reduce the event rates of the Belle 2 secondary detectors to  $30\,\mathrm{kHz}$  at maximum each of  $100\,\mathrm{kB}$  in size. This is fed to the Belle 2 high-level trigger (HLT) which will reduce the event rates to  $10\,\mathrm{kHz}$  each of  $200\,\mathrm{kB}$  in size by reconstructing unpacked data from the secondary detectors into new events. The new events are then filtered and used to provide tracking information to calculate regions of interests in main detector data. The HLT employs  $\sim\!6000\,\mathrm{CPU}$  cores in 2024 and interconnects with detector electronics through a third-party software library called ZeroMQ [24].

# 2.2 Introduction to Data Transfer in General-Purpose Computer Systems

DFV's cornerstone is efficient data transfer in general-purpose computer systems of campus computing facilities. Therefore, it is important to study this process including any inefficiencies.

Data transfer between distributed computer systems is a complex process that involves the participation of the hardware, the operating systems, and user software of computer systems to complete the task.

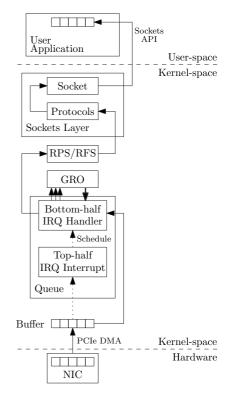

Figure 2.3: Data Transfer Flow inside a Modern Computer System

Fig 2.3 shows the data flow of the data transfer process and the main involved components. A modern computer system has a network interface card (NIC) connected as a peripheral device to the computer system from one side and to other computer systems through a physical link. The physical link employs a physical medium of predefined capacity (or bandwidth) that carry the signal from one computer system to another, e.g. Twisted Pairs, Twinaxial, Fiber Optics, etc. The computer's CPU and NIC communicate via a bus, e.g. modern computer systems extensively use the Peripheral Component Interconnect Express (PCIe) bus. However, this is not sufficient to use and interact with the NIC hardware. The operating system of this device runs an implementation of the NIC driver which defines methods to communicate with the NIC hardware and integrates it within the operating system (OS) of the computer system. The operating system also runs a networking subsystem, called the networking stack, that runs common logic that sits between the operating system and the user application. Components of the networking stack could be: data transfer protocols to reliably move data between heterogeneous computer systems, e.g. the Internet Protocol (IP) or the User Datagram Protocol (UDP), hardware interrupt management, application programming interfaces (APIs), etc. Both the NIC driver and the networking stack runs in a high privileged environment that have direct unmanaged access to all hardware components, this layer is called the operating system kernel-space. Contrarily, the user application interacts with the networking stack through its APIs and runs in an unprivileged execution environment that can only access the NIC hardware by delegating the process to the operating system and its internals.

The rest of this section will discuss each of the components involved in the data transfer process and provide insights about measuring their performance.

### 2.2.1 Key Performance Indicators

The performance of data transfer in general-purpose computer systems is measured as whole due to the interference of all components involved in this process. In this section, we focus on 3 performance indicators that summarize the overall performance of the data transfer system:

**Throughput** is a measure of how much data can pass through the data transfer system in a second. In digital data transfer systems, throughput is measured in bits per second. In practical applications, real throughput does not reach the full capacity (the bandwidth) of the physical link. This is due to overhead by data transfer protocol and line encoding used for synchronization between the sender and the receiver.

**Round-Trip Latency (RTT)** is a measure of how much time it takes to send a data request to a computer system and then receive a response back. Round-trip latency includes the time taken to traverse all the components of Fig. 2.3 4 times (sending request, receiving request, sending response, receiving response) in addition to the time taken to process the request and issuing a suitable response. It is measured in milliseconds or microseconds.

**One-way Latency** is a measure of how much processing time does a received chunk of data take from the moment it reached the NIC hardware to the moment it is available for processing by the user application. In other words, it is the time taken for a received chunk of data to traverse all the components in Fig. 2.3. In this thesis, we also call it dispatching latency. Dispatching latency is usually measured in microseconds.

## 2.2.2 Peripheral Component Interconnect Express

Peripheral Component Interconnect Express (PCIe) is as a data transfer bus that connects peripheral devices like NICs to the CPU where the device driver, interrupt handlers, the networking stack, and further data processing are executed. PCIe's design supports any peripheral device that implements its protocol, and therefore it is not limited to NICs, but it can also accommodate storage and GPU devices among others. However, it is important to remark that PCIe is a different interconnect from PCI, its predecessor, with varying speeds and features. For example, PCIe uses a serial bus architecture compared to the shared parallel architecture of PCI. This section explains PCIe architecture, protocol, and its mechanisms to perform data transfer between the NIC and the host computer.

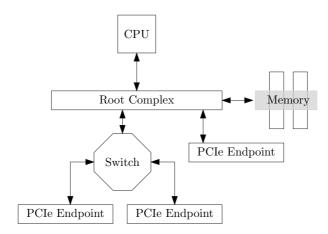

#### 2.2.2.1 PCIe Architecture

PCIe connects PCIe endpoints, i.e. peripheral devices, to the CPU and main memory of the host computer using a point-to-point connection. Fig. 2.4 shows the architecture of PCIe. A PCIe Domain consists of a single Root Complex, main memory, a processor, and PCIe-compatible devices. The Root Complex establishes PCIe connection by generating requests on behalf of the CPU which is interconnected over a local bus. The Root Complex can connect more than one PCIe endpoint, each over a direct interconnect to the Root Complex or by cascading multiple PCIe endpoints over a PCIe switch. A PCIe device's access to main memory is configured through a process called enumeration which builds a device memory map for the operating system by querying each PCIe endpoint device connected to the Root Complex. During this process, the operating system of the host computer assigns configuration tables to set up a map of accessible memory addresses of each PCIe device. There are types of configuration tables: Type 0 Configuration Table and Type 1 Configuration Table. The Type 1 Configuration Table is owned by the host operating systems and contains a map of memory addresses for all available PCIe devices. On the other hand, Type 0

*Configuration Table* is owned by the PCIe device consisting from a copy of the memory map corresponding to this PCIe device.

Figure 2.4: The Architecture of a PCIe Domain

Unlike PCI, PCIe performs all point-to-point interconnects using dedicated serial buses. This means every PCIe endpoint is connected to Root Complex on separate serial links. A PCIe *lane* consists of 4 serial links to perform *Dual Simplex* communication that assigns 2 serial links for transmitting data and 2 other links for receiving data. A PCIe endpoint uses at least x1 lane and up to x32 lanes depending on its throughput requirements and the host computer's configuration. The lanes' throughput is also a function of the PCIe generation that both the PCIe device and the host computer hardware are capable of. For example, PCIe 4.0, whose standard was introduced in 2019, is capable of  $\sim$ 2 GB per lane. As a result, a 100 Gbit/s NIC that is connected over PCIe 4.0 needs at least x8 PCIe lanes of bandwidth (in total  $\sim$ 16 GB/s) to accommodate the full 100 Gbit/s throughput ( $\sim$ 12.5 GB/s).

### 2.2.2.2 PCIe Protocol

The communication between the CPU and the peripheral devices over PCIe lanes uses the PCIe Protocol. The specification of the PCIe protocol describes 3 layers: the Physical Layer, the Data Link Layer, and the Transaction Layer [25]. It is responsible for all communication between the PCIe device and the CPU including data and control messages like interrupts and that used in the configuration space.

The Physical Layer The Physical Layer (PHY) is the closest layer to the serial links in the PCIe protocol and is responsible for actually transmitting and receiving data over the PCIe links. It is divided into 2 sub-layers: the logical and the electrical sub-layers. The logical sub-layer prepares the received packets from the serial links for the Data Link Layer and the sent packets coming from the Data Link Layer for transmission over the serial links. This process involves three primary stages: *data scrambling* to reduce the possibility of electrical resonances on the link, *encoding* for clock recovery, and *packet framing* to identify where a packet starts or ends. On the other hand, the electrical sub-layer transform data in electrical signals that can be transmitted over the serial links by converting parallel data from the logical sub-layer to a serial stream and vice versa.

The Data Link Layer The Data Link Layer has 3 responsibilities for the PCIe link: (1) sequence the packets of the Transaction Layer for identification, (2) ensure reliable delivery through acknowledgements, (3) initialize and manage flow control credits. For transmission, PCIe generates a sequence number and calculates a link cyclic redundancy check (LCRC) for each outgoing Transaction Layer Packet (TLP) as seen in Fig. 2.5. Once received, the receiver checks the sequence number and compares the LCRC to its recalculation to ensure the data link layer packet correctness. If the packer is correct, the receiver sends an acknowledgement (ACK) to the sending PCIe device, otherwise a negative acknowledgement (NAK) is sent requesting re-transmission. The sending device waits until an ACK is received. If ACK is not received after a timeout or if NAK is received, the sending device re-transmits the packet again. The data link layer

also generates and consumes data link layer packets, e.g. ACKs and NAKs, power management messages, and flow control credit information. Flow control credit information are issued by the receiver to the transmitter and provide information about its capability to reliably receive TLPs in order to receive congestion and subsequent re-transmission.

The Transaction Layer The Transaction Layer is the final layer in the PCIe protocol and is the one responsible for forming PCIe requests. Each PCIe request then becomes a TLP or a transaction. Each PCIe generation can process a predefined number of transactions per second. For example, PCIe 4.0 is capable of 16 billion transactions per second. The TLP contains information about the PCIe request in its header that represents control information including the sender and the receiver addresses, in addition to the payload (for example the data to be sent over PCIe), and another cyclic redundancy check for reliable data transmission called End to End Cyclic Redundancy Check (ECRC). The payload size of a TLP ranges from 128 B to 4096 B. The selected payload size is negotiated between the PCIe device and the host computer hardware and honoring the supplied user configuration.

| Layer | PHY   | Data Link | Transaction |          |      | Data Link |

|-------|-------|-----------|-------------|----------|------|-----------|

| Data  | Start | Sequence  | Header      | Payload  | ECRC | LCRC      |

| Size  | 4     | 2         | 12 - 16     | 0 - 4096 | 4    | 4         |

Figure 2.5: PCIe Packet Format and Size in Bytes, as of PCIe 3.0

Fig. 2.5 shows the overall format of a PCIe packet as of PCIe 3.0 in addition to the data sizes (in bytes) for each element in every layer of the PCIe protocol. While the payload of a PCIe transaction is up to  $4096\,\mathrm{B}$ , it has a protocol overhead of  $22\,\mathrm{B} - 30\,\mathrm{B}$ . Larger payload size can increase throughput of the PCIe bus by reducing the transmitted headers and consequently the protocol overhead, but it can increase latency by waiting to accumulate the bytes needed to fill one TLP.

Practical configurations often range from  $128\,\mathrm{B}$  to  $1024\,\mathrm{B}$  and thus increasing the protocol overhead.

### 2.2.2.3 PCIe Device Discovery and Configuration

In addition to devices' memory maps, the enumeration process that is initiated by the host computer constructs the PCIe configuration address space. During this process, the host computer and PCIe protocol exchange information to identify the device address, its vendor, and its class (storage, networking, GPU, etc.) and to negotiate the PCIe generation, lanes and the maximum payload size based on the capabilities and the configurations of the PCIe device and the host operating system. The enumeration process also includes mapping the *Base Address Registers* (BAR) of the PCIe device to main memory to enable the host computer to write configuration to the PCIe device like Type 1 and Type 0 Configuration Tables. This process is usually done during computer startup by the BIOS or the operating system. However, the PCIe protocol also supports *hot swapping* PCIe devices where they can be plugged in or out at runtime without rebooting the system and consequently constructing the configuration space happens at runtime by the operating system.

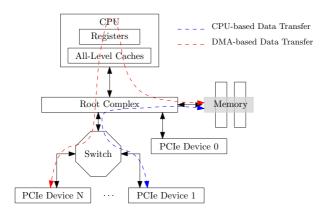

### 2.2.2.4 PCIe Data Transfer via Direct Memory Access

While PCIe BARs provide means for data transfer between the CPU and the PCIe device, they are not suitable for bulky data transfer. PCIe devices use *Direct Memory Access* (DMA) to perform this kind of data transfer where the PCIe device directly writes to and reads from the main memory through the Root Complex without involving the CPU and its caches. Before DMA being introduced as a data transfer mechanism, peripheral devices relied on the CPU to fetch the device data to its registers and caches as an intermediary buffer for writing the data to main memory. This device-to-memory data transfer mechanism is inefficient as it includes unnecessary memory copies to the CPU caches and registers in addition to handling several CPU interrupts that are involved in the completion

Figure 2.6: CPU-based vs DMA-based Data Transfer in Peripheral Devices

of this process. Alternatively and as seen in Fig.2.6, DMA-capable PCIe devices reduces the CPU involvement in the data transfer by directly acting as bus masters that can access the main memory with high privileges similarly to a CPU. A PCIe device operating as a bus master implements a configurable component called the DMA Engine which manages access to main memory through the main memory addresses provided by the operating system. To perform DMA, the DMA engine in a PCIe device requires contiguous memory to prevent the need to assemble and disassemble scattered buffers. The mechanism of assembling and disassembling scatter buffers is called Scatter-Gather DMA. Another mechanism is to provide an overlaying layer of addresses, also known as input/output virtual addresses, that are contiguous from the PCIe device perspective but can be mapped to non-contiguous physical memory. This technique requires the availability of a memory management unit (MMU) for PCIe devices similar to that used by CPUs to translate virtual contiguous addresses to their corresponding scattered physical addresses. Modern computer systems call this device the I/O Memory Management Unit (IOMMU).

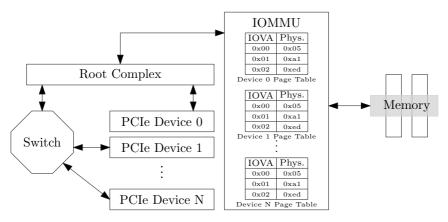

Figure 2.7: IOMMU and its Page Table with respect to the PCIe Bus

### 2.2.2.5 Input/Output Memory Management Unit

While the IOMMU is not part of the PCIe specification itself, it plays a major role in driving data transfer for PCIe devices. It allows each peripheral device have allows each device to have its own per-device contiguous virtual address space and takes over the responsibility of translating each device's address space to the corresponding physical addresses where the actual DMA buffers are located. This has 2 main advantages: (1) Contiguity: the virtual addresses of a device, hereby called I/O Virtual Addresses (IOVA), are also contiguous but can be mapped to non-contiguous DMA buffers in memory without using Scatter-Gather DMA; (2) Security: instead of accessing the whole host computer address space (i.e. main memory physical addresses), the IOMMU - through per-device virtual address spaces - isolates each device from accessing other devices' buffers or other applications' memory which may lead to leaking of sensitive information or data corruption in memory.

As seen in Fig. 2.7, the IOMMU sits between the main memory and the Root Complex to translate per-device IOVAs to physical addresses. Each device is assigned a data structure called a *Page Table* in the IOMMU. A page table is a list of entries that contains mappings between a device's virtual address and its

corresponding physical memory. While virtual addresses are typically contiguous from the peripheral device perspective, they can be mapped to scattered physical memory in the main memory. Therefore, IOVAs mask the memory access to the DMA buffers and provide a transparent mechanism to overcome scattered DMA buffers without relying on Scatter-Gather DMA. Each peripheral device has the same virtual address space as the other devices, but they have different mappings in the IOMMU as each page table belongs one and only one device. For example, address 0x01 in 2 different peripheral devices is mapped to 2 different physical addresses, each mapping uses the corresponding page table of the corresponding peripheral device. This isolates the peripheral device from other devices by limiting its address space to that of IOVAs and prevent memory accesses to physical addresses that they should not have privileges to and, thus, prevent leaking sensitive information from other applications' memory.

The security concern is a highly important concern in computer virtualization scenarios like is the case of DFV. Without IOMMU, a PCIe device belonging to one virtual machine can freely access the memory of another virtual machine because the device is configured to access the address space of physical memory. This is especially important for DFV in order to build secure data acquisition functions in campus computing facilities where diverse applications from different backgrounds and users should run *securely* together.

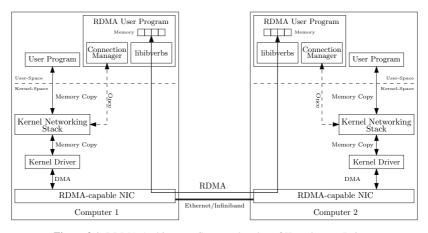

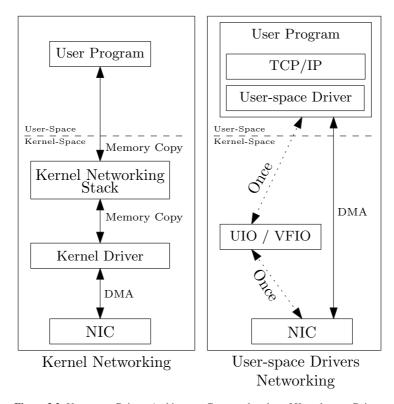

### 2.2.3 Networking Stacks

Networking stacks in OS kernels is a complex software system that provide data transfer services to user applications through user-space APIs and by interacting with the NIC driver and hardware. In this section, we will discuss their architecture and internals. We focus only on the data receiving flow as it is the only relevant data path for DFV.

### 2.2.3.1 Architecture and Data Flow

For security reasons, an operating system is divided into 2 realms of different privileges: kernel-space and userspace. Kernel-space is a privileged environment where software, e.g. NIC drivers, have direct access to hardware and hardware can perform DMA to memory without constraints. Userspace is a restricted environment where software is constrained from directly accessing hardware and protected memory regions. The interaction between user-space and kernel-space is performed through a system call, a programming routine to perform OSrelated tasks, e.g. reading and writing to network. With this architecture, all operations that require exploiting hardware, e.g. NIC, has to go through the kernel-space where the hardware and its memory are managed. Moving memory from kernel-space to user-space requires copying the memory data from kernel-space memory to user-space memory.

Figure 2.8: Architecture and Receiving Data Flow of OS Networking Stacks

Similarly, network operations go through the kernel where the NIC driver, data transfer protocols, and other security and memory management mechanisms are implemented. The NIC driver defines the method to interact with a NIC hardware. When the driver is initialized, it assigns a physical memory or buffer as a channel for communication between the OS and the NIC hardware. The driver also provides information to the NIC hardware on how to perform DMA to this buffer. This information includes the addresses of the memory chunks and their

availability. Each memory chunk have a data structure, called *descriptors*, that represent its information. Descriptors are organized in one or more NIC queues where each queue contains a unique set of DMA addresses or descriptors. Multiple queues linearly scale the performance of the NIC.

When data arrives at a NIC, it goes in the embedded memory buffers of the NIC hardware. The NIC uses the provided descriptors in NIC queues to pick an available memory chunk and then write the received data to the chosen memory chunk using DMA. The OS is notified of new data availability through a mechanism called *interrupts*. Interrupts are notifications generated by peripheral hardware, e.g. NIC, to tell the computer processor that there is an event that needs handling. Once a NIC has new data it generates an interrupt request (IRQ) to be handled. A NIC driver provides the OS with 2 IRQ handlers for each NIC queue. The first IRQ handler is called the top-half IRQ handler, it is dispatched immediately by the corresponding NIC queue once new data is received to acknowledge the event. While running top-half IRQ handlers, the CPU masks other IRQs. Therefore, they should not block the NIC from issuing new IRQs, and thus they must be very fast. Typically, top-half IRQ handlers only acknowledge an IRQ and grab minimal info like memory address. Heavy work like processing the received data through data transfer protocols is deferred to the bottom-half IRO handler which gets queued in the top-half IRQ handler. Bottom-half IRQ handler perform heavy work like protocol processing and passing the data to the user application. In Linux systems, bottom-half IRQ handlers are known as SoftIRQ. The bottom-half IRQ handler allocates a data structure called socket buffer which prepares the received data for further processing until it reaches the user application. Socket buffers act as a buffer abstraction layer that unifies memory management for different NICs from different vendors. The networking stack can reduce the number of allocated socket buffers by merging related ones to reduce their processing overhead through a mechanism called the Generic Receive Offload (GRO). Next, processing data transfer protocols, like IP and UDP, is scheduled on one of CPU cores using 2 mechanisms: Receive Packet Steering (RPS) and Receive Flow Steering (RFS). The goal of both mechanisms is to increase the NIC performance: RPS is the mechanism of using multiple NIC queues for received data, while RFS is the mechanism that ensures the data is received on the same CPU core as the application to decrease data movements from the NIC to the CPU or even inside the CPU itself. The sockets layer, powered by the *socket buffer* abstraction layer, executes the OS implementations of the data transfer protocols on each socket buffer. The OS organizes data flow between the OS and the application through data structures called sockets, after the protocol processing the received is assigned to its corresponding socket data structure. The application can fetch received data from sockets using the sockets API which are OS routines that move data from the socket data structure in the kernel-space to the application in the user-space.

It is important to note that modern NICs have hardware-based implementations of GRO, RPS and RFS that are known as *Large Receive Offload (LRO)*, *Receive Side Steering (RSS)* and *Accelerated Receive Flow Steering (aRFS)* respectively. Modern NIC moves some other components from software to hardware, like protocol processing and checksum calculations. All of these hardware features are known as NIC hardware offloads.

### 2.2.3.2 OS Networking Stack Performance

Different studies have discussed the performance overhead of OS networking stacks. Cai, Chaudhary, Vuppalapati,  $et\ al.$  provide a deep performance analysis of OS networking stacks in their paper [26]. This study shows that the maximum performance of OS networking stack is  $\sim$ 42 GB/s even with the full support of NIC offloads. The study breaks the sources of performance bottlenecks: memory copying between kernel-space and user-space, protocol processing, memory management in the sockets layer are among the most contributing factors to performance degradation [26]. Other works have shown that these performance bottlenecks are starting to limit modern applications like databases [27], [28] and mobile telecommunication services [29], [30].

### 2.2.3.3 Extended Berkeley Packet Filter

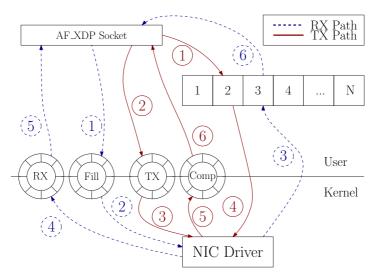

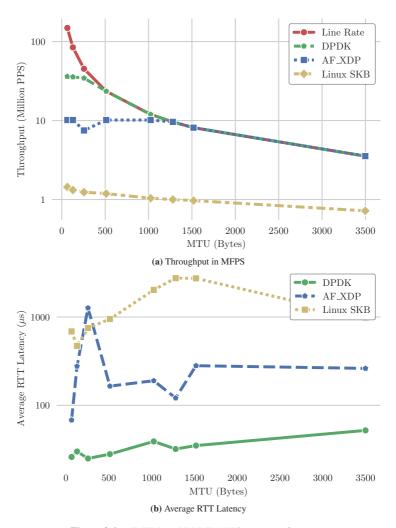

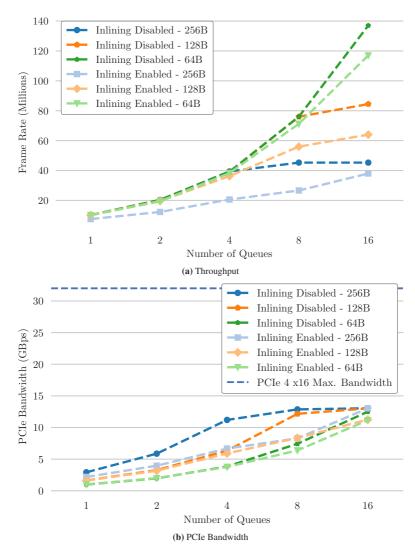

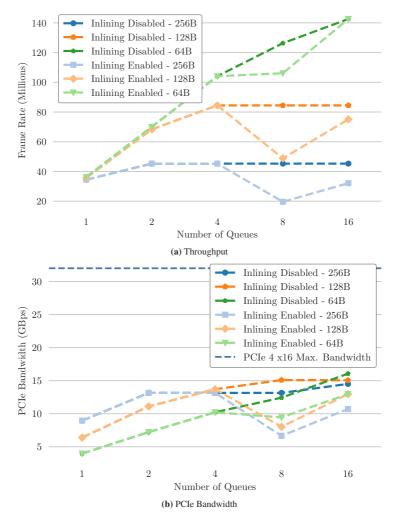

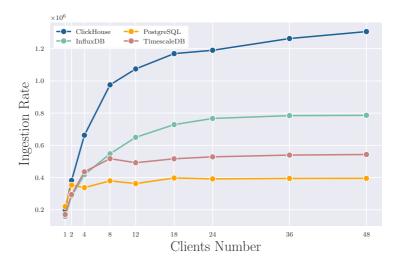

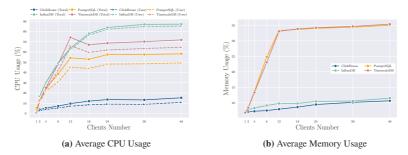

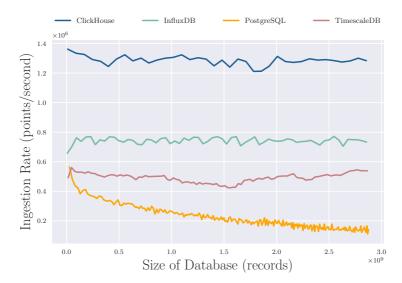

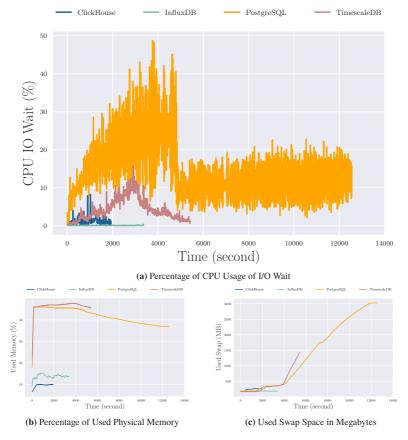

Due to the performance bottlenecks resulting from copying memory from kernel-space to user-space, OS developers have designed a new mechanism to run computers programs inside OS without actual modifications to OS source code. The mechanism is known as Extended Berkeley Packet Filter (eBPF). It started in 2014 in the Linux kernel, and it is expanding to other OSs like Microsoft Windows [31].