# Non-Data-Aided Digital Feedforward Clock Recovery for Optical Communication Systems

Zur Erlangung des akademischen Grades eines

# DOKTORS DER INGENIEURWISSENSCHAFTEN (Dr.-Ing.)

von der KIT-Fakultät für Elektrotechnik und Informationstechnik des Karlsruher Instituts für Technologie (KIT)

angenommene

#### DISSERTATION

von

Patrick André Matalla, M.Sc.

Tag der mündlichen Prüfung: 04.07.2025

Hauptreferent: Prof. Dr.-Ing. Sebastian Randel Korreferent: Prof. Dr.-Ing. Georg Rademacher

# **Table of Contents**

| Kι | urzfa | ssung   |                                                    | V  |

|----|-------|---------|----------------------------------------------------|----|

| Pr | efac  | e       |                                                    | ix |

| 1  | Intr  | oductio | on                                                 | 1  |

| 2  | Fun   | damer   | ntals of Digital Non-Data-Aided Clock Recovery     | 7  |

|    | 2.1   | Imper   | fection of Electrical Oscillators                  | 7  |

|    |       | 2.1.1   | Jitter Specifications                              | 11 |

|    | 2.2   | Clock   | Recovery Architectures                             | 12 |

|    |       | 2.2.1   | All-Analog Clock Recovery                          | 13 |

|    |       | 2.2.2   | Hybrid Analog-and-Digital Clock Recovery           | 14 |

|    |       | 2.2.3   | All-Digital Clock Recovery                         | 16 |

|    | 2.3   | Digita  | l Clock Recovery Components                        | 18 |

|    |       | 2.3.1   | Timing Error Acquisition                           | 19 |

|    |       | 2.3.2   | Interpolation                                      | 34 |

|    |       | 2.3.3   | Elastic Buffer                                     | 49 |

|    |       | 2.3.4   | Phase-Locked Loop                                  | 54 |

|    | 2.4   | Digita  | l Clock Recovery Performance Benchmark             | 58 |

|    |       | 2.4.1   | Jitter Metric for Clock Recovery Algorithms        | 58 |

|    |       | 2.4.2   | Clock Recovery Performance Evaluation              | 60 |

|    |       | 2.4.3   | Impact of Clock Frequency Offset on Clock Recovery | 64 |

| 3  | Elas  | stic Bu | ffer Design for All-Digital Clock Recovery         | 67 |

|    | 3.1   | Introd  | uction                                             | 67 |

|    | 3.2   | Elastic | Buffer Concept                                     | 71 |

|    | 3 3   |         | Implementation                                     | 74 |

|   | 3.4                               | Real-Time Experiment                                     | 75 |  |  |  |  |

|---|-----------------------------------|----------------------------------------------------------|----|--|--|--|--|

| 4 | Chr                               | omatic Dispersion Tolerant Clock Recovery for            |    |  |  |  |  |

|   | IM/I                              |                                                          | 79 |  |  |  |  |

|   | 4.1                               |                                                          | 80 |  |  |  |  |

|   | 4.2                               |                                                          | 82 |  |  |  |  |

|   |                                   |                                                          | 82 |  |  |  |  |

|   |                                   | 1                                                        | 87 |  |  |  |  |

|   | 4.3                               | Chromatic Dispersion Tolerant Clock Recovery for         |    |  |  |  |  |

|   |                                   | $\varepsilon$                                            | 91 |  |  |  |  |

|   | 4.4                               | Chromatic Dispersion Tolerant Clock Recovery for         |    |  |  |  |  |

|   |                                   | Low-Roll-Off and Faster-Than-Nyquist Signals             |    |  |  |  |  |

|   | 4.5                               | Experimental Validation                                  | 00 |  |  |  |  |

| 5 |                                   | nosecond Clock Synchronization for Passive Optical       |    |  |  |  |  |

|   |                                   | works                                                    |    |  |  |  |  |

|   | 5.1                               | Introduction                                             | 05 |  |  |  |  |

|   | 5.2                               | PONs Featuring Free-Running Oscillators with All-Digital |    |  |  |  |  |

|   |                                   | Clock Recovery                                           |    |  |  |  |  |

|   | 5.3                               | Experimental Performance Evaluation for PON Upstream 1   | 08 |  |  |  |  |

| 6 | Non-Data-Aided Clock Recovery for |                                                          |    |  |  |  |  |

|   | Cor                               | ntinuous-Variable Quantum Key Distribution 1             | 15 |  |  |  |  |

|   | 6.1                               | Introduction                                             | 15 |  |  |  |  |

|   | 6.2                               | Pilot-Free Digital Timing Synchronization                |    |  |  |  |  |

|   | 6.3                               | Experimental Validation                                  | 20 |  |  |  |  |

| 7 | Joii                              | nt NDA Clock Recovery for SDM Optical                    |    |  |  |  |  |

|   | Trai                              | nsmission Systems                                        | 25 |  |  |  |  |

|   | 7.1                               | Introduction                                             | 26 |  |  |  |  |

|   | 7.2                               | Non-Data-Aided Joint Clock Recovery                      | 28 |  |  |  |  |

|   |                                   | 7.2.1 MIMO Channel Model                                 | 29 |  |  |  |  |

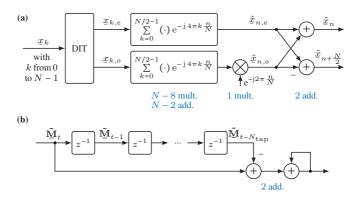

|   |                                   | 7.2.2 Joint Timing Estimation Algorithm                  | 31 |  |  |  |  |

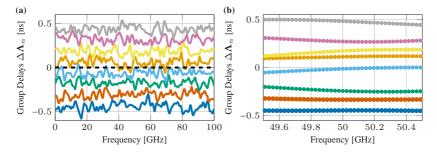

|   |                                   | 7.2.3 Effect of Frequency-Dependent Group Delays 1       | 34 |  |  |  |  |

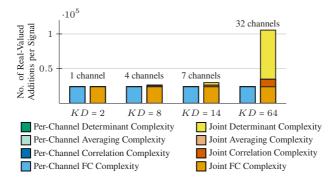

|   |                                   | 7.2.4 Hardware Complexity Analysis                       | 37 |  |  |  |  |

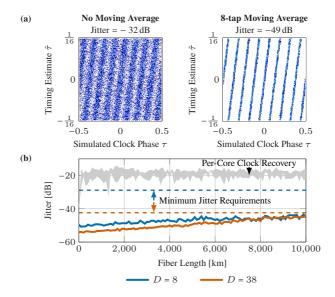

|   | 7.3                               | Performance Simulation                                   | 42 |  |  |  |  |

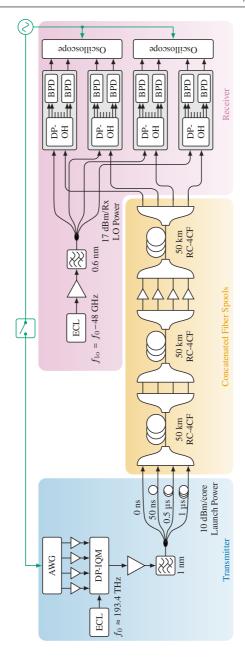

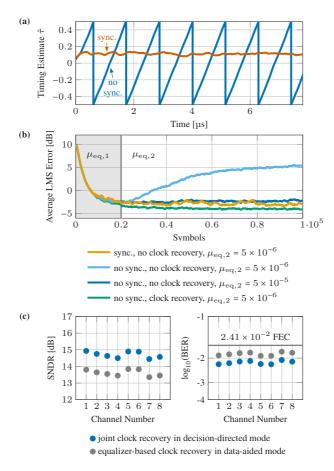

|     | 7.4                        | Experimental Validation                                                                                                                           |

|-----|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 8   | Sun                        | nmary and Outlook                                                                                                                                 |

| Αŗ  | pend                       | dices                                                                                                                                             |

| Α   | A.1<br>A.2                 | Discrete-Time Signals and Systems  Discrete-Time Signals  Discrete-Time Systems  150  A.2.1 Linear Time-Invariant Systems  A.2.2 Z-Transform  160 |

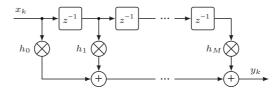

|     |                            | A.2.3 FIR Filters                                                                                                                                 |

| В   | <b>Mul</b> :<br>B.1<br>B.2 | ti-Rate System168Sampling Theorem169Sampling Rate Down- & Upconversion171                                                                         |

| С   | Trar                       | at NDA Clock Recovery for SDM Optical asmission Systems                                                                                           |

|     |                            | Factorization                                                                                                                                     |

| GI  | ossa                       | ry                                                                                                                                                |

| Bi  | bliog                      | raphy                                                                                                                                             |

| Da  | nksa                       | ngung                                                                                                                                             |

| Lis | Jour<br>Cont               | Publications207nal Publications207ference Publications208rint Publications218                                                                     |

# Kurzfassung

Wir leben in einer vernetzten Gesellschaft. Wir verabreden uns per Nachrichtendienst, Besprechungen finden standortübergreifend in der virtuellen Welt statt, das Abendessen wird per Knopfdruck über das Mobiltelefon bestellt und der abendliche Blockbuster wird gestreamt – um nur wenige Beispiele aus dem Alltag zu nennen. Das Internet verbindet Menschen weltweit und längst fordern neue Technologien wie intelligente Städte (sogenannte "Smart Cities"), das Internet der Dinge, kommunizierende Fahrzeugflotten oder das Trainieren von Modellen der künstlichen Intelligenz (KI) in der "Wolke" (engl. Cloud) immer höhere Datenraten mit exponentiellem Wachstum. Technisch ermöglicht wird dieser enorme Datenaustausch durch optische Glasfasernetze, welche das Rückgrat der Telekommunikationsinfrastruktur bilden. In solchen Netzen werden (digitale) Daten auf einem Prozessor zunächst in ein elektrisches Signal umgewandelt und anschließend auf einen optischen Träger moduliert. Das optische Signal propagiert durch die Glasfaser und profitiert hierbei von geringen Verlusten innerhalb eines breiten Frequenzbereiches. Am Empfänger wird das optische Signal in einem Photodetektor zurück in ein elektrisches Signal konvertiert, bevor es digitalisiert wird und in einem Prozessor verarbeitet werden kann.

Die Synchronisierung des Prozessortakts des Empfängers mit dem Sendetakt ist eine essenzielle Voraussetzung für die zuverlässige und fehlerfreie Dekodierung des Empfangssignals. Während die Übertragung des Taktes über eine separate Datenleitung für sehr kurze Distanzen von weniger als etwa einem Kilometer möglich ist, ist dies für größere Distanzen nicht praktikabel. In solchen Fällen wird die Taktinformation aus dem Empfangssignal extrahiert und der Empfängertakt entsprechend synchronisiert. Ein geläufiges Verfahren, um Oszillatoren zu synchronisieren, ist mittels einer rückgekoppelten Regelschleife. Hierbei wird aus

dem Empfangssignal ein Fehlersignal abgeleitet, welches anschließend den Oszillator in den korrekten Arbeitspunkt korrigiert. Diese Regelkreise ermöglichen eine frequenz- und phasenstabile Synchronisation des Empfängertaktes und finden daher Anwendung in optischen Punkt-zu-Punkt-Langstreckennetzen. Regelkreisbasierte Synchronisationsverfahren weisen jedoch eine limitierte Bandbreite auf, sodass hochfrequente Taktfluktuationen (engl. Jitter) unzureichend kompensiert werden und eine schnelle Synchronisation von Datenblöcken in der Burst-Übertragung erschwert wird. Eine alternative Architektur stellt die vorwärtsgerichtete Taktsynchronisation dar. Hierbei findet ein Zeitschätzer Anwendung, welcher den Zeitversatz des Sende- und Empfangstaktes unmittelbar schätzt und folglich das Empfangssignal ohne Regelung korrigieren kann. Da kein rückgekoppelter Regelkreis erforderlich ist, weist diese Methode signifikant bessere Eigenschaften zur Kompensation von hochfrequentem Jitter und zur Synchronisation von Burst-Signalen auf. Darüber hinaus lässt sich die vorwärtsgerichtete Taktsynchronisation voll-digital in modernen CMOS-Schaltungen implementieren, was die Notwendigkeit analoger Schaltungen zur Oszillatorkontrolle überflüssig macht und somit die Sendeempfänger-Komplexität (engl. Transceiver) reduziert. Im Rahmen einer voll-digitalen Synchronisation erfolgt die Korrektur der Oszillatorphase nicht mehr physisch, sondern durch die zeitliche Verzögerung der Abtastpunkte des Signals in einem digitalen Verzögerungselement, welches aus einem temporären Speicher und einer digitalen Verzögerungsleitung besteht. Die Herausforderung einer solchen digitalen Realisierung besteht in dem Verlust von Symbolen beim Überlaufen des temporären Speichers, was die Anwendung in praktischen Systemen derzeit noch limitiert.

Die vorliegende Dissertation untersucht die voll-digitale Implementierung der vorwärtsgerichteten Taktsynchronisation in ihrer Anwendung in modernen optischen Kommunikationssystemen. In diesem Rahmen wurde zunächst ein neuartiger Zeitschätzalgorithmus entwickelt, welcher auf dem Algorithmus von Barton und Al-Jalili basiert. Darüber hinaus wurde ein Verfahren entwickelt, welches den Informationsverlust beim Überlaufen des temporären Speichers durch Übertakten des Prozessors vermeidet und somit die praktische Umsetzung der voll-digitalen

Taktsynchronisation in modernen Transceivern ermöglicht. Während die digitale Taktsynchronisation in Signalverarbeitungsprozessoren kohärenter Systeme in den vergangenen zwei Jahrzehnten eine ausgereifte Technologie darstellt, resultieren aus modernen optischen Kommunikationssystemen neue Anforderungen und Herausforderungen. Gegenstand dieser Dissertation ist die Untersuchung der vorwärtsgerichteten Taktsynchronisation in modernen optischen Kommunikationssystemen.

Infolge steigender Datenraten in Kurzstreckenübertragungen zwischen und innerhalb von Rechenzentren, getrieben durch KI-Applikationen, stellt die chromatische Dispersion einen limitierenden Faktor in der Übertragungsperformance von Systemen mit Direktempfang dar. Die vorliegende Arbeit untersucht erstmalig den Effekt der chromatischen Dispersion auf die Taktsynchronisation und präsentiert zwei neuartige Algorithmen, welche eine hohe Robustheit gegenüber der chromatischen Dispersion aufweisen.

Im weiteren Verlauf der vorliegenden Arbeit wird die nanosekunden-schnelle Synchronisation von Datenblöcken in der Burst-Übertragung in passiven optischen Netzen demonstriert. Die voll-digitale vorwärtsgerichtete Taktsynchronisation erlaubt somit die Substitution herkömmlicher analoger Schaltungen zur Takt- und Datenrückgewinnung und ermöglicht eine platzsparende und energieeffizientere Umsetzung.

Im Bereich der abhörsicheren Datenübertragung stellt die kontinuierlich-variable Quantenverschlüsselung (engl. continuous-variable quantum key distribution, CV-QKD) einen vielversprechenden Ansatz gegenüber der herkömmlichen diskretvariablen Quantenverschlüsselung dar. In solchen Systemen liegt die Leistung der optischen Signale in der Größenordnung des Quantenrauschens, was die Taktsynchronisation erschwert. Um dieser Herausforderung zu begegnen, werden in der Regel zusätzliche "Hilfssignale" wie Pilottöne eingesetzt, um die Taktsynchronisation zu gewährleisten. In dieser Arbeit wurde die Taktsynchronisation ohne den Einsatz von Pilottönen untersucht und demonstriert, welches die Komplexität zukünftiger CV-QKD-Systeme reduzieren kann.

Der kontinuierlich steigende Bedarf an immer höheren Datenraten erfordert die Untersuchung von optischen Übertragungssystemen mit einem Raummultiplex (engl. Space-Division Multiplexing, SDM) zur parallelen Übertragung großer Datenströme. In diesem Kontext werden derzeit Systeme mit gekoppelten Signalwegen, beispielsweise Glasfasern mit mehreren Wellenleitermoden oder dichtgepackten Faserkernen, erforscht. Für SDM-Systeme mit gekoppelten Kanälen wird ein Algorithmus vorgestellt, der erstmals robust gegenüber räumlicher Dispersion ist. Diese Entwicklung ist von wesentlicher Bedeutung für die Kommerzialisierung von SDM-Systemen mit gekoppelten Kanälen.

# **Preface**

We live in a connected world. Dates are arranged via text messengers, meetings take place across offices in the virtual world, dinner is ordered by just a click on the smartphone and the movie in the evening is streamed – to name just a few examples from everyday life. The Internet is connecting people across the globe and new technologies such as smart cities, the Internet of things, communicating vehicle fleets, and the training of artificial intelligence (AI) models in the cloud are driving demand for ever higher data rates at exponential growth rates. This enormous data traffic is facilitated by optical fiber networks, which form the backbone of the telecommunications infrastructure. In such networks, (digital) data on a processor is first converted into an electrical signal and afterwards modulated onto an optical carrier. The optical signal propagates through the optical fiber and thereby benefits from low losses within a broad frequency range. At the receiver, the optical signal is converted back into an electrical signal using a photodetector before it is digitized and can be further processed in a processor.

Synchronizing the processor clock of the receiver with the transmitter clock is an essential prerequisite for reliable and error-free decoding of the received signal. While it is possible to transmit the clock over a dedicated communication channel for very short distances of about less than one kilometer, this is not practical for longer distances. In such cases, the clock information is extracted from the received signal and the receiver clock is synchronized accordingly. A common method for synchronizing oscillators is by using a feedback control loop. Here, an error signal is derived from the received signal, which then corrects the oscillator to the correct operating point. Such control loops enable frequency and phase-stable synchronization of the receiver clock and are thus widely used in

optical point-to-point long-haul links. However, control loop-based synchronization methods exhibit a limited bandwidth, resulting in insufficient compensation of high-frequency clock fluctuations (jitter) and rendering rapid synchronization of data blocks in burst-mode transmission difficult. An alternative architecture is represented by feedforward clock synchronization. Here, a timing estimator is applied, which directly estimates the sampling offset of the transmitter and receiver clock and can therefore correct the receive signal without the need for a control loop. Since no feedback control loop is required, this method has significantly better capabilities for compensating high-frequency jitter and for synchronizing burst-mode signals. In addition, feedforward clock synchronization can be implemented fully-digital in modern complementary metal-oxide semiconductor (CMOS) circuits, eliminating the need for analog circuits for oscillator control and thus reducing the transceiver complexity. In a fully-digital synchronization, the oscillator phase is no longer corrected physically, but by the temporal delay of the sampling points in a digital delay element, which consists of a buffer and a digital delay line. The challenge of such a digital realization is the loss of symbols when the buffer overflows, which currently still limits its application in practical systems.

This doctoral thesis investigates the all-digital implementation of feedforward clock synchronization and its application in modern optical communication systems. In this context, a novel timing estimation algorithm based on the algorithm of Barton and Al-Jalili was developed. In addition, a process was developed which avoids the loss of information when the buffer overflows by overclocking the processor and thus enables the practical implementation of fully-digital clock synchronization in modern transceivers. While digital clock synchronization in coherent system signal processors has become a mature technology over the past two decades, modern optical communication systems pose new requirements and challenges. The subject of this dissertation is the investigation of feedforward clock synchronization in modern optical communication systems.

As a result of increasing data rates in short-distance transmissions between and within data centers, driven by AI applications, chromatic dispersion is a limiting factor in the transmission performance of systems with direct reception. This

thesis studies for the first time the effect of chromatic dispersion on clock synchronization and presents two novel algorithms that are particularly robust against chromatic dispersion.

Furthermore, this thesis demonstrates the nanosecond-fast synchronization of data blocks in burst-mode transmission in passive optical networks. The fully-digital feedforward clock synchronization thus allows the substitution of conventional analog circuits for clock and data recovery and enables a compact and energy-efficient realization.

In the field of secure data transmission, continuous-variable quantum key distribution (CV-QKD) presents a promising approach to conventional discrete-variable quantum key distribution. In such systems, the power of the optical signals is in the order of the shot noise, thus complicating clock synchronization. To overcome this challenge, additional "auxiliary signals", e.g., pilot tones, are usually used to ensure proper clock synchronization. In this work, clock synchronization was investigated and demonstrated without the use of pilot tones, which can reduce the complexity of future CV-QKD-systems.

The continuously increasing demand for ever higher data rates requires the investigation of optical transmission systems with space-division multiplexing (SDM) for the parallel transmission of large data streams. In this context, systems with coupled channels, such as optical fibers with multiple waveguide modes or densely packed fiber cores, are currently being explored. For SDM systems with coupled channels, an algorithm is presented that is robust to spatial dispersion for the first time. This development is of major importance towards the commercialization of SDM systems with coupled channels.

# **Achievements of the Present Work**

In this thesis, the non-data-aided (NDA), digital feedforward (FF) clock recovery is investigated for its application in modern optical communication systems. For this purpose, the algorithms and synchronization architecture are first investigated through simulation and hardware implementation on a field-programmable gate array (FPGA). Due to the advantages of FF clock recovery in terms of high-frequency jitter compensation and fast timing acquisition, its application in different types of systems is investigated. A concise overview of the major achievements is given in the following list:

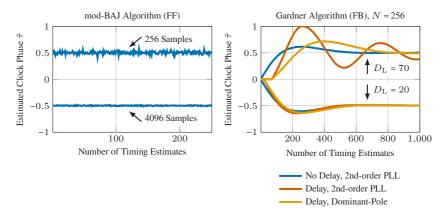

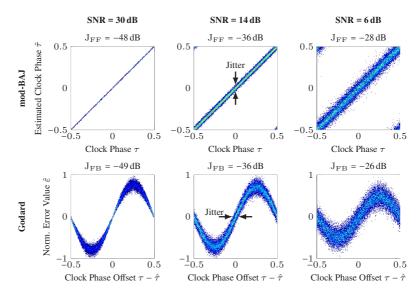

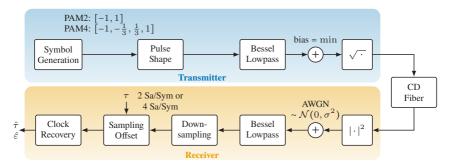

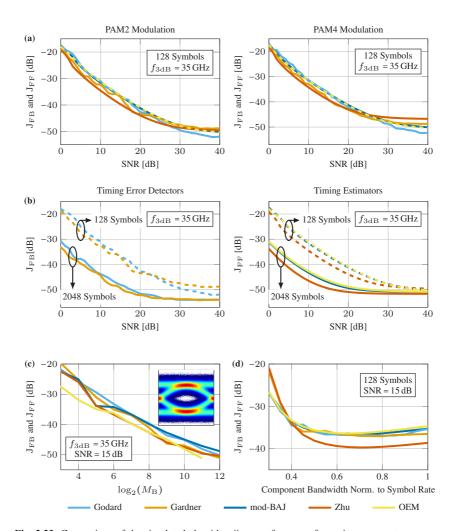

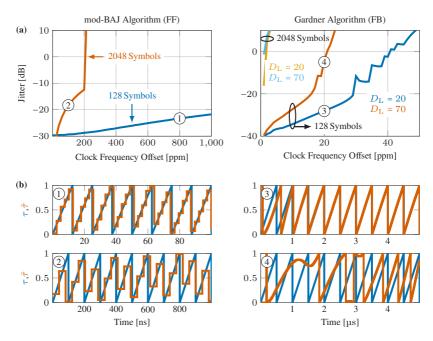

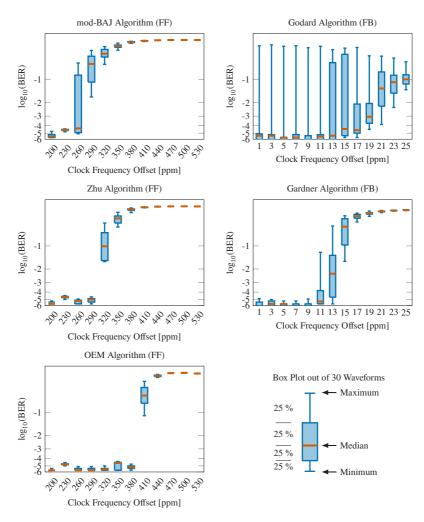

Comprehensive performance benchmark of feedback (FB) and FF clock recovery algorithms and architectures: The performance of various timing estimators (TEs) (used for FF) and timing error detectors (TEDs) (used for FB) is studied in detail for different algorithm and system parameters. The results confirm the finding from [1] stating that the various algorithms perform identically due to mathematical equivalence. Furthermore, the bandwidth of FB and FF clock recovery architectures is discussed, which demonstrates the suitability of FF architectures for high-frequency jitter and large clock frequency offset (CFO) compensation.

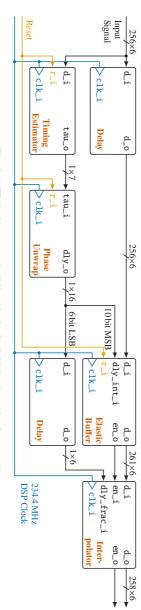

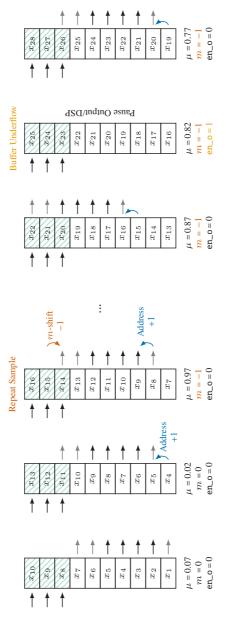

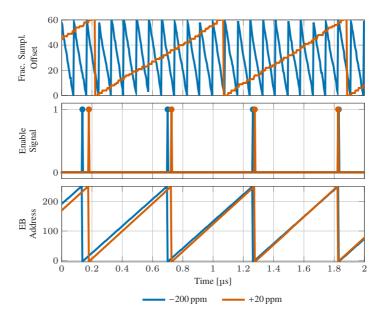

First demonstration of an all-digital clock recovery with free-running receiver oscillator that allows, both, lower and higher frequencies than the transmitter clock frequency: A major limitation of fully digital clock recoveries is the elastic buffer (EB) overflow at a receiver clock frequency less than the transmitter clock frequency. Current literature simply avoids this problem by setting the receiver clock frequency slightly higher than the transmitter clock frequency [2]. In this thesis, an EB method is reported for the first time, which allows to use a

receiver clock frequency lower and higher than the transmitter clock frequency. The functionality of the novel EB method is implemented together with the remaining clock recovery components on an FPGA and demonstrated in an optical transmission experiment. This enables the shared use of a free-running clock without phase-locked loop (PLL) synchronization for the transmitter and receiver in modern transceivers.

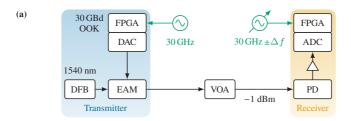

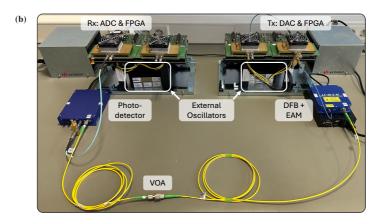

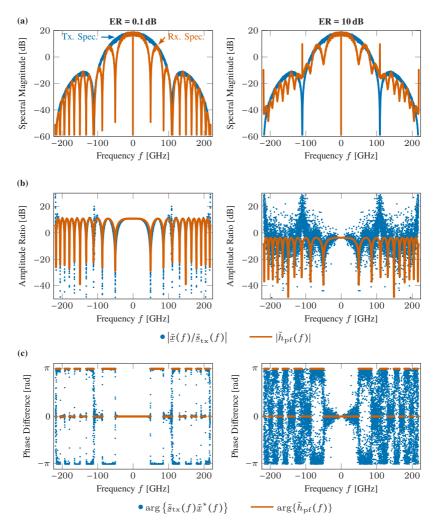

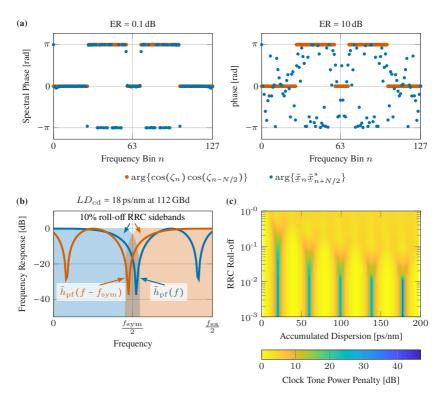

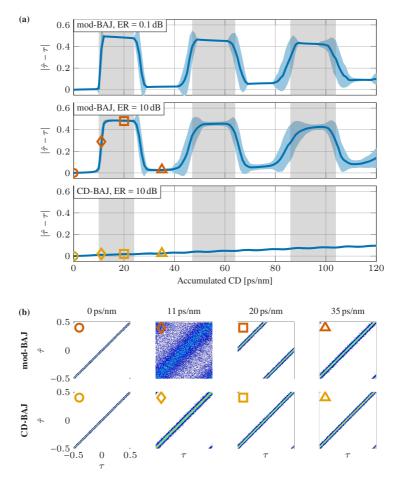

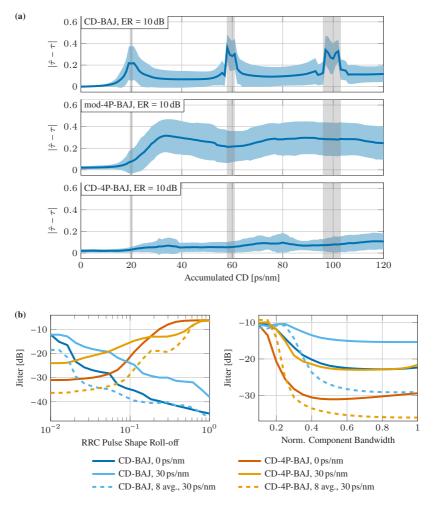

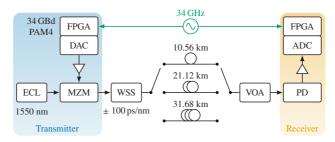

First time analysis of the impact of chromatic dispersion (CD) on the digital clock recovery in intensity modulation and direct detection (IM/DD) systems and development of two novel CD-tolerant algorithms: CD is increasingly becoming a limiting factor in high baud-rate systems that use direct detection. In this thesis, the effect of CD on clock recovery in direct detection systems is investigated analytically and in simulation for the first time. Afterwards, two novel CD-tolerant TEs were developed. The CD penalty was confirmed in experiments and the TEs were validated. The progress made in this area presents an important contribution for future high baud-rate direct-detection systems, which are strongly distorted by CD.

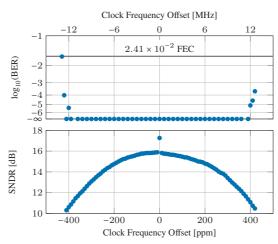

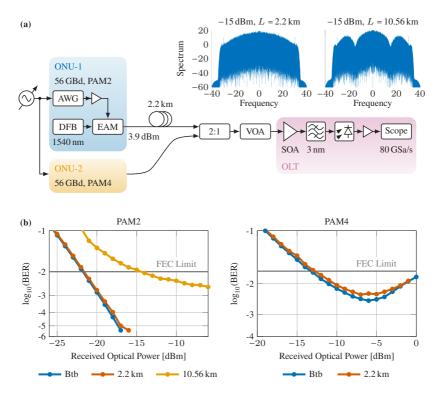

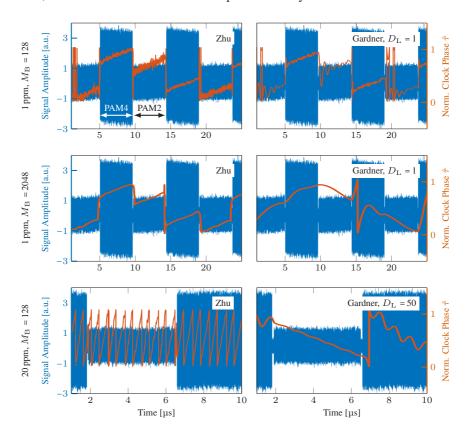

Comprehensive analysis of digital FF clock recovery in passive optical networks (PONs) enabling nanosecond-fast synchronization: With the standardization of the 50-Gbit/s PON, bandwidth limitations, device nonlinearities, and CD present increasing difficulties in the error-free decoding of the received signals. To compensate for such channel effects, 50G-PONs combine an analog-to-digital converter (ADC) with a receiver digital signal processing (DSP). This allows the replacement of analog clock and data recovery (CDR) by digital clock recovery and adaptive equalization. For this purpose, digital FF clock recovery is investigated in this thesis, as it allows fast synchronization of burst-mode signals and the use of low-cost oscillators in the optical network unit (ONU). Successful synchronization within 36.57 ns of two ONUs at 112 Gbit/s data rate in upstream is demonstrated. This paves the way for fast-synchronizing FF clock recoveries in future high-speed PONs with data rates beyond 100 Gbit/s.

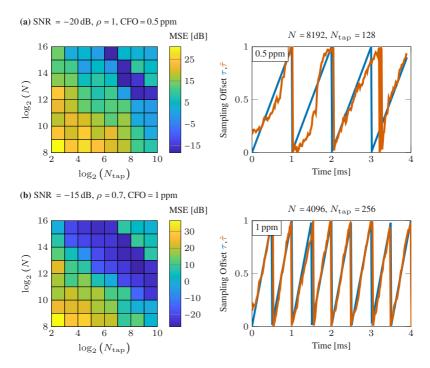

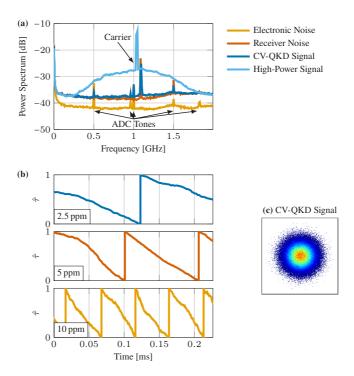

Comprehensive analysis of NDA clock recovery in CV-QKD systems: The challenge in coherent DSP for CV-QKD systems lies in the extremely low signal-to-noise ratio (SNR) of the received signal. This complicates the synchronization of the sampling clock phase and the local oscillator phase. For this reason, auxiliary signals, e.g., pilot tones, are often transmitted alongside the actual quantum signal. The generation, transmission, reception, and processing of such pilot tones increase the overall system complexity. In the course of this thesis, NDA clock recovery using the modified Barton & Al-Jalili TE is investigated. The presented results demonstrate successful clock recovery for long averaging lengths of the TE, which in turn reduce the clock recovery bandwidth. Provided that highly stable oscillators are used, this work proves that NDA clock recovery can replace conventional pilot tone-based clock recovery, thereby reducing the system complexity.

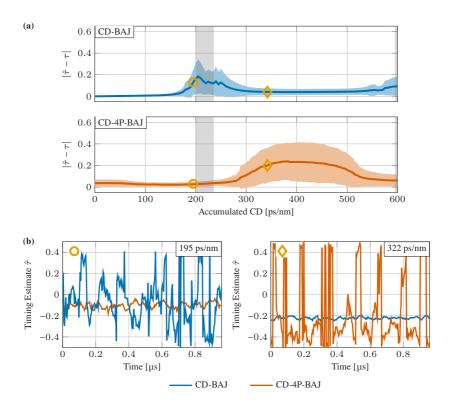

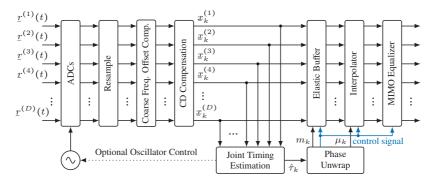

First time demonstration of a digital NDA joint clock recovery tolerant to polarization-and-spatial-mode dispersion: Clock recovery failure in SDM systems with coupled channels is a well-known issue that has not yet been solved. For the first time a joint clock recovery that is tolerant to polarization-and-spatial-mode dispersion is proposed. Successful clock synchronization for a 90-GBd 16-level quadrature amplitude modulation (16-QAM) signal resulting in a total data rate of 2.92 Tbit/s over a 150-km randomly-coupled 4-core fiber (RC-4CF) has been experimentally demonstrated.

# 1 Introduction

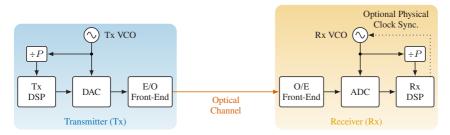

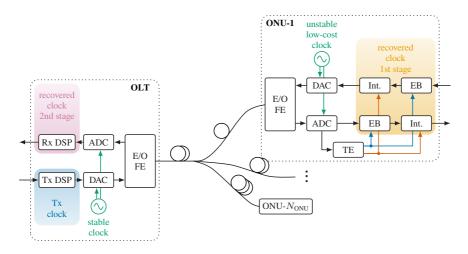

Clock recovery is a fundamental building block in communication systems and refers to the process of synchronizing the sampling clock at the receiver in, both, phase and frequency, with the clock used to generate the data at the transmitter. This is essential to compensate for a sampling offset between the transmitter and receiver clocks and thus sampling the received waveform at the ideal sampling points that minimize intersymbol interference (ISI) and consequently bit errors. The clock recovery is typically located at the beginning of the receiver DSP chain. In coherent systems, the clock recovery is usually performed after CD compensation and before the adaptive equalizer and carrier recovery [3]. In IM/DD systems, the clock recovery is located directly at the beginning of the DSP chain (or after the digital resampling if needed) and before the adaptive equalizer. For this reason, a loss of synchronization affects most DSP modules and leads to a total failure of the transceiver, which will require a reacquisition of all control loops in the system including the NDA equalizer [4]. Therefore, the synchronization of the receiver clock must operate in a reliable and stable manner. Depending on the communication system, this results in different clock recovery requirements, e.g., the choice of the modulation format, SNR (see clock recovery for CV-QKD), jitter tracking and synchronization speed (see clock recovery for PON) as well as signal distortions caused by, e.g., CD (see CD-tolerant clock recovery), polarization-andspatial-mode dispersion (see joint clock recovery for SDM), etc. Fig. 1.1 shows a simplified system overview of an optical communication system that incorporates a receiver DSP.

The clock recovery can be implemented either in a FB architecture based on a PLL, in a FF architecture, or in a combination of both approaches. Under the prerequisite that relatively stable oscillators are used (e.g.,  $\pm 20$  parts-per-million

Fig. 1.1: System overview of an optical communication system including the transmitter and receiver voltage-controlled oscillators (VCOs). The sampling clock is downmixed by a factor P for the signal processor, which processes the samples P-fold in parallel.

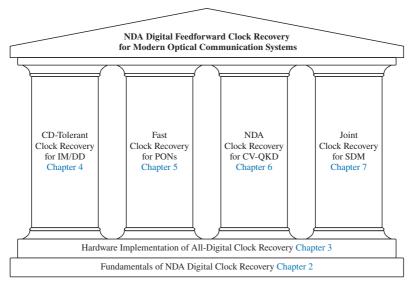

(ppm) for ZR/ZR+ standardized transceivers [5, 6]) and data transmission is continuous, FB structures result in stable phase tracking and are therefore commonly used in optical communications, e.g., in long-haul point-to-point systems [7]. But also in short-reach systems they are frequently deployed because of their low complexity [8, 9]. However, due to their lower clock recovery bandwidth compared to FF synchronization, FB loops suffer by a relatively long acquisition time and therefore might not meet the stringent requirements for fast synchronization in burst-switched systems, such as PONs [10, 11] and data centers [12], or systems that are affected by link outages, e.g., free-space optical communications under atmospheric turbulence [13, 14] or optical camera communications [C6]. Furthermore, the bandwidth limitation results in worse compensation of high-frequency jitter. In scenarios where a fast and robust synchronization is required, FF schemes can be beneficial due to their instantaneous timing estimation and their improved high-frequency jitter performance especially when using low-cost oscillators that feature wider linewidths and lower frequency adjustment accuracies [C2, 15]. On the basis of these advantages, the application of FF clock recovery in various areas of modern optical communication systems is studied in this dissertation. The different fields of application are briefly explained below. Fig. 1.2 gives an overview of the thesis outline with the clock recovery building blocks (*Chapter 2*) and the hardware implementation of all-digital FF clock recovery (Chapter 3) depicted as the foundation and the areas of application visualized as pillars.

### Short-reach optical links

Optical links with distances of less than a few tens of kilometers preferably use IM/DD, as this type of transmission requires less energy and is more cost-effective than coherent transceivers. However, these transceiver types also come with some disadvantages. For example, CD is a nonlinear channel effect with regard to the received optical power, which scales quadratically with the symbol rate assuming a constant fiber length. With currently targeted symbol rates of 112 GBd or even 224 GBd in Ethernet links, CD thus becomes a limiting factor in signal quality. Current research is primarily investigating the compensation of this nonlinear effect using sophisticated nonlinear equalizers and machine learning (ML) methods. However, the impact of CD on clock recovery in IM/DD systems has not yet been investigated. *Chapter 4* analyzes the effect on clock recovery for the first time and demonstrates two novel CD-tolerant clock recovery algorithms for IM/DD systems.

### Passive optical networks (PONs)

PONs are point-to-multipoint optical networks and the preferred network architecture in optical access due to their low cost. They connect an optical line terminal (OLT) located in the central office via a single fiber to a purely passive splitter, from which the respective fibers lead to the individual ONUs. In order to reduce the costs in such networks (especially on the part of the ONU), such networks also utilize IM/DD. Since the feeder fiber from the OLT to the passive splitter is shared by all network users, such a network requires time-allocated transmission slots for each ONU. For this reason, PONs employ time-division multiplexing (TDM) in the downstream and time-division multiple access (TDMA) in the upstream. This makes fast synchronization to the signal bursts in upstream essential. Conventional PON systems use an analog PLL-based synchronization, also referred to as CDR (see section 2.2.1), which derives the timing information from a preamble. As a result of modern applications and services in a smart city, the number of network users will increase from currently 64 users to up to 256 users. In order to guarantee the same latency for 256 users as for 64 users, the burst duration must be shortened. Therefore, efficient preamble design is mandatory to ensure a high net data throughput at the same time [J1]. Chapter 5 analyzes the use

of digital NDA FF clock recovery to ensure fast clock synchronization for future PONs without the need of a preamble.

### Continuous-variable quantum key distribution (CV-QKD)

Quantum key distribution (QKD) is a type of secure communication, which exploits quantum mechanics to implement a secure cryptographic protocol. Here, conventional communication via the Internet is encrypted using a tap-proof quantum channel to exchange an encryption key between to parties. The concept of the secure quantum communication is based on the no-cloning theorem from quantum physics, which states that it is impossible to copy an independent and identical quantum state. As a consequence, an evesdropper cannot intercept, copy, and resend the transmitted quantum states to the intended recipient without changing their quantum states and thus revealing its presence. The first protocol of this kind, the BB84 protocol introduced by Brennett and Brassard in 1984, encodes the key information on discrete physical quantities, for example the polarization of a photon [16]. For this reason, this method is also classified as a discretevariable quantum key distribution (DV-QKD). A disadvantage of this method is the necessity of complex single-photon detectors, which often have to be cooled in cryogenic conditions to minimize noise. This poses difficulties for the integration and scaling of the technology in existing telecommunication systems. An alternative method is CV-QKD, proposed by Grosshans and Gragnier in 2002 [17]. Here, the key information is modulated on the amplitude and phase of a coherent light source, which are continuous physical quantities. These quantum states are generated with the optical power of the signal equal or less than the quantum noise. This method is similar in many ways to modern coherent optical communications and allows the re-use of the technological advances through highly integrated, commercially available transceivers with sophisticated DSP. A major problem in the coherent DSP of CV-QKD systems is the clock and carrier phase synchronization at extremely low SNR of down to -20 dB and below. Auxiliary signals, so-called pilot tones, are therefore often used to enable synchronization. These pilot tones increase the system complexity, which is why pilot tone-free CV-QKD systems are currently an active field of research [18]. Chapter 6 analyzes the requirements for NDA digital clock recovery at extremely low SNR.

### Space-division multiplexing (SDM) optical systems

To cope with the increasing demand for ever higher data rates in telecommunication networks, various multiplexing techniques are used. In conventional coherent fiber-optic systems the amplitude and phase of a coherent light source are modulated as well as both polarizations (polarization multiplexing). Furthermore, different data streams are modulated at a number of different wavelengths (wavelength-division multiplexing (WDM)) in order to exploit the low losses of a broad frequency range of the optical fiber efficiently. The spatial dimension is another physical dimension that can be used to further scale the total data rate. In recent years, SDM has been a field of research that has attracted particular interest. Here, several independent data streams are modulated onto several spatial paths of special optical fibers such as multi-mode fibers (MMFs) or multi-core fibers (MCFs). The coupling of spatially multiplexed signals and their propagation through the fiber with different group velocities is referred to as spatial-mode dispersion. Spatial-mode dispersion is a common issue in coupled SDM systems which leads to a failure of the clock recovery. In Chapter 7, a novel joint clock recovery algorithm that is tolerant to polarization-and-spatial-mode dispersion is presented.

Fig. 1.2: Overview of the thesis structure.

# 2 Fundamentals of Digital Non-Data-Aided Clock Recovery

This chapter summarizes the theoretical and technical background of digital clock recovery with a particular focus on the FF implementation. The necessity of clock recovery is the consequence of the frequency and phase instability of electrical oscillators. For this reason, the voltage-controlled oscillator (VCO) jitter and jitter specifications in communication systems is explained in the first section. Afterwards, the different clock recovery architectures are discussed in the second section and then the necessary building blocks of digital FF and FB clock recovery are explained in the third section. In the last section, a performance benchmark between FB and FF clock recovery is performed to demonstrate the advantages of the FF implementation, which serves as a foundation for the following chapters.

## 2.1 Imperfection of Electrical Oscillators

In an asynchronous communication system, the transmitter and receiver feature their own clocks, which are not synchronized to each other via a physical connection. Even if identical oscillator types are used at the transmitter and receiver, these do not oscillate at the same frequency and phase after start-up and therefore lead to jitter in the communication system. While a stable on-board crystal quartz oscillator at a few GHz and a PLL can be used to stabilize the frequency of the VCO that is fed to the high-frequency signal converters and signal processor, a certain amount of phase noise remains, which is the main source of jitter in the communication system and is commonly referred to as *VCO jitter* [4].

The VCO can be described as a sinusoidal oscillation around the center frequency  $f_0$  and normalized amplitude, which is affected by amplitude noise  $a_n(t)$  and phase noise  $\varphi_n(t)$  [19, 20, J4, C7]. The VCO can hence be modeled as

$$V(t) = (1 + a_{\rm n}(t)) \sin(2\pi f_0 t + \varphi_{\rm n}(t)). \tag{2.1}$$

The amplitude noise  $a_{\rm n}$  can usually be neglected, since electrical oscillators utilize a control circuit for precise amplitude stabilization and therefore  $a_{\rm n}(t)\ll 1$  [21]. Phase noise mainly originates from thermal and flicker noise of the oscillator device [22, 23]. To understanding the effect of phase noise on the VCO oscillation in a simplified example [4, 19, 20, 22, 23], the VCO's phase noise  $\varphi_{\rm n}(t)$  can be assumed to be a single sinusoidal phase modulation with amplitude  $a_{\rm mod}$  normalized to the VCO amplitude and modulation frequency  $f_{\rm mod}$  as

$$\varphi_{\rm n}(t) = a_{\rm mod} \sin\left(2\pi f_{\rm mod}t\right). \tag{2.2}$$

Hence, the VCO voltage can be described as

$$V(t) = \sin(2\pi f_0 t + \varphi_n(t))$$

$$= \sin(2\pi f_0 t)\cos(\varphi_n(t)) + \cos(2\pi f_0 t)\sin(\varphi_n(t)),$$

(2.3)

since  $\sin(x+y) = \sin(x)\cos(y) + \cos(x)\sin(y)$ . Considering that the phase modulation amplitude is small, the cosine and sine involving the phase modulation can be simplified using  $\cos(\varphi_n(t)) \approx 1$  and  $\sin(\varphi_n(t)) \approx \varphi_n(t)$ , respectively. Afterwards, applying the trigonometric identities, the VCO voltage results in

$$V(t) \approx \sin(2\pi f_0 t) + a_{\text{mod}} \cos(2\pi f_0 t) \sin(2\pi f_{\text{mod}} t)$$

$$\approx \sin(2\pi f_0 t) + \frac{a_{\text{mod}}}{2} \left[ \sin(2\pi (f_{\text{mod}} - f_0) t) + \sin(2\pi (f_{\text{mod}} + f_0) t) \right].$$

(2.4)

It can be seen that the phase noise modulation generates two new tones at a distance of  $\pm f_{\rm mod}$  to the oscillator frequency  $f_0$ . The carrier-to-modulation ratio  $\mathcal{L}(\Delta f)$ , i.e., the ratio of the side-tone power and carrier power at a certain frequency offset

$\Delta f$  from the carrier and within a bandwidth of 1 Hz, is specified in dBc/Hz [4]. In this example, the carrier-to-modulation ratio  $\mathcal{L}_{\mathrm{dB}}$  in decibel is

$$\mathcal{L}_{dB}(\Delta f = |f_{mod}|) = 10 \log_{10} \left( \frac{2 \left| \int_{t=0}^{1s} \sin^{2} \left( 2\pi (f_{0} - \Delta f) t \right) dt \right|^{2} + 2 \left| \int_{t=0}^{1s} \sin^{2} \left( 2\pi (f_{0} + \Delta f) t \right) dt \right|^{2}}{2 \left| \int_{t=0}^{1s} \sin^{2} \left( 2\pi f_{0} t \right) dt \right|^{2}} \right) = 10 \log_{10} \left( \frac{2 \left| \frac{a_{mod}}{2} \frac{1}{2} \right|^{2} + 2 \left| \frac{a_{mod}}{2} \frac{1}{2} \right|^{2}}{2 \left| \frac{1}{2} \right|^{2}} \right) = 10 \log_{10} \left( \frac{a_{mod}^{2}}{2} \right). \tag{2.5}$$

Rearranging eq. (2.5), the root-mean-square (RMS) phase modulation amplitude (or VCO jitter J) in unit radians RMS can be expressed as

$$J(\Delta f) = \sqrt{10^{\frac{\mathcal{L}_{dB}(\Delta f)}{10}}} \tag{2.6}$$

and the absolute jitter in picoseconds RMS follows by normalizing to  $2\pi f_0$  as

$$J(\Delta f) = \frac{1}{2\pi f_0} \sqrt{10^{\frac{\mathcal{L}_{dB}(\Delta f)}{10}}} \times 10^{12}.$$

(2.7)

In practical systems, phase noise is not a single-frequency modulation but rather involves a modulation of many frequencies around the carrier, leading to a general broadening of the oscillator's spectral line. Within the linewidth of the oscillator carrier  $f_{\rm 3dB}$ , which is defined as the full-width at half-maximum power, the spectrum of the real-world oscillator decreases by  $\sim 1/f^3$  ( $-30~{\rm dBc/Hz}$  per decade). Beyond the linewidth, the carrier spectrum decreases by  $\sim 1/f^2$  ( $-20~{\rm dBc/Hz}$  per decade) until the spectrum finally disappears below the noise floor [19, 20, J4,

C7, 22, 23]. The  $1/f^2$  region is typically modeled by a Lorentzian function, that is defined as

$$\mathcal{L}_{\text{Lorentzian}}(\Delta f) = \frac{\left(\frac{f_{\text{3dB}}}{2}\right)^2}{\Delta f^2 + \left(\frac{f_{\text{3dB}}}{2}\right)^2}.$$

(2.8)

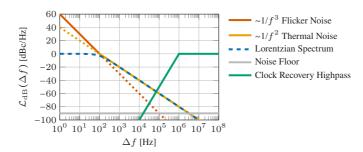

Fig. 2.1 visualizes the single-sideband carrier-to-modulation ratio of an oscillator containing the  $1/f^3$  (red curve) and  $1/f^2$  (orange curve) regions as well as the Lorentzian function (dashed blue curve), which overlaps well with the  $1/f^2$  curve. The highpass behavior of a clock recovery with a 3-dB bandwidth of about 1 MHz is sketched in green. As a result of the highpass behavior, high-frequency jitter of the oscillator is not compensated. For this reason, a high clock recovery bandwidth is preferable, which, however, entails increased self-noise (also referred to as detector jitter) of the clock recovery (see section 2.4) [4].

Fig. 2.1: VCO phase noise spectrum which decreases with  $1/f^3$  and  $1/f^2$  for offset frequencies smaller and larger than the linewidth, respectively. The Lorentzian function is simulated for a 200-MHz linewidth and approaches the  $1/f^2$  decay for frequencies larger than the linewidth. The clock recovery highpass response is transparent for high-frequency jitter.

To calculate the total jitter within a frequency range between  $f_1$  and  $f_2$ , eq. (2.7) is used with the carrier-to-modulation ratio integrated over the frequency range [4, 6], i.e.,

$$J_{f_1, f_2}(\Delta f) = \frac{1}{2\pi f_0} \sqrt{\int_{\Delta f = f_1}^{f_2} 10^{\frac{\mathcal{L}_{dB}(\Delta f)}{10}} d\Delta f} \times 10^{12}.$$

(2.9)

As an example using Fig. 2.1, the total jitter from  $10\,\text{MHz}$  to  $100\,\text{MHz}$  of a 50-GHz oscillator with noise floor at  $-90\,\text{dBc/Hz}$  will result in  $0.96\,\text{ps}$  jitter. In relation to the oscillator period of  $20\,\text{ps}$ , the jitter already accounts for 5% of the oscillator period.

## 2.1.1 Jitter Specifications

As shown in Fig. 2.1, clock recovery compensates only for a part of the VCO jitter. Furthermore, depending on the clock recovery design, it also adds self-noise jitter. If the recovered clock is used to transmit another signal, it can lead to a jitter building up in the network. For this reason, the recovered receiver clock must meet stringent specifications after clock recovery that typically include low jitter in order to be used in a commercial system. These specifications are defined in telecommunication standards, e.g., the Synchronous Digital Hierarchy (SDH) [24, 25], the Optical Transport Network (OTN) [26], or Ethernet (IEEE 802.3). In such standards, a distinction is made between different sources and system levels of jitter generation and transfer, which are explained below.

### Jitter generation

The jitter that is generated at a system output while no jitter is present at the system input.

#### Jitter transfer

The jitter transfer quantifies the extent to which input jitter is propagated through a system to its output. Here, the input jitter represents the cumulative jitter passed on from all preceding stages. If the jitter transfer of a system is too high, the output jitter can accumulate across multiple systems, potentially exceeding the jitter tolerance and resulting in transmission errors.

### **Output jitter**

Output jitter comprises both the internally generated jitter (jitter generation) and the jitter propagated through the system (jitter transfer). Accordingly, the resulting jitter spectrum must comply with the requirements defined by the relevant

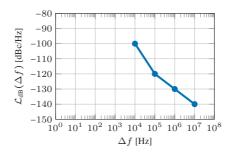

communication standard. For instance, Fig. 2.2 illustrates the phase noise mask specified in the Ethernet-based OpenZR+ Multi-Source Agreement, commonly applied in point-to-point coherent transmission systems spanning distances greater than 500 km [6]. The output jitter must remain below this defined phase noise mask.

#### Jitter tolerance

Jitter tolerance refers to a system's ability to withstand jitter present at its input without compromising performance. It is typically evaluated by superimposing a sinusoidal jitter onto the incoming communication signal. Although real-world jitter is not purely sinusoidal, this approach enables a systematic sweep across different jitter frequencies to verify compliance with system specifications. In the context of this thesis, a CFO between transmitter and receiver is introduced to assess system performance across various jitter frequencies, under the assumption that the measurement equipment's intrinsic jitter is negligible.

Fig. 2.2: Transmitter clock phase noise mask for an oscillator center-frequency of 469.83 MHz as specified in the OpenZR+ multi-source agreement [6].

## 2.2 Clock Recovery Architectures

Clock recovery architectures can be classified according to their circuit architecture, while each architecture has its own advantages and disadvantages. The synchronization of the receive clock can be accomplished in an *analog*, *digital*, or

hybrid analog-and-digital circuit architecture, whereby each of these implementation types can in turn have a feedback (FB) structure, feedforward (FF) structure, or a combination of both structures. The following chapter gives an overview of the different architectures and explains their advantages and disadvantages. This leads from the analog and hybrid architectures to an all-digital implementation, which was examined for modern optical communication systems in the course of this thesis.

## 2.2.1 All-Analog Clock Recovery

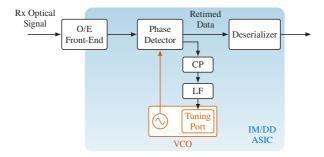

fully analog clock recovery architectures, also referred to as CDR, are the preferred synchronization circuits in short-distance optical transmission links, where low transceiver costs and low power consumption require simple receiver circuits without a receiver DSP. In general, this is the case for IM/DD systems [27], e.g., in intra-datacenter (DC) connections or PONs. CDR circuits can be realized in various ways (an overview is given in [28-30]), of which analog PLL-based techniques with a charge pump (CP), as depicted in Fig. 2.3, are commonly used in multi-gigabit fiber-optic links. Here, the optical signal is first converted into an electrical signal using a photodiode and, if necessary, amplified using a radio frequency (RF) amplifier, usually a transimpedance amplifier (TIA). Optionally, an analog equalizer circuit can follow. Next is the CDR circuit. First, an error signal is generated in a phase detector (PD), which is proportional to the sampling error between the received analog signal and the recovered clock. This error signal then tunes the electrical current in a CP, which is lowpass filtered in a loop filter (LF), and finally adjusts the voltage at the VCO such that the sampling error is reduced. The recovered and phase-locked clock is then used to accurately sample the received signal in the PD [28–30]. The sampling is often accomplished utilizing a D-flip-flop, which also serves as a decision circuit [29]. The retimed signal is thus available in a digital format and can be forwarded to a deserializer for further processing. Note that with a PLL-based analog CDR, no low-GHz reference clock is needed to stabilize the VCO in the start phase, since the PLL can inherently lock the clock to the receive signal in frequency and phase [29, 30].

Drawbacks of analog PLL-based CDR are the relatively large footprint as large LF capacitors are utilized and the low power efficiency in contrast to a digital CMOS-based implementation [29, 30]. Furthermore, analog CDR is difficult to implement in a deep-submicron technology while still providing the necessary performance required for high-speed communications [4, 30]. For these reasons, digital CDR for short-reach optical links currently represents a vivid field of research [11, 30].

Fig. 2.3: Clock recovery architecture of a charge pump PLL-based CDR circuit.

## 2.2.2 Hybrid Analog-and-Digital Clock Recovery

With increasing data rates, transmission distances, and higher-order modulation formats, distortions of the signal also become more pronounced, e.g., caused by CD, which makes reliable convergence of CDR circuits impossible. Modern receivers designed for high data rates and longer reach, for example for datacenter interconnects (DCIs), ultra-high-speed PONs, or coherent long-reach transmission, employ one or multiple ADCs in conjunction with a receiver DSP to compensate for the channel effects. The use of a DSP hence also allows parts of the PLL-based clock recovery to be implemented in digital domain and thus benefit from a space and energy-efficient implementation [4].

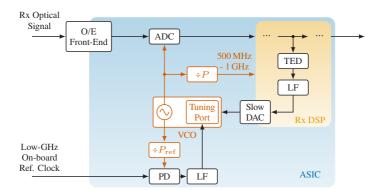

Fig. 2.4: Analog-and-digital clock recovery architecture.

Fig. 2.4 shows the receiver clock architecture for an IM/DD system with a single ADC and an analog-and-digital clock recovery scheme. In the case of coherent detection, multiple ADCs are driven by the clock and the digitized signals all enter the receiver DSP [4]. The VCO is typically operated at a very high frequency that is in the order of the sampling rate of the signal converters. For a sampling rate of 64 GSa/s, the VCO oscillates for example at 16 GHz [4]. Since, due to temperature and CMOS process variations, the high-GHz VCO starts with a large frequency offset in comparison to the desired oscillation frequency, which can be up to  $\pm 10\%$ , a very stable external low-GHz (e.g., 2 GHz) reference crystal oscillator is used [4]. The high-GHz clock is down-mixed by a factor  $P_{\rm ref}$  to the approximate frequency of the stable crystal oscillator. Afterwards, the frequency and phase of the VCO is stabilized to the 2 GHz reference in a PLL consisting of a PD and LF. The VCO is then stable in the order of tens of ppm accuracy and facilitates the subsequent fine-tuning to the transmitter clock by means of an analog-and-digital FB clock recovery.

The received signal is sampled and quantized after the analog front-end in an ADC, which is timed by the VCO. As the digital circuits in the receiver DSP can only operate at a processing clock of 500 MHz to 1 GHz, the ADC parallelizes the output samples. With a sampling rate of 64 GSa/s and a DSP clock of 500 MHz, this corresponds to a parallelization of 128 samples per clock cycle. The digitized

and parallelized sequence of samples then enters the receiver DSP in which the samples can be used to determine a timing error proportional to the sampling offset in a TED. Afterwards, the error signal is filtered in a digital LF and converted into a voltage utilizing a slow digital-to-analog converter (DAC), which in turn drives the VCO to converge to the transmitter clock. Since the temporal dynamic of the clock drift is less than the sampling rate of the signal converter, the low-speed DAC can be operated at a lower sampling rate, about the order of magnitude of the DSP clock, and therefore simplifies the application-specific integrated circuit (ASIC) design and reduces costs. Note that other algorithms can also precede the clock recovery in the DSP chain or can be implemented in a nested clock recovery and equalization structure in order to increase the tolerance of the TED to certain channel effects [15, 31–35].

## 2.2.3 All-Digital Clock Recovery

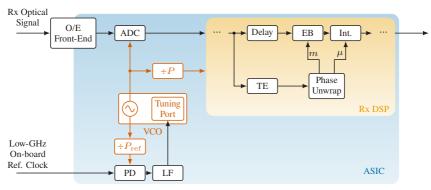

The use of a receiver DSP raises the question of whether the entire clock recovery can be implemented digitally and possibly operate the VCO in a free-running mode apart from the reference clock locking. This eliminates the need for one of the two VCO tuning ports and a low-speed DAC including its power supply, which is expected to result in further savings in energy consumption and reduced space on the chip. In addition to a fully digital PLL-based FB architecture, the all-digital implementation also offers the option of a FF clock recovery architecture. Both architectures are illustrated in Fig. 2.5.

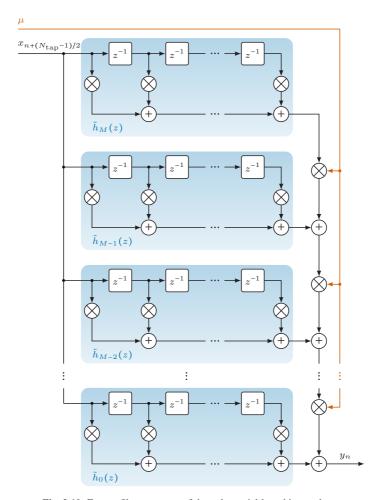

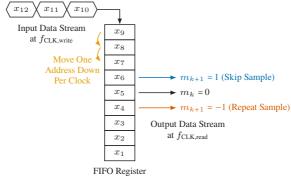

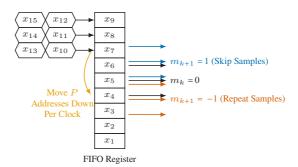

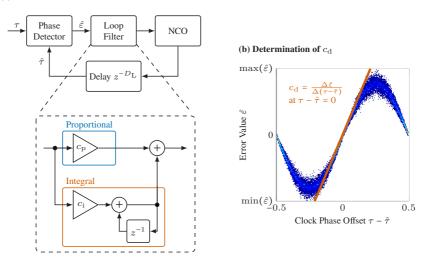

An FB clock recovery utilizing a digital PLL is shown in Fig. 2.5(a). Here, the timing correction is accomplished by an EB and an interpolator which correct the integer sampling delay m and fractional sampling delay  $\mu$ , respectively. The EB is a buffer that compensates for a CFO between the transmitter and receiver clock or absorbs large ranges of clock phase drift due to the non-existent physical adaptation of the receiver VCO to the transmitter VCO. The fractional and integer sampling offsets are provided by a numerical-controlled oscillator (NCO) instead of a VCO. The retimed signal then continues to the following DSP blocks and

#### (a) Digital Feedback Clock Recovery

#### (b) Digital Feedforward Clock Recovery

Fig. 2.5: All-digital FB (a) and FF (b) clock recovery architectures.

also enters the FB loop for the TED and LF, which are identical to the analogand-digital clock recovery. The LF, usually a proportional-integral (PI) filter, and NCO form a second-order PLL, which recursively derives a timing estimate.

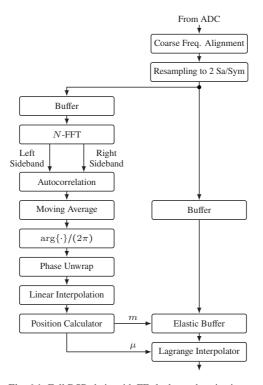

In FF schemes, the signal is split into two paths, as depicted in Fig. 2.5(b). In the first path, a TE directly estimates the sampling phase offset from the signal. Afterwards, the estimated phase is unwrapped at phase jumps of  $2\pi$ . To apply this sampling phase to the associated samples, the signal is delayed in the second path in a buffer and is then corrected in the EB and interpolator. The advantage of FF architectures lies in the immediate timing estimation, which makes a PLL obsolete, thus saving the acquisition time of the feedback control and enabling a higher clock recovery bandwidth. Furthermore, there is no need for a complex PLL design. Due to the higher bandwidth of the FF clock recovery, high-frequency jitter can be compensated more efficiently which increases the jitter tolerance of the transceiver and reduces the jitter transfer in a concatenated network [15]. As a drawback of FF architectures, the hardware complexity of the TEs is often mentioned [31]. This statement usually refers to the most popular TE proposed by Oerder and Meyr [36], which requires an oversampling >2 and for practical reasons is usually implemented at fourfold oversampling, while typical TEDs are often implemented at only twofold oversampling. However, as shown in section 2.3.1, there exist also TEs that require the same oversampling as TEDs. A combination of a slow analog-and-digital FB adjustment to physically align the VCO and a digital FF clock recovery to compensate for residual high-frequency jitter is demonstrated in [15].

## 2.3 Digital Clock Recovery Components

The following chapter explains the respective functional blocks of the digital clock recovery in more detail. To this end, section 2.3.1 first explains the key elements of the clock recoveries, namely the TED and TE. The elements for timing correction, i.e., the interpolator and the EB, are thereafter explained in sections 2.3.2 and section 2.3.3. Finally, a brief chapter on the LF design and

latencies in FB paths as well as the resulting choice of PI coefficients follows in section 2.3.4.

## 2.3.1 Timing Error Acquisition

This subsection explains the underlying mathematical concepts of digital and NDA timing error acquisition using a TED and a TE. Afterwards, the modified version of the algorithm by Barton and Al-Jalili is explained – an algorithm which was developed as part of the thesis. Finally, the last subchapter gives an overview of commonly used TEDs and TEs.

#### 2.3.1.1 Discrete-Time Random Sequence

At the transmitter, a sequence  $a_m^{-1}$  with  $m \in \mathbb{Z}$ , comprising data symbols from a predefined alphabet  $a_m \in \mathcal{A}$ , is generated. For the sake of simplicity and without loss of generality, a real-valued sequence is considered in the following. The elements of the sequence are i.i.d. random realizations every symbol period  $T_{\mathrm{sym}}$  of a zero-mean, cyclostationary random process a with realizations

$$a(t) = \sum_{m=-\infty}^{\infty} a_m \delta(t - mT_{\text{sym}}). \tag{2.10}$$

The autocorrelation function  $R_a(k_0)$  for a symbol delay  $k_0$  and mean value  $E\{\cdot\}$  is defined as

$$R_{\mathsf{a}}(k_0) = \mathrm{E}\left\{a_m^* a_{m+k_0}\right\} = \sigma_{\mathsf{a}}^2 \delta(k_0),$$

(2.11)

Note the analogy to the time-continuous case, where x(t) describes, both, the value of the function at a single point in time t and the whole function of time t. Since discrete-time systems always map series to series, no misunderstandings are to be expected.

with the variance  $\sigma_a^2$  and the Dirac function  $\delta(k_0)$ . The discrete-time Fourier transform (DTFT) of the autocorrelation function yields the power spectral density (PSD)  $S_a(f)$  as

$$S_{\mathsf{a}}(f) = \sum_{k_0 = -\infty}^{\infty} R_{\mathsf{a}}(k_0) \,\mathrm{e}^{\mathrm{j}\,2\pi f k_0 T_{\mathrm{sym}}} = \sigma_{\mathsf{a}}^2 \,.$$

(2.12)

The result shows, that the a random symbol sequence a(t) has in average a flat power spectrum. It follows that the amplitude of the Fourier transform of the random sequence is also constant over the frequency, while the phase has an uniform distribution [37]. Finally, the Dirac comb in eq. (2.10) is periodic in frequency-domain (FD) with the symbol rate  $f_{\rm sym} = 1/T_{\rm sym}$  (see appendix B), i.e.,

$$\mathcal{F}\left\{\sum_{m=-\infty}^{\infty} \delta(t - mT_{\text{sym}})\right\} = f_{\text{sym}} \sum_{m=-\infty}^{\infty} \delta\left(f - mf_{\text{sym}}\right), \qquad (2.13)$$

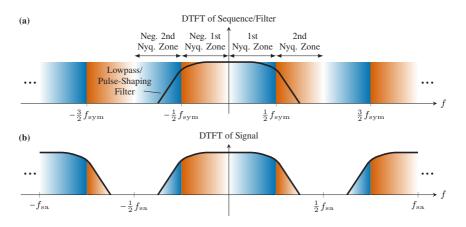

and therefore, also the DTFT of the symbol sequence is periodic with symbol rate. Fig. 2.6(a) visualizes the DTFT of the symbol sequence, where the information content is repeating at integer multiples of the symbol rate. In the following, the signal from eq. (2.10) is sampled with sampling frequency  $f_{\rm sa} > f_{\rm sym}$ , i.e., an oversampling ratio of  $\eta_{\rm os} = f_{\rm sa}/f_{\rm sym}$ , and is denoted as  $s_k$ . For convenience, an integer oversampling ratio greater or equal two is assumed. The periodicity of the N-point discrete Fourier transform (DFT)  $\underline{\tilde{s}}_n$  of the samples  $s_k$  and with frequency bin index n can then be expressed as

$$\tilde{\underline{S}}_n = \tilde{\underline{S}}_{n + \frac{m}{n-1}N} \tag{2.14}$$

for  $m \in \{1, \dots, \eta_{\rm os} - 1\}$  and  $n \in \{0, \dots, N/\eta_{\rm os} - 1\}$ . For simplicity, clock recovery algorithms are often implemented at twofold oversampling. Implementations at fractional oversampling were not considered in this thesis and hence integer

oversampling is assumed in this thesis as well. For twofold oversampling, i.e.,  $\eta_{\rm os}$  = 2, the spectral periodicity is

$$\tilde{\underline{S}}_n = \tilde{\underline{S}}_{n+\frac{N}{2}}. \tag{2.15}$$

Consequently, the product of a signal component  $\underline{\tilde{s}}_n$  and the complex conjugate of its periodic repetition  $\underline{\tilde{s}}_{n+N/2}$  is a real value, whose expected value is proportional to the variance  $\sigma_{\bf a}^2$

$$\tilde{\underline{s}}_{n}\tilde{\underline{s}}_{n+\frac{N}{2}}^{*} = \tilde{\underline{s}}_{n}\tilde{\underline{s}}_{n}^{*} = \left|\tilde{\underline{s}}_{n}\right|^{2} \\

E\left\{\underline{\tilde{s}}_{n}\tilde{\underline{s}}_{n+\frac{N}{2}}^{*}\right\} = E\left\{\tilde{\underline{s}}_{n}\tilde{\underline{s}}_{n}^{*}\right\} = \frac{\sigma_{\mathsf{a}}^{2}}{2}.$$

(2.16)

If the analog or digital pulse-shaped sequence still contains parts of the second (or higher) Nyquist zone, see Fig. 2.6(b), the periodicity of the information content is still preserved. This property is utilized by NDA clock recovery algorithms and is explained in the following subsections.

Fig. 2.6: (a) Discrete-time Fourier transform (DTFT) of a random sequence repeating at multiple integers of the symbol rate  $f_{\rm sym}=1/T_{\rm sym}$ . (b) The lowpass-filtered signal contains spectral components of the first and second Nyquist zone. Due to sampling at a higher rate, the frequency components repeat at multiples of the sampling rate  $f_{\rm sa}=1/T_{\rm sa}$ .

#### 2.3.1.2 Group Delay Estimation

A digital signal  $x_{k,\tau=0}=x(kT_{\rm sa})$  at sampling instance k and without any time delay  $\tau$  is considered. A version of the signal shifted in time by  $\tau$  is expressed as  $x_{k,\tau}=x(T_{\rm sa}(k+\eta_{\rm os}\tau))^1$ , where  $\tau$  is normalized to the symbol period  $T_{\rm sym}$ . A negative and positive time delay corresponds to a too early and too late sampling, respectively. The time delay is composed of the group delays of the various analog components in the communication channel, e.g., analog filters, amplifiers, cables, optical fibers, etc., as well as the asynchronous sampling between the transmitter and receiver clock and can generally vary in time, e.g., due to the clock phase walk of the oscillators. For simplicity, a time delay  $\tau$  constant over time is assumed in the analytical discussion. A time delay  $\tau$  in time domain (TD) corresponds to a linear phase shift in FD [38]. Consequently, the N-point DFT of the sequence  $x_{k,\tau}$  can be decomposed into the DFT of the signal at ideal sampling point  $\tilde{x}_{n,\tau=0}$  and a linear phase as

$$\sum_{k=-\infty}^{\infty} x_{k,\tau} e^{-j 2\pi k \frac{n}{N}} = \tilde{\underline{x}}_{n,\tau} = \tilde{\underline{x}}_{n,\tau=0} e^{j 2\pi \frac{n}{N} \eta_{os} \tau} . \tag{2.17}$$

The purpose of the digital clock recovery circuit is to estimate the sampling phase offset  $\tau$  and delay the signal in time to compensate for this delay. In the following, the total time delay  $\tau$  is attributed to a noise-free linear time-invariant (LTI) channel  $\underline{h}(t)$ , i.e., the group delay of the channel has to be estimated. As the timing phase estimation is implemented in digital domain, the digital impulse response  $\underline{h}_k$  of the channel is considered. The frequency response of the channel using an N-point DFT is defined as  $\underline{\tilde{h}}_n$  and can be decomposed in magnitude and unwrapped phase as

$$\underline{\tilde{h}}_{n} = \left| \underline{\tilde{h}}_{n} \right| e^{j \varphi_{n}},$$

(2.18)

Mathematically, a delay is usually defined as  $\delta(t-\tau)$  and finally the group delay  $\tau$  corresponds to the negative derivative of the spectral phase as in eq. (A.28). In the field of clock recovery, the notation  $\delta(t+\tau)$  is commonly used and, thus, the negative sign when estimating the group delay can be omitted.

for  $n \in \{N/2, \dots, N/2-1\}$ , where n=0 refers to the zero-frequency. According to the definition of the group delay of a system in eq. (A.28) in appendix A.2.3.1, the group delay at the n-th frequency bin can be obtained for a given frequency interval  $1 < \Delta f < N$  as

$$\tau_{\mathrm{g},n}(\Delta f) = \begin{cases} \frac{1}{2\pi} \frac{N}{\Delta f} \left( \varphi_{n-\frac{\Delta f}{2}} - \varphi_{n+\frac{\Delta f}{2}} \right) & \Delta f \text{ even, } -\frac{N-\Delta f}{2} \leq n < \frac{N-\Delta f}{2} \\ \frac{1}{2\pi} \frac{N}{\Delta f} \left( \varphi_{n-\frac{\Delta f-1}{2}} - \varphi_{n+\frac{\Delta f-1}{2}} \right) & \Delta f \text{ odd, } -\frac{N-\Delta f+1}{2} \leq n \leq \frac{N-\Delta f-1}{2} \\ \text{undefined} & \text{otherwise.} \end{cases}$$

$$(2.19)$$

In the following, a frequency interval with even  $\Delta f$  is considered. By averaging over the frequency-dependent group delay, the frequency-averaged group delay  $\overline{\tau}_{\rm g}(\Delta f)$  is obtained as

$$\overline{\tau}_{g}(\Delta f) = \frac{1}{N - \Delta f} \sum_{n = -(N - \Delta f)/2}^{(N - \Delta f)/2 - 1} \tau_{g,n}(\Delta f)

= \frac{1}{2\pi} \frac{N}{(N - \Delta f)\Delta f} \sum_{n = -(N - \Delta f)/2}^{(N - \Delta f)/2 - 1} \varphi_{n - \frac{\Delta f}{2}} - \varphi_{n + \frac{\Delta f}{2}}.$$

(2.20)

Assuming that the frequency-depended group delay is only slightly nonlinear over the frequency range under consideration, a large interval  $\Delta f$  provides a sufficient estimation of the group delay. For the special case of  $\Delta f = N/2$ , the frequency-averaged group delay results in

$$\overline{\tau}_{g}\left(\Delta f = \frac{N}{2}\right) = \frac{1}{2\pi} \frac{4}{N} \sum_{n=-N/4}^{N/4-1} \varphi_{n-\frac{N}{4}} - \varphi_{n+\frac{N}{4}} \\

= \frac{1}{2\pi} \frac{4}{N} \sum_{n=0}^{N/2-1} \varphi_{n} - \varphi_{n+\frac{N}{2}}.$$

(2.21)

Note the re-indexing of  $n \in \{0, ..., N-1\}$  in eq. (2.22). Since averaging the absolute phase can lead to incorrect mean values when phase jumps at  $\pm \pi$  occur, averaging in the complex plane is preferred, i.e.,

$$\frac{1}{N} \sum_{n=0}^{N-1} \varphi_n = \frac{1}{N} \sum_{n=0}^{N-1} \arg \left\{ e^{j \varphi_n} \right\}$$

$$= \arg \left\{ \prod_{n=0}^{N-1} \left( e^{j \varphi_n} \right)^{\frac{1}{N}} \right\}.$$

(2.22)

Using eq. (2.22) and the definition of the channel from eq. (2.18), the frequency-averaged group delay from eq. (2.21) can also be expressed as

$$\overline{\tau}_{g} = \frac{1}{\pi} \arg \left\{ \prod_{n=0}^{N/2-1} \left( e^{i\left(\varphi_{n} - \varphi_{n+\frac{N}{2}}\right)} \right)^{\frac{2}{N}} \right\}$$

$$= \frac{1}{\pi} \arg \left\{ \prod_{n=0}^{N/2-1} \left( \tilde{h}_{n} \tilde{h}_{n+\frac{N}{2}}^{*} \right)^{\frac{2}{N}} \right\}.$$

(2.23)

This equation provides an accurate estimate of the linear phase portion of an arbitrary nonlinear phase over the frequency. However, it comes with two disadvantages. First, the geometric mean determines the exact mean phase, but does not take into account the amplitudes of the complex values, i.e., the phase of signal components with low signal power in the stopband are equally accounted for as the phase of signal components in the passband. This can lead to estimation errors, particularly for signal components below the noise floor. Furthermore, the product expansion consists of a large number of complex-valued multiplications, which result in a high computational effort.

A sufficient approximation of the geometric mean for weak phase nonlinearities in the passband is the arithmetic mean, i.e.,

$$\arg\left\{\prod_{n=0}^{N-1} \left(e^{j\varphi_n}\right)^{\frac{1}{N}}\right\} \approx \arg\left\{\frac{1}{N} \sum_{n=0}^{N-1} e^{j\varphi_n}\right\}. \tag{2.24}$$

This has the advantage that the phases of weak signal components are weighted less strongly and complex-valued multiplications are replaced by complex-valued additions. Using this approximation, eq. (2.23) yields

$$\overline{\tau}_{g} \approx \frac{1}{\pi} \arg \left\{ \sum_{n=0}^{N/2-1} \underline{\tilde{h}}_{n} \underline{\tilde{h}}_{n+\frac{N}{2}}^{*} \right\}. \tag{2.25}$$

Note that here the group delay is related to the sampling period, while the timing estimate for the clock recovery is normalized to the symbol period. Furthermore, it is emphasized that the sum in eq. (2.25) corresponds to the spectral correlation of the filter, which is commonly referred to as clock tone.

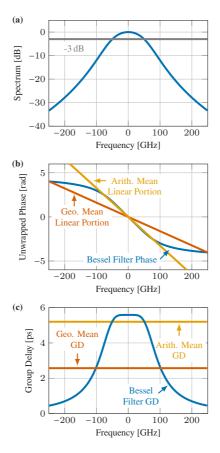

### **Example: 3rd-order Bessel lowpass filter**

In the following example, a channel with lowpass characteristic is considered, which can be modeled as a 3rd-order Bessel lowpass filter that is defined as

$$\tilde{\underline{h}}(f) = \frac{15}{15 - 24\pi^2 f^2 + j(30\pi f - 8\pi^3 f^3)},$$

(2.26)

where the 3-dB bandwidth is defined at the angular frequency  $\omega=2\pi f=1.756$  [39]. Fig. 2.7 shows the simulated filter characteristics of a 3rd-order Bessel lowpass filter with a 3-dB bandwidth of 50 GHz and a sampling rate of 500 GHz. In Fig. 2.7(a), the PSD is shown with the 3-dB limit. In Fig. 2.7(b), the unwrapped phase is obtained as  $\arg\{\tilde{h}(f)\}$  (see eq. (A.27)). From this, the group delay in Fig. 2.7(c) is computed according to eq. (2.19) for  $\Delta f=2$  (blue curve) and the mean group delay according to eq. (2.20) using the geometric mean from eq. (2.22) (red curve) and the arithmetic mean from eq. (2.24) (orange curve). The geometric mean averages the group delay over all frequencies and therefore corresponds to the true mean group delay. The arithmetic mean additionally weights the spectral phase differences according to the amplitudes of the frequency response. For this reason, the arithmetic mean approximates the group delay in the passband, which is relevant for the sampling offset of the signal. Based on the two mean group delays obtained, the linear phase portion of the Bessel filter is plotted in Fig. 2.7(b). Using the geometric mean gives the linear phase portion of the

system over all frequencies. This also includes weak signal components, which in practice are strongly affected by noise and distort the phase estimation. The arithmetic mean, on the other hand, approximates the linear phase in the passband and thus reduces distortions caused by out-of-band frequency components. Note that the arithmetic mean only provides reliable phase estimates as long as the frequency-dependent spectral phase in the passband is weakly nonlinear, which is true for a Bessel filter. Furthermore, if a large frequency interval  $\Delta f = N/2$  is used, the determined geometric and arithmetic group delay is incorrect for strong nonlinear phases. In this case, only a slight nonlinear phase can be tolerated in the observation window.

## 2.3.1.3 Modified Barton & Al-Jalili Algorithm

To obtain an understanding of the TE, the received signal is considered as a function of the transmitted signal and the communication channel. A real-valued upsampled random symbol sequence s(t) (see section 2.3.1.1) is digitally and/or analog pulse-shaped at the transmitter with impulse response p(t). It then passes through a linear channel with real-valued impulse response c(t). At the receiverside, zero-mean additive white Gaussian noise (AWGN) n(t) is added before the signal is filtered by a receive filter p(t), hence, emulating bandwidth limitations of the receiver. For convenience, the transmitter lowpass p(t) and receiver lowpass p(t) have symmetric and real-valued impulse responses and therefore also feature real-valued Fourier transforms with zero spectral phase. Any time delay caused by the transmitter and receiver architecture (circuit group delays or DAC and ADC sampling offset) and the channel is modeled by an overall group delay t normalized to the symbol period as t0 the received signal t1 is then described as

$$x(t) = s(t) * p(t) * c(t) * g(t) * \delta(t + \tau T_{\text{sym}}) + n(t) * g(t), \qquad (2.27)$$

For simplicity, we consider a real-valued signal. However, the considerations are also valid for a complex-valued upsampled symbol sequence  $\underline{s}(t)$ .

**Fig. 2.7:** 3rd-order Bessel lowpass filter for a sampling rate of 500 GHz and a 3-dB bandwidth of 50 GHz. (a) Spectrum in decibel. (b) Nonlinear spectral phase of the Bessel filter with the linear spectral phase portion obtained from the frequency-averaged group delay (GD) shown in (c).

where \* is the convolution operator. To simplify, h(t) = p(t) \* c(t) \* g(t) is abbreviated. After sampling with sampling interval  $T_{\rm sa}$ , the received samples are obtained as  $x_k = x(kT_{\rm sa})$ . In the following, twofold oversampling  $\eta_{\rm os} = 2$  is assumed, i.e., the spectrum of the sampled receive signal contains two copies of  $S_{\rm a}(f)$ , as shown in Fig. 2.6(b). Taking the DFT over a block of N received samples yields the FD representation as

$$\tilde{\underline{x}}_n = \tilde{\underline{s}}_n \tilde{h}_n e^{j 4\pi \frac{n}{N}\tau} + \tilde{\underline{n}}_n \tilde{g}_n$$

(2.28)

with the ensemble average denoted as  $\langle \cdot \rangle$  given by

$$\langle \tilde{x}_n \rangle = \langle \tilde{s}_n \rangle \tilde{h}_n e^{j 4\pi \frac{n}{N} \tau}$$

(2.29)

The TE according to Barton and Al-Jalili [40] exploits the periodicity of the cyclostationary random sequence from eq. (2.15) to cancel the random phase of the sequence  $\underline{\tilde{s}}$  by subtracting the phase of the ensemble average of the two frequency components for a frequency separation of  $\Delta f = N/2$  as

$$\frac{1}{2\pi} \left( \arg\left\{ \left\langle \tilde{x}_{n} \right\rangle \right\} - \arg\left\{ \left\langle \tilde{x}_{n+\frac{N}{2}} \right\rangle \right\} \right)$$

$$= \frac{1}{2\pi} \left( \arg\left\{ \left\langle \tilde{x}_{n} \right\rangle \tilde{h}_{n} e^{j 4\pi \frac{n}{N}\tau} \right\} - \arg\left\{ \left\langle \tilde{x}_{n} \right\rangle \tilde{h}_{n+\frac{N}{2}} e^{j 4\pi \frac{n-\frac{N}{2}}{N}\tau} \right\} \right)$$

$$= \frac{1}{2\pi} \left( \arg\left\{ \left\langle \tilde{x}_{n} \right\rangle \right\} + 4\pi \frac{n}{N}\tau - \arg\left\{ \left\langle \tilde{x}_{n} \right\rangle \right\} - 4\pi \frac{n}{N}\tau + 2\pi\tau \right)$$

$$= \frac{1}{2\pi} (2\pi\tau)$$

$$= \tau, \tag{2.30}$$

where the identity  $\arg\{c_1c_2\} = \arg\{c_1\} + \arg\{c_2\}$  with a phase ambiguity of  $2\pi$  is used. Considering not the ensemble averages and instead the frequency components obtained for the calculation of a single DFT, the estimated sampling offset  $\hat{\tau}$  is obtained as

$$\hat{\tau}_{\text{BAJ}} = \frac{1}{2\pi} \left( \arg \left\{ \underline{\tilde{x}}_n \right\} - \arg \left\{ \underline{\tilde{x}}_{n+\frac{N}{2}} \right\} \right). \tag{2.31}$$

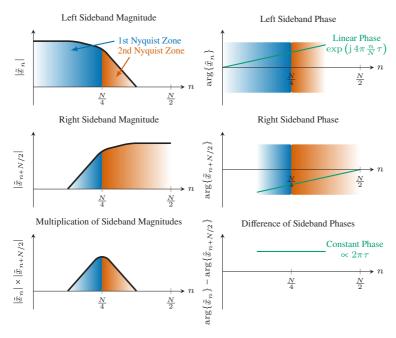

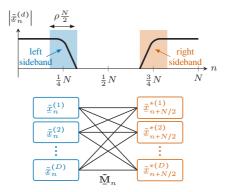

In the course of this thesis, the modified BAJ algorithm (mod-BAJ) was applied and analyzed for the first time in the literature [C1, C2, 41]. Here, the phase difference in the complex plane is averaged over the frequency for  $\Delta f = N/2$  to effectively suppress noise, i.e., the frequency components of the left sideband  $\tilde{x}_n$  are multiplied by the complex conjugate frequency components of the right sideband  $\tilde{x}_{n+N/2}$  (see eq. (2.25)). The TE therefore results in

$$\hat{\tau}_{\text{mod-BAJ}} = \frac{1}{2\pi} \arg \left\{ \sum_{n=0}^{N/2-1} \tilde{x}_n \tilde{x}_{n+\frac{N}{2}}^* \right\}.$$

(2.32)

Again, by examining the ensemble average from eq. (2.29) and using eq. (2.16), it can be shown that this algorithm provides the sampling offset as

$$\frac{1}{2\pi} \arg \left\{ \sum_{n=0}^{N/2-1} \left( \tilde{\underline{x}}_n \tilde{\underline{x}}_{n+\frac{N}{2}}^* \right) \right\}$$

$$= \frac{1}{2\pi} \arg \left\{ \sum_{n=0}^{N/2-1} \left( \tilde{\underline{s}}_n \right) \tilde{h}_n e^{j 4\pi \frac{n}{N} \tau} \left\langle \tilde{\underline{s}}_n^* \right) \tilde{h}_{n+\frac{N}{2}} e^{-j 4\pi \frac{n-\frac{n}{N}}{N} \tau} \right\}$$

$$= \frac{1}{2\pi} \arg \left\{ \sum_{n=0}^{N/2-1} \left( \tilde{\underline{s}}_n \tilde{\underline{s}}_n^* \right) \tilde{h}_n \tilde{h}_{n+\frac{N}{2}} e^{j 2\pi \tau} \right\}$$

$$= \frac{1}{2\pi} \arg \left\{ \sum_{n=0}^{N/2-1} \frac{\sigma_{\mathbf{a}}^2}{2} \tilde{h}_n \tilde{h}_{n+\frac{N}{2}} e^{j 2\pi \tau} \right\}$$

$$= \tau. \tag{2.33}$$

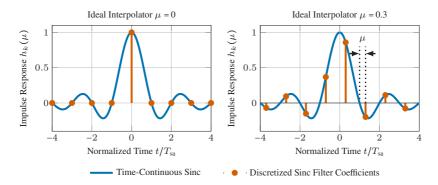

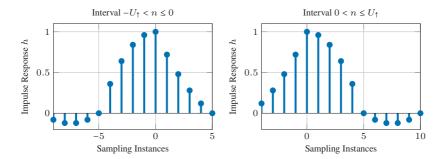

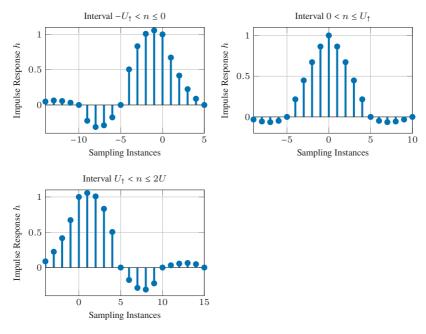

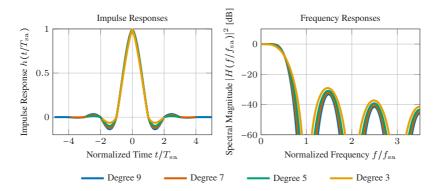

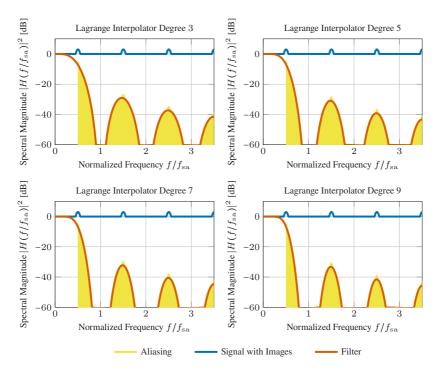

Fig. 2.8 illustrates the magnitude and phase of the multiplication of the left sideband with the complex conjugate right sideband and how a constant spectral phase proportional to the sampling offset can be obtained. Since the BAJ and mod-BAJ algorithms directly provide a timing estimate  $\hat{\tau}$ , they can be implemented in a FF clock recovery architecture.