# Cache Contention-Aware System-Level Resource Optimization on Clustered Multicores using Machine Learning

Zur Erlangung des akademischen Grades eines

Doktors der Ingenieurwissenschaften

von der KIT-Fakultät für Informatik des Karlsruher Instituts für Technologie (KIT)

> genehmigte Dissertation

Mohammed Bakr Sikal

aus Larache (Marokko)

Tag der mündlichen Prüfung: 25. Juli 2025

- 1. Referent/Referentin: Prof. Dr.-Ing. Jörg Henkel

- 2. Referent/Referentin: Prof. Dr. Sridevan Parameswaran

| Hiermit erkläre ich an Eides statt, dass ich die von mir vorgelegte Arbeit selbst-                                                                                                                                                                                                                                                                                             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ständig verfasst habe, dass ich die verwendeten Quellen, Internet-Quellen und Hilfsmittel vollständig angegeben habe und dass ich die Stellen der Arbeit – einschließlich Tabellen, Karten und Abbildungen – die anderen Werken oder dem Internet im Wortlaut oder dem Sinn nach entnommen sind, auf jeden Fall unter Angabe der Quelle als Entlehnung kenntlich gemacht habe. |

|                                                                                                                                                                                                                                                                                                                                                                                |

| Mohammed Bakr Sikal                                                                                                                                                                                                                                                                                                                                                            |

## **Acknowledgements**

This dissertation is dedicated to my father, Ahmed Sikal, whose values, dreams, and belief in me have been a guiding light throughout my life. Though he is no longer here to witness this milestone, his presence was constant in every step of this journey, and I carry his memory in all that I do.

First and foremost, I want to thank Prof. Jörg Henkel for being far more than just a supervisor. His guidance, trust, and constant support shaped not only my research but also the way I think as a scientist. The environment he built, with its balance of research freedom and direction, gave me the needed space to grow and innovate.

I am grateful to Prof. Sri Parameswaran for agreeing to be my co-advisor. His input, help and generosity, especially in traveling all the way from Sydney to Karlsruhe just to attend my defense, is something I will never forget. That gesture meant a great deal to me.

My heartfelt thanks go to Dr.-Ing. Heba Khdr, who has been a constant in my PhD journey from day zero. For five years, her mentorship has been invaluable, with her incredible scientific precision and rigor, with genuine care for my growth as a researcher and as a person. She has challenged me to think critically, guided me with patience, and never hesitated to give honest, constructive feedback, even when it was difficult to hear. Working with her has not only shaped my research, but also left me with lessons in perseverance, humility, and dedication that I will definitely carry throughout my career.

I am grateful to all my colleagues and office mates for making my PhD an enjoyable journey at the office. My collaborations with Dr. -Ing. Heba Khdr, Prof. Dr. -Ing. Jeferson Gonzalez, Dr.-Ing. Hassan Nassar, Benedikt Dietrich, Dr. -Ing. Lars Bauer, Dr. Kostas Balaskas and Dr. Lokesh Siddhu made research an enjoyable effort. I would like to also thank Dr. -Ing. Martin Rapp for his valuable guidance and collaboration during the first two years of my

PhD, which greatly supported my early steps in this journey. Finally, a special thanks to Prof. Dr. Jeferson and Zeynep, whose friendship brought balance during even the most intense deadlines.

I am profoundly grateful to my mother, Najat Draina, who has been my anchor, my constant source of strength, and my greatest supporter. Her sacrifices have shaped who I am today. For more than three decades, she has been there through every success and every setback, offering unconditional love, encouragement, and faith in my abilities. This achievement is as much hers as it is mine, and it rests on the foundation she built with her dedication, hard work, and boundless care.

To my wife and my partner, Ilham Chekrad, thank you for standing beside me through it all. For celebrating my wins as if they were your own, for picking me up when I stumbled, and for never losing faith in me. You have been my anchor in moments of uncertainty and my greatest source of joy in moments of success. Your patience with the long working hours, your understanding of the sacrifices this journey demanded, and your quiet encouragement on the hardest days kept me moving forward. More than anyone, you have seen the full reality of this process, the stress, the setbacks, the self-questioning—and yet you remained true in your support. This achievement is not mine alone; it is ours, and I am endlessly grateful to share it with you.

To my family: my sister Abir, my brother-in-law Ahmed, to Tita, and to the joyful little newcomers to our lives—my nephew Sami and my niece Lyne Lilia—thank you for filling our family with light. Even in their own small ways, these little ones have brought me moments of pure joy and reminded me of what truly matters beyond work. Your love, encouragement, and pride in my work have meant more to me than I can say.

Finally, I am thankful to my family-in-law for their constant support and encouragement throughout this journey, Tonton Tahar, Tati Fatima, Ali, Khaoula and Soukaina, and I am grateful to be part of such a caring family.

Thank you.

Mohammed Bakr Sikal

## **List of Publications**

The following list enumerates papers and book chapters published by the author of this dissertation while pursuing his doctorate.

# First-author publications that present major contributions to this dissertation

- [1] Mohammed Bakr Sikal, Heba Khdr, Martin Rapp, and Jörg Henkel. "Thermal- and Cache-Aware Resource Management based on ML-Driven Cache Contention Prediction". In: 2022 Design, Automation & Test in Europe Conference & Exhibition (DATE). 2022, pp. 1384–1388. DOI: 10.23919/DATE54114.2022.9774776

- [2] Mohammed Bakr Sikal, Heba Khdr, Martin Rapp, and Jörg Henkel. "Machine Learning-based Thermally-Safe Cache Contention Mitigation in Clustered Manycores". In: 2023 60th ACM/IEEE Design Automation Conference (DAC). 2023, pp. 1–6. DOI: 10.1109/DAC56929.2023.10247708

- [3] Mohammed Bakr Sikal, Heba Khdr, Lokesh Siddhu, and Jörg Henkel. "ML-Based Thermal and Cache Contention Alleviation on Clustered Manycores With 3-D HBM". in: *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD)* 43.11 (2024), pp. 3614–3625. DOI: 10.1109/TCAD.2024.3438998

- [4] Mohammed Bakr Sikal, Jeferson González-Gómez, Heba Khdr, and Jörg Henkel. "Contention-Aware Forecasting of Energy Efficiency through Sequence-Based Models in Modern Heterogeneous Processors". In: 2025 62nd ACM/IEEE Design Automation Conference (DAC). 2025

- [5] Mohammed Bakr Sikal, Jeferson González-Gómez, Osama Abboud, Xun Xiao, Heba Khdr, and Jörg Henkel. "PHASEL: Learning Phase-Level Application Sensitivities for Energy-Efficient Resource Management in Heterogeneous 6G Systems". In: Under Review. 2025

[6] Mohammed Bakr Sikal, Jeferson González-Gómez, Heba Khdr, and Jörg Henkel. "ARDiS: A Portable and Unified Resource Management Framework in Real Hardware Systems". In: *ACM Transactions on Design Automation of Electronic Systems (TODAES)* (2025). Under Review

# First-author publications that present minor contributions to this dissertation

[7] Mohammed Bakr Sikal, Hassan Nassar, Heba Khdr, and Jörg Henkel. "A Dataset for LLM-Based Detection of Power-Wasters in Routed FPGA Netlists". In: 2025 IEEE International Conference on LLM-Aided Design (ICLAD). 2025, pp. 235–241. DOI: 10.1109/ICLAD65226.2025.00023

#### Other co-authored publications

- [8] Martin Rapp, Mohammed Bakr Sikal, Heba Khdr, and Jörg Henkel. "SmartBoost: Lightweight ML-Driven Boosting for Thermally-Constrained Many-Core Processors". In: 2021 58th ACM/IEEE Design Automation Conference (DAC). 2021, pp. 265–270. DOI: 10.1109/DAC18074.2021. 9586287

- [9] Jeferson González-Gómez, Mohammed Bakr Sikal, Heba Khdr, Lars Bauer, and Jörg Henkel. "Balancing Security and Efficiency: System-Informed Mitigation of Power-Based Covert Channels". In: IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems 43.11 (2024), pp. 3395–3406. DOI: 10.1109/TCAD.2024.3438999

- [10] Jeferson González-Gómez, Mohammed Bakr Sikal, Heba Khdr, Lars Bauer, and Jörg Henkel. "Smart Detection of Obfuscated Thermal Covert Channel Attacks in Many-core Processors". In: *2023 60th ACM/IEEE Design Automation Conference (DAC)*. 2023, pp. 1–6. DOI: 10.1109/DAC56929.2023.10247844

- [11] Heba Khdr, Mustafa Enes Batur, Kanran Zhou, Mohammed Bakr Sikal, and Jörg Henkel. "Multi-Agent Reinforcement Learning for Thermally-Restricted Performance Optimization on Manycores". In: 2024 Design, Automation & Test in Europe Conference & Exhibition (DATE). 2024, pp. 1–6. DOI: 10.23919/DATE58400.2024.10546574

- [12] Konstantinos Balaskas, Heba Khdr, Mohammed Bakr Sikal, Fabian Kreß, Kostas Siozios, Jürgen Becker, and Jörg Henkel. "Heterogeneous

- Accelerator Design for Multi-DNN Workloads via Heuristic Optimization". In: *IEEE Embedded Systems Letters* 16.4 (2024), pp. 317–320. DOI: 10.1109/LES.2024.3443628

- [13] Heba Khdr, Mohammed Bakr Sikal, Benedikt Dietrich, and Jörg Henkel. "Towards the Optimization of Hardware Efficiency through Machine Learning". In: 2025 IEEE Computer Society Annual Symposium on VLSI (ISVLSI). 2025

## **Abstract**

In the past decade, clustered architectures have become the mainstream design of multi-core processors in mobile devices, data center servers, and HPC systems. Unlike monolithic multi-core chips, clustered architectures partition cores into clusters that share resources like the last-level cache, improving scalability and efficiency. Despite these advantages, they also introduce new challenges, particularly concerning cache contention, which becomes more complex to manage than in traditional monolithic designs. In monolithic systems, where all cores share a single last-level cache, application-to-core mapping does not affect cache contention patterns. In clustered architectures, however, an additional optimization dimension emerges: how to efficiently map applications to clusters to minimize contention. Moreover, modern clustered processors, especially heterogeneous ones, feature multi-level shared caches, leading to contention both within and across clusters. As application behavior evolves dynamically, continuous adjustments to mapping strategies are required at runtime.

Cache contention is not an isolated phenomenon. In fact, unmanaged cache contention impacts performance, temperature, and energy efficiency of clustered multicores, potentially leading to execution slowdowns and creating complex tradeoffs. Addressing these tradeoffs necessitates intelligent resource management, including task mapping, migration, and DVFS. To this end, machine learning-based techniques have emerged as a promising solution, enabling predictive and adaptive decision-making to mitigate cache contention in clustered multi-core systems. To this end, this dissertation presents novel machine learning-based resource management techniques for tackling the cache contention problem and its implications for performance, temperature and energy efficiency, on both homogeneous and heterogeneous clustered multi-core processors.

First, a contention-aware technique for minimizing the temperature of clustered homogeneous multi-core processors under performance constraints is

introduced. The technique employs a neural network-based model to predict the impact of different application-to-cluster mappings and DVFS configurations on the performance of applications considering cache contention effects. After identifying all application-to-cluster mapping options at runtime and eliminating those that violate the performance constraint, the technique evaluates their potential thermal impacts, before applying the configuration that leads to the minimum overall system temperature.

Second, to further explore the implications of cache contention, a machine learning-based contention-aware task migration and DVFS technique to maximize the performance of clustered homogeneous multi-core processors under a thermal constraint is presented. The technique leverages the prediction accuracy of a trained neural network to continuously identify the migration options that would minimize cache contention effects on different clusters. Eventually, the application migration that would maximize the overall system performance without causing thermal violations is chosen.

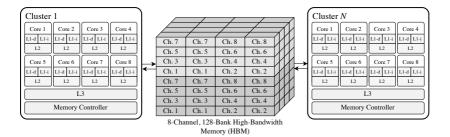

Third, as clustered multicores started adopting 3D memories like the High-Bandwidth Memory (HBM), a machine learning-based contention-aware technique to maximize the overall system performance under temperature constraints of the processor and the HBM is presented. The technique orchestrates four neural network models at runtime, to continuously identify the migration options that minimize contention effects and maximize the overall system performance, while maintaining the thermal safety of both the processor and the HBM.

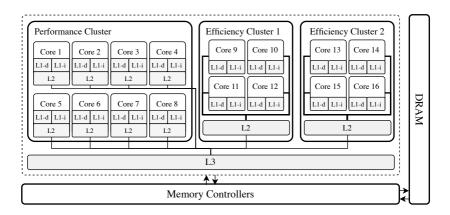

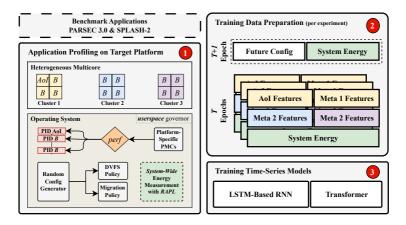

Finally, to address the complexity of cache contention in clustered heterogeneous multicores, a novel methodology for training energy efficiency forecasting models is presented. This methodology integrates structured data generation with LSTM- and Transformer-based models to predict future system states under dynamic and previously unseen runtime conditions. This work is made possible by a portable and open-source framework for system-level resource management on real hardware, also a contribution of this research. The framework enables the experimental validation of the proposed methodology on a real clustered heterogeneous multicore, ensuring its effectiveness in real-world deployments.

The evaluations of these techniques on both simulation and real hardware highlight improvements over the state of the art while maintaining a negligible runtime overhead, which demonstrates that machine learning-based

approaches, when carefully integrated with system-level resource management, can successfully tackle the cache contention problem, and lead to significant improvement in terms of performance, temperature, and energy efficiency in modern homogeneous and heterogeneous multicores.

## Zusammenfassung

In den letzten zehn Jahren haben sich Cluster-Architekturen als dominantes Design für Mehrkernprozessoren in mobilen Endgeräten, Rechenzentrumsservern und HPC-Systemen etabliert. Im Gegensatz zu monolithischen Mehrkernchips partitionieren Cluster-Architekturen die Kerne in Gruppen (Cluster), die Ressourcen wie den Last-Level-Cache (LLC) gemeinsam nutzen, was die Skalierbarkeit und Effizienz verbessert. Trotz dieser Vorteile führen Cluster-Architekturen jedoch auch neue Herausforderungen ein, insbesondere im Hinblick auf Cache-Konkurrenz, die sich komplexer gestaltet als in traditionellen monolithischen Designs. In monolithischen Systemen, in denen alle Kerne einen einzigen Last-Level-Cache teilen, hat die Zuordnung von Anwendungen zu Kernen keinen Einfluss auf das Muster der Cache-Konkurrenz. In Cluster-Architekturen hingegen entsteht eine zusätzliche Optimierungsdimension: die effiziente Zuordnung von Anwendungen zu Clustern zur Minimierung der Konkurrenz. Darüber hinaus weisen moderne Cluster-Prozessoren – insbesondere heterogene Prozessoren – mehrstufige geteilte Caches auf, was zu Konkurrenz sowohl innerhalb als auch zwischen Clustern führt. Da sich das Verhalten von Anwendungen dynamisch verändert, sind kontinuierliche Anpassungen der Zuordnungsstrategien zur Laufzeit erforderlich.

Cache-Konkurrenz ist kein isoliertes Phänomen. Tatsächlich beeinträchtigt eine unzureichend adressierte Cache-Konkurrenz die Leistung, Temperatur und Energieeffizienz von Cluster-Mehrkernsystemen erheblich. Dies kann zu Ausführungsverzögerungen, thermischen Hotspots und unnötig hohem Energieverbrauch führen. Zur Bewältigung dieser Probleme sind intelligente Ressourcenmanagement-Techniken wie Anwendungsverteilung, Thread-Migration und dynamische Spannungs- und Frequenzskalierung (DVFS) erforderlich. In diesem Zusammenhang haben sich Verfahren des maschinellen Lernens als vielversprechende Lösung etabliert, da sie eine vorausschauende und adaptive Entscheidungsfindung zur Minderung der Cache-Konkurrenz in Cluster-Mehrkernsystemen ermöglichen. Diese Dissertation stellt neuartige,

auf maschinellem Lernen basierende Ressourcenmanagementtechniken zur Bewältigung des Cache-Konkurrenzproblems und seiner Auswirkungen auf Leistung, Temperatur und Energieeffizienz in homogenen und heterogenen Cluster-Mehrkernprozessoren vor.

Zunächst wird eine konkurrenzbewusste Technik zur Minimierung der Temperatur homogener Cluster-Mehrkernprozessoren unter Einhaltung von Leistungsanforderungen vorgestellt. Die Technik verwendet ein neuronales Netzwerk zur Vorhersage der Auswirkungen verschiedener Zuordnungen von Anwendungen zu Clustern sowie DVFS-Konfigurationen auf die Anwendungsleistung unter Berücksichtigung von Cache-Konkurrenz-Effekten. Nach der Identifizierung aller möglichen Zuordnungsoptionen zur Laufzeit und der Eliminierung derjenigen, die die Leistungsgrenze verletzen, bewertet die Technik deren potentielle thermische Auswirkungen und wählt schließlich die Konfiguration aus, die zur geringsten Gesamttemperatur des Systems führt.

Zweitens wird eine auf maschinellem Lernen basierende, konkurrenzbewusste Technik zur Anwendungsmigration und DVFS vorgestellt, mit dem Ziel, die Leistung homogener Cluster-Mehrkernprozessoren unter Einhaltung eines Temperaturgrenzwerts zu maximieren. Diese Technik nutzt die Vorhersagegenauigkeit eines trainierten neuronalen Netzwerks, um kontinuierlich die Migrationsoptionen zu identifizieren, die die Cache-Konkurrenz in verschiedenen Clustern minimieren. Letztlich wird diejenige Migrationsentscheidung getroffen, die die Systemleistung maximiert, ohne thermische Grenzwerte zu verletzen.

Drittens wird im Zuge der Einführung von 3D-Speichern wie dem High-Bandwidth Memory (HBM) in Cluster-Mehrkernprozessoren eine weitere maschinell lernbasierte Technik vorgestellt, die auf konkurenzbewusste Migration abzielt, um die Gesamtleistung des Systems unter Berücksichtigung thermischer Grenzen von Prozessor und HBM zu maximieren. Die Technik verwaltet zur Laufzeit vier neuronale Netzwerkmodelle, die kontinuierlich die besten Migrationsoptionen zur Minimierung der Konkurrenz und Maximierung der Systemleistung bei Einhaltung thermischer Sicherheitsgrenzen ermitteln.

Abschließend wird zur Bewältigung der Komplexität der Cache-Konkurrenz in heterogenen Cluster-Mehrkernsystemen eine neuartige Methodik zur Modellierung der Energieeffizienz vorgestellt. Diese Methodik kombiniert strukturierte Datengenerierung mit LSTM- und Transformer-basierten Modellen zur

Vorhersage zukünftiger Systemzustände unter dynamischen und im Voraus unbekannten Laufzeitbedingungen. Die Umsetzung dieser Methodik wurde durch ein portables, quelloffenes Framework für das Ressourcenmanagement auf Systemebene auf realer Hardware ermöglicht, welches ebenfalls ein Beitrag dieser Forschung. Das Framework ermöglicht die experimentelle Validierung der vorgeschlagenen Methodik auf einem realen heterogenen Cluster-Mehrkernsystem und gewährleistet so deren Praxistauglichkeit.

Die Evaluation der vorgestellten Techniken auf Simulationsplattformen sowie realer Hardware zeigt deutliche Verbesserungen gegenüber dem Stand der Technik bei vernachlässigbarem Laufzeit-Overhead und belegt, dass maschinelles Lernen ein entscheidender Ansatz zur Bewältigung des Cache-Konkurrenzproblems in homogenen wie heterogenen Cluster-Mehrkern-prozessoren ist. Darüber hinaus zeigt sich, dass maschinelle Lernverfahren, wenn sie sorgfältig in das systemweite Ressourcenmanagement integriert werden, das Cache-Konkurrenzproblem erfolgreich adressieren und zu signifikanten Verbesserungen hinsichtlich Leistung, Temperatur und Energieeffizienz in modernen homogenen und heterogenen Mehrkernsystemen führen können.

## Research at CES

The Chair for Embedded Systems (CES) at the Karlsruhe Institute of Technology (KIT) conducts research at the forefront of embedded and resource-constrained computing. Its work spans a wide spectrum of topics including system-level optimization, thermal and power management, and machine learning for embedded platforms.

#### **Resource Management and Machine Learning**

Resource management plays a critical role in enhancing energy efficiency, thermal behavior, performance, and reliability of multicore systems [14]. CES has built a rich legacy in this area through a series of doctoral research efforts, each advancing the state of the art with increasing granularity and sophistication. This line of research was initiated by CES researchers who pioneered thermal management strategies that operated independently of application-specific behavior. Their work focused on eco-efficient learning techniques for system-level thermal control [15], a foundational contribution that demonstrated the benefits of machine learning for thermal regulation without detailed application characterization. Building upon this, the next generation of research introduced application-awareness into the resource management process. In particular, CES researchers' effort focused on thermal-aware resource management by incorporating application characteristics into the decision-making process, relying primarily on design-time profiling to build predictive models for runtime control [16, 17, 18, 19, 20]. More recently, the research at CES advanced the field by employing machine learning techniques for dynamic resource management. These contributions included sophisticated runtime mechanisms for thermal and performance optimization, notably with *smart* resource management [21, 8, 22]. However, these efforts did not explicitly address the growing problem of cache contention in clustered multicore architectures.

**Thesis Alignment** This dissertation extends CES's trajectory in resource management by addressing a previously underexplored yet critical challenge: **cache contention-aware system-level resource optimization**. This work focuses on clustered multi-core architectures, where dynamic contention for shared caches can significantly degrade system performance and energy efficiency. This dissertation introduces proactive resource management strategies driven by lightweight machine learning models that operate at runtime. These models predict system behavior under cache contention effects, which enable runtime management of workloads and contention scenarios.

#### **Cross-Layer Security**

Cross-layer security is also a key research area at CES, aimed at addressing vulnerabilities across the hardware-software stack. CES researchers develop techniques to protect embedded systems from threats ranging from physical tampering to sophisticated software-based attacks. This includes the use of lightweight cryptographic methods, countermeasures against side-channel attacks [23], attack-resilient hardware primitives, and real-time intrusion detection mechanisms [10]. By applying security measures [9] across abstraction layers, CES aims to significantly enhance the robustness and trustworthiness of embedded systems operating in adversarial environments.

#### Non-Volatile Memory (NVM)

CES also conducts extensive research on non-volatile memory (NVM) technologies, which offer persistent data storage without requiring power. This line of work explores high-density, low-latency, and durable NVM solutions [24] that are well-suited for emerging memory hierarchies. In particular, CES investigates how the varying retention characteristics of different NVM technologies can be exploited to accelerate machine learning workloads, optimize memory utilization, and improve overall system efficiency.

#### **Reconfigurable Systems**

In the area of reconfigurable computing, CES focuses on the development of adaptive, self-organizing architectures capable of dynamic resource allocation.

Leveraging hardware-software co-design, CES engineers systems that reconfigure in real time based on application demands [25]. This reconfigurability not only enables performance and energy efficiency improvements, but also enhances scalability and hardware longevity—particularly in domains such as approximate computing, where minor precision losses can be traded for substantial computational gains [26].

# **Contents**

| Ac  | know   | ledgements                                               | Ш    |

|-----|--------|----------------------------------------------------------|------|

| Lis | t of P | ublications                                              | v    |

| Ab  | stract | t                                                        | ix   |

| Zu  | samm   | nenfassung                                               | xiii |

| Re  | searc  | h at CES                                                 | cvii |

| Lis | t of F | igures                                                   | αν   |

| Lis | t of T | ables                                                    | xvii |

| 1.  | Intro  | oduction                                                 | 1    |

|     | 1.1.   | The Cache Contention Problem                             | 2    |

|     | 1.2.   | Motivational Examples                                    | 5    |

|     |        | 1.2.1. Application Mapping                               | 5    |

|     |        | 1.2.2. Application Migration                             | 7    |

|     | 1.3.   | Challenges of Cache Contention-Aware Resource Management | 9    |

|     | 1.4.   | Tackling Cache Contention                                | 15   |

|     | 1.5.   | Thesis Contributions                                     | 15   |

|     | 1.6.   | Dissertation Outline                                     | 17   |

| 2.  | The    | State of the Art                                         | 19   |

|     | 2.1.   | Cache Contention Background                              | 19   |

|     |        | 2.1.1. Mechanisms of Cache Contention                    | 20   |

|     |        | 2.1.2. Formulation of the Cache Contention Problem       | 20   |

|     | 2.2.   | Architecture-Level Cache Contention Mitigation           | 22   |

|     | 2.3.   | Pseudo Architecture-Level Cache Contention Mitigation    | 24   |

|     | 2.4.   | System-Level Cache Contention Mitigation                 | 25   |

| 3. | Syst                       |                                                                               | els and Experimental Framework                                                                                                                                                                  |

|----|----------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | 3.1.                       | Proces                                                                        | sor and Memory System Models                                                                                                                                                                    |

|    |                            | 3.1.1.                                                                        | Architectural Instances                                                                                                                                                                         |

|    | 3.2.                       | Simula                                                                        | ation Frameworks                                                                                                                                                                                |

|    |                            | 3.2.1.                                                                        | HotSniper                                                                                                                                                                                       |

|    |                            | 3.2.2.                                                                        | CoMeT                                                                                                                                                                                           |

|    | 3.3.                       | ARDiS                                                                         | S: Experimentation on Real Hardware                                                                                                                                                             |

|    |                            | 3.3.1.                                                                        | Motivation & Related Work                                                                                                                                                                       |

|    |                            | 3.3.2.                                                                        | Design Principles, Requirements and Challenges                                                                                                                                                  |

|    |                            | 3.3.3.                                                                        | The ARDiS Resource Management Framework                                                                                                                                                         |

| 4. | Macl                       |                                                                               | rning-Based Prediction of Cache Contention Impacts .                                                                                                                                            |

|    | 4.1.                       | Machi                                                                         | ne Learning Problem Formulation                                                                                                                                                                 |

|    |                            | 4.1.1.                                                                        | The Generalization Challenge                                                                                                                                                                    |

|    |                            | 4.1.2.                                                                        | Action-Induced and Natural State Transitions                                                                                                                                                    |

|    | 4.2.                       | Traini                                                                        | ng Data Generation Methodology                                                                                                                                                                  |

|    | 4.3.                       | Illustra                                                                      | ative Example                                                                                                                                                                                   |

| 5. | Ther                       | mal Opt                                                                       | imization using ML-Based Contention-Aware Task Map-                                                                                                                                             |

|    | ping                       | and DV                                                                        | FS                                                                                                                                                                                              |

|    | 5.1.                       | Challe                                                                        | nges and Novel Contributions                                                                                                                                                                    |

|    | 5.2.                       |                                                                               | m Formulation                                                                                                                                                                                   |

|    | 5.3.                       | Slowde                                                                        | own Prediction Model                                                                                                                                                                            |

|    |                            | 5.3.1.                                                                        | Training Data Generation                                                                                                                                                                        |

|    |                            | 5.3.2.                                                                        | Feature Selection and Model Architecture                                                                                                                                                        |

|    | 5.4.                       | Conte                                                                         | ntion-Aware Mapping                                                                                                                                                                             |

|    | 5.5.                       |                                                                               |                                                                                                                                                                                                 |

|    | 5.5.                       | Experi                                                                        |                                                                                                                                                                                                 |

|    | J.J.                       | Experi 5.5.1.                                                                 | mental Evaluation                                                                                                                                                                               |

|    | 5.5.                       |                                                                               | mental Evaluation                                                                                                                                                                               |

|    | J.J.                       | 5.5.1.                                                                        | mental Evaluation                                                                                                                                                                               |

|    | 5.6.                       | 5.5.1.<br>5.5.2.<br>5.5.3.                                                    | mental Evaluation                                                                                                                                                                               |

| 6. | 5.6.                       | 5.5.1.<br>5.5.2.<br>5.5.3.<br>Summ                                            | mental Evaluation  Comparison Technique  Experimental Results  Runtime Overhead                                                                                                                 |

| 6. | 5.6.<br>Perfe              | 5.5.1.<br>5.5.2.<br>5.5.3.<br>Summ                                            | mental Evaluation Comparison Technique Experimental Results Runtime Overhead ary  Coptimization using ML-Based Contention-Aware Task                                                            |

| 6. | 5.6.<br>Perfe              | 5.5.1.<br>5.5.2.<br>5.5.3.<br>Summormance<br>ation ar                         | mental Evaluation Comparison Technique Experimental Results Runtime Overhead ary  Comparison Technique  Experimental Results  Runtime Overhead  Comparison Using ML-Based Contention-Aware Task |

| 6. | 5.6. Perfo                 | 5.5.1.<br>5.5.2.<br>5.5.3.<br>Summormance<br>ation ar                         | mental Evaluation Comparison Technique Experimental Results Runtime Overhead ary  Coptimization using ML-Based Contention-Aware Task and DVFS  nges and Novel Contributions                     |

| 6. | 5.6.  Perfe Migr 6.1.      | 5.5.1.<br>5.5.2.<br>5.5.3.<br>Summ<br>ormance<br>ation ar<br>Challe<br>Proble | mental Evaluation Comparison Technique Experimental Results Runtime Overhead ary  Coptimization using ML-Based Contention-Aware Task and DVFS  nges and Novel Contributions                     |

| 6. | 5.6.  Perfe Migr 6.1. 6.2. | 5.5.1.<br>5.5.2.<br>5.5.3.<br>Summ<br>ormance<br>ation ar<br>Challe<br>Proble | mental Evaluation Comparison Technique Experimental Results Runtime Overhead ary  e Optimization using ML-Based Contention-Aware Task and DVFS nges and Novel Contributions m Formulation       |

|    | 6.4.         | Smart            | Cache Contention Mitigation                              | 85  |

|----|--------------|------------------|----------------------------------------------------------|-----|

|    |              | 6.4.1.           | ML-Based Application Migration                           | 86  |

|    |              | 6.4.2.           | Cluster-Level dynamic voltage and frequency scaling      |     |

|    |              |                  | (DVFS)                                                   | 89  |

|    | 6.5.         | Experi           | imental Evaluation                                       | 89  |

|    |              | 6.5.1.           | Comparison Technique                                     | 90  |

|    |              | 6.5.2.           | Experimental Results                                     | 90  |

|    |              | 6.5.3.           | Runtime Overhead                                         | 93  |

|    | 6.6.         | Summ             | ary                                                      | 94  |

| 7. | MI_E         | Racad C          | ontention-Aware Performance Optimization for Clus-       |     |

| 1. |              |                  | cores with HBM                                           | 95  |

|    | 7.1.         |                  | round                                                    | 95  |

|    | 7.1.         |                  | ational Example                                          | 97  |

|    | 7.2.         |                  | enges and Novel Contributions                            | 100 |

|    | 7.3.<br>7.4. |                  | em Formulation                                           | 100 |

|    | 7.4.<br>7.5. |                  | l network (NN)-Based Models                              | 102 |

|    | 7.5.         | 7.5.1.           | Performance and Memory Access Prediction                 | 103 |

|    |              | 7.5.1.<br>7.5.2. | Temperature Prediction for the Multicore and High-       | 103 |

|    |              | 7.5.2.           | Bandwidth Memory (HBM)                                   | 107 |

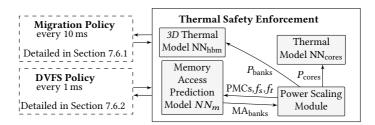

|    | 7.6.         | MI_R             | ased Resource Management for Clustered Multicores        | 107 |

|    | 7.0.         | with F           |                                                          | 110 |

|    |              | 7.6.1.           | ML-Based Application Migration                           | 111 |

|    |              | 7.6.2.           | Cluster-Level dynamic voltage and frequency scaling      | 111 |

|    |              | 7.0.2.           | (DVFS)                                                   | 113 |

|    | 7.7.         | Evneri           | imental Evaluation                                       | 113 |

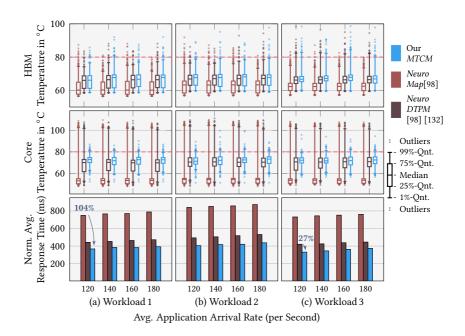

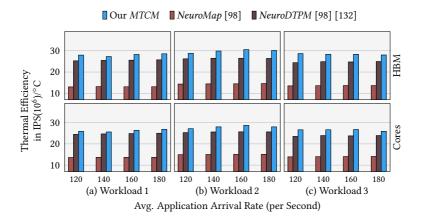

|    | 7.7.         | 7.7.1.           | Comparison Techniques                                    | 113 |

|    |              | 7.7.1.           | Evaluation Results                                       | 115 |

|    |              | 7.7.2.           | Generalization Analysis                                  | 118 |

|    |              | 7.7.4.           | Overhead Analysis                                        | 120 |

|    | 7.8.         |                  | ary                                                      | 121 |

|    |              |                  | ,                                                        |     |

| 8. | Ener         |                  | iency Forecasting for Clustered Heterogeneous Processors |     |

|    | 8.1.         |                  | ational Example                                          | 124 |

|    | 8.2.         |                  | enges and Novel Contributions                            | 126 |

|    | 8.3.         |                  | d Work                                                   | 127 |

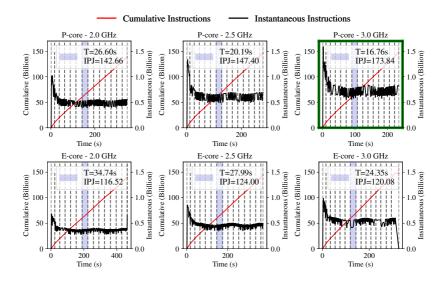

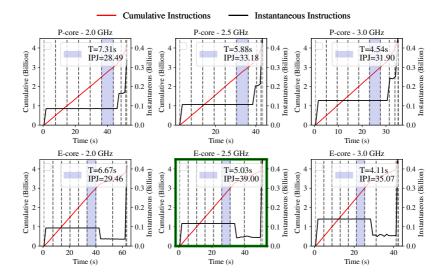

|    | 8.4.         | Analy            | zing Energy Efficiency Sensitivity to Heterogeneity      | 129 |

|    |              | 8.4.1.           | Volatility of Phase-Level Sensitivities                  | 129 |

|    |              | 8.4.2.           | Temporal Variability in Energy Efficiency                | 130 |

|     |         | 8.4.3.  | Intra-Cluster and Cross-Cluster Contention            | 132  |

|-----|---------|---------|-------------------------------------------------------|------|

|     | 8.5.    | Proble  | m Formulation                                         | 134  |

|     | 8.6.    | EffiCas | st: Novel Forecasting Methodology                     | 135  |

|     |         | 8.6.1.  | Training Data Generation                              | 135  |

|     |         | 8.6.2.  | Feature Selection and Engineering                     | 136  |

|     |         | 8.6.3.  | ML Models                                             | 138  |

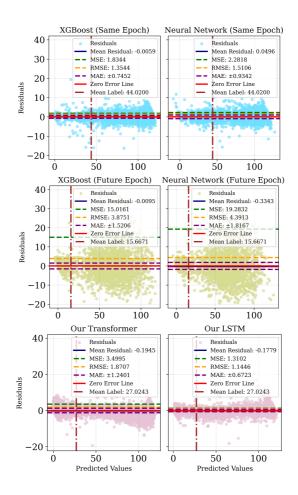

|     | 8.7.    | Experi  | mental Evaluation                                     | 139  |

|     |         | 8.7.1.  | Model Architectures                                   | 139  |

|     |         | 8.7.2.  | Model Performance Comparison                          | 140  |

|     |         | 8.7.3.  | Evaluation of Model Generalization                    | 143  |

|     |         | 8.7.4.  | Training and Inference Overhead                       | 143  |

|     | 8.8.    | Summa   | ary                                                   | 144  |

| 9.  | Conc    | lusion  |                                                       | 147  |

|     | 9.1.    | Conso   | lidated Contributions                                 | 147  |

|     | 9.2.    | Future  | Work                                                  | 148  |

|     | 9.3.    |         | g Takeaways                                           | 151  |

| Bib | oliogra | aphy .  |                                                       | 153  |

| A.  | Appe    | ndix: B | enchmark Suites                                       | 171  |

|     | A.1.    | PARSE   | C: The Princeton Application Repository for Shared-   |      |

|     |         |         | ry Computers                                          | 171  |

|     | A.2.    | SPLAS   | H-2: Stanford ParalleL Applications for SHared Memory | 7174 |

# **List of Figures**

| 1.1. | The AMD Zen 3 microarchitecture                                  | 1  |

|------|------------------------------------------------------------------|----|

| 1.2. | The Intel Alder Lake microarchitecture                           | 3  |

| 1.3. | Motivational example with application-to-cluster mapping         | 5  |

| 1.4. | Motivational example with task migration                         | 8  |

| 1.5. | Correlation between cache and DRAM accesses and slowdown .       | 10 |

| 3.1. | The 64-core homogeneous clustered processor, following the       |    |

|      | £ 3                                                              | 33 |

| 3.2. | The Samsung HBME2 [102] as the main memory of the simulated      |    |

|      | AMD Zen 3 homogeneous clustered processor                        | 34 |

| 3.3. | The 24-core Intel i9 12th Gen Alder Lake heterogeneous clustered |    |

|      | processor [29]                                                   | 35 |

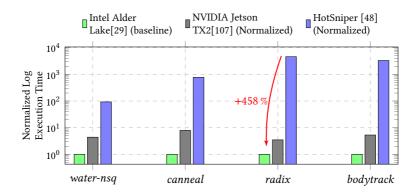

| 3.4. | The prohibitive execution times on the HotSniper simulator, com- |    |

|      | pared to real-hardware counterparts                              | 38 |

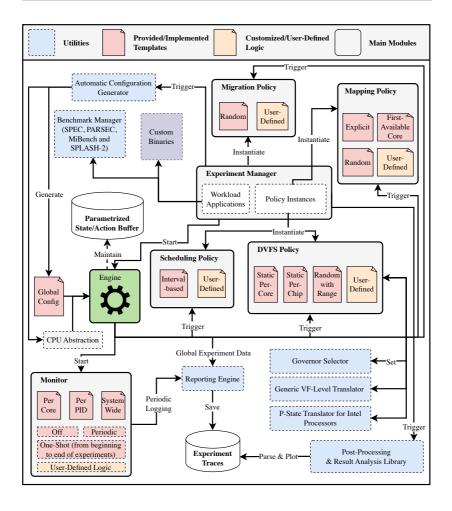

| 3.5. | High-level overview of ARDiS's architecture and modules          | 41 |

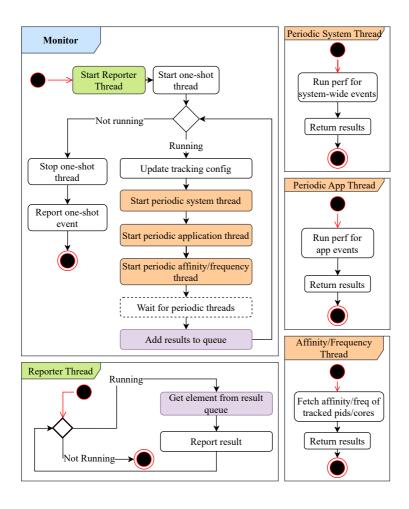

| 3.6. | ARDiS's multi-threaded monitoring system                         | 46 |

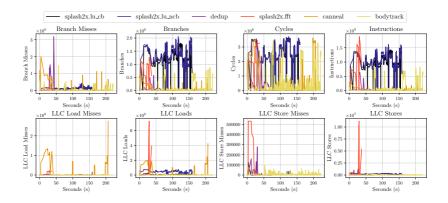

| 3.7. | A series of plots from ARDiS's result analysis library           | 47 |

| 3.8. | An example mapping plot generated by our ARDiS                   | 48 |

| 4.1. | 1 0 1                                                            | 58 |

| 4.2. |                                                                  | 59 |

| 4.3. | 8 1                                                              | 61 |

| 4.4. | Radix's slicing experiment                                       | 62 |

| 5.1. | U                                                                | 68 |

| 5.2. | 1 0                                                              | 73 |

| 5.3. |                                                                  | 75 |

| 5.4. |                                                                  | 76 |

| 5.5. |                                                                  | 76 |

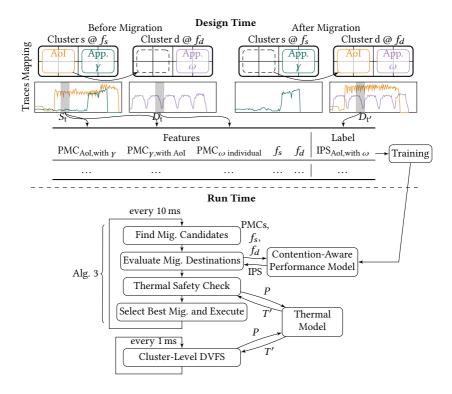

| 6.1. | SmartCM's flow at design and run times                           | 83 |

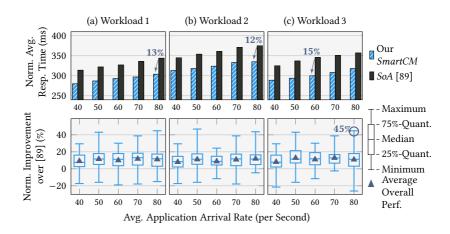

| 6.2. | Performance results of SmartCM                                    | 91  |  |  |  |  |

|------|-------------------------------------------------------------------|-----|--|--|--|--|

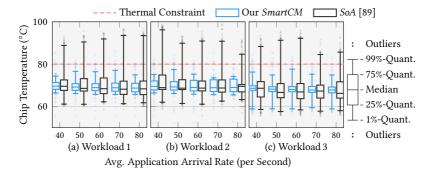

| 6.3. | Temperature results of SmartCM                                    | 92  |  |  |  |  |

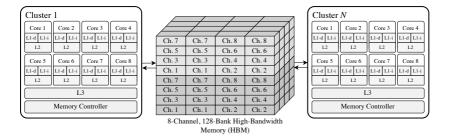

| 7.1. | Targeted multicore and HBM in MTCM                                | 96  |  |  |  |  |

| 7.2. | Motivational example with a 3D HBM                                | 98  |  |  |  |  |

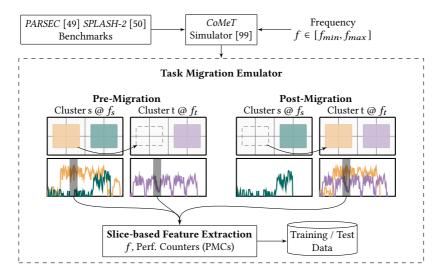

| 7.3. | Training data generation methodology of MTCM                      | 104 |  |  |  |  |

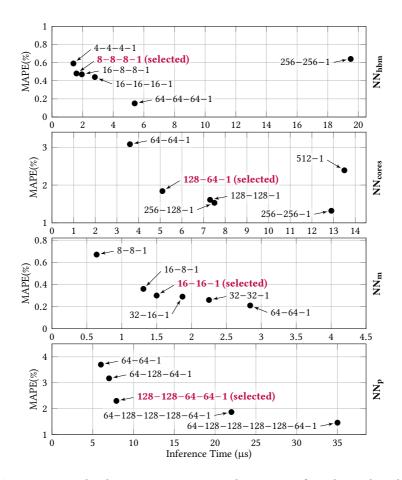

| 7.4. | 4. Neural architecture search for MTCM's neural networks          |     |  |  |  |  |

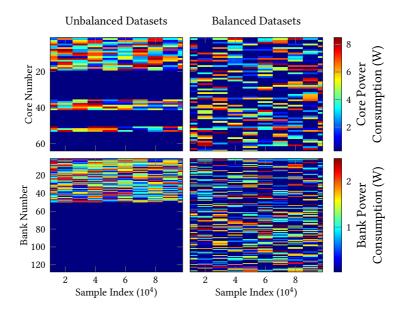

| 7.5. | The challenge of generating training data with balanced temper-   |     |  |  |  |  |

|      | ature distributions                                               | 108 |  |  |  |  |

| 7.6. | Thermal safety enforcement within MTCM's RM technique             | 111 |  |  |  |  |

| 7.7. | Performance and temperature results of MTCM                       | 117 |  |  |  |  |

| 7.8. | Thermal efficiency results of MTCM                                | 118 |  |  |  |  |

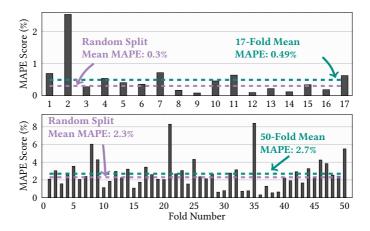

| 7.9. | Cross-validation of MTCM's neural networks                        | 119 |  |  |  |  |

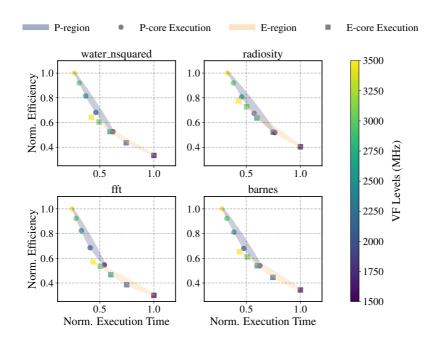

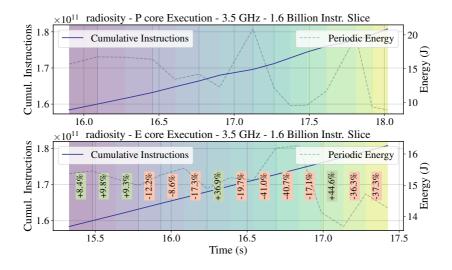

| 8.1. | Executing applications on a heterogeneous processor               | 124 |  |  |  |  |

| 8.2. | Phase-level comparison of radiosity's IPJ across core types       | 130 |  |  |  |  |

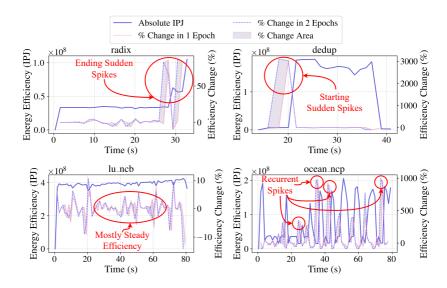

| 8.3. | Sudden variations in the observed IPJ throughout the execution    |     |  |  |  |  |

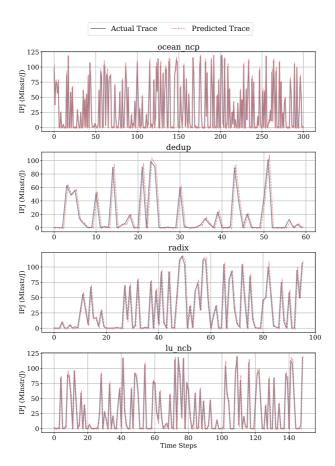

|      | of applications                                                   | 131 |  |  |  |  |

| 8.4. | Schematic of the Intel Alder Lake highlighting the possible cache |     |  |  |  |  |

|      | contention domains                                                | 132 |  |  |  |  |

| 8.5. | Intra- and cross-cluster cache contention on the real Intel Alder |     |  |  |  |  |

|      | Lake heterogeneous processor                                      | 133 |  |  |  |  |

| 8.6. | Overview of our EffiCast methodology                              | 136 |  |  |  |  |

| 8.7. | Transformer and LSTM residuals, compared to state-of-the-art      |     |  |  |  |  |

|      | NN and XGB models for the same task                               | 141 |  |  |  |  |

| 8.8. | Illustrative example of EffiCast's forecasting accuracy           | 142 |  |  |  |  |

|      |                                                                   |     |  |  |  |  |

# **List of Tables**

| 1.1.  | Observed slowdowns between application pairs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 9   |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.1.  | Summary of Mathematical Notations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 31  |

| 7.1.  | Accuracy, inference time and memory footprint of MTCM's neural networks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 110 |

| 7 2   | Overhead analysis of MTCM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

| , .u. | O verification and post of the contract of the | 120 |

## 1. Introduction

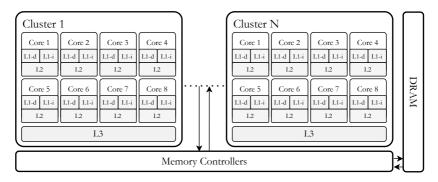

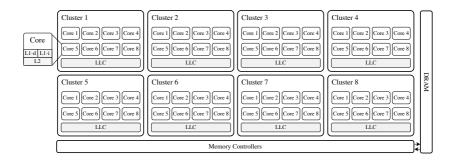

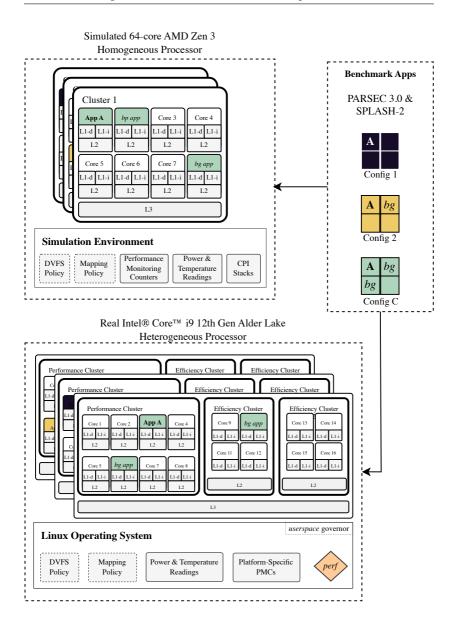

The design philosophy of multi-core processors has undergone a fundamental shift from monolithic, i.e., non-clustered designs to *clustered* architectures in the recent years, exemplified by many commercial implementations such as AMD's EPYC [27], ARM's big.LITTLE [28], Intel's Alder Lake [29], and Apple's M1 processor [30]. This evolution has been primarily driven by the stagnation of transistor scaling predicted by Moore's Law [31, 32], the cessation of Dennard scaling [33], and the escalating manufacturing and packaging challenges associated with large monolithic dies [34, 35]. The resulting architectural paradigm, known as *clustered multi-core architectures*, partitions processor cores into multiple physically or logically grouped clusters, each typically having localized caches, memory controllers, and interconnect fabrics [28, 27]. An example of such an architecture is illustrated in the AMD Zen 3 microarchitecture on Fig. 1.1.

**Figure 1.1.:** The AMD Zen 3 microarchitecture [36], as an example of homogeneous clustered multicores, where contention for the last-level cache occurs only between concurrently-running applications on the same cluster.

The adoption of clustered multi-core designs has grown significantly across various computing domains. In mobile computing, clustered multi-core processors, exemplified by ARM's big.LITTLE architecture introduced in 2011, achieved widespread adoption due to their ability to dynamically balance high performance and low energy consumption [28]. Today, virtually all flagship mobile devices employ some form of clustered architecture, reflecting universal adoption within the industry [37].

In the realm of data centers, clustered architectures have similarly become the standard. AMD's EPYC and Ryzen server CPUs [38], leveraging a chiplet-based clustered approach, have rapidly gained market share, rising from less than 5% in 2017 to approximately 28% by late 2023, and to a 33% by mid-2024, mainly due to significant improvements in scalability, yield, and power efficiency compared to traditional monolithic server processors [39, 40]. Concurrently, Intel has adopted similar clustered strategies in its most recent server processor lines, e.g., Alder Lake, Sapphire Rapids, etc. to achieve higher core counts and efficiency [41, 29].

#### 1.1. The Cache Contention Problem

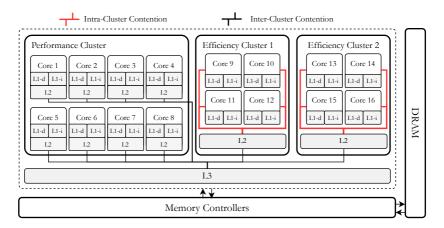

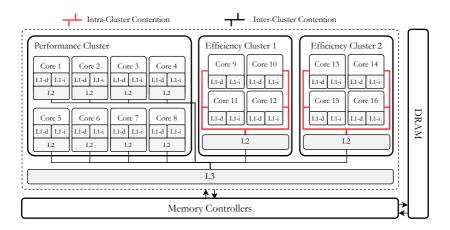

Despite the clear advantages of clustered multi-core architectures, e.g., improved scalability, enhanced power efficiency, and greater design flexibility, they introduce significant challenges in the management of shared resources, particularly the cache and memory subsystems. Cache contention, a wellknown problem in non-clustered designs, persists in these new clustered designs as well. Unlike monolithic processors, clustered architectures feature complex, hierarchical cache structures. They typically implement hierarchical cache subsystems that comprise multiple cache levels, structured in private caches, e.g., L1, L2, and shared caches, e.g., L3 or last-level cache (LLC), shared between the cores within a cluster or across clusters, as shown in Fig. 1.2. Consequently, applications running in parallel on the system compete for the limited available cache space. This competition results in cache contention, where concurrently-executing applications adversely slow down each other's execution, by evicting useful cache lines or saturating shared memory channels [42, 43]. While only chip-wide cache contention is observed on monolithic dies, i.e., all cores on the chip share the same LLC, the new memory hierarchies in modern clustered multicores introduced new forms of contention within clusters (Fig. 1.1) and across clusters (Fig. 1.2).

**Figure 1.2.:** The Intel Alder Lake microarchitecture [29], as an example of clustered heterogeneous multicores where both inter-cluster and intra-cluster contention can occur between concurrently-running applications.

Cache contention is a performance-degrading phenomenon that occurs when multiple concurrently-running applications or processes compete for limited cache resources within a processor [43]. It is primarily caused by two factors: limited cache capacity and conflicting access patterns among applications. In clustered architectures, the LLC remains insufficient relative to the aggregate working set sizes of co-running applications. When applications exhibit substantial spatial or temporal locality—that is, when they frequently access memory addresses that are either close to each other (spatial locality) or reused within short time intervals (temporal locality)— and share a cache level, they tend to compete aggressively for the same cache sets, thereby evicting each other's useful data. Such frequent evictions force the system to access main memory more often, resulting in significantly higher latency and reduced bandwidth [43].

#### **Addressing the Cache Contention Problem**

Addressing cache contention involves strategies that span both hardware and software domains. From a hardware perspective, designers employ several strategies to mitigate contention. These include increasing cache associativity, implementing advanced cache partitioning and isolation techniques, e.g., Cache Allocation Technology (CAT) by Intel [44] and developing adaptive cache replacement policies [45]. Such methods aim to manage cache utilization proactively, allocating cache partitions more efficiently or dynamically adapting policies to workload characteristics to minimize harmful interference. While these hardware-centric approaches offer viable methods for contention mitigation, they typically require significant hardware modifications and additional complexity, while being constrained by their inherent cost, limited flexibility, and relatively longer development cycles [46, 47].

In contrast, *system-level resource management (RM)* strategies provide a more flexible, readily-deployable, and cost-effective means to mitigate cache contention [47]. From a software perspective, system-level RM techniques mainly rely on cache-aware application placement, both statically and dynamically. RM techniques can identify applications with conflicting cache behaviors and strategically separate them across clusters, thus minimizing contention. These strategies can incorporate profiling tools to classify workloads based on cache sensitivity, enabling the system to balance cache demands by co-mapping complementary workloads.

Cache contention remains an open critical performance bottleneck in clustered multi-core architectures, necessitating ongoing innovations in both hardware mechanisms and software management techniques to optimize resource utilization and achieve maximal performance efficiency. Moreover, cache contention is not an isolated phenomenon; it also has significant implications for power consumption, temperature management, and overall energy efficiency, creating *complex* tradeoffs between different optimization objectives at runtime, which have not been observed nor tackled by the state of the art.

### 1.2. Motivational Examples

To illustrate the complexity of the cache contention problem, the following subsections present two motivational examples that highlight the tradeoff between cache contention and system temperature, as exposed by application-to-cluster mapping and migration.

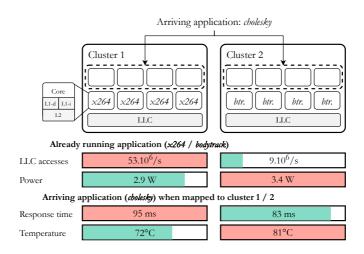

#### 1.2.1. Application Mapping

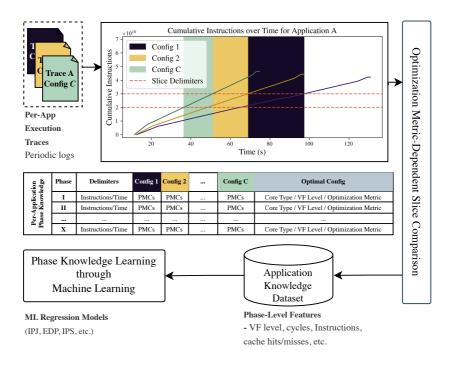

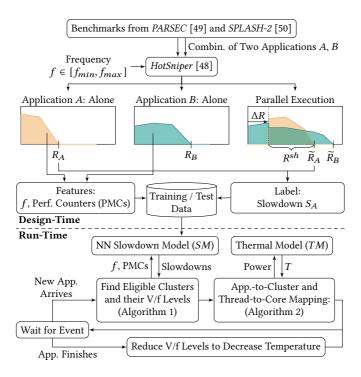

An experiment is conducted on the HotSniper [48] simulator, where two applications from the *PARSEC* [49] and *SPLASH-2* [50] benchmark suites, *x264* and *bodytrack*, are executed on two individual clusters on a simulated clustered homogeneous processor, similar to the AMD Zen 3 microarchitecture (detailed in Section 3.1.1), as shown in Fig. 1.3. Both applications are multi-threaded, running 4 threads in parallel each, and occupying 4 cores on their corresponding cluster, following the one-thread-per-core model [51].

**Figure 1.3.:** Application-to-cluster mapping introduces a trade-off between mitigating cache contention and managing temperature, which has not been observed in the literature.

The *x264* application is memory-intensive, which is reflected in its high number of LLC accesses per second, compared to *bodytrack*, which is compute-

intensive. The average power consumption of bodytrack is higher than the one of x264.

A new application, *cholesky*, arrives to the system, and needs to be mapped to one of the two clusters. *Cholesky* also requires 4 cores, as it has 4 threads. Once scheduled, a system-level RM technique shall decide to which cluster and cores to map the threads of the arriving application. As both clusters have 4 available/free cores each, we analyze the implications of the two possible mappings, in terms of performance and system temperature.

When co-mapped with x264 on Cluster 1, the execution time of *cholesky* is 95 ms. That is 14% slower than its response time when co-mapped with *bodytrack* on Cluster 2, due to the slowdown induced by LLC contention on Cluster 1. From a performance perspective, mapping *cholesky* to Cluster 2 is the better option. However, considering the impact of these mappings on the temperature of the chip suggests otherwise. Co-mapping *cholesky* with *bodytrack* on Cluster 2 leads to an average cluster temperature of 81 °C, due to the high power consumption of *bodytrack*. On the other hand, co-mapping *cholesky* with x264 on Cluster 1, leads to a 9 °C decrease in the average cluster temperature.

This example highlights that application-to-cluster mapping exposes a trade-off between cache contention and temperature. As will be discussed in Chapter 5, this trade-off has not been observed in the literature. Particularly, co-mapping an application with a memory-intensive application increases cache contention and results in an execution slowdown, but might decrease temperature due to the decreased computation on CPU cores. On the other hand, co-mapping with a compute-intensive application decreases cache contention but might increase temperature, as intensive computation typically results in higher power consumption. Depending on the optimization goal at runtime, these observations highlight two possible resource management directions.

**Thermally-Constrained Optimization** If the chip is thermally constrained to 80 °C, mapping to Cluster 2 leads to a runtime violation of the temperature constraint. Such a violation would trigger the Dynamic Thermal Management (DTM) on the chip to throttle down the cores to the minimum voltage/frequency (V/f) level, until the temperature of the chip is reduced below 80 °C. This would also nullify the intended performance gains from avoiding

to map *cholesky* to Cluster 1, where the observed contention-induced slowdown was high. Obviously, if the goal is is to maximize system performance, and temperature is *not constrained* to 80  $^{\circ}$ C, mapping to Cluster 2 remains the best option.

**Performance-Constrained Optimization** If the goal is to minimize temperature, mapping *cholesky* to Cluster 1 is clearly the best option. However, if *cholesky* has a defined execution deadline of 90 ms, the achieved 95 ms execution time is a performance violation, making the mapping to Cluster 2 the only option. Obviously, canceling either constraint would result in different options.

Importantly, the analysis in this motivational example *requires* that the cache contention-induced slowdown between the concurrently-running applications on the cluster *and* the impacts on performance and temperature are *known*, based on which the RM can evaluate the implications of the different mapping options. However, at runtime, as applications arrive to the system, this information is *not available*.

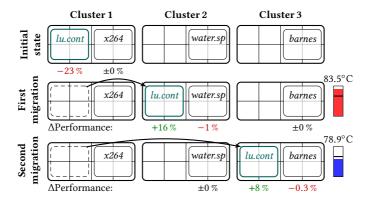

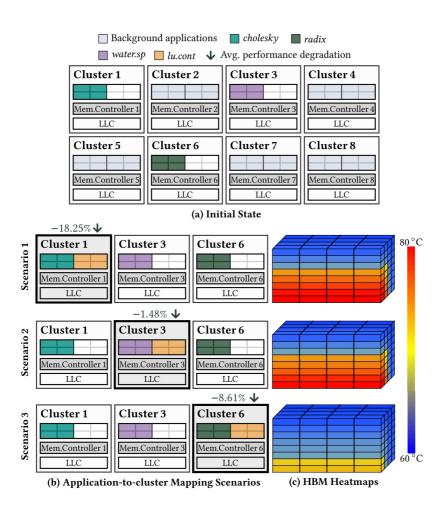

### 1.2.2. Application Migration

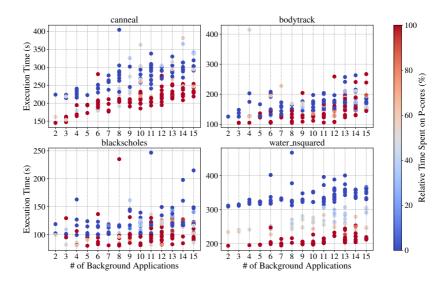

In this second motivational example, we conduct experiments on the same HotSniper [48] simulator, simulating three clusters of the same clustered homogeneous processor in the previous example (detailed in Section 3.1.1). This platform operates under a critical temperature threshold of  $T_{crit} = 80^{\circ}\text{C}$ . The example, illustrated in Fig. 1.4, highlights the consequences of application migration on system performance and thermal behavior, without the interference of emergency thermal management mechanisms such as the Thermal Control Circuitry (TCC) [52].

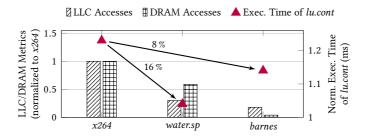

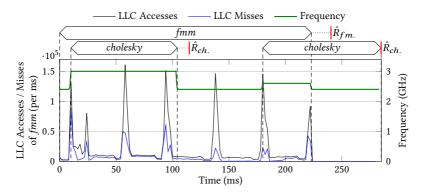

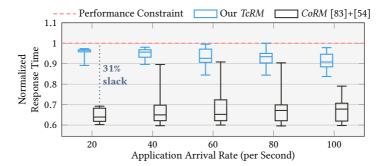

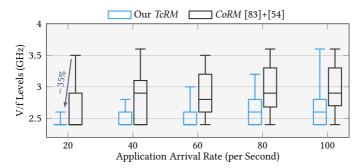

Initially, all three clusters operate uniformly at a V/f level of 2.6 GHz. Two applications from the PARSEC [49] and SPLASH-2 [50] benchmark suites—*lu.cont* and *x264*—are executed concurrently on cluster 1. Meanwhile, clusters 2 and 3 each host a single application: *water.sp* and *barnes*, respectively. Application performance is measured by execution time.

Our application of interest, *lu.cont*, experiences a performance degradation of 23% when co-executed with *x264* on cluster 1, relative to its standalone execution. This significant slowdown is indicative of severe cache contention

**Figure 1.4.:** The initial configuration reveals significant cache contention on cluster 1, evidenced by a 23% performance degradation in *lu.cont*'s execution relative to its standalone execution on a single cluster. Two migration strategies are applied to alleviate the contention and are evaluated against the initial setup. The results demonstrate that application migration introduces a trade-off between mitigating cache contention and managing temperature.

between the two applications. To mitigate this, we explore the potential benefits and trade-offs of migrating *lu.cont* to an alternative cluster.

Migrating lu.cont to cluster 2 yields a 16% performance improvement for the application, with only a minimal 1% performance impact on water.sp. However, this migration elevates the system's peak temperature to 83.5°C, surpassing  $T_{crit}$ . Such a violation would activate the TCC, triggering a system-wide downscaling of all core V/f levels to the minimum, which could negate or even reverse the performance gains achieved by mitigating cache contention. In contrast, migrating lu.cont to cluster 3 leads to a more moderate performance improvement of 8%, without any performance degradation to barnes, and crucially, without breaching the thermal constraint. This outcome preserves the migration-induced performance gains.

This example clearly highlights the necessity of jointly considering cache contention and thermal constraints when performing application migrations to optimize performance under thermal safety requirements.

## 1.3. Challenges of Cache Contention-Aware Resource Management

Building system-level resource management techniques that consider the cache contention problem *and* its implications faces several challenges.

### 1.3.1. Challenge 1: Complexity of Contention-Induced Slowdown Behavior

Cache contention-induced slowdown depends on the memory access characteristics, cache sensitivity, and execution behavior of concurrently-running applications. These interactions are highly non linear, asymmetric, application specific and time varying, making the modeling of slowdown effects challenging.

| App B       | streamclus. | <i>lu.cont</i><br>multaneous Start | cholesky<br>  Shifted Start (40 | lu.ncont      |

|-------------|-------------|------------------------------------|---------------------------------|---------------|

| streamclus. | 0.0%   0.0% | 20.8%   19.4%                      | 3.6%   4.2%                     | 22.0%   26.5% |

| lu.cont     | 0.0%   0.0% | 28.9%   0.7%                       | 12.5%   13.0%                   | 20.8%   17.7% |

| cholesky    | 0.0%   0.0% | 27.2%   0.0%                       | 8.3%   10.1%                    | 17.4%   13.8% |

| lu.ncont    | 0.0%   0.0% | 26.7%   0.0%                       | 18.8%   2.2%                    | 18.8%   8.9%  |

**Table 1.1.:** Comparison of application slowdowns when scheduled simultaneously and with a 40 ms shift in arrival time. Each cell reports the suffered slowdowns suffered by App A when co-mapped with App B, which highlights the asymmetry in the slowdown behavior. Shifting the arrival times of applications by only 40 ms leads to different execution slowdowns.

A concrete illustration is shown in Table 1.1, when representative benchmark applications *streamcluster*, *lu.cont*, *cholesky* and *lu.ncont* are executed in different pair combinations on a cluster, on a simulated homogeneous clustered processor, similar to the AMD Zen 3 microarchitecture. The table highlights multiple observations. First, *streamcluster*, while minimally affected by contention, significantly slows down its co-running applications. Second, *lu.cont* suffers notable performance degradation of 20.8% and 27.2% when co-executed with *streamcluster* and *cholesky*, respectively. Yet, *lu.ncont* exhibits the opposite sensitivity pattern, suffering greater degradation from *streamcluster* (22.0%) compared to *cholesky* (17.4%). Such scenarios illustrate

**Figure 1.5.:** The execution time of *lu.cont* is impacted differently when co-executed with different applications: *x264*, *water.sp* or *barnes* on one cluster. Depending only on DRAM or LLC accesses is not sufficient to estimate cache contention.

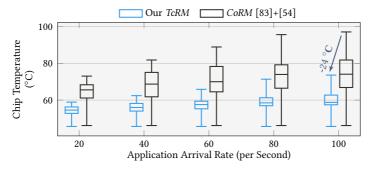

the highly asymmetric and application-specific nature of cache contention interactions, making them difficult to capture or generalize through simple heuristic or analytical models.