#### **OPEN ACCESS**

# Development of in-house plating and hybridisation technologies for hybrid pixel detectors

To cite this article: Haripriya Bangaru et al 2025 JINST 20 C07052

View the article online for updates and enhancements.

# You may also like

- A review of advances in pixel detectors for experiments with high rate and radiation Maurice Garcia-Sciveres and Norbert Wermes

- <u>Study on interfacial morphologies of AA1060 and SS321 magnetic pulse welded joints</u>

Shan Su, Yiming Wang, Yuanyuan Wu et

- <u>Multimillijoule terahertz radiation from laser interactions with microplasma waveguides</u>

Ke Hu, Longqing Yi and Tünde Fülöp

RECEIVED: *May 14*, 2025 ACCEPTED: *May 31*, 2025 PUBLISHED: *July 17*, 2025

20<sup>th</sup> Anniversary Trento Workshop on Advanced Silicon Radiation Detectors Trento, Italy 4–6 February 2025

# Development of in-house plating and hybridisation technologies for hybrid pixel detectors

Haripriya Bangaru, $^{a,*}$  Giovanni Calderini, $^b$  Dominik Dannheim, $^a$  Yahya Khwaira, $^b$  Helge Kristiansen, $^c$  Ahmet Lale, $^a$  Rui De Oliveira, $^a$  Mateus Vicente Barreto Pinto, $^d$  Petra Riedler, $^a$  Janis Viktor Schmidt, $^e$  Peter Svihra, $^{a,1}$  Matteo Centis Vignali, $^f$  Alexander Volker $^e$  and Xiao Yang $^a$

a CERN.

Geneva, Switzerland

<sup>b</sup>LPNHE-Paris, Centre National de la Recherche Scientifique,

Paris, France

<sup>c</sup> Conpart AS,

Skjetten, Norway

<sup>d</sup>Université de Genève,

Geneva, Switzerland

<sup>e</sup>KIT — Karlsruhe Institute of Technology,

Karlsruhe, Germany

$^{f}FBK$ ,

Trento, Italy

E-mail: haripriya.bangaru@cern.ch

ABSTRACT: Future collider experiments place demands on hybrid pixel detectors, particularly in terms of interconnect reliability across a range of die sizes and fine-pitch geometries. In development workflows based on Multi-Project Wafer (MPW) submissions, support for single-die assembly is crucial. To address these challenges, new hybridization methods have been introduced through collaborative efforts at CERN and within the AIDAinnova framework. One such approach utilizes Anisotropic Conductive Film (ACF) combined with Electroless Nickel Immersion Gold (ENIG) surface treatment to form interconnections without conventional solder bumps. Instead, conductive microparticles embedded in an adhesive layer are compressed under heat and pressure to establish electrical contact. This technique has demonstrated excellent yield and mechanical stability, especially for pitches below 100 μm, making it a strong candidate for advanced detector integration in high-energy physics applications.

KEYWORDS: Hybrid detectors; Solid state detectors

<sup>\*</sup>Corresponding author.

<sup>&</sup>lt;sup>1</sup>Now at Faculty of Nuclear Sciences and Physical Engineering, Czech Technical University.

| C | ontents                                               |   |

|---|-------------------------------------------------------|---|

| 1 | Introduction                                          | 1 |

| 2 | Electroless Nickel Immersion Gold (ENIG)              | 1 |

| 3 | Hybridization using Anisotropic Conductive Film (ACF) | 3 |

| 4 | Conclusion                                            | 5 |

|   |                                                       |   |

#### 1 Introduction

In efforts led by the CERN EP R&D program on next-generation experimental technologies [1], and through collaboration with the AIDAinnova consortium [2], innovative fine-pitch interconnection methods specifically suited for bonding individual dies are being developed. Traditional methods for forming fine-pitch interconnections between ASICs and sensors often involve sophisticated, wafer-scale commercial bump-bonding techniques. Although these processes are well-established and deliver high reliability, their complexity and cost make them unsuitable for single-die applications. This limitation is especially relevant in research and development environments or small-scale production, where chips are frequently fabricated using Multi-Project Wafers (MPWs). To address the limitations of conventional fine-pitch interconnection methods for single-die applications, a promising alternative based on Anisotropic Conductive Adhesives (ACA) is currently under investigation. This approach replaces standard solder-bump bonding with thermo-compression of conductive microparticles (CPs) [3–5] embedded in a thin adhesive film, enabling electrical contact without the need for wafer-level processing. A key requirement of this technique is the use of elevated pad topographies to facilitate effective particle compression during bonding. To meet this need, a mask-less Electroless Nickel Immersion Gold (ENIG) plating process has been developed to create the necessary topography. Ongoing work at CERN, in collaboration with the University of Geneva, is focused on establishing a robust in-house ACA bonding process suitable for research and prototyping contexts.

#### 2 Electroless Nickel Immersion Gold (ENIG)

Electroless Nickel Immersion Gold (ENIG) is a chemically driven, autocatalytic plating method that deposits metallic layers without the need for electroplating infrastructure. The process can be carried out using standard laboratory equipment, making it accessible for small-scale or research-oriented environments. Despite its low setup complexity, achieving consistent and uniform metal deposition requires careful control over chemical composition, temperature, and agitation conditions. A significant advantage of ENIG is its compatibility with maskless, single-die processing, which eliminates the need for lithographic steps. This feature, combined with its adaptability for in-house use, enables rapid prototyping and cost-effective customization for diverse application requirements.

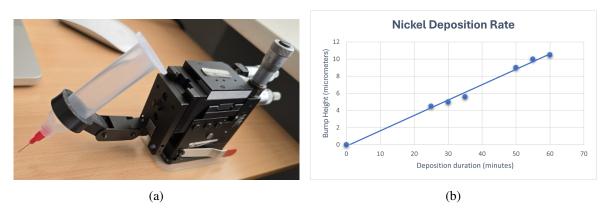

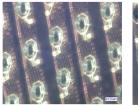

The ENIG process begins with zincation of the contact pads, followed by nickel bump formation and then deposition of a thin gold layer. Chips are first mounted on FR-4 or 3D-printed polypropylene holders, with wire bonding pads masked to prevent undesired metallization. A custom-built microdispenser — adapted from a probe station micro-positioner using a 3D-printed adapter was used to precisely apply the protective coating to peripheral metal regions (figure 1a). Zincation is performed by sequential immersion in four Atotech Xenolyte® solutions, assisted by ultrasonic agitation and gentle chip motion to ensure uniform treatment. Nickel bumps are subsequently formed by immersing the chips in a heated (86 °C) and magnetically stirred plating bath at 50 rpm. Ongoing studies are also investigating no stirring during the Nickel bath step to achieve the required bump height faster while removing the complexities of fluid movement in the bath. Bump height increases approximately linearly with plating time, reaching 10 µm after one hour (figure 1b), with minor variation between chips due to differences in pad metallization. In the final step, a cyanide-based gold bath is used to deposit a thin gold layer, enhancing electrical contact quality and protecting the nickel from corrosion. The initial validation of the ENIG process was performed on FBK-fabricated quartz daisy chain

**Figure 1.** (a) Custom-made micro-dispenser for precise application of protective coating, using a 3D printed adapter attached to a micro-manipulator. (b) Observed height of bumps versus nickel-deposition time.

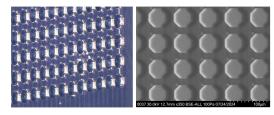

test chips [6]. These daisy-chain test chips were realized in 650 µm thick 6 inch quartz wafers of varying bonding area, pad size and pitch to match different target applications. They were designed to validate interconnect yield, electrical resistance and thermo-mechanical stress. High plating yields exceeding 99% were achieved on large-area chips (~2 cm²) with 55 µm pitch and 22×22 µm² pads, such as Timepix3-type daisy-chain devices. Comparable performance was also observed on dense test structures (~6 mm²) featuring 20 µm pitch and pads as small as 10×8 µm². The ENIG technique was later extended to a diverse set of functional chips varying in both pitch and dimensions. Across all tested devices, the process demonstrated consistent success, achieving complete pad coverage with ongoing characterization tests to confirm the minimal bump height variations. The range of plated components encompassed LGAD detectors developed for the ATLAS HGTD upgrade [7], Timespot ASICs [8] (figure 2a), SiGe ASICs and the KEK AC-LGAD sensors [9], ColorPix2 ASICs [10] (figure 2b), as well as SPHIRD silicon sensors [11]. A detailed overview of the plating outcomes can be found in table 1.

(b) Optical microscope and SEM images of ASICs for the KEK AC-LGAD project.

Figure 2. Examples of results of ENIG-plated functional chips.

**Table 1.** ENIG plating parameters and results.

| Sample                                    | Chip size                                                    | Pad size                    | Pitch  | ENIG height                               |

|-------------------------------------------|--------------------------------------------------------------|-----------------------------|--------|-------------------------------------------|

| "Small-pitch" daisy chain test structures | $3.2 \times 3.2 \mathrm{mm}^2$                               | $10 \times 8 \mu\text{m}^2$ | 20 μm  | $4.5$ μm $\pm 0.2$ μm                     |

| SPHIRD silicon sensor                     | $1.6 \times 3.2  \text{mm}^2$                                | 19 µm                       | 50 mm  | 5–6 µm                                    |

| "Timepix3" test structures                | $14 \times 14 \mathrm{mm}^2$                                 | 12–22 µm                    | 55 µm  | 10 μm ± 0.5 μm                            |

| Timespot1 ASIC                            | $2.4 \times 2.7  \text{mm}^2$                                | 19 µm                       | 55 µm  | 10 μm ± 0.5 μm                            |

| ColorPix2                                 | $3 \times 4.9 \mathrm{mm}^2$                                 | 40 μm                       | 70 µm  | $11  \mu \text{m} \pm 0.5  \mu \text{m}$  |

| SiGE ASICs and KEK<br>AC-LGAD sensors     | A: 1.3 × 2.9 mm <sup>2</sup><br>S: 1.9 × 1.9 mm <sup>2</sup> | 40 μm                       | 100 μm | $8.5  \mu \text{m} \pm 0.6  \mu \text{m}$ |

| ATLAS HGTD LGAD sensors                   | $20 \times 22 \mathrm{mm}^2$                                 | 90 μm                       | 1.3 mm | $8.5  \mu \text{m} \pm 0.7  \mu \text{m}$ |

## 3 Hybridization using Anisotropic Conductive Film (ACF)

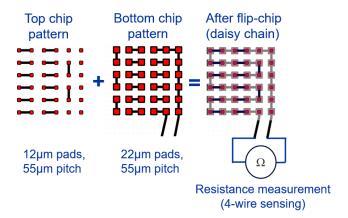

To assess the yield and reliability of the ACF hybridization method, dedicated daisy-chain test devices on quartz substrates, fabricated by FBK were employed. A Timepix3 inspired daisy-chain structure was assembled and tested electrically. The structure mirrors the design of a Timepix3 hybrid detector, with a  $256 \times 256$  matrix of pads placed at a  $55 \, \mu m$  pitch. One die featured  $22 \, \mu m$  square pads, while the other used  $12 \, \mu m$  square pads. A total of 72 chain structures were included, each consisting of 28 interconnects in series, as shown in figure 3.

ENIG bumps were formed on both chips using an earlier version of the in-house ENIG process. One chip exhibited well-formed bumps ( $10 \, \mu m$ ), while the other showed reduced bump sizes near the edges ( $9 \, \mu m$ ). The ACF used was  $18 \, \mu m$  thick and contained  $3 \, \mu m$  gold-coated CPs with a density of  $71,000 \, \text{CP/mm}^2$ . For bonding, the ACF film was laminated at  $90^{\circ}\text{C}$  with a force of  $20 \, \text{kgf}$  for  $5 \, \text{seconds}$ , followed by a cooling period of  $4–5 \, \text{minutes}$ . The final bonding was done with  $100 \, \text{kgf}$  at  $160^{\circ}\text{C}$  for  $5 \, \text{seconds}$ , followed by a  $5–10 \, \text{minute}$  cool-down.

The electrical performance of the 72 chains was evaluated with a probe station, employing the four-wire resistance method. For chains with complete connections, resistance values were mainly determined by the connection lines to the chip edges. However, any disconnected pads resulted in

**Figure 3.** Schematic of one chain sturcture of 28 interconnects of "Timepix3" daisy-chain test structure assembly after hybridization.

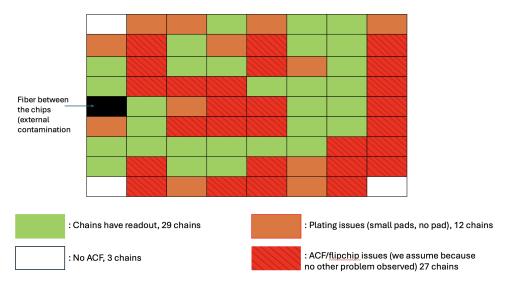

an open circuit for the entire chain. Of the 72 chains tested, 29 were fully connected, yielding a connection probability per pad of 96.8%, derived from the ratio  $p^{28} = 29/72$  (figure 4).

The distribution of functional and non-functional chains is illustrated in (figure 4). Among the 43 non-functional chains, 16 failures were linked to pre-bonding issues such as poor plating, incomplete ACF coverage, or contamination. The remaining 27 failures were likely caused by bonding issues, such as missing CPs between specific bumps.

**Figure 4.** Schematic illustrating the connection chains in a Timepix3 like daisy-chain test hybrid after electrical characterization post-flip-chip bonding, with connectivity status annotated to indicate various issues associated with observed disconnections.

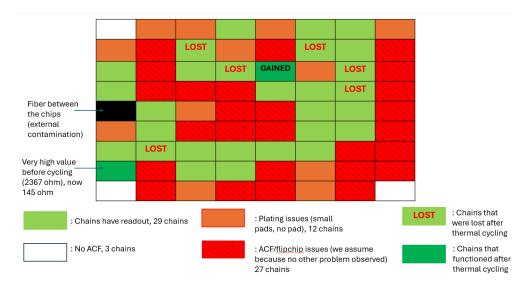

The reliability of the interconnections was further assessed by subjecting the daisy-chain assembly to thermal cycling in a climate chamber. The test involved 25 cycles, with temperatures fluctuating between -55°C and 60°C, at a rate of 10°C per minute. After completing the thermal cycles, 6 chains were found to have lost connectivity as observed in the schematic figure 5, while 1 chain successfully reconnected, resulting in 96.2% of pads still connected. Further analysis is needed

to explore whether mechanical stress — potentially due to the differing thermal expansion rates of materials such as the glass substrate, aluminum pads, epoxy adhesive, and gold-coated polymer CPs — contributed to the failures.

**Figure 5.** Schematic illustrating the connection chains in a Timepix3-type daisy-chain test hybrid after electrical characterization post-thermal cycling, with connectivity status annotated to indicate various issues associated with observed disconnections.

#### 4 Conclusion

Electroless Nickel Immersion Gold (ENIG)—Anisotropic Conductive Film (ACF) hybridization was investigated as a bonding solution for fine-pitch sensor—ASIC assemblies. The ENIG process showed consistent and uniform metal deposition across varying sample geometries, supporting its applicability for single-die processing. Combined with ACF, interconnection yields of approximately 97% were achieved, with initial thermal cycling indicating promising robustness. These results demonstrate the feasibility of ENIG—ACF for reliable and cost-effective interconnects. Future work will aim to optimize the process parameters and assess long-term performance under thermal stress, with a view towards integration in particle physics detector systems.

## Acknowledgments

This project has received funding from the European Union's Horizon 2020 Research and Innovation programme under GA no. 101004761.

#### References

- [1] G. Aglieri Rinella et al., *Strategic R&D Programme on Technologies for Future Experiments Annual Report 2024*, CERN-EP-RDET-2025-004 (2025).

- [2] Consortium for Advancement and Innovation for Detectors at Accelerators (AIDAinnova), https://aidainnova.web.cern.ch/.

- [3] P. Svihra et al., *Development of novel single-die hybridisation processes for small-pitch pixel detectors*, 2023 *JINST* **18** C03008 [arXiv:2210.02132].

- [4] J.V. Schmidt et al., *Pixel detector hybridisation with Anisotropic Conductive Films*, 2023 *JINST* **18** C01040 [arXiv:2210.13046].

- [5] A. Volker et al., *Pixel detector hybridisation and integration with anisotropic conductive adhesives*, 2024 *JINST* **19** C05024 [arXiv:2312.09883].

- [6] G. Calderini et al., Completion of planar sensor production for ACF, DOI: 10.5281/zenodo.7310324 (2022).

- [7] ATLAS collaboration, *Technical Design Report: A High-Granularity Timing Detector for the ATLAS Phase-II Upgrade*, CERN-LHCC-2020-007, CERN, Geneva (2020).

- [8] S. Cadeddu et al., Timespot1: a 28 nm CMOS Pixel Read-Out ASIC for 4D Tracking at High Rates, 2023 JINST 18 P03034 [arXiv:2209.13242].

- [9] T. Imamura, S. Kita, K. Nakamura and K. Hara, *Development of HPK Capacitive Coupled LGAD* (AC-LGAD) detectors, PoS VERTEX2023 (2024) 032 [arXiv:2401.08108].

- [10] J. Jirsa, M. Marcisovsky, Z. Janoska and J. Jakovenko, Winner-Leader-Follower a Novel Hit Allocation Algorithm for Pixel Detectors, IEEE Trans. Nucl. Sci. 71 (2024) 1250.

- [11] D. Magalhaes et al., Characterization results of the first small pixel high rate (SPHIRD) pixel detector prototypes, 2023 JINST 18 C12013.