# Modified Boost Converter Topology for Enhanced Converter-Based DC Protection

Moein Ghadrdan

institute for technical physics

karlsruhe institute of technology

Karlsruhe, Germany

moein.ghadrdan@kit.edu

Giovanni De Carne

institute for technical physics

karlsruhe institute of technology

Karlsruhe, Germany

giovanni.carne@kit.edu

Honeymol Mathew institute for technical physics karlsruhe institute of technology Karlsruhe, Germany honeymol.mathew@kit.edu Ömer Ekin

institute for automation and applied

informatics

karlsruhe institute of technology

Karlsruhe, Germany

oemer.ekin@kit.edu

Abstract—In the past decade, DC power grids have gained renewed attention due to their ability to easily integrate with renewable energy sources and DC loads. The emergence of power electronics has also facilitated this transition, allowing power electronic converters to function as transformers for DC grids. However, protecting DC grids has been challenging due to their low inertia. This paper proposes a modification to a unidirectional boost converter, enabling it to handle grid protection tasks. The main idea is to add a controllable power switch in the source-to-load power path such that faults on the load side can be isolated from the source side. The topology modification is described in detail, and simulation results are presented. Based on these results, the modified boost converter can independently clear pole-to-pole faults on the load side.

Keywords—Boost Converter, converter-based protection, DC circuit breaker, DC-link capacitor.

# I. INTRODUCTION

Political restrictions on fossil fuel supplies have significantly altered the energy landscape in the world, facilitating a transition towards renewable energy sources. Various countries have launched major initiatives to enhance their renewable energy infrastructure. For instance, Germany has doubled its installed solar electricity generation capacity over the past five years, increasing from 48.9 GW in 2019 to 99.2 GW by the end of 2024 [1]. The rapid expansion of renewable DC energy sources, storage, and DC loads such as electric vehicles (EVs), and data centers has renewed interest in DC grids. DC grids can offer higher efficiency compared to AC networks due to fewer conversion stages and lower effective resistance. Additionally, the absence of reactive power in DC systems reduces the size of conductors and the volume of copper needed to transmit a specific amount of active power, thereby enhancing the sustainability of future power grids [2]-[3]. This is particularly advantageous for microgrids, where solar generation is typically located close to consumption, making DC microgrids an obvious choice over AC microgrids.

Despite their obvious advantages, DC networks face complex protection requirements. Large DC-link capacitors and small line inductance result in very low inertia for DC grids, causing fault escalation to several per units within microseconds. This makes the speed of fault detection and interruption critically important, as longer detection times require clearing much larger fault currents, leading to increased complexity in fault isolation mechanisms. Additionally, the lack of current natural zero-crossing points

makes fault isolation of DC systems much more sophisticated compared to their AC counterparts. The presence of zerocrossing points in AC systems can facilitate the natural extinguishing of arcs during the fault interruption process. Consequently, a significant portion of DC grid studies over the past two decades has focused on fault detection and isolation in DC networks. The state of the art in DC microgrid protection has been reviewed in [4]-[5], which thoroughly examine different fault types in DC grids and the currently proposed methods for fault detection and isolation. There are also comprehensive reviews on various types of DC circuit breakers (DCCBs) based on solid-state switches [6]-[7], or hybrid mechanical and solid-state technologies [8]. Moreover, comprehensive reviews are available on energy absorption and voltage clamping circuits tailored to various DC circuit breaker technologies, specifying different reaction times and tolerance levels for overcurrent and overvoltage conditions. [9]-[10].

The main challenge in protecting DC networks appears to be the traditional protection mindset carried over from AC networks. In conventional AC networks, the use of power electronic equipment was minimal, making it logical to develop new devices specifically for isolating short-circuit faults. However, the extensive use of power electronic converters in DC networks presents a new opportunity for network protection. Many researchers question why the semiconductor switches in power electronic converters cannot be utilized for fault isolation, instead of using high-loss, largesized solid-state or hybrid DCCBs. This has led to the concept of converter-based or Breaker-less protection [2]. Based on this concept, power electronics converters can autonomously clear faults, assuming the roles of DCCBs. This approach introduces several advantages. First and foremost, it is possible to use signals typically measured at the converter site for fault detection. Secondly, since fault detection and interruption are performed by the converter, merging these units can significantly reduce fault clearing time. Finally, as power electronic converters are usually equipped with communication systems for power sharing applications, these systems can be utilized to develop more complex protection schemes, such as differential protection. While it is true that some converters inherently cannot isolate faults independently, it is possible to modify their structure to assign them the task of network protection in certain scenarios.

Based on this concept, this paper aims to modify a regular boost converter to independently interrupt pole-to-pole faults on the load side. While this modification can be applied to

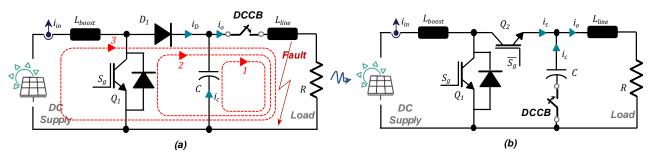

Fig. 1. Modification made to the boost converter (a) regular boost converter under faulty condition, (b) modified boost converter.

other types of converters in DC grids, boost converters, which play a significant role in solar energy conversion, have notable shortcomings in independently clearing faults. Therefore, this paper proposes a solution for their modification. The rest of the paper is organized as follows: the next section describes the characteristics of short-circuit faults on the load side of a boost converter. Section III details the modifications made to enable the boost converter to remove faults. Section IV presents the results, and the final section concludes the paper.

#### II. POLE-TO-POLE FAULT ANALYSIS

Boost converters are one of the basic topologies used for many applications like maximum power point tracking (MPPT) in photovoltaic systems or power factor correction (PFC). However, unlike the other two basic DC-DC topologies, they do not possess any controllable switching device in their power path between their input and output. Therefore, boost converters cannot independently disconnect their power path. If a pole-to-pole fault occurs on the output feeder of a boost converter, three stages of fault can follow as illustrated in Fig. 1.

1) DC-link capacitor discharge: At the initial moment after the fault occurrence, the DC-link capacitor discharges through the line inductor and fault resistance, forming an RLC circuit, as shown in Fig. 1(a) path 1. This results in a drastic increase in the line current. Neglecting the capacitor equivalent series resistance, the loop voltage equation can be expressed as (1).

$$L_f C \frac{d^2 V_c}{dt^2} + R_f C \frac{dV_c}{dt} + V_c = 0 \tag{1}$$

$L_f$ ,  $R_f$ , and  $V_c$  are the fault loop inductance, and resistance and capacitor voltage respectively. Consequently, the capacitor voltage and fault current can be calculated as follows:

$$V_c = e^{-\alpha t} (V_{c0} \frac{\omega}{\omega_d} \sin(\omega_d t + \beta) - \frac{I_{f0}}{\omega_d C} \sin(\omega_d t))$$

(2)

$$I_{f} = -C \frac{dV_{c}}{dt} = e^{-\alpha t} \left( -I_{f0} \frac{\omega}{\omega_{d}} \sin(\omega_{d} t - \beta) + \frac{V_{c0}}{\omega_{d} L_{f}} \sin(\omega_{d} t) \right)$$

(3)

Where  $\alpha=\frac{R_f}{2L_f}$ ,  $\omega_d^2=\frac{1}{L_f C}-\alpha^2$ ,  $\omega^2=\omega_d^2+\alpha^2$ , and  $\beta=tg^{-1}\left(\frac{\omega_d}{\alpha}\right)$ , and  $V_{c0}$  and  $I_{f0}$  are the capacitor initial voltage and line initial current when fault happens. This stage is the primary cause of the drastic escalation of fault current, which can be mitigated by increasing the line inductance using a fault current limiter.

2) Freewheeling diodes conduction: This stage begins when the capacitor voltage reaches zero. At this moment, the fault current flowing through the fault inductor forces the freewheeling diodes to turn on. During this stage, the fault current flows through the second path highlighted in Fig. 1(a). Assuming this stage starts at  $t_1$  and the initial value of fault current in this stage is  $I_{f,t1}$ , fault current in this stage can be expressed as:

$$I_f = I_{f,t1} e^{-\frac{R_f}{L_f}(t - t_1)} \tag{4}$$

3) Source current feeding stage: If an appropriate circuit breaker is not implemented, at this stage the fault current may escalate depending on the fault resistance and the DC source capacity to supply current. This escalation could potentially occur even before the second stage. During this stage, the fault current increases to its final value and the DC source continues to supply the fault (Fig. 1(a) path 3) until the circuit breaker intervenes.

As observed from the fault behaviour analysis, the drastic increase in fault current is primarily due to the rapid discharge of the capacitor. The time constant of the DC-link capacitor discharge is significantly shorter compared to the other two stages. Therefore, it may be more reasonable to use a fast current interruption unit in series with the DC-link capacitor. This approach can prevent the full occurrence of the first two stages. Additionally, modifying or rearranging the converter's semiconductors can enable the converter to independently interrupt the third stage fault current.

### III. PROPOSED MODIFICATION FOR BOOST TOPOLOGY

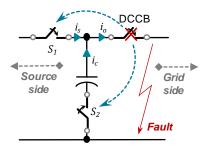

The fundamental principle of the breaker-less or converter-based methodology involves replacing the primary circuit breakers, traditionally installed in series with transmission line feeders, with alternative switching devices that can exhibit equivalent fault interruption capabilities. According to basic electrical circuit theory and as illustrated in Fig. 2, the conventional circuit breaker positioned in series with the transmission line can be substituted by two other switching devices located in separate branches that converge at a common node.

To implement the breaker-less concept in boost converters, and based on the fault analysis presented in the previous section, isolating a short circuit fault on the load side of a boost converter necessitates the use of two controllable switches. One switch should be positioned within the capacitor branch (Capacitor circuit breaker), while another element with adequate fault interruption capability must be placed within the converter branch (Converter circuit

Fig. 2. Breaker-less or converter-based fault interruption methodology

breaker). The capacitor circuit breaker, which blocks the capacitor discharge current (stage 1), must be a bidirectional fast switch capable of conducting the AC ripple current that flows through the capacitor during its normal operation. This switch must be able to block the fault current in only one direction, corresponding to the capacitor's polarity. Consequently, a MOSFET or an IGBT with an anti-parallel diode are suitable choices. On the other side, the converter switch must be positioned between the converter input and output to block the current flowing from the source towards the fault (stages 2 and 3). The optimal solution for the converter switch is to utilize the converter's semiconductors, thereby avoiding the introduction of another lossy switching component into the circuit. This approach highlights the primary advantage of the breaker-less fault interruption concept, which is higher efficiency compared to traditional breakerbased methodologies. The ripple current passing through the capacitor switch results in only a minimal power loss, unlike the significant power loss associated with a full-power DC circuit breaker placed in series with the grid. Furthermore, the power loss of converter semiconductors occurs regardless of their use for fault interruption. Considering that DCCBs have infrequent switching events, employing the breaker-less fault interruption methodology can reduce the power loss of breaker devices by an amount equivalent to the conductive power loss of a potential converter circuit breaker.

However, boost converters lack a fully controllable semiconductor capable of disconnecting the power path between the source and output. To modify their topology without compromising efficiency, the output diode can be replaced with a unidirectional controllable switch (Fig. 1(b)). MOSFETs are unsuitable for this application due to their inherent body diodes. Similarly, thyristors are not viable because the converter circuit breaker must switch in compliment with the converter's main switch, and thyristors cannot achieve the required high switching frequency. Therefore, the only suitable choice for the converter breaker is an IGBT without any embedded antiparallel diodes. Although these devices are less common, they are available on the market.

With this approach, the diode  $(D_1)$  in Fig. 1 is replaced with an IGBT, another IGBT with its anti-parallel diode is placed in series with the capacitor as the capacitor breaker, and the main DCCB is removed (Fig. 1(b)). The IGBT in series with the capacitor remains on during normal operation of the converter, while the other IGBT  $(Q_2)$  switches in complement with the converter's main switch  $(Q_1)$ . It is crucial to emphasize that the modified structure differs from bidirectional boost converters, as the added IGBT is oriented in a different direction relative to the converter's main switch. Consequently, even if both semiconductors are activated simultaneously, their opposing conduction directions prevent them from shorting the DC-Link capacitor.

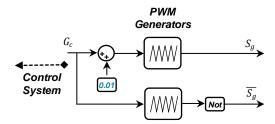

Fig. 3. Negative dead time production

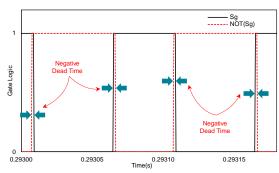

Fig. 4. gate signals of  $Q_1$ ,  $Q_2$ .

However, this modification can introduce complications. In the conventional boost converter configuration, the inductor ( $L_{boost}$ ) current seamlessly transitions between the switch and the diode. In contrast, with the modified version, any delay between the turn-off of one switch and the turn-on of the other can interrupt the inductor current, leading to significant voltage spikes across the semiconductor devices. To avoid blocking the boost inductor current ( $i_{in}$ ), a negative dead time is introduced by adding a small value to the PWM reference of the converter main switch. The logic for generating negative dead time is illustrated in Fig. 3. Additionally, the gate signals for switches  $Q_1$ , and  $Q_2$  are also depicted in Fig. 4.

In the event of a short-circuit fault, the converter main switch, converter circuit breaker, and capacitor circuit breaker switch open rapidly to interrupt the fault current. While the boost inductor current  $(I_{in})$  is a viable option for fault detection, measuring the converter output current  $(I_o)$  offers the fastest possible fault detection due to the inclusion of capacitor discharge current. It is also essential to note that both the converter main switch and the converter circuit breaker require energy absorption snubbers, such as RCD snubbers or varistors, to dissipate the energy stored in the converter and fault inductors. In the subsequent section, the simulation results of the modified topology incorporating two RCD snubbers are presented to demonstrate the effectiveness of the proposed methodology.

# IV. SIMULATION RESULTS

To validate the efficacy of the proposed protection strategy, a 2 kW PV-connected boost converter with a 380V output was simulated using MATLAB/Simulink. The boost converter was regulated using a maximum power point tracking methodology to ensure continuous delivery of maximum output power in response to varying irradiance levels. Detailed specifications of the simulated boost converter and its control system are provided in Table I.

TABLE I. SPECIFICATIONS OF THE SIMULATED BOOST CONVERTER AND FAULT

| Specification                         | Value                       |

|---------------------------------------|-----------------------------|

| PV voltage                            | 300V                        |

| Output voltage -power                 | 380V -2kW                   |

| Solar irradiance                      | 920W/m <sup>2</sup>         |

| Boost inductor inductance -resistance | 11.8mH -106.1mΩ             |

| Input -Output capacitors capacitance  | 1mF -1mF                    |

| Converter main switch snubber         | RCD -3.2mF & 40Ω            |

| Converter breaker snubber             | RCD -3.2mF & 40Ω            |

|                                       | with a varistor in parallel |

|                                       | (clamping voltage = 700V)   |

| Fault inductance -resistance          | 500uH -0.1Ω                 |

The design of snubbers for the converter main switch and the converter and capacitor breakers plays a crucial role in the effective operation of the proposed fault interruption methodology. Given that the capacitor branch should exhibit minimal inductance, implementing a snubber for the capacitor circuit breaker is unnecessary. The snubber used for the converter main switch can be optimized to minimize switching power loss. However, the snubber for the converter breaker must be designed to absorb the fault energy stored in the fault inductor, thereby limiting the voltage across the breaker to twice its nominal operating voltage. This paper employs RCD snubbers for both the converter breaker and the main switch. However, it is more reasonable to utilize more complex snubber designs for the converter breaker. Designing the RCD snubber to limit breaker voltage during faults renders it suboptimal from a power loss perspective, as it increases switching power loss during the converter normal operation. Therefore, the integration of a varistor in parallel with an RCD snubber has been implemented to achieve an optimal balance. This configuration effectively minimizes switching power loss during normal operation while also clamping the breaker voltage in the event of a fault.

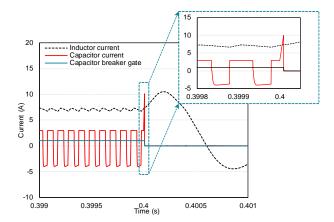

To assess the effectiveness of the proposed fault interruption methodology, a solid pole-to-pole fault is induced at 0.4 seconds, adhering to the impedance specifications outlined in Table I. In this study, both the boost inductor current and capacitor current are measured for fault detection. Although two-point measurement yields more precise results, fault detection can also be achieved by measuring only the capacitor current, inductor current, or even the output current of the converter. The sensed currents are compared to a threshold current, and fault signals are triggered accordingly. Fig. 5 illustrates the boost inductor and capacitor currents along with the gate signal of the capacitor breaker.

As illustrated in Figure 5, despite accounting for a reasonable amount of sensing and driver delay, the capacitor discharge current is effectively blocked within less than 10 microseconds. However, the oscillation of the inductor current persists for up to 5 milliseconds. This phenomenon occurs due to the necessity of discharging the energy stored in the boost and fault inductors. The oscillatory behavior of the inductor currents is attributed to their interaction with the snubber capacitors.

The independent implementation of capacitor discharge detection has been considered to minimize the time required for fault detection and interruption on the capacitor side. In practice, utilizing purely analog circuits on the capacitor side, independent of the converter controller, significantly reduces signal transmission time. The rapid interruption of capacitor

Fig. 5. Fault isolating performance of the modified boost converter.

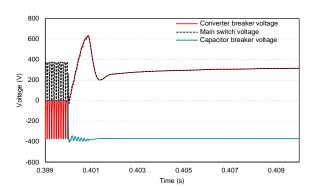

Fig. 6. Voltage drops across semiconductors during fault interruption

discharge current is a critical requirement for the converterbased protection concept.

Fig. 6 illustrates the voltage profiles across semiconductors during the fault interruption process. As previously mentioned, due to the minimal inductance anticipated in the capacitor branch, no snubber is implemented for the capacitor breaker. RCD snubbers are employed for both the converter breaker and the main switch. Additionally, a varistor was utilized in parallel with the RCD snubber of the converter breaker to dissipate the stored energy in the converter and line inductors.

As illustrated in Fig. 6, the voltage across the capacitor breaker exhibits minimal fluctuation, with the final voltage closely matching the converter's output voltage prior to the fault condition. Additionally, the voltage across the other two semiconductors experiences a transient increase but is effectively clamped to twice their normal values, demonstrating the efficacy of the implemented snubber circuits.

# V. CONCLUSION

The primary objective of this paper is to enhance the topology of basic boost converters in PV applications to autonomously fulfill protection roles. In these applications, power is intended to flow unidirectionally from the PV farm to the DC grid. Consequently, a unidirectional boost converter capable of mitigating load-side faults can serve as the DC Circuit Breaker, thereby obviating the need for a dedicated DCCB and improving overall efficiency. The detailed design of snubber circuits is elucidated, and the fault interruption capability of the proposed methodology, along with the energy absorption performance of the snubber circuits, is

thoroughly evaluated. The results indicate that the voltages across the semiconductors are constrained to twice their steady-state values. The high discharge current of the capacitor is also interrupted within several microseconds, while energy dissipation persists for a few milliseconds.

#### REFERENCES

- [1] Energy-Charts by Fraunhofer ISE, Net installed electricity generation capacity in Germany in 2024, available online: https://energy-charts.info/charts/installed\_power/chart.htm?l=en&c=DE&year=2024

- [2] Z. Ali et al., "Fault Management in DC Microgrids: A Review of Challenges, Countermeasures, and Future Research Trends," in IEEE Access, vol. 9, pp. 128032-128054, 2021, doi: 10.1109/ACCESS.2021.3112383.

- [3] L. Xu et al., "A Review of DC Shipboard Microgrids—Part I: Power Architectures, Energy Storage, and Power Converters," in IEEE Transactions on Power Electronics, vol. 37, no. 5, pp. 5155-5172, May 2022, doi: 10.1109/TPEL.2021.3128417.

- [4] L. Zhang, N. Tai, W. Huang, J. Liu and Y. Wang, "A review on protection of DC microgrids," in Journal of Modern Power Systems and Clean Energy, vol. 6, no. 6, pp. 1113-1127, November 2018, doi: 10.1007/s40565-018-0381-9.

- [5] S. Beheshtaein, R. M. Cuzner, M. Forouzesh, M. Savaghebi and J. M. Guerrero, "DC Microgrid Protection: A Comprehensive Review," in

- IEEE Journal of Emerging and Selected Topics in Power Electronics, doi: 10.1109/JESTPE.2019.2904588.

- [6] R. Rodrigues, Y. Du, A. Antoniazzi and P. Cairoli, "A Review of Solid-State Circuit Breakers," in IEEE Transactions on Power Electronics, vol. 36, no. 1, pp. 364-377, Jan. 2021, doi: 10.1109/TPEL.2020.3003358.

- [7] C. E. Ugalde-Loo, Y. Wang, S. Wang, W. Ming, J. Liang and W. Li, "Review on Z-Source Solid State Circuit Breakers for DC Distribution Networks," in CSEE Journal of Power and Energy Systems, vol. 9, no. 1, pp. 15-27, January 2023, doi: 10.17775/CSEEJPES.2022.04320.

- [8] A. R. F. Bento, F. Bento and A. J. M. Cardoso, "A Review on Hybrid Circuit Breakers for DC Applications," in IEEE Open Journal of the Industrial Electronics Society, vol. 4, pp. 432-450, 2023, doi: 10.1109/OJIES.2023.3320900.

- [9] S. Zhao, C. Xu, L. Ravi, Z. Dong and P. Cairoli, "Review and Analysis of Voltage Clamping Circuits With Low Overvoltage Ratios for DC Circuit Breakers," in IEEE Open Journal of the Industrial Electronics Society, vol. 5, pp. 651-662, 2024, doi: 10.1109/OJIES.2024.3420219.

- [10] G. Gregis, L. Piegari, L. Raciti and T. Masper, "A Review of Voltage-Clamping Methods for Solid-State Circuit Breakers," in IEEE Open Journal of Power Electronics, vol. 5, pp. 873-890, 2024, doi: 10.1109/OJPEL.2024.3411110.