# Institut für Technik der Informationsverarbeitung (ITIV)

Institutsleitung

Prof. Dr.-Ing. Dr. h. c. J. Becker (Sprecher)

Prof. Dr.-Ing. E. Sax

Prof. Dr. rer. nat. W. Stork

Masterarbeit Nr. ID-3621

von Herrn B.Sc. Mustafa Burak Cin

#### Future Automotive Gateways: A Paradigm Shift from MCU Based AUTOSAR Implementations to FPGAs

Beginn: 11.12.2024 Abgabe: 11.09.2025

Betreuer: Dipl.-Ing. Benjamin Schüler

Daimler Truck AG

Korreferent: Prof. Dr.-Ing. Dr. h.c. Jürgen Becker

Institut für Technik der Informationsverarbeitung

Hauptreferent: Dr.-Ing. Tanja Harbaum

| und Hilfsmittel vollständig un was aus Arbeiten anderer unver | 3, die Arbeit selbstständig verfasst, alle benutzten Quellen de genau angegeben und alles kenntlich gemacht zu haben, erändert oder mit Abänderungen entnommen wurde, sowie erung guter wissenschaftlicher Praxis in der jeweils gültigen |

|---------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Karlsruhe, den 04.09.2025                                     |                                                                                                                                                                                                                                           |

|                                                               |                                                                                                                                                                                                                                           |

|                                                               | B. Sc. Mustafa Burak Cin                                                                                                                                                                                                                  |

|                                                               |                                                                                                                                                                                                                                           |

# **Acknowledgements**

I would like to express my sincere gratitude to my academic supervisor and examiner, Dr.-Ing. Dipl.-Inform. Tanja Harbaum, for her constructive and detailed feedback, her thorough and insightful reviews, as well as for generously sharing her knowledge and scientific perspective. I am also grateful to Prof. Dr.-Ing. Dr. h. c. Jürgen Becker, who first inspired me with the idea of conducting my master's thesis at ITIV.

I could not have undertaken this journey without the support of Benjamin Schüler, my manager at Daimler Truck AG and supervisor for this thesis.

I would be remiss not to mention the Daimler Truck Academic Programs, which made my master's studies possible by providing the necessary framework to pursue my degree while working.

Words cannot express my gratitude to my colleagues:

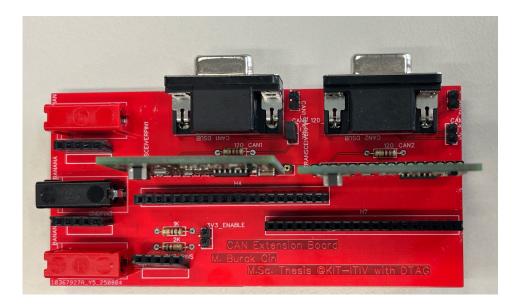

- Alican Yalçın, for his excellent soldering expertise and support in assembling the CAN extension boards, that I designed for this thesis.

- Deepak Naik, for his insightful reviews on the AUTOSAR related chapters and our in-depth discussions on the topic.

- Kevin Schmidt, for listening to my concept in early stages, his valuable insights and inspiring discussions on the latest advancements in IT data processing.

- Lucas Mauser, for his valuable guidance and knowledge sharing on how to conduct a systematic literature review.

- Matthias Schulz, for providing valuable feedback on the AUTOSAR-related subjects and our engaging discussions on this at the office.

- Sushmita Sahana, for her support and collaborative brainstorming during the debugging sessions of the AUTOSAR implementation in this thesis.

- Tayte Daniel Waterman, for sharing valuable perspectives during our discussions about hardware accelerated routing concepts and implementations.

- Wolfgang Griebel, also known as the first driver operating a vehicle with passengers equipped with a CAN XL network [1], for his thorough review and valuable feedback on in-vehicle networks, CAN, and many other chapters of this thesis.

Lastly, I wish to express my heartfelt thanks to my fiancée Jülide, my family and my friends for their patience and support throughout this thesis.

# **Abstract**

Automotive Gateways are fundamental components of In-Vehicle Networks (IVNs) that interconnect different networks, performing routing and protocol translations between them. The majority of today's gateways are processor based solutions implemented on microcontrollers utilizing the Automotive Open System Architecture (AUTOSAR) Classic software architecture. AUTOSAR introduces significant complexity, often requiring long development cycles and large development teams working over several years. Therefore, it is associated with high development costs as well as high initial investments due to required tooling, licenses and basic software stacks. While such complexity and associated costs may be justified for application centric, high end Electronic Control Units (ECUs), in majority of AUTOSAR Gateway projects these substantial efforts and resources fail to deliver adequate performance. These Gateway implementations often suffer from high Central Processing Unit (CPU) loads and in some cases even data loss. Although, recent CPU offloading solutions introduced by silicon vendors have improved the hardware capabilities to address some of the previously mentioned challenges, they remain insufficient in meeting non-functional requirements, particularly flexibility, complexity and cost efficiency. In parallel, emerging trends such as Software Defined Vehicles (SDVs) and Zonal Electric/Electronic (E/E) Architecture are anticipated to significantly redefine the requirements for Automotive Gateways. These trends introduce opportunities for new Gateway designs that were previously constrained by the existence of high number of ECUs and networks in a vehicle. In this thesis, the key requirements for future Automotive Gateways, in particular for Zonal Gateways, are first identified. Subsequently, a critical analysis of AUTOSAR based Gateway solutions is conducted, including its implementation on a microcontroller. Finally, the thesis proposes and demonstrates a novel, hardware centric Gateway architecture realized in the Programmable Logic (PL) of an Field Programmable Gate Array (FPGA), offering a new approach to meet the challenges and opportunities of future Zonal Gateways.

# Zusammenfassung

Fahrzeug-Gateways sind wesentliche Komponenten von fahrzeuginternen Netzwerken, die unterschiedliche Netzwerke miteinander verbinden und dabei das Routing sowie die Protokolübersetzung zwischen ihnen realisieren. Der Großteil der heutigen Gateways sind prozessorbasierte Lösungen, die auf Mikrocontrollern implementiert und unter Verwendung der Automotive Open System Architecture (AUTOSAR) Classic Softwarearchitektur realisiert werden. AUTOSAR bringt eine erhebliche Komplexität mit sich, die häufig lange Entwicklungszyklen sowie große Entwicklungsteams erfordert, die über mehrere Jahre an solchen Projekten arbeiten. Daher ist es mit hohen Entwicklungskosten sowie beträchtlichen Anfangsinvestitionen verbunden, unter anderem aufgrund der erforderlichen Werkzeuge, Lizenzen und Basissoftwarestacks. Während sich eine derartige Komplexität und die damit verbundenen Kosten bei applikationzentierten, leistungsstarken Steuergeräten möglicherweise rechtfertigen lassen, führen sie in der Mehrzahl der AUTOSAR-Gateway-Projekte trotz des erheblichen Aufwands und Ressourceneinsatzes nicht zu einer adäquaten Leistungsfähigkeit. Viele dieser Gatewayimplementierungen leiden unter einer hohen CPU-Auslastung und in einigen Fällen sogar unter Datenverlusten. Obwohl, von Halbleiterherstellern eingeführte CPU-Offloading-Lösungen die Hardwarefähigkeiten zur Bewältigung einiger der zuvor genannten Herausforderungen verbessert haben, sind sie nach wie vor unzureichend, um nicht-funktionale Anforderungen wie Flexibilität, Komplexität und Kosteneffizienz zu erfüllen. Parallel dazu wird erwartet, dass aufkommende Trends wie Software Defined Vehicle (SDV) und die zonale elektrische/elektronische (E/E)-Architektur die Anforderungen an Fahrzeug-Gateways erheblich neu definieren werden. Diese Entwicklungen eröffnen Möglichkeiten für neue Gateway-Designs, die zuvor durch die hohe Anzahl von Steuergeräten und Netzwerken in einem Fahrzeug eingeschränkt waren. In dieser Arbeit werden zunächst die Anforderungen für zukünftige Fahrzeug-Gateways, insbesondere zonaler Gateways, identifiziert. Anschließend wird eine kritische Analyse von AUTOSAR-Basierten Gateway-Lösungen, einschließlich ihrer Implementierung auf einem Mikrocontroller, durchgeführt. Abschließend wird eine neuartige, hardwarezentrierte Gateway-Architektur vorgeschlagen und in der Programmierlogik eines Field-Programmable-Gate-Arrays (FPGA) implementiert, um die zuvor genannten Herausforderungen und neu entstehenden Chancen für zukünftiger zonaler Gateways zu adressieren.

# **Contents**

| ΑI | bstrac          | ct      |                                                          |   |  |  |  |  |

|----|-----------------|---------|----------------------------------------------------------|---|--|--|--|--|

| Ζι | Zusammenfassung |         |                                                          |   |  |  |  |  |

| 1  | Intr            | oductio | on                                                       | 1 |  |  |  |  |

|    | 1.1             | Motiv   | ation                                                    | 1 |  |  |  |  |

|    | 1.2             | Contr   | ibution and Structure                                    | 4 |  |  |  |  |

| 2  | Bac             | kgroun  | d                                                        | 4 |  |  |  |  |

|    | 2.1             |         |                                                          | 4 |  |  |  |  |

|    |                 | 2.1.1   | Node                                                     | 4 |  |  |  |  |

|    |                 | 2.1.2   | Electronic Control Unit (ECU)                            | ١ |  |  |  |  |

|    |                 | 2.1.3   | Network                                                  | ( |  |  |  |  |

|    | 2.2             | Electr  | ic/Electronic (E/E) Architecture                         | ( |  |  |  |  |

|    |                 | 2.2.1   | Domain Centralized E/E Architecture                      | 7 |  |  |  |  |

|    |                 | 2.2.2   | Zonal E/E Architecture                                   | 8 |  |  |  |  |

|    | 2.3             | Contr   | oller Area Network (CAN)                                 | ( |  |  |  |  |

|    |                 | 2.3.1   | History of Controller Area Network (CAN)                 | ( |  |  |  |  |

|    |                 | 2.3.2   | Comparison of CAN Protocol Generations                   | ] |  |  |  |  |

|    |                 | 2.3.3   | Physical Layer of CAN                                    | 4 |  |  |  |  |

|    |                 | 2.3.4   | Data Link Layer of CAN                                   | 4 |  |  |  |  |

|    | 2.4             | Comn    | nunication Design Entities                               | ١ |  |  |  |  |

|    |                 | 2.4.1   | Communication Matrix                                     | ١ |  |  |  |  |

|    |                 | 2.4.2   | Frame                                                    | ( |  |  |  |  |

|    |                 | 2.4.3   | Protocol Data Unit (PDU)                                 | ( |  |  |  |  |

|    |                 | 2.4.4   | Signal                                                   |   |  |  |  |  |

|    | 2.5             |         | notive Open System Architecture (AUTOSAR) 1              |   |  |  |  |  |

|    |                 | 2.5.1   | AUTOSAR Partnership and Releases                         |   |  |  |  |  |

|    |                 | 2.5.2   | AUTOSAR Exchange Format                                  |   |  |  |  |  |

|    |                 | 2.5.3   | AUTOSAR Methodology and ARXML from OEMs' Perspective . 2 |   |  |  |  |  |

|    |                 | 2.5.4   | AUTOSAR Methodology from Tier 1 Supplier's Perspective 2 |   |  |  |  |  |

|    |                 | 2.5.5   | AUTOSAR Layered Architecture                             | 4 |  |  |  |  |

|    |                 | 2.5.6   | An Example of CAN Communication with AUTOSAR Layered     |   |  |  |  |  |

|    |                 |         | Architecture                                             | ( |  |  |  |  |

|    | 2.6             |         | vaying                                                   |   |  |  |  |  |

|    |                 | 2.6.1   | Terminology: Gateway vs. Router                          | ( |  |  |  |  |

## Contents

|    | 2.7                      | 2.6.2 Gatewaying in AUTOSAR                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                            |

|----|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| 3  | 3.1<br>3.2<br>3.3        | rature Review  FPGA-based Gateway Literature                                                                                                                                                                                                                                                                                                                                                                                               | 38<br>38<br>39<br>40                                                       |

| 4  | 4.1<br>4.2<br>4.3        | Targeted Communication Technology and Routing Types Drivers of the Concept: Challenges and Opportunities 4.2.1 Current Challenges 4.2.2 Opportunities Arising from Trends Important Requirements for Gateways 4.3.1 Requirement 1: Latency 4.3.2 Requirement 2: Flexibility 4.3.3 Requirement 3: Complexity 4.3.4 Requirement 4: Availability 4.3.5 Requirement 5: Development Cost 4.3.6 Requirement 6: Adaptation Concept of the Gateway | 42<br>42<br>44<br>44<br>45<br>46<br>46<br>47<br>47<br>48<br>48<br>48<br>48 |

| 5  | 1mp<br>5.1<br>5.2<br>5.3 | lementation  CAN Extension Board                                                                                                                                                                                                                                                                                                                                                                                                           | 53<br>53<br>54<br>58                                                       |

| 6  | 6.1<br>6.2               | Test Setup                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                            |

| 7  | 7.1<br>7.2               | Clusion and Future Work  Summary                                                                                                                                                                                                                                                                                                                                                                                                           | <b>73</b> 73 75                                                            |

| ΑŁ | brev                     | iations                                                                                                                                                                                                                                                                                                                                                                                                                                    | 76                                                                         |

| Bi | bliog                    | raphy                                                                                                                                                                                                                                                                                                                                                                                                                                      | 79                                                                         |

# 1 Introduction

Automotive Gateways serve as the fundamental network processing elements within the In-Vehicle Network (IVN) [2], enabling the routing of data across multiple vehicular networks. Their importance has grown significantly and is expected to further increase, particularly as in-vehicle data traffic is projected to exceed a Gbit/s rates [2].

Currently, most Gateway implementations are based on microcontrollers running the Automotive Open System Architecture (AUTOSAR) Classic software architecture. The automotive industry, however, is undergoing a transformation in Electric/Electronic (E/E) architectures, driven by advancements in IVN technologies and the shift towards the Software Defined Vehicle (SDV). These trends introduce new requirements for gateway design and may enable the adoption of more hardware-centric solutions.

This thesis examines the requirements and Key Performance Indicatorss (KPIs) relevant to both current and emerging Automotive Gateway architectures. It evaluates the advantages and limitations of microcontroller-based Gateways using the AUTOSAR Classic architecture, including a practical implementation on a microcontroller. Furthermore, the thesis proposes and implements a hardware-centric alternative using an Field Programmable Gate Array (FPGA) platform, and benchmarks this solution against the traditional microcontroller-based approach.

#### 1.1 Motivation

Microcontroller-based Gateways implementing the AUTOSAR Classic architecture often struggle to meet emerging requirements for flexibility, scalability, latency, and determinism, particularly as demanded by trends in SDVs and zonal E/E architectures [2]. Moreover, these gateways present notable challenges even in current applications, such as high initial investment, increased system complexity [3], elevated development costs, and lengthy development cycles.

Despite these drawbacks, AUTOSAR remains as the mainstream standard for automotive software architectures [4, 5], offering advantages such as software portability and support for multi-supplier development. These benefits are most evident in complex Electronic Control Units (ECUs) projects, in which complex application design is present. However, Gateway ECUs typically do not host application-level functionality, thereby limiting the practical advantages of using AUTOSAR in this context.

From a systems engineering perspective, Automotive Gateways primarily enable other ECUs to deliver differentiating vehicle functions, rather than providing such functions themselves. Nonetheless, under current microcontroller-centric AUTOSAR Classic paradigms, the development costs and timelines for Gateways are comparable to those for feature rich ECUs. The expansion of routing tables, which must be statically defined in AUTOSAR, further contributes to ongoing development and maintenance challenges.

The emergence of Zonal E/E Architectures and the shift towards SDVs have the potential to fundamentally reshape Automotive Gateway design [6]. In traditional distributed E/E architectures, the Central Gateway (CGW) served as the principal network processor. In contemporary Domain Centralized E/E Architectures, the CGW continues to play a central role, while domain controllers increasingly combine Gateway and application functionalities.

In both architectural models, the CGW often performs additional tasks such as diagnostics, security, and global time synchronization, frequently on the Central Processing Unit (CPU) [7]. As in-vehicle data traffic grows [2], reliance on the CPU for both communication and system services increases computational load, which can degrade throughput and reliability.

Recently, automotive silicon vendors have introduced accelerated networking solutions for microcontrollers [8, 9], designed to offload the CPU in Gateway applications. While these solutions may be suitable for High Performance Computers (HPCs) in Zonal E/E Architectures, where Gateway functionality remains critical, the inherent drawbacks of complexity, cost, and development time associated with microcontroller-based AUTOSAR solutions are likely to persist. These trade-offs are particularly challenging for domain controllers and low-end vehicles that do not employ HPCs.

A clear gap exists in both the academic literature and industry practice regarding the architecture of future Zonal and low-maintenance Gateways. The primary aim of this thesis is to define first fundamental requirements for future Gateways, identify the limitations of microcontroller-based AUTOSAR Classic Gateways and to address these limitations by proposing and implementing a hardware-centric alternative based on FPGA technology for future Zonal Gateways.

## 1.2 Contribution and Structure

This thesis makes three principal contributions to the field:

First, it identifies and analyzes the functional and structural requirements for future gateways, with a particular focus on Zonal Gateways.

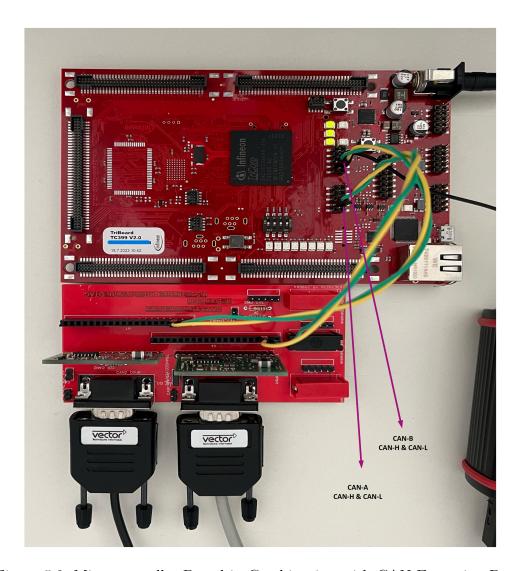

Next, it presents a complete implementation of a microcontroller-based AUTOSAR Classic Gateway using the Infineon TC399XX, illustrating both the strengths and limitations of this approach.

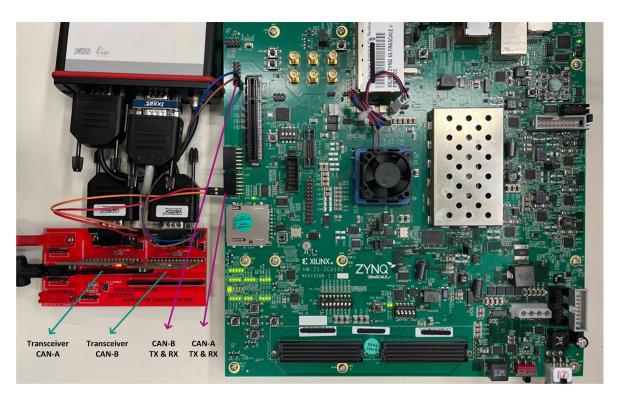

Finally, it proposes and implements a hardware-centric Gateway architecture on a Xilinx (AMD) Zynq UltraScale+<sup>TM</sup> MPSoC ZCU102, utilizing only the Programmable Logic (PL). This prototype includes the design of a Controller Area Network (CAN)-to-Intellectual Property (IP) router.

The thesis is organized as follows:

- Chapter 2 (Background) presents the theoretical foundations and prerequisite knowledge underlying this research.

- Chapter 3 (*Literature Review*) surveys related work, with a focus on AUTOSAR, E/E architectures, and Gateways.

- Chapter 4 (*Concept*) introduces the conceptual framework of the thesis, discusses key drivers of Gateway requirements, and examines the impact of SDV and Zonal E/E Architectures.

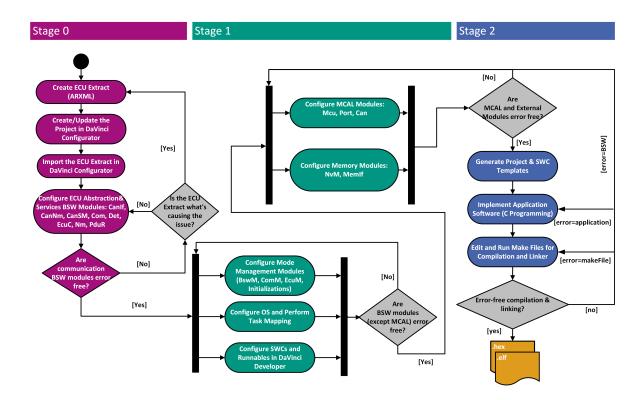

- Chapter 5 (*Implementation*) details the realization of both microcontroller-based and FPGA-based Gateway solutions.

- Chapter 6 (*Evaluation*) presents experimental results and provides a comparative analysis with respect to the requirements defined in Chapter 4.

- Chapter 7 (*Conclusion*) summarizes the main findings, outlines limitations, and suggests directions for future research.

# 2 Background

#### 2.1 Communication Components

This section provides definitions and explanations of technical terms such as Nodes, interfaces, ECUs and networks that will be referenced frequently throughout the remainder of this thesis.

#### 2.1.1 Node

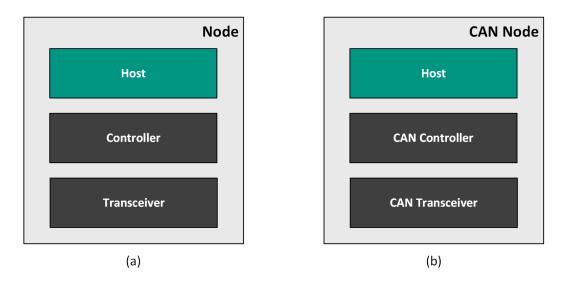

A Node [10] consists of a processing unit that performs the data exchange with processing units in other devices through a communication protocol controller and a transceiver. The processing unit in a Node is commonly referred to as the host [10]. An illustration of a Node is given in the Figure 2.1 (a).

Figure 2.1: Representation of a Node and a CAN Node [10]

In this thesis, the CAN (refer to the Section 2.3) is the main communication protocol being used. When a Node is implemented with the CAN communication capability, it is referred to as a CAN Node and typically comprises a host, a CAN controller and a CAN transceiver. An illustration of a CAN Node is given in the Figure 2.1 (b).

#### 2.1.2 Electronic Control Unit (ECU)

ECUs are essential computing systems in vehicles, originally developed to manage the operation of sensors and actuators to enable specific vehicle functions [2]. In the context of this thesis, an ECU is considered as comprising a host along with its communication interfaces.

In the automotive industry, the host of an ECU is typically implemented using a microcontroller [10]. However, in certain scenarios, it may also be realized using a FPGA[11], an Application Specific Integrated Circuit (ASIC) [11] or a microprocessor [12].

The communication interfaces of an ECU facilitate the data exchange with other ECUs, commonly referred to as the inter-ECU communication. The combination of a CAN controller and a CAN transceiver within a CAN Node constitutes a CAN interface.

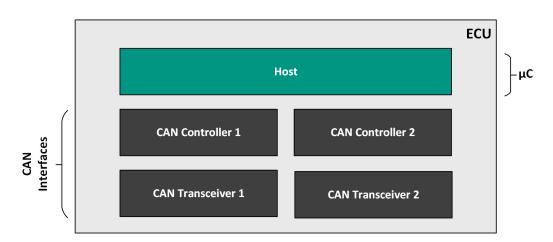

An ECU may have multiple communication interfaces. Consequently, an ECU equipped with several CAN interfaces can connect to multiple CAN channels and functions as a CAN Node on various CAN networks within a vehicle. Within the scope of this thesis, the terms CAN Node and ECU may be used interchangeably. Figure 2.2 illustrates a representative ECU with two CAN interfaces.

Figure 2.2: Representation of an ECU with two CAN interfaces [10]

The CAN controller in an ECU may either be integrated into the host or implemented as an external CAN controller as a hardware. Both configurations can be found later in this thesis in the Figure 2.12. On the other hand, although some CAN controllers are available in the industry with multi-channel support, for the sake of simplicity, the illustrations in this thesis depict each CAN channel with a dedicated CAN controller and a CAN transceiver.

#### 2.1.3 Network

A network, specifically a CAN network consists of two or more ECUs typically connected through a linear bus topology. The CAN interfaces of these ECUs are connected to the CAN network through physical layer components, namely the CAN High (CAN-H) and CAN Low (CAN-L) wires.

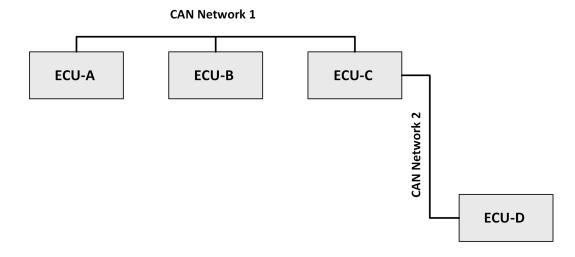

Figure 2.3: A representative E\E Architecture

A representative E/E architecture with four ECUs and two CAN networks is given in the Figure 2.3, where there are three ECUs (ECU-A, ECU-B, ECU-C) connected to the CAN Network 1, while two ECUs (ECU-C and ECU-D) connected to the CAN Network 2. Although not explicitly stated, it can be deduced from the Figure 2.3, that the ECU-C is equipped with two CAN interfaces, as it is connected to both CAN Network 1 and CAN Network 2. The presence of multiple communication interfaces does not inherently qualify an ECU as a gateway. The actual network configuration can only be determined through analysis of the ECU's circuit diagram and the software configuration. However, ECUslike ECU-C, typically functions as gateway ECUs and enables the data exchange between two distinct CAN networks.

# 2.2 Electric/Electronic (E/E) Architecture

This section provides the foundational concepts of Electric/Electronic Architectures, with particular focus on both Domain Centralized and Zonal E/E Architectures.

#### 2.2.1 Domain Centralized E/E Architecture

E/E Architecture is the structural organization of a vehicle's electrical and electronic systems including ECUs, sensors, actuators, wiring and networks that is designed to achieve functional objectives [13].

The initial E/E Architecture trend was the Distributed E/E Architecture, in which each function was realized by a dedicated ECU [14, 2]. With rapidly increasing functions and amount of the software, this methodology became difficult to sustain and manage especially due to large number of ECUs.

The second generation of E/E Architecture is the Domain Centralized E/E Architecture, in which ECUs are distributed into networks according to their functionalities [14, 2], such as Powertrain Domain or Advanced Driver Assistance Systems (ADAS) Domain [15].

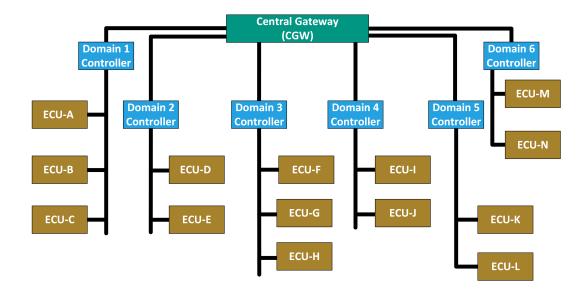

Figure 2.4: Domain Centralized E/E Architecture [14, 16, 13, 6]

Within this architecture, functions are grouped together [6] and each domain is managed by a dedicated domain controller ECU. Sub-domain ECUs are integrated under these domain controllers' sub networks. The Domain Controllers are connected to the CGW, which not only handles the protocol conversion and routing but also typically is responsible for roles such as diagnostics, security and network management coordination [13].

An illustration of the Domain Centralized E/E Architecture is given in the Figure 2.4.

The Domain Centralized E/E Architecture remains the mainstream E/E architecture used in today's vehicles [6]. Since ECUs are allocated to networks based on their functional roles rather than their physical placement within the vehicle, this architecture introduces challenges for Original Equipment Manufacturers (OEMs), particularly due to the long

wiring harnesses required [6, 13]. The wiring harness complexity might be even more challenging for heavy duty vehicle manufacturers, where vehicles are significantly longer than the passenger cars. Given that the wiring constitutes one of the heaviest and most costly elements of a vehicle [17], this challenge represents a major limitation.

Although the transition from the Distributed E/E Architecture to Domain Centralized E/E Architecture sought to move away from the One-ECU-per-function concept [14], the continuous expansion of vehicle functions, mainly due to naturally increased by electrification, autonomy, ADAS features, have nevertheless resulted in a significant increase in the number of ECUs in recent years.

#### 2.2.2 Zonal E/E Architecture

The challenges outlined in the Subsection 2.2.1 have driven the industry to seek alternative E/E Architecture solutions. In this context, the Zonal E/E Architecture has been proposed, wherein ECUs are distributed in the vehicle according to their physical locations. This approach aims to address aforementioned wiring harness challenges, as well as associated cabling costs [2, 6].

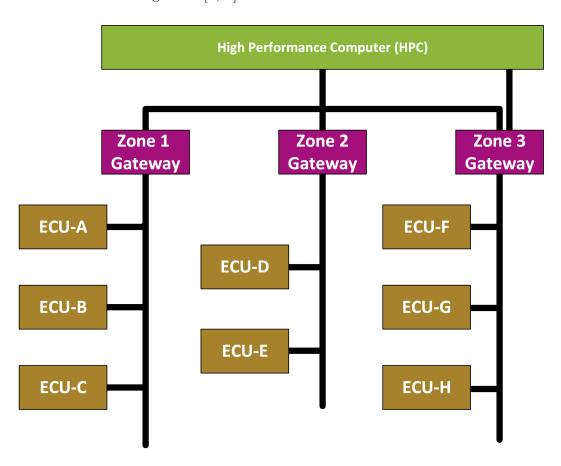

Figure 2.5: Zonal E/E Architecture [16, 13, 6]

In the Zonal E/E Architecture, a central vehicle computer, also referred as HPC, is responsible for implementing the majority of vehicle functions [6]. The physically distributed zones are equipped with dedicated Zonal Gateways, which manage the data traffic between the HPC and end nodes (Zonal ECUs).

An illustrative representation of the Zonal E/E Architecture for a heavy-duty vehicle is given in the Figure 2.5.

By consolidating most of vehicle functions within the HPC, this architecture significantly reduces the overall number of ECUs [13]. Since the network distribution is based on physical rather than functional, the number of networks are typically limited to four in passenger cars [2, 6] and three for heavy-duty vehicles where the vehicle length is considerably greater.

Through these design principles, the Zonal E/E Architecture aims to reduce overall system complexity and costs [2].

In this thesis, the transition toward Zonal E/E Architecture is regarded as an opportunity to redefine the existing gateway designs, with a particular focus on Zonal Gateways. The opportunities and potential implications of this architectural shift on Zonal Gateway designs will be examined in detail in the Subsections 4.2.1 and 4.2.2.

## 2.3 Controller Area Network (CAN)

This section provides an overview of the fundamentals of CAN Protocol, its generations, and its history.

With the increasing number of ECUs and the rising volume of the data exchange in vehicles, the use of point-to-point connections between ECUs has become inefficient. For instance, it is common for a single signal to be required by multiple ECUs, with point-to-point connection this necessitates duplicating the transmission over separate dedicated lines, leading to redundancy and complexity. Additionally, introduction of new features or improvements often requires significant modifications to the physical hardware and wiring harnesses. To overcome these challenges, the adoption of a bus system has become essential in the design of the in-vehicle networks.[10]

## 2.3.1 History of CAN

The transition to bus systems began several decades ago in the automotive industry. In 1983, the development of the CAN communication protocol has been started at Robert Bosch GmbH to address the evolving communication requirements of automotive industry at the time. During the development of CAN, a particular attention was given to followings:

- The protocol should be able to operate reliably in environments where the electromagnetic interference is high.

- The protocol should support rapid recovery following the error detection

- A non-destructive arbitration mechanism is required to guarantee that only one node transmits at a time.

Due to these features, the CAN protocol is capable of meeting the stringent hard real time requirements demanded by automotive applications. [18]

While the reduction of wiring complexity and harness weight represents one of the most substantial advantages of the CAN protocol compared to point-to-point connection, this emerged as a by product rather than a primary design criterion [19].

The development of the CAN protocol involved collaborative efforts between Bosch experts, Mercedes-Benz engineers and academic institutions culminating in its introduction in 1986 at the SAE Congress in Detroit [19]. The following year, in 1987, the first CAN controller chip 82526 is being produced and delivered by Intel [19, 18]. The first series application of the CAN protocol was introduced by Mercedes-Benz in the S-Class model in 1991 [10]. In 1993, formal standardization of the CAN protocol was achieved through the publication of ISO 11898 [19]. The initial implementation -the first generation of CAN- commonly referred to as Classical CAN or CAN 2.0 and it supports data rates up to 1 Mbit/s and allows for up to 8 data bytes in a CAN frame [20, 21].

The CAN protocol continues to evolve continuous enhancements. Following the initial ISO standard in 1993, two subsequent generations of CAN protocol has been introduced:

- The development of CAN Flexible Data-Rate (CAN FD) was initiated in 2011 by General Motors and Bosch with the objective of achieving higher data throughput [19]. Prior to this, several academic studies proposed extensions to the CAN protocol to enhance its capability [20]. Bosch has released the official specification of CAN FD in 2012 [22] and the protocol was formally introduced at the 13th international CAN Conference. CAN FD was incorporated into the ISO 11898 standard in 2015. This advancement increased the maximum payload size from 8 to 64 bytes and enabled data rates up to 8 Mbit/s with CAN FD Signal Improvement Capability (SIC) transceivers [23, 19, 24, 21].

- CAN extended data-field length (CAN XL) is the third and the latest generation of the CAN protocol. Its development began in 2018, initiated by a request from Volkswagen to address increased bandwidth requirements with the zonal architecture and high performance computing [19, 25]. In 2024, CAN XL was formally standardized under ISO 11898-1 and ISO 11898-2. This third generation CAN Protocol, CAN XL, introduces significant enhancements including an increased payload capacity up to 2048 bytes and support for data rates up to 20 MBit/s with CAN SIC XL transceivers. [19, 24, 26, 21].

#### 2.3.2 Comparison of CAN Protocol Generations

In the Table 2.1 a summary and comparison of these can generations is being shown.

| CAN Protocol | Number of Data Bytes | Maximum Data Rate | Year of Introduction |

|--------------|----------------------|-------------------|----------------------|

| CAN 2.0      | 8 Byte               | 1 Mbit/s          | 1986                 |

| CAN FD       | 64 Byte              | 8 Mbit/s          | 2012                 |

| CAN XL       | 2048 Byte            | 20 Mbit/s         | 2024                 |

Table 2.1: Comparison of different CAN protocol versions

The study in [21] compares different CAN protocol generations and proposes an optimal choice based on the payload size. In practical scenarios, the adoption and implementation of different CAN protocols by OEMs are influenced by a range of factors. A key consideration is that not all vehicle functions require data rates exceeding 1 Mbit/s which can be sufficiently supported even by the classical CAN. Furthermore, the E/E architectures developed by OEMs differ significantly across vehicle types and product lines. Typically, the latest in-vehicle network technologies are first implemented in the high-end models, while cost-sensitive products continue to be manufactured using comparatively older technologies. Although the classical CAN was introduced in 1986, it remains widely in use in in-vehicle networks and is expected to continue playing a prominent role, particularly among commercial vehicle OEMs, where the production volume is lower than passenger car OEMs and the cost sensitivity is a more critical factor.

Although Automotive Ethernet based in-vehicle network protocols -such as 10BASE-T1S, 100BASE-T1 and 1000BASE-T1- are increasingly being adopted in the automotive industry, particularly in the context of software defined vehicles and emergence of zonal architectures where Automotive Ethernet serves as the backbone of the E/E architecture, CAN based protocols are still expected to remain prevalent within subnetworks connecting zonal gateways and mechatronic ECUs.

The second generation, CAN FD protocol along with CAN FD SIC transceivers has been widely adopted by OEMs since its introduction. In contrast, CAN XL is still in its early stages of adoption with only a limited selection of CAN SIC XL transceivers and controllers currently available in the market. Nonetheless, several OEMs and Tier1 suppliers plan to implement the latest generation of CAN protocol, CAN XL within zonal architectures [24, 25].

In 2023, a proof of concept project led by Daimler Truck AG, in collaboration with Bosch, NXP, Rohde & Schwarz and Vector Informatik GmbH, involved replacing an existing CAN FD network in a Mercedes-Benz Citaro bus with a CAN XL network. This setup achieved a data rate of 14.5 Mbit/s over 60 meter cables while retaining the original CAN wiring harness used for CAN FD communication [1]. This research project

represented the first real-world application of CAN XL technology in a vehicle carrying passengers; however, its adoption for series production has not yet been confirmed and remains under evaluation.

The choice and usage of CAN protocol generation influences the design of a gateway ECU and impacts KPI such as CPU load and routing latency. However, the primary objective of this thesis is independent of the specific CAN protocol employed, and the findings can be generalized across different CAN protocol generations. Due to hardware availability for the implementation and comparability with existing gateway ECUs, the classical CAN protocol with 29-bit identifier is utilized for the implementation of this thesis.

#### 2.3.3 Physical Layer of CAN

The physical layer of the CAN protocol is standardized in International Organization for Standardization (ISO) 11898-2 [27, 28] and except the Physical Coding Sublayer (PCS), it is implemented in the CAN transceiver hardware.

According to the definition in the Open Systems Interconnection (OSI) Model [29], the physical layer provides the mechanical, electrical, functional and procedural means to activate, maintain and deactivate physical connections for bit transmission between datalink-entities. Physical layer entities are interconnected by means of a physical medium. In the context of CAN, the physical layer entities correspond to CAN transceiver and a part of CAN controller -PCS-. The CAN Physical layer is standardized in ISO 11898-1 and ISO 11898-2. The OSI Layer model for a CAN communication is illustrated in this thesis in Figures 2.6 and later 2.12.

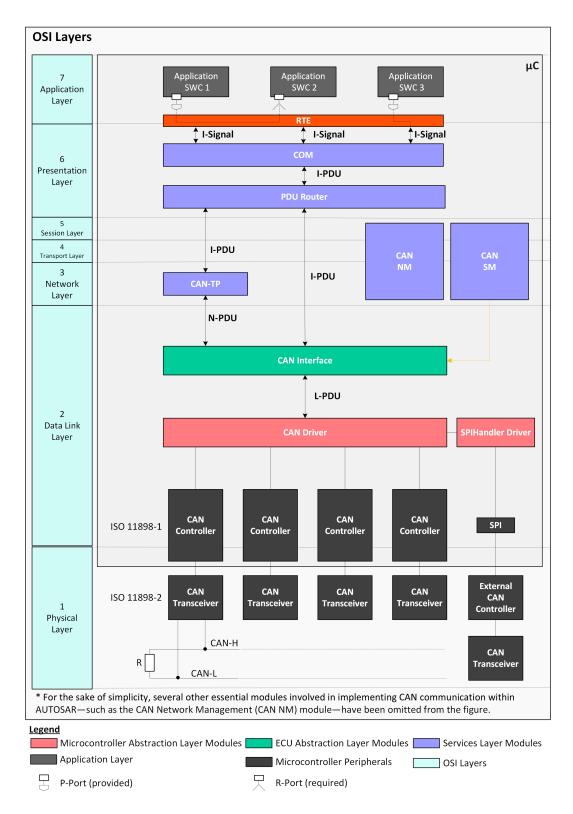

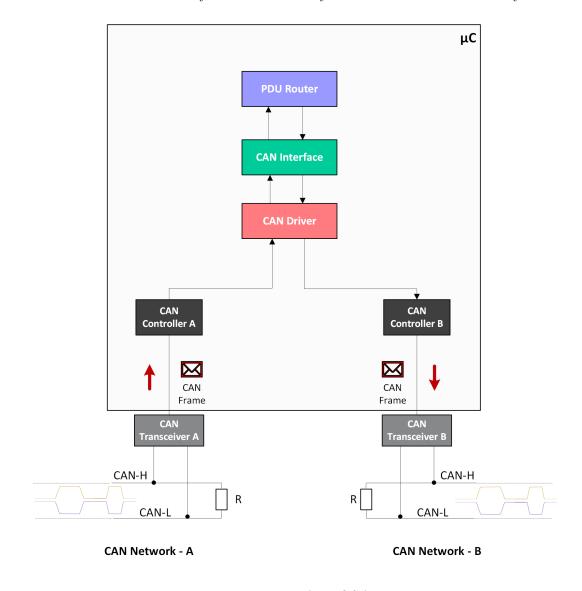

Figure 2.6: CAN Communication with Layered Architecture acc. to AUTOSAR versions >=4.3 and <24-11

ISO 11898-2 [30] defines the bus state in CAN protocol. According to this standard, the dominant bus state represents the logical 0 (where the voltage difference between CAN-H and CAN-L cables are around 2 Volts) and the recessive bus state represents the logical 1 ( $V_{\text{CAN-H}} - V_{\text{CAN-L}} \approx 0 \text{ V}$ ).

#### 2.3.4 Data Link Layer of CAN

The data link layer of CAN protocol is standardized in ISO 11898-1 [27, 28] and implemented in a CAN controller.

According to the definition in the OSI Model [29], the data link layer is in charge of transferring the data link service data units. The data link service data unit corresponds to the CAN frame entity of the data link layer. The OSI Layer model for a CAN communication is illustrated in Figures 2.12 and 2.6 later in this thesis.

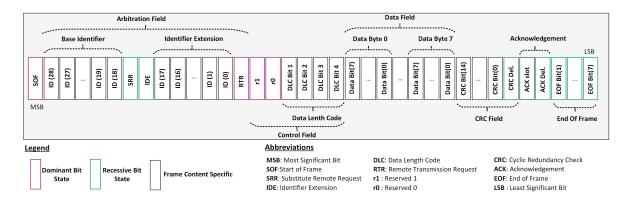

The CAN protocol standardizes several CAN frame formats [28, 27]. In this thesis, only CAN Classical Extended Frame Format (CEFF) for the data frame will be considered. An illustration of CEFF with 8 byte data field is given in the Figure 2.7.

Figure 2.7: CEFF with 29 Bit Identifier [28]

In CEFF, there are fields with predefined bit states (dominant or recessive bit state), which will result into the bus state.

The transmission on the bus begins with the dominant Start of Frame (SOF) bit. Within each field, the Most Significant Bit (MSB) is transmitted first. In the data field, bytes are sent sequentially from Byte 0 to Byte 7 and with each byte, the bits are transmitted from bit 7 down to bit 0 [28].

The CAN protocol defines the bus access method for the CAN protocol by specifying a bitwise arbitration mechanism based on the CAN frame Identifier (ID). This arbitration

mechanism ensures that, in scenarios where multiple CAN nodes attempt to transmit frames simultaneously, only one frame is transmitted on the bus.

Lower CAN frame ID values have higher priority, as the CAN protocol designates the dominant bit state as logical '0'. Frames with higher priority -i.e. those with lower CAN frame ID values- win the arbitration and are allowed to continue being transmitted on the CAN bus.

All CAN Nodes, including those currently transmitting, continuously monitor the CAN bus as well as their own transmission [31]. If a CAN Node attempts to transmit a recessive bit but detects a dominant bit on the CAN bus, it recognizes that it has lost the arbitration. As a result, it ceases transmission and the node which sends the higher priority frame continues uninterrupted.

The arbitration mechanism is non destructive, meaning that the node which lost the arbitration will attempt to retransmit its frame once the bus is in idle state. The idle bus state can be identified via seven consecutive recessive bits marking the end of frame field, followed by the intermission field with three recessive bits.

## 2.4 Communication Design Entities

#### 2.4.1 Communication Matrix

Distributed functionalities are realized by ECUs in a vehicle. ECUs require certain information from other ECUs to perform their own functions. This naturally results in a database created and maintained by the OEM, which stores the data transmitted and received between ECUs. This database is commonly referred to as communication matrix (a.k.a K-Matrix or CAN-Matrix). The data between ECUs are being transmitted via frames.

Typically frames and their attributes are defined by OEMs along with Protocol Data Units (PDUs) and signals. The communication matrix generated by the OEM results into an ECU Extract for an individual ECU. Further information about the ECU Extract is provided in the Section 2.5.

A representative design of a communication matrix is depicted in the Table 2.2:

Although adherence to AUTOSAR standards is not mandatory for implementing the CAN protocol, AUTOSAR strictly conforms to the ISO CAN standardization. Furthermore, many OEMs opt to develop their communication matrices based on the constraints defined in the AUTOSAR System Template [32] . A comprehensive overview of the communication matrix, its relation and usage in AUTOSAR framework, and ECU Extract is provided in the Section 2.5.

| Frame Name | Frame ID  | Length (Byte) | Type        | Launch Type | Timing | ECU-A | ECU-B | ECU-C | Diag<br>Tester |

|------------|-----------|---------------|-------------|-------------|--------|-------|-------|-------|----------------|

| ADAS_01    | CF08B00h  | 8             | Application | Cyclic      | 50 ms  | s     | -     | r     | -              |

| BRAKE_01   | 0F04C01h  | 8             | Application | Cyclic      | 10 ms  | r     | -     | S     | -              |

| DIAG_RQ    | 10DA4CFFh | 8             | Diagnostic  | Spontaneous | -      | r     | r     | r     | s              |

$$\mathbf{s} = \text{send}, \, \mathbf{r} = \text{receive}$$

Table 2.2: A Representative Design of a Communication Matrix on One Network

#### 2.4.2 Frame

In the design of a communication matrix, a frame serves as a container for PDUs. The data field length of a CAN frame is restricted to 8 bytes according to the ISO 11898-1 standard [28, 27].

#### 2.4.3 Protocol Data Unit (PDU)

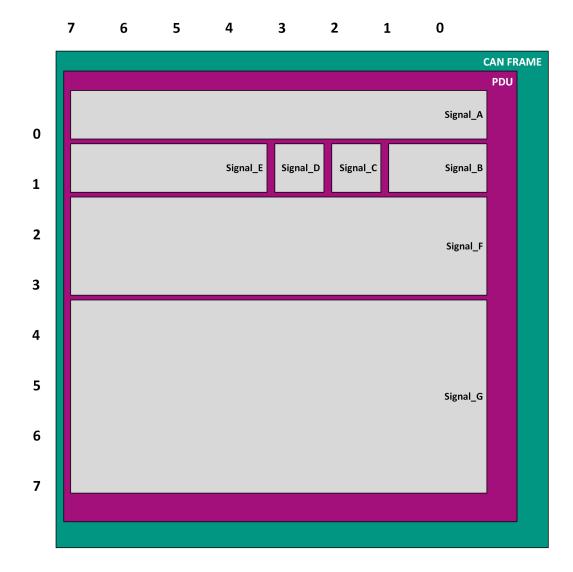

PDUs encapsulate communication signals. OEMs may define multiple PDUs in a frame -if the communication protocol allows- and multiple signals in a PDU.

In the context of classical CAN, each CAN frame is limited to containing a single PDU [32]. A representative CAN frame, a PDU and signals with their hierarchical layout are provided in the Figure 2.8.

Figure 2.8: Representation of a Data Field of a CAN Frame

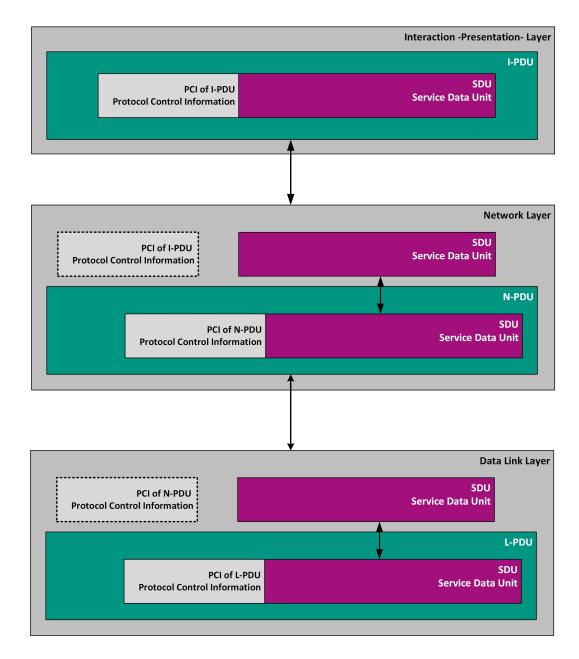

In the OSI Model [29], the CAN protocol [32] and the layered AUTOSAR Architecture [28], a PDU consists of two components:

- 1. Service Data Unit (SDU)

- 2. Protocol Control Information (PCI).

The SDU represents the actual payload transferred by the upper layer, while PCI contains essential information required for transferring the SDU between layers. The process of transferring the SDU across layers is depicted in the Figure 2.9

Figure 2.9: Illustration of PDU, SDU and PCI [32, 29]

In the AUTOSAR Layered architecture, PDUs are assigned specific prefixes that reflect the OSI layer responsible for their handling. These prefixes are:

- Interaction Presentation Layer PDU (I-PDU)

- Network Layer PDU (N-PDU)

- Data Link Layer PDU (L-PDU)

The L-PDU corresponds to the CAN frame mentioned in the Section 2.3.4. A comprehensive depiction of OSI layers along with their associated PDUs is represented later in this thesis in Figures 2.6 and 2.12.

#### **2.4.4 Signal**

A signal is the smallest unit that is used in the communication to transfer information. They are encapsulated within PDUs and are characterized by various attributes in the communication matrix. A representative design of signals inside a PDU is provided in the Table 2.3.

| Level  | Object Name | Signal Length<br>Bit(s) | Data Type         | Signal Bit<br>Start Position |

|--------|-------------|-------------------------|-------------------|------------------------------|

| Frame  | ADAS_01     |                         |                   |                              |

| PDU    | ADAS_01_PDU |                         |                   |                              |

| Signal | $Signal\_A$ | 8                       | SCALED_08_DEG     | 0                            |

| Signal | $Signal\_B$ | 2                       | $ENUM\_02\_STAT$  | 8                            |

| Signal | $Signal\_C$ | 1                       | BOOLEAN           | 10                           |

| Signal | $Signal\_D$ | 1                       | BOOLEAN           | 11                           |

| Signal | $Signal\_E$ | 4                       | ENUM_04_MODE      | 12                           |

| Signal | $Signal\_F$ | 16                      | SCALED_16_YAW     | 16                           |

| Signal | $Signal\_G$ | 32                      | $SCALED\_32\_POS$ | 32                           |

Table 2.3: An Example Design of Signals in a PDU

## 2.5 Automotive Open System Architecture (AUTOSAR)

This section aims to explain fundamentals of AUTOSAR and important pillars of it in the context of gatewaying.

### 2.5.1 AUTOSAR Partnership and Releases

AUTOSAR is a partnership founded in 2003 that brings automotive OEMs, suppliers, service and tool providers together in order to standardize the software development methodology for an open E/E architecture [19, 33].

Thanks to its layered architecture (refer to chapter 2.5.5), AUTOSAR provides the possibility to decouple the development of the differentiator application software from

the hardware. With the usage of AUTOSAR standardization in the ECU development process, significant improvements are expected to be yielded [34]. Through AUTOSAR, standardization of non-competitive software, re-usability and reduction of overall software development costs are outcomes anticipated by OEMs. While these benefits are expected and mentioned by the partnership, their realization in practice may depend on various factors and remains subject to an evaluation.

The partnership standardizes the AUTOSAR Classic Platform and AUTOSAR Adaptive Platform and releases their specification documents annually along with the Foundation standards in order to ensure the interoperability between the two platforms. Adaptive Platform is being developed to address use cases that require high-performance computing. Its implementations are based on microprocessors using Portable Operating System Interface (POSIX) operating systems [35]. The relevant AUTOSAR platform for this thesis is the AUTOSAR Classic platform, where the near hard real-time requirements and safety constraints for automotive embedded ECUs are aimed to be met [36]. Implementations of this platform are typically carried out on microcontrollers.

As the partnership releases new versions of its standards, tool and stack providers typically align their development strategies to support these updates. However, the adoption of a new AUTOSAR release often requires several years to be seen in vehicles on the road. Currently, the majority of ECU development in the automotive industry is based on AUTOSAR stacks version R4.3.0 or later. A common industry practice is for stack providers to deliver OEMs and Tier 1 suppliers their most recent AUTOSAR-compliant stack available at the start of a development cycle, with subsequent updates integrated as needed throughout the project. The selection of stack features and AUTOSAR versions is to a great extent influenced by the Extensible Markup Language (XML) schema version specified by the OEM. A more detailed discussion of the XML schema versions will be presented in the chapter 2.5.2.

In this thesis two key AUTOSAR release versions are referenced: the Classic Platform Release R4.4.0 and latest Classic Platform Release R24-11. While R4.4.0 is widely used in the automotive industry, R24-11 introduces new features such as Link Layer SDU (L-SDU) Router which is relevant to thesis topic.

#### 2.5.2 AUTOSAR Exchange Format

With the software-defined vehicle trend, OEMs seek to expand their in-house software development capabilities. However, at present, the predominant portion of software continues to be developed in collaboration with suppliers [37].

AUTOSAR specifies a standardized exchange format in order to facilitate and streamline this collaboration. In AUTOSAR Classic Platform, the content of the exchange format is primarily specified by the system template and software component template documents, both created and maintained by the AUTOSAR Working Group Methodology and Templates (WG-MT). These documents build upon the AUTOSAR meta-model which is

written using the Unified Modeling Language (UML)2.0 language. The chosen exchange format in AUTOSAR is XML, with its production rules also standardized by the partnership and the specific file name extension used is .arxml (AUTOSAR XML (ARXML)), which will be referred to as ARXML and ECU Extract throughout this thesis [32, 38, 39]. The standardized AUTOSAR facilitates the interoperability across various development tools [40].

Each AUTOSAR release is accompanied by a corresponding XML schema version for ARXML. As outlined in the chapter 2.5.1, this thesis focuses on AUTOSAR Releases R4.4.0 and R24-11, which are associated with the XML schema versions AUTOSAR\_00046 and AUTOSAR\_00053 respectively [35].

# 2.5.3 AUTOSAR Methodology and ARXML from OEMs' Perspective

In the automotive software development process, suppliers may be responsible for one or multiple ECUs, while OEMs are responsible for the overall system. Consequently, prior to the generation of an ECU Extract, OEMs shall complete several pre-requisite tasks related to the system level design. These tasks include, but are not limited to, the following:

- 1. Creating E/E Architecture

- 2. Assigning ECUs to Specific In-Vehicle Networks

- 3. Distributing Functions into ECUs

- 4. Creating Communication Design of ECUs in a Database

- 5. Creating Software Component Design of an ECU in a Database

The sequence or the existence of the above tasks may vary depending on the ECU being developed and the strategic approach adopted by the OEM.

In scenarios where the ECU's functionality does not serve as a differentiating factor (e.g. gateway ECUs) or when OEMs do not possess sufficient in-house expertise for a specific functionality (e.g. steering angle sensor ECUs), OEMs may opt not to define the software component architecture in terms of atomic software components and their internal behaviors. Instead, OEMs might generate a top level software compositions that are structurally defined but do not include any internal content. These empty software compositions are called root software compositions and specify all provided and required ports, along with their communication attributes (e.g. data element reference, init value). ECU Extracts of this nature are being generated with the system category of SYSTEM\_EXTRACT [32].

The AUTOSAR XML schema is very detailed and has numerous constraints, therefore, manually creating ARXML files can be a cumbersome and error prone process, even for relatively simple ECU projects. Hence, the usage of a tool that might partially automate

the repetitive tasks and provides built-in consistency checks is generally preferred in ARXML generation.

For the creation of ECU Extracts, there are several well established tools in the automotive industry. Among these are the PREEvision -provided by Vector Informatik GmbH- [41] and ARTOP -accessible exclusively to ARXML partners- [42]. In addition, there are proprietary tools such as XDIS -a tool used by Daimler Truck AG and Mercedes-Benz AG- [43, 5]. These tools possess varying strengths and differ in their approaches to communication and software component design. However, a comparison of their advantages falls outside the scope of this thesis. While the tools mentioned represent some of the solutions, it should be noted that additional tools exist beyond those discussed in this thesis.

A legacy practice that sometimes being followed in the AUTOSAR ECU development process involves the usage of non-AUTOSAR exchange formats such as Database for CAN (DBC) files. However, relying on such formats limits the ability to fully leverage the capabilities and standardization benefits offered by AUTOSAR methodology.

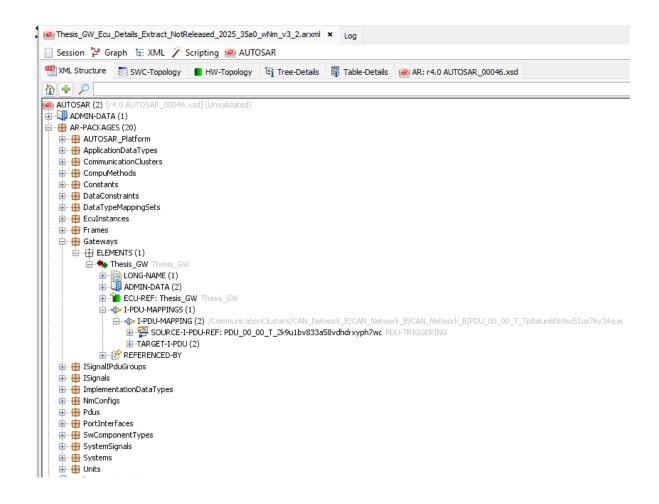

In this thesis, the ARXML files which will be used later in the implementation phase will be generated by the tool XDIS [43, 5].

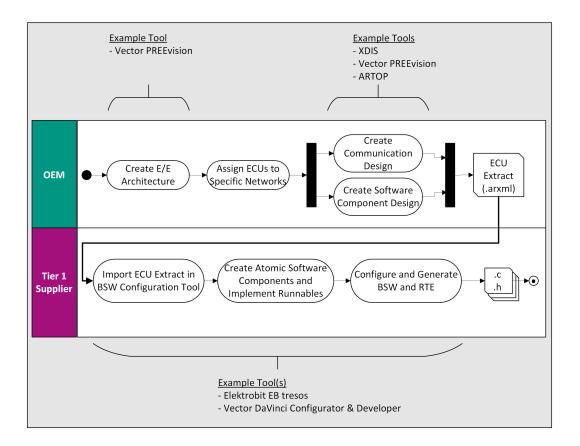

An exemplary development process of an AUTOSAR ECU in a collaboration with a Tier 1 supplier is being shown in the Figure 2.10. The tasks assigned to the OEM in this figure are outlined with the assumption that the process begins at the initial phase of the project, commonly referred to as ECU creation. However, in the automotive industry, most ECUs continue to receive updates even after the Start of Production (SOP). During such post-SOP update cycles, updating communication and software component is still necessary, but the first three tasks originally designated for the OEM at project initiation may no longer be required and can be omitted.

Figure 2.10: Development Process of an AUTOSAR ECU with a Tier 1 Supplier

#### 2.5.4 AUTOSAR Methodology from Tier 1 Supplier's Perspective

The AUTOSAR Basic Software (BSW) stack constitutes the real-time embedded software [44] that provides services to application software components [45]. It comprises a range of standardized modules, inter alia, Network Management (NM) module, diagnostic module, Operating System (OS) module, or End to End (E2E)-Protection module [46]. These BSW modules facilitate communication, timing, diagnostics, safety and many other fundamental functions for the ECU. Typically, the BSW stack is procured from a third-party stack provider such as Vector Informatik, Elektrobit, ETAS.

OEMs might follow different strategies regarding the procurement and provision of BSW stacks, at times these strategies may form a partnership with a BSW stack provider. In that case, the OEM may have licenses and rights to distribute BSW stacks to their Tier 1 suppliers. However, for the purposes of this thesis, scenarios are considered in which the Tier 1 supplier independently procures the BSW stack. In this context, the supplier selects an appropriate stack provider and chooses required BSW modules based on the specific requirement of the ECU project.

BSW stack providers usually offer dedicated BSW configuration toolchains along with their BSW stack. Consequently, the selection of the configuration tool is highly linked to the choosen BSW stack. Commonly used tools include Vector DaVinci Configurator [47] and Elektrobit EB Tresos [48], among others.

Following the delivery of the ECU Extract, the supplier imports it into BSW configuration tool. The tool automatically derives a significant portion of the BSW parameters from the ECU Extract directly such as, bus timings, frame lengths, among other parameters. However, some parameters, especially those dependent on the hardware or OS specific should be manually configured by the BSW integrator for instance baudrate prescaler, number of cores and OS tasks. Since ECU Extracts are mostly generated without having a prior knowledge about the hardware or the OS in this type of collaboration, these inputs should be given by the supplier.

As depicted in the Figure 2.10, the supplier will develop or integrate its own atomic software components to provide the intended ECU functionality. These atomic components may then be used to define one or multiple runnable entities [49] with their internal behaviors. These runnable entities are the functions which contain the real code implementation, i.e. C or Rust code. This software component development or integration can be carried out in tools like Vector DaVinci Developer or ETAS ASCET [47].

The modular approach regarding software component integration highlights one key advantage of AUTOSAR for Tier 1 suppliers. For instance, a Tier 1 supplier developing a steering angle sensor may deliver its solution to multiple OEMs with minimal modification to the application software component design, since the application software design is decoupled and independent from the hardware. In such cases, previously developed atomic software components can be reused across projects, eliminating the need to create them from scratch.

#### 2.5.5 AUTOSAR Layered Architecture

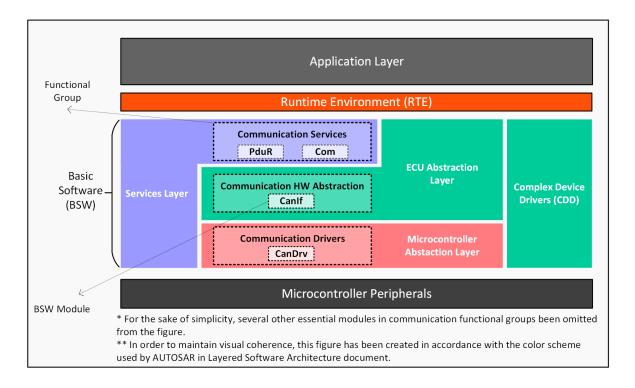

This subsection aims to summarize the AUTOSAR layered architecture and mostly refers to the AUTOSAR Layered Software Architecture document [36].

AUTOSAR Architecture is mainly being split into three software layers:

- 1. Application Layer

- 2. Runtime Environment (Rte)

- 3. BSW

The BSW is also further divided into four layers:

- Services Layer

- ECU Abstraction Layer

- Microcontoller Abstraction Layer (MCAL)

- Complex Device Driver (CDD)

Figure 2.11 illustrates layered architecture of AUTOSAR, with particular emphasis on the communication functional group.

Figure 2.11: AUTOSAR Layered Architecture [32]

CDD aims to implement enhanced services, protocols or maintains legacy functionality (e.g. Offene Systeme und deren Schnittstellen für die Elektronik in Kraftfahrzeugen (OSEK) NM) which are not standarized in AUTOSAR [36], therefore goes beyond the scope of this thesis. The remaining three layers are in detail divided into functional groups, which are further subdivided into modules, commonly referred to as BSW modules. The important functional group for this thesis would be related to communication:

- Communication Services

- Communication Hardware Abstraction

- Communication Drivers

In the subsection 2.5.6 a detailed explanation of the purpose of the relevant BSW modules and their interactions is provided.

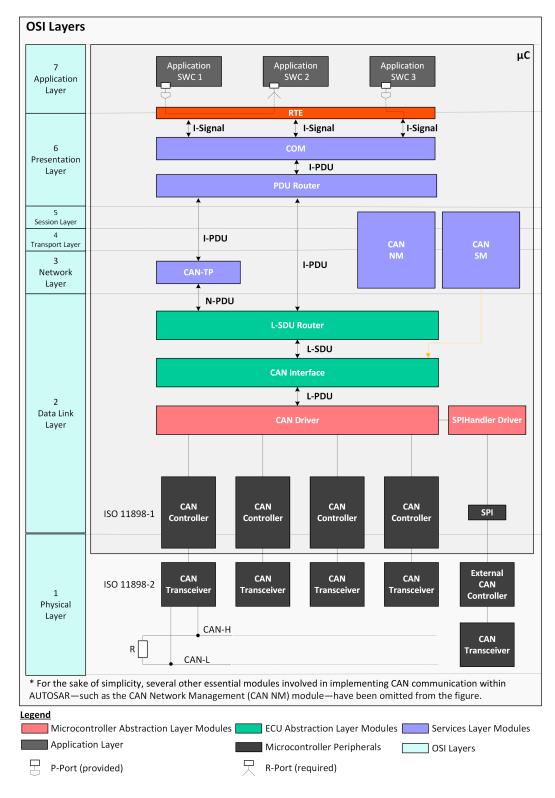

# 2.5.6 An Example of CAN Communication with AUTOSAR Layered Architecture

Although the layered architecture remains largely similar between AUTOSAR release versions 24-11 and earlier versions (<24-11), a notable addition in version 24-11 is the introduction of the L-SDU router.

The operational flow of AUTOSAR - from the application software layer to the point at which a CAN frame appears on the bus- is illustrated in Figures 2.12 and 2.6.

In this section, the working principles of AUTOSAR flow will be explained using an example, with reference to the AUTOSAR version 24-11 and the Figure 2.12.

In this subsection, the ECU under consideration corresponds to the configuration shown in the Figure 2.12: an ECU equipped with a microcontroller, five CAN controllers (four integrated and one external), and five CAN transceivers. As a scenario, the transmission of a CAN frame on the bus will be carried out using the leftmost CAN controller and its associated transceiver.

The interactions between AUTOSAR modules, as illustrated in Figure 2.12, are bidirectional.

In this scenario, it is assumed that Application Software Component (SWC) - 3 is responsible for processing the steering angle value obtained from a sensor. The development of the atomic software component corresponding to Application SWC-3, including its runnables and the logic for calculating the steering angle, falls under the responsibility of the Tier 1 as illustrated in the Figure 2.5.4 in Section 2.5.4.

According to our assumed collaboration model in this thesis, the communication signal, its associated data type, the PDU and CAN frame design along with other configuration details are provided by the OEM in the ECU Extract.

In the described scenario, it is assumed that the runnable of the steering angle sensor is a cyclic runnable executed every ten miliseconds. Similarly, the transmission trigger defined for the corresponding signal, PDU and CAN frame is set to 10 ms. This implies that the Application SWC-3 calculates and writes the signal value for steering angle using the Rte\_Write() Application Programming Interface (API) every 10 ms. Then, the AUTOSAR Rte handles the conversion from the application data type to the implementation data type and forwards the signal to the Communication (COM) Module.

The COM subsequently stores it in an internal buffer. Based on the defined I-SIGNAL-TO-I-PDU-MAPPING in the ECU Extract - consequently reflected in the module configuration - the COM maps the signal into the appropriate I-PDU. The COM then invokes the PduR\_ComTransmit() API to pass the I-PDU to the PDU Router (PduR).

The PduR is responsible for determining the destination modules for each I-PDU. In this case, it calls the LSduR\_Transmit() API to forward the I-PDU to the newly

introduced L-SDU Router module. The routing paths for both PDU and the L-SDU Router are statically defined in the configuration based on parameters derived from the ECU Extract.

The L-SDU Router converts the I-PDU into an L-PDU (refer to Figure 2.9) and subsequently calls the CanIf\_Transmit() API. The CAN Interface module then encapsulates the L-PDU into the appropriate CAN frame and invokes the Can\_Write() API to forward the L-PDU to the CAN Driver.

If the CAN hardware available, the CAN Driver copies data into the CAN hardware object and sets the transmit request flag within the CAN controller. The CAN transceiver then converts the digital data coming from the CAN controller into the physical signals, which are transmitted over the CAN bus via the CAN-H and CAN-L cables.

Figure 2.12: CAN Communication with Layered Architecture acc. to AUTOSAR 24-11 [32]

# 2.6 Gatewaying

This section aims to explain fundamentals of gatewaying in the context of automotive in-vehicle networks.

#### 2.6.1 Terminology: Gateway vs. Router

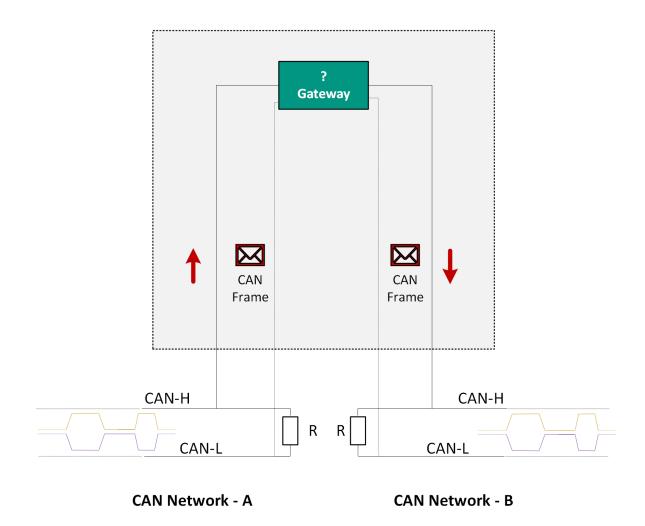

In principle, a gateway refers to a device that connects different network technologies (e.g. CAN to Automotive Ethernet) and performs protocol translation between them. In contrast, the term router typically denotes a device that forwards data between networks adopting the same communication protocol (e.g. Automotive Ethernet to Automotive Ethernet). [2]

However, in practice, both gatewaying and routing functionalities are often integrated together into a single unit [2], which commonly results into a Gateway ECU.

As outlined in Section 2.3, this thesis focuses on a single in-vehicle network communication protocol: CAN. From a theoretical standpoint, this would imply the use of the term router rather than a gateway, since no protocol translation is required between CAN networks. Nonetheless, the CAN protocol exists in multiple generations (refer to Section 2.3.2), and a Gateway ECU is expected to handle communication between these different CAN protocols. Therefore, even though the analyzed and proposed implementations in this thesis primarily forwards data between CAN networks, they will be referred to as a Gateway throughout this thesis.

#### 2.6.2 Gatewaying in AUTOSAR

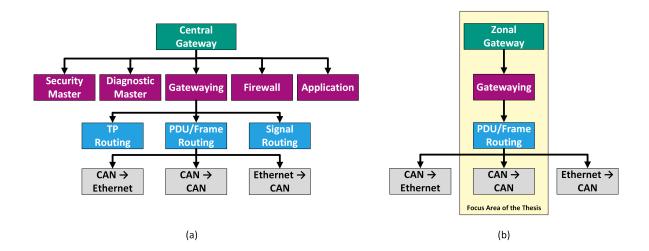

This section provides an overview of the gatewaying mechanisms within the AUTOSAR standard.

In today's vehicles, AUTOSAR is the predominant software architecture for ECUs, including Gateway ECUs with microcontroller based implementations [2].

The main gatewaying mechanism provided by AUTOSAR is known as the PDU based Gateway [32] which is within the PDU Router module of the AUTOSAR BSW [50, 51]. With PDU based Gateways, the payload stays intact but the PDU ID used in different communication interfaces are different. Different PDU IDs are required to ensure Tx Confirmation mechanisms in the AUTOSAR.

The Signal Gateway refers to an implementation in which routed signals inside a routed PDU (from source) can be placed into different PDUs in the destination. In AUTOSAR, such functionality can be achieved using AUTOSAR COM Module, as the PDU Router does not support this mechanism. As a result, configuring signal routings requires

additional effort during integration and introduces increased runtime load and latencies additional efforts during the runtime.

In this thesis, signal gatewaying mechanism are excluded from the conceptual work and implementation, as they constitute only a small percentage of overall routings in a vehicle, based on the research results given in the Chapter 4. Accordingly, throughout this thesis, the term AUTOSAR Gateway refers exclusively to the PDU based Gateway.

Figure 2.13: PDU Routing in AUTOSAR versions <24-11

Figure 2.13 illustrates the flow of a PDU routing for AUTOSAR versions prior to the release 24-11.

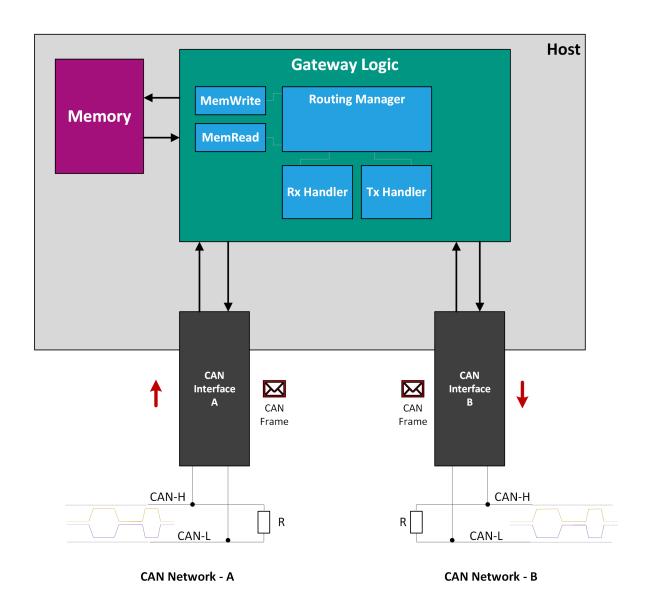

PDU Router Module is the highest level BSW module required in PDU Routings and consist of the PDU Router routing paths and the PDU Router Engine [50, 51].

The routing paths of PDUs, including both their source and destination, are defined statically [50, 51]. Consequently, I-PDUs are routed dynamically at the runtime.

The static routings configurations between communication interfaces of an ECU are usually specified in the ECU Extract by the OEM and can be derived into the PDU Router module upon importing the ECU Extract into the BSW Configuration tool. The ECU Extract and the Methodology has been discussed in the Subsection 2.5.3 in detail.

The PDU Router Engine is responsible for executing the actual routing from source to the destination. With the PDU Router, the data payload stays intact [50, 51].

As illustrated in the Figure 2.13, the PDU Router represents the highest level BSW Module in gatewaying, interfacing with lower level communication modules.

I-PDUs can be routed from a source communication multiple communication interfaces (1:n), such as CAN Interface (CanIf), Ethernet Interface (EthIf), LIN Interface (LinIf), FlexRayInterface. Although, the PDU Router supports gatewaying between different network technology interfaces, the focus of this thesis is the CAN Protocol. Therefore, in this thesis only the gatewaying between two CanIfs will be considered further.

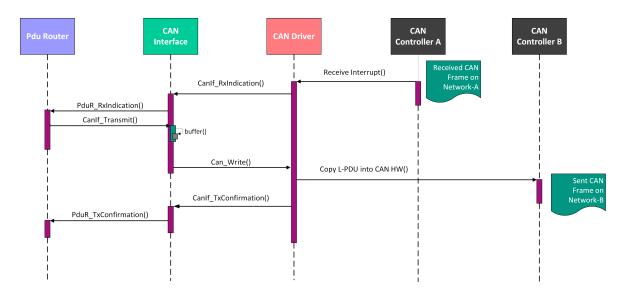

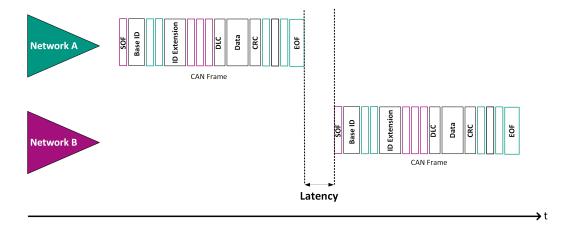

The sequence diagram of a PDU Routing between two CAN networks is given in the Figure 2.14.

Figure 2.14: Sequence Diagram of the Routing between CAN-Network-A and Network-B

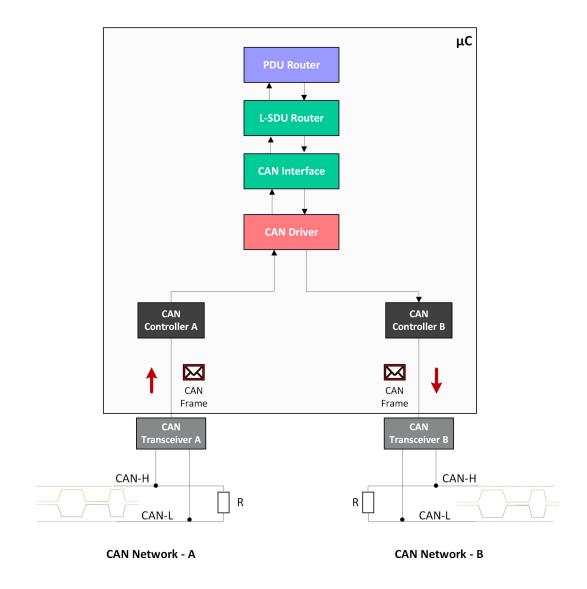

In the AUTOSAR release 24-11, the routing flow has been updated to include newly introduced L-SDU Router module. This revised routing flow is depicted in the Figure 2.15.

Figure 2.15: PDU Routing in AUTOSAR versions = 24-11

The L-SDU Router module was introduced in AUTOSAR release R24-11 [32] and has become the mandatory upper layer for all communication interfaces [52].

The main motivation behind introducing the L-SDU Router module is to enable Institute of Electrical and Electronics Engineers (IEEE) 1722 use cases across all communication interfaces, and facilitate data exchange from non-Ethernet communication interfaces to Ethernet based ones [52].

As the L-SDU Router module is an recent addition, there is currently no pbulished research on this topic, nor is the funtionality yet available as a BSW module from BSW vendors. Consequently, its impact on the standard PDU Routing remains subject to a further evaluation.

In this thesis, the L-SDU Router module is described and included in figures to illustrate the state-of-the-art AUTOSAR Layered Software Architecture. However, this module will not be used in the implementation of the AUTOSAR Gateway developed as part of this thesis.

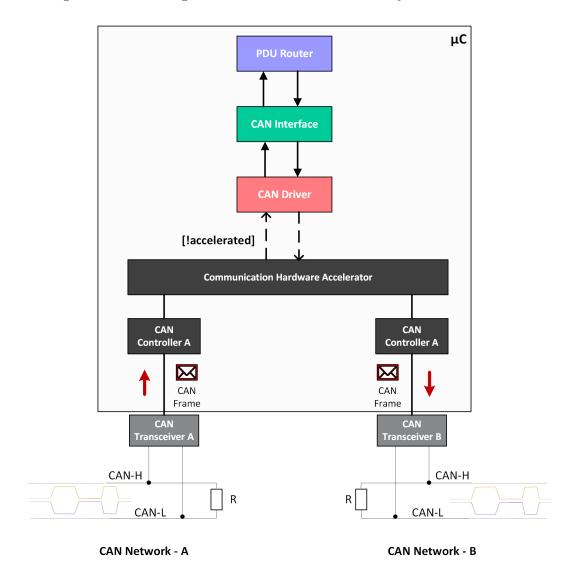

#### 2.6.3 Gatewaying with Hardware Acceleration

Recently, most silicon vendors have introduced communication hardware acceleration solutions for gatewaying [8, 9, 53, 54]. These solutions aim to offload the CPU by performing low level routing in hardware with a low latency.

Figure 2.16: Routing with Hardware Acceleration [9, 53]

Communication hardware acceleration solutions are proprietary and lack standardization [55, 9, 54]. The specific implementations and mechanisms used differ among hardware vendors. Nonetheless, as a common practice (similar to AUTOSAR PDU Router), these solutions retain statically defined routing configurations and do not support dynamic routing mechanisms.

As illustrated in the Figure 2.16, while internal mechanisms of communication hardware accelerators may vary, they generally process incoming CAN frames within their hardware itself. This approach reduces both CPU and interrupt load compared to the traditional AUTOSAR PDU Routing methodology. Frames are only forwarded to upper layers (CAN Driver) if they are not configured to be routed with hardware accelerators.

Due to the absence of the standardized hardware acceleration mechanisms, integrating AUTOSAR Classic Gateway solutions with proprieatry hardware acceleration from different vendors also remains a non-standardized practice. Despite these challanges, communication hardware accelerated Gateway solutions have demonstrated promising performance in proof-of-concept studies[54].

Given these promising results and the increasing availability of this feature in next generation microcontrollers and BSW Stacks, communication hardware acceleration solution may represent a viable approach for HPCs. However, they are generally considered costly, inflexible and complex in this thesis, making them less suitable for Zonal Gateways, which might face specific challenges as outlined in the Section 1.1.

This thesis explores an alternative hardware centric gateway architecture and does not consider existing communication hardware acceleration solutions in its scope.

## 2.7 CAN Bit Rate and Bus Timing

CAN is an asynchronous communication protocol that does not synchronize the clocks of the CAN Nodes on a network [56]. To achieve the desired bit rate and minimize the clock drift and its effects, each CAN node shall implement a bit timing logic as per ISO 11898-1 which synchronies all CAN Nodes [28, 27].

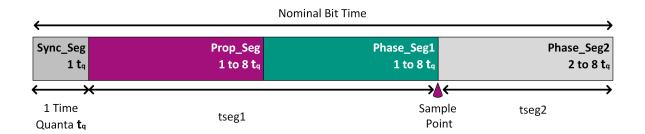

According to the ISO 11898-1 [28], the nominal bit time is divided into four different segments. In the Figure 2.17 these four segments are depicted.

Figure 2.17: CAN Bit Time Segments [28, 27, 57, 58]

The Sync\_Seg is the nominal start of each bit [57] synchronization segment which is used to synchronize the CAN Nodes [28]. The Prop\_Seg is the propagation time segment which is used to compensate for physical delay times which is consisting of the signal propagation time on the bus and internal delay time of CAN Nodes [28]. In other words, Prop\_Seg is being used to delay the earliest possible sample of the bit by a node until the transmitted bit values from all transmitting nodes have reached all of the nodes in order to keep the arbitration mechanism sage [57]. The Phase\_Seg1 and Phase\_Seg2 are buffer segments to compensate edge phase errors.

There are two different synchronization defined in the ISO 11898-1 [28]:

- 1. Hard Synchronization: It is performed only at the beginning of each CAN frame once every CAN Node aligns the Sync\_Seg of its current bit time to the recessive to dominant edge of the transmitted SOF bit.

- 2. Resynchronization: It is performed during the remainder of the CAN frame whenever a change of bit value from recessive to dominant occurs [57].

The time quantum or also called time quanta  $(t_q)$  is the fixed unit of time derived from the CAN node clock period. The CAN Node clock frequency  $(f_{\text{CAN}})$  is dependent on the CAN clock frequency  $(f_{\text{SystemCAN}})$  and Baudrate Prescaler (BRP) and can be calculated as the following:

$$f_{\text{CAN}} = \frac{f_{\text{SystemCAN}}}{BRP} \tag{2.1}$$

Also the equation 2.2 is being deduced from the Figure 2.17 which shows the total period for Nominal Bit Time (NBT).

$$t_{\text{NBT}} = t_{\text{Sync\_Seg}} + t_{\text{Prop\_Seg}} + t_{\text{Phase\_Seg1}} + t_{\text{Phase\_Seg2}}$$

(2.2)

As per the definition from the ISO 11898-1[28] the bit timings shall be calculating considering following constraints:

$$8 \le t_{\text{NBT}} \le 25 \tag{2.3}$$

$$1 \le BRP \le 32 \tag{2.4}$$

Some other constraints are coming from the ECU Extract due to OEM design and requirements and can be depicted as followings:

$$75\% \le \text{Sample Point} \le 81.25\% \tag{2.5}$$

$$10 \le t_{\text{NBT}} \le 20$$

(2.6)

In the CAN protocol, since no additional modulation is applied and each symbol corresponds directly to a single bit, the bit time and symbol time are effectively equivalent. As a result, the terms bit rate and baud rate can be used interchangeably. For consistency, the term bit rate will be used throughout this thesis, with the understanding that it also refers to the baud rate.

The chosen bit rate for the CAN bus implementation in this thesis is 500 kbit/s, as this value is commonly used not only in Classical CAN, but also serves as arbitration phase bit rate in other CAN generations. The system clock for classical CAN used in the CAN IPs is usually up to 24 MHz [59], and therefore this value will be taken as a reference. From these values and considering the equation 2.1 we can derive:

Bit Time =

$$\frac{1}{500 \,\text{kbit/s}} = 2 \,\mu\text{s} \tag{2.7}$$

$$t_{\rm q} = \frac{1}{f_{\rm CAN}} \tag{2.8}$$

$$t_{\rm NBT} = \frac{\rm Bit\ Time}{t_{\rm q}} \tag{2.9}$$

If we use the value found from the equation 2.7 with the equation 2.9 we can derive a new definition:

$$t_{\text{NBT}} = \frac{2\,\mu\text{s}}{\frac{1}{f_{\text{CAN}}}} = 2\,\mu\text{s} \times f_{\text{CAN}} \tag{2.10}$$

If we combine equation 2.10 and the constraint 2.6:

$$10 \le 2\,\mu\text{s} \times f_{\text{CAN}} \le 20\tag{2.11}$$

From the equation 2.11 we can derive a range for our CAN clock frequency ( $f_{\text{CAN}}$ ):

$$5 \,\mathrm{MHz} \le f_{\mathrm{CAN}} \le 10 \,\mathrm{MHz} \tag{2.12}$$

In this thesis, BRP has been chosen as 3 to comply with the constraint 2.12:

$$f_{\rm CAN} = \frac{24 \,\rm MHz}{3} = 8 \,\rm MHz$$

(2.13)

Based on this assumption and the equations 2.8 and 2.10 the  $t_{\mathrm{NBT}}$  can be calculated:

$$t_{\rm q} = \frac{1}{8MHz} = 125\,\rm ns \tag{2.14}$$

$$t_{\text{NBT}} = \frac{2\,\mu\text{s}}{125\,\text{ns}} = 16\,\text{Time Quanta} \tag{2.15}$$

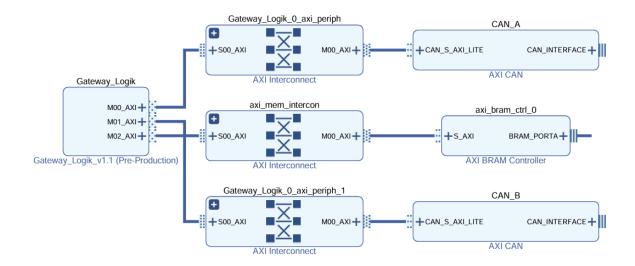

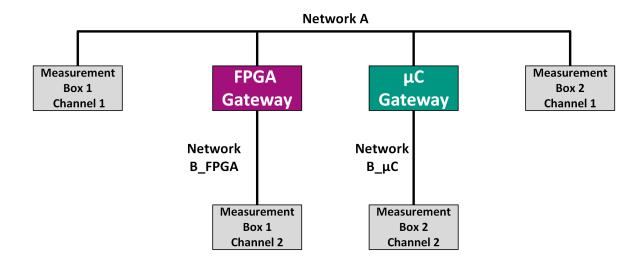

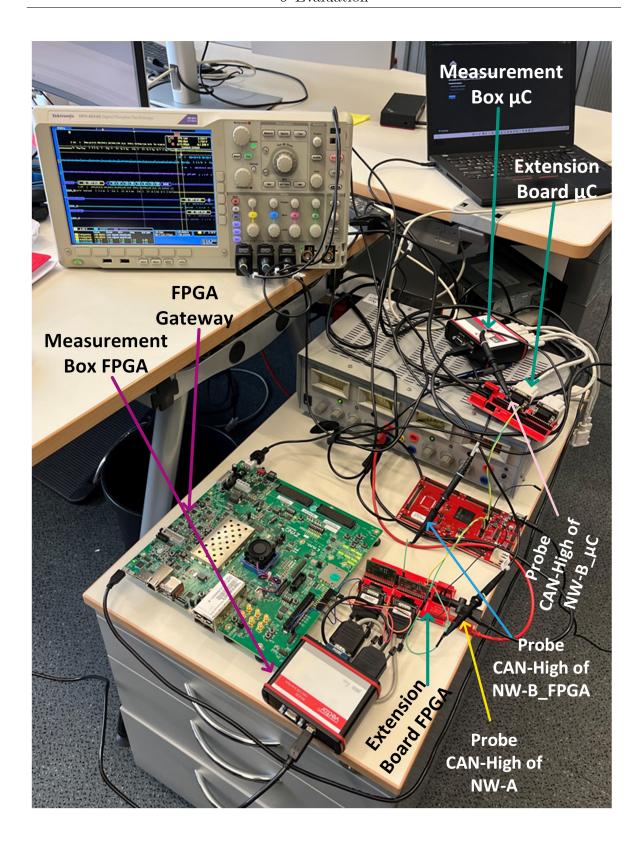

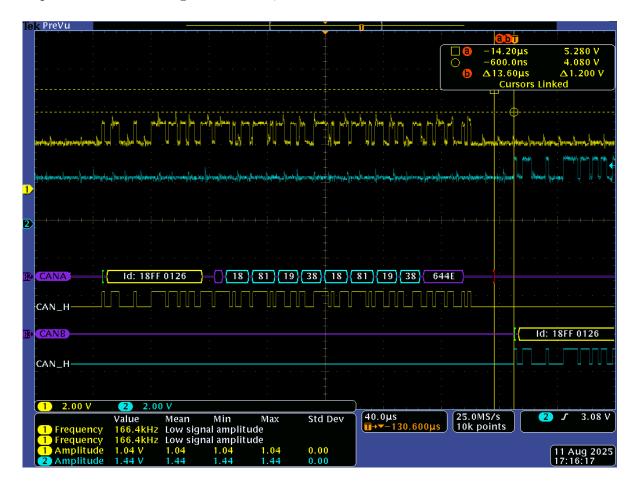

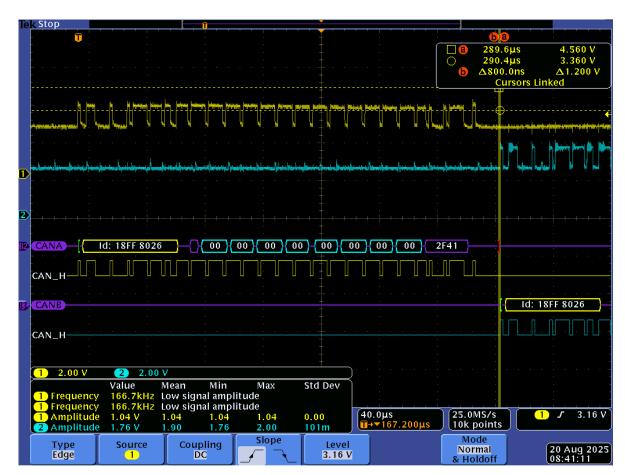

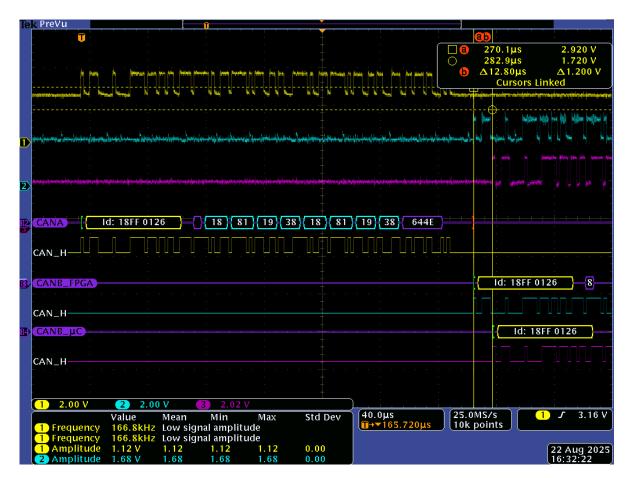

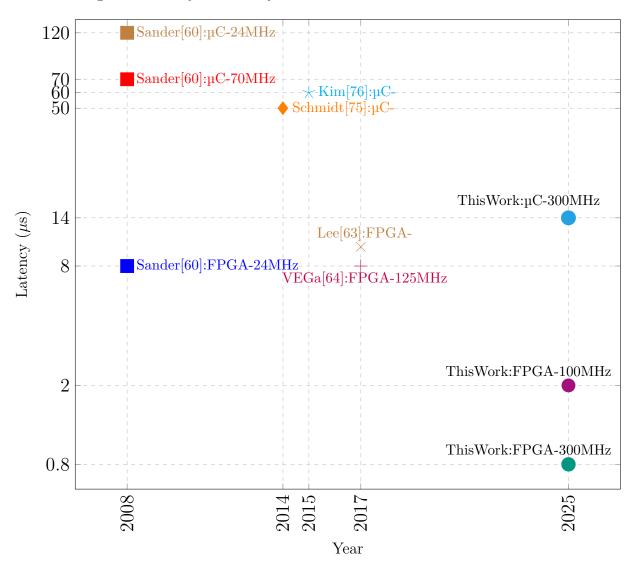

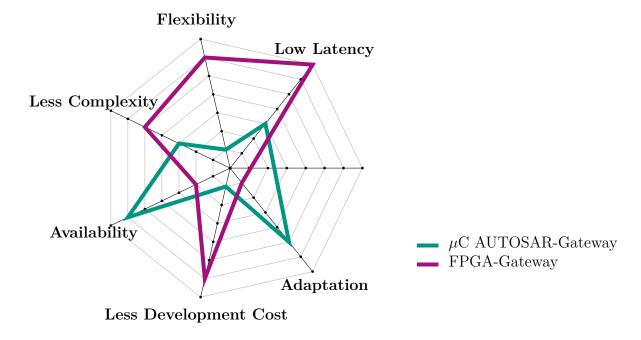

The  $t_{\rm NBT}$  value as 16 Time Quanta satisfies the constraint given in the 2.6.